**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

|                                                                                                                                                                                                                                      |                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| (51) Int. Cl. <sup>6</sup><br>G11C 16/00                                                                                                                                                                                             | (45) 공고일자 2000년03월02일<br>(11) 등록번호 10-0242683<br>(24) 등록일자 1999년11월11일 |

| (21) 출원번호 10-1992-0001713<br>(22) 출원일자 1992년02월06일                                                                                                                                                                                   | (65) 공개번호 특 1992-0017119<br>(43) 공개일자 1992년09월26일                      |

| (30) 우선권주장 651,817 1991년02월07일 미국(US)<br>(73) 특허권자 텍사스 인스트루먼츠 인코포레이티드 윌리엄 비. 캠플러<br>미국 텍사스주 75265 달拉斯 노스센트럴 익스프레스웨이 13500<br>(72) 발명자 존에프. 쉬렉<br>미합중국77096텍사스주휴스톤문라이트 10618<br>팻트시. 트렁<br>미합중국77083텍사스주휴스톤발비스타 15815<br>(74) 대리인 주성민 |                                                                        |

**심사관 : 이철희**

**(54) 집적회로메모리어레이용공통라인접속부**

**요약**

본 발명은 판독, 프로그래밍, 공급 전압 및 데이터 신호와 같은 신호들이 메모리 칩 상의 원격 위치로부터 발생되는 곳에서 판독 및 프로그래밍 기능을 수행하는데 필요한 큰 칩 영역을 감소시키기 위한 공통 접속부를 제공한다. 이 공통 접속부는 제어 회로(21)를 갖고 있는 집적 회로, 커럼 라인(17, 19)를 갖고 있는 다수의 메모리 셀 어레이, 감지 증폭기 회로 및 최소한 제1 및 제2 부분을 포함하는 프로그래밍 회로 A, B를 포함한다. 1개의 메모리 셀 어레이의 최소한 1개의 커럼(19)은 제어 회로로부터 최소한 제1 신호 Y0를 수신함과 동시에 공통 라인/노드 BL2에 선택적으로 접속된다. 프로그래밍 회로의 제1 부분 A는 제어 회로로부터 제2 신호 2P를 수신함과 동시에 공통 라인/노드에 선택적으로 접속된다. 프로그래밍 회로의 제2 부분 B는 제어 회로로부터 제3 신호 CEBOT를 수신함과 동시에 공통 라인/노드에 접속된다. 감지 증폭기 회로는 제어 회로로부터 제4 신호 SADEF를 수신함과 동시에 공통 라인/노드에 선택적으로 접속된다. 공통 라인/노드는 집적 회로 메모리의 제1 영역으로부터 집적 회로 메모리의 제2 영역으로 연장되는 도체이고, 제1 및 제2 영역은 예를 들어, 집적 회로 메모리의 대향 단부에 각각 배치된 프로그래밍 회로의 제1 및 제2 부분 A 및 B를 포함한다. 프로그래밍 회로의 제1 부분 A는 고전압 Vrw를 집적 회로 메모리의 소오스-커럼 라인(17)에 공급한다. 프로그래밍 회로의 제2 부분 B는 기준 전압 Vss 및 공급 전압 Vcc를 공통 라인/노드 BLZ에 공급한다.

**대표도**

**도1**

**명세서**

[발명의 명칭]

집적 회로 메모리 어레이용 공통 라인 접속부

[도면의 간단한 설명]

제1도는 4 메가비트 EPROM 어레이용 집적 회로 레이아웃을 도시한 도면.

제2도는 제1도의 집적 회로의 메모리 셀 어레이의 일부 및 이와 관련된 회로를 도시한 도면.

제3도는 종래 기술의 접속 회로의 개략도.

제4도는 본 발명의 접속부를 도시한 개략도.

\* 도면의 주요 부분에 대한 부호의 설명

10 : 셀

11 : 소오스

12 : 드레인

13 : 부동 게이트

14 : 제어 게이트

15 : 워드 라인

17, 19 : 커럼 라인

18 : 커럼 회로

21 : 판독/기입 제어 회로

### [발명의 상세한 설명]

본 발명은 전기적으로 프로그램 가능한 판독 전용 메모리(EPROM)를 포함하는 집적 회로 메모리 어레이에 관한 것으로, 이들 메모리의 개개의 셀들을 프로그램하고 판독하기 위한 세그먼트 어레이 및 분배 히로를 갖고 있는 집적 회로 메모리용 공통 라인 접속부에 관한 것이다.

특히, 본 발명은 집적 메모리 디바이스 내의 프로그래밍 논리 신호, 프로그래밍 전압, 데이터 신호 전송 및 감지 증폭기 바이어스 전압용 공통 경로를 제공하기 위한 접속부에 관한 것이다.

EPROM 어레이의 본 발명의 장치 및 방법이 사용될 수 있는 집적 회로의 한 예이다. EPROM 어레이의 로우(row) 및 컬럼(column)으로 배열된 부동 게이트 메모리 셀을 포함하고 있다. 프로그램 메모리 셀의 부동 게이트는 전자로 충전되고 선택된 로우 라인 선택 전압이 제어 게이트에 인가되는 경우에 차례로 전자는 충전부동 게이트 하의 소오스 드레인 경로를 비도전성이 되게 한다. 이 비도전성 상태는 '0' 비트로서 판독된다. 비프로그램 셀의 부동 게이트는 동일하게 선택된 로우라인 선택 전압이 제어 게이트에 인가되는 경우에 비프로그램 부동 게이트 하의 소오스-드레인 경로가 도전성이 되도록 증성으로 충전된다. 이 도전 상태는 '1' 비트로서 판독된다.

EPROM 어레이의 각각의 컬럼 및 로우는 수 천개의 셀을 포함할 수 있다. 컬럼 내의 각 셀의 소오스는 가상 접지 라인(소오스-컬럼 라인)에 접속된다. 컬럼내의 각 셀의 드레인은 분리 비트 라인(드레인-컬럼 라인)에 접속된다. 열 내의 각 셀의 제어 게이트는 워드 라인에 접속된다.

프로그램 가능한 메모리는 일반적으로 공통 노드에서 결합하는 판독 회로 및 프로그램 회로를 갖고 있는데, 이 경우에 소정의 디바이스를 공유한다. 본 명세서에 사용된 용어 '판독 회로'는 메모리 셀의 상태를 결정하기 위해 실행되는 구성 부품과 관련되어 있다. 본 명세서에 사용된 용어 '프로그램 회로'는 메모리 셀의 상태를 프로그램하거나 변경하는 구성 부품과 관련되어 있다. 판독 및 프로그램 회로 모두에 사용되는 트랜지스터 및 상호 접속부의 한 예는 EPROM 내의 컬럼을 선택하도록 사용되는 디코딩 회로이다.

종래 기술의 회로는 디코더로부터의 신호에 응답하여 프로그램 또는 판독될 컬럼을 선택하는 스위칭 트랜지스터를 포함하고 있다. 이러한 종래 기술의 회로에서, 프로그램은 인에이블 입력 신호는 어느 회로의 블럭, 프로그램 회로 또는 판독회로가 활성화될지를 결정한다. 2개의 회로 블럭은 컬럼에 판독 회로를 접속하거나 컬럼 상에 프로그래밍 전위를 강요시키는 기능을 갖는 공통 노드에 의해 결합된다.

특히 판독 및 프로그래밍 회로에 대한 신호가 칩 상의 원격 위치에 분포되는 판독 및 프로그래밍 기능을 수행하기 위해 칩 영역을 감소할 필요가 있다.

본 발명의 회로는 공통 라인/노드 접속부를 사용함으로써 판독 및 프로그래밍 기능을 수행하는데 요구되는 총 칩 영역을 감소시킨다. 판독, 프로그래밍, 공급전압 및 데이터 신호가 메모리 칩 상의 원거리 위치로부터 발생되는 경우에, 요구 영역의 감소는 칩의 한 부분으로부터 다른 부분으로 이 신호들을 전송하도록 신호 라인 또는 노드를 사용함으로써 달성된다.

공통 접속부는 전기적으로 프로그램 가능한 판독 전용 메모리, 제어 회로를 갖고 있는 메모리, 컬럼 라인을 갖고 있는 다수의 메모리 셀 어레이, 및 최소한 제1 및 제2 부분을 포함하는 프로그래밍 회로와 관련하여 기술되어 있다. 1개의 메모리 어레이의 최소한 1개의 컬럼은 제어 회로로부터 최소한 제1 신호를 수신함과 동시에 공통 라인/노드에 선택적으로 접속된다. 프로그래밍 회로의 제1 부분은 제어 회로로부터 제2 신호를 수신함과 동시에 공통 라인/노드에 선택적으로 접속된다. 프로그래밍 회로의 제2 부분은 제어 히로로부터 제2 신호를 수신함과 동시에 공통 라인/노드에 접속된다. 감지 증폭기 회로는 제어 회로로부터 제4 신호를 수신함과 동시에 공통 라인/노드에 선택적으로 접속된다. 공통 라인/노드는 집적 회로 메모리의 제1 영역으로부터 집적 회로 메모리의 제2 영역으로 연장되는 도체일 수 있고, 상기 제1 및 제2 영역은, 예를 들어 집적 회로 메모리의 대향 단부에 각각 배치된 프로그래밍 회로의 제1 및 제2 부분을 포함한다. 프로그래밍 회로의 제1 부분은 집적 회로 메모리의 소오스 컬럼 라인에 높은 전압을 제공한다. 프로그래밍 회로의 제2 부분은 공통 라인/노드에 기준 전위 및 공급 전압을 제공할 수 있다.

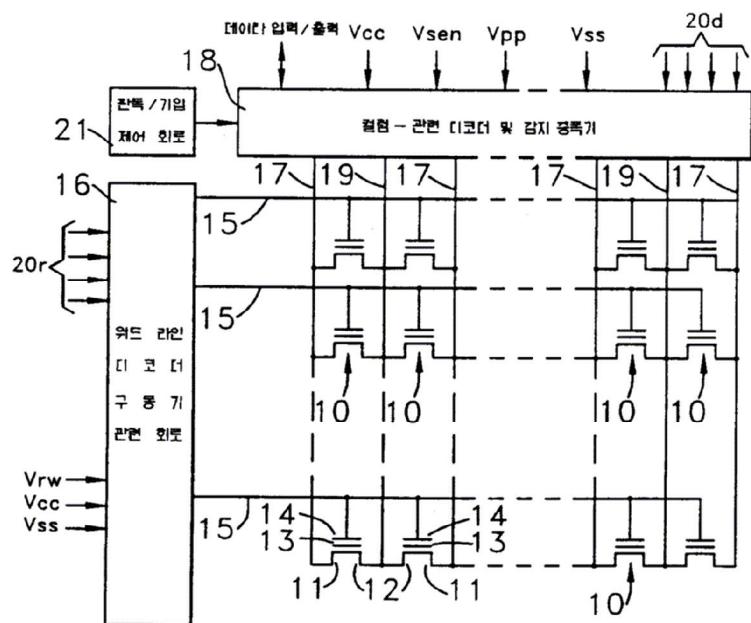

제1도를 참조하면, 공칭 4 메가비트 EPROM용 집적 회로의 한 예가 도시되어 있다. 제조시의 실제 크기가 아닌것을 나타내는 레이아웃은 고장 셀을 갖고 있는 로우 및 컬럼을 교체하도록 사용된 용장 로우 및 컬럼을 갖는 16개의  $512 \times 512$  메모리 서브어레이를 도시하고 있다. 워드 디코더, 컬럼 디코더, 가상 접지 디코더, 워드 라인 구동기 및 컬럼/세그먼트 통과 게이트를 포함하는 주변 회로는 전자 디코더 및 프로그램 경로를 통해 루트되는 어드레스 입력에 응답하여 셀의 로우 및 컬럼에 판독 및 프로그래밍 전압을 접속하도록 동작한다. 데이터는 프로그래밍 동작중에 메모리 어레이 내에 기입된다. 판독 동작 중에, 메모리 어레이로부터의 데이터가 감지 증폭기를 통해 출력으로 루트된다.

제2도를 참조하면, 제1도에 도시된 바와 같은 메모리 칩의 일부인 메모리 셀의 예시적인 어레이가 도시되어 있다. 각 셀은 소오스(11), 드레인(12), 부동 게이트(13) 및 제어 게이트(14)를 갖고 있는 부동 게이트 트랜지스터(10)이다. 셀(10)의 로우 내의 각각의 제어 게이트(14)는 워드 라인(15)[또는 로우 라인(15)]에 접속되고, 각각의 워드 라인(15)은 워드 라인 디코더, 구동기 및 관련 회로를 포함하는 워드 라인 히로(16)에 접속된다. 셀(10)의 컬럼 내의 각각의 소오스(11)은 소오스 컬럼 라인(17; 가상 접지 라인일 수 있음)에 접속되고, 각각의 소오스 컬럼 라인(17)은 컬럼/세그먼트 디코더, 가상 접지 디코더 및 컬럼/세그먼트 통과 게이트를 포함하는 컬럼 회로(18)에 접속된다. 셀(10)의 컬럼 내의 각각의 드레인(12)는 드레인 컬럼 라인(19)에 접속되고 각각의 드레인 컬럼 라인(19)은 컬럼 회로(18)에 접속된다.

기입 또는 프로그램 모드에서, 워드 라인 회로(16)은 선택된 제어 게이트 도체(14)를 포함하는 선택된 워드 라인(15) 상에 미리 선택된 제1 프로그래밍 전압  $V_{pp}$ (약 +12.5V)를 인가하기 위해 라인(20r) 상의 워드 라인 어드레스 신호 및 판독/기입 제어 회로(21)[또는 마이크로프로세서(21)]로부터의 신호에 응답하여 동작할 수 있다. 컬럼 회로(18)은 또한 선택된 소오스 컬럼 라인(17) 및 선택 셀(10)의 소오스(11)

상에 제2 프로그래밍 전압  $V_{rw}$ ( $V_{pp}$ 는 임피던스를 통해 약 +5V 내지 +10V로 감소됨)를 인가하도록 동작한다. 선택 드레인 컬럼 라인(19)은 기준 전위  $V_{ss}$ 에 접속된다. 비선택 소오스 컬럼 라인(17) 및 비선택 드레인 컬럼 라인(19)은 부동이다. 이 프로그래밍 전압은 선택 메모리 셀(10)의 채널 내에 높은 전류 조건[드레인(12)에서 소오스(11)로]을 발생시켜 드레인 채널 접합부에 채널 산화물을 통하여 선택 셀(10)의 부동 게이트(13)으로 주입되는 채널 열 전자 및 전자사태 항복 전자를 발생시킨다. 프로그래밍 시간은 채널 영역에 대하여 약 -2V 내지 -6V의 부(-) 프로그램 전하를 갖는 부동 게이트(13)을 프로그램시키기에 충분히 긴 시간이 되도록 선택된다. 이 주입 전자 및 부전압은 부동 게이트(13) 하의 소오스-드레인 경로를 '0'비트로 판독되는 비도전 상태로 만든다. 비선택 셀(10)은 도전성을 유지하는 부동 게이트(13) 하의 소오스-드레인 경로를 갖고, 이 셀(10)은 '1'비트로 판독된다.

셀은 예를 들어 자외 방사선으로 소거될 수 있다.

판독 모드에서, 워드 라인 회로(16)은, 라인(20r)의 워드 라인 어드레스 신호 및 판독/기입 제어 회로(21)로부터의 신호에 응답하여, 선택 워드 라인(15)[및 선택 제어 게이트(14)]에 미리 선택된 정 전압  $V_{cc}$ (약 +3 내지 +5V)를, 및 비선택 워드 라인(15)에 낮은 전압(그라운드 또는  $V_{ss}$ )을 인가시키도록 동작한다. 컬럼 회로(18)은, 라인(20d)의 컬럼 어드레스 신호에 응답하여, 감지 증폭기가 선택 드레인 컬럼 라인(19)에 이미 선택된 정 전압  $V_{sen}$ (약 +1 내지 +1.5V)을 공급하도록 동작한다. 컬럼 회로(18)은 또한 판독되는 셀(10)에 접속되는 동일한 드레인 컬럼 라인을 공유하는 소오스 컬럼 라인(17)을 제외하고 그라운드(또는  $V_{ss}$ )에 모든 소오스 컬럼 라인(17)을 접속시키도록 동작한다. 이 소오스 컬럼 라인(17)은 선택 드레인 컬럼 라인과 동일한 전압 레벨로 구동된다. 선택 드레인 컬럼 라인(19)에 접속되고 선택 워드 라인(15)는 데이터 출력 단자에 접속된 셀(10)의 도전 또는 비도전 상태는 감지 증폭기에 의해 검출된다.

공지된 바와 같이, 메모리 셀(10)의 소오스(11) 영역 및 드레인(12) 영역은 여러가지 모드의 동작을 위해 서로 바뀔 수 있다. 상기 판독 예에서 소오스(11) 및 드레인(12) 영역에 인가되는 전압은 서로 바뀔 수 있다. 그려므로, 본 명세서에 사용된 '소오스' 및 '드레인'이 서로 바뀔 수 있다.

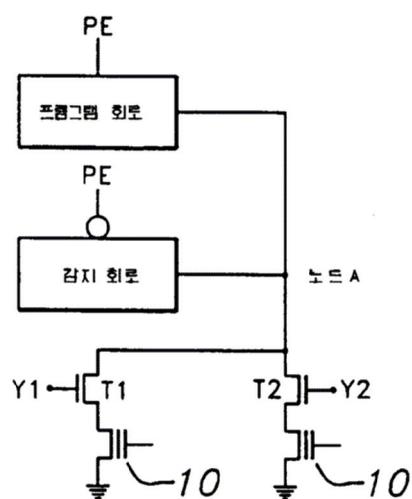

제3도를 참조하면, 종래 기술의 회로의 예가 도시되어 있다. 트랜지스터(T1 및 T2)는 디코더 신호  $Y_1$  및  $Y_2$ 에 응답하여 프로그램 또는 판독하도록 셀(10)의 컬럼을 선택한다. 프로그램 인에이블 입력 신호  $PE$ 는 어느 회로 블럭, 프로그램 또는 판독 회로가 활성화 될지를 결정한다. 2개의 회로 블러과 결합하는 노드 A의 동작은 두 동작을 제한된다. 이 두 동작은 셀(10)의 컬럼에 판독 회로를 접속시키거나 셀(10)의 컬럼 상에 프로그래밍 전위를 인가시킨다. 표준 EPROM에 있어서, 셀(10)의 드레인(12)에 접속되는 어레이의 드레인 컬럼 라인(19)에 높은 전압이 인가된다. 가상 접지 EPROM에 있어서, 메모리 셀의 다른 확산 영역에 높은 전압이 인가되는 경우에 프로그래밍 전위는 기준 전위  $V_{ss}$ 이다. 플래쉬 EPROM은 동일한 프로그래밍 전압을 사용할 수 있거나, 높은 전압 또는 기준 전위  $V_{ss}$  이외의 소거 및/또는 프로그래밍 전위 값을 갖는 프로그래밍 전압을 사용할 수 있다.

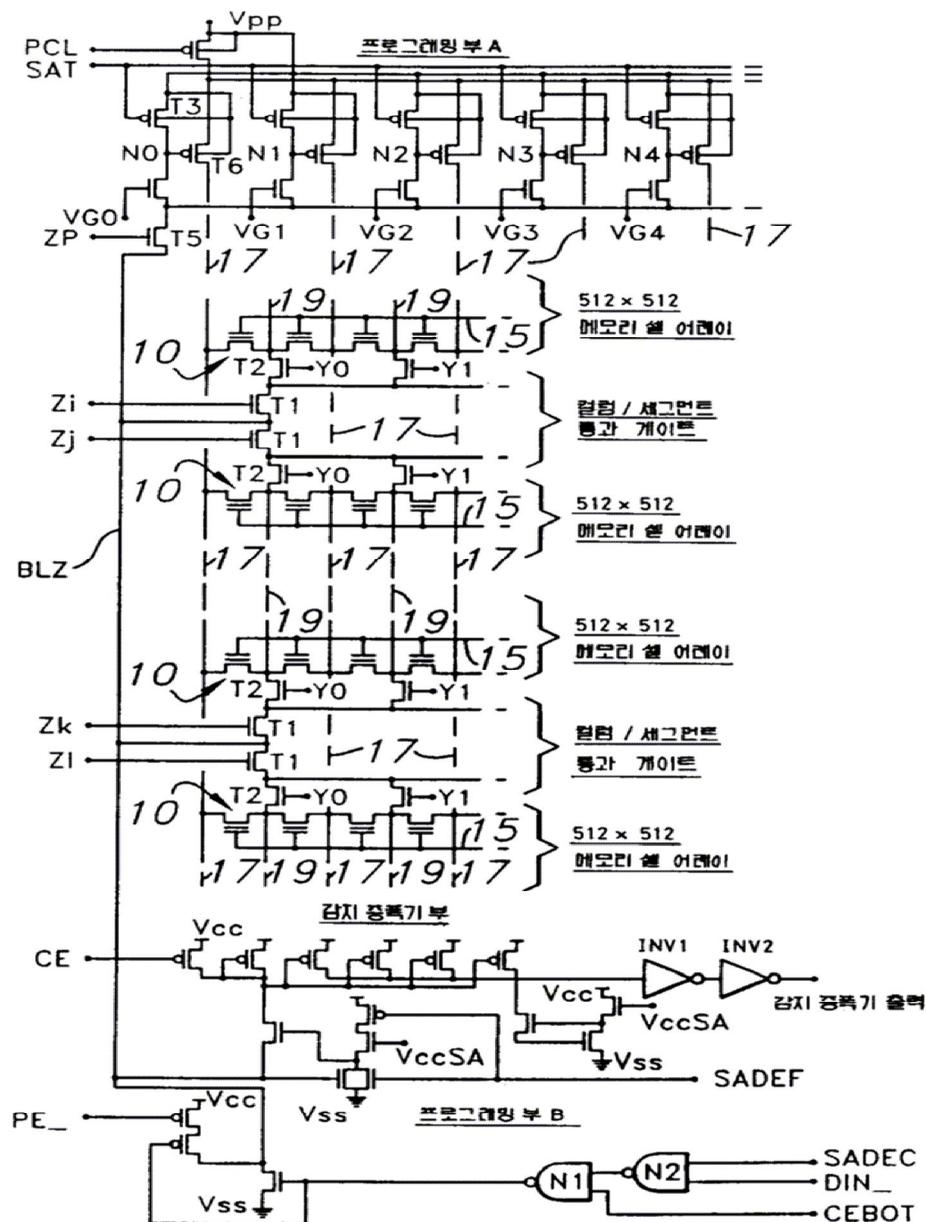

이제 제4도를 참조하면, 제3도의 노드 A는 프로그래밍용 경로, 판독 동작 바이어스 전압용 경로, 및 판독 신호 데이터용 경로로서 분리된 프로그래밍 회로 사이에 논리 신호용 경로를 제공하도록 연장된다. 제4도에서 공통 신호 라인  $BLZ$ 는 제3도의 노드 A에 대응한다. 이 공통 신호 라인  $BLZ$ 는 프로그래밍 동작 중에 프로그래밍부 A 와 프로그래밍부 B 사이의 논리 신호 경로로 제공되고, 프로그래밍 동작 중에  $V_{ss}$  용 경로로 제공되며, 판독 동작 중에 감지 증폭기로부터의 바이어스 전압  $V_{sen}$  인가용 경로로 제공되고 판독 동작 중에 512x512 메모리 셀 어레이로부터 감지 증폭기에 도달하도록 데이터용 경로로 제공된다.

제4도의 예시적인 회로에서, 제1도의 예에서와 같이 프로그래밍부 A 회로는 칩의 상부에 배치되어 있다. 또한 제1도에 도시된 바와 같이 감지 증폭기 회로 및 프로그래밍부 B 회로가 칩의 하부에 배치되어 있다. 제1도의 예에서와 같이, 512x512 메모리 셀 어레이는 메모리 칩을 통해 분포된다. 디코드된 신호에 응답하여 기준 전위  $V_{ss}$ 에 개별적인 연속 소오스 컬럼 라인(17)을 접속시키는 트랜지스터는 도시되어 있지 않다. 또한, 다른 디코드된 신호에 응답하여 바이어스 발생기에 연속 소오스 컬럼 라인(17)을 접속시키는 트랜지스터도 도시되어 있지 않다.

판독 모드 동작 중에, 프로그래밍부 A 회로 및 프로그래밍부 B 회로는 Z-디코드 신호  $ZP$ ,  $VGP(VG0$  이하 참조),  $DIN_{-}$ , 및  $PE_{-}$  신호에 의해 비활성화된다. 프로그래밍 모드 동작 중에, 감지 증폭기부는 감지 증폭기 방해 신호  $SADEF$ 에 의해 턴 오프되지만 프로그래밍부 A 및 프로그래밍 B는 활성화된다.

프로그래밍부 A 회로를 참조하면,  $POL$  신호는 허용 레벨로 프로그래밍 전류를 제한한다.  $SAT$  신호는 P 채널 로드 디바이스가 낮은 전류에서 동작하도록 P 채널 로드 디바이스(T3)의 저항을 제어한다. Z-디코드 신호  $ZP$  및 가상 접지 신호  $VGP(VG0, VG1$  이하 참조)는 프로그래밍 모드에서만 활성화되는 디코딩 신호이다.

프로그래밍부 B 회로를 참조하면, 반전 프로그램 인에이블 신호  $PE_{-}$ 는 프로그래밍 모드의 동작 중에로 ( $!low$ )이고, 칩 인에이블 하부 신호  $CEBOT$ 는 칩이 활성화되는 경우에 하이( $high$ )이며, 감지 증폭기 디코드 신호  $SADEC$ 는 디코드 신호이고, 로 데이터 인 신호  $DIN_{-}$ 는 프로그래밍 데이터가 '0'인 경우 하이이고 프로그래밍 데이터가 '1'인 경우에 로이다.

프로그래밍 모드 동작 중에, 라인  $BLZ$ 는 로 데이터 인 신호  $DIN_{-}$ 이 로( $!low$ )로 됨(데이터 '1'이 프로그램 됨)에 응답하여 공급 전압  $V_{cc}$ 로 구동된다. 예를 들어, 좌측 소오스 컬럼 라인(17)이 프로그래밍( $VG0=ZP=V_{cc}$ )을 위해 선택되는 경우에, 노드 N0은 트랜지스터 T3에 의해 프로그래밍 전압  $V_{pp}$ 로 풀(pull)된다. 이것은 트랜지스터 T4 및 T5가 비도전성이고, 트랜지스터의 게이트에는 전위  $V_{cc}$ 가 걸리며 이 트랜지스터의 소오스에  $V_{cc}$  이상의 전위가 걸리기 때문에 발생한다. 라인  $BLZ$ 가 로 데이터 인 신호  $DIN_{-}$  하이로 됨(데이터 '0'이 프로그램됨)에 응답하여 그라운드로 구동되는 경우에, 노드 N0은 트랜지스터 T3이  $SAT$  신호를 통해 저항성 상태로 배치되기 때문에 로 신호로 풀된다. 노드 N0이 로인 경우에, 트랜지스터 T6은 좌측 소오스 컬럼 라인(17)로 프로그래밍 전압  $V_{rw}$ 를 공급한다. 또한, 로인 경우에 라인  $BLZ$ 는 선택된 Y 및 Z 신호에 의해 활성화되는 트랜지스터 T1 및 T2를 통해 프로그래밍 중에 선택

비트용으로 그라운드 경로를 제공한다.

그러므로, 프로그래밍 모드 동작 중에, 단일 도체 BLZ는 제4도의 메모리 회로의 하부에 있는 프로그래밍부 B 회로로부터 상기 메모리 회로의 상부에 있는 프로그래밍부 A로 '프로그램' 또는 '프로그램 없음' 명령을 전송하도록 이용된다. 부수적으로, 단일 도체는 프로그램될 선택 512x512 어레이 세그먼트용으로 그라운드를 제공한다. VGO(이하 참조) 정보를 제공하는 다중 도체 버스는 상부 프로그래밍부 A 회로에만 접속되고 프로그래밍부 B 회로 또는 개개의 512x512 어레이 세그먼트에 접속되지 않는 것이 필요하다. '1'이 프로그램되는 경우에, 공급 전압 Vcc는 라인 BLZ가 Vcc로 구동되기 때문에 어레이 내로 인가된다. 그러나, 대부분의 응용시에 전압 Vcc는 과도 스트레스를 발생하는 레벨 이하이다.

판독 모드 동작 중에, 공통 신호 라인 BLZ는 어레이로부터, 판독될 컬럼에 바이어스 전압을 제공하고 특정 셀이 데이터 '0' 또는 데이터 '1'로 프로그램되어 있는지의 여부를 감지하며 감지 증폭기 출력 단자에 데이터를 제공하는 감지 증폭기에게 데이터를 전송한다. 감지 증폭기로서 제4도에 도시된 감지 증폭기 회로는 공통 노드 또는 라인 BLZ를 사용하여 메모리 칩 내에 사용될 수 있는 감지 증폭기의 한 예만을 도시하였다. 제4도의 입력 단자(VccSA)는 기준 전압 전력이다.

요약하면, 본 명세서에 기술된 공통 접속부는 판독 및 프로그래밍 기능을 실행하는데 필요한 총 칩 영역을 감소시키는데, 특히 판독, 프로그래밍, 공급 전압 및 데이터 신호와 같은 신호들이 메모리 칩 상의 원격 위치로부터 발생될 때 칩 영역을 감소시킨다. 공통 접속부는 제어 회로(21)를 갖고 있는 집적 회로 메모리, 컬럼 라인(17 및 19)를 갖고 있는 다수의 메모리 셀 어레이, 감지 증폭기부 회로, 및 제1 프로그래밍부 A 회로와 제2 프로그래밍부 B 회로를 포함하는 프로그래밍 회로에 대해 기술되어 있다. 1개의 메모리 셀 어레이의 최소한 1개의 컬럼 라인(19)가 신호 Y0(이하 참조) 및 Zi(이하 참조)의 수신과 동시에 공통 컬럼 라인/노드 BLZ에 선택적으로 접속된다. 프로그래밍 회로의 프로그래밍부 A 회로는 제어 회로(21)로부터 신호 Zp의 수신과 동시에 공통 라인/노드 BLZ에 선택적으로 접속된다. 프로그래밍 회로의 프로그래밍부 B 회로는 제어 회로(21)로부터 신호 CEBOT, SADEC 및 PE\_의 수신과 동시에 공통 라인/노드 BLZ에 선택적으로 접속된다. 감지 증폭기부 회로는 제어 회로(21)로부터 (로 인) 신호 SADEF의 수신과 동시에 공통 라인/노드 BLZ에 선택적으로 접속된다. 공통 라인/노드 BLZ는 집적 회로 메모리의 제1 영역으로부터 집적 회로의 제2 영역으로 연장되는 도체일 수 있는데, 상기 제1 및 제2 영역은 예를들어 집적 회로 칩의 대형 단부에 각각 배치된 프로그래밍 회로의 프로그래밍부 A 및 프로그래밍부 B를 포함한다. 프로그래밍 회로의 프로그래밍부 A는 집적 회로 메모리의 소오스 컬럼 라인(17)에 높은 전압 Vrw를 제공할 수 있다. 프로그래밍 회로의 프로그래밍부 B는 특정 메모리 셀(10)이 프로그램될지의 여부에 따라 공통 라인/노드 BLZ에 기준 전위 Vss 및 공급 전압 Vcc를 제공할 수 있다.

본 발명이 예시적인 실시예에 대해 기술되었지만, 본 설명으로 한정하려는 것은 아니다. 본 분야에 속련된 기술자들은 본 발명을 참조하여 본 발명을 여러가지로 변형하여 다르게 실시할 수 있다. 첨부된 특허 청구의 범위는 본 발명의 범위내에서 이러한 변형 및 실시를 커버할 수 있다.

## (57) 청구의 범위

### 청구항 1

제어 회로, 컬럼 라인을 갖고 있는 최소한 1개의 메모리 셀 어레이, 및 최소한 제1 및 제2 부분을 포함하는 프로그래밍 회로를 갖고 있는 집적 회로 메모리용 공통 접속부에 있어서,

상기 제어 회로로부터 최소한 제1 신호를 수신함과 동시에 공통 도체에 선택적으로 접속되는 최소한 1개의 메모리 어레이의 최소한 1개의 컬럼을 포함하고,

상기 프로그래밍 회로의 상기 제1 부분은 상기 제어 회로로부터 최소한 제2 신호를 수신함과 도시에 상기 공통 도체에 선택적으로 접속되고,

상기 프로그래밍 회로의 상기 제2 부분은 상기 제어 회로로부터 최소한 제3 신호를 수신함과 동시에 상기 공통 도체에 선택적으로 접속되는

을 포함하는 것을 특징으로 하는 공통 접속부.

### 청구항 2

제1항에 있어서, 상기 공통 도체가 상기 집적 회로 메모리의 제1 영역으로부터 상기 집적 회로 메모리의 제2 영역으로 연장되는 것을 특징으로 하는 공통 접속부.

### 청구항 3

제1항에 있어서, 상기 공통 도체가 회로 노드인 것을 특징으로 하는 공통 접속부.

### 청구항 4

제1항에 있어서, 상기 제어 회로로부터 최소한 제4 신호를 수신함과 동시에 상기 공통 도체에 선택적으로 접속되는 감지 증폭기 회로(sense amplifier circuit)를 포함하는 것을 특징으로 하는 공통 접속부.

### 청구항 5

제1항에 있어서, 상기 프로그래밍 회로의 상기 제1 및 제2 부분이 상기 집적 회로 메모리의 대형 단부에 배치되는 것을 특징으로 하는 공통 접속부.

### 청구항 6

제1항에 있어서, 상기 프로그래밍 회로의 상기 제1 부분이 상기 집적 회로 메모리의 소오스-컬럼 라인에

높은 전압을 제공하는 것을 특징으로 하는 공통 접속부.

#### 청구항 7

제1항에 있어서, 상기 프로그래밍 회로의 상기 제2 부분이 상기 공통 도체에 기준 전위 및 공급 전압을 제공하는 것을 특징으로 하는 공통 접속부.

#### 청구항 8

제1항에 있어서, 상기 접속 회로 메모리가 EEPROM(electrically-programmable read-only memory)인 것을 특징으로 한느 공통 접속부.

#### 청구항 9

제1항에 있어서, 상기 메모리 셀 어레이들 중 1개의 메모리 셀 어레이의 상기 1개의 컬럼이 상기 제어 회로로부터 최소한 제4 신호를 수신함과 동시에 상기 공통 도체에 선택적으로 접속되는 다수의 메모리 셀 어레이를 포함하는 것을 특징으로 하는 공통 접속부

#### 청구항 10

제어 회로, 컬럼 라인을 갖고 있는 다수의 메모리 셀 어레이, 감지 증폭기 회로 및 최소한 제1 및 제2 부분을 포함하는 프로그래밍 회로를 갖고 있는 접속 회로 메모리용 공통 접속부에 있어서,

상기 제어 회로로부터 최소한 제1 신호를 수신함과 동시에 공통 도체에 선택적으로 접속되는 최소한 1개의 메모리 어레이의 최소한 1개의 컬럼을 포함하고,

상기 프로그래밍 회로의 상기 제1 부분은 상기 제어 회로로부터 최소한 제2 신호를 수신함과 동시에 상기 공통 도체에 선택적으로 접속되고,

상기 프로그래밍 회로의 상기 제2 부분은 상기 제어 회로로부터 최소한 제3 신호를 수신함과 동시에 상기 공통 도체에 선택적으로 접속되고,

상기 공통 도체가 상기 접속 회로 메모리의 제1 영역으로부터 상기 접속 회로 메모리의 제2 영역으로 연장되고,

상기 감지 증폭기 회로가 상기 제어 회로로부터 최소한 제4 신호를 수신함과 동시에 상기 공통 도체에 선택적으로 접속되며,

상기 프로그래밍 회로의 상기 제1 및 제2 부분이 상기 접속 회로 메모리의 대향 단부에 배치되고,

상기 프로그래밍 회로의 상기 제1 부분이 상기 접속 회로 메모리의 소오스 컬럼 라인에 높은 전압을 제공하며,

상기 프로그래밍 회로의 상기 제2 부분이 상기 공통 도체에 기준 전위 및 공급 전압을 제공하고,

상기 접속 회로 메모리가 EEPROM이며,

상기 메모리 셀 어레이들 중 1개의 메모리 셀 어레이의 상기 1개의 컬럼이 상기 제어 회로로부터 최소한 제5 신호를 수신함과 동시에 상기 공통 도체에 선택적으로 접속되는

것을 특징으로 하는 공통 접속부.

#### 청구항 11

제어 회로, 컬럼 라인을 갖고 있는 최소한 1개의 메모리 셀 어레이, 및 최소한 제1 및 제2 부분을 포함하는 프로그래밍 회로를 갖고 있는 접속 회로 메모리에 있어서,

상기 제어 회로로부터 최소한 제1 신호를 수신함과 동시에 공통 도체에 선택적으로 접속된느 최소한 1개의 메모리 어레이의 최소한 1개의 컬럼,

상기 프로그래밍 회로의 상기 제1 부분은 상기 제어 회로로부터 최소한 제2 신호를 수신함과 동시에 상기 공통 도체에 선택적으로 접속되고,

상기 프로그래밍 회로의 상기 제2 부분은 상기 제어 회로로부터 최소한 제3 신호를 수신함과 동시에 상기 공통 도체에 접속되는

것을 특징으로 하는 접속 회로 메모리.

#### 청구항 12

제11항에 있어서, 상기 공통 도체가 상기 메모리의 제1 영역으로부터 상기 메모리의 제2 영역으로 연장되는 것을 특징으로 하는 메모리.

#### 청구항 13

제11항에 있어서, 상기 공통 도체가 회로 노드인 것을 특징으로 하는 메모리.

#### 청구항 14

제11항에 있어서, 상기 제어 회로로부터 최소한 제4 신호를 수신함과 동시에 상기 공통 도체에 선택적으로 접속되는 감지 증폭기 회로를 포함하는 것을 특징으로 한느 메모리.

**청구항 15**

제11항에 있어서, 상기 프로그래밍 회로의 상기 제1 및 제2 부분이 상기 메모리의 대향 단부에 배치되는 것을 특징으로 하는 메모리.

**청구항 16**

제11항에 있어서, 상기 프로그래밍 회로의 상기 제1 부분이 상기 메모리의 소奥斯 컬럼 라인에 높은 전압을 제공하는 것을 특징으로 하는 메모리.

**청구항 17**

제11항에 있어서, 상기 프로그래밍 회로의 상기 제2 부분이 상기 공통 도체에 기준 전위 및 공급 전압을 제공하는 것을 특징으로 하는 메모리.

**청구항 18**

제11항에 있어서, 상기 메모리가 EEPROM인 것을 특징으로 하는 메모리.

**청구항 19**

제11항에 있어서, 다수의 메모리 셀 어레이를 포함하되 상기 메모리 셀 어레이들 중 1개의 메모리 셀 어레이의 상기 1개의 컬럼이 상기 제어 회로로부터 최소한 제4 신호를 수신함과 동시에 상기 공통 도체에 선택적으로 접속되는 것을 특징으로 하는 메모리.

**도면**

## 도면1

## 어드레스 입력

| 전치 디코더<br>프로그램 경로           |                         |                             |                             |                             |                             |                             |

|-----------------------------|-------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| 용장 로우                       | 워드 라인                   | 용<br>장<br>활<br>성            | 용장 로우                       | 용장 로우                       | 워드 라인                       | 용장 로우                       |

| 512 × 512<br>메모리 셀<br>어 래 이 | 디코더 및<br>구 통 기          | 512 × 512<br>메모리 셀<br>어 래 이 |

| 결합 / 세그먼트<br>통과 개이트         | 세그먼트<br>디 코 더           | 결합 / 세그먼트<br>통과 개이트         | 결합 / 세그먼트<br>통과 개이트         | 세그먼트<br>디 코 더               | 결합 / 세그먼트<br>통과 개이트         | 결합 / 세그먼트<br>통과 개이트         |

| 512 × 512<br>메모리 셀<br>어 래 이 | 워드 라인<br>디코더 및<br>구 통 기 | 512 × 512<br>메모리 셀<br>어 래 이 | 512 × 512<br>메모리 셀<br>어 래 이 | 워드 라인<br>디코더 및<br>구 통 기     | 512 × 512<br>메모리 셀<br>어 래 이 | 512 × 512<br>메모리 셀<br>어 래 이 |

| 512 × 512<br>메모리 셀<br>어 래 이 | 워드 라인<br>디코더 및<br>구 통 기 | 512 × 512<br>메모리 셀<br>어 래 이 | 512 × 512<br>메모리 셀<br>어 래 이 | 워드 라인<br>디코더 및<br>구 통 기     | 512 × 512<br>메모리 셀<br>어 래 이 | 512 × 512<br>메모리 셀<br>어 래 이 |

| 결합 / 세그먼트<br>통과 개이트         | 세그먼트<br>디 코 더           | 결합 / 세그먼트<br>통과 개이트         | 결합 / 세그먼트<br>통과 개이트         | 세그먼트<br>디 코 더               | 결합 / 세그먼트<br>통과 개이트         | 결합 / 세그먼트<br>통과 개이트         |

| 512 × 512<br>메모리 셀<br>어 래 이 | 워드 라인<br>디코더 및<br>구 통 기 | 512 × 512<br>메모리 셀<br>어 래 이 | 512 × 512<br>메모리 셀<br>어 래 이 | 워드 라인<br>디코더 및<br>구 통 기     | 512 × 512<br>메모리 셀<br>어 래 이 | 512 × 512<br>메모리 셀<br>어 래 이 |

| 가상 접지<br>디 코 더              | 결합 디코더                  | 가상 접지 디코더                   | 가상 접지<br>디 코 더              | 결합 디코더                      | 가상 접지<br>디 코 더              | 가상 접지<br>디 코 더              |

| 감지 증폭기                      |                         | 감지 증폭기                      | 감지 증폭기                      |                             | 감지 증폭기                      | 감지 증폭기                      |

## 데이터 입력 / 출력

## 도면2

### 도면3

## 도면4