**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

|                                                                                                                                                                                                                                                                  |                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| (51) Int. Cl. <sup>6</sup><br>G01R 31/28                                                                                                                                                                                                                         | (45) 공고일자 2003년01월14일<br>(11) 등록번호 10-0358609<br>(24) 등록일자 2002년10월15일         |

| (21) 출원번호 10-1995-0703486<br>(22) 출원일자 1995년08월16일<br>번역문제출일자 1995년08월16일<br>(86) 국제출원번호 PCT/IB1994/00389<br>(86) 국제출원일자 1994년12월05일<br>(81) 지정국 국내특허 : 일본 대한민국 EP 유럽특허 : 오스트리아 벨기에 스위스 리히텐슈타인 사이프러스 독일 덴마크 스페인 핀란드 프랑스 영국 그리스 아일랜드 이탈리아 룩셈부르크 모나코 네덜란드 포르투칼 스웨덴 | (65) 공개번호 특1996-0701372<br>(43) 공개일자 1996년02월24일<br>(87) 국제공개번호<br>(87) 국제공개일자 |

| (30) 우선권주장 93203546.2 1993년12월16일 EP(EP)<br>94200505.9 1994년02월28일 EP(EP)                                                                                                                                                                                        |                                                                                |

| (73) 특허권자 코닌클리케 필립스 일렉트로닉스 엔.브이.<br>네델란드왕국, 아인드호펜, 그로네보드스베그 1<br>(72) 발명자 마노즈사흐데프<br>네델란드, 베아아인드호펜5621, 그로네보드세베그1<br>(74) 대리인 이병호                                                                                                                                |                                                                                |

**심사관 : 권호영**

**(54) 반도체기판에 집적된 전자회로의 검사방법, 전자회로 및 집적회로**

**영세서**

&lt;1&gt;

**발명의 분야**

&lt;2&gt;

본 발명은 반도체 기판에 집적된 전자회로를 검사하는 방법에 관한 것이다. 상기 기판은 회로의 전원용 전원 노드 및 전도형 영역을 바이어스하기 위해 바이어스 전압에 접속되는 바이어스 노드를 갖는 전도형 영역을 포함한다. 상기 방법은 상기 회로를 통하는 영 입력 전류(quiescent current)를 결정하는 단계를 포함한다.

&lt;3&gt;

**배경기술**

&lt;4&gt;

전자 회로, 특히 집적 회로의 체계적이고 자동적인 검사(testing)가 갈수록 중요해지고 있다. 차세대의 각 회로들은 구성요소의 밀도가 더욱 높아지고 시스템 기능의 수는 더 많아지도록 발전하는 경향이 있다. 각 회로들은 철저하고 값비싼 검사법에 의하지 않고서는 더 이상 공정(process)의 결함을 검출하거나 찾아낼 수 없을 정도로 복잡해지고 있다. 동작시 장복된 결함을 나타내어 시스템을 신뢰할 수 없게 만드는 회로제품을 소비자들이 받아들이리라고 기대할 수는 없다. 따라서 회로제품의 완전한 동작을 보장하도록 검사를 하는 것이 제조자 및 소비자 모두에게 극히 중요하다.

&lt;5&gt;

전류 공급 감시법(Current Supply Monitoring Method; CSM)이라고도 하는 집적회로의 영 입력 전류 검사법(I<sub>DDQ</sub> 검사법)은 영 입력 전류를 감시함으로써 회로에 있는 공정의 결함 위치를 찾는 것을 목적으로 한다. I<sub>DDQ</sub> 검사법에 관해 더 상세한 것은 1992년 5월, IEEE Transactions on Computer-Aided Design지, 제 2권 제 5호의 659 내지 669 쪽에 게재된 K.J.Lee 와 M.A.Breuer의 논문, "Design and Test Rules for CMOS Circuits to Facilitate I<sub>DDQ</sub> Testing of Bridging Faults." 를 참조하기 바란다. I<sub>DDQ</sub> 검사 기술은, 대표적으로 정적(static) CMOS IC에서, 실제의 공정의 결함을 분석함에 있어서 많은 가능성을 보여주었다. CMOS 논리 회로에서의 영 입력 전류, 즉 안정상태 전류(steady state current)는 예컨대, 1μA 정도로 매우 작어야 한다. 그러므로 어떠한 편차도 쉽게 검출될 수 있다. 이 검사기술의 잠재력을 비용 절감과 품질 및 신뢰성 향상의 면에서 중요하다.

&lt;6&gt;

고착 고장(stuck-at fault)들은 회로의 노드들과 전원 라인들 사이의 의도하지 않은 전도성 상호 접속에 의해 일어나는 증상이며, 이에 의해 논리 동작을 방해하는 고정 배선에 의한(hard-wired) 풀업(pull-up) 또는 풀다운(pull-down)을 초래한다. 전원 라인과 신호 라인 사이의 저저항 전도성 브리지(conductive bridge)에 의해 형성된 브리지 결함(bridging fault)은 고착(stuck-at) 현상을 일으킨다. 게이트 산화물의 결함의 영향은 특성상 많은 변수에 의해 결정된다. 즉 논리 전압 레벨들에 의해 규정되지 않는다. 따라서 종래의 전압 방법으로는 종종 검출되지 않는다. 게이트 산화물의 결함은 또한 고착 작용을 일으킬 수도 있다.

&lt;7&gt;

**본 발명의 목적**

<8> 본 발명의 목적은 측정된 영 입력 전류를 보다 정확하게 진단하는  $I_{DDQ}$  검사법을 제공하는 것이다. 본 발명의 또 하나의 목적은 영 입력 전류들의 원인들(origins)간을 구별하는  $I_{DDQ}$  검사법을 제공하는 것이다.

#### 발명의 개요

<10> 이를 위해 본 발명은, 전제부에서 소개된 것과 같은, 영 입력 전류를 결정 단계가 상기 노드들 중 하나의 단일 노드를 통해 전류의 크기를 결정하는 단계를 포함하는 것을 특징으로 하는 방법을 제공한다.

<11>  $I_{DDQ}$  검사법에서 전자회로의 허용이나 거부의 판정은 극히 작은 측정된 전류값들을 근거로 행해진다. 종래에는  $10\mu A$  이상의 통상적인 영 입력 전류가 결함있는 장치를 나타내는 것으로서 해석되는 반면, 결함없는 장치는 적어도  $10\mu A$  이하 정도의 크기의 영 입력 전류를 발생한다. 본 발명은, 큰 영 입력 전류들이 공정상의 결함 이외의 원인들로부터도 발생할 수 있기 때문에, 큰 영 입력 전류가 회로의 기능적 동작이 부정확하다는 것을 암시할 필요가 없다는 통찰에 근거한다. p-n 접합에서 발생하는 누설 전류 또는 기판 전류는 더 완벽하게 잘 동작하는 전자회로에서 상당한 크기의 영 입력 전류를 일으킬 수 있다. 예를 들면, 비-에피택실 기판에 대한 누설 전류밀도의 크기는 통상  $10^{-6} A/cm^2$  정도이다. 예를 들면, 1983년 11월, IEEE Electron Device Letters 지의 제 EDL-4권 제 11호 403 내지 406 쪽에 게재된, J.W.Slotboom, M.J.J Theunissen 및 A.J.R. de Kock 의 논문, "Impact of Silicon Substrate on Leakage Currents" 를 참조하기 바란다. 또한 영 입력 전류는 베이스 웨이퍼의 품질, 그 웨이퍼가 제공된 공정, 또는 기판 및 우물접촉(well contact)들의 잘못된 위치 설정에 기인할 수도 있다. 이들 모든 누설 전류들은 전자회로의 기능적인 동작 그 자체, 예컨대, 디지털 회로에서의 논리 동작이나 아날로그 회로에서의 신호 조작에 직접적으로 영향을 미치지는 않는다. 비-배터리 동작형 장치에 대해, 전류 누설은 기대 수명(lifetime) 및 동작상의 사용에 있어서 큰 중요성을 갖지 않는다.

<12> 따라서 종래의  $I_{DDQ}$  검사법하에서 단지 큰 정상 상태 전류를 일으키는 것만을 근거로, 결함있는 장치로서 전자 장치를 거부하는 것이 항상 옳은 것은 아니다. 그러므로 본 발명은 예컨대, 검사를 하는 동안 서로 직류적으로(galvanically) 분리된 노드들을 가짐으로써, 전원 노드(supply node)를 통해 영 입력 전류를 검사하는 것과 바이어스노드(bias node)를 통해 전류를 검사하는 것을 분리한다. 직류적으로 분리된다는 것은, 전자회로의 기능적 동작을 나타내는, 상기 노드들을 통한 전류들이 개별적으로 측정될 수 있도록 상기 노드들 사이에 단락 회로가 존재하지 않는다는 것으로 이해되어야 한다. 즉, 전원 노드들을 통한 전류 경로는 검사를 하는 동안 두 전류들을 구별하기 위해 바이어스 노드들을 통한 전류 경로와 기능적으로 분리된다. 전원 노드들을 통한 정상 상태 전류는 결합된 바이어스 노드들과 전원 노드들을 통한 집합적인 정상 상태 전류보다 회로의 동작상의 적합성을 더 잘 표시한다. 본 발명에 따른 제조 공정의 생산성은 p-n 접합들을 가로지르는 누설전류와 회로의 기능적 동작을 위한 전원 전류를 구별함으로써 효과적으로 증가된다. 환언하면, 본 발명에 의한 검사법은 또한, 그렇지 않았으면 종래의  $I_{DDQ}$  검사법에 의해 버려졌을지도 모르는, 장치들을 올바르게 기능하는 장치로 분류한다.

<13> 회로의 기능적 동작은 전원 노드들을 통한 영 입력 전류들을 결정함으로써 검사된다. 누설 전류들은 바이어스 노드들을 통한 전류를 결정함으로써 검사된다. 전원 노드들과 바이어스 노드들 사이의 직류적 분리(galvanic separation)는 전원 전압들 및 이 전원 전압과 상이한 바이어스 전압들의 다양한 조합 하에서 회로를 검사할 수 있게 한다.

<14> 1991년 Proc.3-nd NASA Symposium on VLSI Design 의 1 내지 11 쪽에 게재된 J.Burr 와 A.Peterson 의 논문, "Ultra Low Power CMOS Technology" 에서는 매우 낮은 전원 전압, 예를 들면, 수백 밀리볼트 정도에서의 디지털 회로의 구현을 논의하고 있음을 알 수 있다. 다양한 병렬 신호 처리기들에서의 동작 당 에너지를 감소시키는 것이 추구된다. PFET 게이트들은 p+ 도핑되고 NFET 게이트들은 n+ 도핑된다. 채널 주입이 제외된다면, 두 장치는 0 볼트에 가까운 문턱치를 갖는다. 따라서 문턱치는 기판 바이어스 전압을 조정함으로써 조정될 수 있다. 이 장치는 바이어스 노드들 중 적어도 하나가 전원 노드들로부터 직류적으로 분리될 것을 요구한다. 그러나 이 종래 기술의 회로에서 노드 분리는 극히 낮은 전압 전원 디지털 회로의 기능적 동작에 적용된다. 본 발명에서, 노드 분리는 특정의 검사 방법을 가능케 하는 회로에서 실행된다. 여기서 노드들은 통상 정상 동작에서 예를 들면, 5 볼트, 3.3 볼트 또는 2.7 볼트의 고정 전원 전압에 접속된다. 즉, 본 발명의 회로는 실질적으로 1 볼트보다 큰 전원 전압하에서 동작한다. 여기서는 동작상의 사용에 있어서 문턱치 조절이 필요없다.

<15> 한 회로에서의 영 입력 전류들의 측정은 매우 민감한 측정 장치를 요구한다. 이를 위해 그 회로 안에 접적될 수 있는 소위 내부 전류(Built-In-Current; BIC) 센서가 개발되어 왔다. 미국 특허 제 5,057,774호에서는 BIC 센서를 위한 회로 장치의 한 예를 개시하고 있다. BIC 센서는 전원 노드를 통한 영 입력 전류의 측정 및 바이어스 노드를 통한 영 입력 전류의 측정용으로 사용될 수 있다.

#### **도면의 간단한 설명**

<16> 제 1도는 종래기술에서 검사하는 동안의 전자 장치의 일예를 도시하는 도면.

<17> 제 2도 내지 제 4도는 본 발명에 따른 검사용 전자 장치의 예를 도시하는 도면.

<18> 제 5도 내지 제 10도는 본 발명에 의해 실현가능한 검사 방법들의 대표적인 예들을 도시하는 도면.

<19> 제 11도는 영 입력 전류 측정용 내부 전류 센서(Built-In-Current Sensors)의 일예를 도시하는 도면.

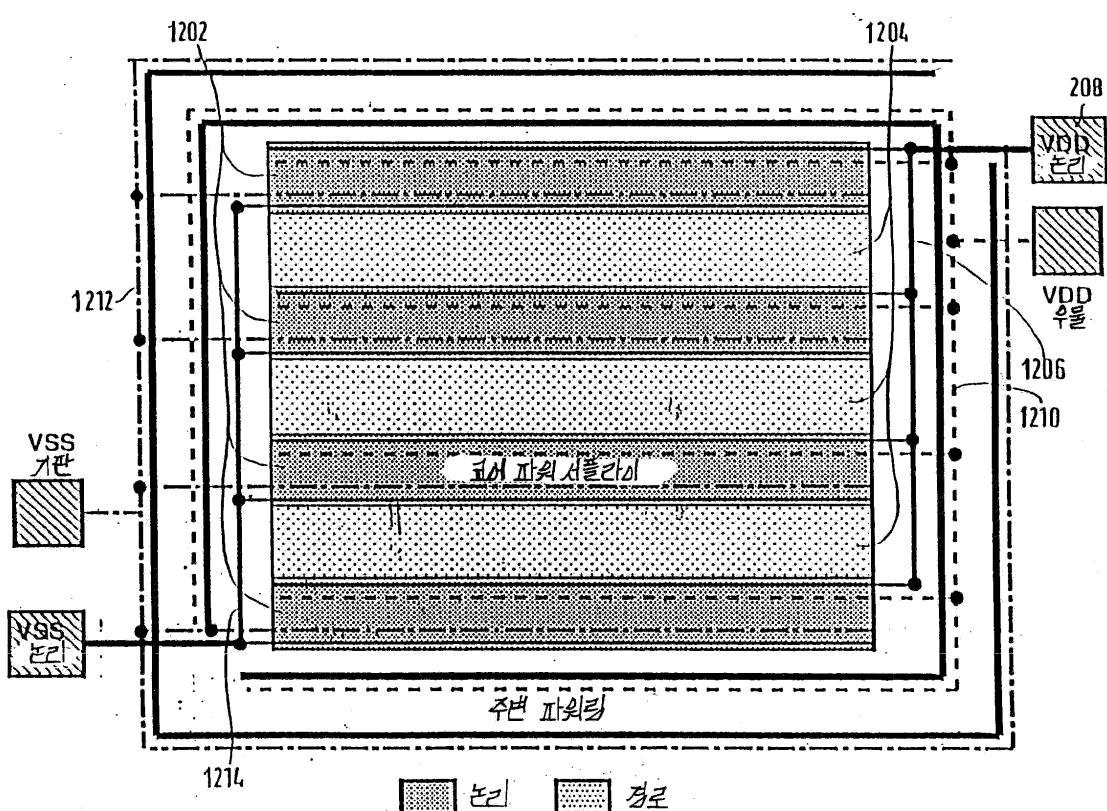

<20> 제 12도는 본 발명에 따른 전자 장치들을 포함하는 접적 회로를 위한 전원 라인들의 구조를 도시하는 도면.

<21> 상세한 설명

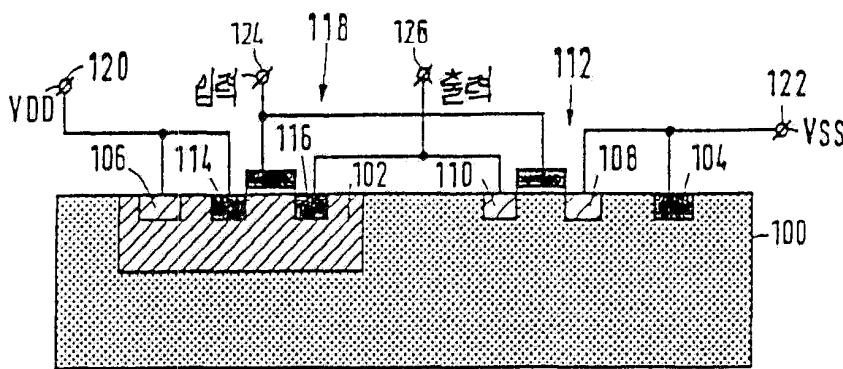

<22> 제 1도는 n-우울 공정으로 제조된 종래기술 장치의 n 우울(102)을 갖는 p-반도체 기판(100)의 일부분을 도시하는 개략적인 단면도이다. 본 예에서, p-기판(100)에는 통상 p<sup>+</sup> 도핑된 기판 접촉부(104)가 제공된다. 본 예에서, n-우울(102)에는 통상 n<sup>+</sup> 도핑된 우울 접촉부(106)가 제공된다. 또한 NFET(112)에 대한 소스(108) 및 드레인(110)은 기판(100) 내에 형성되고, PFET(118)에 대한 소스(114) 및 드레인(116)은 n-우울(102) 내에 형성된다. NFET(112)와 PFET(118)는 입력단(124) 및 출력단(126)을 갖는 CMOS 인버터(inverter) 타입의 논리 게이트로서 상호 접속된다. NFET들 및 PFET들의 형성과 논리 게이트들의 생성은 기술적으로 잘 공지되어 있으므로 본원에서는 더 이상 언급하지 않았다. 통상 PFET(118)의 소스(114)는 단자(120)에서 전원 전압 VDD에 접속될 전원 노드로서 작용하며, VDD는 전원 전압 VDD와 VSS 중 더 높은 쪽이다. 반면, NFET(112)의 소스(108)는 단자(122)에서 VSS에 접속될 전원 노드로서 작용하며, VSS는 전원 전압 VDD와 VSS 중 더 낮은 쪽이다.

<23> 한 측면의 기판(100)과 다른 측면의 드레인(110) 및 소스(108) 사이의 p-n 접합들이 도통되는 것을 방지하기 위해, 기판 접촉부(104)는 기판(100)을 VSS에 접속시키고, 이에 따라 기판(100)을 바이어스시키는 역할을 한다. n-우울(102)과 기판(100) 사이 그리고, n-우울(102)과 소스(114) 및 드레인(116) 사이의 도통을 피하기 위해, 우울 접촉부(106)는 n-우울(102)을 VDD에 접속시키고, 이에 따라 n-우울(102)을 바이어스시킨다.

<24> 통상, 회로를 통과하는 영 입력 전류는 VDD 단자(120)와 VSS 단자(122) 사이의 경로에서 전류를 측정함으로써 결정된다. 즉, 기판(100)을 통과하는 누설 전류, 예컨대, 기판(100)과 n-우울(102)의 P-n 접합을 통과하는 전류뿐만 아니라, 예를 들면, 트랜지스터(112, 118) 사이의 상호접속들 내의 브리지 결함으로 인해 발생하는 전류도 결합되어 측정된다.

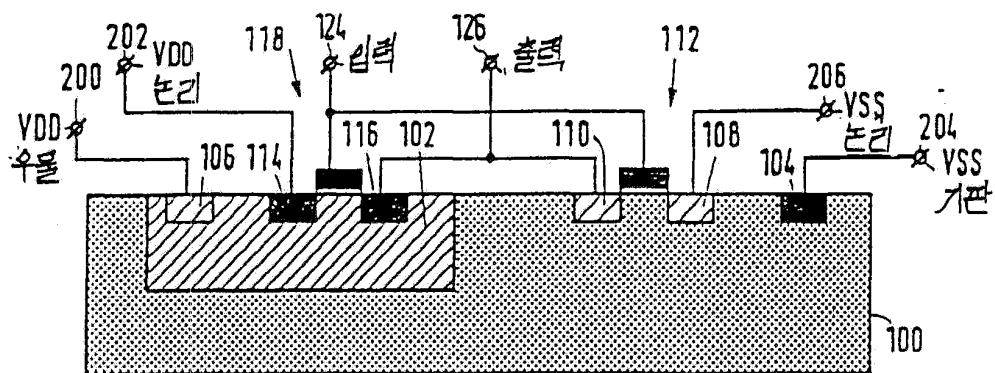

<25> 제 2 도는 n-우울 공정으로 제조된, 본 발명에 따른, 장치의 n-우울(102)을 가진 p-반도체 기판(100)의 일부분을 도시하는 개략적인 단면도이다. 본 발명에서 I<sub>DDQ</sub> 검사를 하는 동안, n-우울 접촉부(106)와 전원 접촉부(114)는 각각 상이한 VDD 전원 단자들(200, 202)에 접속되고, 기판 접촉부(104) 및 소스(108)는 각각 상이한 VSS 전원 단자들(204, 206)에 접속된다. 결국, 트랜지스터들 내의 결함과 트랜지스터들 사이의 상호접속으로 인해 발생하는 정상 상태 전류에의 제 1 기여는 기술에 내재된 현재의 기생 효과로부터 발생하는 정상 상태 전류에의 제 2 기여로부터 분리되어 측정될 수 있다. 상기 제 1 기여는 단자들(202, 206) 사이의 경로를 통과하는 전류를 측정함으로써 결정되는 반면, 제 2 기여는 단자들(200, 204) 사이의 경로 내의 전류를 측정함으로써 결정된다.

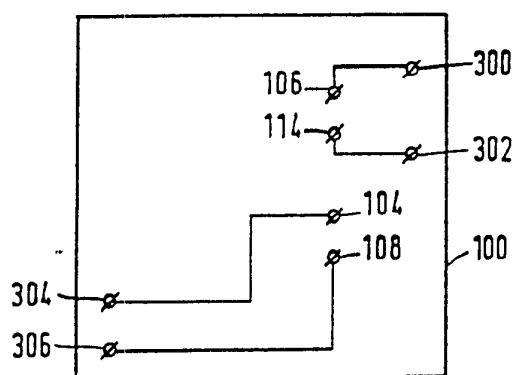

<26> 전원 노드(114, 108)와 바이어스 노드(106, 104)의 직류적인 분리는 다양한 방법으로 행해질 수 있다. 제 1 선택은 기판 위에 개별적인 본딩 패드(bonding pad)들을 제공하는 것이다. 제 3도는 n-우울 접촉부(106)에 접속된 바이어스 본딩 패드(300), 전원 노드(114)에 접속된 전원 본딩 패드(302), 기판 접촉부(104)에 접속된 바이어스 본딩 패드(304) 및 전원 노드(108)에 접속된 VSS 전원 본딩 패드(306)가 상부에 제공된 기판(100)의 개략적인 배치를 도시한다. 기판(100)은 웨이퍼거나 칩일 수 있다. 검사에 의해 회로가 양호함을 확인한 후에, 기판(100)에 리드 프레임(lead frame)을 제공하고 이를 캡슐로 둘러싼다. 본딩 패드(300, 302)는 리드 프레임의 상이한 접속핀(connection pin)들에 접속되거나 또는 이중 본딩을 이용하여 동일한 접속핀에 접속될 수 있다. 마찬가지로, 본딩 패드(304, 306)는 리드 프레임의 상이한 접속핀들에 접속되거나 또는 이중 본딩을 이용하여 동일한 접속핀에 접속될 수 있다. 이중 본딩이 사용된 경우, 본 발명에 따른 검사는 더 이상 수행될 수 없다.

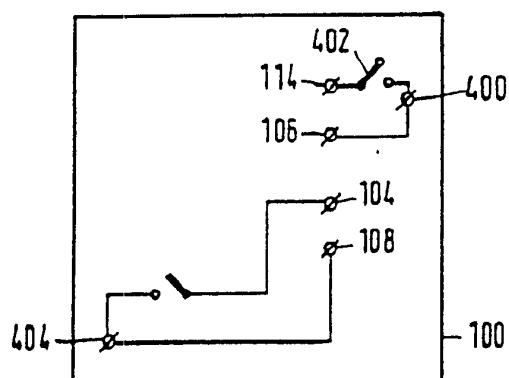

<27> 제 4 도는 전원 노드(예컨대, 노드(114))와 본딩 패드(예컨대, 400) 사이, 그리고 바이어스 노드(예컨대, 106)와 동일한 본딩 패드(예컨대, 400) 사이의 접속들 중 적어도 하나의 접속에서 스위치(402)를 기능적으로 포함하는 제 2 선택을 도시한다. 스위치(402)는 예를 들면, 전용의 온-칩(on-chip) 회로(도시되지 않음)를 통해 프로그램 제어될 수도 있고 또는 외부 수단에 의해서 제어될 수도 있다. 도면에서, 스위치(402)는 전원 노드(예를 들면, 114)와 본딩 패드 사이에 위치하는 반면, 바이어스 노드는 본딩 패드에 접속된 채 유지된다. 이런 방식으로, 회로는 누설 전류를 결정하기 위해 기능적으로 디스에이블(disable)될 수 있다.

<28> 기판(100)이 CPU, 메모리, 버스 인터페이스, 레지스터 등과 같은 복수의 부속 회로(도시되지 않음)를 갖는 회로, 예컨대, 마이크로프로세서를 포함하고 있다고 가정한다. 스위치(402)와 같은 스위치들은 특정의 부속 회로 내의 영 입력 전류를 감시하기 위해 부속 회로들 중 특정의 한 부속 회로를 선택적으로 이네이블(enable)시킬 수 있도록 부속 회로들 각각과 전원 단자들 및 바이어스 단자들의 사이에 개별적으로 배치될 수도 있다. 이는 발생 가능한 결함의 위치를 찾을 수 있게 한다.

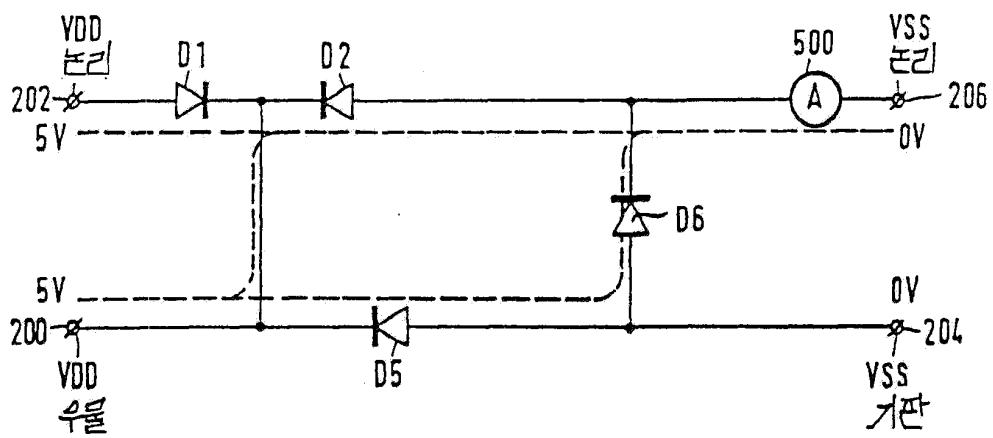

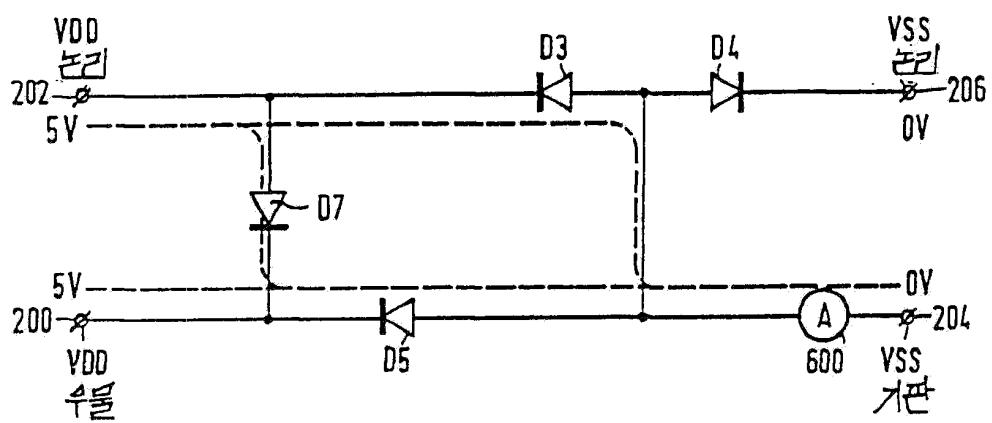

<29> 제 5 도 내지 제 10 도는 대응하는 영 입력 전류들을 결정하기 위해 상이한 구성들로 단자들(200, 202, 204 및 206)을 조합함으로써 측정 방법들의 대표적인 예들을 도시하는 제 2 도의 기판(100)을 개략적으로 도시하고 있다. 기판(100) 내의 p-n 접합들은 다이오드들(D1, D2, D3, D4, D5, D6 및 D7)로 표현된다. D1 은 소스(114)의 p<sup>+</sup>-영역과 n-우울(102) 사이의 다이오드를 나타낸다. D2 는 n-우울(102)과 드레인(116)의 p<sup>+</sup>-영역 사이의 다이오드를 나타낸다. D3 은 드레인(110)의 n<sup>+</sup>-영역과 p<sup>-</sup>-기판(100) 사이의 다이오드를 나타낸다. D4 는 p<sup>-</sup>-기판(100)과 소스(108)의 n<sup>+</sup>-영역 사이의 다이오드를 나타낸다. D5 는 n<sup>-</sup>-우울(102)과 p<sup>-</sup>-기판(100) 사이의 다이오드를 나타낸다. NFET(112)가 도통할 때, 전도 채널과 p<sup>-</sup>-기판(100) 사이에는 다이오드가 존재한다. 이 다이오드는 D6 으로 표현된다. PFET(118)가 도통할 때, 전도 채널과 n<sup>-</sup>-우울(102) 사이에는 다이오드가 존재한다. 이 다이오드는 D7 로 표현된다.

<30> 제 5 도는 단자(206)로 흘러 들어가는 영 입력 전류를 결정하기 위한 제 1 선택을 도시하고 있다. 단자(200, 202)는 예를 들면, 5 볼트 또는 3 볼트로 유지되며, 단자(204, 206)는 접지되고, 입력단(124)은 하이(high)로 설정된다. 이제 NFET(112)가 도통하기 때문에, D3 과 D4 는 사라지고 다이오드 D6 이 존재한다. 전류 측정 장치(500)는 단자(206) 근처의 전류 분기(branch)에 배치된다. 단자(206)로 흘러 들어가는 전체 전류에 기여하는 부속 전류들은 점선으로 표현된다. 이 제 1 선택은 예를 들면, 트랜지스

터들(112, 118) 사이의 상호접속들에 관한 정보를 제공한다. 단자들(200, 202)이 직류적으로 (galvanically) 분리되어 있음으로 인해, 단자 (200, 202)에서의 전압은 상호 상이하게 선택될 수 있음을 유의한다.

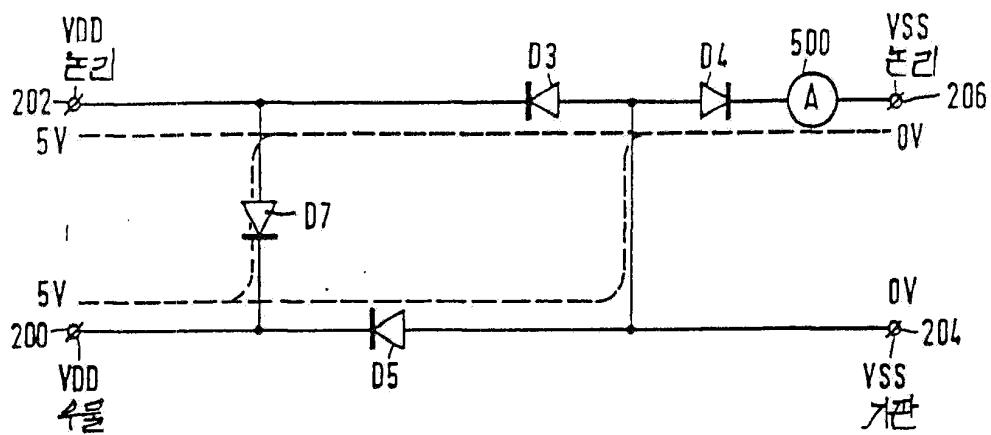

<31> 제 6 도는 제 5 도와 같은 설정을 도시하고 있지만, 여기서는 입력단(124)이 로우(low)로 설정된다. 이제 PFET(118)가 도통하기 때문에, D1 과 D2는 사라지고 D7이 존재한다. NFET(112)는 도통되지 않기 때문에 D3 과 D4가 존재하고 D6이 사라진다.

<32> 제 7 도는 단자(204)로 흘러 들어가는 영 입력 전류를 결정하기 위한 제 2 선택을 도시하고 있다. 단자(200, 202)는 예를 들면, 5 볼트 또는 3 볼트로 유지되며, 단자(204, 206)는 접지되고, 입력단 (124)은 하이(high)로 설정된다. 이어서 NFET(112)가 도통되기 때문에 다이오드(D6)가 존재하고, PFET(118)는 도통되지 않기 때문에 다이오드(D1 과 D2)가 존재한다. 전류 측정 장치(600)는 단자(204) 근처의 전류 분기부에 배치된다. 단자(204)로 흘러 들어가는 전체 전류에 기여하는 부속 전류들은 점선으로 표현된다. 제 2 선택은 예를 들면, n-우물(102)의 그리고 기판 접촉부(104)의 p-n 접합들에 관하여 알려준다.

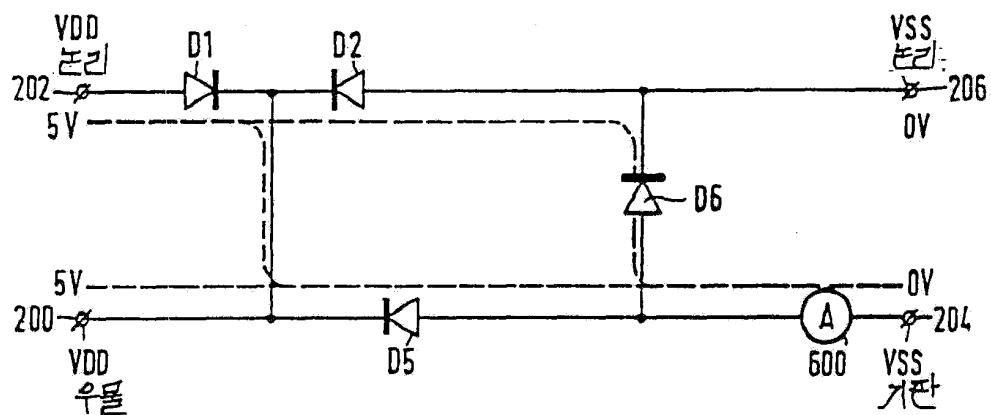

<33> 제 8 도는 제 7 도와 같은 설정을 도시하고 있지만 이제 입력단(124)은 로우로 설정된다. 이러한 설정은 PFET(118)를 도통되게 하기 때문에 다이오드(D7)가 존재하고, NFET(112)를 도통되지 않게 하기 때문에 다이오드(D3, D4)가 존재한다.

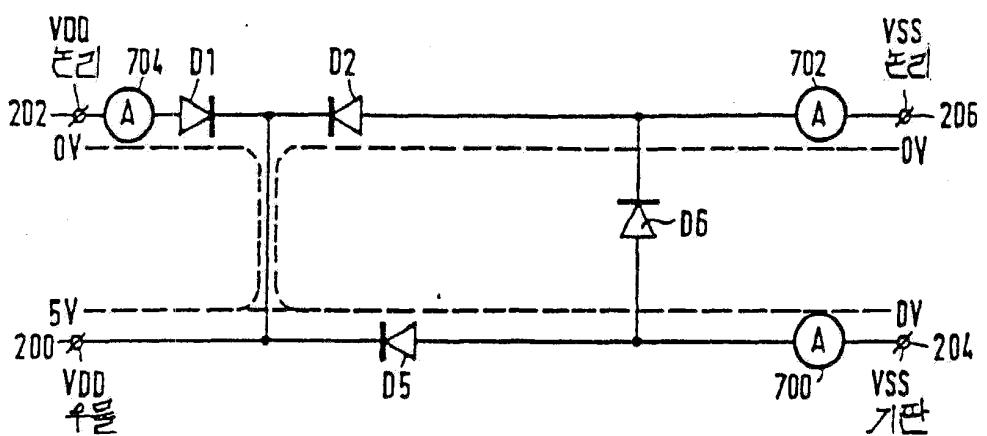

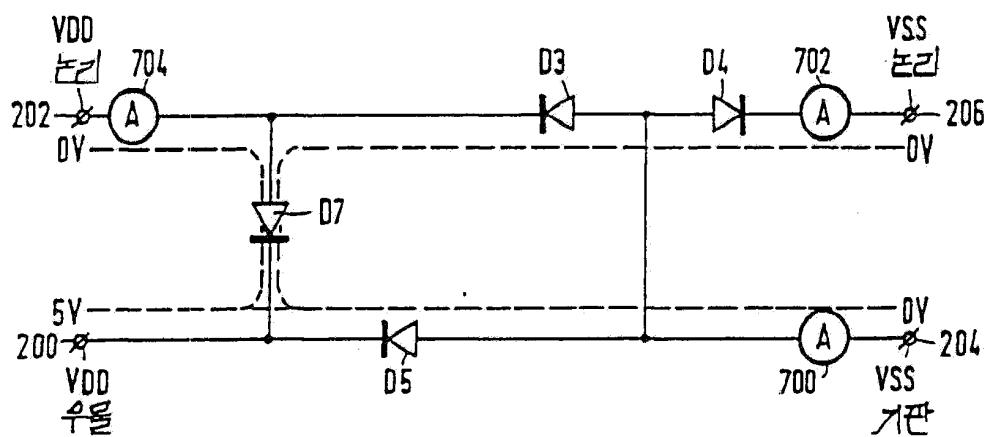

<34> 제 9 도는 단자(206)로 흘러 들어가는 영 입력 전류를 결정하기 위한 제 3 선택을 도시하고 있다. 단자(200)는 예를 들면, 5 볼트로 유지되고, 단자(202, 204, 206)는 접지되며 입력단(124)은 하이로 설정된다. 이어서 NFET(112)가 도통되기 때문에 다이오드(D6)가 존재하고, PFET(118)는 도통되지 않기 때문에 다이오드(D1, D2)가 존재한다. 전류 측정 장치(700, 702 및 704)는 각각 단자(204, 206 및 202) 근처의 전류 분기부에 배치된다. 상기 단자들로 흘러 들어가는 전체 전류에 기여하는 부속 전류들은 점선으로 표현된다. 측정들의 조합은 여러 가지 p-n 접합들 및 상호접속에 관하여 개별적으로 알려준다.

<35> 제 10 도는 제 9 도와 같은 설정을 도시하고 있지만 입력단(124)은 로우로 설정된다. 이러한 설정은 PFET(118)를 도통되게 하기 때문에 다이오드(D7)가 존재하고, NFET(112)를 도통되지 않게 하기 때문에 다이오드(D3 과 D4)가 존재한다.

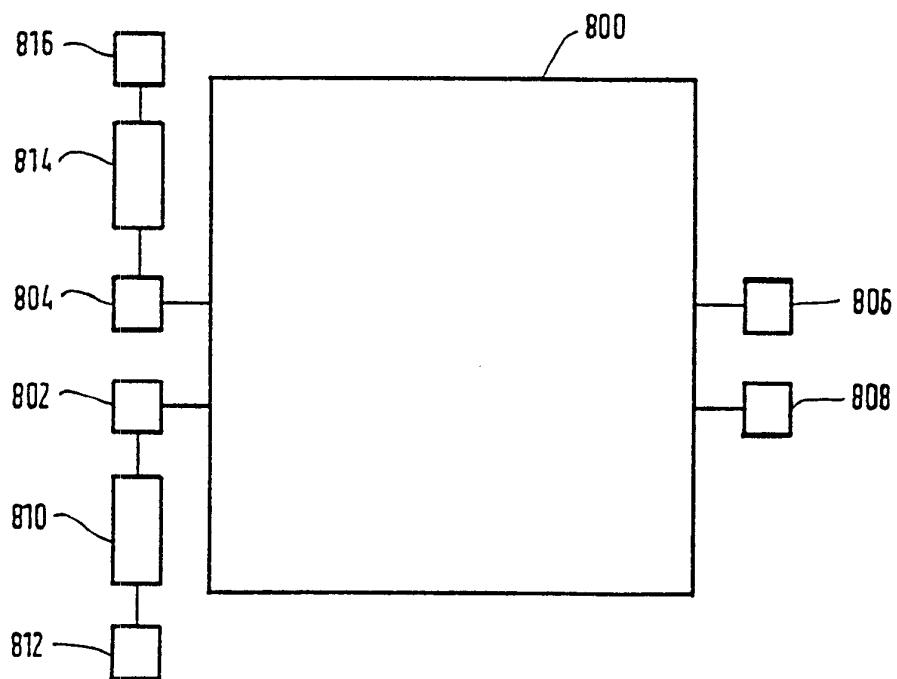

<36> 제 11 도는 VSS<sub>논리</sub>, VSS<sub>기판</sub>, VDD<sub>논리</sub> 및 VDD<sub>우물</sub>의 각 전원에 대한 전원 패드(802, 804, 806 및 808)를 갖는 전체 칩 레이아웃(800)을 개략적으로 도시하고 있다. BIC 센서(810)는 패드(802)와 패드(812) 사이에 접속되고 다른 BIC 센서(814)는 패드(804)와 패드(816) 사이에 접속된다. BIC 센서는 이 센서를 통해 흐르는 전류를 측정하고 본원에서는 더 이상 언급하지 않는 어떤 논리(logic)에 의해 그 측정값들을 전달한다. BIC 센서의 상세한 설명은 미국 특허 제 5,057,774를 참조하기 바란다. 정상 모드에서 회로는 패드들(802, 804, 806 및 808) 위에서 직접 다양한 전원 형태를 수신하며, BIC 센서들은 어떠한 전원 라인에도 없으며 동작하지 않는다. 이러한 방식으로, BIC 센서는 회로의 동작 특성에 관한 아무런 해로운 효과도 갖지 않는다. 검사 모드에서, 영 입력 전류들을 측정할 때 VSS<sub>논리</sub>의 전원은 패드(812)를 통해서 발생함으로써 BIC 센서로 이동되며, VSS<sub>기판</sub>의 전원은 패드(816)를 통해서 발생함으로써 BIC 센서(814)로 이동된다. 이제 영 입력 전류 측정은 측정 장치로서 두 개의 센서를 이용하여 실행될 수 있다.

<37> IDQ 검사는 패키지화된 회로에서뿐만 아니라 다이(die)에서도 수행 될 수 있다. 상기 다이를 검사한 결과를 기초로, 상기 다이를 거부할 것인지 패키지화할 것인지를 결정한다. 전원 패드들을 외부 핀(pin)들에 본딩하는 것에 관해서는, 다음을 포함하는 다양한 선택이 가능하다.

<38> - 패드들(802, 804, 806, 808, 812 및 816)을 각각의 외부 핀들에 본딩한다. 노드들을 통과하는 그리고 기판을 통과하는 영 입력 전류를 개별적으로 측정하기 위한 전체 기능성은 BIC 센서들의 사용을 포함하여 패키징 후에도 이용가능하게 남아있다.

<39> - 패드들(802, 804, 806 및 808)을 각각의 외부 핀들에 본딩하고 패드들(812, 816)을 버린다. 영 입력 전류 측정에 대한 전체 기능성은 남아 있지만 BIC 센서들은 패키징 후에는 더 이상 사용될 수 없다.

<40> - 패드들(802, 804)을 한 개의 외부 핀에 함께 본딩하고, 패드(806, 808)를 또 하나의 외부 핀에 함께 본딩하며, 패드(812, 816)를 버린다. 통상의 IDQ검사를 위한 유일한 가능성은 패키징 후에도 가능하게 남아 있고 노드와 기판을 통과하는 전류는 개별적으로 측정될 수 없다.

<41> 어떤 선택이 사용될 것인지는 패키지 상의 추가적인 핀들의 수와 동작상의 수명 동안의 IDQ 검사의 필요 및 구조 사이의 흡정의 결과이다.

<42> 제 11 도의 전원 패드들에 접속된 BIC 센서들의 사용례는 2 개의 특정 패드들에 대한 2 개의 센서를 포함한다. 센서들과 패드들의 다른 조합 및 다른 수의 센서들과의 조합도 가능하다.

<43> 제 12 도는 접적 회로의 레벨에서의 전원 라인들의 구조를 도시하는데, 상기 접적 회로는 본 발명을 이용하는 다수의 전자회로들을 포함한다. 논리 채널들(logic channels)(1202)이 전자회로들을 유지(hold)하기 위해 제공된다. 그러한 전자회로의 한 예의 단면도가 제 2 도에 제공된다. 경로 채널들(routing channels)(1204)은 전체적인 접적회로가 그가 원하는 기능을 수행하는 방식으로 전자회로들을 상호 접속시키는 배선들을 유지하기 위해서 제공된다. 본 발명에 따른 전자회로는 네 개의 상이한 전력 접속들을 요구한다. 이들은 논리 채널(1202)에서 실행되는 네 개의 별렬 전원 라인들에 의해서 제공된다. 상이한 논리 채널들의 제 1 전원 라인들은 함께 접속되어 메시(mesh)(1206)를 형성하는데, 상기 메시는 외부 접속을 위한 본딩 패드(208)에 접속된다. 유사한 메시들(1210, 1212 및 1214)은 다른 전원 라인들을 위해 실현된다.

<44> 본 기술분야의 숙련자들에게는 본 발명에 따른 회로 검사가 p 우물 기술, n-우물 기술 또는 쌍둥이(twin) 우물 기술로 조립되는 회로에 관계없이 수행될 수 있고, 또한 단지 한 가지 종류의 전계효과 트랜지스터(예를 들면, NMOS, PMOS), 두 개의 상보형 전계효과 트랜지스터(예를 들면, CMOS) 또는 양극성

트랜지스터 및 상보형 전계효과 트랜지스터(예를 들면, BiCMOS)로 구현되는 회로에도 관계없이 수행될 수 있음이 명백하다.

### (57) 청구의 범위

#### 청구항 1

반도체 기판(100)에 집적된 전자회로를 검사하는 방법으로서, 상기 기판(100)은 회로의 전원용 전원 노드(114) 및 제 1 전도형 영역을 바이어스하기 위해 바이어스 전압에 접속하는 바이어스 노드(106)를 가진 상기 제 1 전도형 영역을 포함하고, 상기 기판은 추가적인 노드(104, 108)를 더 포함하며, 또한 상기 방법은 회로를 통과하는 영 입력 전류(quiescent current)를 결정하는 단계를 포함하는, 상기 검사 방법에 있어서,

상기 영 입력 전류를 결정하는 단계는 한 쪽에 있는 상기 전원 노드(114) 및 상기 바이어스 노드(106), 그리고 다른 쪽에 있는 추가적인 노드(104, 108) 중 하나의 단일 노드를 통과하는 전류의 크기를 결정하는 단계를 포함하는 것을 특징으로 하는, 전자회로 검사 방법.

#### 청구항 2

제 1 항에 있어서,

상기 기판은 상기 제 1 전도형의 반대인 제 2 전도형의 제 2 영역을 포함하고; 상기 제 2 영역은 제 2 전원 노드(108) 및 상기 제 2 영역을 바이어스하기 위해 제 2 바이어스 전압에 접속하는 제 2 바이어스 노드(104)를 포함하며, 상기 추가적인 노드(104, 108)는 상기 제 2 전원 노드(108) 및 상기 제 2 바이어스 노드(104) 중 적어도 하나를 포함하고, 상기 전류의 크기는;

- 상기 제 1 전원 노드(114)로부터 상기 제 2 전원 노드(108)로 흘러 들어가는 전류의 크기를 결정하는 단계;

- 상기 제 1 바이어스 노드(106)로부터 상기 제 2 바이어스 노드(104)로 흘러 들어가는 전류의 크기를 결정하는 단계;

- 결합된 상기 제 1 전원 노드(114) 및 제 1 바이어스 노드(106)를 통해서 제 2 전원 노드(108)로 흘러 들어가는 전류의 크기를 결정하는 단계; 및

- 결합된 상기 제 1 전원 노드(114) 및 제 1 바이어스 노드(106)를 통해서 제 2 바이어스 노드(104)로 흘러 들어가는 전류의 크기를 결정하는 단계 중 적어도 하나의 단계를 포함하는, 전자회로 검사 방법.

#### 청구항 3

제 1 항에 있어서,

상기 전원 노드(114)와 상기 바이어스 노드(106)는 검사를 하는 동안 서로 직류적으로 (galvanically) 분리되는, 전자회로 검사 방법.

#### 청구항 4

제 1 항에 있어서,

상기 노드들(106, 114) 중 적어도 하나의 단일 노드를 통과하는 전류는 상기 기판(100)에 집적된 내부 전류(Built-In-Current) 센서(810, 814)로 결정될 수 있는 것을 특징으로 하는, 전자회로 검사 방법.

#### 청구항 5

실질적으로 1 볼트 보다 더 높은 전원 전압으로 동작하는 전자회로로서, 상기 회로는 회로의 전원용 전원 노드(114) 및 전도형 영역을 바이어스하기 위해 바이어스 전압에 접속하는 바이어스 노드(106)를 가진 적어도 하나의 전도형 영역은 포함하는 반도체 기판(100)을 가지며, 상기 기판(100)은 회로를 통과하는 영 입력 전류의 결정을 가능하게 하기 위한 추가적인 노드(104, 108)를 더 포함하는, 상기 전자회로에 있어서,

상기 바이어스 노드(106)와 전원 노드(114)는 서로 직류적으로 분리되거나 직류적으로 분리될 수 있는 것을 특징으로 하는, 전자회로.

#### 청구항 6

제 5 항에 있어서,

상기 바이어스 노드(106)는 바이어스 본딩 패드(bias bonding pad)(300)에 접속되고, 상기 전원 노드(114)는 전원 본딩 패드(302)에 접속되는, 전자회로.

#### 청구항 7

제 5 항에 있어서,

상기 전원 노드(114)는 전원 본딩 패드(400)로부터 가역적으로 분리될 수 있고, 상기 바이어스 노드(106)는 상기 전원 본딩 패드(400)에 접속되는, 전자회로.

#### 청구항 8

제 5 항에 있어서,

접속핀(connection pin)들을 가지는 리드 프레임(lead frame) 위에 장착되어 캡슐에 둘러싸이며, 상기 리드 프레임은 상기 바이어스 노드에 직류적으로 접속된 제 1 접속핀 및 상기 전원 노드에 직류적으로 접속된 제 2 접속핀을 가지는, 전자회로.

#### 청구항 9

제 5 항에 있어서,

적어도 상기 전원 노드(114) 또는 상기 바이어스 노드(106)는 내부 전류 센서(810, 814)에 접속되는, 전자회로.

#### 청구항 10

제 5 항에 따른 전자회로들이 위치한 다수의 병렬 경로 채널들(routing channels)(1204) 및 논리 채널들(1202)을 포함하는 집적 회로에 있어서,

각 경로 채널(1204)은 네 개의 병렬 전원 라인들을 포함하고, 이들 전원 라인들 모두는 논리 채널(1202) 내의 전자회로들에 급전하기 위해 경로 채널(1204)에 대해 길이방향으로 놓여 있으며,

상기 네 개의 라인들 중 제 1 라인은 상기 제 1 전원 노드들에 급전하고, 제 2 라인은 상기 제 1 바이어스 노드들에, 제 3 라인은 상기 제 2 전원 노드들에, 그리고 제 4 라인은 상기 제 2 바이어스 노드들에 급전하기 위한 것이며,

모든 논리 채널들(1202)의 상기 제 1 전원 라인들은 상기 채널들(1202, 1204)의 영역 외부에 위치한 제 1 접속 라인에 의해 상호 접속되고, 제 1 본딩 패드(208)에 접속되는 제 1 메시(mesh)(1206)를 형성하며,

유사한 메시들(1210, 1212, 1214) 및 본딩 패드들은 상기 제 2, 제 3 및 제 4 전원 라인들에 대해 형성되는 것을 특징으로 하는, 집적 회로.

#### 요약

IC는  $I_{DDQ}$  측정을 통해서 검사된다. IC 기판은 회로의 전원을 위한 전원 노드 및 전도형 영역을 바이어스하기 위해 바이어스 전압에 접속하는 바이어스 노드를 갖는 전도형 영역을 포함한다. 상기 회로의  $I_{DDQ}$  검사는, 상기 전원 노드 및 상기 바이어스 노드가 회로의 기능적인 특징에 의한 영 입력 전류(a quiescent current)에의 영향으로부터 분리하도록 직류적으로 분리되는 동안, 이루어진다.

#### 도면

##### 도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12