**Veröffentlicht:**

- mit internationalem Recherchenbericht (Artikel 21 Absatz 3)

---

Es wird ein optoelektronisches Modul (100) angegeben, umfassend einen Träger (1) mit zumindest einer Kontaktstelle (1A); einen Strahlungsemittierenden Halbleiterchip (2), wobei der Strahlungsemittierende Halbleiterchip (2) eine erste Kontaktfläche (2A) und eine zweite Kontaktfläche (2B) aufweist; eine elektrisch isolierende Schicht (4), die eine erste (4A) und eine zweite Aussparung (4B) aufweist; zumindest eine elektrisch leitfähige Leitstruktur (8), wobei die erste Kontaktfläche (2A) auf der von dem Träger (1) abgewandten Seite des Strahlungsemittierenden Halbleiterchips (2) angeordnet ist, die elektrisch isolierende Schicht (4) zumindest stellenweise auf den Träger (1) und dem Halbleiterchip (2) aufgebracht ist und die erste Aussparung (4A) im Bereich der ersten Kontaktfläche (2A) und die zweite Aussparung (4B) im Bereich der Kontaktstelle (1A) aufweist, die elektrisch leitfähige Leitstruktur (8) auf der elektrisch isolierenden Schicht (4) angeordnet ist und die erste Kontaktfläche (2A) mit der Kontaktstelle (1A) des Trägers (1) elektrisch kontaktiert, und die elektrisch isolierende Schicht (4) überwiegend mit einem keramischen Material gebildet ist.

## Beschreibung

### Optoelektronisches Modul

5 Es wird ein optoelektronisches Modul angegeben.

Eine zu lösende Aufgabe besteht darin, ein optoelektronisches Modul anzugeben, welches besonders alterungsstabil ist und eine hohe Lebensdauer aufweist.

10

Diese Patentanmeldung beansprucht die Priorität der deutschen Patentanmeldung 10 2009 042 205.6, deren Offenbarungsgehalt hiermit durch Rückbezug aufgenommen wird.

15

Gemäß zumindest einer Ausführungsform des optoelektronischen Moduls umfasst dieses einen Träger mit zumindest einer Kontaktstelle. Bei dem Träger kann es sich um eine Leiterplatte oder einen Trägerrahmen (Leadframe) handeln. Ebenso ist denkbar, dass der Träger flexibel und

20

beispielsweise als Folie ausgebildet ist. Der Träger kann mit einem elektrisch leitenden Material, beispielsweise einem Metall, oder einem elektrisch isolierenden Material,

beispielsweise einem duro- oder thermoplastischen oder auch einem keramischen Material, gebildet sein. Ist der Träger mit einem elektrisch isolierenden Material gebildet, ist denkbar, dass der Träger an einer Montagefläche und/oder einer der Montagefläche gegenüberliegenden Bodenfläche Anschlussstellen und Leiterbahnen aufweist. Die zumindest eine Kontaktstelle ist mit einem elektrisch leitfähigen Material, beispielsweise

25

einem Metall, gebildet.

30

Gemäß zumindest einer Ausführungsform umfasst das optoelektronische Modul einen strahlungsemittierenden

Halbleiterchip, wobei der strahlungsemittierende Halbleiterchip eine erste Kontaktfläche und eine zweite Kontaktfläche aufweist. Die beiden Kontaktflächen dienen zur Kontaktierung des strahlungsemittierenden Halbleiterchips.

- 5 Beispielsweise ist der strahlungsemittierende Halbleiterchip mit der zweiten Kontaktfläche auf einer Anschlussstelle des Trägers befestigt und elektrisch kontaktiert. Bei dem strahlungsemittierenden Halbleiterchip kann es sich beispielsweise um einen Lumineszenzdiodenchip handeln. Bei

- 10 dem Lumineszenzdiodenchip kann es sich um einen Leucht- oder Laserdiodenchip handeln, dessen strahlungserzeugende aktive Zone Strahlung im Bereich von ultraviolettem bis infrarotem Licht emittiert. Die erste und die zweite Kontaktfläche des strahlungsemittierenden Halbleiterchips sind vorzugsweise mit

- 15 einem elektrisch leitfähigen Material, beispielsweise einem Metall, gebildet.

Gemäß zumindest einer Ausführungsform umfasst das optoelektronische Modul eine elektrisch isolierende Schicht, die eine erste und eine zweite Aussparung aufweist. Beispielsweise sind die Aussparungen mittels eines Materialabtrags erzeugt. Die beiden Aussparungen sind dann zum Beispiel seitlich von der elektrisch isolierenden Schicht begrenzt und weisen jeweils zwei sich gegenüberliegende Öffnungen auf. Vorzugsweise sind die beiden Aussparungen dann von außen frei zugänglich.

Gemäß zumindest einer Ausführungsform des optoelektronischen Moduls ist die erste Kontaktfläche auf der von dem Träger abgewandten Seite des strahlungsemittierenden Halbleiterchips angeordnet. Beispielsweise ist die erste Kontaktfläche an der Oberfläche auf der von dem Träger abgewandten Seite des strahlungsemittierenden Halbleiterchips aufgebracht.

Gemäß zumindest einer Ausführungsform umfasst das optoelektronische Modul zumindest eine elektrisch leitfähige Leitstruktur. Bei der elektrisch leitfähigen Leitstruktur kann es sich beispielsweise um elektrische Leiterbahnen handeln, die bevorzugt mit einem Metall oder einer Metalllegierung gebildet sind. Ebenso ist denkbar, dass die elektrisch leitfähige Leitstruktur mit einem elektrisch leitfähigen Klebstoff oder einer Metallpaste gebildet ist.

10

Gemäß zumindest einer Ausführungsform des optoelektronischen Moduls ist die elektrisch isolierende Schicht zumindest stellenweise auf den Träger und den Halbleiterchip aufgebracht. Vorzugsweise ist die elektrisch isolierende Schicht an diesen Stellen formschlüssig angeformt, sodass sich zwischen der elektrisch isolierenden Schicht und den von der elektrisch isolierten Schicht bedeckten Stellen weder ein Spalt noch eine Unterbrechung ausbildet.

20

Ferner weist die elektrisch isolierende Schicht die erste Aussparung im Bereich der ersten Kontaktfläche und die zweite Aussparung im Bereich der Kontaktstelle auf. Aussparung und Kontaktfläche/Kontaktstelle sind somit zumindest stellenweise deckungsgleich zueinander angeordnet, sodass der strahlungsemittierende Halbleiterchip von außen durch die in der elektrisch isolierenden Schicht eingebrachten Aussparungen hindurch kontaktiert werden kann.

30

Gemäß zumindest einer Ausführungsform des optoelektronischen Moduls ist die elektrisch leitfähige Leitstruktur auf der elektrisch isolierenden Schicht angeordnet und kontaktiert die erste Kontaktfläche mit der Kontaktstelle des Trägers elektrisch. Vorzugsweise ist die elektrisch leitfähige

Leitstruktur an die elektrisch isolierende Schicht formschlüssig angeformt. Mit anderen Worten bildet sich vorzugsweise zwischen der elektrisch isolierenden Schicht und der elektrisch leitfähigen Leitstruktur weder ein Spalt noch 5 eine Unterbrechung aus. Dazu ist die elektrisch leitfähige Leitstruktur auf die elektrisch isolierende Schicht beispielsweise mittels Siebdruck, eines Jet- oder Dispensverfahrens oder eines Spritzverfahrens aufgebracht. Beispielsweise sind die Aussparungen zumindest stellenweise 10 mit der Leitstruktur gefüllt. Vorzugsweise durchdringt die elektrisch leitfähige Leitstruktur die Aussparungen, sodass die elektrisch leitfähige Leitstruktur mit dem Halbleiterchip vollständig kontaktiert ist. Die Aussparung ist zum Beispiel mit dem Material der elektrisch leitfähigen Leitstruktur 15 gefüllt.

Gemäß zumindest einer Ausführungsform des optoelektronischen Moduls ist die elektrisch isolierende Schicht überwiegend mit einem keramischen Material gebildet. "Überwiegend" heißt, 20 dass die elektrisch isolierende Schicht wenigstens 50 Gew-%, bevorzugt wenigstens 75 Gew-%, keramisches Material enthält. Denkbar ist in diesem Zusammenhang auch, dass die elektrisch isolierende Schicht vollständig aus einem keramischen Material besteht. Ferner ist es möglich, dass die elektrisch 25 isolierende Schicht aus einer Glaskeramik besteht, die aus einer Glasschmelze durch gesteuerte Kristallisation hergestellt ist.

Gemäß zumindest einer Ausführungsform umfasst das 30 optoelektronische Modul einen Träger mit zumindest einer Kontaktstelle und einen strahlungsemittierenden Halbleiterchip, wobei der strahlungsemittierende Halbleiterchip eine erste Kontaktfläche und eine zweite

Kontaktfläche aufweist. Ferner umfasst das optoelektronische Modul eine elektrisch isolierende Schicht, die eine erste und eine zweite Aussparung aufweist, sowie zumindest eine elektrisch leitfähige Leitstruktur. Die erste Kontaktfläche

5 ist auf der von dem Träger abgewandten Seite des strahlungsemittierenden Halbleiterchips angeordnet. Ferner ist die elektrisch isolierende Schicht zumindest stellenweise auf den Träger und den Halbleiterchip aufgebracht und weist die erste Aussparung im Bereich der ersten Kontaktfläche und

10 die zweite Aussparung im Bereich der zweiten Kontaktstelle auf. Die elektrisch leitfähige Leitstruktur ist auf der elektrisch isolierenden Schicht angeordnet und kontaktiert die erste Kontaktfläche mit der Kontaktstelle des Trägers elektrisch. Ferner ist die elektrisch isolierende Schicht

15 überwiegend mit einem keramischen Material gebildet.

Das hier beschriebene optoelektronische Modul beruht dabei unter anderem auf der Erkenntnis, dass eine mit organischen Materialien gebildete elektrisch isolierende Schicht, die

20 beispielsweise bei optoelektronischen Modulen mit planarer Kontaktierung Verwendung findet, wenig alterungsstabil ist. Das heißt, dass externe Einflüsse wie beispielsweise Bestrahlung, Feuchtigkeit oder Temperaturschwankungen das Material der elektrisch isolierenden Schicht beschädigen.

25 Dies führt bereits nach kurzer Betriebsdauer des optoelektronischen Moduls beispielsweise zu einer brüchigen elektrisch isolierenden Schicht. Das heißt, dass ein solches optoelektronisches Modul bereits nach kurzer Betriebsdauer alterungsbedingte Schäden aufweisen kann.

30

Um ein optoelektronisches Modul zu schaffen, welches besonders alterungsstabil ist, macht das hier beschriebene optoelektronische Modul unter anderem von der Idee Gebrauch,

die elektrisch isolierende Schicht überwiegend mit einem keramischen Material zu bilden. Keramische Materialien sind insbesondere bei äußerer Strahlungs- und Hitzeinwirkung alterungsstabiler, wodurch eine solche elektrisch isolierende Schicht selbst unter starker äußerer Beanspruchung auch nach längerer Betriebsdauer kaum Materialschäden aufweist.

Vorteilhaft wird so ein optoelektronisches Modul geschaffen, welches eine stark erhöhte Lebensdauer aufweist.

10

Gemäß zumindest einer Ausführungsform umfasst das optoelektronische Modul zumindest zwei strahlungsemittierende Halbleiterchips, wobei die elektrisch isolierende Schicht stellenweise zwischen den strahlungsemittierenden

15 Halbleiterchips angeordnet ist. Beispielsweise sind zwischen den Halbleiterchips Zwischenräume ausgebildet. Mit anderen Worten sind die Halbleiterchips dann beabstandet zueinander angeordnet. Beispielsweise sind die Zwischenräume mit dem Material der elektrisch isolierenden Schicht gefüllt.

20 Vorzugsweise berührt dann die elektrisch isolierende Schicht Seitenflächen der Halbleiterchips und bedeckt diese formschlüssig.

Gemäß zumindest einer Ausführungsform des optoelektronischen Moduls ist die elektrisch isolierende Schicht bis auf die Aussparungen formschlüssig auf die freiliegenden Außenflächen des optoelektronischen Moduls aufgebracht. Das heißt, dass sich zwischen den freiliegenden Außenflächen des optoelektronischen Moduls und der elektrisch isolierenden

30 Schicht weder ein Spalt noch eine Unterbrechung ausbildet. Die elektrisch isolierende Schicht übernimmt in diesem Fall die Funktion einer Einkapselungsschicht, beispielsweise der strahlungsemittierenden Halbleiterchips. Das kann heißen,

dass die Halbleiterchips von der elektrisch isolierenden Schicht bis auf Bereiche der elektrischen Kontaktierung vollständig eingekapselt sind. Dadurch erfolgt vorteilhaft ein Schutz der strahlungsemittierenden Halbleiterchips vor 5 mechanischen Einflüssen, wie beispielsweise Stößen.

Gemäß zumindest einer Ausführungsform des optoelektronischen Moduls ist die elektrisch isolierende Schicht strahlungsdurchlässig und bedeckt eine 10 Strahlungsaustrittsfläche des Halbleiterchips stellenweise. "Strahlungsdurchlässig" bedeutet, dass die elektrisch isolierende Schicht bevorzugt die von der aktiven Schicht emittierte Strahlung lediglich teilweise absorbiert. Die von den strahlungsemittierenden Halbleiterchips emittierte 15 elektromagnetische Strahlung kann so zumindest teilweise durch die elektrisch isolierende Schicht aus dem optoelektronischen Modul ausgekoppelt werden.

Gemäß zumindest einer Ausführungsform des optoelektronischen 20 Moduls besteht die elektrisch isolierende Schicht aus einem keramischen Leuchtstoff. Ist die elektrisch isolierende Schicht stellenweise auf die Strahlungsaustrittsfläche des Halbleiterchips aufgebracht, so kann die elektrisch isolierende Schicht von dem Halbleiterchip primär emittierte 25 elektromagnetische Strahlung teilweise absorbieren und zumindest teilweise die primär emittierte Strahlung in Strahlung anderer Wellenlänge umwandeln und wieder reemittieren. Die elektrisch isolierende Schicht hat also die Funktion eines Lichtkonverters. Beispielsweise besteht die 30 elektrisch isolierende Schicht dann aus YAG:Ce.

Gemäß zumindest einer Ausführungsform des optoelektronischen Moduls verläuft die erste Aussparung in der elektrisch

isolierenden Schicht durchgängig zwischen der Strahlungsaustrittsfläche des Halbleiterchips und dem Träger entlang von Seitenflächen des Halbleiterchips und ist seitlich durch die Kontaktfläche und den Träger begrenzt. Das 5 kann heißen, dass die Strahlungsaustrittsfläche sowie eine oder mehrere der Seitenflächen des Halbleiterchips zumindest stellenweise "freiliegen".

Gemäß zumindest einer Ausführungsform des optoelektronischen 10 Moduls verläuft die erste Aussparung in der elektrisch isolierenden Schicht durchgängig zwischen benachbarten Halbleiterchips und ist durch die Kontaktflächen seitlich begrenzt. "Benachbart" heißt in diesem Zusammenhang, dass die Halbleiterchips beispielsweise paarweise angeordnet sind und 15 jedes Paar zwischen sich den Zwischenraum ausbildet. Der Zwischenraum ist nicht von der elektrisch leitenden Schicht abgedeckt und somit "freiliegend". Ferner ist in diesem Zusammenhang denkbar, dass neben dem freiliegenden Zwischenraum ebenso stellenweise die 20 Strahlungsaustrittsflächen der Halbleiterchips frei von der elektrisch isolierenden Schicht sind.

Gemäß zumindest einer Ausführungsform des optoelektronischen Moduls ist zwischen den Halbleiterchips eine 25 Isolationsschicht angeordnet. Beispielsweise füllt die Isolationsschicht die Zwischenräume zwischen den Halbleiterchips zumindest stellenweise formschlüssig aus. Ferner ist denkbar, dass die Isolationsschicht und die elektrisch isolierende Schicht mit dem gleichen Material 30 gebildet sind.

Gemäß zumindest einer Ausführungsform des optoelektronischen Moduls ist die elektrisch isolierende Schicht eine Folie.

Vorzugsweise weist die elektrisch isolierende Schicht dann eine Schichtdicke von 10 bis 300 µm, vorzugsweise von 150 µm, auf. Ebenso ist es möglich, dass die elektrisch isolierende Schicht aus einer Vielzahl einzelner Folien besteht, die 5 übereinander angeordnet, beispielsweise aufgeklebt, sein können und so einen stapelförmigen Folienverbund ausbilden. In diesem Zusammenhang ist es denkbar, dass es sich bei den Folien um Hybridfolien oder auch um Multilayerfolien handelt. "Hybridfolien" bezeichnet beispielsweise eine Folie, die mit 10 einem keramischen Material in einer Polymermatrix gebildet ist. "Multilayerfolien" sind beispielsweise Keramikfolien mit einer Kleberbeschichtung.

Gemäß zumindest einer Ausführungsform des optoelektronischen Moduls ist die elektrisch isolierende Schicht mittels eines 15 Laminierprozesses aufgebracht. Handelt es sich bei der elektrisch isolierenden Schicht um eine Folie, so kann sie mittels des Laminierprozesses auf freiliegende Außenflächen, beispielsweise der Halbleiterchips und der Montagefläche des 20 Trägers, auflaminert werden.

Gemäß zumindest einer Ausführungsform des optoelektronischen Moduls ist die elektrisch isolierende Schicht mittels eines Sinterprozesses aufgebracht. Beispielsweise wird dazu das 25 aufgebrachte Material der elektrisch isolierenden Schicht mittels hoch energetischem Laserlichts oder mittels thermischen Sinterns ausgeformt. Dazu liegt das Material der elektrisch isolierenden Schicht beispielsweise in Form eines Nanopulvers oder eines Composites vor.

30

Gemäß zumindest einer Ausführungsform ist die elektrisch isolierende Schicht mittels eines Mold-Prozesses aufgebracht. Beispielsweise wird dazu vor dem Aufbringen des Materials der

elektrisch isolierenden Schicht ein Stempel auf die Kontaktstellen/-flächen aufgebracht der die Kontaktstellen/-flächen abdeckt. In einem weiteren Schritt kann dann das Material der elektrisch isolierenden Schicht aufgespritzt

5 werden. Nach dem Aushärten können dann die Stempel entfernt werden, wodurch die Aussparungen in der elektrisch isolierenden Schicht freigelegt werden. Vorzugsweise liegt dann das Material der elektrisch isolierenden Schicht in Form einer Dispersion oder eines Aerosols vor.

10

Bei den Merkmalen, wonach die elektrisch isolierende Schicht über einen Laminierprozess, einen Sinterprozess oder einen Mold-Prozess aufgebracht ist, handelt es sich um jeweils gegenständliche Merkmale, da die Aufbringungsmethode direkt

15 am optoelektronischen Modul nachweisbar ist.

Ebenso ist denkbar, dass die elektrisch isolierende Schicht aufgesprüht wird. Dazu liegt das Material der elektrisch isolierenden Schicht beispielsweise in flüchtiger Lösung oder

20 in einer Polymermatrix vor.

Ferner kann das Material der elektrisch isolierenden Schicht mittels selektivem Abscheiden, zum Beispiel mittels eines Plasmaprozesses, eines Plasma-Spray-Prozesses oder mittels

25 Sputtern aufgebracht werden.

Ebenso ist denkbar, dass die elektrisch isolierende Schicht mittels eines Schablonendruckverfahrens aufgebracht ist. Dazu wird eine vorgefertigte Schablone auf den Träger und die

30 Halbleiterchips aufgelegt, welche beispielsweise im Bereich der Kontaktstellen/-flächen Abdeckungen aufweist. Mittels eines derartigen Schablonenrasters bleiben nach dem Aufdrucken des Materials Bereiche vom Material der elektrisch

isolierenden Schicht frei, die dann die Aussparungen der elektrisch isolierenden Schicht bilden.

Im Folgenden wird das hier beschriebene optoelektronische

5 Modul anhand von Ausführungsbeispielen und den dazugehörigen Figuren näher erläutert.

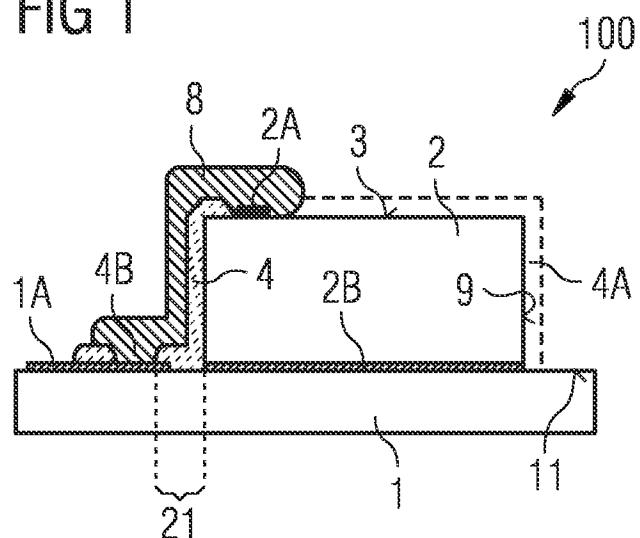

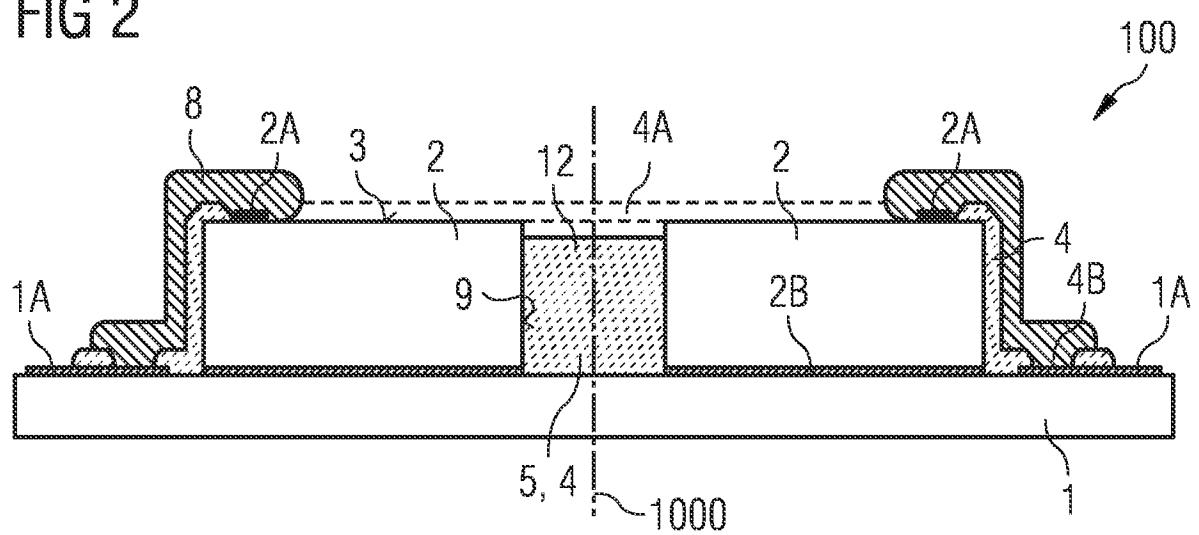

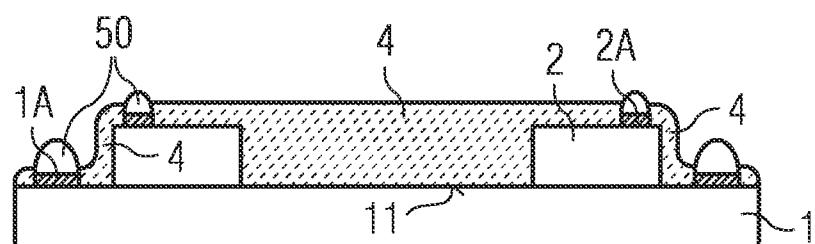

Die Figuren 1 und 2 zeigen schematische Ansichten von

Ausführungsbeispielen eines hier beschriebenen

10 optoelektronischen Moduls.

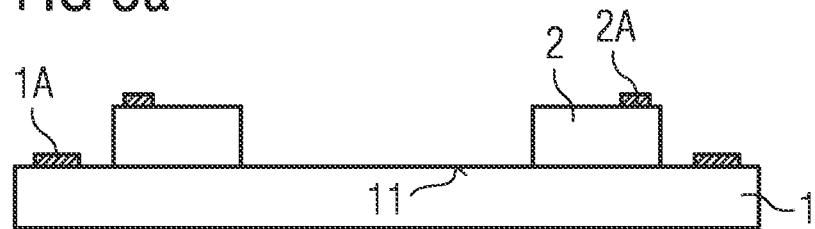

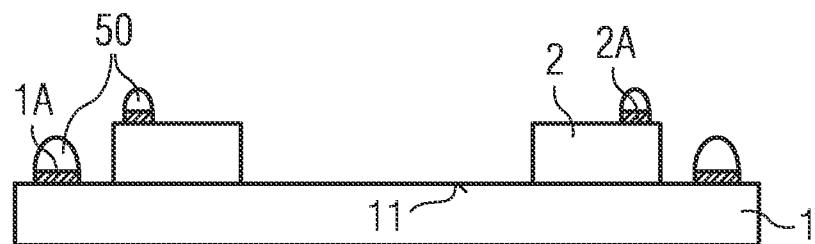

Die Figuren 3a bis 3d zeigen einzelne Fertigungsschritte zur Herstellung eines Ausführungsbeispiels eines hier beschriebenen optoelektronischen Moduls.

15

In den Ausführungsbeispielen und den Figuren sind gleiche oder gleich wirkende Bestandteile jeweils mit den gleichen Bezugszeichen versehen. Die dargestellten Elemente sind nicht als maßstabsgerecht anzusehen, vielmehr können einzelne

20

Elemente zum besseren Verständnis übertrieben groß dargestellt sein.

Die Figur 1 zeigt in einer schematischen Seitenansicht ein Ausführungsbeispiel eines hier beschriebenen

25

optoelektronischen Moduls 100. Ein Träger 1 weist eine Kontaktstelle 1A auf. Auf eine Montagefläche 11 ist ein strahlungsemittierender Halbleiterchip 2 aufgebracht, der eine aktive Zone zur Erzeugung von elektromagnetischer Strahlung aufweist. Ferner weist der strahlungsemittierende Halbleiterchip 2 eine erste Kontaktfläche 2A und eine zweite Kontaktfläche 2B auf. Der strahlungsemittierende Halbleiterchip 2 ist mit seiner zweiten Kontaktfläche 2A auf die Montagefläche 11 des Trägers 1 aufgebracht und dort mit

dem Träger 1 elektrisch kontaktiert. Beispielsweise ist der strahlungsemittierende Halbleiterchip 2 aufgeklebt oder mittels eines Lotmaterials mit dem Träger 1 verbunden. Auf freiliegende Seitenflächen 9 des Halbleiterchips 2 sowie eine 5 Strahlungsaustrittsfläche 3 des Halbleiterchips 2 ist stellenweise eine elektrisch isolierende Schicht 4 formschlüssig aufgebracht. Ferner bedeckt die elektrisch isolierende Schicht 4 die Montagefläche 11 des Trägers 1 im Bereich 21, sodass die elektrisch isolierende Schicht 4 10 zwischen der Kontaktstelle 1A und der ersten Kontaktfläche 2A ohne Unterbrechung verläuft. Die elektrisch isolierende Schicht 4 weist eine erste Aussparung 4A auf, die durchgängig zwischen der Strahlungsaustrittsfläche 3 entlang der Seitenfläche 9 bis zum Träger 1 hin verläuft. Die erste 15 Aussparung 4A ist daher von dem Träger 1 und der ersten Kontaktfläche 2A seitlich begrenzt. Die Strahlungsaustrittsfläche 3 des strahlungsemittierenden Halbleiterchips 2 ist dann stellenweise frei von der elektrisch isolierenden Schicht 4. Eine elektrisch leitfähige 20 Leitstruktur 8 kontaktiert die erste Kontaktfläche 2A mit der Kontaktstelle 1A des Trägers 1 elektrisch. Vorliegend ist die elektrisch leitfähige Leitstruktur 8 auf die elektrisch isolierende Schicht 4 und den beiden Kontaktflächen 1A und 2A aufgedruckt. Bei der elektrisch isolierenden Schicht 4 25 handelt es sich vorliegend um eine Folie, die mittels eines Laminierprozesses aufgebracht ist. In dem Ausführungsbeispiel gemäß Figur 1 besteht die elektrisch isolierende Schicht 4 aus einem keramischen Material. Ebenso ist denkbar, dass die elektrisch isolierende Schicht 4 aus einem keramischen 30 Leuchtstoff besteht und die elektrisch isolierende Schicht 4 zumindest teilweise von vom strahlungsemittierenden Halbleiterchip 2 primär emittierte elektromagnetische

Strahlung in Strahlung anderer Wellenlänge umwandelt, sodass das optoelektronische Modul 100 Mischlicht emittiert.

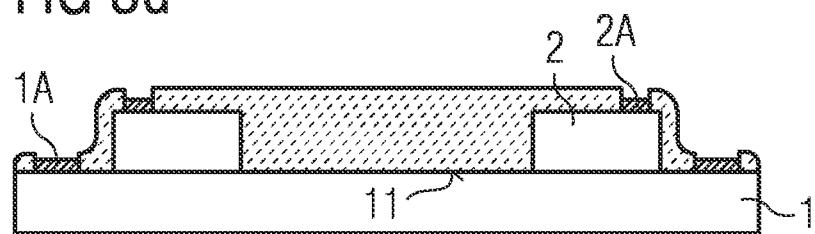

Die Figur 2 zeigt das optoelektronische Modul 100 mit zwei nebeneinander angeordneten strahlungsemittierenden Halbleiterchips 2. Die Halbleiterchips 2 bilden zwischen sich einen Zwischenraum 12 aus, der seitlich jeweils durch die Seitenflächen 9 sowie durch den Träger 1 begrenzt ist. In dem Zwischenraum 12 ist eine Isolationsschicht 5 angeordnet, die den Zwischenraum 12 zumindest stellenweise ausfüllt und formschlüssig auf die Seitenflächen 9 und den Träger 1 aufgebracht ist. Ebenso ist denkbar, dass anstatt oder zusätzlich zur Isolationsschicht 5 die elektrisch isolierende Schicht 4 in den Zwischenraum 12 eingebracht ist. Die erste Aussparung 4A verläuft ohne Unterbrechung zwischen den beiden Halbleiterchips 2 und ist durch die Kontaktflächen 2A seitlich begrenzt. Dies hat zur Folge, dass die Strahlungsaustrittsflächen 3 der Halbleiterchips zumindest stellenweise freiliegen.

20

Die Figuren 3a bis 3d zeigen einzelne Fertigungsschritte zur Herstellung eines Ausführungsbeispiels eines hier beschriebenen optoelektronischen Moduls 100. Dazu wird zunächst, wie in der Figur 3a dargestellt, der Träger 1 bereitgestellt, wobei auf die Montagefläche 11 des Trägers 1 die Halbleiterchips 2 aufgebracht sind.

In einem weiteren Schritt werden, wie in der Figur 3b gezeigt, die Kontaktflächen 1A des Trägers 1 und die Kontaktflächen 2A der Halbleiterchips 2 mit einem Lack 50 abgedeckt. Alternativ können die Kontaktflächen mit Folien, einem Wachs oder anderen Haftungsschichten abgedeckt werden.

Gemäß der Figur 3c wird in einem weiteren Schritt auf freiliegende Außenflächen des optoelektronischen Moduls 100 das Material der elektrisch isolierenden Schicht 4 aufgebracht, sodass die Seitenflächen 9 und die

- 5 Strahlungsaustrittsflächen 3 zumindest stellenweise mit der elektrisch isolierenden Schicht 4 bedeckt sind. Das Aufbringen kann beispielsweise mittels eines Sinter- oder Moldprozesses geschehen. Ebenso ist denkbar, dass die elektrisch isolierende Schicht 4 mittels eines

10 Laminierprozesses oder eines Sprühprozesses aufgebracht wird.

Ferner kann das Material der elektrisch isolierenden Schicht 4 mittels selektivem Abscheiden, zum Beispiel mittels eines Plasmaprozesses, eines Plasma-Spray-Prozesses oder mittels

15 Sputtern aufgebracht werden.

In einem weiteren Schritt wird in der Figur 3d mittels eines physikalischen und/oder mechanischen Materialabtrags der Lack 50 entfernt, sodass zumindest die Kontaktflächen 1A und 2A

20 freiliegen.

Die Strahlungsaustrittsflächen 3 sind dann mit dem Material der elektrisch isolierenden Schicht 4 bis auf die Stellen, an denen die Kontaktflächen 2A verlaufen, vollständig bedeckt,

25 wobei vorliegend die elektrisch isolierende Schicht 4 mit einer strahlungsdurchlässigen Keramik gebildet ist oder aus einem keramischen Leuchtstoff besteht.

In einem letzten Schritt kann die Ankontaktierung der

30 Halbleiterchips 2 über die elektrisch leitfähigen Leitstrukturen 8 an Stellen der Kontaktstellen 1A und 2A erfolgen.

Alternativ kann die Aufbringung der elektrisch isolierenden Schicht 4 mittels der Verwendung einer vorstrukturierten Maske erfolgen. Beispielsweise kann die elektrisch isolierende Schicht 4 dann durch einen Sprühprozess, zum

5 Beispiel mittels Plasmaabscheidung, aufgebracht werden.

Die Erfindung ist nicht durch die Beschreibung anhand der Ausführungsbeispiele beschränkt. Vielmehr umfasst die Erfindung jedes neue Merkmal sowie jede Kombination von

10 Merkmalen, was insbesondere jede Kombination von Merkmalen in den Patentansprüchen beinhaltet, auch wenn dieses Merkmal oder diese Kombination selbst nicht explizit in den Patentansprüchen oder den Ausführungsbeispielen angegeben ist.

## Patentansprüche

1. Optoelektronisches Modul (100), umfassend

- einen Träger (1) mit zumindest einer Kontaktstelle (1A);

5 - einen strahlungsemittierenden Halbleiterchip (2), wobei der strahlungsemittierende Halbleiterchip (2) eine erste Kontaktfläche (2A) und eine zweite Kontaktfläche (2B) aufweist;

10 - eine elektrisch isolierende Schicht (4), die eine erste (4A) und eine zweite Aussparung (4B) aufweist;

- zumindest eine elektrisch leitfähige Leitstruktur (8), wobei

- die erste Kontaktfläche (2A) auf der von dem Träger (1) abgewandten Seite des strahlungsemittierenden Halbleiterchips

15 (2) angeordnet ist,

- die elektrisch isolierende Schicht (4) zumindest stellenweise auf den Träger (1) und dem Halbleiterchip (2) aufgebracht ist und die erste Aussparung (4A) im Bereich der ersten Kontaktfläche (2A) und die zweite Aussparung (4B) im

20 Bereich der Kontaktstelle (1A) aufweist,

- die elektrisch leitfähige Leitstruktur (8) auf der elektrisch isolierenden Schicht (4) angeordnet ist und die erste Kontaktfläche (2A) mit der Kontaktstelle (1A) des Trägers (1) elektrisch kontaktiert, und

25 - die elektrisch isolierende Schicht (4) überwiegend mit einem keramischen Material gebildet ist.

2. Optoelektronisches Modul (100) nach dem vorhergehenden Anspruch,

30 mit zumindest zwei strahlungsemittierenden Halbleiterchips (2), wobei die elektrisch isolierende Schicht (4) stellenweise zwischen den strahlungsemittierenden Halbleiterchips (2) angeordnet ist.

3. Optoelektronisches Modul (100) nach einem der vorhergehenden Ansprüche,

bei dem die elektrisch isolierende Schicht (4) bis auf die Aussparungen (4A, 4B) formschlüssig auf die freiliegenden

5 Außenflächen des optoelektronischen Moduls (100) aufgebracht ist.

4. Optoelektronisches Modul (100) nach einem der vorhergehenden Ansprüche,

10 bei dem die elektrisch isolierende Schicht (4) strahlungsdurchlässig ist und eine Strahlungsaustrittsfläche (3) des Halbleiterchips (2) stellenweise bedeckt.

5. Optoelektronisches Modul (100) nach einem der vorhergehenden Ansprüche,

15 bei dem die elektrisch isolierende Schicht (4) aus einem keramischen Leuchtstoff besteht.

6. Optoelektronisches Modul (100) nach einem der

20 vorhergehenden Ansprüche,

bei dem die erste Aussparung (4A) in der elektrisch isolierenden Schicht (4) durchgängig zwischen der Strahlungsaustrittsfläche (3) des Halbleiterchips (2) und dem Träger (1) entlang von Seitenflächen (9) des Halbleiterchips 25 verläuft und durch die ersten Kontaktflächen (2A) und den Träger (1) seitlich begrenzt ist.

7. Optoelektronisches Modul (100) nach einem der vorhergehenden Ansprüche,

30 bei dem sich die erste Aussparung (4A) in der elektrisch isolierenden Schicht (4) durchgängig zwischen benachbarten Halbleiterchips (2) verläuft und durch die Kontaktflächen (2A) seitlich begrenzt ist.

8. Optoelektronisches Modul (100) nach einem der vorhergehenden Ansprüche,

bei dem zwischen den Halbleiterchips (2) eine Isolationsschicht (5) angeordnet ist.

5

9. Optoelektronisches Modul (100) nach einem der vorhergehenden Ansprüche,

bei dem die elektrisch isolierende Schicht (4) eine Folie ist.

10

10. Optoelektronisches Modul (100) nach dem vorhergehenden Anspruch,

bei dem die elektrisch isolierende Schicht (4) mittels eines Laminierprozesses aufgebracht ist.

15

11. Optoelektronisches Modul (100) nach einem der Ansprüche 1 bis 8,

bei dem die elektrisch isolierende Schicht (4) mittels eines Sinterprozesses aufgebracht ist.

20

12. Optoelektronisches Modul (100) nach einem der Ansprüche 1 bis 8,

bei dem die elektrische isolierende Schicht (4) mittels eines Moldprozesses aufgebracht ist.

FIG 1

FIG 2

**FIG 3a****FIG 3b****FIG 3c****FIG 3d**

# INTERNATIONAL SEARCH REPORT

International application No

PCT/EP2010/063035

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. H01L25/075 H01L33/44

ADD. H01L33/50 H01L33/62

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

**H01L H01K**

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

**EPO-Internal**

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                  | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | WO 2007/025521 A2 (OSRAM OPTO SEMICONDUCTORS GMBH [DE]; WEIDNER KARL [DE]) 8 March 2007 (2007-03-08)<br>page 6, line 32 – page 8, line 33; figure 1 | 1,3,4,6               |

| Y         | DE 10 2008 019902 A1 (OSRAM OPTO SEMICONDUCTORS GMBH [DE])<br>25 June 2009 (2009-06-25)<br>paragraph [0053] – paragraph [0060]; figures 1,2         | 1-12                  |

| A         | US 2007/241661 A1 (YIN CHUA B [MY])<br>18 October 2007 (2007-10-18)<br>paragraph [0021] – paragraph [0025]                                          | 5                     |

|           | -----<br>-/-                                                                                                                                        |                       |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*&\* document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

21 December 2010

29/12/2010

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Ott, André

**INTERNATIONAL SEARCH REPORT**International application No

PCT/EP2010/063035**C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                               | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | DE 10 2007 011123 A1 (OSRAM OPTO SEMICONDUCTORS GMBH [DE])<br>11 September 2008 (2008-09-11)<br>paragraphs [0034] - [0038]; figures 1,2<br>----- | 1-12                  |

# INTERNATIONAL SEARCH REPORT

Information on patent family members

|                              |

|------------------------------|

| International application No |

| PCT/EP2010/063035            |

| Patent document cited in search report | Publication date | Patent family member(s)                                                                                          |  | Publication date                                                                 |

|----------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------|

| WO 2007025521 A2                       | 08-03-2007       | CN 101253623 A<br>DE 102005041099 A1<br>EP 1920462 A2<br>JP 2009506558 T<br>KR 20080039904 A<br>US 2009278157 A1 |  | 27-08-2008<br>29-03-2007<br>14-05-2008<br>12-02-2009<br>07-05-2008<br>12-11-2009 |

| DE 102008019902 A1                     | 25-06-2009       | CN 101904005 A<br>WO 2009079985 A2<br>EP 2223337 A2<br>KR 20100114042 A<br>US 2010301355 A1                      |  | 01-12-2010<br>02-07-2009<br>01-09-2010<br>22-10-2010<br>02-12-2010               |

| US 2007241661 A1                       | 18-10-2007       | NONE                                                                                                             |  |                                                                                  |

| DE 102007011123 A1                     | 11-09-2008       | CN 101636839 A<br>WO 2008106941 A1<br>EP 2130225 A1<br>KR 20090117905 A<br>US 2010117103 A1                      |  | 27-01-2010<br>12-09-2008<br>09-12-2009<br>13-11-2009<br>13-05-2010               |

# INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/EP2010/063035

**A. KLASIFIZIERUNG DES ANMELDUNGSGEGENSTANDES**

INV. H01L25/075 H01L33/44

ADD. H01L33/50 H01L33/62

Nach der Internationalen Patentklassifikation (IPC) oder nach der nationalen Klassifikation und der IPC

**B. RECHERCHIERTE GEBIETE**

Recherchierte Mindestprüfstoff (Klassifikationssystem und Klassifikationssymbole )

**H01L H01K**

Recherchierte, aber nicht zum Mindestprüfstoff gehörende Veröffentlichungen, soweit diese unter die recherchierten Gebiete fallen

Während der internationalen Recherche konsultierte elektronische Datenbank (Name der Datenbank und evtl. verwendete Suchbegriffe)

**EPO-Internal**

**C. ALS WESENTLICH ANGESEHENE UNTERLAGEN**

| Kategorie* | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile                                                            | Betr. Anspruch Nr. |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| X          | WO 2007/025521 A2 (OSRAM OPTO SEMICONDUCTORS GMBH [DE]; WEIDNER KARL [DE]) 8. März 2007 (2007-03-08)<br>Seite 6, Zeile 32 – Seite 8, Zeile 33;<br>Abbildung 1 | 1,3,4,6            |

| Y          | DE 10 2008 019902 A1 (OSRAM OPTO SEMICONDUCTORS GMBH [DE])<br>25. Juni 2009 (2009-06-25)<br>Absatz [0053] – Absatz [0060]; Abbildungen<br>1,2                 | 1-12               |

| Y          | DE 10 2008 019902 A1 (OSRAM OPTO SEMICONDUCTORS GMBH [DE])<br>25. Juni 2009 (2009-06-25)<br>Absatz [0053] – Absatz [0060]; Abbildungen<br>1,2                 | 1-12               |

| A          | US 2007/241661 A1 (YIN CHUA B [MY])<br>18. Oktober 2007 (2007-10-18)<br>Absatz [0021] – Absatz [0025]                                                         | 5                  |

|            |                                                                                                                                                               | -/-                |

Weitere Veröffentlichungen sind der Fortsetzung von Feld C zu entnehmen

Siehe Anhang Patentfamilie

- \* Besondere Kategorien von angegebenen Veröffentlichungen :

"A" Veröffentlichung, die den allgemeinen Stand der Technik definiert, aber nicht als besonders bedeutsam anzusehen ist

"E" älteres Dokument, das jedoch erst am oder nach dem internationalen Anmeldedatum veröffentlicht worden ist

"L" Veröffentlichung, die geeignet ist, einen Prioritätsanspruch zweifelhaft erscheinen zu lassen, oder durch die das Veröffentlichungsdatum einer anderen im Recherchenbericht genannten Veröffentlichung belegt werden soll oder die aus einem anderen besonderen Grund angegeben ist (wie ausgeführt)

"O" Veröffentlichung, die sich auf eine mündliche Offenbarung, eine Benutzung, eine Ausstellung oder andere Maßnahmen bezieht

"P" Veröffentlichung, die vor dem internationalen Anmeldedatum, aber nach dem beanspruchten Prioritätsdatum veröffentlicht worden ist

- "T" Spätere Veröffentlichung, die nach dem internationalen Anmeldedatum oder dem Prioritätsdatum veröffentlicht worden ist und mit der Anmeldung nicht kollidiert, sondern nur zum Verständnis des der Erfindung zugrundeliegenden Prinzips oder der ihr zugrundeliegenden Theorie angegeben ist

"X" Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann allein aufgrund dieser Veröffentlichung nicht als neu oder auf erforderlicher Tätigkeit beruhend betrachtet werden

"Y" Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann nicht als auf erforderlicher Tätigkeit beruhend betrachtet werden, wenn die Veröffentlichung mit einer oder mehreren anderen Veröffentlichungen dieser Kategorie in Verbindung gebracht wird und diese Verbindung für einen Fachmann nahelegend ist

"&" Veröffentlichung, die Mitglied derselben Patentfamilie ist

|                                                     |                                                     |

|-----------------------------------------------------|-----------------------------------------------------|

| Datum des Abschlusses der internationalen Recherche | Absendedatum des internationalen Recherchenberichts |

| 21. Dezember 2010                                   | 29/12/2010                                          |

|                                                                                                                                                                                              |                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Name und Postanschrift der Internationalen Recherchenbehörde<br>Europäisches Patentamt, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016 | Bevollmächtigter Bediensteter<br><br>Ott, André |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

**INTERNATIONALER RECHERCHENBERICHT**Internationales Aktenzeichen

PCT/EP2010/063035**C. (Fortsetzung) ALS WESENTLICH ANGESEHENE UNTERLAGEN**

| Kategorie* | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile                                                 | Betr. Anspruch Nr. |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| A          | DE 10 2007 011123 A1 (OSRAM OPTO SEMICONDUCTORS GMBH [DE])<br>11. September 2008 (2008-09-11)<br>Absätze [0034] - [0038]; Abbildungen 1,2<br>----- | 1-12               |

**INTERNATIONALER RECHERCHENBERICHT**

Angaben zu Veröffentlichungen, die zur selben Patentfamilie gehören

Internationales Aktenzeichen

PCT/EP2010/063035

| Im Recherchenbericht angeführtes Patentdokument | Datum der Veröffentlichung | Mitglied(er) der Patentfamilie                                                                                   | Datum der Veröffentlichung                                                       |

|-------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| WO 2007025521 A2                                | 08-03-2007                 | CN 101253623 A<br>DE 102005041099 A1<br>EP 1920462 A2<br>JP 2009506558 T<br>KR 20080039904 A<br>US 2009278157 A1 | 27-08-2008<br>29-03-2007<br>14-05-2008<br>12-02-2009<br>07-05-2008<br>12-11-2009 |

| DE 102008019902 A1                              | 25-06-2009                 | CN 101904005 A<br>WO 2009079985 A2<br>EP 2223337 A2<br>KR 20100114042 A<br>US 2010301355 A1                      | 01-12-2010<br>02-07-2009<br>01-09-2010<br>22-10-2010<br>02-12-2010               |

| US 2007241661 A1                                | 18-10-2007                 | KEINE                                                                                                            |                                                                                  |

| DE 102007011123 A1                              | 11-09-2008                 | CN 101636839 A<br>WO 2008106941 A1<br>EP 2130225 A1<br>KR 20090117905 A<br>US 2010117103 A1                      | 27-01-2010<br>12-09-2008<br>09-12-2009<br>13-11-2009<br>13-05-2010               |