(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-16024

(P2008-16024A)

(43) 公開日 平成20年1月24日(2008.1.24)

| (51) Int.C1.      | F 1              | テーマコード (参考)          |

|-------------------|------------------|----------------------|

| <b>G06F 3/06</b>  | <b>(2006.01)</b> | G06F 3/06 302A 5B005 |

| <b>G06F 12/08</b> | <b>(2006.01)</b> | G06F 3/06 540 5B065  |

|                   |                  | G06F 12/08 501F      |

|                   |                  | G06F 12/08 557       |

|                   |                  | G06F 12/08 543B      |

審査請求 未請求 請求項の数 19 O L 外国語出願 (全 15 頁)

|              |                              |          |                                                                      |

|--------------|------------------------------|----------|----------------------------------------------------------------------|

| (21) 出願番号    | 特願2007-172478 (P2007-172478) | (71) 出願人 | 500373758<br>シーゲイト テクノロジー エルエルシー                                     |

| (22) 出願日     | 平成19年6月29日 (2007.6.29)       |          | アメリカ合衆国, カリフォルニア, スコット<br>バレイ, ピー. オー. ボックス 66<br>360, ディスク ドライブ 920 |

| (31) 優先権主張番号 | 11/480, 128                  | (74) 代理人 | 100066692<br>弁理士 浅村 翔                                                |

| (32) 優先日     | 平成18年6月30日 (2006.6.30)       | (74) 代理人 | 100072040<br>弁理士 浅村 肇                                                |

| (33) 優先権主張国  | 米国(US)                       | (74) 代理人 | 100091339<br>弁理士 清水 邦明                                               |

|              |                              | (74) 代理人 | 100094673<br>弁理士 林 銀三                                                |

最終頁に続く

(54) 【発明の名称】キャッシュされたデータのダイナミック適応キャッシング

## (57) 【要約】

【課題】キャッシュされたライトバックデータを記憶アレイにキャッシングする方法および装置を得る。

【解決手段】ライトバックデータのセットが記憶アレイの異なる場所にわたってデータの実質的に均一な分布を維持する目的でキャッシュメモリ内に整列して蓄積される。その後、データの整列されたセットは実質的にライトバックデータの付加セットがホストによりキャッシングメモリへ提供されるレートでキャッシングメモリから記憶アレイへ転送される。好ましくは、各ライトバックデータは複数の隣接データブロックを含み、好ましくは記憶アレイに関してデータの選択された近接範囲内の別個のアクセスコマンドの操作と共に記憶装置に書き込まれる(キャッシングされる)。好ましくは、アレイ内のライトバックデータの各セットに対してストライプデータ記述子(SDD)が維持される。

【選択図】図8

**【特許請求の範囲】****【請求項 1】**

記憶アレイの場所に関して記憶アレイ内のライトバックデータのセットのアレイを形成するステップと、実質的にライトバックデータの付加セットがホストによりキャッシュメモリへ提供されるレートでライトバックデータの前記セットをキャッシュメモリから記憶アレイへ転送するステップと、を含む方法。

**【請求項 2】**

請求項 1 に記載の方法であって、ライトバックデータの各セットは複数の隣接データブロックを含む方法。

**【請求項 3】**

請求項 1 に記載の方法であって、転送ステップは記憶アレイのトランステューサを記録媒体に隣接する選択された場所へ移動させて選択されたアクセスコマンドをサービスするステップと、選択されたアクセスコマンドの選択された場所とライトバックデータの選択されたセットに対する関連場所との近接に関してライトバックデータの選択されたセットをキャッシュメモリから媒体へ転送するステップと、を含む方法。

**【請求項 4】**

請求項 3 に記載の方法であって、前記近接はトランステューサの選択されたシーク長を含む方法。

**【請求項 5】**

請求項 1 に記載の方法であって、さらに、アレイ内のライトバックデータの各セットに対してストライプデータ記述子 (S D D) を与えるステップを含み、S D D はライトバックデータを記憶アレイへフラッシングするための準備完了として識別する値を含む方法。

**【請求項 6】**

請求項 1 に記載の方法であって、キャッシュメモリはライトバックデータの m セットを格納し、蓄積ステップは記憶アレイへのフラッシングに備えてアレイの異なる非隣接場所に関連する前記ライトバックデータの n セットを配列するステップを含み、n は m よりも小さい方法。

**【請求項 7】**

請求項 1 に記載の方法であって、さらに、ライトバックデータの前記付加セットがキャッシュメモリへ移されるレートを監視するステップを含み、それに関連して転送ステップを実施して前記キャッシュメモリ内に前記ライトバックデータの実質的に均一な分布を維持する方法。

**【請求項 8】**

記憶アレイの関連する場所へ転送するのに利用できるライトバックデータのセットを格納するキャッシュメモリと、ライトバックデータの前記セットをキャッシュメモリ内に配列して実質的に均一な分布を記憶アレイを横切って提供し、かつ実質的にライトバックデータの付加セットがホストによりキャッシュメモリへ提供されるレートでライトバックデータの前記セットをキャッシュメモリから記憶アレイへ転送するように構成されたプロセッサと、を含む装置。

**【請求項 9】**

請求項 8 に記載の装置であって、プロセッサはライトバックデータのセットを選択的にフラッシングリストへ移すキャッシュ・マネージャを含む装置。

**【請求項 10】**

請求項 8 に記載の装置であって、記憶アレイは記録媒体に隣接する選択された場所へ移されて選択されたアクセスコマンドをサービスするように構成されたトランステューサを含み、プロセッサは選択されたアクセスコマンドの選択された場所とライトバックデータの選択されたセットに対する関連場所との間の近接に関してライトバックデータの選択されたセットをキャッシュメモリから媒体へ転送する装置。

**【請求項 11】**

請求項 10 に記載の装置であって、前記近接はトランステューサの選択されたシーク長

10

20

30

40

50

を含む装置。

【請求項 1 2】

請求項 8 に記載の装置であって、プロセッサはアレイ内のライトバックデータの各セットに対するストライプデータ記述子 (S D D) を発生し、S D D はライトバックデータを記憶アレイへのフラッシング準備完了として識別する値を含む装置。

【請求項 1 3】

請求項 8 に記載の装置であって、キャッシュメモリはライトバックデータの m セットを格納し、プロセッサは前記ライトバックデータの n セットを記憶アレイフラッシングするために配置し、n は m よりも小さい装置。

【請求項 1 4】

請求項 8 に記載の装置であって、プロセッサはさらにライトバックデータの前記付加セットがキャッシュメモリへ移されるレートを監視し、それに関して前記データを転送してキャッシュメモリ内に前記ライトバックデータの実質的に均一な分布を維持する装置。

【請求項 1 5】

記憶アレイの関連する場所へ転送するのに利用できるライトバックデータの複数のセットを配列するキャッシュメモリと、実質的にライトバックデータの付加セットがホストによりキャッシュメモリへ提供されるレートでライトバックデータの前記セットを前記アレイから記憶アレイへ転送する第 1 の手段と、を含む装置。

【請求項 1 6】

請求項 1 5 に記載の装置であって、第 1 の手段はキャッシュ・マネージャを含む装置。

【請求項 1 7】

請求項 1 5 に記載の装置であって、記憶アレイは記録媒体に隣接する選択された場所へ移されて選択されたアクセスコマンドをサービスするように構成されたトランステューサを含み、第 1 の手段は選択されたアクセスコマンドの選択された場所とライトバックデータの選択されたセットに対する関連場所との間の近接に関してライトバックデータの選択されたセットをキャッシュメモリから媒体へ転送する装置。

【請求項 1 8】

請求項 1 7 に記載の装置であって、前記近接はトランステューサの選択されたシーク長を含む装置。

【請求項 1 9】

請求項 1 5 に記載の装置であって、第 1 の手段はさらにライトバックデータの前記付加セットがキャッシュメモリへ移されるレートを監視し、前記データを転送してプール内にライトバックデータの実質的に均一な分布を維持する装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は一般的にデータ記憶システムの分野に関し、制約はしないが、特に、記憶アレイへのキャッシュされたデータのダイナミック適応フラッシング方法および装置に向かっている。

【背景技術】

【0 0 0 2】

高速かつ効率的方法でデータにアクセスするために記憶装置が使用される。ある種の記憶装置は、媒体表面上に規定されたトラックにデータを書き込みその後データを読み出す 1 つ以上のデータトランステューサと共に、回転可能な記録媒体を使用する。

【0 0 0 3】

マルチデバイス・アレイ (M D A) は多数の記録装置を利用して統合されたメモリスペースを形成する。M D A に対する 1 つの広く利用されるフォーマットは R A I D (redundant array of independent discs) 構成を利用し、入力データはアレイ内の多数の記憶装置にわたって格納される。R A I D レベルに応じて、ミラーリング、ストライピングおよびパリティコード発生を含むさまざまな技術を利

10

20

30

40

50

用して格納されたデータの完全性を高めることができる。

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0004】**

記憶容量および性能のレベルは絶えず高まることが要求され続けているため、このようなアレイ内の記憶装置の動作が管理される方法の改善が継続的に必要とされている。本発明の好ましい実施例は一般的にこれらおよびその他の改善に向けられる。

**【課題を解決するための手段】**

**【0005】**

本発明の好ましい実施例は一般的に記憶アレイへキャッシュされたライトバックデータをフラッシングする装置および方法に向けられている。 10

**【0006】**

好ましい実施例では、記憶アレイの異なる場所にわたってデータの実質的に均一な分布を維持する目的で、ライトバックデータのセットがキャッシュメモリ内に整列して蓄積される。その後、データの整列されたセットは実質的にライトバックデータの附加セットがホストによりキャッシュメモリへ提供されるレートでキャッシュメモリから記憶アレイへ転送される。

**【0007】**

ライトバックデータの各セットは好ましくは複数の隣接データブロックを含み、好ましくは記憶アレイに関してデータの選択された近接範囲内の別個のアクセスコマンドの操作と共に記憶装置に書き込まれる（フラッシュされる）。好ましくは、アレイ内のライトバックデータの各セットに対してストライプデータ記述子（SDD）が維持される。 20

**【0008】**

このようにして、キャッシュされたライトバックデータのフラッシングは全体ホストI/Oアクセスレートに著しい変動を生じることはない。

**【0009】**

下記の詳細な説明を読みかつ添付図を検討すれば、特許請求された本発明を特徴づけるこれらおよびさまざまな他の特徴および利点が明白となる。

**【実施例】**

**【0010】**

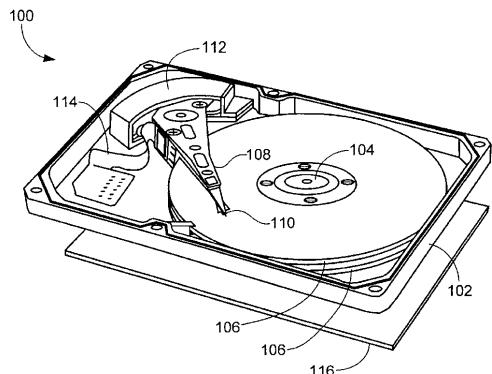

図1はユーザデータを格納かつ検索するように構成された典型的な記憶装置100を示す。好ましくは、装置100はハードディスクドライブとして特徴づけられるが、所望により、他の装置構成も容易に利用することができる。 30

**【0011】**

ベースデッキ102がトップカバー（図示せず）と嵌合して密閉筐体を形成する。スピンドルモータ104が筐体内に搭載されて、好ましくは、磁気記録ディスクとして特徴づけられる媒体106を制御可能に回転させる。

**【0012】**

制御可能に移動可能なアクチュエータ108はボイスコイルモータ（VCM）112へ電流を印加することにより、媒体表面上に規定されたトラックに隣接するリード／ライト・トランスデューサ110のアレイを移動させる。フレックス回路アセンブリ114はアクチュエータ108および外部搭載印刷回路板（PCB）116上の装置制御エレクトロニクス間の電気通信バスを提供する。 40

**【0013】**

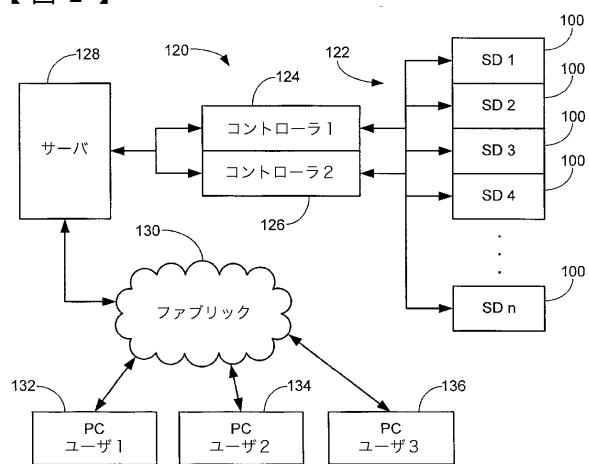

図2はn個の記憶装置（SD）100を有利に内蔵して統合記憶アレイ122を形成する典型的なネットワークシステム120を一般的に示している。冗長コントローラ124, 126が好ましくは記憶アレイ122およびサーバ128間でデータを転送するように動作する。サーバ128はローカルエリアネットワーク（LAN）、インターネット、等のファブリック130に接続されている。

**【0014】**

10

20

30

40

50

遠隔ユーザは、それぞれ、パーソナルコンピュータ( P C ) 1 3 2 , 1 3 4 , 1 3 6 を介してファブリック 1 3 0 にアクセスする。このようにして、選択されたユーザは記憶スペース 1 2 2 にアクセスして、所望により、データを書き込みまたは検索することができる。

#### 【 0 0 1 5 】

好ましくは、装置 1 0 0 およびコントローラ 1 2 4 , 1 2 6 はマルチデバイス・アレイ( M D A ) 1 3 8 に内蔵される。好ましくは、 M D A は 1 つ以上の選択された R A I D ( redundant array of independent discs ) 構成を使用して装置 1 0 0 に亘ってデータを格納する。図 2 には 1 つだけの M D A と 3 人の遠隔ユーザしか例示されていないが、これは単なる説明が目的であって制約的意味合いは無く、所望により、ネットワークシステム 1 2 0 は任意数およびタイプの M D A 、サーバ、クライアントおよびホスト装置、ファブリック構成およびプロトコル、等を利用することができる。図 3 は図 2 のネットワーク内で有用なアレイコントローラ構成 1 4 0 を示している。

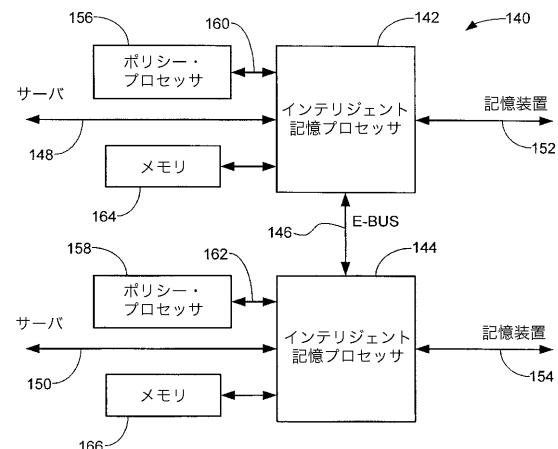

#### 【 0 0 1 6 】

図 3 は中間バス 1 4 6 ( 「 E バス 」 と呼ばれる ) により接続された 2 つのインテリジェント記憶プロセッサ( I S P ) 1 4 2 , 1 4 4 を説明する。好ましくは、各 I S P 1 4 2 , 1 4 4 は共通コントローラボード上の別個の集積回路パッケージ内に配置される。好ましくは、各 I S P 1 4 2 , 1 4 4 はファイバチャネル・サーバリンク 1 4 8 , 1 5 0 を介してアップストリーム・アプリケーション・サーバと通信し、かつファイバチャネル・記憶リンク 1 5 2 , 1 5 4 を介して記憶装置 1 0 0 と通信する。

#### 【 0 0 1 7 】

ポリシープロセッサ 1 5 6 , 1 5 8 はコントローラ 1 4 0 に対するリアルタイム・オペレーティングシステム( R T O S )を実行し、 P C I バス 1 6 0 , 1 6 2 を介して各 I S P 1 4 2 , 1 4 4 と通信する。ポリシープロセッサ 1 5 6 , 1 5 8 は、さらに、カスタマイズされた論理を実行して定められた記憶アプリケーションに対して I S P 1 4 2 , 1 4 4 と共に精巧な処理タスクを実施する。所望により、 I S P 1 4 2 , 1 4 4 およびポリシープロセッサ 1 5 6 , 1 5 8 は動作中に必要とされるメモリモジュール 1 6 4 , 1 6 6 にアクセスする。

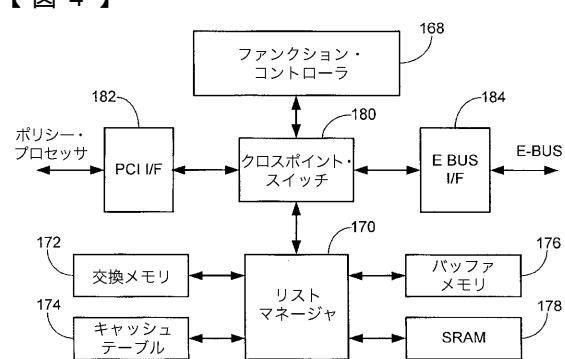

#### 【 0 0 1 8 】

図 4 は図 3 の選択された I S P に対する好ましい構造を提供する。纏めて 1 6 8 に示すいくつかのファンクション・コントローラはホスト交換、直接メモリアクセス( D M A )、排他的 o r ( X O R )、コマンドルーティング、メタデータ制御、およびディスク交換等のいくつかのコントローラ動作に対するファンクション・コントローラ・コア( F C C )として機能する。好ましくは、各 F C C はメモリ交換その他のスケジューリングタスクを容易にする非常に柔軟な機能セットおよびインターフェイスを含んでいる。

#### 【 0 0 1 9 】

一般的に 1 7 0 に示すいくつかのリストマネージャは、キャッシュテーブル管理、メタデータ保守、およびバッファ管理等のコントローラ動作中にさまざまなデータおよびメモリ管理タスクに使用される。好ましくは、リストマネージャ 1 7 0 はメモリ上の単純ではあるが明確に定義された操作を実施して F C C 1 6 8 により指令されるタスクを遂行する。好ましくは、各リストマネージャは F C C によるメモリアクセスに対するメッセージプロセッサとして作動して、好ましくは、規定されたプロトコルに従って受信メッセージにより規定される操作を実行する。

#### 【 0 0 2 0 】

リストマネージャ 1 7 0 は、それぞれ、交換メモリブロック 1 7 2 、キャッシュテーブル・ブロック 1 7 4 、バッファメモリ・ブロック 1 7 6 および S R A M 1 7 8 を含むいくつかのメモリモジュールと通信しつつ制御する。ファンクション・コントローラ 1 6 8 およびリストマネージャ 1 7 0 は、それぞれ、クロスポイントスイッチ( C P S )モジュール 1 8 0 を介して通信する。このようにして、コントローラ 1 6 8 の選択されたファンク

10

20

30

40

50

ション・コアは C P S 1 8 0 を介した対応するリストマネージャ 1 7 0 への通信パスウェイを確立して状態を通信し、メモリモジュールをアクセスし、あるいは所望の I S P 動作を呼び出すことができる。

#### 【 0 0 2 1 】

同様に、選択されたリストマネージャ 1 7 0 は C P S 1 8 0 を介してファンクション・コントローラ 1 6 8 へ応答を通信し返すことができる。図示されてはいないが、好ましくは、図 4 の各エレメント間にその間のデータ転送を調整するために別個のデータバス接続が確立される。所望により、他の構成を容易に利用できることがあ判りであろう。

#### 【 0 0 2 2 】

P C I インターフェイス ( I / F ) モジュール 1 8 2 はポリシープロセッサ 1 5 6 および I S P 1 4 2 間でトランザクションを確立して指示する。E - B U S I / F モジュール 1 8 4 は F C C および各 I S P 1 4 2 , 1 4 4 のリストマネージャ間の E - B U S 1 4 6 を介した通信を容易にする。所望により、ポリシープロセッサ 1 5 6 , 1 5 8 は E - B U S 1 4 6 を介したシステムの他の部分との通信を開始し受信することもできる。

#### 【 0 0 2 3 】

図 3 および 4 のコントローラ・アーキテクチュアはアレイに対するスケーラブルで、非常に機能的なデータ管理および制御を有利に提供する。好ましくは、ストライプ・バッファリスト ( S B L ) および他のメタデータ構造は記録媒体上のストライプ境界および記憶トランザクション中にディスクストライプに関連付けられるデータを専用に格納するキャッシュ内の基準データバッファに揃えられる。

#### 【 0 0 2 4 】

処理効率をさらに高めるために、好ましくは、コントローラ・アーキテクチュアは新しいライトバックデータ・キャッシング方法論を利用する。一般的に、これはメモリ内の記憶装置 1 0 0 に書き込まれるデータのキャッシング、および後でこのようなライトバックデータの記憶装置 1 0 0 への転送をスケジューリングする ( フラッシング ) ことを含んでいる。

#### 【 0 0 2 5 】

一般的に、データの時間および局所性の両方を考慮する 2 次元方法を使用してライトバックデータの隣接ブロックのセットがキャッシュメモリ内に配列される。キャッシュされたライトバックデータの実質的に均一な分布が維持されて、他のアクセス操作と共にデータを書き込むための最適機会を提供する。

#### 【 0 0 2 6 】

好ましくは、データの隣接ブロックのセットは付加ライトバックデータセットがホストによりキャッシュメモリへ提供されるレートと実質的に一致するレートでキャッシュメモリから記憶アレイへ書き込まれる。このようにして、観察されたホスト I / O 転送レートの大きな変動は実質的に解消される。

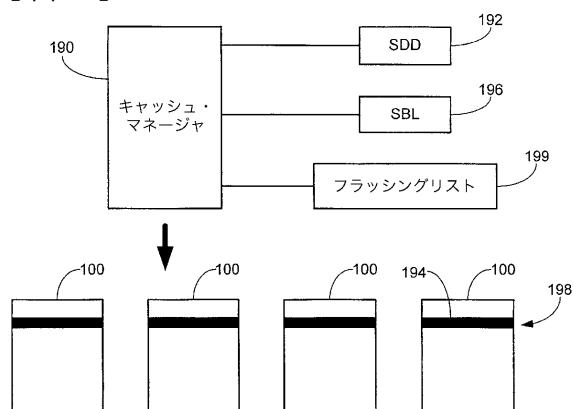

#### 【 0 0 2 7 】

図 5 に示すように、好ましくは、キャッシングされたデータはストライプ・データ記述子 ( S D D ) 1 9 2 と呼ばれるデータ構造を使用してキャッシング・マネージャ ( C M ) 1 9 0 によりノードベースで管理される。各 S D D は関連するデータへの最近および現在のアクセスに関するデータを保持する。各 S D D は好ましくは対応する R A I D ストライプ 1 9 4 ( すなわち、特定のパーティションに関連する選択された装置 1 0 0 上の全データ ) に揃えられ、特定の S B L 1 9 6 に従う。

#### 【 0 0 2 8 】

C M 1 9 0 により管理される各キャッシングノードは、好ましくは、ある特定の S D D を参照し、論理ディスクの定められたセット ( 装置 1 0 0 のサブセット ) に対するアクティプ S D D は、好ましくは、標準フォワードおよびバックワード・リンクリストを使用して仮想ブロックアドレス ( V B A ) を介して昇べき順でリンクされる。

#### 【 0 0 2 9 】

好ましくは、V B A 値はしばしば R A I D Allocation Grid System

10

20

30

40

50

em ( R A G S ) と呼ばれるグリッドシステムを使用して R A I D データ編成と揃えられる。一般的に、同じ R A I D ストリップ 198 に属するブロックの任意特定の集り（たとえば、特定のパリティセットに寄与する全データ）が特定のシート上の特定の信頼できる記憶ユニット ( R S U ) に割当てられる。

#### 【 0 0 3 0 】

数枚のシートからなるブックが異なる装置 100 からのブロックの多数の隣接セットから構成される。実際のシートおよび V B A に基づいて、ブックは特定の装置または装置セットを示す（冗長度が利用される場合）ゾーンへ細分割される。

#### 【 0 0 3 1 】

好ましくは、各 S D D はアクセス歴、ロック状態、最終オフセット、最終ブロック、タイムスタンプデータ（一日の時間、TOD）、データがどのゾーン（ブック）に属するかの識別子、および利用される R A I D レベルを含むデータのさまざまな状態を示す変数を含んでいる。好ましくは、S D D に関連するデータのライトバック（「ダーティ」データ）状態がダーティデータ、ダーティバッファ、ダーティ L R U およびフラッシング L R U 値に関して管理される。

#### 【 0 0 3 2 】

好ましくは、C M 190 は同時に作動していくつかの異なるレベルのライトバックデータ・プロセスをシステム要求条件に応じて管理する。第 1 のレベルは一般的にフル R A I D ストリップ 198 が検出される時のフル S D D 構造の周期的フラッシングを含んでいる。これは S D D が関連するデータをダーティとして識別する時に R A I D レベル変数に基づいて定められた S D D 192 に対して容易に実施することができる。好ましくは、これは十分連続的な隣接 S D D 構造がダーティデータで十分満たされているかを決定するバックワード検査を含んでいる。そうであれば、S D D 構造はフラッシングリスト（199 に示す）上に置かれ、データのフラッシングを開始する要求がなされる。フラッシングリスト状態は S D D 192 のフラッシング L R U 値を使用して設定することができる。

#### 【 0 0 3 3 】

データの小さなセットのフラッシングは好ましくは S D D ベースで処理される。ダーティロックを有しロックブロックの無い任意の S D D は好ましくはダーティ L R U として設定され経過期間（age）（たとえば、データがキャッシュ待機フラッシングにおいて過ごした時間）によりソートされる。特定の経過期間に達すると、好ましくはフラッシング L R U 変数が設定されフラッシングリスト 199 が更新される。

#### 【 0 0 3 4 】

好ましくは、フラッシングリストからのデータのフラッシングの攻撃性は実質的に付加ダーティデータがキャッシュ内に入るレートでダーティデータを押出すように適応的に調節される。特定範囲の連続的ダーティロックをフラッシングする予定の時は、C M 190 は好ましくは近似局所性を有する R A I D レベルに基づいて他の範囲のダーティロック、すなわち、シーク時間に関して「すぐ近い」または同じ R A I D パリティストリップ 199 へのアクセスを伴うロックを探し出す。

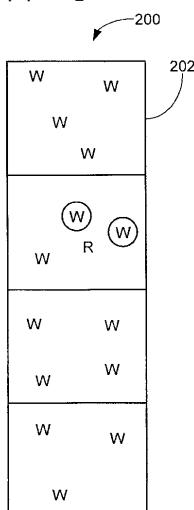

#### 【 0 0 3 5 】

コントローラーアーキテクチャがこれを実施する好ましい方法を図 6 について見ることができ、それはキャッシュされたライトバックデータのアレイ 200 を表している。アレイ 200 は C M 190 またはコントローラの他の処理ブロックにより維持される。

#### 【 0 0 3 6 】

アレイ 200 内の各セル 202 は一般的に記憶装置 100 内の選択された局所性に対応し、ブック、シートおよび / またはアレイ内のゾーンとして編成することができる。装置内の境界は、たとえば、各コラムが異なる記憶装置 100 を表しコラム内の各セルはその装置を横切る異なる半径方向バンドを表すように選択することができる。

#### 【 0 0 3 7 】

セルはフラッシングリスト 199 にフラグを付されている隣接ライトバックデータのセットで「占用されている（populated）」。特に、各占用ブロック 204 ( 図 6

10

20

30

40

50

に「X」で示す)は記憶装置100内の異なる論理的または物理的場所に対応する変動するサイズのデータブロックの1つの(またはいくつかの)グループを表す。このようにして、キャッシュ内のライトバックデータのセットは記憶アレイ122へ転送されることを予測してプールすることができる。

#### 【0038】

アレイ200はさまざまなデータ装置100にわたってデータのライトバックをスケジューリングする有用なフォーマットを提供する。好ましい実施例では、記憶装置100内の選択された場所にわたってアクセスする(たとえば、リードコマンドを実施する)よう 10 に特定のアクセスコマンドがスケジュールされると、アレイ200はアクセスコマンドと共に効率的にサービスされるライトバックデータの利用可能なブロックを識別するように参照される。

#### 【0039】

アレイ200を横切って占用セル204の実質的に均一な分布を維持し、着信データのレートをキャッシュと整合させるためにデータセットが選択的にアレイ200に加えられる。あるシステム負荷の元で、CM190は比較的多数のフラッシング操作をロードアップして、論理的セットまたは物理的媒体を横切ってIDからODへ進行するライト等の、ショートシークのクラスタを生成するように構成することができる。

#### 【0040】

関連する実施例では、図6のアレイ200は個別のRAIDストライプ(対応するSD 20 D192を有する図5の194等)を表すようにセル202を配置するように構成することができ、アレイ200のコラムは前記したRAGSグリッドのコラムに対応することができる。このような場合、定められたロー内の特定の占用セル204のフラッシングを使用して同じロー内の他の占用セルにより使用されるパリティ(グリッド内には示されていない)への参照を示すことができる。

#### 【0041】

このようなフラッシング操作の同時スケジューリングにより、特に、RAID-5およびRAID-6環境において性能改善を導くことができ、それはそのロー内の全占用セルに対する4つの(RAID-6の場合は6つの)I/Oアクセスの内の2つが同じパリティRAIDストライプ194にアクセスするためである。

#### 【0042】

もう1つの好ましい実施例では、アレイ200は各コラム(またはロー)が別個の記憶装置100を表し、各セル202は一般的に装置の媒体106の半径方向幅にわたって異なる隣接ゾーン、すなわち領域、に対応するように配置される。

#### 【0043】

図7の「W」表記は一般的にこれらのさまざまな場所内のデータの未決ライトバックセットに対応し、したがって各セル202内の装置にわたって分布されるライト機会を表す。各セル202内のW表記の空間的場所は一般的に関連する領域内のそのデータの論理的または物理的場所を表す。W表記は媒体106へ書き込むためにフラッシングリスト199から利用可能な全ライトバックデータセットを必ずしも表すものではない。

#### 【0044】

リード優先環境では、リードコマンドが優先権を有し、したがって一般的にライトコマンドのサービスよりも優先的にサービスされる。しかしながら、ライト優勢環境では、一般的にリードに較べて比較的多数のライトコマンドがある。1つのこのようなリードコマンドは図7において「R」表記で識別され、一般的に関連するデータが検索される媒体106の領域に対応する。

#### 【0045】

この実施例では、キャッシュ・マネージャ190は好ましくは関連するリードコマンドを実施してR表記のデータを検索するよう装置100に指令する。このリード操作の終りに、キャッシュ・マネージャ190は、さらに、好ましくは一般的にリードコマンドの近くの(たとえば、同じセル202内の)1つ以上ライトバック操作を装置100に実施さ

10

20

30

40

50

せるように進行する。

#### 【0046】

図7は「丸W」表記を使用してこのようにサービスされる2つのこのようなライトバックデータセットを識別する、すなわち、2つの丸W表記ライトバックフラッシュが関連するリードコマンドの終りに生じる(R表記)。リードコマンド近くの(たとえば、セル202内の)全ライトバックデータがフラッシュされる必要はなく、望ましくないことさえあることに注目願いたい。しかしながら、近くのデータの少なくともいくつかはフラッシュされ、装置100のトランスデューサ110は一般的にこの近くにあるため、これらのライトバックデータ・フラッシュ操作は低減されたシークレーテンシ(seek latency)で実施することができる。

10

#### 【0047】

選択されたライトバックデータがフラッシュされると、キャッシュ・マネージャ190は、フラッシュリストから得られる、この同じ領域への付加ライトバックデータ・セットでアレイ200を「埋め戻す」ように進行する。このようにして、新しいライトコマンドは媒体106のさまざまな半径方向幅にわたってライトバックデータ機会の均一な分布を実質的に維持するようにアレイ200に対して計られる(metered)。

#### 【0048】

ディスクアクセスを要する未決リードコマンドが無い限り、キャッシュ・マネージャ190は一般的に前と同様にライトバックデータをフラッシュするように動作する。しかしながら、各新しいリードコマンドが発せられると、リードコマンドに優先権が与えられ1つ以上の付加ライトバックセットがリードコマンドの一般的に近くからフラッシュされる。

20

#### 【0049】

好ましくは、これは次のリードコマンドがどこへ向けられても効率的でフラッシュすることができる1つ以上のライトバックデータセットがその近くにある環境を提供する。好ましい実施例では、キャッシュ・マネージャ190は、任意の定められた時間に未決の30を超えるWおよび2を超えるRが無いように(待ち行列コマンドに対する合計32の「スロット」に対して)、各装置100に対するアレイ200内の「R」に対する「W」の選択された比率を維持するように動作する。しかしながら、他の比率も容易に使用することができる。比率はキャッシュ・マネージャ190により経験されるリード/ライト・コマンドミックス内のバースト変化に関して時間と共に調節することもできる。

30

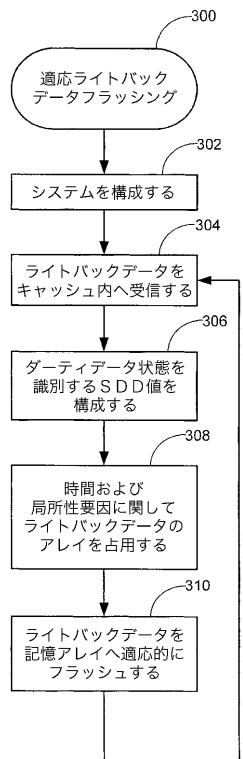

#### 【0050】

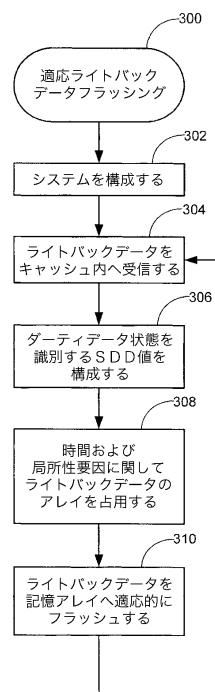

図8はライトバックデータ・フラッシング・ルーチン300を説明し、一般的に本発明の好ましい実施例に従って実施されるステップを表す。

#### 【0051】

システムはステップ302において初期構成される。好ましくは、これはフラッシングリスト199に対するさまざまな境界および記憶装置100の物理的領域をカバーする対応するアレイ200の初期識別を含む。所望により、記憶スペースの適切なサブセットに対する異なるアレイおよびリストを維持することができ、あるいは単一の統合リスト/アレイを維持することができる。

40

#### 【0052】

正規のシステム操作が次に開始され、ステップ304に示すように、これはキャッシュメモリへのライトバック(ダーティ)データの周期的提供を含む。このようなライトバックデータは主として図1のPC132, 134, 136等のホストからのデータライト操作から生じるものと考えられ、その場合、コントローラ124は好ましくはライトバックデータを選択されたキャッシュ場所(図4の176等)に格納し、ライト完了信号を開始装置へ返す。しかしながら、ライトバックデータはシステム状態データ、選択されたメモリバックアップ、メタデータ、等の内部発生ライトとすることもできる。

#### 【0053】

ステップ306に示すように、SDD192は好ましくは関連するライトバックデータ

50

に対して更新される。ダーティデータおよびダーティバッファ値はデータをダーティとして識別するように初期設定することができる。その後、データセットはフルストリップ198とのデータの関係、経過期間、および付加データのキャッシュ内への進入レートを含む前記したいくつかの要因に関してフラッシングリスト199へ移される。アレイ200は前記ブロックのフラッシングリスト199への移動に応答してフラッシングに利用できる隣接データブロックのセットを識別するようにステップ308において対応的に占用される。

#### 【0054】

ステップ310において、ライトバックデータの選択されたセットは記憶装置100へフラッシュされる。好ましくは、これは他の近接アクセス操作と共に生じるが、装置100にわたってより大きい逐次フラッシング操作をスケジュールすることもできる。前記したように、CM190または他のプロセスは好ましくはキャッシュされたライトバックデータがさらにキャッシュメモリへ導入されるレートに関して利用できるライトバックデータブロックの実質的に均一な分布を維持するように動作する。

#### 【0055】

ここで検討されたさまざまな好ましい実施例は従来技術に優る利点を提供する。開示された方法論は時間と局所性の両方がフラッシング・アルゴリズムの要因として記憶装置100へのデータの効率的フラッシングを提供する点においてダイナミックである。さらに、方法論は付加ダーティデータがキャッシュメモリへ導入されるレートに実質的に揃えるのに適応的である。好ましい実施例では、キャッシュメモリ内の付加ダーティデータのセットはアレイ200へかつアレイ200から記憶ディスクへ選択的に計られて実質的に平坦な負荷量を維持する。このようにして、ホストI/O内の著しい変動が回避される。

#### 【0056】

ここに提示された好ましい実施例は複数のディスクドライブ記憶装置を利用するマルチデバイスアレイに向かっているが、それは単なる説明の目的であって制約的意味合いはない。むしろ、特許請求される発明は任意数のさまざまな環境で利用して効率的なデータ処理を促進させることができる。

#### 【0057】

本発明のさまざまな実施例の非常に多くの特徴および利点を、本発明のさまざまな実施例の構造および機能の詳細と共に、前記した明細書に記載してきたが、この詳細な説明は説明用にすぎず詳細、特に、部品の構造および配置に関して本発明の原理内で添付特許請求の範囲が表現される用語の広範な一般的の意味により示される限界まで変更を行うことができる。たとえば、特定のエレメントは特定の応用に応じて本発明の精神および範囲を逸脱することなく変動することができる。

#### 【図面の簡単な説明】

#### 【0058】

【図1】本発明の好ましい実施例に従って構成かつ作動される記憶装置を一般的に示す図である。

【図2】図1に示すようないくつかの記憶装置を利用するネットワークシステムの機能的ブロック図である。

【図3】図2のコントローラの好ましいアーキテクチャの一般的表現を示す図である。

【図4】図3の選択されたインテリジェント記憶プロセッサの機能的ブロック図である。

【図5】好ましい実施例に従って記憶アレイにデータをフラッシュするように動作するキャッシュ・マネージャを一般的に示す図である。

【図6】好ましい実施例に従って記憶アレイのいくつかの異なる場所にわたってライトバックデータ機会の分布を提供する図5のキャッシュ・マネージャにより維持されるライトバックデータセットのアレイを表す図である。

【図7】もう1つの好ましい実施例に従った図6のアレイの一部を示す図である。

【図8】好ましい実施例に従って実施されるステップを示すライトバックデータ・フラッシング・ルーチンに対するフロー図である。

10

20

30

40

50

## 【符号の説明】

## 【0059】

|                       |                      |    |

|-----------------------|----------------------|----|

| 1 0 0                 | 記憶装置                 |    |

| 1 0 2                 | ベースデッキ               |    |

| 1 0 4                 | スピンドルモータ             |    |

| 1 0 6                 | 回転媒体                 |    |

| 1 0 8                 | アクチュエータ              |    |

| 1 1 0                 | リード／ライト・トランスデューサ     |    |

| 1 1 2                 | ボイスコイルモータ            |    |

| 1 1 4                 | フレックス回路アセンブリ         | 10 |

| 1 1 6                 | 印刷回路板                |    |

| 1 2 0                 | ネットワーク・システム          |    |

| 1 2 2                 | 記録アレイ                |    |

| 1 2 4 , 1 2 6         | 冗長コントローラ             |    |

| 1 2 8                 | サーバ                  |    |

| 1 3 0                 | ファブリック               |    |

| 1 3 2 , 1 3 4 , 1 3 6 | パーソナルコンピュータ          |    |

| 1 4 0                 | アレイコントローラ構成          |    |

| 1 4 2 , 1 4 4         | インテリジェント記憶プロセッサ      |    |

| 1 4 6                 | 中間バス                 | 20 |

| 1 4 8 , 1 5 0         | ファイバチャネル・サーバリンク      |    |

| 1 5 2 , 1 5 4         | ファイバチャネル記憶リンク        |    |

| 1 5 6 , 1 5 8         | ポリシー・プロセッサ           |    |

| 1 6 0 , 1 6 2         | P C I バス             |    |

| 1 6 4 , 1 6 6         | アクセスメモリ・モジュール        |    |

| 1 6 8                 | ファンクション・コントローラ       |    |

| 1 7 0                 | リストマネージャ             |    |

| 1 7 2                 | 交換メモリブロック            |    |

| 1 7 4                 | キャッシュテーブル・ブロック       |    |

| 1 7 6                 | バックファメモリ・ブロック        | 30 |

| 1 7 8                 | S R A M              |    |

| 1 8 0                 | クロスポイントスイッチ・モジュール    |    |

| 1 8 2                 | P C I インターフェイス・モジュール |    |

| 1 8 4                 | E - B U S I F モジュール  |    |

| 1 9 0                 | キャッシュ・マネージャ          |    |

| 1 9 2                 | ストライプ・データ記述子         |    |

| 1 9 4 , 1 9 8         | R A I D ストライプ        |    |

| 1 9 6                 | S B L                |    |

| 1 9 9                 | フラッシングリスト            |    |

| 2 0 0                 | アレイ                  | 40 |

| 2 0 2 , 2 0 4         | セル                   |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

|   |   |   |   |   |

|---|---|---|---|---|

| X |   |   | X |   |

|   | X | X |   | X |

| X | X | X | X |   |

|   |   | X |   |   |

【図8】

---

フロントページの続き

(72)発明者 クラーク イー・レッペルス

アメリカ合衆国、コロラド、コロラドスプリングス、ピニョン バレー ロード 5301

(72)発明者 マイケル ディー・ウォーカー

アメリカ合衆国、コロラド、コロラドスプリングス、イースト ウィラメット 219

(72)発明者 デーヴィッド ピー・デセンゾ

アメリカ合衆国、コロラド、ブエブロ、ミッドナイト アベニュー 319

F ターム(参考) 5B005 JJ12 MM11 NN02 VV01

5B065 CA30 CH01

【外國語明細書】

2008016024000001.pdf