(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5068932号

(P5068932)

(45) 発行日 平成24年11月7日(2012.11.7)

(24) 登録日 平成24年8月24日(2012.8.24)

|                      |            |

|----------------------|------------|

| (51) Int.Cl.         | F 1        |

| HO4B 7/005 (2006.01) | HO4B 7/005 |

| HO4B 3/06 (2006.01)  | HO4B 3/06  |

| HO4L 25/03 (2006.01) | HO4L 25/03 |

| HO4L 27/38 (2006.01) | HO4L 27/00 |

| HO4L 27/22 (2006.01) | HO4L 27/22 |

請求項の数 14 (全 22 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2004-529882 (P2004-529882)  |

| (86) (22) 出願日 | 平成15年8月19日 (2003.8.19)        |

| (65) 公表番号     | 特表2005-536932 (P2005-536932A) |

| (43) 公表日      | 平成17年12月2日 (2005.12.2)        |

| (86) 国際出願番号   | PCT/US2003/026399             |

| (87) 国際公開番号   | W02004/019577                 |

| (87) 国際公開日    | 平成16年3月4日 (2004.3.4)          |

| 審査請求日         | 平成18年7月19日 (2006.7.19)        |

| 審判番号          | 不服2010-22793 (P2010-22793/J1) |

| 審判請求日         | 平成22年10月8日 (2010.10.8)        |

| (31) 優先権主張番号  | 10/226,031                    |

| (32) 優先日      | 平成14年8月21日 (2002.8.21)        |

| (33) 優先権主張国   | 米国 (US)                       |

|           |                                                                                                                |

|-----------|----------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595020643<br>クアアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                         |

| (74) 代理人  | 100091351<br>弁理士 河野 哲                                                                                          |

| (74) 代理人  | 100088683<br>弁理士 中村 誠                                                                                          |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                         |

最終頁に続く

(54) 【発明の名称】仮想並列イコライザを備えた通信レシーバー

## (57) 【特許請求の範囲】

## 【請求項 1】

パラメーターのセットにより定義される単一のイコライザを用いて受信されたサンプルから送信された信号を評価する

ことにより前記単一のイコライザの構成を決定する方法において、

前記単一のイコライザは、

前記パラメーターのセットに関する値の第1のセットを決定するステップと、

前記単一のイコライザを訓練し、値の更新された第1のセットを発生するステップと、

前記単一のイコライザの性能パラメーターの第1の大きさ(measure)を評価するステップであって、前記性能パラメーターの第1の大きさは、前記値の更新された第1のセットに関連している前記第1の大きさを評価するステップと、ここにおいて、前記性能パラメータは、前記単一のイコライザの搬送波対干渉(C/I)比であり、

前記パラメーターのセットに関する値の第2のセットを設定するステップであって、前記値の第2のセットは、前記単一のイコライザの構成を効率的に変更する前記第2のセットを設定をするステップと、

前記単一のイコライザを訓練して値の更新された第2のセットを発生するステップと、

前記単一のイコライザの前記性能パラメータ(C/I)の第2の大きさを評価するステップであって、前記性能パラメーターの第2の大きさは、前記値の更新された第2のセットと関連している前記第2の大きさを評価するステップと、

前記第1の大きさを前記第2の大きさと比較するステップと、

10

20

前記第1の大きさと前記第2の大きさの比較に基づいて、前記値の更新された第1および第2のセットの一方を選択するステップと、および

前記選択の結果を用いて、前記単一のイコライザを構成するステップと、

を備える

前記単一のイコライザの構成を決定する方法。

**【請求項2】**

前記単一のイコライザの訓練のために、周知のサンプルのシーケンスが使用される、請求項1の方法。

**【請求項3】**

データサンプルを受信することと、

10

サンプルメモリ記憶装置に前記データサンプルを記憶することと、

前記データサンプルの少なくとも一部を検索することと、および

前記構成された単一のイコライザを用いて前記データサンプルの少なくとも一部を処理することと、

をさらに備えた、請求項1の方法。

**【請求項4】**

前記値の第1および第2のセットの選択された一方をパラメーターメモリ記憶装置に記憶することをさらに具備する、請求項1の方法。

**【請求項5】**

前記パラメーターのセットは、前記単一のイコライザの第1のフィルターに関するフィルター係数を含む、請求項1の方法。

20

**【請求項6】**

前記パラメーターのセットは、さらに前記単一のイコライザの第2のフィルターに関するフィルター係数を含む、請求項5の方法。

**【請求項7】**

前記パラメーターのセットは、前記受信されたサンプルのDCオフセットを含む、請求項1の方法。

**【請求項8】**

前記パラメーターのセットは、セクター識別子を含む、請求項1の方法。

**【請求項9】**

30

前記パラメーターのセットは、前記受信されたサンプルの位相を含む、請求項1の方法。

。

**【請求項10】**

パラメーターのセットにより定義される単一のイコライザを用いて受信されたサンプルから送信された信号を評価するための装置において、

前記パラメーターのセットに関する値の第1のセットを決定する手段と、

前記単一のイコライザを訓練し、値の更新された第1のセットを発生する手段と、

前記単一のイコライザの性能パラメーターの第1の大きさを評価する手段であって、前記性能パラメーターの第1の大きさは、前記値の更新された第1のセットに関連している前記第1の大きさを評価する手段と、ここにおいて、前記性能パラメータは、前記単一のイコライザの搬送波対干渉(C/I)比である、

40

前記パラメーターのセットに関する値の第2のセットを設定する手段であって、前記値の第2のセットは前記単一のイコライザの構成を効率的に変更する前記第2のセットを設定する手段と、

前記単一のイコライザを訓練して値の更新された第2のセットを発生する手段と、

前記単一のイコライザの前記性能パラメーターの第2の大きさを評価する手段であって、前記性能パラメーターの第2の大きさは、前記値の更新された第2のセットに関連する前記第2の大きさを評価する手段と、

前記第1の大きさを前記第2の大きさと比較する手段と、

前記第1および第2の大きさの比較に基づいて値の更新された第1および第2のセット

50

の一方を選択する手段と、

前記選択の結果を用いて前記单一のイコライザを構成する手段と、

を備えた装置。

【請求項 1 1】

受信されたサンプルからの送信された信号を評価するように構成された单一のイコライザであり、前記单一のイコライザを内で操作する無線装置であって、

前記单一のイコライザは、パラメーターのセットにより定義され、

さらに、前記無線装置においては、

前記パラメーターのセットに関する値の第 1 のセットを決定し、

値の更新された第 1 のセットを発生するように訓練し、

性能パラメーターの第 1 の大きさを評価し、前記性能パラメーターの第 1 の大きさは前記値の更新された第 1 のセットに関連し、ここにおいて、前記性能パラメータは前記单一のイコライザの搬送波対干渉 (C / I) 比である、

パラメーターのセットに関する値の第 2 のセットを設定し、前記单一のイコライザの構成を効率的に変更し、

値の更新された第 2 のセットを発生するように訓練し、

性能パラメーターの第 2 の大きさを評価し、前記性能パラメーターの第 2 の大きさは前記値の更新された第 2 のセットに関連し、

前記第 1 の大きさを前記第 2 の大きさと比較し、

前記第 1 および第 2 の大きさの比較に基づいて前記値の更新された第 1 および第 2 のセットの一方を選択し、

前記値の第 1 および第 2 のセットの選択された一方を用いて前記单一のイコライザを構成する

無線装置。

【請求項 1 2】

单一のイコライザを構成する方法であって、

前記单一のイコライザは、

パラメーターの第 1 のセットを用いて单一のイコライザを構成するステップと、

受信されたパイロット信号上の前記パラメーターの第 1 のセットを用いて構成された前記单一のイコライザを訓練し、パラメータの更新された第 1 のセットを発生するステップと、

前記パラメーターの第 1 のセットで構成された前記单一のイコライザに関連する前記受信されたパイロット信号の性能パラメーターの第 1 の大きさを決定するステップと、ここにおいて、前記性能パラメータは、前記单一イコライザの搬送波対干渉 (C / I) 比である、

パラメーターの第 2 のセットを用いて前記单一のイコライザを構成するステップと、

前記受信されたパイロット信号上の前記パラメーターの第 2 のセットで構成された前記单一のイコライザを訓練し、パラメーターの更新された第 2 のセットを発生するステップと、

前記パラメーターの第 2 のセットで構成された前記单一のイコライザに関連する前記受信されたパイロット信号の第 2 の大きさを決定するステップと、

前記第 1 の大きさと前記第 2 の大きさを比較するステップと、

前記比較に基づいて、前記パラメーターの更新された第 1 のセットと前記パラメーターの更新された第 2 のセットの一方を選択するステップと、

前記パラメーターの選択されたセットで前記单一のイコライザを構成するステップと、

を備える

单一のイコライザを構成する方法。

【請求項 1 3】

前記構成された单一のイコライザで受信されたデータサンプルを処理することをさらに備えた、請求項 1 2 の方法。

## 【請求項 14】

单一の構成可能なイコライザと、構成選択ユニットを備えた装置であって、

前記選択ユニットは、

パラメーターの第1のセットで前記单一のイコライザを構成し、

受信されたパイロット信号上の前記パラメーターの第1のセットで構成された前記单一のイコライザを訓練して、パラメーターの更新された第1のセットを発生し、

前記パラメーターの第1のセットで構成された前記单一のイコライザに関連する前記受信されたパイロット信号の性能パラメーターの第1の大きさを決定し、ここにおいて、前記性能パラメータは前記单一イコライザの搬送波対干渉(C/I)比である、

パラメーターの第2のセットで前記单一のイコライザを構成し、

10

前記受信されたパイロット信号上の前記パラメーターの第2のセットで構成された前記单一のイコライザを訓練し、パラメーターの更新された第2のセットを発生し、

前記パラメーターの第2のセットで構成された前記单一のイコライザに関連する前記受信されたパイロット信号の前記性能パラメーターの第2の大きさを決定し、

第1の大きさと前記第2の大きさを比較し、

前記比較に基づいて、前記パラメーターの更新された第1のセットと前記パラメーターの更新された第2のセットの一方を選択し、

前記パラメーターの選択されたセットで前記单一のイコライザを構成する構成選択ユニットである

单一の構成可能なイコライザと構成選択ユニットを備えた装置。

20

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、一般に通信システムにおける等化に関し、特に、仮想並列イコライザを組み込んだユニバーサルレシーバーに関する。

## 【背景技術】

## 【0002】

通信システムはある装置から別の装置まで情報を送信するために使用される。

## 【0003】

送信に先立って、情報は、通信チャネル上の送信にふさわしいフォーマットにコード化される。送信された信号が通信チャネルを介して移動するとき歪を生じる。また、信号は、送信の間に拾い上げられた雑音と干渉からの劣化を経験する。帯域制限されたチャネルで一般に遭遇する干渉の一例は符号間干渉(IISI)と呼ばれる。IISIは、チャネルの分散的な性質により、送信されたシンボルパルスの拡散の結果生じる。分散的な性質は隣接したシンボルパルスの重複を結果として生じる。受信信号は復号され、オリジナルのあらかじめ符号化された形式に変換される。送信器とレシーバーの両方は、チャネルの欠陥および干渉の影響を最小化するように設計されている。この開示のために、チャネル欠陥、あるいはその任意の組合せによる、干渉あるいはひずみは、一般に雑音と呼ばれるであろう。

30

## 【0004】

様々なレシーバー設計は送信器とチャネルによって引き起こされた雑音を補償するために実施してもよい。一例として、イコライザは、IISIに対処するための共通の選択である。イコライザは歪を修正し、送信されたシンボルの推定値を生成する。無線環境では、イコライザは時間が変化するチャネル条件を取り扱うために必要とされる。理想的には、イコライザの応答はチャネル特性の変化に合わせて調節する。イコライザが変化する条件に応答する能力は、イコライザのタップの数と関係がある。より多くのタップは、イコライザが変化に対してより正確に調節することを可能にし、一方より少数のタップは、より高速な適応を可能にする。タップの数を選択することによりイコライザを最適化することは困難である。なぜならば、競合する目標の平衡度を必要とするからである。

## 【0005】

40

50

それゆえ、多様なシステムおよび条件に対して性能を最適化するイコライザの設計の必要性が存在する。

【発明を実施するための最良の形態】

【0006】

通信システムはあるデバイスから別のデバイスに情報を送信するのに使用される。送信の前に、情報は、通信チャネル上の送信に適切なフォーマットに符号化される。通信チャネルは、送信器とレシーバーの間の送信線路または空きスペースかもしれない。信号がチャネルを介して伝播するとともに、送信された信号はチャネルの欠陥によって歪を生じる。更に、信号は、送信の間に拾い上げられた雑音と干渉からの劣化を経験する。帯域制限されたチャネルで一般に遭遇する干渉の一例はシンボル間干渉 ( ISI ) と呼ばれる。 ISI が、チャネルの分散的な性質により、送信されたシンボルパルスの拡散の結果生じる。チャネルの分散的な性質は隣接したシンボルパルスの重複を結果として生じる。レシーバーでは、信号は処理され、オリジナルのあらかじめ符号化された形態に変換される。送信器とレシーバーの両方は、チャネル欠陥および干渉の影響を最小化するように設計されている。この開示のために、チャネル欠陥、あるいはそれの任意の組合せによる、干渉あるいはひずみは、一般に雑音と呼ばれるだろう。

【0007】

様々なレシーバー設計は送信器とチャネルによって引き起こされた雑音を補償するために実施されるかもしれない。一例として、イコライザは、 ISI に対処するための共通の選択である。イコライザはトランスバーサルフィルタ、すなわち  $T$  秒のタップ ( $T$  はシンボル持続時間) を備えた遅延線を用いて実施してもよい。タップの内容は増幅され、加算され送信されたシンボルの推定値を発生する。タップ係数は所望のシンボルに時間的に隣接しているシンボルからの干渉を低減するために調節される。一般に、適応等化技術が採用され、それによりタップ係数は、連続的にかつ自動的に調節される。適応性のあるイコライザは、タップ係数を決定するために最小二乗 ( LMS ) または再帰的最小二乗 ( RLS ) のような所定のアルゴリズムを使用する。シンボル推定値は、デコーダあるいはシンボルスライサーのような意志決定装置に接続される。

【0008】

レシーバーが、雑音が存在する状態で信号を検出する能力は、受信信号電力と雑音電力の比にもとづく。この比は、信号対雑音電力比 ( SNR ) として、あるいは搬送波対干渉比 ( C / I ) として一般に知られている。これらの用語または類似の用語の産業上の使用は、しばしば交換可能である。しかし、意味は同じである。従って、ここにおける C / I へのどんな参照も当業者により理解され、通信システムにおける種々のポイントにおける雑音の影響を測定する広い概念を含むであろう。

【0009】

典型的には、 C / I は、既知の送信されたシンボルシーケンスのシンボル推定値の評価により、レシーバーの中で決定してもよい。これは、送信されたパイロット信号用の C / I の計算により、レシーバーの中で遂行してもよい。パイロット信号が知られているので、レシーバーはイコライザからのシンボル推定値に基づいて C / I を計算してもよい。

【0010】

結果として得られる C / I の計算は多くの目的に使用されてもよい。可変率データ要求スキームを使用する通信システムでは、レシーバーは、レシーバーが C / I に基づいてサポートしてもよい最大データ転送速度で送信器に通信してもよい。更に、レシーバーがターボデコーダを含むなら、送信された星座に応じて、対数尤度比 ( LLR ) 計算は、 C / I の正確な推定値を必要とする。

【0011】

無線通信システム内のイコライザは、時間変化するチャネル条件に順応するように設計される。チャネル特性が変わるとともに、それに応じてイコライザはそのレスポンスを調節する。そのような変化は、伝播媒体における変化、または送信器およびレシーバーにおける相対移動、並びに他の条件を含んでいてもよい。上述したように、適応フィルタリン

10

20

30

40

50

グアルゴリズムは、しばしば、イコライザタップ係数を変更するために使用される。適応アルゴリズムを使用するイコライザは一般に適応イコライザと呼ばれる。適応アルゴリズムは共有資産を共有する：イコライザタップの数が増加するとともに、適応速度は減少する。遅い順応は、適応イコライザのトラッキング作用に影響を与える。「長い」イコライザ、すなわち、多数のタップを有するイコライザは望ましい。なぜならば、長いイコライザは、より正確にチャネル歪を反転し、良い定常状態性能を生じるからである。しかしながら、長いイコライザは、チャネル変化に、よりゆっくりと反応し、貧弱な遷移拳動、すなわち、チャネルが迅速に変化しているときに貧弱な性能に結びつく。タップの最適数はそのような考察の平衡を保ち、よい定常性能と良い過度性能との間で妥協する。

## 【0012】

10

実際上、タップの最適数を決定することは困難である。なぜならば、最適条件は、さまざまな条件および目標に依存しており、これらに限定されるものではないが、チャネルの瞬時の応答およびチャネルの変化の割合を含む。したがって、イコライザが様々な時間的に変化する条件下で、さまざまなチャネル上で使用されるなら、タップの最適な数を先驗的に決定することは困難である。

## 【0013】

20

ここに開示するように、一実施形態は、「並列」に動作する異なる長さの複数の「仮想」適応イコライザを訓練することによりタップの最適数を選択する。ここで使用される並列という用語は、同じサンプルのセット上のこれらの複数の仮想イコライザの訓練に言及する。ここで使用される仮想という用語は、これらのイコライザの各々が異なる構成で同じ物理ハードウェアの要素を使用するという事実に言及する。ハードウェアがどのように異なって構成されるかは、例えば、イコライザの長さ、または他のイコライザパラメーターに依存する。実際には、所定の固定長のイコライザが使用され、イコライザの効率的な長さは、あるタップ係数をゼロに設定することにより動的に調節される。複数の適応イコライザは、「並列」に訓練される。1つのイコライザ構成は、性能に基づいて選択される。例えば、選択は、送信されたパイロット信号と所定長のイコライザにより発生された推定値との間の最も低い平均平方誤差（MSE）に相当するかもしれないし、与えられた長さのイコライザによって与えられた推定値に相当するかもしれないし、または他の基準に相当するかもしれない。達成度の尺度または推定値は、さまざまなイコライザの構成を比較する手段を提供する。次に、選択されたイコライザ構成は、受信データ信号の処理のために使用される。

30

## 【0014】

レシーバーは、レシーバーの性能が、可能なチャネル条件およびチャネル変化の割合の「全体」にわたってレシーバーの性能が最適であるならば「普遍的特性」（ユニバーサル）という名前がつけられる。MSE推定値またはC/I推定値に基づいて選択されたイコライザが実際には、すべての評価した構成の中で最良のイコライザ構成であるならば、複数の仮想並列イコライザを備えたレシーバーは、「ユニバーサル」である。したがって、正確なMSE推定値あるいはC/I推定値は、複数の仮想並列イコライザを備えたレシーバーを「ユニバーサル」にするために必要である。そのようなレシーバーの例示実施形態は以下に記載される。

40

## 【0015】

「例示」という言葉は、ここでは「例、インスタンスあるいは実例として役立つこと」を意味するために使用される。「例示」としてここに記載される任意の実施形態は、他の実施形態に対して好適であるまたは利点があると必ずしも解釈されない。

## 【0016】

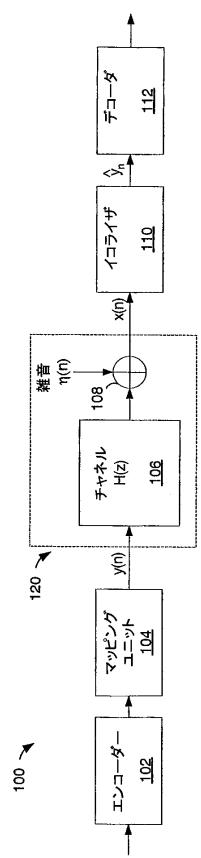

図1Aは、通信システム100の要素の一部を図解する。他のブロックおよびモジュールは図解されたこれらのブロックに加えて通信システムに組み入れてもよい。ソース（図示せず）によって生成されたビットは、シグナリング星座のシンボルに組み立てられ、コード化され、次に、写像される。ソースによって提供される2進法数字のシーケンスは情報系列と呼ばれる。情報系列は、ビットシーケンスを出力するエンコーダ102によって

50

コード化される。エンコーダ 102 の出力はマッピングユニット 104 に供給される。マッピングユニットは、通信チャネルへのインターフェースとして役立つ。マッピングユニット 104 は、複雑な価値のあるシグナリング星座のシンボル  $y(n)$  へエンコーダ出力シーケンスを写像する。さらに、通信チャネルおよびアナログレシーバー処理と同様に変調ブロックを含む送信処理も、セクション 120 によりモデル化される。

【0017】

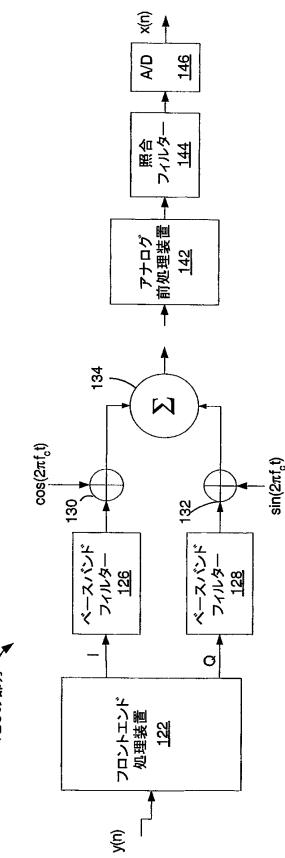

図 1B は、図 1A のセクション 120 の内に含まれた詳細のうちのいくつかを図解する。

【0018】

図 1B に図解されるように、複合記号  $y(n)$  は、アナログ信号パルスに変調され、結果として生じる複雑なベースバンド波形は、搬送波信号の同相ブランチおよび直交位相ブランチに正弦波的に変調される。結果として生じるアナログ信号は、通信チャネルを介して R F アンテナ（図示せず）によって送信される。M 進位相シフトキーイング（M-PSK）、 $2^M$  進直交振幅変調（ $2^M$ QAM）、等のようなさまざまな変調スキームがこの方法で実施されてもよい。

【0019】

各変調スキームは、1つ以上のビットを固有の複素シンボルに写像する関連する「シグナリング星座」を有する。例えば、4-PSK 変調では、2つの符号化ビットが、4つの可能な複素数値 {1, i, -1, -i} の1つへ写像される。従って、複合記号  $y(n)$  はそれぞれ4つの可能な値を取ってもよい。一般に、M-PSK の場合、 $\log_2 M$  の符号化ビットは、単位複素数円上に横たわっている M の可能な複素値の1つに写像される。

【0020】

図 1B を続けると、レシーバーでは、アナログ波形は、ナイキスト周波数の適切な倍数でのように、ダウンコンバートされ、フィルターされ、サンプルされる。結果として生じるサンプルは、イコライザ 110 により処理される。イコライザ 110 は、セクション 120 によりモデル化されるように、チャネルにより導入される、信号歪、および他の雑音および干渉を修正する。イコライザ 110 は、送信されたシンボル  $y(n)$  の推定値を出力する。次に、シンボル推定値はデコーダーによって処理され、オリジナル情報ビット、すなわち、エンコーダー 102 への入力であるソースビットを決定する。

【0021】

図 1A および 1B に図解されるパルスフィルタ、I-Q 変調器、チャネル、およびレシーバーのフロントエンド中のアナログプロセッサの組合せは、インパルス応答  $\{h_k\}$  および z 変換  $H(z)$  を有する線形フィルター 106 によってモデル化される。この場合、チャネルにより導入される干渉と雑音は付加的白色ガウス雑音（AWGN）としてモデル化される。

【0022】

図 1B は、それぞれ同相（I）成分および直交（Q）成分を処理するために、ベースバンドフィルター 126 および 128 に接続されたフロントエンド処理装置 122 を含む処理セクション 120 の詳細を示す。次に、ベースバンドフィルタ 126, 128 はそれぞれの搬送波との乗算のために乗算器に接続される。次に、結果として得られる波形は、加算ノード 134 で加算され、通信チャネルを介してレシーバーに送信される。レシーバーでは、アナログ前処理装置 142 は送信された信号を受信する。送信された信号は処理され、照合フィルター 144 にわたされる。次に、照合フィルター 144 の出力は、アナログ / デジタル（A/D）コンバーター 146 に供給される。他のモジュールを、設計および運用上の基準に従って実施してもよいことに留意する必要がある。図 1A および図 1B のコンポーネントおよびエレメントは以下の記述の理解のために提供され、通信システムの完全な記載であるようには意図されない。

高データレート通信システム

【0023】

可変レートデータ要求スキームを採用する例示 H D R 通信システムにおけるレシーバー

10

20

30

40

50

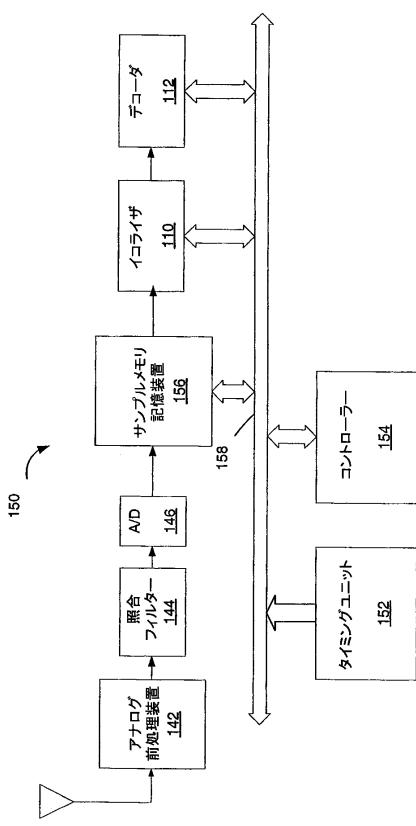

は図2に示される。レシーバー150は、基地局(図示せず)にリバースリンク上のデータを送信することにより地上にあるデータネットワークと通信している加入者局である。基地局はデータを受信し、そのデータを基地局コントローラー(BSC)(図示せず)を介して地上にあるネットワークに送る。反対に、加入者設備150への通信は、BSCを経由して、地上にあるネットワークから基地局に送ってもよく、基地局からフォワードリンク上の加入者装置150に送信してもよい。フォワードリンクは、基地局から加入者設備までの送信を指す。また、リバースリンクは加入者設備から基地局への送信を指す。

#### 【0024】

典型的なHDR通信システムにおいて、基地局から加入者設備150までのフォワードリンクデータ送信が、フォワードリンクに支援されてもよい最大データ転送速度で、あるいはその最大データ転送速度の近くで生じなくてはならない。最初に、加入者設備150は、所定のアクセス手続きを使用して、基地局との通信を確立する。この接続状態では、加入者設備150は基地局からデータメッセージおよび制御メッセージを受信してもよく、データおよび制御メッセージを基地局に送信することができる。次に、加入者設備150は、基地局150からのフォワードリンク送信のC/Iを評価する。フォワードリンク送信のC/Iは基地局からのパイロット信号を測定することにより得てもよい。C/I推定に基づいて、加入者設備150は、割り当てられたDRCチャネル上のData Rate Control(DRC)メッセージとして基地局へデータレート要求メッセージを送信する。DRCメッセージは要求されたデータレート、または、二者択一的に、フォワードリンクチャネルの品質の表示、例えば、C/I測定自体、ビットエラーレートあるいはパケットエラーレートを含んでいてもよい。基地局は、加入者設備150からのDRCメッセージを用いて最高の可能な速度でフォワードリンクデータを効率的に送信する。

#### 【0025】

BSC(図示せず)は、パケットネットワークインターフェース、PSTNおよび/または他の基地局とインターフェースしてもよい。そして、加入者設備と他のユーザーとの間の通信を調整するように働く。

#### 【0026】

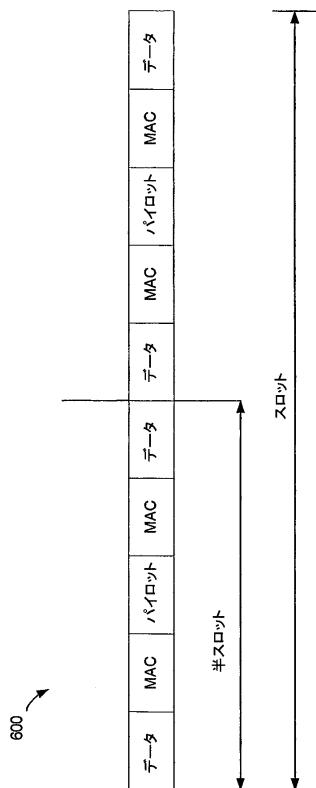

フォワードリンクパイロットチャネルは、パイロット信号を供給する。パイロット信号は、初期取得、位相回復、およびタイミング回復のために加入者設備150により使用されてもよい。さらに、パイロット信号は加入者設備150により使用されてC/I測定を実行してもよい。記載された例示実施形態において、フォワードリンク上の各タイムスロットは2048チップの長さであり、2つのパイロットバースト(pilot bursts)がタイムスロットの第1四半期および第3四半期で生じる。各パイロットバーストは、持続時間が96チップである。HDRシステムでのスロットの一例は図8で図解される。図8において、各スロットは2つの部分を有する。各半スロットは、パイロットバーストを含む。

#### 【0027】

フォワードリンク送信は加入者設備150でアンテナによって受信される。受信信号は、アンテナから、アナログ前処理装置142内のレシーバー、照合フィルター144、アナログ/デジタル(A/D)変換器に送られる。レシーバーは信号をフィルタし、増幅し、ベースバンドにダウンコンバートし、ベースバンド信号を直交復調し、ベースバンド信号をデジタル化する。デジタル化されたベースバンド信号は、復調器に接続される。復調器は、搬送波とタイミング回復回路を含み、さらにイコライザ110を含む。イコライザ110は ISIを補償し、デジタル化されたベースバンド信号からのシンボル推定値を生成する。シンボル推定値は通信バス158によってコントローラー154につながれる。

#### 【0028】

次に、コントローラーはDRCメッセージを生成する。イコライザ110の出力もデコーダ112に供給される。デコーダ112、イコライザ110およびコントローラー154は各々、通信バス158につながれる。

#### 【0029】

10

20

30

40

50

D R C メッセージの生成に加えて、コントローラー 154 はリバースリンク上のデータおよびメッセージ送信を支援するために使用してもよい。コントローラー 154 はマイクロコントローラ、マイクロプロセッサー、デジタル信号処理 (D S P) チップ、ここに記載した機能を行なうようにプログラムされた A S I C、または技術的に知られた任意の他の実施で実施してもよい。タイミングユニット 152 も通信バス 158 につながれる。

### 【0030】

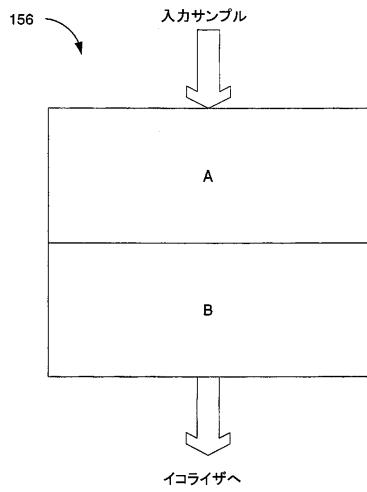

典型的な実施形態は、通信バス 158 を経由して、イコライザ 110 およびコントローラー 154 につながれたサンプルメモリ記憶装置 156 を含む。サンプルメモリ記憶装置 156 は図 4 に図解され以下に記載される。

#### 仮想並列イコライザ

10

上記に議論されるように、ユニバーサルレシーバーの性能は、複数のチャネルタイプにわたって、およびチャネル変化の複数のレートのために効率的に最適化される。

### 【0031】

ユニバーサルレシーバーを実現する 1 つの方法は並列イコライザを使用することである。このオプションはコストなしではない。特に並列有限インパルス応答 (F I R) フィルターを実施するためのハードウェアのコストはひどく高い。しかしながら、ハードウェアの処理速度および柔軟性を利用することにより、並列イコライザを仮想的に実施してもよい。

### 【0032】

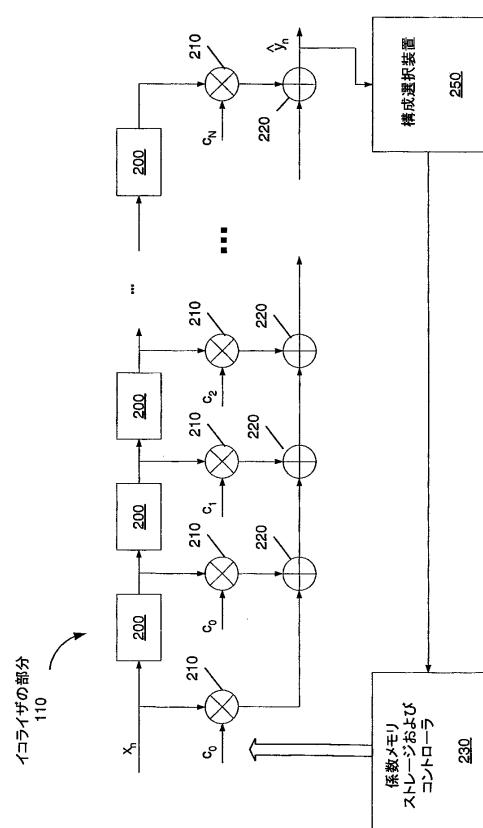

イコライザ 110 は 1 セットの仮想並列イコライザとして動作するようにレシーバー 150 内で操作される。イコライザ 110 の部分は、図 3 にさらに図解される。例示実施形態によって、受信されるサンプル  $X_n$  は、イコライザ 110 に印加される前にサンプルメモリ記憶装置 156 に記憶される。記憶装置 156 は、サンプルの複数の半スロットを同時に記憶するように設計されている。このように、サンプルの 1 つの半スロットがサンプルメモリ記憶装置 156 に書かれている間に、サンプルの以前の半スロットがイコライザ 110 により読み出され、処理される。例えば、 $T = 0.833 \text{ ms}$  である H D R の場合のように、 $T$  秒の持続時間を有する半スロットの場合、メモリのリード / ライト衝突は、サンプルの各半スロットが  $T$  秒未満で読み出され処理される限り回避されるかもしれない。サンプルの半スロットを処理することは、適応フィルタリングアルゴリズムを介してのよう半スロット内のパイロットバーストに関するイコライザ係数を訓練し、イコライザ 110 を用いて半スロット内の 1 つ以上のデータセグメントをフィルタリングすることを含む。コントローラー 154 およびタイミングユニット 152 として。現在の実施形態によれば、イコライザは、シンボル送信レートより高い内部クロックレートを有する F I R フィルターを実施する。この実施形態によれば、F I R 実施は、仮想イコライザを実施するための能力を提供する。そのような訓練およびフィルタリングは、許容可能時間  $T$  の一部に過ぎない。例えば、イコライザを訓練し、データセグメントをフィルターするのに、それぞれ、 $0.1T$  秒および  $0.3T$  秒かかるかもしれない。もし他の信号処理が必要でなかったならば、イコライザ 110 は、およそ  $0.6T$  秒の期間アイドル状態であり、イコライザ 110 の再使用のために  $0.4T$  秒許容したであろう。

20

### 【0033】

30

サンプル記憶装置 156 は、リードアクセスメモリ (R A M) のような、受信サンプル情報を書いたり、再書き込みできる揮発性メモリである。サンプル記憶装置 156 は図 4 に図解され、2 つの部分 A および B を有する。A / D 出力からのサンプルは、サンプルメモリ記憶装置 156 に連続して記憶され、そこからイコライザ 110 に供給される。1 つの半スロットの期間に、A / D 出力からのサンプルは、A で示される R A M の部分に連続して書き込まれる。これらのサンプルが書かれている間に、イコライザは B で示される R A M の部分からサンプルを読み処理してもよい。イコライザが、A で示される R A M 部分を充填するのにかかる時間よりも、B で示される R A M 部分からサンプルを読み出して処理する時間が少ない限り、メモリにリード / ライト衝突は起きない。イコライザが B からのサンプルの処理を完了し、R A M 部分 A が充填されると、イコライザは次に、次の半ス

40

50

ロットのサンプル、すなわち、RAM部分Aのサンプルを処理し、一方、A/D出力サンプルは、RAM部分Bに現在連続的に書かれている。

## 【0034】

イコライザ110は複数の遅延装置200を含む。遅延装置200間に接続されるのは、乗算器またはタップ210である。各乗算器は対応する係数を有する。この係数は、種々のタップ構成のための重み付け係数として考えてもよい。係数は $c_i$ として識別される。但し $i = 0, 1, \dots, N-1$ である。次に、乗算器210の各々は一連の加算器220につながれる。加算器220は直列に接続され、累積出力

## 【数1】

10

$\hat{y}_n$

## 【0035】

を出力する。この累積出力は、対応する係数値により乗算された各タップ値の期間を含む。

## 【0036】

20

イコライザ110の出力

## 【数2】

$\hat{y}_n$

## 【0037】

30

は、送信されたシンボルの推定値である。

## 【0038】

1つ以上の出力

## 【数3】

$\hat{y}_n$

40

## 【0039】

が構成選択装置250に供給される。構成選択装置250は、各構成に対して結果の出力

【数4】

$$\{\hat{y}_n\}$$

【0040】

を記憶する。構成はそれぞれ、係数値の異なるセットを持っている。1つ以上の係数をゼロに設定するように係数値を変更することは、イコライザの長さを効率的に変更することに留意する必要がある。例えば、係数  $c_0, c_1, c_{N-2}$  および  $c_{N-1}$  がゼロに設定されるなら、イコライザの長さは、NタップからN-4タップに効率的に低減される。半スロット毎に、構成選択装置250は、出力、すなわち、各構成のシンボル推定値

【数5】

$$\{\hat{y}_n\}$$

20

【0041】

を解析し、その半スロットに最良の構成を決定する。次に、構成選択装置250は構成情報、すなわち係数値を係数メモリストレージおよびコントローラー230に供給する。コントローラー230は乗算器210に適切な係数値を供給する。1つの実施形態によれば、構成選択装置250が出力

【数6】

$$\{\hat{y}_n\}$$

30

【0042】

と既知パイロットシンボルの間のMSEを評価し最も小さな評価されたMSEを備えた構成を決定することに注意する必要がある。別の実施形態において、構成選択装置250は、

出力

【数7】

$$\{\hat{y}_n\}$$

40

【0043】

を与えてC/Iを評価し、最も高く評価されたC/Iを備えた構成をそこから決定する。

50

## 【0044】

1つの実施形態では、イコライザ110は、システムに必要とされた最長の長さのために設計されている。イコライザ110はNの係数を有するNタップFIR、および対応する遅延線を含む。イコライザ110用のFIR係数には所望の値がロードされる。

## 【0045】

1セットの中間のイコライザ長さ {  $N_i$  :  $i = 1 \dots n$  } は、nの「仮想」イコライザに対して選択される。仮想イコライザは、有効にイコライザの長さを変更するために、ゼロに設定された係数を備えたフルレンジスイコライザに言及する。選択された長さのセットは、以下によって決定される：

【数8】

10

$$0 = N_0 < 1 \leq N_1 < N_2 < \dots < N_n \leq N < N_{n+1} = \infty \quad (1)$$

## 【0046】

(1) 方法がNを仮定し、 $N_i$ の各々が奇数であるなら、i番目の仮想イコライザは、さらなる限定

20

【数9】

$$h_i(k) = 0, \quad \text{for } (N_i - 1)/2 < |k| \leq (N - 1)/2 \quad (2)$$

## 【0047】

を備えて、

30

【数10】

$$\{h_i(k) : |k| \leq (N - 1)/2\}$$

## 【0048】

として書いてもよい。

40

## 【0049】

i番目の仮想イコライザは $N_i$ のノンゼロ係数のみを有する、すなわち、i番目の係数は長さ $N_i$ を有することに留意する必要がある。イコライザ110は、nの仮想イコライザの各々に対してイコライザ係数 {  $h_i(k)$  } を記憶するための係数メモリストレージおよびコントローラー230を含む。

## 【0050】

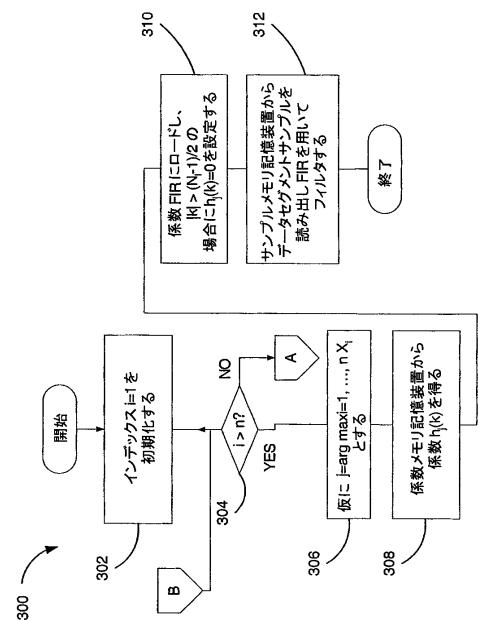

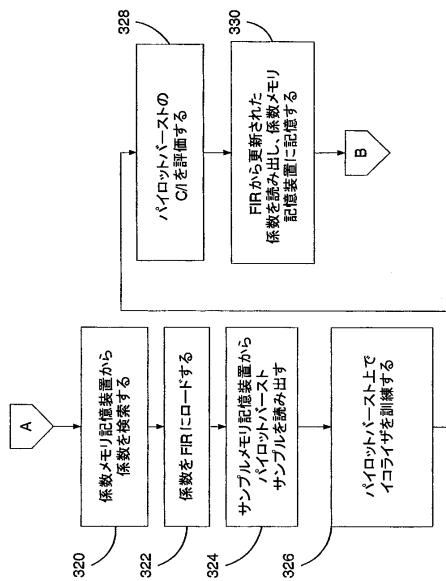

図5は、イコライザ110中のサンプルを処理する1つの方法300を図解する。

## 【0051】

そのプロセスはステップ302で $i = 1$ としてインデックスを初期化する。決定ダイヤモンド304では、インデックスは仮想イコライザnの数と比較される。n以下のインデッ

50

クス  $i$  の場合、処理は図 6 のステップ 320 に継続し、係数メモリストレージおよびコントローラー 230 から係数  $\{ h_i(k) : |k| < (N_i - 1) / 2 \}$  を検索する。次に、係数はステップ 322 で FIR にロードされる。次に、プロセスはステップ 324 でサンプルメモリ記憶装置 156 からパイロットバーストサンプルを読む。次に、イコライザは上述のステップ 326 で供給された式 (2) の制限を強化しながらパイロットバースト上で訓練する。トレーニングは、適応アルゴリズムのために、係数更新中にある係数用の加算器 220 を不能にすることにより行われてもよい。適応アルゴリズムステップサイズは、またイコライザが  $N_i - N$  を有することを認識するために調節される必要があることに留意する必要がある。レシーバー 150 は、イコライザ 110 の FIR のトレーニングと同時に、C/I あるいはパイロットバーストの MSE をステップ 328 において、評価する。

10

#### 【0052】

パイロットバースト上で訓練した後に、プロセスは、FIR から更新された係数を読み、その値を係数メモリ記憶装置 230 に返す。評価された C/I は、 $X_i$  と呼ばれる。処理は図 5 のステップ 306 に戻り、

#### 【数 11】

$$j = \arg \max_{i=1, \dots, n} X_i$$

20

#### 【0053】

を設定する。

#### 【0054】

次に、プロセスはイコライザ長さを  $j$  番目の仮想イコライザの長さ、すなわち  $N_j$  として設定する。 $N_j$  はステップ 308 において現在の半スロット上で最適であると考えられる。対応する係数  $\{ h_j(k) : |k| < (N_j - 1) / 2 \}$  は、係数メモリ記憶装置 230 から検索される。次に、係数はステップ 310 においてイコライザ 110 にロードされ、 $h_j(k) = 0$ 、但し  $(N_j - 1) / 2 < |k| < (N_j - 1) / 2$  を設定する。次に、データセグメントサンプルはサンプル記憶装置 156 から読まれ、ステップ 312 で FIR を使用してフィルタされる。

30

#### 【0055】

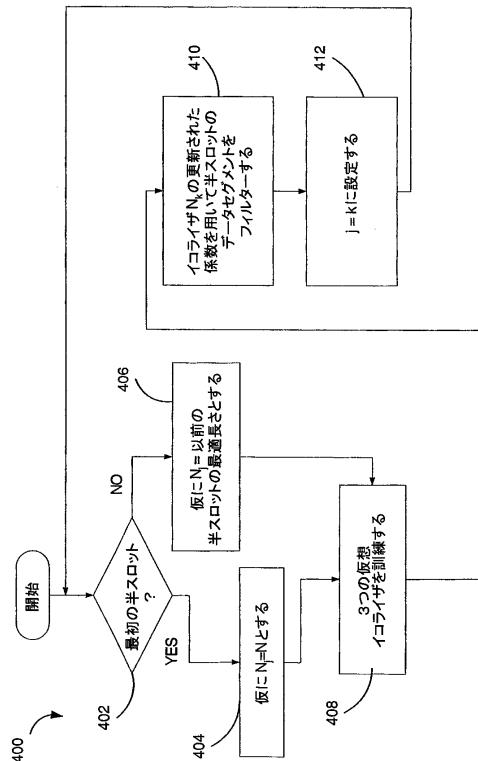

無線通信システムにおいて典型的なチャネルに関しては、最適のイコライザ長さが単にゆっくり変わりそうである。従って、最適のイコライザ長さは大多数の連続する半スロットに対してたぶん変化しないであろう。長さ  $N_j$ 、 $N_{j-1}$ 、 $N_{j+1}$  の並列の 3 つのイコライザを考える。長さ  $N_j$  は、以前の半スロット上の最適な長さとして選択される。すなわち  $j$  番目の構成は以前の半スロット上で最適である。長さ  $N_j$ 、 $N_{j-1}$  および  $N_{j+1}$  は式 (19) によって選ばれる。いつも  $n$  の仮想イコライザの全体のファミリーを訓練するよりもむしろ、変形された実施形態は、3 つの仮想イコライザのみを訓練する。方法 400 は図に図解される。プロセスは、 $j$  を  $n$  に設定し、長さ  $N_j$  を  $N$  に設定することにより開始される。長さが  $\max(N_{j-1}, 1)$ 、 $N_j$ 、および  $\min(N_{j-1}, N)$  の 3 つの仮想イコライザが 408 で訓練される。長さ  $N_k$  のイコライザ構成が最高に評価された C/I をステップ 409 で生じるように  $k$  を設定する。ステップ 410 において、プロセスは、イコライザ  $N_k$  の更新された係数を使用して、半スロットのデータセグメントをフィルターする。インデックス  $j$  はステップ 412 で  $k$  と等しく設定される。また、プロセスは決定ダイヤモンド 402 に返る。プロセスは、 $j$  を  $k$  に設定し、 $N_i$  を  $N_k$  に設定し、次の半スロットに続く。3 つのイコライザが代表例として提供される。任意の数の仮想イコライザへの拡張は、同様の方法で実施される。

40

#### 【0056】

50

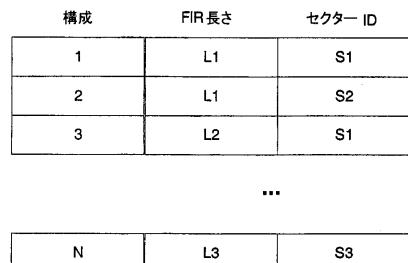

上述した仮想並列イコライザは、特定のフィルター構成を組込むイコライザ、すなわち、固定された所定の長さの F I R フィルターを考えるけれども、概念は任意のイコライザ構成に適用してもよい。さらに、他のイコライザパラメーターは選択処理に組み込んでもよい。イコライザパラメーターは、イコライザの機能および動作を定義する任意の変数を包含する。イコライザパラメーターは、これらに限定されないが、D C オフセット値または入力サンプルのための位相オフセットまたはセクター識別子を含む。さらに、訓練は、複数のパラメーターが各構成のために変更される様々なイコライザ構成のために実行してもよい。例えば、並列に訓練されたイコライザ構成中で、1つの構成はセクター M に割り当てられた長さ L のイコライザでありえる。別の構成はセクター M' に割り当てられた長さ L' のイコライザでありえる。各構成については、M S E、C / I あるいはS I N R のような性能測定または評価が記憶される。次に、各構成の性能測定が比較され、最適な構成が決定される。

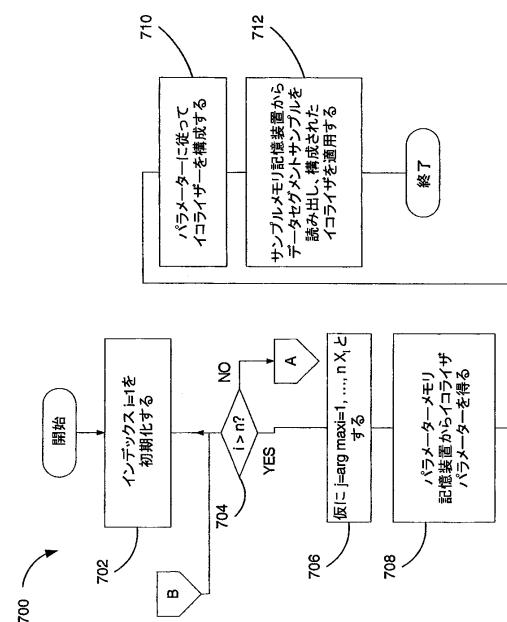

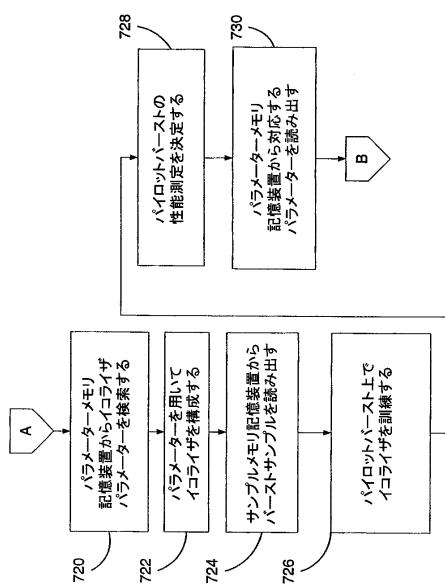

【0057】

一般的な場合は図9および図10に図解される。イコライザ110中のサンプルを処理する方法700は、ステップ702で  $i = 1$  としてインデックスを初期化する。決定ダイヤモンド704では、インデックスは仮想イコライザ n の数と比較される。n 以下のインデックス  $i$  の場合、処理は、図10のステップ720に続き、メモリストレージおよびコントローラー230と同様のパラメーターメモリ記憶装置からイコライザパラメーターを検索する。次に、パラメーターはステップ722でイコライザを構成するために使用される。次に、プロセスは、ステップ724で、サンプルメモリストレージ装置156のようなサンプルメモリ記憶装置からパイロットバーストサンプルを読む。次に、イコライザはステップ726でパイロットバースト上で訓練する。レシーバー150は、イコライザ110のトレーニングと同時に、パイロットバーストの性能手段をステップ728で評価する。パイロットバースト上で訓練した後に、プロセスは対応するパラメーターを読み、ステップ730でパラメーターメモリ記憶装置に値を返す。測定された性能パラメータは  $X_i$  と呼ばれる。処理は図9のステップ706に戻り、

【数12】

$$j = \arg \max_{i=1,\dots,n} X_i$$

【0058】

を設定する。

【0059】

次に、プロセスは仮想イコライザ N j の長さとしてイコライザ長さを選択する。イコライザ長さはステップ708において、現在の半スロットに最適である。対応するイコライザパラメーターはパラメーターメモリ記憶装置から検索される。次に、パラメーターはステップ710でイコライザ110を構成するために使用される。次に、データセグメントサンプルがサンプルメモリ記憶装置から読まれ、ステップ712において、構成されたイコライザを用いて処理される。

【0060】

イコライザ110の最適化は並列のイコライザの訓練により行なってもよい。この場合、並列のイコライザの各々は、イコライザ110の構成を定義する。最適の構成は各構成の性能の比較により選択される。そのようなトレーニングおよび比較に選ばれた並列のイコライザは、任意のイコライザのパラメーター、あるいはイコライザパラメーターの組合せによって定義してもよい。例えば、1つのシナリオでは、並列イコライザは、決定フィードバックイコライザとして実施してもよい。そして異なる構成は、各構成において使用

10

20

30

40

50

されるフィードバックフィルターおよびフィードフォワードフィルターの長さを別個に指定してもよい。別のシナリオでは、イコライザパラメーターはセクター識別子を含んでいてもよい。この場合、レシーバーは、ソフトハンドオフ状況でのように複数の送信器からのデータサンプルを受信することができる。この場合、セクター識別子は、比較のためにさらに条件またはイコライザパラメーターを提供する。目標は、受信のために最良のセクターを選択することである。図11は、イコライザ110を最適化するために使用してもよい、インデックス1乃至Nがつけられた構成のテーブルを図解する。最初の構成は長さL1を有するFIR110により定義される。この場合、長さは、ノンゼロ係数を有するフィルタータップの数およびセクターS1を識別する受信セクターの数を指す。他の構成は同様に与えられる。この場合、L2はL1に等しくないかもしれない。またセクターS1およびS2は、通信システム内の異なるセクターであってもよい。種々の構成がイコライザに適用され、性能測定が行われまたは評価される。次に、性能手段は各基準に対して比較され、最適な構成を決定する。次に、最適の構成は、サンプル記憶装置に記憶されたデータに適用される。この場合、最適の構成は、さらに、最適の受信のための最良のセクターに関してレシーバーに指示を供給する。任意の数のパラメーターおよびパラメーターの組み合わせを採用してもよい。

#### 【0061】

上記に提供される例において、サンプル記憶装置の使用は、仮想並列イコライザの実施を可能にする。所定の送信レートで受信したサンプルを記憶することにより、レシーバーは、さまざまな構成のイコライザを訓練するための時間が提供され、それにより最適な構成を選択し、サンプルデータを実際に処理する前に最適構成に調節する。パイロットペーストもサンプル記憶装置に記憶され、イコライザを訓練する際に使用のためにそこから検索される。

#### 【0062】

##### 性能測定

上記に記述されるように、イコライザ構成は、SINR、C/Iあるいは他の性能基準の測定に基づいて選択してもよい。他の性能基準は、例えば、パイロットサンプル上で測定されたイコライザ構成の平均平方誤差を含んでいるかもしれない。例えば、パイロットサンプル上のイコライザ出力が

#### 【数13】

$$\{\hat{y}_n : n = 1, \dots, K\}$$

#### 【0063】

によって与えられ、所望のパイロットシンボルが

#### 【数14】

$$\{y_n : n = 1, \dots, K\}$$

#### 【0064】

により示されるなら、この構成の平均平方誤差は、

10

20

30

40

【数15】

$$MSE = \frac{1}{K} \sum_{n=1}^K |\hat{y}_n - y_n|^2 \quad (3)$$

【0065】

により与えられる。SINRまたはC/I評価の1つの定義は下記である：

【数16】

$$SINR = \frac{1}{MSE} - 1 \quad (4)$$

【0066】

他の定義または性能測定も可能である。

【0067】

上記に示されたモデル、方法、および装置は、異なるシステム、チャネル条件およびレシーバー設計を支援する種々の実施形態の例として役立つ。上記に記述されるような並列イコライザのアプリケーションは、これに限定されないが、高いデータレートシステムを含み、様々な通信システムでの動作に適応された任意の様々なレシーバーにおいて実施してもよい。

【0068】

当業者は、ここに開示した実施の形態に関連して記載した種々の実例となる論理ブロック、モジュール、回路、およびアルゴリズムステップは、電子ハードウェア、コンピュータソフトウェアまたは両方の組合せで実施してもよいことを理解するであろう。このハードウェアとソフトウェアの互換性を明瞭に説明するために、種々の実例となる部品、ブロック、モジュール、回路、およびステップが一般にそれらの機能性の観点から上に記載された。そのような機能性がハードウェアまたはソフトウェアとして実現されるかは特定のアプリケーションおよび全体のシステムに課せられた設計制約に依存する。熟達した職人は、各特定のアプリケーションに対して記載した機能性を変形した方法で実施することができるが、そのような実施の判断は、この発明の範囲を逸脱するものとして解釈されるべきでない。

【0069】

ここに開示された実施の形態に関連して記載された種々の実例となる論理ブロック、モジュール、および回路は、汎用プロセッサ、デジタルシグナルプロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)または他のプログラマブル論理装置、ディスクリートゲートまたはトランジスタロジック、ディスクリートハードウェアコンポーネント、またはここに記載した機能を実行するように設計されたいずれかの組合せを用いて実施または実行してもよい。汎用プロセッサは、マイクロプロセッサであってよいが、別の方法では、プロセッサは、いずれかの一般的なプロセッサ、コントローラ、マイクロコントローラ、またはステートマシンであってよい。プロセッサはまた、計算装置の組合せとしても実施できる。例えば、DSPとマイクロプロセッサの組合せ、複数のマイクロプロセッサ、DSPコアと協力した1つ以上のマイクロプロセッサまたはいずれかの他のそのような構成として実施してもよい。

【0070】

ここに開示された実施の形態に関連して記載された方法またはアルゴリズムのステップ

10

20

30

40

50

は、ハードウェアにおいて、プロセッサにより実行されるソフトウェアモジュールにおいて、または両者の組合せにおいて直接具現化してもよい。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、脱着可能ディスク、CD-ROM、または技術的に知られているその他のいずれかの形態の記憶媒体に常駐してもよい。例示記憶媒体は、プロセッサに接続される。そのようなプロセッサは記憶媒体から情報を読み出し、記憶媒体に情報を書き込むことができる。別の方では、記憶媒体は、プロセッサに集積可能である。プロセッサと記憶媒体はASICに存在してもよい。ASICはユーザ端末に存在してもよい。別の方では、プロセッサと記憶媒体はユーザー端末内のディスクリートコンポーネントとして存在してもよい。

10

#### 【0071】

好適実施の形態の上述の記載は当業者がこの発明を製作または使用することを可能にするために提供される。これらの実施の形態に対する種々の変更は当業者には容易に明白であろう、そしてここに定義される包括的原理は発明力の使用なしに他の実施の形態に適用可能である。従って、この発明は、ここに示した実施の形態に限定されることを意図したものではなく、ここに開示した原理と新規な特徴に一致する最も広い範囲が許容されるべきである。

#### 【図面の簡単な説明】

#### 【0072】

【図1A】図1Aは通信システムでのコンポーネントのブロック図である。

20

【図1B】図1Bは、図1Aのような通信システムの詳細な部分である。

【図2】図2は、線形イコライザを使用するレシーバーのブロック図である。

【図3】図3は、図2のような線形イコライザの図である。

【図4】図4はサンプルメモリ記憶装置の図である。

【図5】図5は、複数の「仮想並列」イコライザを実施するプロセスを図解する。

【図6】図6は、複数の「仮想並列」イコライザを実施するプロセスを図解する。

【図7】図7は、3つの「仮想並列」イコライザを実施するためのプロセスを図解する。

【図8】図8は高データレートシステムにおけるスロット構造のブロック図である。

【図9】図9は、様々なイコライザパラメーターのためにイコライザを訓練するプロセスを図解する。

30

【図10】図10は、様々なイコライザパラメーターのためにイコライザを訓練するプロセスを図解する。

【図11】図11は様々なイコライザ構成を図解する。

【図 1 A】

【図 1 B】

【図 2】

【図 3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

## フロントページの続き

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 ジャヤラマン、スリカント

アメリカ合衆国、カリフォルニア州 92109、サン・ディエゴ、ナンバー1、パシフィック・

ビーチ・ドライブ 1254

(72)発明者 フエルナンデズ・コーバトン、イバン・ジーザス

アメリカ合衆国、カリフォルニア州 92109、サン・ディエゴ、ダイアモンド・ストリート

1033

(72)発明者 スミー、ジョン・イー

アメリカ合衆国、カリフォルニア州 92122、サン・ディエゴ、ナンバーエフ-406、トス

カナ・ウェイ 5340

(72)発明者 ハワード、マイケル・エー

アメリカ合衆国、カリフォルニア州 92007、カーディフ、ワーウィック・アベニュー 46

5

## 合議体

審判長 吉村 博之

審判官 近藤 聰

審判官 加藤 恵一

(56)参考文献 特表2002-527997(JP,A)

特開2000-286817(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04B 3/00

H04L 27/00