(19)中華民國智慧財產局

(12)發明說明書公告本 (11)證書號數：TW I662710 B

(45)公告日：中華民國 108(2019)年 06 月 11 日

(21)申請案號：103117141

(22)申請日：中華民國 103(2014)年 05 月 15 日

(51)Int. Cl. : H01L29/78 (2006.01)

H01L29/40 (2006.01)

(30)優先權：2013/05/20 日本 2013-106284

2013/07/16 日本 2013-147191

2013/09/23 日本 2013-196300

2014/04/21 日本 2014-087067

(71)申請人：日商半導體能源研究所股份有限公司(日本) SEMICONDUCTOR ENERGY

LABORATORY CO., LTD. (JP)

日本

(72)發明人：花岡一哉 HANAOKA, KAZUYA (JP) ; 松林大介 MATSUBAYASHI, DAISUKE (JP) ; 小林由幸 KOBAYASHI, YOSHIYUKI (JP) ; 山崎舜平 YAMAZAKI, SHUNPEI (JP) ; 松田慎平 MATSUDA, SHINPEI (JP)

(74)代理人：林志剛

(56)參考文獻：

|    |                |    |                |

|----|----------------|----|----------------|

| TW | I356497        | TW | 200505016A     |

| TW | 201120947A     | TW | 201236157A     |

| US | 8274079B2      | US | 8431927B2      |

| US | 2011/0140100A1 | US | 2012/0058598A1 |

| US | 2012/0146713A1 | US | 2012/0146713A1 |

| US | 2012/0319114A1 | US | 2012/0319183A1 |

| US | 2013/0009209A1 |    |                |

審查人員：劉聖尉

申請專利範圍項數：13 項 圖式數：40 共 153 頁

(54)名稱

半導體裝置

SEMICONDUCTOR DEVICE

(57)摘要

本發明的一個方式的目的之一是提供一種能夠抑制隨著微型化而逐漸顯著的電特性下降的半導體裝置。該半導體裝置包括：第一氧化物膜；第一氧化物膜上的氧化物半導體膜；與氧化物半導體膜接觸的源極電極及汲極電極；氧化物半導體膜、源極電極及汲極電極上的第二氧化物膜；第二氧化物膜上的閘極絕緣膜；以及與閘極絕緣膜接觸的閘極電極，其中，從通道寬度方向看時，氧化物半導體膜的上端部帶弧形。

Provided is a semiconductor device in which deterioration of electric characteristics which becomes more noticeable as the semiconductor device is miniaturized can be suppressed. The semiconductor device includes a first oxide film, an oxide semiconductor film over the first oxide film, a source electrode and a drain electrode in contact with the oxide semiconductor film, a second oxide film over the oxide semiconductor film, the source electrode, and the drain electrode, a gate insulating film over the second

oxide film, and a gate electrode in contact with the gate insulating film. A top end portion of the oxide semiconductor film is curved when seen in a channel width direction.

指定代表圖：

圖 1B

符號簡單說明：

- 400 . . . 基板

- 402 . . . 基底絕緣膜

- 404 . . . 多層膜

- 404a . . . 第一氧化物膜

- 404b . . . 氧化物半導體膜

- 404c . . . 第二氧化物膜

- 406a . . . 源極電極

- 406b . . . 沖極電極

- 408 . . . 閘極絕緣膜

- 410 . . . 閘極電極

- 412 . . . 氧化物絕緣膜

- 450 . . . 電晶體

# 發明專利說明書

(本說明書格式、順序，請勿任意更動)

## 【發明名稱】(中文/英文)

半導體裝置

Semiconductor device

## 【技術領域】

[0001] 本發明係關於一種半導體裝置。

[0002] 在本說明書中，半導體裝置是指能夠藉由利用半導體特性而工作的所有裝置，因此電光裝置、半導體電路以及電子裝置都是半導體裝置。

## 【先前技術】

[0003] 藉由利用形成在具有絕緣表面的基板上的半導體薄膜來構成電晶體的技術受到關注。該電晶體被廣泛地應用於如積體電路（IC）及影像顯示裝置（顯示裝置）等的電子裝置。作為可以應用於電晶體的半導體薄膜，矽類半導體材料被周知。另外，作為其他材料，氧化物半導體受到關注。

[0004] 例如，專利文獻 1 公開了一種電晶體，該電晶體的活性層包括包含銦（In）、鎵（Ga）及鋅（Zn）的非晶氧化物半導體。

[0005] 另外，專利文獻 2 和專利文獻 3 公開了藉由使氧化物半導體膜具有疊層結構，來提高載子移動率的技

術。

[0006]

[專利文獻 1] 日本專利申請公開第 2006-165528 號公報

[專利文獻 2] 日本專利申請公開第 2011-124360 號公報

[專利文獻 3] 日本專利申請公開第 2011-138934 號公報

[0007] 一般而言，在電路的高積體化中，電晶體的微型化是必不可少的技術。然而，已知隨著電晶體的微型化，通態電流、臨界電壓或 S 值（亞臨界值）等電晶體的電特性卻劣化。

[0008] 例如，已知在使用矽的電晶體中，當縮短通道長度時，發生 S 值的上升或者臨界電壓的向負方向的變動等的短通道效應。

[0009] 另一方面，由於使用氧化物半導體的電晶體為以電子為多數載子的積累型電晶體（通道形成在積累層中的電晶體），因此與使用矽等的反轉型電晶體（通道形成在反轉層中的電晶體）相比，當通道長度短時也不容易發生 DIBL (Drain-Induced Barrier Lowering) 效應。換而言之，使用氧化物半導體的電晶體對短通道效應具有耐性。

[0010] 此外，當縮短電晶體的通道寬度時，通態電流有可能減少。已知為了增加通態電流，加厚活性層以使

通道還形成在活性層的側面的方法，但是，這樣會增加形成有通道的表面積，所以在通道形成區與閘極絕緣膜之間的介面處載子散射增加，因此不能期待通態電流充分增加。

### 【發明內容】

[0011] 鑑於上述問題，本發明的一個方式的目的之一是提供一種能夠抑制隨著微型化而逐漸顯著的電特性下降的半導體裝置。另外，本發明的一個方式的目的之一是提供一種積體度高的半導體裝置。另外，本發明的一個方式的目的之一是提供一種通態電流特性的劣化得到抑制的半導體裝置。另外，本發明的一個方式的目的之一是提供一種低功耗的半導體裝置。另外，本發明的一個方式的目的之一是提供一種可靠性高的半導體裝置。另外，本發明的一個方式的目的之一是提供一種在關閉電源的狀態下也能保持資料的半導體裝置。另外，本發明的一個方式的目的之一是提供一種新穎的半導體裝置。

[0012] 注意，這些目的的記載不妨礙其他目的的存在。此外，本發明的一個方式並不需要實現所有上述目的。另外，可以從說明書、圖式、申請專利範圍等的記載得知並抽出上述以外的目的。

[0013] 本發明的一個方式涉及一種包括被層疊的氧化物半導體膜的半導體裝置。

[0014] 本發明的一個方式是一種半導體裝置，該半

導體裝置包括：第一氧化物膜；第一氧化物膜上的氧化物半導體膜；與氧化物半導體膜接觸的源極電極及汲極電極；氧化物半導體膜、源極電極及汲極電極上的第二氧化物膜；第二氧化物膜上的閘極絕緣膜；以及與閘極絕緣膜接觸的閘極電極，其中，當從通道寬度方向看時，氧化物半導體膜的上端部帶弧形。

[0015] 另外，在本說明書等中使用的“第一”、“第二”等序數詞是為了方便識別構成要素而附的，而不是為了在數目方面上進行限定的。

[0016] 在上述結構中，氧化物半導體膜的頂面可以具有平坦部。

[0017] 在上述結構中，當從通道寬度方向看時，氧化物半導體膜的端部的曲率半徑  $r$ （在具有兩個端部的情況下，各曲率半徑  $r_1$ 、 $r_2$ ）比 0 大且為通道寬度  $W$  的一半以下 ( $0 < r$  (或  $r_1$ 、 $r_2$ )  $\leq W/2$ )。

[0018] 在上述結構中，第二氧化物膜的上端部的位置可以與閘極絕緣膜的下端部的位置一致，並且，閘極絕緣膜的上端部的位置可以與閘極電極的下端部的位置一致。

[0019] 在上述結構中，第一氧化物膜及第二氧化物膜的導帶底的能量都較佳為比氧化物半導體膜的導帶底的能量更接近真空能階  $0.05\text{eV}$  以上且  $2\text{eV}$  以下。

[0020] 在上述結構中，可以設置有障壁膜，該障壁膜接觸並覆蓋第一氧化物膜、氧化物半導體膜、源極電

極、汲極電極、第二氧化物膜、閘極絕緣膜以及閘極電極。

[0021] 在上述結構中，可以設置有隔著障壁膜設置在第一氧化物膜、氧化物半導體膜、源極電極及汲極電極的側面上的第一側壁絕緣膜。

[0022] 在上述結構中，可以設置有隔著障壁膜設置在第二氧化物膜、閘極絕緣膜及閘極電極的側面上的第二側壁絕緣膜。

[0023] 藉由採用本發明的一個方式，能夠提供一種能夠抑制隨著微型化而逐漸顯著的電特性下降的半導體裝置。另外，能夠提供一種積體度高的半導體裝置。另外，能夠提供一種通態電流特性的劣化得到抑制的半導體裝置。另外，能夠提供一種低功耗的半導體裝置。另外，能夠提供一種可靠性高的半導體裝置。另外，能夠提供一種在關閉電源的狀態下也能保持資料的半導體裝置。另外，能夠提供一種新穎的半導體裝置。注意，這些效果的記載不妨礙其他效果的存在。此外，本發明的一個方式並不需要具有所有上述效果。另外，可以從說明書、圖式、申請專利範圍等的記載得知並抽出上述以外的效果。

### 【圖式簡單說明】

[0024] 在圖式中：

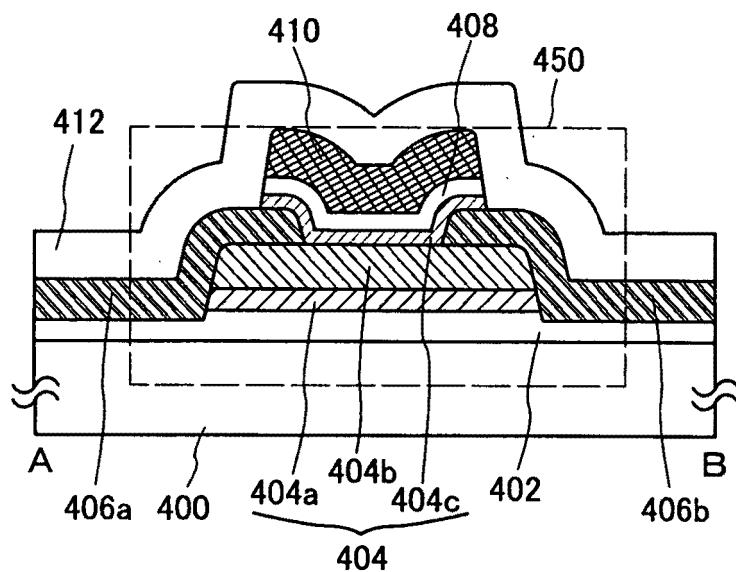

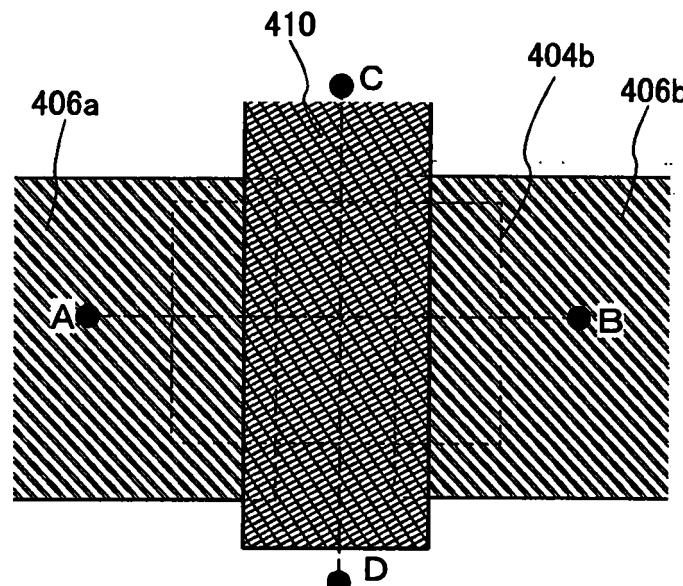

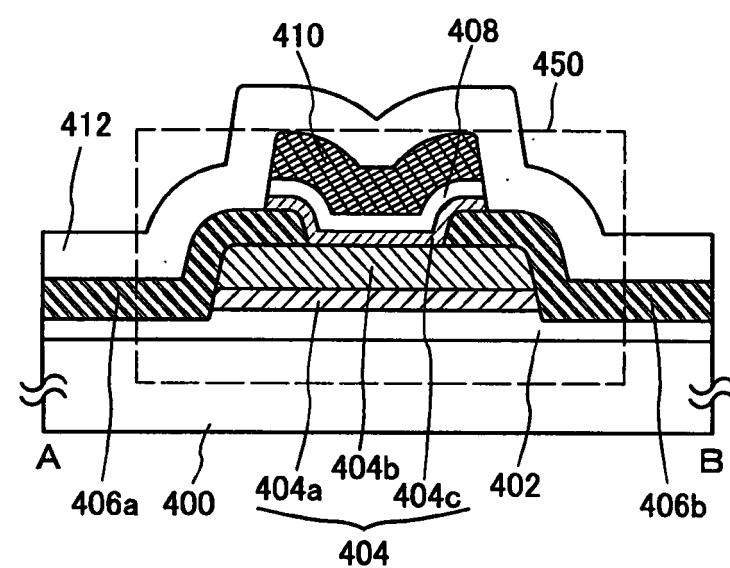

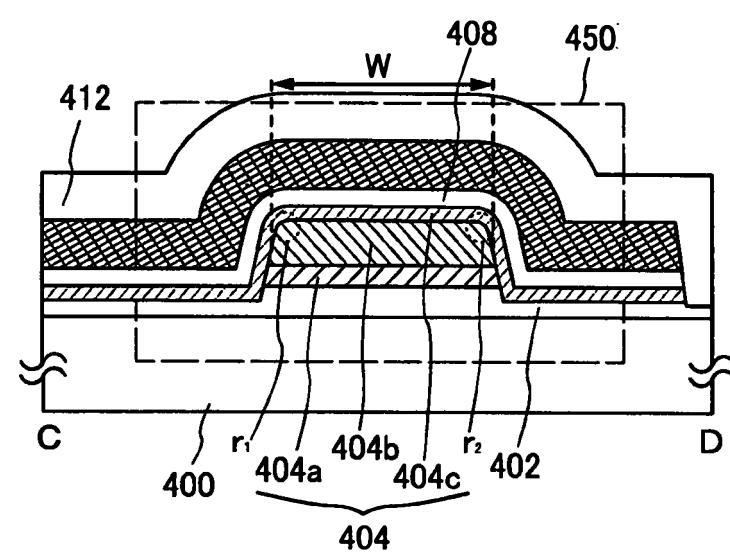

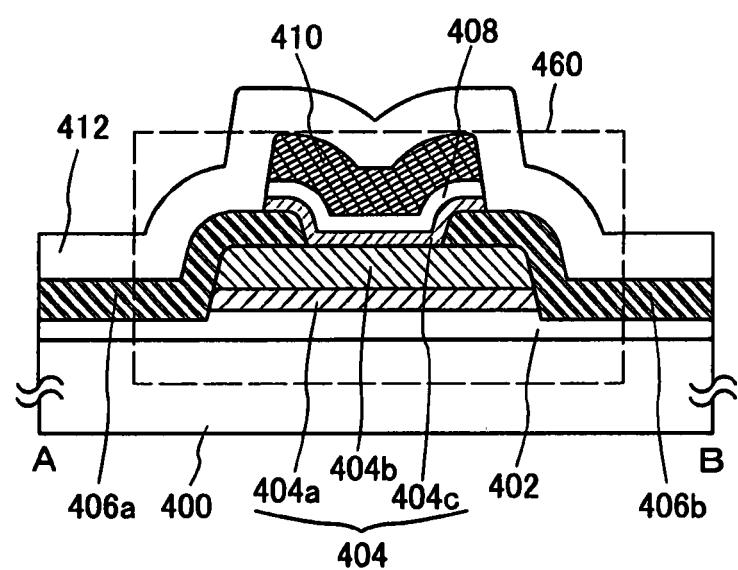

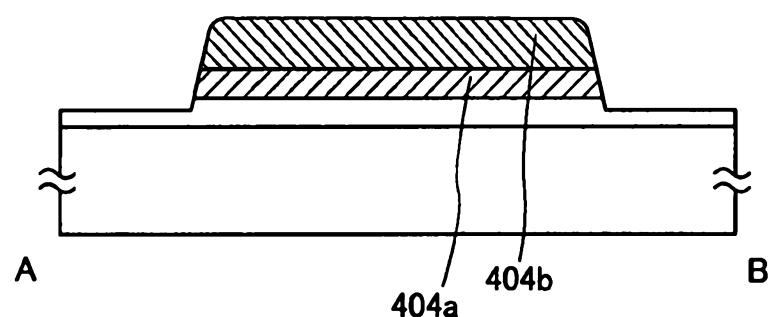

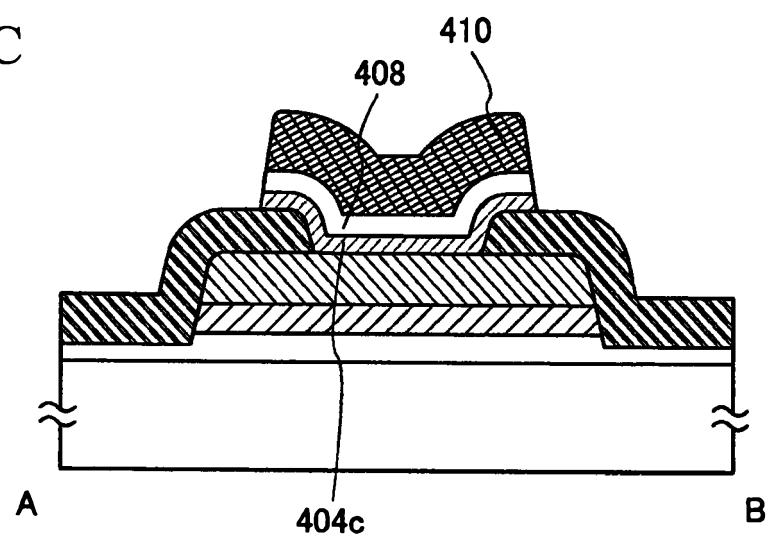

圖 1A 至圖 1C 是電晶體的俯視圖及剖面圖；

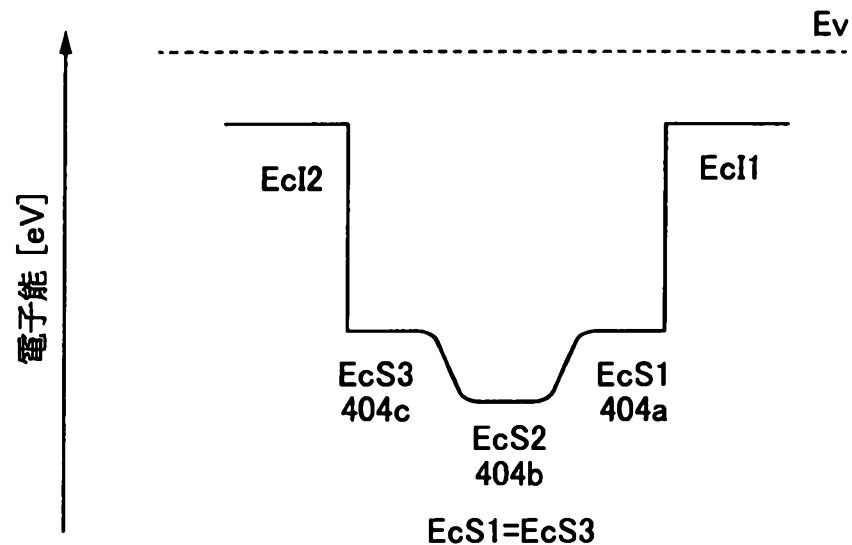

圖 2A 和圖 2B 是說明多層膜的能帶結構的圖；

圖 3 是電晶體的放大剖面圖；

圖 4A 和圖 4B 是電晶體的通道寬度方向上的剖面圖；

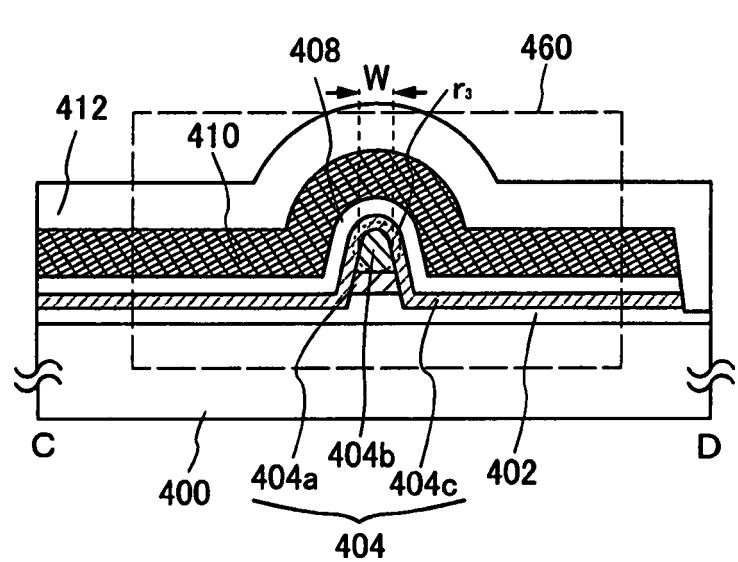

圖 5A 和圖 5B 是電晶體的通道寬度方向上的剖面圖；

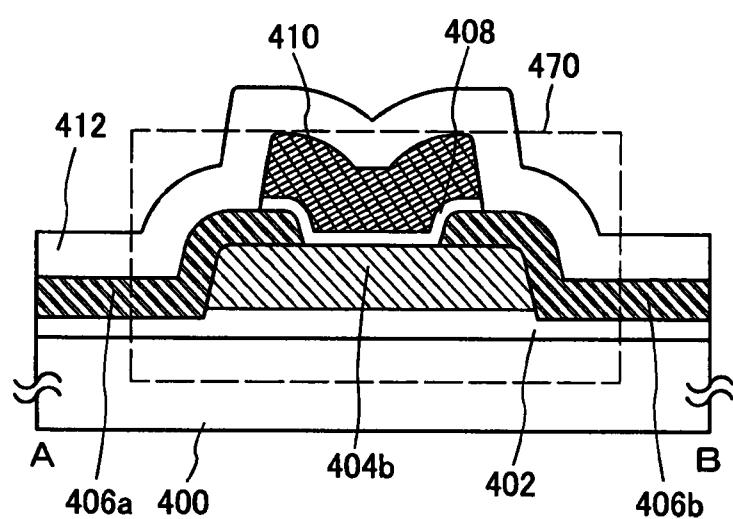

圖 6A 至圖 6C 是電晶體的俯視圖及剖面圖；

圖 7 是電晶體的剖面圖；

圖 8A 至圖 8C 是說明電晶體的製造方法的圖；

圖 9A 至圖 9C 是說明電晶體的製造方法的圖；

圖 10A 和圖 10B 是在實施例中製造的電晶體的剖面 STEM 照片；

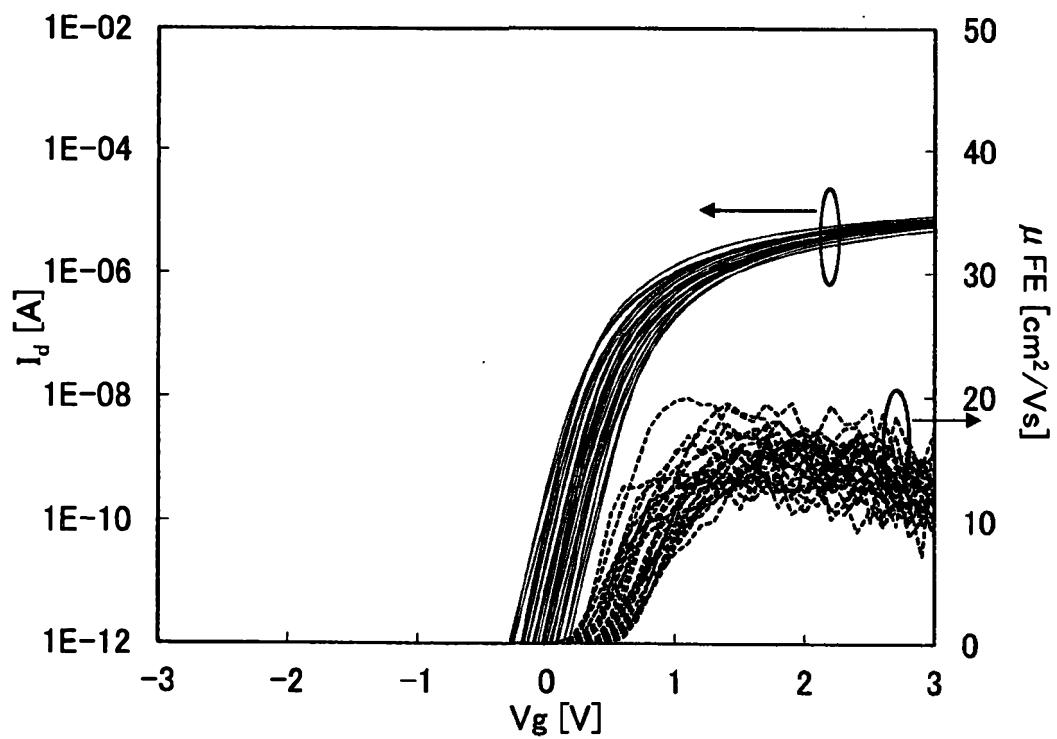

圖 11 示出在實施例中製造的電晶體的電特性的測定結果；

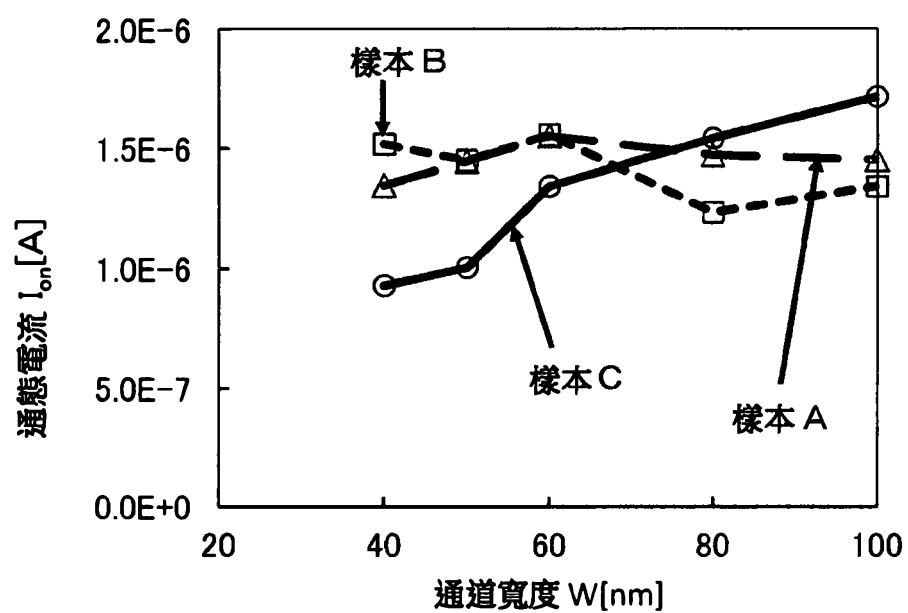

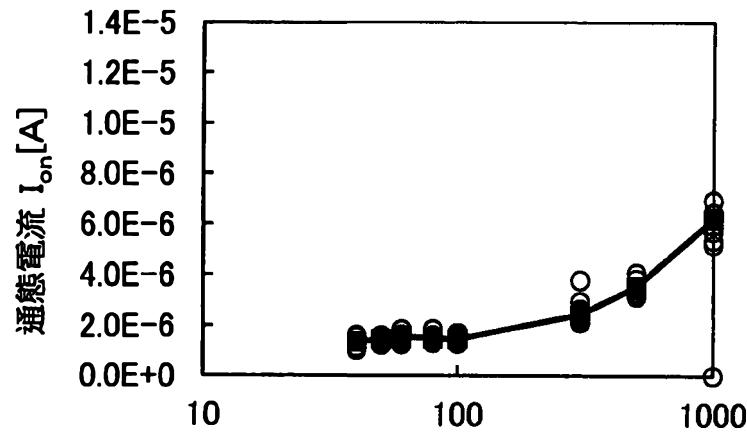

圖 12 示出在實施例中製造的電晶體的電特性的測定結果；

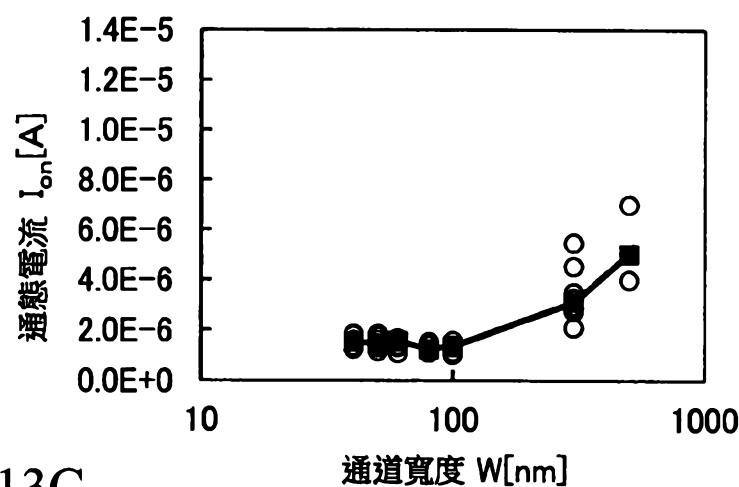

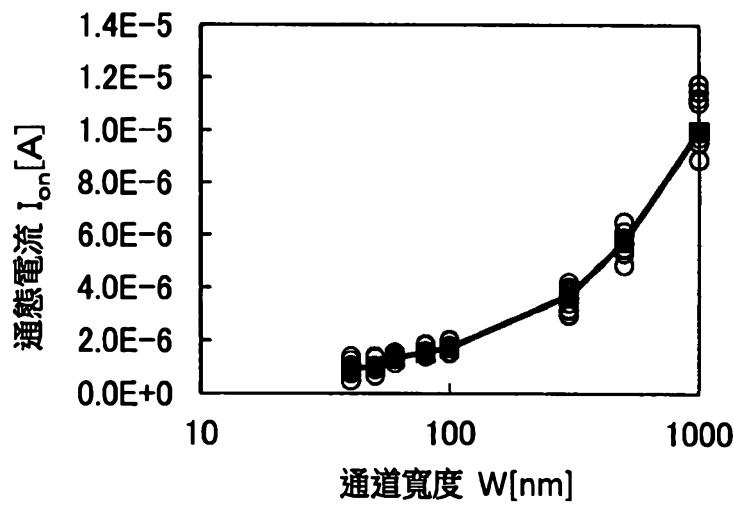

圖 13A 至圖 13C 示出在實施例中製造的電晶體的電特性的測定結果；

圖 14A 至圖 14C 是電晶體的俯視圖及剖面圖；

圖 15A 至圖 15C 是說明電晶體的製造方法的圖；

圖 16A 至圖 16C 是說明電晶體的製造方法的圖；

圖 17A 至圖 17C 是說明電晶體的製造方法的圖；

圖 18A 至圖 18C 是說明電晶體的製造方法的圖；

圖 19A 至圖 19D 是說明使用本發明的一個方式的半導體裝置的反相器的圖；

圖 20 是根據實施方式的半導體裝置的電路圖；

圖 21 是根據實施方式的半導體裝置的方塊圖；

圖 22 是根據實施方式的記憶體裝置的電路圖；

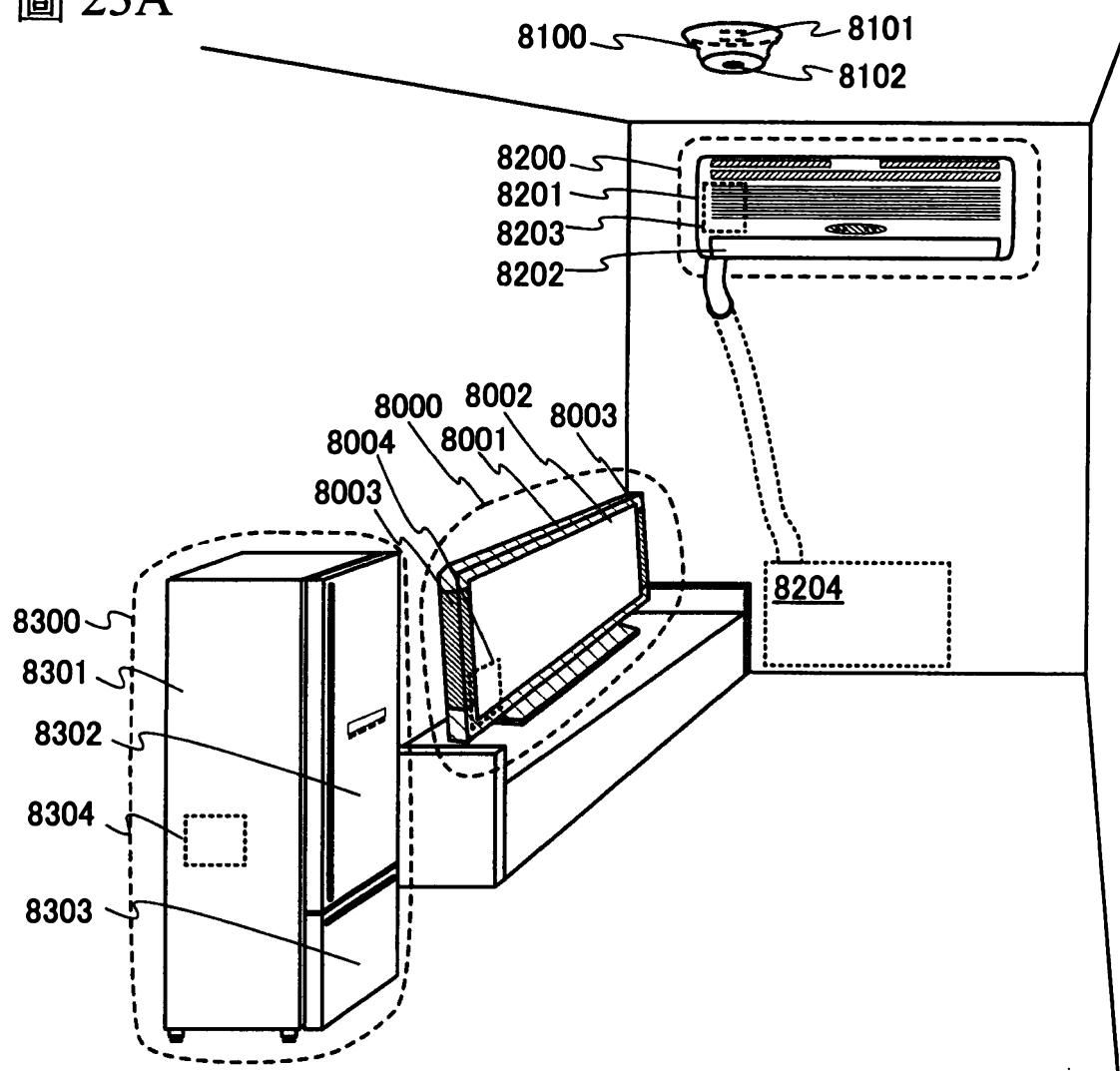

圖 23A 至圖 23C 示出根據實施方式的電子裝置；

圖 24 是說明半導體裝置的一個例子的等效電路圖；

圖 25A 和圖 25B 是電晶體的通道寬度方向上的剖面圖；

圖 26 是電晶體的通道長度方向上的剖面圖；

圖 27 示出電晶體的  $I_d$ - $V_g$  特性；

圖 28 示出電晶體的  $I_d$ - $V_g$  特性；

圖 29 示出電晶體的  $I_d$ - $V_g$  特性；

圖 30 示出電晶體的溫度依賴性；

圖 31 示出電晶體的溫度依賴性；

圖 32A 和圖 32B 示出電晶體的可靠性；

圖 33 示出電晶體的可靠性；

圖 34A 至圖 34D 示出電晶體的電特性；

圖 35A 和圖 35B 示出電晶體的電特性；

圖 36 是電晶體結構的示意圖；

圖 37A 和圖 37B 示出氧化物半導體膜的奈米束電子繞射圖案；

圖 38A 和圖 38B 示出穿透式電子繞射測定裝置的一個例子；

圖 39 示出利用穿透式電子繞射測定的結構分析的一個例子；

圖 40A 至圖 40C 示出電晶體的溫度依賴性。

### 【實施方式】

[0025] 參照圖式對實施方式進行詳細說明。注意，本發明不侷限於以下說明，所屬技術領域的普通技術人員可以很容易地理解一個事實就是，其方式及詳細內容在不脫離本發明的精神及其範圍的情況下可以被變換為各種各樣的形式。因此，本發明不應該被解釋為僅限定於以下所示的實施方式的記載內容中。注意，在以下說明的發明的結構中，在不同的圖式中共同使用相同的元件符號來表示相同的部分或具有相同功能的部分，而省略其重複說明。

[0026]

#### 實施方式 1

在本實施方式中，參照圖式對本發明的一個方式的半導體裝置進行說明。

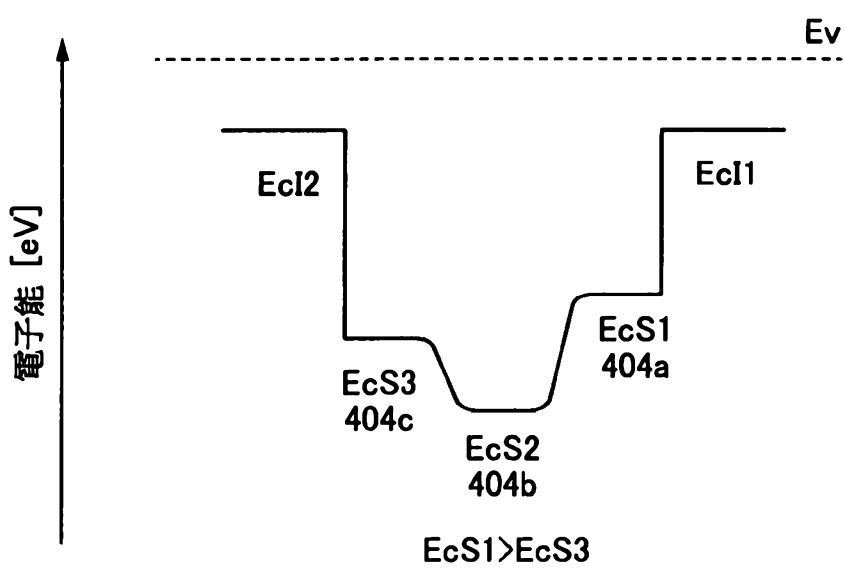

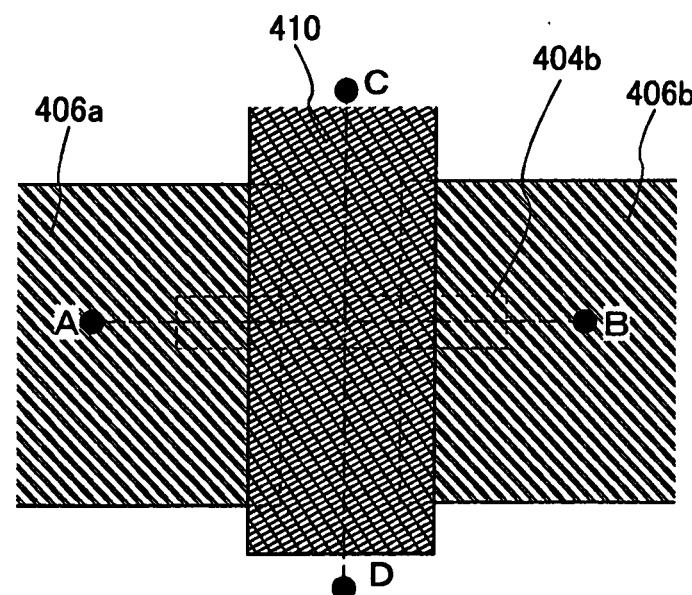

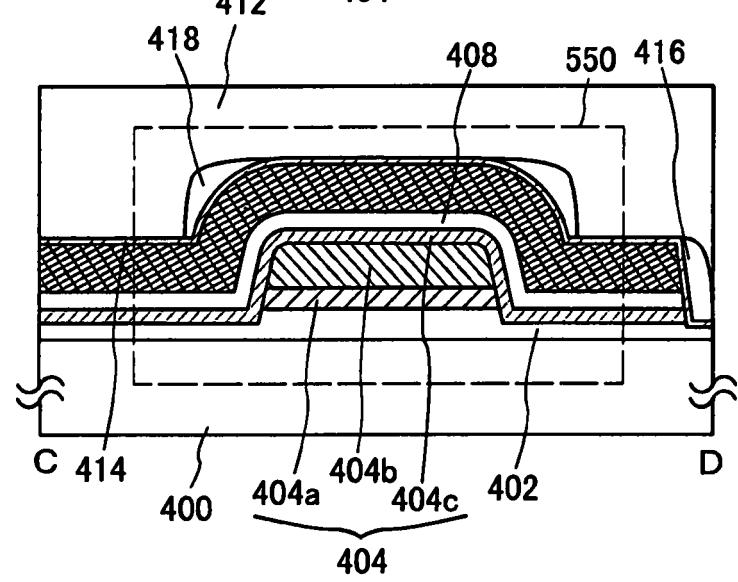

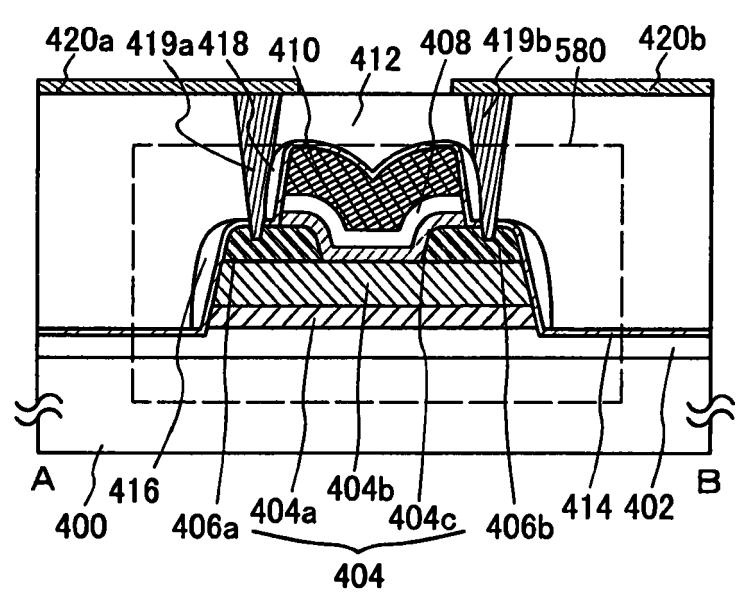

[0027] 圖 1A 至圖 1C 為本發明的一個方式的電晶體的俯視圖及剖面圖。圖 1A 為俯視圖，圖 1B 為沿著圖 1A 所示的點劃線 A-B 的剖面，圖 1C 為沿著點劃線 C-D 的剖面。另外，在圖 1A 的俯視圖中，為了明確起見，省略一部分的構成要素。另外，有時將點劃線 A-B 的方向稱為通道長度方向，將點劃線 C-D 的方向稱為通道寬度方向。通道長度是指通道形成區的流動載子的方向的長度。通道寬度是指通道形成區的垂直於通道長度方向的方向的長度。

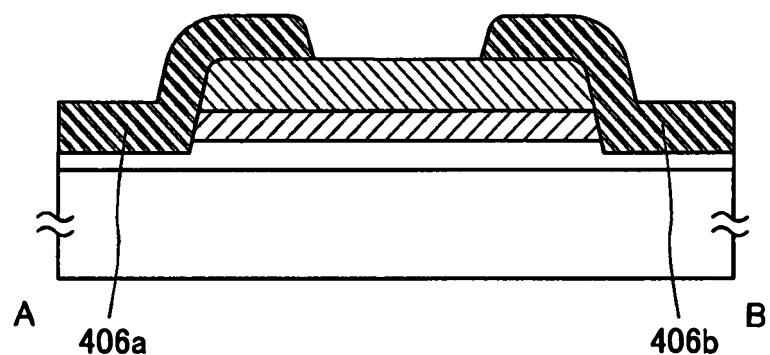

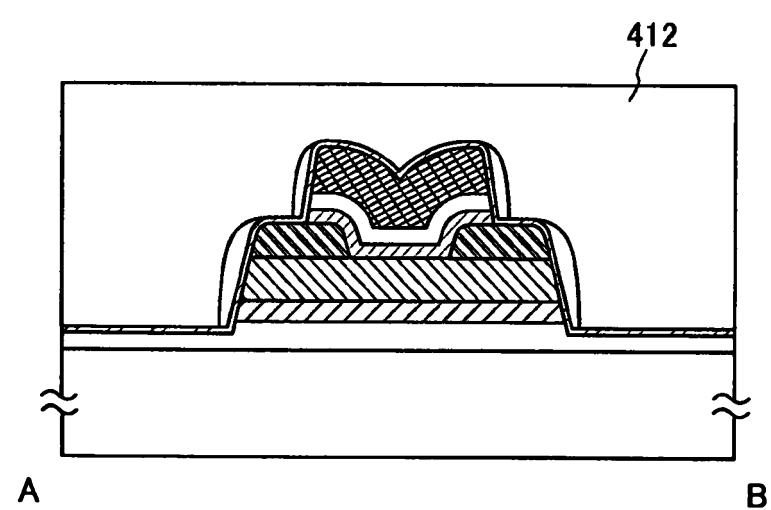

[0028] 圖 1A 至圖 1C 所示的電晶體 450 包括：基板

400 上的基底絕緣膜 402；基底絕緣膜 402 上的第一氧化物膜 404a 及氧化物半導體膜 404b；第一氧化物膜 404a 及氧化物半導體膜 404b 上的源極電極 406a 及汲極電極 406b；氧化物半導體膜 404b、源極電極 406a 及汲極電極 406b 上的第二氧化物膜 404c；第二氧化物膜 404c 上的閘極絕緣膜 408；閘極絕緣膜 408 上的閘極電極 410；源極電極 406a、汲極電極 406b 以及閘極電極 410 上的氧化物絕緣膜 412。注意，將第一氧化物膜 404a、氧化物半導體膜 404b 以及第二氧化物膜 404c 總稱為多層膜 404。

[0029] 當縮短電晶體的通道長度及通道寬度時，使用光阻遮罩進行加工的電極或半導體膜等的端部有時帶弧形（具有曲面）。在剖面中，本實施方式的氧化物半導體膜 404b 的上端部帶弧形，呈現半圓形狀。藉由採用這種結構，可以提高形成在氧化物半導體膜 404b 上的閘極絕緣膜 408、閘極電極 410 以及氧化物絕緣膜 412 的覆蓋性。此外，可以緩和在源極電極 406a 及汲極電極 406b 的端部有可能產生的電場集中，而可以抑制電晶體的劣化。

[0030] 注意，氧化物半導體膜 404b 具有曲率半徑為  $r$  的密切圓的曲率。曲率半徑等於曲線的密切圓的半徑。另外，氧化物半導體膜 404b 也可以具有兩個以上的具有不同密切圓的曲率的部分。

[0031] 明確而言，在圖 1A 至圖 1C 所示的氧化物半導體膜 404b 中，從通道寬度方向看時的上端部的曲率半徑  $r_1$  較佳為大於 0 且為通道寬度  $W$  的一半以下；同樣

地，從通道寬度方向看時的上端部的曲率半徑  $r_2$ （具有曲率半徑  $r_2$  的上端部離具有曲率半徑  $r_1$  的上端部有通道寬度  $W$ ）較佳為大於 0 且為通道寬度  $W$  的一半以下 ( $0 < r_1, r_2 \leq W/2$ )。另外，如圖 6C 所示，當從通道寬度方向看時，在氧化物半導體膜 404b 的頂面不具有平坦部的情況下，上端部的曲率半徑  $r_3$  較佳為大於 0 且為通道寬度  $W$  的一半以下 ( $0 < r_3 \leq W/2$ )。

[0032] 另外，電晶體的“源極”和“汲極”的功能在使用極性不同的電晶體的情況下或在電路工作中當電流方向變化時，有時互相調換。因此，在本說明書中，“源極”和“汲極”可以互相調換。

[0033] 基板 400 不侷限於僅進行支撐的基板，也可以是形成有電晶體等其他裝置的基板。此時，電晶體 450 的閘極電極 410、源極電極 406a 和汲極電極 406b 中的至少一個也可以與上述裝置電連接。

[0034] 基底絕緣膜 402 除了防止雜質從基板 400 擴散的功能以外，還可以具有對多層膜 404 供應氧的功能。因此，基底絕緣膜 402 較佳為包含氧，更佳為包含比化學計量組成多的氧。此外，如上所述，當基板 400 是形成有其他裝置的基板時，基底絕緣膜 402 還用作層間絕緣膜。在此情況下，基底絕緣膜 402 的表面為凹凸狀，所以較佳為利用 CMP (Chemical Mechanical Polishing：化學機械拋光) 法等進行平坦化處理，以使其表面平坦。

[0035] 基底絕緣膜 402 較佳為使用能夠供應氧的氧

化鋁膜。該氧化鋁膜除了能夠供應氧之外，還能夠阻擋氫、水及氧。另外，也可以使用利用混有氧化鋁和氧化矽的靶材形成的包含氧化矽的氧化鋁膜。此時，氧化矽的含量較佳為 0.1wt%以上且 30wt%以下。

[0036] 另外，在形成電晶體 450 的通道的區域中，多層膜 404 具有從基板 400 一側層疊有第一氧化物膜 404a、氧化物半導體膜 404b 及第二氧化物膜 404c 的結構。另外，氧化物半導體膜 404b 具有被第一氧化物膜 404a 及第二氧化物膜 404c 包圍的結構。另外，如圖 1C 所示，當從通道寬度方向看時，閘極電極 410 電性上包圍氧化物半導體膜 404b。

[0037] 在此，例如，氧化物半導體膜 404b 使用其電子親和力（真空能階與導帶底之間的能量差）大於第一氧化物膜 404a 及第二氧化物膜 404c 的氧化物半導體。電子親和力是從真空能階與價帶頂之間的能量差（游離電位）減去導帶底與價帶頂之間的能量差（能隙）的值。

[0038] 第一氧化物膜 404a 及第二氧化物膜 404c 較佳為包含一種以上的構成氧化物半導體膜 404b 的金屬元素。例如，第一氧化物膜 404a 及第二氧化物膜 404c 較佳為使用其導帶底的能量比氧化物半導體膜 404b 的導帶底的能量更接近真空能階 0.05eV、0.07eV、0.1eV 或 0.15eV 以上且 2eV、1eV、0.5eV 或 0.4eV 以下的氧化物半導體形成。

[0039] 在上述結構中，當對閘極電極 410 施加電場

時，通道形成在多層膜 404 中的導帶底的能量最低的氧化物半導體膜 404b 中。換言之，由於在氧化物半導體膜 404b 與閘極絕緣膜 408 之間形成有第二氧化物膜 404c，所以電晶體的通道不與閘極絕緣膜 408 接觸。

[0040] 另外，第一氧化物膜 404a 包含一種以上的構成氧化物半導體膜 404b 的金屬元素，因此，與氧化物半導體膜 404b 與基底絕緣膜 402 接觸時的兩者之間的界面相比，在氧化物半導體膜 404b 與第一氧化物膜 404a 之間的界面不容易形成界面能階。上述界面能階有時形成通道，因此有時導致電晶體的臨界電壓的變動。所以，藉由設置第一氧化物膜 404a，能夠抑制電晶體的臨界電壓等電特性的偏差。此外，可以提高該電晶體的可靠性。

[0041] 另外，第二氧化物膜 404c 包含一種以上的構成氧化物半導體膜 404b 的金屬元素，因此，與氧化物半導體膜 404b 與閘極絕緣膜 408 接觸時的兩者之間的界面相比，在氧化物半導體膜 404b 與第二氧化物膜 404c 之間的界面不容易發生載子散射。所以，藉由設置第二氧化物膜 404c，能夠提高電晶體的場效移動率。

[0042] 例如，第一氧化物膜 404a 及第二氧化物膜 404c 可以使用如下材料：包含 Al、Ti、Ga、Ge、Y、Zr、Sn、La、Ce 或 Hf 且該元素的原子數比高於氧化物半導體膜 404b 的材料。明確而言，上述元素的原子數比為氧化物半導體膜 404b 的 1.5 倍以上，較佳為 2 倍以上，更佳為 3 倍以上。上述元素與氧堅固地鍵合，所以具有抑

制在氧化物半導體膜中產生氧缺陷的功能。由此可說，與氧化物半導體膜 404b 相比，在第一氧化物膜 404a 及第二氧化物膜 404c 中不容易產生氧缺陷。

[0043] 另外，在第一氧化物膜 404a、氧化物半導體膜 404b 及第二氧化物膜 404c 為至少包含銻、鋅及 M (Al、Ti、Ga、Ge、Y、Zr、Sn、La、Ce 或 Hf 等金屬) 的 In-M-Zn 氧化物，且第一氧化物膜 404a 的原子數比為  $In:M:Zn=x_1:y_1:z_1$ ，氧化物半導體膜 404b 的原子數比為  $In:M:Zn=x_2:y_2:z_2$ ，第二氧化物膜 404c 的原子數比為  $In:M:Zn=x_3:y_3:z_3$  的情況下， $y_1/x_1$  及  $y_3/x_3$  較佳為大於  $y_2/x_2$ 。 $y_1/x_1$  及  $y_3/x_3$  為  $y_2/x_2$  的 1.5 倍以上，較佳為 2 倍以上，更佳為 3 倍以上。此時，在氧化物半導體膜 404b 中，在  $y_2$  為  $x_2$  以上的情況下，能夠使電晶體的電特性變得穩定。注意，在  $y_2$  為  $x_2$  的 3 倍以上的情況下，電晶體的場效移動率降低，因此  $y_2$  較佳為低於  $x_2$  的 3 倍。

[0044] 第一氧化物膜 404a 及第二氧化物膜 404c 中的除了 Zn 及 O 之外的 In 與 M 的原子百分比較佳為如下：In 的比率低於 50atomic%，M 的比率為 50atomic% 以上，更佳為如下：In 的比率低於 25atomic%，M 的比率為 75atomic% 以上。另外，氧化物半導體膜 404b 中的除了 Zn 及 O 之外的 In 與 M 的原子百分比較佳為如下：In 的比率為 25atomic% 以上，M 的比率低於 75atomic%，更佳為如下：In 的比率為 34atomic% 以上，M 的比率低於 66atomic%。

[0045] 第一氧化物膜 404a 及第二氧化物膜 404c 的厚度為 3nm 以上且 100nm 以下，較佳為 3nm 以上且 50nm 以下。另外，氧化物半導體膜 404b 的厚度為 3nm 以上且 200nm 以下，較佳為 3nm 以上且 100nm 以下，更佳為 3nm 以上且 50nm 以下。

[0046] 第一氧化物膜 404a、氧化物半導體膜 404b 及第二氧化物膜 404c 例如可以使用包含銦、鋅及鎵的氧化物半導體。尤其是，當氧化物半導體膜 404b 包含銦時，載子移動率得到提高，所以是較佳的。

[0047] 此外，為了對其通道形成在氧化物半導體膜中的電晶體賦予穩定的電特性，藉由降低氧化物半導體膜中的雜質濃度，來使氧化物半導體膜成為本質或實質上本質是有效的。在此，“實質上本質”是指氧化物半導體膜的載子密度低於  $1 \times 10^{17}/\text{cm}^3$ ，較佳為低於  $1 \times 10^{15}/\text{cm}^3$ ，更佳為低於  $1 \times 10^{13}/\text{cm}^3$ 。

[0048] 另外，氧化物半導體膜中的氫的一部分被氧缺陷俘獲而使氧化物半導體膜成為 n 型。因此，包含多量的氫的氧化物半導體膜的費米能階 (Ef) 比高純度本質的氧化物半導體膜的費米能階更接近導帶底 (Ec)，可以期待電晶體的場效移動率的提高。若使氧化物半導體膜成為本質或實質上本質，氧化物半導體膜的費米能量與中間隙（氧化物半導體膜的能隙中間的能量）一致，或无限趨近它。此時，由於氧化物半導體膜所包含的載子數減少，所以場效移動率有可能降低。

[0049] 然而，在本發明的一個方式的電晶體中，除了垂直方向上的閘極電場之外，側面方向上的閘極電場也被施加到氧化物半導體膜。換而言之，閘極電場被施加到整個氧化物半導體膜，所以電流流過整個氧化物半導體膜。由此，在抑制因高純度本質化而產生的電特性變動的同時，可以提高電晶體的場效移動率。

[0050] 此外，對氧化物半導體膜來說，氫、氮、碳、矽以及主要成分以外的金屬元素是雜質。例如，氫和氮引起施體能階的形成，而增高載子密度。此外，矽引起氧化物半導體膜中的雜質能階的形成。該雜質能階成為陷阱，有可能使電晶體的電特性劣化。因此，較佳為降低第一氧化物膜 404a、氧化物半導體膜 404b 及第二氧化物膜 404c 中或各層之間的介面的雜質濃度。

[0051] 為了使氧化物半導體膜成為本質或實質上本質，在 SIMS (Secondary Ion Mass Spectrometry：二次離子質譜) 分析中，例如在氧化物半導體膜的某個深度或氧化物半導體膜的某個區域中較佳為包含如下部分：矽濃度低於  $1 \times 10^{19} \text{ atoms/cm}^3$ ，較佳為低於  $5 \times 10^{18} \text{ atoms/cm}^3$ ，更佳為低於  $1 \times 10^{18} \text{ atoms/cm}^3$  的部分。此外，例如在氧化物半導體膜的某個深度或氧化物半導體膜的某個區域中較佳為包含如下部分：氫濃度為  $2 \times 10^{20} \text{ atoms/cm}^3$  以下，較佳為  $5 \times 10^{19} \text{ atoms/cm}^3$  以下，更佳為  $1 \times 10^{19} \text{ atoms/cm}^3$  以下，進一步較佳為  $5 \times 10^{18} \text{ atoms/cm}^3$  以下的部分。此外，例如在氧化物半導體膜的某個深度或氧化物半導體膜的某個區

域中較佳為包含如下部分：氮濃度低於  $5 \times 10^{19} \text{ atoms/cm}^3$ ，較佳為  $5 \times 10^{18} \text{ atoms/cm}^3$  以下，更佳為  $1 \times 10^{18} \text{ atoms/cm}^3$  以下，進一步較佳為  $5 \times 10^{17} \text{ atoms/cm}^3$  以下的部分。

[0052] 此外，當氧化物半導體膜包含結晶時，如果以高濃度包含矽或碳，氧化物半導體膜的結晶性則有可能降低。為了防止氧化物半導體膜的結晶性的降低，例如在氧化物半導體膜的某個深度或氧化物半導體膜的某個區域中包含如下部分即可：矽濃度低於  $1 \times 10^{19} \text{ atoms/cm}^3$ ，較佳為低於  $5 \times 10^{18} \text{ atoms/cm}^3$ ，更佳為低於  $1 \times 10^{18} \text{ atoms/cm}^3$  的部分。此外，例如在氧化物半導體膜的某個深度或氧化物半導體膜的某個區域中包含如下部分即可：碳濃度低於  $1 \times 10^{19} \text{ atoms/cm}^3$ ，較佳為低於  $5 \times 10^{18} \text{ atoms/cm}^3$ ，更佳為低於  $1 \times 10^{18} \text{ atoms/cm}^3$  的部分。

[0053] 此外，將如上述那樣的被高度純化了的氧化物半導體膜用於通道形成區的電晶體的關態電流（off-state current）極小。例如，可以使以源極與汲極之間的電壓為 0.1V、5V 或 10V 左右時的電晶體的通道寬度歸一化的關態電流降低到幾  $\mu\text{A}/\mu\text{m}$  至幾  $\text{nA}/\mu\text{m}$ 。

[0054] 另外，作為電晶體的閘極絕緣膜，大多使用包含矽的絕緣膜，由於上述原因較佳為如本發明的一個方式的電晶體那樣不使多層膜的用作通道的區域與閘極絕緣膜接觸。另外，當通道形成在閘極絕緣膜與多層膜之間的介面時，有時在該介面產生載子散射而使電晶體的場效移動率降低。從上述觀點來看，可以說較佳為使多層膜的用

作通道的區域與閘極絕緣膜離開。

[0055] 因此，藉由使多層膜 404 具有第一氧化物膜 404a、氧化物半導體膜 404b 及第二氧化物膜 404c 的疊層結構，能夠將通道形成在氧化物半導體膜 404b 中，由此能夠形成具有高場效移動率及穩定的電特性的電晶體。

[0056] 接著，對多層膜 404 的能帶結構進行說明。在能帶結構的分析中，將能隙為 3.5eV 的 In-Ga-Zn 氧化物用於相當於第一氧化物膜 404a 及第二氧化物膜 404c 的層，並將能隙為 3.15eV 的 In-Ga-Zn 氧化物用於相當於氧化物半導體膜 404b 的層，由此形成相當於多層膜 404 的疊層。

[0057] 將第一氧化物膜 404a、氧化物半導體膜 404b 及第二氧化物膜 404c 的厚度都設定為 10nm，能隙利用光譜橢圓偏光計（HORIBA JOBIN YVON 公司製造的 UT-300）進行測定。真空中能階與價帶頂之間的能量差利用紫外線光電子能譜（UPS：Ultraviolet Photoelectron Spectroscopy）裝置（PHI 公司製造的 VersaProbe）進行測定。

[0058] 圖 2A 是示意地示出從真空中能階與價帶頂之間的能量差減去各層的能隙而算出的真空中能階與導帶底之間的能量差（電子親和力）的能帶結構的一部分。圖 2A 為以與第一氧化物膜 404a 和第二氧化物膜 404c 接觸的方式設置氧化矽膜時的能帶圖。在此，Ev 表示真空中能階的能量，EcI1 及 EcI2 表示氧化矽膜的導帶底的能量，EcS1 表示第一氧化物膜 404a 的導帶底的能量，EcS2 表示氧化物

半導體膜 404b 的導帶底的能量，EcS3 表示第二氧化物膜 404c 的導帶底的能量。

[0059] 如圖 2A 所示，第一氧化物膜 404a、氧化物半導體膜 404b 及第二氧化物膜 404c 的導帶底的能量連續地變化。這是可以理解的，因為：由於第一氧化物膜 404a、氧化物半導體膜 404b 及第二氧化物膜 404c 的組成相互相似，氧容易互相擴散。由此可以說，雖然第一氧化物膜 404a、氧化物半導體膜 404b 及第二氧化物膜 404c 是組成互不相同的疊層體，但是在物性上是連續的。因此，在圖式中，各層之間的界面由虛線表示。

[0060] 主要成分相同而層疊的多層膜 404 不是簡單地將各層層疊，而以形成連續結合（在此，尤其是指各層之間的導帶底的能量連續地變化的 U 型井（U-shape well）結構）的方式形成。換言之，以在各層的界面之間不存在會形成陷阱中心或再結合中心等缺陷能階的雜質的方式形成疊層結構。如果，雜質混入被層疊的多層膜的層間，能帶則失去連續性，因此載子在界面被俘獲或者再結合而消失。

[0061] 注意，圖 2A 示出 EcS1 與 EcS3 相同的情況，但是也可以相互不同。例如，圖 2B 示出 EcS1 高於 EcS3 時的能帶結構的一部分。

[0062] 例如，在  $\text{EcS1}=\text{EcS3}$  的情況下，第一氧化物膜 404a 及第二氧化物膜 404c 可以使用  $\text{In:Ga:Zn}=1:3:2$ 、 $1:3:3$ 、 $1:3:4$ 、 $1:3:6$ 、 $1:4:5$ 、 $1:6:4$  或  $1:9:6$ （原子數比）

的 In-Ga-Zn 氧化物等，氧化物半導體膜 404b 可以使用  $In:Ga:Zn=1:1:1$  或  $3:1:2$  (原子數比) 的 In-Ga-Zn 氧化物等。另外，在  $E_{cS1} > E_{cS3}$  的情況下，第一氧化物膜 404a 可以使用  $In:Ga:Zn=1:6:4$  或  $1:9:6$  (原子數比) 的 In-Ga-Zn 氧化物等，氧化物半導體膜 404b 可以使用  $In:Ga:Zn=1:1:1$ 、 $1:1:1.2$ 、 $1:1:1.5$  或  $3:1:2$  (原子數比) 的 In-Ga-Zn 氧化物等，第二氧化物膜 404c 可以使用  $In:Ga:Zn=1:3:2$ 、 $1:3:3$  或  $1:3:4$  (原子數比) 的 In-Ga-Zn 氧化物等。

[0063] 由圖 2A 和圖 2B 可知，多層膜 404 中的氧化物半導體膜 404b 用作井 (well)，而在包括多層膜 404 的電晶體中，通道形成在氧化物半導體膜 404b 中。另外，多層膜 404 的導帶底的能量連續地變化，因此，也可以將多層膜 404 稱為 U 型井。另外，也可以將具有上述結構的通道稱為埋入通道。

[0064] 另外，雖然在第一氧化物膜 404a 與氧化矽膜等絕緣膜之間以及第二氧化物膜 404c 與氧化矽膜等絕緣膜之間的界面附近有可能形成起因於雜質或缺陷的陷阱能階，但是藉由設置第一氧化物膜 404a 及第二氧化物膜 404c，可以使氧化物半導體膜 404b 和該陷阱能階相隔。注意，當  $E_{cS1}$  與  $E_{cS2}$  之間或  $E_{cS3}$  與  $E_{cS2}$  之間的能量差小時，有時氧化物半導體膜 404b 的電子越過該能量差到達陷阱能階。當電子被陷阱能階俘獲時，在絕緣膜的界面產生固定負電荷，使得電晶體的臨界電壓向正方向漂

移。

[0065] 因此，為了抑制電晶體的臨界電壓的變動，需要使 EcS1 與 EcS2 之間及 EcS3 與 EcS2 之間產生能量差。該能量差都較佳為 0.1eV 以上，更佳為 0.15eV 以上。

[0066] 另外，較佳的是，第一氧化物膜 404a、氧化物半導體膜 404b 及第二氧化物膜 404c 包含結晶部。尤其是，藉由使用 c 軸配向結晶，能夠對電晶體賦予穩定的電特性。

[0067] 另外，在多層膜 404 使用 In-Ga-Zn 氧化物的情況下，為了防止 In 擴散到閘極絕緣膜，較佳為第二氧化物膜 404c 中的 In 的含量小於氧化物半導體膜 404b。

[0068] 源極電極 406a 及汲極電極 406b 較佳為使用容易與氧鍵合的導電材料。例如，可以使用 Al、Cr、Cu、Ta、Ti、Mo 和 W 等。在上述材料中，尤其較佳為使用容易與氧鍵合的 Ti 或在後面能以較高的溫度進行處理的熔點高的 W。此外，容易與氧鍵合的導電材料包括氧容易擴散的材料。

[0069] 當使容易與氧鍵合的導電材料與多層膜接觸時，發生多層膜中的氧擴散到容易與氧鍵合的導電材料一側的現象。該現象隨著溫度的提高而明顯。因為在電晶體的製程中有幾個加熱製程，所以因上述現象而在多層膜的與源極電極或汲極電極接觸的區域的附近發生氧缺陷，包含於膜中的微量的氫與該氧缺陷鍵合而使該區域 n 型化。

因此，可以將被 n 型化了的該區域用作電晶體的源極或汲極。

[0070] 在圖 3 的電晶體的放大剖面圖（通道長度方向上的剖面）中示出上述被 n 型化了的區域。氧化物半導體膜 404b 中的由虛線表示的界線 435 為本質半導體區域與 n 型半導體區域之間的界線，氧化物半導體膜 404b 中的與源極電極 406a 或汲極電極 406b 接觸的區域的附近為被 n 型化了的區域。另外，界線 435 是示意性地示出的，實際上有時該界線 435 不明確。另外，雖然圖 3 示出界線 435 在氧化物半導體膜 404b 中沿著橫向方向延伸的狀態，但是，有時氧化物半導體膜 404b 中的夾在源極電極 406a 或汲極電極 406b 與第一氧化物膜 404a 之間的厚度方向的整個區域 n 型化。另外，雖然未圖示，但是有時在第一氧化物膜 404a 或第二氧化物膜 404c 中也會形成 n 型化區域。

[0071] 注意，當形成通道長度極小的電晶體時，有時因上述氧缺陷的發生而 n 型化的區域向電晶體的通道長度方向超出。此時，電晶體的電特性發生變化，例如臨界電壓漂移或不能由閘極電壓控制開關（此時電晶體處於導通狀態）。因此，當形成通道長度極小的電晶體時，不一定較佳為將容易與氧鍵合的導電材料用於源極電極及汲極電極。

[0072] 在此情況下，源極電極 406a 及汲極電極 406b 較佳為使用比上述材料更不容易與氧鍵合的導電材料。作

為該導電材料，例如可以使用包含氮化鉭、氮化鈦或釤的材料等。另外，當該導電材料與氧化物半導體膜 404b 接觸時，源極電極 406a 及汲極電極 406b 也可以具有該導電材料與上述容易與氧鍵合的導電材料的疊層結構。

[0073] 作為閘極絕緣膜 408，可以使用包含氧化鋁、氧化鎂、氧化矽、氫氧化矽、氮氧化矽、氮化矽、氧化鎗、氧化鋒、氧化鈦、氧化鋯、氧化鑭、氧化釔、氧化欒、氧化鉻和氧化鉭中的一種以上的絕緣膜。此外，閘極絕緣膜 408 也可以是上述材料的疊層。

[0074] 作為閘極電極 410，可以使用 Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、Ta 和 W 等的導電膜。此外，該閘極電極也可以是上述材料的疊層。另外，閘極電極 410 可以使用包含氮的導電膜。

[0075] 在閘極絕緣膜 408 及閘極電極 410 上也可以形成有氧化物絕緣膜 412。作為該氧化物絕緣膜 412，可以使用包含氧化鋁、氧化鎂、氧化矽、氫氧化矽、氮氧化矽、氮化矽、氧化鎗、氧化鋒、氧化鈦、氧化鈦、氧化鋯、氧化鑭、氧化釔、氧化欒、氧化鉻和氧化鉭中的一種以上的絕緣膜。此外，該氧化物絕緣膜 412 也可以是上述材料的疊層。

[0076] 在此，氧化物絕緣膜 412 較佳為包含過剩氧。包含過剩氧的氧化物絕緣膜是指因加熱處理等而能夠釋放氧的氧化物絕緣膜。較佳的是，藉由利用熱脫附譜分析，換算為氧原子的氧的釋放量為  $1.0 \times 10^{19} \text{ atoms/cm}^3$  以上的膜。能夠將該氧化物絕緣膜釋放的氧經由閘極絕緣膜

408 擴散到多層膜 404 的通道形成區，因此即使在通道形成區形成氧缺陷的情況下也能夠補充氧。因此，能夠獲得穩定的電晶體電特性。

[0077] 氧化物絕緣膜 412 較佳為使用氧化鋁膜。氧化鋁膜除了能夠供應氧之外，還能夠阻擋氫、水及氧。另外，也可以使用利用混有氧化鋁和氧化矽的靶材形成的包含氧化矽的氧化鋁膜。此時，氧化矽的含量較佳為 0.1 wt% 以上且 30 wt% 以下。

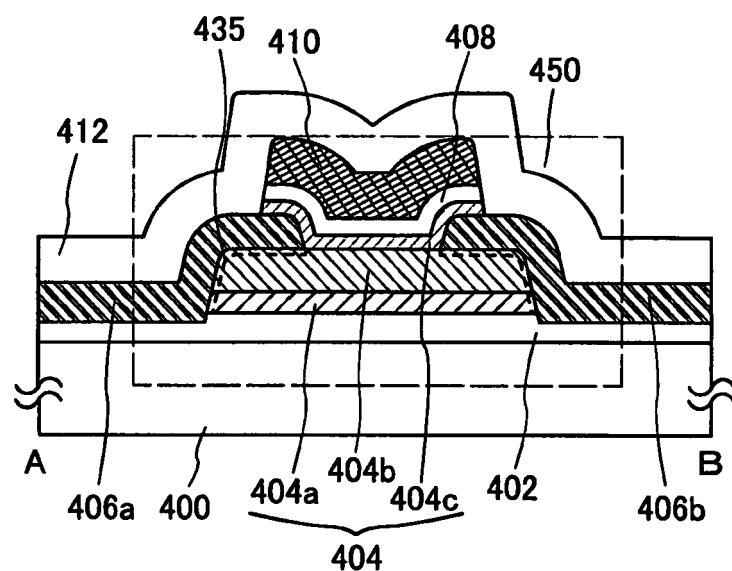

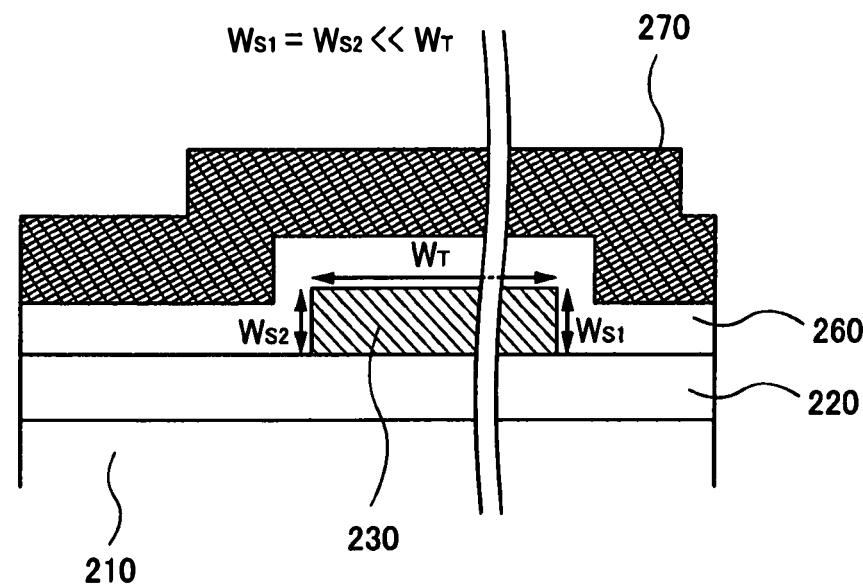

[0078] 為了實現半導體裝置的高積體化，必須進行電晶體的微型化。另一方面，已知伴隨著電晶體的微型化，電晶體的電特性劣化，特別是通道寬度的縮短直接導致的通態電流的減少顯著。

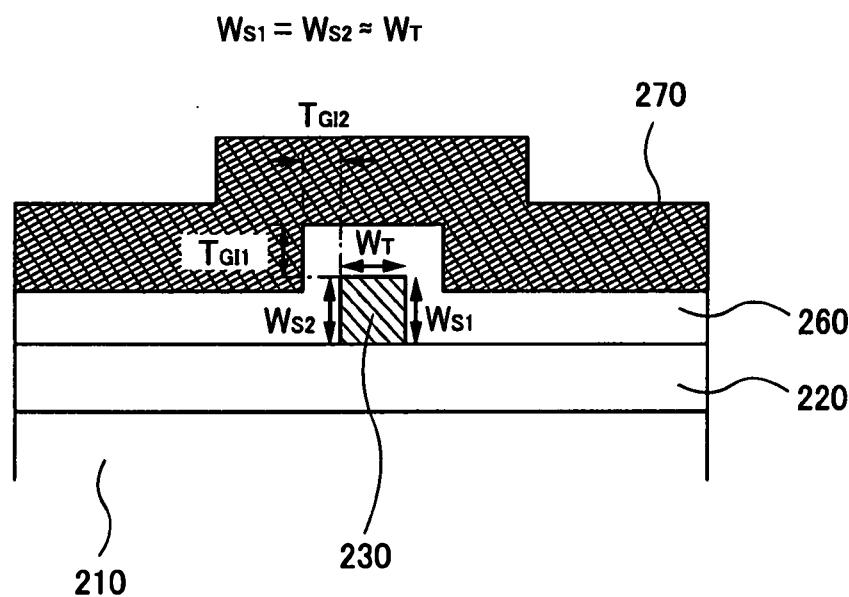

[0079] 圖 4A 和圖 4B 為習知的使用氧化物半導體膜的電晶體的通道寬度方向上的剖面圖。該電晶體包括基板 210 上的基底絕緣膜 220、形成在該基底絕緣膜上的氧化物半導體膜 230、形成在該氧化物半導體膜上的閘極絕緣膜 260 以及閘極電極 270。

[0080] 圖 4A 示出一種電晶體，其中，氧化物半導體膜 230 的厚度比該氧化物半導體膜的通道寬度方向上的頂面的長度 ( $W_T$ ) 長得多。此時，可以將通道寬度定義為  $W_T$ 。

[0081] 從閘極電極 270 施加到氧化物半導體膜 230 的側面的電場不涉及到整個氧化物半導體膜 230，因此，氧化物半導體膜 230 的側面的通道的形成不夠充分。另

外，由於相當於氧化物半導體膜 230 的厚度的側面的長度 ( $W_{S1}$ 、 $W_{S2}$ ) 對頂面的長度 ( $W_T$ ) 的比率小，因此即使在此形成了通道，也可以估計其作為通道的作用是很小的。因此，可以說  $W_T$  越小，即越進行微型化，通態電流越減少。

[0082] 另外，如圖 4B 所示，在  $W_T$  縮短到氧化物半導體膜 230 的厚度左右的電晶體中，從閘極電極 270 施加到氧化物半導體膜 230 的側面的電場涉及到整個氧化物半導體膜 230，因此在氧化物半導體膜 230 的側面也形成通道。為此，藉由增加氧化物半導體膜 230 的厚度等，可以期待通態電流的增加，但是在習知的電晶體中，在通道形成層（氧化物半導體膜 230）與閘極絕緣膜 260 的介面產生載子散射，因此不能充分增加通態電流。

[0083] 另外，在有的成膜方法中，閘極絕緣膜 260 的覆蓋氧化物半導體膜 230 的側面的區域的厚度 ( $T_{G12}$ ) 容易比該閘極絕緣膜的覆蓋該氧化物半導體膜的頂面的區域的厚度 ( $T_{G11}$ ) 薄。因此，在閘極絕緣膜 260 中產生耐受電壓低的部分，而有可能降低電晶體的可靠性。

[0084] 另外，由於  $T_{G11}$  與  $T_{G12}$  不同，因此從閘極電極 270 施加到氧化物半導體膜 230 的電場不均勻。為此，有可能產生通態電流的偏差。

[0085] 另一方面，在本發明的一個方式的電晶體中，如上所述，其中形成通道的氧化物半導體膜 404b 與閘極絕緣膜 408 之間形成有第二氧化物膜 404c。因此，

能夠抑制在通道形成層與閘極絕緣膜之間的介面產生的載子散射，而可以提高電晶體的場效移動率。

[0086] 另外，在本發明的一個方式的電晶體中，以覆蓋其中形成通道的氧化物半導體膜 404b 的方式形成有第二氧化物膜 404c，因此與頂面同樣地可以抑制在氧化物半導體膜 404b 的側面產生的載子散射。因此，本發明的一個方式的電晶體的通態電流可以比習知的電晶體多。

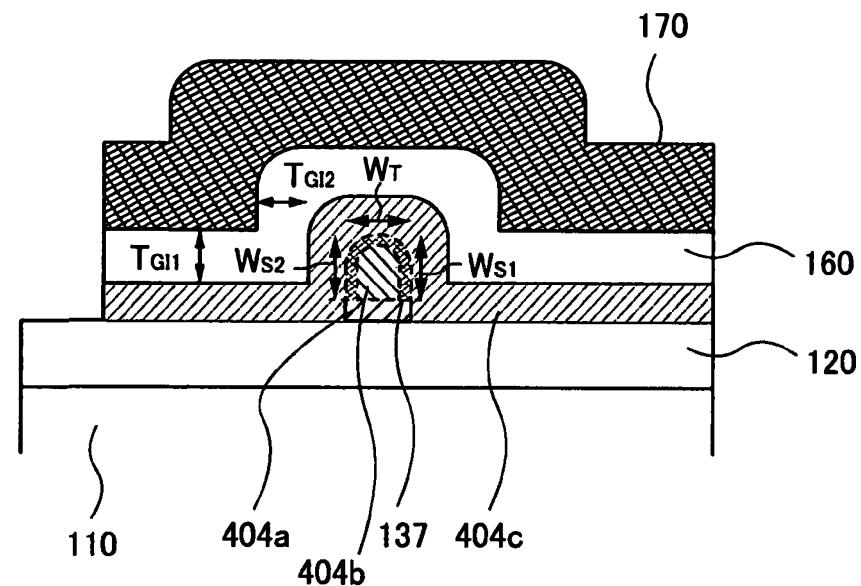

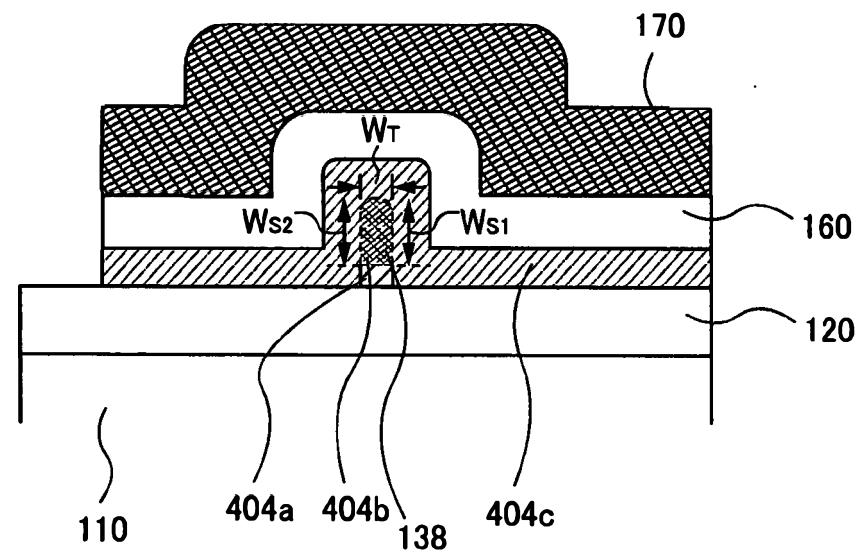

[0087] 因此，本發明的一個方式的電晶體在具有如圖 5A 和圖 5B 所示那樣的  $W_T$  縮短到氧化物半導體膜 404b 的厚度左右或該厚度以下的結構的情況下特別發揮良好的效果。

[0088] 在圖 5A 和圖 5B 所示的電晶體中，從閘極電極 170 施加到氧化物半導體膜 404b 的側面的電場涉及到整個氧化物半導體膜 404b，因此在氧化物半導體膜 404b 的側面也形成與頂面同等的通道。

[0089] 在如圖 5A 所示的通道區 137 形成在電晶體中的情況下，可以將通道寬度定義為  $W_T$ 、 $W_{S1}$  及  $W_{S2}$  的總和，在該電晶體中對應於該通道寬度的通態電流流動。

[0090] 另外，在圖 5B 所示的  $W_T$  極小的電晶體中，通道區 138 有時形成在氧化物半導體膜 404b 中的整個  $W_T$  方向。在此情況下，在整個氧化物半導體膜 404b 中電流流動，因此在電晶體中極多的通態電流流動。另外，在圖 5A 所示的電晶體中，如果  $W_T$ 、 $W_{S1}$  足夠小，則在整個氧化物半導體膜 404b 中電流流動。

[0091] 另外，本發明的一個方式的電晶體的特徵之一是閘極絕緣膜 160 的  $T_{G11}$  和  $T_{G12}$  幾乎相同。因此，不發生從閘極電極 170 施加到氧化物半導體膜 404b 的電場的不均勻，因此在氧化物半導體膜 404b 的頂面及側面形成均勻的通道。因此，在  $W_{S1}$  及  $W_{S2}$  與  $W_T$  同等的情況下，與僅在頂面形成通道的情況相比，能夠獲得 3 倍左右的通態電流。另外，當  $W_{S1}$  及  $W_{S2}$  為  $W_T$  的 2 倍時，與僅在頂面形成通道的情況相比，能夠獲得 5 倍左右的通態電流。

[0092] 另外，在本發明的一個方式的電晶體中，閘極絕緣膜 160 的  $T_{G11}$  與  $T_{G12}$  幾乎相同，所以可以形成可靠性高的電晶體，而不使在閘極絕緣膜 260 中產生耐受電壓低的部分。

[0093] 為了高效地增加電晶體的通態電流，將  $W_T/W_{S1}$  ( $W_{S2}$ ) 設定為 3 以下，較佳為 1 左右。明確而言，將  $W_T/W_{S1}$  ( $W_{S2}$ ) 設定為 0.7 至 1.3。在  $W_T/W_{S1}$  ( $W_{S2}$ ) 大於 3 的情況下，S 值或關態電流有可能增加。

[0094] 如上所述，在本發明的一個方式的電晶體中，在進行電晶體的微型化的情況下也能夠獲得足夠大的通態電流。將這種由閘極電極電性上包圍氧化物半導體膜而增加通態電流的電晶體的結構也稱為 surrounded channel (s-channel) 結構。

[0095] 另外，在本發明的一個方式的電晶體中，藉由將氧化物半導體膜 404b 形成在第一氧化物膜 404a 上，

來使介面能階不容易產生。此外，藉由使氧化物半導體膜 404b 位於三層結構中的中間層，來消除從上下方混入的雜質的影響。由於氧化物半導體膜 404b 被第一氧化物膜 404a 及第二二氧化物膜 404c 包圍，因此，除了可以增加上述電晶體的通態電流之外，還可以實現臨界電壓的穩定化或 S 值的下降。因此，可以降低  $I_{cut}$ （閘極電壓  $V_G$  為 0V 時的電流），而可以降低功耗。另外，由於電晶體的臨界電壓穩定，所以可以提高半導體裝置的長期可靠性。

[0096] 另外，本發明的一個方式的電晶體也可以包括基底絕緣膜 120 與基板 110 之間的導電膜。藉由將該導電膜用作第二閘極電極，能夠進一步增加通態電流或控制臨界電壓。當想要增加通態電流時，例如，對閘極電極 170 和導電膜供應相同的電位來實現雙閘極電晶體即可。另外，當想要控制臨界電壓時，對導電膜供應與閘極電極 170 不同的恆電位即可。

[0097] 此外，還可以使用圖 6A 至圖 6C 所示的電晶體 460。圖 6A 至圖 6C 為電晶體 460 的俯視圖及剖面圖。圖 6A 為俯視圖，圖 6B 為沿著圖 6A 所示的點劃線 A-B 的剖面，圖 6C 為沿著點劃線 C-D 的剖面。另外，在圖 6A 的俯視圖中，為了明確起見，省略一部分的構成要素。

[0098] 圖 6A 至圖 6C 與圖 1A 至圖 1C 之間的不同點在於如圖 1C 所示那樣從通道寬度方向看時的氧化物半導體膜 404b 的頂面是否具有平坦部。

[0099] 圖 1A 至圖 1C 所示的電晶體 450 和圖 6A 至

圖 6C 所示的電晶體 460 包括由第一氧化物膜 404a 與第二氧化物膜 404c 夾持氧化物半導體膜 404b 的多層膜 404，但是不侷限於此，如圖 7 的電晶體 470 所示，也可以僅包括氧化物半導體膜 404b 而不包括第一氧化物膜 404a 及第二氧化物膜 404c。

[0100] 注意，本實施方式可以與本說明書所示的其他實施方式適當地組合。

[0101]

## 實施方式 2

在本實施方式中，參照圖 8A 至圖 9C 對實施方式 1 所說明的圖 1A 至圖 1C 所示的電晶體 450 的製造方法進行說明。

[0102] 首先，在基板 400 上形成基底絕緣膜 402（參照圖 8A）。

[0103] 基板 400 可以使用玻璃基板、陶瓷基板、石英基板、藍寶石基板等。此外，也可以採用以矽或碳化矽等為材料的單晶半導體基板或多晶半導體基板、以矽鋒等為材料的化合物半導體基板、SOI (Silicon On Insulator：絕緣體上矽晶片) 基板等，並且，也可以在上述基板上設置半導體元件並將其用作基板 400。

[0104] 作為基底絕緣膜 402 可以藉由電漿 CVD 法或濺射法等形成氧化鋁、氧化鎂、氧化矽、氮氧化矽、氧化鎗、氧化鋒、氧化鈮、氧化鋯、氧化鑭、氧化欒、氧化釤、氧化鉻和氧化鉬等的氧化物絕緣膜、氮化矽、氮氧化矽、氮化

鋁、氮氧化鋁等的氮化物絕緣膜或者混合上述材料而形成的膜。此外，基底絕緣膜 402 也可以是上述材料的疊層，其中，較佳為與多層膜 404 接觸的上層至少使用包含過剩氧的材料形成，以對多層膜 404 供應氧。

[0105] 另外，也可以利用離子植入法、離子摻雜法、電漿浸沒離子植入法（Plasma-immersion ion implantation method）等對基底絕緣膜 402 添加氧。藉由添加氧，可以更容易地將氧從基底絕緣膜 402 供應到多層膜 404 中。

[0106] 注意，在基板 400 的表面由絕緣體構成，並且，雜質不會擴散到後面形成的多層膜 404 中的情況下，也可以不設置基底絕緣膜 402。

[0107] 接著，利用濺射法、CVD 法、MBE 法、ALD 法或 PLD 法在基底絕緣膜 402 上形成第一氧化物膜 404a 及氧化物半導體膜 404b（參照圖 8B）。此時，如圖所示，也可以對基底絕緣膜 402 稍微進行過度蝕刻。藉由對基底絕緣膜 402 進行過度蝕刻，可以容易由在後面形成的閘極電極 410 覆蓋第二氧化物膜 404c。

[0108] 當將第一氧化物膜 404a 及氧化物半導體膜 404b 形成為島狀時，首先，在氧化物半導體膜 404b 上設置成為硬遮罩的膜（例如，鎢膜）及光阻遮罩，對成為硬遮罩的膜進行蝕刻形成硬遮罩，然後去除光阻遮罩，以硬遮罩為遮罩對第一氧化物膜 404a 及氧化物半導體膜 404b 進行蝕刻。此後，去除硬遮罩。此時，當進行蝕刻時硬遮

罩逐漸縮退，硬遮罩的端部自然會帶弧形而具有曲面。其結果，氧化物半導體膜 404b 的端部也帶弧形而具有曲面。藉由採用這種結構，形成在氧化物半導體膜 404b 上的第二氧化物膜 404c、閘極絕緣膜 408、閘極電極 410 以及氧化物絕緣膜 412 的覆蓋性得到提高，而可以防止斷開等形狀不良。此外，可以緩和在源極電極 406a 及汲極電極 406b 的端部有可能產生的電場集中，而可以抑制電晶體的劣化。

[0109] 為了在第一氧化物膜 404a 與氧化物半導體膜 404b 的疊層以及包括在後面的製程中形成的第二氧化物膜 404c 的疊層中形成連續結合，需要使用具備負載鎖定室的多室成膜裝置（例如，濺射裝置）以不暴露於大氣的方式連續地層疊各個層。在濺射裝置中的各處理室中，較佳為使用低溫泵等吸附式真空泵進行高真空抽氣（抽空到  $5 \times 10^{-7}$  Pa 至  $1 \times 10^{-4}$  Pa 左右）且將被成膜的基板加熱到 100 °C 以上，較佳為 500 °C 以上，來盡可能地去除對氧化物半導體來說是雜質的水等。或者，較佳為組合渦輪分子泵和冷阱來防止將包含碳成分或水分等的氣體從排氣系統倒流到處理室內。

[0110] 為了獲得高純度本質的氧化物半導體，不僅需要對處理室進行高真空抽氣，而且需要進行濺射氣體的高度純化。藉由作為用作濺射氣體的氧氣體或氬氣體，使用露點為 -40 °C 以下，較佳為 -80 °C 以下，更佳為 -100 °C 以下的高純度氣體，能夠盡可能地防止水分等混入氧化物半

導體膜。

[0111] 第一氧化物膜 404a、氧化物半導體膜 404b 及在後面的製程中形成的第二氧化物膜 404c 可以使用實施方式 1 所說明的材料。例如，第一氧化物膜 404a 可以使用原子數比為  $In:Ga:Zn=1:3:4$  或  $1:3:2$  的 In-Ga-Zn 氧化物，氧化物半導體膜 404b 可以使用原子數比為  $In:Ga:Zn=1:1:1$  的 In-Ga-Zn 氧化物，第二氧化物膜 404c 可以使用原子數比為  $In:Ga:Zn=1:3:4$  或  $1:3:2$  的 In-Ga-Zn 氧化物。

[0112] 另外，能夠用於第一氧化物膜 404a、氧化物半導體膜 404b 及第二氧化物膜 404c 的氧化物半導體較佳為至少包含銻（In）或鋅（Zn）。或者，較佳為包含 In 和 Zn 的兩者。另外，為了減少使用該氧化物半導體的電晶體的電特性偏差，除了上述元素以外，較佳為還包含穩定劑（stabilizer）。

[0113] 作為穩定劑，可以舉出鎵（Ga）、錫（Sn）、鉿（Hf）、鋁（Al）或鋯（Zr）等。另外，作為其他穩定劑，可以舉出鑭系元素的鑭（La）、鈦（Ce）、镨（Pr）、钕（Nd）、钐（Sm）、铕（Eu）、釔（Gd）、铽（Tb）、镝（Dy）、钬（Ho）、铒（Er）、铥（Tm）、镱（Yb）、镥（Lu）等。

[0114] 例如，作為氧化物半導體，可以使用氧化銻、氧化錫、氧化鋅、In-Zn 氧化物、Sn-Zn 氧化物、Al-Zn 氧化物、Zn-Mg 氧化物、Sn-Mg 氧化物、In-Mg 氧化物、In-Ga 氧化物、In-Ga-Zn 氧化物、In-Al-Zn 氧化物、

In-Sn-Zn 氧化物、Sn-Ga-Zn 氧化物、Al-Ga-Zn 氧化物、Sn-Al-Zn 氧化物、In-Hf-Zn 氧化物、In-La-Zn 氧化物、In-Ce-Zn 氧化物、In-Pr-Zn 氧化物、In-Nd-Zn 氧化物、In-Sm-Zn 氧化物、In-Eu-Zn 氧化物、In-Gd-Zn 氧化物、In-Tb-Zn 氧化物、In-Dy-Zn 氧化物、In-Ho-Zn 氧化物、In-Er-Zn 氧化物、In-Tm-Zn 氧化物、In-Yb-Zn 氧化物、In-Lu-Zn 氧化物、In-Sn-Ga-Zn 氧化物、In-Hf-Ga-Zn 氧化物、In-Al-Ga-Zn 氧化物、In-Sn-Al-Zn 氧化物、In-Sn-Hf-Zn 氧化物、In-Hf-Al-Zn 氧化物。

[0115] 注意，例如 In-Ga-Zn 氧化物是指作為主要成分包含 In、Ga 和 Zn 的氧化物。另外，也可以包含 In、Ga、Zn 以外的金屬元素。此外，在本說明書中，將由 In-Ga-Zn 氧化物構成的膜稱為 IGZO 膜。

[0116] 另外，也可以使用以  $\text{InMO}_3(\text{ZnO})_m$  (  $m > 0$ ，且  $m$  不是整數) 表示的材料。注意，M 表示選自 Ga、Fe、Mn 和 Co 中的一種金屬元素或多種金屬元素。另外，也可以使用以  $\text{In}_2\text{SnO}_5(\text{ZnO})_n$  (  $n > 0$ ，且  $n$  是整數) 表示的材料。

[0117] 注意，如在實施方式 1 中詳細地說明那樣，以使第一氧化物膜 404a 及第二氧化物膜 404c 的電子親和力小於氧化物半導體膜 404b 的方式選擇材料。

[0118] 另外，當形成氧化物膜和氧化物半導體膜時，較佳為利用濺射法。作為濺射法，可以使用 RF 濣射法、DC 濣射法、AC 濣射法等。尤其較佳為使用 DC 濣射

法，因為可以降低進行成膜時產生的塵屑，並且，可以使膜厚度均勻。

[0119] 當作為第一氧化物膜 404a、氧化物半導體膜 404b 及第二氧化物膜 404c 使用 In-Ga-Zn 氧化物時，例如藉由使用 In、Ga、Zn 的原子數比為  $In:Ga:Zn=1:1:1$ 、 $In:Ga:Zn=1:1:1.2$ 、 $In:Ga:Zn=1:1:1.5$ 、 $In:Ga:Zn=2:2:1$ 、 $In:Ga:Zn=3:1:2$ 、 $In:Ga:Zn=1:3:2$ 、 $In:Ga:Zn=1:3:4$ 、 $In:Ga:Zn=1:4:3$ 、 $In:Ga:Zn=1:5:4$ 、 $In:Ga:Zn=1:6:6$ 、 $In:Ga:Zn=2:1:3$ 、 $In:Ga:Zn=1:6:4$ 、 $In:Ga:Zn=1:9:6$ 、 $In:Ga:Zn=1:1:4$ 、 $In:Ga:Zn=1:1:2$  中的任一個的材料，來使第一氧化物膜 404a 及第二氧化物膜 404c 的電子親和力小於氧化物半導體膜 404b 即可。

[0120] 另外，例如 In、Ga、Zn 的原子數比為  $In:Ga:Zn=a:b:c$  ( $a+b+c=1$ ) 的氧化物的組成與原子數比為  $In:Ga:Zn=A:B:C$  ( $A+B+C=1$ ) 的氧化物的組成相似是指 a、b、c 滿足如下算式： $(a-A)^2+(b-B)^2+(c-C)^2 \leq r^2$ 。r 例如可以為 0.05。其他氧化物也是同樣的。

[0121] 另外，較佳的是，氧化物半導體膜 404b 的銦的含量多於第一氧化物膜 404a 及第二氧化物膜 404c 的銦的含量。在氧化物半導體中，重金屬的 s 軌道主要有助於載子傳導，並且，藉由增加 In 的比率來增加 s 軌道的重疊，由此 In 的比率多於 Ga 的氧化物的移動率比 In 的比率等於或少於 Ga 的氧化物高。因此，藉由將銦的比率多的氧化物用於氧化物半導體膜 404b，可以實現高移動率

的電晶體。

[0122] 下面，對氧化物半導體膜的結構進行說明。

[0123] 注意，在本說明書中，“平行”是指兩條直線形成的角度為 $-10^{\circ}$ 以上且 $10^{\circ}$ 以下的狀態，因此也包括角度為 $-5^{\circ}$ 以上且 $5^{\circ}$ 以下的狀態。另外，“垂直”是指兩條直線形成的角度為 $80^{\circ}$ 以上且 $100^{\circ}$ 以下的狀態，因此也包括角度為 $85^{\circ}$ 以上且 $95^{\circ}$ 以下的狀態。

[0124] 另外，在本說明書中，六方晶系包括三方晶系和菱方晶系。

[0125] 氧化物半導體膜大致分為非單晶氧化物半導體膜和單晶氧化物半導體膜。非單晶氧化物半導體膜包括CAAC-OS (C-Axis Aligned Crystalline Oxide Semiconductor:c軸配向結晶氧化物半導體) 膜、多晶氧化物半導體膜、微晶氧化物半導體膜、非晶氧化物半導體膜等。

[0126] 首先，對CAAC-OS膜進行說明。

[0127] CAAC-OS膜是包含多個c軸配向的結晶部的氧化物半導體膜之一。

[0128] 在CAAC-OS膜的穿透式電子顯微鏡(TEM:Transmission Electron Microscope)影像中，觀察不到結晶部與結晶部之間的明確的邊界，即晶界(grain boundary)。因此，在CAAC-OS膜中，不容易發生起因於晶界的電子移動率的降低。

[0129] 根據從大致平行於樣本面的方向觀察的CAAC-OS膜的TEM影像(剖面TEM影像)可知在結晶

部中金屬原子排列為層狀。各金屬原子層具有反映形成 CAAC-OS 膜的面（也稱為被形成面）或 CAAC-OS 膜的頂面的凸凹的形狀並以平行於 CAAC-OS 膜的被形成面或頂面的方式排列。

[0130] 另一方面，根據從大致垂直於樣本面的方向觀察的 CAAC-OS 膜的 TEM 影像（平面 TEM 影像）可知在結晶部中金屬原子排列為三角形狀或六角形狀。但是，在不同的結晶部之間金屬原子的排列沒有規律性。

[0131] 另外，在 CAAC-OS 膜的電子繞射圖案中，觀察到表示配向性的斑點（亮點）。例如，在使用例如為 1 nm 以上且 30 nm 以下的電子束獲得的 CAAC-OS 膜的頂面的電子繞射圖案（也稱為奈米束電子繞射圖案）中，觀察到斑點（參照圖 37A）。

[0132] 由剖面 TEM 影像及平面 TEM 影像可知，CAAC-OS 膜的結晶部具有配向性。

[0133] 使用 X 射線繞射（XRD：X-Ray Diffraction）裝置對 CAAC-OS 膜進行結構分析。例如，當利用 out-of-plane 法分析包括  $\text{InGaZnO}_4$  結晶的 CAAC-OS 膜時，在繞射角 ( $2\theta$ ) 為  $31^\circ$  附近時常出現峰值。由於該峰值來源於  $\text{InGaZnO}_4$  結晶的 (009) 面，由此可知 CAAC-OS 膜中的結晶具有 c 軸配向性，並且，c 軸朝向大致垂直於 CAAC-OS 膜的被形成面或頂面的方向。

[0134] 另一方面，當利用從大致垂直於 c 軸的方向使 X 射線入射到樣本的 in-plane 法分析 CAAC-OS 膜時，

在  $2\theta$  為  $56^\circ$  附近時常出現峰值。該峰值來源於  $\text{InGaZnO}_4$  結晶的 (110) 面。在此，將  $2\theta$  固定為  $56^\circ$  附近並在以樣本面的法線向量為軸 ( $\varphi$  軸) 旋轉樣本的條件下進行分析 ( $\varphi$  掃描)。當該樣本是  $\text{InGaZnO}_4$  的單晶氧化物半導體膜時，出現六個峰值。該六個峰值來源於相等於 (110) 面的結晶面。另一方面，當該樣本是 CAAC-OS 膜時，即使在將  $2\theta$  固定為  $56^\circ$  附近的狀態下進行  $\varphi$  掃描也不能觀察到明確的峰值。

[0135] 由上述結果可知，在具有 c 軸配向性的 CAAC-OS 膜中，雖然 a 軸及 b 軸的方向在結晶部之間不同，但是 c 軸都朝向平行於被形成面或頂面的法線向量的方向。因此，在上述剖面 TEM 影像中觀察到的排列為層狀的各金屬原子層相當於與結晶的 ab 面平行的面。

[0136] 注意，結晶部在形成 CAAC-OS 膜或進行加熱處理等晶化處理時形成。如上所述，結晶的 c 軸朝向平行於 CAAC-OS 膜的被形成面或頂面的法線向量的方向。由此，例如，當 CAAC-OS 膜的形狀因蝕刻等而發生改變時，結晶的 c 軸不一定平行於 CAAC-OS 膜的被形成面或頂面的法線向量。

[0137] 此外，CAAC-OS 膜中的結晶度不一定均勻。例如，當 CAAC-OS 膜的結晶部是由 CAAC-OS 膜的頂面近旁的結晶生長而形成時，有時頂面附近的結晶度高於被形成面附近的結晶度。另外，當對 CAAC-OS 膜添加雜質時，被添加了雜質的區域的結晶度改變，所以有時

CAAC-OS 膜中的結晶度根據區域而不同。

[0138] 注意，當利用 out-of-plane 法分析包括  $\text{InGaZnO}_4$  結晶的 CAAC-OS 膜時，除了在  $2\theta$ 為  $31^\circ$ 附近的峰值之外，有時還在  $2\theta$ 為  $36^\circ$ 附近觀察到峰值。 $2\theta$ 為  $36^\circ$ 附近的峰值意味著 CAAC-OS 膜的一部分中含有不具有 c 軸配向性的結晶。較佳的是，在 CAAC-OS 膜中在  $2\theta$ 為  $31^\circ$ 附近時出現峰值而在  $2\theta$ 為  $36^\circ$ 附近時不出現峰值。

[0139] CAAC-OS 膜是雜質濃度低的氧化物半導體膜。雜質是指氫、碳、矽、過渡金屬元素等氧化物半導體膜的主要成分之外的元素。尤其是，與構成氧化物半導體膜的金屬元素相比，與氧的鍵合力強的元素諸如矽等從氧化物半導體膜奪取氧而擾亂氧化物半導體膜的原子排列，成為降低結晶性的主要原因。另外，因為鐵和鎳等重金屬、氬、二氧化矽等的原子半徑（或分子半徑）大，所以如果包含在氧化物半導體膜內部，則擾亂氧化物半導體膜的原子排列，成為降低結晶性的主要原因。此外，包含在氧化物半導體膜中的雜質有時成為載子陷阱或載子發生源。

[0140] 此外，CAAC-OS 膜是缺陷態密度低的氧化物半導體膜。例如，氧化物半導體膜中的氧缺陷有時成為載子陷阱或者藉由俘獲氫而成為載子發生源。

[0141] 將雜質濃度低且缺陷態密度低（氧缺陷少）的狀態稱為“高純度本質”或“實質上高純度本質”。高純度本質或實質上高純度本質的氧化物半導體膜具有很少

的載子發生源，因此可以具有較低的載子密度。因此，使用該氧化物半導體膜的電晶體很少具有負臨界電壓的電特性（也稱為常導通（normally-on）特性）。此外，高純度本質或實質上高純度本質的氧化物半導體膜具有很少的載子陷阱。因此，使用該氧化物半導體膜的電晶體的電特性變動小，而成為可靠性高的電晶體。此外，被氧化物半導體膜的載子陷阱俘獲的電荷到被釋放為止需要的時間長，有時像固定電荷那樣動作。因此，使用雜質濃度高且缺陷態密度高的氧化物半導體膜的電晶體的電特性有時不穩定。

[0142] 此外，在使用 CAAC-OS 膜的電晶體中，起因於可見光或紫外光的照射的電特性的變動小。

[0143] 接下來，對多晶氧化物半導體膜進行說明。

[0144] 在多晶氧化物半導體膜的 TEM 影像中，可以觀察到晶粒。在 TEM 影像中，多晶氧化物半導體膜中含有的晶粒的粒徑大多為 2nm 以上且 300nm 以下、3nm 以上且 100nm 以下或 5nm 以上且 50nm 以下。另外，在多晶氧化物半導體膜的 TEM 影像中，有時觀察到晶界。

[0145] 多晶氧化物半導體膜包含多個晶粒，並且，在該多個晶粒之間結晶定向有時不同。另外，使用 XRD 裝置對多晶氧化物半導體膜進行結構分析。例如，當利用 out-of-plane 法分析包括  $\text{InGaZnO}_4$  結晶的多晶氧化物半導體膜時，有時在  $2\theta$  為  $31^\circ$  或  $36^\circ$  等附近時出現峰值。

[0146] 由於多晶氧化物半導體膜具有高結晶性，因

此有時具有高電子移動率。所以，使用多晶氧化物半導體膜的電晶體具有高場效移動率。注意，在多晶氧化物半導體膜中，雜質有時偏析在晶界。另外，多晶氧化物半導體膜的晶界成為缺陷能階。多晶氧化物半導體膜的晶界有可能成為載子陷阱或載子發生源，因此，與使用 CAAC-OS 膜的電晶體相比，有時使用多晶氧化物半導體膜的電晶體的電特性變動大，而成為可靠性低的電晶體。

[0147] 接下來，對微晶氧化物半導體膜進行說明。

[0148] 在微晶氧化物半導體膜的 TEM 影像中有時觀察不到明確的結晶部。微晶氧化物半導體膜中含有的結晶部的尺寸大多為 1nm 以上且 100nm 以下或 1nm 以上且 10nm 以下。尤其是，將尺寸為 1nm 以上且 10nm 以下或 1nm 以上且 3nm 以下的微晶稱為奈米晶 (nc:nanocrystal)。並且，包含該奈米晶 (nc) 的氧化物半導體膜稱為 nc-OS (奈米晶氧化物半導體：nanocrystalline Oxide Semiconductor) 膜。另外，例如在 nc-OS 膜的 TEM 影像中，有時觀察不到明確的晶界。

[0149] 在 nc-OS 膜中，微小的區域（例如 1nm 以上且 10nm 以下的區域，特別是 1nm 以上且 3nm 以下的區域）中的原子排列具有週期性。另外，在 nc-OS 膜中的不同的結晶部之間沒有晶體配向的規律性。因此，在膜整體上觀察不到配向性。所以，在有的分析方法中，有時無法將 nc-OS 膜與非晶氧化物半導體膜區別開來。例如，當利用使用其束徑比結晶部大的 X 射線的 XRD 裝置藉由 out-

of-plane 法對 nc-OS 膜進行結構分析時，檢測不出表示結晶面的峰值。此外，在使用其束徑比結晶部大（例如，50nm 以上）的電子射線獲得的 nc-OS 膜的選區電子繞射圖案中，觀察到光暈圖案。另一方面，在使用其束徑近於或小於結晶部的電子射線獲得的 nc-OS 膜的奈米束電子繞射圖案中，觀察到斑點。另外，在 nc-OS 膜的奈米束電子繞射圖案中，有時觀察到如圓圈那樣的（環狀的）亮度高的區域。而且，在 nc-OS 膜的奈米束電子繞射圖案中，有時觀察到環狀的區域內的多個斑點（參照圖 37B）。

[0150] nc-OS 膜是其規律性比非晶氧化物半導體膜高的氧化物半導體膜。因此，nc-OS 膜的缺陷態密度比非晶氧化物半導體膜低。但是，在 nc-OS 膜中的不同的結晶部之間沒有晶體配向的規律性。所以，nc-OS 膜的缺陷態密度比 CAAC-OS 膜高。

[0151] 因此，nc-OS 膜有時具有比 CAAC-OS 膜高的載子密度。載子密度高的氧化物半導體膜有時具有高電子移動率。因此，使用 nc-OS 膜的電晶體有時具有較高的場效移動率。此外，因為 nc-OS 膜有時具有比 CAAC-OS 膜高的缺陷態密度，所以有時具有較多的載子陷阱。因此，有時與使用 CAAC-OS 膜的電晶體相比，使用 nc-OS 膜的電晶體的電特性變動較大，而成為可靠性低的電晶體。注意，因為 nc-OS 膜即使包含較多的雜質也可以形成，所以與 CAAC-OS 層相比容易形成。因此，有時根據用途較佳為使用 nc-OS 膜。因此，有時能夠高生產率地製造具有使

用 nc-OS 膜的電晶體的半導體裝置。

[0152] 接著，對非晶氧化物半導體膜進行說明。

[0153] 非晶氧化物半導體膜是具有無序的原子排列並不具有結晶部的氧化物半導體膜。其一個例子為具有如石英那樣的無定形狀態的氧化物半導體膜。

[0154] 在非晶氧化物半導體膜的 TEM 影像中，觀察不到結晶部。

[0155] 使用 XRD 裝置對非晶氧化物半導體膜進行結構分析。當利用 out-of-plane 法分析時，檢測不到示出結晶面的峰值。另外，在非晶氧化物半導體膜的電子繞射圖案中，觀察到光暈圖案。另外，在非晶氧化物半導體膜的奈米束電子繞射圖案中，觀察不到斑點，而觀察到光暈圖案。

[0156] 非晶氧化物半導體膜是以高濃度包含氫等雜質的氧化物半導體膜。此外，非晶氧化物半導體膜是缺陷態密度高的氧化物半導體膜。

[0157] 雜質濃度高且缺陷態密度高的氧化物半導體膜是載子陷阱或載子發生源多的氧化物半導體膜。

[0158] 因此，非晶氧化物半導體膜有時具有比 nc-OS 膜更高的載子密度。因此，使用非晶氧化物半導體膜的電晶體容易具有常導通特性。因此，有時可以將非晶氧化物半導體膜用於需要常導通特性的電晶體。非晶氧化物半導體膜具有較高的缺陷態密度，因此有時具有較多的載子陷阱。因此，與使用 CAAC-OS 膜或 nc-OS 膜的電晶體相

比，使用非晶氧化物半導體膜的電晶體的電特性變動大，而成為可靠性低的電晶體。

[0159] 接著，對單晶氧化物半導體膜進行說明。

[0160] 單晶氧化物半導體膜是雜質濃度低且缺陷態密度低（氧缺陷少）的氧化物半導體膜。因此，可以降低載子密度。因此，使用單晶氧化物半導體膜的電晶體很少具有常導通特性。另外，由於單晶氧化物半導體膜具有較低的雜質濃度和較低的缺陷態密度，因此有時具有很少的載子陷阱。因此，使用單晶氧化物半導體膜的電晶體的電特性變動小，而成為可靠性高的電晶體。

[0161] 此外，氧化物半導體膜的缺陷越少其密度越高。此外，氧化物半導體膜的結晶性越高其密度越高。另外，當氧化物半導體膜中的氫等雜質的濃度越低其密度越高。單晶氧化物半導體膜的密度比 CAAC-OS 膜高。另外，CAAC-OS 膜的密度比微晶氧化物半導體膜高。另外，多晶氧化物半導體膜的密度比微晶氧化物半導體膜高。另外，微晶氧化物半導體膜的密度比非晶氧化物半導體膜高。

[0162] 注意，氧化物半導體膜例如也可以是包括非晶氧化物半導體膜、微晶氧化物半導體膜和 CAAC-OS 膜中的兩種以上的疊層膜。

[0163] 在氧化物半導體膜具有多種結構時，有時藉由利用奈米束電子繞射可以進行結構分析。

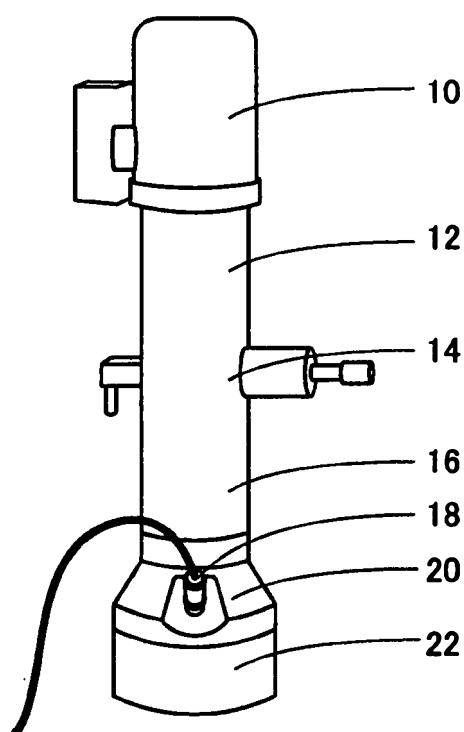

[0164] 圖 38A 示出一種穿透式電子繞射測定裝置，

該穿透式電子繞射測定裝置包括：電子槍室 10；電子槍室 10 下的光學系統 12；光學系統 12 下的樣品室 14；樣品室 14 下的光學系統 16；光學系統 16 下的觀察室 20；設置於觀察室 20 的照相裝置 18；以及觀察室 20 下的膠片室 22。照相裝置 18 以朝向觀察室 20 的內部的方式設置。另外，該穿透式電子繞射測定裝置也可以不包括膠片室 22。

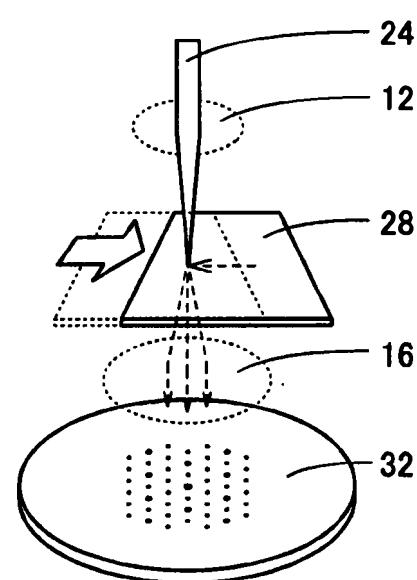

[0165] 此外，圖 38B 示出圖 38A 所示的穿透式電子繞射測定裝置內部的結構。在穿透式電子繞射測定裝置內部中，從設置在電子槍室 10 的電子槍發射的電子經由光學系統 12 照射到配置在樣品室 14 中的物質 28。穿過物質 28 的電子經由光學系統 16 入射到設置在觀察室 20 內部的螢光板 32。在螢光板 32 上出現對應於所入射的電子的強度的圖案，因此可以測定穿透式電子繞射圖案。

[0166] 因為照相裝置 18 朝向螢光板 32 地設置，所以可以拍攝出現在螢光板 32 上的圖案。經過照相裝置 18 的透鏡的中央及螢光板 32 的中央的直線與螢光板 32 的頂面所形成的角度例如為  $15^\circ$ 以上且  $80^\circ$ 以下， $30^\circ$ 以上且  $75^\circ$ 以下或  $45^\circ$ 以上且  $70^\circ$ 以下。該角度越小，由照相裝置 18 拍攝的穿透式電子繞射圖案的應變越大。但是，如果預先知道該角度，則能夠校正所得到的穿透式電子繞射圖案的應變。另外，有時也可以將照相裝置 18 設置於膠片室 22。例如，也可以以與電子 24 的入射方向相對的方式將照相裝置 18 設置於膠片室 22。在此情況下，可以從螢光

板 32 的背面拍攝應變少的穿透式電子繞射圖案。

[0167] 樣品室 14 設置有用來固定樣本的物質 28 的支架。支架使穿過物質 28 的電子透過。例如，支架也可以具有在 X 軸、Y 軸、Z 軸等的方向上移動物質 28 的功能。支架例如具有在 1nm 以上且 10nm 以下、5nm 以上且 50nm 以下、10nm 以上且 100nm 以下、50nm 以上且 500nm 以下、100nm 以上且 1μm 以下等的範圍中移動物質的精度，即可。至於這些範圍，根據物質 28 的結構設定最適合的範圍，即可。

[0168] 接著，說明使用上述穿透式電子繞射測定裝置測定物質的穿透式電子繞射圖案的方法。

[0169] 例如，如圖 38B 所示，藉由改變作為奈米束的電子 24 的照射到物質的位置（進行掃描），可以確認物質的結構逐漸變化。此時，如果物質 28 是 CAAC-OS 膜，則可以觀察到圖 37A 所示的繞射圖案。如果物質 28 是 nc-OS 膜，則可以觀察到圖 37B 所示的繞射圖案。

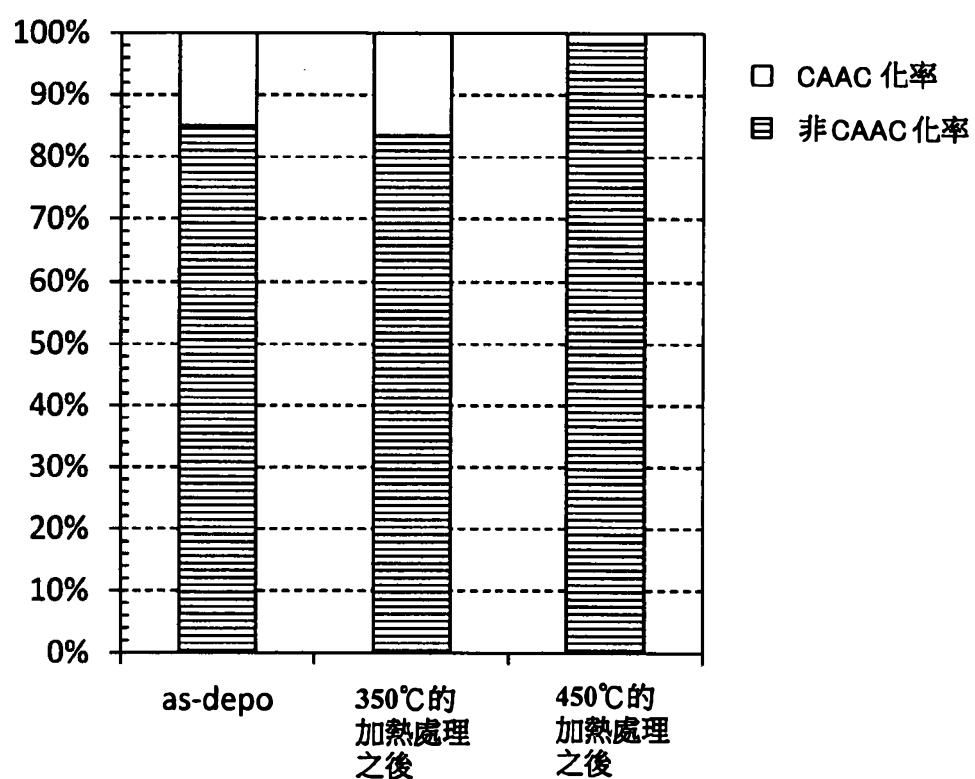

[0170] 即使物質 28 是 CAAC-OS 膜，也有時部分地觀察到與 nc-OS 膜等同樣的繞射圖案。因此，有時可以由在一定區域中觀察到 CAAC-OS 膜的繞射圖案的區域所占的比例（也稱為 CAAC 化率）表示 CAAC-OS 膜的優劣。例如，優良的 CAAC-OS 膜的 CAAC 化率為 60% 以上，較佳為 80% 以上，更佳為 90% 以上，進一步較佳為 95% 以上。另外，將觀察到與 CAAC-OS 膜不同的繞射圖案的區域的比例記作為非 CAAC 化率。

[0171] 作為一個例子，對具有剛成膜之後（記作為 as-depo）的 CAAC-OS 膜、以 350°C 或 450°C 進行加熱處理之後的 CAAC-OS 膜的各樣本的頂面進行掃描，來得到穿透式電子繞射圖案。在此，以 5 nm/秒鐘的速度進行掃描 60 秒鐘來觀察繞射圖案，並且，在每個 0.5 秒鐘將觀察到的繞射圖案轉換為靜態影像，由此導出 CAAC 化率。在此，使用束徑為 1 nm 的奈米束。

[0172] 圖 39 示出各樣本的 CAAC 化率。由此可知，與剛成膜之後和 350°C 的加熱處理之後的 CAAC 化率相比，450°C 的加熱處理之後的 CAAC 化率更高。也就是說，可以知道比 350°C 高的溫度（例如 400°C 以上）下的加熱處理會降低非 CAAC 化率（提高 CAAC 化率）。在此，與 CAAC-OS 膜不同的繞射圖案的大部分是與 nc-OS 膜同樣的繞射圖案。由此可知，藉由加熱處理，具有與 nc-OS 膜同樣的結構的區域受到相鄰的區域的結構的影響而重新排列，因此該區域被 CAAC 化。

[0173] 藉由採用這種測定方法，有時可以對具有多種結構的氧化物半導體膜進行結構分析。

[0174] CAAC-OS 膜例如可以使用多晶的氧化物半導體濺射靶材，利用濺射法形成。當離子碰撞到該濺射靶材時，有時包含在濺射靶材中的結晶區域沿著 a-b 面劈開，即具有平行於 a-b 面的面的平板狀或顆粒狀的濺射粒子剝離。此時，由於該平板狀或顆粒狀的濺射粒子帶電，所以濺射粒子不在電漿中凝聚而保持結晶狀態的狀態到達基

板，由此可以形成 CAAC-OS 膜。

[0175] 在形成氧化物半導體膜 404b 之後可以進行第一加熱處理。第一加熱處理在 250°C 以上且 650°C 以下，較佳為 300°C 以上且 500°C 以下的溫度下且在惰性氣體氛圍、包含 10ppm 以上的氧化氣體的氛圍或減壓狀態下進行即可。作為第一加熱處理，也可以進行惰性氣體氛圍下的加熱處理，然後為了補充脫離了的氧而進行包含 10ppm 以上的氧化氣體的氛圍下的加熱處理。藉由進行第一加熱處理，可以提高氧化物半導體膜 404b 的結晶性，而且可以從基底絕緣膜 402 和第一氧化物膜 404a 中去除氫或水等雜質。此外，也可以在用來形成氧化物半導體膜 404b 的蝕刻之前進行第一加熱處理。

[0176] 接著，在第一氧化物膜 404a 及氧化物半導體膜 404b 上形成成為源極電極 406a 及汲極電極 406b 的第一導電膜。作為第一導電膜，可以使用 Al、Cr、Cu、Ta、Ti、Mo、W 或以它們為主要成分的合金材料。例如，利用濺射法等形成 100nm 厚的鈦膜。此外，也可以利用 CVD 法形成鎢膜。

[0177] 接著，以在氧化物半導體膜 404b 上使第一導電膜分割的方式對第一導電膜進行蝕刻，來形成源極電極 406a 及汲極電極 406b（參照圖 8C）。此時，由於第一導電膜的過蝕刻，基底絕緣膜 402 的一部分也可以被蝕刻。

[0178] 接著，在第一氧化物膜 404a、氧化物半導體膜 404b、源極電極 406a 及汲極電極 406b 上形成第二氧

化物膜 403c。

[0179] 在形成第二氧化物膜 403c 之後可以進行第二加熱處理。第二加熱處理可以在與第一加熱處理相同的條件下進行。藉由進行第二加熱處理，可以從第二氧化物膜 403c 中去除氫或水等雜質。此外，還可以從第一氧化物膜 404a 及氧化物半導體膜 404b 中進一步去除氫或水等雜質。

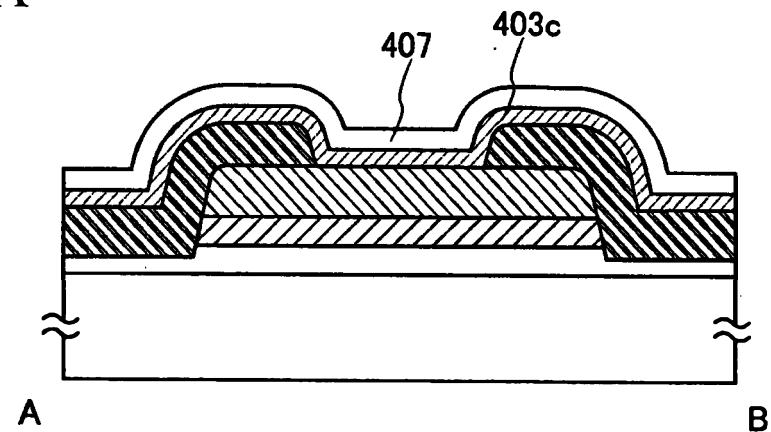

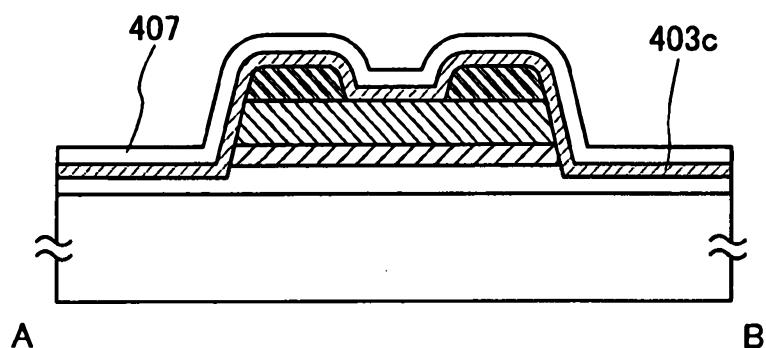

[0180] 接著，在第二氧化物膜 403c 上形成成為閘極絕緣膜 408 的絕緣膜 407（參照圖 9A）。絕緣膜 407 可以使用氧化鋁、氧化鎂、氧化矽、氮氧化矽、氮氧化鋁、氮化矽、氧化鎗、氧化鋒、氧化鈷、氧化鋁、氧化鑭、氧化銻、氧化鉻和氧化鉭等形成。此外，絕緣膜 407 也可以是上述材料的疊層。絕緣膜 407 可以利用濺射法、CVD 法、MBE 法、ALD 法或 PLD 法等形成。另外，較佳為藉由調節原材料、溫度、壓力、電極間距離、投入功率等而形成閘極絕緣膜 408，來獲得圖 5A 所示的  $T_{G11}$  與  $T_{G12}$  幾乎相同的覆蓋性得到提高的結構。例如，藉由在能夠維持閘極絕緣膜的性質的範圍內以高溫、高壓的條件進行成膜，可以提高覆蓋性。

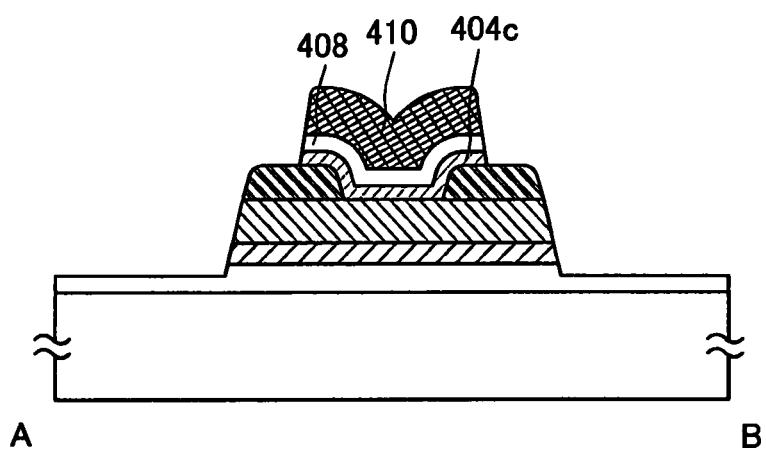

[0181] 接著，在絕緣膜 407 上形成成為閘極電極 410 的第二導電膜 409（參照圖 9B）。作為第二導電膜 409，可以使用 Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、Ta、W 或以它們為主要成分的合金材料。第二導電膜 409 可以利用濺射法或 CVD 法等形成。另外，第二導

電膜 409 可以使用包含氮的導電膜，也可以使用包含上述材料的導電膜與包含氮的導電膜的疊層。

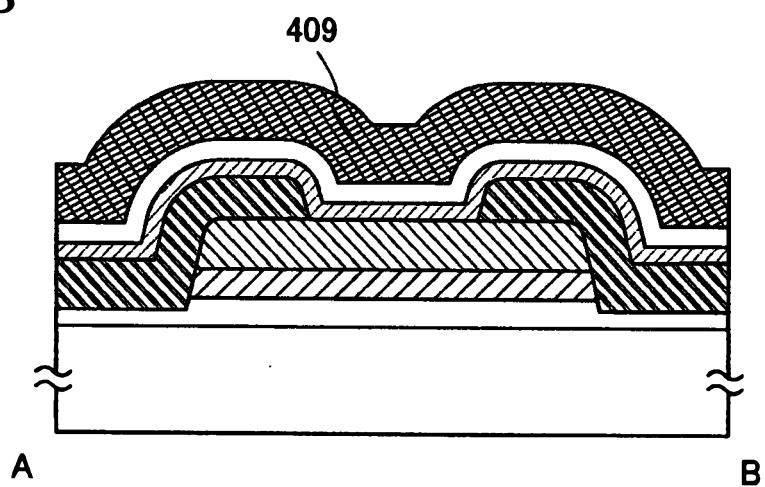

[0182] 接著，使用用來形成閘極電極 410 的光阻遮罩對第二導電膜 409 選擇性地進行蝕刻，來形成閘極電極 410（參照圖 9C）。

[0183] 接著，以上述光阻遮罩或者閘極電極 410 為遮罩對絕緣膜 407 選擇性地進行蝕刻，來形成閘極絕緣膜 408。

[0184] 接著，以上述光阻遮罩或者閘極電極 410 為遮罩對第二氧化物膜 403c 進行蝕刻，來形成第二氧化物膜 404c。

[0185] 換而言之，第二氧化物膜 404c 的上端部的位置與閘極絕緣膜 408 的下端部的位置一致，閘極絕緣膜 408 的上端部的位置與閘極電極 410 的下端部的位置一致。在此，以閘極電極 410 為遮罩形成閘極絕緣膜 408 及第二氧化物膜 404c，但是不侷限於此，也可以在形成第二導電膜 409 之前形成閘極絕緣膜 408 及第二氧化物膜 404c。

[0186] 接著，在源極電極 406a、汲極電極 406b 及閘極電極 410 上形成氧化物絕緣膜 412（參照圖 1B）。氧化物絕緣膜 412 可以與基底絕緣膜 402 同樣的材料及方法形成。氧化物絕緣膜 412 較佳為使用氧化鋁膜、氧化鎂膜、氧化矽膜、氧氮化矽膜、氮氧化矽膜、氮化矽膜、氧化鎗膜、氧化鋒膜、氧化釔膜、氧化鋯膜、氧化鑭膜、氧化銣膜、氧化欒

膜、氧化鉻膜、氧化鋟膜或包含氮的氧化物絕緣膜形成。氧化物絕緣膜 412 可以利用濺射法、CVD 法、MBE 法、ALD 法或 PLD 法形成，較佳為包含過剩的氧以對多層膜 404 供應氧。

[0187] 另外，也可以利用離子植入法、離子摻雜法、電漿浸沒離子植入法等對氧化物絕緣膜 412 添加氧。藉由添加氧，可以更容易地將氧從氧化物絕緣膜 412 供應到多層膜 404 中。

[0188] 接著，也可以進行第三加熱處理。第三加熱處理可以在與第一加熱處理相同的條件下進行。藉由進行第三加熱處理，容易使基底絕緣膜 402、閘極絕緣膜 408 及氧化物絕緣膜 412 釋放過剩氧，因此可以減少多層膜 404 中的氧缺陷。

[0189] 藉由上述製程，可以製造圖 1A 至圖 1C 所示的電晶體 450。

[0190] 注意，本實施方式可以與本說明書所示的其他實施方式適當地組合。

[0191]

### 實施方式 3

在本實施方式中，對具有與在實施方式 1 中說明的電晶體不同結構的電晶體進行說明。

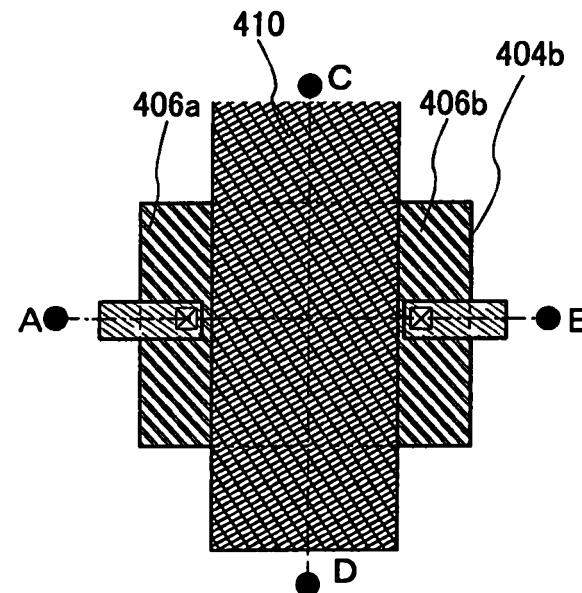

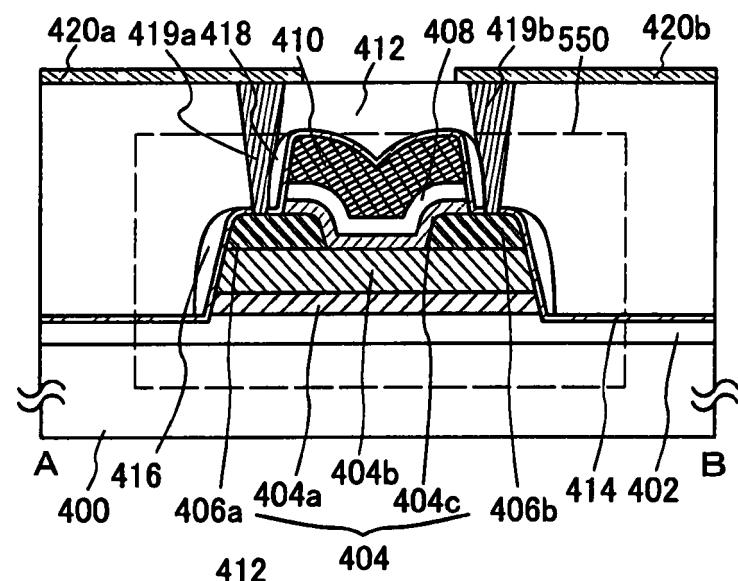

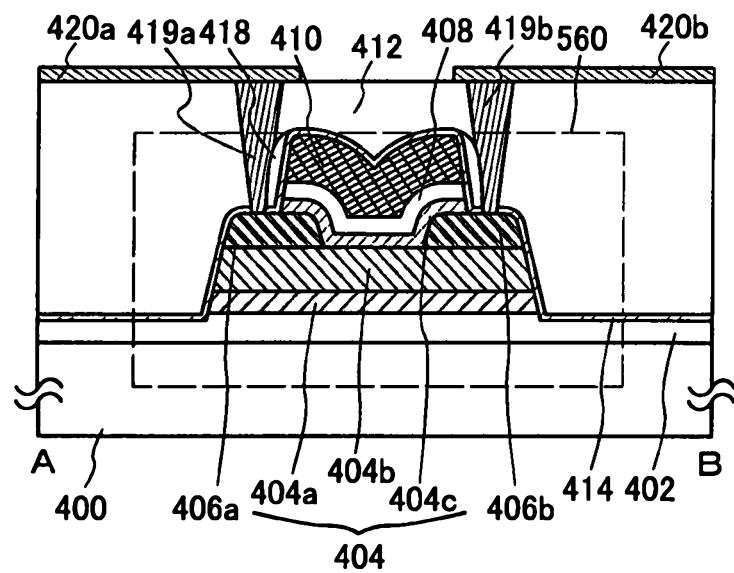

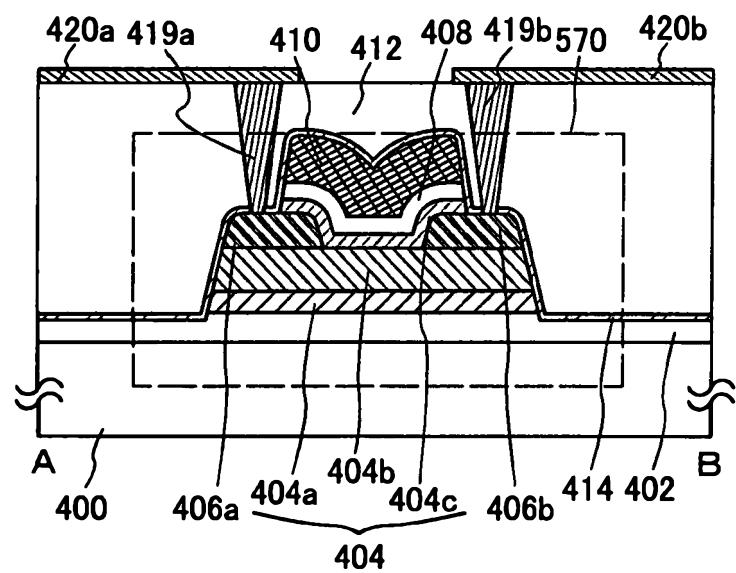

[0192] 圖 14A 至圖 14C 為本發明的一個方式的電晶體的俯視圖及剖面圖。圖 14A 為俯視圖，圖 14B 為圖 14A 所示的點劃線 A-B 的剖面，圖 14C 為點劃線 C-D 的

剖面。注意，在圖 14A 的俯視圖中，為了明確起見，省略一部分的構成要素。另外，有時將點劃線 A-B 的方向稱為通道長度方向，將點劃線 C-D 的方向稱為通道寬度方向。

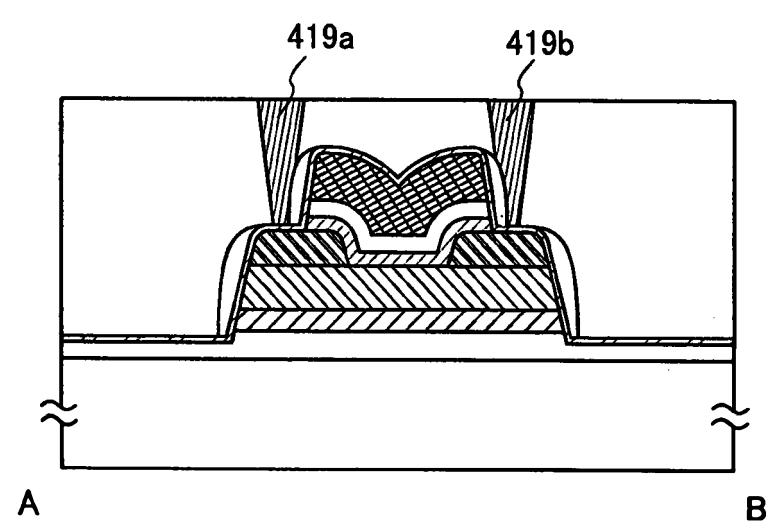

[0193] 圖 14A 至圖 14C 所示的電晶體 550 包括：基板 400 上的基底絕緣膜 402；基底絕緣膜 402 上的第一氧化物膜 404a 及氧化物半導體膜 404b；第一氧化物膜 404a 及氧化物半導體膜 404b 上的源極電極 406a 及汲極電極 406b；氧化物半導體膜 404b、源極電極 406a 及汲極電極 406b 上的第二氧化物膜 404c；第二氧化物膜 404c 上的閘極絕緣膜 408；閘極絕緣膜 408 上的閘極電極 410；源極電極 406a、汲極電極 406b、第二氧化物膜 404c 以及閘極電極 410 上的障壁膜 414；隔著障壁膜 414 覆蓋第一氧化物膜 404a、氧化物半導體膜 404b、源極電極 406a 及汲極電極 406b 的側面的側壁絕緣膜 416；隔著障壁膜 414 覆蓋第二氧化物膜 404c、閘極絕緣膜 408 及閘極電極 410 的側面的側壁絕緣膜 418；源極電極 406a、汲極電極 406b、閘極電極 410、側壁絕緣膜 416 及側壁絕緣膜 418 上的氧化物絕緣膜 412；填埋於設置在氧化物絕緣膜 412 中的開口且與源極電極 406a 及汲極電極 406b 電連接的電極 419a 及電極 419b；與電極 419a 及電極 419b 電連接的佈線 420a 及佈線 420b。另外，將第一氧化物膜 404a、氧化物半導體膜 404b 以及第二氧化物膜 404c 總稱為多層膜 404。

[0194] 氧化物半導體膜 404b 的端部帶弧形，具有半

圓形狀。藉由採用這種結構，可以提高形成在氧化物半導體膜 404b 上的閘極絕緣膜 408 及閘極電極 410 的覆蓋性。

[0195] 障壁膜 414 較佳為使用對氫、水及氧具有阻擋效果的絕緣膜形成，典型地使用氧化鋁膜形成。氧化鋁膜除了阻擋效果之外，還具有供應氧的功能。另外，也可以使用利用混有氧化鋁和氧化矽的靶材形成的包含氧化矽的氧化鋁膜。此時，氧化矽的含量較佳為 0.1wt%以上且 30wt%以下。

[0196] 由於障壁膜 414 的與多層膜 404 及閘極電極 410 的側面接觸的部分的覆蓋性有可能下降，因此也可以藉由由側壁絕緣膜 416 及側壁絕緣膜 418 覆蓋該部分，可以阻擋氫、水及氧。側壁絕緣膜 416 及側壁絕緣膜 418 可以使用與基底絕緣膜 402 或閘極絕緣膜 408 相同的材料。

[0197] 電極 419a 及電極 419b 分別與源極電極 406a 及汲極電極 406b 電連接。佈線 420a 及佈線 420b 分別與電極 419a 及電極 419b 電連接。在進行微細加工的情況下，當在氧化物絕緣膜 412 中形成開口並以藉由開口分別與源極電極 406a 及汲極電極 406b 電連接的方式形成佈線 420a 及佈線 420b 時，佈線 420a 及佈線 420b 不到達開口的底部，不能使佈線 420a 及佈線 420b 分別電連接到源極電極 406a 及汲極電極 406b。因此，需要先用電極 419a 及電極 419b 填充開口，再形成佈線 420a 及佈線 420b。注意，在使用能夠與源極電極 406a 及汲極電極 406b 接觸的

材料形成佈線 420a 及佈線 420b 的情況下，不需要電極 419a 及電極 419a。

[0198] 電極 419a、電極 419b、佈線 420a 及佈線 420b 可以使用與源極電極 406a、汲極電極 406b 及閘極電極 410 相同的材料。

[0199] 此外，也可以採用圖 18A 所示的電晶體 560 那樣的沒有側壁絕緣膜 416 的結構。另外，也可以採用圖 18B 所示的電晶體 570 那樣的沒有側壁絕緣膜 416 及側壁絕緣膜 418 的結構。

[0200] 再者，也可以採用圖 18C 所示的電晶體 580 那樣的電極 419a 及電極 419b 到達源極電極 406a 及汲極電極 406b 的結構。

[0201] 注意，本實施方式可以與本說明書所示的其他實施方式適當地組合。

[0202]

#### 實施方式 4

在本實施方式中，參照圖 15A 至圖 17C 對在實施方式 3 中說明的圖 14A 至圖 14C 所示的電晶體 550 的製造方法進行說明。

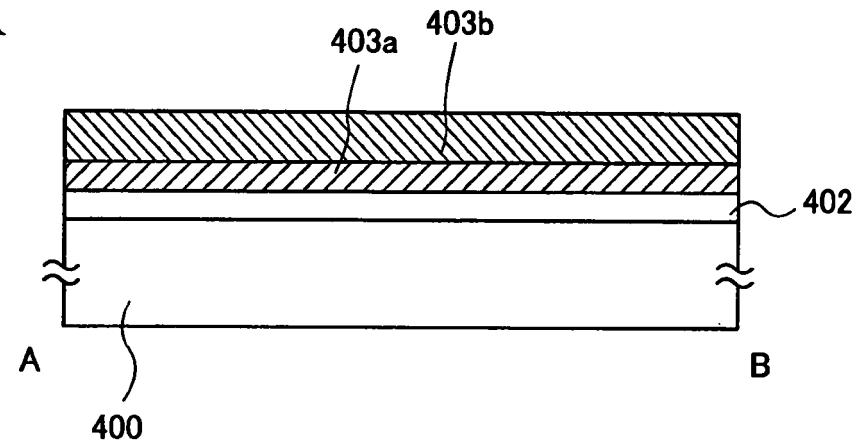

[0203] 首先，在基板 400 上形成基底絕緣膜 402、第一氧化物膜 403a 及氧化物半導體膜 403b（參照圖 15A）。基板 400、基底絕緣膜 402、第一氧化物膜 403a 及氧化物半導體膜 403b 的材料及製造方法可以參照前面的實施方式的記載。

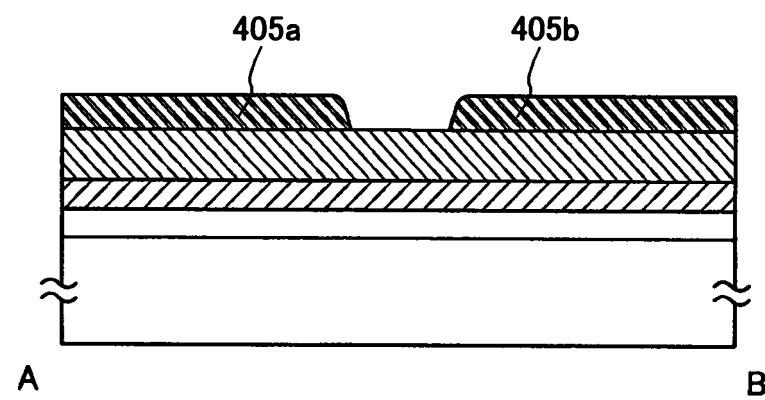

[0204] 接著，在氧化物半導體膜 403b 上形成成為源極電極 406a 及汲極電極 406b 的導電膜，僅對與成為通道區域的部分重疊的部分進行蝕刻，來形成導電膜 405a 及導電膜 405b（參照圖 15B）。成為源極電極 406a 及汲極電極 406b 的導電膜的材料及製造方法可以參照前面的實施方式的記載。

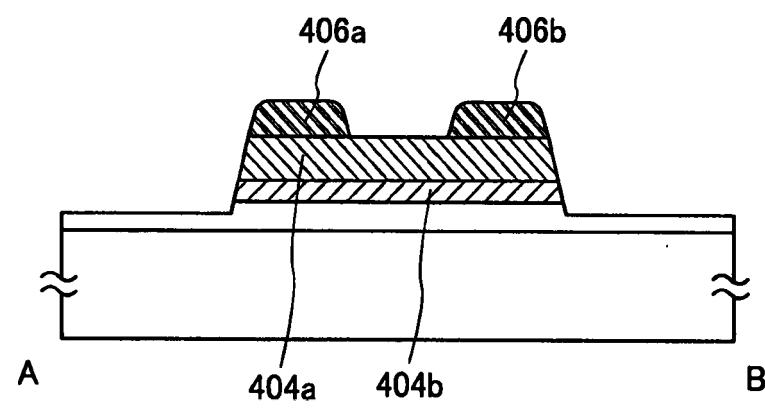

[0205] 接著，在導電膜 405a 及導電膜 405b 上形成光阻遮罩，對第一氧化物膜 403a、氧化物半導體膜 403b、導電膜 405a 及導電膜 405b 選擇性地進行蝕刻，來形成第一氧化物膜 404a、氧化物半導體膜 404b、源極電極 406a 及汲極電極 406b（參照圖 15C）。此時，在該光阻遮罩被形成為薄且微細的情況下，當進行蝕刻時光阻遮罩逐漸縮退，有時導電膜 405a 及導電膜 405b 的端部自然會帶弧形而具有曲面。其結果，形成在源極電極 406a 及汲極電極 406b 上的第二氧化物膜 404c、閘極絕緣膜 408、閘極電極 410 及氧化物絕緣膜 412 的覆蓋性得到提高，而可以防止斷開等的形狀不良。

[0206] 接著，在第一氧化物膜 404a、氧化物半導體膜 404b、源極電極 406a 及汲極電極 406b 上形成第二氧化物膜 403c 及絕緣膜 407（參照圖 16A）。第二氧化物膜 403c 及絕緣膜 407 的材料及製造方法可以參照前面的實施方式的記載。

[0207] 此外，也可以在形成第二氧化物膜 403c 之後進行第二加熱處理。第二加熱處理可以與第一加熱處理

相同的條件進行。藉由進行第二加熱處理，可以從第二氧化物膜 404c 去除氫或水等雜質。另外，也可以從第一氧化物膜 404a 及氧化物半導體膜 404b 進一步去除氫或水等雜質。

[0208] 接著，在絕緣膜 407 上形成成為閘極電極 410 的第二導電膜，使用光阻遮罩對第二導電膜選擇性地進行蝕刻，來形成閘極電極 410（參照圖 16B）。閘極電極 410 的材料及製造方法可以參照前面的實施方式的記載。

[0209] 接著，以上述光阻遮罩或閘極電極 410 為遮罩對絕緣膜 407 選擇性地進行蝕刻，來形成閘極絕緣膜 408。

[0210] 接著，以上述光阻遮罩或閘極電極 410 為遮罩對第二氧化物膜 403c 進行蝕刻，來形成第二氧化物膜 404c。

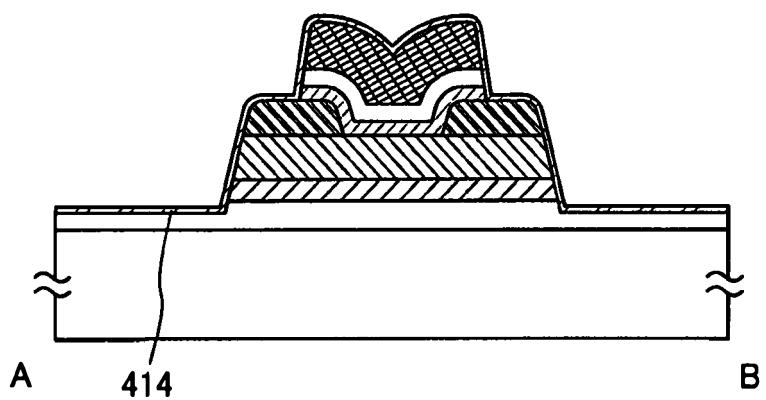

[0211] 接著，在基底絕緣膜 402、源極電極 406a、汲極電極 406b 以及閘極電極 410 上形成障壁膜 414（參照圖 16C）。

[0212] 障壁膜 414 為對氫、水及氧具有阻擋效果的絕緣膜，因此可以抑制包含於多層膜 404、基底絕緣膜 402 以及閘極絕緣膜 408 的氧擴散到外部，而可以高效地對氧化物半導體膜供應氧而減少氧缺陷。因此，電特性得到提高，而可以提供可靠性高的半導體裝置。

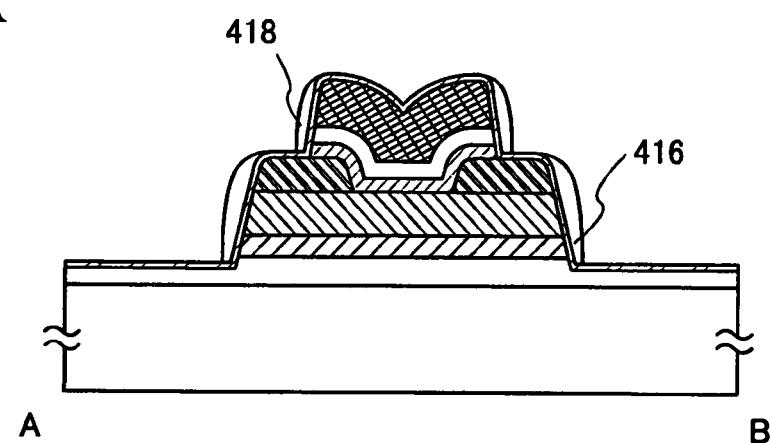

[0213] 接著，藉由對成為側壁絕緣膜 416 和側壁絕緣膜 418 的絕緣膜進行各向異性高的蝕刻處理，可以在多

層膜 404、源極電極 406a、汲極電極 406b、閘極絕緣膜 408 以及閘極電極 410 的側面隔著障壁膜 414 形成側壁絕緣膜 416 和側壁絕緣膜 418（參照圖 17A）。

[0214] 接著，在障壁膜 414 上形成氧化物絕緣膜 412（參照圖 17B）。氧化物絕緣膜 412 的材料及製造方法可以參照前面的實施方式的記載。

[0215] 接著，也可以進行第三加熱處理。第三加熱處理可以與第一加熱處理相同的條件進行。藉由進行第三加熱處理，過剩氧容易從基底絕緣膜 402、閘極絕緣膜 408 及氧化物絕緣膜 412 釋放出，而可以減少多層膜 404 中的氧缺陷。

[0216] 接著，在氧化物絕緣膜 412 及障壁膜 414 中形成開口，在氧化物絕緣膜 412 上及開口中形成藉由該開口分別與源極電極 406a 及汲極電極 406b 電連接的電極 419a 及電極 419b。

[0217] 電極 419a 及電極 419b 填埋於開口中。將電極 419a 及電極 419b 填埋於開口中的方法為如下：在氧化物絕緣膜 412 上及開口中形成成為電極 419a 及電極 419b 的導電膜，並且，利用去除（拋光）處理以使氧化物絕緣膜 412 露出的方式去除導電膜的一部分（參照圖 17C）。

[0218] 作為去除方法，較佳為使用化學機械拋光（Chemical Mechanical Polishing：CMP）處理。

[0219] 注意，在本實施方式中，利用 CMP 處理去除導電膜的一部分，但是也可以利用其他去除處理。或者，

還可以組合 CMP 處理等拋光處理與蝕刻（乾蝕刻、濕蝕刻）處理或電漿處理等。例如，也可以藉由在進行 CMP 處理之後進行乾蝕刻處理或電漿處理（反濺射等），來提高處理表面的平坦性。當在去除處理中組合蝕刻處理或電漿處理等與 CMP 處理時，對製程順序沒有特別的限制，可以根據導電膜的材料、厚度及表面的凹凸狀態適當地設定。另外，也可以利用 CMP 處理去除導電膜的大部分並利用乾蝕刻處理等去除剩下的部分。

[0220] 另外，既可進行 CMP 處理一次，又可進行 CMP 處理多次。當進行 CMP 處理多次時，較佳為在進行高拋光率的初期拋光之後，進行低拋光率的精拋光。如此，藉由將拋光率不同的拋光組合，可以進一步提高導電膜（電極 419a、電極 419b）的表面的平坦性。

[0221] 接著，在氧化物絕緣膜 412、電極 419a 及電極 419b 上形成與電極 419a 及電極 419b 電連接的佈線 420a 及佈線 420b（參照圖 14B）。

[0222] 藉由上述製程，可以製造圖 14A 至圖 14C 所示的電晶體 550。

[0223] 注意，本實施方式可以與本說明書所示的其他實施方式適當地組合。

[0224]

#### 實施方式 5

在本實施方式中，參照圖式說明利用本發明的一個方式的電晶體的電路的一個例子。

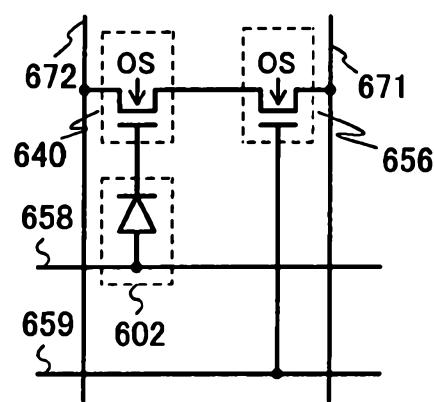

[0225] 圖 19A 和圖 19B 示出半導體裝置的電路圖，圖 19C 和圖 19D 示出半導體裝置的剖面圖。在圖 19C 及圖 19D 中，在圖式中的左邊示出電晶體 450 的通道長度方向上的剖面圖，在圖式中的右邊示出電晶體 450 的通道寬度方向上的剖面圖。在電路圖中，為了表示使用氧化物半導體的電晶體，附上“OS”的符號。

[0226] 圖 19C 和圖 19D 所示的半導體裝置在其下部包括使用第一半導體材料的電晶體 2200，並在其上部包括使用第二半導體材料的電晶體。在此，說明採用在實施方式 1 中例示出的電晶體 450 作為使用第二半導體材料的電晶體的例子。

[0227] 這裡，第一半導體材料和第二半導體材料的能隙較佳為不同。例如，可以將氧化物半導體以外的半導體材料（矽、鍺、矽鍺、碳化矽或砷化鎵等）用於第一半導體材料，並且將在實施方式 1 中說明的氧化物半導體用於第二半導體材料。作為氧化物半導體以外的材料使用單晶矽等的電晶體容易進行高速工作。另一方面，使用氧化物半導體的電晶體的關態電流小。

[0228] 在此，說明電晶體 2200 為 p 通道電晶體的情況，但是當然也可以使用 n 通道電晶體構成不同的電路。另外，除了使用氧化物半導體的實施方式 1 所示那樣的電晶體以外，半導體裝置的材料或結構等半導體裝置的具體結構不需要侷限於在此所示的結構。

[0229] 圖 19A、圖 19C 及圖 19D 示出將 p 通道電晶

體及 n 通道電晶體串聯連接且將各閘極連接的所謂的 CMOS 電路的結構實例。

[0230] 本發明的一個方式的使用氧化物半導體的電晶體的通態電流很大，所以可以實現電路的高速工作。

[0231] 在圖 19C 所示的結構中，在電晶體 2200 的上部隔著絕緣膜 2201 設置有電晶體 450。另外，在電晶體 2200 與電晶體 450 之間設置有多個佈線 2202。填埋於各絕緣膜中的多個插頭 2203 電連接該絕緣膜上及下的佈線或電極。另外，設置有覆蓋電晶體 450 的絕緣膜 2204、絕緣膜 2204 上的佈線 2205、對與電晶體 450 的一對電極相同的導電膜進行加工來形成的佈線 2206。

[0232] 如此，藉由層疊兩個電晶體，可以降低電路所占的面積，從而可以以更高密度配置多個電路。

[0233] 在圖 19C 中，電晶體 450 的源極和汲極中的一個藉由佈線 2202 及插頭 2203 與電晶體 2200 的源極和汲極中的一個電連接。另外，電晶體 450 的閘極藉由佈線 2205、佈線 2206、插頭 2203 及佈線 2202 等與電晶體 2200 的閘極電連接。

[0234] 在圖 19D 所示的結構中，在電晶體 450 的閘極絕緣層中設置有用來埋入插頭 2203 的開口部，並且電晶體 450 的閘極與插頭 2203 接觸。藉由採用上述結構，容易實現電路的積體化，而且可以使佈線或插頭的個數或長度比圖 19C 所示的結構小，從而可以使電路以更高速工作。

[0235] 在圖 19C 或圖 19D 所示的結構中，藉由改變電晶體 450 及電晶體 2200 的電極的連接結構，可以構成各種電路。例如，如圖 19B 所示，藉由採用使各電晶體的源極與汲極連接的電路結構，可以將它用作所謂的類比開關。

[0236] 另外，藉由使用上述實施方式的電晶體，可以製造具有讀取目標物的資料的影像感測器功能的半導體裝置。

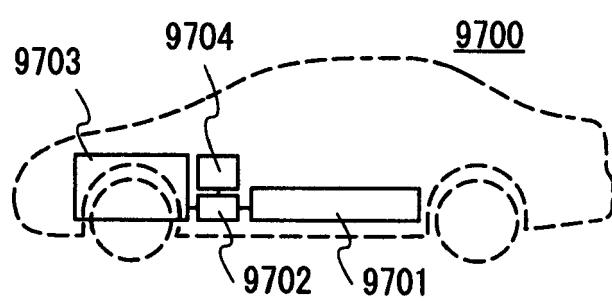

[0237] 圖 24 示出具有影像感測器功能的半導體裝置的等效電路的一個例子。

[0238] 光電二極體 602 的一個電極與光電二極體重設信號線 658 電連接，光電二極體 602 的另一個電極與電晶體 640 的閘極電連接。電晶體 640 的源極和汲極中的一個與光感測器參考信號線 672 電連接，電晶體 640 的源極和汲極中的另一個與電晶體 656 的源極和汲極中的一個電連接。電晶體 656 的閘極與閘極信號線 659 電連接，電晶體 656 的源極和汲極中的另一個與光感測器輸出信號線 671 電連接。

[0239] 作為光電二極體 602，例如可以使用層疊有具有 p 型導電型的半導體層、高電阻的（具有 i 型導電型的）半導體層及具有 n 型導電型的半導體層的 pin 型光電二極體。

[0240] 藉由檢測入射到光電二極體 602 的光，可以讀取檢測目標的資料。另外，在讀取檢測目標的資料時，

也可以使用背光等的光源。

[0241] 另外，作為電晶體 640 及電晶體 656，可以使用上述實施方式中的任一個所示的通道形成在氧化物半導體中的電晶體。在圖 24 中，為了明確表示電晶體 640 及電晶體 656 包含氧化物半導體，附上“OS”的符號。

[0242] 電晶體 640 及電晶體 656 為在上述實施方式中例示出的電晶體，較佳為具有由閘極電極電性上包圍氧化物半導體膜的結構。另外，由於氧化物半導體膜的上端部帶弧形而具有曲面，因此可以提高形成在氧化物半導體膜上的膜的覆蓋性。另外，可以緩和在源極電極及汲極電極的端部有可能產生的電場集中，所以可以抑制電晶體的劣化。因此，電晶體 640 及電晶體 656 為電特性變動得到抑制的在電性上穩定的電晶體。藉由包含該電晶體，作為圖 24 所示的具有影像感測器功能的半導體裝置，可以提供可靠性高的半導體裝置。

[0243] 注意，本實施方式可以與本說明書所示的其他實施方式適當地組合。

[0244]

#### 實施方式 6

在本實施方式中，參照圖式對一種半導體裝置（記憶體裝置）的一個例子進行說明，該半導體裝置（記憶體裝置）使用本發明的一個方式的電晶體，即使在沒有電力供應的情況下也能夠保持儲存資料，並且，對寫入次數也沒有限制。

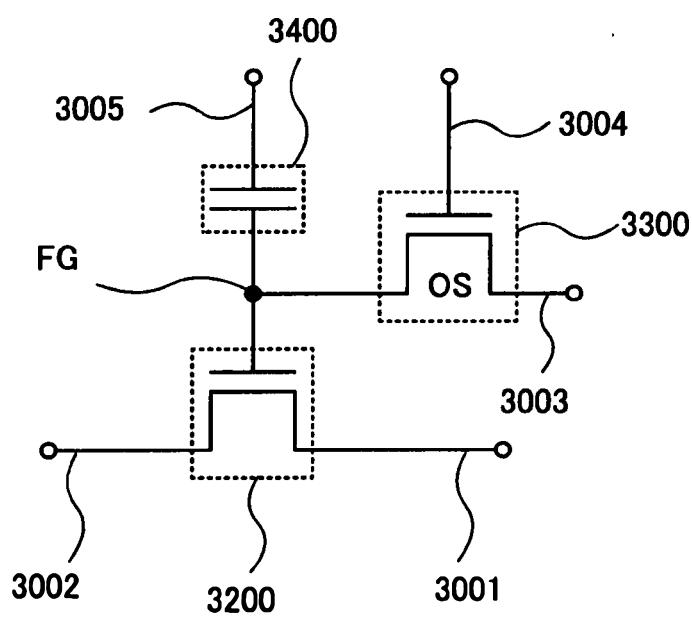

[0245] 圖 20 示出半導體裝置的電路圖。

[0246] 在圖 20 所示的半導體裝置包括：使用第一半導體材料的電晶體 3200；使用第二半導體材料的電晶體 3300；以及電容元件 3400。此外，作為電晶體 3300，可以使用在實施方式 1 中說明的電晶體。

[0247] 電晶體 3300 是其通道形成在包含氧化物半導體的半導體層中的電晶體。因為電晶體 3300 的關態電流小，所以藉由使用該電晶體，可以長期保持儲存資料。換言之，因為可以形成不需要更新工作或更新工作的頻率極低的半導體記憶體裝置，所以可以充分降低功耗。

[0248] 在圖 20 中，第一佈線 3001 與電晶體 3200 的源極電極電連接，第二佈線 3002 與電晶體 3200 的汲極電極電連接。此外，第三佈線 3003 與電晶體 3300 的源極電極和汲極電極中的一個電連接，第四佈線 3004 與電晶體 3300 的閘極電極電連接。再者，電晶體 3200 的閘極電極及電晶體 3300 的源極電極和汲極電極中的另一個與電容元件 3400 的電極的一個電連接，第五佈線 3005 與電容元件 3400 的電極的另一個電連接。

[0249] 在圖 20 所示的半導體裝置中，藉由有效地利用能夠保持電晶體 3200 的閘極電極的電位的特徵，可以如下所示那樣進行資料的寫入、保持以及讀出。

[0250] 對資料的寫入及保持進行說明。首先，將第四佈線 3004 的電位設定為使電晶體 3300 成為導通狀態的電位，使電晶體 3300 成為導通狀態。由此，第三佈線

3003 的電位施加到電晶體 3200 的閘極電極及電容元件 3400。換言之，對電晶體 3200 的閘極電極施加規定的電荷（寫入）。這裡，施加賦予兩種不同電位位準的電荷（以下，稱為低位準電荷、高位準電荷）中的任一種。然後，藉由將第四佈線 3004 的電位設定為使電晶體 3300 成為關閉狀態的電位，來使電晶體 3300 成為關閉狀態，而保持施加到電晶體 3200 的閘極電極的電荷（保持）。

[0251] 因為電晶體 3300 的關態電流極小，所以電晶體 3200 的閘極電極的電荷被長時間地保持。

[0252] 接著，對資料的讀出進行說明。當在對第一佈線 3001 施加規定的電位（恆電位）的狀態下對第五佈線 3005 施加適當的電位（讀出電位）時，根據保持在電晶體 3200 的閘極電極中的電荷量，第二佈線 3002 具有不同的電位。這是因為如下緣故：一般而言，在電晶體 3200 為 n 通道電晶體的情況下，對電晶體 3200 的閘極電極施加高位準電荷時的外觀上的臨界電壓  $V_{th\_H}$  低於對電晶體 3200 的閘極電極施加低位準電荷時的外觀上的臨界電壓  $V_{th\_L}$ 。在此，外觀上的臨界電壓是指為了使電晶體 3200 成為“導通狀態”所需要的第五佈線 3005 的電位。因此，藉由將第五佈線 3005 的電位設定為  $V_{th\_L}$  與  $V_{th\_H}$  之間的電位  $V_0$ ，可以辨別施加到電晶體 3200 的閘極電極的電荷。例如，在寫入時被供應高位準電荷的情況下，如果第五佈線 3005 的電位為  $V_0 (> V_{th\_H})$ ，電晶體 3200 則成為“導通狀態”。當被供應低位準電荷時，即使第五佈

線 3005 的電位為  $V_0 (< V_{th\_L})$ ，電晶體 3200 還保持“關閉狀態”。因此，藉由辨別第二佈線 3002 的電位，可以讀出所保持的資料。

[0253] 注意，當將記憶單元配置為陣列狀時，需要僅讀出所希望的記憶單元的資料。如此，當不讀出資料時，對第五佈線 3005 施加不管閘極電極的狀態如何都使電晶體 3200 成為“關閉狀態”的電位，即小於  $V_{th\_H}$  的電位，即可。或者，對第五佈線 3005 施加不管閘極電極的狀態如何都使電晶體 3200 成為“導通狀態”的電位，即大於  $V_{th\_L}$  的電位，即可。

[0254] 在本實施方式所示的半導體裝置中，藉由使用將氧化物半導體用於通道形成區的關態電流極小的電晶體，可以極長期地保持儲存資料。換言之，因為不需要進行更新工作，或者，可以使更新工作的頻率變得極低，所以可以充分降低功耗。另外，即使在沒有電力供給的情況下（注意，較佳為固定電位），也可以長期保持儲存資料。

[0255] 另外，在本實施方式所示的半導體裝置中，資料的寫入不需要高電壓，而且也沒有元件劣化的問題。由於例如不需要如習知的非揮發性記憶體那樣地對浮動閘極注入電子或從浮動閘極抽出電子，因此不發生如閘極絕緣層的劣化等的問題。換言之，在根據所公開的發明的半導體裝置中，對重寫的次數沒有限制，這限制是習知的非揮發性記憶體所具有的問題，所以可靠性得到極大提高。

再者，根據電晶體的導通狀態或關閉狀態而進行資料寫入，而可以容易實現高速工作。

[0256] 如上所述，能夠提供一種實現了微型化及高積體化且具有高電特性的半導體裝置。

[0257]

### 實施方式 7

在本實施方式中，說明可以使用上述實施方式所說明的電晶體且包含上述實施方式所說明的記憶體裝置的 CPU。

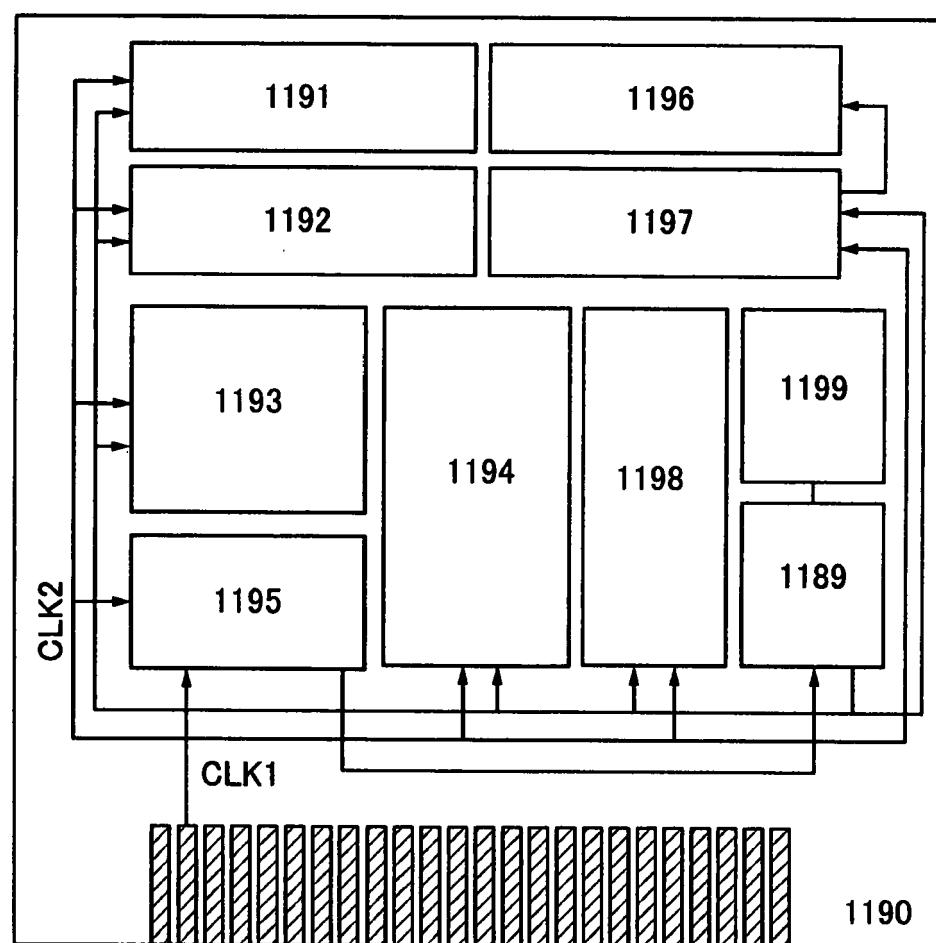

[0258] 圖 21 是示出將在實施方式 1 中說明的電晶體用於至少其一部分的 CPU 的結構的一個例子的方塊圖。

[0259] 圖 21 所示的 CPU 在基板 1190 上包括：ALU (Arithmetic logic unit：算術邏輯單元) 1191；ALU 控制器 1192；指令解碼器 1193；中斷控制器 1194；時序控制器 1195；暫存器 1196；暫存器控制器 1197；匯流排介面 1198；可改寫的 ROM 1199；以及 ROM 介面 1189。作為基板 1190，使用半導體基板、SOI 基板或玻璃基板等。可改寫的 ROM 1199 和 ROM 介面 1189 可以設置在另一晶片上。當然，圖 21 所示的 CPU 只是將其結構簡化而示出的一個例子，並且，實際上的 CPU 根據其用途具有各種各樣的結構。例如，也可以以包括圖 21 所示的 CPU 或算術邏輯單元的結構為核心，設置多個該核心並使其同時工作。另外，在 CPU 的內部算術邏輯單元或資料通路中能處理的位數例如為 8 位、16 位、32 位、64 位等。

[0260] 藉由匯流排介面 1198 輸入到 CPU 的指令輸入到指令解碼器 1193 且被解碼之後，輸入到 ALU 控制器 1192、中斷控制器 1194、暫存器控制器 1197 和時序控制器 1195。

[0261] ALU 控制器 1192、中斷控制器 1194、暫存器控制器 1197、時序控制器 1195 根據被解碼的指令而進行各種控制。明確而言，ALU 控制器 1192 生成用來控制 ALU1191 的工作的信號。另外，當 CPU 在執行程式時，中斷控制器 1194 根據其優先度或遮罩狀態而判斷來自外部的輸入/輸出裝置或週邊電路的中斷要求，且處理該要求。暫存器控制器 1197 生成暫存器 1196 的位址，並根據 CPU 的狀態而從暫存器 1196 讀出資料或對暫存器 1196 寫入資料。

[0262] 另外，時序控制器 1195 生成控制 ALU1191、ALU 控制器 1192、指令解碼器 1193、中斷控制器 1194 以及暫存器控制器 1197 的工作時序的信號。例如，時序控制器 1195 具備根據基準時脈信號 CLK1 生成內部時脈信號 CLK2 的內部時脈生成部，將該內部時脈信號 CLK2 供應到上述各種電路。

[0263] 在圖 21 所示的 CPU 中，在暫存器 1196 中設置有記憶單元。作為暫存器 1196 的記憶單元，可以使用在上述實施方式中示出的電晶體。

[0264] 在圖 21 所示的 CPU 中，暫存器控制器 1197 根據來自 ALU1191 的指示，進行暫存器 1196 中的保持工

作的選擇。換言之，在暫存器 1196 所具有的記憶單元中，選擇利用正反器保持資料還是利用電容元件保持資料。當選擇利用正反器保持資料時，對暫存器 1196 中的記憶單元供應電源電壓。當選擇利用電容元件保持資料時，改寫電容元件的資料，而可以停止對暫存器 1196 內的記憶單元供應電源電壓。

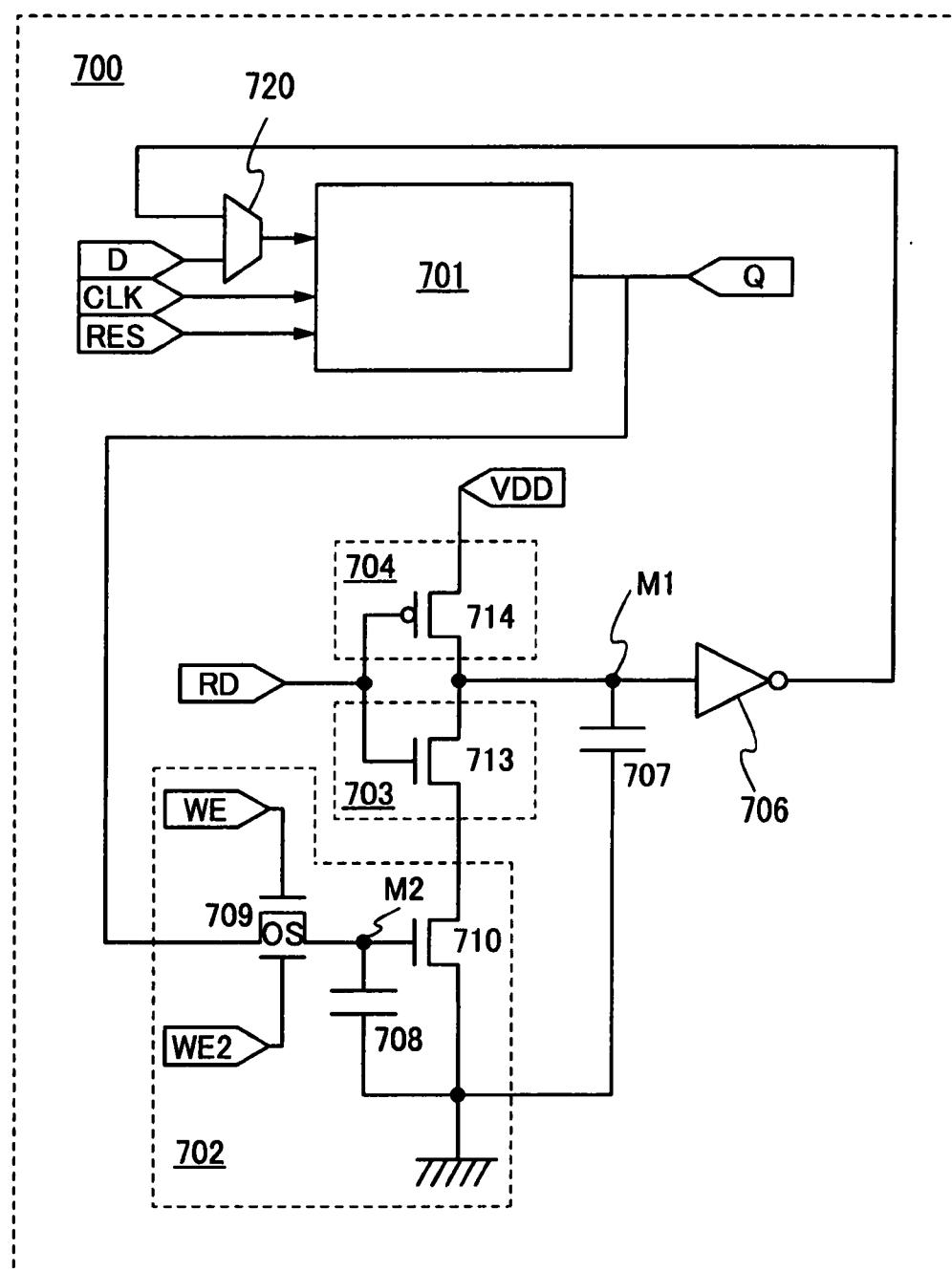

[0265] 圖 22 示出可用作暫存器 1196 的記憶元件的電路圖的一個例子。記憶元件 700 包括當電源關閉時丟失儲存資料的電路 701、當電源關閉時不丟失儲存資料的電路 702、開關 703、開關 704、邏輯元件 706、電容元件 707 以及具有選擇功能的電路 720。電路 702 包括電容元件 708、電晶體 709 及電晶體 710。另外，記憶元件 700 根據需要還可以包括其他元件，例如二極體、電阻元件或電感器等。

[0266] 在此，電路 702 可以使用在上述實施方式中說明的記憶體裝置。在停止對記憶元件 700 供應電源電壓之後，接地電位 (0V) 或使電晶體 709 成為關閉狀態的電位繼續輸入到電路 702 中的電晶體 709 的第一閘極。例如，電晶體 709 的第一閘極藉由電阻器等負載接地。

[0267] 在此示出如下例子：開關 703 使用具有一導電型（例如，n 通道型）的電晶體 713 構成，而開關 704 使用具有與此不同導電型（例如，p 通道型）的電晶體 714 構成。這裡，開關 703 的第一端子對應於電晶體 713 的源極和汲極中的一個，開關 703 的第二端子對應於電晶

體 713 的源極和汲極中的另一個，並且，開關 703 的第一端子與第二端子之間的導通或非導通（即，電晶體 713 的導通狀態或關閉狀態）由輸入到電晶體 713 的閘極的控制信號 RD 選擇。開關 704 的第一端子對應於電晶體 714 的源極和汲極中的一個，開關 704 的第二端子對應於電晶體 714 的源極和汲極中的另一個，並且，開關 704 的第一端子與第二端子之間的導通或非導通（即，電晶體 714 的導通狀態或關閉狀態）由輸入到電晶體 714 的閘極的控制信號 RD 選擇。

[0268] 電晶體 709 的源極和汲極中的一個電連接到電容元件 708 的一對電極中的一個及電晶體 710 的閘極。在此，將連接部分稱為節點 M2。電晶體 710 的源極和汲極中的一個電連接到能夠供應低電源電位的佈線（例如，GND 線），而另一個電連接到開關 703 的第一端子（電晶體 713 的源極和汲極中的一個）。開關 703 的第二端子（電晶體 713 的源極和汲極中的另一個）電連接到開關 704 的第一端子（電晶體 714 的源極和汲極中的一個）。開關 704 的第二端子（電晶體 714 的源極和汲極中的另一個）電連接到能夠供應電源電位 VDD 的佈線。開關 703 的第二端子（電晶體 713 的源極和汲極中的另一個）、開關 704 的第一端子（電晶體 714 的源極和汲極中的一個）、邏輯元件 706 的輸入端子和電容元件 707 的一對電極中的一個是電連接著的。在此，將連接部分稱為節點 M1。可以對電容元件 707 的一對電極中的另一個輸入固

定電位。例如，可以輸入低電源電位（GND 等）或高電源電位（VDD 等）。電容元件 707 的一對電極中的另一個電連接到能夠供應低電源電位的佈線（例如，GND 線）。可以對電容元件 708 的一對電極中的另一個輸入固定電位。例如，可以輸入低電源電位（GND 等）或高電源電位（VDD 等）。電容元件 708 的一對電極中的另一個電連接到能夠供應低電源電位的佈線（例如，GND 線）。

[0269] 另外，當積極地利用電晶體或佈線的寄生電容等時，可以不設置電容元件 707 及電容元件 708。

[0270] 控制信號 WE 被輸入到電晶體 709 的第一閘極（第一閘極電極）。開關 703 及開關 704 的第一端子與第二端子之間的導通狀態或非導通狀態由與控制信號 WE 不同的控制信號 RD 選擇，當一個開關的第一端子與第二端子之間處於導通狀態時，另一個開關的第一端子與第二端子之間處於非導通狀態。

[0271] 對應於保持在電路 701 中的資料的信號被輸入到電晶體 709 的源極和汲極中的另一個。圖 22 示出從電路 701 輸出的信號被輸入到電晶體 709 的源極和汲極中的另一個的例子。由邏輯元件 706 使從開關 703 的第二端子（電晶體 713 的源極和汲極中的另一個）輸出的信號的邏輯值反轉而形成反轉信號，將其經由電路 720 輸入到電路 701。

[0272] 另外，雖然圖 22 示出從開關 703 的第二端子

(電晶體 713 的源極和汲極中的另一個) 輸出的信號藉由邏輯元件 706 及電路 720 被輸入到電路 701 的例子，但是本發明的一個方式不侷限於此。也可以不使從開關 703 的第二端子(電晶體 713 的源極和汲極中的另一個) 輸出的信號的邏輯值反轉而輸入到電路 701。例如，當在電路 701 內設置有節點並在該節點中保持使從輸入端子輸入的信號的邏輯值反轉的信號時，可以將從開關 703 的第二端子(電晶體 713 的源極和汲極中的另一個) 輸出的信號輸入到該節點。

[0273] 另外，圖 22 所示的電晶體 709 可以使用在實施方式 1 中說明的電晶體。另外，如實施方式 3 所說明那樣，電晶體 709 較佳為使用具有第二閘極(第二閘極電極)的電晶體。可以對第一閘極輸入控制信號 WE 並對第二閘極輸入控制信號 WE2。控制信號 WE2 可以是具有固定電位的信號。該固定電位例如可以選自接地電位 GND 和低於電晶體 709 的源極電位的電位等。控制信號 WE2 為具有用來控制電晶體 709 的臨界電壓的電位的信號，能夠降低電晶體 709 的  $I_{cut}$ 。另外，電晶體 709 也可以使用不具有第二閘極的電晶體。

[0274] 在圖 22 所示的用於記憶元件 700 的電晶體中，電晶體 709 以外的電晶體也可以使用其通道形成在由氧化物半導體以外的半導體構成的層或基板 1190 中的電晶體。例如，可以使用其通道形成在矽層或矽基板中的電晶體。或者，也可以作為用於記憶元件 700 的所有的電晶

體使用其通道形成在氧化物半導體膜中的電晶體。或者，記憶元件 700 也可以包括電晶體 709 以外的其通道形成在氧化物半導體膜中的電晶體，並且，作為剩下的電晶體使用其通道形成在由氧化物半導體以外的半導體構成的層或基板 1190 中的電晶體。

[0275] 圖 22 所示的電路 701 例如可以使用正反器。另外，邏輯元件 706 例如可以使用反相器或時脈反相器等。

[0276] 在本發明的一個方式的半導體裝置中，在不向記憶元件 700 供應電源電壓的期間，可以由設置在電路 702 中的電容元件 708 保持儲存在電路 701 中的資料。

[0277] 另外，其通道形成在氧化物半導體膜中的電晶體的關態電流極小。例如，其通道形成在氧化物半導體膜中的電晶體的關態電流比其通道形成在具有結晶性的矽中的電晶體的關態電流小得多。因此，藉由將這種電晶體用作電晶體 709，即使在不向記憶元件 700 供應電源電壓的情況下也可以長期間地儲存電容元件 708 中的信號。因此，記憶元件 700 在停止供應電源電壓的期間也可以保持儲存資料（資料）。

[0278] 另外，藉由設置開關 703 及開關 704，能夠使儲存元件進行預充電工作，因此可以縮短直到在再次開始供應電源電壓之後電路 701 重新保持原來的資料為止的時間。

[0279] 另外，在電路 702 中，由電容元件 708 保持

的信號被輸入到電晶體 710 的閘極。因此，在再次開始向記憶元件 700 供應電源電壓之後，可以將由電容元件 708 保持的信號轉換為電晶體 710 的狀態（導通狀態或關閉狀態），並從電路 702 讀出。因此，即使在對應於保持在電容元件 708 中的信號的電位有些變動的情況下，也可以準確地讀出原來的信號。

[0280] 藉由將這種記憶元件 700 用於處理單元所具有的暫存器或快取記憶體等記憶體裝置，可以防止記憶體裝置內的資料因停止電源電壓的供應而消失。另外，可以在再次開始供應電源電壓之後在短時間內恢復到停止供應電源之前的狀態。因此，在整個處理單元或構成處理單元的一個或多個邏輯電路中在短時間內也可以停止供應電源而抑制功耗。

[0281] 在本實施方式中，說明了將記憶元件 700 用於 CPU 的例子，但是也可以將記憶元件 700 應用於 DSP (Digital Signal Processor：數位訊號處理器)、定製 LSI、PLD (Programmable Logic Device：可程式邏輯裝置) 等的 LSI、RF-ID (Radio Frequency Identification：射頻識別)。

[0282] 注意，本實施方式可以與本說明書所示的其他實施方式適當地組合。

[0283]

### 實施方式 8

在本實施方式中，說明可以使用在實施方式 1 中說明

的電晶體、在實施方式 5、實施方式 6 中說明的記憶體裝置或在實施方式 7 中說明的 CPU 等（包括 DSP、定製 LSI、PLD、RF-ID）的電子裝置的例子。

[0284] 在實施方式 1 中說明的電晶體、在實施方式 5、實施方式 6 中說明的記憶體裝置或在實施方式 7 中說明的 CPU 等可以應用於各種電子裝置（包括遊戲機）。作為電子裝置，可以舉出電視機、顯示器等顯示裝置、照明設備、個人電腦、文字處理機、影像再現裝置、可攜式音訊播放機、收音機、磁帶錄音機、音響、電話機、無繩電話子機、行動電話機、車載電話、步話機、無線設備、遊戲機、計算器、可攜式資訊終端、電子筆記本、電子書閱讀器、電子翻譯器、聲音輸入器、攝影機、數位靜態照相機、電動剃鬚刀、IC 晶片、微波爐等高頻加熱裝置、電鍋、洗衣機、吸塵器、空調器等空調設備、洗碗機、烘碗機、乾衣機、烘被機、電冰箱、電冷凍箱、電冷藏冷凍箱、DNA 保存用冰凍器、輻射計數器（radiation counters）、透析裝置、X 射線診斷裝置等醫療設備等。另外，也可以舉出感煙探測器、感熱探測器、氣體警報裝置、防盜警報裝置等警報裝置。再者，還可以舉出工業設備諸如引導燈、信號機、傳送帶、電梯、自動扶梯、工業機器人、蓄電系統等。另外，利用使用燃料的發動機或來自非水類二次電池的電力藉由電動機推進的移動體等也包括在電子裝置的範疇內。作為上述移動體，例如可以舉出電動汽車（EV）、兼具內燃機和電動機的混合動力汽車

(HEV)、插電式混合動力汽車(PHEV)、使用履帶代替上述汽車的車輪的履帶式車輛、包括電動輔助自行車的電動自行車、摩托車、電動輪椅、高爾夫球車、小型或大型船舶、潛水艇、直升機、飛機、火箭、人造衛星、太空探測器、行星探測器、太空船。圖 23A 至圖 23C 示出這些電子裝置的一些具體例子。

[0285] 在圖 23A 所示的電視機 8000 中，外殼 8001 組裝有顯示部 8002，利用顯示部 8002 可以顯示影像，並且，從揚聲器部 8003 可以輸出聲音。上述實施方式所示的電晶體可以應用於用來使安裝在外殼 8001 中的顯示部 8002 工作的驅動電路或像素。

[0286] 作為顯示部 8002，可以使用液晶顯示裝置、在各個像素中具備有機 EL 元件等發光元件的發光裝置、電泳顯示裝置、DMD (Digital Micromirror Device：數位微鏡裝置)、PDP (Plasma Display Panel：電漿顯示面板) 等半導體顯示裝置。

[0287] 電視機 8000 也可以具備接收機及數據機等。電視機 8000 可以藉由利用接收機，接收一般的電視廣播。再者，藉由數據機機連接到有線或無線方式的通信網路，也可以進行單向（從發送者到接收者）或雙向（發送者和接收者之間或接收者之間等）的資訊通信。

[0288] 另外，電視機 8000 也可以具備用來進行資訊通信的 CPU8004、記憶體等。藉由將上述實施方式所示的電晶體、記憶體裝置或 CPU 用於 CPU8004 或記憶體，來

可以實現低功耗化。

[0289] 圖 23A 所示的警報裝置 8100 是住宅用火災警報器，是包括感煙或感熱檢測部 8102 和微型電腦 8101 的電子裝置的一個例子。微型電腦 8101 包括在上述實施方式中示出的電晶體、記憶體裝置或 CPU。

[0290] 另外，圖 23A 所示的包括室內機 8200 和室外機 8204 的空調器是包含在上述實施方式中示出的電晶體、記憶體裝置或 CPU 等的電子裝置的一個例子。明確而言，室內機 8200 具有外殼 8201、出風口 8202、CPU8203 等。在圖 23A 中，例示出 CPU8203 設置在室內機 8200 中的情況，但是 CPU8203 也可以設置在室外機 8204 中。或者，也可以在室內機 8200 和室外機 8204 中都設置有 CPU8203。藉由將在上述實施方式中示出的電晶體用於空調器的 CPU，可以實現低功耗化。

[0291] 另外，圖 23A 所示的電冷藏冷凍箱 8300 是包括在上述實施方式中示出的電晶體、記憶體裝置或 CPU 等的電子裝置的一個例子。明確而言，電冷藏冷凍箱 8300 包括外殼 8301、冷藏室門 8302、冷凍室門 8303 及 CPU8304 等。在圖 23A 中，CPU8304 設置在外殼 8301 的內部。藉由將在上述實施方式中示出的電晶體用於電冷藏冷凍箱 8300 的 CPU8304，可以實現低功耗化。

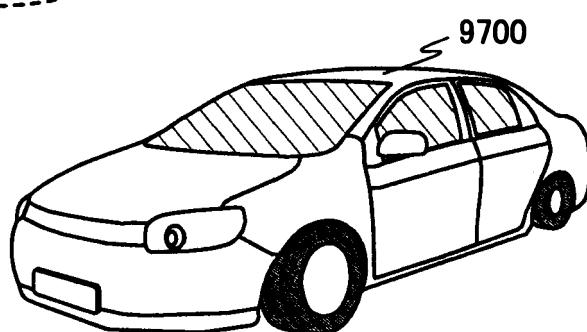

[0292] 圖 23B 和圖 23C 例示出電子裝置的一個例子的電動汽車。電動汽車 9700 安裝有二次電池 9701。二次電池 9701 的電力由電路 9702 調整輸出而供應到驅動裝置

9703。電路 9702 由具有未圖示的 ROM、RAM、CPU 等的處理裝置 9704 控制。藉由將在上述實施方式中示出的電晶體用於電動汽車 9700 的 CPU，可以實現低功耗化。

[0293] 驅動裝置 9703 包括直流電動機或交流電動機，或者將電動機和內燃機組合而構成。處理裝置 9704 根據電動汽車 9700 的駕駛員的操作數據（加速、減速、停止等）、行車資料（爬坡、下坡等資料，或者車輪所受到的負載資料等）等的輸入資料，向電路 9702 輸出控制信號。電路 9702 根據處理裝置 9704 的控制信號而調整從二次電池 9701 供應的電能並控制驅動裝置 9703 的輸出。當安裝交流電動機時，雖然未圖示，但是還安裝有將直流轉換為交流的逆變器。

[0294] 注意，本實施方式可以與本說明書所示的其他實施方式適當地組合。

## 實施例 1

[0295] 在本實施例中，作為實施例樣本製造與圖 6A 所示的電晶體 460 相同結構的電晶體，並觀察其剖面形狀。此外，對所製造的電晶體的電特性進行評估。

[0296] 首先，示出實施例樣本的製造方法。

[0297] 首先，在矽基板上形成成為基底絕緣膜的 300nm 厚的氧氮化矽（SiON）膜。氧氮化矽膜利用濺射法在如下條件下形成：使用氬和氧（氬:氧 = 25sccm:25sccm）的混合氛圍，壓力為 0.4Pa，電源功率（電源輸出）為

5.0kW，矽基板與靶材之間的距離為 60mm，基板溫度為 100°C。

[0298] 在對氮化矽膜的表面進行拋光處理之後，層疊形成 10nm 厚的第一氧化物膜與 40nm 厚的氧化物半導體膜。第一氧化物膜使用 In:Ga:Zn=1:3:2 (原子數比) 的氧化物靶材 (IGZO (132)) 利用濺射法在如下條件下形成：使用氬和氧 (氬:氧 = 30sccm:15sccm) 的混合氛圍，壓力為 0.4Pa，電源功率為 0.5kW，靶材與基板之間的距離為 60mm，基板溫度為 200°C。氧化物半導體膜使用 In:Ga:Zn=1:1:1 (原子數比) 的氧化物靶材 (IGZO (111)) 利用濺射法在如下條件下形成：使用氬和氧 (氬:氧 = 30sccm:15sccm) 的混合氛圍，壓力為 0.4Pa，電源功率為 0.5kW，靶材與基板之間的距離為 60mm，基板溫度為 300°C。第一氧化物膜和氧化物半導體膜以不暴露於大氣的方式連續地形成。

[0299] 接著，進行加熱處理。在氮氛圍下以 450°C 進行 1 小時的加熱處理，此後在氧氛圍下以 450°C 進行 1 小時的加熱處理。

[0300] 接著，在氧化物半導體膜上形成成為硬遮罩的 5nm 厚的鎢膜，進行蝕刻來形成硬遮罩。蝕刻利用 ICP (Inductively Coupled Plasma:感應耦合電漿) 蝕刻法進行。首先，在使用四氟化碳 ( $\text{CF}_4=100\text{sccm}$ ) 氣圍，電源功率為 2000W，偏壓功率為 50W，壓力為 0.67Pa 的條件下進行蝕刻，然後，在使用四氟化碳和氧 ( $\text{CF}_4:\text{O}_2=$

60sccm:40sccm) 的混合氛圍，電源功率為 1000W，偏壓功率為 25W，壓力為 2.0Pa 的條件下進行蝕刻。

[0301] 接著，對第一氧化物膜及氧化物半導體膜利用 ICP 蝕刻法在使用甲烷和氬 ( $\text{CH}_4:\text{Ar}=16\text{sccm}:32\text{sccm}$ ) 的混合氛圍，電源功率為 600W，偏壓功率為 100W，壓力為 1.0Pa，基板溫度為 70°C 的條件下進行蝕刻來加工為島狀的第一氧化物膜以及氧化物半導體膜。

[0302] 接著，在第一氧化物膜及氧化物半導體膜上形成 10nm 厚的成為源極電極及汲極電極的鎢 (W) 膜。鎢膜使用鎢靶材利用濺射法在如下條件下形成：使用氬 ( $\text{Ar}=80\text{sccm}$ ) 氛圍，壓力為 0.8Pa，電源功率（電源輸出）為 1.0kW，矽基板與靶材之間的距離為 60mm，基板溫度為 230°C。

[0303] 接著，在鎢膜上形成光阻遮罩進行蝕刻。蝕刻利用 ICP 蝏刻法進行。首先，在使用四氟化碳 ( $\text{CF}_4=100\text{sccm}$ ) 氛圍，電源功率為 2000W，偏壓功率為 50W，壓力為 0.67Pa 的條件下進行第一蝕刻，然後，在使用四氟化碳和氧 ( $\text{CF}_4:\text{O}_2=60\text{sccm}:40\text{sccm}$ ) 的混合氛圍，電源功率為 1000W，偏壓功率為 25W，壓力為 2.0Pa 的條件下進行第二蝕刻，由此形成源極電極及汲極電極。

[0304] 接著，在氧化物半導體膜、源極電極及汲極電極上形成 5nm 厚的第二氧化物膜。第二氧化物膜使用  $\text{In}:\text{Ga}:\text{Zn}=1:3:2$  (原子數比) 的氧化物靶材 (IGZO (132)) 利用濺射法在如下條件下形成：使用氬和氧

( 氩 : 氧 =30sccm:15sccm ) 的混合氛圍，壓力為 0.4Pa ，電源功率為 0.5kW ，靶材與基板之間的距離為 60mm ，基板溫度為 200°C 。

[0305] 接著，利用 CVD 法形成成為閘極絕緣膜的 10nm 厚的氧氮化矽膜。

[0306] 在氧氮化矽膜上利用濺射法形成 10nm 厚的氮化鈦膜，成膜條件為如下：使用氮 ( N<sub>2</sub>=50sccm ) 氣圍，壓力為 0.2Pa ，電源功率為 12kW ，靶材與基板之間的距離為 400mm ，基板溫度為常溫。在其上層疊 10nm 厚的鎢膜，成膜條件為如下：使用氩 ( Ar=100sccm ) 氣圍，壓力為 2.0Pa ，電源功率為 4kW ，靶材與基板之間的距離為 60mm ，基板溫度為 230°C 。

[0307] 接著，利用 ICP 蝕刻法對 10nm 厚的氮化鈦膜以及 10nm 厚的鎢膜的疊層進行蝕刻。首先，在使用氯、四氟化碳以及氧 ( Cl<sub>2</sub>:CF<sub>4</sub>:O<sub>2</sub>=45sccm:55sccm:55sccm ) 的混合氛圍，電源功率為 3000W ，偏壓功率為 110W ，壓力為 0.67Pa 的條件下進行第一蝕刻，然後在使用三氯化硼和氯 ( BC<sub>1</sub><sub>3</sub>:Cl<sub>2</sub>=150sccm:50sccm ) 的混合氛圍，電源功率為 1000W ，偏壓功率為 50W ，壓力為 0.67Pa 的條件下進行第二蝕刻，由此形成閘極電極。

[0308] 接著，利用 ICP 蝏刻法以閘極電極為遮罩對閘極絕緣膜與第二氧化物膜的疊層進行蝕刻。蝕刻在甲烷和氬 ( CH<sub>4</sub>:Ar=16sccm:32sccm ) 的混合氛圍下，電源功率為 600W ，偏壓功率為 100W ，壓力為 1.0Pa 、基板溫度為

70°C 的條件下進行。

[0309] 接著，在閘極電極上利用濺射法形成 20nm 厚的氧化鋁膜，在其上利用 CVD 法形成 150nm 厚的氮化矽膜。

[0310] 圖 10A 和圖 10B 示出藉由上述方法形成的實施例樣本的剖面 STEM 照片。圖 10A 為通道長度方向上的剖面圖，圖 10B 為通道寬度方向上的剖面圖。

[0311] 如圖 10B 所示，氧化物半導體膜的 IGZO (111) 的通道寬度方向上的剖面的端部帶弧形，呈現半圓狀。確認到這種結構提高形成在氧化物半導體膜上的第二氧化物膜、閘極絕緣膜以及閘極電極的覆蓋性，並防止斷開等的形成不良的發生。

[0312] 另外，所製造的電晶體的通道長度為 68nm，通道寬度為 34nm。

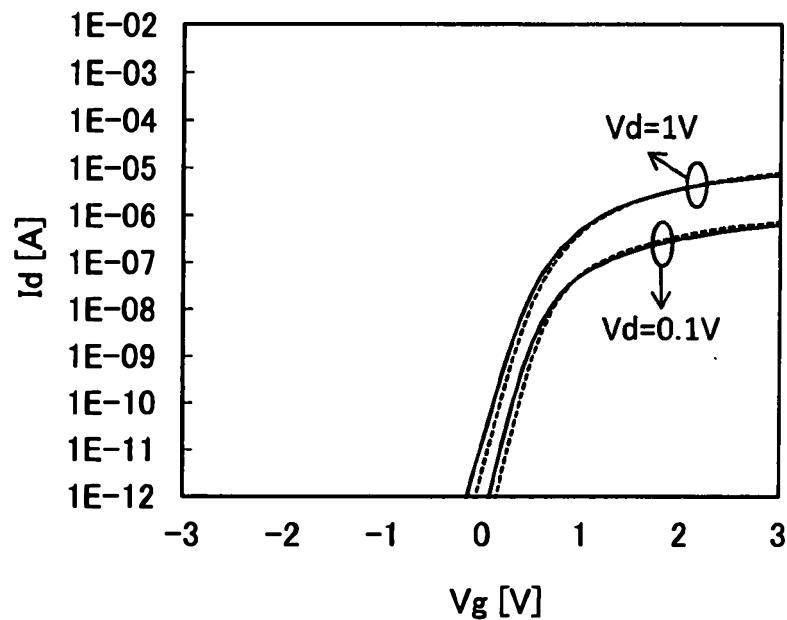

[0313] 接著，對所製造的電晶體的汲極電流 ( $I_d$ :[A]) 進行測定。其中，將汲極電壓 ( $V_d$ :[V]) 設定為 0.1V 或 1V，並將閘極電壓 ( $V_g$ :[V]) 從 -3V 掃描到 3V 而進行測定。圖 29 示出實施例電晶體的測定結果。在圖 29 中，實線示出汲極電壓 ( $V_d$ :[V]) 為 1V 時的測定結果，虛線示出汲極電壓 ( $V_d$ :[V]) 為 0.1V 時的測定結果，橫軸表示閘極電壓 ( $V_g$ :[V])，縱軸表示汲極電流 ( $I_d$ :[A])。另外，“汲極電壓 ( $V_d$ :[V])”是指以源極為基準時的汲極與源極之間的電位差，“閘極電壓 ( $V_g$ :[V])”是指以源極為基準時的閘極與源極之間的電位差。

[0314] 如圖 29 所示，在本實施例中製造的電晶體的通態電流在汲極電壓（ $V_d$ :[V]）為 1V 時為  $5.31\mu A$ 。汲極電壓為 0.1V 時的場效移動率為  $20.0\text{cm}^2/\text{Vs}$ 。汲極電壓為 1V 時的移位值（shift value）為 0.13A。在此，將移位值定義為汲極電流為  $1\times 10^{-12}\text{A}$  時的閘極電壓的值。另外，汲極電壓為 1V 時的臨界電壓為 0.65V。汲極電壓為 0.1V 時的 S 值為  $113.1\text{mV/dec}$ 。汲極電壓為 1V 時的關態電流為測定下限以下。

[0315] 上述結果示出本實施例的電晶體的電特性很高。

## 實施例 2

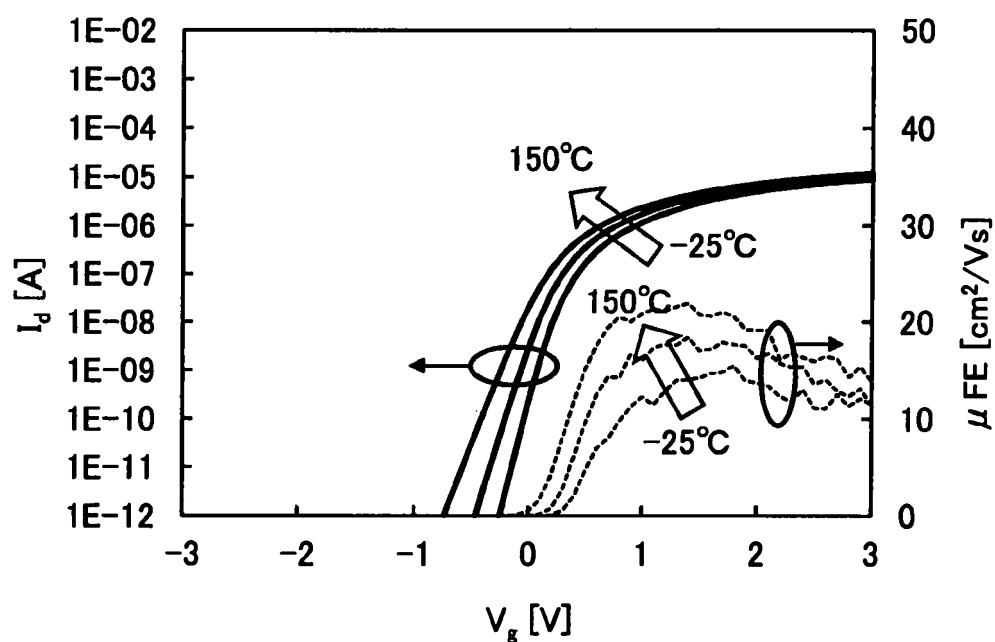

[0316] 在本實施例中，對在實施例 1 中製造的電晶體的溫度依賴性進行評估。

[0317] 對汲極電流（ $I_d$ :[A]）及場效移動率（ $\mu FE$ ）進行測定。在評估中，在  $-25^\circ\text{C}$ 、 $50^\circ\text{C}$  以及  $150^\circ\text{C}$  的三個條件下將汲極電壓（ $V_d$ :[V]）設定為 1V，並將閘極電壓（ $V_g$ :[V]）從 -3V 掃描到 3V 而進行測定。圖 30 示出實施例電晶體的測定結果。在圖 30 中，橫軸表示閘極電壓（ $V_g$ :[V]），左邊的縱軸表示汲極電流（ $I_d$ :[A]），右邊的縱軸表示場效移動率（ $\mu FE:\text{cm}^2/\text{Vs}$ ）。

[0318] 圖 30 示出在實施例 1 中製造的電晶體中，通態電流及場效移動率不易因溫度變化而變化。

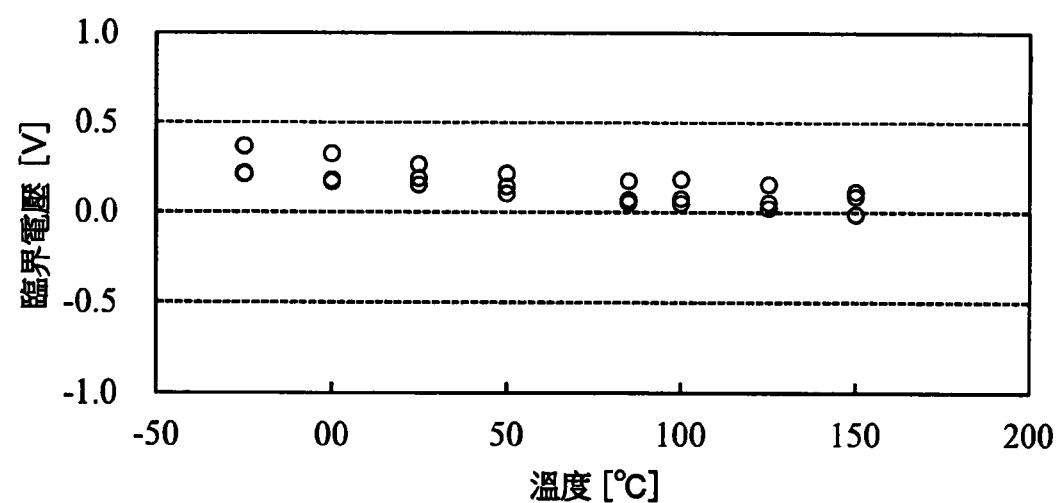

[0319] 圖 31 示出臨界電壓的溫度依賴性。

[0320] 確認到臨界電壓不易因溫度變化而變化。

[0321] 上述結果示出本實施例的電晶體具有溫度耐性。

### 實施例 3

[0322] 在本實施例中，對在實施例 1 中製造的電晶體的可靠性進行評估。

[0323] 在評估中，進行應力測試，其條件為如下：將源極電壓 ( $V_s:[V]$ ) 及汲極電壓 ( $V_d:[V]$ ) 設定為 0V，並以  $150^\circ\text{C}$  施加 -1.8V 的閘極電壓 1 小時，而測定汲極電流 ( $I_d:[A]$ )。圖 32A 示出實施例電晶體的測定結果。圖 32A 示出汲極電壓 ( $V_d:[V]$ ) 為 0.1V 及 1V 時的測定結果，橫軸示出閘極電壓 ( $V_g:[V]$ )，縱軸示出汲極電流 ( $I_d:[A]$ )。

[0324] 此外，進行應力測試，其條件為如下：將源極電壓 ( $V_s:[V]$ ) 及閘極電壓 ( $V_g:[V]$ ) 設定為 0V，並以  $150^\circ\text{C}$  施加 1.8V 的汲極電壓 1 小時，而測定汲極電流 ( $I_d:[A]$ )。圖 32B 示出實施例電晶體的測定結果。圖 32B 示出汲極電壓 ( $V_d:[V]$ ) 為 0.1V 及 1V 時的測定結果，橫軸表示閘極電壓 ( $V_g:[V]$ )，縱軸表示汲極電流 ( $I_d:[A]$ )。

[0325] 注意，圖式中的實線表示應力測試之前的測定結果，虛線表示應力測試之後的測定結果。如圖 32A 和圖 32B 所示，在實施例 1 中製造的電晶體中，汲極電壓

( $V_d$ :[V]) 為 1V 時的臨界電壓的變化量  $\Delta V_{th}$  在圖 32A 中為 0.03V，而在圖 32B 中為 0.11V，為很小的變化量。

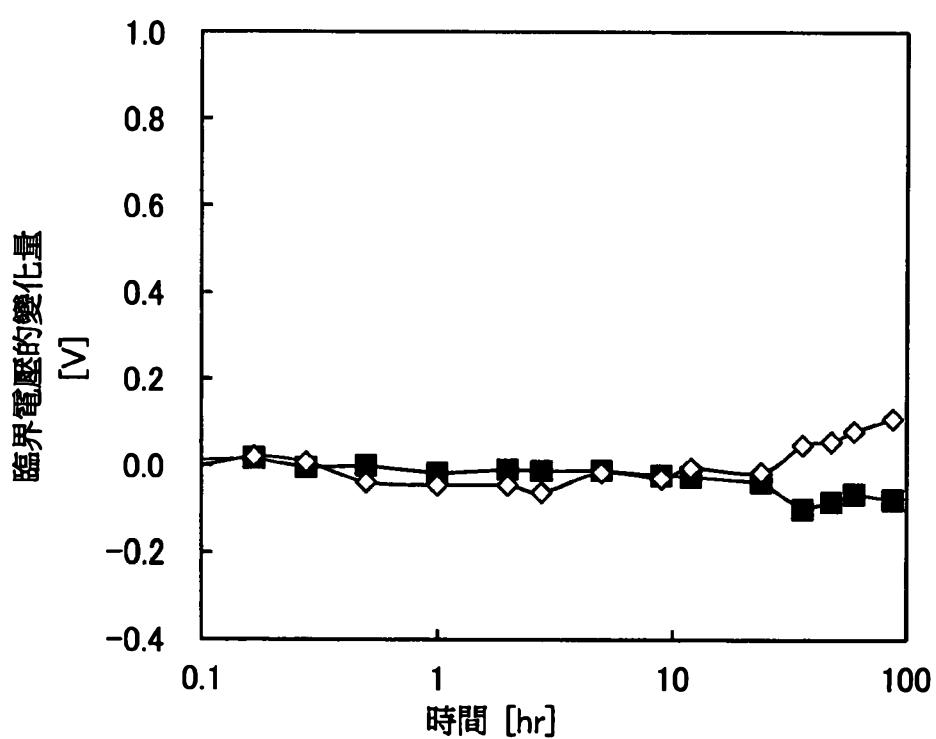

[0326] 另外，圖 33 中的方形示出將源極電壓 ( $V_s$ :[V]) 及閘極電壓 ( $V_g$ :[V]) 設定為 0V，並以 125°C 施加 1.8V 的汲極電壓 ( $V_d$ :[V]) 0.01 年 (87.6 小時)，而測定臨界電壓的變化量。

[0327] 另外，圖 33 中的菱形示出將源極電壓 ( $V_s$ :[V]) 及汲極電壓 ( $V_d$ :[V]) 設定為 0V，並以 125°C 施加 -1.8V 的閘極電壓 ( $V_g$ :[V]) 0.01 年 (87.6 小時)，而測定臨界電壓的變化量。

[0328] 圖 33 示出在實施例 1 中製造的電晶體中，即使經過 0.01 年之後，臨界電壓的變化量也很小。

[0329] 上述結果示出本實施例的電晶體具有很高的電穩定性。

#### 實施例 4

[0330] 在本實施例中，對在實施例 1 中製造的電晶體的電特性的通道寬度依賴性進行評估。

[0331] 首先，評估汲極電壓 ( $V_d$ :[V]) 為 1V 時的通態電流 ( $I_{on}$ :[A]) 的通道寬度依賴性。圖 34A 示出實施例電晶體的測定結果。在圖 34A 中，橫軸表示通道長度 [nm]，縱軸表示通態電流 ( $I_{on}$ :[A])。圖式中的菱形表示通道寬度為 40nm 時的測定結果，三角表示通道寬度為 100nm 時的測定結果，方形表示通道寬度為 500nm 時的測

定結果。

[0332] 圖 34A 示出即使通道寬度小，通態電流  $I_{on}$  也多。

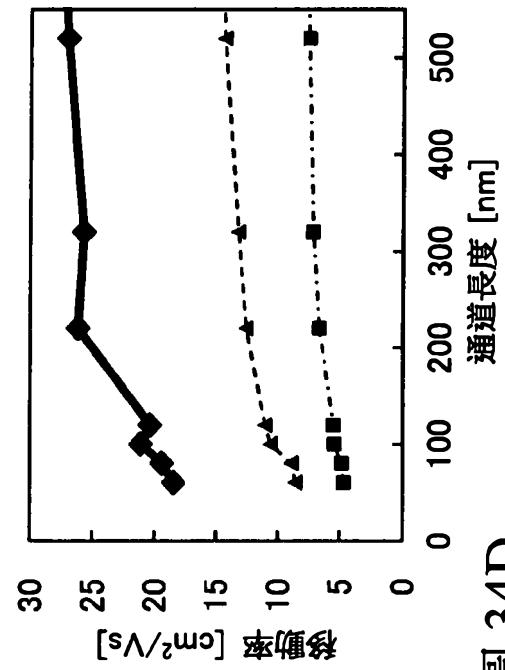

[0333] 接著，評估汲極電壓 ( $V_d$ :[V]) 為 0.1V 時的場效移動率的通道寬度依賴性。圖 34B 示出實施例電晶體的測定結果。在圖 34B 中，橫軸表示通道長度 [nm]，縱軸表示場效移動率 ( $\mu FE:cm^2/Vs$ )。圖式中的菱形表示通道寬度為 40nm 時的測定結果，三角表示通道寬度為 100nm 時的測定結果，方形表示通道寬度為 500nm 時的測定結果。

[0334] 圖 34B 示出通道寬度越小，移動率越高。

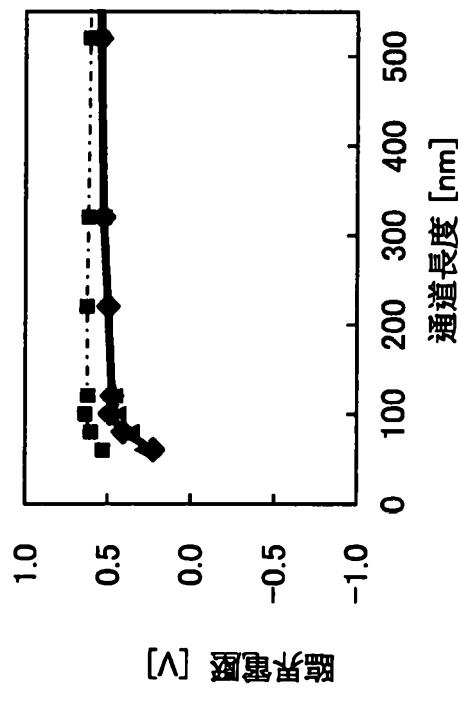

[0335] 接著，評估汲極電壓 ( $V_d$ :[V]) 為 1V 時的臨界電壓的通道寬度依賴性。圖 34C 示出實施例電晶體的測定結果。在圖 34C 中，橫軸表示通道長度 [nm]，縱軸表示臨界電壓 ( $V_{th}$ :[V])。圖式中的菱形表示通道寬度為 40nm 時的測定結果，三角表示通道寬度為 100nm 時的測定結果，方形表示通道寬度為 500nm 時的測定結果。

[0336] 圖 34C 示出臨界電壓的變化不大。

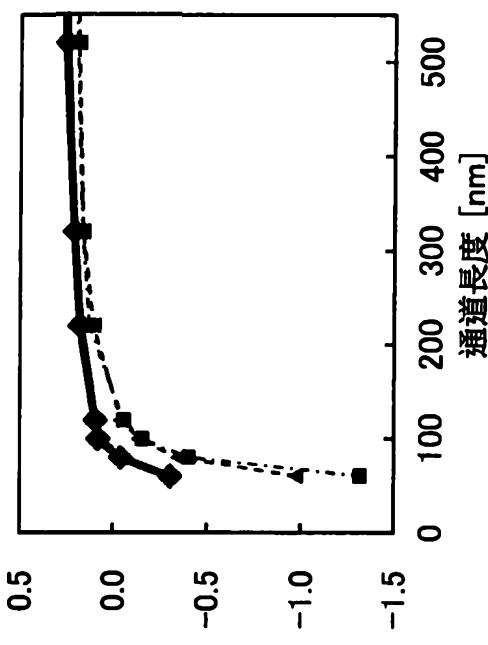

[0337] 接著，評估汲極電壓 ( $V_d$ :[V]) 為 1V 時的移位值的通道寬度依賴性。移位值是指上升電壓 (rising voltage)，被定義為汲極電流 ( $I_d$ :[A]) 為  $1E^{-12}A$  時的閘極電壓 ( $V_g$ :[V])。圖 34D 示出實施例電晶體的測定結果。在圖 34D 中，橫軸表示通道長度 [nm]，縱軸表示移位值 [V]。圖式中的菱形表示通道寬度為 40nm 時的測定結

果，三角表示通道寬度為 100nm 時的測定結果，方形表示通道寬度為 500nm 時的測定結果。

[0338] 圖 34D 示出通道寬度越小，移位值的變化越小。

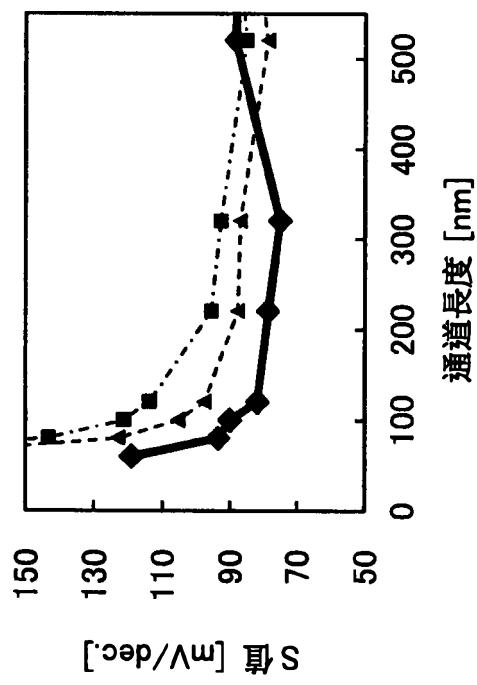

[0339] 接著，評估汲極電壓 ( $V_d$ :[V]) 為 0.1V 時的 S 值的通道寬度依賴性。圖 35A 示出實施例電晶體的測定結果。在圖 35A 中，橫軸表示通道長度 [nm]，縱軸表示 S 值 [mV/dec.]。圖式中的菱形表示通道寬度為 40nm 時的測定結果，三角表示通道寬度為 100nm 時的測定結果，方形表示通道寬度為 500nm 時的測定結果。

[0340] 圖 35A 示出通道寬度越小，S 值越低。

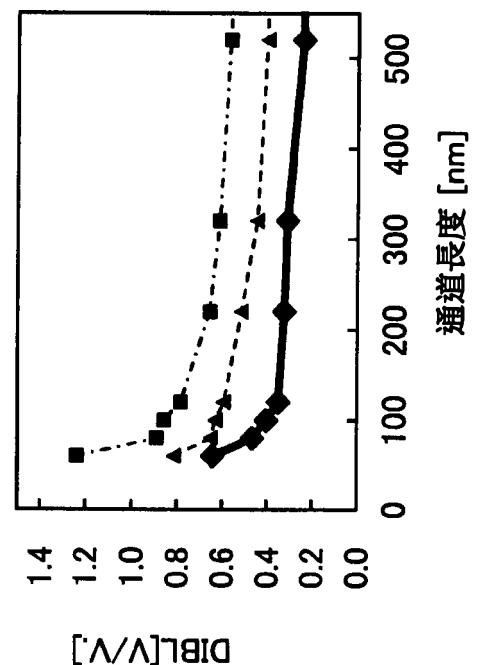

[0341] 接著，評估 DIBL 的通道寬度依賴性。DIBL 為從汲極電壓 ( $V_d$ :[V]) 為 0.1V 時的臨界電壓減去汲極電壓 ( $V_d$ :[V]) 為 1V 時的臨界電壓，並除以 0.9 而獲得的值。圖 35B 示出實施例電晶體的測定結果。在圖 35B 中，橫軸表示通道長度 [nm]，縱軸表示 DIBL 值 [V/V.]。圖式中的菱形表示通道寬度為 40nm 時的測定結果，三角表示通道寬度為 100nm 時的測定結果，方形表示通道寬度為 500nm 時的測定結果。

[0342] 圖 35B 示出通道寬度越小，DIBL 越低。

[0343] 上述結果示出在本實施例的電晶體中，通道寬度越小，電特性越高。

## 實施例 5

[0344] 在本實施例中，作為實施例樣本製造具有與圖 6A 所示的電晶體 460 相同結構的電晶體，並進行電特性的評估。

[0345] 首先，示出實施例樣本的製造方法。

[0346] 實施例樣本的製造方法可以參照實施例 1。注意，僅第一氧化物膜與實施例 1 不同，本實施例的第一氧化物膜的厚度為 10nm，使用 In:Ga:Zn=1:3:4（原子數比）的氧化物靶材（IGZO（134））利用濺射法在如下條件下形成：使用氰和氧（氰：氧 = 30sccm:15sccm）的混合氛圍，壓力為 0.4Pa，電源功率為 0.5kW，靶材與基板之間的距離為 60mm，基板溫度為 200°C。

[0347] 本實施例的電晶體的通道長度為 70nm，通道寬度為 40nm。

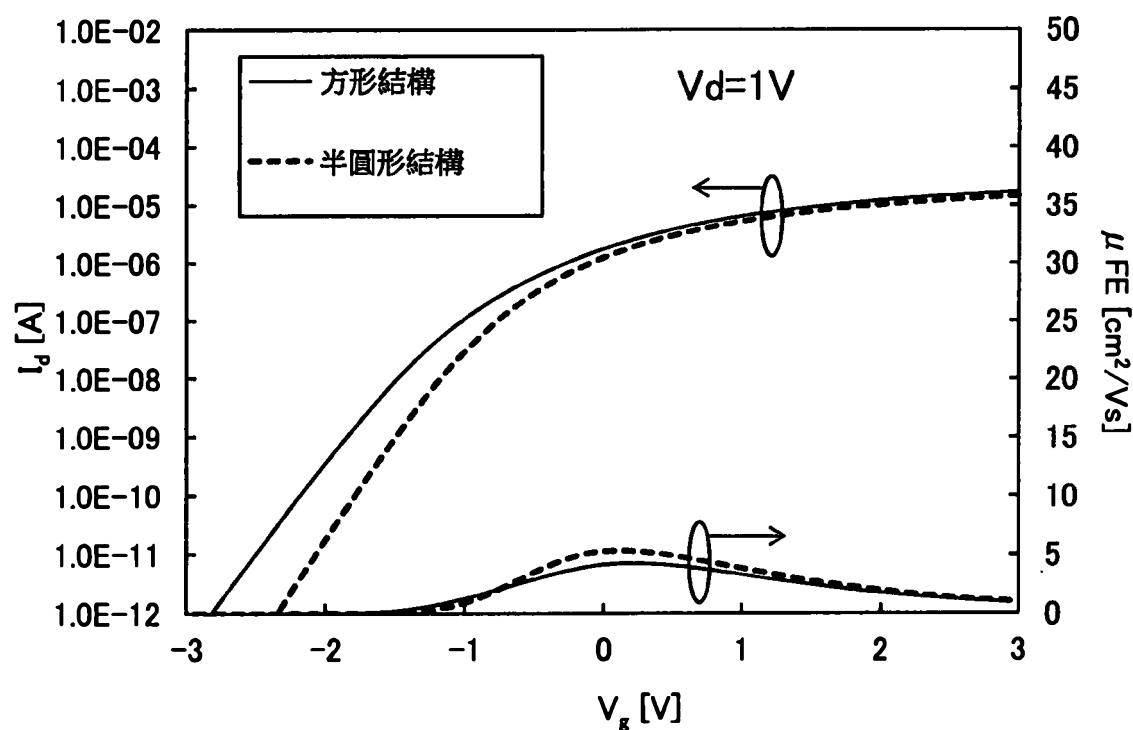

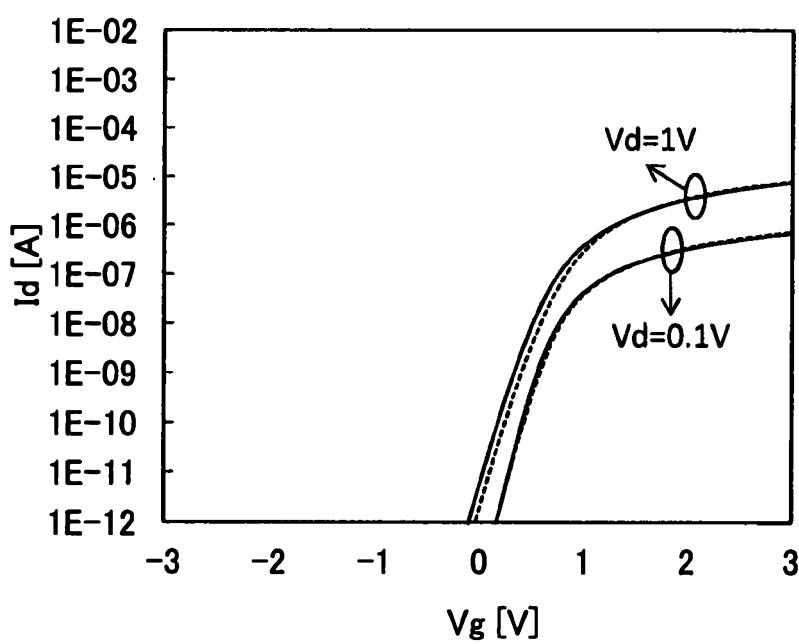

[0348] 接著，對所製造的電晶體的汲極電流（ $I_d$ :[A]）進行測定。其中，將汲極電壓（ $V_d$ :[V]）設定為 1V，並將閘極電壓（ $V_g$ :[V]）從 -3V 掃描到 3V 而進行測定。另外，測定汲極電壓為 0.1V 時的場效移動率（ $\mu FE$ ）。圖 11 示出實施例電晶體的測定結果。圖 11 示出汲極電壓（ $V_d$ :[V]）為 1V 時的測定結果，橫軸表示閘極電壓（ $V_g$ :[V]），左邊的縱軸表示汲極電流（ $I_d$ :[A]），右邊的縱軸表示場效移動率（ $\mu FE:cm^2/Vs$ ）。

[0349] 如圖 11 所示，在本實施例中製造的電晶體的通態電流在汲極電壓（ $V_d$ :[V]）為 1V 時為 5.08μA。汲極電壓為 0.1V 時的場效移動率為 17.0cm<sup>2</sup>/Vs。

[0350] 上述結果示出本實施例的電晶體的電特性很高。

## 實施例 6

[0351] 在本實施例中，作為實施例樣本製造具有與圖 6A 所示的電晶體 460 相同結構的電晶體，並對電特性的通道寬度依賴性進行評估。

[0352] 首先，示出實施例樣本的製造方法。

[0353] 實施例樣本的製造方法可以參照實施例 1。製造如下三個樣本：樣本 A，樣本 A 為在實施例 1 中使用的樣本（第一氧化物膜為 10nm 厚的 IGZO（132），氧化物半導體膜為 40nm 厚的 IGZO（111））；樣本 B，樣本 B 為在實施例 5 中使用的樣本（第一氧化物膜為 10nm 厚的 IGZO（134），氧化物半導體膜為 40nm 厚的 IGZO（111））；樣本 C，其中第一氧化物膜為 20nm 厚的 IGZO（132），氧化物半導體膜為 15nm 厚的 IGZO（111），其他結構與樣本 A 相同。注意，在樣本 C 中，第一氧化物膜使用  $In:Ga:Zn=1:3:2$ （原子數比）的氧化物靶材（IGZO（132））利用濺射法在如下條件下形成：使用氬和氧（氬:氧 = 30sccm:15sccm）的混合氛圍，壓力為 0.4Pa，電源功率為 0.5kW，靶材與基板之間的距離為 60mm，基板溫度為 200°C。氧化物半導體膜使用  $In:Ga:Zn=1:1:1$ （原子數比）的氧化物靶材（IGZO（111））利用濺射法在如下條件下形成：使用氬和氧（氬:氧 = 30sccm:15sccm）的混

合氛圍，壓力為  $0.4\text{Pa}$ ，電源功率為  $0.5\text{kW}$ ，靶材與基板之間的距離為  $60\text{mm}$ ，基板溫度為  $300^\circ\text{C}$ 。

[0354] 本實施例的電晶體的通道長度為  $40\text{nm}$ 。

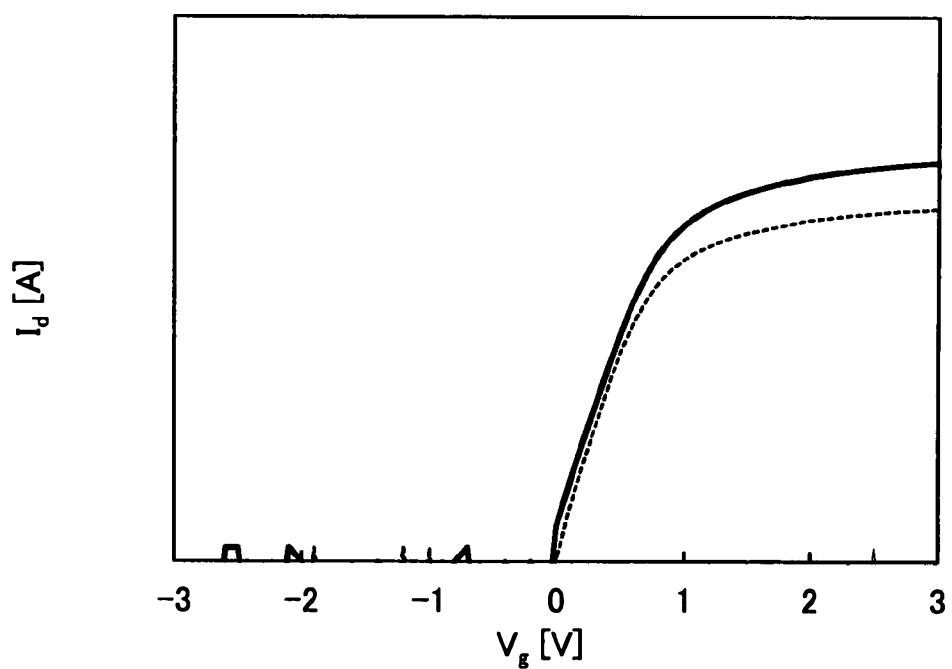

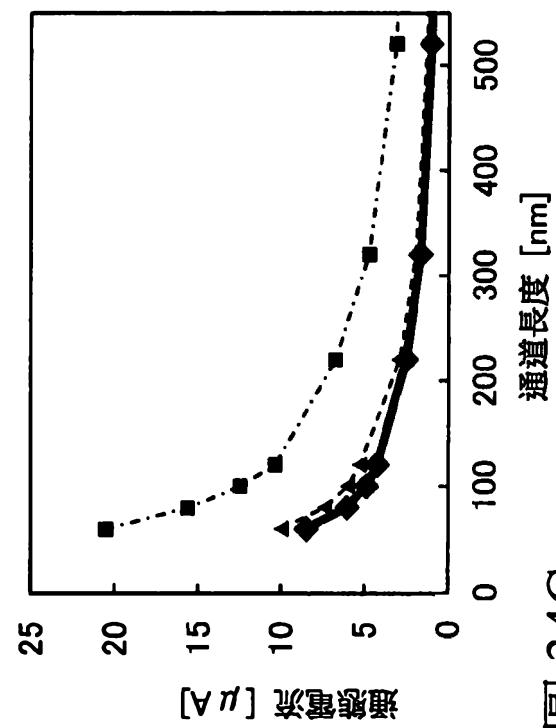

[0355] 接著，評估汲極電壓 ( $V_d:[\text{V}]$ ) 為  $1\text{V}$  時的通態電流 ( $I_{on}:[\text{A}]$ ) 的通道寬度  $W$  依賴性。注意，在本實施例中，通態電流是閘極電壓為臨界電壓加  $1\text{V}$  時的電流值。圖 12 和圖 13A 至圖 13C 示出實施例電晶體的測定結果。在圖 12 和圖 13A 至圖 13C 中，橫軸表示通道寬度 ( $W:[\text{nm}]$ )，縱軸表示通態電流 ( $I_{on}:[\text{A}]$ )。

[0356] 圖 12 示出在氧化物半導體膜的厚度為  $15\text{nm}$  的樣本 C 中，通道寬度  $W$  越小，通態電流  $I_{on}$  越小。另一方面，在氧化物半導體膜的厚度為  $40\text{nm}$  的樣本 A 和樣本 B 中，即使通道寬度  $W$  越小，通態電流  $I_{on}$  也不減少。

[0357] 這可以被認為是因為：在通道寬度小的情況下，較厚的氧化物半導體膜增加在橫方向上施加的閘極電極的電場，而增加通態電流  $I_{on}$ 。

[0358] 另外，圖 13A 示出樣本 A 的電晶體的特性，圖 13B 示出樣本 B 的電晶體的特性，圖 13C 示出樣本 C 的電晶體的特性。圖 13A 至圖 13C 示出不管在樣本 A、樣本 B、樣本 C 的哪一個條件下，通道寬度  $W$  越大，通態電流  $I_{on}$  越大。

## 實施例 7

[0359] 在本實施例中，作為實施例樣本製造與圖 6A

所示的電晶體 460 相同結構的電晶體，並對所製造的電晶體的電特性進行評估。

[0360] 首先，示出實施例樣本的製造方法。

[0361] 首先，在矽基板上形成用作基底絕緣膜的 300nm 厚的氧氮化矽（SiON）膜。氧氮化矽膜利用濺射法在如下條件下形成：使用氬和氧（氬:氧 = 25sccm:25sccm）的混合氛圍，壓力為 0.4Pa，電源功率（電源輸出）為 5.0kW，矽基板與靶材之間的距離為 60mm，基板溫度為 100°C。

[0362] 在對氧氮化矽膜的表面進行拋光處理之後，層疊形成 20nm 厚的第一氧化物膜與 20nm 厚的氧化物半導體膜。第一氧化物膜使用 In:Ga:Zn=1:3:4（原子數比）的氧化物靶材（IGZO（134））利用濺射法在如下條件下形成：使用氬和氧（氬:氧 = 40sccm:5sccm）的混合氛圍，壓力為 0.4Pa，電源功率為 0.5kW，靶材與基板之間的距離為 60mm，基板溫度為 200°C。氧化物半導體膜使用 In:Ga:Zn=1:1:1（原子數比）的氧化物靶材（IGZO（111））利用濺射法在如下條件下形成：使用氬和氧（氬:氧 = 30sccm:15sccm）的混合氛圍，壓力為 0.4Pa，電源功率為 0.5kW，靶材與基板之間的距離為 60mm，基板溫度為 300°C。第一氧化物膜和氧化物半導體膜以不暴露於大氣的方式連續地形成。

[0363] 接著，進行加熱處理。在氮氛圍下以 450°C 進行 1 小時的加熱處理，此後在氧氛圍下以 450°C 進行 1 小

時的加熱處理。

[0364] 接著，在氧化物半導體膜上形成 150nm 厚的成為源極電極及汲極電極的鎢膜。鎢膜使用鎢靶材利用濺射法在如下條件下形成：使用氬（氬 = 80sccm）氛圍，壓力為 0.8Pa，電源功率（電源輸出）為 1.0kW，矽基板與靶材之間的距離為 60mm，基板溫度為 230°C。

[0365] 接著，在鎢膜上形成光阻遮罩進行蝕刻。蝕刻利用 ICP 蝕刻法進行。首先，在使用氯、四氟化碳以及氧 ( $\text{Cl}_2:\text{CF}_4:\text{O}_2=45\text{sccm}:55\text{sccm}:55\text{sccm}$ ) 的混合氛圍，電源功率為 3000W，偏壓功率為 110W，壓力為 0.67Pa 的條件下進行第一蝕刻，然後，在使用氧 ( $\text{O}_2=100\text{sccm}$ ) 氛圍，電源功率為 2000W，偏壓功率為 0W，壓力為 3.0Pa 的條件下進行第二蝕刻，在使用氯、四氟化碳以及氧 ( $\text{Cl}_2:\text{CF}_4:\text{O}_2=45\text{sccm}:55\text{sccm}:55\text{sccm}$ ) 的混合氛圍，電源功率為 3000W，偏壓功率為 110W，壓力為 0.67Pa 的條件下進行第三蝕刻，由此形成源極電極及汲極電極。

[0366] 接著，在氧化物半導體膜上形成光阻遮罩，對第一氧化物膜及氧化物半導體膜利用 ICP 蝕刻法在三氯化硼 ( $\text{BCl}_3=80\text{sccm}$ ) 氛圍下，電源功率為 450W，偏壓功率為 100W，壓力為 1.2Pa，基板溫度為 70°C 的條件下進行蝕刻來加工為島狀的第一氧化物膜以及氧化物半導體膜。

[0367] 接著，在氧化物半導體膜、源極電極及汲極電極上形成 5nm 厚的第二氧化物膜。第二氧化物膜使用

In:Ga:Zn=1:3:2 (原子數比) 的氧化物靶材 (IGZO (132)) 利用濺射法在如下條件下形成：使用氬和氧 (氬:氧 = 30sccm:15sccm) 的混合氛圍，壓力為 0.4Pa，電源功率為 0.5kW，靶材與基板之間的距離為 60mm，基板溫度為 200°C。

[0368] 接著，利用 CVD 法形成成為閘極絕緣膜的 20nm 厚的氮化矽膜。

[0369] 在氮化矽膜上利用濺射法形成 30nm 厚的氮化鉭膜，成膜條件為如下：使用氮化鉭及氬 (TaN:Ar=50sccm:10sccm) 的氛圍，壓力為 0.6Pa，電源功率為 1kW，靶材與基板之間的距離為 60mm，基板溫度為常溫。在其上層疊 135nm 厚的鎢膜，成膜條件為如下：使用氬 (Ar=100sccm) 氛圍，壓力為 2.0Pa，電源功率為 4kW，靶材與基板之間的距離為 60mm，基板溫度為 230°C。

[0370] 接著，利用 ICP 蝕刻法對 30nm 厚的氮化鉭膜以及 135nm 厚的鎢膜的疊層進行蝕刻。首先，在使用氯、四氟化碳以及氧 (Cl<sub>2</sub>:CF<sub>4</sub>:O<sub>2</sub>=45sccm:55sccm:55sccm) 的混合氛圍，電源功率為 3000W，偏壓功率為 110W，壓力為 0.67Pa 的條件下進行第一蝕刻，然後在使用氯 (Cl<sub>2</sub>=100sccm) 氛圍，電源功率為 1000W，偏壓功率為 50W，壓力為 0.67Pa 的條件下進行第二蝕刻，由此形成閘極電極。

[0371] 接著，利用 ICP 蝏刻法對閘極絕緣膜與第二

氧化物膜的疊層進行蝕刻。蝕刻在三氯化硼( $\text{BCl}_3=80\text{sccm}$ )氛圍下，電源功率為450W，偏壓功率為100W，壓力為1.2Pa、基板溫度為70°C的條件下進行。

[0372] 接著，在閘極電極上利用濺射法形成140nm厚的氧化鋁膜，在其上利用CVD法形成300nm厚的氮氧化矽膜。

[0373] 所製造的電晶體的通道長度為 $0.48\mu\text{m}$ ，通道寬度為 $0.5\mu\text{m}$ 。

[0374] 接著，對所製造的電晶體的溫度依賴性進行評估。

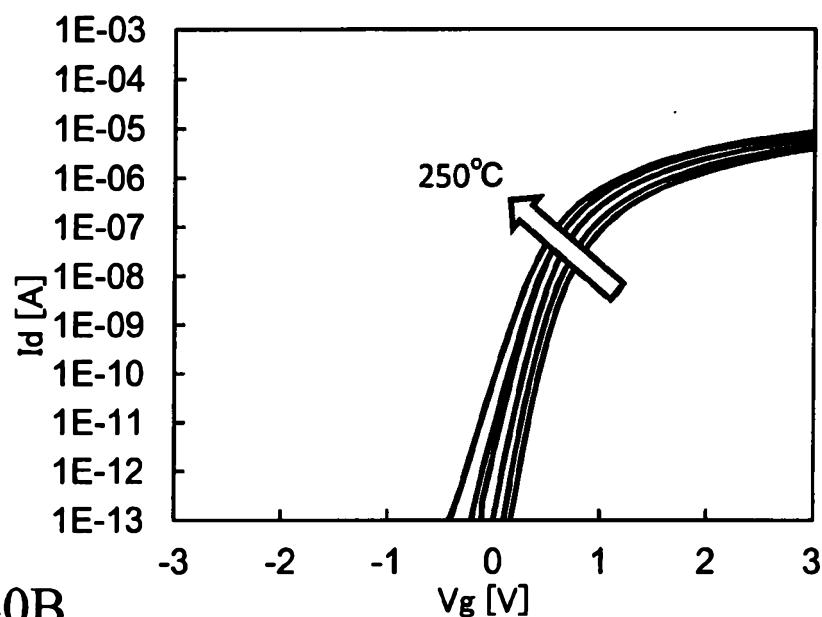

[0375] 在測定中，在25°C、50°C、100°C、150°C、200°C以及250°C的六個條件下將汲極電壓( $V_d:[\text{V}]$ )設定為1V，並將閘極電壓( $V_g:[\text{V}]$ )從-3V掃描到3V而測定每通道寬度 $1\mu\text{m}$ 的汲極電流( $I_d:[\text{A}]$ )。圖40A示出實施例電晶體的測定結果。在圖40A中，橫軸表示閘極電壓( $V_g:[\text{V}]$ )，縱軸表示汲極電流( $I_d:[\text{A}]$ )。在圖式中，溫度向箭頭所示的方向提高。

[0376] 圖40A示出在本實施例中製造的電晶體中，通態電流不易因溫度變化而變化。

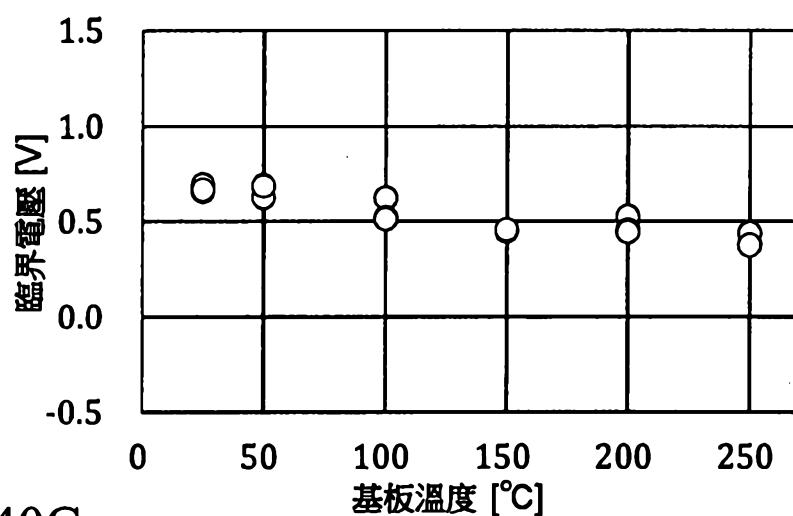

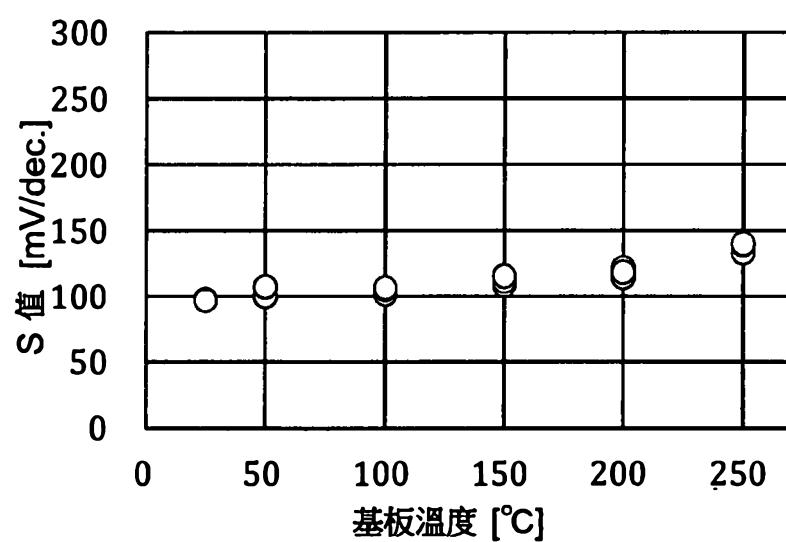

[0377] 圖40B和圖40C示出臨界電壓及S值的溫度依賴性。

[0378] 確認到臨界電壓及S值不易因溫度變化而變化。

[0379] 上述結果示出本實施例的電晶體具有溫度耐

性。

## 實施例 8

[0380] 在本實施例中，對氧化物半導體膜的形狀對電特性的影響進行評估。

[0381] 首先，對電晶體的結構進行說明。

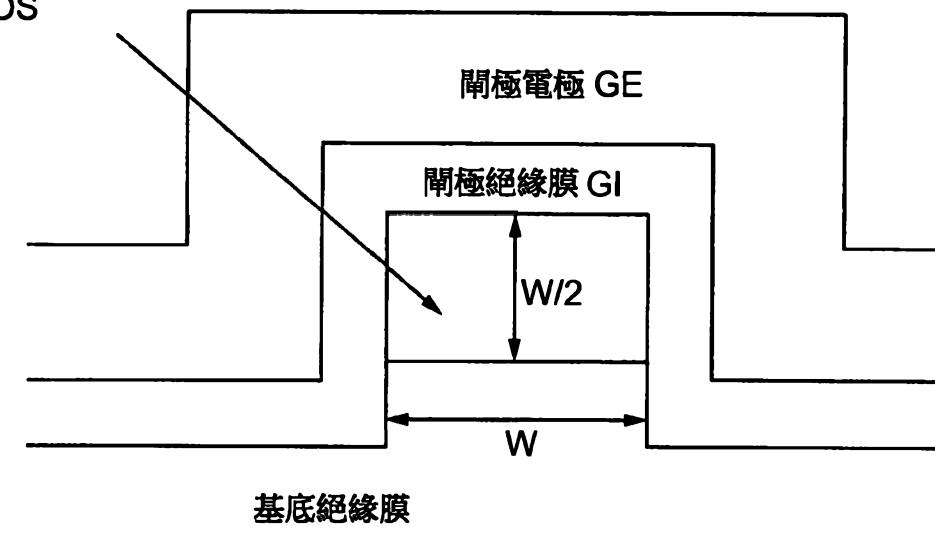

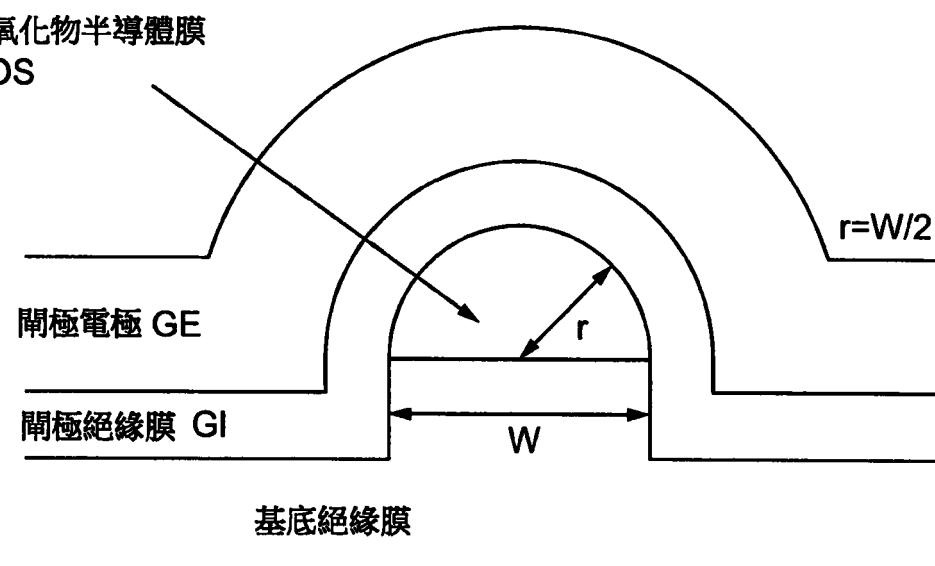

[0382] 圖 25A 為氧化物半導體膜的上端部帶角形的電晶體（以下，也稱為方形結構的電晶體）的通道寬度方向上的剖面圖。圖式中的  $W$  表示通道寬度，氧化物半導體膜的厚度為  $W/2$ 。

[0383] 圖 25B 為本發明的一個方式的結構的氧化物半導體膜的上端部帶弧形的電晶體（以下，也稱為半圓形結構的電晶體）的通道寬度方向上的剖面圖。圖式中的  $r$  表示曲率半徑， $r=W/2$ 。

[0384] 在方形結構中，實效通道寬度為側面和頂面的總和的  $2W$ ，在半圓形結構中，實效通道寬度為半圓的圓周的  $\pi r=\pi W/2=1.57W$ ，此時的實效通道寬度  $W$  的比率為 0.785。

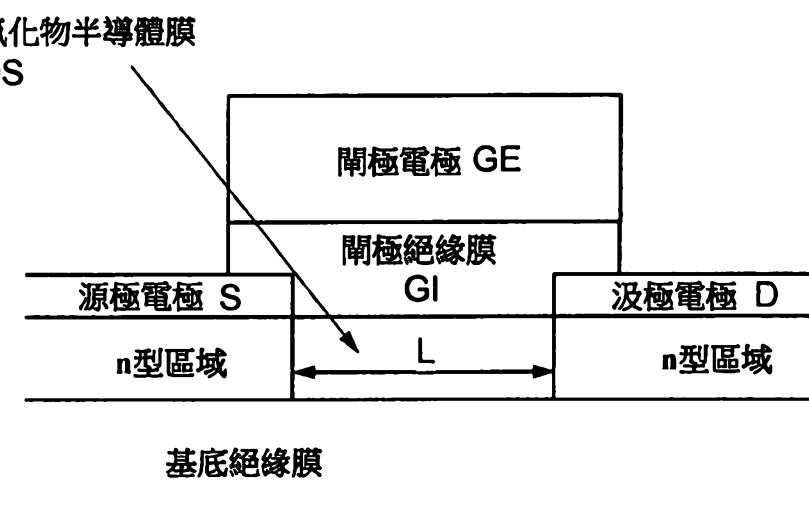

[0385] 圖 26 示出圖 25A 和圖 25B 所示的電晶體的通道長度方向上的剖面圖。圖式中的  $L$  表示通道長度。

[0386] 接著，對計算條件進行說明。

[0387] 使用 synopsys 公司的 Sentaurus，並在表 1 所示的條件下進行計算。

[0388]

[表 1]

|                    |                         |                          |

|--------------------|-------------------------|--------------------------|

| 尺寸                 | 通道長度 L                  | 40nm                     |

|                    | 通道寬度 W                  | 40nm                     |

| GI (閘極絕緣膜)         | 相對介電常數                  | 4.1                      |

|                    | 厚度                      | 10nm                     |

| OS<br>(氧化物半導體膜)    | 組成                      | IGZO (111)               |

|                    | 電子親和力                   | 4.6eV                    |

|                    | Eg                      | 3.2eV                    |

|                    | 相對介電常數                  | 15                       |

|                    | 通道部分的施體密度               | 6.60E-9cm <sup>-3</sup>  |

|                    | 源極電極、汲極電極之下<br>的部分的施體密度 | 5.00E+18cm <sup>-3</sup> |

|                    | 電子移動率                   | 15cm <sup>2</sup> /Vs    |

|                    | 電洞移動率                   | 0.01cm <sup>3</sup> /Vs  |

|                    | Nc                      | 5.00E+18cm <sup>-3</sup> |

| 基底絕緣膜              | Nv                      | 5.00E+18cm <sup>-3</sup> |

|                    | 厚度                      | 20nm                     |

| GE (閘極電極)          | 相對介電常數                  | 4.1                      |

|                    | 厚度                      | 400nm                    |

| S/D<br>(源極電極/汲極電極) | 功函數                     | 5eV                      |

|                    | 功函數                     | 4.6eV                    |

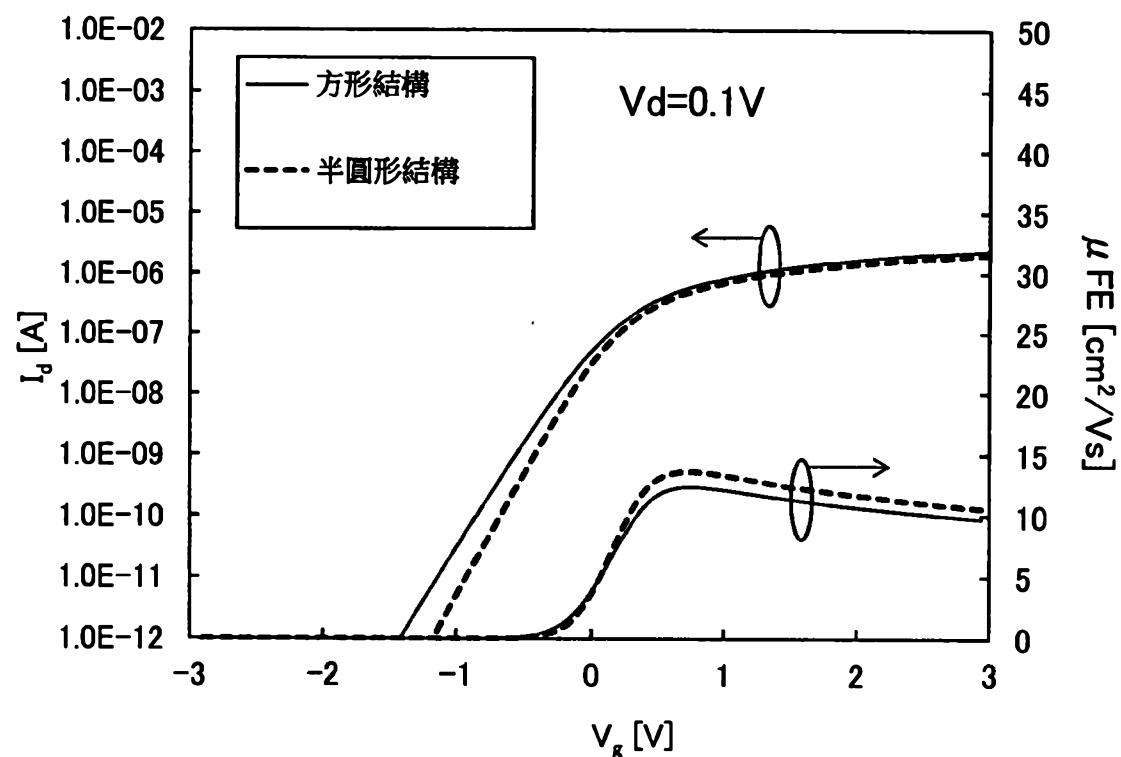

[0389] 圖 27 示出汲極電壓 ( $V_d$ :[V]) 為 0.1V 時的  $I_d$ - $V_g$  特性及移動率，圖 28 示出汲極電壓 ( $V_d$ :[V]) 為 1V 時的  $I_d$ - $V_g$  特性及移動率。

[0390] 圖 27 及圖 28 示出與方形結構相比，在半圓

形結構的  $I_d$ - $V_g$  特性中上升電壓急劇上升。另外，半圓形結構的利用實效通道寬度  $W$  計算出的移動率比方形結構高。

[0391] 另外，表 2 示出利用圖 27 及圖 28 獲得的各種特性值的比較。

[0392]

[表 2]

|                                     | 方形結構                    | 半圓形結構                   |

|-------------------------------------|-------------------------|-------------------------|

| 臨界電壓 ( $V_d=1$ )                    | -0.518V                 | -0.443V                 |

| 通態電流<br>( $V_d=1$ , $V_g$ =臨界電壓+3V) | 18.4 $\mu$ A            | 16.4 $\mu$ A            |

| S 值 ( $V_d=0.1$ )                   | 198mV/dec               | 177mV/dec               |

| 移動率 ( $V_d=0.1$ )                   | 14.3cm <sup>2</sup> /Vs | 15.6cm <sup>2</sup> /Vs |

[0393] 表 2 表示半圓形結構的通態電流以外的特性比方形結構好。另外，通態電流的比率也是 0.892，比實效通道寬度  $W$  的比率 0.785 大。換而言之，在半圓形結構中，電子更容易被移動到通道部。

[0394] 在半圓形結構中電子更容易被移動到通道部的原因之一是實效通道寬度  $W$  與通態電流的關係。可認為通態電流與閘極絕緣膜的電容（以下，稱為 GI 電容）成正比，但是，半圓形結構中的 GI 電容不能由平行板的形式表示，被近似為以下式。

[0395]

[算式 1]

$$C_r = \varepsilon \frac{\pi}{\ln(1 + \frac{t_{GI}}{t_{OS}})}$$

[0396]  $C_r$  表示半圓形結構的單位通道長度的 GI 電容， $\varepsilon$  表示閘極絕緣膜的介電常數， $t_{GI}$  表示閘極絕緣膜的厚度， $t_{OS}$  表示氧化物半導體膜的厚度。

[0397] 在半圓形結構的情況下，GI 電容不與實效通道寬度  $W(\pi t_{OS})$  成正比，不能與上述同樣地利用實效通道寬度  $W$  的比率比較通態電流。

[0398] 另一方面，方形結構的單位通道長度的 GI 電容被近似為以下式。

[0399]

[算式 2]

$$C_s = \varepsilon \frac{4t_{OS}}{t_{GI}}$$

[0400] 為了算出通態電流，需要利用 GI 電容的比率，由算式 2 求出的方形結構的 GI 電容與由算式 1 求出的半圓形結構的 GI 電容的比率為  $C_r/C_s=0.968$  左右，比實效通道寬度  $W$  的比率 0.785 大。由於該估計是近似的，所以不與利用計算結果獲得的比率一致，但是可以說在半圓形結構中，電子更容易被移動到通道部。

參考例子

[0401] 在本參考例子中，說明使用 CAAC-OS 膜的電晶體對短通道效應充分具有耐性。

[0402] 作為對短通道效應的耐性的指標，特性長（Characteristic Length）被廣泛應用。特性長是通道部的勢能的彎曲的指標，當特性長短時，勢能急劇上升，對短通道效應具有高耐性。

[0403] 由於使用 CAAC-OS 膜的電晶體為積累型電晶體，所以使用 CAAC-OS 膜的電晶體所具有的對短通道效應的高耐性是起因於該特性長比反轉型電晶體短。

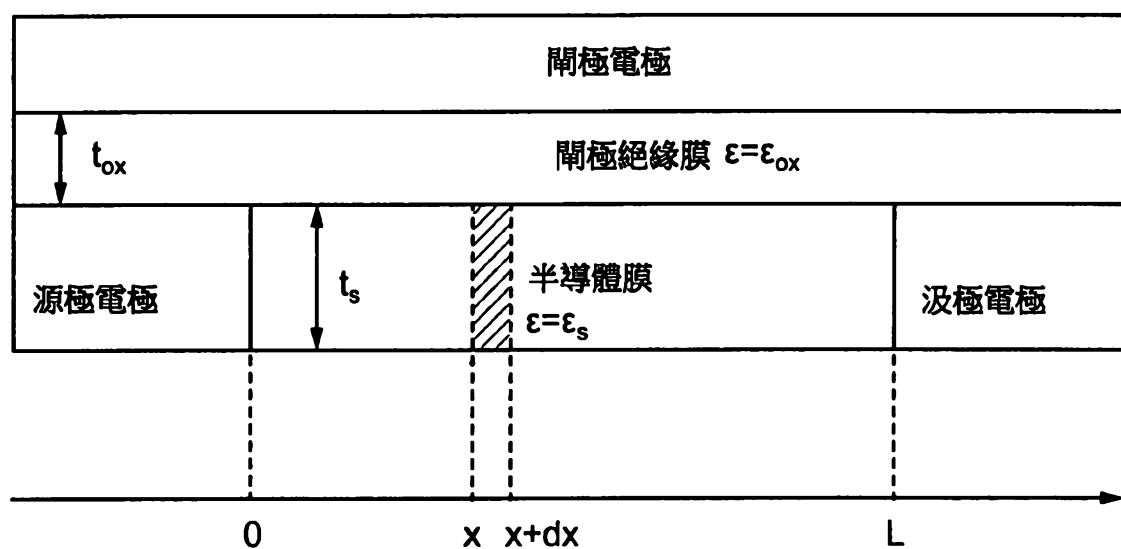

[0404] 使用圖 36 所示的電晶體結構的示意圖進行詳細的說明。注意， $\epsilon_s$  表示半導體膜的介電常數， $\epsilon_{ox}$  表示閘極絕緣膜的介電常數， $t_s$  表示半導體膜的厚度， $t_{ox}$  表示閘極絕緣膜的厚度。

[0405] 首先，假設 n 通道反轉型電晶體，藉由求解其泊松方程（Poisson's equation）來解析通道部的勢能。在此，藉由將高斯定理應用於圖式中的斜線陰影所示的用作通道部的半導體膜的微小的區間  $x$  至  $x+dx$ ，來導出以下算式。

[0406]

[算式 3]

$$-\epsilon_s t_s \left[ -\frac{d\phi(x)}{dx} + \frac{d\phi(x+dx)}{dx} \right] - \epsilon_{ox} \frac{V_G - V_{FB} - \phi(x)}{t_{ox}} dx = -e N_A t_s dx$$

[0407] 在此， $\phi(x)$  表示位置  $x$  的勢能（表面勢能）， $\phi(x+dx)$  表示位置  $x+dx$  的勢能（表面勢能）， $V_G$  表示閘極電壓， $V_{FB}$  表示平帶電壓， $e$  表示基本電荷，

$N_A$  表示受體密度。

[0408] 藉由上述算式 3 獲得以下算式。

[0409]

[算式 4]

$$\frac{d^2\phi(x)}{dx^2} + \frac{\varepsilon_{ox}}{\varepsilon_s t_s t_{ox}} \left[ V_G - V_{FB} - \phi(x) - \frac{eN_A t_s t_{ox}}{\varepsilon_{ox}} \right] = 0$$

[0410] 在此，將以下算式 5 代入算式 4 獲得算式 6。

[0411]

[算式 5]

$$\frac{1}{l^2} = \frac{\varepsilon_{ox}}{\varepsilon_s t_s t_{ox}}$$

[0412]

[算式 6]

$$\frac{d^2\phi(x)}{dx^2} - \frac{1}{l^2}\phi(x) + \frac{1}{l^2} \left( V_G - V_{FB} - \frac{eN_A t_s t_{ox}}{\varepsilon_{ox}} \right) = 0$$

[0413] 並且，使用以下算式 7 求出算式 6 的一般解，獲得算式 8。

[0414]

[算式 7]

$$V_L = V_G - V_{FB} - \frac{eN_A t_s t_{ox}}{\varepsilon_{ox}}$$

[0415]

[算式 8]

$$\phi(x) = A \exp(x/l) + B \exp(-x/l) + V_L$$

[0416] 勢能  $\phi(x)$  滿足以下所示的邊界條件。

[0417]

## [算式 9]

$$\begin{cases} \phi(0) = V_{bi} \\ \phi(L) = V_{bi} + V_{DS} \end{cases}$$

[0418] 以滿足上述邊界條件的方式，求出係數 A 和 B，來可以獲得微分方程的特解，獲得以下勢能  $\phi(x)$ 。

[0419]

## [算式 10]

$$\phi(x) = V_L + \frac{1}{\sinh\left(\frac{L}{l}\right)} \left[ (V_{bi} - V_{DS} - V_L) \sinh\left(\frac{x}{l}\right) + (V_{bi} - V_L) \sinh\left(\frac{L-x}{l}\right) \right]$$

[0420] 實際上藉由將  $x=0$  或  $x=L$  代入，容易確認到算式 10 滿足算式 9 的邊界條件。

[0421] 在此，算式中的 l 表示特性長，是勢能的彎曲的指標，特性長越短，FET 的通道部的勢能越急劇變化。

[0422] 因此，反轉型電晶體的特性長由以下算式表示。

[0423]

## [算式 11]

$$\frac{1}{l^2} = \frac{\epsilon_{ox}}{\epsilon_s t_s t_{ox}}$$

[0424] 接著，對包括使用 CAAC-OS 膜的電晶體的積累型電晶體進行同樣的考察而比較特性長。同樣地，藉由將高斯定理應用於用作通道部的半導體膜的微小的區間 x 至  $x+dx$ ，來導出以下算式。

[0425]

[算式 12]

$$-\varepsilon_s l_s \left[ -\frac{d\phi(x)}{dx} + \frac{d\phi(x+dx)}{dx} \right] - \varepsilon_{ox} \frac{V_G - V_{FB} - \phi(x)}{l_{ox}} dx = -en_i \exp\left(\frac{e(\phi(x) - \phi_F)}{k_B T}\right) l_s dx$$

[0426] 在此， $n_i$  表示本質載子密度， $k_B$  表示波茲曼常數， $\phi_F$  表示費米能階。

[0427] 藉由上述算式 12 獲得以下算式。

[0428]

[算式 13]

$$\frac{d^2\phi(x)}{dx^2} + \frac{1}{l^2} [V_G - V_{FB} - \phi(x)] = \frac{e}{\varepsilon_s} n_i \exp\left(\frac{e(\phi(x) - \phi_F)}{k_B T}\right)$$

[0429] 注意， $l$  等於反轉型電晶體的特性長。

[0430] 利用以下近似式（算式 14）展開算式 13 的右邊，而獲得算式 15。

[0431]

[算式 14]

$$x = x_1 + x'，\phi(x) = \phi_1 + \Delta\phi(x') \quad (\text{注意 } \phi_1 = \phi(x_1))$$

[0432]

[算式 15]

$$\begin{aligned} & \frac{d^2\Delta\phi(x')}{dx'^2} + \frac{1}{l^2} [V_G - V_{FB} - \phi_1 - \Delta\phi(x')] \\ &= \frac{e}{\varepsilon_s} n_i \exp\left(\frac{e(\phi_1 - \phi_F)}{k_B T}\right) \exp\left(\frac{e\Delta\phi(x')}{k_B T}\right) = \frac{e}{\varepsilon_s} n_i \exp\left(\frac{e\Delta\phi(x')}{k_B T}\right) \approx \frac{e}{\varepsilon_s} n_i \left[ 1 + \frac{e\Delta\phi(x')}{k_B T} \right] \end{aligned}$$

[0433] 在此， $n_1$  表示位置  $x_1$  的電子密度。另外，將以下算式 16 和算式 17 代入算式 15 而獲得算式 18。

[0434]

[算式 16]

$$\frac{1}{\lambda_1^2} = \frac{e^2 n_1}{\varepsilon_s k_B T}$$

[0435]

[算式 17]

$$n_1 = n_i \exp\left(\frac{e(\phi_1 - \phi_F)}{k_B T}\right)$$

[0436]

[算式 18]

$$\frac{d^2 \Delta \phi(x')}{dx'^2} - \left( \frac{1}{l^2} + \frac{1}{\lambda_1^2} \right) \Delta \phi(x') + \frac{1}{l^2} (V_G - V_{FB} - \phi_1) - \frac{e}{\varepsilon_s} n_1 = 0$$

[0437] 並且，將以下算式 19 應用於算式 18，而獲得算式 20。

[0438]

[算式 19]

$$\frac{1}{l'^2} = \frac{1}{l^2} + \frac{1}{\lambda_1^2}$$

[0439]

[算式 20]

$$\frac{d^2 \Delta \phi(x')}{dx'^2} - \frac{1}{l'^2} \Delta \phi(x') + \frac{1}{l'^2} \left[ \frac{l'^2}{l^2} (V_G - V_{FB} - \phi_1) - l'^2 \frac{e}{\varepsilon_s} n_1 \right] = 0$$

[0440] 注意，上述算式僅可應用於點  $x_1$  附近。

[0441] 因此，積累型電晶體的點  $x_1$  附近的特性長由以下算式表示。

[0442]

[算式 21]

$$\frac{1}{l'^2} = \frac{\varepsilon_{ox}}{\varepsilon_s t_s t_{ox}} + \frac{e^2 n_1}{\varepsilon_s k_B T}$$

為了比較反轉型電晶體和積累型電晶體，反轉型電晶體的特性長  $l$  由  $l(\text{inv})$  表示，積累型電晶體的特性長  $l'$  由  $l(\text{acc})$  表示，並且，比較兩者。

[0443]

[算式 22]

$$\begin{cases} \frac{1}{l(\text{inv})^2} = \frac{\epsilon_{ox}}{\epsilon_s t_s t_{ox}} \\ \frac{1}{l(\text{acc})^2} = \frac{\epsilon_{ox}}{\epsilon_s t_s t_{ox}} + \frac{e^2 n_i}{\epsilon_s k_B T} \end{cases}$$

[0444] 藉由上述算式可知  $l(\text{inv}) > l(\text{acc})$ 。

[0445] 注意，根據點  $x_1$ ，計算出的積累型電晶體的特性長  $l(\text{acc})$  的值發生變化，但是在任何情況下比反轉型電晶體短，並且，由於源極和汲極附近的電子密度高，因此勢能更急劇地上升。

[0446] 上述結果示出積累型電晶體的特性長比反轉型電晶體的特性長短。

【符號說明】

[0447]

110：基板

120：基底絕緣膜

137：通道區

138：通道區

160：閘極絕緣膜

170：閘極電極

- 210 : 基板

220 : 基底絕緣膜

230 : 氧化物半導體膜

260 : 閘極絕緣膜

270 : 閘極電極

400 : 基板

402 : 基底絕緣膜

403a : 第一氧化物膜

403b : 氧化物半導體膜

403c : 第二氧化物膜

404 : 多層膜

404a : 第一氧化物膜

404b : 氧化物半導體膜

404c : 第二氧化物膜

405a : 導電膜

405b : 導電膜

406a : 源極電極

406b : 沖極電極

407 : 絝緣膜

408 : 閘極絕緣膜

409 : 導電膜

410 : 閘極電極

412 : 氧化物絕緣膜

414 : 障壁膜

416：側壁絕緣膜

418：側壁絕緣膜

419a：電極

419b：電極

420a：佈線

420b：佈線

435：界線

450：電晶體

460：電晶體

470：電晶體

550：電晶體

560：電晶體

570：電晶體

580：電晶體

602：光電二極體

640：電晶體

656：電晶體

658：光電二極體重設信號線

659：閘極信號線

672：光感測器參考信號線

700：記憶元件

701：電路

702：電路

703：開關

- 704 : 開關

- 706 : 邏輯元件

- 707 : 電容元件

- 708 : 電容元件

- 709 : 電晶體

- 710 : 電晶體

- 713 : 電晶體

- 714 : 電晶體

- 720 : 電路

- 1189 : ROM 介面

- 1190 : 基板

- 1191 : ALU

- 1192 : ALU 控制器

- 1193 : 指令解碼器

- 1194 : 中斷控制器

- 1195 : 時序控制器

- 1196 : 暫存器

- 1197 : 暫存器控制器

- 1198 : 匯流排介面

- 1199 : ROM

- 2200 : 電晶體

- 2201 : 絝緣膜

- 2202 : 佈線

- 2203 : 插頭

2204 : 絶緣膜

2205 : 佈線

2206 : 佈線

3001 : 佈線

3002 : 佈線

3003 : 佈線

3004 : 佈線

3005 : 佈線

3200 : 電晶體

3300 : 電晶體

3400 : 電容元件

8000 : 電視機

8001 : 外殼

8002 : 顯示部

8003 : 揚聲器部

8004 : CPU

8100 : 警報裝置

8101 : 微型電腦

8102 : 檢測部

8200 : 室內機

8201 : 外殼

8202 : 出風口

8203 : CPU

8204 : 室外機

8300 : 電冷藏冷凍箱

8301 : 外殼

8302 : 冷藏室門

8303 : 冷凍室門

8304 : CPU

9700 : 電動汽車

9701 : 二次電池

9702 : 電路

9703 : 驅動裝置

9704 : 處理裝置

I662710

## 發明摘要

※申請案號：103117141

※申請日：103 年 05 月 15 日

※IPC 分類：

*H01L 29/78* (2006.01)

*H01L 29/40* (2006.01)

【發明名稱】(中文/英文)

半導體裝置

Semiconductor device

【中文】

本發明的一個方式的目的之一是提供一種能夠抑制隨著微型化而逐漸顯著的電特性下降的半導體裝置。該半導體裝置包括：第一氧化物膜；第一氧化物膜上的氧化物半導體膜；與氧化物半導體膜接觸的源極電極及汲極電極；氧化物半導體膜、源極電極及汲極電極上的第二氧化物膜；第二氧化物膜上的閘極絕緣膜；以及與閘極絕緣膜接觸的閘極電極，其中，從通道寬度方向看時，氧化物半導體膜的上端部帶弧形。

## 【英文】

Provided is a semiconductor device in which deterioration of electric characteristics which becomes more noticeable as the semiconductor device is miniaturized can be suppressed. The semiconductor device includes a first oxide film, an oxide semiconductor film over the first oxide film, a source electrode and a drain electrode in contact with the oxide semiconductor film, a second oxide film over the oxide semiconductor film, the source electrode, and the drain electrode, a gate insulating film over the second oxide film, and a gate electrode in contact with the gate insulating film. A top end portion of the oxide semiconductor film is curved when seen in a channel width direction.

【代表圖】

【本案指定代表圖】：第(1B)圖。

【本代表圖之符號簡單說明】：

400：基板

402：基底絕緣膜

404：多層膜

404a：第一氧化物膜

404b：氧化物半導體膜

404c：第二氧化物膜

406a：源極電極

406b：汲極電極

408：閘極絕緣膜

410：閘極電極

412：氧化物絕緣膜

450：電晶體

【本案若有化學式時，請揭示最能顯示發明特徵的化學式】：無

## 圖 式

圖 1A

圖 1B

圖 1C

圖 2A

圖 2B

圖 3

I662710

圖 4A

圖 4B

圖 5A

$$W_{S1} = W_{S2} \doteq W_T$$

圖 5B

$$W_{S1} = W_{S2} \gg W_T$$

圖 6A

圖 6B

圖 6C

圖 7

I662710

圖 8A

圖 8B

圖 8C

圖 9A

圖 9B

圖 9C

圖 11

圖 12

圖 13A

圖 13B

圖 13C

圖 14A

圖 14B

圖 14C

圖 15A

圖 15B

圖 15C

I662710

圖 16A

圖 16B

圖 16C

圖 17A

圖 17B

圖 17C

圖 18A

圖 18B

圖 18C

I662710

圖 20

圖 21

圖 22

I662710

圖 23A

圖 23B