(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-58770

(P2006-58770A)

(43) 公開日 平成18年3月2日(2006.3.2)

| (51) Int.C1.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36  | 2 H 09 3    |

| <b>G02F 1/133</b> (2006.01) | G02F 1/133 | 5 C 00 6    |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20  | 5 C 08 0    |

| <b>G11C 19/28</b> (2006.01) | G09G 3/20  | 5 J 05 5    |

| <b>H03K 17/10</b> (2006.01) | G09G 3/20  | 6 2 2 E     |

審査請求 未請求 請求項の数 4 O L (全 13 頁) 最終頁に続く

---

|                       |                                                        |                                                                                                                                                                                                                                                                                                                         |

|-----------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号<br>(22) 出願日 | 特願2004-242535 (P2004-242535)<br>平成16年8月23日 (2004.8.23) | (71) 出願人<br>東芝松下ディスプレイテクノロジー株式会社<br>東京都港区港南4-1-8<br><br>(74) 代理人<br>弁理士 三好 秀和<br><br>(74) 代理人<br>100083806<br><br>(74) 代理人<br>弁理士 岩▲崎▼ 幸邦<br><br>(74) 代理人<br>100100929<br><br>(74) 代理人<br>弁理士 川又 澄雄<br><br>(74) 代理人<br>100108707<br><br>(74) 代理人<br>弁理士 中村 友之<br><br>(74) 代理人<br>100095500<br><br>(74) 代理人<br>弁理士 伊藤 正和 |

|-----------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

最終頁に続く

(54) 【発明の名称】表示装置の駆動回路

## (57) 【要約】

【課題】表示装置の駆動回路において、各トランジスタに加わる電圧ストレスの増大を防止しつつ、出力信号のハイレベル電圧とローレベル電圧間の電位差を大きくする。

【解決手段】イネーブル信号OEのハイレベル電圧VDDとローレベル電圧VSS間の電位差よりも、シフトレジスタ及びバッファのハイレベル電源電圧VDDとローレベル電源電圧VSS2間の電位差の方を小さく設定する。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

走査線又は信号線のうちの少なくとも一方を駆動する表示装置の駆動回路において、

入力された入力信号の位相をシフトさせて出力するシフトレジスタと、

シフトレジスタの出力信号の振幅をイネーブル信号を用いて増幅し走査線又は信号線に

出力するバッファとを備え、

前記イネーブル信号のハイレベル電圧とローレベル電圧との電位差を走査線又は信号線

の駆動用の電位差とし、シフトレジスタ及びバッファでのハイレベル電源電圧とローレベル

電源電圧との電位差を、前記イネーブル信号のハイレベル電圧とローレベル電圧との電位

差よりも小さく設定したことを特徴とする表示装置の駆動回路。

10

**【請求項 2】**

前記バッファは、イネーブル信号が入力されるイネーブル端子と増幅した信号を出力す

る出力端子との間の導電パスをもつトランジスタと、

前記出力端子と電源電圧との間の導電パスをもつトランジスタと、

を備えた出力回路を有することを特徴とする表示装置の駆動回路。

**【請求項 3】**

前記シフトトランジスタおよび前記バッファを構成する各トランジスタは、pMOSト

ランジスタであって、前記イネーブル信号のローレベル電圧よりも、シフトレジスタ及び

バッファでのローレベル電源電圧を高く設定したことを特徴とする請求項1又は2記載の

表示装置の駆動回路。

20

**【請求項 4】**

前記シフトトランジスタおよび前記バッファを構成する各トランジスタは、nMOSト

ランジスタであって、前記イネーブル信号のハイレベル電圧よりも、シフトレジスタ及び

バッファでのハイレベル電源電圧を低く設定したことを特徴とする請求項1又は2記載の

表示装置の駆動回路。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示装置における走査線あるいは信号線を駆動するための駆動回路に関する

。

30

**【背景技術】****【0002】**

液晶表示装置に代表される表示装置は、薄型、軽量かつ低消費電力であることから、各

種機器のディスプレイとして用いられている。中でも、画素毎にトランジスタを配置した

アクティブマトリクス型液晶表示装置は、ノート型パソコンや携帯型情報端末のディスプレ

イとして普及しつつある。近年、従来の液晶表示装置に用いられていたアモルファスシリ

コン薄膜トランジスタ(Thin Film Transistor: TFT)に比べて、電子移動度が高い

ポリシリコンTFT(p-si TFT)を比較的低温のプロセスで形成する技術が確立され、

液晶表示装置に用いるトランジスタの小型化が可能となった。これにより、複数の走査線

と複数の信号線との各交差部にトランジスタを配置した画素部と、走査線および信号線を

駆動する駆動回路とを同一の製造プロセスによってガラス製の透明基板上に一体的に形成

することができるようになった。

40

**【0003】**

さらには、駆動回路の出力信号の電位を十分なレベルにするためのブーストランプ回

路の開発が進められている(例えば特許文献1参照)。

**【特許文献1】特開2003-344873号公報****【発明の開示】****【発明が解決しようとする課題】****【0004】**

ところで、駆動回路の出力信号のハイレベル電圧とローレベル電圧間の電位差は、駆動

50

回路の出力信号が映像信号の各画素への書き込みを制御するためのものであるため、安定的な書き込みを実現する観点からはできるだけ大きい電位差であることが望ましい。しかしながら、ハイレベル電圧とローレベル電圧間の電位差が大きいということは、トランジスタに加わる電圧ストレスが大きいということであり、駆動回路を構成する各トランジスタの動作上の信頼性が低下するおそれがある。また、駆動回路を高電圧で駆動することになるため、消費電力が大きくなるという問題もある。

#### 【0005】

本発明は、上記に鑑みてなされたものであり、その目的とするところは、各トランジスタに加わる電圧ストレスの増大を防止しつつ、出力信号のハイレベル電圧とローレベル電圧間の電位差を大きく設定することが可能な表示装置の駆動回路を提供することにある。10

#### 【課題を解決するための手段】

#### 【0006】

本発明に係る表示装置の駆動回路は、走査線又は信号線のうちの少なくとも一方を駆動する表示装置の駆動回路において、入力された入力信号の位相をシフトさせて出力するシフトレジスタと、シフトレジスタの出力信号の振幅をイネーブル信号を用いて増幅し走査線又は信号線に出力するバッファとを備え、前記イネーブル信号のハイレベル電圧とローレベル電圧との電位差を走査線又は信号線の駆動用の電位差とし、シフトレジスタ及びバッファでのハイレベル電源電圧とローレベル電源電圧との電位差を、前記イネーブル信号のハイレベル電圧とローレベル電圧との電位差よりも小さく設定したことを特徴とする。20

#### 【0007】

本発明にあっては、イネーブル信号のハイレベル電圧とローレベル電圧間の電位差よりも、シフトレジスタ及びバッファでのハイレベル電源電圧とローレベル電源電圧間の電位差の方を小さく設定したことで、イネーブル信号を用いて増幅されるバッファの出力信号についてのハイレベル電圧とローレベル電圧間の電位差を大きくするとともに、シフトレジスタやバッファについては電位差が小さいハイレベル電源電圧とローレベル電源電圧を用いて動作させ、各トランジスタにかかる電圧ストレスを小さくしている。20

#### 【0008】

本表示装置の駆動回路は、より具体的な構成として、前記バッファは、イネーブル信号が入力されるイネーブル端子と増幅した信号を出力する出力端子との間の導電パスをもつトランジスタと、前記出力端子と電源電圧との間の導電パスをもつトランジスタと、を備えた出力回路を有することを特徴とする。30

#### 【0009】

本表示装置の駆動回路は、さらに具体的な構成として、前記シフトトランジスタおよび前記バッファを構成する各トランジスタは、pMOSトランジスタであって、前記イネーブル信号のローレベル電圧よりも、シフトレジスタ及びバッファでのローレベル電源電圧を高く設定したことを特徴とする。

#### 【0010】

本表示装置の駆動回路は、別の具体的な構成として、前記シフトトランジスタおよび前記バッファを構成する各トランジスタは、nMOSトランジスタであって、前記イネーブル信号のハイレベル電圧よりも、シフトレジスタ及びバッファでのハイレベル電源電圧を低く設定したことを特徴とする。40

#### 【発明の効果】

#### 【0011】

本発明に係る表示装置の駆動回路によれば、バッファの出力信号についてハイレベル電圧とローレベル電圧間の電位差を大きく設定でき、映像信号を画素に安定して書き込むことができる。また、シフトレジスタやバッファの内部では各トランジスタにかかる電圧ストレスを小さくでき、信頼性の高い動作を実現することができる。また、駆動回路を低電圧で駆動でき、消費電力を低く抑えることができる。

#### 【発明を実施するための最良の形態】

#### 【0012】

10

20

30

40

50

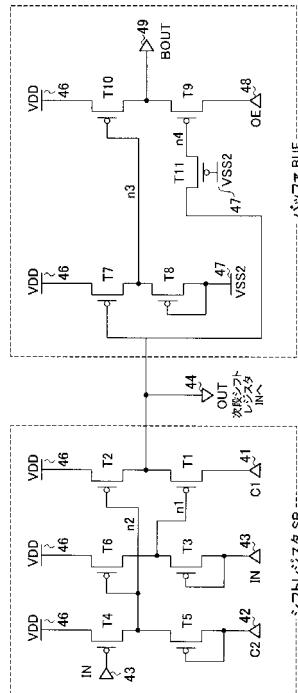

図1は、一実施の形態における表示装置の構成を示す回路図である。ここでは、アクティブマトリクス型の液晶表示装置を例に説明する。同図の表示装置は、ガラス製の透明基板10上に画素部11、走査線駆動回路21、信号線駆動回路31を備える。

#### 【0013】

画素部11では、複数の走査線G1, G2, Gn(以下「G」と総称する)と、複数の信号線S1, S2, Sm(以下「S」と総称する)とが交差するように配線され、各交差部にスイッチング素子12、画素電極13、液晶容量14、補助容量15を備える。スイッチング素子には、一例としてポリシリコン薄膜トランジスタを用いる。

#### 【0014】

走査線駆動回路21は、電気的に縦続接続された複数のシフトレジスタからなる垂直シフトレジスタ22と、この出力段に接続されたバッファ23を備える。信号線駆動回路31は、電気的に縦続接続された複数のシフトレジスタからなる水平シフトレジスタ32と、この出力段に接続されたバッファ33と、映像信号が供給されてくる映像信号線34と、映像信号線34を各信号線Sに接続するための複数のアナログスイッチ35とを備える。

10

#### 【0015】

垂直シフトレジスタ22、水平シフトレジスタ32にはスタートパルス信号(STP)とクロック信号(CK)が入力される。ここでは、垂直シフトレジスタ22に入力されるスタートパルス信号をSTV、水平シフトレジスタ32に入力されるスタートパルス信号をSTHと呼ぶ。また、垂直シフトレジスタ22に入力されるクロック信号をCKV、水平シフトレジスタ32に入力されるクロック信号をCKHと呼ぶ。

20

#### 【0016】

垂直シフトレジスタ22、水平シフトレジスタ32は、入力されたスタートパルス信号STPの位相をシフトさせて出力する。この点について、走査線駆動回路21では、内部の各シフトレジスタから各走査線Gに対して垂直走査パルスを1段ずつ位相をシフトさせながら出力する。信号線駆動回路31では、内部の各シフトレジスタから各信号線Sに設けられたアナログスイッチ35に対して水平走査パルスを1段ずつ位相をシフトさせながら出力してアナログスイッチ35をオンさせ、外部から映像信号線34に供給されてきた映像信号をアナログスイッチ35を通じて各信号線Sに出力させる。

30

#### 【0017】

各バッファ23, 33におけるトランジスタのチャネルの幅Wと長さLは、走査線G、アナログスイッチ35を充分に駆動可能なパルスを出力できるよう、垂直シフトレジスタ22、水平シフトレジスタ23におけるトランジスタのものより大きく形成される。また、各駆動回路は、製造工程を短縮し低コスト化を実現するために、pMOS又はnMOSのいずれか一方のトランジスタのみを用いて構成することが望ましい。

40

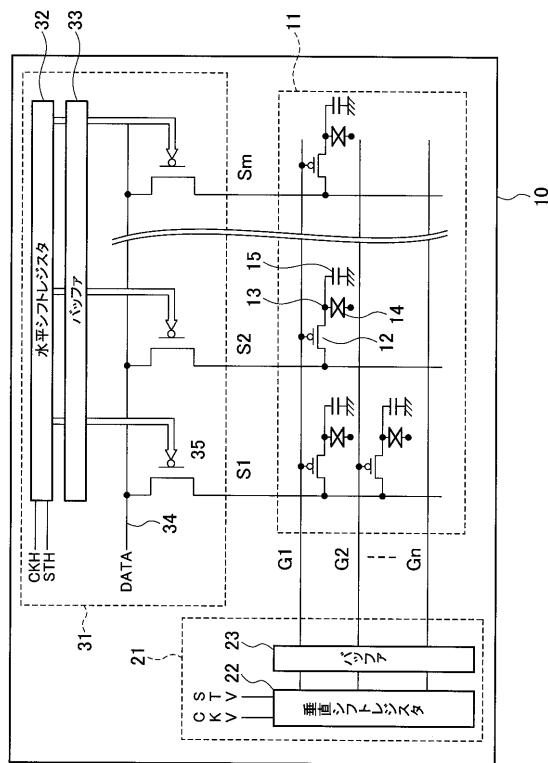

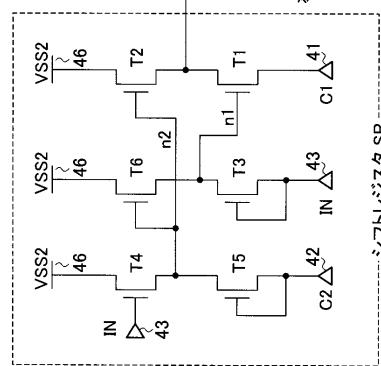

#### 【0018】

図2は、駆動回路の内部構成を示す回路図である。走査線駆動回路21も信号線駆動回路31も基本的には同様の構成である。もちろん、いずれか一方の駆動回路だけを同図の構成としてもよい。この駆動回路は、電気的に縦列接続された複数のシフトレジスタSR1, SR2, ~SRn(以下、総称SR)と、各シフトレジスタSRに対して位相をずらした3本のクロック信号CK1、CK2、CK3のうちのいずれか2本を入力するためのクロック線36と、各シフトレジスタSR1, SR2, ~SRnの出力段に接続された複数のバッファBUF1, BUF2, ~BUFnと、各バッファBUFにイネーブル信号OE(OUTPUT ENABLE)を供給するための出力線37を備えた構成である。各クロック信号CK1～CK3は、垂直シフトレジスタ22においては垂直クロック信号CKVであり、水平シフトレジスタ32においては水平クロック信号CKHである。

50

#### 【0019】

シフトレジスタSR1、SR2、~SRnは、それぞれ第1ステージ、第2ステージ、~第nステージに対応する。各シフトレジスタSRは、第1クロック端子41、第2クロック端子42を有する。例えば、シフトレジスタSR1では、第1クロック端子41に第

1クロック信号CK1が入力され、第2クロック端子42に第2クロック信号CK2が入力される。シフトレジスタSR2では、第1クロック端子41に第2クロック信号CK2が入力され、第2クロック端子42に第3クロック信号CK3が入力される。

#### 【0020】

各シフトレジスタSRは、入力された入力信号INの位相を2つのクロック信号に同期するようにシフトさせて出力信号OUTとして出力する。入力信号INとして、初段のシフトレジスタSR1ではスタートパルス信号STPが入力され、2段目以降のシフトレジスタSRでは前段のシフトレジスタSRの出力信号OUTが入力される。各バッファBUFは、出力信号OUTの振幅を増幅して出力信号BOUFとして出力する。

#### 【0021】

走査線駆動回路21では、各バッファBUFからの出力信号BOUFを垂直走査パルスとして各走査線Gに出力し、信号線駆動回路31では、各バッファBUFからの出力信号BOUFを水平走査パルスとして各アナログスイッチ35の制御電極に出力する。

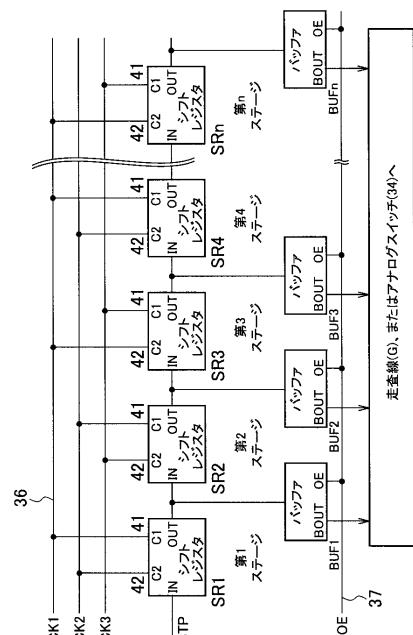

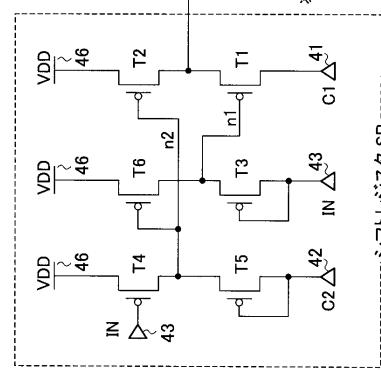

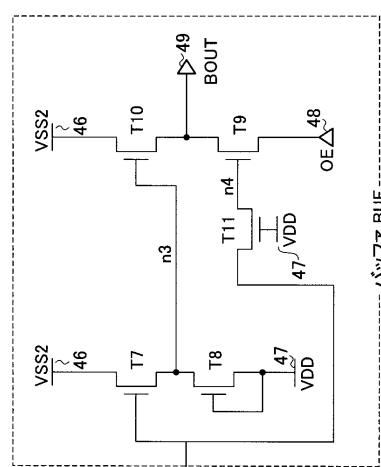

#### 【0022】

図3は、シフトレジスタSR及びバッファBUFの構成を示す回路図である。入力端子43には入力信号INが入力される。また、位相をシフトさせたCK1～CK3の3本のクロック信号のうちのいずれか2本のクロック信号がクロック端子に入力される。同図では、一例として第1クロック信号CK1が第1クロック端子41に入力され、第2クロック信号CK2が第2クロック端子42に入力されるものとする。シフトレジスタSR及びバッファBUFに含まれるトランジスタは一例として全てpMOSトランジスタとする。

#### 【0023】

シフトレジスタSRは、出力回路、入力回路、リセット回路を有する構成である。出力回路は、第1トランジスタT1と第2トランジスタT2により構成される。第1トランジスタT1のドレインは第1クロック端子41に、ソースは出力端子44にそれぞれ電気的に接続される。第2トランジスタT2のソースは電源電極46に、ドレインは出力端子44にそれぞれ電気的に接続される。第1クロック端子41には第1クロック信号CK1が入力され、電源電極46にはハイレベルの電源電圧VDDが供給される。この出力回路は、第1トランジスタT1がオンで第2トランジスタT2がオフのときには、第1クロック信号CK1を出力端子44へ出力し、第1トランジスタT1がオフで第2トランジスタT2がオンのときには、電源電圧VDDを出力端子44へ出力する。

#### 【0024】

入力回路は、第3トランジスタT3と第4トランジスタT4により構成される。第3トランジスタT3のドレイン及びゲートは入力端子43に、ソースは第1トランジスタT1の制御電極にそれぞれ電気的に接続される。また、第4トランジスタT4のソースは電源電極46に、ドレインは第2トランジスタの制御電極に、ゲートは入力端子43にそれぞれ電気的に接続される。この入力回路は、入力端子43を通じて入力信号INを受ける。ここでは、第1トランジスタT1の制御電極への導電バスのことをノードn1、第2トランジスタT2の制御電極への導電バスのことをノードn2と表す。

#### 【0025】

リセット回路は、第5トランジスタT5と第6トランジスタT6により構成される。第5トランジスタT5のドレイン及びゲートは第2クロック端子42に、ソースは第2トランジスタT2の制御電極にそれぞれ電気的に接続される。また、第6トランジスタT6のドレインは第1トランジスタT1の制御電極に、ゲートは第4トランジスタT4のドレインと第2トランジスタT2の制御電極に、ソースは電源電極46にそれぞれ電気的に接続される。第2クロック端子42には第2クロック信号CK2が入力される。このリセット回路は、第1トランジスタT1又は第2トランジスタT2のいずれか一方をオンし、他方をオフする。

#### 【0026】

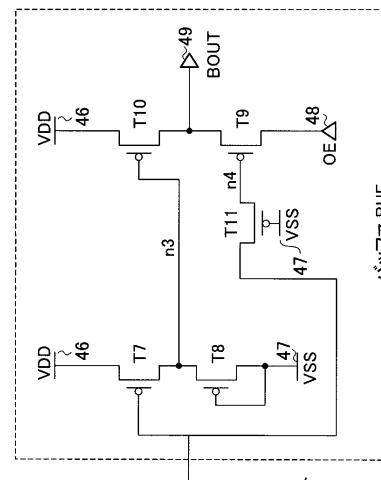

一方、バッファは、第7トランジスタT7と第8トランジスタT8により構成されるインバータ、第9トランジスタT9と第10トランジスタT10により構成される出力回路

10

20

30

40

50

、シフトレジスタの出力端子 4 4 と第 9 ドラミジスタ T 9 の制御電極との間に接続された第 11 ドラミジスタ T 11 を備える。

【 0 0 2 7 】

より具体的には、第 7 ドラミジスタ T 7 のゲートはシフトレジスタの出力端子 4 4 に接続され、ソースは電源電圧 V DD が供給される電源電極 4 6 に接続される。第 8 ドラミジスタ T 8 のゲートおよびドレインはローレベル電源電圧 V SS 2 の電源電極 4 7 に接続され、ソースは第 7 ドラミジスタ T 7 のドレインに接続される。

【 0 0 2 8 】

第 9 ドラミジスタ T 9 は、イネーブル信号 O E が入力されるイネーブル端子 4 8 と増幅した信号を出力する出力端子 4 9 との間の導電バスをもち、第 10 ドラミジスタ T 10 は、出力端子 4 9 と電源電圧 V DD との間の導電バスをもつ。具体的には、第 9 ドラミジスタ T 9 のドレインはイネーブル端子 4 8 に接続され、ソースは出力端子 4 9 に接続され、ゲートはシフトレジスタの出力端子 4 4 に第 11 ドラミジスタ T 11 を介して接続される。この第 11 ドラミジスタ T 11 のゲートにはローレベル電源電圧 V SS 2 が供給される。第 10 ドラミジスタ T 10 のドレインは出力端子 4 9 に接続され、ソースは電源電圧 V DD が供給される電源電極 4 6 に接続され、ゲートは第 7 ドラミジスタ T 7 と第 8 ドラミジスタ T 8 の接続点に接続される。ここでは、第 10 ドラミジスタ T 10 の制御電極への導電バスをノード n 3 、第 9 ドラミジスタ T 9 の制御電極への導電バスをノード n 4 とそれぞれ表す。

【 0 0 2 9 】

本駆動回路では、イネーブル信号 O E のハイレベル電圧とローレベル電圧との電位差よりも、シフトレジスタ S R 及びバッファ B U F でのハイレベル電源電圧とローレベル電源電圧との電位差を小さくしたことを特徴とする。

【 0 0 3 0 】

具体的には、ハイレベルの電源電位 V DD は一定とし、イネーブル信号 O E のローレベル電圧 V SS よりも、シフトレジスタ S R 及びバッファ B U F におけるローレベルの電源電圧 V SS 2 の方を高い電位にする。この点について、図 3 及び図 4 を用いて詳しく説明する。

【 0 0 3 1 】

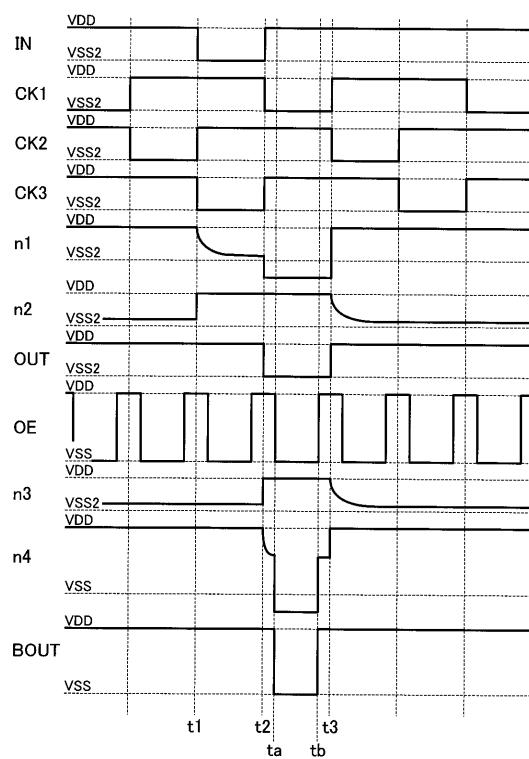

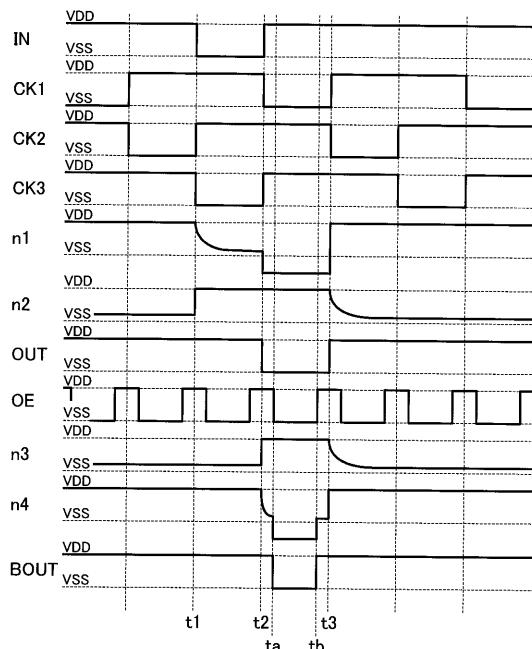

図 4 は、シフトレジスタ S R 1 における入力信号 I N 、クロック信号 C K 1 ~ C K 3 、イネーブル信号 O E 、ノード n 1 ~ n 4 、シフトレジスタの出力信号 O U T 、バッファの出力信号 B O U T の関係を示すタイミングチャートである。シフトレジスタ出力信号 O U T は、入力信号 I N の位相をシフトさせたものである。なお、他のシフトレジスタ S R も図 4 のタイミングチャートに従ってシフトレジスタ S R 1 と同様に動作する。

【 0 0 3 2 】

図 4 に示すように、ローレベル電源電圧と、入力信号 I N 、クロック信号 C K 1 ~ C K 3 といった各種信号のローレベル電圧については、イネーブル信号 O E のローレベル電圧 V SS よりも電位が高い V SS 2 に設定することで、ハイレベル電圧とローレベル電圧との電位差を小さくする。ハイレベル電圧 V DD とローレベル電圧 V SS 2 間の電位差は、後述するように、時刻 t 2 - t a の期間で第 9 ドラミジスタ T 9 をオンさせる程度のものであれば充分であり、それ以上の電位差とする必要はない。

【 0 0 3 3 】

時刻 t 1 - t 2 の期間において、入力信号 I N の電位がハイレベル電圧 V DD からローレベル電圧 V SS 2 になると、第 3 ドラミジスタ T 3 及び第 4 ドラミジスタ T 4 がオンする。第 2 クロック信号 C K 2 はハイレベル電圧なので、第 5 ドラミジスタ T 5 はオフ状態である。ノード n 2 の電位は、第 4 ドラミジスタ T 4 を通じてハイレベル電源電圧 V DD が供給されてハイレベルになり、第 2 ドラミジスタ T 2 及び第 6 ドラミジスタ T 6 をオフさせる。

【 0 0 3 4 】

第 3 ドラミジスタ T 3 がオン、第 6 ドラミジスタ T 6 がオフであるので、ノード n 1 に

10

20

30

40

50

は第3トランジスタT3を通じてローレベルの入力信号INが供給され、ノードn1の電位はVSS2となり、第1トランジスタT1がオンする。この結果、シフトレジスタの出力端子44には、第1トランジスタT1を通じてハイレベル電圧の第1クロック信号CK1が供給されるので、シフトレジスタの出力信号OUTはハイレベル電圧を維持する。

#### 【0035】

時刻t2-t3の期間では、入力信号INの電位がローレベル電圧VSS2からハイレベル電圧VDDになると同時に、第1クロック信号CK1の電位がハイレベル電圧VDDからローレベル電圧VSS2に反転する。入力信号INの電位がハイレベルになることで第3トランジスタT3および第6トランジスタT6がオフし、ノードn1は、電圧がかからないフローティング状態になる。そして、ノードn1は、第1クロック信号CK1の電位がローレベルに反転する影響を第1トランジスタT1を介して受け、ノードn1の電位は、ローレベル電圧VSS2よりもさらに低い電位(LLLレベル)になる。

#### 【0036】

これは、第1トランジスタT1のゲート・ソース間あるいはゲート・ドレイン間に寄生容量があるため、ゲートすなわちノードn1がフローティング状態であると、第1トランジスタT1のドレイン・ソース間の電位変動に伴ってノードn1の電位が変動するためである。このように、接続先のトランジスタにおける電位変動の影響を受けてフローティング状態にあるノードの電位が変動する現象のことをブートストラップといい、このときのノードのことをブートストラップノードという。この結果、ノードn1の電位がより低くなることで第1トランジスタT1は確実なオン状態となり、シフトレジスタの出力端子44には、第1トランジスタT1を通じてローレベル電圧の第1クロック信号CK1が供給されて、出力信号OUTはローレベル電圧VSS2となる。

#### 【0037】

また、第2クロック信号CK2はハイレベル電圧のため第5トランジスタT5はオフ状態であり、第4トランジスタT4もオフ状態であるので、ノードn2は、電圧が供給されないフローティング状態となり、寄生容量によってハイレベル電圧を維持する。

#### 【0038】

すなわち、この期間においては、ノードn1はLLLレベル、ノードn2はハイレベル電圧VDDでそれぞれフローティング状態にある。ここで、第1トランジスタT1及び、第2トランジスタT2のチャネル幅Wを他のトランジスタよりも大きく設定しておくことで、第1トランジスタT1および第2トランジスタT2の寄生容量が大きくなり、ノードn1、ノードn2は安定してLLLレベル電位、ハイレベル電位をそれぞれ保持することができる。

#### 【0039】

時刻t3においては、第1クロック信号CK1の電位がハイレベル電圧VDDになり、第2クロック信号CK2の電位がローレベル電圧VSS2になる。第2クロック信号CK2の電位がローレベルになることで、第5トランジスタT5がオンする。このとき、第4トランジスタT4はオフ状態にあるので、ノードn2の電位は、第5トランジスタT5を通じてローレベル電圧VSS2になる。この結果、第2トランジスタT2及び第6トランジスタT6がオンする。第6トランジスタT6がオンすることで、ノードn1はハイレベル電圧となり、第1トランジスタT1はオフする。このように、第1トランジスタT1がオフし、第2トランジスタT2がオンするので、シフトレジスタの出力端子44には第2トランジスタT2を通じてハイレベル電源電圧VDDが供給され、シフトレジスタの出力信号OUTの電位はハイレベルになる。

#### 【0040】

時刻t3以降は、入力信号INの電位はハイレベルに固定されるので、ノードn1はハイレベル電圧VDDを、ノードn2はローレベル電圧VSS2を、出力信号OUTはハイレベル電圧VDDをそれぞれ維持する。ここで、第2トランジスタT2のチャネル幅Wを第5トランジスタのチャネル幅より十分大きく設定しておくことで、第5トランジスタT5のゲート・ドレイン間のカップリングの影響を少なくし、ノードn2の電位をローレベ

10

20

30

40

50

ルに確実に保持することができる。

#### 【0041】

次に、バッファBUFの動作を説明する。図4に示すように、イネーブル信号OEについては、ハイレベル電圧をVDDとし、ローレベル電圧をVSSとする。この電圧VSSは、前述したローレベル電圧VSS2よりも低い電圧である。また、同図に示すように、イネーブル信号OEの電位がローレベルになる期間を、第1～第3クロック信号CK1～CK3の電位がローレベルになる期間よりも短く設定することで、大きな電位差がかかる第9トランジスタT9、第10トランジスタT10への電圧ストレスを軽減する。

#### 【0042】

時刻t2-taの期間において、ローレベル電圧VSS2のシフトレジスタ出力信号OUTがバッファBUFに入力されると、第7トランジスタT7及び第8トランジスタT8がインバータ回路を構成しているので、ノードn3の電位はハイレベル電圧VDDとなり、第10トランジスタT10はオフする。また、第11トランジスタT11を通じて供給されるローレベルのシフトレジスタ出力信号OUTにより、ノードn4はローレベル電圧VSS2となり、第9トランジスタT9はオンする。バッファBUFの出力端子49には第9トランジスタT9を通じてハイレベル電圧のイネーブル信号OEが供給され、バッファの出力信号BOUTは、ハイレベル電圧VDDを維持する。10

#### 【0043】

時刻ta-tbの期間において、イネーブル信号OEの電位がローレベル電圧VSSになると、ブートストラップが働き、フローティング状態にあるノードn4の電位がVSS2よりもさらに(VDD-VSS)に相当する分だけ低いレベルになって第9トランジスタT9はオン状態を維持し、バッファの出力信号BOUTの電位は、イネーブル信号OEの電圧変化に追従してローレベル電圧VSSになる。20

#### 【0044】

時刻tb-t3の期間において、イネーブル信号OEの電位がハイレベル電圧VDDになると、ノードn4の電位は通常のローレベル電圧VSS2に戻り、第9トランジスタT9がオン状態を維持し、バッファの出力信号BOUTの電位は、イネーブル信号OEの電圧変化に追従してハイレベル電圧に戻る。

#### 【0045】

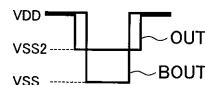

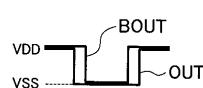

時刻t3以降において、シフトレジスタの出力信号OUTの電位がハイレベル電圧VDになると、ノードn3、ノードn4の電位がそれぞれ反転し、ノードn3の電位はローレベル電圧VSS2に、ノードn4の電位はハイレベル電圧VDDになる。その結果、第9トランジスタT9がオフし、第10トランジスタT10がオンになり、バッファの出力信号BOUTの電位は、第10トランジスタT10を通じて電源電圧VDDが供給され、イネーブル信号OEの電位に関わらずハイレベル電圧を維持する。参考のため、シフトレジスタの出力信号OUTとバッファの出力信号BOUTとを重ねて示すと図5のようになる。30

#### 【0046】

このように、本駆動回路では、イネーブル信号OEのハイレベル電圧VDDとローレベル電圧VSSとの電位差よりも、シフトレジスタSR及びバッファBUFのハイレベル電源電圧VDDとローレベル電源電圧VSS2との電位差を小さく設定したことで、シフトレジスタの出力信号OUTがVDD～VSS2間の信号であるのに対し、バッファの出力信号BOUTは、それよりも電位差が大きいVDD～VSS間の信号になり、バッファ回路で信号の増幅が行われることになる。例えば、シフトレジスタとバッファの出力回路を除く部分は18V駆動とし、バッファの出力回路は22.5V駆動とする。40

#### 【0047】

すなわち、本表示装置の駆動回路は、バッファBUFが、ハイレベル電圧とローレベル電圧間の電位差が大きい出力信号BOUTを出力できるので、映像信号を画素へ安定的に書き込むことができるとともに、シフトレジスタSRやバッファBUFの内部では、バッファBUFの出力回路以外の回路は、電位差が小さいハイレベル電圧とローレベル電圧を50

用いて動作するので、各トランジスタにかかる電圧ストレスが小さくなり、高い信頼性をもって動作することが可能になる。また、駆動回路を低電圧で駆動するので、消費電力を低く抑えることができる。

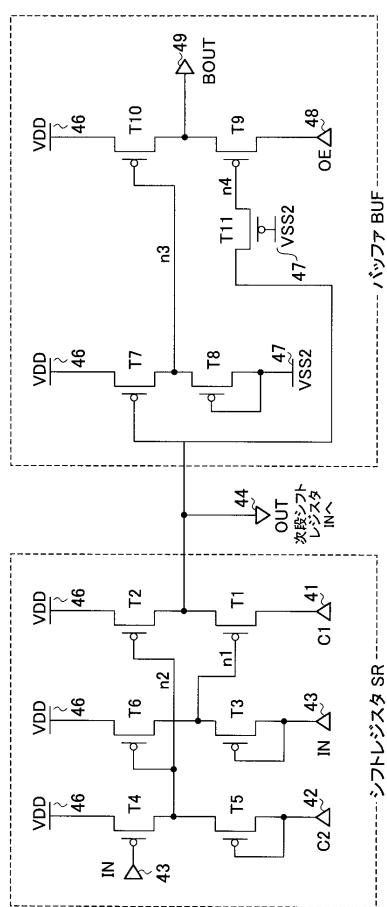

#### 【0048】

次に、比較例の駆動回路について説明する。図6は、比較例の駆動回路におけるシフトレジスタとバッファの構成を示す回路図である。基本的には、図3に示した回路と同様の構成であるが、比較例では、イネーブル信号OEのローレベル電圧の他、各種信号のローレベル電圧と、シフトレジスタ及びバッファにおけるローレベル電源電圧は、同じVSSとなっている。

#### 【0049】

図7は、比較例の駆動回路の動作を示すタイミングチャートである。比較例の駆動回路は、基本的には、図4に示したタイミングチャートと同様の動作をするが、各種信号は全て電位差が大きいVDD - VSS間の信号となっている。このため、駆動回路の出力信号BOUTは電位差が大きいので、映像信号を各画素へ安定的に書き込むことは可能であるものの、シフトレジスタやバッファ内部には電位差が大きいハイレベル電圧、ローレベル電圧が供給されることになり、各トランジスタにかかる電圧ストレスが高くなるため、動作上の信頼性が低下する。また、駆動回路を高電圧で駆動することになるため消費電力が大きくなる。参考のため、比較例についてシフトレジスタの出力信号OUTとバッファの出力信号BOUTとを重ねて示すと図8のようになる。

#### 【0050】

これに対し、本実施形態における駆動回路は、各トランジスタにかかる電圧ストレスが高くなることではなく、動作上の信頼性が低下することはない。また、駆動回路を低電圧で駆動するので消費電力が大きくなることもない。

#### 【0051】

したがって、本実施の形態によれば、バッファが出力回路で用いるイネーブル信号OEのハイレベル電圧VDDとローレベル電圧VSS間の電位差よりも、シフトレジスタ及びバッファでのハイレベル電源電圧VDDとローレベル電源電圧VSS2間の電位差の方を小さく設定したことで、イネーブル信号OEを用いて増幅されるバッファの出力信号BOUTについてハイレベル電圧とローレベル電圧間の電位差が大きいので、映像信号を各画素に安定的に書き込むことができる。また、シフトレジスタやバッファの内部では、バッファの出力回路を除いて、電位差が小さいハイレベル電圧VDDとローレベル電圧VSS2を用いて動作するので、各トランジスタにかかる電圧ストレスを小さくでき、動作上の信頼性を向上できるとともに、消費電力を低減することができる。

#### 【0052】

なお、シフトレジスタは、図3の構成のものに限らず、入力信号の位相をシフト可能なものであれば、どのような構成のものであってもよい。

#### 【0053】

また、バッファも、図3の構成のものに限られず、シフトレジスタの出力信号OUTの振幅をイネーブル信号OEを用いて増幅可能なものであれば、どのような構成のものであっても構わない。この場合には、イネーブル信号OEのハイレベル電圧とローレベル電圧間の電位差よりも、シフトレジスタ及びバッファでのハイレベル電源電圧とローレベル電源電圧との電位差を小さく設定するようにする。なお、バッファの出力回路としては、第9トランジスタT9及び第10トランジスタT10を含み、第9トランジスタT9のブーストストラップを用いて、出力信号BOUTを出力する構成とすることが望ましい。

#### 【0054】

最後に、本実施の形態においては、シフトレジスタとバッファにpMOSトランジスタを用いることとして、凸型パルスが下に向くスタートパルス信号STOPを伝送する駆動回路について説明を行ったが、これに限られるものではない。例えば、図9に示すように、シフトレジスタやバッファをnMOSトランジスタを用いて構成することとし、凸型パルスが上に向くスタートパルス信号STOPを伝送する駆動回路の構成としてもよく、この場

合にも上記と同様の効果を得ることができる。

【図面の簡単な説明】

【0055】

【図1】一実施の形態における表示装置の構成を示す回路図である。

【図2】上記表示装置における駆動回路の構成を示す回路図である。

【図3】上記駆動回路におけるシフトレジスタとバッファの構成を示す回路図である。

【図4】上記駆動回路の動作を示すタイミングチャートである。

【図5】シフトレジスタの出力信号とバッファの出力信号を重ねて示す図である。

【図6】比較例の駆動回路におけるシフトレジスタとバッファの構成を示す回路図である

10

【図7】比較例の駆動回路の動作を示すタイミングチャートである。

【図8】比較例のシフトレジスタの出力信号とバッファの出力信号を重ねて示す図である

。

【図9】駆動回路のシフトレジスタとバッファの別の構成を示す回路図である。

【符号の説明】

【0056】

1 0 ... 透明基板 , 1 1 ... 画素部

1 2 ... スイッチング素子

1 3 ... 画素電極 , 1 4 ... 液晶容量

1 5 ... 補助容量 , 2 1 ... 走査線駆動回路

20

2 2 ... 垂直シフトレジスタ

2 3 , 3 3 ... バッファ

3 1 ... 信号線駆動回路

3 2 ... 水平シフトレジスタ

3 4 ... 映像信号線

3 5 ... アナログスイッチ

4 1 ... 第1クロック端子

4 2 ... 第2クロック端子

4 3 ... 入力端子 , 4 4 , 4 9 ... 出力端子

4 6 , 4 7 ... 電源電極

30

4 8 ... イネーブル端子

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

- ハッファ BUF -

- シフトレジスタ SR -

【図7】

【図9】

- ハッファ BUF -

- シフトレジスタ SR -

【図8】

## フロントページの続き

|                                |               |            |

|--------------------------------|---------------|------------|

| (51)Int.Cl.                    | F I           | テーマコード(参考) |

| <b>H 03 K 17/687 (2006.01)</b> | G 09 G 3/20   | 6 23 B     |

|                                | G 09 G 3/20   | 6 23 H     |

|                                | G 11 C 19/28  | D          |

|                                | H 03 K 17/10  |            |

|                                | H 03 K 17/687 | A          |

(74)代理人 100101247

弁理士 高橋 俊一

(74)代理人 100098327

弁理士 高松 俊雄

(72)発明者 森田 哲生

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

F ターム(参考) 2H093 NA16 NA43 NA53 NC09 NC11 NC22 NC23 NC34 ND38 ND39

5C006 BB16 BC03 BC11 BC20 BF03 BF25 BF34 FA46 FA47

5C080 AA10 BB05 DD19 DD26 FF01 FF11 JJ02 JJ03 JJ04

5J055 AX64 BX16 CX30 DX14 DX48 DX83 EX07 EY21 EZ69 FX05

FX12 GX01