(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6063919号

(P6063919)

(45) 発行日 平成29年1月18日(2017.1.18)

(24) 登録日 平成28年12月22日(2016.12.22)

(51) Int.Cl.

H02M 3/155 (2006.01)

F 1

H02M 3/155

H

請求項の数 20 (全 16 頁)

(21) 出願番号 特願2014-501216 (P2014-501216)

(86) (22) 出願日 平成24年3月21日 (2012.3.21)

(65) 公表番号 特表2014-509185 (P2014-509185A)

(43) 公表日 平成26年4月10日 (2014.4.10)

(86) 國際出願番号 PCT/US2012/029996

(87) 國際公開番号 WO2012/129337

(87) 國際公開日 平成24年9月27日 (2012.9.27)

審査請求日 平成27年2月3日 (2015.2.3)

(31) 優先権主張番号 13/069, 251

(32) 優先日 平成23年3月22日 (2011.3.22)

(33) 優先権主張国 米国(US)

(73) 特許権者 513239634

レディリオン テクノロジーズ インコーポレイテッド

アメリカ合衆国、カリフォルニア州 94027, アザートン、パーカー アベニュー

- 61

(74) 代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100109346

弁理士 大貫 敏史

(72) 発明者 カッサヤン, レザ

アメリカ合衆国、カリフォルニア州 94027, アザートン、パーカー アベニュー

- 61

最終頁に続く

(54) 【発明の名称】広範な電圧振幅を通じた効率のよいDC-D C変換のための装置および方法

## (57) 【特許請求の範囲】

## 【請求項1】

共通コアに結合された2以上のインダクタと、

少なくとも1つの能動スイッチが入力電流路内にある2以上の能動スイッチと、

入力電圧に基づいて、2以上の可能なDC-D CトポロジーからDC-D Cトポロジーを選択し、電流を導通しているインダクタの総数が交互に変化し、前記選択されたトポロジーに従って電力変換が実施されるように、前記2以上の能動スイッチの1つが、前記選択されたトポロジーが変化しない限り、前記選択されたトポロジーに従ってオン又はオフに恒久的に固定され、前記2以上の能動スイッチの残りが、相補的方法で交互に電流を導通するように、前記2以上の能動スイッチを操作するコントローラと、

10

を備えるDC-D Cコンバータであって、

前記DC-D Cコンバータは、入力ノード及び出力ノードを有し、

前記入力電圧は、コンデンサを備えない経路に沿って、前記入力ノードから前記出力ノードに送られる、

DC-D Cコンバータ。

## 【請求項2】

前記電力変換がブースト動作である、請求項1に記載のDC-D Cコンバータ。

## 【請求項3】

前記電力変換がバック動作である、請求項1に記載のDC-D Cコンバータ。

## 【請求項4】

20

前記電力変換がフライバック動作である、請求項 1 に記載の DC - DC コンバータ。

**【請求項 5】**

受動スイッチをさらに含む、請求項 1 に記載の DC - DC コンバータ。

**【請求項 6】**

前記少なくとも 1 つの入力スイッチが入力負荷特性を監視する、請求項 1 に記載の DC - DC コンバータ。

**【請求項 7】**

少なくとも 1 つのスイッチが出力負荷特性を監視する、請求項 1 に記載の DC - DC コンバータ。

**【請求項 8】**

前記少なくとも 1 つの入力スイッチが残りのスイッチより大きい、請求項 1 に記載の DC - DC コンバータ。

**【請求項 9】**

前記出力ノードにセラミックコンデンサをさらに含む、請求項 1 に記載の DC - DC コンバータ。

**【請求項 10】**

前記コントローラが 25 % 以上のデューティサイクルのみを採用する、請求項 1 に記載の DC - DC コンバータ。

**【請求項 11】**

共通コアに結合された 2 以上のインダクタと、

20

少なくとも 1 つの能動スイッチが入力電流路内にある 2 ~ 4 の能動スイッチと、

入力電圧に基づいて、2 以上の可能な DC - DC トポロジーから DC - DC トポロジーを選択し、電流を導通しているインダクタの総数が交互に変化し、前記選択されたトポロジーに従って電力変換が実施されるように、前記 2 ~ 4 の能動スイッチの 1 つが、前記選択されたトポロジーが変化しない限り、前記選択されたトポロジーに従ってオン又はオフに恒久的に固定され、前記 2 ~ 4 の能動スイッチの残りが、相補的方法で交互に電流を導通するように、前記 2 ~ 4 の能動スイッチを操作するコントローラと、

を備える DC - DC コンバータであって、

前記 DC - DC コンバータは、入力ノード及び出力ノードを有し、

前記入力電圧は、コンデンサを備えない経路に沿って、前記入力ノードから前記出力ノードに送られる、

30

DC - DC コンバータ。

**【請求項 12】**

受動スイッチをさらに含む、請求項 11 に記載の DC - DC コンバータ。

**【請求項 13】**

前記少なくとも 1 つの入力スイッチが入力負荷特性を監視する、請求項 11 に記載の DC - DC コンバータ。

**【請求項 14】**

少なくとも 1 つのスイッチが出力負荷特性を監視する、請求項 11 に記載の DC - DC コンバータ。

40

**【請求項 15】**

前記少なくとも 1 つの入力スイッチが残りのスイッチより大きい、請求項 11 に記載の DC - DC コンバータ。

**【請求項 16】**

前記出力ノードにセラミックコンデンサをさらに含む、請求項 11 に記載の DC - DC コンバータ。

**【請求項 17】**

前記コントローラが 25 % 以上のデューティサイクルのみを採用する、請求項 11 に記載の DC - DC コンバータ。

**【請求項 18】**

50

入力電圧を受け取ることと、

25%～100%の交流デューティサイクルをもつ制御信号を複数の能動スイッチに印加することと、

前記制御信号に応答して、前記入力電圧に基づいて、2以上の可能なDC-DCTポロジーからDC-DCTポロジーを選択し、電流を導通しているインダクタの総数が交互に変化し、前記選択されたトポロジーに従って電力変換が実施されるように、前記複数の能動スイッチの1つが、前記選択されたトポロジーが変化しない限り、前記選択されたトポロジーに従ってオン又はオフに恒久的に固定され、前記複数の能動スイッチの残りが、相補的方法で交互に電流を導通するように、前記複数の能動スイッチを操作することと、

を含み、

10

前記複数の能動スイッチを操作することは、コンデンサを備えない経路に沿って、入力ノードから出力ノードに前記入力電圧を送ることを含む、

DC電力変換方法。

#### 【請求項19】

入力負荷特性を監視するための能動スイッチを採用することをさらに含む、請求項18に記載の方法。

#### 【請求項20】

出力負荷特性を監視するための能動スイッチを採用することをさらに含む、請求項18に記載の方法。

#### 【発明の詳細な説明】

20

#### 【技術分野】

#### 【0001】

[0001] 本発明は、全体として、電力変換に関する。特に、本発明は、広範な電圧振幅を通して動作可能な効率のよいDC-DCTコンバータに関する。

#### 【0002】

[0002] 改善された変換効率を有し、小型化されたDC-DCTコンバータに対する需要が高まっている。設計技術は様々であって、電圧または電流を下げる技術もあれば、電圧または電流を上げる技術もあり、さらに、電圧または電流を交互に上下させる技術もある。典型的なDC-DCTコンバータでは、1つ以上のスイッチが入力電力に接続され、コンデンサまたはインダクタがある位相において余剰エネルギーを蓄積し、この蓄積されたエネルギーが別の位相において出力ノードに放出される。

30

#### 【0003】

[0003] 各技術にはそれぞれ利点と欠点がある。コンポーネントのサイズ、全体的な効率および入力/出力電圧比の最適帯の間で複数のトレードオフが存在する。例えば、スイッチング周波数を上げることは、通常コンポーネントサイズの縮小につながるが、同時に、寄生容量によるスイッチング損失とスイッチ遷移損失を増大させる。結果として、全体的な効率が下がる。

#### 【0004】

[0004] 一般的なAC-DCT変換方法は、ブリッジ整流器を用いてAC入力をDCに変換した後、DC-DCTスイッチングコンバータを用いて適切なDC出力を生成するというものである。変換効率の改善とコンバータサイズの縮小という目的を同時に達成するためのこれまでの試みでは、全体的な効率への関心が支配的であった。AC-DCT変換において経験されるような、より広範な入力/出力電圧比にわたって、効率は特に重要である。AC電源は、通常、各サイクルにおいて広い範囲の瞬時電圧を経過し、このことが、特定の入力/出力電圧比のためにDC-DCTコンバータを最適化する試みを妨げている。

40

#### 【0005】

[0005] 入力電圧の大きな変動による負の影響を克服するための1つのアプローチとして、蓄積コンデンサに電荷を蓄積し、この蓄積された電荷をAC入力電圧が一定のレベルを下回ったとき（「遷移期間」という）に使うというアプローチがある。この方法には2つの欠点が伴う。第1に、遷移期間を通して十分なエネルギーを蓄積するために相対的に

50

大きなコンデンサが必要となる。第2に、遷移期間中、入力からわずかな電流しか流出しない、あるいは、電流が全く流出しないため、入力AC線からの電流流出がより狭い時間フレームに、たいていの場合、ピーク入力電圧近辺で起こることになる。このことが結果として、効率の悪い電力伝達および低効率をもたらす。

#### 【0006】

[0006] スイッチングコンバータは、採用する能動電力スイッチの数により主に3つのコンバータクラスに分類できる。2スイッチコンバータクラスには、バック、ブーストおよびフライバックコンバータが含まれる。3スイッチコンバータクラスには、フォワードコンバータが含まれる。4スイッチコンバータクラスには、ハーフブリッジおよびプッシュプルスイッチングDC-DCコンバータが含まれる。スイッチは能動スイッチまたは受動スイッチであり得る。能動スイッチはゲートを調節することにより制御される。ダイオードのような受動スイッチは個別に制御する必要はない。10

#### 【0007】

[0007] 以上を鑑みると、改善された電力変換技術を提供することが望ましい。特に、広範な電圧振幅に関連して利用されるコンバータにおいてスイッチング損失を減らし、コンポーネントサイズを縮小することが望ましい。

#### 【発明の概要】

#### 【0008】

[0008] 本発明の一実施形態は、共通コアに結合された2以上のインダクタと、2以上の能動スイッチとを有し、少なくとも1つの能動スイッチが入力電流路内にあるDC-DCコンバータを含む。コントローラは、DC入力が2以上のインダクタのうちの1つ以上を通して送られて電力変換動作が実施されるように、2以上の能動スイッチを操作する。20

#### 【0009】

[0009] 本発明の別の実施形態は、共通コアに結合された2以上のインダクタと、2~4の能動スイッチとを有し、少なくとも1つの能動スイッチが入力電流路内にあるDC-DCコンバータを含む。コントローラは、DC入力が2以上のインダクタのうちの1つ以上を通して送られてバック、ブーストおよびフライバック電力変換動作が交互に実施されるように、2~4の能動スイッチを操作する。

#### 【0010】

[0010] 本発明の一実施形態は、DC電力変換方法を含む。DC入力が受け取られる。25%~100%の交流デューティサイクルをもつ制御信号が能動スイッチに印加される。制御信号に応答して、共通コア上の2以上のインダクタのうちの少なくとも1つを通してDC入力が送られ、バック、ブーストおよびフライバック電力変換動作が交互に実施される。30

#### 【0011】

[0011] 開示されるDC-DCコンバータは、スイッチング損失の削減から超高効率を有し、非常に高いスイッチング周波数とコンポーネントの小型化、軽量化を可能にしている。さらに、上記コンバータは、小型の磁気コンポーネントを有する。また、上記コンバータは、高い出力DC負荷電流能力を提供する。

#### 【0012】

[0012] 開示される技術はスイッチングデューティサイクル変動を減らして改善された効率をもたらす。デューティサイクル変動は、ある範囲の電圧比または電流比を実施するために用いられる。デューティサイクルが変化して異なる伝達比に対応すると、寄生容量および/またはスイッチ遷移損失の影響でスイッチ損失が上昇する可能性がある。本発明は、1以上のスイッチをスイッチングモードチェンジャーとして利用する。これにより、大きな電圧または電流伝達比を達成しつつ、スイッチングデューティサイクルの大幅な変化の必要が低減される。40

#### 【図面の簡単な説明】

#### 【0013】

[0013] 本発明は、以下の詳細な説明を添付の図面と併せて参照することで、さらに十50

分に理解される。

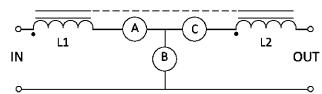

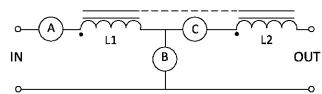

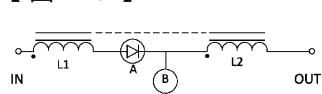

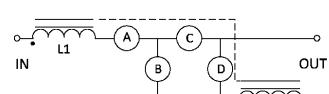

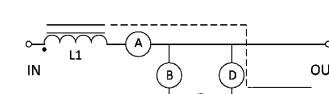

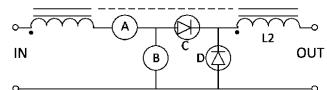

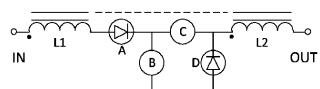

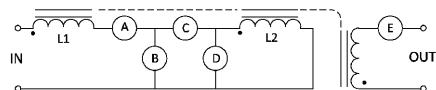

【図1】[0014] 図1a～1jは、本発明の3スイッチ実装のさまざまな実施形態を示す。

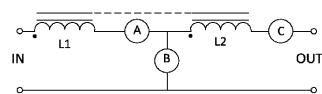

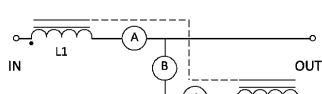

【図2】[0015] 図2a～2dは、受動スイッチを採用した3スイッチ実装のさまざまな実施形態を示す。

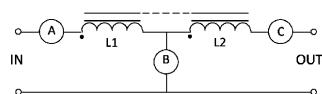

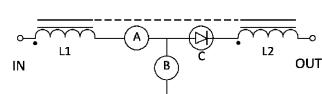

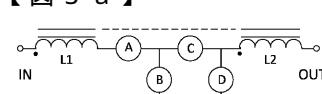

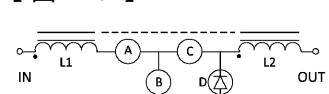

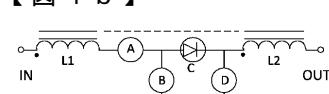

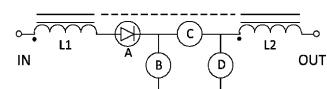

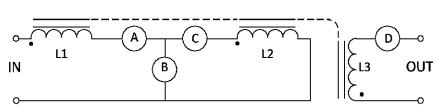

【図3】[0016] 図3a～3dは、本発明の4スイッチ実装のさまざまな実施形態を示す。

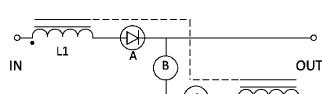

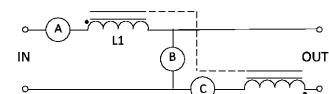

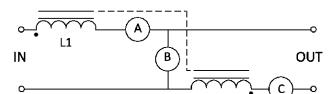

【図4】[0017] 図4a～4eは、受動スイッチを採用した4スイッチ実装のさまざまな実施形態を示す。

【図5】[0018] 図5a～5bは、分離出力を含む本発明の実施形態を示す。 10

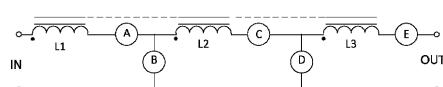

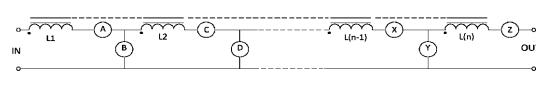

【図6】[0019] 図6a～6bは、本発明の開示された回路をデイジーチェーン構成としたものを示す。

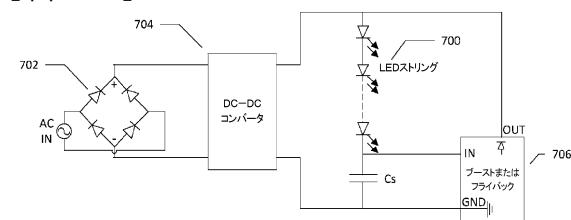

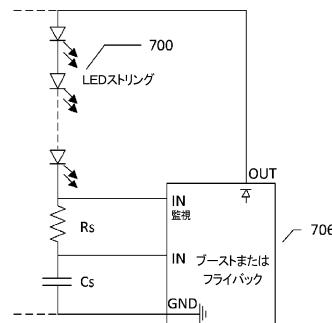

【図7】[0020] 図7a～7bは、本発明の実施形態にしたがって構成されたちらつき削減回路を示す。

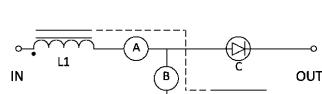

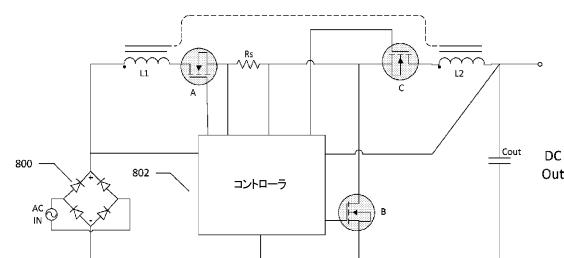

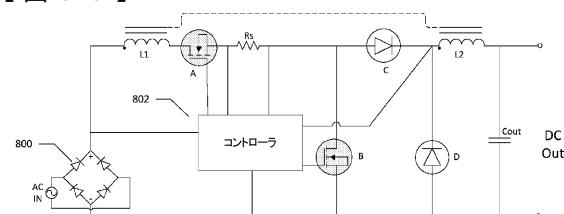

【図8】[0021] 図8aは、本発明の3スイッチ実施形態を組み込んだAC-DCコンバータを示す。 [0022] 図8bは、本発明の4スイッチ実施形態を組み込んだAC-DCコンバータを示す。

#### 【0014】

[0023] 同様の参照符号は、上記図面の複数の図にわたって対応する部分を指す。

#### 【発明を実施するための形態】 20

#### 【0015】

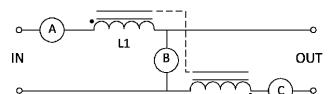

[0024] 図1a～1jは、本発明の3スイッチ実装のさまざまな実施形態を示す。スイッチAは常に入力経路内にあり、スイッチCは常に出力経路内にあることに注目する。スイッチBおよび/またはスイッチCの状態により、インダクタのエネルギー蓄積は、L1のみを通して、または、直列のL1およびL2を通して行うことができる。

#### 【0016】

[0025] 図1aにおいて、スイッチAは降圧(バック)変換を達成するための主切り替えスイッチとすることができます。スイッチBの状態はスイッチAの反転状態である。スイッチCは常にオン状態である。例えば、スイッチAが閉じられると、スイッチBは開かれるので、入力電圧が出力電圧よりも高いたびに、正電流がL1、スイッチA、スイッチCおよびL2を通って出力まで流れる。スイッチAを開いてスイッチBを閉じると入力が遮断される。この結果、インダクタL2に蓄積されたエネルギーがスイッチCおよびスイッチBを通して出力に放出される。 30

#### 【0017】

[0026] この構成は、インダクタのエネルギー蓄積経路及び放出経路がL1とL2の両方を使用するバックコンバータとは対照的である。図1aにおいて、L1=L2=L<sub>x</sub>である典型的な例では、インダクタコア内部にエネルギーが蓄積される間、バックコンバータの実効インダクタンスはおよそ4×L<sub>x</sub>である。図1aでは、L2だけがエネルギー放出経路内にあるため、実効インダクタンスはL<sub>x</sub>に等しい。

#### 【0018】 40

[0027] 図1aの別の運用の実施形態では、スイッチBがオンされ、スイッチCがスイッチAの反転状態として構成される。したがって、スイッチAがオンになると、出力電圧にかかるエネルギーがインダクタL1に蓄積される。スイッチAがオフされると、インダクタL2のエネルギーがスイッチCおよびスイッチBを通して放出される。この構成は、入力および出力が1つの線を共有するフライバックコンバータとして作用する。例えば、L1=L2=L<sub>x</sub>である場合、エネルギー蓄積経路および放出経路はL<sub>x</sub>を考慮し、これは1対1のフライバック変換を表す。L1およびL2に異なる値を選択し、デューティサイクルを変更することにより、本モードにおいて異なる実効電流または電圧伝達比を生成することができる。

#### 【0019】 50

[0028] 第3の構成では、図1aの回路がブースト(昇圧)モードの動作を模倣する。ここで、スイッチAは常にオンされており、スイッチCはスイッチBの反転状態として構成される。スイッチBをオンすると、インダクタL1にエネルギーが蓄積される。スイッチBをオフすると、インダクタのエネルギーがL1、L2、スイッチAおよびスイッチCを通して放出される。L1 = L2 = Lxである場合、インダクタエネルギー放出経路は4 × Lxに等しい。

#### 【0020】

[0029] スイッチA、BまたはCは、位相が一致して動作することも、位相がずれて動作することも可能であり、デューティサイクルが重なっていても、または、重なっていないなくてもよく、あるいはランダムに動作することも可能である。予め選択したL1およびL2の値によって、非常に広範囲の実効電流または電圧伝達比を生成することができる。これが、1つの物理的インダクタ(L1とL2は同じコア上にある)と少なくとも3つのスイッチのみで達成される。場合によって、システム内の異なるノードにコンデンサを追加して入力および出力リップル電流および/または電圧を減らすことができる。

10

#### 【0021】

[0030] 非常に広い入力電圧範囲にわたってデューティサイクル変化を最小限にとどめることにより、スイッチング損失が最小限に維持される。例えば、入力電圧が出力電圧より著しく低い場合、ブーストモードを選択することができる。入力/出力比が、L1/L2の比により近い場合、フライバックに等価な挙動が選択される。入力が出力電圧より高く一定の閾値を超える場合、バックモードが選択される。

20

#### 【0022】

[0031] ここで再びL1 = L2 = Lxの例を考える。さらに、出力電圧(Vo)の理想値がピーク入力電圧(Vi)の1/3、つまり、Vo = Viピーク/3と仮定する。バックモード動作に構成された場合、ピーク入力電圧の間、スイッチAは4 × Lxのインダクタンスを考慮する。両方の巻線が同じコア上にあるので、インダクタンス飽和電流(Isat)はただ1つの巻線が電流を受ける場合の半分である。インダクタンス実効電圧はVi - Vo = 3 × Vo - Vo = 2 × Voである。インダクタコアの飽和に必要な時間は、インダクタンスおよびインダクタ飽和電流に比例し、電圧：(4 × Lx × Isat / 2) / (2 × Vo) = Lx × Isat / Voに逆比例する。

30

#### 【0023】

[0032] 今度は、入力電圧がVo(この例ではViピークの1/3)に近く、フライバックモードが選択されると仮定する。本モードでは、入力インダクタンスはLxであり、L1を通した電圧はVi = Voである。インダクタコアの飽和に必要な時間は、Lx × Isat / Voに比例する。そのため、入力電圧がピーク電圧の1/3であっても、インダクタコアの飽和に必要な時間は同じである。

#### 【0024】

[0033] ブーストモードでは、スイッチAは常にオンされ、入力電流流出は、スイッチBがオンであるときにもオフであるときにも生じる。これにより入力電流流出を増加させることができる。そのため、フライバックモードと比較して、半分の入力電圧で同じ電力が入力から流出する。このことは、入力電力を流出可能な入力電圧範囲をさらに拡大する一方、従来の方法に比べて、スイッチング周波数をより狭い範囲に維持し、デューティサイクルの変動をより少なくする。

40

#### 【0025】

[0034] この方法のスイッチング損失に対する効果を検討するため、全てのコイルと全てのスイッチが寄生抵抗を有さず、スイッチの寄生容量と遷移損失以外に損失要因がないと仮定する。L1 = L2 = Lxである上述の例において、バックモードが用いられるピーク入力電圧では、ピーク入力電圧の1/3に相当するVoに達するために、スイッチAに対してわずか50%のデューティサイクルで十分である。数百ボルトでのスイッチングが可能で数アンペアの電流能力をもつ典型的なMOSFETは、通常、およそ10ナノ秒のスイッチ遷移時間と、およそ数百ピコファラッドの寄生容量をもつ。スイッチのスイッチ

50

ング損失を簡単に計算すると、 $P_{SW} = (V \times I \times (tRISE + tFALL)) / (2 \times T)$  となり、この式において、 $P_{SW}$ はスイッチ電力損失、 $V$ はスイッチがオフされている間にスイッチを通した電圧、 $I$ はスイッチ電流、 $tRISE$ および $tFALL$ はスイッチ立ち上がり時間および立ち下がり時間、 $T$ はスイッチング周期である。 $tRISE$ および $tFALL$ が 10 ns である場合、各能動スイッチ（スイッチ A および B）におけるスイッチ遷移損失を 2 % 未満に維持するためにスイッチング周波数をおよそ 1 MHz に制限することが望まれるかもしれない。ここで入力電圧が 300 V、入力電流が 1 A と仮定してみる。50 % のデューティサイクルでは、入力電力は、 $300 \times 1 \times 50\% = 150$  W である。合計損失が 4 %（おおよそスイッチ A に 2 %、スイッチ B に 2 %）では、効率は 96 % となり、144 W が出力に伝達される。 $300V$ の $1/3$ （ $300/3 = 100$  V）の理想出力電圧のため、これにより 1.44 A の出力が生成される。このシナリオでは、スイッチ A および B 合わせて 6 W が失われる。今度は、入力電圧が入力ピーク電圧の $1/9$ （ $300/9 = 33.33$  ボルト）であり、ブーストモードが選択されていると仮定する。スイッチ B および C において 50 % のデューティサイクルスイッチングであると、出力で 100 V が生成される。インダクタ放電経路は L1 および L2 であるので、入力からの合計流出電力は $(33.33 \times 2 \times 50\% + 33.33 \times 1 \times 50\%) = 50$  W である。これが 333.33 KHz で達成できるので、合計スイッチング損失はわずかおよそ 1.33 % である。この場合、49.33 W が出力に伝達され、0.67 W がスイッチ B および C で失われる。

## 【0026】

[0035] 本発明の上記の例では、最小効率は、ピーク入力電圧で、1 A の飽和電流を有するコイルを直列巻線 L1 および L2 の両方に用いた場合に、96 % であった。これは、従来技術のフライバックコンバータとは対照的である。従来技術のフライバックコンバータで同レベルの低電圧性能を達成するためには、1 ~ 3 の比率のトランスが必要である。この比率で、33.33 V の入力電圧と、入力および出力スイッチに 50 % のデューティサイクルにより、出力に 100 V が生成され、同等の効率が生成される。ここで、入力電圧が 300 V に上がった場合、同じ 1 ~ 3 の比率のトランスで出力に 100 V を生成するためにはデューティサイクルを 10 % に下げなければならない（ $300 \times 3 / 1 \times (10\% / 90\%) = 100$  V）。このことは、相対的スイッチング損失が 5 の倍数で増加（本発明では 50 % であるのに対してフライバックコンバータを用いると 10 %）し、入力電力流出が 5 倍割られる（ $300V \times 1A \times 10\% = 30W$ ）ことを意味している。

## 【0027】

[0036] 要するに、このことは、入力電圧 300 V の従来技術のフライバックコンバータでは、本発明と比較して、合計入力電力流出、および、その後の出力電力供給が 5 の倍数で減少する（150 W に対して 30 W）。従来技術のフライバックコンバータにおけるこの損失を補償するためにとりうる選択肢は、インダクタ飽和電流およびインダクタ蓄積容量を 5 倍に上げ、オン状態の入力電流を 5 A に上げ、スイッチング周波数を比率 5 で下げて  $P_{SW}$  の上昇を補償することのみである。インダクタンスと飽和電流を 5 倍に上げることは、概略で、5 倍を超えるコイルサイズの増加を意味する。入力電流が上昇し、動作周波数が低下すると、同じ入力リップル電圧を維持するために、入力コンデンサは  $5 \times 5 = 25$  倍の大きさが必要になる。インダクタンスの上昇はインダクタ寄生抵抗の上昇を伴う。

## 【0028】

[0037] このように、従来技術では、失われたデューティサイクルを補償するためにコンポーネントサイズを拡大する必要がある。本発明ではこの問題がない。なぜなら、デューティサイクルの変動はごくわずかだからである。実際、本発明におけるスペースの節約は、従来技術と比較した場合、1 枝より大きな違いに達し得る。最新式の高電圧スイッチングレギュレータのほとんどは、スイッチング損失の懸念からおよそ 100 キロヘルツのスイッチング動作で制限されている。本発明は、300 V の入力から 100 V の出力で 150 W の場合に、500 KHz を超えるスイッチング周波数で、95 % を超える効率で動

作することができる。同時に、合計コンポーネント容積が10～30倍減少する。著しく小さい入力コンデンサ（上記の例では25倍の小ささ）は、設計者が通常の電解コンデンサの代わりにセラミックコンデンサのような信頼性の高いコンデンサを使用することを可能にする。このことは、信頼性の高い電源を設計する上で非常に重要である。電解コンデンサの寿命は105程度で通常およそ数千時間であるのに対して、セラミックコンデンサは同様の条件で数十年も使用できる。

#### 【0029】

[0038] 各構成において、スイッチAは入力経路内にあり、入力負荷特性を監視するために使用できることに注目する。スイッチCは常に出力経路内にあり、出力負荷特性を監視するために使用することができる。これは、設計者がシステムの力率を監視し、スイッチング周波数またはスイッチデューティサイクルを調整して一定の入力または出力負荷特性を維持しようと意図する場合に特に有益である。例えば、入力電圧に基づいて、疑似抵抗挙動を示すように入力電流を調整して、1に非常に近い力率を達成することが可能である。あるいは、あるほぼ一定の値のために入力電流または合計入力電力を調整することもできる。実効等価入力抵抗と比較してより低い入力電圧で入力電流が上昇すると、「動的負性抵抗（dynamic negative resistance）」が生成され、これは、より低い入力電圧で入力等価インピーダンスが減少することを意味する。家庭または工業環境において、これは、AC線上に設けられた他の主要な装置の非線形電流流出を補償するため、かつ、場合によってはグリッド電力線効率を上げるために用いることができる。10

#### 【0030】

[0039] 図1bは図1aと同様であるが、スイッチAとインダクタL1の位置が変更されており、スイッチAが入力に直接接続され、続いてインダクタL1が接続されている。図1cは図1aと同様であるが、スイッチCとインダクタL2の位置が変更されており、スイッチCが出力に直接接続され、続いてインダクタL2が接続されている。図1dは図1aと同様であるが、スイッチAが入力に、スイッチCが出力にあり、インダクタL1およびL2が共通の配線を有している。20

#### 【0031】

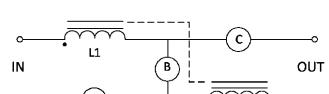

[0040] 図1eは、スイッチCとL2が出力の戻り経路内にある構成を示している。図1fは図1eと同様であるが、スイッチAとインダクタL1の位置が変更されており、スイッチAが入力に直接接続され、続いてインダクタL1が接続されている。図1gは図1eと同様であるが、スイッチCとインダクタL2の位置が変更されており、スイッチCが出力に直接接続されている。図1hは図1gと同様であるが、スイッチAが入力に直接接続されている。30

#### 【0032】

[0041] 図1iは図1eと同様であるが、スイッチAおよびCが戻り経路内にあり、インダクタL1およびL2が共通の配線を有する。図1jは図1eと同様であるが、スイッチAが入力戻り経路内にあり、インダクタL2が出力戻り経路内にある。

#### 【0033】

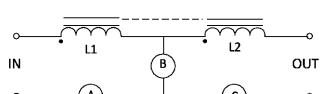

[0042] 図2a～2dは、少なくとも1つの受動スイッチ（すなわち、能動的に制御されないスイッチ、ダイオードは受動スイッチである）を含む3スイッチ実装を示す。図2aは図1aと同じであるが、スイッチCがダイオードである。図2bは図1eと同じであるが、スイッチAがダイオードである。図2cでは、スイッチCがダイオードであり、インダクタL2が出力戻り経路内にある。図2dでは、スイッチAがダイオードであり、スイッチCが出力戻り経路内にある。40

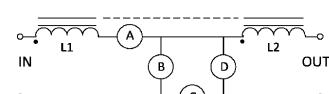

#### 【0034】

[0043] 本発明の別の実施形態は4つのスイッチを利用する。この構成の利点の1つは、より簡易なスイッチ制御である。図3a～3dは、本発明のさまざまな4スイッチ実施形態を示す。図3aは、図1aにおける3スイッチ構成を拡張したものであり、スイッチDが追加されている。図3bは図3aと同様であるが、スイッチCが入力戻り経路と出力戻り経路の間の合流点にある。図3cは図3aと同様であるが、インダクタL2が出力戻50

り経路内にある。図3dは図3bと同様であるが、インダクタL2が出力戻り経路内にある。

#### 【0035】

[0044] 図4a～4eは、能動的に制御されるスイッチのうちの1つまたは2つがダイオードに置き換えられたものを示す。図4aは図3aと同じであるが、スイッチDがダイオードである。図4bは図3aと同じであるが、スイッチCがダイオードである。図4cは図3aと同じであるが、スイッチCおよびDがともにダイオードである。図4dは図3aと同じであるが、スイッチAおよびDがともにダイオードである。図4eは図3aと同じであるが、スイッチAがダイオードである。

#### 【0036】

[0045] 図4cは、図4aを簡略化したもので、能動的に制御されるスイッチのうちの2つがダイオードに置き換えられている。図4cでは、スイッチBが閉じられると、スイッチAが切り替えられることにより、共有線をもつフライバックコンバータとして有効に機能することができる。L1は一次的トランス、L2は二次的トランスとして機能する。

#### 【0037】

[0046] 図4a～4eの回路において、スイッチBが開かれた状態でスイッチAを切り替えることはバックコンバータという結果になる。この条件では、出力電圧が入力電圧より常に低い。スイッチAとCが閉じられ、ViがVoより高いと、正電流がL1、スイッチA、CおよびL2を流れる。その結果、エネルギーがL1およびL2に蓄積される。スイッチAが開くと、L2およびスイッチDが伝導路として機能し、エネルギーが出力に伝達される。

#### 【0038】

[0047] 異なる構成では、スイッチBが閉じられ、スイッチAを切り替えることが入力および出力間に共通線をもつフライバックコンバータという結果になる。この条件では、出力電圧が入力電圧より低い場合も高い場合もあり得る。スイッチAが閉じられてスイッチCが開かれると、出力電圧にかかわらず、L1、スイッチAおよびスイッチBを電流が流れる。この結果、エネルギーがL1に蓄積される。スイッチAが開くと、L2およびスイッチDが伝導路として機能し、エネルギーが出力に伝達される。

#### 【0039】

[0048] また別の構成では、スイッチAがオンされ、スイッチBがオンオフを切り替えて使用される。この場合、コンバータは改良型ブーストコンバータとして機能する。スイッチBがオン、スイッチCがオフであると、出力電圧にかかわらず、電流がスイッチA、BおよびL1を流れる。そのため、L1がエネルギーを蓄積する。スイッチBがオフされ、スイッチCがオンされると、L1およびL2からのインダクタエネルギーが出力に印加される。

#### 【0040】

[0049] スイッチAおよびBを切り替えることと、重複するデューティサイクルとの他の組合せを用いて、他の電圧または電流伝達比を達成することができる。これにより、異なる電流または電圧伝達比、および、等価分離パイ型トポロジー(equivalent Split-pi topology)を含む、他のスイッチング挙動が可能になる。

#### 【0041】

[0050] 本発明の1つの利点は、バック・ブースト機能を実施するための簡易化された制御スキームにある。全てのシナリオにおいて、スイッチAは常に入力電流を切り替える入力電流経路内にある。あるシナリオでは、スイッチBが伝達比の「モードチェンジャー」として機能して、フライバックコンバータモードかバックコンバータモードかを選択することができる。これら2つのスイッチは連動して動作することも、あるいは、それぞれ独立して動作することも可能である。これら2つのスイッチが独立して動作すると、高電圧DC-DCおよびAC-DCコンバータの設計をさらに容易にすることが可能になる。例えば、スイッチAをその電流に応じて起動し、スイッチBを瞬時入力電圧レベルに基づいて起動することができる。これにより、スイッチAは、他のスイッチと通信する必要な

10

20

30

40

50

しに、高周波かつ非常に高い電圧で動くことができる。高電圧差で動くことが可能な高速通信経路を設計することは難しい課題であり、スイッチングされる高電圧DC - DCコンバータにとっての主な制限要因の1つでもある。スイッチAが常に入力電流経路内にあるので、当該スイッチを、入力負荷特性を監視し、かつ、所望の力率のために必要な調整をするために使用することができる。

#### 【0042】

[0051] 本発明の1つの利点は、より広い範囲での任意の伝達比にある。 $L_1$ および $L_2$ の両方が同一コア上にあるため、入力電力が $L_1$ および $L_2$ の両方を通ると、インダクタンスは、 $L_1$ 、 $L_2$ 、または $L_1$ と $L_2$ の合計よりかなり高くなる。例えば $L_1 = L_2 = L_x$ である場合、実効インダクタンスはほぼ $4 \times L_x$ である。このことは、コンバータがバックモードで動作する際により低いリップル電流とするのに役立つ。フライバックまたはブーストモードでは、 $L_1$ だけが入力伝導経路内にあるので、入力スイッチAは $L_1$ だけを考慮し、この $L_1$ は $L_x$ に等しい。この条件は、とりわけフライバックモードにとって有益であり、より高い周波数での動作が可能になる。より低いインダクタンスは電流をより速く立ち上げ、インダクタコア材料内部に同レベルの蓄積エネルギーをより短時間で達成する。フライバックまたはブーストモードの動作は、通常、入力電圧が出力電圧より低いかそれに近いときに必要になる。より高い周波数での動作は、寄生容量がより低い電圧で動作するために、より耐性が高い。入力電圧が低ければスイッチ遷移損失は小さい。バックモードの間、直列の $L_1$ および $L_2$ によって形成される入力経路が考慮する高いインダクタンスは、リップル電流を下げるのに役立ち、寄生容量およびスイッチング損失を減少させる。異なる $L_1$ および $L_2$ の値と比率を選択することにより、少ない数のコンポーネントで、非常に広い範囲で任意の電圧および電流伝達比を達成することができる一方、スイッチング損失を最小限にとどめることができる。10

#### 【0043】

[0052] 同一コア上に第3のインダクタ $L_3$ を追加して、3スイッチ構成または4スイッチ構成のいずれかで分離出力を生成することが可能である。それぞれの場合に、DC出力を生成するために、能動的に制御されるスイッチまたはダイオードが新たに必要になる。図5aおよび5bは分離インダクタ $L_3$ の例を示す。図5aは、図1aの回路に追加のインダクタ $L_3$ とスイッチDを加えて分離出力を生成するものを示す。図5bは、図3aの分離出力版であり、インダクタ $L_3$ とスイッチEが追加されているものを示す。この構成は、2つの結合されたインダクタを用いる場合の利点の全てを備えつつ、分離DC出力を有する。20

#### 【0044】

[0053] この新規なコンバータの複数のステージを、同様のステージや他の標準的DC - DCステージにデイジーチェーン式につなげて電力変換の可能性を拡大することが可能である。後続ステージまたは先行ステージにおける単一または結合されたインダクタは、 $L_1$ および $L_2$ （および分離版では $L_3$ ）と同一コアに結合することも、あるいは、別個のコア上とすることも可能である。図6aおよび6bはこのマルチステージアプローチの例を示す。図6aでは、スイッチBがオンされるか、または、スイッチDがオンされると、スイッチAの異なる戻り経路が生成される。スイッチAが閉じられると、他のスイッチの状態、この場合はスイッチBおよびDの状態によって、電流は同一コア上の異なる巻線を通り得る。 $L_1$ 、 $L_2$ 、 $L_3$ の値およびスイッチA～Eのデューティサイクルにより、異なる電圧または電流伝達比が生成可能である。同一コア上に新たなインダクタ、この場合は $L_3$ が存在すると、周波数またはデューティサイクルを極端な条件にすることなく、任意の伝達比を得るさらなる可能性が提供される。図6bは、同一コア上にn個のインダクタがあり、さらに多くのデイジーチェーン式につながれたステージを形成するためにより多くのスイッチがある場合を示している。30

#### 【0045】

[0054] この新規なコンバータの1つの用途として、発光ダイオード(LED)の駆動がある。AC入力は、0からピーク正電圧まで、そして0に戻った後、負電圧になり、負40

のピークに達した後、再び 0 に戻るという変動する電圧をもつ。従来の商用および工業用 A C 電源では、これが通常 1 秒当たり 50 または 60 回起こる。このように広範囲に変動する電圧が高効率 A C - D C コンバータの設計を難しいものにしている。L E D ストリングは、これを通して大きな電圧降下をもつことがある。良好な効率を維持するため、抵抗負荷と同様に、各サイクルにおいて A C 線から電力を流出させる必要がある。

#### 【 0 0 4 6 】

[0055] 典型的な A C - D C 変換のアプローチは、ダイオードブリッジを用いて入力 A C を整流された D C 電圧に変換し、その後、この D C 電圧を D C - D C コンバータの入力に用いて適切な出力電圧を生成するというものである。入力電圧が L E D ストリングの電圧降下よりも概ね高い場合、降圧レギュレータが必要である。入力電圧が L E D ストリングの電圧降下よりも概ね低い場合、昇圧レギュレータが必要である。開示されるコンバータは降圧および昇圧動作をサポートする。10

#### 【 0 0 4 7 】

[0056] A C 電圧の変動により生じる A C 線のちらつき効果を除去または低減することが望ましい。ちらつく光の一般的な例は蛍光灯である。A C で動作する蛍光ランプは、これを駆動する A C 線の周波数の 2 倍の周波数を生成することができる。A C で駆動される L E D 光では、通常、ダイオードブリッジ整流器が A C 線周波数の 2 倍の優位周波数成分を有する出力を生成する。例えば 60 H z の A C 線の場合、ダイオードブリッジ整流器は 120 H z の優位周波数を有する出力を生成する。システムにエネルギーが蓄積されていないと、線間電圧の変化について光強度が変わり 120 H z のちらつきを起こし得る。人間は 50 H z 程度より高い周波数の光のちらつきを目で見ることはできないが、人によっては、感覚系が何らかの形でこのちらつきを検出することができる。蛍光光が作業場に導入されて以来、頭痛、眼精疲労および全般的な目の不調が訴えられている。20

#### 【 0 0 4 8 】

[0057] 本発明はバックまたはブースト動作を実施する能力を有する。これにより、電力が入力から流出されない期間が短縮される。そのため、「遷移期間」と呼ばれる低い瞬時入力電圧中に L E D を駆動するために必要な蓄積量が減少する。本発明で使用される別のアプローチは、出力負荷を、当該負荷と直列のコンデンサまたは超コンデンサを使って遷移期間中に駆動するというものである。簡易なブーストまたはフライバックステージをこのコンデンサに接続することができ、そのエネルギーを使って必要なときに L E D を駆動することができる。30

#### 【 0 0 4 9 】

[0058] 図 7 a は、直列の蓄積コンデンサ C s をもつ L E D ストリング 700 を示す。A C 入力が整流器 702 に印加されると、この整流器が D C 入力を生成し、それが D C - D C コンバータ 704 に印加される。D C - D C コンバータ 704 の出力は L E D ストリング 700 に印加される。コンデンサ C s は L E D ストリング 700 と直列になっており、電流が L E D ストリング 700 を流れるとエネルギーを蓄積する。コントローラ 706 はコンデンサ C s の入力および出力ノードに接続される。コントローラ 706 がブーストまたはフライバック変換を実施する。40

#### 【 0 0 5 0 】

[0059] コントローラ 706 は、遷移期間中、コンデンサ C s の蓄積エネルギーを使って L E D ストリング 700 を駆動するように設計することができる。A C 線から受け取る電気エネルギーが高い場合、エネルギーが蓄積され、このエネルギーが、A C 線から受け取るエネルギーが低いときに L E D ストリング 700 を駆動するために用いられる。D C - D C コンバータ 704 からの電力が増加するにつれて、出力電流によって L E D ストリング 700 および直列コンデンサ C s が充電される。L E D ストリング 700 の電圧降下は、コンデンサ C s の電圧降下と相まって、D C - D C コンバータ 704 により生成される電流を減少させる。瞬時電力はほぼ一定であり、 $P = V \times I$  である。ここで、「P」は瞬時電力、「V」は出力電圧、「I」は出力電流である。出力に放出されるエネルギーのあるパケットにとっては、出力電圧降下の増大により実効電流が減少する。直列コンデン50

サ  $C_s$  に蓄積されたエネルギーは、 $0.5 \times C_s \times V^2$  として計算可能である。このエネルギーを使って LEDストリング700を駆動すると、直列コンデンサの電圧降下が減少し、それにより実効スイッチングDC-D C出力電流が増加する。適切な設計により、この直列コンデンサ（または超コンデンサ）の定格電圧を、LEDストリング700の電圧降下より低く、これと等しく、または高くすることができる。このアプローチはちらつき削減のために必要な蓄積システムの設計を簡易化する。

#### 【0051】

[0060] 図7bは、同じステージに抵抗成分  $R_s$  を追加したものを示す。 $R_s$  は、LEDストリング700および  $C_s$  と直列にすることが可能なセンス抵抗器である。 $R_s$  は、LEDストリング電流の厳密な監視を可能にし、かつ、ちらつき削減ステージの精度を高めるための、非常に低い抵抗である。 10

#### 【0052】

[0061] 図8aは、本発明の3スイッチ実施形態を組み込んだAC-DCコンバータの例を示す。AC入力は整流器800に印加される。コントローラ802はスイッチA、BおよびCのスイッチングを調節する。整流器800からの整流されたDC電圧がDC出力より高い場合、コントローラ802はスイッチA、BおよびCを以下のように構成する。スイッチAを主切り替えスイッチとし、スイッチCをスイッチAの反対状態とする一方、スイッチBはオフとする。これによりバックモードを模倣する。 $R_s$  を流れる電流が直列のL1およびL2の飽和電流に達するまで、スイッチAをオンにし、その後、L2を流れる電流がゼロに達するまでスイッチAをオフ、スイッチCをオンにする。これによりスイッチAがアクティブとなる次のサイクルが開始される。 20

#### 【0053】

[0062] ブリッジ整流器800からの整流されたDC電圧が、 $(L_1 / (L_1 + L_2)) \times DC\text{出力}$  よりも低い場合、コントローラ802はスイッチAをオンに構成し、スイッチBを主切り替えスイッチ、スイッチCをスイッチBの反転とする。これによりブースト等価な変換が提供される。スイッチBは、 $R_s$  の電流がL1飽和電流に達するまでオンにされ、その後、直列のL1およびL2を流れる電流がゼロに達するまでオフされる。 20

#### 【0054】

[0063] ブリッジ整流器800からの整流されたDC電圧が、 $(L_1 / (L_1 + L_2)) \times DC\text{出力}$  とDC出力の間にある場合、コントローラ802は各スイッチを以下の通り構成する。スイッチAを主切り替えスイッチに、スイッチBをオンに、スイッチCをスイッチAの反転状態にする。上述のように、これにより1つの共通入力出力線をもつフライバック変換が模倣される。スイッチAは、 $R_s$  の電流がL1飽和電流に達するまでオンされ、その後、L2を流れる電流がゼロに達するまでオフされる。図8aにおいて、出力リップル電圧を減らすために、場合によってコンデンサ  $C_{out}$  がDC出力に追加される。この種の出力コンデンサは本発明の他の実施形態でも使用し得る。 30

#### 【0055】

[0064] 図8bは4スイッチによる同様の回路を示す。コントローラ802はスイッチAおよびBのみを制御する。スイッチCおよびスイッチDはダイオードである。このコントローラは、本発明の他のコントローラと同様、バック、フライバック、ブーストの3つのモードを実施することができる。 40

#### 【0056】

[0065] 当業者であれば、本発明の比較的簡単な回路がわずか2つの能動スイッチによってバック、フライバックおよびブーストモードの動作をサポートすることを理解するであろう。これは、コンポーネントコストの削減、小型化および製造の容易性を促進する。有利なことに、各動作モードの間のデューティサイクル遷移は比較的小さく、それにより電力損失が減少する。例えば、 $3.6 \times$ の入力電圧スパン ( $V_{out}/6$  から  $V_{out} \times 6$  の範囲の入力電圧) を、25%を下ることのないデューティサイクル範囲によってサポートすることができる。1対1のフライバックコンバータでは、同じ $3.6 \times$ の入力電圧スパンにわたって、デューティサイクルが2.7%にも降下してしまい、大きな電力損失とな 50

る。したがって、本発明は、従来技術のフライバックコンバータに対してデューティサイクル効率の面で9.25倍の向上をもたらす。

【0057】

[0066] 本発明は、 $100 \times (t_{FALL} + t_{RISE})$  の周期のスイッチング周波数をサポートしつつ、9×の入力電圧変化（例えば、 $V_{out}/3$  から  $V_{out} \times 3$ ）にわたって95%を超える効率を維持する。これは、10nSの立ち下がり・立ち上がり時間と有する典型的なスイッチでは、500KHzのスイッチング速度になる。有利なことに、本発明の回路の構成は、わずか0.25c.c程のインダクタコアを使って50Wを超える変換を可能にする。

【0058】 10

[0067] LEDドライバ以外にも、本発明は、広範囲に変動するACまたはDC電圧をもつあらゆる環境で使用することができる。かかる用途の例としては、ノイズのある線からの電気通信機器駆動電力、ノート型コンピュータ、手持ち型デバイスといったバッテリで動作するデバイス、あるいは、自動車、電車、船舶、飛行機、その他の乗物の電源のためのAC-DCまたはDC-DCコンバータがある。

【0059】

[0068] 本発明の別の用途としては、あらゆる分離されたAC-DCまたはDC-DC電源がある。これには、携帯型電源、携帯型コンピュータ電源、サーバコンピュータ電源が含まれるがこれらに限られない。

【0060】 20

[0069] 説明を目的とした上記の記載では、本発明の十分な理解のために特定の用語を用いた。しかしながら、特定の具体的な事項が本発明の実施のために必要であるわけではないことが当業者には明らかであろう。したがって、本発明の特定の実施形態に関する上記の記載は、例示および説明の目的で提示される。かかる記載は、網羅的であること、あるいは、開示された形態そのものに本発明を限定することを意図したものではなく、当然のことながら、上記教示を考慮して多くの改変および変更が可能である。本発明の原理とその実際の用途をもっともよく説明し、それによって、本発明と、検討される特定の使用に適するようさまざまな改変を加えたさまざまな実施形態とを他の当業者がもっともよく利用できるように、上記実施形態は選ばれかつ説明された。添付の特許請求の範囲およびその均等物によって本発明の範囲が画定されることが意図されている。 30

【図1a】

Figure 1a

【図1b】

Figure 1b

【図1c】

Figure 1c

【図1d】

Figure 1d

【図1e】

Figure 1e

【図2a】

Figure 2a

【図2b】

Figure 2b

【図2c】

Figure 2c

【図2d】

Figure 2d

【図3a】

Figure 3a

【図1f】

Figure 1f

【図1g】

Figure 1g

【図1h】

Figure 1h

【図1i】

Figure 1i

【図1j】

Figure 1j

【図3b】

Figure 3b

【図3c】

Figure 3c

【図3d】

Figure 3d

【図4a】

Figure 4a

【図4b】

Figure 4b

【図4c】

Figure 4c

【図4d】

Figure 4d

【図4e】

Figure 4e

【図5a】

Figure 5a

【図5b】

Figure 5b

【図6a】

Figure 6a

【図6b】

Figure 6b

【図7a】

【図7b】

【図8a】

【図8b】

---

フロントページの続き

審査官 鈴木 重幸

(56)参考文献 特開2008-109775(JP,A)

特開2010-068619(JP,A)

特開2008-092635(JP,A)

特開2011-035949(JP,A)

特開2004-135442(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/00 - 3/44