OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

⑪ Número de publicación: **2 268 815**

⑮ Int. Cl.:

**G11B 20/18** (2006.01)

**G11B 20/12** (2006.01)

**G11B 20/10** (2006.01)

**G11B 19/04** (2006.01)

⑫

### TRADUCCIÓN DE PATENTE EUROPEA

T3

⑯ Número de solicitud europea: **99108324 .7**

⑯ Fecha de presentación : **19.12.1994**

⑯ Número de publicación de la solicitud: **0949619**

⑯ Fecha de publicación de la solicitud: **13.10.1999**

⑭ Título: **Aparato de reproducción de datos.**

⑯ Prioridad: **18.12.1993 JP 5-344012**

⑮ Titular/es: **SONY CORPORATION**

6-7-35 Kitashinagawa Shinagawa-ku

Tokyo 141, JP

⑯ Fecha de publicación de la mención BOPI:

**16.03.2007**

⑯ Inventor/es: **Kawamura, Makoto y

Fujinami, Yasushi**

⑯ Fecha de la publicación del folleto de la patente:

**16.03.2007**

⑯ Agente: **Elzaburu Márquez, Alberto**

ES 2 268 815 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

## DESCRIPCIÓN

Aparato de reproducción de datos.

5 **Campo técnico**

El presente invento se refiere a un aparato de reproducción de datos y a un medio de almacenamiento de datos que pueden aplicarse preferiblemente, por ejemplo, a los sistemas que utilizan un medio de almacenamiento con imágenes en movimiento digitalizadas almacenadas.

10 **Antecedentes**

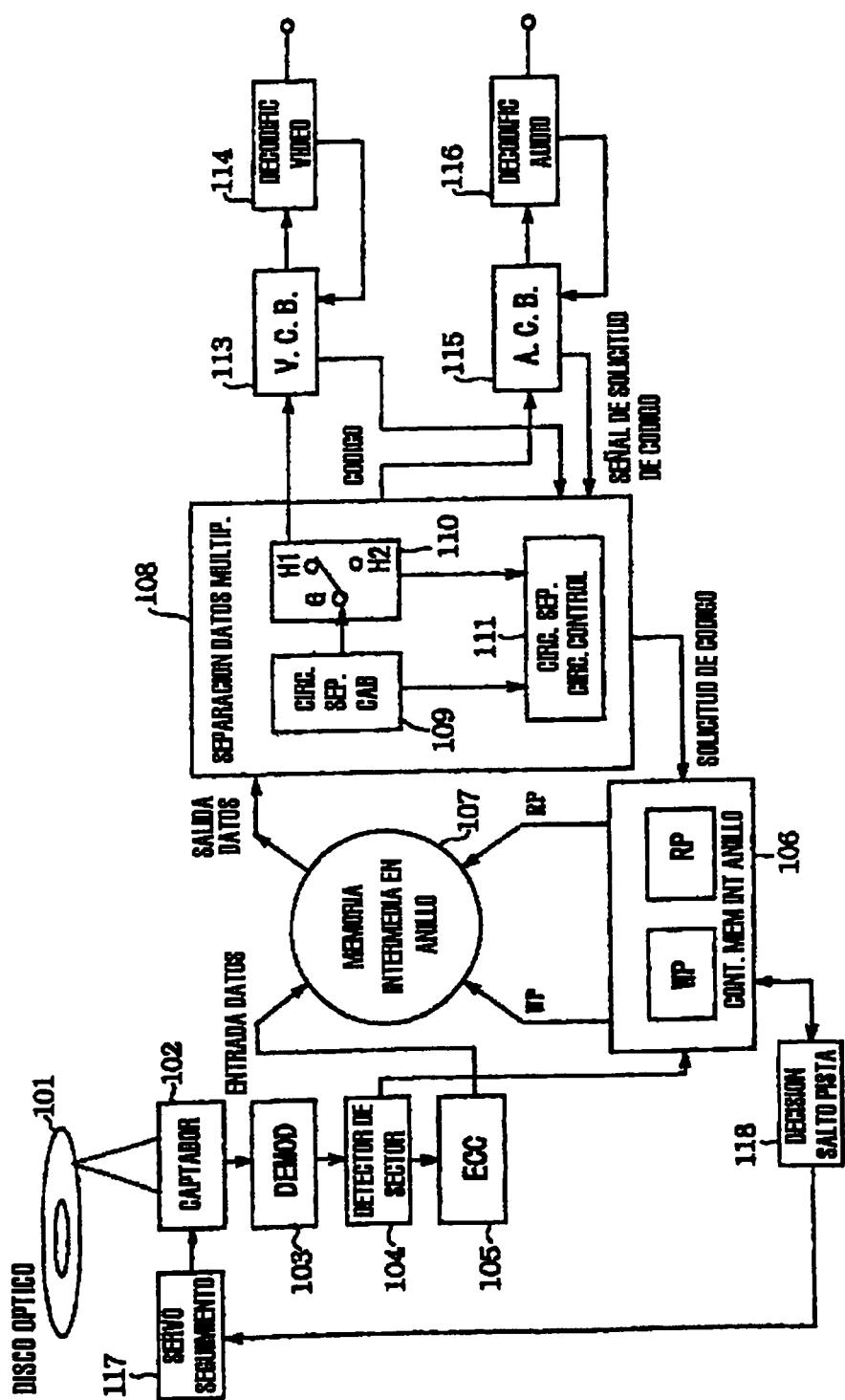

Un aparato de reproducción de datos convencional que reproduce datos de un disco como medio de almacenamiento con imágenes en movimiento digitalizadas almacenadas en el mismo, se describe como aparato de reproducción de datos sensible a velocidades de reproducción variables, como se muestra en la figura 35, en la patente japonesa del solicitante expuesta a inspección pública el 6 de mayo de 1994 con el número 6-124,168. Este aparato de reproducción reproduce datos almacenados en un disco óptico 101 utilizando un captador 102. El captador 102 irradia el disco óptico 101 con haces de láser y utiliza la luz reflejada por el disco óptico 101 para reproducir los datos almacenados en el mismo. Las señales reproducidas por el captador 102 son suministradas a un demodulador 103. El demodulador 103 demodula las señales reproducidas proporcionadas por el captador 102 óptico para transferirlas a un detector 104 de sectores.

El detector 104 de sectores detecta una dirección almacenada en cada sector de los datos suministrados para suministrarla a un circuito 106 de control de memoria intermedia en anillo. Transmite también los datos a un circuito 105 de corrección de error situado después del detector de sectores manteniendo la sincronización de sectores. El detector 104 de sectores envía una señal de error de número de sector a un circuito 118 de determinación de salto de pista a través del circuito 106 de control de memoria intermedia en anillo si el detector falla en detectar direcciones o si las direcciones detectadas no tienen continuidad.

30 El circuito 105 de corrección de error detecta un error en los datos suministrados por el detector 104 de sectores, y utiliza bits redundantes contenidos en los datos para corregir el error y suministrar los datos corregidos a una memoria intermedia 107 en anillo para realizar el salto cíclico. Adicionalmente, si el detector 104 de sectores falla en la corrección de un error en los datos, envía una señal de generación de error al circuito 118 de determinación de salto de pista.

35 El circuito 106 de control de memoria intermedia en anillo controla, inscribe y lee datos de la memoria intermedia 107 en anillo, y vigila una señal de solicitud de código que solicita salida de datos de un circuito 108 de separación de datos multiplexados.

40 El circuito 118 de determinación de salto de pista vigila la salida del circuito 106 de control de memoria intermedia en anillo para transmitir una señal de salto de pista a un servocircuito 117 de seguimiento como se requiere para saltar una pista la posición de reproducción del captador 102 con respecto al disco óptico 101. El circuito 118 de determinación de salto de pista detecta también una señal de error de número de sector del detector 104 de sectores o una señal de generación de error del circuito 105 de corrección de error para enviar la señal de salto de pista al servocircuito 117 de seguimiento para realizar el salto de pista de la posición de reproducción del captador 102.

55 La salida de la memoria intermedia 107 en anillo está aplicada al circuito 108 de separación de datos multiplexados. Un circuito 109 de separación de cabecera en el circuito 108 de separación de datos multiplexados separa cabeceras de grupo y cabeceras de paquete de datos suministrados por la memoria intermedia 107 en anillo para su transferencia a un circuito 111 de control de separador, y suministra datos multiplexados por división de tiempo al terminal G de entrada de un circuito 110 de conmutación. Los terminales H1, H2 de salida (terminales conmutados) del circuito 110 de conmutación están conectados a los terminales de entrada de una memoria intermedia 113 de código de video y una memoria intermedia 115 de código de audio, respectivamente. La salida de la memoria intermedia 113 de código de video está conectada a la entrada de un decodificador 114 de video, mientras que la salida de la memoria intermedia 115 de código de audio está conectada a la entrada de un decodificador 116 de audio.

60 Adicionalmente, se aplican como entrada a la memoria intermedia 113 de código de video señales de solicitud de código generadas por el decodificador 114 de video, mientras que se aplican como entrada al circuito 108 de separación de datos multiplexados señales de solicitud de código generadas por la memoria intermedia 113 de código de video. Similarmente, se aplican como entrada a la memoria intermedia 115 de código de audio señales de solicitud de código emitidas por el decodificador 116 de audio, mientras que se aplican como entrada al circuito 108 de separación de datos multiplexados señales de solicitud de código emitidas por la memoria intermedia 115 de código de audio.

65 Se describe a continuación el funcionamiento de cada componente de este aparato de reproducción de datos. El captador 102 irradia el disco óptico 101 con haces de láser, y utiliza la luz reflejada por el disco óptico para reproducir los datos almacenados en el mismo. Las señales reproducidas generadas por el captador 102 se aplican al demodulador 103 para demodulación. Los datos demodulados por el demodulador 103 se aplican como entrada al circuito 105 de corrección de error a través del detector 104 de sectores para detectar y corregir un error.

## ES 2 268 815 T3

Es transmitida una señal de error de número de sector al circuito 118 de determinación de salto de pista si el detector 104 de sectores falla en la detección correcta de números de sector (las direcciones asignadas a los sectores del disco óptico 101). El circuito 105 de corrección de error transmite una señal de generación de error al circuito 118 de determinación de salto de pista si se produce un error incorregible en los datos. Los datos corregidos se transfieren 5 desde el circuito 105 de corrección de error hasta la memoria intermedia 107 en anillo para su almacenamiento.

El circuito 106 de control de memoria intermedia en anillo lee la dirección de cada sector de la salida del detector 104 de sectores para designar la dirección de inscripción (punto de inscripción (WP)) en la memoria intermedia 107 en anillo, en correspondencia con la dirección del sector. El circuito 106 de control de memoria intermedia en 10 anillo designa también direcciones de lectura (puntos de reproducción (RPs)) para los datos inscritos en la memoria intermedia 107 en anillo, en base a una señal de solicitud de código procedente del circuito 108 de separación de datos multiplexados dispuesto después del circuito de control de memoria intermedia en anillo. Dicho circuito lee a continuación datos de los puntos de reproducción (RP) para transferirlos al circuito 108 de separación de datos multiplexados.

15 El circuito 109 de separación de cabecera en el circuito 108 de separación de datos multiplexados separa cabeceras de grupo y cabeceras de paquete de los datos suministrados por la memoria intermedia 107 en anillo, para su transferencia a un circuito 111 de control de circuito de separación. El circuito 111 de control de circuito de separación conecta secuencialmente el terminal G de entrada del circuito 110 de commutación al terminal H1 o H2 de salida 20 (terminal commutado) del mismo de acuerdo con la información de identificación de cadena de datos contenida en las cabeceras de paquete suministradas por el circuito 109 de separación de cabecera, para separar correctamente los datos multiplexados por división de tiempo. Dicho circuito suministra a continuación los datos a la correspondiente memoria intermedia 113 o 115 de datos.

25 La memoria intermedia 113 de código de video envía una señal de solicitud de código al circuito 108 de separación de datos multiplexados utilizando la sección disponible de su memoria intermedia de código interno. La memoria intermedia 113 de código de video almacena entonces los datos recibidos. Recibe también señales de solicitud de código del decodificador 114 de video para presentar en su salida los datos que contiene. El decodificador 114 de video reproduce señales de video de los datos suministrados para transferirlas a través del terminal de salida.

30 La memoria intermedia 115 de código de audio envía una señal de solicitud de código al circuito 108 de separación de datos multiplexados utilizando la sección disponible de su memoria intermedia de código interno. La memoria intermedia 115 de código de audio almacena entonces los datos recibidos. Recibe también señales de solicitud de código del decodificador 116 de audio y presenta como salida los datos que contiene. El decodificador 116 de audio 35 reproduce señales de audio de los datos suministrados para su presentación como salida en el terminal de salida.

40 El decodificador 114 de video solicita así datos de la memoria intermedia 113 de código de video, mientras que la memoria intermedia 113 de código de video solicita datos del circuito 108 de separación de datos multiplexados. El circuito 108 de separación de datos multiplexados, a su vez, solicita datos del circuito 106 de control de memoria intermedia en anillo. En este caso, los datos fluyen desde la memoria intermedia 107 en anillo en dirección inversa a la correspondiente a la solicitud.

45 Por ejemplo, las lecturas de la memoria intermedia 107 en anillo disminuyen al disminuir los datos consumidos por el decodificador 114 de video por unidad de tiempo debido al tratamiento continuo de datos para pantallas simples. En este caso, puede aumentar la cantidad de datos almacenados en la memoria intermedia 107 en anillo, produciendo su desbordamiento por exceso. El circuito 118 de determinación de salto de pista utiliza así los puntos de inscripción (WPs) y los puntos de reproducción (RPs) para calcular la cantidad de datos almacenados en cada momento en la memoria intermedia 107 en anillo y, si los datos superan un criterio predeterminado, determina que la memoria intermedia 107 en anillo puede desbordarse para enviar una instrucción de salto de pista al servocircuito 117 de seguimiento.

50 Si el circuito 118 de determinación de salto de pista detecta una señal de error de número de sector procedente del detector 104 de sectores o una señal de generación de error del circuito 105 de corrección de error, utiliza direcciones de inscripción (WPs) y direcciones de lectura (RPs) para calcular la cantidad de datos que quedan en la memoria intermedia 107 en anillo y la cantidad de datos requeridos para asegurar las lecturas de la memoria intermedia 107 en anillo para el circuito 108 de separación de datos multiplexados, mientras el disco óptico 101 está realizando una única revolución a partir de la posición de pista en curso (es decir, mientras está esperando a que el disco óptico 101 complete una única revolución).

60 Si permanece una gran cantidad de datos en la memoria intermedia 107 en anillo, el circuito 118 de determinación de salto de pista determina que puede recuperarse el error forzando al captador 102 a que intente nuevamente reproducir datos de la posición en que se produjo el error, y envía una instrucción de salto de pista al servocircuito 117 de seguimiento porque no se produce un desbordamiento por defecto incluso si los datos de la memoria intermedia 107 en anillo se leen a la máxima velocidad de transferencia.

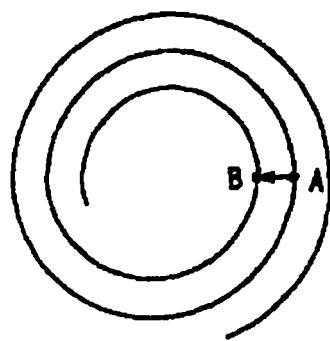

65 Cuando la instrucción de salto de pista es emitida por el circuito 118 de determinación de salto de pista, por ejemplo, el servocircuito 117 de seguimiento fuerza el salto del captador 102 una pista desde la posición A hasta la posición B circunferencialmente hacia el interior desde la posición A, como se muestra en la figura 13. El circuito 106 de control de memoria intermedia en anillo inhibe la inscripción de nuevos datos en la memoria intermedia 107 en

anillo, y los datos almacenados en la memoria intermedia 107 en anillo son transferidos al circuito 108 de separación de datos multiplexados como se requiere hasta que el disco óptico realiza otra revolución desde la posición B hasta la posición A, es decir hasta que el número de sector obtenido del detector 104 de sectores coincide con el obtenido antes del salto de pista.

5 Incluso cuando el número de sector obtenido del detector 104 de sectores coincide con el obtenido antes del salto de pista, las inscripciones en la memoria intermedia 107 en anillo no se reinician y se realiza otro salto de pista si la cantidad de datos almacenados en la memoria intermedia 107 en anillo supera el criterio predeterminado, es decir 10 si puede desbordarse la memoria intermedia 107 en anillo. El aparato de reproducción de datos puede utilizar así la memoria intermedia 107 en anillo para direccionar una tasa de transferencia variable y para realizar reintentos al producirse errores.

La utilidad de este aparato de reproducción de datos convencional puede mejorarse sustancialmente reproduciendo 15 sintonicamente datos multiplexados con datos de video, audio y de dialogo superpuesto comprimidos con una tasa de compresión variable en conformidad con la norma ISO11172 (MPEG1) o con la norma ISO13818 (MPEG2) mientras se corrigen errores de sincronismo, y para realizar una búsqueda, una parada o una operación de alimentación de cuadro al producirse errores.

20 Un aparato de reproducción de datos de acuerdo con este invento que tiene un dispositivo de corrección de error, una memoria intermedia de anillo, una memoria intermedia de código de video, una memoria intermedia de código de audio y/o una memoria intermedia de código de diálogo superpuesto, comprueba el funcionamiento de la memoria contenida en uno o más de los dispositivos anteriores cuando se activan o en un instante arbitrario.

## Breve descripción de los dibujos

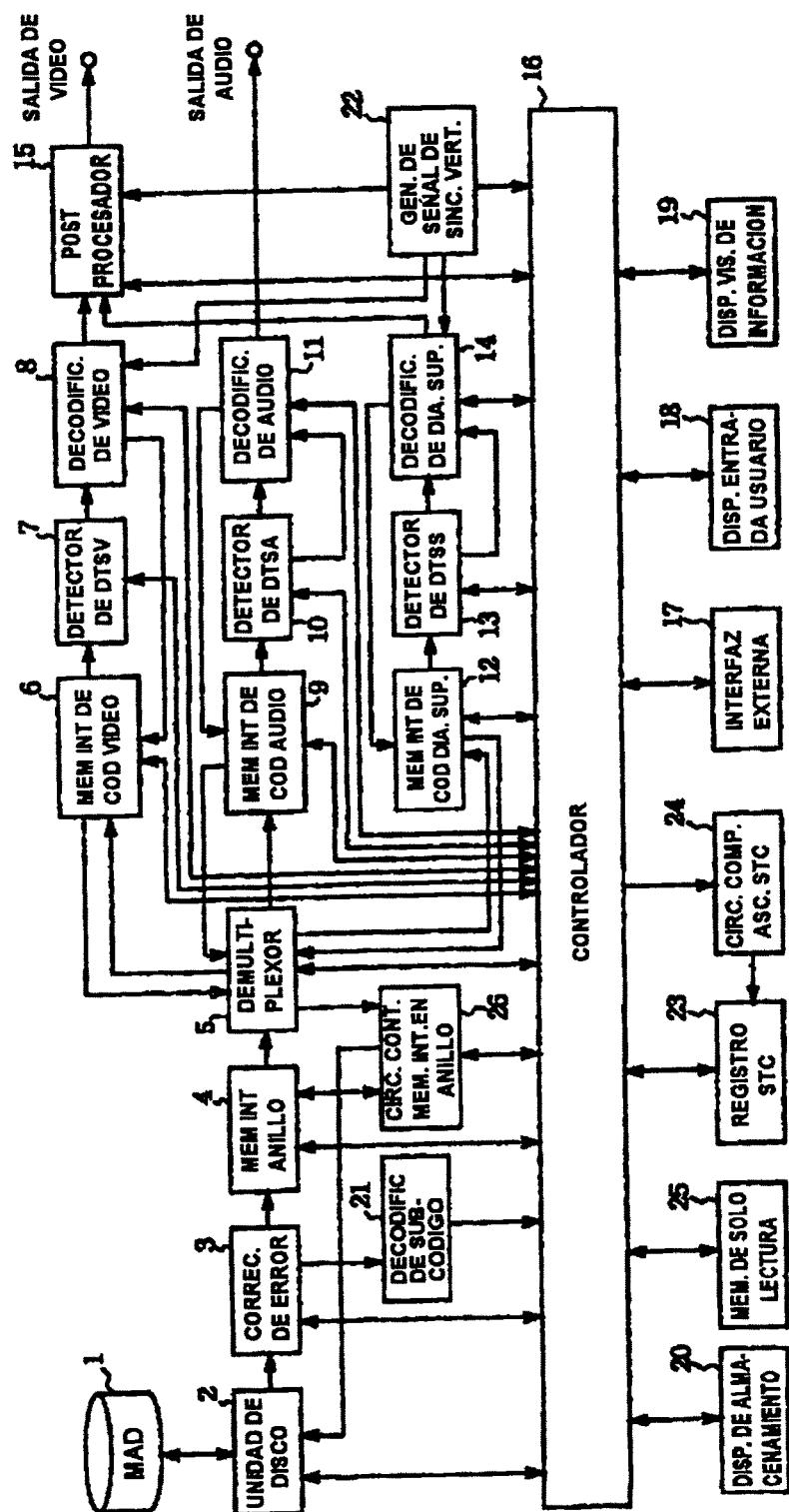

25 La figura 1 es un diagrama de bloques que ilustra la configuración de un aparato de reproducción de datos de acuerdo con una realización de este invento;

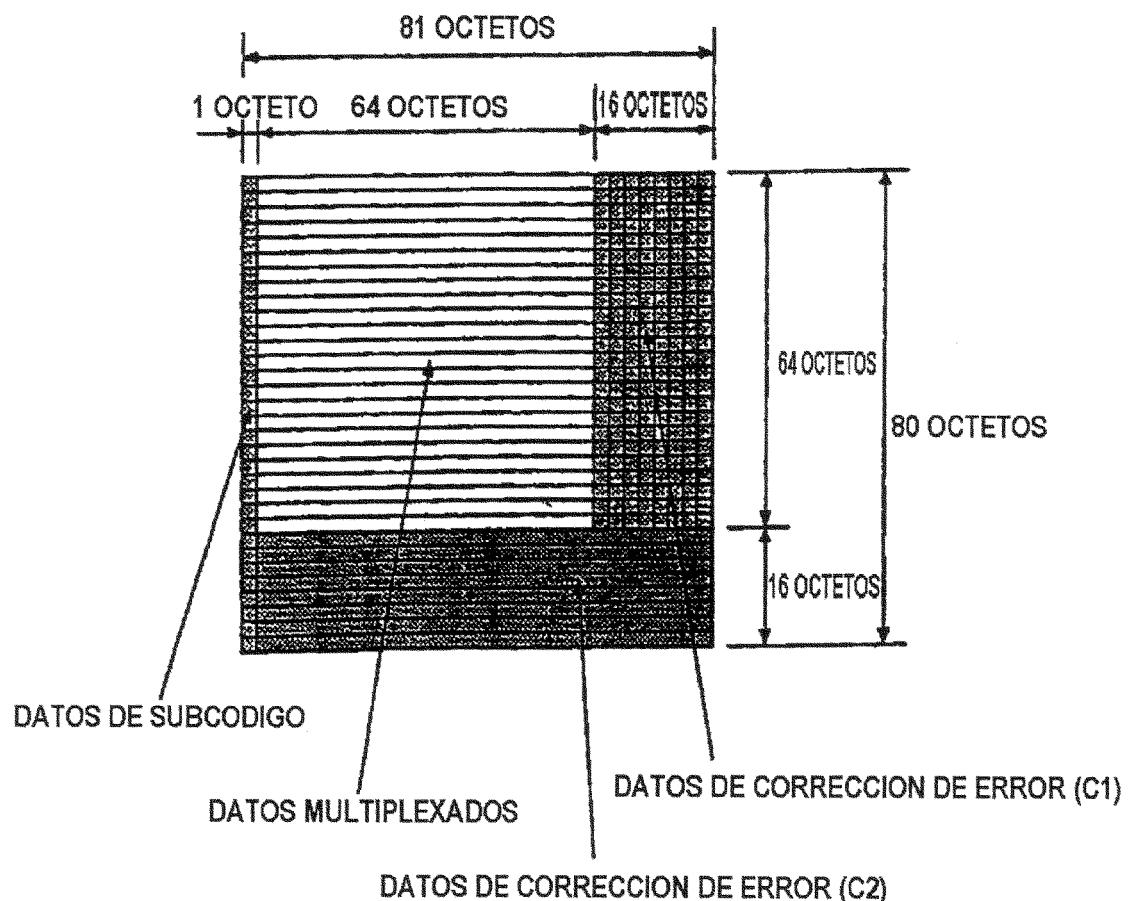

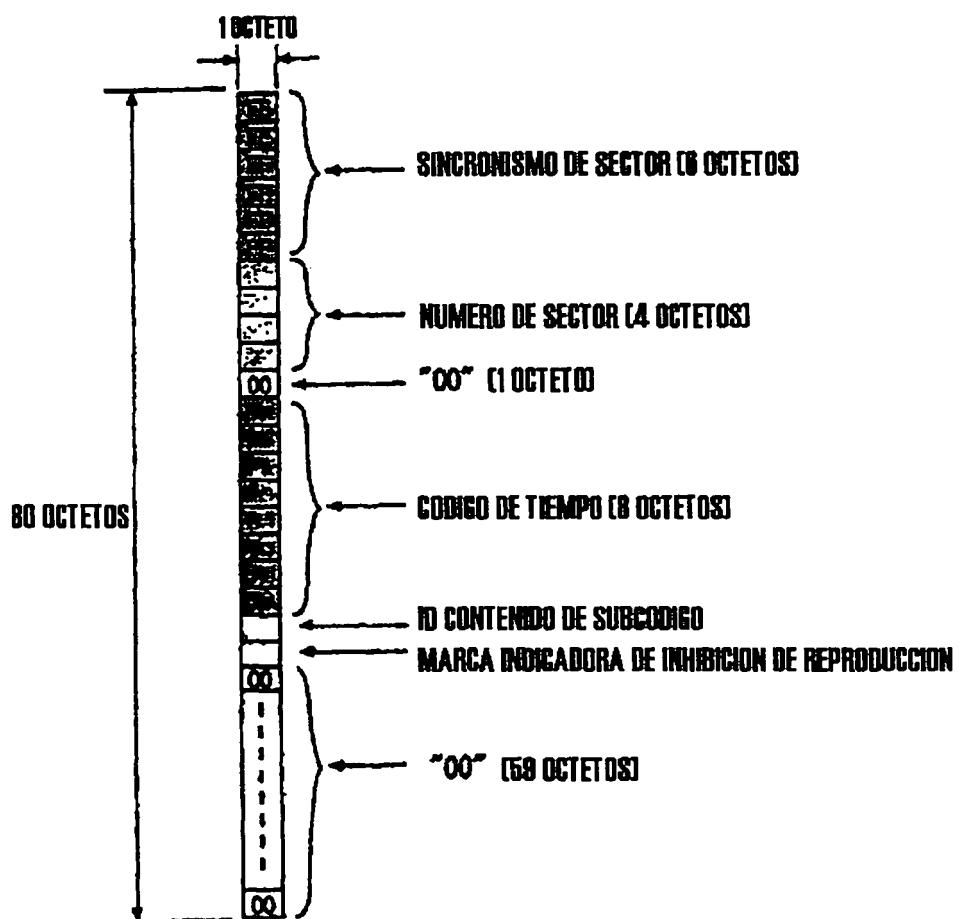

30 La figura 2 es un diagrama esquemático que describe el formato de sector para datos reproducidos en el aparato de reproducción de datos;

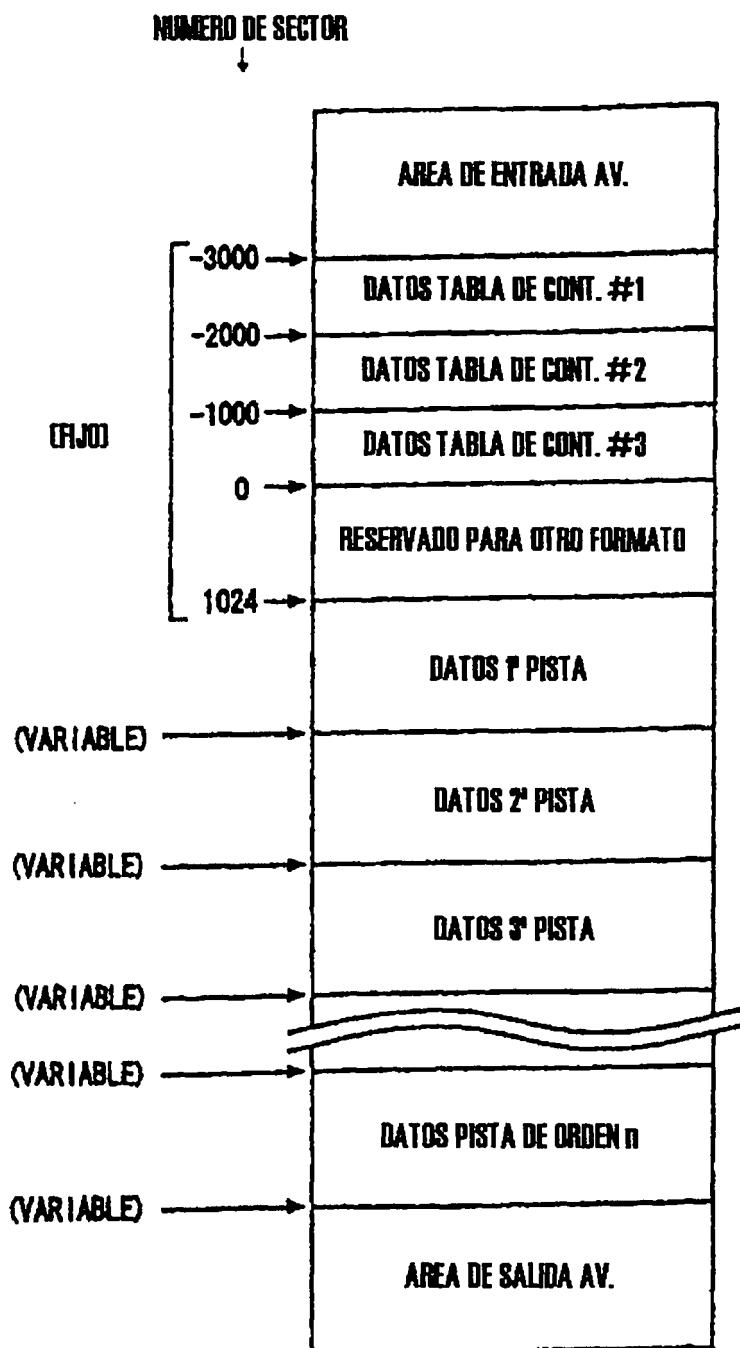

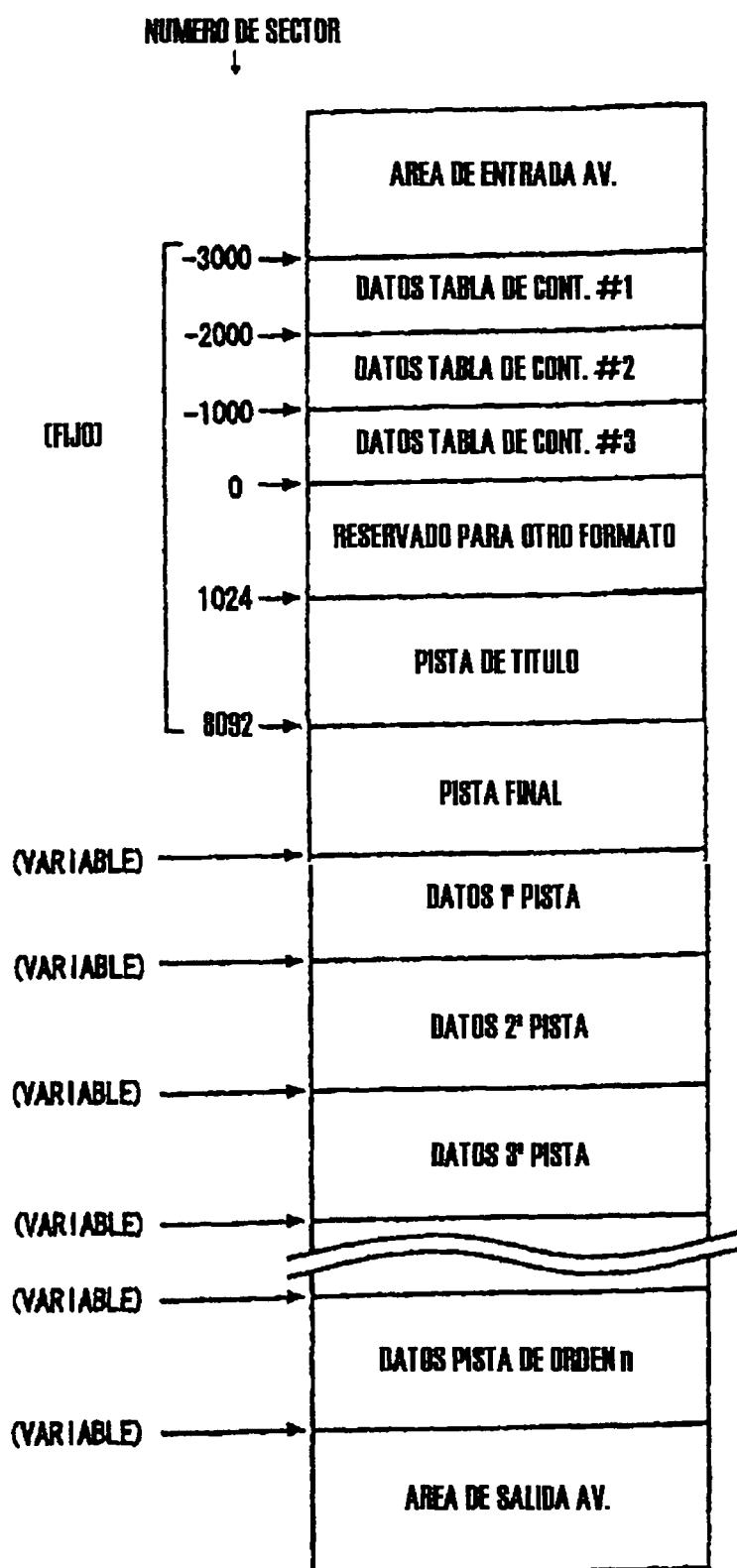

La figura 3 es un diagrama esquemático que describe la configuración de un medio de almacenamiento de datos del cual reproduce datos el aparato de reproducción de datos;

35 La figura 4 es un diagrama esquemático que describe la configuración de un medio de almacenamiento de datos diferente del medio de almacenamiento de datos de la figura 3, del que reproduce datos el aparato de reproducción de datos;

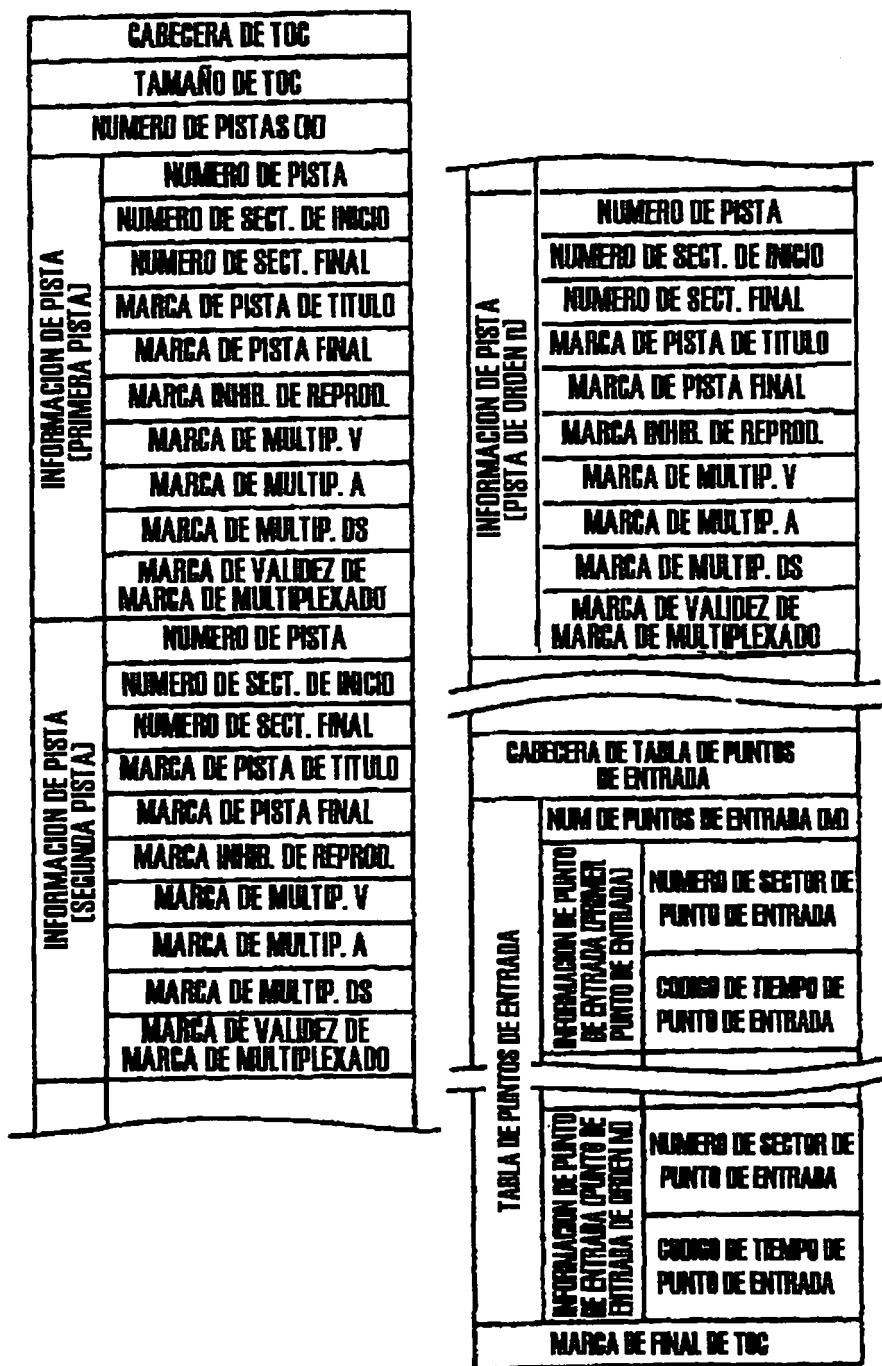

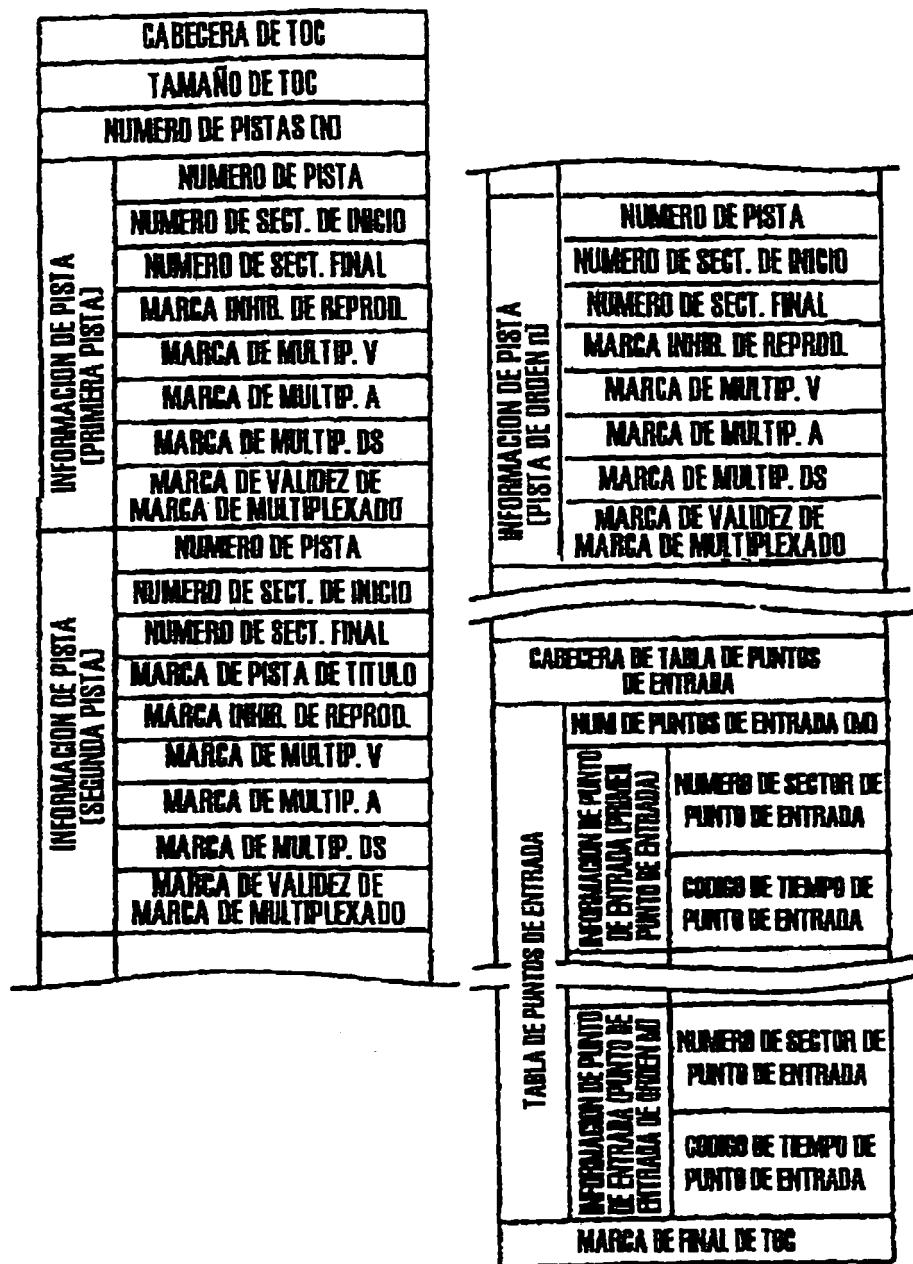

40 La figura 5 es un diagrama esquemático que describe la estructura de datos de tabla de contenidos en el medio de almacenamiento de datos;

La figura 6 es un diagrama esquemático que describe la estructura de datos de tabla de contenidos en el medio de almacenamiento de datos, que difiere de la estructura de los datos de tabla de contenidos de la figura 5;

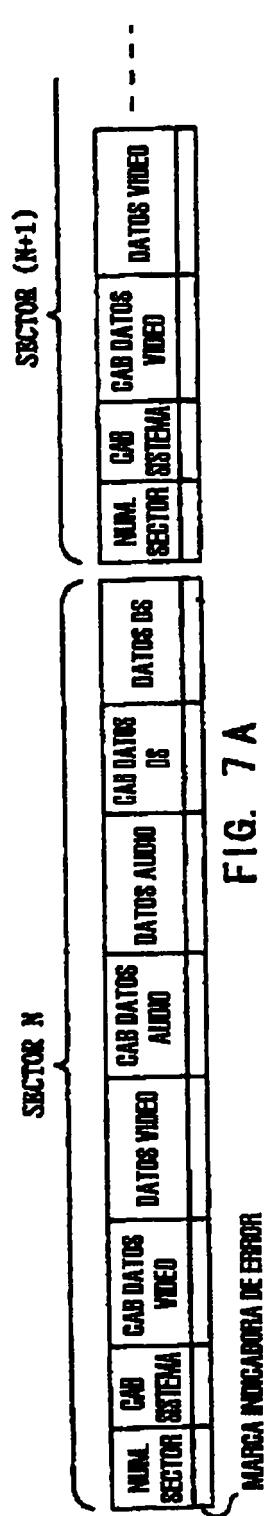

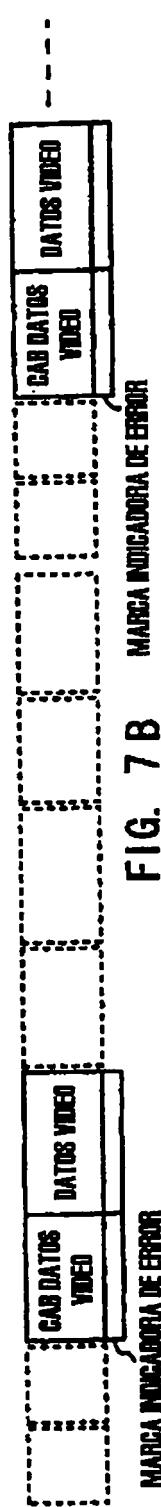

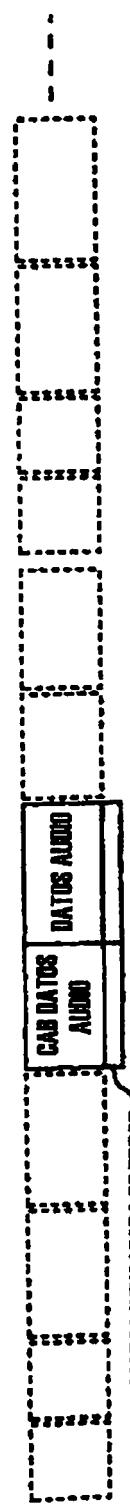

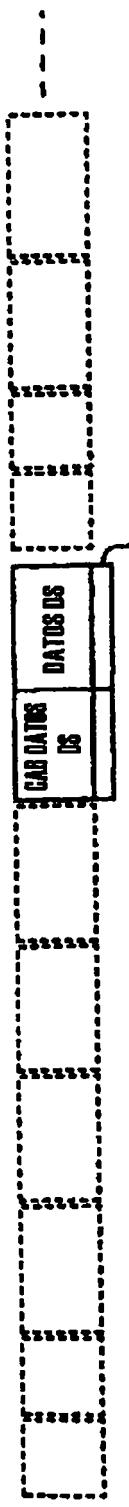

45 Las figuras 7A a 7D son diagramas esquemáticos que describen la estructura de una entrada de cadena de bits multiplexados a un demultiplexor, y la estructura de una salida de cadena de bits a cada memoria intermedia de código;

50 La figura 8 es un diagrama esquemático que describe la estructura de una cabecera de sistema en la cadena de bits de las figuras 7A a 7D;

La figura 9 es un diagrama esquemático que describe la estructura de cabeceras de datos de video, audio y de diálogo superpuesto en la cadena de bits de las figuras 7A a 7D;

55 La figura 10 es un diagrama esquemático que describe el formato de datos de subcódigo;

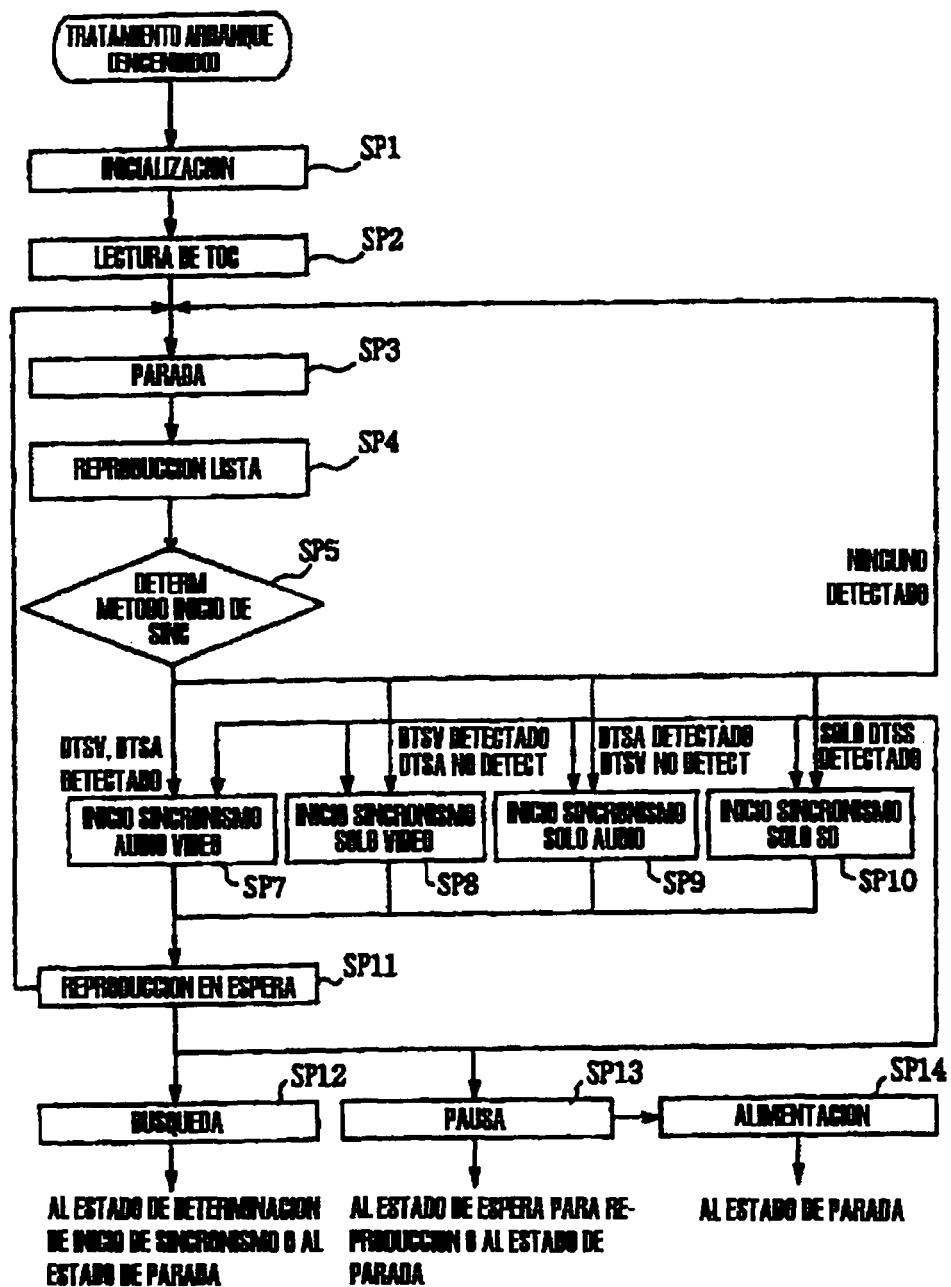

La figura 11 es un diagrama de flujo que describe la transición del estado de un controlador para explicar el funcionamiento del aparato de reproducción de datos;

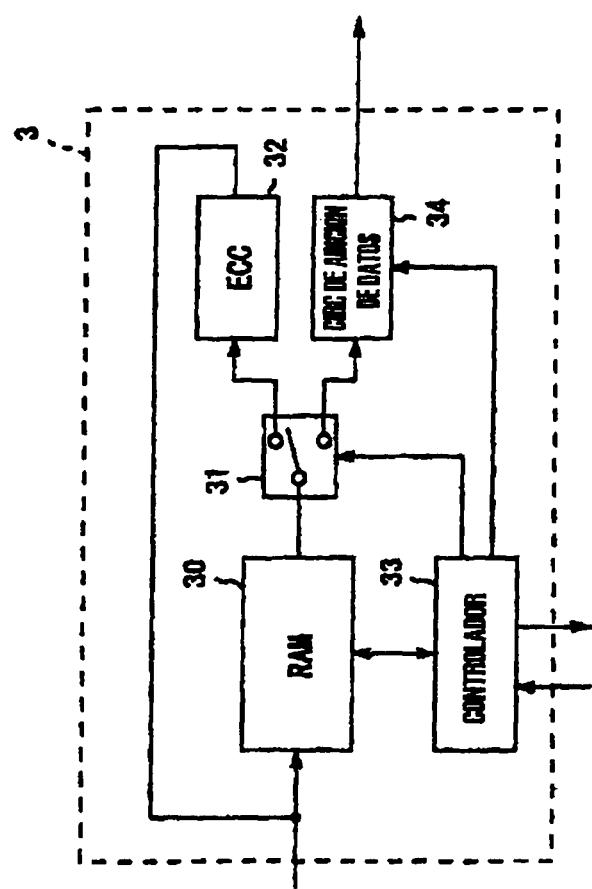

60 La figura 12 es un diagrama de bloques que ilustra la configuración de un dispositivo 3 de corrección de error;

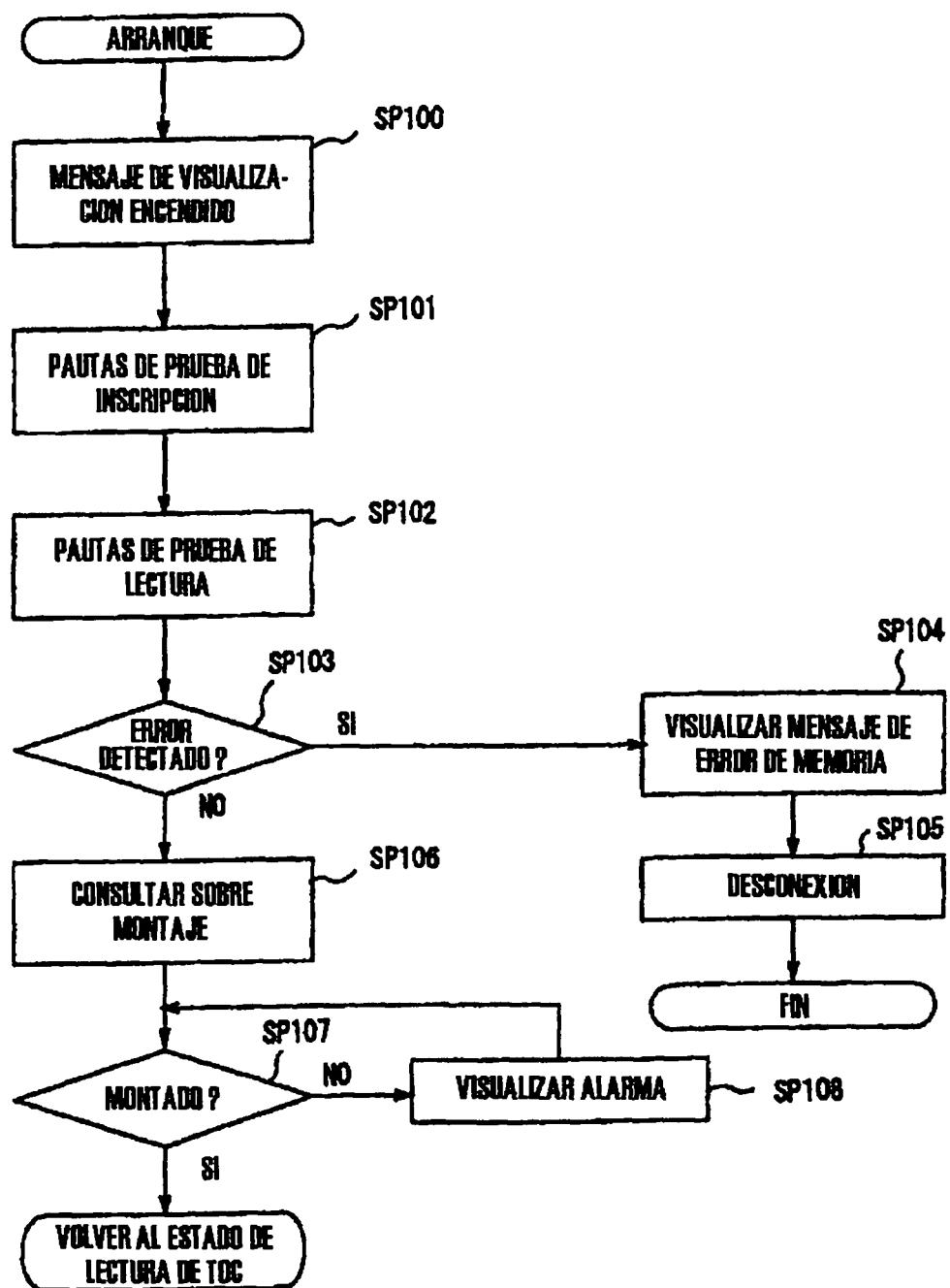

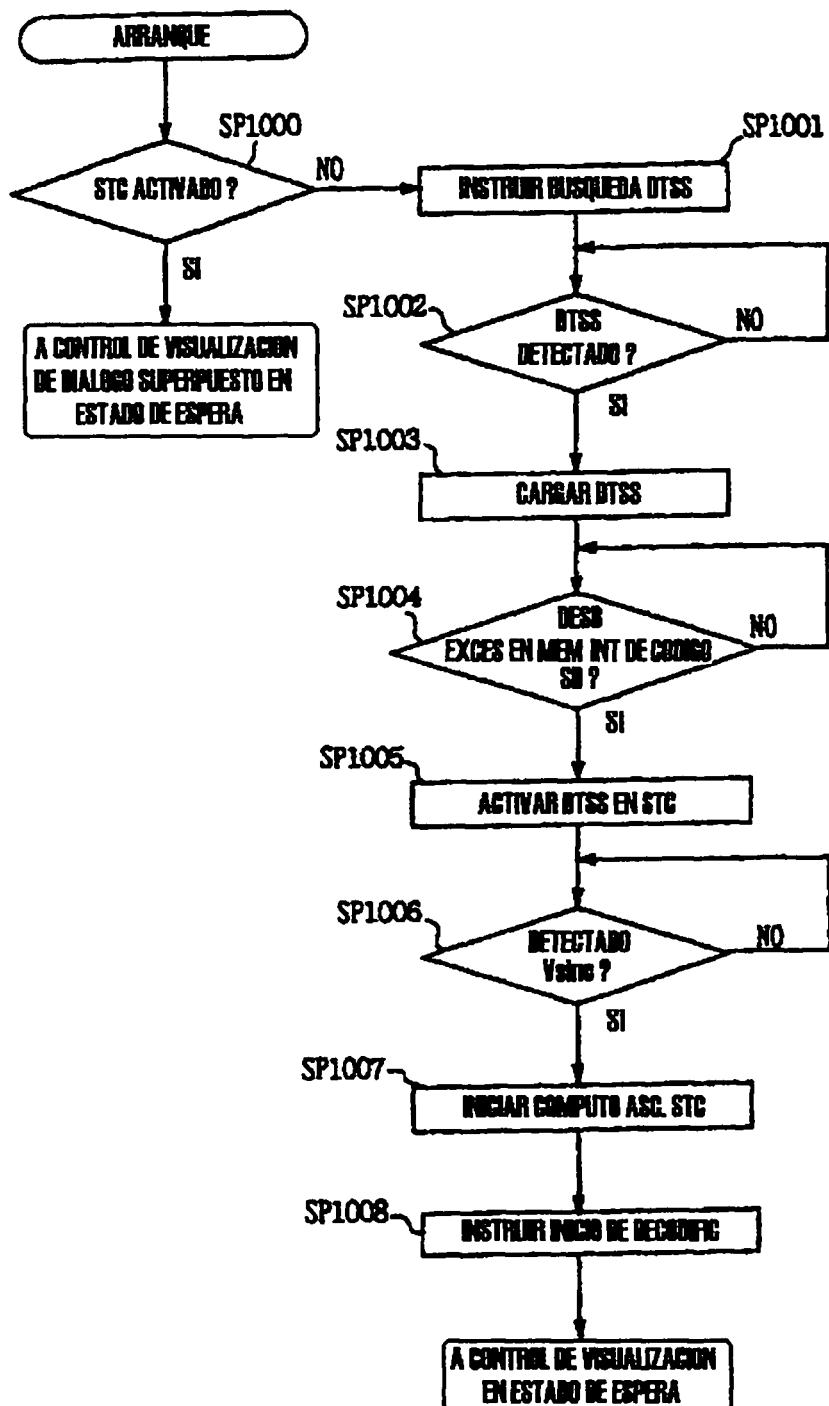

La figura 13 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 en su estado de inicialización;

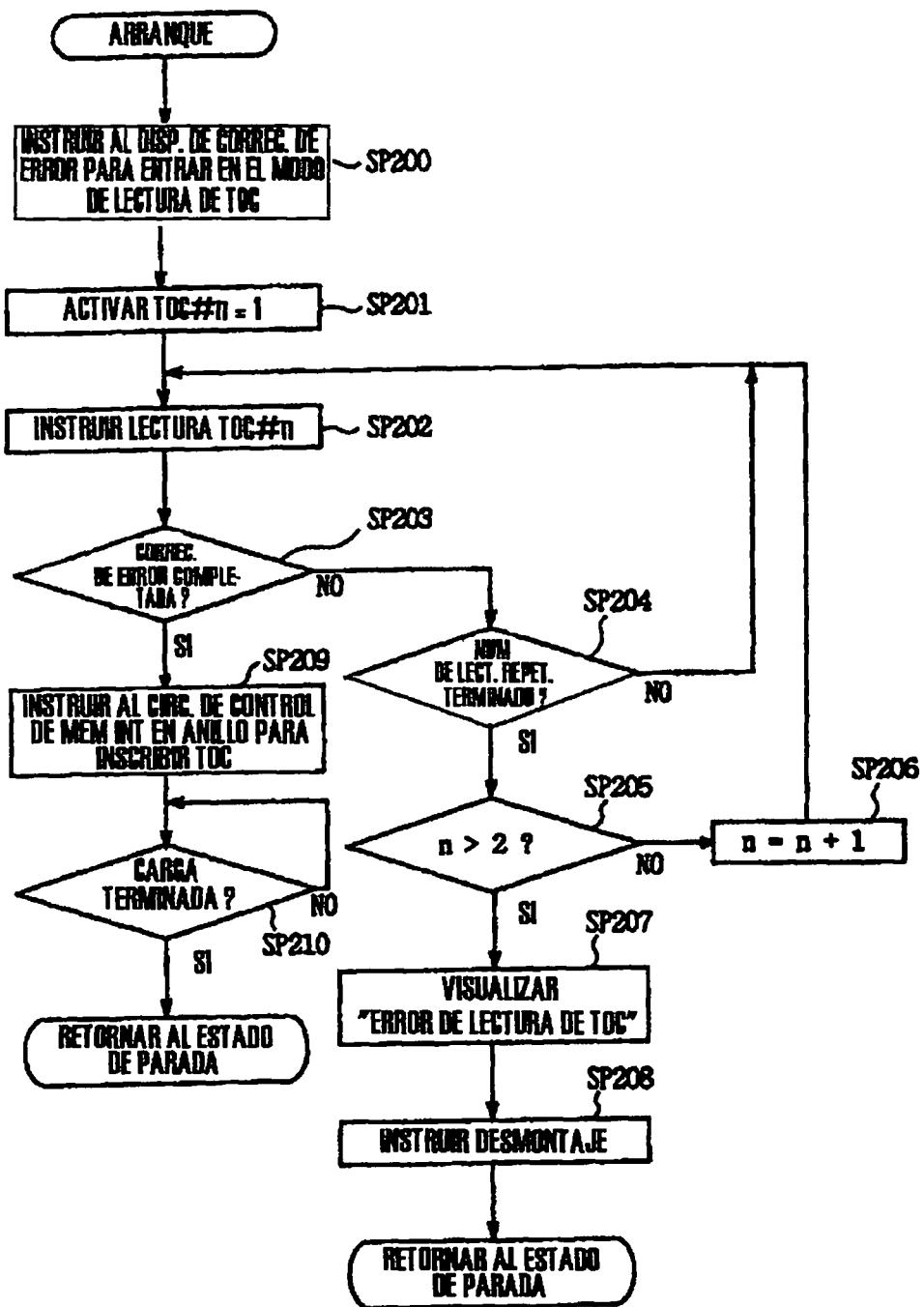

65 La figura 14 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 en su estado de lectura de tabla de contenidos;

## ES 2 268 815 T3

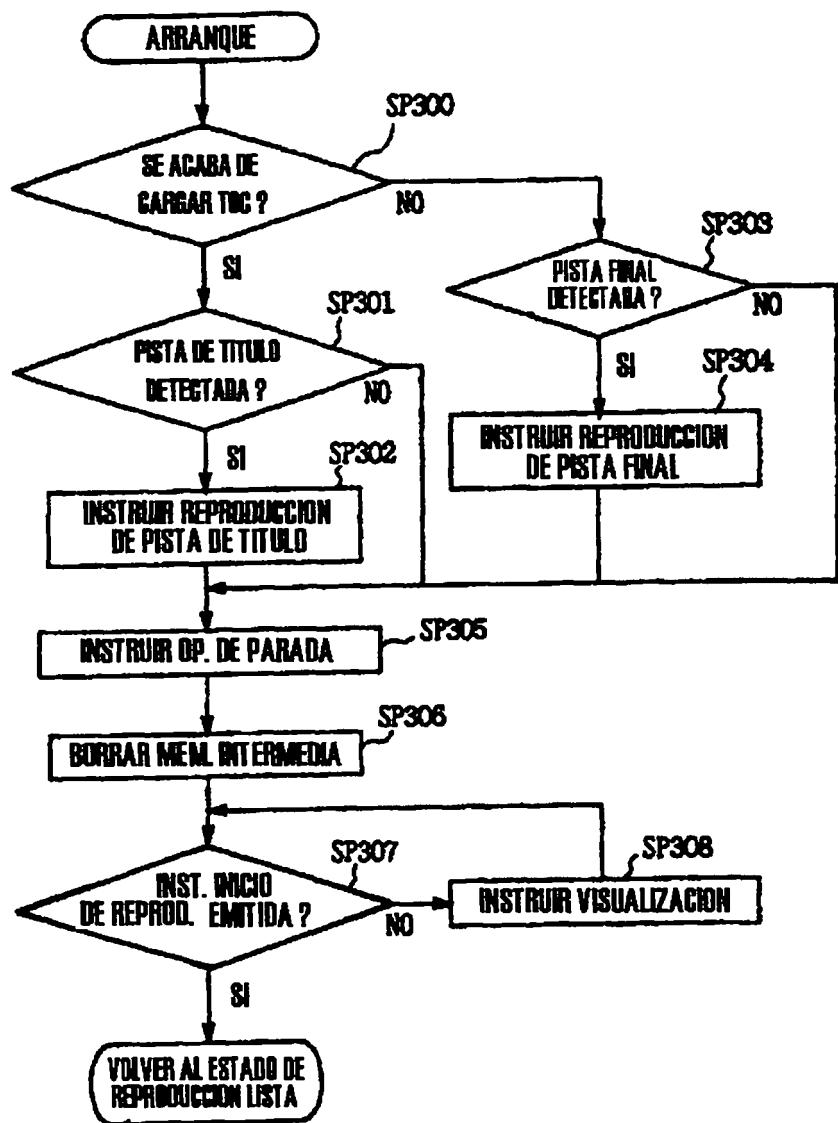

- La figura 15 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 en su estado de parada;

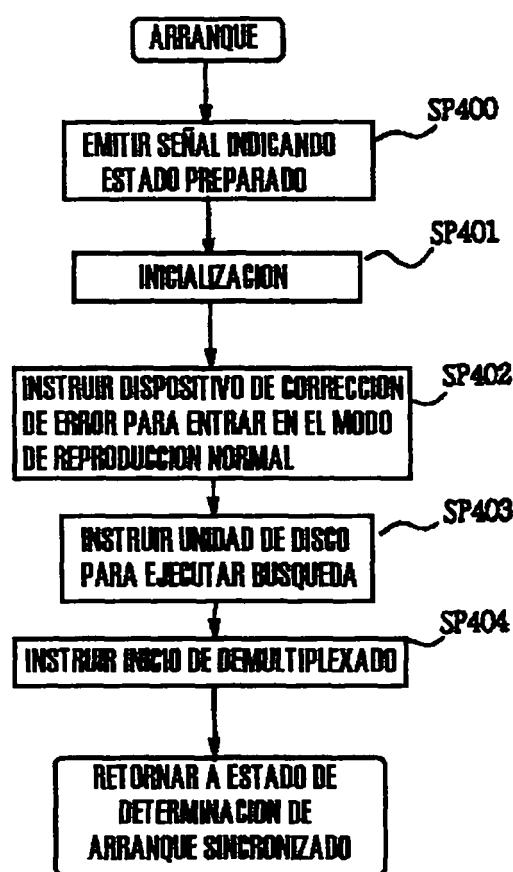

- 5 La figura 16 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 en su estado de estado de preparación para reproducción;

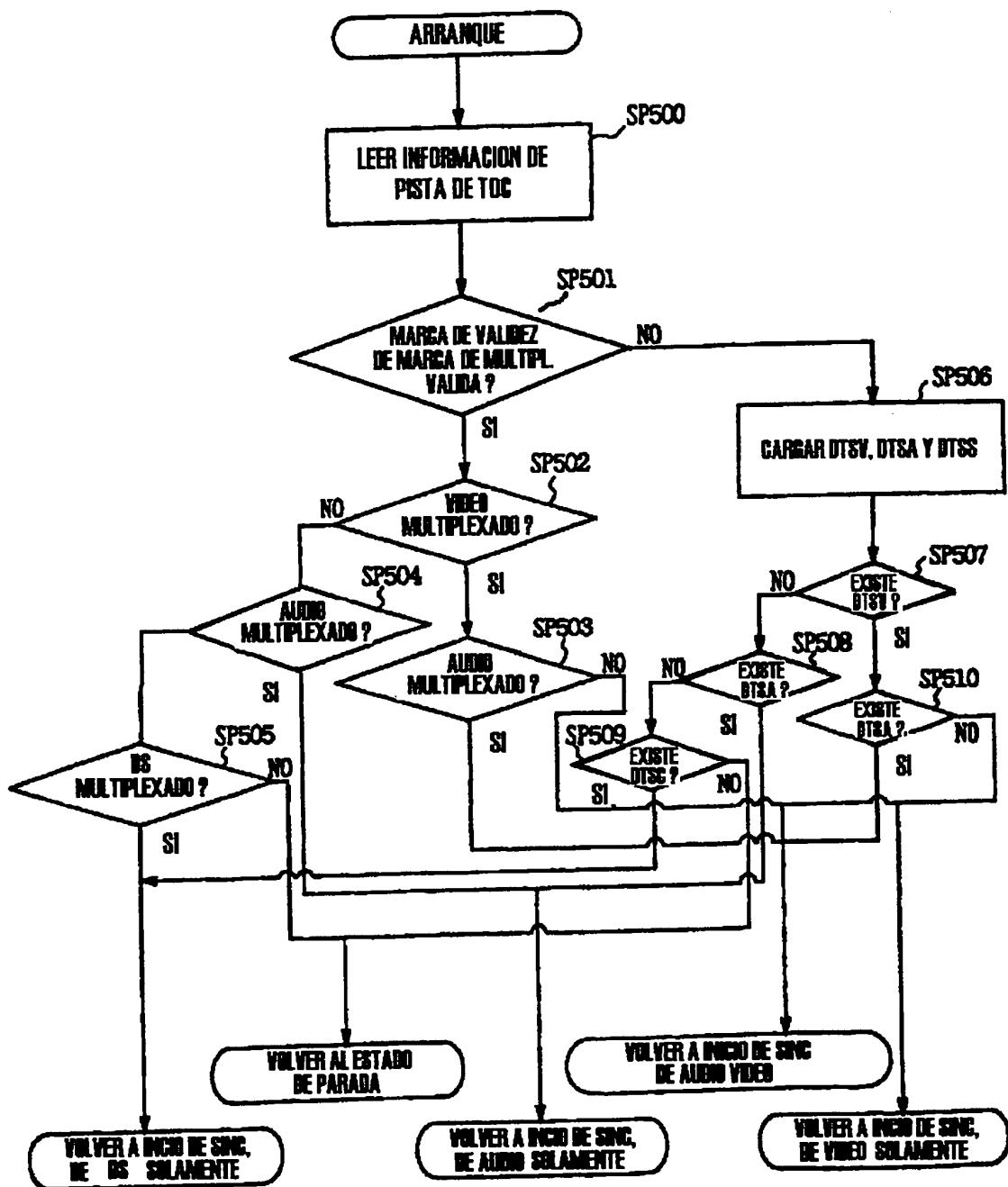

- La figura 17 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 en su estado de determinación de método de arranque sincronizado;

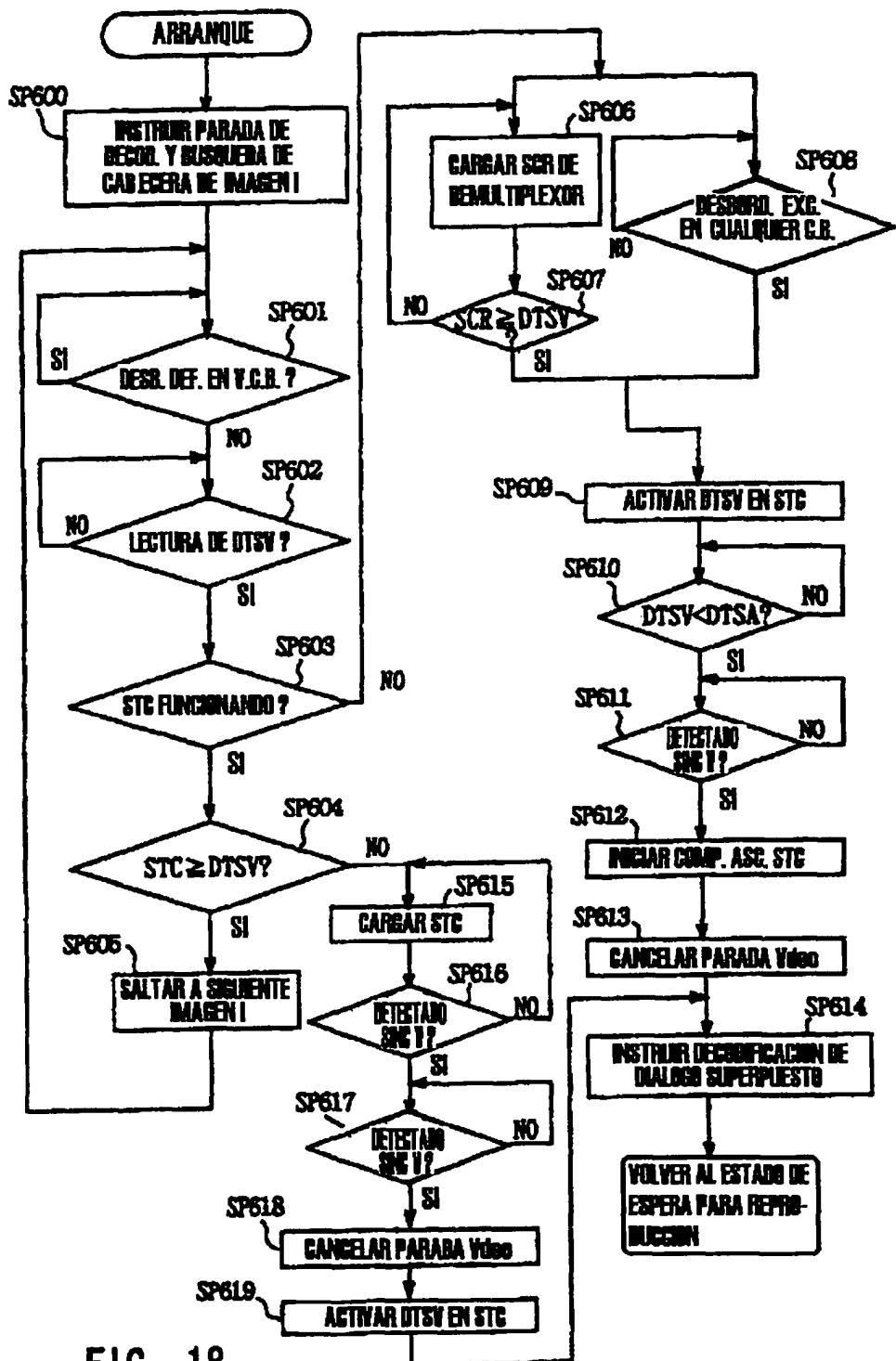

- 10 La figura 18 es un diagrama de flujo que ilustra el tratamiento de video realizado por el controlador 16 en su estado sincronizado de audio y video;

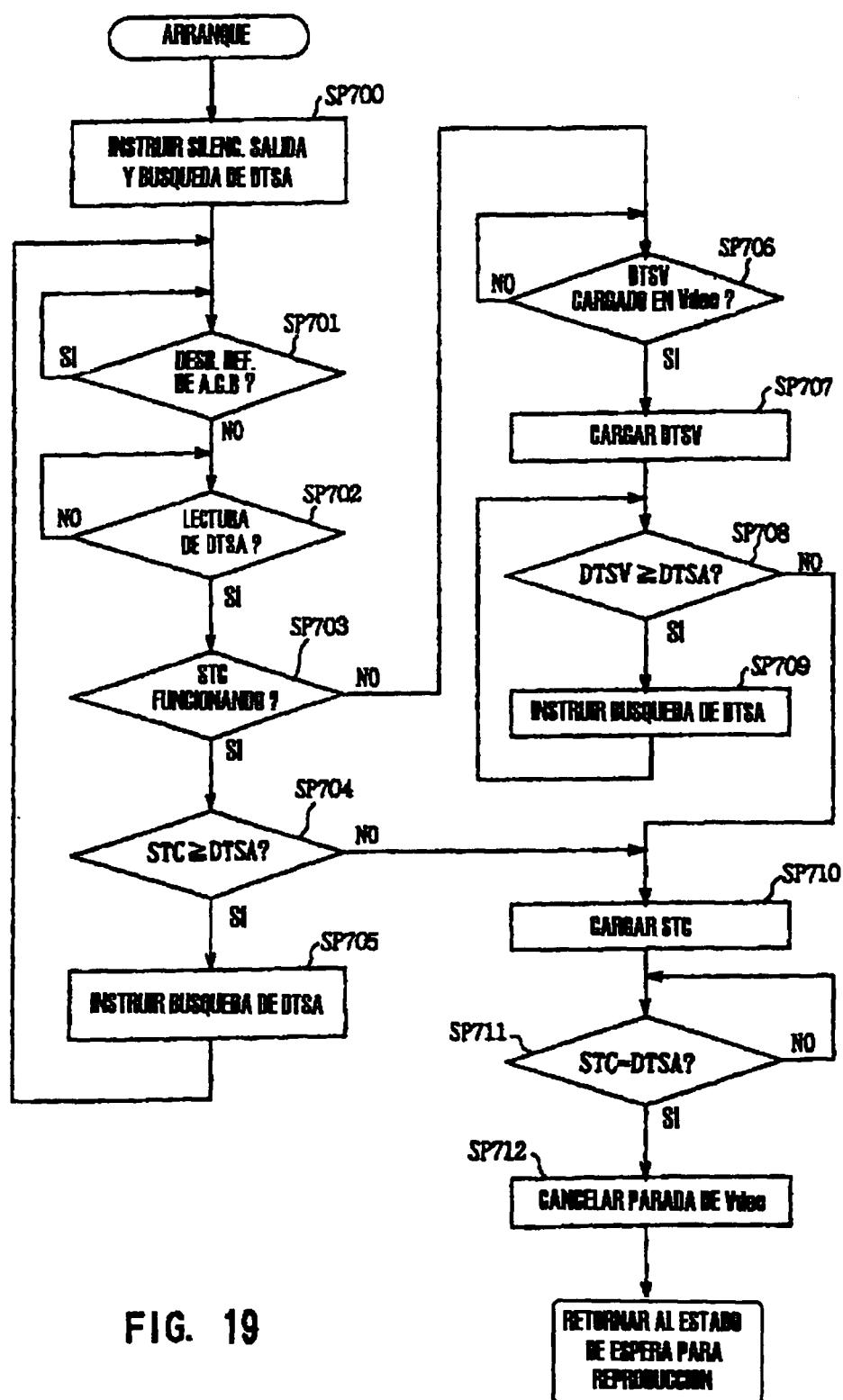

- La figura 19 es un diagrama de flujo que ilustra el tratamiento de audio realizado por el controlador 16 en su estado de arranque sincronizado de audio y video;

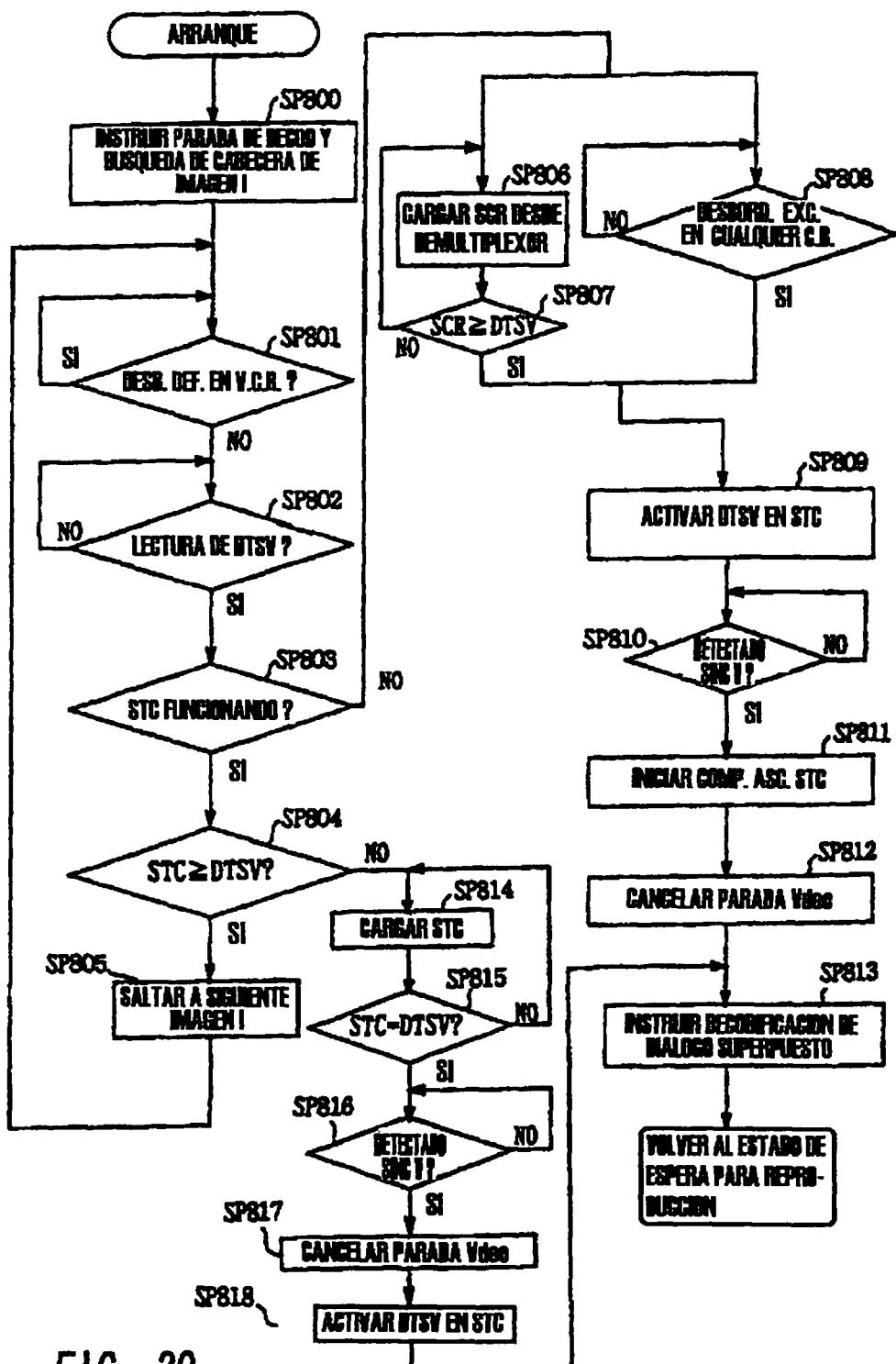

- 15 La figura 20 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 en su estado de arranque sincronizado solamente de video;

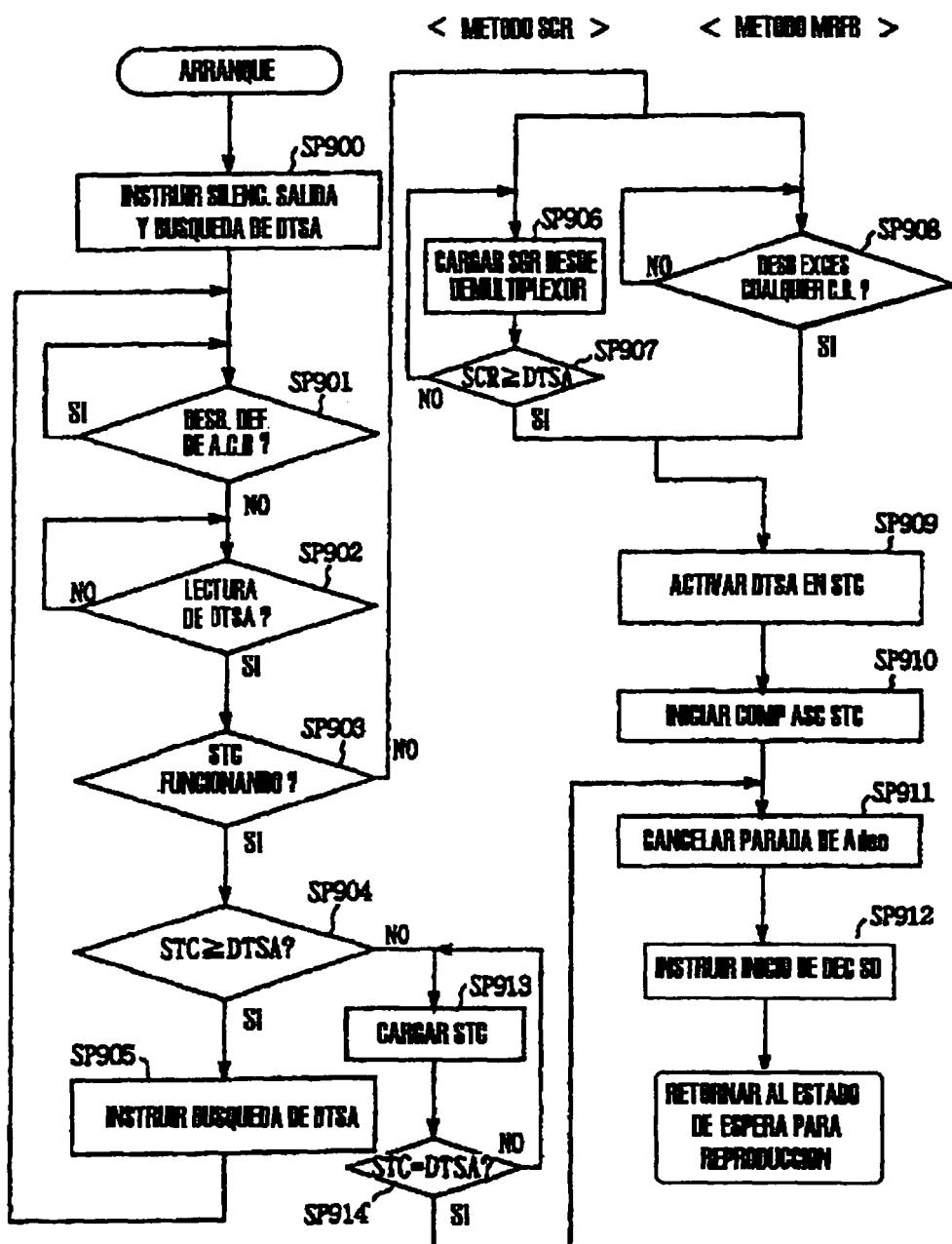

- La figura 21 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 en su estado de arranque sincronizado solamente de audio;

- 20 La figura 22 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 en su estado de arranque sincronizado solamente para datos de diálogo superpuesto;

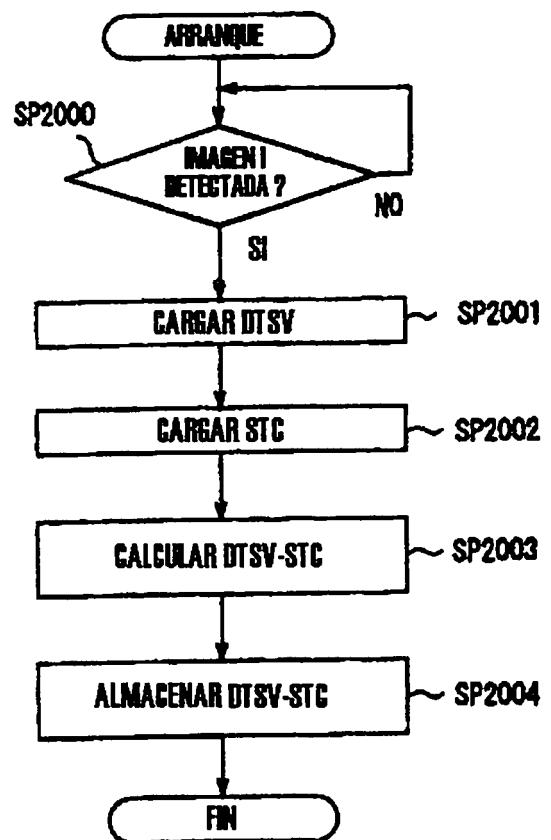

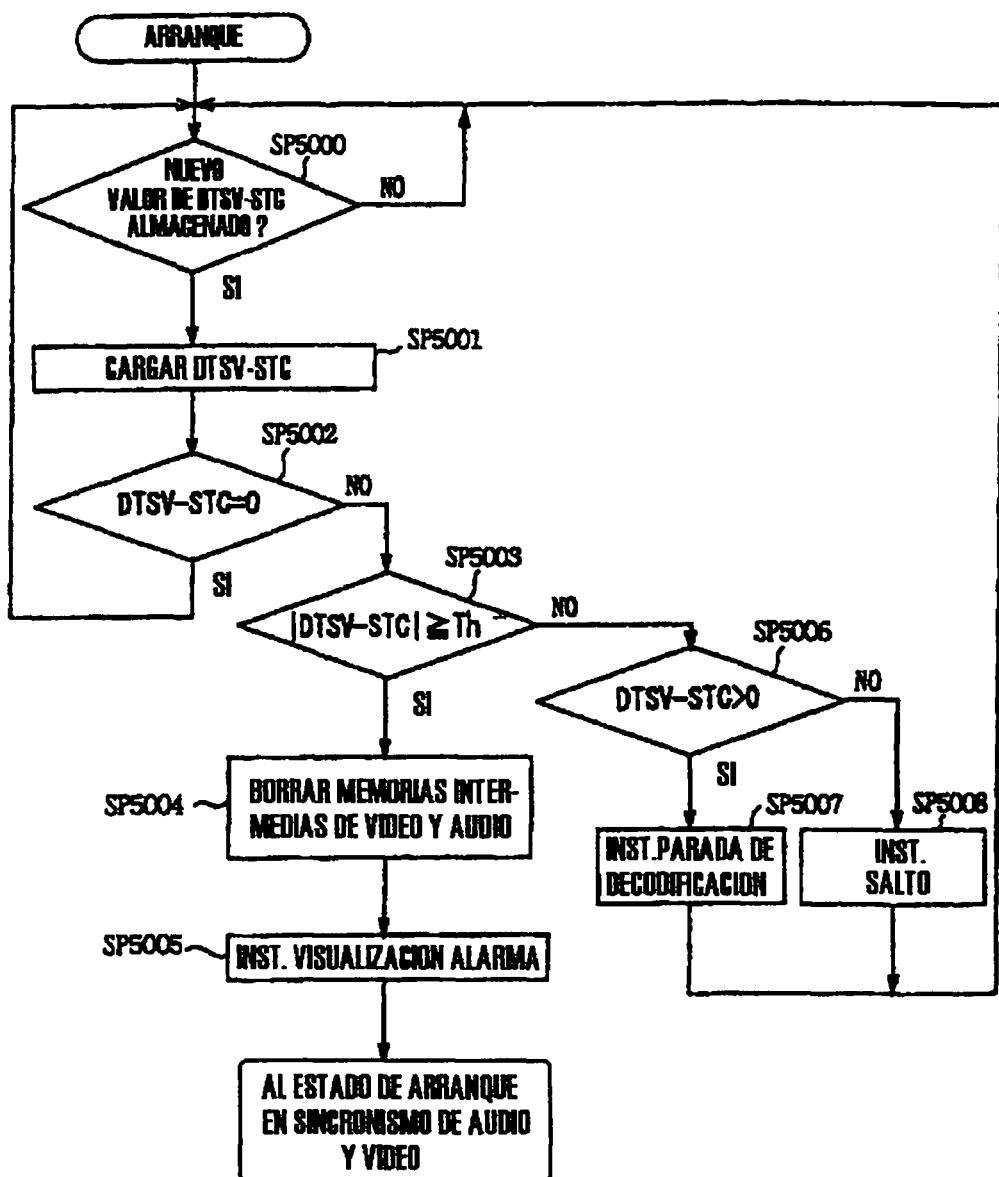

- La figura 23 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 para detectar un error de sincronismo en términos de datos de video;

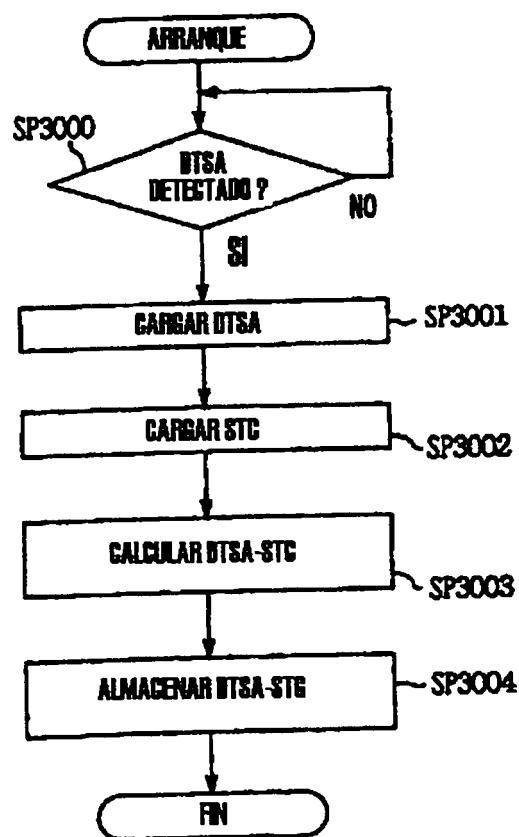

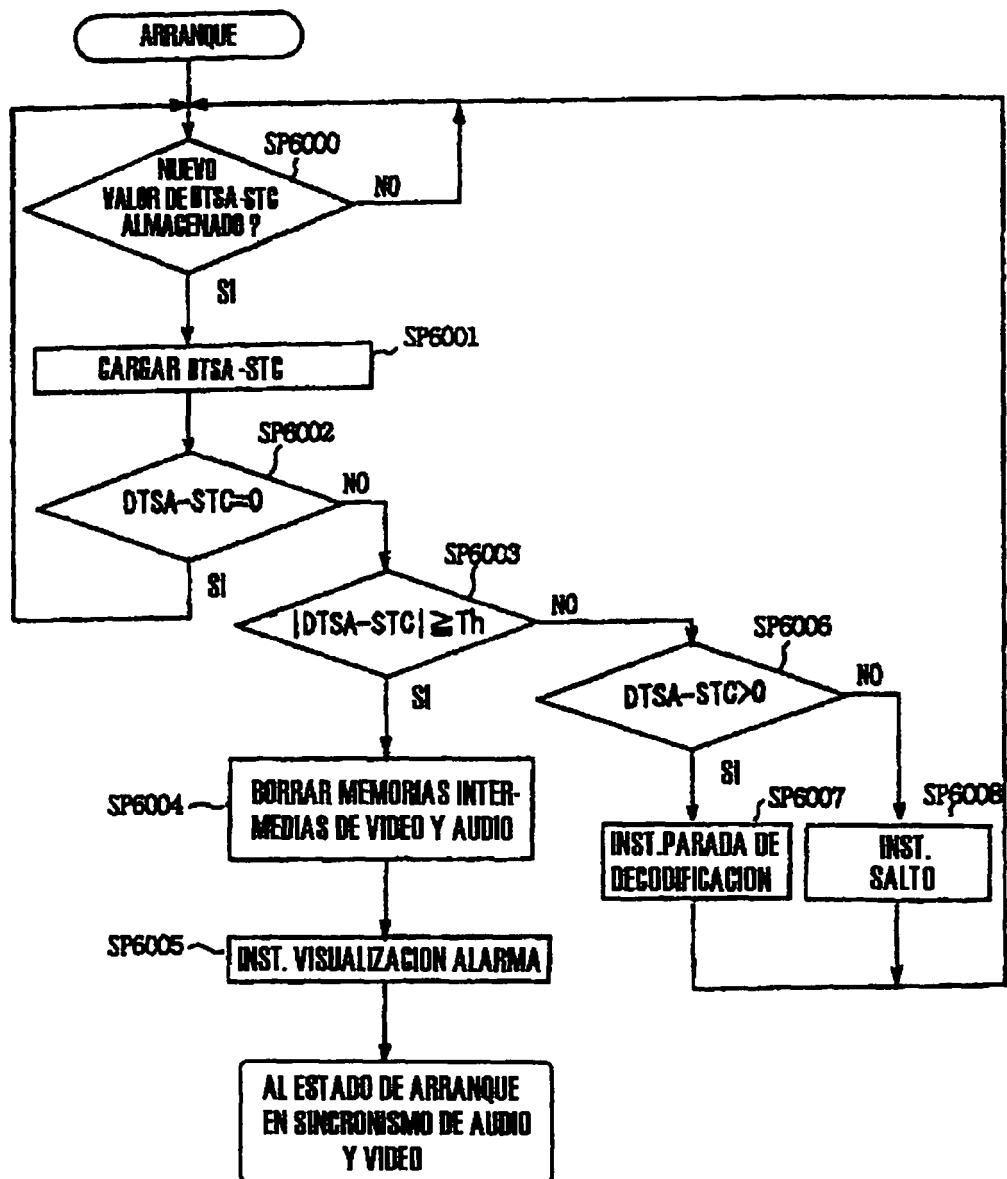

- 25 La figura 24 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 para detectar un error de sincronismo en términos de datos de audio;

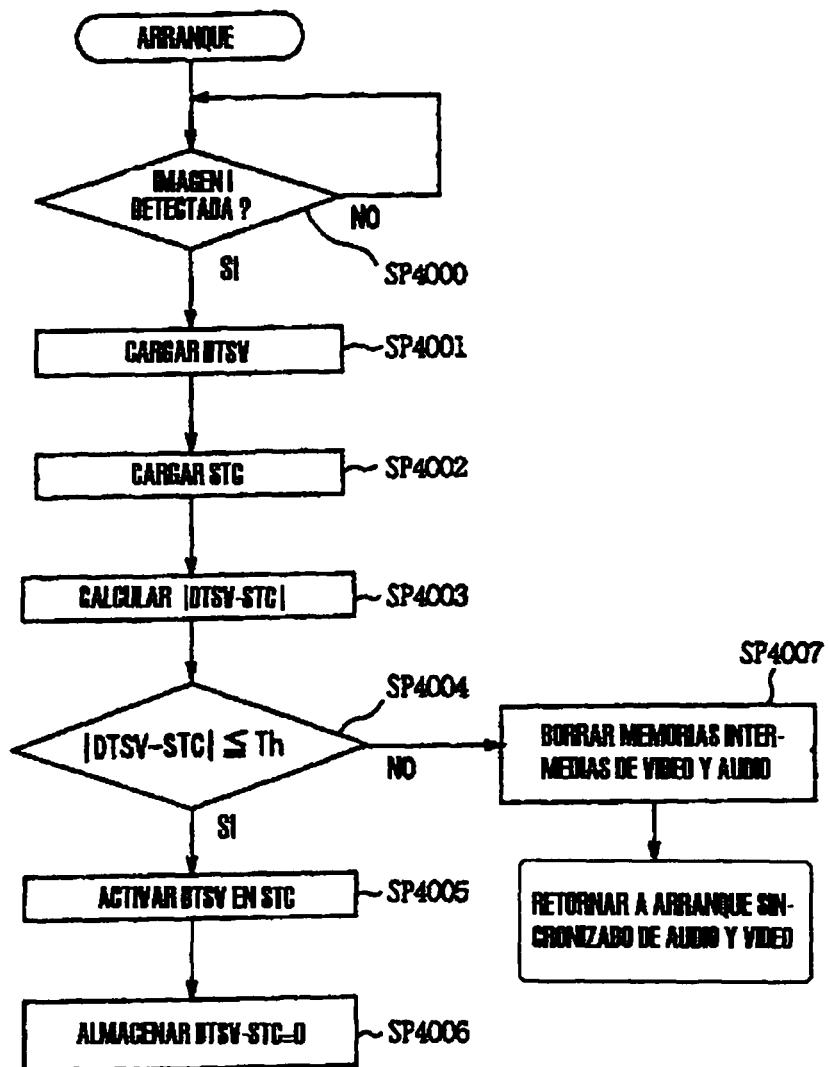

- La figura 25 es un diagrama de flujo que ilustra otro tratamiento realizado por el controlador 16 para detectar un error de sincronismo en términos de datos de video;

- 30 La figura 26 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 para corregir un error de sincronismo en términos de datos de video;

- La figura 27 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 para corregir un error de sincronismo en términos de datos de audio;

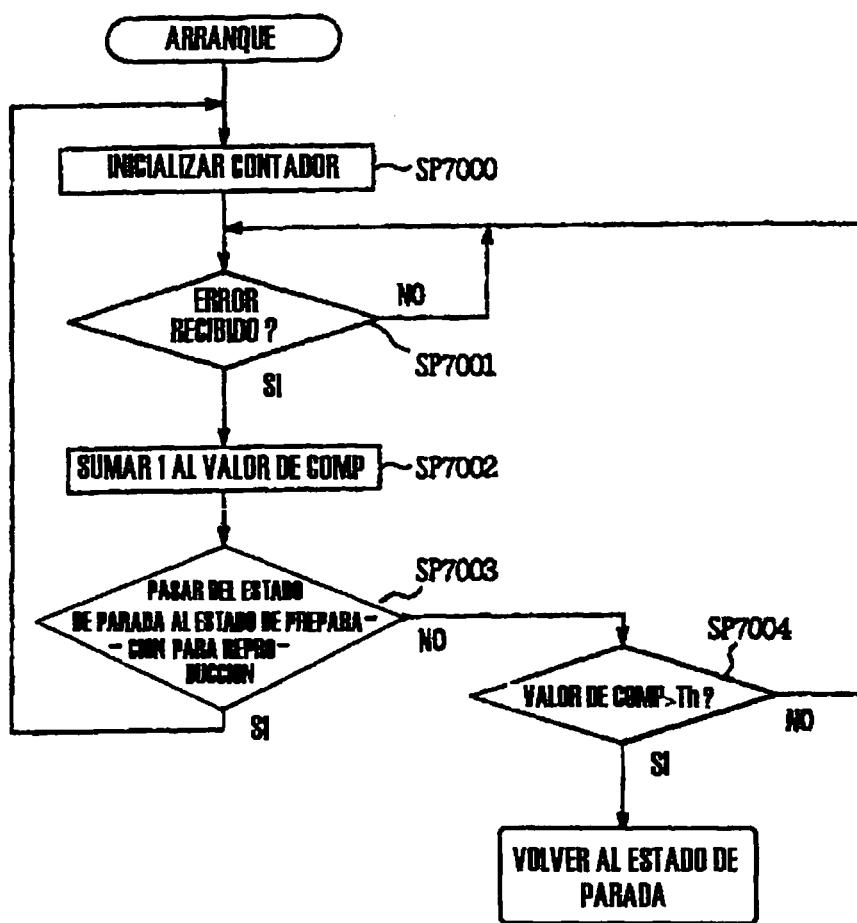

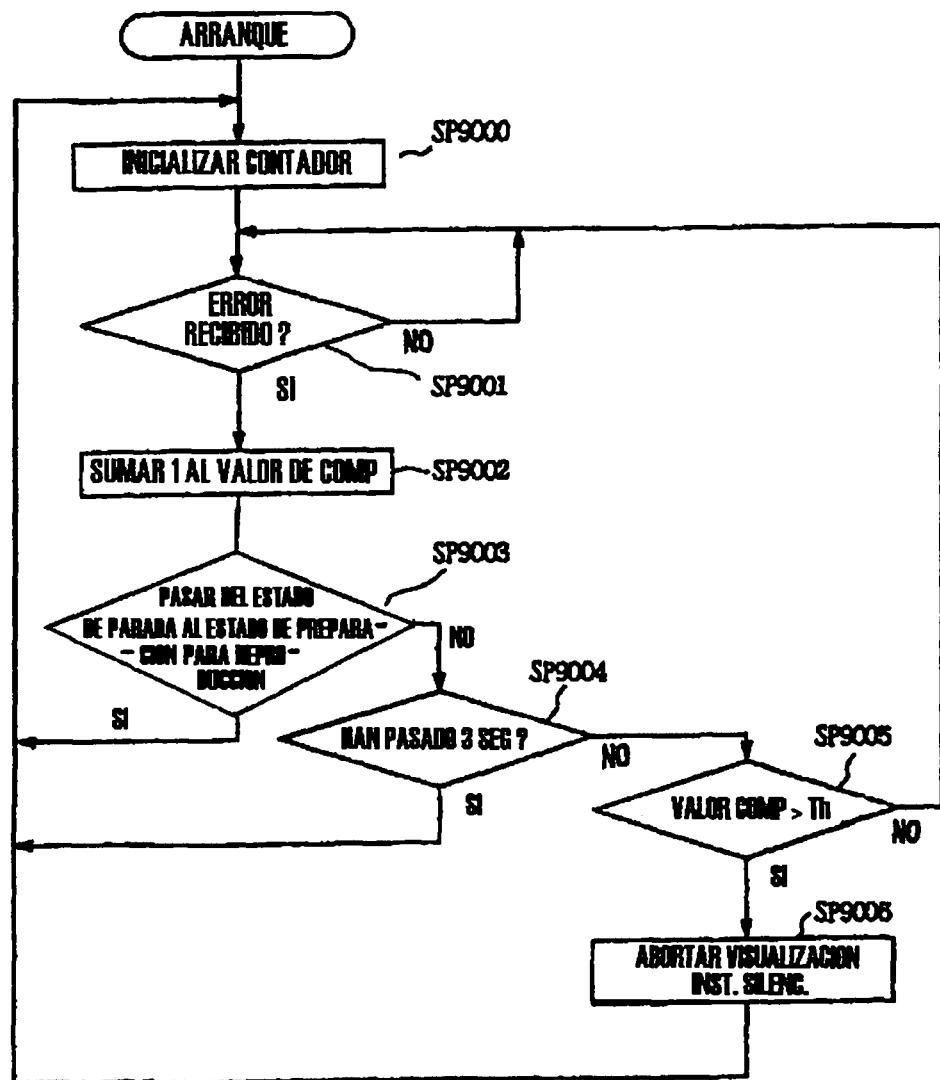

- 35 La figura 28 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 para detectar un error;

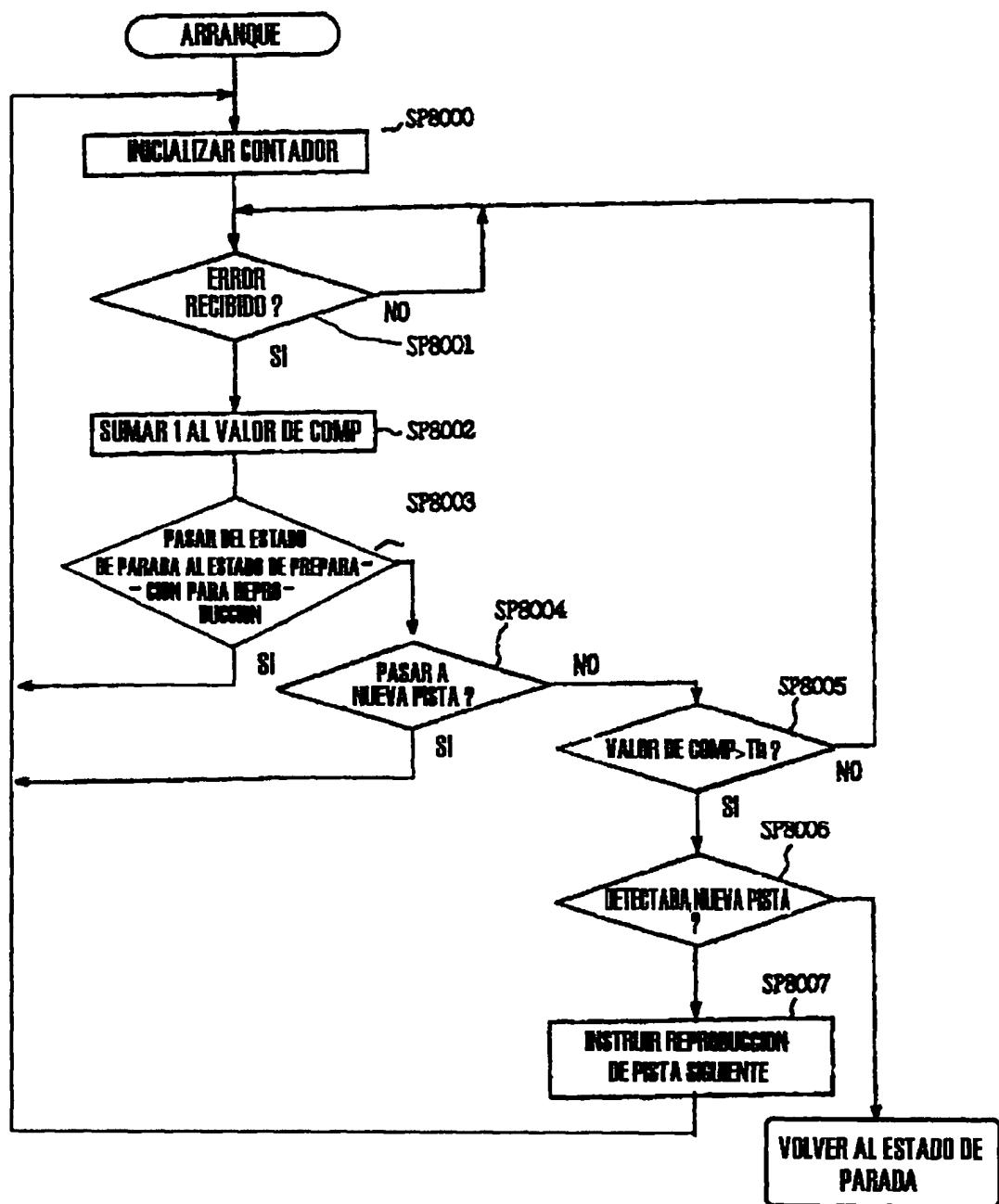

- La figura 29 es un diagrama de flujo que ilustra otro tratamiento realizado por el controlador 16 para detectar un error;

- 40 La figura 30 es un diagrama de flujo que ilustra otro tratamiento realizado por el controlador 16 para detectar un error;

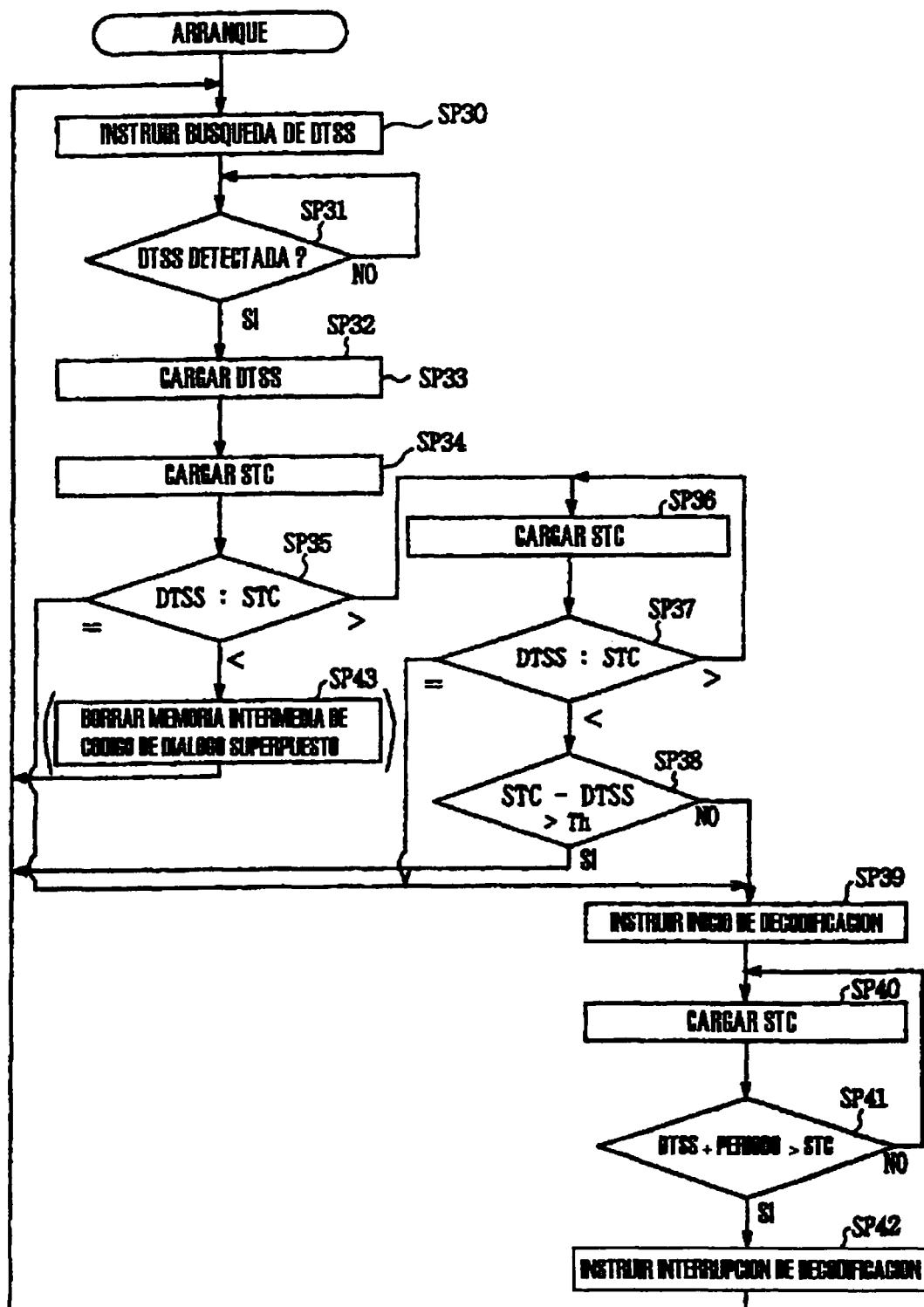

- La figura 31 es un diagrama de flujo que ilustra el tratamiento de datos de diálogo superpuesto realizado por el controlador 16;

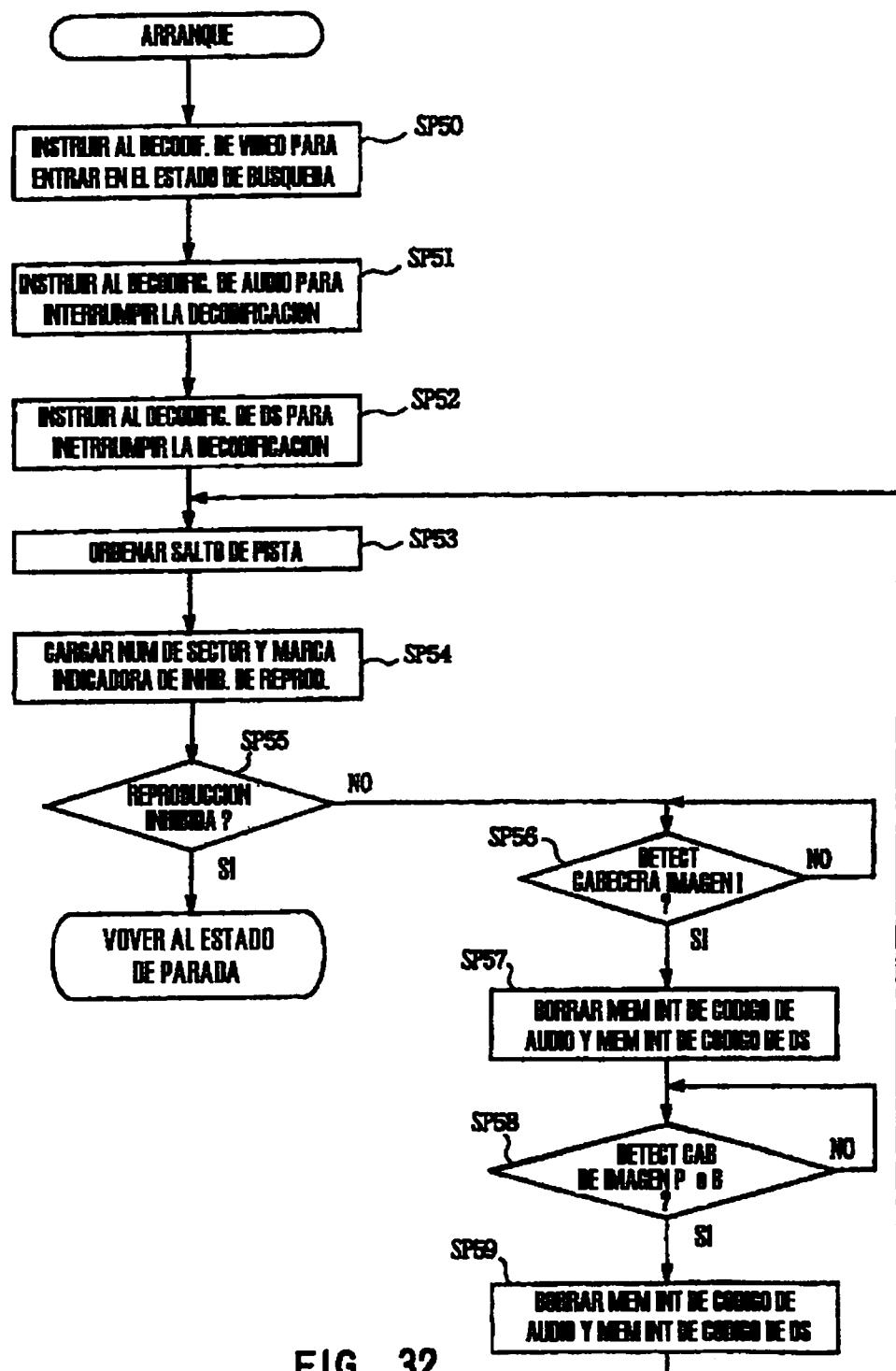

- 45 La figura 32 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 en su estado de búsqueda;

- La figura 33 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 en su estado de parada;

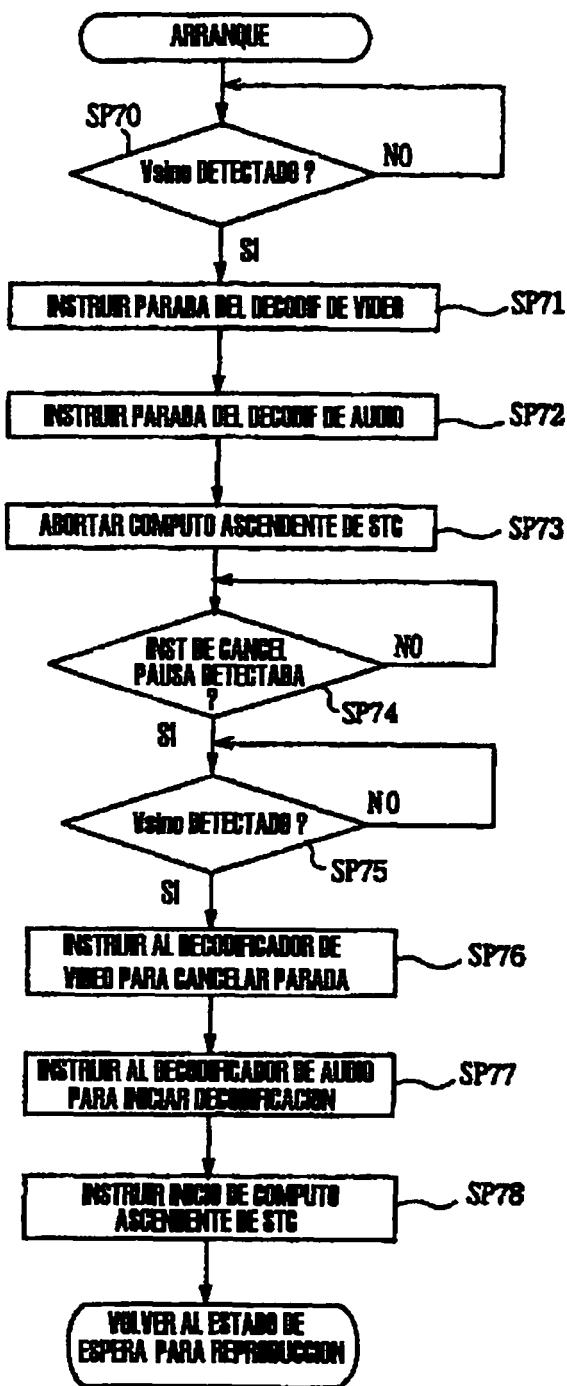

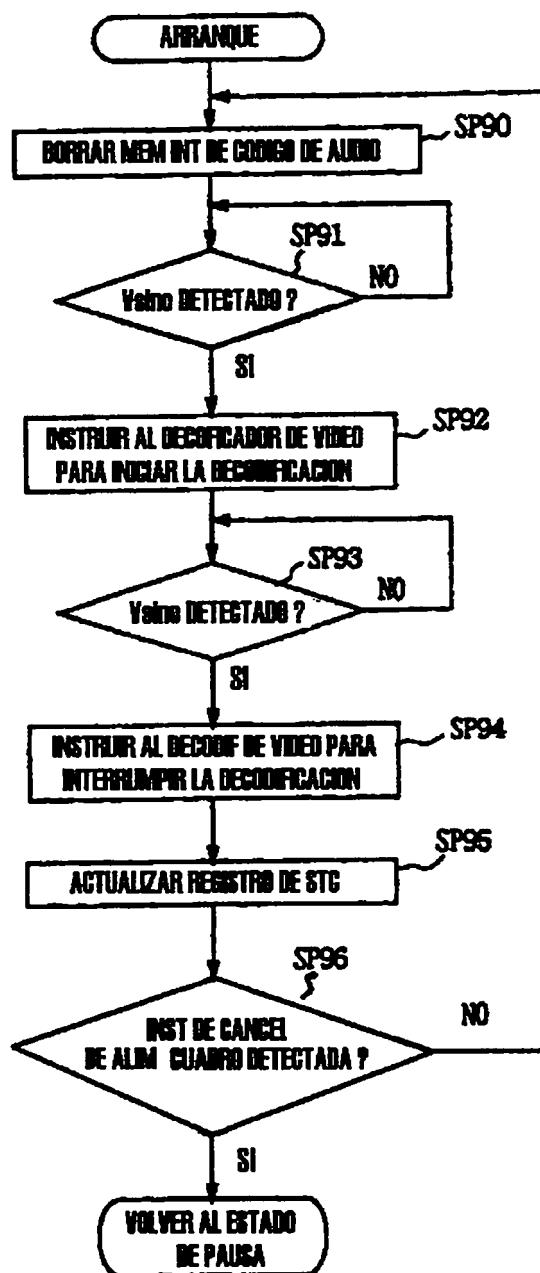

- 50 La figura 34 es un diagrama de flujo que ilustra el tratamiento realizado por el controlador 16 en su estado de alimentación de cuadro;

- La figura 35 es un diagrama de bloques que ilustra la configuración de un aparato de reproducción de datos convencional; y

- 55 La figura 36 es un diagrama esquemático que describe un salto de pista en el aparato de reproducción de datos de la figura 35.

**Modo idóneo para realizar el invento**

Se describe una realización de este invento con referencia a los dibujos.

5 (1) *Configuración del Aparato de Reproducción de Datos*

La figura 1 ilustra en general un aparato de reproducción de datos de acuerdo con una realización de este invento, en el que un medio 1 de almacenamiento de datos comprende un disco óptico que puede extraerse de una unidad 2 de disco que almacena datos digitales, tales como datos de video, datos de audio, datos de diálogo superpuesto, e 10 información de tabla de contenidos (TOC). Sin embargo, el medio 1 de almacenamiento de datos puede ser un medio de almacenamiento óptico extraíble o separable, un medio de almacenamiento magnético, un medio de almacenamiento optoelectrónico o un elemento de almacenamiento semiconductor, u otro medio de almacenamiento de datos digitales.

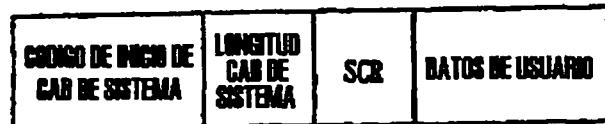

La unidad 2 de disco tiene una sección de mecanismo para cargar y descargar mecánicamente el medio 1 de 15 almacenamiento de datos, y un controlador que controla un captador que contiene una cabeza óptica para leer señales de reproducción del medio 1 de almacenamiento de datos. El captador corresponde al medio 1 de almacenamiento de datos, y puede ser una cabeza magnética o una cabeza optoelectrónica. El captador actúa también como puntero de direcciones si el medio 1 de almacenamiento de datos es un elemento semiconductor. La unidad 2 de disco tiene 20 un demodulador que demodula señales de reproducción leídas para obtener datos de subcódigo, datos multiplexados, datos de corrección de error (C1), y datos de corrección de error (C2), y envía dichas señales al dispositivo 3 de corrección de error en el formato ilustrado en la figura 2.

El dispositivo 3 de corrección de error recibe datos de subcódigo, datos multiplexados, datos de corrección de error (C1) y datos de corrección de error (C2) enviados por la unidad 2 de disco en el formato ilustrado en la figura 25 2, y utiliza los datos de corrección de error para detectar y corregir errores. Analiza también datos de subcódigo con error corregido para obtener datos de número de sector. Asocia también datos de número de sector y una marca indicadora de error, obtenida de los datos de subcódigo, a datos multiplexados con error corregida, y transfiere los datos multiplexados a una memoria intermedia 4 en anillo en el formato ilustrado en la figura 7A. La figura 12 muestra la configuración de un dispositivo 3 de corrección de error. Una memoria 30 de acceso aleatorio almacena 30 datos suministrados por la unidad 2 de disco. Un conmutador 31 comunica el destino de los datos leídos de la memoria de acceso aleatorio a un circuito 32 de corrección de error o a un circuito 34 de adición de datos. El circuito 32 de corrección de error utiliza datos de corrección de error (C1) y datos de corrección de error (C2) para corregir errores. El circuito 34 de adición de datos suma datos de número de sector y datos de una marca indicadora de error suministrados 35 por un controlador 33, a datos multiplexados leídos de la memoria 30 de acceso aleatorio. El controlador 33 controla las direcciones de la memoria 30 de acceso aleatorio y el conmutador 31, y analiza los datos de subcódigo. En el estado de lectura de tabla de contenidos que se describe posteriormente, el conmutador 31 puede estar activado continuamente al circuito 32 de corrección de error para realizar la corrección de error para los mismos datos una pluralidad de veces.

Para datos que comprenden ocho bits de datos multiplexados a los cuales se añade un bit según se requiera, se 40 añade una marca indicadora de error de estado "0" a los datos multiplexados si los datos no implican error o el error de los datos está corregido completamente, mientras que se añade una marca indicadora de error de estado "1" a los datos si el error es incorregible. El dispositivo 3 de corrección de error envía datos de subcódigo a un decodificador 21 de subcódigo solamente si los datos no implican error o si el error se ha corregido completamente.

45 El decodificador 21 de subcódigo decodifica datos de subcódigo suministrados por el dispositivo 3 de corrección de error para transferir los datos decodificados a un circuito 16 de control.

La memoria intermedia 4 en anillo contiene una memoria de salida en el orden de entrada, y almacena transitoriamente 50 los datos multiplexados, datos de número de sector, y una marca indicadora de error enviada por el dispositivo 3 de corrección de error en el formato ilustrado en la figura 7A para transferir datos multiplexados, los datos de número de sector asociados y la marca indicadora de error en el formato ilustrado en la figura 7A en respuesta a un puntero de lectura indicado por un circuito 26 de control de memoria intermedia en anillo.

Todos los datos transmitidos por el dispositivo 3 de corrección de error pueden ser memorizados transitoriamente 55 de un modo incondicional; solamente puede seleccionarse y memorizarse un número limitado de datos partiendo del número de sector de un punto de iniciación de lectura especificado por el controlador 16; solamente puede memorizarse transitoriamente una cantidad limitada de datos finalizando con un punto de finalización especificado por el controlador; o solamente puede memorizarse transitoriamente una cantidad limitada de datos dentro del margen específico definido entre el número de sector de un punto de iniciación especificado por el controlador 16 y el número de sector de un punto de finalización especificado también por el controlador 16. Este modo de funcionamiento puede ser conmutado mediante un circuito 26 de control de memoria intermedia en anillo.

Si el punto de iniciación y/o punto de finalización ha sido especificado por el controlador 16, el circuito 26 de control de memoria intermedia en anillo informa al controlador 16 cuando se detectan los datos en un punto de iniciación o en un punto de finalización de memoria intermedia. Recibe también una instrucción de carga de datos de tabla de contenidos para cargar datos de tabla de contenidos procedentes del dispositivo 3 de corrección de error en una región específica para datos de tabla de contenidos en una memoria intermedia, y detecta el final de la carga de datos para comunicarlo al controlador 16. El circuito 26 de control de memoria intermedia en anillo transfiere datos

de tabla de contenidos cargados y almacenados en la memoria intermedia 4 en anillo en respuesta a una solicitud del controlador 16. Adicionalmente, como en el caso del circuito 106 de control de memoria intermedia en anillo y el circuito 118 de determinación de salto de pista ilustrados en la figura 35, el circuito 26 de control de memoria intermedia en anillo vigila la cantidad de datos almacenados en la memoria intermedia 4 en anillo y ordena a la sección 5 de accionamiento de la unidad 2 de disco que realice un salto de pista según cuando se requiere.

El demultiplexor 5 divide los datos multiplexados enviados por la memoria intermedia 4 en anillo e ilustrados en la figura 7A, en una cadena de bits de video, una cadena de bits de audio y una cadena de bits de datos de diálogo superpuesto, y transfiere cabeceras de video y datos, cabeceras de audio y datos, y cabeceras de diálogo superpuesto 10 y datos, a la memoria intermedia 6 de código de video, a la memoria intermedia 9 de código de audio y a la memoria intermedia 12 de código de diálogo superpuesto, como se muestra en las figuras 7B, 7C y 7D, respectivamente.

El demultiplexor 5 envía una marca indicadora de error correspondiente a cada uno de los datos de video, de audio 15 o de diálogo superpuesto, a la memoria intermedia 6 de código de video, a la memoria intermedia 9 de código de audio, o a la memoria intermedia 12 de código de diálogo superpuesto, respectivamente. Sin embargo, interrumpe las solicitudes de código a la memoria intermedia 26 en anillo y aborta la transferencia de datos a la memoria intermedia 6 de código de video, a la memoria intermedia 9 de código de audio, y a la memoria intermedia 12 de código de diálogo superpuesto, si recibe una señal que indica que la memoria intermedia 6 de código de video, la memoria intermedia 9 20 de código de audio, o la memoria intermedia 12 de código de diálogo superpuesto, se han desbordado.

El demultiplexor 5 detecta también datos de número de sector, señales de referencia de reloj de sistema (SCR) almacenadas en una cabecera de sistema, una marca de instante de inicio de decodificación de video (DTSV) almacenada en una cabecera de datos de video para indicar el instante de iniciación de decodificación de datos de video, una marca de instante de inicio de decodificación de datos de audio (DTSA) almacenada en una cabecera de datos de audio para indicar el instante de iniciación de decodificación de datos de audio, y una marca de instante de inicio de decodificación 25 de datos de diálogo superpuesto (DTSS) almacenada en una cabecera de datos de diálogo superpuesto para indicar el instante de iniciación de decodificación de datos de diálogo superpuesto, para enviar una señal al controlador 16 que indica que ha detectado los datos de número de sector, una de las señales de referencia de reloj de sistema, una marca de instante de inicio de decodificación de video, una marca de instante de inicio de decodificación de audio, y una marca de instante de inicio de decodificación de datos de diálogo superpuesto. Retiene también datos de número de 30 sector detectado, señales de referencia de reloj de sistema, una marca de instante de inicio de decodificación de video, una marca de instante de inicio de decodificación de audio y una marca de instante de inicio de decodificación de datos de diálogo superpuesto, y comunica sus contenidos al controlador 16 cuando es ordenado por este último.

Si el demultiplexor 5 comprueba la continuidad de números de sector para encontrar que han sido suministrados 35 por la memoria intermedia 4 en anillo datos con números de sector discontinuos, inserta entre el sector discontinuo datos de relleno que contienen una marca indicadora de error de uno o más octetos, y transfiere los datos a la memoria intermedia 6 de código de video, a la memoria intermedia 9 de código de audio, y a la memoria intermedia 12 de código de diálogo superpuesto, para informar a estas memorias de la pérdida de datos en esa posición, o de la presencia de un 40 límite de sector discontinuo creado por una operación de búsqueda.

La memoria intermedia 6 de código de video contiene una memoria de salida en el orden de entrada, y memoriza transitoriamente cabeceras de datos de video y datos de video enviados por el demultiplexor 5 para transferirlos a un detector 7 de marca de instante de inicio de decodificación de video cuando es solicitado por el decodificador 8 de 45 video. Emite también una señal que informa al demultiplexor 5 y al controlador 16 del desbordamiento por exceso o desbordamiento por defecto de la memoria intermedia de código de video si la memoria intermedia se desborda por exceso o por defecto.

El detector 7 de marca de instante de inicio de decodificación de video permite solamente la transferencia de los 50 datos de video de la cabecera de datos de video, y de los datos de video enviados por la memoria intermedia 6 de código de video, con el fin de transferirlos al decodificador 8 de video. Detecta también una marca de instante de inicio de decodificación de video en una cabecera de datos de video para transmitir una señal al controlador 16 que indica que ha sido detectada la marca de instante de inicio de decodificación de video, y retiene la marca de instante de inicio de decodificación de video detectada en su registro interno para informar al controlador 16 de dicha retención 55 cuando es ordenado por este último.

El decodificador 8 de video incluye un decodificador MPEG acorde con la norma ISO1172 (MPEG1) o con la norma ISO13818 (MPEG2), y decodifica datos de video transferidos desde el detector 7 de marca de instante de inicio 60 de decodificación de video para enviar los resultados a un post procesador 15. Durante la decodificación, interrumpe la decodificación, reanuda la decodificación, busca una cabecera de imagen I, y comunica la detección de una cabecera de imagen I al controlador 16. El decodificador MPEG puede detectar una cabecera de imagen, determinar el tipo de cabecera de imagen, es decir si la cabecera de imagen es una cabecera de imagen I, P o B, y comunicar la detección de la cabecera de imagen y su tipo al controlador 16. El decodificador 8 de video sustituye transitoriamente los datos de video resultantes de la decodificación por una pantalla negra o azul para suprimir la salida. Envía también una señal 65 que informa al controlador 16 de que se está produciendo un error si encuentra que los datos comprimidos recibidos contienen una descripción sintácticamente incoherente o si intenta decodificar datos con una marca indicadora de error.

## ES 2 268 815 T3

La memoria intermedia 9 de código de audio contiene una memoria de salida en el orden de entrada, y memoriza cabeceras de datos de audio y datos de audio enviados por el demultiplexor 5 para transferir dichos datos a un detector 10 de marca de instante de inicio de decodificación de audio cuando es solicitado por el decodificador 11 de audio. Emite también una señal que informa al demultiplexor 5 y al controlador 16 del desbordamiento por exceso o del desbordamiento por defecto de la memoria intermedia de código de audio si la memoria intermedia se desborda por exceso o por defecto.

Al igual que el detector 7 de marca de instante de inicio de decodificación de video, el detector 10 de marca de instante de inicio de decodificación de audio permite solamente la transferencia de los datos de audio de la cabecera de datos de audio y de los datos de audio enviados por la memoria intermedia 9 de código de audio, con el fin de transferir dichos datos al decodificador 11 de audio. Detecta también una marca de instante de inicio de decodificación de audio en una cabecera de datos de audio para transmitir una señal al controlador 16 y al decodificador 11 de audio indicando que ha sido detectada la marca de instante de inicio de decodificación de audio. Retiene también la marca de instante de inicio de decodificación de audio detectada en su registro interno para informar al controlador 16 del estado de retención cuando es ordenado por este último.

El decodificador 11 de audio decodifica datos de audio comprimidos o no comprimidos transferidos desde el detector 10 de marca de instante de inicio de decodificación de audio para enviar los resultados al terminal de salida de audio. Durante la decodificación, interrumpe la decodificación, reanuda la decodificación, repite la decodificación de datos de audio durante un período especificado, y omite datos de audio durante un período especificado. Por ejemplo, el período especificado se refiere a cuatro niveles de duración: 1 s, 100 ms, 10 ms y 1 ms, y la unidad de decodificación mínima para datos comprimidos. El decodificador 11 de audio interrumpe la decodificación cuando recibe una señal del detector 10 de marca de instante de inicio de decodificación de audio que indica que ha sido detectada una marca de instante de inicio de decodificación de audio. Tiene también una función de reducción de volumen a un nivel intermedio, para reducir transitoriamente el volumen del sonido de las salidas de audio decodificadas a un nivel especificado, y una función de atenuación total para eliminar el volumen del sonido.

La memoria intermedia 12 de código de diálogo superpuesto contiene una memoria de salida en el mismo orden de entrada, y memoriza transitoriamente cabeceras de datos de diálogo superpuesto y datos de diálogo superpuesto transmitidos por el demultiplexor 5 para transferir dichos datos a un detector 13 de marca de instante de inicio de decodificación de datos de diálogo superpuesto. Emite también una señal que informa al demultiplexor 5 y al controlador 16 del desbordamiento por exceso o del desbordamiento por defecto de la memoria intermedia 12 de código de diálogo superpuesto si la memoria intermedia se desborda por exceso o por defecto.

El detector 13 de marca de instante de inicio de decodificación de datos de diálogo superpuesto permite solamente la transferencia de los datos de diálogo superpuesto de la cabecera de datos de diálogo superpuesto, y de los datos de diálogo superpuesto enviados por la memoria intermedia 12 de código de diálogo superpuesto, para transferir dichos datos al decodificador 14 de datos de diálogo superpuesto. Detecta también una marca de instante de inicio de decodificación de datos de diálogo superpuesto en la cabecera de datos de diálogo superpuesto y el tiempo de duración en los datos de diálogo superpuesto para transmitir una señal al controlador 16 que indica que han sido detectados dichos datos, y retiene la marca de instante de inicio de decodificación de datos de diálogo superpuesto detectada y la información de tiempo de duración en su registro interno para informar al controlador 16 del estado de retención cuando es ordenado por este último.

Cuando es detectada una marca de instante de inicio de decodificación de datos de diálogo superpuesto durante una operación de búsqueda de marca de instante de inicio de decodificación de datos de diálogo superpuesto, el detector 13 de marca de instante de inicio de decodificación de datos de diálogo superpuesto envía una señal al decodificador 14 de datos de diálogo superpuesto y al controlador 16 indicando que ha sido detectada la marca de instante de inicio de decodificación de datos de diálogo superpuesto. El decodificador 14 de datos de diálogo superpuesto decodifica los datos de diálogo superpuesto enviados por el detector 13 de marca de instante de inicio de decodificación de datos de diálogo superpuesto para transferir los resultados al post procesador 15.

Durante la decodificación, el decodificador 14 de datos de diálogo superpuesto interrumpe la decodificación, reanuda la decodificación e interrumpe la salida de los resultados de la decodificación. Durante la búsqueda de marca de instante de inicio de decodificación de datos de diálogo superpuesto, omite datos de diálogo superpuesto, en vez de decodificar dichos datos, hasta que recibe una señal de detección de marca de instante de inicio de decodificación de datos de diálogo superpuesto del detector 13 de marca de instante de inicio de decodificación de datos de diálogo superpuesto.

El post procesador 15 genera una señal de video para visualizar información que muestra el estado en curso del aparato de reproducción de datos en respuesta a una instrucción procedente del controlador 16, y sintetiza una señal de video enviada por el decodificador 8 de video, una señal de video enviada por el decodificador 14 de datos de diálogo superpuesto, y una señal de video transmitida para mostrar el estado en curso del aparato de reproducción de datos para transmitir la señal de video sintetizada al terminal de salida de video.

El controlador 16 puede recibir información de cada sección y emitir señales, y también puede controlar el funcionamiento de todo el aparato de reproducción de datos ilustrado en la figura 1. Una interfaz externa 17 recibe órdenes de un equipo de computador o de sistemas de edición para transmitir dichas órdenes al controlador 16. Un dispositivo

18 de entrada de usuario recibe entradas de teclado aplicados por un usuario a través de pulsadores o por un generador remoto de órdenes, para transmitir dichas señales al controlador 16.

- Un dispositivo 19 de visualización de información visualiza información que muestra el estado en curso del aparato de reproducción en respuesta a una instrucción procedente del controlador 16, utilizando, por ejemplo, lámparas o un dispositivo de visualización de cristal líquido. Un circuito 22 de generación de señal de sincronismo vertical genera señales de sincronismo vertical para aplicarlas al decodificador 8 de video, al decodificador 14 de datos de diálogo superpuesto, al post procesador 15 y al controlador 16.

- Un registro 23 de impulsos de reloj de sistema (STC) es incrementado en respuesta a una señal procedente de un circuito 24 de cómputo ascendente de STC, e implementa una señal de reloj de referencia para reproducir sincrónicamente datos de video, datos de audio y datos de diálogo superpuesto. El controlador 16 puede fijar arbitrariamente valores para el registro 23 de STC. El registro 23 de STC en esta realización es independiente del controlador 16, mientras que en otra realización puede estar incorporado en el controlador 16 como programa.

- El circuito 24 de cómputo ascendente de STC genera señales, tales como señales pulsatorias de una frecuencia especificada, para enviarlas al registro 23 de STC. Dicho circuito interrumpe también la salida al registro 23 de STC en respuesta a una instrucción procedente del controlador 16. El circuito 24 de cómputo ascendente de STC y el registro 23 de STC actúan como sistema generador de señales de reloj interno. Al igual que el registro 23 de STC, el circuito 24 de cómputo ascendente de STC en esta realización es independiente del controlador 16, mientras que en otra realización puede estar implementado como generador de señal de cómputo en la forma de un programa.

## (2) Configuración del Medio de Almacenamiento de Datos

- En el medio 1 de almacenamiento de datos, todos los datos están almacenados en sectores, y la posición de inicio para leer datos del medio 1 de almacenamiento de datos es especificada por el controlador 16 utilizando un número de sector. Una vez que ha sido especificada una posición de iniciación, se leen continuamente los sectores subsiguientes, a no ser que el controlador 16 especifique una nueva posición. Por ejemplo, cuando se especifica el sector 100 como posición de iniciación, los sectores son leídos en el orden 100, 101, 102, 103 ..., hasta que se especifica una nueva posición de lectura.

La figura 2 muestra que cada sector consiste en 6208 octetos y comprende cuatro tipos de datos: datos de subcódigo, datos multiplexados, datos de corrección de error (C1), y datos de corrección de error (C2). La cantidad de estos datos en cada sector es de 64, 4096, 1024 y 1024 octetos, respectivamente. Entre los cuatro tipos de datos, se reproducen los datos multiplexados, y los tres tipos de datos restantes, es decir los datos de subcódigo, los datos de corrección de error (C1) y los datos de corrección de error (C2), son datos suplementarios para aumentar la velocidad de multiplexado y la precisión de reproducción.

- Como se muestra en la figura 10, los datos de subcódigo comprenden información de número de sector, información de código de tiempo, información de identificación de contenido de subcódigo, y una marca indicadora de inhibición de reproducción. La información de número de sector contiene el número de sector de un sector, la información de código de tiempo contiene información que representa el instante en que será reproducido el sector, la información de contenido de datos contiene información que muestra el contenido de los datos de subcódigo (por ejemplo, "01" si los datos contienen una marca indicadora de inhibición de reproducción), y la marca indicadora de inhibición de reproducción contiene una marca indicadora (por ejemplo, "FF") que muestra si el sector es o no una zona de entrada, una zona de salida o una zona en que se almacenan datos, tales como datos de tabla de contenidos que no se reproducen. Los restantes 59 octetos están reservados, y puede inscribirse otra información en estos octetos como datos de subcódigo. Los datos multiplexados incluyen datos multiplexados que comprenden datos de video, datos de audio y datos de diálogo superpuesto a reproducir, y otros datos tales como programas de computador.

Los datos de corrección de error (C1) y los datos de corrección de error (C2) corresponden a información para detectar y corregir errores en datos de subcódigo y datos multiplexados, así como los propios datos de corrección de error. Puesto que los datos de corrección de error (C1) y los datos de corrección de error (C2) tienen diferentes direcciones de intercalación, la repetición de correcciones con ambos datos C1 y C2 mejora la capacidad de corrección de error.

La figura 3 muestra el tipo de datos almacenados en la sección de datos multiplexados de cada sector, donde los datos están clasificados utilizando números de sector. Los datos almacenados en los datos multiplexados contienen datos de video, datos de audio, y datos de diálogo superpuesto multiplexados, pero contienen excepcionalmente datos especiales, tales como datos de tabla de contenidos almacenados en los sectores -3000 a 1023. Los datos de video, de audio y los datos de diálogo superpuesto a reproducir están almacenados en el sector 1024 y sectores subsiguientes.

Está dispuesta en los sectores -3000 a -1 del medio DMS1 un área denominada área de tabla de contenidos. El área de tabla de contenidos contiene datos de tabla de contenidos, es decir información correspondiente al contenido de los datos almacenados en el medio DMS1. Como se muestra en la figura 3, los mismos datos de tabla de contenidos están almacenados en tres regiones, a saber en los sectores -3000 a -2001, en los sectores -2000 a -1001, y en los sectores -1000 a -1, para mejorar la fiabilidad de detección de error. Sin embargo, el tamaño de los datos de tabla de contenidos no deberá superar mil sectores. Los usuarios pueden especificar números de sector a través del dispositivo

# ES 2 268 815 T3

18 de entrada de usuario o a través de las diez teclas en la interfaz externa 17 para obtener imágenes y voces deseadas. Sin embargo, puesto que los datos de tabla de contenidos están previstos para control y no deberá establecerse acceso a ellos durante la reproducción normal, el área de tabla de contenidos está preparada con números de sector negativos que no pueden ser especificados por teclas ordinarias de teclados de diez teclas.

5 Los sectores del medio DSM 1 que contienen datos que corresponden a datos de video, datos de audio, y datos de diálogo superpuesto multiplexados, están agrupados en una o más pistas de acuerdo con el contenido. Este grupo que comprende una pluralidad de sectores continuos se denomina pista. La figura 5 muestra la configuración de los datos de tabla de contenidos. Los datos de tabla de contenidos comprenden una cabecera de tabla de contenidos, un tamaño 10 de tabla de contenidos, un número de pistas-información para cada pista, una cabecera de tabla de puntos de entrada, una tabla de puntos de entrada, y una marca de final de tabla de contenidos.

15 La cabecera de tabla de contenidos contiene un patrón de datos especiales que muestra que la tabla de contenidos se inicia en esta posición. El tamaño de la tabla de contenidos contiene la longitud de los datos de tabla de contenidos en octetos. Esta información para cada pista comprende el número de pista para cada pista, un número de sector de iniciación, y un número de sector final, una marca indicadora de pista de título y una marca indicadora de pista final, una marca indicadora de pista de inhibición de reproducción, una marca indicadora de codificador de video, una marca indicadora de codificador de audio, una marca indicadora de codificador de diálogo superpuesto, y una marca indicadora de información válida de marca indicadora de codificación.

20 El número de pista contiene el número de serie de una pista. El rango normal de los valores de número de pista debe estar definido entre 1 y 254. El número de sector de iniciación en el punto de iniciación y el número de sector final en el punto de finalización representan el rango de la pista en el medio DSM 1. Las marcas indicadoras de título y pista muestran que la pista es una pista de título o una pista final, respectivamente.

25 La marca indicadora de inhibición de reproducción está activada para inhibir la reproducción de la pista, y no está activada cuando no está inhibida la reproducción de la pista. La marca indicadora de video, audio y diálogo superpuesto muestra si están multiplexados o no datos de video, datos de audio y datos de diálogo superpuesto en los datos multiplexados en la pista, respectivamente. Cada marca indicadora de multiplexado puede mostrar el grado de multiplexado para cada tipo de datos dentro de la pista.

30 La marca indicadora de información válida de marca indicadora de multiplexado muestra si son o no válidos los contenidos de las marcas indicadoras de multiplexado precedentes de video, audio y diálogo superpuesto. Por ejemplo, cada una de las tres marcas indicadoras precedentes no pueden estar fijadas en un solo valor si el estado 35 del multiplexado para datos de video, datos de audio y datos de diálogo superpuesto varía dentro de una sola pista. En este caso, se inscribe un valor arbitrario en las tres marcas indicadoras, y se almacena en la marca indicadora de información válida de marca indicadora de multiplexado un valor que representa la condición de no validez.

40 En el ejemplo anterior de información en una pista, puede añadirse a cualquiera de las pistas 1 a 254 un atributo que indica que la pista corresponde a un título o a una pista final. Sin embargo, el tratamiento de datos del aparato de reproducción puede simplificarse reduciendo el tamaño de los datos de tabla de contenidos y asegurando que el medio DSM 1 de almacenamiento de datos contiene solamente una pista de título y una pista final, sustituyendo la estructura del medio de almacenamiento de datos de la figura 3 por la estructura representada en la figura 4, y sustituyendo la estructura de los datos de tabla de contenidos de la figura 5 por la estructura de la figura 6, y disponiendo pistas especiales con números de pista de 0 y 255 para una pista de título y una pista final y fijando sus posiciones en el medio DSM 1 de almacenamiento de datos.

45 La cabecera de tabla de puntos de entrada contiene una pauta de datos especial que indica que la tabla de puntos de entrada comienza en esta posición. La tabla de puntos de entrada comprende un número de puntos de entrada e información para los puntos de entrada. El número de puntos de entrada comprende el número de puntos de entrada en el medio DSM 1 de almacenamiento de datos, las posiciones de los puntos de entrada representados por números de sector, e información de código de tiempo almacenada en los datos de subcódigo en el sector.

50 La tabla de puntos de entrada se utiliza durante procedimientos de acceso aleatorio y búsqueda. La tabla de puntos de entrada debe ser referenciada cuando los datos de video están comprimidos con una tasa de compresión variable en conformidad con las normas ISO11172 (MPEG1) o ISO13818 (MPEG2), porque el aumento en los números de sectores no es proporcional al aumento en los códigos de tiempo. La marca de final de tabla de contenidos contiene una pauta especial de datos que indica que la tabla de contenidos finaliza en esta posición.

## 60 (3) *Funcionamiento del Aparato de Reproducción de Datos*

### (3-1) *Encendido*

65 La figura 11 es un diagrama de transición del estado de funcionamiento del controlador 16. El controlador 16 entra en el estado de inicialización cuando se conecta la potencia de alimentación del aparato de reproducción de datos representado en la figura 1. La figura 13 muestra el flujo de tratamiento correspondiente al controlador en su estado de inicialización. En este estado, el controlador 16 instruye al dispositivo 19 de visualización de información para encender una lámpara que indica que se ha conectado la alimentación, e instruye también al post procesador 15 para

- hacer que un dispositivo de visualización, tal como un tubo de rayos catódicos (no representado) visualice un mensaje indicando que se ha conectado la alimentación de potencia (operación SP100). El controlador 16 lee subsiguientemente las pautas de prueba almacenadas en la memoria 25 de solo lectura para inscribirlas en las correspondientes memorias instaladas en el dispositivo 3 de corrección de error, en la memoria intermedia 4 en anillo, en la memoria intermedia 6 de código de video, en la memoria intermedia 9 de código de audio, en la memoria intermedia 12 de código de diálogo superpuesto, y en el dispositivo 20 de almacenamiento, y lee a continuación dichos datos de las memorias (operación SP102) para comprobar si estas memorias están o no funcionando con precisión (comprobación de memorias; operación SP103).

- 5 10 Si se descubre un error durante la comprobación de memorias, el controlador 16 instruye al dispositivo 19 de visualización de información para encender una lámpara que indica que se está produciendo un error, e instruye también al post procesador 15 para hacer que un dispositivo de visualización, tal como un tubo de rayos catódicos (no representado), visualice un mensaje que indica que se está produciendo un error en una memoria (operación SP104). En este estado, el controlador 16 ignora subsiguientemente todas las entradas de la interfaz externa 17 y del dispositivo 15 18 de entrada de usuario, con la excepción de una instrucción de descarga de disco. Adicionalmente, no lee datos ni señales del medio DSM 1 de almacenamiento de datos. El controlador 16 desactiva también la fuente de alimentación durante un período de tiempo especificado si se está produciendo un error en una memoria (operación SP105).

20 Si no se está produciendo ningún error en las memorias, el controlador 16 envía una señal a la unidad 2 de disco consultando si está cargado o no el medio DSM 1 de almacenamiento de datos (operación SP106). Cuando recibe esta señal, la unidad 2 de disco transmite una señal al controlador 16 indicando si está cargado o no en ese momento el medio DSM 1 de almacenamiento de datos. Se determina si está cargado o no dicho medio utilizando para la detección un microinterruptor instalado en la sección de mecanismo de la unidad 2 de disco, o comprobando si puede aplicarse o no un foco luminoso en una parte predeterminada del medio DSM 1 de almacenamiento de datos. Si el controlador 25 16 recibe una señal que indica que está cargado en ese momento el medio DSM 1 de almacenamiento de datos, entra en el estado de lectura de tabla de contenidos (TOC) en la operación SP2 ilustrada en la figura 11 (operación SP107). Recíprocamente, si el controlador 16 recibe una señal que indica que no está cargado en ese momento el medio DSM 1 de almacenamiento de datos, instruye al dispositivo 19 de visualización de información para encender una lámpara que indica que no está cargado el medio DSM 1 de almacenamiento de datos, e instruye también al post procesador 15 30 para visualizar un mensaje que muestra que el medio DSM 1 de almacenamiento de datos no está cargado (operación SP108). El controlador 16 espera subsiguientemente hasta que recibe una señal de la unidad 2 de disco que indica que está cargado el medio DSM 1 de almacenamiento de datos.

35 La unidad 2 de disco detecta la introducción por el usuario del medio DSM 1 de almacenamiento de datos en la unidad 2 de disco para realizar la carga mecánica, tal como la alineación del medio DSM 1 de almacenamiento de datos, con el fin de hacer posible que el captador de la unidad 2 de disco lea señales. Una vez que se ha completado la carga, la unidad 2 de disco envía una señal al controlador 16 indicando que está cargado el medio DSM 1 de almacenamiento de datos. El controlador 16 entra en el estado de lectura de TOC (tabla de contenidos) en la operación SP2 de la figura 11 cuando recibe una señal que indica que se ha completado la carga mientras espera una señal 40 procedente de la unidad 2 de disco que indica que está cargado el medio DSM 1 de almacenamiento de datos.

### *(3-2) Lectura de TOC (tabla de contenidos)*

45 La figura 14 muestra el flujo de tratamiento realizado por el controlador 16 en su estado de lectura de tabla de contenidos. Cuando entra en el estado de lectura de tabla de contenidos, el controlador 16 instruye al dispositivo 3 de corrección de error para entrar en el modo de lectura de tabla de contenidos (operación SP200). El controlador 16 instruye también a la unidad 2 de disco para buscar una sección en la que están inscritos los primeros datos de tabla de contenidos, es decir el sector -3000 (operaciones SP201 y SP202).

50 La unidad 2 de disco lee datos del medio DSM 1 de almacenamiento de datos para transferirlos al dispositivo 3 de corrección de error. El dispositivo 3 de corrección de error detecta y corrige cualquier error en los datos enviados por la unidad 2 de disco y transfiere los datos multiplexados a la memoria intermedia 4 en anillo y los datos de subcódigo al decodificador 21 de subcódigo. Sin embargo, el número de posibles repeticiones de correcciones C1 y C2 debe fijarse de modo que sea mayor que en la reproducción normal, porque el controlador 16 ha instruido a la unidad de disco para entrar en el modo de lectura de tabla de contenidos.

55 Es decir, ambos procedimientos C1 y C2 de corrección de error ejecutados por el dispositivo 3 de corrección de error se realizan solamente una vez durante la reproducción normal de datos para reducir el tiempo comprendido entre la carga de datos procedentes del medio DSM 1 de almacenamiento de datos y la salida de video del post procesador 15 o del decodificador 11 de audio, apareciendo los datos en el terminal de salida de audio.

60 Sin embargo, la capacidad de corrección de error puede mejorarse repitiendo los procedimientos C1 y C2 de corrección de error un gran número de veces si no es necesario reducir el tiempo entre la carga de datos y la reproducción. En consecuencia, para la lectura de datos de tabla de contenidos, que no necesita ser rápida sino que requiere una alta fiabilidad de datos, el dispositivo 3 de corrección de error repite la secuencia de tratamiento de corrección de error si el controlador 16 ha fallado en corregir un error a pesar de su primer intento utilizando una sola corrección C1 de error y una sola corrección C2 de error. El dispositivo 3 de corrección de error puede repetir incondicionalmente ambas correcciones C1 y C2 varias veces, por ejemplo cuatro veces.

Aunque el número de correcciones de error se aumenta para datos de tabla de contenidos para potenciar la capacidad de corrección de error, no puede ser completamente corregido, incluso mediante correcciones de error repetidas, un error de ráfaga en el medio DSM 1 de almacenamiento de datos, es decir la pérdida de datos en un rango amplio. De este modo, si no puede corregirse un error después de un número especificado de correcciones de error, el controlador 5 16 instruye a la unidad 2 de disco para buscar la posición en la que se está produciendo el error, y lee datos nuevamente del medio DSM 1 de almacenamiento de datos para intentar detectar y corregir el error en los datos cargados. Este tratamiento de lectura repetida no se realiza durante la reproducción normal porque ocupa una gran cantidad de tiempo. En este estado de lectura de tabla de contenidos, sin embargo, el controlador 16 realiza esta operación.

10 Si no puede corregirse un error después de un número predeterminado de lecturas repetidas de datos del medio DSM 1 de almacenamiento de datos, el controlador instruye a la unidad de disco para buscar la segunda información de tabla de contenidos almacenada en tres posiciones diferentes en el medio DSM 1 de almacenamiento de datos para su carga, e intenta entonces cargar la información en la memoria intermedia 4 en anillo, como en la carga de los primeros datos de tabla de contenidos. El controlador 16 ejecuta la misma operación para la tercera información 15 de tabla de contenidos si ha fallado en la lectura de la segunda información de tabla de contenidos. Tales lecturas de posiciones diferentes son posibles porque están almacenados los mismos datos de tabla de contenidos en tres posiciones, e imposibles durante la reproducción normal. En este estado de lectura de tabla de contenidos, sin embargo, el controlador 16 realiza esta operación (operaciones SP202, SP203, SP204, SP205, SP206).

20 Si el controlador 16 falla en la lectura de todos los datos de tabla de contenidos almacenados en las tres posiciones, instruye al dispositivo 19 de visualización de información para encender un indicador luminoso que indica que ha fallado la lectura de tabla de contenidos, e instruye también al post procesador 15 para visualizar un mensaje en la pantalla que muestra un error de lectura de tabla de contenidos (operación SP207). El controlador 16 instruye también a la unidad 2 de disco para descargar el disco (operación SP208) y entra en el estado de inicialización. La unidad 2 de 25 disco descarga el disco cuando recibe una instrucción de descarga del controlador 16.

30 El controlador 16 instruye al circuito 26 de control de memoria intermedia en anillo para iniciar la carga de tabla de contenidos cuando se ha completado la corrección de error de tabla de contenidos (operación SP209). El circuito 26 de control de memoria intermedia en anillo controla un puntero de inscripción para cargar los datos de tabla de contenidos en una región específica para carga de datos de tabla de contenidos en la memoria instalada en la memoria intermedia 4 en anillo. La memoria intermedia 4 en anillo inscribe en la región destinada a datos de tabla de contenidos 35 en su memoria datos de reproducción transferidos desde el dispositivo 3 de corrección de error. En este caso, todos los datos de tabla de contenidos ilustrados en la figura 5 se cargan en la memoria si la memoria intermedia 4 en anillo tiene una capacidad suficiente para almacenar esta cantidad de datos, mientras que en otro caso se cargan los datos de tabla de contenidos excluyendo la cabecera de tabla de puntos de entrada y la tabla de puntos de entrada.

40 La memoria intermedia 4 en anillo puede detectar la carga de una marca de final de tabla de contenidos para detectar el final de la carga de datos de tabla de contenidos; cuando detecta el final de la carga, la memoria intermedia 4 en anillo informa al controlador 16 de esta situación. El controlador 16 recibe una señal de la memoria intermedia 4 en anillo que indica el final de la carga, y entra a continuación en el estado de parada (operación SP210).

### *(3-3) Estado de Parada (reproducción de pista de título/pista final)*

45 La figura 15 muestra el flujo de tratamiento realizado por el controlador 16 en su estado de parada. Cuando entra en el estado de parada, el controlador 16 determina si se acaba de cargar o no la tabla de contenidos (operación SP300). El controlador 16 reproduce la pista de título si se acaba de cargar la tabla de contenidos. En otro caso, por ejemplo si ha finalizado justamente la reproducción de todos o parte de los datos del medio DSM 1 de almacenamiento de datos, el controlador 16 instruye la reproducción de la pista final.

50 Para la reproducción de una pista de título, el controlador 16 referencia los datos de tabla de contenidos (operación SP301), y si existe una pista con una marca que indica que es una pista de título, reproduce la pista independientemente de una instrucción de reproducción generada por el usuario (operación SP302). Para la reproducción de una pista final, como en el caso de la reproducción de una pista de título, el controlador 16 referencia datos de tabla de contenidos (operación SP303), y si existe una pista con una marca que indica que es una pista final, reproduce esa 55 pista independientemente de una instrucción de reproducción generada por el usuario (operación SP304).

60 En el estado de parada, el controlador 16 envía una instrucción de parada, una instrucción de parada de corrección de error, una instrucción de parada de memorización intermedia y una instrucción de interrupción de multiplexor, a la unidad 2 de disco, al dispositivo 3 de corrección de error, a la memoria intermedia 4 en anillo y al demultiplexor 5, respectivamente, si no puede encontrar una pista de título o una pista final a reproducir o si ha finalizado la reproducción de una pista de título o una pista final (operación SP305). Borra también la memoria intermedia 6 de código de video, la memoria intermedia 9 de código de audio y la memoria intermedia 12 de código de diálogo superpuesto (operación SP306).

65 En el estado de parada, el controlador 16 espera una instrucción de iniciar reproducción, enviada por el usuario a través del dispositivo 18 de entrada de usuario o a través de la interfaz externa 17 (operación SP307). Instruye también al dispositivo 19 de visualización de información y al post procesador 15 para encender una lámpara que indica el estado de parada y para visualizar el mensaje asociado en la pantalla (operación SP308).

## ES 2 268 815 T3

El dispositivo 18 de entrada de usuario envía una señal de inicio de reproducción al controlador 16 cuando el usuario realiza entradas por teclado requeridas para iniciar la reproducción. En este caso, si las pistas a reproducir han sido especificadas por el usuario, la información correspondiente a los números de pista es transferida también al controlador 16. La interfaz externa 17 envía una señal de inicio de reproducción al controlador 16 cuando recibe la correspondiente instrucción de un equipo externo (no representado). En este caso, o si el equipo externo ha especificado los números de pistas a reproducir, los números de pista son transferidos el controlador 16.

- 5 El controlador 16 entra en estado de preparación para reproducción en la operación SP4 en la figura 11 cuando recibe una señal de inicio de reproducción del dispositivo 18 de entrada de usuario o del circuito 17 de interfaz externa.

- 10 10 El controlador 16 inicia la reproducción con la pista representada por el número “1” de pista si el dispositivo 18 de entrada de usuario o la interfaz externa 17 no han especificado los números de pistas a reproducir.

### *(3-4) Estado de Preparación para Reproducción*

- 15 La figura 16 muestra el flujo de tratamiento realizado por el controlador 16 en su estado de preparación para reproducción. Cuando entra en el estado de preparación para reproducción, el controlador 16 instruye al dispositivo 19 de visualización de información y al post procesador 15 para encender una lámpara que indica que está siendo preparada la reproducción y para visualizar el mensaje asociado en la pantalla (operación SP400). El controlador 16 inicializa entonces la memoria intermedia 4 en anillo, el demultiplexor 5, la memoria intermedia 6 de código de video, el decodificador 8 de video, la memoria intermedia 9 de código de audio, el decodificador 11 de audio, la memoria intermedia 12 de código de diálogo superpuesto, el decodificador 14 de datos de diálogo superpuesto, el post procesador 15 y el dispositivo 20 de almacenamiento (operación SP401). Sin embargo, no inicializa los datos de tabla de contenidos cargados y almacenados en la memoria intermedia 4 en anillo.

- 20 25 El controlador 16 instruye al dispositivo 3 de corrección de error para entrar en el modo de reproducción normal (operación SP402). Esta instrucción hace que el dispositivo 3 de corrección de error realice ambas correcciones C1 y C2 de error una vez cuando se produce un error. El controlador 16 referencia a continuación los datos de tabla de contenidos para obtener el número de sector al comienzo de las pistas a reproducir, y envía una instrucción de búsqueda a la unidad 2 de disco utilizando el número de sector (operación SP403).

- 30 35 El controlador 16 envía una instrucción de inicio de demultiplexado al demultiplexor 5 (operación SP404). El demultiplexor 5 demultiplexa las cadenas de bits multiplexadas transferidas desde la memoria intermedia en anillo en el formato ilustrado en la figura 7A, y transfiere a continuación dichas cadenas a la memoria intermedia 6 de código de video, a la memoria intermedia 9 de código de audio y a la memoria intermedia 12 de código de diálogo superpuesto, como se muestra en las figuras 7B, 7C y 7D, respectivamente. Detecta también las señales de referencia de reloj de sistema almacenadas en la cabecera de sistema, y las retiene en su registro interno.

- 40 La memoria intermedia 6 de código de video almacena datos transferidos desde el demultiplexor 5 en su memoria intermedia, y transfiere dichos datos a continuación al detector 7 de marca de instante de inicio de decodificación de video (DTSV). Similarmente, la memoria intermedia 9 de código de audio y la memoria intermedia 12 de código de diálogo superpuesto almacenan datos transferidos desde el demultiplexor 5 en sus respectivas memorias intermedias, y transfieren estos datos a continuación al detector 10 de marca de instante de inicio de decodificación de audio (DTSA) y al detector 13 de marca de instante de inicio de decodificación de datos de diálogo superpuesto (DTSS).

- 45 50 55 60 El detector 7 de marca de instante de inicio de decodificación de video selecciona solamente los datos de video de los datos enviados por la memoria intermedia 6 de código de video, para transferir dichos datos al decodificador 8 de video. Intenta también detectar una marca de instante de inicio de decodificación de video (DTSV) en la cabecera de video representada en la figura 9, y cuando detecta una marca de instante de inicio de decodificación de video, comunica la detección al controlador 16 y retiene el valor de la marca de instante de inicio de decodificación de video. Similarmente, el detector 10 de marca de instante de inicio de decodificación de audio y el detector 13 de marca de instante de inicio de decodificación de datos de diálogo superpuesto seleccionan solamente los datos de audio y los datos de diálogo superpuesto de los datos enviados por la memoria intermedia 9 de código de audio y la memoria intermedia 12 de código de diálogo superpuesto, para transferir dichos datos al decodificador 11 de audio y al detector 13 de marca de instante de inicio de decodificación de datos de diálogo superpuesto, respectivamente. Intenta también detectar una marca de instante de inicio de decodificación de audio (DTSA) en la cabecera de audio representada en la figura 9, y una marca de instante de inicio de decodificación de datos de diálogo superpuesto (DTSS) en la cabecera de datos de diálogo superpuesto ilustrada también en la figura 9, y cuando detecta una marca de instante de inicio de decodificación de audio y una marca de instante de inicio de decodificación de datos de diálogo superpuesto, comunica la detección al controlador 16 y retiene sus valores, respectivamente. Después de finalizar este tratamiento, el controlador 16 entra en el estado de determinación de método de arranque sincronizado en la operación SP5 de la figura 11.

### *(3-5) Estado de Determinación de Método de Arranque Sincronizado*

- 65 La figura 17 muestra el flujo de tratamiento realizado por el controlador 16 en el estado de determinación de método de arranque sincronizado. Cuando entra en el estado de determinación de método de arranque sincronizado, el controlador 16 ejecuta el tratamiento requerido para iniciar la reproducción de datos de video, datos de audio, y/o datos de diálogo superpuesto. Selecciona un procedimiento de tratamiento utilizado al principio de la reproducción de

datos utilizando datos contenidos en la tabla de contenidos y el estado de detección de una marca de instante de inicio de decodificación de video, una marca de instante de inicio de decodificación de audio, o una marca de instante de inicio de decodificación de datos de diálogo superpuesto, para detectar la presencia de datos de video, datos de audio, y datos de diálogo superpuesto en los datos a reproducir.

5 El controlador 16 referencia las marcas indicadoras de multiplexado de datos de video, datos de audio y datos de diálogo superpuesto en la información correspondiente a cada pista en los datos de tabla de contenidos representados en la figura 5, para detectar la presencia de datos de video, datos de audio y datos de diálogo superpuesto en los datos a reproducir. El controlador 16 carga primero desde la tabla de contenidos almacenada en la memoria intermedia 4 en anillo la información de pista correspondiente a las pistas a reproducir (operación SP500). Determina a continuación si son o no válidas cada una de las marcas indicadoras de multiplexado en base a la marca indicadora de información válida de marca indicadora de multiplexado contenida en la información de pista obtenida (operación SP501). Si falla en esta operación porque la marca indicadora de información válida de marca indicadora de multiplexado es portadora de un valor que indica no validez, ejecuta la misma determinación en base a la presencia de una señal que informa sobre la detección de una marca de instante de inicio de decodificación de video, una marca de instante de inicio de decodificación de audio, o una marca de instante de inicio de decodificación de datos de diálogo superpuesto, enviadas por el detector 7 de marca de instante de inicio de decodificación de video, el detector 10 de marca de instante de inicio de decodificación de audio o el detector 13 de marca de instante de inicio de decodificación de datos de diálogo superpuesto, dentro de un período especificado a partir de la iniciación de la operación de demultiplexado.

10 20 25 30 35 El controlador 16 entra en el estado de arranque sincronizado de audio y video si determina a partir de las marcas indicadoras de multiplexado en la información de tabla de contenidos que están presentes tanto datos de video como datos de audio en las pistas a reproducir, o si se detectan una marca de instante de inicio de decodificación de video y una marca de instante de inicio de decodificación de audio dentro de un período especificado. El controlador entra en el estado de arranque sincronizado solamente de video si determina a partir de las marcas indicadoras de multiplexado contenidas en la información de tabla de contenidos que están presentes datos de video en las pistas a reproducir, mientras que no están presentes datos de audio en estas pistas, o si ha sido detectada una marca de instante de inicio de decodificación de video dentro de un período especificado mientras no ha sido detectada una marca de instante de inicio de decodificación de audio dentro del mismo período. Entra en el estado de arranque sincronizado solamente de audio si determina a partir de las marcas indicadoras de multiplexado contenidas en la información de tabla de contenidos que están presentes datos de audio en las pistas a reproducir, mientras que no están presentes datos de video en estas pistas o si ha sido detectada una marca de instante de inicio de decodificación de audio dentro de un período especificado mientras no ha sido detectada una marca de instante de inicio de decodificación de video dentro del mismo período.

40 45 Adicionalmente, si el controlador 16 determina a partir de las marcas indicadoras de multiplexado contenidas en la información de tabla de contenidos que no están presentes datos de video ni datos de audio en las pistas a reproducir o si no ha sido detectada una marca de instante de inicio de decodificación de video ni una marca de instante de inicio de decodificación de audio dentro de un período especificado, entra en el estado de arranque sincronizado de diálogo superpuesto si ha sido detectada una marca de instante de inicio de decodificación de datos de diálogo superpuesto en ese instante. Adicionalmente, el controlador 16 entra en el estado de parada si determina a partir de la información de tabla de contenidos que no están presentes datos de video ni datos de audio ni datos de diálogo superpuesto, o si no ha sido detectada una marca de instante de inicio de decodificación de video ni una marca de instante de inicio de decodificación de audio ni una marca de instante de inicio de decodificación de datos de diálogo superpuesto dentro de un período de duración especificada (operaciones SP502 a SP510).

### *(3-6) Estado de Arranque Sincronizado de Audio y Video*

50 La figura 18 muestra el flujo de tratamiento para datos de video ejecutado por el controlador 16 en su estado de arranque sincronizado de audio y video. Cuando entra en el estado de arranque sincronizado de audio y video, el controlador 16 ordena al decodificador 8 de video interrumpir la decodificación y buscar una cabecera de imagen I (operación SP600). Puesto que esto promueve la búsqueda de una cabecera de imagen I mientras está interrumpida la decodificación, el decodificador 8 de video no inicia la decodificación después de detectar una cabecera de imagen I, y espera una instrucción de liberación de interrupción del controlador 16. La cabecera de imagen I es una pauta de datos particular colocada al comienzo de datos intra imágenes en datos de video, tales como cadenas de bits de video definidas por las normas ISO11172 (MPEG1) o ISO13818 (MPEG2).

60 Una regla específica que debe almacenarse una marca de instante de inicio de decodificación de video en la cabecera de datos de video en datos de video que contienen una cabecera de imagen I, utilizando el método de codificación ilustrado en el “caso de que la marca indicadora de marca de instante de inicio de decodificación de video sea igual a 1”, cuando están almacenados datos en el medio de almacenamiento de datos en el cual están almacenadas cadenas de bits multiplexadas en conformidad con las normas ISO11172 (MPEG1) o ISO13818 (MPEG2). Esto permite al controlador 16 cargar la marca de instante de inicio de decodificación de video correspondiente a una cabecera de imagen I detectada por el detector 7 de marca de instante de inicio de decodificación de video. La sincronización se inicia con imágenes I porque las imágenes diferentes de las imágenes I, es decir las imágenes P e imágenes B, son codificadas predictivamente utilizando imágenes cargadas transitoriamente antes y/o después de estas imágenes P y B, y el inicio de la decodificación con estas imágenes P y B es así imposible.