(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4004948号

(P4004948)

(45) 発行日 平成19年11月7日(2007.11.7)

(24) 登録日 平成19年8月31日(2007.8.31)

(51) Int.C1.

F 1

HO1L 21/8247 (2006.01)

HO1L 27/10 434

HO1L 27/115 (2006.01)

HO1L 29/78 371

HO1L 29/788 (2006.01)

HO1L 29/792 (2006.01)

請求項の数 49 (全 41 頁)

(21) 出願番号

特願2002-380022 (P2002-380022)

(22) 出願日

平成14年12月27日 (2002.12.27)

(65) 公開番号

特開2003-234422 (P2003-234422A)

(43) 公開日

平成15年8月22日 (2003.8.22)

審査請求日 平成15年1月30日 (2003.1.30)

(31) 優先権主張番号 60/343634

(32) 優先日 平成13年12月27日 (2001.12.27)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 60/355363

(32) 優先日 平成14年2月6日 (2002.2.6)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 10/183834

(32) 優先日 平成14年6月25日 (2002.6.25)

(33) 優先権主張国 米国(US)

(73) 特許権者 500147506

シリコンストーリッジ テクノロジー

インコーポレイテッド

SILICON STORAGE TEC

HNOLOGY, INC.

アメリカ合衆国 94086 カリフォル

ニア州 サニーヴェイル ソノラ コート

1171

(74) 代理人 100059959

弁理士 中村 梓

(74) 代理人 100067013

弁理士 大塚 文昭

(74) 代理人 100082005

弁理士 熊倉 賢男

最終頁に続く

(54) 【発明の名称】水平に向けたエッジをもつフロー・ティングゲートメモリセルの半導体メモリアレーを形成するセルフ・アライン型方法及びそれにより形成されたメモリアレー

## (57) 【特許請求の範囲】

## 【請求項1】

電気的にプログラム可能で且つ消去可能なメモリデバイスのアレーにおいて、

第1導電型の半導体材料の基板と、

上記基板上に形成され、互いにほぼ平行で、且つ第1方向に延びる離間された分離領域とを備え、各対の隣接する分離領域間には活性領域があり、そして

上記活性領域の各々は、複数のメモリセルを含み、各メモリセルは、

上記基板に形成された、第2導電型を有する互いに離間された第1及び第2領域を含み、それらの間には上記基板のチャンネル領域が画成され、

又、上記チャンネル領域の少なくとも一部分の上に配置されてそこから絶縁された導電性のフロー・ティングゲートを含み、このフロー・ティングゲートは、該フロー・ティングゲートの側縁から延びる水平に向けられたエッジを含み、そして

更に、少なくとも一部分が上記水平に向けられたエッジに横方向に隣接して配置されてそこから絶縁された導電性の制御ゲートを含む、ように構成されたメモリデバイスのアレー。

## 【請求項2】

上記メモリセルの各々に対し、上記フロー・ティングゲートの一部分が上記第1領域の一部分の上に配置されてそこから絶縁された請求項1に記載のデバイスのアレー。

## 【請求項3】

上記基板の表面へと形成された複数のトレンチを更に備え、これらのトレンチは、互い

10

20

にほぼ平行で、且つ上記第1方向にほぼ垂直な第2方向に上記分離及び活性領域を横切って延び、上記第2領域の各々は、1つのトレンチの下に形成される請求項1に記載のデバイスのアレー。

【請求項4】

上記メモリセルの各々に対し、上記チャンネル領域は、1つのトレンチの側壁にほぼ沿って延びる第1部分と、上記基板の表面にほぼ沿って延びる第2部分とを有する請求項3に記載のデバイスのアレー。

【請求項5】

上記メモリセルの各々に対して、上記チャンネル領域の第1及び第2部分は、互いにほぼ垂直な方向に延びる請求項4に記載のデバイスのアレー。 10

【請求項6】

上記メモリセルの各々に対し、上記制御ゲートの少なくとも一部分は上記トレンチへと延びる請求項4に記載のデバイスのアレー。

【請求項7】

上記メモリセルの各々に対し、それに含まれる上記第1領域及び上記第2領域を通る方向に平行で、かつ、上記基板の表面に垂直である平面で切った断面において、

上記フローティングゲートは、上記基板の表面にほぼ平行な方向に細長く延び、そして上記制御ゲートは、上記基板の表面にほぼ垂直な方向に細長く延びる請求項3に記載のデバイスのアレー。 20

【請求項8】

各活性領域に対し、上記制御ゲートの各々は、隣接する分離領域を横切って延び、そして別の活性領域に配置された制御ゲートの1つに電気的に接続される請求項6に記載のデバイスのアレー。

【請求項9】

上記第1領域の1つの上に各々配置されて電気的に接触される導電性材料の複数のプロックを更に備えた請求項1に記載のデバイスのアレー。

【請求項10】

上記フローティングゲートの各々は、上記導電性材料のプロックの1つに横方向に隣接して配置されてそこから絶縁される請求項9に記載のデバイスのアレー。 30

【請求項11】

上記フローティングゲートの各々は、上記チャンネル領域の1つのほぼ全第2部分上に配置される請求項4に記載のデバイスのアレー。

【請求項12】

上記フローティングゲートのエッジの各々は、電荷のファウラー・ノルドハイムトンネリングを許す厚みを有する絶縁材料により上記制御ゲートの1つから絶縁される請求項1に記載のデバイスのアレー。

【請求項13】

上記チャンネル領域の第1部分の各々は、上記フローティングゲートの1つに直接的に向かう方向に延びる請求項4に記載のデバイスのアレー。

【請求項14】

上記メモリセルは、メモリセルの対として形成され、そしてメモリセルの各対は、それらの間の1つの第2領域を共有する請求項1に記載のデバイスのアレー。 40

【請求項15】

上記メモリセルは、メモリセルの対として形成され、そしてメモリセルの各対は、それらの間の1つの第1領域を共有する請求項1に記載のデバイスのアレー。

【請求項16】

上記メモリセルの各々は、上記フローティングゲート上に配置されて上記導電性材料のプロックに横方向に隣接する絶縁材料層を更に備えた請求項10に記載のデバイスのアレー。

【請求項17】

50

上記絶縁材料層は、窒化シリコンで作られる請求項 1 6 に記載のデバイスのアレー。

【請求項 1 8】

上記制御ゲートの各々は、

1つのトレンチの側壁に沿って延びてそこから絶縁された第 1 部分と、

1つのトレンチの底壁に沿って延びてそこから絶縁された第 2 部分と、

を備えた請求項 4 に記載のデバイスのアレー。

【請求項 1 9】

上記制御ゲートの各々は、「L」字型である請求項 1 8 に記載のデバイスのアレー。

【請求項 2 0】

上記制御ゲートの各々は、長方形である請求項 1 8 に記載のデバイスのアレー。 10

【請求項 2 1】

上記チャンネル領域の各々は、1つのトレンチの底壁にほぼ沿って延びる第 3 部分を含む請求項 1 8 に記載のデバイスのアレー。

【請求項 2 2】

上記チャンネル領域の各々は、「S」字型である請求項 2 1 に記載のデバイスのアレー。

。

【請求項 2 3】

上記メモリセルの各々は、上記第 2 領域上に配置されてそこに電気的接続された第 1 部分及び上記制御ゲート上に配置されてそこから絶縁された第 2 部分を有するメタルコンタクトを更に備えている請求項 1 に記載のデバイスのアレー。 20

【請求項 2 4】

上記メモリセルの各々に対し、上記ブロックの導電性材料は金属である請求項 9 に記載のデバイスのアレー。

【請求項 2 5】

半導体メモリセルのアレーを形成する方法において、

第 1 導電型を有する半導体基板上に、互いにほぼ平行で且つ第 1 方向に延びる離間された分離領域を形成し、各対の隣接する分離領域間には活性領域が設けられ、

上記半導体基板に、第 2 導電型を有する複数の互いに離間された第 1 及び第 2 領域を形成し、上記基板の活性領域における複数のチャンネル領域が、上記第 1 領域の 1 つと第 2 領域の 1 つの間に各々延びるように画成され。 30

1つのチャンネル領域の少なくとも一部分の上に各々配置されてそこから絶縁された導電性材料の複数のフローティングゲートを形成し、各フローティングゲートは、該フローティングゲートの側縁から延びる水平に向けられたエッジを含み、そして

各々の少なくとも一部分が上記水平に向けられたエッジの 1 つに横方向に隣接して配置されてそこから絶縁された複数の導電性制御ゲートを形成する、

という段階を備えた方法。

【請求項 2 6】

上記複数の制御ゲートは、互いにほぼ平行であり、そして上記活性及び分離領域を横切って上記第 1 方向にほぼ垂直の第 2 方向に延びる請求項 2 5 の記載の方法。

【請求項 2 7】

上記フローティングゲートの各々は、1つの上記第 1 領域の一部分の上に配置されてそこから絶縁される請求項 2 5 に記載の方法。 40

【請求項 2 8】

上記半導体基板の表面へと複数のトレンチを形成する段階を更に備え、これらのトレンチは、互いにほぼ平行で、且つ上記分離及び活性領域を横切って上記第 1 方向にほぼ垂直な第 2 方向に延び、上記第 2 領域の各々は、1つのトレンチの下に形成される請求項 2 5 に記載の方法。

【請求項 2 9】

上記チャンネル領域の各々は、1つのトレンチの側壁にほぼ沿って延びる第 1 部分と、上記基板の表面にほぼ沿って延びる第 2 部分とを有する請求項 2 8 に記載の方法。 50

**【請求項 3 0】**

上記チャンネル領域の第1及び第2部分は、互いにほぼ垂直な方向に延びる請求項29に記載の方法。

**【請求項 3 1】**

各制御ゲートの少なくとも一部分は、1つのトレンチへと延びるように形成される請求項29に記載の方法。

**【請求項 3 2】**

上記制御ゲート各々の形成は、1つのトレンチの側壁に沿って延びてそこから絶縁される第1部分と、1つの水平に向けられたエッジに横方向に隣接して配置されてそこから絶縁された第2部分とを有する導電性材料のスペーサを形成することを含む請求項29に記載の方法。10

**【請求項 3 3】**

上記半導体メモリセルに含まれる上記第1領域及び上記第2領域を通る方向に平行で、かつ、上記基板の表面に垂直である平面で切った断面において、

上記フローティングゲートの各々は、上記基板の表面にほぼ平行な方向に細長く延び、そして

上記制御ゲートの各々は、上記基板の表面にほぼ垂直な方向に細長く延びる請求項28に記載の方法。

**【請求項 3 4】**

互いにほぼ平行であって、且つ上記活性及び分離領域を横切って上記第1方向にほぼ垂直な第2方向に延びる導電性材料の複数のブロックを形成する段階を更に備え、これら導電性材料ブロックの各々は、幾つかの第1領域の上に配置されそしてそれと電気的接触される請求項25に記載の方法。20

**【請求項 3 5】**

上記フローティングゲートの各々は、上記導電性材料ブロックの1つに横方向に隣接して配置されてそこから絶縁された請求項34に記載の方法。

**【請求項 3 6】**

上記フローティングゲートの各々は、1つのチャンネル領域のほぼ第2部分全体の上に形成されてそこから絶縁される請求項29に記載の方法。

**【請求項 3 7】**

上記フローティングゲートエッジの各々と、それに隣接する制御ゲートとの間に、電荷のファウラー-ノルドハイムトンネリングを許す厚みを有する絶縁材料形成する段階を更に備えた請求項25に記載の方法。30

**【請求項 3 8】**

上記チャンネル領域の第1部分の各々は、上記フローティングゲートの1つに直接的に向かう方向に延びる請求項29に記載の方法。

**【請求項 3 9】**

上記フローティングゲートの各々の上に配置され且つ上記導電性材料ブロックの1つに横方向に隣接する絶縁材料層を形成する段階を更に備えた請求項35に記載の方法。

**【請求項 4 0】**

上記絶縁材料層は、窒化シリコンで作られる請求項39に記載の方法。40

**【請求項 4 1】**

上記制御ゲート各々の形成は、

1つのトレンチの側壁に沿って延びそしてそこから絶縁された制御ゲートの第1部分を形成し、そして

1つのトレンチの底壁に沿って延びそしてそこから絶縁された制御ゲートの第2部分を形成する、

という段階を含む請求項29に記載の方法。

**【請求項 4 2】**

上記制御ゲートの各々は、「L」字型である請求項41に記載の方法。50

**【請求項 4 3】**

上記制御ゲートの各々は、長方形である請求項 4 1 に記載の方法。

**【請求項 4 4】**

上記チャンネル領域の各々は、1つのトレンチの底壁にほぼ沿って延びる第3部分を含む請求項 4 1 に記載の方法。

**【請求項 4 5】**

上記チャンネル領域の各々は、「S」字型である請求項 4 4 に記載の方法。

**【請求項 4 6】**

上記第2領域の1つの上に配置されてそこに電気的接続された第1部分、及び上記制御ゲートの1つの上に配置されてそこから絶縁された第2部分を各々有する複数のメタルコントタクトを形成する段階を更に備えた請求項 2 5 に記載の方法。 10

**【請求項 4 7】**

上記ブロックの導電性材料は金属である請求項 3 4 に記載の方法。

**【請求項 4 8】**

半導体材料の基板上に配置されてそこから絶縁された導電性フローティングゲートと、少なくとも一部分がこのフローティングゲートに横方向に隣接して配置されそして絶縁材料によりそこから絶縁された導電性制御ゲートとを有する電気的にプログラム可能で且つ消去可能なメモリデバイスを動作する方法において、

フローティングゲートに電子を誘起するためにフローティングゲートの電圧に対して充分に正である電圧を制御ゲートに印加して、フローティングゲートの側縁から延びる水平に向けられたエッジから、絶縁材料を通して、制御ゲートへとファウラー・ノルドハイムのトンネリングにより横方向にトンネル作用を生じさせる段階を備えた方法。 20

**【請求項 4 9】**

上記フローティングゲートの下に少なくとも部分的に形成されてそこから絶縁された基板のソース領域に正の電圧を印加して、その正の電圧をフローティングゲートに容量性結合し、

上記基板の表面に形成されたトレンチの下に配置された基板のドレイン領域に正の電圧を印加し、そして

上記トレンチへと下方に延びる第1部分と、上記フローティングゲートのエッジに横方向に隣接して配置された第2部分とを有する制御ゲートに正の電圧を印加するという段階を更に備え、 30

電子が誘起されて、上記ドレイン領域から、上記トレンチの側壁にほぼ沿って、上記フローティングゲートへと移動する請求項 4 8 に記載の方法。

**【発明の詳細な説明】****【0 0 0 1】****【発明の属する技術分野】**

本発明は、フローティングゲートメモリセルの半導体メモリアレーを形成するセルフ・アライン型方法に係る。又、本発明は、上記形式のフローティングゲートメモリセルの半導体メモリアレーにも係る。

**【0 0 0 2】****【従来の技術】**

フローティングゲートを使用してそこに電荷を蓄積する不揮発性半導体メモリセル、及び半導体基板に形成されたそのような不揮発性メモリセルのメモリアレーがこの技術で良く知られている。典型的に、このようなフローティングゲートメモリセルは、分割ゲート型又は積層ゲート型となっている。

**【0 0 0 3】****【発明が解決しようとする課題】**

半導体フローティングゲートメモリセルアレーの製造に直面した1つの問題は、ソース、ドレイン、制御ゲート及びフローティングゲートのような種々のコンポーネントを整列することである。半導体集積処理のデザインルールが緩和されるにつれ、最小リソグラフィ 50

一特徴部が減少すると、正確な整列の必要性がより重要となる。又、種々の部品の整列は、半導体製品の製造の収率も決定する。

#### 【0004】

セルフ・アラインは、この技術において良く知られている。セルフ・アラインとは、1つ以上の材料を含む1つ以上のステップ処理において特徴部が互いに自動的に整列されるようにそれらステップを処理する行為を指す。従って、本発明は、セルフ・アライン技術を使用して、フローティングゲートメモリセル形式の半導体メモリアレーの製造を行うものである。

#### 【0005】

単一ウェハ上に形成するメモリセルの数を最大にするためにメモリセルアレーのサイズを縮小することが常に必要とされる。メモリセルを対で形成し、各対が単一ソース領域を共有するようにし、そして隣接セル対が共通のドレイン領域を共有するようにすると、メモリセルアレーのサイズが減少することが良く知られている。しかしながら、通常は、ドレイン領域へのピットライン接続のために、アレーの大きな領域が指定される。このピットライン領域は、メモリセル対間の接触開口、ワードライン間隔に対する接触（これはリソグラフィー発生に大きく依存する）、接触整列及び接触完全性によってしばしば占有される。更に、ワードライントランジスタのために著しいスペースが指定され、そのサイズは、リソグラフィー発生及び接合部スケーリングによって設定される。

10

#### 【0006】

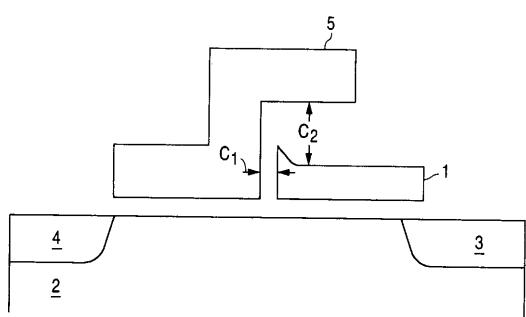

本発明が向けられる別の特徴は、メモリセルの消去性能である。図1は、良く知られた不揮発性メモリセルの設計を示すもので、フローティングゲート1を備え、このフローティングゲートは、ソース及びドレイン領域3/4を有する半導体基板2の上に配置されそしてそこから絶縁される。制御ゲート5は、フローティングゲート1に隣接して横方向に配置された第1部分と、フローティングゲート1の上に垂直方向に配置されてそれに重畠した第2部分とを有する。フローティングゲート1は、制御ゲートの第2部分に向かって上方に延びる比較的鋭いエッジ6を含む。制御ゲート5の重畠部分に向かって延びるこのエッジ6は、メモリセルを消去するのに使用されるファウラー・ノルドハイム(FowlerNordheim)トンネリングを改善する。セルのサイズが縮小されるにつれて、制御ゲート5とフローティングゲート1との間に少なくともある程度の重畠を維持して、上方に向けられた鋭いエッジを消去機能に使用できるようにしなければならない。このセルアーキテクチャーは、制御ゲート5とフローティングゲート1との間の限定重畠キャパシタンスのために消去結合比にスケーリング限界を課する。

20

そこで、メモリセルの消去結合比を不利に妥協せず、セルサイズが著しく減少された不揮発性のフローティングゲート型メモリセルアレーが要望される。

30

#### 【0007】

##### 【課題を解決するための手段】

本発明は、ピットライン接続及びワードライントランジスタに必要なスペースを最小にすると共に制御ゲートとフローティングゲートとの間の垂直方向の重畠の必要性を排除することによりサイズの減少されたメモリセルを形成するためのセルフ・アライン型方法と、それにより形成されたメモリセルアレーとを提供することにより、上記問題を解消する。

40

#### 【0008】

本発明によれば、電気的にプログラム可能で且つ消去可能なメモリデバイスのアレーは、第1導電型の半導体材料の基板と、この基板上に形成され、互いにほぼ平行で、且つ第1方向に延びる離間された分離領域とを備え、各対の隣接する分離領域間には活性領域が設けられる。活性領域の各々は、複数のメモリセルを含み、各メモリセルは、第2導電型を有する基板に形成された第1及び第2の離間された領域を備え、それらの間には基板のチャンネル領域が画成され、更に、各メモリセルは、上記チャンネル領域の少なくとも一部分の上に配置されてそこから絶縁された導電性のフローティングゲートも備え、このフローティングゲートは、該フローティングゲートの側縁から延びる水平に向けられたエッジを含み、そして更に、各メモリセルは、少なくとも一部分が上記水平に向けられたエッジ

50

に横方向に隣接して配置されてそこから絶縁された導電性の制御ゲートも備えている。

#### 【0009】

本発明の別の特徴において、半導体メモリセルのアレーを形成する方法は、第1導電型を有する基板上に、互いにほぼ平行で且つ第1方向に延びる離間された分離領域を形成し、各対の隣接する分離領域間には活性領域が設けられ、更に、第2導電型を有する半導体基板に、複数の離間された第1及び第2領域を形成し、上記基板の活性領域における複数のチャンネル領域が、上記第1領域の1つと第2領域の1つとの間に各々延びるように画成され、更に、1つのチャンネル領域の少なくとも一部分上に各々配置されてそこから絶縁された導電性材料の複数のフローティングゲートを形成し、各フローティングゲートは、該フローティングゲートの側縁から延びる水平に向けられたエッジを含み、そして更に、各々の少なくとも一部分が上記水平に向けられたエッジの1つに横方向に隣接して配置されてそこから絶縁された複数の導電性制御ゲートを形成するという段階を備えている。10

#### 【0010】

本発明の更に別の特徴において、半導体材料の基板上に配置されてそこから絶縁された導電性フローティングゲートと、少なくとも一部分がこのフローティングゲートに横方向に隣接して配置されそして絶縁材料によりそこから絶縁された導電性制御ゲートとを有する電気的にプログラム可能で且つ消去可能なメモリデバイスを動作する方法は、フローティングゲートに電子を誘起するためのフローティングゲートの電圧に対して充分に正である電圧を制御ゲートに印加して、フローティングゲートの側縁から延びる水平に向けられたエッジから、絶縁材料を通して、制御ゲートへとファウラー・ノルドハイムのトンネリングにより横方向にトンネル作用を生じさせる段階を備えている。20

本発明の他の目的及び特徴は、以下の説明、特許請求の範囲及び添付図面から容易に明らかとなろう。

#### 【0011】

##### 【発明の実施の形態】

本発明は、分離領域によって分離された活性領域に不揮発性メモリセルの列を形成するための方法、及びそれにより形成されたメモリセルのアレーに係る。これらメモリセルは、メモリセルの消去結合比を不利に妥協せずに著しいセルサイズ減少を許す独特のメモリセル設計を利用する。

#### 【0012】

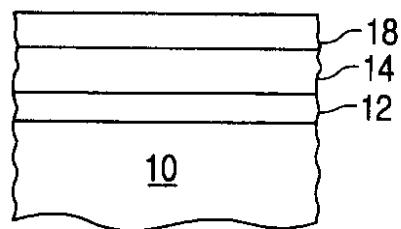

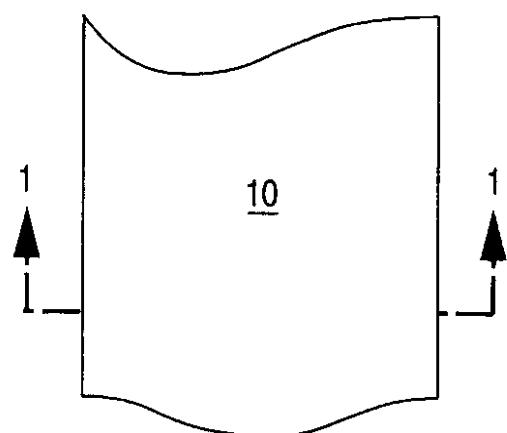

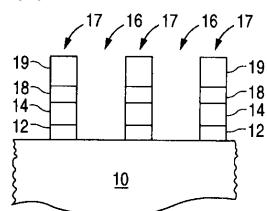

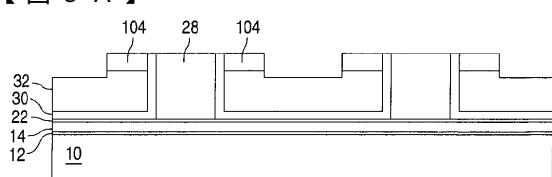

##### 分離領域の形成

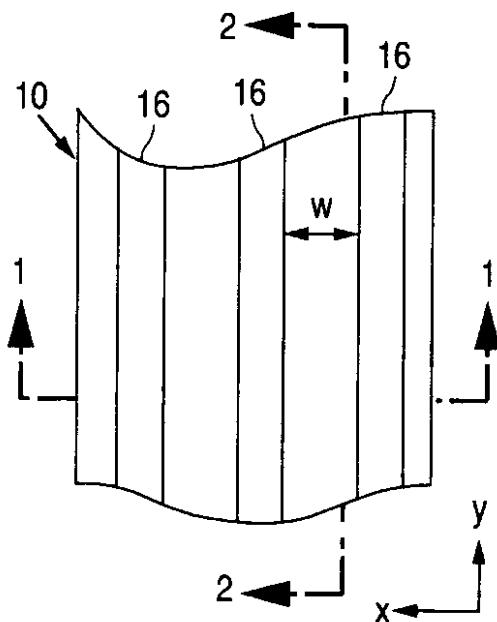

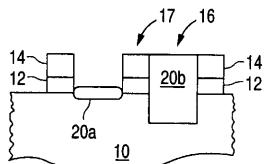

図2Aは、好ましくはP型である良く知られた半導体基板10（又は半導体ウェル）の上面図である。二酸化シリコン（以下「酸化物」という）のような絶縁材料の層12が、図2Bに示すように付着される。この絶縁層12は、酸化又は付着（例えば、化学蒸着即ちCVD）のような公知技術により基板10上に形成され、好ましくは80 厚みの酸化物層が形成される。絶縁材料層12の上にはポリシリコン層14（以下「ポリ」）が付着される（例えば、200ないし700 厚み）。絶縁層12上にポリシリコン層14を付着しそして形成することは、低圧力CVD即ちLPCVDのような公知のプロセスで行うことができる。このポリ層14は、イオンインプランテーションによりドープすることもできるし又は現場でドープすることもできる。ポリシリコン層14の上には、好ましくはCVDにより窒化シリコン層18（以下「窒化物」）が付着される（例えば、500ないし1000 厚み）。この窒化物層18は、分離形成中に活性領域を画成するのに使用される。もちろん、以上に述べたパラメータ及び以下に述べるパラメータは、全て、デザインルール及びプロセス技術の世代に依存する。ここには、0.13ミクロンプロセスについて説明する。しかしながら、本発明は、特定のプロセス技術世代に限定されるものではなく、又、以下に述べるプロセスパラメータの特定値に限定されるものでもないことが当業者に理解されよう。40

#### 【0013】

絶縁層12、ポリシリコン層14及び窒化シリコン層18が形成されると、適当なホトレジスト材料19が窒化シリコン層18上に付着され、そしてマスキングステップが実行され50

て、ある領域（縞 16）からホトレジスト材料が選択的に除去される。ホトレジスト材料 19 が除去されたところでは、窒化シリコン 18、ポリシリコン 14 及びその下の絶縁材料 12 が、図 2 C に示すように、Y 即ち列方向に形成された縞 16 において、標準的なエッティング技術（即ち非等方性エッティングプロセス）を使用してエッティング除去される。隣接する縞 16 間の距離 W は、使用するプロセスの最小リソグラフィー特徴部と同程度に小さくすることができる。ホトレジスト 19 が除去されないところでは、窒化シリコン 18、ポリシリコン領域 14 及びその下の絶縁材料 12 が維持される。それにより得られる構造が図 2 D に示されており、活性領域 17 が分離領域 16 とインターレースしている。以下に述べるように、分離領域の形成には 2 つの実施形態、即ち LOCOS 及び STI がある。STI 実施形態では、エッティングが基板 10 へと所定の深さまで続けられる。

10

#### 【0014】

この構造体は、残留ホトレジスト 19 を除去するように更に処理される。次いで、二酸化シリコンのような分離材料 20a 又は 20b が領域即ち「グループ」16 に形成される。次いで、窒化物層 18 が選択的に除去されて、図 2 E に示す構造体が形成される。分離は、良く知られた LOCOS プロセスを経て形成されて局部フィールド酸化物 20a を生じさせる（例えば、露出した基板を酸化することにより）こともできるし、或いは浅いトレンチプロセス（STI）を経て形成されて、領域 20b に形成された二酸化シリコンを生じさせる（例えば、酸化物層を付着した後に、化学的 - 機械的 - ポリシング（CMP）エッティングにより）こともできる。LOCOS 形成中には、局部フィールド酸化物の形成中にポリ層 14 の側壁を保護するためにスペーサが必要となることに注意されたい。

20

#### 【0015】

残留ポリシリコン層 14 と、その下の絶縁材料 12 が活性領域を形成する。従って、この点において、基板 10 は、活性領域と分離領域の交互の縞を有し、分離領域は、LOCOS 絶縁材料 20a 又は浅いトレンチの絶縁材料 20b のいずれかで形成される。図 2 E は、LOCOS 領域 20a 及び浅いトレンチ領域 20b の両方の形成を示しているが、LOCOS 領域（20a）又は浅いトレンチ領域（20b）の一方のみが使用される。好ましい実施形態では、絶縁材料の浅いトレンチ 20b が形成される。というのは、小さなデザインルールで正確に形成できるからである。図 2 E の構造は、セルフ・アライン構造を表わしており、これは、非セルフ・アライン方法により形成された構造体より更にコンパクトである。

30

#### 【0016】

図 2 E に示す構造体を形成する良く知られた従来の非セルフ・アライン方法は、次の通りである。最初に、分離領域 20 が基板 10 に形成される。これは、基板 10 上に窒化シリコンの層を付着し、ホトレジストを付着し、第 1 マスキングステップを使用して窒化シリコンをパターン化して基板 10 の選択的部分を露出させ、そしてシリコンのトレンチ形成及びトレンチ埋めに関連した場所で LOCOS プロセス又は STI プロセスのいずれかを使用してその露出された基板 10 を酸化することにより実行できる。その後、窒化シリコンが除去され、そして二酸化シリコン層 12（ゲート酸化物を形成するための）が基板 10 上に付着される。このゲート酸化物 12 の上にポリシリコン層 14 が付着される。ポリシリコン層 14 は、次いで、第 2 マスキングステップを使用してパターン化され、そして選択的部分が除去される。従って、ポリシリコン 14 は、分離領域 20 とセルフ・アラインされず、第 2 マスキングステップが必要となる。更に、この付加的なマスキングステップは、ポリシリコン 14 の寸法が、分離領域 20 に対して整列余裕度を有することを必要とする。非セルフ・アライン方法は、窒化物層 18 を使用しないことに注意されたい。本発明のメモリアレーは、セルフ・アラインプロセス又は非セルフ・アラインプロセスのいずれによっても形成できる。

40

#### 【0017】

##### メモリアレーの形成

図 2 E に示す構造体が、セルフ・アライン方法又は非セルフ・アライン方法のいずれかを使用して作られると、その構造体は、次のように更に処理される。図 3 A ないし 3 U は、

50

本発明のプロセスにおいて次のステップが実行されるときに図 2 B 及び 2 E に直交する方向から見た活性領域構造体 17 の断面図である。活性領域 17 の小さなセグメントしか示されていないが、以下に示す処理ステップは、このような領域のアレーを形成する。

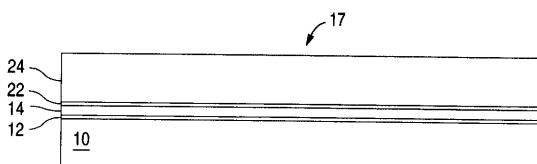

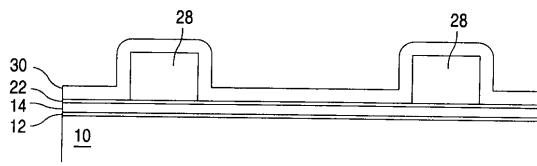

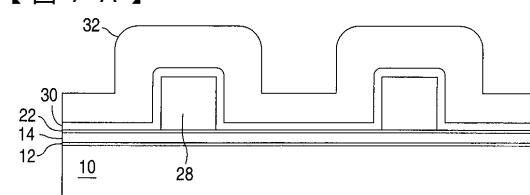

最初に、絶縁層 22 が構造体上に形成される。より詳細には、酸化物層 22 がポリ層 14 の上に形成される（例えば、100ないし200 厚み）。次いで、この酸化物層 22 の上に厚いポリ層 24 が形成される（例えば、3000 厚みまで）。それにより得られる活性領域構造体が図 3 A に示されている。

#### 【0018】

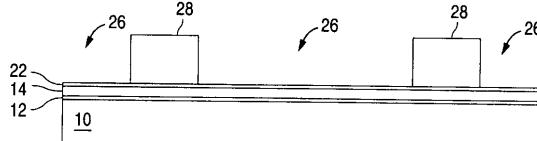

従来のホトリソグラフィー（マスキング）スキムを次に使用して、半くぼみの第 1 トレンチ 26 が構造体に次のように形成される。適当なホトレジスト材料がポリ層 24 に付着され、そしてマスキングステップが実行されて、選択された平行な縞領域からホトレジスト材料が選択的に除去される（その下に第 1 のトレンチ 26 が形成される）。ホトレジスト材料が除去された場所では、露出されたポリシリコン 24 が、標準的なポリエッティングプロセス（例えば、酸化物層 22 をエッティングストッパーとして使用する非等方性ポリエッティング）を使用して除去され、ポリシリコンのブロック 28 が残され、それらの間に第 1 トレンチ 26 が形成される。ポリブロック 28 の巾は、使用するプロセスの最小リソグラフィー特徴部と同程度に小さなものでよい。残留ホトレジストが除去されて、図 3 B に示す構造体が形成される。

#### 【0019】

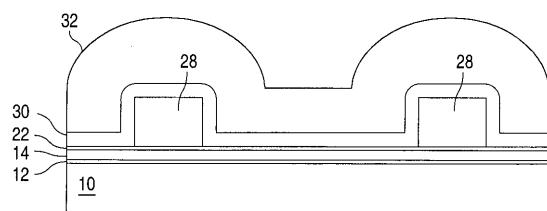

窒化物付着ステップを使用して、図 3 C に示すように、構造体の上に窒化物層 30 が形成される（例えば、300ないし500 厚み）。次いで、図 3 D に示すように、窒化物層 30 の上に、厚い酸化物層 32（例えば、2500 厚み）が付着される。平坦化エッティングプロセスがそれに続き（例えば、化学的 - 機械的 - ポリシング（C M P）エッティング）、これは、厚い酸化物層 32 を下方に、ポリブロック 28 の上部と一緒にエッティング除去する（ポリブロック 28 をポリシングストッパーとして使用して）。又、C M P エッティングは、ポリブロック 28 上の窒化物層 30 の部分も除去する。それにより生じる構造体が図 3 E に示されている。

#### 【0020】

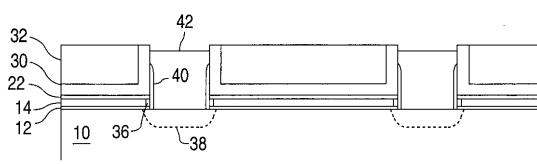

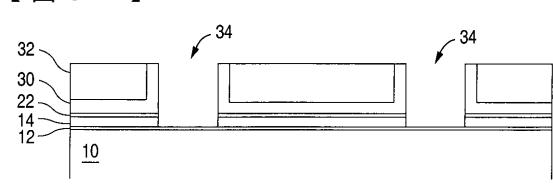

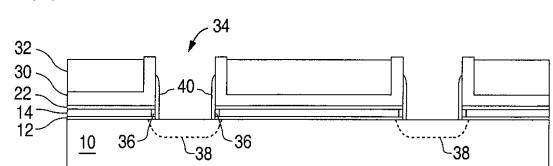

ポリエッティングプロセスを使用して、ポリブロック 28 を除去し（酸化物層 22 をエッティングストッパーとして使用して）、第 2 のトレンチ 34 を形成する。制御された酸化物エッティングを使用して、第 2 のトレンチ 34 の底に露出された酸化物層 22 の部分を除去する（ポリ層 14 をエッティングストッパーとして使用して）。又、この酸化物エッティングは、厚い酸化物層 32 をある程度消費する。別のポリエッティングプロセスを実行して、第 2 のトレンチ 34 の底に露出されたポリ層 14 の部分を除去する（酸化物層 12 をエッティングストッパーとして使用して）。それにより生じる構造体が図 3 F に示されている。

#### 【0021】

熱酸化プロセスを使用してトレンチ 34 においてポリ層 14 の露出端に酸化物側壁層 36 が形成される。次いで、構造体の全表面にわたり適当なイオンインプランテーションが行われる。イオンは、それが各第 2 のトレンチ 34 において酸化物層 12 の露出部分に貫通するに充分なエネルギーをもつ場所では、周囲基板の導電型（例えば P 型）とは異なる導電型（例えば N 型）を有する基板 10 に第 1 領域（ソース領域）38 を形成する。他の全ての領域では、イオンがその下の構造体により吸収され、何の作用も及ぼさない。インプランテーションされたソース領域 38 は、第 2 のトレンチ 34 にセルフ・アラインされる。次いで、側壁スペーサ 40 が第 2 のトレンチ 34 の壁に対して形成される。スペーサの形成は、公知であり、構造体の輪郭にわたって材料を付着し、その後、非等方性エッティングプロセスを実行し、それにより、構造体の水平面から材料を除去する一方、構造体の垂直方向を向いた表面では材料がほぼそのまま残される。スペーサ 40 は、窒化物層 30 及び基板シリコン 10 に対して良好なエッティング選択性をもつ任意の誘電体材料で形成することができる。好ましい実施形態では、絶縁スペーサ 40 は、全構造体上に薄い酸化物層（例えば、200 ）を付着し、その後、良く知られた反応性イオンエッティング（R I E 50

ドライエッティング)のような非等方性エッティングプロセスを行って、スペーサ40を除き付着酸化物層を除去することにより、酸化物で形成される。この酸化物エッティングプロセスは、第2のトレンチ34の底において酸化物層12の露出部分も除去し、基板10及び若干の酸化物層32を露出させる。それにより生じる構造体が図3Gに示されている。

#### 【0022】

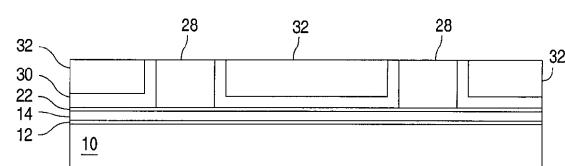

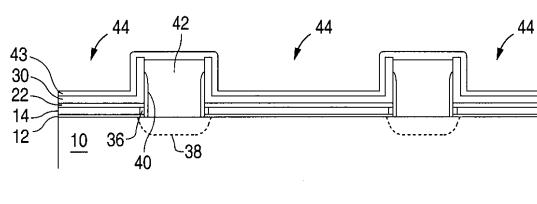

第2のトレンチには、好ましくは次のようにポリブロック42が埋められる。構造体の上にポリシリコンの厚い層が付着される。平坦化プロセス(即ちCMP)を使用して、第2のトレンチ34においてポリブロック42以外の付着ポリシリコンが除去される。ポリブロック42を互いに偶発的に短絡し得るトポグラフィーの問題がもしあれば、それに対処するために、任意のポリエッティングを行って、窒化物層30及び酸化物層32に対してポリブロック34の上面を若干くぼませることができる。ポリブロック42は、アレーの列を横切って延び(図2Cの1-1線に沿って)、そして基板10のソース領域38に直接電気的接触する。それにより得られる構造が図3Hに示されている。

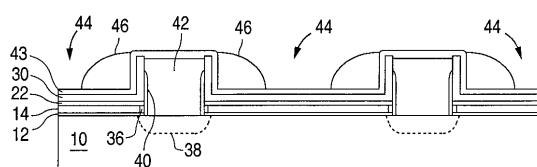

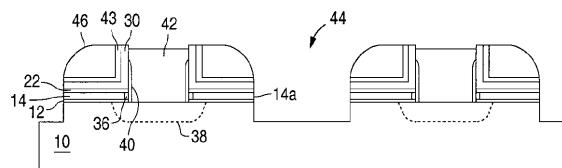

#### 【0023】

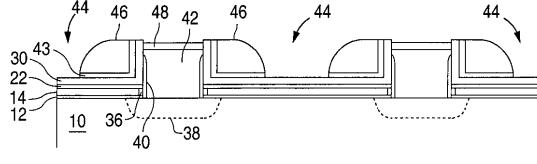

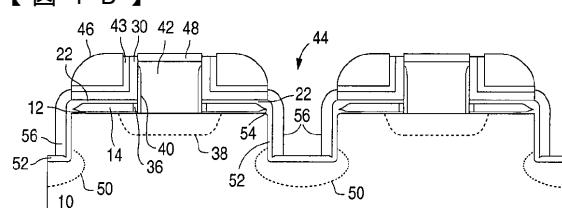

酸化物エッティングを使用して、酸化物層32が除去され、ポリブロック42間に配置された半くぼみの第3のトレンチ44が残される。次いで、従来の技術(例えば、LPCVD)により構造体上に酸化物層43が形成される(例えば、200ないし300)。それにより生じる構造体が図3Iに示されている。窒化物の厚い層(例えば、2000)を付着し、その後、非等方性窒化物(RIEドライ)エッティングを行って、スペーサ46(例えば、巾が1500までのスペーサ)以外の付着窒化物を除去することにより、第3のトレンチ44の側壁に対して窒化物スペーサ46が形成される。それにより生じる構造体が図3Jに示されている。

#### 【0024】

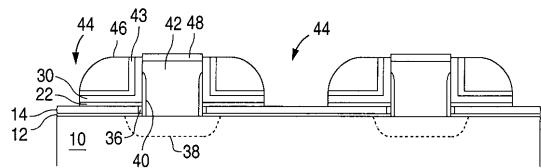

次いで、酸化物エッティングを使用して、酸化物層43の露出部分(即ち、スペーサ46によって保護されていない部分)が除去される。次いで、構造体は、熱酸化プロセスを受け、ポリブロック42上に酸化物層48が形成される。酸化物層48は、ポリブロック42に対してセルフ・アラインされる(例えば、600までの厚みで)。この酸化プロセスの熱サイクル中に、ソース領域38は、基板へと深く押し入る。それにより得られる構造体が図3Kに示されている。

#### 【0025】

非等方性(ドライ)窒化物エッティングを使用して、第3のトレンチに露出された(窒化物スペーサ46間で)窒化物層30の部分が除去される。このときは、酸化物層22がエッティングストッパーとして使用される。この窒化物エッティングは、ポリブロック42及びスペーサ46に隣接する窒化物層30の露出部分も若干除去する。非等方性酸化物エッティングがそれに続き、ポリ層14をエッティングストッパーとして使用して、第3のトレンチ44に露出された(窒化物スペーサ46間で)酸化物層22の部分が除去される。この酸化物エッティングは、酸化物層48の小さな部分も若干消費する。それにより生じる構造体が図3Lに示されている。

#### 【0026】

非等方性(ドライ)ポリエッティングを次に実行し、酸化物層12をエッティングストッパーとして使用して、第3のトレンチに露出された(窒化物スペーサ46間で)ポリ層14の部分が除去される。非等方性(ドライ)酸化物エッティングがそれに続き、第3のトレンチに露出された(窒化物スペーサ46間で)酸化物層12の部分を除去し、第3のトレンチ44の底に基板10を露出させる。この酸化物エッティングは、酸化物層48の小さな部分も若干消費させる。それにより得られる構造体が図3Mに示されている。

#### 【0027】

次いで、シリコン基板10が第3のトレンチ44の底に露出されたままの状態で、シリコンエッティングプロセスを実行して、第3のトレンチ44を基板10へと下方に延長する(例えば、基板表面より下へ500ないし1500の深さまで)。次いで、酸化物エッティングを使用して、酸化物層48を除去し、そして分離酸化物20a又は20b(図2Eに

10

20

20

30

40

50

示す)の上部を、トレンチ44の底にほぼ等しいレベルまで下方にエッティングする。従つて、第3のトレンチ44が連続的に形成され、そして活性及び分離領域17/16を横切って延びる。構造体の表面全体にわたって適當なイオンインプランテーションが再び実行される。このイオンインプランテーションは、基板10の活性領域において第3のトレンチ44の下に第2領域50(埋設ビットラインドレイン領域)を形成する。又、イオンインプランテーションは、露出したポリブロック42をドーピングする(又は更にドーピングする)という作用も有する。第3のトレンチ44の外側で、且つポリブロック42を除いて、イオンが阻止されそして何の作用も果たさない。それにより生じる構造体が図3Nに示されている。第2の領域50は、分離領域内にある第3のトレンチの部分の下には形成されない。というのは、分離酸化物20a又は20bによってイオンが阻止されるからである。

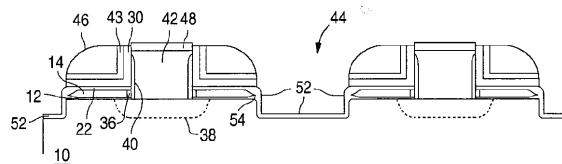

#### 【0028】

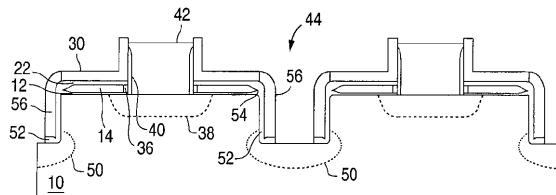

次いで、酸化プロセスが実行され、第3のトレンチ44の露出したシリコン表面を酸化して、これらシリコン表面のライナーとなる薄い酸化物層52が形成される。この酸化プロセスは、第3のトレンチ44の上部の側壁の一部分を形成するポリ層14の露出側縁14aも酸化し、水平に向かれたエッジ54を形成する。各エッジは、図3Oに示すように、第3のトレンチ44の側壁の1つに直接的に向けられる。エッジ54は、細長いエッジ(即ち、かみそりの刃の鋭いエッジのような)であってもよいし、又は短いエッジ(即ち、鉛筆の先端のような)であってもよい。又、この酸化プロセスは、ポリブロック42上に酸化物層48を再成長させる。

それに続き、第3のトレンチ44の側壁に沿ってポリスペーサ56が形成され、これは、構造体上にポリ層を最初に付着する(例えば、2000厚み)ことにより行われる。次いで、乾式の非等方性ドライエッティングプロセスを使用して、第3のトレンチ44の側壁に沿って残されるポリスペーサ56を除き、付着されたポリ層が除去される。それにより生じる構造体が図3Pに示されている。

#### 【0029】

次いで、窒化物エッティングプロセスを使用して、窒化物スペーサ46が除去される。酸化物エッティングがそれに続き、酸化物層48及び43が除去されると共に、図3Qに示すように、第3のトレンチ44の底にある(ポリスペーサ56間に於いて)酸化物層52の露出部分が除去される。窒化物エッティングプロセスがそれに続き(例えば、高温の燐酸において)、図3Rに示すように、窒化物層30が除去される。構造体上に酸化物層を付着し(例えば、500ないし1200厚み)、その後、酸化物エッティング(例えば、RIE)を行うことにより、第3のトレンチの側壁の底に沿って絶縁スペーサ58(好ましくは酸化物)が形成される。又、この酸化物付着及びエッティングプロセスは、ポリスペーサ56に隣接して(ポリエッジ54の上に)酸化物スペーサ60を形成すると共に、酸化物スペーサ40に隣接して酸化物スペーサ62を形成する。これにより生じる構造体が図3Sに示されている。

#### 【0030】

次いで、金属付着ステップが実行され、タングステン、コバルト、チタン、ニッケル、白金、又はモリブデンのような金属が構造体上に付着される。次いで、構造体がアニールされ、高温の金属を第3のトレンチ44の底において基板10の露出部分へ流し込み且つ浸透させて、酸化物スペーサ58間に金属化シリコンの導電層64(シリサイド)を形成できるようにする。基板10における金属化シリコン領域64は、スペーサ58によって第2領域50にセルフ・アラインされるので、セルフ・アラインシリサイド(即ち、サリサイド)と称することができる。又、高温金属は、ポリスペーサ56の露出した上部に金属化ポリシリコンの導電層66(ポリサイド)を形成すると共に、ポリブロック42の露出した上部にポリサイド層68を形成する。残留構造体に付着した金属は、金属エッティングプロセスにより除去される。それにより生じる構造体が図3Tに示されている。

#### 【0031】

BPSG70のようなパッシベーションを使用して構造体をカバーし、これは第3のトレ

10

20

30

40

50

ンチ 4 4 を埋めることを含む。マスキングステップを実行して、サリサイド領域 6 4 の上にエッティング領域が画成される。このエッティング領域において B P S G 7 0 が選択的にエッティングされ、理想的にはサリサイド領域 6 4 ( 及び第 2 領域 5 0 ) を中心とする接触開口が形成される。この接触開口には、次いで、金属付着及び平坦化エッチバックにより導体金属が埋められ、導体コンタクト 7 2 を形成する。サリサイド層 6 4 は、導体 7 2 と第 2 領域 5 0 との間の導通を向上させる。ポリサイド層 6 6 / 6 8 は、ポリスペーサ 5 6 及びポリプロック 4 2 の長さに沿った導通を向上させる。ビットラインコネクタ 7 4 が B P S G 7 0 上の金属マスキングによって各活性領域に追加され、その活性領域において全てのコンタクト 7 2 を一緒に接続する。最終的な構造が図 3 U に示されている。

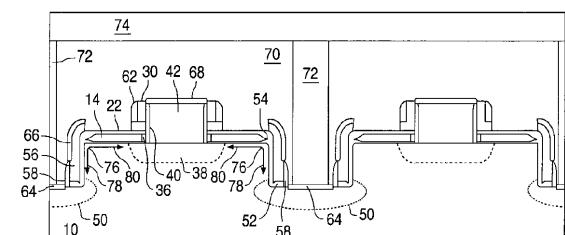

## 【 0 0 3 2 】

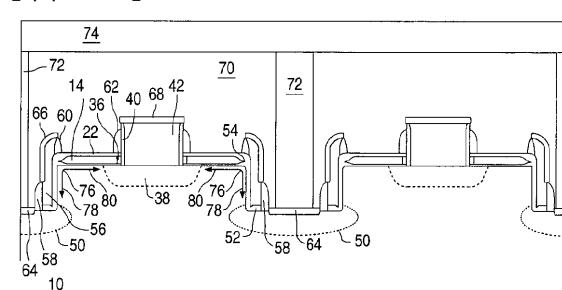

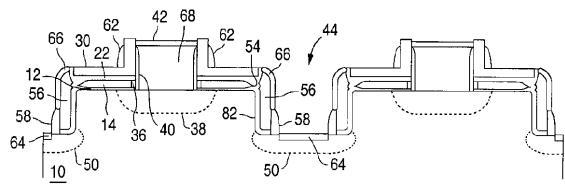

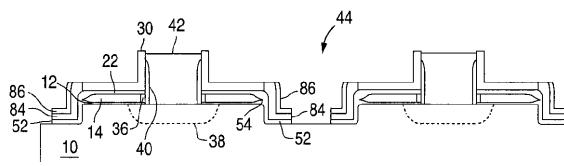

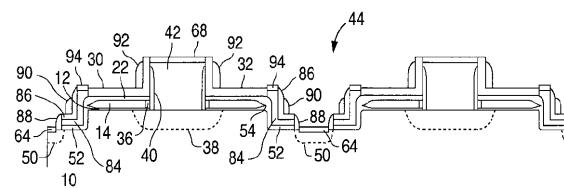

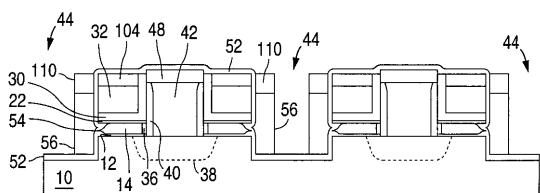

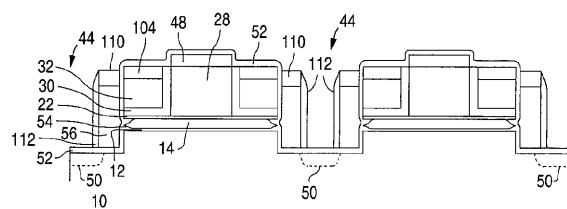

図 3 U に示すように、第 1 及び第 2 の領域 3 8 / 5 0 は、各セルのソース及びドレインを形成する ( ソース及びドレインは動作中に交換できることが当業者に知られているが ) 。ポリ層 1 4 は、フローティングゲートを構成し、そしてポリスペーサ 5 6 は、各メモリセルの制御ゲートを構成する。各メモリセルのチャンネル領域 7 6 は、ソース及びドレイン 3 8 / 5 0 間の基板の表面部分である。各チャンネル領域 7 6 は、互いに直角に接合された 2 つの部分、即ち第 3 のトレンチ 4 4 の垂直壁に沿って延びる垂直部分 7 8 と、第 3 のトレンチ 4 4 とソース領域 3 8 との間に延びる水平部分 8 0 とを有する。各フローティングゲート 1 4 は、チャンネル領域 7 6 の水平部分 8 0 と、ソース領域 3 8 の一部分の上に配置されるが、そこから絶縁される。フローティングゲート 1 4 は、各々、水平に向かれたエッジ 5 4 を有し、これは、制御ゲート 5 6 の 1 つに直接対面するが、酸化物層 5 2 によりそこから絶縁される。本発明のプロセスは、互いに鏡像関係のメモリセルの対を形成し、第 3 のトレンチ 4 4 の各側にメモリセルが形成されて、共通のビットライン領域 5 0 を共有する。同様に、ポリプロック 4 2 に電気的に接觸する各ソースライン領域 3 8 が、隣接メモリセル間で、異なる鏡像セットのメモリセルから共有される。各制御ゲート 5 6 、ソース領域 3 8 ( ポリプロック 4 2 が電気的に接続された ) 及びドレイン領域 5 0 は、分離領域 1 6 及び活性領域 1 7 を横切って連続的に延び、各活性領域 1 7 から 1 つのメモリセルを一緒にリンクする。

## 【 0 0 3 3 】

メモリセルの動作

図 3 U を参照してメモリセルの動作を以下に説明する。このようなメモリセルの動作及び動作理論は、米国特許第 5 , 5 7 2 , 0 5 4 号にも開示されており、フローティングゲート及び制御ゲートを有する不揮発性メモリセルを消去し及び読み取る動作及び動作理論、フローティングゲートから制御ゲートへのトンネル作用、並びにこのようなメモリセルのアレーについては、その開示を参考としてここに援用する。

## 【 0 0 3 4 】

所与の活性領域 1 7 において選択されたメモリセルを最初に消去するために、そのソース 3 8 及びドレイン 5 0 の両方に接地電位が印加される。制御ゲート 5 6 には、高い正の電圧 ( 例えば、 + 5 ないし 1 0 ボルト ) が印加される。フローティングゲート 1 4 の電子は、酸化物層 5 2 を経て制御ゲート 5 6 へとトンネル通過するファウラー - ノルドハイムトンネリングメカニズムによって誘起され、フローティングゲート 1 4 を正に荷電したままにする。このトンネリングは、各フローティングゲート 1 4 に形成された水平に向いたエッジ 5 4 により改善される。各制御ゲート 5 6 は、活性領域 1 7 及び分離領域 1 6 を横切って連続的に延びるので、制御ゲート 5 6 の 1 つに高電圧が印加されると、各活性領域から 1 つのメモリセルが消去されることに注意されたい。

## 【 0 0 3 5 】

選択されたメモリセルをプログラミングすることが望まれるときには、小さな電圧 ( 例えば、 0 . 5 ないし 1 . 0 V ) がそのドレイン領域 5 0 に印加される。制御ゲート 5 6 により画成された M O S 構造体のスレッシュホールド電圧付近の正の電圧レベル ( 約 + 1 . 8 ボルト程度 ) がその制御ゲート 5 6 に印加される。そのソース領域 3 8 には、 9 又は 1 0 ボルト程度の正の高い電圧が印加される。ドレイン領域 5 0 により発生された電子は、ド

10

20

30

40

50

レイン領域 50 から、チャンネル領域 76 の弱く反転した垂直部分 78 を経てソース領域 38 に向かって流れる。これらの電子は、チャンネル領域 76 の水平部分 80 に到着すると、フローティングゲート 14 の近方端の高い電位を見る（フローティングゲート 14 は、制御ゲート 56 よりも、正に荷電されたソース領域 38 に強く容量性結合されているために）。電子は加速しそして加熱され、そのほとんどが絶縁層 12 へ注入されそして絶縁層を貫通してフローティングゲート 14 へと注入される。接地電位及び Vdd (デバイスの電源電圧に基づき約 1.5 ないし 3.3 ボルト) が、選択されたメモリセルを含まないメモリセルの行及び列に対し、ソースライン 38 及びビットライン領域 50 に各々印加される。選択されたメモリセルを含まないメモリセルの行に対し制御ゲート 56 に接地電位が印加される。従って、選択された行及び列のメモリセルのみがプログラムされる。

10

## 【0036】

フローティングゲート 14 への電子の注入は、フローティングゲート 14 の近方端における電荷の減少が、熱電子を発生するための高い表面電位を水平チャンネル領域部分 80 に沿ってもはや維持できなくなるまで続く。その点において、フローティングゲート 14 の減少された電荷が、ドレイン領域 50 からフローティングゲート 14 への電子の流れを減少する。

## 【0037】

最後に、選択されたメモリセルを読み取るために、接地電位がそのソース領域 38 に印加される。約 +1 ボルトの読み取り電圧がそのドレイン領域 50 に印加され、そして約 1.5 ないし 3.3 ボルト (デバイスの電源電圧に基づく) がその制御ゲート 56 に印加される。フローティングゲート 14 が正に荷電された (即ち、フローティングゲートの電子が放電した) 場合には、チャンネル領域 76 の水平部分 80 (フローティングゲート 14 の真下の) がターンオンされる。制御ゲート 56 が読み取り電位まで上昇すると、チャンネル領域 76 の垂直部分 78 (制御ゲート 56 に直接隣接する) もターンオンされる。従って、全チャンネル領域 76 がターンオンし、ソース領域 38 からドレイン領域 50 へ電流を通流させる。これは、「1」状態となる。

20

## 【0038】

一方、フローティングゲート 14 が負に荷電された場合には、チャンネル領域 76 の水平部分 80 (フローティングゲート 14 の真下) が弱くターンオンするか、又は完全にシャットオフする。制御ゲート 56 及びドレイン領域 50 が読み取り電位まで上昇しても、チャンネル領域 76 の水平部分 80 にはほとんど又は全く電流が流れない。この場合に、電流が「1」状態に比して非常に僅かであるか、又は全く電流が流れない。このようにして、メモリセルは、「0」状態でプログラムされるセンスとされる。非選択の列及び行に対してソースライン 38、ビットライン領域 50 及び制御ゲート 56 に接地電位が印加され、従って、選択されたメモリセルだけが読み取られる。

30

## 【0039】

メモリセルアレーは、良く知られた従来の行アドレスデコード回路、列アドレスデコード回路、センス增幅回路、出力バッファ回路及び入力バッファ回路を含む周辺回路を備えている。

本発明のメモリセルアーキテクチャーは、フローティングゲートの上方に延びるエッジと制御ゲートとの間に垂直方向に重畳する限定領域を使用しないので、効果的である。図 1 の公知構成に示したように、フローティングゲート 1 と制御ゲート 5 との間には第 1 の結合キャパシタンス C<sub>1</sub> が横方向にあり、そしてフローティングゲート 1 と制御ゲート 5 との間には第 2 の結合キャパシタンス C<sub>2</sub> が垂直方向にある。その目標とするところは、これら 2 つの素子間の容量性結合を最小にしながらトンネリングの効率を最大にすることである。C<sub>2</sub> は、フローティングゲート 1 の上に張り出した制御ゲート 5 の量を減少することにより最小にすることができる。しかしながら、フローティングゲートは、製造プロセスの制約により一定厚みを有するので、C<sub>1</sub> を最小にするには制約がある。C<sub>1</sub> を減少するためにフローティングゲートと制御ゲートとの間の横方向距離を増加する場合には、それらの間の絶縁材料がトンネル作用により質低下される。トンネル作用を向上するために横

40

50

方向距離を狭くした場合には、容量性結合  $C_1$  が大きくなる。従って、容量性結合  $C_1$  がスケーリング限界として働く。

#### 【 0 0 4 0 】

しかしながら、本発明では、このスケーリング限界がバイパスされる。というのは、水平に向けられたエッジ 5 4 が、その横方向に隣接して配置された垂直に向けられた制御ゲートスペーサ 5 6 に直接対向するからである。垂直に向けられた容量性結合（例えば  $C_2$ ）はなく、そして横方向に向けられた容量性結合（例えば  $C_1$ ）は充分に小さいが、水平に向けられたエッジ 5 4 と制御ゲート 5 6 との間には依然充分なトンネリングを生じさせることができる。

#### 【 0 0 4 1 】

本発明は、サイズが減少されそしてプログラム効率が優れたメモリセルアレーも提供する。メモリセルのサイズは、50%程度減少される。というのは、ビットライン領域 5 0 が基板 1 0 内に埋設され、そしてビットライン領域 5 0 が第 3 のトレンチとセルフ・アラインされ、そこでは、リソグラフィー発生、接触整列及び接触完全性の制約によりスペースが浪費されることがない。本発明では、0.18 μm 及び 0.13 μm の技術世代を各々使用して約 0.21 μm 及び 0.14 μm のセル領域を得ることができる。プログラム効率は、チャンネル領域 7 6 の垂直部分 7 8 をフローティングゲート 1 4 に「照準」することによって大幅に改善される。従来のプログラミング構成では、チャンネル領域の電子がフローティングゲートの平行な経路に流れ、そこで、比較的少数の電子が加熱されそしてフローティングゲートに注入される。推定プログラム効率（全電子数に対する注入電子数）は、約 1 / 1 0 0 0 と推定される。しかしながら、チャンネル領域の第 1 部分は、フローティングゲートに直接「照準」される電子経路を定義するので、本発明のプログラム効率は、ほぼ全部の電子がフローティングゲートに注入される 1 / 1 付近であると推定される。

#### 【 0 0 4 2 】

又、本発明では、第 3 のトレンチ 4 4 の側壁に沿って形成される制御ゲートは、セルのサイズに影響せずに、導通性能及びパンチスルーリー余裕度に対して別々に最適化することができる。更に、ソース領域 3 8 と埋設ビットライン領域 5 0 との間のパンチスルーリー抑制は、第 1 導電型（例えば、N 型）を有するソース領域を、その第 1 導電型とは異なる第 2 導電型（例えば、P 型）を有するウェルに埋設すると共に、メモリセルの導通特性に影響しない他のサブ表面インプラントを使用することにより、最適化することができる。更に、ソース領域 3 8 及びビットライン領域 5 0 を垂直方向及び水平方向に分離すると、セルサイズに影響なく、信頼性パラメータを容易に最適化することができる。

#### 【 0 0 4 3 】

最後に、本発明のメモリセル構造体は、「持ち上がったソースライン」 4 2 を備え、これは、導電性ポリブロック 4 2 がソースライン 3 8 に沿って延びる（及びそれに電気的に接続される）が、基板表面より上に配置されることを意味する。持ち上がったソースライン 4 2 は、それらの側壁がフローティングゲート 1 4 の側壁に横方向に隣接して配置されるが、酸化物層 3 6 及び酸化物スペーサ 4 0 によってそこから絶縁されている。この構成は、ソースライン 3 8 の長さに沿って電気的抵抗の減少を与え、そして持ち上がったソースライン 4 2 とフローティングゲート 1 4 との間に容量性結合を与える（フローティングゲート 1 4 とソース領域 3 8 との間の重畳により生じる容量性結合に加えて）。

本発明では、ポリブロック 4 2 がソース領域 3 8 にセルフ・アラインされ、そしてフローティングゲート 1 4 がポリブロック 4 2 と制御ゲートのポリスペーサ 5 6 との間にセルフ・アラインされる（従って、チャンネル領域 7 6 の第 1 及び第 2 部分 7 8 / 8 0 にセルフ・アラインされる）。

#### 【 0 0 4 4 】

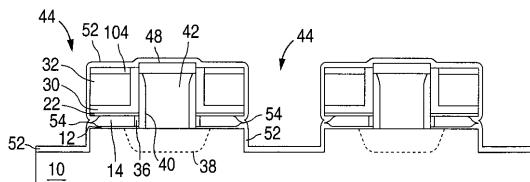

##### 第 1 の別の実施形態

図 4 A ないし 4 G は、図 3 U に示したものと同様のメモリセル構造体を形成するための第 1 の別のプロセスを示し、この場合には、窒化物層 3 0 を除去するために使用される窒化

10

20

30

40

50

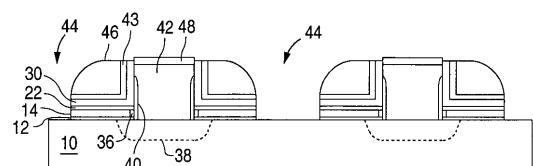

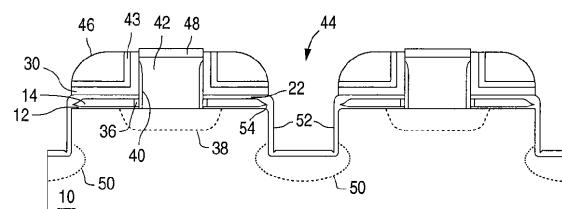

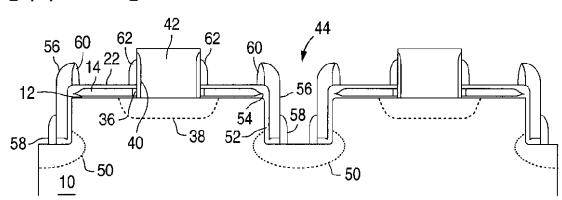

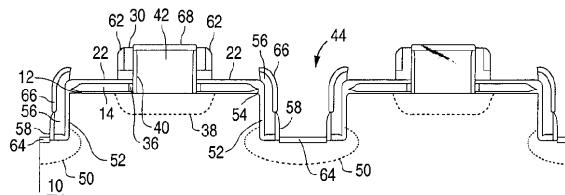

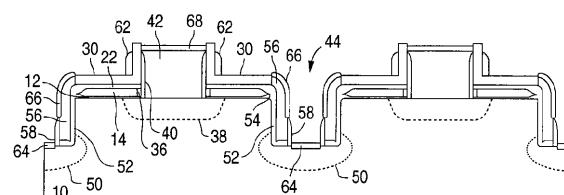

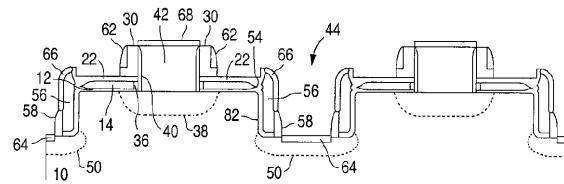

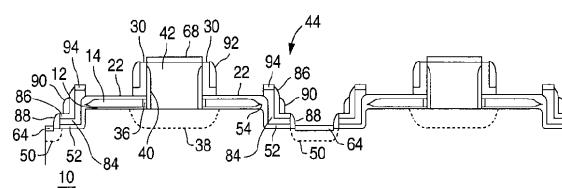

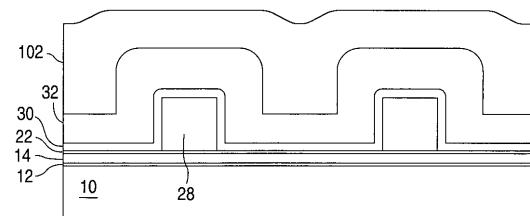

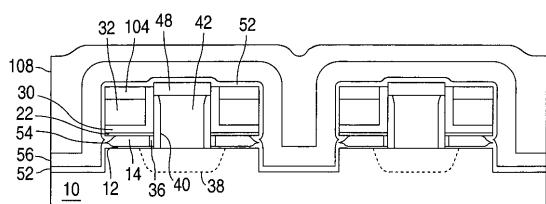

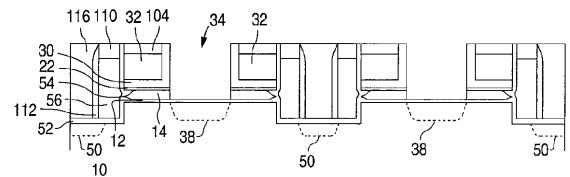

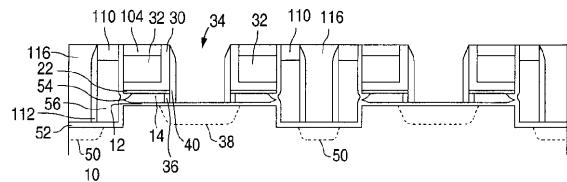

物エッチングが、窒化物層の一部分を保存するためにプロセスにおいて後で実行される。この第1の別のプロセスは、図3Oに示された同じ構造体で始まり、これは、図4Aに再び示されている。

#### 【0045】

第3のトレンチ44の側壁に沿ったポリスペーサ56の形成は、図3Pを参照して上述したのと同様に行われるが、好ましくは薄いポリ層が構造体上に付着され（例えば、700厚み）、その後、乾式非等方性ドライエッチングプロセスを行い、第3のトレンチ44の側壁に沿って残されたポリスペーサ56を除いて、付着ポリ層を除去する。各ポリスペーサ56の上縁が、その隣接窒化物層30の上縁とほぼ水平になる（図4Bに示すよう10）か、又は隣接するフローティングゲートのエッジ54と窒化物層30の隣接上縁との間に位置するよう確保するためにポリエッチングが実行されるのが好ましい。

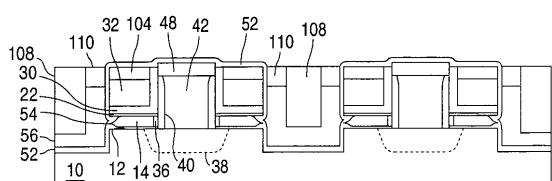

#### 【0046】

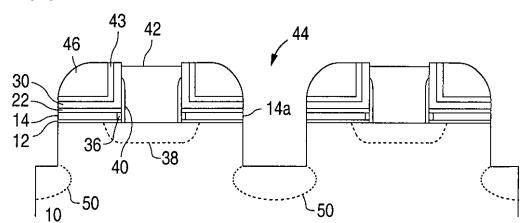

次いで、窒化物エッチングプロセスを使用して、窒化物スペーサ46が除去される。酸化物エッチングがそれに続き、酸化物層48及び43が除去されると共に、図4Cに示すように、第3のトレンチ44の底において（ポリスペーサ56間にある）酸化物層52の露出部分が除去される。絶縁スペーサ58（好ましくは酸化物）は、構造体上に酸化物の層を付着し（例えば、500ないし1200厚み）、その後、酸化物エッチング（例えば、RIE）を行うことにより、第3のトレンチ44の側壁に沿って形成される。又、この酸化物付着及びエッチングプロセスは、窒化物層30の垂直部分に隣接して酸化物スペーサ62を形成する。それにより得られる構造体が図4Dに示されている。20

#### 【0047】

次いで、金属付着ステップが実行されて、タングステン、コバルト、チタン、ニッケル、白金又はモリブデンのような金属が構造体上に付着される。次いで、構造体がアニールされ、高温の金属を第3のトレンチ44の底において基板10の露出部分へ流しこみ且つ浸透させて、サリサイド層64を形成することができる。又、高温金属は、ポリスペーサ56の露出した上部にポリサイド層66を形成すると共に、ポリブロック42の露出した上部にポリサイド層68を形成する。残留金属を除去するための金属エッチングプロセスの後に得られる構造体が、図4Eに示されている。

#### 【0048】

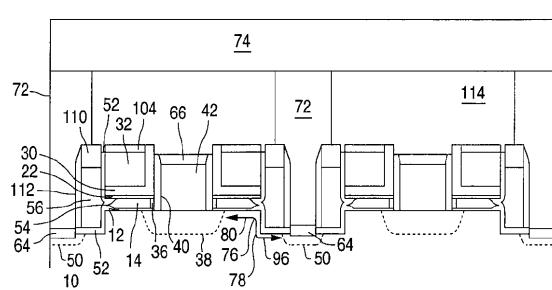

窒化物エッチングプロセスがそれに続き（例えば、高温の磷酸において）、図4Fに示すように、窒化物層30の露出部分（即ち酸化物スペーサ62により保護されない部分）を除去する。この構造体は、図3Uを参照して述べたように処理され（即ち、パッシベーション、接触形成及びビットライン形成）、図4Gに示す構造体が得られる。30

#### 【0049】

図3Aないし3Uのプロセスからのこの第1の別の実施形態の主たる相違は、窒化物層30を除去するための窒化物エッチングステップがプロセスにおいて後で実行されることである。その結果、窒化物層30は、サリサイド／ポリサイド金属化プロセス中に酸化物層22（フローティングゲート14の上の）を保護するためにそのまま残される。更に、窒化物層30の一部分は、最終的なメモリセル構造体においてそのまま残される（フローティングゲート14の上で且つポリブロック42に横方向に隣接して）。窒化物の高い誘電率（酸化物に比して）が与えられると、窒化物層30のこの残留部分は、より強力な側壁フリンジフィールドを与え、従って、メモリセルの各々に対しソース領域38（ポリブロック42を含む）とフローティングゲート14との間の容量性結合を改善する。40

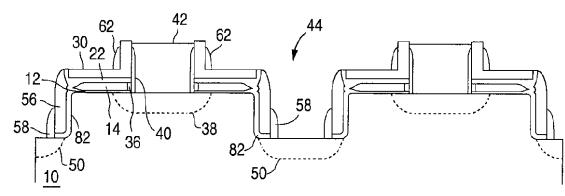

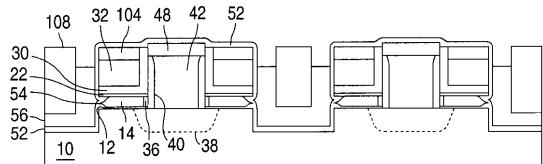

#### 【0050】

#### 第2の別の実施形態

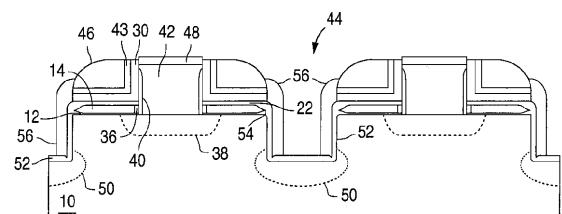

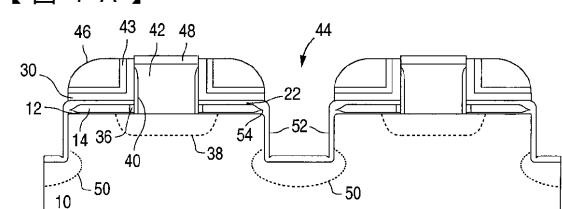

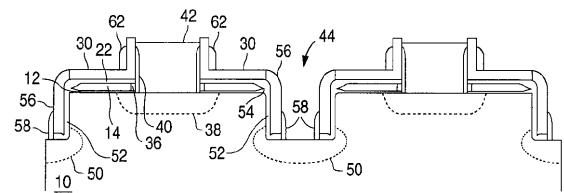

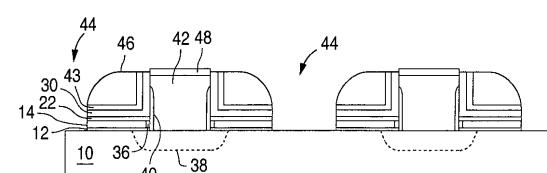

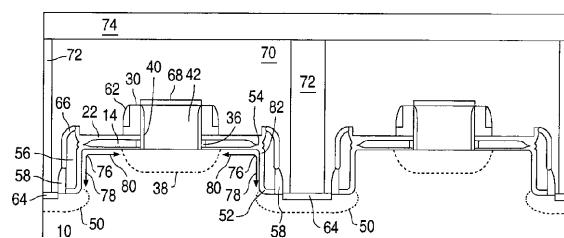

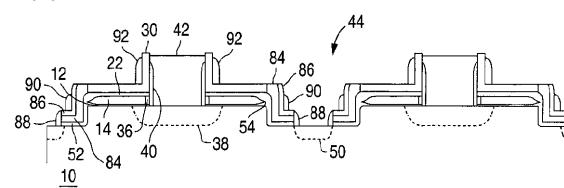

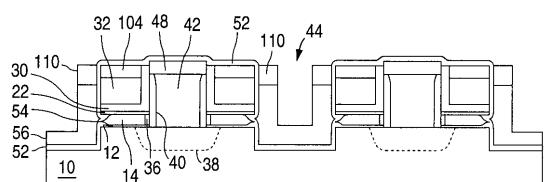

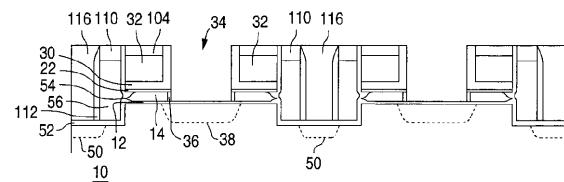

図5Aないし5Iは、図3Uに示されたものと同様のメモリセル構造体を形成するための第2の別のプロセスを示し、この場合には、第2の領域50を形成するのに使用されるイオンインプランテーションがプロセスにおいて後で実行されそして付加的なトンネル酸化物の形成が含まれる。この第2の別のプロセスは、図3Mに示されたものと同じ構造で始まり、これは図5Aに再び示されている。50

## 【0051】

同じシリコン及び酸化物エッチングプロセスが図3Nを参照して述べたように実行され、図5Bに示すように、第3のトレンチ44が基板10へと下方に拡張され、そして酸化物層48が除去される。しかしながら、第2領域50を形成するのに使用されるイオンインプランテーションは、このときには実行されない。むしろ、図3Oを参照して述べた酸化プロセスが実行されて、図5Cに示すように、酸化物層52及びフローティングゲートのエッジ54が形成され、そして酸化物層48が再成長される。

## 【0052】

制御型酸化物エッチングプロセス（例えば、10対1に希釈されたHFエッチング剤を伴う）が実行されて、酸化物層52が除去され、そしてフローティングゲートの鋭いエッジ54が露出される。薄い酸化物層82（例えば、130）が構造体上に付着される（例えば、HTO付着により）。酸化物層52を除去しそして酸化物層82を付着すると、制御された厚みをもつトンネル酸化物層が鋭いエッジ54に隣接して形成される。次いで、ポリ層を構造体上に付着し（例えば、700厚み）、その後、乾式非等方性ドライエッチングプロセスを行って、第3のトレンチ44において酸化物層82に沿って残されるポリスペーサ56を除き付着ポリ層を除去することにより、ポリスペーサ56が第3のトレンチ44の側壁に沿って形成される。各ポリスペーサ56の上縁が、その隣接窒化物層30の上縁とほぼ水平になる（図5Dに示すように）か、又は隣接するフローティングゲートのエッジ54と窒化物層30の隣接上縁との間に位置するよう確保するために、ポリエッチングが実行されるのが好ましい。

## 【0053】

次いで、酸化物エッチングプロセスを使用し、酸化物層82の露出部分（即ちポリスペーサ56により保護されない部分）と、酸化物層48とが除去される。次いで、窒化物エッチングを使用して、窒化物スペーサ46が除去され、その後、酸化物エッチングにより、酸化物層43が除去される。それにより得られる構造体が図5Eに示されている。構造体の全表面にわたって適当なイオンインプランテーションが行われて、第3のトレンチ44の下で基板10に第2領域50（埋設ビットライン領域）が形成される。第3のトレンチ44の外側では、イオンが阻止され、何の作用も与えない。絶縁スペーサ58（好ましくは酸化物）は、構造体上に酸化物層を付着し（例えば、500ないし1200厚み）、その後、酸化物エッチング（例えば、RIE）を行うことにより第3のトレンチ44の側壁に沿って形成される。この酸化物付着及びエッチングプロセスは、窒化物層30の垂直部分に隣接して酸化物スペーサ62を形成する。それにより生じる構造体が図5Fに示されている。絶縁スペーサ58を形成した後、又は制御ゲート56を形成した後であってスペーサ46を除去する前に、イオンインプランテーションプロセスを実行できることに注意されたい。

## 【0054】

熱アニールプロセス（例えば、RTA又は炉熱アニール）を使用して、第1及び第2領域38/50が基板10の深部へ押し込まれる。次いで、金属付着ステップが実行されて、タンクステン、コバルト、チタン、ニッケル、白金又はモリブデンのような金属が構造体上に付着される。次いで、構造体がアニールされて、サリサイド領域64を形成し（第3のトレンチ44の底において酸化物スペーサ58間に）、ポリサイド領域66を形成し（ポリスペーサ56の露出上部の上に）、そしてポリサイド領域68を形成する（ポリプロック42の露出上部に）。残留構造体に付着された金属は、金属エッチングプロセスにより除去される。それにより得られる構造体が図5Gに示されている。

## 【0055】

窒化物エッチングプロセスがそれに続き（例えば、高温の磷酸において）、図5Hに示すように、窒化物層30の露出部分（即ち酸化物スペーサ62により保護されない部分）を除去する。この構造体は、次いで、図3Uを参照して述べたように処理され（即ち、パッシベーション、接触形成及びビットライン形成）、図5Iに示す構造体が得られる。

## 【0056】

10

20

30

40

50

この第2の別の実施形態は、第2領域50を形成するのに使用されるイオンインプランテーションステップを、制御ゲートのスペーサ56が形成された後までシフトする。フローティングゲートのエッジ54と制御ゲート56との間のトンネリングに使用される酸化物層82は、熱成長ステップではなく、酸化物付着ステップ（例えば、HTO）により形成され、第3のトレンチ44の輪郭により誘起されるストレスが与えられると、良好に均一性を達成する。最後に、窒化物層の残留部分は、より強力な側壁フリンジフィールドを与える、ひいては、ソース領域38（ポリブロック42を含む）とフローティングゲート14との間の容量性結合を改善する。

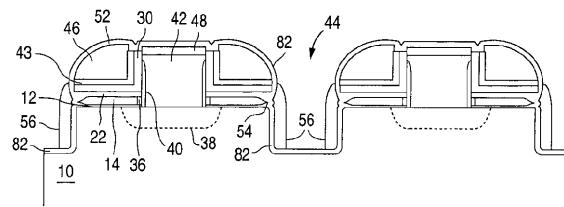

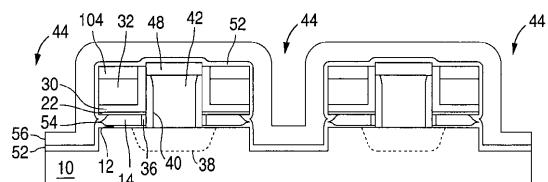

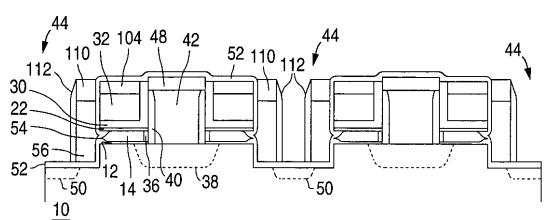

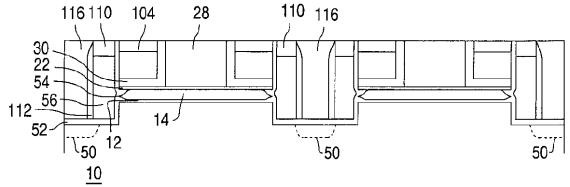

#### 【0057】

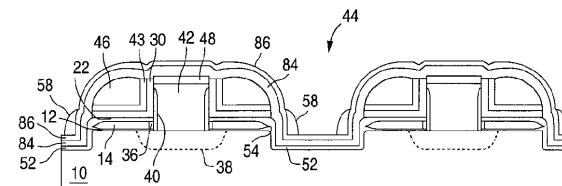

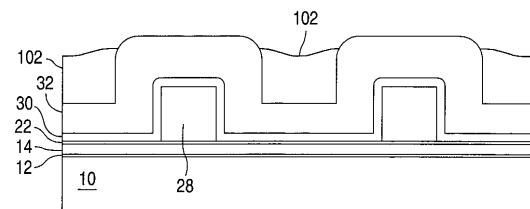

##### 第3の別の実施形態

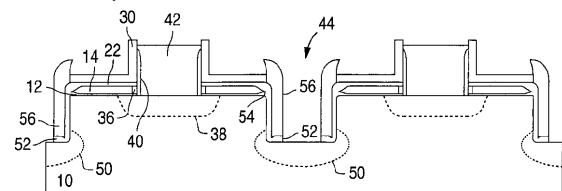

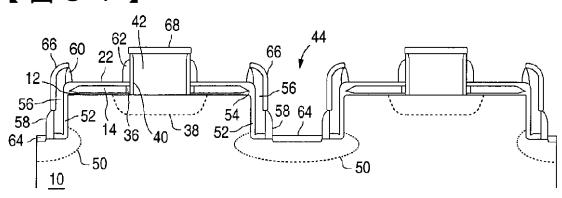

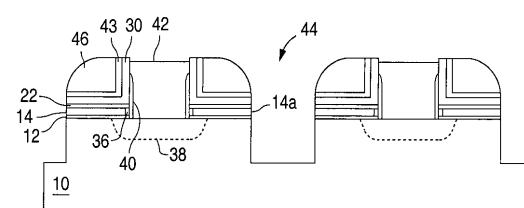

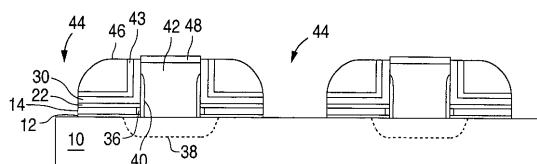

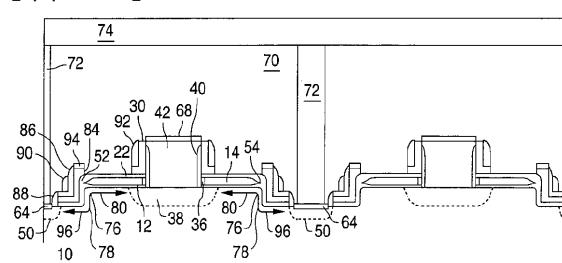

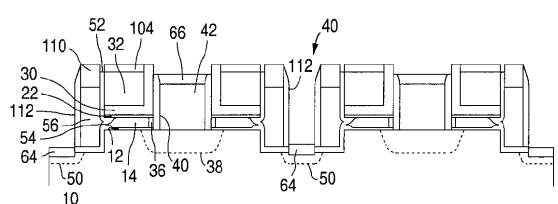

図6Aないし6Jは、図3Uに示したものと同様のメモリセル構造体を形成するための第3の別のプロセスを示し、これは、「L」字型の制御ゲート及びチャンネル領域を備え、その各々は、2つの個別の水平部分が垂直部分で分離されたものを有している。この第3の別のプロセスは、図3Mに示されたものと同じ構造体で始まり、これは、図6Aに再び示されている。

#### 【0058】

図3Nを参照して述べたように、同じエッティングプロセスが実行されて、図6Bに示すように、第3のトレンチ44を基板10へと下方に拡張する。しかしながら、第2領域50を形成するのに使用されるイオンインプランテーションは、このときには実行されない。むしろ、図3Oを参照して述べた酸化プロセスが実行されて、図6Cに示すように、酸化物層52及びフローティングゲートのエッジ54が形成される。

ポリ層84が構造体上に形成される。ポリ層84の上面に任意のポリサイド層86が形成され、上述した金属付着及びアニールプロセスが行われる。層84及び86の全厚みは、約700であるのが好ましい。次いで、酸化物層が構造体上に形成され、その後、酸化物エッティングが行われ、第3のトレンチ44においてポリ層84に対して形成された酸化物スペーサ58を除き、酸化物層が除去される。それにより生じる構造体が図6Dに示されている。

#### 【0059】

ポリエッティングプロセスを使用して、ポリサイド層86及びポリ層84の露出部分（即ち、酸化物スペーサ58により保護されない部分）が除去され、トレンチ44の側壁及び底壁に沿ってポリ及びポリサイド層84/86の「L」字型セグメントが残される。このポリエッティング、及び酸化物スペーサ58の形成は、各ポリ/ポリサイドセグメント84/86の上縁が、その隣接窒化物層30の上縁とほぼ水平になる（図6Eに示すように）か、又は隣接するフローティングゲートのエッジ54と窒化物層30の隣接上縁との間に位置するよう確保するために行われるのが好ましい。

#### 【0060】

窒化物エッティングプロセスは、露出された窒化物スペーサ46を除去するのに使用される。次いで、酸化物エッティングが使用されて、図6Fに示すように、酸化物スペーサ58（第3のトレンチ44における）、酸化物層48（ポリブロック42上の）、酸化物層43及び酸化物層52の部分（第3のトレンチ44の底においてポリセグメント84間にある）が除去される。酸化物付着及びエッチバックプロセス（例えば、RIEドライエッティング）を使用して、酸化物スペーサ88を形成し（第3のトレンチ44において層52、84及び86の露出され垂直に向けられた端部に対して）、酸化物スペーサ90を形成し（第3のトレンチ44においてポリサイド層86の垂直に向けられた部分に対して）、そして酸化物スペーサ92を形成する（窒化物層30の垂直に向けられた部分に対して）。構造体の全表面にわたって適当なイオンインプランテーションを行って、第3のトレンチ44の下で基板10に第2領域50（埋設ビットライン領域）を形成する。又、ポリブロック42にもイオンインプランテーションされて、これらブロックがドープ（又は更にドープ）される。第3のトレンチ44の外側の領域では、ポリブロック42を除き、イオンが阻止され、何の作用も及ぼさない。イオンインプランテーションプロセスは、酸化物ス

10

20

30

40

50

ペーサ 88 / 90 / 92 を形成する前に行うこともできるし、又は窒化物スペーサ 46 を除去する前に行うこともできる点に注意されたい。それにより得られる構造が図 6 G に示されている。

#### 【0061】

次いで、金属付着ステップが行われて、タングステン、コバルト、チタン、ニッケル、白金又はモリブデンのような金属が構造体上に付着される。次いで、構造体がアニールされて、サリサイド領域 64 を形成し（第 3 のトレント 44 の底において酸化物スペーサ 58 間に）、ポリサイド領域 94 を形成し（ポリ層セグメント 84 の露出上部の上に）、そしてポリサイド領域 68 をポリブロック 42 の露出上部に形成する。残留構造体に付着された金属は、金属エッティングプロセスにより除去される。それにより得られる構造体が図 6 H に示されている。10

窒化物エッティングプロセスがそれに続き（例えば、高温の磷酸において）、図 6 I に示すように、窒化物層 30 の露出部分（即ち酸化物スペーサ 92 により保護されない部分）を除去する。この構造体は、次いで、図 3 U を参照して述べたように処理され（即ち、パッシベーション、接触形成及びビットライン形成）、図 6 J に示す構造体が得られる。

#### 【0062】

この第 3 の別の実施形態は、第 2 の領域 50 を形成するのに使用されるイオンインプランテーションステップを、ポリ層セグメント 84 及びポリサイド 86 の形成により第 3 のトレント 44 の底が狭められる後までシフトする。従って、第 2 領域 50 は、第 3 のトレントの底壁の中央部分の下だけに形成される。これは、ほぼ直角に接合された 3 つの部分を有する各セルに対して基板にチャンネル領域 76 を形成し、即ち第 1 の水平部分 80 は、第 3 のトレント 44 とソース領域 38 との間に延び、垂直部分 78 は、第 3 のトレント 44 の垂直壁に沿って延び、そして第 2 の水平部分 96 は、垂直部分 78 とドレイン領域 50 との間に延び、従って、チャンネル領域 76 は、ほぼ「S」字型となる。窒化物層 30 の残りの部分は、より強力な側壁フリンジフィールドを与え、従って、ソース領域 38（ポリブロック 42 を含む）とフローティングゲート 14 との間の容量性結合を改善する。最後に、制御ゲートの厚みは、正確に制御することが非常に困難なポリ付着及びエッチバッカプロセスではなく、ポリ付着ステップによって指令される。20

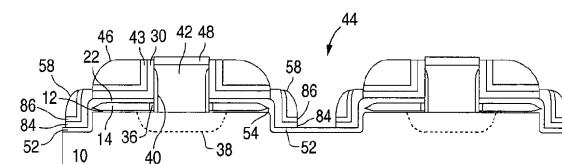

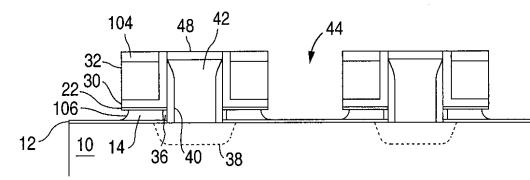

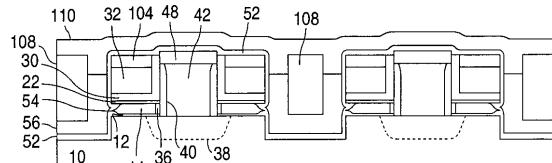

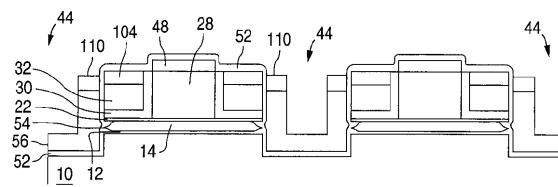

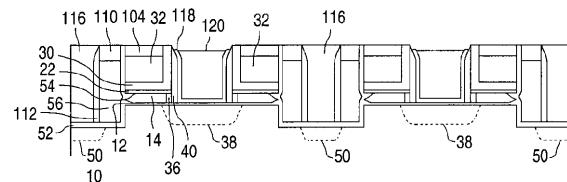

#### 【0063】

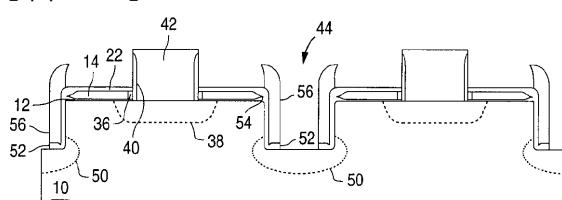

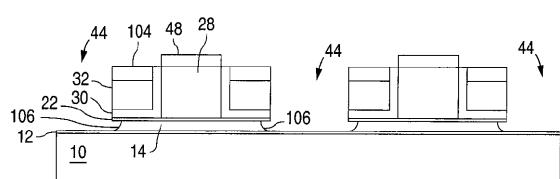

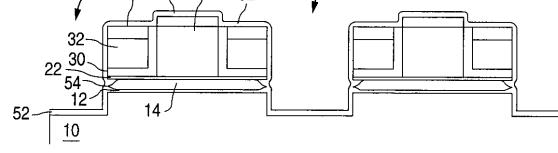

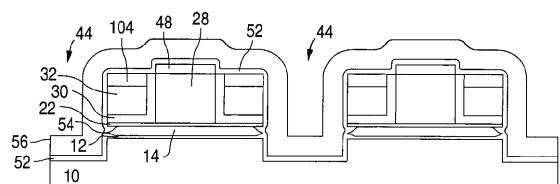

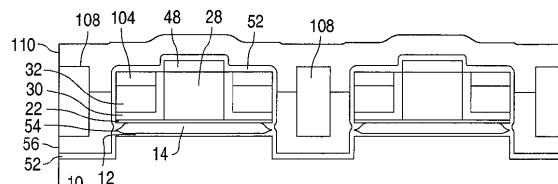

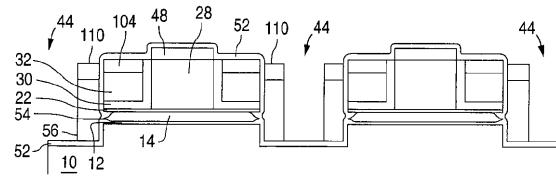

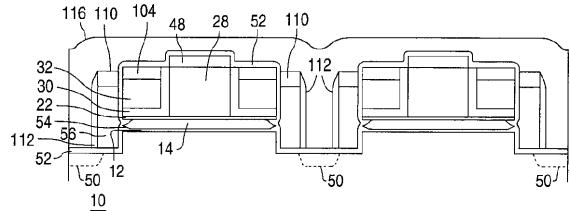

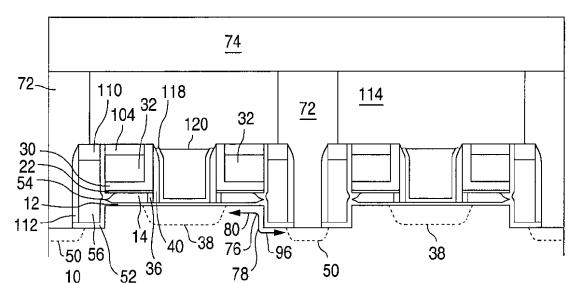

##### 第 4 の別の実施形態

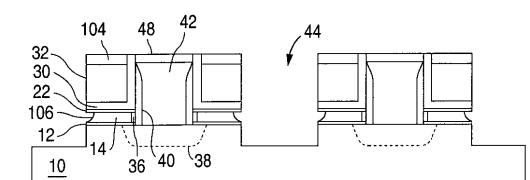

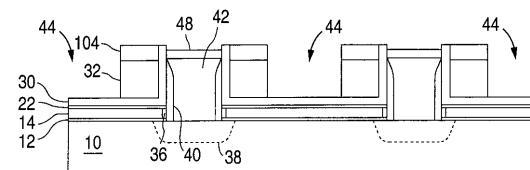

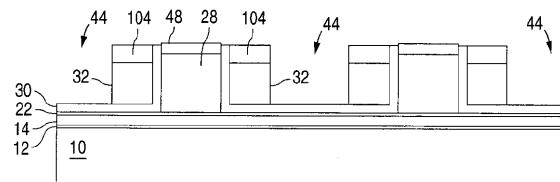

図 7 A ないし 7 Z は、図 3 U に示したものと同様のメモリセル構造体を、セルフ・アライン接触（SAC）構成を使用して形成するための第 4 の別のプロセスを示す。この第 4 の別のプロセスは、図 3 C に示したものと同じ構造体で始まり、これは図 7 A に再び示されている。30

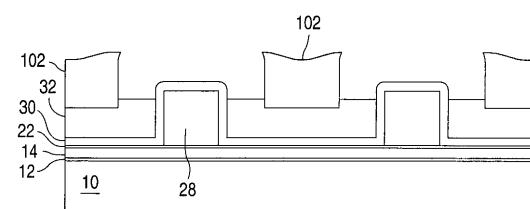

#### 【0064】

誘電体材料の厚い層 102（例えば、BSG）が、図 7 B に示すように構造体上に付着され、酸化物層 32 の部分間のギャップを埋める。BSG エッティングプロセスを使用して、BSG 層 102 を、酸化物層 32 の上部とほぼ平らになるまで下方にエッティングし、このとき、酸化物層 32 をエッティングストッパーとして使用する。BSG エッティングプロセスは、図 7 C に示すように、酸化物層 32 の上部間に配置された BSG 102 のブロックを形成する。酸化物エッティングプロセスを使用して、酸化物層 32 の露出部分を、窒化物層 30 の上部とほぼ平らになるまで下方にエッティングし、このとき、窒化物層 30 をエッティングストッパーとして使用する。制御型酸化物オーバーエッティングを使用して、酸化物層 32 の露出部分を、図 7 D に示すように、窒化物層 30 の上部から所定の距離だけ下へと下方にエッティングする。40

#### 【0065】

次いで、厚い窒化物層 104 が、図 7 E に示すように、構造体上に付着される。平坦化工エッティングプロセス（例えば、CMP）がそれに続き、窒化物層 104、BSG 102 及び窒化物 30 を、ポリブロック 28 の上部と平らになるように下方にエッティングし（ポリブロック 28 をポリシングストッパーとして使用して）、そしてポリブロック 28 の上面を

露出したままにする。それにより得られる構造体が図 7 F に示されている。

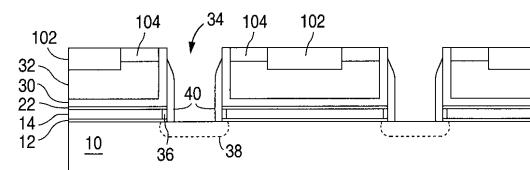

ポリエッチングプロセスを使用して、ポリブロック 2 8 を除去し（酸化物層 2 2 をエッティングストッパーとして使用して）、第 2 のトレンチ 3 4 を形成する。制御型の酸化物エッチングを使用して、第 2 のトレンチ 3 4 の底に露出した酸化物層 2 2 の部分を除去する（ポリ層 1 4 をエッティングストッパーとして使用して）。別のポリエッチングプロセスを実行して、第 2 のトレンチ 3 4 の底に露出したポリ層 1 4 の部分を除去する（酸化物層 1 2 をエッティングストッパーとして使用して）。それにより生じる構造体が図 7 G に示されている。

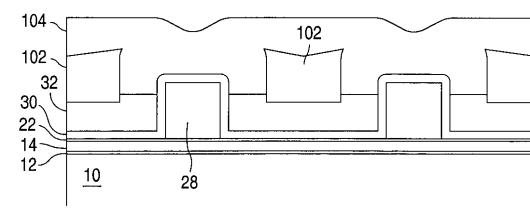

#### 【 0 0 6 6 】

トレンチ 3 4 において熱酸化プロセスを使用してポリ層 1 4 の露出端に酸化物側壁層 3 6 10 が形成される。次いで、適当なイオンインプランテーションを使用し、周囲基板の導電型（例えば P 型）とは異なる導電型（例えば N 型）を有する基板 1 0 に第 1 領域（ソース領域）3 8 が形成される。次いで、全構造体上に薄い酸化物層（例えば、2 0 0 ）を付着し、その後、非等方性エッチングプロセス（例えば、RIE ドライエッチング）を行って、スペーサ 4 0 以外の付着酸化物層を除去することにより、第 2 のトレンチ 3 4 の壁に側壁スペーサ 4 0 が形成される。又、この酸化物エッチングプロセスは、第 2 のトレンチ 3 4 の底において酸化物層 1 2 の露出部分も除去し、基板 1 0 を露出させる。それにより得られる構造体が図 7 H に示されている。

#### 【 0 0 6 7 】

第 2 のトレンチがポリブロック 4 2 で埋められ、これは、構造体上にポリシリコンの厚い層を付着し、その後、平坦化プロセス（即ち CMP）を行って、第 2 のトレンチ 3 4 においてポリブロック 4 2 を除き付着ポリシリコンを除去することにより行われるのが好ましい。任意のポリエッチングを実行して、窒化物層 1 0 4 及び酸化物層 3 2 に対してポリブロック 4 2 の上面を若干くぼませ、トポロジーの問題がもしあれば、それに対処する。ポリブロック 4 2 は、基板 1 0 のソース領域 3 8 と直接電気的接触し、そしてその場でドープすることもできるし又は個別のインプランテーションによってドープすることもできる。それにより得られる構造体が図 7 I に示されている。

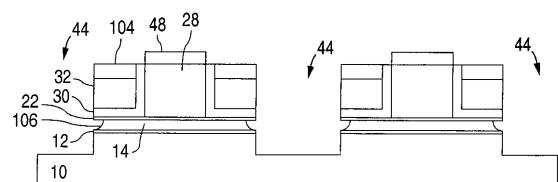

#### 【 0 0 6 8 】

B SG エッチングプロセス（湿式又は乾式）を使用して、B SG 1 0 2 が除去され、酸化物層 3 2 の一部分が露出される。次いで、非等方性エッチング（例えば、RIE）を使用して、酸化物層 3 2 の露出部分（即ち、窒化物 1 0 4 により保護されない部分）を除去し、図 7 J に示すように、酸化物ブロック 3 2 間に露出された半くぼみの第 3 のトレンチ 4 4 を残す。

次いで、構造体は、熱酸化プロセスを受け、ポリブロック 1 2 上に酸化物層 4 8 が形成される。この酸化物層 4 8 は、ポリブロック 4 2 とセルフ・アラインされる（例えば、6 0 0 までの厚みで）。この酸化プロセスの熱サイクル中に、ソース領域 3 8 は、基板へと深く押し込まれる。それにより生じる構造体が図 7 K に示されている。

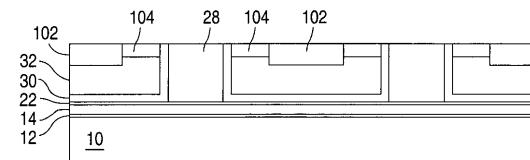

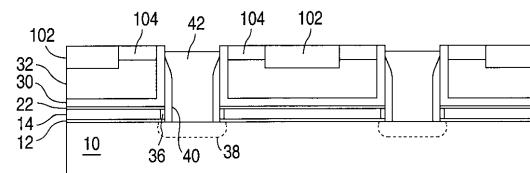

#### 【 0 0 6 9 】

非等方性（乾式）窒化物エッチングを使用して、第 3 のトレンチに（酸化物ブロック 3 2 間で）露出された窒化物層 3 0 の部分を除去し、このとき、酸化物層 2 2 をエッティングストッパーとして使用する。又、この窒化物エッチングは、ポリブロック 4 2 に隣接した窒化物層 3 0 の露出部分もある程度除去し、そして窒化物層 1 0 4 の厚みを減少する（例えば、3 0 0 ないし 5 0 0 までの厚みに）。非等方性酸化物エッチングがそれに続き、ポリ層 1 4 をエッティングストッパーとして使用して、第 3 のトレンチ 4 4 に（酸化物ブロック 3 2 間で）露出された酸化物層 2 2 の部分を除去する。又、この酸化物エッチングは、酸化物層 4 8 の小さな部分を若干消費する。それにより生じる構造体が図 7 L に示されている。

#### 【 0 0 7 0 】

非等方性（乾式）ポリエッチングを次いで実行して、酸化物層 1 2 をエッティングストッパーとして使用して、第 3 のトレンチに（酸化物ブロック 3 2 間で）露出されたポリ層 1 4 50

の部分を除去する。このポリエッティングは、図 7 M に示すように、第 3 のトレンチ 4 4 に面するポリ層 1 4 の縁に傾斜即ちテーパー領域 1 0 6 を形成するように実行されるのが好み。

#### 【 0 0 7 1 】

非等方性(乾式)酸化物エッティングがそれに続き、第 3 のトレンチに(酸化物ブロック 3 2 間で)露出された酸化物層 1 2 の部分が除去されて、第 3 のトレンチ 4 4 の底において基板 1 0 を露出させる。又、この酸化物エッティングは、酸化物層 4 8 の小さな部分を若干消費する。それにより生じる構造体が図 7 M に示されている。次いで、シリコン基板 1 0 が第 3 のトレンチ 4 4 の底に露出されたままである状態で、シリコン(乾式)エッティングプロセスが実行されて、第 3 のトレンチ 4 4 を、基板表面より 5 0 0 ないし 1 5 0 0 10 低い深さまで、基板 1 0 へと下方に拡張する。このエッティングは、シリコンと酸化物との間で 1 対 1 の選択性をもつように選択され、従って、酸化物分離領域 1 6 にも同様の深さのトレンチをエッティングし(LOCOS 又は STI)、ここでは、第 3 のトレンチ 4 4 が連続的に形成されそして活性及び分離領域 1 7 / 1 6 を横切って延びる。それにより生じる構造体が図 7 N に示されている。

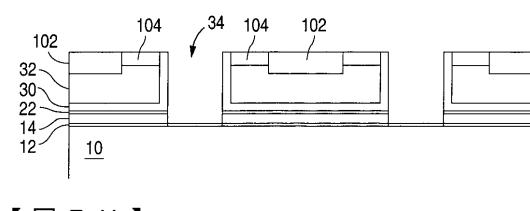

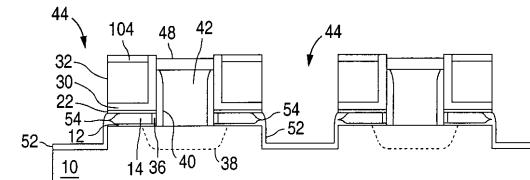

#### 【 0 0 7 2 】

次いで、酸化プロセスが実行され、第 3 のトレンチ 4 4 の露出シリコン面が酸化されて、これらシリコン面のライニングとなる薄い酸化物層 5 2(例えば、1 5 0 )が形成される。又、この酸化プロセスは、第 3 のトレンチ 4 4 の上部の側壁の一部分を形成するポリ層 1 4 の露出テーパー面 1 0 6 も酸化し、図 7 O に示すように、第 3 のトレンチ 4 4 の側壁の 1 つを各々直接的に指す水平に向けられたエッジ 5 4 を形成する。エッジ 5 4 は、細長いエッジでもよいし(即ちかみそりの刃の鋭いエッジのような)、又は短いエッジ(鉛筆の先端のような)でもよい。又、この酸化プロセスは、酸化物層 4 8 をポリブロック 4 2 より厚くする。

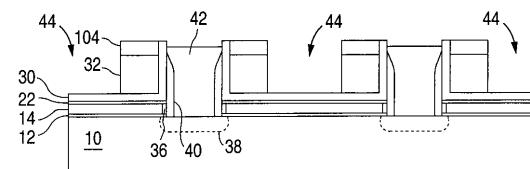

#### 【 0 0 7 3 】

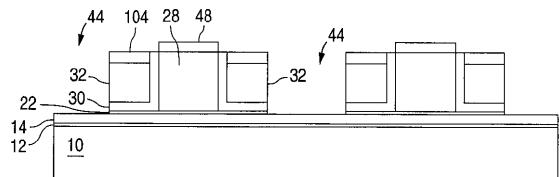

任意の酸化物層最適化プロセスが次に行われ、第 3 のトレンチ 4 4 から酸化物層 5 2 を除去し、その後、HTO 酸化物付着ステップを行って、良好に制御された厚み(例えば、1 5 0 )を有する酸化物層 5 2 を全構造体上に再形成することにより、熱成長ファウラー-ノルドハイムトンネリング酸化物の厚みを最適化することができる。それにより生じる構造体が図 7 P に示されている。

図 7 Q に示すように、ポリ層 5 6 が構造体上に形成される(例えば、8 0 0 厚み)。ポリ層 5 6 の上面には、金属化ポリシリコン(図示せず)を形成することができる。次いで、図 7 R に示すように、ポリ層 5 6 上に、誘電体材料の層 1 0 8(例えば、BSG、1 0 0 0 まで)が形成される。次いで、BSG エッティングプロセスを使用して、BSG 1 0 8 を、酸化物層 5 2 と平らになるように下方にエッティングし、その後、ポリエッティングにより、ポリ層 5 6 を、酸化物層 5 2 と平らになるように下方にエッティングする。これら BSG 及びポリエッティングに代わって、CMP 平坦化を使用することもできる。付加的なポリエッティングを行って、図 7 S に示すように、ポリ層 5 6 の上部を酸化物層 5 2 の上部及び BSG 1 0 8 より下にくぼませる。

#### 【 0 0 7 4 】

次いで、窒化物層 1 1 0 が、図 7 T に示すように、構造体上に付着される(例えば、8 0 0 )。その後、窒化物エッティングが、酸化物層 5 2 をエッティングストッパーとして使用して行われ、図 7 U に示すように、ポリ層 5 6 の上に窒化物ブロック 1 1 0 を残す。窒化物ブロック 1 1 0 は、酸化物層 5 2 (及び酸化物ブロック 3 2 )と、BSG 1 0 8 とにより、ポリ層 5 6 にセルフ・アラインされる。次いで、BSG エッティングを使用して、第 3 のトレンチ 4 4 から BSG ブロック 1 0 8 が除去される。それにより生じる構造体が図 7 V に示されている。

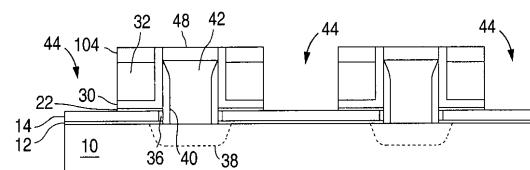

#### 【 0 0 7 5 】

非等方性ポリエッティングを使用して、図 7 W に示すように、第 3 のトレンチ 4 4 の底においてポリ 5 6 の露出部分(窒化物 1 1 0 により保護されない部分)が除去される。次いで 50

、窒化物が構造体上に付着され（例えば、300 厚み）、その後、非等方性窒化物エッチング（例えば、RIE）を実行し、第3のトレンチ44において窒化物スペーサ112を除き付着窒化物が除去される。構造体の全面にわたって適当なイオンインプランテーションがもう一度行われ、第3のトレンチ44の下で基板10に第2領域50（埋設ビットラインドレイン領域）が形成される。第3のトレンチ44の外部では、イオンが阻止され、何の作用も果たさない。イオンインプランテーションプロセスは、酸化物エッチングが次に行われた後に実行できることに注意されたい。それにより生じる構造体が図7Xに示されている。

#### 【0076】

酸化物エッチングステップが次に行われて、酸化物層52及び酸化物層48の露出部分が除去される。次いで、金属付着ステップが行われて、タンゲステン、コバルト、チタン、ニッケル、白金、又はモリブデンのような金属が構造体上に付着される。次いで、構造体がアニールされて、酸化物スペーサ112間で露出基板に金属化シリコン64（シリサイド）の導電層が形成され、そしてポリプロック42の露出した上部に金属化ポリシリコン66（ポリサイド）の導電層が形成される。残りの構造体に付着された金属は、金属エッチングプロセスにより除去される。それにより得られる構造体が図7Yに示されている。

#### 【0077】

酸化物層114（例えば、BPTEOS）を使用して、構造体がカバーされる。マスキングステップを実行して、サリサイド領域64の上にエッチング領域が画成される。このエッチング領域において酸化物層114が選択的にエッチングされ、理想的にはサリサイド領域64（及び第2領域50）を中心とする接触開口が形成される。次いで、接触開口には、金属付着及び平坦化エッチバックにより導体金属が埋められ、導体コンタクト72を形成する。サリサイド層64は、導体72と第2領域50との間の導通を改善する。ポリサイド層66は、ポリプロック42の長さに沿った導通を改善する。酸化物114上に金属マスキングを行うことにより各活性領域にビットライインコネクタ74が追加され、その活性領域において全てのコンタクト72が一緒に接続される。最終的な構造が図7Zに示されている。

#### 【0078】

コンタクト72の形成は、セルフ・アライン型接触構成（SAC）と称される。というのは、コンタクトの巾が、隣接対向窒化物スペーサ112間の分離距離より広くされ、従って、ドレイン領域50にセルフ・アラインされるからである。コンタクト72の一部分は、ポリプロック56の真上に形成されるが、窒化物層110によりそこから絶縁され、従って、ドレイン領域50との良好な接触が得られるように確保する。

#### 【0079】

セルフ・アライン型接触構成（SAC）は、対構成のメモリセルの隣接セット間の最小間隔要件に関する重要な制約を排除する。より詳細には、図7Zは、好ましくはドレイン領域50を中心とする接触領域（従って、導体72）を示しているが、実際には、ドレイン領域50に対してある程度の望ましくない水平シフトなしに接触開口を形成することが非常に困難である。コンタクト72がスペーサ112間の空間を完全に埋めるのを妨げるに充分なほど水平シフトが大きくなった場合には、欠陥接続が発生する。図3Uに示した実施形態に使用されるような非セルフ・アライン接触構成では、ポリスペーザ56上に窒化物の保護層がないところでは、コンタクト72がシフトしてポリスペーザ56と接触した場合に、電気的な短絡が生じ得る。非セルフ・アライン接触構成において電気的な短絡を防止するために、接触開口にはスペーザ58から充分離れたエッジが形成され、したがって、接触領域において考えられる最大のシフトがあっても、それらがスペーザ58を越えて延びることはない。これは、もちろん、図3Uに示した実施形態に対しスペーザ58間の最小距離に関する制約を与え、対構成の鏡像セルの隣接セット間に充分な許容距離がとれるようにする。

#### 【0080】

第4の別の実施形態で使用されるSACは、ポリプロック56上に保護材料層（窒化物層

10

20

30

40

50

110)を使用することによりこの制約を排除する。この保護層があると、形成中に接触開口が著しく水平にシフトしても、接触開口とドレン領域50の重畠を確保するに充分な巾で接触開口を酸化物層114に形成することができる。窒化物層110は、コンタクト72の部分を、ポリブロック56に短絡させることなく、ポリブロック56上に形成できるようにする。従って、スペーサ72間の接触領域の巾を最小にし、全セル寸法をスケールダウンすることができる。SACは、本明細書に説明するいかなる方法実施形態にも使用できることに注意されたい。

#### 【0081】

第3の別の実施形態と同様に、この第4の別の実施形態でも、第2領域50が第3のトレンチの底壁の中央部分の下だけに形成され、従って、「S」字型のチャンネル領域76は、ほぼ直角に接合された3つの部分を有し、即ち第1の水平部分80は、第3のトレンチ44とソース領域38との間に延び、垂直部分78は、第3のトレンチ44の垂直壁に沿って延び、そして第2の水平部分96は、垂直部分78とドレン領域50との間に延びる。ほぼ長方形の制御ゲート56は、チャンネル領域の垂直部分78に直接隣接した第1部分と、チャンネル領域の第2の水平部分96に直接隣接した第2部分とを各々有している。窒化物層30の残りの部分は、より強力な側壁フリンジフィールドを与え、従って、ソース領域38(ポリブロック42を含む)とフローティングゲート14との間の容量性結合を改善する。フローティングゲート14は、それに対して横方向に隣接配置された垂直に向いた制御ゲートブロック56に直接対向する水平に向いたエッジ54を有している。最後に、制御ゲート酸化物の厚みは、正確に制御することが非常に困難なポリ付着及びエッチバックプロセスではなく、ポリ付着ステップにより指令される。

#### 【0082】

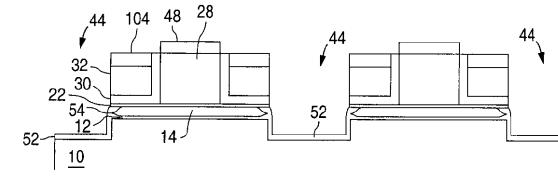

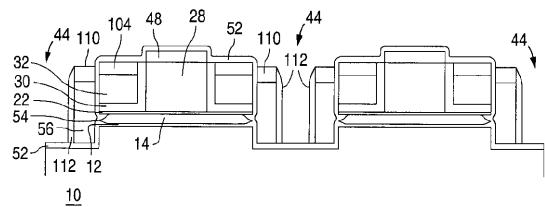

##### 第5の別の実施形態

図8Aないし8Wは、図7Zに示したものと同様のメモリセル構造体を、金属のソースライン構成で形成するための第5の別のプロセスを示す。この第5の別のプロセスは、図7Fに示したものと同じ構造体で開始される。

BSGエッティング(例えば、湿式エッティング)を使用して、図8Aに示すようにBSG102が除去され、その後、非等方性酸化物エッティング(例えば、RIE)を行って、酸化物層32の露出部分(即ち窒化物104で保護されない部分)が除去され、酸化物ブロック32間に配置された半くぼみの第3のトレンチ44が残される。次いで、構造体が熱酸化処理を受け、ポリブロック28上に酸化物層48を形成する。酸化物層48は、ポリブロック28にセルフ・アラインされる(例えば、600までの厚みで)。それにより生じる構造体が図8Bに示されている。

#### 【0083】

非等方性(乾式)窒化物エッティングを使用して、第3のトレンチ44に(酸化物ブロック32間で)露出された窒化物層30の部分が除去され、このとき、酸化物層22がエッティングストッパーとして使用される。又、この窒化物エッティングは、窒化物層104をある程度除去すると共に(例えば、500までの厚みを残して)、ポリブロック28に隣接する窒化物層30の露出部分を除去する。非等方性酸化物エッティングがそれに続き、第3のトレンチ44に(酸化物ブロック32間で)露出された酸化物層22の部分が除去され、このとき、ポリ層14がエッティングストッパーとして使用される。又、この酸化物エッティングは、酸化物層48の小さな部分も若干消費する。それにより生じる構造体が図8Cに示されている。

#### 【0084】

次いで、非等方性(乾式)ポリエッティングを実行して、第3のトレンチに(酸化物ブロック32間で)露出されたポリ層14の部分が除去され、このとき、酸化物層12がエッティングストッパーとして使用される。このポリエッティングは、図8Dに示すように、第3のトレンチ44に対向するポリ層14の縁に傾斜即ちテーパー領域106を形成するように実行されるのが好ましい。

#### 【0085】

10

20

30

40

50

非等方性(乾式)酸化物エッティングがそれに続き、第3のトレンチ44に(酸化物ブロック32間で)露出された酸化物層12の部分が除去され、第3のトレンチ44の底に基板10を露出させる。又、この酸化物エッティングは、酸化物層48の小さな部分も若干消費する。シリコン基板10が第3のトレンチ44の底に露出されたままである状態で、シリコン(乾式)エッティングプロセスが実行されて、第3のトレンチ44を、基板表面より500ないし1500低い深さまで、基板10へと下方に拡張させる。このエッティングは、シリコンと酸化物との間に1対1の選択性をもつように選択され、従って、酸化物分離領域16にも同様の深さのトレンチをエッティングし(LOCOS又はSTI)、ここでは、第3のトレンチ44が連続的に形成されそして活性領域及び分離領域17/16にわたって延びる。

10

## 【0086】

次いで、酸化プロセスが実行され、第3のトレンチ44の露出したシリコン表面が酸化されて、それらシリコン表面のライニングとなる薄い酸化物層52(例えば、150)が形成される。又、この酸化プロセスは、第3のトレンチ44の上部の側壁の一部分を形成するポリ層14の露出したテーパー面106も酸化し、図8Fに示すように、第3のトレンチ44の側壁の1つを各々直接的に指す水平に向いたエッジ54が形成され。これらエッジ54は、細長いエッジ(即ち、かみそりの刃の鋭いエッジのような)でもよいし、短いエッジ(鉛筆の先端のような)でもよい。又、この酸化プロセスは、ポリブロック42よりも酸化物層48を厚くする。

## 【0087】

20

任意の酸化物層最適化プロセスが次に行われ、第3のトレンチ44から酸化物層52を除去し、その後、HTO酸化物付着ステップを行って、良好に制御された厚み(例えば、150)を有する酸化物層52を全構造体上に再形成することにより、熱成長ファウラー・ノルドハイムトンネリング酸化物の厚みを最適化することができる。それにより生じる構造体が図8Gに示されている。

図8Hに示すように、ポリ層56が構造体上に形成される(例えば、800厚み)。ポリ層56の上面には、金属化ポリシリコン(図示せず)を形成することができる。次いで、図8Iに示すように、ポリ層56上に、誘電体材料の層108(例えば、BSG、1000まで)が形成される。次いで、BSGエッティングプロセスを使用して、BSG108を、酸化物層52と平らになるように下方にエッティングし、その後、ポリエッティングにより、ポリ層56を、酸化物層52と平らになるように下方にエッティングする。これらBSG及びポリエッティングに代わって、CMP平坦化を使用することもできる。付加的なポリエッティングを行って、図8Jに示すように、ポリ層56の上部を酸化物層52の上部及びBSG108より下にくぼませる。

30

## 【0088】

次いで、窒化物層110が、図8Kに示すように、構造体上に付着される(例えば、800)。その後、窒化物エッティングが、酸化物層52をエッティングストッパーとして使用して行われ、図8Lに示すように、ポリ層56の上に窒化物ブロック110を残す。窒化物ブロック110は、酸化物層52(及び酸化物ブロック32)と、BSG108とにより、ポリ層56にセルフ・アラインされる。次いで、BSGエッティングを使用して、第3のトレンチ44からBSGブロック108が除去される。それにより生じる構造体が図8Mに示されている。

40

## 【0089】

非等方性ポリエッティングを使用して、図8Nに示すように、第3のトレンチ44の底においてポリ56の露出部分(即ち、窒化物110により保護されない部分)が除去される。次いで、窒化物が構造体上に付着され(例えば、300厚み)、その後、非等方性窒化物エッティング(例えば、RIE)を実行し、図8Oに示すように、第3のトレンチ44において窒化物スペーサ112を除き、付着窒化物が除去される。

構造体の全面にわたって適当なイオンインプランテーションが行われ、第3のトレンチ44の下で基板10に第2領域50(埋設ビットラインドレイン領域)が形成される。第3

50

のトレンチ 4 4 の外部では、イオンが阻止され、何の作用も果たさない。このイオンインプランテーションプロセスは、プロセスにおいて早い段階又は遅い段階で実行できることに注意されたい。それにより生じる構造体が図 8 P に示されている。

#### 【 0 0 9 0 】

酸化物層 1 1 6 が構造体上に付着され、図 8 Q に示すように、第 3 のトレンチを埋める。構造体の上面は、窒化物層 1 1 0 をエッティングストッパーとして使用し、そして図 8 R に示すように、ポリブロック 2 8 を露出させて、平坦化される（例えば、C M P プロセス）。

。

ポリエッティングプロセスを使用して、ポリブロック 2 8 が除去され（酸化物層 2 2 をエッティングストッパーとして使用して）、第 2 のトレンチ 3 4 が形成される。制御型酸化物エッティング（例えば、H F ）を使用して、第 2 のトレンチ 3 4 の底に露出した酸化物層 2 2 の部分が除去される（ポリ層 1 4 をエッティングストッパーとして使用して）。別のポリエッティングプロセスが実行されて、第 2 のトレンチ 3 4 の底に露出したポリ層 1 4 の部分が除去される（酸化物層 1 2 をエッティングストッパーとして使用して）。次いで、適当なイオンインプランテーションを使用して、周囲基板の導電型（例えば P 型）とは異なる導電型（例えば N 型）を有する基板 1 0 に第 1 領域（ソース領域）3 8 が形成される。これにより生じる構造体が図 8 S に示されている。

10

#### 【 0 0 9 1 】

図 8 T に示すように、熱酸化プロセスを使用して、トレンチ 3 4 においてポリ層 1 4 の露出端に酸化物側壁層 3 6 が形成される。次いで、第 2 のトレンチ 3 4 の壁に側壁スペーサ 4 0 が形成され、これは、全構造体上に薄い酸化物層（例えば、2 0 0 ）を付着し、その後、非等方性エッティングプロセス（例えば、R I E ドライエッティング）を行って、スペーサ 4 0 を除き付着酸化物層を除去することにより行われる。又、この酸化物エッティングプロセスは、第 2 のトレンチ 3 4 の底において酸化物層 1 2 の露出部分も除去し、基板 1 0 を露出すると共に、酸化物層 5 2 をある程度消費する。それにより得られる構造体が図 8 U に示されている。次いで、第 2 のトレンチ 3 4 が、金属材料のブロック 1 2 0 で次のように埋められる。T i N 材料の層 1 1 8 が構造体上に付着され、その後、アルミニウム又はタンゲステンのような導電性金属の厚い層が付着されるのが好ましい。次いで、金属平坦化ステップがそれに続き（例えば、C M P ）、これは、金属層を、第 2 のトレンチ 3 4 の上部と平らになるように下方にエッティングし、第 2 のトレンチ 3 4 に導電性金属のブロック 1 2 0 を残し、そして T i N 材料層 1 1 8 を経てソース領域 3 8 に電気的接触した状態にする。任意の金属くぼみエッティングを実行して、第 2 のトレンチ 3 4 の外部に付着した全ての金属が除去されるよう確保することができる。それにより得られる構造体が図 8 V に示されている。

20

30

#### 【 0 0 9 2 】

酸化物層 1 1 4 （例えば、B P T E O S ）を使用して、構造体がカバーされる。マスキングステップを実行して、ドレイン領域 5 0 上にエッティング領域を画成する。エッティング領域から酸化物層 1 1 4 、1 1 6 及び 5 2 を選択的にエッティングし、第 2 領域 5 0 の露出部分を理想的に中心としそしてそれより著しく広い接触開口を形成する。次いで、接触開口は、金属付着及び平坦化エッチャックにより導体金属で埋められ、導体コンタクト 7 2 を形成する。酸化物 1 1 4 上に金属マスキングを行うことにより各活性領域にビットラインコネクタ 7 4 が追加され、その活性領域において全てのコンタクト 7 2 が一緒に接続される。最終的な構造が図 8 W に示されている。

40

#### 【 0 0 9 3 】

垂直に向けられた制御ゲートに向かう水平に向けられたフロー・ティングゲートの先鋭なエッジ、金属コンタクト 7 2 の S A C 整列、「S」字型チャンネル領域、及びポリ付着ステップにより指令される制御ゲートの長さの利点に加えて、この実施形態は、金属材料のブロックがその長さに沿って取り付けられる状態でソースライン 3 8 を形成し、従って、ソースライン 3 8 の全抵抗をその長さにわたって減少するという更に別の効果を有する。

#### 【 0 0 9 4 】

本発明は、上述した実施形態に限定されるものではなく、特許請求の範囲内に入る全ての変更も包含することを理解されたい。例えば、第3のトレンチ44は、図示された細長い長方形だけではなく、いかなる形状で基板へと延びて終了してもよい。又、上述した方法は、メモリセルを形成するのに使用する導電性材料として適当にドープされたポリシリコンの使用を説明したが、いかなる適当な導電性材料も使用できることが当業者に明らかであろう。更に、二酸化シリコン又は窒化シリコンに代わっていかなる適当な絶縁材を使用することもできる。更に、エッティング特性が二酸化シリコン（又は絶縁材）及びポリシリコン（又は導体）から相違するような適当な材料を、窒化シリコンに代わって使用することができる。更に、請求の範囲から明らかなように、上述した又は請求の範囲に述べた厳密な順序で全ての方法段階を実行する必要はなく、本発明のメモリセルを適切に形成できるものであれば、いかなる順序でもよい。又、本発明のメモリセル素子は、均一にドープされた基板において形成されるものとして示されたが、基板の他の部分に比して異なる導電型を有するようにドープされた領域である基板のウェル領域にも形成できることが明らかであり且つ意図される。最後に、絶縁材料又は導電性材料の単一層は、そのような材料の多層として形成することもでき、又、その逆のことも言える。

【図面の簡単な説明】

【図1】従来の分割ゲート不揮発性メモリセルを示す側面断面図である。

【図2A】分離領域を形成するための本発明の方法の第1ステップに使用される半導体基板の上面図である。

【図2B】1-1線に沿った構造体の断面図で、本発明の初期処理ステップを示す図である。

【図2C】図2Bの構造体の処理において分離領域を形成する次のステップを示す構造体の上面図である。

【図2D】図2Cの1-1線に沿った構造体の断面図で、構造体に形成された分離縞を示す図である。

【図2E】図2Cの1-1線に沿った構造体の断面図で、半導体基板に形成することのできる2つの形式の分離領域、即ちLOCOS又は浅いトレンチを示す図である。

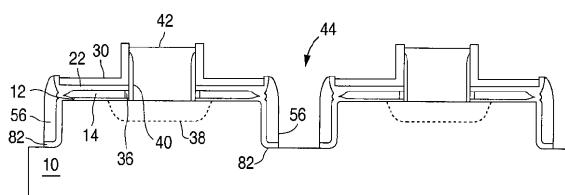

【図3A】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3B】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3C】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3D】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3E】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3F】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3G】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3H】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

10

20

30

40

50

↑ ップを示す図である。

【図3I】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローイングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図 3 J】図 2 C の 2 - 2 線に沿った構造体の断面図で、本発明によるフロー・ティング・メモリセルの不揮発性メモリアレーの形成において、図 2 C に示す構造体の処理の次のステップを示す図である。

【図3K】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3L】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3M】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図 3 N】図 2 C の 2 - 2 線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図 2 C に示す構造体の処理の次のステップを示す図である。

【図30】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3P】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3Q】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3R】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図 3 S】図 2 C の 2 - 2 線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図 2 C に示す構造体の処理の次のステップを示す図である。

【図3T】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

【図3U】図2Cの2-2線に沿った構造体の断面図で、本発明によるフローティングメモリセルの不揮発性メモリアレーの形成において、図2Cに示す構造体の処理の次のステップを示す図である。

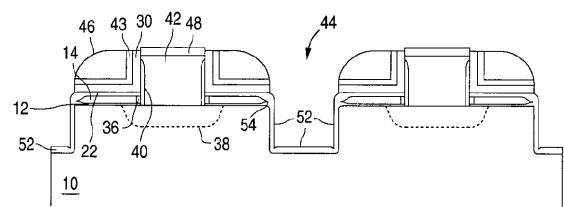

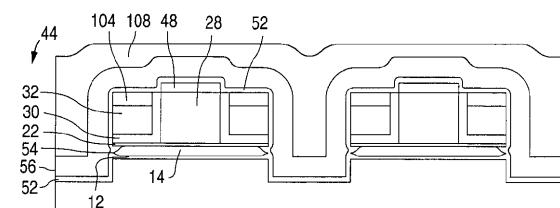

【図4A】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図3Oの半導体構造体の第1の別の処理のステップを示す図である。

【図4B】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図3Oの半導体構造体の第1の別の処理の次のステップを示す。

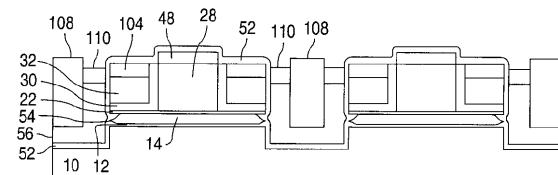

【図 4 C】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 3 O の半導体構造体の第 1 の別の処理の次のステップを示す

【図である。】当道体構造体の断面図で、主発明の第一、二、三の気筒部材との差異が示されている。

図である。

【図 7 L】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 3 C の半導体構造体の第 4 の別の処理の次のステップを示す図である。

【図7M】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図3Cの半導体構造体の第4の別の処理の次のステップを示す図である。

【図 7 N】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 3 C の半導体構造体の第 4 の別の処理の次のステップを示す図である。

【図70】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図3Cの半導体構造体の第4の別の処理の次のステップを示す図である。

【図7P】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図3Cの半導体構造体の第4の別の処理の次のステップを示す図である。

【図7Q】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図3Cの半導体構造体の第4の別の処理の次のステップを示す図である。

【図 7 R】半導体構造体の断面図で、本発明のフロー・ティングメモリセルの不揮発性メモリアレーの形成において、図 3 C の半導体構造体の第 4 の別の処理の次のステップを示す図である。

【図7S】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図3Cの半導体構造体の第4の別の処理の次のステップを示す図である。

【図7T】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図3Cの半導体構造体の第4の別の処理の次のステップを示す図である。

【図 7 U】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 3 C の半導体構造体の第 4 の別の処理の次のステップを示す。

【図 7 V】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 3 C の半導体構造体の第 4 の別の処理の次のステップを示す。図 7 V

【図 7 W】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 3 C の半導体構造体の第 4 の別の処理の次のステップを示す。図 7 W

【図 7 X】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 3 C の半導体構造体の第 4 の別の処理の次のステップを示す

【図 7 Y】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 3 C の半導体構造体の第 4 の別の処理の次のステップを示す

【図 7 Z】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 3 C の半導体構造体の第 4 の別の処理の次のステップを示す

【図 8 A】半導体構造体の断面図で、本発明のフロー・ティングメモリセルの不揮発性メモリアレーの形成において、図 7 F の半導体構造体の第 5 の別の処理のステップを示す図で

五、在本办法施行前，已经取得《医疗机构执业许可证》的医疗机构，应当自本办法施行之日起六个月内，向所在地县级人民政府卫生行政部门申请换发《医疗机构执业许可证》，并按照本办法的规定重新登记。

【図 8 S】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 7 F の半導体構造体の第 5 の別の処理の次のステップを示す図である。

【図 8 T】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 7 F の半導体構造体の第 5 の別の処理の次のステップを示す図である。

【図 8 U】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 7 F の半導体構造体の第 5 の別の処理の次のステップを示す図である。

【図 8 V】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 7 F の半導体構造体の第 5 の別の処理の次のステップを示す図である。 10

【図 8 W】半導体構造体の断面図で、本発明のフローティングメモリセルの不揮発性メモリアレーの形成において、図 7 F の半導体構造体の第 5 の別の処理の次のステップを示す図である。

【符号の説明】

|             |            |    |

|-------------|------------|----|

| 1 0         | 半導体基板      |    |

| 1 2         | 絶縁材料層      |    |

| 1 4         | ポリシリコン層    |    |

| 1 6         | 縞          | 20 |

| 1 8         | 窒化物層       |    |

| 1 7         | 活性領域       |    |

| 1 9         | ホトレジスト層    |    |

| 2 0 a、2 0 b | 分離材料       |    |

| 2 2         | 絶縁層        |    |

| 2 4         | ポリ層        |    |

| 2 6         | 第 1 トレンチ   |    |

| 2 8         | ポリブロック     |    |

| 3 0         | 窒化物層       |    |

| 3 2         | 酸化物層       | 30 |

| 3 4         | 第 2 トレンチ   |    |

| 3 8         | ソース領域      |    |

| 4 0         | 側壁スペーサ     |    |

| 4 2         | ポリブロック     |    |

| 4 3         | 酸化物層       |    |

| 4 4         | 第 3 トレンチ   |    |

| 4 6         | スペーサ       |    |

| 4 8         | 酸化物層       |    |

| 5 0         | 第 2 領域     |    |

| 5 2         | 薄い酸化物層     | 40 |

| 5 4         | 水平を向いたエッジ  |    |

| 5 6         | ポリスペーサ     |    |

| 5 8         | 絶縁スペーサ     |    |

| 6 0、6 2     | 酸化物スペーサ    |    |

| 6 4         | シリサイド      |    |

| 6 6         | ポリサイド      |    |

| 6 8         | ポリサイド層     |    |

| 7 0         | B P S G    |    |

| 7 2         | 導体コンタクト    |    |

| 7 4         | ビットラインコネクタ | 50 |

- 7 6 チャンネル領域

7 8 垂直部分

8 0 水平部分

【図1】

従来技術

【図2 B】

【図2 A】

【図 2 C】

【図 2 E】

【図 2 D】

【図 3 A】

【図 3 B】

【図 3 C】

【図 3 D】

【図 3 H】

【図 3 E】

【図 3 I】

【図 3 F】

【図 3 J】

【図 3 G】

【図 3 K】

【図3L】

【図3M】

【図3N】

【図3O】

【図3P】

【図3Q】

【図3R】

【図3U】

【図3S】

【図4A】

【図3T】

【図4B】

【図 4 C】

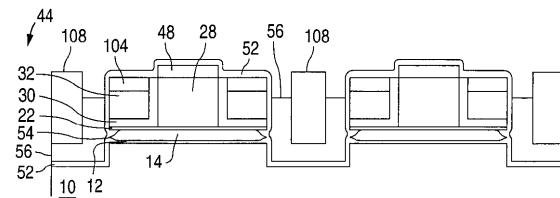

【図 4 F】

【図 4 D】

【図 4 G】

【図 4 E】

【図 5 A】

【図 5 B】

【図 5 E】

【図 5 C】

【図 5 F】

【図 5 D】

【図 5 G】

【図 5 H】

【図 5 I】

【図 6 A】

【図 6 B】

【図 6 C】

【図 6 D】

【図 6 E】

【図 6 F】

【図 6 I】

【図 6 G】

【図 6 J】

【図 6 H】

【図 7 A】

【図 7 B】

【図 7 C】

【図 7 D】

【図 7 E】

【図 7 F】

【図 7 G】

【図 7 H】

【図 7 I】

【図 7 M】

【図 7 J】

【図 7 N】

【図 7 K】

【図 7 O】

【図 7 L】

【図 7 P】

【図 7 S】

【図 7 Q】

【図 7 T】

【図 7 R】

【図 7 U】

【図 7 V】

【図 7 Y】

【図 7 W】

【図 7 Z】

【図 7 X】

【図 8 A】

【図 8 B】

【図 8 E】

【図 8 C】

【図 8 F】

【図 8 D】

【図 8 G】

【図 8 H】

【図 8 K】

【図 8 I】

【図 8 L】

【図 8 J】

【図 8 M】

【図 8 N】

【図 8 Q】

【図 8 O】

【図 8 R】

【図 8 P】

【図 8 S】

【図 8 T】

【図 8 W】

【図 8 U】

【図 8 V】

---

フロントページの続き

(74)代理人 100065189

弁理士 宮戸 嘉一

(74)代理人 100074228

弁理士 今城 俊夫

(74)代理人 100084009

弁理士 小川 信夫

(74)代理人 100082821

弁理士 村社 厚夫

(74)代理人 100086771

弁理士 西島 孝喜

(74)代理人 100084663

弁理士 箱田 篤

(72)発明者 チー シン ワン

アメリカ合衆国 カリフォルニア州 95120 サンホセ ギリス ドライヴ 6585

(72)発明者 ピン イエー

アメリカ合衆国 カリフォルニア州 94024 ロス アルトス ヒルズ ジェイビル レーン

24055

審査官 粟野 正明

(56)参考文献 特開平11-274328(JP,A)

特開2002-158302(JP,A)

特開2002-158303(JP,A)

特開2003-179170(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8247

H01L 27/115

H01L 29/788

H01L 29/792