(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-112136

(P2008-112136A)

(43) 公開日 平成20年5月15日(2008.5.15)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>G09F 9/30</b> (2006.01)   | G09F 9/30  | 2 H 092     |

| <b>H01L 29/786</b> (2006.01) | H01L 29/78 | 4 M 104     |

| <b>H01L 21/28</b> (2006.01)  | H01L 29/78 | 5 C 094     |

| <b>H01L 29/417</b> (2006.01) | H01L 29/78 | 5 F 110     |

| <b>H01L 29/423</b> (2006.01) | H01L 29/78 | 6 2 3 Z     |

審査請求 未請求 請求項の数 18 O L (全 20 頁) 最終頁に続く

|              |                              |          |                                            |

|--------------|------------------------------|----------|--------------------------------------------|

| (21) 出願番号    | 特願2007-160651 (P2007-160651) | (71) 出願人 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号 |

| (22) 出願日     | 平成19年6月18日 (2007. 6. 18)     | (74) 代理人 | 100103894<br>弁理士 家入 健                      |

| (31) 優先権主張番号 | 特願2006-273106 (P2006-273106) | (72) 発明者 | 西浦 篤徳<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内       |

| (32) 優先日     | 平成18年10月4日 (2006. 10. 4)     | (72) 発明者 | 竹口 徹<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内        |

| (33) 優先権主張国  | 日本国 (JP)                     | (72) 発明者 | 今村 阜司<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内       |

最終頁に続く

(54) 【発明の名称】表示装置及びその製造方法

## (57) 【要約】

【課題】本発明による表示装置においては、生産性が高く、表示品位の優れた表示装置及びその製造方法を提供することを目的とする。

【解決手段】本発明にかかる表示装置は、基板と、基板上に設けられ、半導体層とキャパシタ電極6及びゲート電極15を含む第1導電層との間に配置されるゲート絶縁膜5と、半導体層、第1導電層、及びゲート絶縁膜5の上層に形成された層間絶縁膜8と、層間絶縁膜8上に形成され、信号線9を含む第2導電層と、層間絶縁膜8及び第2導電層の上に形成された保護膜10と、保護膜10の上に形成された画素電極層12と、を備え、画素電極層12が、保護膜10を貫通して第2導電層まで到達し、かつ保護膜10、層間絶縁膜8、及びゲート絶縁膜5を貫通して半導体層まで到達することによって、半導体層と第2導電層とが画素電極層12を介して接続されている。

【選択図】 図2

## 【特許請求の範囲】

## 【請求項 1】

基板と、

前記基板上に設けられ、半導体層とキャパシタ電極及びゲート電極を含む第1導電層との間に配置されるゲート絶縁膜と、

前記半導体層、前記第1導電層、及び前記ゲート絶縁膜の上層に形成された層間絶縁膜と、

前記層間絶縁膜上に形成され、信号線を含む第2導電層と、

前記層間絶縁膜及び前記第2導電層の上に形成された保護膜と、

前記保護膜の上に形成された画素電極層と、を備え、

10

前記画素電極層が、前記保護膜を貫通して前記第2導電層まで到達し、かつ前記保護膜、前記層間絶縁膜、及び前記ゲート絶縁膜を貫通して前記半導体層まで到達することによって、前記半導体層と第2導電層とが前記画素電極層を介して接続されている表示装置。

## 【請求項 2】

前記画素電極層が、前記保護膜を貫通して前記第2導電層まで到達し、かつ前記保護膜及び前記層間絶縁膜を貫通して前記第1導電層まで到達することによって、前記第1導電層と前記第2導電層とが前記画素電極層を介して接続されている請求項1記載の表示装置。

## 【請求項 3】

前記画素電極層が、前記保護膜及び前記層間絶縁膜を貫通して前記第1導電層まで到達し、かつ前記保護膜、前記層間絶縁膜、及び前記ゲート絶縁膜を貫通して前記半導体層まで到達することによって、前記第1導電層と前記半導体層とが前記画素電極層を介して接続されている請求項1又は2記載の表示装置。

20

## 【請求項 4】

前記基板上の表示領域に形成されるゲート配線及びソース配線と、

前記ゲート配線又は前記ソース配線に信号を供給する駆動回路と、

前記基板上の表示領域外の額縁領域に形成され、前記駆動回路と前記ゲート配線及び前記ソース配線とを接続する、第1引き回し配線又は第2引き回し配線とを有し、

前記第1導電層は前記第1引き回し配線を含み、

前記第2導電層は前記第2引き回し配線を含み、

30

前記画素電極層が、前記保護膜を貫通して前記第2引き回し配線まで到達し、かつ前記保護膜及び前記層間絶縁膜を貫通して前記第1引き回し配線まで到達することによって、前記第1引き回し配線と前記第2引き回し配線とが前記画素電極層を介して接続されている請求項2記載の表示装置。

## 【請求項 5】

前記基板上の表示領域に形成されるゲート配線及びソース配線と、

前記ゲート配線又は前記ソース配線に信号を供給する駆動回路と、

前記基板上の表示領域外の額縁領域に形成され、前記駆動回路と前記ゲート配線及び前記ソース配線とを接続する、第1引き回し配線又は第2引き回し配線と、

前記基板上の前記表示領域外の額縁領域に形成され、前記ゲート配線と前記ソース配線の間の絶縁破壊、又は前記第1引き回し配線と前記第2引き回し配線の間の絶縁破壊から各配線を保護する保護回路とを有し、

40

前記保護回路では、前記画素電極層が、前記保護膜及び前記層間絶縁膜を貫通して前記ゲート電極まで到達し、かつ前記保護膜、前記層間絶縁膜、及び前記ゲート絶縁膜を貫通して前記半導体層まで到達することによって、前記ゲート電極と前記半導体層とが前記画素電極層を介して接続されている請求項3記載の表示装置。

## 【請求項 6】

前記第2導電層が設けられた全領域において、前記第2導電層直下にはコンタクトホールを有しない請求項1乃至5のいずれかに記載の表示装置。

## 【請求項 7】

50

一回のエッティング工程で形成される前記半導体層まで到達するコンタクトホールと、前記第2導電層まで到達するコンタクトホールと、を有する請求項1乃至6のいずれかに記載の表示装置。

**【請求項8】**

一回のエッティング工程で形成される前記半導体層まで到達するコンタクトホールと、前記第1導電層まで到達するコンタクトホールと、前記第2導電層まで到達するコンタクトホールと、を有する請求項1乃至7のいずれかに記載の表示装置。

**【請求項9】**

前記画素電極層が透明導電膜を含んでいる請求項1乃至8のいずれかに記載の表示装置。

10

**【請求項10】**

前記画素電極層と前記半導体層がバリアメタルを介して接続される請求項9に記載の表示装置。

**【請求項11】**

前記画素電極層がメタルまたはメタルを主成分とする合金を含んでいる請求項1乃至10のいずれかに記載の表示装置。

**【請求項12】**

前記画素電極層が、上層導電膜と下層導電膜とを有する積層構造である請求項1乃至11のいずれかに記載の表示装置。

**【請求項13】**

前記基板上の表示領域外に設けられ、前記層間絶縁膜の下に形成された端子配線を備え、

前記画素電極層が、前記保護膜及び前記層間絶縁膜を貫通して前記端子配線まで到達することによって、前記端子配線と前記画素電極層とが接続されている請求項1乃至12のいずれかに記載の表示装置。

**【請求項14】**

基板上に、半導体層、キャパシタ電極及びゲート電極を含む第1導電層、並びに前記半導体層と前記第1導電層との間に配置されるゲート絶縁膜を形成する工程と、

前記半導体層、前記第1導電層、及び前記ゲート絶縁膜の上層に層間絶縁膜を成膜する工程と、

20

前記層間絶縁膜上に信号線を含む第2導電層を形成する工程と、

前記層間絶縁膜及び前記第2導電層の上層に保護膜を形成する工程と、

前記保護膜形成後、前記保護膜を貫通して前記第2導電層まで到達するコンタクトホールと、前記保護膜及び前記層間絶縁膜を貫通して前記第1導電層まで到達するコンタクトホールと、前記保護膜、前記層間絶縁膜及び前記ゲート絶縁膜を貫通して前記半導体層まで到達するコンタクトホールと、を形成するコンタクトホール形成工程と、

前記コンタクトホール形成後、前記保護膜上に画素電極層を形成する工程と、を有する表示装置の製造方法。

**【請求項15】**

前記半導体層まで到達するコンタクトホールと、前記第2導電層まで到達するコンタクトホールと、が1回のエッティング工程で形成される請求項14に記載の表示装置の製造方法。

40

**【請求項16】**

前記半導体層まで到達するコンタクトホールと、前記第1導電層まで到達するコンタクトホールと、前記第2導電層まで到達するコンタクトホールと、が1回のエッティング工程で形成される請求項14又は15に記載の表示装置の製造方法。

**【請求項17】**

前記基板上に、前記半導体層、前記第1導電層、及び前記ゲート絶縁膜を形成する工程において、前記基板上の前記表示領域外に前記端子配線が形成され、

前記コンタクトホール形成工程において、前記端子配線まで到達するコンタクトホール

50

が形成される請求項 1 4 乃至 1 6 のいずれか 1 項に記載の表示装置の製造方法。

【請求項 1 8】

前記第 2 導電層まで到達するコンタクトホールと、前記端子配線まで到達する前記コンタクトホールと、が 1 回のエッティング工程で形成される請求項 1 7 に記載の表示装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、表示装置及びその製造方法に関する。

【背景技術】

【0 0 0 2】

薄膜トランジスタ(Thin Film Transistor : TFT)を画素スイッチング素子として用いたアクティブマトリックス型液晶表示装置・有機EL (Electroluminescence : 電界発光) 等の表示デバイスにおいて、TFT のチャネル活性層として多結晶シリコンを用いた多結晶シリコン薄膜トランジスタは、移動度が高く、画素スイッチング素子として用いられた場合、高精細化が可能であり、画素スイッチング素子を駆動するための周辺回路部にも適用することができる。

【0 0 0 3】

従来 TFT の活性層として用いている多結晶シリコン膜やゲート電極・キャパシタ電極として用いている導電膜へは、その上部に位置し信号線として用いているソースドレインメタルを介して導通していた。この場合、信号線形成前に多結晶シリコン膜及びゲート電極・キャパシタ電極へのコンタクトホールを形成し、その後信号線を形成することが一般的である。

【0 0 0 4】

信号線上にも絶縁膜(パッシベーション膜とも言う)を配する構造をとるのが一般的であり、信号線への導通は、信号線上の絶縁膜にもスルーホールを形成する必要があった(図 12 参照)。

【0 0 0 5】

また、従来の表示装置の TFT を含む TFT アレイ部では、信号線下にコンタクトホールを有する構造であった。このため、TFT アレイ部と同時に、TFT が形成される基板上に形成される回路と表示領域とを接続するための端子部を形成するためには、端子部においても層間絶縁膜、保護膜の各々にコンタクトホールを形成し、信号線を介して端子配線と画素電極層を接続する必要があった(図 13 (a) 及び (b) 参照)。

【特許文献 1】特開 2001-168343 号公報

【発明の開示】

【発明が解決しようとする課題】

【0 0 0 6】

従来の製造方法においては、第 2 配線としての信号線がその下層にある第 1 配線としてのゲート電極・キャパシタ電極または半導体層としてのポリシリコン膜との導通をとるために、信号線形成前に信号線下となる部分にコンタクトホールを形成する必要があった。さらに、一般的に信号線形成後に信号線上に絶縁膜(パッシベーション膜ともいう)を配するため、スルーホールを形成し、最上層との導通をとる必要があった。このため、マスク工数が多くコスト面での問題があった。また、信号線とゲート電極・キャパシタ電極がコンタクトホールで導通する部分は、導電層が重なり合うため、最上部である画素電極形成表面の凹凸が大きくなるという問題点があった。この場合、表示品位が劣化してしまう。このように、従来の液晶表示装置では、生産性が低く、表示品位が劣化するという問題点がある。

【0 0 0 7】

また、TFT 基板の端子部は、TFT が形成される基板の表示領域と同時に形成される。このため、画素電極層をゲート電極と同層に形成された端子配線に接続させるためには

10

20

30

40

50

、まず画素電極層と信号線を、コンタクトホールを介して接続し、信号線と端子配線を、コンタクトホールを介して接続する必要がある。すなわち、コンタクトホールを一括して形成することができず、TFT基板の製造工数が多かった。また、信号線と端子配線との間の絶縁膜に形成されるコンタクトホール、及び信号線と画素電極との間の絶縁膜に形成されるスルーホールを設けるための基板面積が必要となる。すなわち、端子部の面積が拡大するという問題点があった。

#### 【0008】

本発明は、このような問題を解決するためになされたものであり、生産性が高く、表示品位の優れた表示装置及びその製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0009】

本発明の第1の態様にかかる表示装置は、基板と、前記基板上に設けられ、半導体層とキャパシタ電極及びゲート電極を含む第1導電層との間に配置されるゲート絶縁膜と、前記半導体層、前記第1導電層、及び前記ゲート絶縁膜の上層に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、信号線を含む第2導電層と、前記層間絶縁膜及び第2導電層の上に形成された保護膜と、前記保護膜の上に形成された画素電極層と、を備え、前記画素電極層が、前記保護膜を貫通して前記第2導電層まで到達し、かつ前記保護膜、前記層間絶縁膜、及び前記ゲート絶縁膜を貫通して前記半導体層まで到達することによって、前記半導体層と第2導電層とが前記画素電極層を介して接続されている。

#### 【発明の効果】

#### 【0010】

本発明によれば、生産性が高く、表示品位の優れた表示装置及びその製造方法、提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0011】

以下に、本発明を適用可能な実施の形態の説明をする。以下の説明は、本発明の実施形態についてのものであり、本発明は以下の実施形態に限定されるものではない。

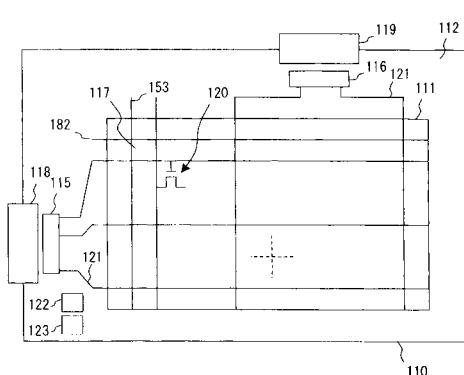

#### 【0012】

##### 実施例1.

始めに、図1を用いて、本発明に係るTFT基板が適用されるアクティブマトリクス型の表示装置について説明する。図1は、表示装置に用いられるTFT基板の構成を示す正面図である。本発明に係る表示装置は、液晶表示装置を例として説明するが、あくまでも例示的なものであり、有機EL表示装置等の平面型表示装置（フラットパネルディスプレイ）等を用いることも可能である。

#### 【0013】

本発明に係る液晶表示装置は、TFT基板110を有している。TFT基板110は、例えば、TFTアレイ基板である。TFT基板110には、表示領域111と表示領域111を囲むように設けられた額縁領域112とが設けられている。この表示領域111には、後述するTFT120に信号を供給する複数のゲート配線（走査信号線）182と複数のソース配線（表示信号線）153とが形成されている。複数のゲート配線182は平行に設けられている。同様に、複数のソース配線153は平行に設けられている。ゲート配線182とソース配線153とは、互いに交差するように形成されている。ゲート配線182とソース配線153とは直交している。そして、隣接するゲート配線182とソース配線153とで囲まれた領域が画素117となる。従って、TFT基板110では、画素117がマトリクス状に配列される。

#### 【0014】

更に、TFT基板110の額縁領域112には、走査信号駆動回路115と表示信号駆動回路116とが設けられている。ゲート配線182は、表示領域111から額縁領域112まで延設されている。TFT基板110の端部である額縁領域112において、ゲート配線182は引き回し配線121を介して走査信号駆動回路115に接続される。引き

10

20

30

40

50

回し配線 121 には、配線レイヤが変化される変換部 122 が設けられている。ソース配線 153 も同様に、表示領域 111 から額縁領域 112 まで延設されている。ソース配線 153 は、TFT 基板 110 の端部である額縁領域 112 において、表示信号駆動回路 116 に引き回し配線 121 を介して接続される。引き回し配線 121 には、配線レイヤが変化される変換部 122 が設けられている。走査信号駆動回路 115 の近傍には、外部配線 118 が接続されている。また、表示信号駆動回路 116 の近傍には、外部配線 119 が接続されている。外部配線 118、119 は、例えば、FPC (Flexible Printed Circuit) 等の配線基板である。そして、TFT 基板 110 の額縁領域 112 には、ゲート配線 182 とソース配線 153 の間の絶縁破壊、又は層が異なる引き回し配線 121 間の絶縁破壊から各配線を保護するための保護回路 123 を有する。詳細は後述する。

10

#### 【0015】

外部配線 118、119 を介して走査信号駆動回路 115、及び表示信号駆動回路 116 に外部からの各種信号が供給される。走査信号駆動回路 115 は外部からの制御信号に基づいて、ゲート信号（走査信号）をゲート配線 182 に供給する。このゲート信号によって、ゲート配線 182 が順次選択されていく。表示信号駆動回路 116 は外部からの制御信号や、表示データに基づいて表示信号をソース配線 153 に供給する。これにより、表示データに応じた表示電圧を各画素 117 に供給することができる。

#### 【0016】

画素 117 内には、少なくとも 1 つの TFT 120 が形成されている。TFT 120 はソース配線 153 とゲート配線 182 の交差点近傍に配置される。例えば、この TFT 120 が画素電極に表示電圧を供給する。即ち、ゲート配線 182 からのゲート信号によって、スイッチング素子である TFT 120 がオンする。これにより、ソース配線 153 から、TFT のドレイン電極に接続された画素電極に表示電圧が印加される。そして、画素電極と対向電極との間に、表示電圧に応じた電界が生じる。なお、TFT 基板 110 の表面には、配向膜（図示せず）が形成されている。

20

#### 【0017】

更に、TFT 基板 110 には、対向基板が対向して配置されている。対向基板は、例えば、カラーフィルタ基板であり、視認側に配置される。対向基板には、カラーフィルタ、ブラックマトリクス (BM)、対向電極、及び配向膜等が形成されている。なお、対向電極は、TFT 基板 110 側に配置される場合もある。そして、TFT 基板 110 と対向基板との間に液晶層が挟持される。即ち、TFT 基板 110 と対向基板との間には液晶が注入されている。更に、TFT 基板 110 と対向基板との外側の面には、偏光板、及び位相差板等が設けられる。また、液晶表示パネルの反視認側には、バックライトユニット等が配設される。

30

#### 【0018】

画素電極と対向電極との間の電界によって、液晶が駆動される。即ち、基板間の液晶の配向方向が変化する。これにより、液晶層を通過する光の偏光状態が変化する。即ち、偏光板を通過して直線偏光となつた光は液晶層によって、偏光状態が変化する。具体的には、バックライトユニットからの光は、アレイ基板側の偏光版によって直線偏光になる。そして、この直線偏光が液晶層を通過することによって、偏光状態が変化する。

40

#### 【0019】

従って、偏光状態によって、対向基板側の偏光版を通過する光量が変化する。即ち、バックライトユニットから液晶表示パネルを透過する透過光のうち、視認側の偏光板を通過する光の光量が変化する。液晶の配向方向は、印加される表示電圧によって変化する。従って、表示電圧を制御することによって、視認側の偏光板を通過する光量を変化させることができる。即ち、画素ごとに表示電圧を変えることによって、所望の画像を表示することができる。

#### 【0020】

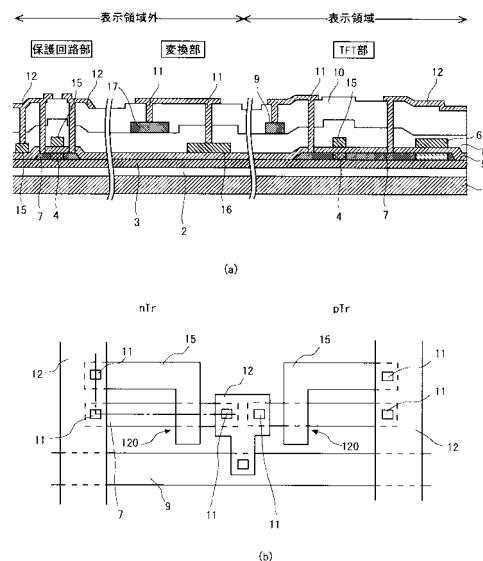

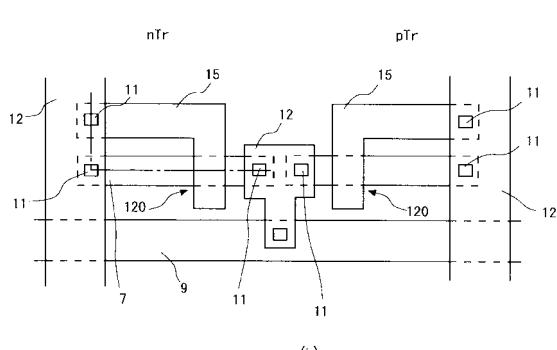

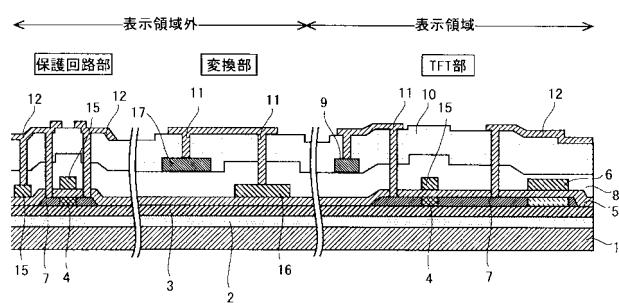

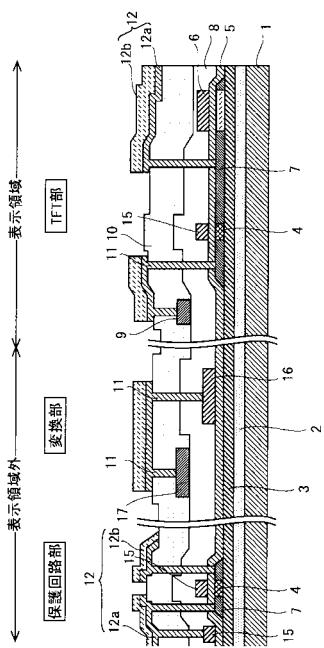

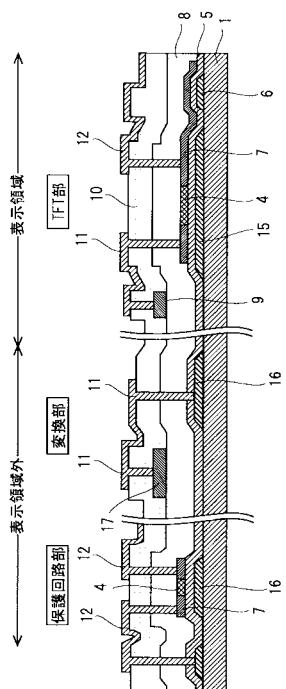

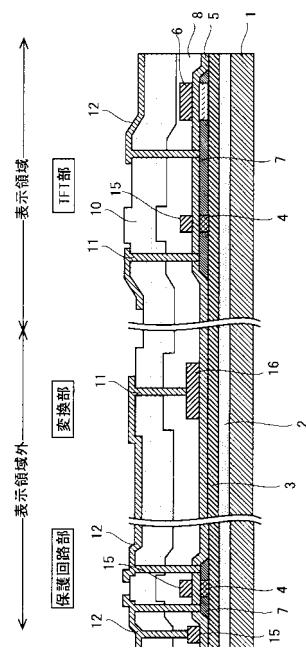

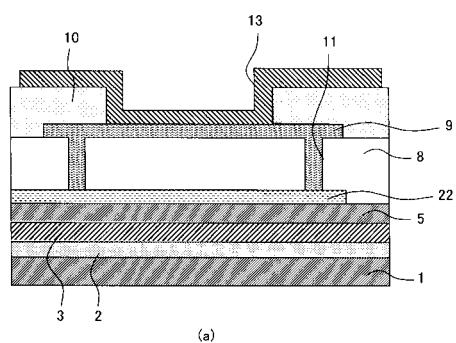

次に、TFT 基板 110 に設けられた TFT 120 の構成、及び製造工程について図 2 (a) 及び (b) を用いて説明する。図 2 (a) に、実施例 1 にかかる表示装置の TFT

50

部及び変換部の断面図を示す。図2(a)の右領域は表示領域に形成されるTFT部を示し、左領域は表示領域外に形成される変換部及び保護回路部を示す。また、図2(b)に実施例1にかかる表示装置の基板上の額縁領域に形成される保護回路の平面図を示す。なお、図2(b)に示す一点鎖線部の断面図が図2(a)に示す断面図である。まず、図2(a)を主に用いて本実施例の表示装置について説明する。本実施例では、トップゲート型のTFT120として説明する。ガラス基板1上に絶縁膜となる下地膜を設ける。まず、プラズマCVD法で下地膜である窒化シリコン膜2を50nm形成する。この窒化シリコン膜2は、ガラス基板1からのNa(ナトリウム)汚染を防止するために形成される。続いて、プラズマCVD法で酸化シリコン膜3を200nm形成する。この酸化シリコン膜3は、後ほど行われるアモルファスシリコンを結晶化させる際の補助的な役割をおこなう。窒化シリコン膜2及び酸化シリコン膜3は基板1の略全面に形成される。なお、窒化シリコン膜2又は酸化シリコン膜3以外の材料で下地膜を形成してもよい。さらに、下地膜を単層で形成してもよい。このように、下地膜を形成することによって、TFTの特性を安定させることができる。

10

## 【0021】

次に、プラズマCVD法でアモルファスシリコンを50nm形成する。熱処理をおこない、アモルファスシリコン中の水素濃度を低下させる。そして、レーザアニール法によりアモルファスシリコンを結晶化させポリシリコン膜4にする。レーザアニール法はエキシマレーザアニール法、YAGレーザアニール法などがあるが、これらに限定されるものではない。具体的には、レーザ照射によってアモルファスシリコンを溶融し、その後、冷却、固化させることによりポリシリコンとなる。そして、写真製版によりレジストパターンを形成する。レジストパターンを介してドライエッチングを行い、トランジスタを形成するためのポリシリコン膜4を所望の形状にパターニングする。そして、レジストを除去する。ポリシリコン膜4は、酸化シリコン膜3上に島状に形成される。これにより、TFTを形成する箇所に、半導体層となるポリシリコン膜4が形成される。

20

## 【0022】

次に、プラズマCVD法でゲート絶縁膜5をポリシリコン膜4上に形成する。ゲート絶縁膜5としては、例えば、厚さ80nmの酸化シリコン膜を用いることができる。これにより、ポリシリコン膜4がゲート絶縁膜5によって覆われる。次に、写真製版によりレジストパターンを形成し、半導体層のキャパシタ下部電極となる領域に選択的に不純物を導入する。これにより、後に形成されるキャパシタ電極6の直下の半導体層の導電率が向上し、キャパシタの電圧依存性を低減できる。

30

## 【0023】

次にスパッタ法によりゲート電極15、及びキャパシタ電極6及び第1引き回し配線16を含む第1導電層を形成するための金属薄膜を形成する。当該金属薄膜としては、例えばAl、Cr、Mo、Ti、W等や、これらに他の物質を微量に添加した合金などを用いることができる。ゲート電極15、キャパシタ電極6、及び第1引き回し配線16を形成するための金属薄膜を成膜後、写真製版によりレジストパターンを形成する。そして、エッチング液で金属薄膜を所望の形状にパターニングする。これにより、ゲート電極15、キャパシタ電極6、及び表示領域外に設けられる第1引き回し配線16が形成される。ゲート電極15は、ポリシリコン膜4のチャネル領域の上に形成される。キャパシタ電極6は、ゲート絶縁膜5の上に直接形成される。そして、ゲート電極15、及びキャパシタ電極6上のレジストを除去する。このゲート電極15は、例えばゲート配線182等である。

40

## 【0024】

次に、ゲート電極15、及びキャパシタ電極6をマスクとして、ポリシリコン膜4に不純物を導入する。これにより、チャネル領域の両側に配置されたソースドレイン領域7に不純物が導入される。ここでは、イオン注入法や、イオンドーピング法等を用いることができる。なお、信頼性向上のため、LDD(Lightly Doped Drain)構造にしてもよい。これにより、TFTが形成される。

50

## 【0025】

次に、プラズマCVD法により層間絶縁膜8となる酸化シリコン膜をゲート絶縁膜5の上に形成する。これにより、キャパシタ電極6及びポリシリコン膜4が層間絶縁膜8によって覆われる。層間絶縁膜8は、TEOSとO<sub>2</sub>を反応させた酸化シリコン膜を500nm形成したものである。なお、層間絶縁膜8の膜厚として、500nmの例を挙げたが、これに限定されるものではない。また、層間絶縁膜8は、酸化シリコン膜に限らず、窒化シリコン膜や有機膜などでもよい。

## 【0026】

次に、ポリシリコン膜4中に導入したP(リン)やB(ボロン)を活性化させるため、熱処理を行う。熱処理は、窒素雰囲気中で400、1時間とする。

10

## 【0027】

次に、スパッタ法によりソースドレインメタルよりなる信号線9及び第2引き回し配線17を含む第2導電層を形成するための金属薄膜を成膜する。信号線9はAl、Cr、Mo、Ti、W等の金属材料または合金材料である。ここではMo合金/A1合金/Mo合金の積層構造とし、膜厚はそれぞれ100nm/300nm/100nmとする。次に写真製版にレジストパターンを形成して、ドライエッチング法で信号線9を所望の形状にパターニングする。

## 【0028】

これにより、層間絶縁膜8の上に複数の信号線9、及び表示領域外に設けられる第2引き回し配線17が形成される。この信号線9は、例えば、ソース配線153等である。信号線9及び第2引き回し配線17は、第1引き回し配線16に接続されるコンタクトホール11上、及びポリシリコン膜4のソースドレイン領域7に接続されるコンタクトホール11上には形成されていない。このコンタクトホール11の形成工程については、後述する。この信号線9及び第2引き回し配線17は、層間絶縁膜8のコンタクトホール形成工程の前に形成される。すなわち、層間絶縁膜8を成膜した後、層間絶縁膜8、あるいはゲート絶縁膜5に対して形成するコンタクトホール11のパターニングを行う前に、信号線9及び第2引き回し配線17を形成する。

20

## 【0029】

次に、プラズマCVD法により保護膜10となる窒化シリコン膜を300nm形成する。次に、ダメージ回復のため、熱処理を行う。熱処理は、大気中で250、1時間とする。保護膜10は、窒化シリコン膜に限らず、酸化シリコン膜や有機膜などの絶縁膜でもよい。

30

## 【0030】

保護膜10形成後、保護膜10を貫通して信号線9及び第2引き回し配線17に到達するコンタクトホール11を形成する。また、この工程で保護膜10及び層間絶縁膜8を貫通して、第1引き回し配線16に到達するコンタクトホール11を形成する。さらに、この工程で、保護膜10、層間絶縁膜8及びゲート絶縁膜5を貫通してポリシリコン膜4のソースドレイン領域に到達するコンタクトホール11を形成する。具体的には、フォトリソグラフィー法によって保護膜10上にレジストパターンを形成する。そして、保護膜10、層間絶縁膜8、及びゲート絶縁膜5を順番にドライエッチングする。これにより、コンタクトホール11が形成される。一つのフォトマスクで、保護膜10、層間絶縁膜8、及びゲート絶縁膜5を貫通するコンタクトホール11を形成することができる。

40

## 【0031】

コンタクトホール11形成後、画素電極層12を成膜する。そして、画素電極層12をフォトリソグラフィー法などによってパターニングする。画素電極層12はITO膜などの透明導電膜により形成することができる。あるいは、画素電極層12をCr、Mo、Al、Ta、Tiなどのメタルもしくはこれらのメタルを主成分とする合金によって形成することも可能である。この画素電極層12には、液晶を駆動するための駆動電圧(表示電圧)が印加される画素電極が含まれている。例えば、液晶表示装置の場合、画素電極は、TFTのドレインと接続される。この画素電極層12は、コンタクトホール11に埋設さ

50

れる。コンタクトホール 11 に埋設された画素電極層 12 を介して表示領域内の TFT 部において、ポリシリコン膜 4 のソース領域と信号線 9 とが物理的・電気的に接続される。また、TFT 基板 110 上の表示領域に形成されるゲート配線及びソース配線と駆動回路とが引き回し配線を介して接続される。この引き回し配線は、第 1 の引き回し配線 16 及び第 2 の引き回し配線 17 を含み、配線レイヤが変化される変換部 122 が設けられている。そして、変換部 122 では、コンタクトホール 11 に埋設された画素電極層 12 を介して第 1 引き回し配線 16 と第 2 引き回し配線 17 が物理的・電気的に接続される。ポリシリコン膜 4 と信号線 9 との間には相互に直接接続はなく、画素電極層 12 を介してのみ間接的に電気的接続がされている。同様に、第 1 引き回し配線 16 と第 2 引き回し配線 17 との間には、相互に直接接続はなく、画素電極層 12 を介してのみ間接的に電気的接続がされている。

10

## 【0032】

すなわち、表示領域外の変換部 122 において、第 2 引き回し配線 17 とゲートレイヤにて形成される第 1 引き回し配線 16 とは、画素電極層 12 を介して接続される。また、表示領域内の TFT 部において、信号線 9 とポリシリコン膜 4 とは、画素電極層 12 を介して接続される。このように、信号線 9 は画素電極層 12 を介して TFT のポリシリコン膜 4 と接続される。したがって、層間絶縁膜 8 にコンタクトホールを形成するマスク工程を従来より少なくすることができ、かつ、画素表面上の平坦性が向上する。

20

## 【0033】

すなわち、信号線 9 及び第 2 引き回し配線 17 の直下にコンタクトホールを形成しないため、層間絶縁膜 8 成膜後、信号線 9 の形成前の、層間絶縁膜 8 をパターニングする写真製版工程を省くことができる。よって、写真製版工程に用いられるマスク数を削減することができる。これにより、生産性を向上させることができる。

## 【0034】

この場合、ポリシリコン膜 4 には、信号線 9 からの信号が画素電極層 12 を介して供給される。また、ポリシリコン膜 4 から直接画素電極に信号を供給することができる。このように、全ての信号線レイヤが、ポリシリコン膜 4 、ゲートレイヤと直接接続されていない。

30

## 【0035】

なお、信号線 9 の直下では、層間絶縁膜 8 が除去されていない。そのため、信号線レイヤの直下には、必ず層間絶縁膜 8 が形成されている。換言すると、信号線レイヤの全てが層間絶縁膜 8 が形成された領域上に配置される。すなわち、信号線レイヤが形成された領域の全てにおいて、信号線レイヤ直下に層間絶縁膜 8 が配置される。さらに、画素電極層 12 に含まれる画素電極の直下に信号線レイヤやそれにつながるコンタクトホールが配置されない構成とすることができる。よって、画素電極直下の層間絶縁膜 8 の平坦性を向上することができる。これにより、表示品位を向上することができる。

## 【0036】

また、図 2 (b) を用いて、表示装置の TFT 基板 110 上の額縁領域 112 に形成される保護回路 123 について説明する。保護回路 123 は、第 1 の半導体素子及び第 2 の半導体素子を有している。これらの半導体素子は、それぞれの抵抗値が非線形で変化する整流素子であり、例えば第 1 の半導体素子が n 型のトランジスタ (n-T r) であり、他方の第 2 の半導体素子が異なる導電型である p 型のトランジスタ (p-T r) である。この導電型は逆の関係であってもよく、具体的にはソースドレイン領域 7 に不純物を注入する際のイオン種によって作り分けられる。なお、これら第 1 の半導体素子と第 2 の半導体素子とは適宜置き換えて効果は同じである。

40

## 【0037】

第 1 の半導体素子のゲート電極及びドレイン電極が第 1 のショートリング (図示せず) に接続されていて、ソース電極がソース配線 153 又はゲート配線 182 に接続されている。すなわち、第 1 の半導体素子は、TFT 120 のゲートを、当該 TFT 120 のソース又はドレインに接続した 2 端子素子からなる。また、第 2 の半導体素子のゲート電極及

50

びドレイン電極が第2のショートリング(図示せず)に接続されていて、ソース電極がソース配線153又はゲート配線182に接続されている。すなわち、第2の半導体素子は、TFT120のゲートを、当該TFT120のソース又はドレインに接続した2端子素子からなる。なお、例えば、第1の半導体素子と第2の半導体素子は並列に接続される。第1の半導体素子が第1のショートリングに接続され、第2の半導体素子が第2のショートリングに接続されている。

【0038】

そして、これらショートリング間に電位差が生じた場合に応じて、第1の半導体素子と第2の半導体素子のどちらか一方が開いて瞬間に同電位となる。ここで、開くというのは、第1の半導体素子と第2の半導体素子のいずれか一方がONとなることであって、電位差はONとなった半導体素子を介して電荷が流れることにより解消されることになる。図2(b)においては、信号線9及び画素電極12を同電位とする場合を示している。例えば、信号線9の電位が画素電極12の電位より高い場合、pTrがONし、信号線9から画素電極12にキャリアである正孔が移動する。一方、信号線9の電位が画素電極12の電位より低い場合、nTrがONし、画素電極12から信号線9にキャリアである電子が移動する。さらに、例えば、画素電極層12がゲート電極15に接続されれば、ONとなった半導体素子を介して信号線9とゲート電極15が接続され、信号線9とゲート電極15の電位差を解消することができる。以上のように、導電型が互いに異なる半導体素子を組み合わせることにより、第1のショートリング又は第2のショートリングを介して、ソース配線153及びゲート配線182等に蓄積される静電気を逃がすことが可能である。なお、保護回路123は、TFT基板110の額縁領域112に形成され、第1の導電層と第2の導電層の間の絶縁破壊を防止する。これにより、ソース配線153及びゲート配線182を保護する。

10

20

30

【0039】

保護回路123の形成方法は上述の表示装置のTFT部及び変換部と同様である。ただし、図2(a)に示すように、保護膜10形成後、保護膜10及び層間絶縁膜8を貫通してゲート電極15に到達するコンタクトホール11を形成する。また、この工程で保護膜10、層間絶縁膜8、及びゲート絶縁膜5を貫通して、ポリシリコン膜4に到達するコンタクトホール11を形成する。その後、保護膜10上に画素電極層12を成膜する。画素電極層12は、コンタクトホール11に埋設される。そして、TFT基板110の額縁領域112に形成される保護回路123では、コンタクトホール11に埋設された画素電極層12を介してポリシリコン膜4とゲート電極15とが物理的・電気的に接続される。

【0040】

上述のように形成したTFT基板は、対向電極を備えた対向基板と貼り合わせ、その間に液晶を注入する。バックライトユニットである面状光源装置を背面側に載置し、液晶表示装置を製造する。また、本実施形態においては液晶表示装置に限定されるものではなく、有機ELディスプレイ等の表示装置や各種電子機器全般についても適用可能である。

【0041】

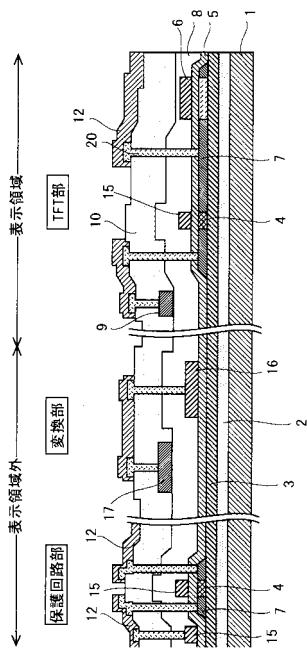

実施例2.

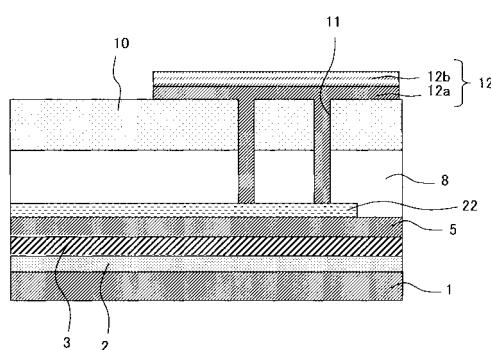

本発明の実施例2にかかるTFT基板について図3を参照して説明する。図3は、本実施例にかかるTFT基板を示す断面図である。本実施例において、実施例1と異なる点は、画素電極層12の構造のみであるため、詳細な説明は省略する。

40

【0042】

図3は、画素電極を二層以上の導電膜で形成した構造である。画素電極層12はITO膜などの透明導電膜、及びCr、Mo、Al、Ta、Tiなどのメタルもしくはこれらのメタルを主成分とする金属膜を有している。すなわち、本実施例では、画素電極層12が、下層導電膜12aと、上層導電層12bとを有する積層構造になっている。ここで、上層導電層12bは、メタル又はメタルを主成分とする合金によって形成され、下層導電膜12aは透明導電膜によって形成される。これにより、実施例1と同様に、生産性を向上することができ、かつ表示品位を向上することができる。さらに、積層構造とすることに

50

よって、第1引き回し配線16と第2引き回し配線17、及びポリシリコン膜4と信号線9との間の画素電極層12の抵抗を低減することができる。これにより、表示品位を向上することができる。画素電極層12を積層構造とすることにより、例えば、半透過型液晶表示装置を形成することができる。すなわち、画素内において、透過部では透明導電膜のみで画素電極を形成し、反射部では、メタル又は合金で画素電極を形成する。

#### 【0043】

また、実施例2においては、上層導電層12bがメタル又はメタルを主成分とする合金であり、下層導電膜12aが透明導電膜である構造について説明したが、この反対の構造であってもよい。すなわち、上層導電層12bは透明導電膜であり、下層導電膜12aがメタル又はメタルを主成分とする合金であってもよい。さらに、このメタルはCr、Mo、Ta、Ti等の高融点金属であってもよい。このような構造を用いることにより、上述の生産性向上や抵抗低減に加えてさらなる効果を奏するが、以下、この効果について詳細に説明する。

10

#### 【0044】

一般に、画素電極層に用いられるITOとポリシリコン膜のような半導体薄膜を直接コンタクトさせる構造においては、実質上n型半導体であるITOと半導体薄膜とのコンタクトとなることから、非オーム性接触となり、接触抵抗も高抵抗値を示すという問題があった。そのため、上記の構造を適用できるのは、例えば画素コンタクト部のようにデバイス性能上の影響が小さい箇所でしかなかった。ここで、上記のようにITOと半導体薄膜との間にCr、Mo、Ta、Ti等のメタルを介在させることにより、透明導電膜であるITO/メタル/半導体薄膜という構造が得られ、ITOと半導体薄膜間でオーム性接触かつ接触抵抗が低抵抗となる効果が得られるのである。すなわち、画素電極層12とポリシリコン膜4との間の接触抵抗を低減するという効果が得られるのである。

20

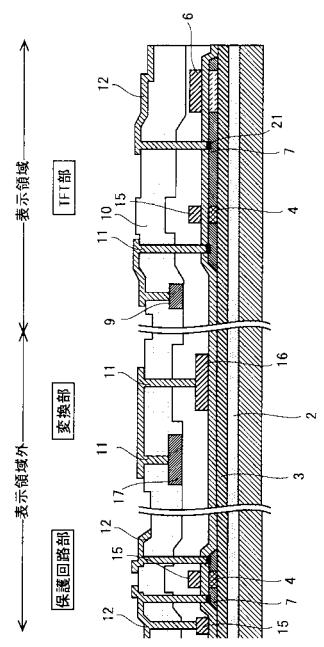

#### 【0045】

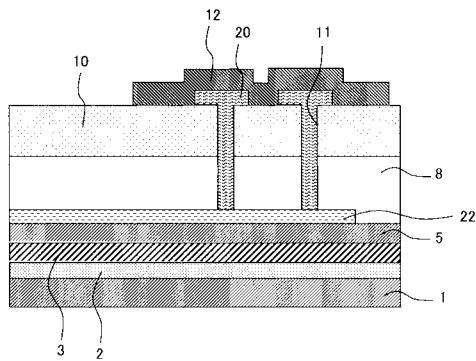

##### 実施例3.

本発明の実施例3にかかるTFT基板について図4を参照して説明する。図4は、本実施例にかかるTFT基板を示す断面図である。本実施例において、実施例1と異なる点は、画素電極がITO等の透明導電膜のときにコンタクトホール11にバリアメタル20を形成する点である。したがって、実施例1と共に通する内容については説明を省略する。また、バリアメタル20については、実施例2のメタルと同様、本実施例3においてもITOと半導体薄膜との接触抵抗を低減させる効果があるが、これについても説明を省略する。ここで、バリアメタル20は、例えば、コンタクトホール11に埋設されている。よって、バリアメタル20を介して、画素電極層12とポリシリコン膜4のソースドレイン領域7が接続されている。また、バリアメタル20を介して、画素電極層12と第1引き回し配線16が接続されている。さらに、バリアメタル20を介して、画素電極層12、信号線9、及び第2引き回し配線17が接続されている。この場合、バリアメタル20を形成することによって、ITOとその下層の信号線レイヤ、ゲートレイヤ又はポリシリコン膜4との接触抵抗を低減することができる。よって、表示品位をさらに向上させることができる。

30

#### 【0046】

なお、本実施例と実施例2とを組み合わせてもよい。また、バリアメタル20は保護膜10の形成後にコンタクトホール11を開口した後に形成され、また、バリアメタル20にはMo、Ti、Cr、W等を用いることができる。また、図4において、信号線9に接続されるバリアメタル20と、ソースドレイン領域7に接続されるバリアメタル20とは分離しているが、バリアメタル20を成膜後に両方がつながるようパターニングすることにより、信号線9とソースドレイン領域7とをバリアメタル20も介して接続してもよい。接続抵抗が低減し、特性が向上する効果が得られる。第1引き回し配線16と第2引き回し配線17との間についても同様である。

40

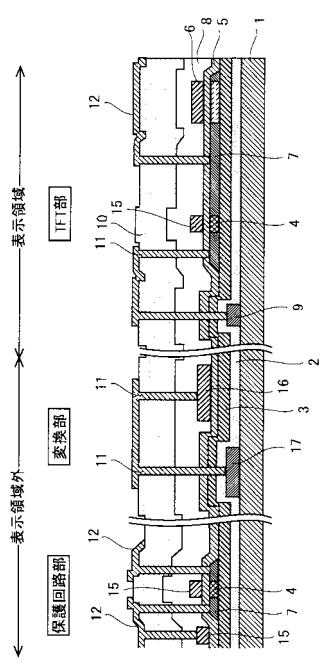

#### 【0047】

##### 実施例4.

50

本発明の実施例4にかかるTFT基板について図5を参照して説明する。図5は、本実施例にかかるTFT基板を示す断面図である。本実施例において、実施例1と異なる点は、画素電極形成前に少なくとも画素電極層12とポリシリコン膜4との接触部にシリサイド21を形成することである。したがって、実施例1と共に通する内容については説明を省略する。シリサイド21は、ポリシリコン膜4のソースドレイン領域7の表面に形成されている。ここで、画素電極層12がITO等の透明導電膜により構成されているとする。あるいは、画素電極層12の下層導電膜が透明導電膜により形成されているとする。この場合、シリサイド21を介して画素電極層12と、ポリシリコン膜4のソースドレイン領域7とが接続される。したがって、接続抵抗を低減することができ、表示品位をさらに向上させることができる。

10

## 【0048】

## 実施例5.

本発明の実施例5にかかるTFT基板について図6を参照して説明する。図6は、本実施例にかかるTFT基板を示す断面図である。本実施例において、実施例1と異なる点は、信号線9及び第2引き回し配線17が下地膜としての窒化シリコン膜2及び酸化シリコン膜3より下層に形成されていることである。したがって、実施例1と共に通する内容については説明を省略する。

20

## 【0049】

ここで窒化シリコン膜2の下には、信号線9及び第2引き回し配線17が形成されている。ここで、信号線9及び第2引き回し配線17のパターンの上では、窒化シリコン膜2、酸化シリコン膜3、ゲート絶縁膜5、層間絶縁膜8、及び保護膜10にコンタクトホール11が形成されている。このコンタクトホール11を介して、信号線9及び第2引き回し配線17と画素電極層12とが接続される。窒化シリコン膜2、及び酸化シリコン膜3を貫通して信号線9及び第2引き回し配線17まで到達するコンタクトホール11は、保護膜10の形成後に形成される。よって、1枚のフォトマスクで、窒化シリコン膜2、酸化シリコン膜3、ゲート絶縁膜5、層間絶縁膜8、及び保護膜10を貫通するコンタクトホール11が形成される。これにより、上記の実施例と同様の効果を得ることができる。なお、本実施例では、ガラス基板1上に、信号線9及び第2引き回し配線17、窒化シリコン膜2、酸化シリコン膜3を順次形成する。窒化シリコン膜2を形成する工程は、実施例1と同様であるため、説明を省略する。なお、本実施例では、信号線9及び第2引き回し配線17が窒化シリコン膜2の下に形成されるため、層間絶縁膜8形成工程と、保護膜10形成工程との間に、信号線9及び第2引き回し配線17を形成する工程を設ける必要が無い。また、下地膜には窒化シリコン膜2、酸化シリコン膜3以外の材料を用いてもよく、単層構造でもよい。

30

## 【0050】

## 実施例6.

本発明の実施例6にかかるTFT基板について図7を参照して説明する。図7は、TFT基板にボトムゲート型のTFTが形成されている。すなわち、ポリシリコン膜4の下層にゲート絶縁膜5及びキャパシタ電極が形成される。さらに、ゲート絶縁膜5の下層に、ゲート電極15、キャパシタ電極6、及び第1引き回し配線16が形成される。そして、ゲート電極15は、ポリシリコン膜4の下に配置される。この場合、ガラス基板1上に、ゲート電極15、ゲート絶縁膜5、及びポリシリコン膜4の順番で形成される。なお、これらの形成工程については、実施例1と同様であるため説明を省略する。

40

## 【0051】

## 実施例7.

本発明の実施例7にかかるTFT基板について図8を参照して説明する。実施例7では、信号線9及び第2引き回し配線17が形成されていない構成を有している。すなわち、層間絶縁膜8の形成後、保護膜10の形成前、あるいは、窒化シリコン膜2の形成前に信号線9及び第2引き回し配線17を形成していない。したがって、層間絶縁膜8と保護膜10との間、及び、窒化シリコン膜2の下に、信号線9及び第2引き回し配線17が配置

50

されていない。この工程では、信号線 9 及び第 2 引き回し配線 17 形成工程を省略することができるため、より生産性を向上することができる。

#### 【0052】

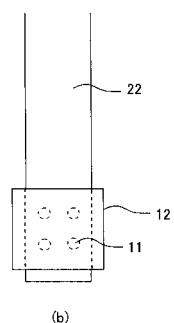

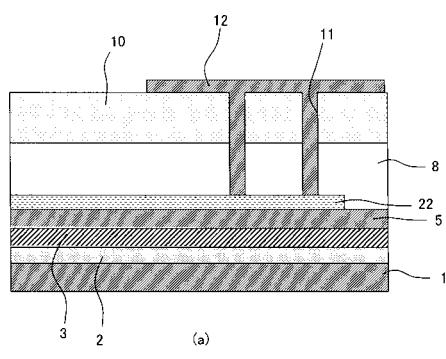

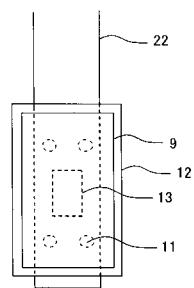

##### 実施例 8 .

本発明の実施例 8 にかかる TFT 基板について図 9 (a)、(b) を参照して説明する。実施例 8 では、図 1 に示す基板 110 の額縁領域 112 に形成され、走査信号駆動回路 115 又は表示信号駆動回路 116 のパッドと接続される端子部の構造について説明する。ここで、図 9 (a) は実施例 8 にかかる TFT 基板の端子部を示す断面図である。また、図 9 (b) は実施例 8 にかかる TFT 基板の端子部を示す平面図である。ここでは、複数の端子部のうち 1 つの端子部の構成について示す。また、図 9 (a) 及び (b) に示す実施例 8 において、実施例 1 と同一の構成要素についてはその説明を省略する。

10

#### 【0053】

図 9 (a) に示すように、ガラス基板 1 上にプラズマ CVD 法で下地膜となる窒化シリコン膜 2 及び酸化シリコン膜 3 を形成する。次に、TFT 120 では半導体層となるポリシリコン膜 4 を形成するが、実施例 8 にかかる端子部においては、このポリシリコン膜 4 はエッチングにより除去される。そして、酸化シリコン膜 3 上にプラズマ CVD 法を用いてゲート絶縁膜 5 を形成する。次に、スパッタ法により、例えば、Al、Cr、Mo、Ti、又は W 等や、これらに他の物質を微量に添加した合金などを用いて端子配線 22 となる金属薄膜を形成する。この金属薄膜上に写真製版法を用いてレジストパターンを形成する。そして、エッチング液で金属薄膜を所望の形状にパターニングし、金属薄膜上のレジストを除去する。これにより、端子配線 22 が形成される。ここで、TFT 120 では、端子配線 22 と同層にゲート電極 15、キャパシタ電極 6、及び第 1 引き回し配線 16 が形成される。また、ゲート電極 15、及びキャパシタ電極 6 をマスクにして、酸化シリコン膜 3 上に形成されたポリシリコン膜 4 に不純物が導入される。

20

#### 【0054】

プラズマ CVD 法により端子配線 22 上に層間絶縁膜 8 となる酸化シリコン膜を形成する。これにより、端子配線 22 が層間絶縁膜 8 で覆われる。この層間絶縁膜 8 は、TEOS と O<sub>2</sub> を反応させた酸化シリコン膜を膜厚 500 nm 形成したものである。なお、層間絶縁膜 8 の膜厚は 500 nm としたが、これに限定されるものではない。また、層間絶縁膜 8 は、酸化シリコン膜に限らず、窒化シリコン膜又は有機膜等でもよい。

30

#### 【0055】

ここで、TFT 120 では、ポリシリコン膜 4 中に導入した P (リン) や B (ボロン) を活性化させるため、熱処理を行う。次に、TFT 120 では、スパッタ法によりソースドレインメタルとなる信号線 9、及び変換部等では第 2 引き回し配線 17 を形成するが、端子部の構成である本実施例においては、信号線 9 は形成されない。

#### 【0056】

次に、層間絶縁膜 8 上にプラズマ CVD 法により保護膜 10 となる窒化シリコン膜を 300 nm 形成する。この保護膜 10 は、端子配線 22 の上方に配置される。また、保護膜 10 は、窒化シリコン膜に限らず、酸化シリコン膜や有機膜などの絶縁膜でもよい。ここで、TFT 120 におけるポリシリコン膜 4 のダメージ回復のため、熱処理を行う。

40

#### 【0057】

保護膜 10 形成後、保護膜 10 及び層間絶縁膜 8 を貫通して端子配線 22 に到達するコンタクトホール 11 を形成する。このとき、変換部等では、保護膜 10 及び層間絶縁膜 8 を貫通して、第 1 引き回し配線 16 に到達するコンタクトホール 11 が形成される。さらに、TFT 120 では、保護膜 10、層間絶縁膜 8、及びゲート絶縁膜 5 を貫通してポリシリコン膜 4 のソースドレイン領域 7 に到達するコンタクトホール 11 が形成される。具体的には、フォトリソグラフィー法によって保護膜 10 上にレジストパターンを形成する。そして、保護膜 10、層間絶縁膜 8、及びゲート絶縁膜 5 を順番にドライエッチングする。これにより、コンタクトホール 11 が形成される。一つのフォトマスクで、保護膜 10、層間絶縁膜 8、及びゲート絶縁膜 5 を貫通するコンタクトホール 11 を形成すること

50

ができる。ここでは、1つの端子部に4つのコンタクトホール11が形成される。

【0058】

コンタクトホール11形成後、画素電極層12を成膜する。そして、画素電極層12をフォトリソグラフィー法などによってパターニングする。画素電極層12はITO膜などの透明導電膜により形成することができる。あるいは、画素電極層12をCr、Mo、Al、Ta、Tiなどのメタルもしくはこれらのメタルを主成分とする合金によって形成することも可能である。この画素電極層12はITO膜などの透明導電膜により形成することができる。あるいは、画素電極層12をCr、Mo、Al、Ta、Tiなどのメタル、もしくはこれらのメタルを主成分とする合金によって形成することも可能である。この画素電極層12はコンタクトホール11に埋設される。これにより、端子配線22と画素電極層12とが物理的・電気的に接続される。このとき、TFT120では、液晶を駆動するための駆動電圧(表示電圧)が印加される画素電極などが形成される。

10

【0059】

実施例8において、端子配線22と画素電極層12は1回のコンタクトホール形成により接続することが可能となる。すなわち、従来コンタクトホール11は、層間絶縁膜8、保護膜10の各々に対して形成工程を有し、各々のコンタクトホールは基板表面上の異なる位置に形成されていたが、本実施例においては層間絶縁膜8及び保護膜10の各々に形成されるコンタクトホール11を一括して形成する。これにより、コンタクトホール11を基板表面上に配置する領域を縮小することが可能となる。よって、額縁領域112の面積を縮小することが可能となる。

20

【0060】

実施例9.

本発明の実施例9にかかるTFT基板について図10を参照して説明する。実施例10では、実施例2に示したTFT120と同一基板上に形成された端子部の構造について説明する。図10は、本実施例にかかるTFT基板の端子部を示す断面図である。また、本実施例において、実施例8で示した端子部と異なる点は、画素電極層12の構造のみであるため、詳細な説明は省略する。

30

【0061】

図10は、画素電極を二層以上の導電膜で形成した構造である。画素電極層12はITO膜などの透明導電膜、及びCr、Mo、Al、Ta、Tiなどのメタルもしくはこれらのメタルを主成分とする金属膜を有している。すなわち、本実施例では、画素電極層12が下層導電膜12aと、上層導電層12bとを有する積層構造となっている。ここで、上層導電層12bは、メタル又はメタルを主成分とする合金によって形成され、下層導電膜12aは透明導電膜によって形成される。これにより、生産性を向上することができ、かつ表示品位を向上することができる。上記の構成は、透過型液晶表示装置及び反射型液晶表示装置に好適である。

【0062】

実施例10.

本発明の実施例10にかかるTFT基板について図11を参照して説明する。実施例10では、実施例3に示したTFT120と同一基板上に形成された端子部の構造について説明する。図11は、本実施例にかかるTFT基板を示す断面図である。また、本実施例において、実施例8と異なる点は、画素電極がITO等の透明導電膜のときにコンタクトホール11にバリアメタル20を形成する点である。したがって、実施例8と共に通する内容については説明を省略する。

40

【0063】

ここで、バリアメタル20は、例えば、コンタクトホール11に埋設されている。よって、バリアメタル20を介して画素電極層12と端子配線22が接続されている。この場合、バリアメタル20を形成することによって、例えば、TFT120ではITOとその下層の信号線レイヤ、ゲートレイヤ、又はポリシリコン膜4との接触抵抗を低減することができる。また、変換部ではITOとその下層の信号線レイヤ、ゲートレイヤ、又はポリ

50

シリコン膜4との接触抵抗を低減することができる。よって、表示品位をさらに向上させることができる。

【0064】

なお、本実施例を実施例9と組み合わせてもよい。また、バリアメタル20は保護膜10の形成後にコンタクトホール11を開口した後に形成され、また、バリアメタル20には、Mo、Ti、Cr、W等を用いることができる。

【0065】

実施例11。

本発明の実施例11にかかるTFT基板について説明する。実施例11は、実施例4に示したTFT120と同一基板上に形成された端子部の構造について説明する。本実施例において、実施例8と異なる点は、TFT120において画素電極形成前に画素電極層12とポリシリコン膜4との少なくとも接触部においてシリサイド21を形成することである。したがって、端子部に限っては実施例8と同じ構造となるため、詳細な説明を省略する。すなわち、実施例11において、実施例4に示したTFT120と、実施例8に示した端子部を有する。

10

【0066】

実施例12。

本発明の実施例12にかかるTFT基板について説明する。実施例12は、実施例5に示したTFT120と同一基板上に形成された端子部の構造について説明する。本実施例において、実施例8と異なる点は、信号線9及び第2引き回し配線17が下地膜としての窒化シリコン膜2及び酸化シリコン膜3より下層に形成されていることである。したがって、端子部に限っては実施例8と同じ構造となるため、詳細な説明を省略する。すなわち、実施例12において、実施例3に示したTFT120と、実施例8に示した端子部を有する。

20

【0067】

上記実施例の製造方法で作成されたTFT基板は、1回の工程でコンタクトホールを形成することができ、マスク工数を少なくとも一回減らすことができる。この場合、信号線下にはコンタクトホールが形成されず、最上部の画素電極表面の平坦性が向上する。なお、上記の実施例1～12では、キャパシタ電極6をゲート電極15と同じ導電層によって形成したが、信号線9と同じ層で形成することも可能である。さらに、実施例1～12を適宜組み合わせてもよい。

30

【0068】

本発明の実施の形態1～12で示されたTFTアレイ基板は生産性が高く、表示装置に用いるのに好適である。より具体的には、表示装置の表示領域内において信号配線と走査線とが交差し、その交差付近にTFTを配置してなるアクティブマトリクス型アレイ基板を備えた表示装置に用いることが可能である。

30

【0069】

たとえば、アレイ基板とカラーフィルタとをシール材を介して貼りあわせ、その内部に液晶材料を封入することにより形成される液晶表示装置に適用することが可能である。また、表示領域だけでなく表示領域の周辺に位置する駆動回路のTFTにも適用してもよく、その場合は表示領域内のTFTと同時に形成することができる。その他、本発明は上述した実施の形態のみに限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能であることは勿論である。

40

【図面の簡単な説明】

【0070】

【図1】TFT基板の構成を示す平面図である。

【図2】(a)実施例1にかかるTFT基板のTFT部及び変換部の構成を示す断面図である。(b)実施例1にかかるTFT基板の保護回路の構成を示す平面図である。

【図3】実施例2にかかるTFT基板の構成を示す断面図である。

【図4】実施例3にかかるTFT基板の構成を示す断面図である。

50

【図5】実施例4にかかるTFT基板の構成を示す断面図である。

【図6】実施例5にかかるTFT基板の構成を示す断面図である。

【図7】実施例6にかかるTFT基板の構成を示す断面図である。

【図8】実施例7にかかるTFT基板の構成を示す断面図である。

【図9】(a)実施例8にかかるTFT基板の構成を示す断面図である。(b)実施例8にかかるTFT基板の構成を示す平面図である。

【図10】実施例9にかかるTFT基板の構成を示す断面図である。

【図11】実施例10にかかるTFT基板の構成を示す断面図である。

【図12】従来のTFT基板の構成を示す断面図である。

【図13】(a)従来のTFT基板の構成を示す断面図である。(b)従来のTFT基板の構成を示す平面図である。 10

【符号の説明】

【0071】

1 ガラス基板、2 窒化シリコン膜、3 酸化シリコン膜、

4 ポリシリコン膜、5 ゲート絶縁膜、6 キヤパシタ電極、

7 ソースドレイン領域、8 層間絶縁膜、9 信号線、

10 保護膜、11 コンタクトホール、12 画素電極層、

12a 下層導電膜、12b 上層導電層、13 スルーホール、

15 ゲート電極、16 第1引き回し配線、17 第2引き回し配線、

20 バリアメタル、21 シリサイド、22 端子配線

110 基板、111 表示領域、112 額縁領域、

115 走査信号駆動回路、116 表示信号駆動回路、

117 画素、118、119 外部配線、

120 TFT、121 引き回し配線、122 変換部、123 保護回路、

153 ソース配線、182 ゲート配線

【図1】

【図2】

【 図 3 】

【 図 4 】

【図5】

【 図 6 】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

(b)

## フロントページの続き

| (51) Int.CI.   |               | F I              | テーマコード(参考)                          |

|----------------|---------------|------------------|-------------------------------------|

| <i>H 0 1 L</i> | <i>29/49</i>  | <i>(2006.01)</i> | <i>H 0 1 L</i> 21/28 <i>L</i>       |

| <i>G 0 2 F</i> | <i>1/136</i>  | <i>(2006.01)</i> | <i>H 0 1 L</i> 21/28 <i>3 0 1 R</i> |

| <i>G 0 2 F</i> | <i>1/1368</i> | <i>(2006.01)</i> | <i>H 0 1 L</i> 29/50 <i>M</i>       |

|                |               |                  | <i>H 0 1 L</i> 29/58 <i>G</i>       |

|                |               |                  | <i>G 0 2 F</i> 1/136                |

|                |               |                  | <i>G 0 2 F</i> 1/1368               |

F ターム(参考) 2H092 GA12 GA29 GA32 GA40 GA59 HA02 HA06 HA12 HA19 JA24

JA41 JA46 JB56 KB04 KB25 MA14 MA18 MA37 NA25 NA27

PA06

4M104 AA01 AA09 BB02 BB14 BB16 BB18 BB36 CC01 CC05 DD08

DD37 DD64 DD78 FF18 GG10 GG14 GG19 HH20

5C094 AA02 AA31 AA42 AA43 BA03 BA43 CA19 DA13 DA15 DB10

EA04 EA10 FB12 GB10

5F110 AA03 AA16 AA22 BB02 BB04 CC02 DD02 DD13 DD14 DD17

EE03 EE04 EE06 EE44 FF02 FF30 GG02 GG13 GG25 GG45

HJ01 HJ12 HJ13 HJ23 HL03 HL04 HL06 HL07 HL11 HL12

HL23 HM15 HM17 HM19 NN04 NN23 NN24 NN27 NN35 NN73

PP03 PP35 QQ11