(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2016-0090470

(43) 공개일자 2016년08월01일

(51) 국제특허분류(Int. Cl.)

*G09G 3/20* (2006.01) *G09G 3/32* (2016.01)

*G09G 3/36* (2006.01)

(52) CPC특허분류

*G09G 3/20* (2013.01)

*G09G 3/3225* (2013.01)

(21) 출원번호 10-2015-0010221

(22) 출원일자 2015년01월21일

심사청구일자 없음

(71) 출원인

삼성디스플레이 주식회사

경기도 용인시 기흥구 삼성로 1 (농서동)

(72) 발명자

조덕한

서울특별시 강남구 개포로31길 15-4 202호 (개포동)

김범준

서울특별시 용산구 백범로90길 74 103-807

(뒷면에 계속)

(74) 대리인

특허법인 고려

전체 청구항 수 : 총 20 항

(54) 발명의 명칭 게이트 구동회로

### (57) 요 약

게이트 구동회로의 구동 스테이지들 각각은 제1 출력 트랜지스터, 커패시터, 제1 제어 트랜지스터, 및 제2 제어 트랜지스터를 포함한다. 상기 제1 출력 트랜지스터는 제1 노드에 접속된 제어전극을 포함한다. 상기 제1 제어 트랜지스터는 상기 k번째 게이트 신호가 출력되기 이전에, 상기 제1 노드의 전위를 제어하는 제1 제어 신호를 제2 노드에 출력한다. 상기 제2 제어 트랜지스터는 상기 제2 노드로부터 상기 제1 노드로 전류패스가 형성되도록 상기 제2 노드와 상기 제1 노드 사이에 다이오드 접속된다. 상기 제2 노드에 상기 제1 제어 신호가 인가된 이후에, 상기 제2 노드에 상기 k번째 게이트 신호와 동기된 제2 제어 신호가 인가된다.

### 대 표 도

(52) CPC특허분류

**G09G 3/3648** (2013.01)

(72) 발명자

**김윤호**

충청남도 아산시 배방읍 호서로 460 배방자이 1차

110동 1105호

**타케우치, 노보루**

충청남도 아산시 배방읍 광장로 210 111동 2505호

**김강남**

충청남도 아산시 탕정면 삼성로 261 청옥동 1304

호 (명암리, 삼성크리스탈기숙사)

## 명세서

### 청구범위

#### 청구항 1

표시패널의 게이트 라인들에 게이트 신호들을 제공하는 구동 스테이지들을 포함하는 게이트 구동회로에 있어서, 상기 구동 스테이지들 중  $k$ 번째(여기서  $k$ 는 2 이상의 자연수) 구동 스테이지는,

제1 노드에 접속된 제어전극, 클럭 신호를 수신하는 입력전극, 상기 클럭 신호에 근거하여 생성된  $k$ 번째 게이트 신호를 출력하는 출력전극을 포함하는 제1 출력 트랜지스터;

상기 제1 출력 트랜지스터의 상기 출력전극과 상기 제1 출력 트랜지스터의 상기 제어전극 사이에 접속된 커패시터;

상기  $k$ 번째 게이트 신호가 출력되기 이전에, 상기 제1 노드의 전위를 제어하는 제1 제어 신호를 제2 노드에 출력하는 제1 제어 트랜지스터; 및

상기 제2 노드로부터 상기 제1 노드로 전류패스가 형성되도록 상기 제2 노드와 상기 제1 노드 사이에 다이오드 접속된 제2 제어 트랜지스터를 포함하고,

상기 제2 노드에 상기 제1 제어 신호가 인가된 이후에, 상기 제2 노드에 상기  $k$ 번째 게이트 신호와 동기된 제2 제어 신호가 인가되는 것을 특징으로 하는 게이트 구동회로.

#### 청구항 2

제1 항에 있어서,

상기 제1 제어 트랜지스터는  $k-1$ 번째 구동 스테이지로부터 출력된 신호를 공통으로 수신하는 제어전극 및 입력 전극, 및 상기 제1 제어 신호를 출력하는 출력전극을 포함하는 것을 특징으로 하는 게이트 구동회로.

#### 청구항 3

제2 항에 있어서,

상기  $k-1$ 번째 구동 스테이지로부터 출력된 신호는  $k-1$ 번째 캐리 신호인 것을 특징으로 하는 게이트 구동회로.

#### 청구항 4

제1 항에 있어서,

상기 제1 제어 트랜지스터는  $k-1$ 번째 구동 스테이지로부터 출력된 신호를 수신하는 제어전극, 바이어스 전압을 수신하는 입력전극, 및 상기 제1 제어 신호를 출력하는 출력전극을 포함하는 것을 특징으로 하는 게이트 구동회로.

#### 청구항 5

제4 항에 있어서,

상기  $k-1$ 번째 구동 스테이지로부터 출력된 신호는  $k-1$ 번째 캐리 신호이고,

상기 바이어스 전압은 상기  $k-1$ 번째 캐리 신호의 하이레벨과 실질적으로 동일한 것을 특징으로 하는 게이트 구동회로.

#### 청구항 6

제1 항에 있어서,

상기 제1 노드에 접속된 제어전극, 상기 클럭 신호를 수신하는 입력전극, 상기 클럭 신호에 근거하여 생성된  $k$ 번째 캐리 신호를 출력하는 출력전극을 포함하는 제2 출력 트랜지스터를 더 포함하는 것을 특징으로 하는 게이트 구동회로.

**청구항 7**

제6 항에 있어서,

상기 제2 제어 신호는 상기 k번째 캐리 신호인 것을 특징으로 하는 게이트 구동회로.

**청구항 8**

제6 항에 있어서,

상기 k번째 캐리 신호를 공통으로 수신하는 제어전극 및 입력전극, 및 상기 제2 제어 신호를 출력하는 제3 제어 트랜지스터를 더 포함하는 게이트 구동회로.

**청구항 9**

제1 항에 있어서,

상기 k번째 게이트 신호가 출력된 이후에, 상기 제1 출력 트랜지스터가 턴-오프되도록 상기 제1 노드에 방전 전압(VSS2)을 제공하는 제4 제어 트랜지스터를 더 포함하는 것을 특징으로 하는 게이트 구동회로.

**청구항 10**

제9 항에 있어서,

상기 k번째 게이트 신호가 출력된 이후에, 상기 제2 노드에 상기 방전 전압(VSS2)을 제공하는 제5 제어 트랜지스터를 더 포함하는 것을 특징으로 하는 게이트 구동회로.

**청구항 11**

제10 항에 있어서,

상기 제5 제어 트랜지스터는 스위칭 신호를 수신하는 제어전극, 상기 방전 전압을 수신하는 입력전극, 및 상기 제2 노드에 접속된 출력전극을 포함하고,

상기 스위칭 신호는 k+1번째 구동 스테이지로부터 출력된 k+1번째 캐리 신호인 것을 특징으로 하는 게이트 구동회로.

**청구항 12**

표시패널의 게이트 라인들에 게이트 신호들을 제공하는 구동 스테이지들을 포함하는 게이트 구동회로에 있어서, 상기 구동 스테이지들 중 k번째(여기서 k는 2 이상의 자연수) 구동 스테이지는,

제1 노드의 전압에 응답하여, 클럭 신호에 근거하여 생성된 k번째 게이트 신호 및 k번째 캐리 신호를 출력하는 출력부;

상기 제1 노드의 전압을 제어하는 제어부;

상기 클럭 신호에 근거하여 생성된 스위칭 신호를 출력하는 인버터부; 및

상기 k번째 게이트 신호 및 상기 k번째 캐리 신호가 출력된 이후에, 상기 출력부의 전압을 다운시키는 풀다운부를 포함하고,

상기 제어부는,

상기 k번째 게이트 신호가 출력되기 이전에, 상기 제1 노드의 전위를 제어하는 제1 제어 신호를 제2 노드에 출력하는 제1 제어 트랜지스터;

상기 제2 노드에 공통으로 접속된 제어전극 및 입력전극, 및 상기 제1 노드에 접속된 출력전극을 포함하는 제2 제어 트랜지스터; 및

상기 k번째 캐리 신호를 공통으로 수신하는 제어전극 및 입력전극, 및 상기 제2 노드에 접속된 출력전극을 포함하는 제3 제어 트랜지스터를 포함하는 게이트 구동회로.

### 청구항 13

제12 항에 있어서,

상기 제1 제어 트랜지스터는 k-1번째 구동 스테이지로부터 출력된 k-1번째 캐리 신호를 공통으로 수신하는 제어 전극 및 입력전극, 및 상기 제1 제어 신호를 출력하는 출력전극을 포함하는 것을 특징으로 하는 게이트 구동회로.

### 청구항 14

제12 항에 있어서,

상기 제1 제어 트랜지스터는 k-1번째 구동 스테이지로부터 출력된 k-1번째 캐리 신호를 수신하는 제어전극, 상기 k-1번째 캐리 신호의 하이레벨과 실질적으로 동일한 레벨의 바이어스 전압을 수신하는 입력전극, 및 상기 제1 제어 신호를 출력하는 출력전극을 포함하는 것을 특징으로 하는 게이트 구동회로.

### 청구항 15

제12 항에 있어서,

상기 제어부는,

상기 k번째 게이트 신호에 응답하여 상기 제1 노드의 전압을 부스팅하는 커패시터;

상기 k번째 게이트 신호가 출력된 이후에, k+1번째 구동 스테이지로부터 출력된 k+1번째 캐리 신호에 응답하여 상기 제1 노드에 방전 전압(VSS2)을 제공하는 제4 제어 트랜지스터; 및

상기 제4 제어 트랜지스터로부터 상기 제1 노드에 상기 방전 전압(VSS2)이 제공된 이후에, 상기 스위칭 신호에 응답하여 상기 제1 노드에 상기 방전 전압(VSS2)을 제공하는 제5 제어 트랜지스터를 더 포함하는 것을 특징으로 하는 게이트 구동회로.

### 청구항 16

제15 항에 있어서,

상기 제어부는,

상기 k번째 게이트 신호가 출력된 이후에, 상기 k+1번째 구동 스테이지로부터 출력된 k+1번째 캐리 신호에 응답하여 상기 제2 노드에 상기 방전 전압(VSS2)을 제공하는 제6 제어 트랜지스터를 더 포함하는 것을 특징으로 하는 게이트 구동회로.

### 청구항 17

제12 항에 있어서,

상기 출력부는,

상기 k번째 게이트 신호를 출력하는 제1 출력 트랜지스터; 및

상기 k번째 캐리 신호를 출력하는 제2 출력 트랜지스터를 포함하는 것을 특징으로 하는 게이트 구동회로.

### 청구항 18

제17 항에 있어서,

상기 풀다운부는,

상기 k번째 게이트 신호가 출력된 이후에, 상기 제1 출력 트랜지스터의 출력 전극을 다운시키는 제1 풀다운부; 및

상기 k번째 캐리 신호가 출력된 이후에, 상기 제2 출력 트랜지스터의 출력 전극을 다운시키는 제2 풀다운부를 포함하는 것을 특징으로 하는 게이트 구동회로.

## 청구항 19

제18 항에 있어서,

상기 제1 풀다운부는,

k+1번째 구동 스테이지로부터 출력된 k+1번째 캐리 신호에 응답하여 상기 제1 출력 트랜지스터의 상기 출력 전극에 제1 방전 전압(VSS1)을 제공하는 제1 풀다운 트랜지스터; 및

상기 제1 풀다운 트랜지스터로부터 상기 제1 출력 트랜지스터의 상기 출력 전극에 상기 제1 방전 전압(VSS1)이 제공된 이후에, 상기 스위칭 신호에 응답하여 상기 제1 출력 트랜지스터의 상기 출력 전극에 상기 제1 방전 전압(VSS1)을 제공하는 제2 풀다운 트랜지스터를 포함하는 것을 특징으로 하는 게이트 구동회로.

## 청구항 20

제19 항에 있어서,

상기 제2 풀다운부는,

상기 k+1번째 구동 스테이지로부터 출력된 상기 k+1번째 캐리 신호에 응답하여 상기 제2 출력 트랜지스터의 상기 출력 전극에 제2 방전 전압(VSS2)을 제공하는 제3 풀다운 트랜지스터; 및

상기 제3 풀다운 트랜지스터로부터 상기 제2 출력 트랜지스터의 상기 출력 전극에 상기 제2 방전 전압(VSS2)이 제공된 이후에, 상기 스위칭 신호에 응답하여 상기 제2 출력 트랜지스터의 상기 출력 전극에 상기 제2 방전 전압(VSS2)을 제공하는 제4 풀다운 트랜지스터를 포함하고,

상기 제2 방전 전압(VSS2)은 상기 제1 방전 전압(VSS1)보다 낮은 바이어스 전압인 것을 특징으로 하는 게이트 구동회로.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 게이트 구동회로에 관한 것으로, 좀더 상세하게는 표시패널에 접적된(integrated) 게이트 구동회로에 관한 것이다.

### 배경 기술

[0002]

표시장치는 복수 개의 게이트 라인들, 복수 개의 데이터 라인들, 상기 복수 개의 게이트 라인들과 상기 복수 개의 데이터 라인들에 연결된 복수 개의 화소들을 포함한다. 상기 표시장치는 상기 복수 개의 게이트 라인들에 게이트 신호들을 제공하는 게이트 구동회로 및 상기 복수 개의 데이터 라인들에 데이터 신호들을 출력하는 데이터 구동회로를 포함한다.

[0003]

상기 게이트 구동회로는 복수 개의 구동 스테이지 회로들(이하, 구동 스테이지들)을 포함하는 쉬프트 레지스터를 포함한다. 상기 복수 개의 구동 스테이지들은 상기 복수 개의 게이트 라인들에 대응하는 게이트 신호를 각각 출력한다. 상기 복수 개의 구동 스테이지들 각각은 유기적으로 연결된 복수 개의 트랜지스터들을 포함한다.

## 발명의 내용

### 해결하려는 과제

[0004]

본 발명은 불량률이 감소된 게이트 구동회로를 제공하는 것을 목적으로 한다.

### 과제의 해결 수단

[0005]

본 발명의 실시 예에 따른 게이트 구동회로는 표시패널의 게이트 라인들에 게이트 신호들을 제공하는 구동 스테이지들을 포함한다. 상기 구동 스테이지들 중 k번째(여기서 k는 2 이상의 자연수) 구동 스테이지는 제1 출력 트랜지스터, 커패시터, 제1 제어 트랜지스터, 및 제2 제어 트랜지스터를 포함한다.

[0006]

상기 제1 출력 트랜지스터는 제1 노드에 접속된 제어전극, 클럭 신호를 수신하는 입력전극, 상기 클럭 신호에 근거하여 생성된 k번째 게이트 신호를 출력하는 출력전극을 포함한다. 상기 커패시터는 상기 제1 출력 트랜지스

터의 상기 출력전극과 상기 제1 출력 트랜지스터의 상기 제어전극 사이에 접속된다. 상기 제1 제어 트랜지스터는 상기 k번째 게이트 신호가 출력되기 이전에, 상기 제1 노드의 전위를 제어하는 제1 제어 신호를 제2 노드에 출력한다. 상기 제2 제어 트랜지스터는 상기 제2 노드로부터 상기 제1 노드로 전류패스가 형성되도록 상기 제2 노드와 상기 제1 노드 사이에 다이오드 접속된다. 상기 제2 노드에 상기 제1 제어 신호가 인가된 이후에, 상기 제2 노드에 상기 k번째 게이트 신호와 동기된 제2 제어 신호가 인가된다.

[0007] 상기 제1 제어 트랜지스터는 k-1번째 구동 스테이지로부터 출력된 신호를 공통으로 수신하는 제어전극 및 입력전극, 및 상기 제1 제어 신호를 출력하는 출력전극을 포함할 수 있다.

[0008] 상기 k-1번째 구동 스테이지로부터 출력된 신호는 k-1번째 캐리 신호일 수 있다.

[0009] 상기 제1 제어 트랜지스터는 k-1번째 구동 스테이지로부터 출력된 신호를 수신하는 제어전극, 바이어스 전압을 수신하는 입력전극, 및 상기 제1 제어 신호를 출력하는 출력전극을 포함할 수 있다.

[0010] 상기 k-1번째 구동 스테이지로부터 출력된 신호는 k-1번째 캐리 신호일 수 있다. 상기 바이어스 전압은 상기 k-1번째 캐리 신호의 하이레벨과 실질적으로 동일할 수 있다.

[0011] 상기 제1 노드에 접속된 제어전극, 상기 클럭 신호를 수신하는 입력전극, 상기 클럭 신호에 근거하여 생성된 k 번째 캐리 신호를 출력하는 출력전극을 포함하는 제2 출력 트랜지스터를 더 포함할 수 있다. 상기 제2 제어 신호는 상기 k번째 캐리 신호일 수 있다.

[0012] 상기 k번째 캐리 신호를 공통으로 수신하는 제어전극 및 입력전극, 및 상기 제2 제어 신호를 출력하는 제3 제어 트랜지스터를 더 포함할 수 있다.

[0013] 상기 k번째 게이트 신호가 출력된 이후에, 상기 제1 출력 트랜지스터가 턴-오프되도록 상기 제1 노드에 방전 전압(VSS2)을 제공하는 제4 제어 트랜지스터를 더 포함할 수 있다.

[0014] 상기 k번째 게이트 신호가 출력된 이후에, 상기 제2 노드에 상기 방전 전압(VSS2)을 제공하는 제5 제어 트랜지스터를 더 포함할 수 있다.

[0015] 상기 제5 제어 트랜지스터는 스위칭 신호를 수신하는 제어전극, 상기 방전 전압을 수신하는 입력전극, 및 상기 제2 노드에 접속된 출력전극을 포함할 수 있다. 상기 스위칭 신호는 상기 k+1번째 구동 스테이지로부터 출력된 k+1번째 캐리 신호일 수 있다.

[0016] 본 발명의 실시 예에 따른 게이트 구동회로는 표시패널의 게이트 라인들에 게이트 신호들을 제공하는 구동 스테이지들을 포함할 수 있다. 상기 구동 스테이지들 중 k번째(여기서 k는 2 이상의 자연수) 구동 스테이지는 출력부, 제어부, 인버터부, 및 풀다운부를 포함한다.

[0017] 상기 출력부는 제1 노드의 전압에 응답하여, 클럭 신호에 근거하여 생성된 k번째 게이트 신호 및 k번째 캐리 신호를 출력한다. 상기 제어부는 상기 제1 노드의 전압을 제어한다. 상기 인버터부는 상기 클럭 신호에 근거하여 생성된 스위칭 신호를 출력한다. 상기 풀다운부는 상기 k번째 게이트 신호 및 상기 k번째 캐리 신호가 출력된 이후에, 상기 출력부의 전압을 다운시킨다.

[0018] 상기 제어부는 상기 k번째 게이트 신호가 출력되기 이전에, 상기 제1 노드의 전위를 제어하는 제1 제어 신호를 제2 노드에 출력하는 제1 제어 트랜지스터, 상기 제2 노드에 공통으로 접속된 제어전극 및 입력전극, 및 상기 제1 노드에 접속된 출력전극을 포함하는 제2 제어 트랜지스터, 및 상기 k번째 캐리 신호를 공통으로 수신하는 제어전극 및 입력전극, 및 상기 제2 노드에 접속된 출력전극을 포함하는 제3 제어 트랜지스터를 포함한다.

[0019] 상기 제1 제어 트랜지스터는 k-1번째 구동 스테이지로부터 출력된 k-1번째 캐리 신호를 공통으로 수신하는 제어전극 및 입력전극, 및 상기 제1 제어 신호를 출력하는 출력전극을 포함할 수 있다.

[0020] 상기 제1 제어 트랜지스터는 k-1번째 구동 스테이지로부터 출력된 k-1번째 캐리 신호를 수신하는 제어전극, 상기 k-1번째 캐리 신호의 하이레벨과 실질적으로 동일한 레벨의 바이어스 전압을 수신하는 입력전극, 및 상기 제1 제어 신호를 출력하는 출력전극을 포함할 수 있다.

[0021] 상기 제어부는 상기 k번째 게이트 신호에 응답하여 상기 제1 노드의 전압을 부스팅하는 커패시터, 상기 k번째 게이트 신호가 출력된 이후에, k+1번째 구동 스테이지로부터 출력된 k+1번째 캐리 신호에 응답하여 상기 제1 노드에 방전 전압(VSS2)을 제공하는 제4 제어 트랜지스터, 및 상기 제4 제어 트랜지스터로부터 상기 제1 노드에 상기 방전 전압(VSS2)이 제공된 이후에, 상기 스위칭 신호에 응답하여 상기 제1 노드에 상기 방전 전압(VSS2)을

제공하는 제5 제어 트랜지스터를 더 포함할 수 있다.

[0022] 상기 제어부는 상기 k번째 게이트 신호가 출력된 이후에, 상기 k+1번째 구동 스테이지로부터 출력된 k+1번째 캐리 신호에 응답하여 상기 제2 노드에 상기 방전 전압(VSS2)을 제공하는 제6 제어 트랜지스터를 더 포함할 수 있다.

[0023] 상기 출력부는 상기 k번째 게이트 신호를 출력하는 제1 출력 트랜지스터, 및 상기 k번째 캐리 신호를 출력하는 제2 출력 트랜지스터를 포함할 수 있다.

[0024] 상기 풀다운부는 상기 k번째 게이트 신호가 출력된 이후에, 상기 제1 출력 트랜지스터의 출력 전극을 다운시키는 제1 풀다운부, 및 상기 k번째 캐리 신호가 출력된 이후에, 상기 제2 출력 트랜지스터의 출력 전극을 다운시키는 제2 풀다운부를 포함할 수 있다.

[0025] 상기 제1 풀다운부는 k+1번째 구동 스테이지로부터 출력된 k+1번째 캐리 신호에 응답하여 상기 제1 출력 트랜지스터의 상기 출력 전극에 제1 방전 전압(VSS1)을 제공하는 제1 풀다운 트랜지스터, 및 상기 제1 풀다운 트랜지스터로부터 상기 제1 출력 트랜지스터의 상기 출력 전극에 상기 제1 방전 전압(VSS1)이 제공된 이후에, 상기 스위칭 신호에 응답하여 상기 제1 출력 트랜지스터의 상기 출력 전극에 상기 제1 방전 전압(VSS1)을 제공하는 제2 풀다운 트랜지스터를 포함할 수 있다.

[0026] 상기 제2 풀다운부는 상기 k+1번째 구동 스테이지로부터 출력된 상기 k+1번째 캐리 신호에 응답하여 상기 제2 출력 트랜지스터의 상기 출력 전극에 제2 방전 전압(VSS2)을 제공하는 제3 풀다운 트랜지스터 및 상기 제3 풀다운 트랜지스터로부터 상기 제2 출력 트랜지스터의 상기 출력 전극에 상기 제2 방전 전압(VSS2)이 제공된 이후에, 상기 스위칭 신호에 응답하여 상기 제2 출력 트랜지스터의 상기 출력 전극에 상기 제2 방전 전압(VSS2)을 제공하는 제4 풀다운 트랜지스터를 포함할 수 있다. 상기 제2 방전 전압(VSS2)은 상기 제1 방전 전압(VSS1)보다 낮은 바이어스 전압일 수 있다.

### 발명의 효과

[0027] 상기 제2 노드에 상기 제1 제어 신호가 인가됨으로써 상기 k번째 게이트 신호가 출력되는 구간 동안에, 상기 제1 및 제2 제어 트랜지스터들 각각의 드레인-소스 전압이 감소된다. 따라서, 상기 제1 및 제2 제어 트랜지스터들의 열화(degradation)가 감소된다.

[0028] 상기 제1 및 제2 제어 트랜지스터들의 열화가 감소됨으로써 상기 출력 트랜지스터의 제어전극이 접속된 노드의 전위를 목적하는 레벨로 제어할 수 있다. 따라서, 상기 k번째 게이트 신호 및 상기 k번째 캐리 신호가 지연되지 않는다.

[0029] 상기 제1 제어 트랜지스터의 입력전극에 바이어스 전압이 인가됨으로써 상기 제1 제어 트랜지스터에는 k-1번째 수평 구간뿐만 아니라 k번째 수평 구간에도 일정한 방향으로 전류가 흐른다. 따라서, k번째 수평 구간 동안에, 상기 제1 제어 트랜지스터의 열화가 방지될 수 있다.

### 도면의 간단한 설명

[0030] 도 1은 본 발명의 일 실시예에 따른 표시장치의 평면도이다.

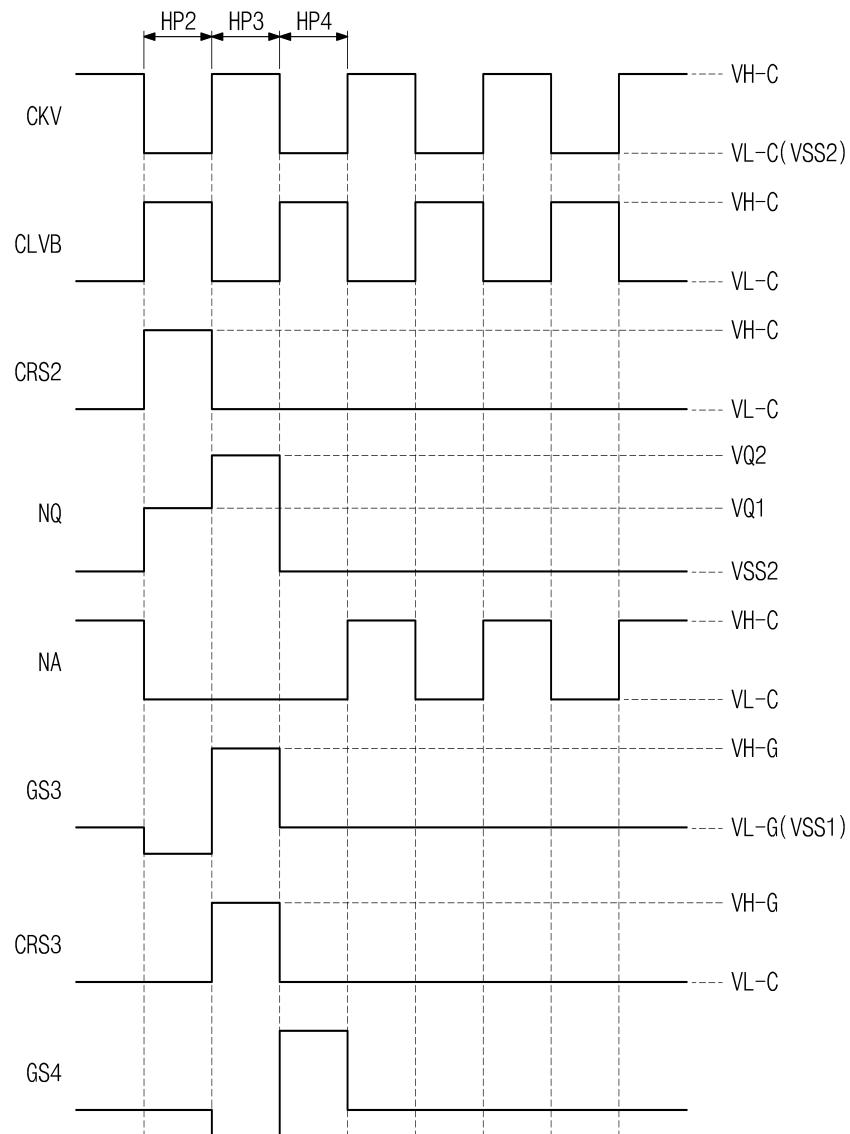

도 2는 본 발명의 일 실시예에 따른 표시장치의 신호들의 타이밍도이다.

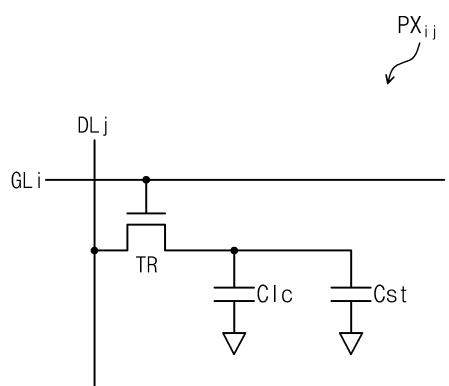

도 3은 본 발명의 일 실시예에 따른 화소의 등가회로도이다.

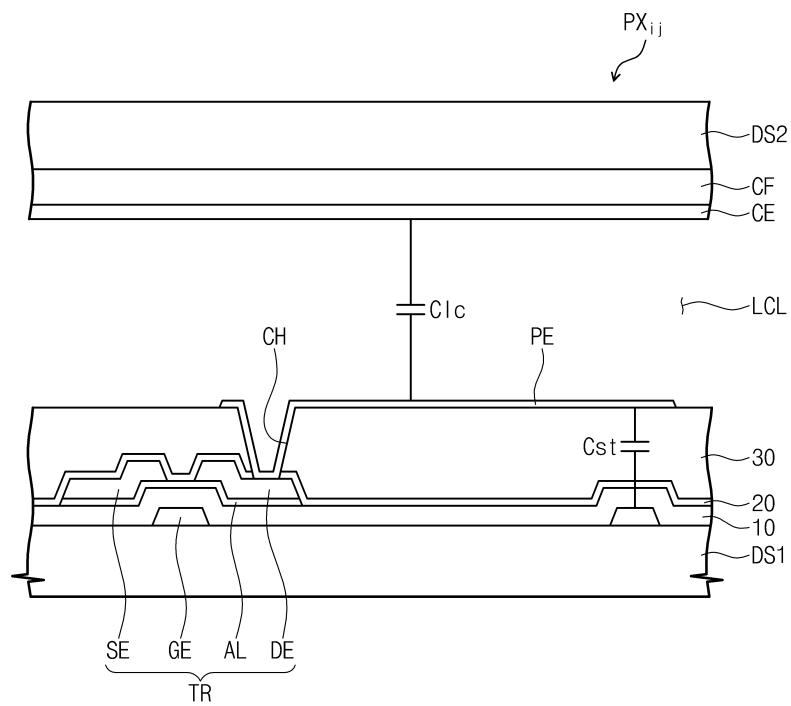

도 4는 본 발명의 일 실시예에 따른 화소의 단면도이다.

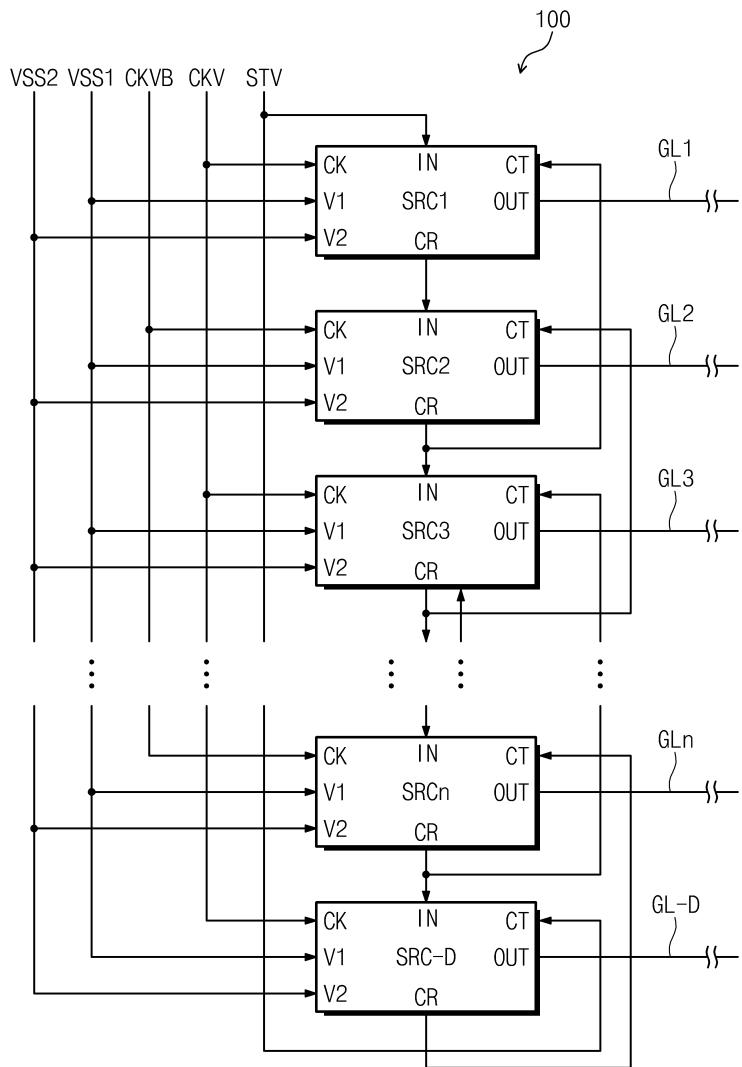

도 5는 본 발명의 일 실시예에 따른 게이트 구동회로의 블럭도이다.

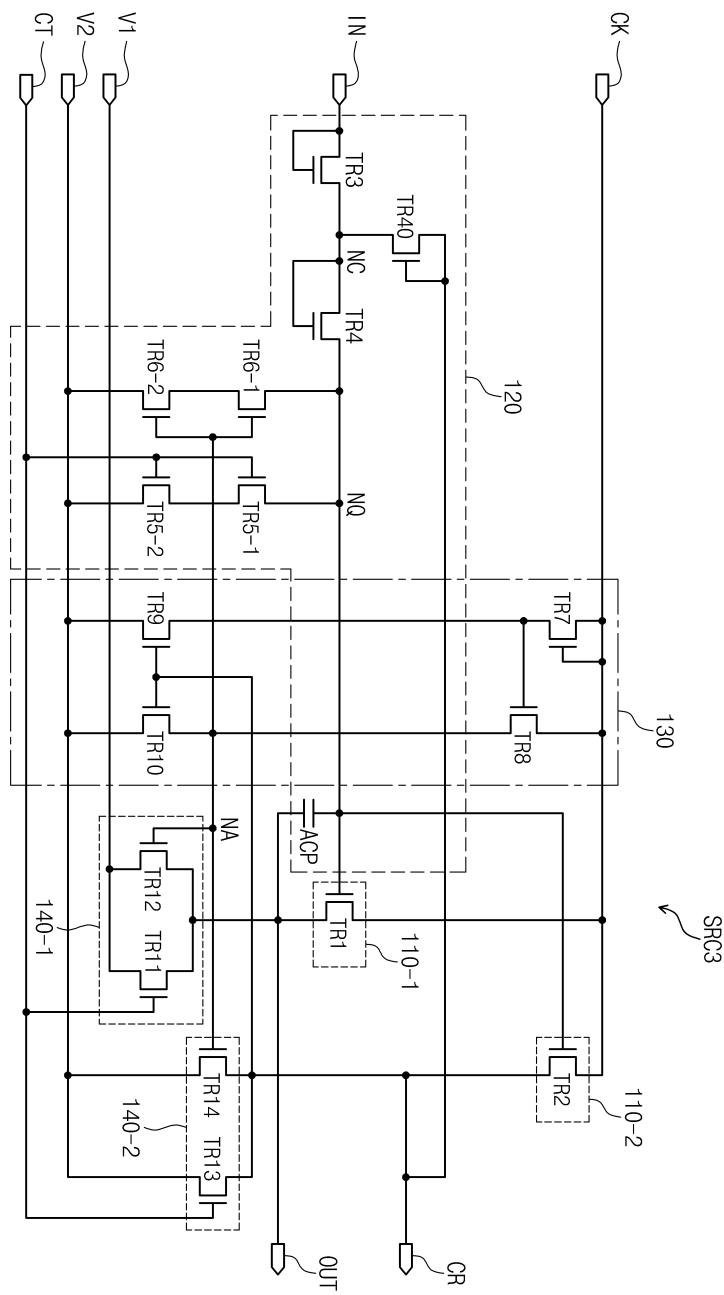

도 6은 본 발명의 일 실시예에 따른 구동 스테이지의 회로도이다.

도 7은 본 발명의 일 실시예에 따른 구동 스테이지의 입출력신호 파형도이다.

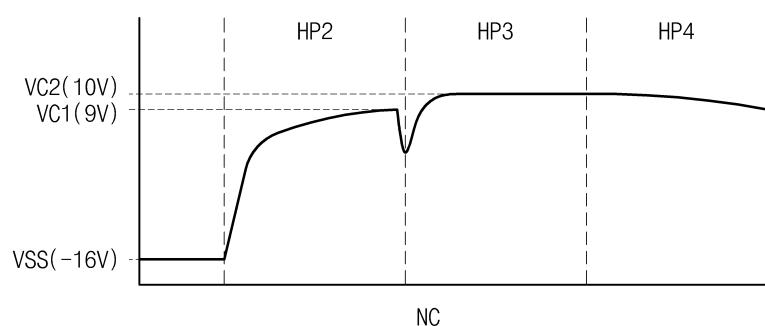

도 8은 도 6에 도시된 제2 노드의 전압 변화를 도시한 파형도이다.

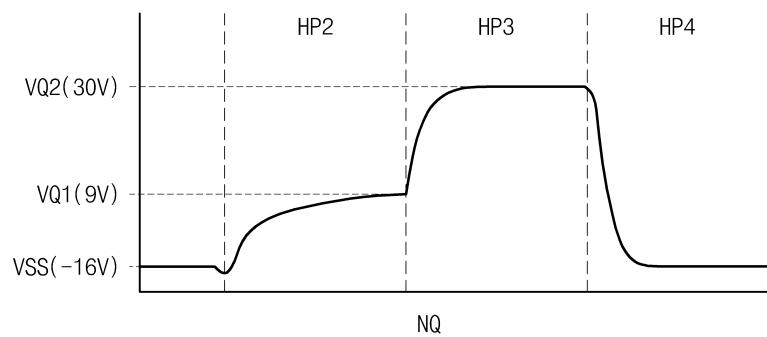

도 9는 도 6에 도시된 제1 노드의 전압 변화를 도시한 파형도이다.

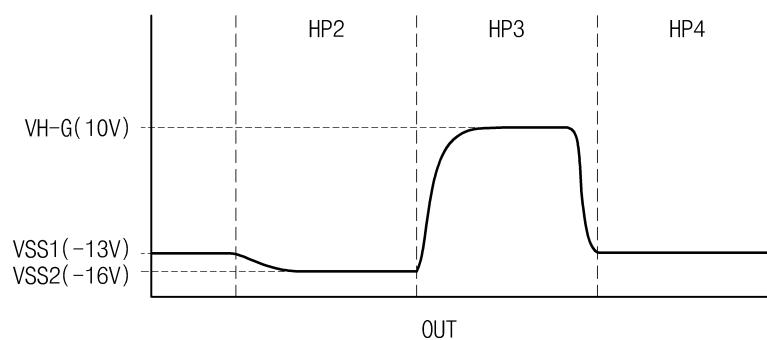

도 10은 도 6에 도시된 출력단자의 전압 변화를 도시한 파형도이다.

도 11은 본 발명의 일 실시예에 따른 구동 스테이지의 회로도이다.

도 12는 본 발명의 일 실시예에 따른 구동 스테이지의 회로도이다.

도 13은 도 12에 도시된 제2 노드의 전압 변화를 도시한 과정도이다.

도 14는 본 발명의 일 실시예에 따른 게이트 구동회로의 출력도이다.

도 15는 본 발명의 일 실시예에 따른 구동 스테이지의 회로도이다.

### 발명을 실시하기 위한 구체적인 내용

[0031]

이하 첨부된 도면들을 참조하여 본 발명의 바람직한 실시예를 보다 상세하게 설명한다.

[0032]

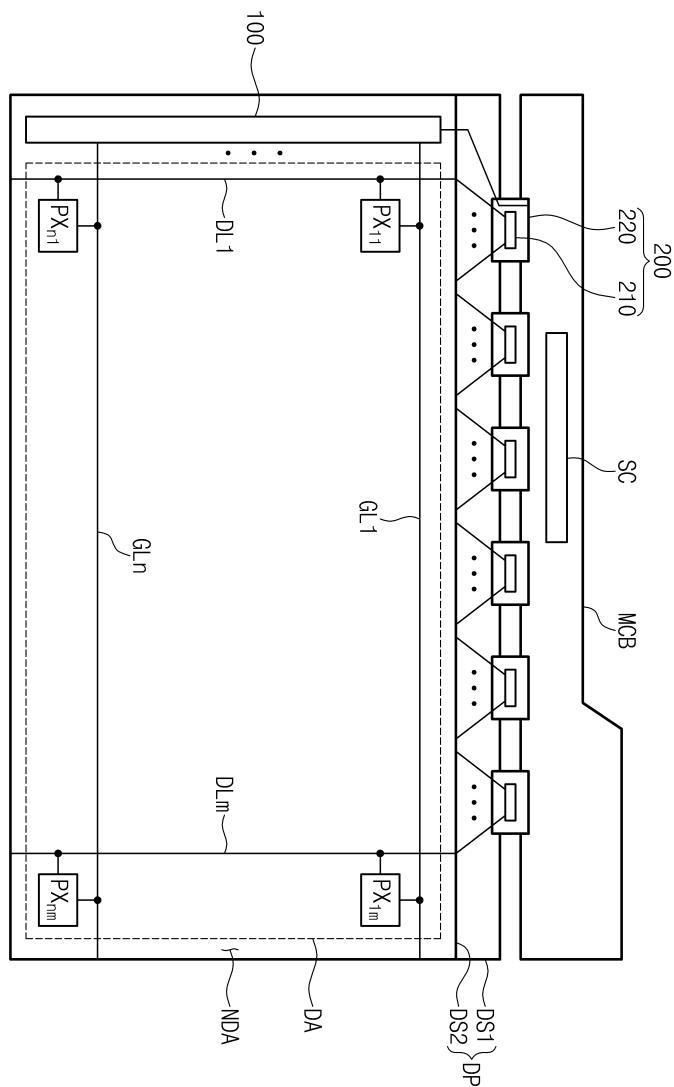

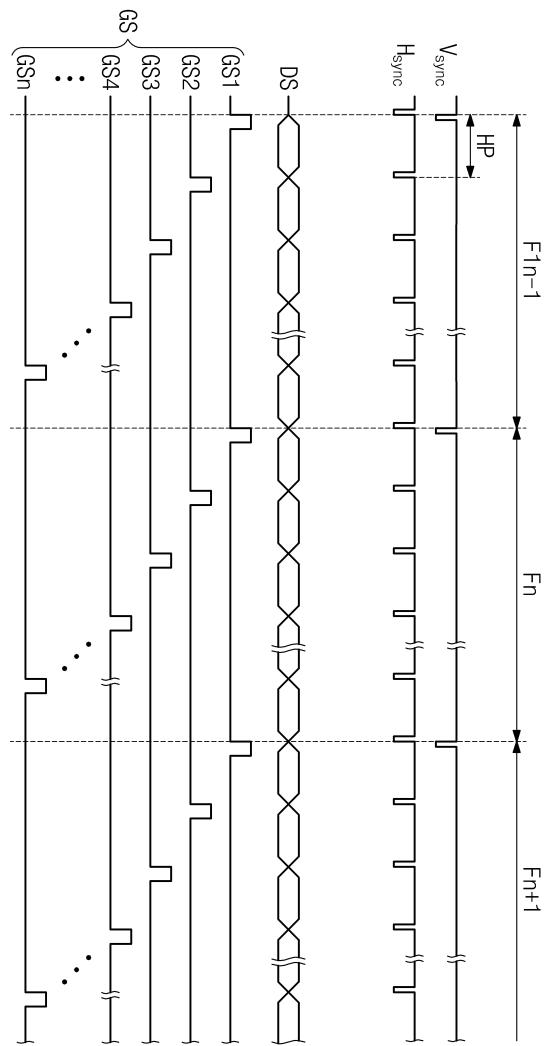

도 1은 본 발명의 일 실시예에 따른 표시장치의 평면도이다. 도 2는 본 발명의 일 실시예에 따른 표시장치의 신호들의 타이밍도이다.

[0033]

도 1 및 도 2에 도시된 것과 같이, 본 발명의 실시 예에 따른 표시장치는 표시패널(DP), 게이트 구동회로(100), 및 데이터 구동회로(200)를 포함한다.

[0034]

상기 표시패널(DP)은 특별히 한정되는 것은 아니며, 예를 들어, 액정 표시패널(liquid crystal display panel), 유기발광 표시패널(organic light emitting display panel), 전기영동 표시패널(electrophoretic display panel), 및 일렉트로웨팅 표시패널(electrowetting display panel)등의 다양한 표시패널을 포함할 수 있다. 본 실시예에서 상기 표시패널(DP)은 상기 액정 표시패널로 설명된다. 한편, 액정 표시패널을 포함하는 액정 표시장치는 미 도시된 편광자, 백라이트 유닛 등을 더 포함할 수 있다.

[0035]

상기 표시패널(DP)은 제1 기판(DS1), 상기 제1 기판(DS1)과 이격된 제2 기판(DS2) 및 상기 제1 기판(DS1)과 상기 제2 기판(DS2) 사이에 배치된 액정층(LCL)을 포함한다. 평면 상에서, 상기 표시패널(DP)은 복수 개의 화소들(PX<sub>11</sub>~PX<sub>nm</sub>)이 배치된 표시영역(DA) 및 상기 표시영역(DA)을 둘러싸는 비표시영역(NDA)을 포함한다.

[0036]

상기 표시패널(DP)은 상기 제1 기판(DS1) 상에 배치된 복수 개의 게이트 라인들(GL1~GL<sub>n</sub>) 및 상기 게이트 라인들(GL1~GL<sub>n</sub>)과 교차하는 복수 개의 데이터 라인들(DL1~DL<sub>m</sub>)을 포함한다. 상기 복수 개의 게이트 라인들(GL1~GL<sub>n</sub>)은 상기 게이트 구동회로(100)에 연결된다. 상기 복수 개의 데이터 라인들(DL1~DL<sub>m</sub>)은 상기 데이터 구동회로(200)에 연결된다. 도 1에는 상기 복수 개의 게이트 라인들(GL1~GL<sub>n</sub>) 중 일부와 상기 복수 개의 데이터 라인들(DL1~DL<sub>m</sub>) 중 일부만이 도시되었다. 또한, 상기 표시패널(DP)은 상기 제1 기판(DS1)의 상기 비표시영역(NDA)에 배치된 더미 게이트 라인(GL-D)을 더 포함할 수 있다.

[0037]

도 1에는 복수 개의 화소들(PX<sub>11</sub>~PX<sub>nm</sub>) 중 일부만이 도시되었다. 상기 복수 개의 화소들(PX<sub>11</sub>~PX<sub>nm</sub>)은 상기 복수 개의 게이트 라인들(GL1~GL<sub>n</sub>) 중 대응하는 게이트 라인 및 상기 복수 개의 데이터 라인들(DL1~DL<sub>m</sub>) 중 대응하는 데이터 라인에 각각 연결된다. 다만, 상기 더미 게이트 라인(GL-D)은 상기 복수 개의 화소들(PX<sub>11</sub>~PX<sub>nm</sub>)에 연결되지 않는다.

[0038]

상기 복수 개의 화소들(PX<sub>11</sub>~PX<sub>nm</sub>)은 표시하는 컬러에 따라 복수 개의 그룹들로 구분될 수 있다. 상기 복수 개의 화소들(PX<sub>11</sub>~PX<sub>nm</sub>)은 주요색(primary color) 중 하나를 표시할 수 있다. 상기 주요색은 레드, 그린, 블루, 및 화이트를 포함할 수 있다. 한편, 이에 제한되는 것은 아니고, 상기 주요색은 엘로우, 시안, 마젠타 등 다양한 색상을 더 포함할 수 있다.

[0039]

상기 게이트 구동회로(100) 및 상기 데이터 구동회로(200)는 신호 제어부(SC, 예컨대 타이밍 컨트롤러)로부터 제어 신호를 수신한다. 상기 신호 제어부(SC)는 메인 회로기판(MCB)에 실장될 수 있다. 상기 신호 제어부(SC)는 외부의 그래픽 제어부(미 도시)로부터 영상 데이터 및 제어 신호를 수신한다. 상기 제어 신호는 프레임 구간들(Fn-1, Fn, Fn+1)을 구별하는 신호인 수직 동기 신호(Vsync), 수평 구간들(HP)을 구별하는 신호, 즉 행 구별 신호인 수평 동기 신호(Hsync), 데이터가 들어오는 구역을 표시하기 위해 데이터가 출력되는 구간 동안만 하이 레벨인 데이터 인레이블 신호 및 클록 신호들을 포함할 수 있다.

[0040]

상기 게이트 구동회로(100)는 상기 프레임 구간들(Fn-1, Fn, Fn+1) 동안에 상기 신호 제어부(SC)로부터 수신한 제어 신호(이하, 게이트 제어 신호)에 기초하여 게이트 신호들(GS1~GS<sub>n</sub>)을 생성하고, 상기 게이트 신호들(GS1~GS<sub>n</sub>)를 상기 복수 개의 게이트 라인들(GL1~GL<sub>n</sub>)에 출력한다. 상기 게이트 신호들(GS1~GS<sub>n</sub>)은 수평 구간들(HP)에 대응하게 순차적으로 출력될 수 있다. 상기 게이트 구동회로(100)는 박막공정을 통해 상기 화소들

( $PX_{11} \sim PX_{nm}$ )과 동시에 형성될 수 있다. 예컨대, 상기 게이트 구동회로(100)는 상기 비표시영역(NDA)에 ASG(Amorphous Silicon TFT Gate driver circuit) 형태 또는 OSG(Oxide Semiconductor TFT Gate driver circuit) 형태로 실장될 수 있다.

[0041] 도 1은 상기 복수 개의 게이트 라인들(GL<sub>1</sub>~GL<sub>n</sub>)의 좌측 말단들에 연결 하나의 게이트 구동회로(100)를 예시적으로 도시하였다. 본 발명의 일 실시예에서, 상기 표시장치는 2개의 게이트 구동회로들을 포함할 수 있다. 상기 2개의 게이트 구동회로들 중 하나는 상기 복수 개의 게이트 라인들(GL<sub>1</sub>~GL<sub>n</sub>)의 좌측 말단들에 연결되고, 다른 하나는 상기 복수 개의 게이트 라인들(GL<sub>1</sub>~GL<sub>n</sub>)의 우측 말단들에 연결될 수 있다. 또한, 상기 2개의 게이트 구동회로들 중 하나는 홀수 번째 게이트 라인들에 연결되고, 다른 하나는 짝수 번째 게이트 라인들에 연결될 수 있다.

[0042] 상기 데이터 구동회로(200)는 상기 신호 제어부(SC)로부터 수신한 제어 신호(이하, 데이터 제어 신호)에 기초하여 상기 신호 제어부(SC)로부터 제공된 영상 데이터에 따른 계조 전압들을 생성한다. 상기 데이터 구동회로(200)는 상기 계조 전압들을 데이터 전압들(DS)로써 상기 복수 개의 데이터 라인들(DL<sub>1</sub>~DL<sub>m</sub>)에 출력한다.

[0043] 상기 데이터 전압들(DS)은 상기 공통 전압에 대하여 양의 값을 갖는 정극성 데이터 전압들 및/또는 음의 값을 갖는 부극성 데이터 전압들을 포함할 수 있다. 각각의 상기 수평 구간들(HP) 동안에 상기 데이터 라인들(DL<sub>1</sub>~DL<sub>m</sub>)에 인가되는 데이터 전압들 중 일부는 정극성을 갖고, 다른 일부는 부극성을 가질 수 있다. 상기 데이터 전압들(DS)의 극성은 액정의 열화를 방지하기 위하여 프레임 구간들(Fn-1, Fn, Fn+1)에 따라 반전될 수 있다. 상기 데이터 구동회로(200)는 상기 반전 신호에 응답하여 프레임 구간 단위로 반전된 데이터 전압들을 생성할 수 있다.

[0044] 상기 데이터 구동회로(200)는 구동칩(210) 및 상기 구동칩(210)을 실장하는 연성회로기판(220)을 포함할 수 있다. 상기 데이터 구동회로(200)는 복수 개의 상기 구동칩(210)과 상기 연성회로기판(220)을 포함할 수 있다. 상기 연성회로기판(220)은 상기 메인 회로기판(MCB)과 상기 제1 기판(DS1)을 전기적으로 연결한다. 상기 복수 개의 구동칩들(210)은 상기 복수 개의 데이터 라인들(DL<sub>1</sub>~DL<sub>m</sub>) 중 대응하는 데이터 라인들에 대응하는 데이터 신호들을 제공한다.

[0045] 도 1은 테이프 캐리어 패키지(TCP: Tape Carrier Package) 타입의 데이터 구동회로(200)를 예시적으로 도시하였다. 본 발명의 일 실시예에서, 상기 데이터 구동회로(200)는 칩 온 글래스(COG: Chip on Glass) 방식으로 상기 제1 기판(DS1)의 상기 비표시영역(NDA) 상에 배치될 수 있다.

[0046] 도 3은 본 발명의 일 실시예에 따른 화소의 등가회로도이다. 도 4는 본 발명의 일 실시예에 따른 화소의 단면도이다. 도 1에 도시된 복수 개의 화소들( $PX_{11} \sim PX_{nm}$ ) 각각은 도 3에 도시된 등가회로를 가질 수 있다.

[0047] 도 3에 도시된 것과 같이, 상기 화소( $PX_{ij}$ )는 화소 박막 트랜지스터(TR, 이하 화소 트랜지스터), 액정 커패시터(C<sub>1c</sub>), 및 스토리지 커패시터(C<sub>st</sub>)를 포함한다. 이하, 본 명세서에서 트랜지스터는 박막 트랜지스터를 의미한다. 본 발명의 일 실시예에서 상기 스토리지 커패시터(C<sub>st</sub>)는 생략될 수 있다.

[0048] 상기 화소 트랜지스터(TR)는 i번째 게이트 라인(GL<sub>i</sub>)과 j번째 데이터 라인(DL<sub>j</sub>)에 전기적으로 연결된다. 상기 화소 트랜지스터(TR)는 상기 i번째 게이트 라인(GL<sub>i</sub>)으로부터 수신한 게이트 신호에 응답하여 상기 j번째 데이터 라인(DL<sub>j</sub>)으로부터 수신한 데이터 신호에 대응하는 화소 전압을 출력한다.

[0049] 상기 액정 커패시터(C<sub>1c</sub>)는 상기 화소 트랜지스터(TR)로부터 출력된 상기 화소 전압을 충전한다. 상기 액정 커패시터(C<sub>1c</sub>)에 충전된 전하량에 따라 상기 액정층(LCL, 도 4 참조)에 포함된 액정 방향자의 배열이 변화된다. 상기 액정 방향자의 배열에 따라 상기 액정층으로 입사된 광은 투과되거나 차단된다.

[0050] 상기 스토리지 커패시터(C<sub>st</sub>)는 상기 액정 커패시터(C<sub>1c</sub>)에 병렬로 연결된다. 상기 스토리지 커패시터(C<sub>st</sub>)는 상기 액정 방향자의 배열을 일정한 구간 동안 유지시킨다.

[0051] 도 4에 도시된 것과 같이, 상기 화소 트랜지스터(TR)는 상기 i번째 게이트 라인(GL<sub>i</sub>, 도 3 참조)에 연결된 제어 전극(GE), 상기 제어전극(GE)에 중첩하는 활성화부(AL), 상기 j번째 데이터 라인(DL<sub>j</sub>, 도 3 참조)에 연결된 입력전극(SE), 및 상기 입력전극(SE)와 이격되어 배치된 출력전극(DE)을 포함한다.

[0052] 상기 액정 커패시터(C<sub>1c</sub>)는 화소전극(PE)과 공통전극(CE)을 포함한다. 상기 스토리지 커패시터(C<sub>st</sub>)는 상기 화소전극(PE)과 상기 화소전극(PE)에 중첩하는 스토리지 라인(STL)의 일부분을 포함한다.

[0053] 상기 제1 기판(DS1)의 일면 상에 상기 i번째 게이트 라인(GL<sub>i</sub>) 및 상기 스토리지 라인(STL)이 배치된다. 상기

제어전극(GE)은 상기 i번째 게이트 라인(GLi)으로부터 분기된다. 상기 i번째 게이트 라인(GLi) 및 상기 스토리지 라인(STL)은 알루미늄(Al), 은(Ag), 구리(Cu), 몰리브덴(Mo), 크롬(Cr), 탄탈륨(Ta), 티타늄(Ti) 등의 금속 또는 이들의 합금 등을 포함할 수 있다. 상기 i번째 게이트 라인(GLi) 및 상기 스토리지 라인(STL)은 다층 구조, 예컨대 티타늄층과 구리층을 포함할 수 있다.

[0054] 상기 제1 기판(DS1)의 상기 일면 상에 상기 제어전극(GE) 및 스토리지 라인(STL)을 커버하는 제1 절연층(10)이 배치된다. 상기 제1 절연층(10)은 무기물 및 유기물 중 적어도 어느 하나를 포함할 수 있다. 상기 제1 절연층(10)은 유기막이거나, 무기막일 수 있다. 상기 제1 절연층(10)은 다층 구조, 예컨대 실리콘 나이트라이드층과 실리콘 옥사이드층을 포함할 수 있다.

[0055] 상기 제1 절연층(10) 상에 상기 제어전극(GE)과 중첩하는 상기 활성화부(AL)가 배치된다. 상기 활성화부(AL)는 반도체층(SCL)과 오믹 컨택층(OCL)을 포함할 수 있다. 상기 제1 절연층(10) 상에 상기 반도체층(SCL)이 배치되고, 상기 반도체층(SCL) 상에 상기 오믹 컨택층(OCL)이 배치된다.

[0056] 상기 반도체층(SCL)은 아몰포스 실리콘 또는 폴리 실리콘을 포함할 수 있다. 또한, 상기 반도체층(SCL)은 금속 산화물 반도체를 포함할 수 있다. 상기 오믹 컨택층(OCL)은 상기 반도체층보다 고밀도로 도핑된 도편트를 포함할 수 있다. 상기 오믹 컨택층(OCL)은 이격된 2개의 부분을 포함할 수 있다. 본 발명의 일 실시예에서 상기 오믹 컨택층(OCL)은 일체의 형상을 가질 수 있다.

[0057] 상기 활성화부(AL) 상에 상기 출력전극(DE)과 상기 입력전극(SE)이 배치된다. 상기 출력전극(DE)과 상기 입력전극(SE)은 서로 이격되어 배치된다. 상기 출력전극(DE)과 상기 입력전극(SE) 각각은 상기 제어전극(GE)에 부분적으로 중첩한다.

[0058] 좀 더 구체적으로, 상기 출력전극(DE)과 상기 입력전극(SE)은 상기 오믹 컨택층(OCL) 상에 배치된다. 평면상에서, 상기 출력전극(DE)은 상기 오믹 컨택층(OCL)의 하나의 부분에 완전히 중첩하고, 상기 입력전극(SE)은 상기 오믹 컨택층(OCL)의 다른 하나의 부분에 완전히 중첩할 수 있다.

[0059] 상기 제1 절연층(10) 상에 상기 활성화부(AL), 상기 출력전극(DE), 및 상기 입력전극(SE)을 커버하는 제2 절연층(20)이 배치된다. 상기 제2 절연층(20)은 무기물 및 유기물 중 적어도 어느 하나를 포함할 수 있다. 상기 제2 절연층(20)은 유기막이거나, 무기막일 수 있다. 상기 제2 절연층(20)은 다층 구조, 예컨대 실리콘 나이트라이드층과 실리콘 옥사이드층을 포함할 수 있다.

[0060] 도 1에는 스태거 구조를 갖는 화소 트랜지스터(TR)를 예시적으로 도시하였으나, 상기 화소 트랜지스터(TR)의 구조는 이에 제한되지 않는다. 상기 화소 트랜지스터(TR)는 플래너 구조를 가질 수도 있다.

[0061] 상기 제2 절연층(20) 상에 제3 절연층(30)이 배치된다. 상기 제3 절연층(30)은 평탄면을 제공한다. 상기 제3 절연층(30)은 유기물을 포함할 수 있다.

[0062] 상기 제3 절연층(30) 상에 상기 화소전극(PE)이 배치된다. 상기 화소전극(PE)은 상기 제2 절연층(20) 및 상기 제3 절연층(30)을 관통하는 컨택홀(CH)을 통해 상기 출력전극(DE)에 연결된다. 상기 제3 절연층(30) 상에 상기 화소전극(PE)을 커버하는 배향막(미 도시)이 배치될 수 있다.

[0063] 상기 제2 기판(DS2)의 일면 상에 컬러필터층(CF)이 배치된다. 상기 컬러필터층(CF) 상에 공통전극(CE)이 배치된다. 상기 공통전극(CE)에는 공통 전압이 인가된다. 상기 공통 전압과 상기 화소 전압과 다른 값을 갖는다. 상기 공통전극(CE) 상에 상기 공통전극(CE)을 커버하는 배향막(미 도시)이 배치될 수 있다. 상기 컬러필터층(CF)과 상기 공통전극(CE) 사이에 또 다른 절연층이 배치될 수 있다.

[0064] 상기 액정층(LCL)을 사이에 두고 배치된 상기 화소전극(PE)과 상기 공통전극(CE)은 액정 커페시터(C1c)를 형성한다. 또한, 상기 제1 절연층(10), 상기 제2 절연층(20), 및 상기 제3 절연층(30)을 사이에 두고 배치된 상기 화소전극(PE)과 상기 스토리지 라인(STL)의 일부분은 스토리지 커페시터(Cst)를 형성한다. 상기 스토리지 라인(STL)은 상기 화소 전압과 다른 값의 스토리지 전압을 수신한다. 상기 스토리지 전압은 상기 공통 전압과 동일한 값을 가질 수 있다.

[0065] 한편, 도 3에 도시된 화소(PX<sub>ij</sub>)의 단면은 하나의 예시에 불과하다. 도 3에 도시된 것과 달리, 상기 컬러필터층(CF) 및 상기 공통전극(CE) 중 적어도 어느 하나는 상기 제1 기판(DS1) 상에 배치될 수 있다. 다시 말해, 본 실시예에 따른 액정 표시패널은 VA(Vertical Alignment)모드, PVA(Patterned Vertical Alignment) 모드, IPS(in-plane switching) 모드 또는 FFS(fringe-field switching) 모드, PLS(Plane to Line Switching) 모드 등의 화

소를 포함할 수 있다.

[0066] 도 5는 본 발명의 일 실시예에 따른 게이트 구동회로의 블럭도이다. 도 5에 도시된 것과 같이, 상기 게이트 구동회로(100)는 복수 개의 구동 스테이지들(SRC1~SRCn)을 포함한다. 상기 복수 개의 구동 스테이지들(SRC1~SRCn)은 서로 종속적으로 연결된다.

[0067] 본 실시예에서 상기 복수 개의 구동 스테이지들(SRC1~SRCn)은 상기 복수 개의 게이트 라인들(GL1~GLn)에 각각 연결된다. 상기 복수 개의 구동 스테이지들(SRC1~SRCn)은 상기 복수 개의 게이트 라인들(GL1~GLn)에 게이트 신호들을 각각 제공한다. 본 발명의 일 실시예에서 상기 복수 개의 구동 스테이지들(SRC1~SRCn)에 연결된 게이트 라인들은 전체의 게이트 라인들 중 홀수 번째 게이트 라인들이거나, 짝수 번째 게이트 라인들일 수 있다.

[0068] 상기 게이트 구동회로(100)는 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 중 말단에 배치된 구동 스테이지(SRCn)에 연결된 더미 스테이지(SRC-D)를 더 포함할 수 있다. 상기 더미 스테이지(SRC-D)는 더미 게이트 라인(GL-D)에 연결된다.

[0069] 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 각각은 출력단자(OUT), 캐리단자(CR), 입력단자(IN), 제어단자(CT), 클럭단자(CK), 제1 전압 입력단자(V1), 및 제2 전압 입력단자(V2)를 포함한다.

[0070] 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 각각의 출력단자(OUT)는 상기 복수 개의 게이트 라인들(GL1~GLn) 중 대응하는 게이트 라인에 연결된다. 상기 복수 개의 구동 스테이지들(SRC1~SRCn)로부터 생성된 게이트 신호들은 상기 출력단자(OUT)를 통해 상기 복수 개의 게이트 라인들(GL1~GLn)에 제공한다.

[0071] 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 각각의 캐리단자(CR)는 해당 구동 스테이지 다음의 구동 스테이지의 입력단자(IN)에 전기적으로 연결된다. 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 각각의 캐리단자(CR)는 캐리 신호를 출력한다.

[0072] 복수 개의 구동 스테이지들(SRC1~SRCn) 각각의 입력단자(IN)는 해당 구동 스테이지 이전의 구동 스테이지의 캐리 신호를 수신한다. 예컨대, 3번째 구동 스테이지들(SRC3)의 입력단자(IN)는 2번째 구동 스테이지(SRC2)의 캐리 신호를 수신한다. 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 중 첫번째 구동 스테이지(SRC1)의 입력단자(IN)는 상기 이전 구동 스테이지의 캐리 신호 대신에 상기 게이트 구동회로(100)의 구동을 개시하는 개시신호(STV)를 수신한다.

[0073] 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 각각의 제어단자(CT)는 해당 구동 스테이지 다음의 구동 스테이지의 캐리단자(CR)에 전기적으로 연결된다. 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 각각의 제어단자(CT)는 해당 구동 스테이지 다음의 구동 스테이지의 캐리 신호를 수신한다. 예컨대, 상기 2번째 구동 스테이지(SRC2)의 제어단자(CT)는 상기 3번째 구동 스테이지(SRC3)의 캐리단자(CR)로부터 출력된 캐리 신호를 수신한다. 본 발명의 일 실시예에서 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 각각의 제어단자(CT)는 해당 구동 스테이지 다음의 구동 스테이지의 출력단자(OUT)에 전기적으로 연결될 수도 있다.

[0074] 상기 말단에 배치된 구동 스테이지(SRCn)의 제어단자(CT)는 상기 더미 스테이지(SRC-D)의 캐리단자(CR)로부터 출력된 캐리 신호를 수신한다. 상기 더미 스테이지(SRC-D)의 제어단자(CT)는 상기 개시신호(STV)를 수신한다.

[0075] 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 각각의 클럭단자(CK)는 제1 클럭 신호(CKV)와 제2 클럭 신호(CKVB) 중 어느 하나를 각각 수신한다. 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 중 홀수 번째 구동 스테이지들(SRC1, SRC3)의 상기 클럭단자들(CK)은 상기 제1 클럭 신호(CKV)를 각각 수신할 수 있다. 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 중 짝수 번째 구동 스테이지들(SRC2, SRCn)의 클럭단자들(CK)은 상기 제2 클럭 신호(CKVB)를 각각 수신할 수 있다. 상기 제1 클럭 신호(CKV)와 상기 제2 클럭 신호(CKVB)는 위상이 다른 신호일 수 있다.

[0076] 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 각각의 제1 전압 입력단자(V1)는 제1 방전 전압(VSS1)을 수신한다. 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 각각의 제2 전압 입력단자(V2)는 제2 방전 전압(VSS2)을 수신한다. 상기 제2 방전 전압(VSS2)은 상기 제1 방전 전압(VSS1)보다 낮은 레벨을 갖는다.

[0077] 본 발명의 일 실시예에서 상기 복수 개의 구동 스테이지들(SRC1~SRCn) 각각은 그 회로구성에 따라 상기 출력단자(OUT), 상기 입력단자(IN), 상기 캐리단자(CR), 상기 제어단자(CT), 상기 클럭단자(CK), 상기 제1 전압 입력단자(V1), 및 상기 제2 전압 입력단자(V2) 중 어느 하나가 생략되거나, 다른 단자들이 더 포함될 수 있다. 예컨대, 상기 제1 전압 입력단자(V1), 및 상기 제2 전압 입력단자(V2) 중 어느 하나는 생략될 수 있다. 또한, 상기

복수 개의 구동 스테이지들(SRC1~SRCn)의 연결관계도 변경될 수 있다.

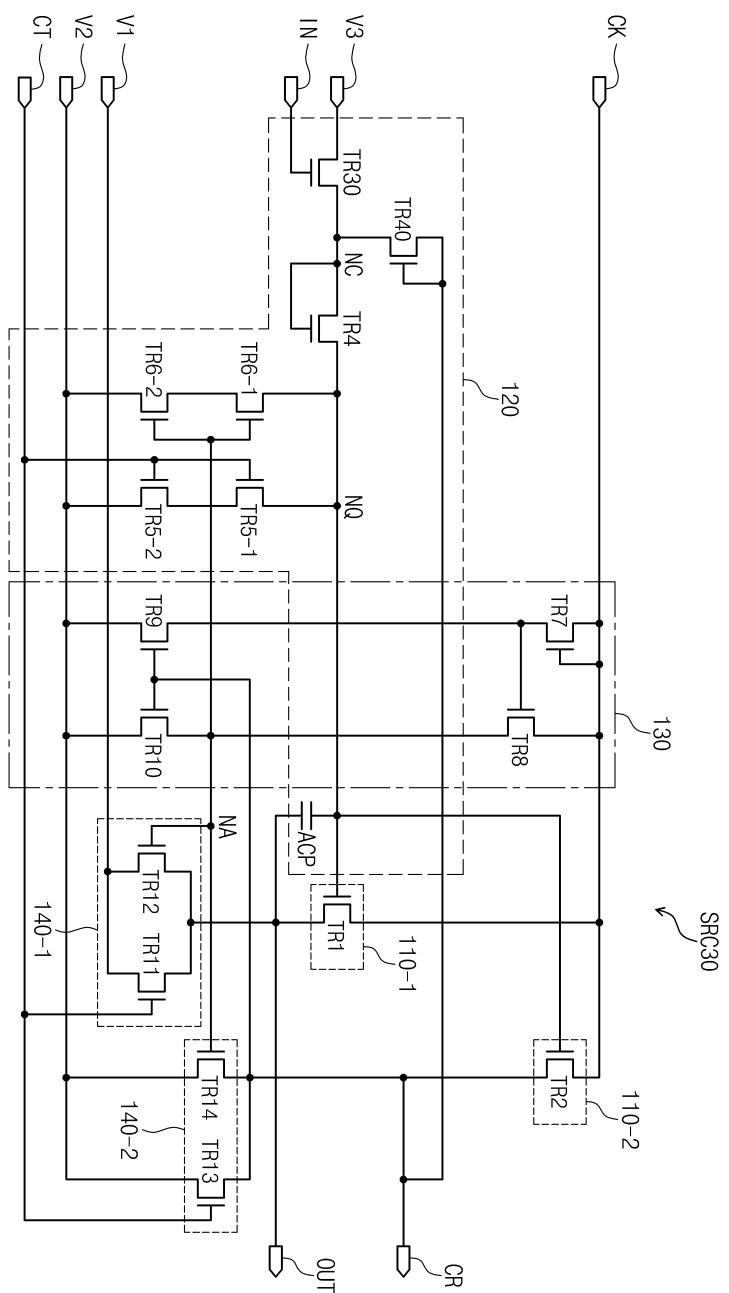

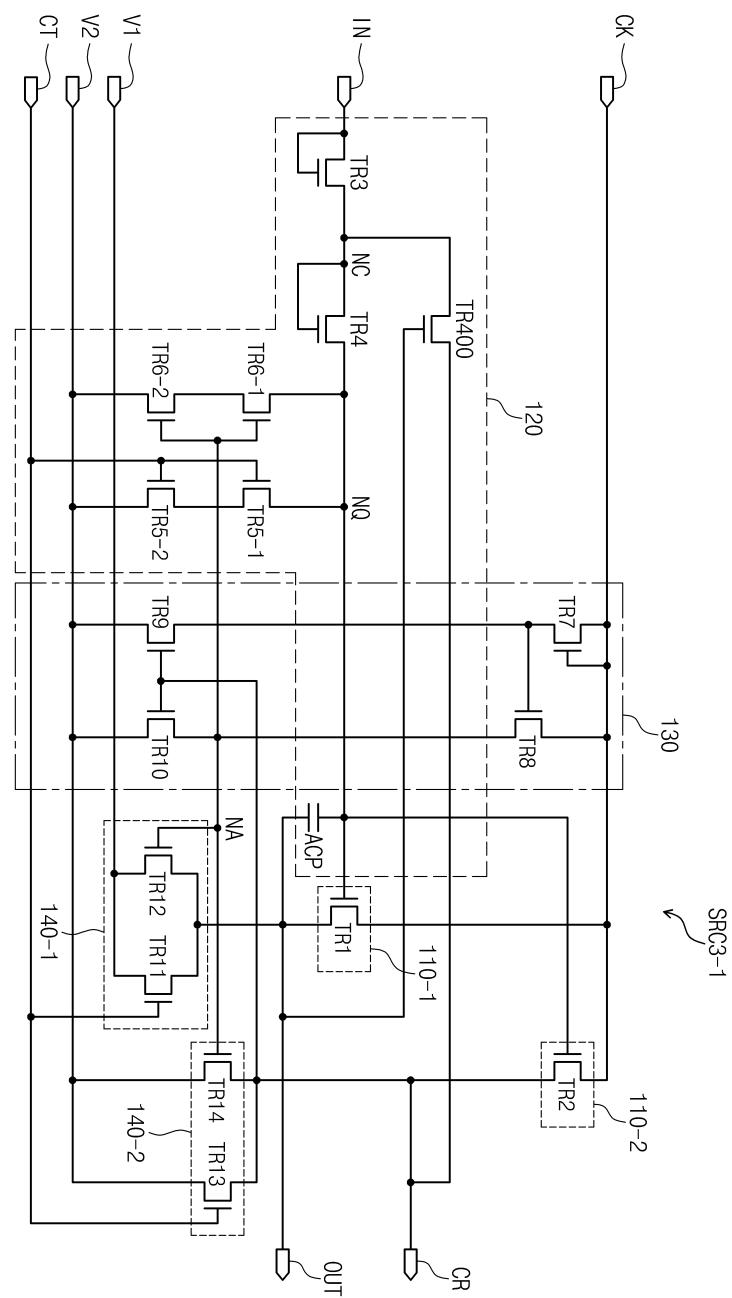

[0078] 도 6은 본 발명의 일 실시예에 따른 구동 스테이지의 회로도이다. 도 7은 본 발명의 일 실시예에 따른 구동 스테이지의 입출력신호 파형도이다.

[0079] 도 6은 도 5에 도시된 복수 개의 구동 스테이지들(SRC1~SRCn) 중 3번째 구동 스테이지(SRC3)를 예시적으로 도시하였다. 도 5에 도시된 복수 개의 구동 스테이지들(SRC1~SRCn) 각각은 상기 3번째 구동 스테이지(SRC3)와 동일한 회로를 가질 수 있다.

[0080] 도 6 및 도 7을 참조하면, 상기 3번째 구동 스테이지(SRC3)는 출력부(110-1, 110-2), 제어부(120), 인버터부(130), 및 풀다운부(140-1, 140-2)를 포함한다. 상기 출력부(110-1, 110-2)는 3번째 게이트 신호(GS3)를 출력하는 제1 출력부(110-1) 및 3번째 캐리 신호(CRS3)를 출력하는 제2 출력부(110-2)를 포함한다. 상기 풀다운부(140-1, 140-2)는 출력단자(OUT)를 다운시키는 제1 풀다운부(140-1) 및 캐리단자(CR)를 다운시키는 제2 풀다운부(140-2)를 포함한다. 상기 3번째 상기 구동 스테이지(SRC3)의 회로는 예시적인 것에 불과하며, 이는 변경될 수 있다.

[0081] 상기 제1 출력부(110-1)는 제1 출력 트랜지스터(TR1)를 포함한다. 상기 제1 출력 트랜지스터(TR1)는 상기 제1 클럭 신호(CKV)를 수신하는 입력전극, 제1 노드(NQ)에 접속된 제어전극, 및 상기 3번째 게이트 신호(GS3)를 출력하는 출력전극을 포함한다.

[0082] 상기 제2 출력부(110-2)는 제2 출력 트랜지스터(TR2)를 포함한다. 상기 제2 출력 트랜지스터(TR2)는 상기 제1 클럭 신호(CKV)를 수신하는 입력전극, 상기 제1 노드(NQ)에 연결된 제어전극, 및 상기 3번째 캐리 신호(CRS3)를 출력하는 출력전극을 포함한다.

[0083] 도 7에 도시된 것과 같이, 상기 제1 클럭 신호(CKV)와 상기 제2 클럭 신호(CKVB)는 위상이 반전된 신호일 수 있다. 상기 제1 클럭 신호(CKV)와 상기 제2 클럭 신호(CKVB)는  $180^{\circ}$ 의 위상차를 가질 수 있다. 상기 제1 클럭 신호(CKV)와 상기 제2 클럭 신호(CKVB) 각각은 레벨이 낮은 로우구간들(VL-C, 로우 전압)과 레벨이 상대적으로 높은 하이구간들(VH-C, 하이 전압)을 포함한다. 상기 제1 클럭 신호(CKV)와 상기 제2 클럭 신호(CKVB) 각각은 교번하는 상기 로우구간들과 상기 하이구간들을 포함한다. 상기 하이 전압(VH-C)은 약 10V 일 수 있다. 상기 로우 전압(VL-C)은 약 -16V 일 수 있다. 상기 로우 전압(VL-C)은 상기 제2 방전 전압(VSS2, 도 5 참조)과 동일한 레벨일 가질 수 있다.

[0084] 상기 3번째 게이트 신호(GS3)는 레벨이 낮은 로우구간(VL-G, 로우 전압)과 레벨이 상대적으로 높은 하이구간(VH-G, 하이 전압)을 포함한다. 상기 3번째 게이트 신호(GS3)의 상기 로우 전압(VL-G)은 상기 제1 방전 전압(VSS1, 도 5 참조)과 동일한 레벨일 가질 수 있다. 상기 로우 전압(VL-G)은 약 -13V 일 수 있다. 상기 3번째 게이트 신호(GS3)는 일부의 구간들 동안에 상기 제1 클럭 신호(CKV)의 로우 전압(VL-C)과 동일한 레벨을 가질 수 있다. 상기 3번째 게이트 신호(GS3)의 상기 하이 전압(VH-G)은 상기 제1 클럭 신호(CKV)의 상기 하이 전압(VH-C)과 동일한 레벨일 가질 수 있다. 이에 대한 상세한 설명은 후술한다.

[0085] 상기 3번째 캐리 신호(CRS3)는 레벨이 낮은 로우구간(VL-C, 로우 전압)과 레벨이 상대적으로 높은 하이구간(VH-C, 하이 전압)을 포함한다. 상기 3번째 캐리 신호(CRS3)는 상기 제1 클럭 신호(CKV)에 근거하여 생성되었기 때문에 상기 제1 클럭 신호(CKV)와 유사한 전압 레벨을 갖는다.

[0086] 도 6 및 도 7을 참조하면, 상기 제어부(120)는 상기 제1 출력부(110-1) 및 제2 출력부(110-2)의 동작을 제어한다. 상기 제어부(120)는 2번째 구동 스테이지(SRC2)로부터 출력된 2번째 캐리 신호(CRS2)에 응답하여 상기 제1 출력부(110-1) 및 상기 제2 출력부(110-2)를 턠-온 시킨다. 상기 제어부(120)는 상기 4번째 구동 스테이지로부터 출력된 4번째 캐리 신호(CRS2)에 응답하여 상기 제1 출력부(110-1) 및 상기 제2 출력부(110-2)를 턠-오프 시킨다. 그밖에 상기 제어부(120)는 상기 인버터부(130)로부터 출력된 스위칭 신호에 따라 상기 제1 출력부(110-1) 및 상기 제2 출력부(110-2)의 턠-오프를 유지한다.

[0087] 상기 제어부(120)는 제1 제어 트랜지스터(TR3), 제2 제어 트랜지스터(TR4), 제3 제어 트랜지스터(TR40), 제4 제어 트랜지스터(TR5-1, TR5-2), 제5 제어 트랜지스터(TR6-1, TR6-2), 및 커패시터(CAP)를 포함한다. 본 실시예에서 직렬 연결된 2개의 제4 제어 트랜지스터들(TR5-1, TR5-2) 및 직렬 연결된 2개의 제5 제어 트랜지스터(TR6-1, TR6-2)가 예시적으로 도시되었다.

[0088] 상기 제1 제어 트랜지스터(TR3)는 상기 제1 노드(NQ)의 전위를 제어하는 제1 제어 신호를 상기 3번째 게이트 신호(GS3)가 출력되기 이전에 제2 노드(NC)에 출력한다. 도 7은 복수 개의 수평 구간들 중 상기 3번째 게이트 신

호(GS3)가 출력되는 수평 구간(HP3, 이하 3번째 수평 구간), 바로 이전 수평 구간(HP2, 이하 2번째 수평 구간), 및 바로 이후 수평 구간(HP4, 이하 4번째 수평 구간)을 표시하였다.

[0089] 상기 제1 제어 트랜지스터(TR3)는 상기 2번째 캐리 신호(CRS2)를 공통으로 수신하는 제어전극과 입력전극을 포함한다. 상기 제1 제어 트랜지스터(TR3)는 상기 제2 노드(NC)에 연결된 출력전극을 포함한다. 본 실시예에서 상기 제1 제어 신호는 상기 2번째 캐리 신호(CRS2)일 수 있다.

[0090] 상기 제2 제어 트랜지스터(TR4)는 상기 제2 노드(NC)로부터 상기 제1 노드(NQ)로 전류패스가 형성되도록 상기 제2 노드(NC)와 상기 제1 노드(NQ) 사이에 다이오드 접속된다. 상기 제2 제어 트랜지스터(TR4)는 상기 제2 노드(NC)에 공통으로 접속된 제어전극과 입력전극 및 상기 제1 노드(NQ)에 연결된 출력전극을 포함한다.

[0091] 상기 제2 노드(NC)에 상기 2번째 캐리 신호(CRS2)가 인가된 이후에, 제2 제어 신호가 인가된다. 상기 제2 제어 신호는 상기 3번째 게이트 신호(GS3)에 동기된 신호일 수 있다. 여기서 "상기 제2 제어 신호가 상기 3번째 게이트 신호(GS3)에 동기되었다"는 것은 "상기 제2 제어 신호가 적어도 상기 3번째 게이트 신호(GS3)와 동일한 시간에 하이 전압을 갖는다"는 것을 의미한다.

[0092] 상기 제3 제어 트랜지스터(TR40)가 상기 제2 노드(NC)에 제2 제어 신호를 인가한다. 상기 제3 제어 트랜지스터(TR40)는 상기 제2 출력 트랜지스터(TR2)의 출력전극으로부터 상기 제2 노드(VC)로 전류패스가 형성되도록 상기 제2 출력 트랜지스터(TR2)의 상기 출력전극과 상기 제2 노드(NC) 사이에 다이오드 접속된다. 상기 제3 제어 트랜지스터(TR40)는 상기 제2 출력 트랜지스터(TR2)의 출력전극에 공통으로 접속된 제어전극과 입력전극 및 상기 제2 노드(NC)에 연결된 출력전극을 포함한다.

[0093] 실질적으로 상기 제2 제어 신호는 상기 2번째 캐리 신호(CRS2)와 동일한 신호일 수 있다. 본 발명의 일 실시예에서 상기 제3 제어 트랜지스터(TR40)는 상기 제1 출력 트랜지스터(TR1)의 출력전극과 상기 제2 노드(NC) 사이에 다이오드 접속될 수도 있다. 이때, 상기 제3 제어 트랜지스터(TR40)는 상기 3번째 게이트 신호(GS3)와 실질적으로 동일한 제2 제어 신호를 상기 제2 노드(NC)에 제공할 수 있다.

[0094] 상기 커패시터(CAP)는 상기 제1 출력 트랜지스터(TR1)의 상기 출력전극과 상기 제1 출력 트랜지스터(TR1)의 상기 제어전극(또는 제1 노드(NQ)) 사이에 접속된다.

[0095] 상기 2개의 상기 제4 제어 트랜지스터들(TR5-1, TR5-2)이 상기 제2 전압 입력단자(V2)와 상기 제1 노드(NQ) 사이에 직렬로 연결된다. 상기 2개의 상기 제4 제어 트랜지스터들(TR5-1, TR5-2)의 제어전극들은 공통적으로 상기 제어단자(CT)에 접속된다. 상기 2개의 상기 제4 제어 트랜지스터들(TR5-1, TR5-2)은 4번째 구동 스테이지로부터 출력된 4번째 캐리 신호(미 도시)에 응답하여 상기 제1 노드(NQ)에 상기 제2 방전 전압(VSS2)을 제공한다. 본 발명의 일 실시예에서 상기 2개의 상기 제4 제어 트랜지스터들(TR5-1, TR5-2)은 4번째 게이트 신호(GS4)에 의해 턴-온 될 수도 있다.

[0096] 상기 2개의 상기 제5 제어 트랜지스터들(TR6-1, TR6-2)이 상기 제2 전압 입력단자(V2)와 상기 제1 노드(NQ) 사이에 직렬로 연결된다. 상기 2개의 상기 제5 제어 트랜지스터들(TR5-1, TR5-2)의 제어전극들은 공통적으로 제3 노드(NA)에 접속된다. 상기 2개의 상기 제5 제어 트랜지스터들(TR6-1, TR6-2)은 상기 인버터부(130)로부터 출력된 상기 스위칭 신호에 응답하여 상기 제1 노드(NQ)에 상기 제2 방전 전압(VSS2)을 제공한다.

[0097] 본 발명의 일 실시예에서 상기 2개의 상기 제4 제어 트랜지스터들(TR5-1, TR5-2) 중 어느 하나는 생략될 수 있고, 상기 2개의 상기 제5 제어 트랜지스터들(TR6-1, TR6-2) 중 어느 하나는 생략될 수 있다. 또한, 제4 제어 트랜지스터(TR5-1, TR5-2)와 제5 제어 트랜지스터(TR6-1, TR6-2) 중 어느 하나는 상기 제2 전압 입력단자(V2)가 아닌 상기 제1 전압 입력단자(V1)에 접속될 수 있다.

[0098] 도 7에 도시된 것과 같이, 상기 2번째 수평 구간(HP2) 동안에 상기 제1 노드(NQ)의 전위는 상기 2번째 캐리 신호(CRS2)에 의해 제1 하이 전압(VQ1)으로 상승한다. 상기 2번째 캐리 신호(CRS2)가 제1 노드(NQ)에 인가되면 커패시터(CAP)는 그에 대응하는 전압을 충전한다. 상기 3번째 수평 구간(HP3) 동안에, 상기 3번째 게이트 신호(GS3)가 출력된다. 이때, 상기 제1 노드(NQ)는 상기 제1 하이 전압(VQ1)으로부터 제2 하이 전압(VQ2)으로 부스팅된다.

[0099] 상기 제2 제어 신호가 상기 제2 노드(NC)에 제공됨으로써, 상기 3번째 수평 구간(HP3) 동안의 상기 제1 및 제2 제어 트랜지스터들(TR3, TR4) 각각의 드레인-소스 전압이 감소된다. 이에 대한 상세한 설명은 도 8 내지 도 10을 참조하여 후술한다.

[0100] 상기 4번째 수평 구간(HP4) 동안에 상기 제1 노드(NQ)의 전압은 상기 제2 방전 전압(VSS2)으로 하락된다. 그에

따라 상기 제1 출력 트랜지스터(TR1) 및 상기 제2 출력 트랜지스터(TR2)는 턴-오프된다. 상기 4번째 수평 구간(HP4) 이후 다음 프레임 구간의 3번째 게이트 신호(GS3)가 출력되기 이전까지, 상기 제1 노드(NQ)의 전압은 상기 제2 방전 전압(VSS2)으로 유지된다. 그에 따라 상기 4번째 수평 구간(HP4) 이후 다음 프레임 구간의 3번째 게이트 신호(GS3)가 출력되기 이전까지, 상기 제1 출력 트랜지스터(TR1) 및 상기 제2 출력 트랜지스터(TR2)의 오프 상태가 유지된다.

[0101] 도 6 및 도 7을 참조하면, 상기 인버터부(130)는 상기 제3 노드(NA)에 스위칭 신호를 출력한다. 상기 인버터부(130)는 제1 내지 제4 인버터 트랜지스터(TR7, TR8, TR9, TR10)를 포함한다. 상기 제1 인버터 트랜지스터(TR7)는 상기 클럭단자(CK)에 공통적으로 연결된 입력전극과 제어전극, 및 상기 제2 인버터 트랜지스터(TR8)의 제어전극에 연결된 출력전극을 포함한다. 상기 제2 인버터 트랜지스터(TR8)는 상기 클럭단자(CK)에 연결된 입력전극, 상기 제3 노드(NA)에 연결된 출력전극을 포함한다.

[0102] 상기 제3 인버터 트랜지스터(TR9)는 제1 인버터 트랜지스터(TR7)의 출력전극에 연결된 출력전극, 상기 캐리단자(CR)에 연결된 제어전극, 및 상기 제2 전압 입력단자(V2)에 연결된 입력전극을 포함한다. 상기 제4 인버터 트랜지스터(TR10)는 상기 제3 노드(NA)에 연결된 출력전극, 상기 캐리단자(CR)에 연결된 제어전극, 및 상기 제2 전압 입력단자(V2)에 연결된 입력전극을 포함한다. 본 발명의 일 실시예에서 상기 제3 및 제4 인버터 트랜지스터(TR9, TR10)의 제어전극은 상기 출력단자(OUT)에 연결될 수 있고, 상기 제3 및 제4 인버터 트랜지스터(TR9, TR10)의 출력전극은 상기 제1 전압 입력단자(V1)에 연결될 수 있다.

[0103] 도 7에 도시된 것과 같이, 상기 제3 노드(NA)는 상기 3번째 수평 구간(HP3)을 제외하고 상기 제1 클럭 신호(CKV)와 실질적으로 동일한 위상을 갖는다. 상기 3번째 수평 구간(HP3) 동안에, 상기 제3 및 제4 인버터 트랜지스터(TR9, TR10)는 상기 3번째 캐리 신호(CRS3)에 응답하여 턴-온된다. 이때, 상기 제2 인버터 트랜지스터(TR8)로부터 출력된 상기 제1 클럭 신호(CKV)의 하이 전압(VH-C)은 제2 방전 전압(VSS2)으로 방전된다. 상기 3번째 수평 구간(HP3) 이외의 구간들 동안에, 상기 제2 인버터 트랜지스터(TR8)로부터 출력된 상기 제1 클럭 신호(CKV)의 하이 전압(VH-C)과 로우 전압(VL-C)은 상기 제3 노드(NA)에 제공된다. 상기 제1 클럭 신호(CKV)의 교변하는 하이 전압(VH-C)과 로우 전압(VL-C)은 스위칭 신호로써 다른 트랜지스터들에 제공된다.

[0104] 상기 제1 풀다운부(140-1)는 제1 풀다운 트랜지스터(TR11) 및 제2 풀다운 트랜지스터(TR12)를 포함한다. 상기 제1 풀다운 트랜지스터(TR11)는 상기 제1 전압 입력단자(V1)에 접속된 입력전극, 상기 제어단자(CT)에 접속된 제어전극, 및 상기 제1 출력 트랜지스터(TR1)의 출력전극에 접속된 출력전극을 포함한다. 상기 제2 풀다운 트랜지스터(TR12)는 상기 제1 전압 입력단자(V1)에 접속된 입력전극, 상기 제3 노드(NA)에 접속된 제어전극, 및 상기 제1 출력 트랜지스터(TR1)의 출력전극에 접속된 출력전극을 포함한다. 본 발명의 일 실시예에서 상기 제1 풀다운 트랜지스터(TR11)의 입력전극 및 상기 제2 풀다운 트랜지스터(TR12)의 입력전극 중 적어도 어느 하나는 상기 제2 전압 입력단자(V2)에 연결될 수도 있다.

[0105] 도 7에 도시된 것과 같이, 상기 4번째 수평 구간(HP4) 이후의 상기 3번째 게이트 신호(GS3)의 전압은 상기 제1 출력 트랜지스터(TR1)의 출력전극의 전압에 대응한다. 상기 4번째 수평 구간(HP4) 동안에 상기 제1 풀다운 트랜지스터(TR11)는 상기 4번째 캐리 신호에 응답하여 상기 제1 출력 트랜지스터(TR1)의 출력전극에 제1 방전 전압(VSS1)을 제공한다. 상기 4번째 수평 구간(HP4) 이후에 상기 제2 풀다운 트랜지스터(TR12)는 상기 제3 노드(NA)로부터 출력된 상기 스위칭 신호에 응답하여 상기 제1 출력 트랜지스터(TR1)의 출력전극에 상기 제1 방전 전압(VSS1)을 제공한다.

[0106] 상기 제2 풀다운부(140-2)는 제3 풀다운 트랜지스터(TR13) 및 제4 풀다운 트랜지스터(TR14)를 포함한다. 상기 제3 풀다운 트랜지스터(TR13)는 상기 제2 전압 입력단자(V2)에 접속된 입력전극, 상기 제어단자(CT)에 접속된 제어전극, 및 상기 제2 출력 트랜지스터(TR2)의 출력전극에 접속된 출력전극을 포함한다. 상기 제4 풀다운 트랜지스터(TR14)는 상기 제2 전압 입력단자(V2)에 접속된 입력전극, 상기 제3 노드(NA)에 접속된 제어전극, 및 상기 제2 출력 트랜지스터(TR2)의 출력전극에 접속된 출력전극을 포함한다. 본 발명의 일 실시예에서 상기 제3 풀다운 트랜지스터(TR13)의 입력전극 및 상기 제4 풀다운 트랜지스터(TR14)의 입력전극 중 적어도 어느 하나는 상기 제1 전압 입력단자(V1)에 연결될 수도 있다.

[0107] 도 7에 도시된 것과 같이, 상기 4번째 수평 구간(HP4) 이후의 상기 3번째 캐리 신호(CRS3)의 전압은 상기 제2 출력 트랜지스터(TR2)의 출력전극의 전압에 대응한다. 상기 4번째 수평 구간(HP4) 동안에 상기 제3 풀다운 트랜지스터(TR13)는 상기 4번째 캐리 신호에 응답하여 상기 제2 출력 트랜지스터(TR2)의 출력전극에 상기 제2 방전 전압(VSS2)을 제공한다. 상기 4번째 수평 구간(HP4) 이후에 상기 제4 풀다운 트랜지스터(TR14)는 상기 제3 노드(NA)로부터 출력된 상기 스위칭 신호에 응답하여 상기 제2 출력 트랜지스터(TR2)의 출력전극에 상기 제2 방전

전압(VSS2)을 제공한다.

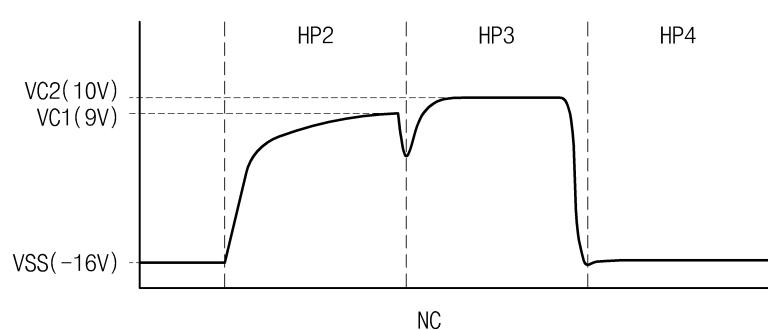

[0108] 도 8은 도 6에 도시된 제2 노드(NC)의 전압 변화를 도시한 과정도이다. 도 9는 도 6에 도시된 제1 노드(NQ)의 전압 변화를 도시한 과정도이다. 도 10은 도 6에 도시된 출력단자(OUT)의 전압 변화를 도시한 과정도이다. 이하, 도 6에서 설명된 트랜지스터들 및 도 7에서 설명된 신호들을 참조한다.

[0109] 도 8에 도시된 것과 같이, 상기 2번째 수평 구간(HP2) 동안에, 상기 제2 노드(NC)는 상기 제1 제어 트랜지스터(TR3) 통해 상기 2번째 캐리 신호(CRS2)를 수신함으로써 제1 하이 전압(VC1)을 갖는다. 상기 제1 하이 전압(VC1)은 상기 2번째 캐리 신호(CRS2)의 하이 전압(VH-C)과 실질적으로 동일하거나 다소 낮은 레벨을 가질 수 있다.

[0110] 도 9에 도시된 것과 같이, 상기 2번째 수평 구간(HP2) 동안에, 상기 제1 노드(NQ)는 상기 제2 제어 트랜지스터(TR4) 통해 상기 2번째 캐리 신호(CRS2)에 대응하는 전압을 수신함으로써 제1 하이 전압(VQ1)을 갖는다. 상기 제1 노드(NQ)의 상기 제1 하이 전압(VQ1)은 상기 제2 노드(NC)의 상기 제1 하이 전압(VC1)과 실질적으로 동일하거나 다소 낮은 레벨을 가질 수 있다.

[0111] 도 10에 도시된 것과 같이, 상기 2번째 수평 구간(HP2) 동안에 상기 출력단자(OUT)는 상기 제1 클럭신호(CKV)의 로우 전압(VH-C)과 실질적으로 동일한 레벨을 갖는다. 상기 3번째 수평 구간(HP3) 동안에 상기 제1 출력 트랜지스터(TR1)가 상기 제1 노드(NQ)의 상기 제1 하이 전압(VQ1)에 응답하여 턴-온되었기 때문이다.

[0112] 도 8에 도시된 것과 같이, 상기 3번째 수평 구간(HP3) 동안에, 상기 제2 노드(NC)는 제3 제어 트랜지스터(TR40) 통해 상기 3번째 캐리 신호(CRS3)를 수신함으로써 제2 하이 전압(VC2)을 갖는다. 상기 제2 하이 전압(VC2)은 상기 3번째 캐리 신호(CRS3)의 하이 전압(VH-C)과 실질적으로 동일하거나 다소 낮은 레벨을 가질 수 있다. 도 8은 상기 제2 노드(NC)의 제2 하이 전압(VC2)이 상기 제2 노드(NC)의 제1 하이 전압(VC1)보다 다소 높은 예를 도시하였다. 상기 제2 노드(NC)의 제1 하이 전압(VC1)과 상기 제2 노드(NC)의 제2 하이 전압(VC2)의 레벨들은 상기 제1 제어 트랜지스터(TR3)과 제3 제어 트랜지스터(TR40)의 특성에 따라 변경될 수 있다.

[0113] 도 9에 도시된 것과 같이, 상기 3번째 수평 구간(HP3) 동안에, 상기 제1 노드(NQ)는 제2 하이 전압(VQ2)을 갖는다. 상기 제1 노드(NQ)의 상기 제2 하이 전압(VQ2)은 약 30V일 수 있다. 이때, 도 10에 도시된 것과 같이, 상기 제2 노드(NC)의 상기 제2 하이 전압(VC2)은 약 10V일 수 있다. 또한, 상기 입력단자(IN)는 상기 2번째 캐리 신호(CRS2)의 로우 전압(VH-C)에 대응하는 약 -16V일 수 있다.

[0114] 상기 2번째 수평 구간(HP2)에 대비하여, 상기 3번째 수평 구간(HP3) 동안에 상기 제1 제어 트랜지스터(TR3)와 상기 제3 제어 트랜지스터(TR40)의 입력전극-출력전극 사이의 전압 레벨의 높고/낮음은 서로 바뀐다. 상기 3번째 수평 구간(HP3) 동안에, 상기 제1 제어 트랜지스터(TR3)의 입력전극-출력전극 사이에는 약 26V의 드레인-소스 전압이 형성되고, 상기 제3 제어 트랜지스터(TR40)의 입력전극-출력전극 사이에는 약 20V의 드레인-소스 전압이 형성된다.

[0115] 상기 제3 제어 트랜지스터(TR40)가 생략된 비교예에 따르면, 제2 제어 트랜지스터(TR4)의 입력전극-출력전극 사이에는 약 46V의 드레인-소스 전압이 형성된다. 비교예에 따르면, 상기 3번째 수평 구간(HP3) 동안에 제2 제어 트랜지스터(TR4)의 입력전극-출력전극 사이에는 매우 높은 드레인-소스 전압이 형성됨으로써 제2 제어 트랜지스터(TR4)의 열화가 발생할 수 있다. 상기 3번째 수평 구간(HP3) 동안에 상기 제2 제어 트랜지스터(TR4)를 통해 상기 제1 노드(NQ)에서 상기 제2 노드(NC)로 오프 누설전류가 발생할 수 있다. 상기 오프 누설전류는 상기 제1 노드(NQ)의 전압을 다운시키고, 상기 3번째 게이트 신호(GS3) 및 상기 3번째 캐리 신호(CRS3)를 지연시킬 수 있다.

[0116] 상기 제2 제어 트랜지스터(TR4) 및 상기 제3 제어 트랜지스터(TR40)가 생략된 비교예에 따르면, 제1 제어 트랜지스터(TR3)의 입력전극-출력전극 사이에는 약 46V의 드레인-소스 전압이 형성된다. 비교예에 따르면, 상기 3번째 수평 구간(HP3) 동안에 제1 제어 트랜지스터(TR3)의 입력전극-출력전극 사이에는 매우 높은 드레인-소스 전압이 형성됨으로써 제1 제어 트랜지스터(TR3)의 열화가 발생할 수 있다. 상기 제1 제어 트랜지스터(TR3)가 열화됨으로써 상기 제1 제어 트랜지스터(TR3)의 응답시간이 지연되고, 이는 스테이지 회로에 불량을 유발한다.

[0117] 그에 반하여 본 실시예에 따르면, 상기 제1 제어 트랜지스터(TR3) 및 상기 제3 제어 트랜지스터(TR40)에 상대적으로 낮은 드레인-소스 전압이 형성된다. 그에 따라 상기 제1 제어 트랜지스터(TR3) 및 상기 제2 제어 트랜지스터(TR4)의 열화는 방지될 수 있다. 상기 제1 제어 트랜지스터(TR3) 및 상기 제2 제어 트랜지스터(TR4)의 오프 누설전류가 감소됨으로써 상기 제1 노드(NQ)의 전압이 기준 레벨을 유지할 수 있다. 따라서, 상기 3번째 게이트

신호(GS3) 및 상기 3번째 캐리 신호(CRS3)가 지연되지 않는다.

[0118] 또한, 오프 누설전류가 발생한다는 것은 트랜지스터의 입력전극-출력전극 사이의 전압레벨의 높고/낮음이 시간에 따라 변화된다는 것을 의미한다. 그에 따라 트랜지스터가 열화(degradation)된다. 금속 산화물 반도체를 포함하는 박막 트랜지스터는 열화에 더욱 취약하다. 본 실시예에 따르면, 상기 제1 제어 트랜지스터(TR3)를 비롯하여 상기 제1 노드(NQ) 또는 상기 제2 노드(NC)에 접속된 트랜지스터들이 금속 산화물 반도체를 포함하더라도, 상기 제2 노드(NC)에 제어 신호를 제공함으로써 상기 트랜지스터들의 열화를 방지할 수 있다.

[0119] 도 8을 참조하면, 상기 제2 노드(NC)는 상기 3번째 수평 구간(HP3) 이후의 수평 구간들에 거쳐 자연 방전될 수 있다. 도 9 및 도 10을 참조하면, 상기 제1 노드(NQ)는 상기 제2 방전 전압(VSS2)으로 방전되고, 상기 출력단자(OUT)는 상기 제1 방전 전압(VSS1)으로 방전될 수 있다.

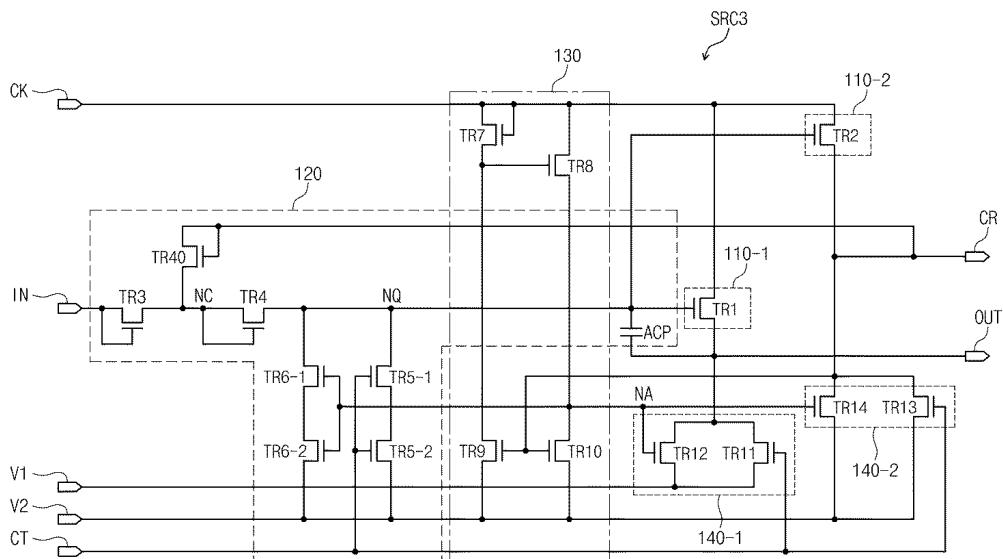

[0120] 도 11은 본 발명의 일 실시예에 따른 구동 스테이지(SRC3-1)의 회로도이다. 본 실시예에 따르면, 도 6에 도시된 구동 스테이지(SRC3) 대비 제3 제어 트랜지스터(TR400)의 구성만 일부 상이하다. 이하, 도 7 내지 도 10을 참조하여 설명한 구성과 중복되는 구성에 대한 상세한 설명은 생략한다.

[0121] 상기 제3 제어 트랜지스터(TR400)는 상기 제2 노드(NC)에 연결된 출력전극, 상기 캐리단자(CR)에 연결된 입력전극, 및 상기 출력단자(OUT)에 연결된 제어전극을 포함한다. 상기 제3 제어 트랜지스터(TR400)는 상기 3번째 수평 구간(HP3) 동안에 상기 3번째 게이트 신호(GS3)에 응답하여 상기 제2 노드(NC)에 상기 3번째 캐리 신호(CRS3)를 제공한다. 그에 따라 상기 3번째 수평 구간(HP3) 동안에 상기 제1 제어 트랜지스터(TR3) 및 상기 제2 제어 트랜지스터(TR4)의 오프 누설전류가 감소된다.

[0122] 본 발명의 일 실시예에서, 상기 제3 제어 트랜지스터(TR400)의 입력전극은 상기 출력단자(OUT)에 연결되고, 제어전극은 상기 캐리단자(CR)에 연결될 수도 있다.

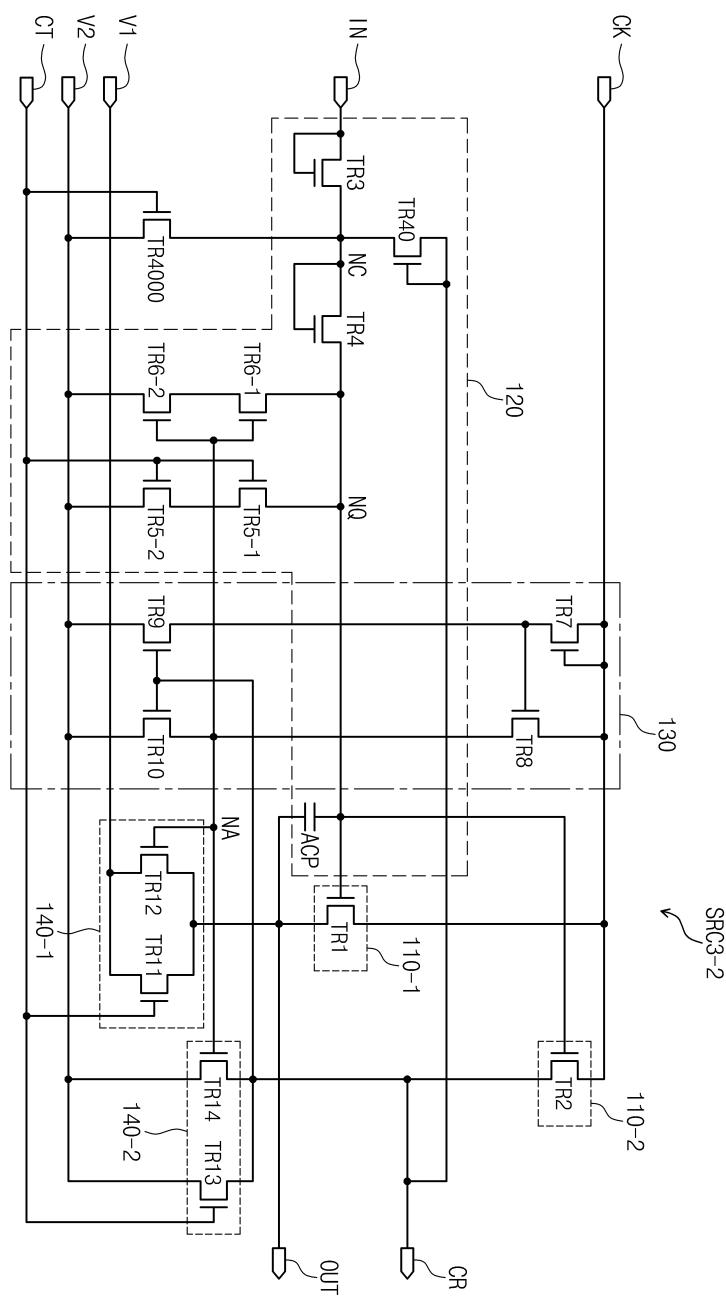

[0123] 도 12는 본 발명의 일 실시예에 따른 구동 스테이지의 회로도이다. 도 13은 도 12에 도시된 제2 노드의 전압 변화를 도시한 과정도이다.

[0124] 본 실시예에 따르면, 도 6에 도시된 구동 스테이지(SRC3) 대비 제6 제어 트랜지스터(TR4000)를 더 포함한다. 이하, 도 7 내지 도 10을 참조하여 설명한 구성과 중복되는 구성에 대한 상세한 설명은 생략한다. 또한, 상기 제6 제어 트랜지스터(TR4000)는 도 11에 도시된 구동 스테이지(SRC3-1)에도 추가할 수 있다.

[0125] 상기 제6 제어 트랜지스터(TR4000)는 상기 제2 노드(NC)에 연결된 출력전극, 상기 제2 전압 입력단자(V2)에 연결된 입력전극, 및 상기 제어단자(CT)에 연결된 제어전극을 포함한다. 상기 제6 제어 트랜지스터(TR4000)는 상기 4번째 수평 구간(HP4) 동안에 상기 4번째 캐리 신호(CRS4)에 응답하여 상기 제2 노드(NC)에 상기 제2 방전 전압(VSS2)을 제공한다.

[0126] 그에 따라 상기 4번째 수평 구간(HP4) 동안에, 상기 입력단자(IN), 상기 제2 노드(NC), 및 상기 제1 노드(NQ)는 실질적으로 동일한 전압을 가질 수 있다. 상기 입력단자(IN), 상기 제2 노드(NC), 및 상기 제1 노드(NQ)는 모두 상기 제2 방전 전압(VSS2)과 동일한 레벨을 갖는다. 상기 4번째 수평 구간(HP4) 동안에, 상기 제1 제어 트랜지스터(TR3) 및 상기 제2 제어 트랜지스터(TR4)의 열화가 감소된다.

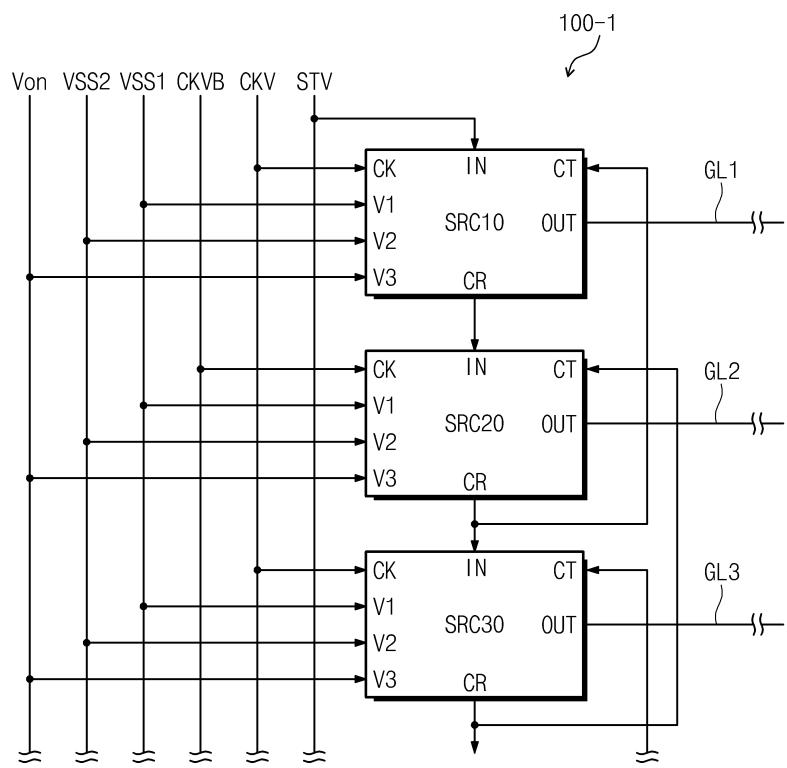

[0127] 도 14는 본 발명의 일 실시예에 따른 게이트 구동회로(100-1)의 블럭도이다. 도 15는 본 발명의 일 실시예에 따른 구동 스테이지(SRC30)의 회로도이다.

[0128] 도 14는 도 5 대비 3개의 구동 스테이지들(SRC10, SRC20, SRC30)을 도시하였다. 3개의 구동 스테이지들(SRC10, SRC20, SRC30)은 도 5의 3개의 구동 스테이지들(SRC1, SRC2, SRC3)에 각각 대응한다. 3개의 구동 스테이지들(SRC10, SRC20, SRC30)은 도 5의 3개의 구동 스테이지들(SRC1, SRC2, SRC3) 대비 제3 전압 입력단자(V3)를 더 포함한다. 또한, 구동 스테이지(SRC30)는 도 6에 도시된 구동 스테이지(SRC3) 대비 제1 제어 트랜지스터(TR30)의 구성만 일부 상이하다. 이하, 도 1 내지 도 13을 참조하여 설명한 구성과 동일한 구성에 대한 상세한 설명은 생략한다.

[0129] 상기 제3 전압 입력단자(V3)는 상기 바이어스 전압(Von)을 수신한다. 상기 바이어스 전압(Von)은 상기 2번째 캐리 신호(CRS2)의 하이 전압(VH-C)과 실질적으로 동일한 레벨을 갖는다.

[0130] 상기 제1 제어 트랜지스터(TR30)는 상기 제2 노드(NC)에 연결된 출력전극, 상기 제3 전압 입력단자(V3)에 연결된 입력전극, 및 상기 입력단자(IN)에 연결된 제어전극을 포함한다. 상기 제1 제어 트랜지스터(TR30)는 상기 2번째 수평 구간(HP2) 동안에 상기 2번째 캐리 신호(CRS2)에 응답하여 상기 제2 노드(NC)에 상기 바이어스 전압

(Von)을 제공한다.

[0131] 상기 제3 제어 트랜지스터(TR40)는 상기 3번째 수평 구간(HP3) 동안에 상기 제2 노드(NC)에 상기 3번째 캐리 신호(CRS3)를 제공한다. 그에 따라 상기 3번째 수평 구간(HP3) 동안에 상기 제1 제어 트랜지스터(TR30) 및 상기 제2 제어 트랜지스터(TR4)의 열화가 감소된다.

[0132] 상기 제1 제어 트랜지스터(TR30)의 입력전극은 수평 구간들에 무관하게 상기 2번째 캐리 신호(CRS2)의 하이 전압(VH-C), 즉 제1 클럭 신호의 하이 전압(VH-C)으로 바이어스된다. 상기 3번째 수평 구간(HP3), 상기 4번째 수평 구간(HP4), 및 그 이후에도 상기 제1 제어 트랜지스터(TR30)의 입력전극의 전압은 상기 제1 제어 트랜지스터(TR30)의 출력전극의 전압, 즉 상기 제2 노드(NC)의 전압보다 크거나 같다. 상기 제1 제어 트랜지스터(TR30)의 전류패스는 변경되지 않고, 상기 제1 제어 트랜지스터(TR30)의 열화는 방지된다.

[0133] 이상 실시 예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다. 또한 본 발명에 개시된 실시 예는 본 발명의 기술 사상을 한정하기 위한 것이 아니고, 하기의 특허 청구의 범위 및 그와 동등한 범위 내에 있는 모든 기술 사상은 본 발명의 권리범위에 포함되는 것으로 해석되어야 할 것이다.

### 부호의 설명

[0134] DP: 표시패널 DS1: 제1 기판

DS2: 제2 기판 100: 게이트 구동회로

200: 데이터 구동회로 MCB: 메인 회로기판

SRC1~SRCn: 구동 스테이지 110-1: 제1 출력부

110-2: 제2 출력부 120: 제어부

130: 인버터부 140-1: 제1 풀다운부

140-2: 제2 풀다운부

도면

도면1

도면2

도면3

도면4

## 도면5

도면6

## 도면7

## 도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15