(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4589665号

(P4589665)

(45) 発行日 平成22年12月1日(2010.12.1)

(24) 登録日 平成22年9月17日(2010.9.17)

(51) Int.Cl.

F 1

|             |             |                  |      |      |

|-------------|-------------|------------------|------|------|

| <b>H03F</b> | <b>1/02</b> | <b>(2006.01)</b> | H03F | 1/02 |

| <b>H03F</b> | <b>1/06</b> | <b>(2006.01)</b> | H03F | 1/06 |

| <b>H03F</b> | <b>3/19</b> | <b>(2006.01)</b> | H03F | 3/19 |

| <b>H03F</b> | <b>3/21</b> | <b>(2006.01)</b> | H03F | 3/21 |

| <b>H03F</b> | <b>3/68</b> | <b>(2006.01)</b> | H03F | 3/68 |

B

請求項の数 19 (全 20 頁) 最終頁に続く

|              |                               |           |                                                        |

|--------------|-------------------------------|-----------|--------------------------------------------------------|

| (21) 出願番号    | 特願2004-184669 (P2004-184669)  | (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部 1753 番地 |

| (22) 出願日     | 平成16年6月23日 (2004.6.23)        | (74) 代理人  | 110000350<br>ポレール特許業務法人                                |

| (65) 公開番号    | 特開2005-102146 (P2005-102146A) | (74) 代理人  | 100068504<br>弁理士 小川 勝男                                 |

| (43) 公開日     | 平成17年4月14日 (2005.4.14)        | (74) 代理人  | 100086656<br>弁理士 田中 恭助                                 |

| 審査請求日        | 平成19年2月23日 (2007.2.23)        | (72) 発明者  | 松本 秀俊<br>東京都国分寺市東恋ヶ窪一丁目280 番地<br>株式会社日立製作所 中央研究所内      |

| (31) 優先権主張番号 | 特願2003-305657 (P2003-305657)  | (72) 発明者  | 田上 知紀<br>東京都国分寺市東恋ヶ窪一丁目280 番地<br>株式会社日立製作所 中央研究所内      |

| (32) 優先日     | 平成15年8月29日 (2003.8.29)        |           | 最終頁に続く                                                 |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                                        |

(54) 【発明の名称】 増幅器及びそれを用いた高周波電力増幅器

## (57) 【特許請求の範囲】

## 【請求項 1】

入力信号の第1の低周波成分を増幅して、第1の出力信号及び前記第1の出力信号より電圧レベルが大きい第2の出力信号を出力するDC/DCコンバータと、

前記入力信号の高周波成分及び第2の低周波成分を増幅し、増幅後の高周波成分をハイパスフィルタを介して出力するB級増幅器とを備え、

前記DC/DCコンバータと前記B級増幅器とは並列接続され、

前記第1の出力信号は、前記DC/DCコンバータ及び前記B級増幅器の並列接続出力端子に供給され、

前記第2の出力信号は、前記B級増幅器の電源電圧として前記B級増幅器に供給されることを特徴とする増幅器。

## 【請求項 2】

請求項1において、

前記第1の出力信号と前記B級増幅器の電源電圧とが一定比となるように制御されることを特徴とする増幅器。

## 【請求項 3】

請求項2において、

前記一定比は、前記増幅器を用いるシステムのピークファクタとほぼ等しいことを特徴とする増幅器。

## 【請求項 4】

請求項 2 において、

前記 B 級増幅器への入力信号の前記第 2 の低周波成分が前記入力信号の高周波成分に対して減衰している

ことを特徴とする増幅器。

【請求項 5】

請求項 1 において、

前記 D C / D C コンバータは、前記第 1 の出力信号を出力する第 1 の S 級変調器と前記第 2 の出力信号を出力する第 2 の S 級変調器とを含んで成る

ことを特徴とする増幅器。

【請求項 6】

10

請求項 1 において、

前記増幅器の出力信号を入力信号側に帰還する負帰還ループが形成されている

ことを特徴とする増幅器。

【請求項 7】

請求項 1 において、

前記増幅器の出力信号にオフセットを付加してオフセット電圧を補正する回路を更に具備する

ことを特徴とする増幅器。

【請求項 8】

20

請求項 5 において、

前記第 1 の S 級増幅器の電源電圧よりも高い電源電圧を前記第 2 の S 級増幅器に供給する第 2 の D C / D C コンバータを具備する

ことを特徴とする増幅器。

【請求項 9】

請求項 5 において、

前記第 1 及び第 2 の S 級増幅器にはローパスフィルタを経た前記入力信号が与えられ、前記ローパスフィルタのカットオフ周波数が、前記第 1 及び第 2 の出力信号の電圧値を設定するために用いられる鋸歯形信号の周波数よりも低い

ことを特徴とする増幅器。

【請求項 10】

30

請求項 1 において、

前記増幅器は、

第 1 のオペアンプと第 1 および第 2 の抵抗素子とを含んで成るシユミット回路と、第 2 のオペアンプと第 3 の抵抗素子と第 1 の容量素子とを含んで成る積分回路と、前記第 1 のオペアンプと前記第 2 のオペアンプへのバイアス電圧を供給するためのバイアス端子とを含んで成る発振器と、

第 4 の抵抗素子と第 2 の容量素子とを含んで成るローパスフィルタと、

第 3 のオペアンプと第 1 の電界効果トランジスタと第 1 のダイオードとを含んで成る第 1 の S 級変調器と、

第 4 のオペアンプと第 2 の電界効果トランジスタと第 2 のダイオードとを含んで成る第 2 の S 級変調器と、

第 5 のオペアンプと第 4 および第 5 の抵抗素子とを含んで成る前段増幅器と、第 3 および第 4 の電界効果トランジスタと第 3 および第 4 のダイオードと第 6 および第 7 の抵抗素子とを含んで成る後段増幅器とを有する B 級増幅器と、

前記 B 級増幅器の入力に接続された第 6 のオペアンプと、

第 7 のオペアンプと第 5 の電界効果トランジスタと第 5 のダイオードとインダクタと第 3 の容量素子とを含んで成る昇圧型 D C / D C コンバータと、

前記昇圧型 D C / D C コンバータの入力に接続された第 8 のオペアンプとを具備して成り、

前記シユミット回路の出力は前記積分回路に接続され、前記積分回路の出力は前記シユ

50

ミット回路に帰還され、

前記バイアス端子に電源電圧の略1/2のバイアス電圧が印加されるよう構成され、

前記ローパスフィルタのカットオフ周波数は前記発振器の発振周波数より低くなるよう構成され、

前記第3のオペアンプはコンパレータであり、前記発振器からの入力電圧と前記ローパスフィルタからの入力電圧とを比較して前記第1の電界効果トランジスタをオンオフ動作させるよう構成され、

前記第4のオペアンプはコンパレータであり、前記発振器からの入力電圧と前記ローパスフィルタからの入力電圧とを比較して前記第2の電界効果トランジスタをオンオフ動作させるよう構成され、

前記前段増幅器は前記第6のオペアンプからの入力信号を非反転増幅し、前記後段増幅器は非反転増幅された前記入力信号を電流増幅し、

前記第3および第4のダイオードのバイアス電流は前記第6および第7の抵抗素子から供給され、

前記第7のオペアンプはコンパレータであり、前記発振器からの入力電圧と前記第8のオペアンプからの入力電圧とを比較して前記第5の電界効果トランジスタをオンオフ動作させるよう構成され、

前記第6のオペアンプの出力信号が前記ローパスフィルタに入力され、

前記第3の電界効果トランジスタのソース電極に前記第2のS級変調器の出力信号が供給され、

前記B級増幅器は、前記第6のオペアンプの入力信号の高周波成分を増幅して出力し、前記第1のS級変調器は、前記第6のオペアンプの入力信号の低周波成分を増幅して出力する

ことを特徴とする増幅器。

【請求項11】

請求項10において、

前記シュミット回路の出力電圧は電源電圧によって示される正または接地電圧によって示される0のいずれかの値を取り、前記シュミット回路の出力電圧が正の場合、前記積分回路の出力電圧は略一定のスロープで減少し、

前記積分回路の出力電圧が前記シュミット回路のしきい電圧より小さい場合、前記シュミット回路の出力電圧は0であり、かつ、前記積分回路の出力電圧は略一定のスロープで増加し、

前記積分回路の出力電圧が前記シュミット回路のしきい電圧より大きい場合、前記シュミット回路の出力電圧は正であり、かつ、前記積分回路の出力電圧は略一定のスロープで減少する

ことを特徴とする増幅器。

【請求項12】

請求項10において、

前記発振器からの入力電圧は三角波であり、該三角波の周期で前記第1の電界効果トランジスタはオンオフ動作し、

前記ローパスフィルタからの入力電圧が低い程、前記三角波の1周期の中で前記発振器からの入力電圧の方が高い期間が長くなり、前記第1の電界効果トランジスタがオフである期間が長くなり、

前記ローパスフィルタからの入力電圧が高い程、前記三角波の1周期の中で前記発振器からの入力電圧の方が低い期間が長くなり、前記第1の電界効果トランジスタがオンである期間が長くなる

ことを特徴とする増幅器。

【請求項13】

請求項10において、

前記第1の電界効果トランジスタのソース電極に電源電圧が印加され、前記第1の電界

10

20

30

40

50

効果トランジスタのオン時に前記第1のS級変調器の出力が前記電源電圧まで上昇し、前記第1の電界効果トランジスタのオフ時に前記第1のS級変調器の出力が前記第1のダイオードにクリップされるまで下降し、

前記第1のS級変調器の出力は平滑化され、前記ローパスフィルタからの入力電圧に比例した信号となる

ことを特徴とする増幅器。

【請求項14】

請求項10において、

前記第2の電界効果トランジスタのソース電極に前記昇圧型DC/DCコンバータの出力電圧が印加され、前記第2の電界効果トランジスタのオン時に前記第2のS級変調器の出力が前記昇圧型DC/DCコンバータの出力電圧まで上昇し、前記第2の電界効果トランジスタのオフ時に前記第2のS級変調器の出力が前記第2のダイオードにクリップされるまで下降し、

前記第2のS級変調器の出力は平滑化され、前記ローパスフィルタからの入力電圧に比例した信号となる

ことを特徴とする増幅器。

【請求項15】

請求項10において、

前記昇圧型DC/DCコンバータの昇圧比をjとした場合、前記第2のS級変調器の出力を平滑化した信号レベルは、前記第1のS級変調器の出力を平滑化した信号レベルのj倍である

ことを特徴とする増幅器。

【請求項16】

請求項10において、

前記第3および第4のダイオードはレベルシフトダイオードであり、前記第3および第4のトランジスタのしきい電圧相当分、信号電圧をシフトさせるものである

ことを特徴とする増幅器。

【請求項17】

請求項10において、

前記発振器からの入力電圧は三角波であり、該三角波の周期で前記第5の電界効果トランジスタはオンオフ動作し、

前記第8のオペアンプからの入力電圧が高い程、前記三角波の1周期の中で前記発振器からの入力電圧の方が低い期間が長くなり、前記第5の電界効果トランジスタがオフである期間が長くなり、前記昇圧型DC/DCコンバータの出力電圧が増加し、

前記第8のオペアンプからの入力電圧が低い程、前記三角波の1周期の中で前記発振器からの入力電圧の方が高い期間が長くなり、前記第5の電界効果トランジスタがオンである期間が長くなり、前記昇圧型DC/DCコンバータの出力電圧が減少する

ことを特徴とする増幅器。

【請求項18】

入力された高周波信号を飽和動作によって増幅する搬送波増幅器と、

前記高周波信号の包絡線成分を増幅し、増幅後の出力信号を前記搬送波増幅器の電源電圧として出力する包絡線増幅器とを備え、

前記包絡線増幅器は、

前記高周波信号の包絡線成分の第1の低周波成分を増幅して、第1の出力信号及び前記第1の出力信号より電圧レベルが大きい第2の出力信号を出力するDC/DCコンバータと、

前記高周波信号の包絡線成分の高周波成分及び第2の低周波成分を増幅し、増幅後の高周波成分をハイパスフィルタを介して出力するB級増幅器とを備え、

前記DC/DCコンバータと前記B級増幅器とは並列接続され、

前記第1の出力信号は、前記DC/DCコンバータ及び前記B級増幅器の並列接続出力

10

20

30

40

50

端子に供給され、

前記第2の出力信号は、前記B級増幅器の電源電圧として前記B級増幅器に供給されることを特徴とする高周波電力増幅器。

**【請求項19】**

入力された高周波信号を飽和動作によって増幅する搬送波増幅器と、

電源電圧制御信号を入力して該搬送波増幅器の電源電圧を生成する電源電圧調整回路と

を備え、

前記電源電圧調整回路は、

前記電源電圧制御信号の第1の低周波成分を増幅して、第1の出力信号及び前記第1の

出力信号より電圧レベルが大きい第2の出力信号を出力するDC/DCコンバータと、 10

前記電源電圧制御信号の高周波成分及び第2の低周波成分を増幅し、増幅後の高周波成

分をハイパスフィルタを介して出力するB級増幅器とを備え、

前記DC/DCコンバータと前記B級増幅器とは並列接続され、

前記第1の出力信号は、前記DC/DCコンバータ及び前記B級増幅器の並列接続出力

端子に供給され、

前記第2の出力信号は、前記B級増幅器の電源電圧として前記B級増幅器に供給され

ることを特徴とする高周波電力増幅器。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、高周波電力増幅器に係り、特に、携帯電話等の無線機器の送信部に適用して好適な高周波電力増幅器に関する。

**【背景技術】**

**【0002】**

携帯電話は近年急速に普及し、通信データ量が増大している。このため、W-CDMA (wideband code division multiple access) 等の大容量通信方式の導入が進められている。

**【0003】**

携帯電話端末の送信部に用いられる高周波電力増幅器は、端末構成部品の中でも消費電力が大きく、バッテリー持続時間を増やすため、その高効率化が重要である。また、W-CDMA 等の大容量通信方式に用いるには、高効率化に加えてその低歪み化が必須となる。

**【0004】**

ところが、高周波電力増幅器に通常用いられるAB級増幅器では、高効率と低歪みを同時に達成することができない。AB級増幅器は、低出力時には線形動作するため低歪みであるが効率が低く、高出力時には飽和動作するため高効率であるが歪みが多い。

**【0005】**

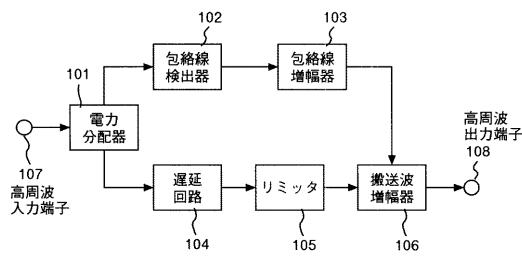

高効率かつ低歪みを実現する電力増幅器として、EER (envelope elimination and restoration) 型増幅器が例えば特許文献1に開示され、知られている。同文献に記載されたEER型増幅器の一例を図11に示す。 40

**【0006】**

入力端子107に入力された高周波信号は、電力分配器101によって包絡線検出器102と遅延回路104に分配される。包絡線検出器102では、高周波信号の包絡線成分が検出される。この包絡線成分は、包絡線増幅器103で増幅され、搬送波増幅器106の電源端子に供給される。また、遅延回路104は、包絡線検出器102と包絡線増幅器103の遅延時間を補償する。遅延回路104の出力信号は、リミッタ105で振幅制限され、搬送波増幅器106で増幅される。

**【0007】**

高周波信号の包絡線成分は、リミッタ105で一旦失われるが、搬送波増幅器106の電源端子に包絡線成分が供給されるので、失われた包絡線成分が搬送波増幅器106にお

10

20

30

40

50

いて回復される。E E R型増幅器は、入力電力によらずに搬送波増幅器106が常に飽和動作するよう設計されているため、低出力時・高出力時とも高効率である。飽和動作の欠点である歪みの問題は、このように搬送波増幅器106が高周波信号の包絡線成分を回復することによって解決され、出力端子108において歪の少ない高電力の高周波信号が得られる。

【0008】

E E R型増幅器全体を高効率・低歪み化するためには、搬送波増幅器106だけでなく、包絡線増幅器103も高効率・低歪み化する必要がある。包絡線信号は高周波信号の搬送波に比べて低周波であるが、W - C D M Aのような広帯域システムでは包絡線成分と云えども周波数帯域が広く、数M H zに及ぶ。

10

【0009】

一方、包絡線増幅器103に良く用いられるD C / D C コンバータは、その周波数帯域が高々100 k H z程度であるので、D C / D C コンバータをそのままW - C D M Aのような広帯域システムの包絡線増幅器103に用いることができない。

【0010】

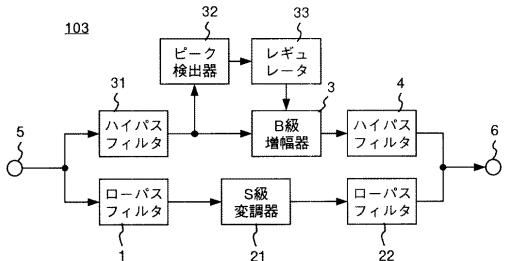

特許文献1で開示された包絡線増幅器103の例を図12に示す。この従来例では、S級変調器21とB級増幅器3の並列接続が用いられる。端子5に入力された包絡線信号は、ローパスフィルタ1、ハイパスフィルタ31で低周波成分と高周波成分に分離される。低周波成分はS級変調器21で増幅され、高周波成分はB級増幅器3で増幅される。低周波成分と高周波成分はそれぞれローパスフィルタ22、ハイパスフィルタ4を通過した後に合成され、高電力の包絡線信号が出力端子6に出力される。

20

【0011】

S級変調器21とローパスフィルタ22は、D C / D C コンバータを構成し、高効率であるが挾帯域である。一方、B級増幅器3は広帯域であるが低効率である。そこで、S級変調器21とB級増幅器3を並列接続することで、全体の広帯域・高効率化を実現している。

【0012】

更に、この従来例では、B級増幅器3の効率向上のため、ピーク検出器32とレギュレータ33からなる電源回路を付加している。この電源回路は、ピーク検出器32で高周波成分のピーク値を検出し、このピーク値でレギュレータ33を制御することにより、B級増幅器3の電源電圧を最小限に低くし、B級増幅器3を高効率化している。

30

【0013】

【特許文献1】米国特許第6,084,468号明細書

【発明の開示】

【発明が解決しようとする課題】

【0014】

上記の包絡線増幅器103は広帯域・高効率であるが、周波数帯域が広いW - C D M Aの包絡線信号を増幅するには不十分である。以下に説明するように、数M H zに及ぶ包絡線信号が入力された場合に、ピーク検出器32とレギュレータ33からなる電源回路が高周波成分のピーク値変化に追随することができなくなり、B級増幅器3においてクリッピング歪みが発生する。

40

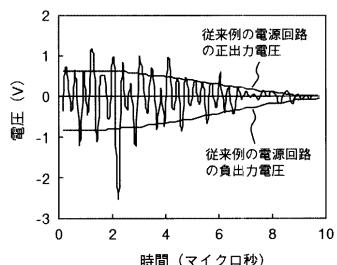

【0015】

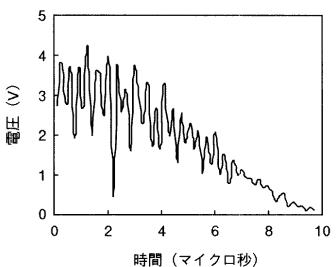

図13にW - C D M Aの包絡線信号を、図14にその高周波成分を示した。高周波成分はマイクロ秒以下の間隔でピークを持つが、そのピーク値は不規則に増減している。このような場合、従来例の電源回路が正常動作するためには、レギュレータ33がマイクロ秒以下の短時間で応答する必要がある。

【0016】

高効率化の目的から、レギュレータ33にはD C / D C コンバータを用いるのが妥当であるが、D C / D C コンバータは高速のものでも10マイクロ秒程度の時定数を持つので、マイクロ秒以下の短時間には応答しない。その結果、電源回路出力はD C / D C コンバ

50

ータの時定数で平滑化されてしまう。

【0017】

図14に従来例の電源回路の出力電圧を重ねて示した。なお、従来例のB級増幅器3は正電源と負電源を必要とするので、それぞれに対応する電源回路出力電圧を示した。大きい信号ピークは、電源回路の出力電圧を超てしまっている。実際の回路動作においてB級増幅器の出力電圧は電源電圧を超えることができないから、包絡線増幅器103は、大きい信号ピークではクリッピング歪みを発生する。

【0018】

本発明の目的は、クリッピング歪みのない広帯域・高効率・低歪みの増幅器及びそれを用いた、広帯域無線通信システムに適用可能な高効率・低歪みの高周波電力増幅器を実現することにある。

10

【課題を解決するための手段】

【0019】

即ち、上記目的を達成するための本発明の増幅器は、入力信号の低周波成分を増幅するDC/DCコンバータと、該入力信号を増幅して増幅後の高周波成分を出力するB級増幅器とを備えており、DC/DCコンバータとB級増幅器は並列接続され、上記低周波成分によって該B級増幅器の電源電圧が制御されることを特徴とする。

【0020】

例えば、入力信号が包絡線成分である場合、後で詳述するように、包絡線成分の上限値と該包絡線成分の低周波成分との比がほぼ一定であり、その比が無線通信システムに固有の定数であるということが本発明において利用される。従ってその場合、本発明では、B級増幅器の電源電圧が上限値と一定比を持つ包絡線成分の低周波成分によって制御されることになり、本発明の上記増幅器は、包絡線成分の上限値に対してクリッピングを起こすことなく包絡線成分を増幅することが可能になる。それにより、広帯域・高効率・低歪みの増幅器が実現され、広帯域無線通信システムに適用可能な高効率・低歪みの高周波電力増幅器が実現される。なお、B級増幅器の電源電圧を入力信号の低周波成分と一定比を保つように制御することが特に好ましい。更に、この一定比は、該増幅器を用いる無線通信システムのピークファクタとほぼ等しいことが望ましい。

20

【発明の効果】

【0021】

30

本発明によれば、B級増幅器においてクリッピング歪みの発生が回避され、広帯域・高効率・低歪みの増幅器を実現することができる。この増幅器を搬送波増幅器に電源電圧を供給する包絡線増幅器として用いることにより、広帯域の無線通信システムに用いて好適の高効率・低歪みの高周波電力増幅器を実現することができる。

【発明を実施するための最良の形態】

【0022】

以下、本発明に係る増幅器及びそれを用いた高周波電力増幅器を図面に示した幾つかの発明の実施形態を参照して更に詳細に説明する。なお、図1、図3～図5及び図7～図10における同一の符号は、同一物又は類似物を表示するものとする。

【0023】

40

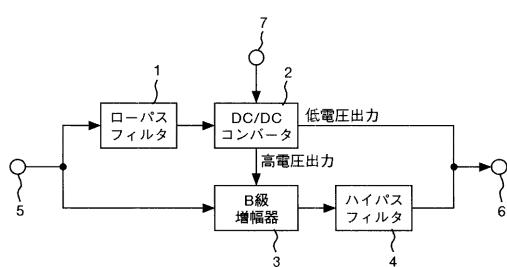

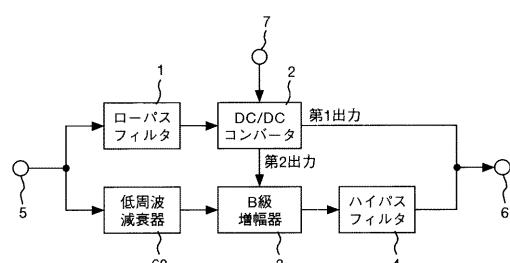

本発明による増幅器の第1の実施形態を図1に示す。図1において、1は、入力端子5に入力した入力信号即ち包絡線成分の高周波成分を除去するローパスフィルタ、2は、ローパスフィルタ1の出力信号を増幅するDC/DCコンバータ、3は、入力端子5からの包絡線成分を増幅するB級増幅器、4は、B級増幅器3の低周波成分を除去するハイパスフィルタを示す。DC/DCコンバータ2は2つの出力端子を持ち、一方は増幅器の出力端子6に、他方はB級増幅器3の電源端子に接続されている。ハイパスフィルタ4の出力端子は出力端子6に接続されている。

【0024】

本実施形態では、ローパスフィルタ1の出力信号を増幅するDC/DCコンバータ2は、電圧利得がピークファクタ倍異なる、2種類の出力信号を発生する。このピークファク

50

タについては後に詳述する。電圧利得の小さい低電圧出力は出力端子 6 に供給される。電圧利得の大きい高電圧出力は B 級増幅器 3 に電源として供給される。B 級増幅器 3 は入力端子 5 からの入力信号を増幅する。B 級増幅器 3 の電圧利得は、D C / D C コンバータ 2 の低電圧出力の電圧利得に等しい。

【 0 0 2 5 】

本発明の増幅器即ち包絡線増幅器は、図 1 2 に示した従来例と同じく、D C / D C コンバータ 2 と B 級増幅器 3 の並列接続を用い、包絡線信号の低周波成分を D C / D C コンバータ 2 で、高周波成分を B 級増幅器 3 で増幅しているので、広帯域・高効率である。

【 0 0 2 6 】

しかし、包絡線増幅器として用いられる本発明の増幅器は、B 級増幅器 3 の電源電圧制御方法が図 1 2 に示した従来例と異なる。従来例では、上述のように、包絡線信号の高周波成分ピーク値を用いて B 級増幅器 3 の電源電圧を制御するため、クリッピング歪みの問題があった。本発明では、以下に説明するように、包絡線信号の低周波成分を用いて B 級増幅器 3 の電源電圧を制御することにより、クリッピング歪みを発生させずに B 級増幅器 3 を高効率化している。

【 0 0 2 7 】

本発明では、包絡線信号の上限値が包絡線信号の平均値と相関を持つという、広帯域無線通信システムに特有の性質が利用される。図 1 3 に示したように、包絡線信号は不規則に増減する。しかし、その値は無制限に大きくなるわけではなく、一定の上限値が有る。この上限値は、包絡線信号の低周波成分、即ち平均値と比例関係にある。

【 0 0 2 8 】

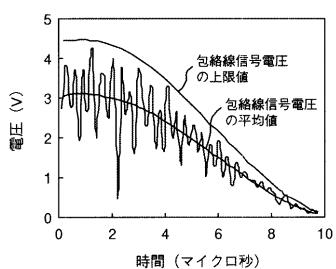

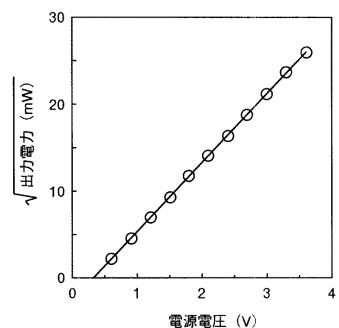

図 2 には、包絡線信号電圧に加えて、その平均値と上限値を同時に示した。(包絡線信号電圧の上限値) / (包絡線信号電圧の平均値) で与えられるピークファクタは、無線通信システムのそれぞれに固有の定数で、包絡線信号の平均値が変化してもピークファクタは一定である。同様に、包絡線信号の下限値も包絡線信号の平均値に比例するが、特に W - C D M A 信号の場合は、比例係数が 0 である。図 2 は、そのような W - C D M A 信号の場合を示している。

【 0 0 2 9 】

B 級増幅器の電源電圧  $V_{bp}$ 、平均出力電圧  $V_{ba}$ 、包絡線増幅器の最大出力電圧  $V_{op}$ 、平均出力電圧  $V_{oa}$ 、最小出力電圧  $V_{om}$  とすると、B 級増幅器がクリッピング歪みを発生しない条件は、

$$V_{bp} - V_{ba} \leq V_{op} - V_{oa}, \quad V_{ba} \leq V_{oa} - V_{om} \dots (1)$$

である。ピークファクタ  $F_p = V_{op} / V_{oa}$ 、 $F_m = V_{om} / V_{oa}$  を用いると、式(1)は、

$$V_{bp} - V_{ba} \leq (F_p - 1) V_{oa}, \quad V_{ba} \geq (1 - F_m) V_{oa} \dots (2)$$

となる。

【 0 0 3 0 】

本発明では、B 級増幅器の電源電圧  $V_{bp}$  及び B 級増幅器の平均出力電圧  $V_{ba}$  は、包絡線増幅器の平均出力電圧  $V_{oa}$  に対して比例するように制御される。従って、制御係数  $K_{bp} = V_{bp} / V_{oa}$ 、 $K_{ba} = V_{ba} / V_{oa}$  とすると、

$$K_{bp} = K_{ba} = F_p, \quad K_{ba} = 1 - F_m \dots (3)$$

となる。これが、本発明の基本式である。特に、制御係数  $K_{ba} = 1$  または  $K_{bp} = 1$  とした場合には、

$$K_{ba} = 1, \quad K_{bp} = F_p, \quad F_m = 0 \dots (4)$$

$$K_{bp} = 1, \quad 2 - F_p = K_{ba} = 1 - F_m, \quad 1 - F_p = F_m \dots (5)$$

となる。これらの場合は制御が簡単になるので、実用上特に有用である。

【 0 0 3 1 】

但し、式(4)の第 3 式は常に成立するが、式(5)の第 3 式は常に成立するとは限らず、式(5)の適用範囲は限られる。式(3)または式(4)、(5)が成立すれば、クリッピング歪みは抑えられる。不等式両辺の差が大きいほど、歪みに対するマージンは大

10

20

30

40

50

きくなるが効率は低下する。不等式両辺の差が小さいほど歪みに対するマージンは小さくなるが効率は向上する。

【0032】

本実施形態では、用途をW-CDMA端末としている。この場合、前述の説明から、 $F_p - F_m > 1$ なので、式(5)を適用することができない。そこで、式(4)を満たすように制御係数 $K_{bp} = F_p$ ,  $K_{ba} = 1$ が設定される。即ち、(a) B級増幅器の電源電圧 $V_{bp}$ は、包絡線増幅器の平均出力電圧 $V_{oa}$ のピークファクタ倍となるように制御される。(b) B級増幅器の平均出力電圧 $V_{ba}$ は、包絡線増幅器の平均出力電圧 $V_{oa}$ と等しくなるように制御される。

【0033】

本実施形態では、入力信号の低周波成分をローパスフィルタ1で検出し、この低周波成分でD/C/D/Cコンバータ2を制御して、入力信号の低周波成分に比例しつつその比例係数がピークファクタ倍異なる2出力を生成し、比例係数の小さい低電圧出力を出力端子6に供給し、比例係数の大きい高電圧出力をB級増幅器3に供給することにより、上記(a)の条件を実現することができた。更に、本実施形態では、D/C/D/Cコンバータ2の低電圧出力の電圧利得とB級増幅器3の電圧利得を等しくしているので、入力信号をそのままB級増幅器に与えることによって上記(b)の条件を容易に実現することができた。

【0034】

本実施形態では、制御係数 $K_{bp}$ をピークファクタ $F_p$ に等しくした場合について説明した。しかし実際の設計では、常に $K_{bp} = F_p$ とは限らない。歪みの許容度が大きいシステムに対しては、意図的に $K_{bp} < F_p$ として更に高効率化する設計も可能である。また、歪みの許容度が小さいシステムに対しては、製造マージン等を考慮して意図的に $K_{bp} > F_p$ とする設計も可能である。これらの設計も、本発明の動作原理を利用して可能となるものであり、本発明の範疇に含まれる。

【0035】

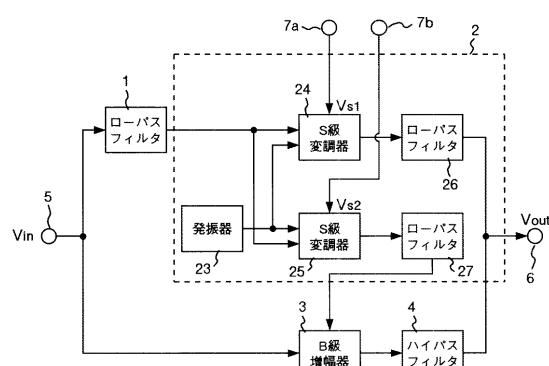

本実施形態の増幅器の構成のより詳細を図3示す。包絡線増幅器は、ローパスフィルタ1、発振器23、第1のS級変調器24、第2のS級変調器25、第1のローパスフィルタ26、第2のローパスフィルタ27、B級増幅器3、ハイパスフィルタ4、入力端子5、出力端子6、第1の電源端子7a、第2の電源端子7bによって構成される。発振器23、第1のS級変調器24、第2のS級変調器25、第1のローパスフィルタ26、第2のローパスフィルタ27が、図1のD/C/D/Cコンバータ2を構成する。

【0036】

ローパスフィルタ1により入力信号から抽出された低周波成分は、第1のS級変調器24と第2のS級増幅器25に入力される。また、発振器23からの鋸歯形信号が、第1のS級変調器24と第2のS級増幅器25に入力される。第1のS級変調器24は、第1の電源端子7aから電源電圧 $V_{s1}$ の供給を受け、低周波成分と鋸歯形信号でパルス幅変調された、振幅 $V_{s1}$ の矩形波を発生する。この矩形波は、第1のローパスフィルタ26で平滑化され、出力端子6に供給される。

【0037】

第2のS級変調器25は、第2の電源端子7bから電源電圧 $V_{s2}$ の供給を受け、低周波成分と鋸歯形信号パルス幅変調された、振幅 $V_{s2}$ の矩形波を発生する。この矩形波は、第2のローパスフィルタ27で平滑化され、B級増幅器3の電源端子に供給される。また、入力信号は、B級増幅器3で増幅され、ハイパスフィルタ4で低周波成分を除かれて、出力端子6に供給される。

【0038】

包絡線増幅器において、低歪み・高効率動作を実現するために、電源電圧 $V_{s1}$ ,  $V_{s2}$ が適切に設定される。第1のS級変調器24と第2のS級変調器25の入力信号は共通であるから、2つの出力矩形波の違いは振幅のみであり、第1のローパスフィルタ26、第2のローパスフィルタ27で平滑化して得られる2つの出力電圧は、常に一定の電圧比を持つ。この電圧比は、元の矩形波の振幅比、即ちS級変調器24、25の電源電圧比で

決定される。

【0039】

従って、第1のS級変調器24と第2のS級変調器25の電源電圧比 $V_{s2}/V_{s1}$ を増幅したい変調信号のピークファクタに設定すれば、B級増幅器3に供給される電源電圧は、常に低周波成分出力のピークファクタ倍となるように制御することができる。また、第1のS級変調器24と第1のローパスフィルタ26による電圧増幅率とB級増幅器3の電圧増幅率を揃えるためには、 $V_{s2}/V_{s1}$ の比を保ったまま、 $V_{s1}$ を調整すれば良い。以上により、包絡線増幅器において、本発明の低歪み・高効率動作が実現される。

【0040】

本実施形態の動作原理より、2つのS級変調器24, 25の特性は揃っていることが望ましい。但し、出力電圧波形が揃えば良いので、2つのS級変調器24, 25を同一サイズの部品で構成する必要は無く、構成部品間の相対関係を保ったままのスケーリングが可能である。但し、2つのローパスフィルタ26, 27も同時にスケーリングする必要がある。スケーリングが可能であることを利用すると、2つのS級変調器24, 25で平均出力電流値が異なる場合に、平均出力電流値が小さい側を小型化することができる。

10

【0041】

本実施形態では、動作状態が揃った2つのS級変調器24, 25を用いているので、2つの電源端子7a, 7bの電圧比という単純な手段で、B級増幅器3の電源電圧を最適条件に制御することができる。温度等の環境条件変化に対しても、2つのS級変調器24, 25の特性が同一方向に変化する限りB級増幅器3の動作状態は最適のまま保たれるので、包絡線増幅器は動作マージンが大きく安定動作する。

20

【0042】

以上、本実施形態により、クリッピング歪みを発生させずにB級増幅器3を高効率化することができ、広帯域・高効率・低歪みの包絡線増幅器即ち増幅器を実現することができた。本実施形態の包絡線増幅器は、周波数帯域10MHz、効率85%を実現し、W-C DMAの包絡線信号増幅時にもクリッピング歪みを発生しない。

【0043】

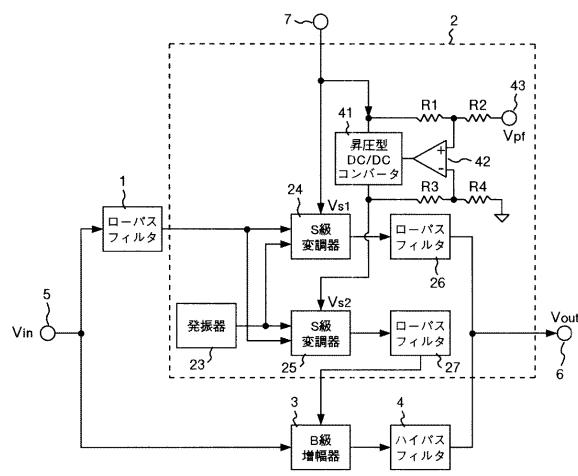

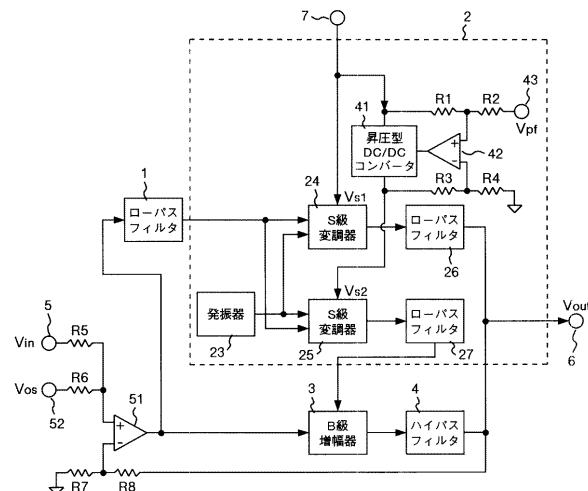

本発明による増幅器の第2の実施形態を図4に示す。本実施形態は、図3の構成から第2の電源端子7bを除き、第1の電源端子7a(以下では、電源端子7とする)と第2のS級変調器25の間に、昇圧型DC/DCコンバータ41、オペアンプ42、抵抗素子R1, R2, R3, R4、及びピークファクタ設定端子43を含む $V_{s2}$ 調整回路を加えたものである。

30

【0044】

昇圧型DC/DCコンバータ41の電源端子は包絡線増幅器の電源端子7に、出力端子は第2のS級変調器25の電源端子に接続されている。オペアンプ42の非反転入力端子は、抵抗R1を介して包絡線増幅器の電源端子7に接続されると共に、抵抗R2を介してピークファクタ設定端子43に接続されている。

【0045】

反転入力端子は、抵抗R3を介して昇圧型DC/DCコンバータ41の出力端子に接続されると共に、抵抗R4を介してグランド(接地)に接続されている。オペアンプ42の出力端子は、昇圧型DC/DCコンバータ41の制御端子に接続されている。

40

【0046】

抵抗値を $R1 = R2 = R3 = R4$ とすることで、加算回路が構成され、包絡線増幅器の電源端子7の電圧 $V_{s1}$ 、ピークファクタ設定端子43の電圧 $V_{pf}$ 、昇圧型DC/DCコンバータ41の出力電圧 $V_{s2}$ に対して、 $V_{s2} = V_{s1} + V_{pf}$ となる。従って、ピークファクタ設定端子43に $V_{s2}$ と $V_{s1}$ の差分を印加すれば、 $V_{s2}$ を所望の値に制御することができる。

【0047】

本実施形態では、昇圧型DC/DCコンバータ41を用いたことにより、包絡線増幅器が必要とする電源電圧が $V_{s1}$ のみとなり、 $V_{s1}$ 、 $V_{s2}$ の2種類の電源供給を受ける

50

図3の実施形態と比べて、包絡線増幅器を使用する際の外部回路が簡略化できるという利点がある。本実施形態の代替案として、外部からV<sub>s</sub>2の電源供給を受け、降圧型DC/DCコンバータでV<sub>s</sub>1を発生させる方法も考えられる。

【0048】

しかし、携帯機器のように低電圧化要求が強い用途では、より低電圧のV<sub>s</sub>1の電源供給を受ける本実施形態の方が有利である。また、本実施形態では、昇圧型DC/DCコンバータ41の出力電圧を外部制御できるピークファクタ設定端子43を設けた。ピークファクタは適用システムにより値が異なるので、設定端子43を設けることにより、单一品種で複数システムに適用することができ、高周波電力増幅器の汎用性が高まる。

【0049】

本発明による増幅器の第3の実施形態を図5に示す。本実施形態は、図4の構成に、オペアンプ51、抵抗素子R5、R6、R7、R8を用いた負帰還回路とオフセット調整端子52を加えたものである。この負帰還回路により、出力端子6における出力信号を入力信号側に帰還する負帰還ループが形成される。

【0050】

オペアンプ51の非反転入力端子は、抵抗R5を介して包絡線増幅器の入力端子5に接続されると共に、抵抗R6を介してオフセット設定端子52に接続され、更に、抵抗R7を介してグランドに、抵抗R8を介して包絡線増幅器の出力端子6に接続されている。抵抗値はR5=R7、R6=R8、R6/R5=Kとした。

【0051】

これは重み付き加算回路であり、包絡線増幅器の入力端子5の電圧V<sub>in</sub>、オフセット設定端子52の電圧V<sub>os</sub>に対し、包絡線増幅器の出力端子6の電圧V<sub>out</sub>=K×V<sub>in</sub>+V<sub>os</sub>となる。ここで重み付き加算回路を用いたのは、以下に述べる補正を行なうためである。

【0052】

包絡線増幅器を搬送波増幅器と組合わせてEER型増幅器を構成する際には、搬送波増幅器の制御特性を考慮する必要がある。飽和動作している搬送波増幅器の電源電圧V<sub>sup</sub>と出力電力P<sub>out</sub>の関係は、図6のようになる。これは、HBT(Heterojunction bipolar transistor)を用いた搬送波増幅器の例である。P<sub>out</sub>はV<sub>sup</sub>の2乗にはほぼ比例するので、縦軸にP<sub>out</sub>の平方根を用いることによって直線関係が得られている。但し、この直線関係をP<sub>out</sub>=0に外挿した点のV<sub>sup</sub>は、0ではなく、ある正電圧(オフセット電圧)となっている。

【0053】

搬送波増幅器を線形性良く電源変調するためには、このオフセット電圧を補正する必要がある。包絡線信号にオフセット電圧相当分を予め加算してから、搬送波増幅器の電源端子に印可すれば、搬送波増幅器のオフセット電圧が相殺され、線形性のよい電源変調が可能となる。本実施形態の包絡線増幅器では、重み付き加算回路を用いてこのオフセット電圧を補正する機能を実現しており、補正電圧は外部から任意に設定することができる。

【0054】

また、本実施形態の増幅器即ち包絡線増幅器では、負帰還回路の効果により、利得の周波数依存性が改善されている。本実施形態の包絡線増幅器は低周波成分と高周波成分を別の経路で増幅しているので、部品の製造ばらつき等を考慮すると、各経路の利得を正確に揃えることが困難な場合がある。本実施形態では負帰還回路によりこの問題が解決されている。オペアンプ51が充分な利得を持っているので、帰還回路の利得は実質的にオペアンプ51に接続した抵抗値で決定され、増幅経路によらずほぼ一定となる。

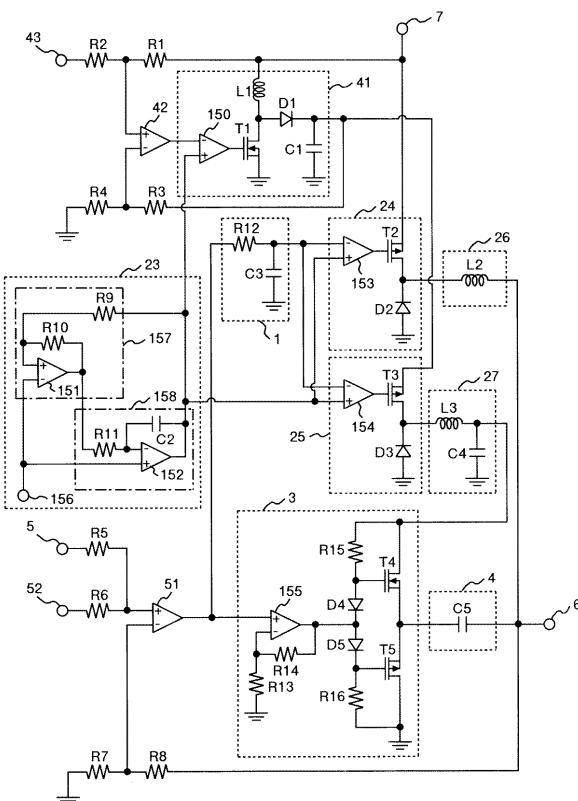

【0055】

本実施形態の増幅器の詳細な回路の例を図15に示す。発振器23として、シュミット回路157と積分回路158からなる良く知られた三角波発振器が用いられる。オペアンプ151、抵抗素子R9、R10がシュミット回路である。オペアンプ152、抵抗素子R11、容量素子C2が積分回路である。シュミット回路157の出力は積分回路158に

10

20

30

40

50

接続され、積分回路 158 の出力はシュミット回路 157 に抵抗素 R9 を介して帰還されている。オペアンプ 151、152 へのバイアス電圧を供給するためのバイアス端子 156 には電源電圧の約 1/2 のバイアス電圧が印加されている。

#### 【0056】

シュミット回路 157 の出力電圧は正(電源電圧)または 0(接地電圧)のいずれかの値をとる。シュミット回路 157 の出力電圧が正の場合、積分回路 158 の出力電圧は一定スロープで減少する。積分回路 158 の出力電圧がシュミット回路 157 のしきい電圧より小さくなると、シュミット回路 157 の出力電圧は 0 に変わり、積分回路 158 の出力電圧は一定スロープで増加する。積分回路 158 の出力電圧がシュミット回路 157 のしきい電圧より大きくなると、シュミット回路 157 の出力電圧は正に戻り、積分回路 158 の出力電圧は再び一定スロープで減少する。この動作の繰り返しにより、積分回路 158 の出力に三角波が得られる。この三角波発振器の発振周波数は、 $f_o = (R10 / R9) / (4 \times C2 \times R11)$  となる。本実施形態では、 $R9 = 8.2k$ 、 $R10 = 10k$ 、 $R11 = 300$ 、 $C2 = 1000 \mu F$  であり、発振周波数  $f_o$  は約 1MHz である。10

#### 【0057】

ローパスフィルタ 1 には、抵抗素子 R12 と容量素子 C3 からなる RC フィルタが用いられる。ローパスフィルタ 1 の出力電圧が発振器 23 の発振周波数  $f_o$  より高い周波数成分を持つと、S 級変調器 24、25 の出力レベルが切り替わる際にチャタリングを起こすので、それを避けるため、ローパスフィルタ 1 のカットオフ周波数  $f_c$  は発振器 23 の発振周波数  $f_o$  より低く設定される。本実施形態では、 $R12 = 1.5k$ 、 $C3 = 1nF$  であり、カットオフ周波数  $f_c$  は約 100kHz である。20

#### 【0058】

S 級変調器 24 は、オペアンプ 153、トランジスタ T2、ダイオード D2 で構成される。トランジスタ T2 は、p-MOSFET である。インダクタ L2 はローパスフィルタ 26 に相当する。本実施形態では、 $L2 = 7.5 \mu H$  である。

#### 【0059】

オペアンプ 153 はコンパレータであり、発振器 23 からの入力電圧とローパスフィルタ 1 からの入力電圧を比較し、トランジスタ T2 をオンオフさせる。発振器 23 からの入力電圧が三角波なので、その周期でトランジスタ T2 はオンオフされる。ローパスフィルタ 1 からの入力電圧が低い程、1 周期の中で発振器 23 からの入力電圧の方が高い期間が長くなり、トランジスタ T2 がオフの期間が長くなる。逆に、ローパスフィルタ 1 からの入力電圧が高い程、トランジスタ T2 がオンの期間が長くなる。このように、ローパスフィルタ 1 からの入力電圧でトランジスタ T2 がオンの期間が変調される。トランジスタ T2 のソース電極が電源端子 7 に接続されているため、S 級変調器 24 の出力は、トランジスタ T2 がオンの時には電源電圧まで上昇する。トランジスタ T2 がオフのときには、S 級変調器 24 の出力はダイオード D2 にクリップされるまで下降する。S 級変調器 24 の出力はローパスフィルタ 26 で平滑化され、ローパスフィルタ 1 からの入力電圧に比例した信号となる。即ち、B 級増幅器 3 の出力は、ローパスフィルタ 1、26 で高周波成分を除かれ、低周波成分が出力端子 6 に供給される。30

#### 【0060】

S 級変調器 25 は、オペアンプ 154、トランジスタ T3、ダイオード D3 で構成される。トランジスタ T3 は、p-MOSFET である。また、ローパスフィルタ 27 は、インダクタ L3 と容量素子 C4 で構成される。本実施形態では、 $L3 = 7.5 \mu H$ 、 $C4 = 300nF$  である。

#### 【0061】

S 級変調器 25 の動作は、S 級変調器 24 と同様であるが、出力電圧が異なっている。トランジスタ T3 のソース電極が昇圧型 DC/DC コンバータ 41 の出力に接続されているので、トランジスタ T3 がオンのときには、S 級変調器 25 の出力は昇圧型 DC/DC コンバータ 41 の出力電圧まで上昇する。S 級変調器 25 の出力はローパスフィルタ 27 40

で平滑化され、ローパスフィルタ 1 からの入力電圧に比例した信号となる。DC / DC コンバータ 4 1 の昇圧比を  $j$  とすると、S 級変調器 2 5 の出力を平滑化した信号は、S 級変調器 2 4 の出力を平滑化した信号の  $j$  倍となる。

#### 【0062】

B 級増幅器 3 は、オペアンプ 1 5 5、抵抗素子 R 1 3、R 1 4 からなる前段増幅器と、トランジスタ T 4、T 5、ダイオード D 4、D 5、抵抗素子 R 1 5、R 1 6 からなる後段増幅器の 2 段で構成される。後段増幅器はブッシュブル回路で、トランジスタ T 4 は n - MOSFET、T 5 は p - MOSFET である。容量素子 C 5 はハイパスフィルタ 4 に相当する。本実施形態では C 5 = 3 nF である。

#### 【0063】

オペアンプ 5 1 からの入力信号は、前段増幅器で非反転増幅され、後段増幅器で電流増幅される。ダイオード D 4、D 5 はレベルシフトダイオードで、トランジスタ T 4、T 5 のしきい電圧相当分、信号電圧をシフトさせ、トランジスタ T 4、T 5 のクロスオーバー歪を防止する。ダイオード D 4、D 5 のバイアス電流は抵抗素子 R 1 5、R 1 6 から供給される。B 級増幅器 3 の出力は、ハイパスフィルタ 4 で直流成分および低周波成分を除かれ、高周波成分が出力端子 6 に供給される。

#### 【0064】

昇圧型 DC / DC コンバータ 4 1 は、オペアンプ 1 5 0、トランジスタ T 1、ダイオード D 1、インダクタ L 1、容量素子 C 1 で構成される。トランジスタ T 1 は n - MOSFET である。

#### 【0065】

オペアンプ 1 5 0 はコンパレータであり、発振器 2 3 からの入力電圧とオペアンプ 4 2 からの入力電圧を比較して、トランジスタ T 1 をオンオフさせる。発振器 2 3 からの入力電圧が三角波なので、その周期でトランジスタ T 1 はオンオフされる。オペアンプ 4 2 からの入力電圧が高い程、1 周期の中で発振器 2 3 からの入力電圧の方が低い期間が長くなり、トランジスタ T 1 がオフの期間が長くなる。トランジスタ T 1 がオフのときには、ドレイン電圧が上昇し、ダイオード D 1 は導通状態になる。トランジスタ T 1 がオンのときには、ドレイン電圧が下降し、ダイオード D 1 は非導通状態になる。導通状態のときにダイオード D 1 に流れる電流で容量素子 C 1 が充電される。トランジスタ T 1 のオフの期間が長い程、容量素子 C 1 が充電される期間も長くなり、DC / DC コンバータ 4 1 の出力電圧は増加する。従って、オペアンプ 4 2 からの入力電圧レベルが高い程、DC / DC コンバータ 4 1 の出力電圧は増加する。DC / DC コンバータ 4 1 の出力は、S 級変調器 2 5 に供給される。

#### 【0066】

本発明による増幅器の第 4 の実施形態を図 7 に示す。本実施形態は、図 1 の包絡線増幅器の入力端子 5 と B 級増幅器 3 の間に、低周波減衰器 6 0 を加えたものである。本実施形態の低周波減衰器 6 0 は、包絡線信号の低周波成分に対しある減衰比を持ち、高周波成分に対しては減衰を殆ど持たない。

#### 【0067】

本実施形態の増幅器即ち包絡線増幅器は、低周波減衰器 6 0 を加えたことにより、B 級増幅器 3 の動作状態をより柔軟に設定することができる。DC / DC コンバータ 2 の第 1 出力の電圧利得 G 1、第 2 出力の電圧利得 G 2、B 級増幅器 3 の利得 G B、低周波減衰器 6 0 の減衰比 L A とする。G B = G 1 とすると、制御係数 K b p = G 2 / G 1、K b a = L A となる。このように、低周波減衰器 6 0 を用いることにより、制御係数 K b p と K b a を個別に設定することができる。

#### 【0068】

本実施形態では、式(3)を満たすため、制御係数 K b p - K b a = F p - 1、K b a = 1 - F m とした。これは、G 2 / G 1 = F p - F m、L A = 1 - F m に相当し、(a) DC / DC コンバータ 2 の出力電圧比を F p - F m に設定し、(b) 低周波減衰器 6 0 の減衰比を 1 - F m に設定することにより、システムのピークファクタ F p、F m に対して

10

20

30

40

50

最適値を与えるように制御することができた。

【0069】

なお、本実施形態では式(3)の等号が成り立つ場合について説明したが、実際には等号が丁度成立するよう設計するとは限らないことは、既に説明した図1の場合と同様である。

【0070】

本実施形態の包絡線増幅器は、 $F_m > 0$  となる PDC (Personal Digital Cellular) 等のシステムに好適である。PDC 等に適用した場合、図1の実施形態の  $V_{bp} = F_p \times V_{oa}$  に対し、本実施形態では  $V_{bp} = (F_p - F_m) \times V_{oa}$  とすることができる、B級増幅器3の電源電圧を下げて、より高効率化することができる。

10

【0071】

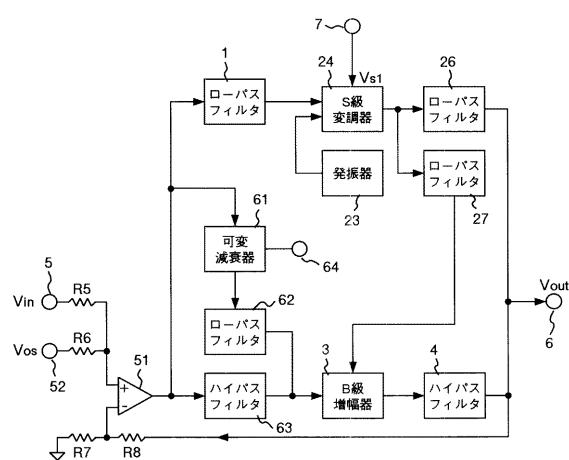

本発明による増幅器の第5の実施形態を図8に示す。本実施形態は、図3の構成から第2のS級変調器25、第2の電源端子7bを除き、可変減衰器61、ローパスフィルタ62、ハイパスフィルタ63、ピークファクタ設定端子64、オペアンプ51、オフセット設定端子52、抵抗R5, R6, R7, R8を加えたものである。

【0072】

発振器23、S級変調器24、第1のローパスフィルタ26、第2のローパスフィルタ27は、図7のDC/DCコンバータ2を構成する。可変減衰器61、ローパスフィルタ62、ハイパスフィルタ63、ピークファクタ設定端子64は、図7の低周波減衰器60を構成する。

20

【0073】

ローパスフィルタ1により入力信号から抽出された低周波成分と、発振器23からの鋸歯形信号が、S級変調器24に入力される。S級変調器24は、電源端子7から電源電圧  $V_{s1}$  の供給を受け、パルス幅変調された、振幅  $V_{s1}$  の矩形波を発生する。

【0074】

この矩形波は、第1のローパスフィルタ26で平滑化され出力端子6に、第2のローパスフィルタ27で平滑化されB級増幅器3の電源端子に、それぞれ供給される。また、入力信号の高周波成分は、ハイパスフィルタ63を経由してB級増幅器3に入力される。低周波成分は、ピークファクタ設定端子64に制御された可変減衰器61で減衰された後、ローパスフィルタ62を経由してB級増幅器3に入力される。

30

【0075】

これらの成分はB級増幅器3で増幅された後、ハイパスフィルタ4で低周波成分を除かれて、出力端子6に供給される。なお、オペアンプ51、オフセット設定端子52、抵抗R5, R6, R7, R8は図5の実施形態と同様の負帰還回路を構成しており、その効果も図5の実施形態と同様である。

【0076】

本実施形態は、ピークファクタ  $F_p - F_m = 1$  となるシステムに好適な包絡線増幅器を有している。この場合、式(5)が利用でき、 $K_{bp} = 1, 2 - F_p - K_{ba} = 1 - F_m$  とすれば良い。即ち、(a) B級増幅器3の電源電圧  $V_{bp}$  は包絡線増幅器の平均出力電圧  $V_{oa}$  と等しくなるように制御し、(b) 可変減衰器61の減衰比  $L_v$  は、 $2 - F_p - L_v = 1 - F_m$  の範囲に制御すれば良い。

40

【0077】

本実施形態では、包絡線増幅器の低周波出力とB級増幅器3の電源を同一のS級変調器24から供給する方法により、(a)の条件を容易に実現することができた。また、本実施形態では、減衰比  $L_v = 0.5$  とした。これにより、ピークファクタ  $F_p = 1.5, F_m = 0.5$  のシステムの包絡線信号を、クリッピング歪みを発生させずに増幅可能である。

【0078】

本実施形態では、本発明による式(5)の条件を用いたことにより、DC/DCコンバータ2の構成を大幅に簡略化することができた。また、本実施形態の低周波減衰器60は

50

ピークファクタ設定端子 64 により外部から設定可能であり、包絡線増幅器の汎用性を高めている。単一品種を量産する場合など、外部設定が必要無い場合には、低周波減衰器 60 の構成は簡略化可能である。

【 0079 】

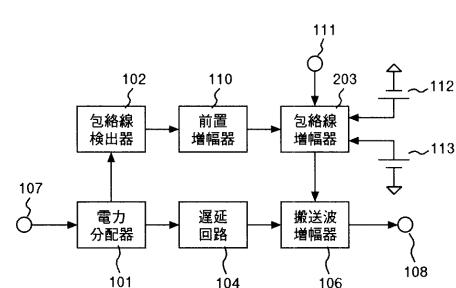

高周波電力増幅器による本発明の第 6 の実施形態を図 9 に示す。本実施形態は W - C D M A 端末送信部用に好適な E E R 型増幅器である。本実施形態の E E R 型増幅器は、包絡線検出器 102 、前置増幅器 110 、包絡線増幅器 203 、電力分配器 101 、遅延回路 104 、搬送波増幅器 106 、高周波入力端子 107 、高周波出力端子 108 、及び電源端子 111 で構成される。包絡線増幅器 203 には図 5 に示したものが用いられる。搬送波増幅器 106 は、飽和動作によって増幅を行なう増幅器である。

10

【 0080 】

高周波入力端子 107 からの高周波入力信号は電力分配器 101 で分配され、一方は包絡線検出器 102 に入力される。包絡線検出器 102 で検出された包絡線信号は、前置増幅器 110 で増幅された後、包絡線増幅器 203 に入力される。包絡線増幅器 203 の電源電圧は 3.5 V である。搬送波増幅器 106 の電源電圧 - 出力電力特性に合わせて、包絡線増幅器 203 のオフセット設定電圧 113 として 0.3 V が印加される。

【 0081 】

また、 W - C D M A の信号波形に合わせて、包絡線増幅器 203 のピークファクタ設定電圧 112 として 1.3 V が印加される。包絡線増幅器 203 の出力は搬送波増幅器 106 の電源端子に供給される。

20

【 0082 】

電力分配器 101 で分配されたもう一方の信号は、遅延回路 104 に入力される。この遅延回路 104 は、包絡線信号経路の遅延を補償する。遅延回路 104 の出力は搬送波増幅器 106 で増幅される。搬送波増幅器 106 は飽和動作しており、 27 dBm 出力時の電力付加効率は 70 % である。搬送波増幅器 106 の出力電力は包絡線増幅器 203 の出力で電源変調され、包絡線成分が回復された高周波出力信号が出力端子 108 において得られる。

【 0083 】

本実施形態の E E R 型増幅器は、本発明の包絡線増幅器 203 を用いた効果により、 W - C D M A 信号を高効率・低歪みで増幅することができ、電力付加効率 60 % 、隣接チャネル漏洩電力 - 42 dBc の良好な特性を実現することができた。

30

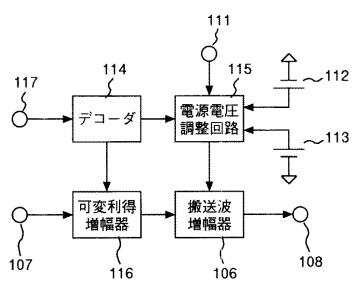

【 0084 】

本発明の増幅器を電源電圧調整回路として使用した高周波電力増幅器による第 7 の実施形態を図 10 に示す。本実施形態は、 G S M ( Global system for Mobile Communication ) 端末送信部用の高周波電力増幅器である。高周波電力増幅器は、デコーダ 114 、電源電圧調整回路 115 、可変利得増幅器 116 、搬送波増幅器 106 、高周波入力端子 107 、高周波出力端子 108 、電源端子 111 、及び出力電力制御端子 117 によって構成される。本実施形態では、図 5 の包絡線増幅器を電源電圧調整回路 115 として使用した。

【 0085 】

40

出力電力制御端子 117 から入力された電力制御信号は、デコーダ回路 114 で変換され、利得制御信号と電源電圧制御信号が生成される。利得制御信号は可変利得増幅器 116 の制御端子に入力される。また、電源電圧制御信号は電源電圧調整回路 115 の入力端子に入力される。電源電圧調整回路 115 には 3.5 V の電源が供給されている。電源電圧調整回路 115 には、搬送波増幅器 106 の電源電圧 - 出力電力特性に合わせて、 0.3 V のオフセット設定電圧 113 が印加されている。

【 0086 】

G S M 方式の電力制御信号は、 W - C D M A 信号のような高速変調成分を含まないので、理論上のピークファクタは 1 だが、 B 級増幅器の動作余裕確保のため、 0.9 V のピークファクタ設定電圧 112 が印加される。高周波入力端子 107 から入力される高周波信

50

号電力は - 3 d B m で一定であり、デコーダ 114 から利得制御信号を受けた可変利得増幅器 116 により、必要な電力に増幅される。

【0087】

可変利得増幅器 116 の出力は搬送波増幅器 106 に入力される。搬送波増幅器 106 は飽和動作であり、出力電力は電源電圧調整回路 115 により制御される。

【0088】

搬送波増幅器 106 が飽和動作している限り、その出力電力は可変利得増幅器 116 からの入力電力に依存せず、可変利得増幅器 116 の利得を厳密に制御する必要は無い。そこで、可変利得増幅器 116 の利得は、搬送波増幅器 106 の利得が 24 d B で一定と仮定して、必要な出力電力から計算した値に制御されている。

【0089】

本実施形態では、動作周波数 900 MHz、出力電力 33 d B m において、電力利得 36 d B、電力付加効率 60 % の GSM 用電力増幅器を実現することができた。電源電圧を用いて出力電力を制御する方法により、ほぼ正確な 2 乗特性で高周波出力電力を制御でき、バイアス電圧を用いて出力電力を制御する一般的な方法と比べて、出力電力の制御性を改善することができた。

【0090】

GSM は時分割方式のため電力制御信号がステップ波形となり、ステップ立ち上がり時間は数マイクロ秒以内が要求される。従って、電源電圧調整回路 115 に通常の DC/D C コンバータを用いると、応答速度に難点がある。また、電源電圧調整回路 115 にシリーズレギュレータを用いると、レギュレータの電圧降下による損失のため、効率が低下する。

【0091】

本実施形態は、包絡線増幅器において上記のような高速性が得られたことにより、2 マイクロ秒以下の立ち上がり時間を実現することができた。また、本実施形態の高周波電力増幅器は、本発明の包絡線増幅器の高効率を反映し、60 % の高効率が得られている。

【図面の簡単な説明】

【0092】

【図 1】本発明に係る増幅器の第 1 の実施形態を説明するための構成図。

【図 2】W - C D M A 包絡線信号の平均値及び上限値を説明するための図。

30

【図 3】図 1 の包絡線増幅器の構成の詳細を説明するための構成図。

【図 4】本発明の第 2 の実施形態を説明するための構成図。

【図 5】本発明の第 3 の実施形態を説明するための構成図。

【図 6】搬送波増幅器の電源電圧と出力電圧の関係を示す図。

【図 7】本発明の第 4 の実施形態を説明するための構成図。

【図 8】本発明の第 5 の実施形態を説明するための構成図。

【図 9】本発明の第 6 の実施形態を説明するための構成図。

【図 10】本発明の第 7 の実施形態を説明するための構成図。

【図 11】従来の高周波電力増幅器を説明するための構成図。

【図 12】図 11 の高周波電力増幅器用いる包絡線増幅器を説明するための構成図。

40

【図 13】W - C D M A 包絡線信号を説明するための図。

【図 14】W - C D M A 包絡線信号の高周波成分を説明するための図。

【図 15】本発明の第 3 の実施形態の詳細な回路例を説明するための回路図。

【符号の説明】

【0093】

1 ... ローパスフィルタ、2 ... D C / D C コンバータ、3 ... B 級増幅回路、4 ... ハイパスフィルタ、5 ... 入力端子、6 ... 出力端子、7 ... 電源端子、23 ... 発振器、24 ... 第 1 の S 級変調器、25 ... 第 2 の S 級変調器、26 ... 第 1 のローパスフィルタ、27 ... 第 2 のローパスフィルタ、101 ... 電力分配器、102 ... 包絡線検出器、104 ... 遅延回路、106 ... 搬送波増幅器、107 ... 高周波入力端子、108 ... 高周波出力端子、203 ... 包絡線増幅

50

器。

【図1】

図 1

【図2】

図 2

【図3】

図 3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

四 10

【図11】

図 11

【图 1-4】

四 14

【図12】

四 12

【図13】

13

【 15 】

図 15

---

フロントページの続き

(51)Int.Cl. F I

H 04 B 1/04 (2006.01) H 04 B 1/04

R

(72)発明者 大西 正己

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

審査官 宮本 秀一

(56)参考文献 特開昭55-149512(JP, A)

特表2001-519612(JP, A)

特開平10-224159(JP, A)

米国特許第03486128(US, A)

特開平06-252647(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 03 C 1/00 - 1/62、

H 03 F 1/00 - 3/45、 3/50 - 3/52、

3/62 - 3/64、 3/68 - 3/72、

H 04 B 1/02 - 1/04