(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5871715号

(P5871715)

(45) 発行日 平成28年3月1日(2016.3.1)

(24) 登録日 平成28年1月22日(2016.1.22)

(51) Int.Cl.

F 1

H03K 23/00 (2006.01)

H03K 19/096 (2006.01)H03K 23/00

H03K 19/096C

B

請求項の数 8 (全 65 頁)

(21) 出願番号 特願2012-119536 (P2012-119536)

(22) 出願日 平成24年5月25日 (2012.5.25)

(65) 公開番号 特開2013-9368 (P2013-9368A)

(43) 公開日 平成25年1月10日 (2013.1.10)

審査請求日 平成27年3月18日 (2015.3.18)

(31) 優先権主張番号 特願2011-118125 (P2011-118125)

(32) 優先日 平成23年5月26日 (2011.5.26)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 藤田 雅史

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 前橋 幸男

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 栗栖 正和

最終頁に続く

(54) 【発明の名称】 分周回路、及び分周回路を用いた半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のインバータと第2のインバータを有し、

p型トランジスタである第1のトランジスタ及び第5のトランジスタと、

n型トランジスタである第2乃至第4のトランジスタ及び第6乃至第8のトランジスタ

と、を有し、

前記第1のトランジスタのソースまたはドレインの一方は、前記第5のトランジスタの

ソースまたはドレインの一方と、第1の電源と、電気的に接続され、

前記第1のトランジスタのソースまたはドレインの他方は、前記第2のトランジスタの

ソースまたはドレインの一方と、電気的に接続され、

前記第2のトランジスタのソースまたはドレインの他方は、第3のトランジスタのソース

またはドレインの一方と、電気的に接続され、

前記第5のトランジスタのソースまたはドレインの他方は、前記第6のトランジスタの

ソースまたはドレインの一方と、電気的に接続され、

前記第6のトランジスタのソースまたはドレインの他方は、第7のトランジスタのソース

またはドレインの一方と、電気的に接続され、

前記第3のトランジスタのソースまたはドレインの他方は、前記第7のトランジスタの

ソースまたはドレインの他方と、第2の電源と、電気的に接続され、

前記第1のトランジスタのゲートは、前記第2のトランジスタのゲートと、前記第8の

トランジスタのゲートと、前記第1のインバータの入力と、電気的に接続され、

10

20

前記第8のトランジスタのソースまたはドレインの一方は、前記第1のトランジスタのソースまたはドレインの他方と、電気的に接続され、

前記第8のトランジスタのソースまたはドレインの他方は、前記第7のトランジスタのゲートと、電気的に接続され、

前記第2のインバータの入力は、前記第5のトランジスタのソースまたはドレインの他方と、電気的に接続され、

前記第2のインバータの出力は、前記第4のトランジスタのソースまたはドレインの一方と、電気的に接続され、

10 前記第4のトランジスタのソースまたはドレインの他方は、前記第3のトランジスタのゲートと、電気的に接続され、

前記第1のインバータの出力は、前記第4のトランジスタのゲートと、前記第5のトランジスタのゲートと、前記第6のトランジスタのゲートと、電気的に接続され、

入力端子は、前記第1のインバータの入力と電気的に接続され、

出力端子は、前記第2のインバータの入力と電気的に接続されていることを特徴とする分周回路。

#### 【請求項2】

請求項1において、

前記第1の電源は、前記第2の電源よりも高い電位を供給することを特徴とする分周回路。

20

#### 【請求項3】

請求項1または請求項2において、

前記第8のトランジスタのソースもしくはドレインの一方または前記第2のインバータの入力の少なくとも一方、容量素子が電気的に接続されていることを特徴とする分周回路。

#### 【請求項4】

請求項1乃至請求項3のいずれか一項において、

前記第4のトランジスタは、チャネルが形成される半導体層が酸化物半導体であることを特徴とする分周回路。

30

#### 【請求項5】

請求項1乃至請求項4のいずれか一項において、

前記第8のトランジスタは、チャネルが形成される半導体層が酸化物半導体であることを特徴とする分周回路。

30

#### 【請求項6】

請求項1乃至請求項5のいずれか一項において、

前記第2のトランジスタまたは前記第3のトランジスタの少なくとも一方は、チャネルが形成される半導体層が酸化物半導体であることを特徴とする分周回路。

40

#### 【請求項7】

請求項1乃至請求項6のいずれか一項において、

前記第6のトランジスタまたは前記第7のトランジスタの少なくとも一方は、チャネルが形成される半導体層が酸化物半導体であることを特徴とする分周回路。

40

#### 【請求項8】

請求項1乃至請求項7のいずれか一項において、

前記分周回路を用いた半導体装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は分周回路に関する。また、分周回路を用いた半導体装置に関する。

#### 【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、半導体素子、電気光学装置、記憶装置、信号処理装置、半導体回路および電

50

子機器は全て半導体装置である。

【背景技術】

【0003】

中央演算処理装置(CPU: Central Processing Unit)などの半導体装置は、その用途によって多種多様な構成を有している。また、このような半導体装置は、複数の回路により構成されており、例えば、データやプログラムを記憶するための回路(メインメモリ)の他に、レジスタ、キャッシュメモリなど、各種の記憶回路が設けられている。

【0004】

レジスタは、演算回路による演算処理や、プログラムの実行状態の保持などのために一時的にデータ信号を保持する役割を担っている。また、キャッシュメモリは、演算回路とメインメモリの間に介在し、低速なメインメモリへのアクセスを減らして、演算回路による演算処理を高速化させることを目的として設けられている。10

【0005】

このような複数の回路を有する半導体装置では、発振回路で生成された高い周波数のクロック信号を、分周回路を用いて低い周波数のクロック信号に変換し、変換されたクロック信号を各回路の同期を取るために用いている。

【0006】

分周回路は、一般的に、遅延型フリップフロップ(DFD: Delay Flip Flop)回路を用いて構成される(例えば、特許文献1参照)。20

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2000-224026号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

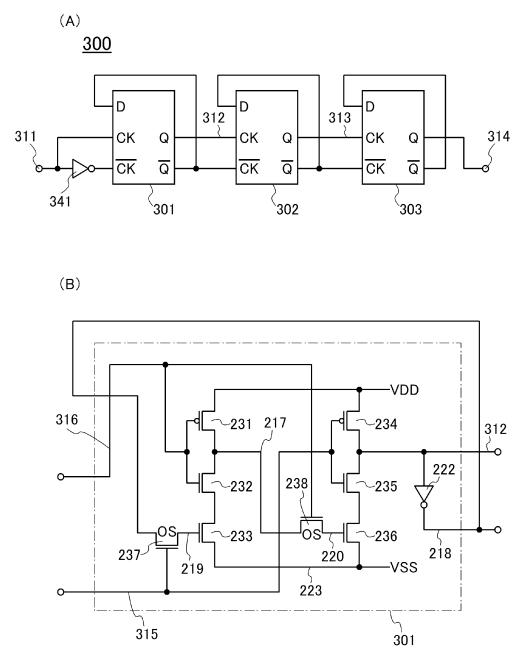

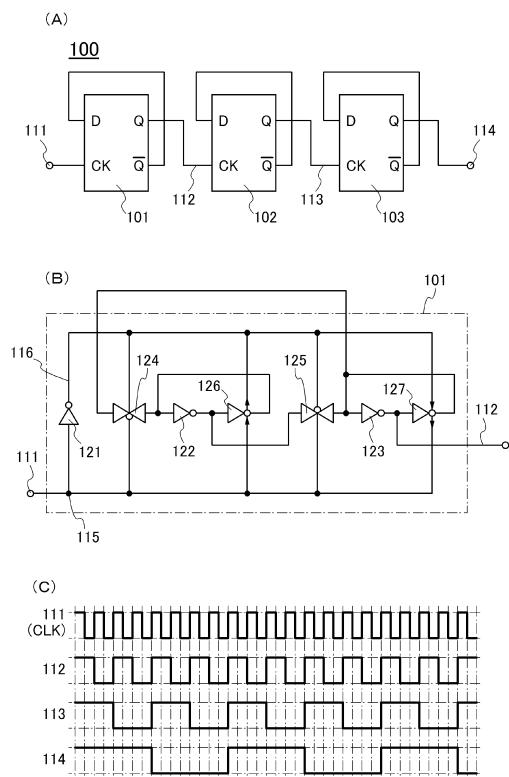

まず、図9を用いて一般的な分周回路の構成と動作の一例を示しておく。図9(A)は、DFD(Delay Flip Flop)回路を用いた分周回路100のブロック図である。分周回路100は、DFD回路101、DFD回路102、及びDFD回路103で示す3つのDFD回路を、3段直列に接続した構成を示している。30

【0009】

DFD回路101乃至DFD回路103は、それぞれ、クロック信号入力部CK、入力部D、出力部Q、及び出力部Qバーを有している。DFD回路101は、クロック信号入力部CKが端子部111と電気的に接続されている。端子部111には、特定の周波数を有するクロック信号CLKが入力される。端子部111に入力されたクロック信号CLKは、クロック信号入力部CKを介してDFD回路101に入力される。DFD回路101の出力部Qバーは、DFD回路101の入力部Dと電気的に接続されている。また、DFD回路101の出力部Qは、ノード112を介して、DFD回路102のクロック信号入力部CKに電気的に接続されている。DFD回路102の出力部Qバーは、DFD回路102の入力部Dと電気的に接続されている。また、DFD回路102の出力部Qは、ノード113を介して、DFD回路103のクロック信号入力部CKに電気的に接続されている。DFD回路103の出力部Qバーは、DFD回路103の入力部Dと電気的に接続されている。また、DFD回路103の出力部Qは、端子部114と電気的に接続されている。40

【0010】

図9(B)は、一般的なDFD回路101の構成を回路記号を用いて示した図である。図9(B)に示すDFD回路101は、インバータ121、インバータ122、及びインバータ123と、アナログスイッチ124及びアナログスイッチ125と、クロックドインバータ126、及びクロックドインバータ127を有している。50

**【0011】**

図9(B)において、端子部111とインバータ121の入力部が接続するノード115がクロック信号入力部CKに相当する。インバータ121は、入力されたクロック信号CLKの反転信号であるクロックバー信号CLKBを生成し、ノード116へ出力する。アナログスイッチ124、アナログスイッチ125、クロックドインバータ126、及びクロックドインバータ127は、クロック信号CLK及びクロックバー信号CLKBと同期して動作する。また、アナログスイッチ124の入力が入力部Dに相当し、アナログスイッチ125の出力が出力部Qバーに相当する。

**【0012】**

なお、DFF回路102、及びDFF回路103も、DFF回路101と同様の構成を有する。 10

**【0013】**

図9(C)は、分周回路100の動作を説明するタイミングチャートであり、端子部111、ノード112、ノード113、及び端子部114における電位の時間変化を示している。端子部111に入力されたクロック信号CLKは、DFF回路101により、周波数が1/2倍(周期が2倍)されてノード112に出力される。

**【0014】**

また、端子部111に入力されたクロック信号CLKは、DFF回路101及びDFF回路102により、周波数が1/4倍(周期が4倍)されてノード113に出力される。 20

**【0015】**

また、端子部111に入力されたクロック信号CLKは、DFF回路101、DFF回路102、及びDFF回路103により、周波数が1/8倍(周期が8倍)されて、端子部114に出力される。このように、DFF回路が一段増える毎に、クロック信号CLKの周波数が1/2倍される。

**【0016】**

つづいて、図10に、図9(B)に示した回路記号と、その回路構成を説明する回路図を示す。

**【0017】**

図10(A1)は、インバータを示す回路記号であり、図10(A2)は、インバータの回路構成を説明する回路図である。インバータは、p型トランジスタ131と、n型トランジスタ132を有し、p型トランジスタ131のソースまたはドレインの一方が高電源電位VDDに電気的に接続され、ソースまたはドレインの他方が出力端子Outに電気的に接続されている。また、n型トランジスタ132のソースまたはドレインの一方が低電源電位VSSに電気的に接続され、ソースまたはドレインの他方が出力端子Outに電気的に接続されている。p型トランジスタ131及びn型トランジスタ132のゲートは、入力端子Inに電気的に接続されている。 30

**【0018】**

ここで、高電源電位VDD(以下、単に「VDD」ともいう)とは、低電源電位VSSよりも高い電位の電源電位を示す。また、低電源電位VSS(以下、単に「VSS」ともいう)とは、高電源電位VDDよりも低い電位の電源電位を示す。また、接地電位をVDDまたはVSSとして用いることもできる。例えばVDDが接地電位の場合には、VSSは接地電位より低い電位であり、VSSが接地電位の場合には、VDDは接地電位より高い電位である。 40

**【0019】**

インバータは、入力された信号を反転して出力する機能を有する。例えば、インバータの入力端子Inに「1」に相当する信号(例えば、VDD)が入力されると、出力端子Outに「0」(例えば、VSS)が出力される。また、インバータの入力端子Inに「0」に相当する信号が入力されると、出力端子Outに「1」が出力される。

**【0020】**

図10(B1)は、アナログスイッチを示す回路記号であり、図10(B2)は、アナロ 50

ゲスイッチの回路構成を説明する回路図である。アナログスイッチは、n型トランジスタ133とp型トランジスタ134を有し、n型トランジスタ133のソースまたはドレインの一方と、p型トランジスタ134のソースまたはドレインの一方が入力端子Inに電気的に接続され、n型トランジスタ133のソースまたはドレインの他方と、p型トランジスタ134のソースまたはドレインの他方が出力端子Outに電気的に接続されている。また、ここでは、p型トランジスタ134のゲートにクロック信号CLKが供給され、n型トランジスタ133のゲートにクロックバー信号CLKBが供給される例を示している。

#### 【0021】

このような構成とすることで、クロック信号CLK及びクロックバー信号CLKBに同期して、入力端子Inと出力端子Outの間を導通、非導通とすることができます。10

#### 【0022】

図10(C1)は、クロックドインバータを示す回路記号であり、図10(C2)は、クロックドインバータの回路構成を説明する回路図である。クロックドインバータは、図10(A2)に示したインバータのp型トランジスタ131とVDDの間に、さらにp型トランジスタ135を設け、インバータのn型トランジスタ132とVSSの間に、さらにn型トランジスタ136を設けた構成を有する。

#### 【0023】

具体的には、p型トランジスタ135のソースまたはドレインの一方がVDDに電気的に接続され、ソースまたはドレインの他方がp型トランジスタ131のソースまたはドレインの一方に電気的に接続される。また、n型トランジスタ136のソースまたはドレインの一方がVSSに電気的に接続され、ソースまたはドレインの他方がn型トランジスタ132のソースまたはドレインの一方に電気的に接続される。図10(C2)では、p型トランジスタ135のゲートにクロックバー信号CLKBが供給され、n型トランジスタ136のゲートにクロック信号CLKが供給される例を示している。20

#### 【0024】

クロックドインバータは、p型トランジスタ135とn型トランジスタ136がオン状態の時に、入力端子Inに”1”に相当する信号(例えば、VDD)が入力されると、出力端子Outに”0”(例えば、VSS)が出力される。また、p型トランジスタ135とn型トランジスタ136がオン状態の時に、入力端子Inに”0”に相当する信号(例えば、VSS)が入力されると、出力端子Outに”1”(例えば、VDD)が出力される。また、p型トランジスタ135とn型トランジスタ136がオフ状態のときは、出力されない。30

#### 【0025】

このような構成とすることで、クロック信号CLK及びクロックバー信号CLKBに同期して、入力された信号を反転して出力することができます。

#### 【0026】

このように、これまでの一般的な分周回路100では、一つのDFF回路101において、3つのインバータ、2つのアナログスイッチ、2つのクロックドインバータが用いられ、少なくとも合計18個のトランジスタが使用されることとなり、占有面積が大きくなるという問題があった。また、使用するトランジスタ数が多いため、消費電力が増えるという問題があった。40

#### 【0027】

また、従来のインバータでは、出力信号が”1”から”0”、もしくは”0”から”1”へ切りかわる時に、VDDとVSSの間に貫通電流が生じやすく、消費電力の低減が難しいという問題があった。

#### 【課題を解決するための手段】

#### 【0028】

従来よりも少ないトランジスタ数で分周回路を構成することで、分周回路の占有面積と、消費電力の低減を可能とする。50

## 【0029】

本発明の一態様は、第1のインバータと第2のインバータを有し、p型トランジスタである第1のトランジスタ及び第5のトランジスタと、n型トランジスタである第2乃至第4のトランジスタ、及び第6乃至第8のトランジスタと、を有し、第1のトランジスタ、及び第5のトランジスタのソースまたはドレインの一方は、第1の電源に電気的に接続され、第1のトランジスタのソースまたはドレインの他方は、第2のトランジスタのソースまたはドレインの一方と電気的に接続され、第2のトランジスタのソースまたはドレインの他方は、第3のトランジスタのソースまたはドレインの一方と電気的に接続され、第5のトランジスタのソースまたはドレインの他方は、第6のトランジスタのソースまたはドレインの一方と電気的に接続され、第7のトランジスタのソースまたはドレインの一方と電気的に接続され、第3のトランジスタのソースまたはドレインの他方と、第7のトランジスタのソースまたはドレインの他方は、第2の電源に電気的に接続され、第1のトランジスタのゲートと、第2のトランジスタのゲートは、第8のトランジスタのゲートと、第1のインバータの入力と電気的に接続され、第8のトランジスタのソースまたはドレインの一方は、第1のトランジスタのソースまたはドレインの他方と、第2のトランジスタのソースまたはドレインの一方と電気的に接続され、第8のトランジスタのソースまたはドレインの他方は、第7のトランジスタのゲートに電気的に接続され、第2のインバータの入力は、第5のトランジスタのソースまたはドレインの他方と、第6のトランジスタのソースまたはドレインの一方と電気的に接続され、第2のインバータの出力は、第4のトランジスタのソースまたはドレインの一方と電気的に接続され、第4のトランジスタのソースまたはドレインの他方は、第3のトランジスタのゲートと電気的に接続され、第1のインバータの出力は、第4のトランジスタのゲートと、第5及び第6のトランジスタのゲートと電気的に接続されていることを特徴とする。

10

20

30

## 【0030】

第1の電源は、第2の電源よりも高い電位を供給する。また、チャネルが形成される半導体層に酸化物半導体を用いたトランジスタ（以下、OS（Oxide Semiconductor）トランジスタともいう）のオフ電流は、シリコンを用いたトランジスタのオフ電流に比べて著しく少ない。

## 【0031】

第4のトランジスタに、OSトランジスタを用いることで、第4のトランジスタのソースまたはドレインに接続するノードの電位を安定して維持することができる。また、第8のトランジスタに、OSトランジスタを用いることで、第8のトランジスタのソースまたはドレインに接続するノードの電位を安定して維持することができる。

## 【0032】

また、OSトランジスタは、第4のトランジスタや、第8のトランジスタ以外のトランジスタに用いることも可能である。このように、OSトランジスタを用いることで、動作が安定し、信頼性の高い半導体装置を実現することができる。

## 【発明の効果】

## 【0033】

40

本発明の一態様により、占有面積の小さい分周回路を提供することができる。

## 【0034】

本発明の一態様により、消費電力が低減された分周回路を提供することができる。

## 【0035】

本発明の一態様である分周回路を用いることにより、消費電力が低減された半導体装置を提供することができる。

## 【0036】

本発明の一態様により、動作が安定し、信頼性の高い半導体装置を提供することができる。

## 【0037】

50

本発明の一態様は、少なくとも上記課題の一を解決する。

【図面の簡単な説明】

【0038】

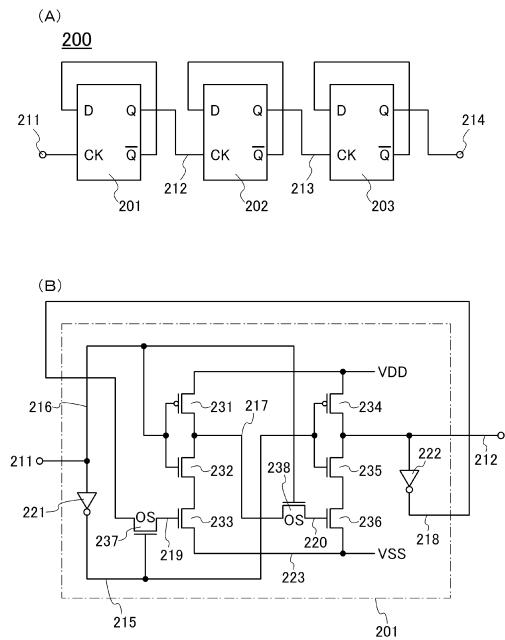

【図1】分周回路とFF回路の構成を示す図。

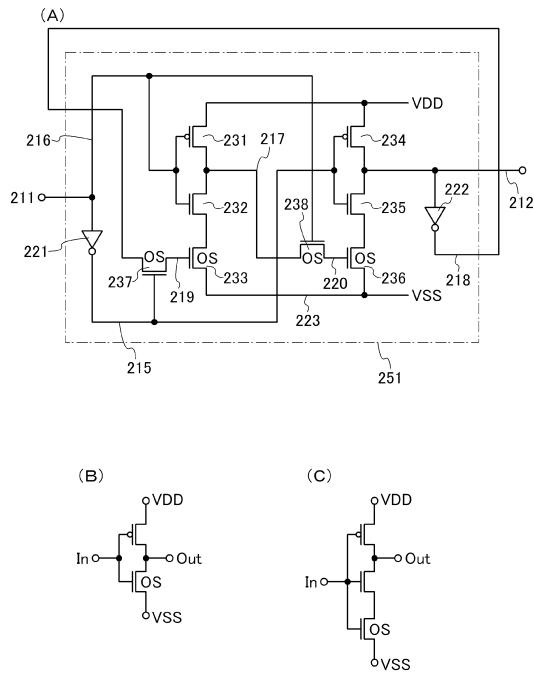

【図2】FF回路の構成を示す図。

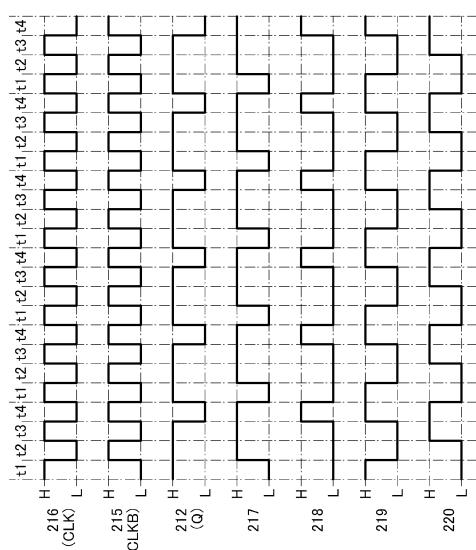

【図3】FF回路の動作を説明するタイミングチャート。

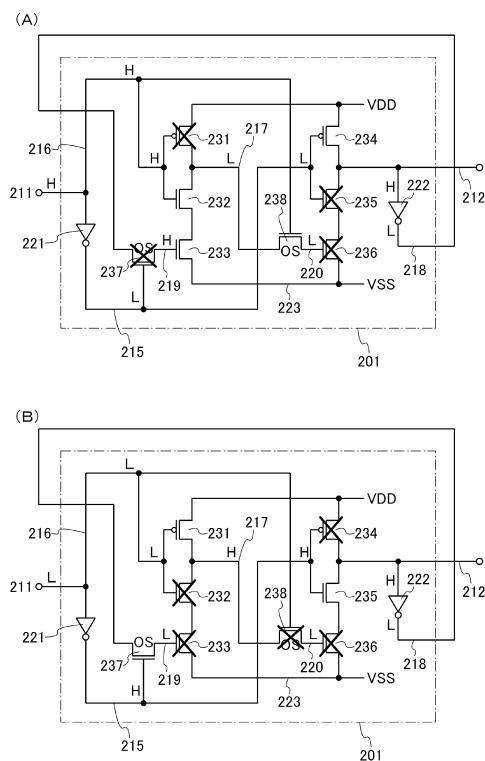

【図4】各動作期間におけるFF回路が有するトランジスタの状態を示す図。

【図5】各動作期間におけるFF回路が有するトランジスタの状態を示す図。

【図6】分周回路の動作を説明するタイミングチャート。

【図7】FF回路の構成を示す回路図。

10

【図8】分周回路とFF回路の構成を示す図。

【図9】一般的な分周回路の構成と動作の一例を示す図。

【図10】回路記号及びその回路構成を説明する回路図。

【図11】CPUの構成を説明する図。

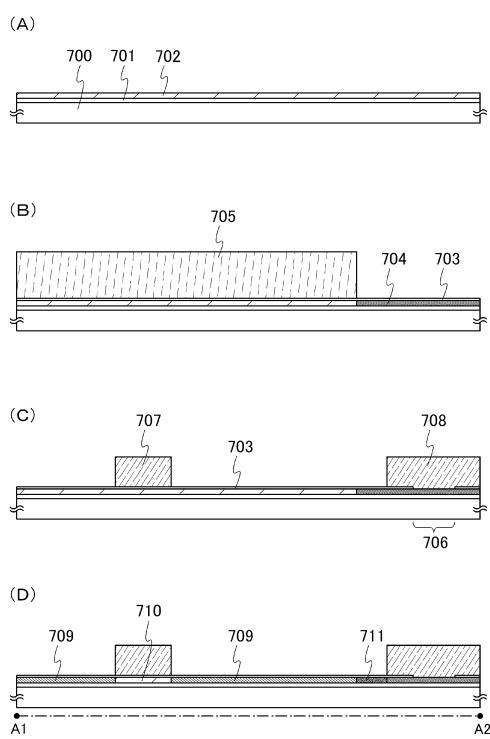

【図12】トランジスタの作製方法を説明する断面図。

【図13】トランジスタの作製方法を説明する断面図。

【図14】トランジスタの作製方法を説明する断面図。

【図15】トランジスタの構成例を示す断面図。

【図16】トランジスタの構成例を示す断面図。

【図17】電子機器の例を示す図。

20

【図18】酸化物材料の結晶構造を説明する図。

【図19】酸化物材料の結晶構造を説明する図。

【図20】酸化物材料の結晶構造を説明する図。

【図21】酸化物材料の結晶構造を説明する図。

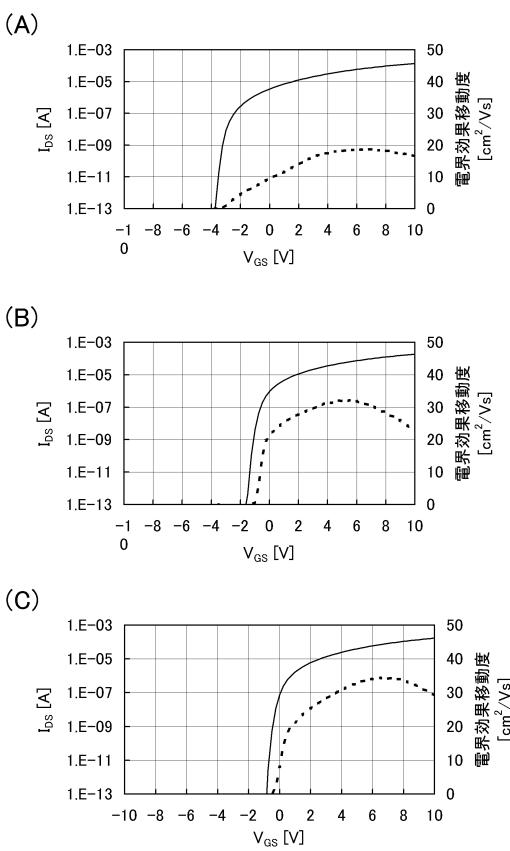

【図22】計算によって得られた電界効果移動度のゲート電圧依存性を説明する図。

【図23】計算によって得られたドレイン電流と電界効果移動度のゲート電圧依存性を説明する図。

【図24】計算によって得られたドレイン電流と電界効果移動度のゲート電圧依存性を説明する図。

【図25】計算によって得られたドレイン電流と電界効果移動度のゲート電圧依存性を説明する図。

30

【図26】計算に用いたトランジスタの断面構造を説明する図。

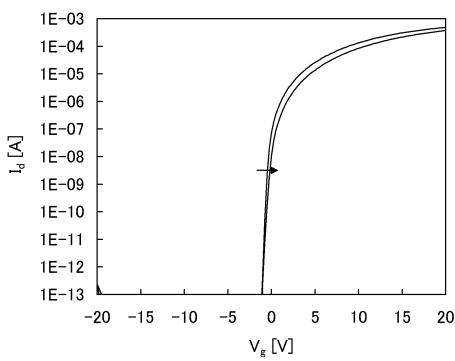

【図27】酸化物半導体膜を用いたトランジスタ特性のグラフ。

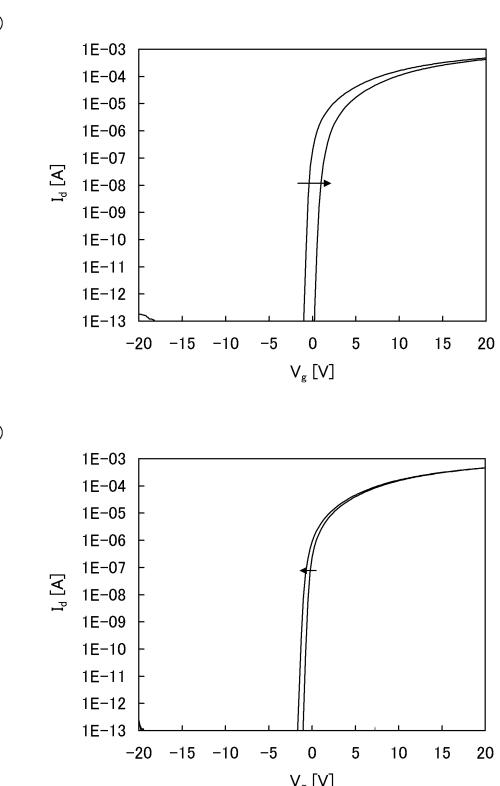

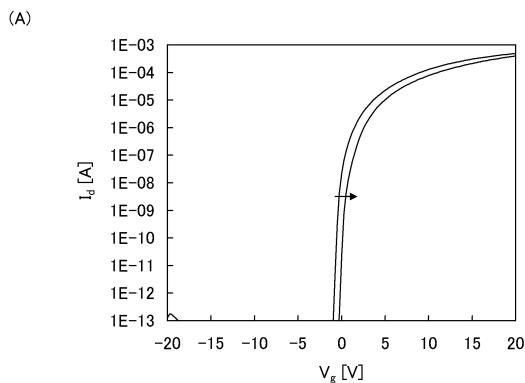

【図28】試料1のトランジスタのBT試験後の $V_g - I_d$ 特性を示す図。

【図29】試料2であるトランジスタのBT試験後の $V_g - I_d$ 特性を示す図。

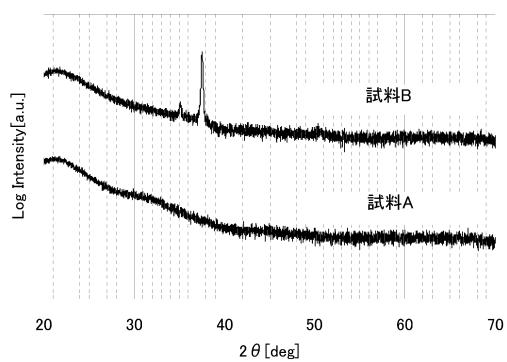

【図30】試料Aおよび試料BのXRDスペクトルを示す図。

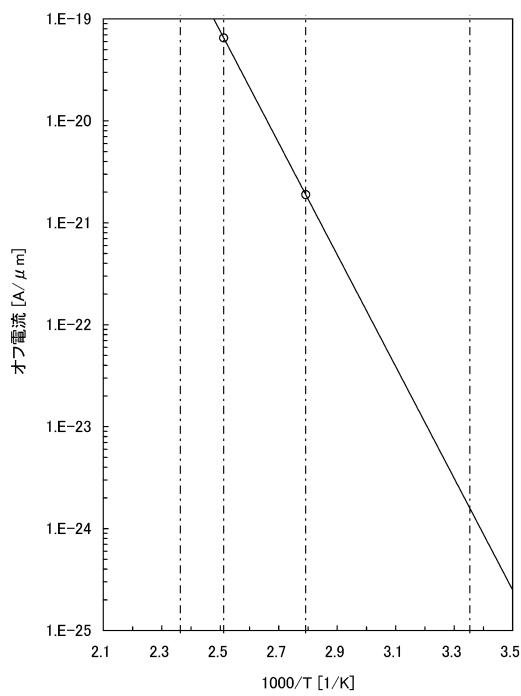

【図31】トランジスタのオフ電流と測定時基板温度との関係を示す図。

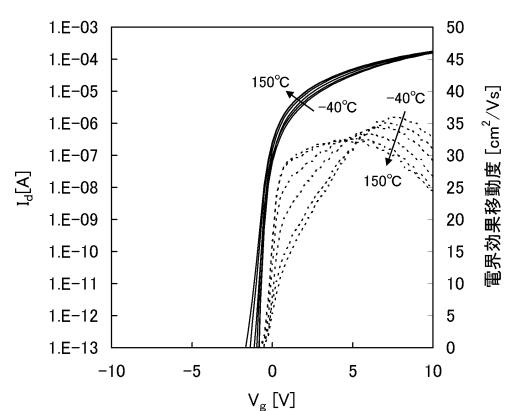

【図32】 $I_d$ および電界効果移動度の $V_g$ 依存性を示す図。

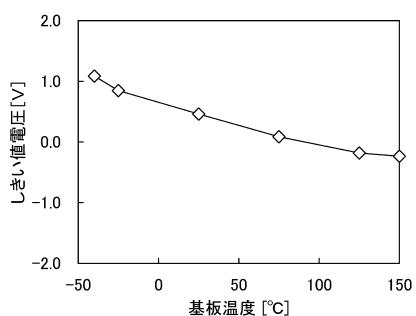

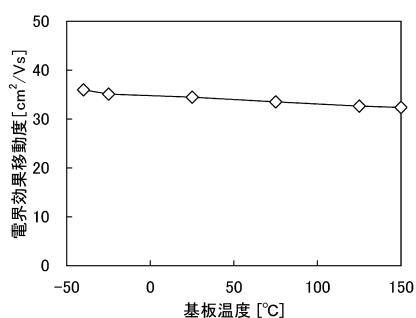

【図33】基板温度としきい値電圧の関係および基板温度と電界効果移動度の関係を示す図。

40

【発明を実施するための形態】

【0039】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0040】

なお、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れかわることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れかえて用いることがで

50

きるものとする。

**【0041】**

「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限はない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

**【0042】**

回路図上は独立している構成要素どうしが電気的に接続しているように図示されている場合であっても、実際には、例えば配線の一部が電極としても機能する場合など、一の導電膜が、複数の構成要素の機能を併せ持っている場合もある。本明細書において電気的に接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

10

**【0043】**

図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

**【0044】**

「第1」、「第2」、「第3」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではない。

20

**【0045】**

なお、電圧とは2点間における電位差のことをいい、電位とはある一点における静電場の中にある単位電荷が持つ静電エネルギー（電気的な位置エネルギー）のことをいう。ただし、一般的に、ある一点における電位と基準となる電位（例えば接地電位）との電位差のことを、単に電位もしくは電圧と呼び、電位と電圧が同義語として用いられることが多い。このため、本明細書では特に指定する場合を除き、電位を電圧と読み替えてよいし、電圧を電位と読み替えてよいこととする。

**【0046】**

(実施の形態1)

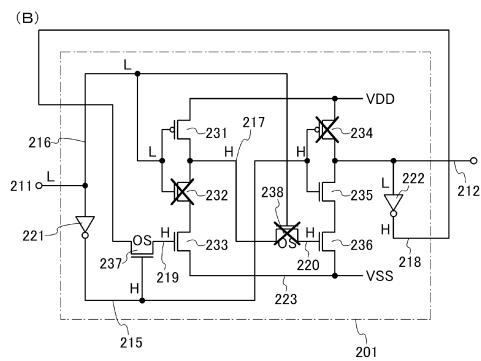

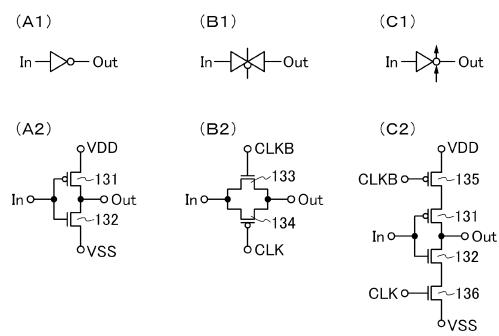

図1乃至図6を用いて、本発明の一態様である分周回路の構成と動作の一例について説明する。分周回路は、1つまたは複数のFF(Flip Flop)回路を有する。本実施の形態では、FF回路201、FF回路202、及びFF回路203で示す、3つのFF回路を有する分周回路200を例示して説明する。

30

**【0047】**

図1(A)は、分周回路200の構成を示すブロック図であり、FF回路201乃至FF回路203が、3段直列に接続されている。

**【0048】**

FF回路201乃至FF回路203は、それぞれ、クロック信号入力部CK、入力部D、出力部Q、及び出力部Qバーを有している。FF回路201は、クロック信号入力部CKが端子部211と電気的に接続されている。端子部211には、特定の周波数を有するクロック信号CLKが入力される。端子部211に入力されたクロック信号CLKは、クロック信号入力部CKを介してFF回路201に入力される。FF回路201の出力部Qバーは、FF回路201の入力部Dと電気的に接続されている。また、FF回路201の出力部Qは、ノード212を介して、FF回路202のクロック信号入力部CKに電気的に接続されている。FF回路202の出力部Qバーは、FF回路202の入力部Dと電気的に接続されている。また、FF回路202の出力部Qは、ノード213を介して、FF回路203のクロック信号入力部CKに電気的に接続されている。FF回路203の出力部Qバーは、FF回路203の入力部Dと電気的に接続されている。また、FF回路203の出力部Qは、端子部214と電気的に接続されている。

40

**【0049】**

50

図1(B)は、FF回路201の構成を示す回路図である。

**【0050】**

なお、図中、トランジスタに、OSトランジスタを用いる箇所に、「OS」の符号を付している。

**【0051】**

図1(B)に示すFF回路201は、インバータ221(第1のインバータともいう)、及びインバータ222(第2のインバータともいう)を有し、p型のトランジスタ231(第1のトランジスタともいう)、及びトランジスタ234(第5のトランジスタともいう)と、n型のトランジスタ232(第2のトランジスタともいう)、トランジスタ233(第3のトランジスタともいう)、トランジスタ235(第6のトランジスタともいう)、及びトランジスタ236(第7のトランジスタともいう)を有し、OSトランジスタであるトランジスタ237(第4のトランジスタともいう)、及びトランジスタ238(第8のトランジスタともいう)を有する。

10

**【0052】**

端子部211とインバータ221の入力部が接続するノード216がクロック信号入力部CKに相当する。インバータ221は、入力されたクロック信号CLKの反転信号であるクロックバー信号CLKBを生成し、ノード215へ出力する。トランジスタ231のソースまたはドレインの一方はVDDに電気的に接続され、ソースまたはドレインの他方はノード217に電気的に接続されている。トランジスタ232のソースまたはドレインの一方はノード217に電気的に接続されている。トランジスタ231及びトランジスタ232のゲートは、ノード216に電気的に接続されている。トランジスタ233のソースまたはドレインの一方はVSSに電気的に接続され、ソースまたはドレインの他方は、トランジスタ232のソースまたはドレインの他方に電気的に接続されている。トランジスタ237のソースまたはドレインの一方は、ノード219を介してトランジスタ233のゲートに電気的に接続され、ソースまたはドレインの他方は、ノード218に電気的に接続されている。インバータ222は、入力部がノード212に電気的に接続され、出力部がノード218に電気的に接続されている。

20

**【0053】**

トランジスタ234のソースまたはドレインの一方はVDDに電気的に接続され、ソースまたはドレインの他方はノード212に電気的に接続されている。トランジスタ235のソースまたはドレインの一方はノード212に電気的に接続されている。トランジスタ234及びトランジスタ235のゲートは、ノード215に電気的に接続されている。トランジスタ236のソースまたはドレインの一方はVSSに電気的に接続され、ソースまたはドレインの他方は、トランジスタ235のソースまたはドレインの他方と電気的に接続されている。トランジスタ238のソースまたはドレインの一方は、ノード220を介してトランジスタ236のゲートに電気的に接続され、ソースまたはドレインの他方は、ノード217に電気的に接続されている。

30

**【0054】**

次に、FF回路201の動作について図3乃至図6を用いて説明する。図3は、FF回路201の動作を説明するタイミングチャートであり、動作期間t1乃至t4における各ノードの電位を示している。図4及び図5は各動作期間におけるFF回路201が有するトランジスタの状態を示している。

40

**【0055】**

なお、以下に示す動作説明はこれに限定されず、各トランジスタの導通状態が同じ動作となれば、適宜各トランジスタの導電型、論理回路の組み合わせ、及び各信号の電位を設定することができる。ここでは、各信号をH電位とL電位で表し、H電位はn型トランジスタをオン状態、p型トランジスタをオフ状態とする電位(例えば、VDD)とし、L電位はp型トランジスタをオン状態、n型トランジスタをオフ状態とする電位(例えば、VSS)とする。なお、ノード219の電位は初期状態としてH電位であるとし、ノード220の電位は初期状態としてL電位であるとする。また、クロック信号CLKは、特定の周

50

期（周波数）でH電位またはL電位に変化するものとする。また、図4及び図5において、オフ状態となったトランジスタには、×印を付記している。

**【0056】**

まず、図3の期間t1の動作について、図4(A)を用いて説明する。

**【0057】**

期間t1では、端子部211からクロック信号CLKのH電位が入力され、ノード216の電位がH電位となり、インバータ221によりクロックバー信号CLKBが生成されて、ノード215の電位がL電位となる。すると、トランジスタ237がオフ状態となり、ノード219にはH電位が保持され、トランジスタ233もオン状態が保持される。

**【0058】**

また、ノード216がH電位となるため、トランジスタ231がオフ状態、トランジスタ232がオン状態となり、ノード217とノード223が導通され、ノード217にL電位(VSS)が供給される。

**【0059】**

また、ノード215の電位はL電位であるため、トランジスタ234がオン状態となり、トランジスタ235がオフ状態となる。すると、ノード212にH電位(VDD)が供給され、インバータ222からL電位が出力されて、ノード218がL電位となる。

**【0060】**

また、トランジスタ238がオン状態となり、ノード217とノード220が導通し、ノード220の電位がL電位となる。よって、トランジスタ236はオフ状態となる。

**【0061】**

次に、図3の期間t2の動作について、図4(B)を用いて説明する。

**【0062】**

期間t2では、端子部211からクロック信号CLKのL電位が入力され、ノード216の電位がL電位となり、インバータ221によりクロックバー信号CLKBが生成されて、ノード215の電位がH電位となる。ノード216の電位がL電位になると、トランジスタ238、及びトランジスタ232がオフ状態となり、トランジスタ231がオン状態となり、ノード217にH電位が供給される。

**【0063】**

トランジスタ238はオフ状態であるため、ノード217とノード220は導通されず、ノード220の電位はL電位のまま保持され、トランジスタ236もオフ状態が保持される。

**【0064】**

また、ノード215の電位がH電位となるため、トランジスタ234がオフ状態、トランジスタ235がオン状態となるが、トランジスタ236がオフ状態であるため、ノード212は電気的に浮遊した状態(フローティング状態)となり、ノード212の電荷は移動できずに保持される。ここでは、結果的にノード212にH電位が保持される。よって、インバータ222からは、ノード218にL電位が出力される。また、ノード215がH電位となるため、トランジスタ237がオン状態となり、ノード218とノード219が導通し、ノード219の電位がL電位となる。よって、トランジスタ233はオフ状態となる。

**【0065】**

次に、図3の期間t3の動作について、図5(A)を用いて説明する。

**【0066】**

期間t3では、端子部211からクロック信号CLKのH電位が入力され、ノード216の電位がH電位となり、インバータ221によりクロックバー信号CLKBが生成されて、ノード215の電位がL電位となる。ノード215の電位がL電位になると、トランジスタ237がオフ状態となり、ノード219の電位(L電位)が保持され、トランジスタ233もオフ状態が保持される。

**【0067】**

10

20

30

40

50

また、ノード216の電位がH電位になると、トランジスタ232がオン状態となり、トランジスタ231がオフ状態となるが、トランジスタ233がオフ状態であるため、ノード217は電気的に浮遊した状態（フローティング状態）となり、ノード217の電荷は移動できずに保持される。ここでは、結果的にノード217にH電位が保持される。また、トランジスタ238がオン状態となり、ノード217とノード220が導通し、ノード220の電位がH電位となる。よって、トランジスタ236がオン状態となる。

## 【0068】

ノード215の電位がL電位となるため、トランジスタ234がオン状態、トランジスタ235がオフ状態となり、ノード212にH電位が供給され、インバータ222からL電位が出力されて、ノード218がL電位となる。

10

## 【0069】

次に、図3の期間t4の動作について、図5（B）を用いて説明する。

## 【0070】

期間t4では、端子部211からクロック信号CLKのL電位が入力され、ノード216の電位がL電位となり、インバータ221によりクロックバー信号CLKBが生成されて、ノード215の電位がH電位となる。ノード216の電位がL電位になると、トランジスタ238がオフ状態となり、ノード220の電位（H電位）が保持され、トランジスタ236もオン状態が保持される。

## 【0071】

また、ノード215の電位がH電位になると、トランジスタ234がオフ状態となり、トランジスタ235がオン状態となり、ノード212とノード223が導通され、ノード212にL電位（VSS）が供給される。ノード212にL電位が供給されると、インバータ222からH電位が出力されて、ノード218がH電位となる。

20

## 【0072】

また、ノード215の電位がH電位になると、トランジスタ237がオン状態となり、ノード218とノード219が導通され、ノード219がH電位となり、トランジスタ233がオン状態となる。

## 【0073】

また、ノード216の電位がL電位になると、トランジスタ231がオン状態となり、トランジスタ232がオフ状態となり、ノード217がH電位となる。

30

## 【0074】

このように、本発明の一態様であるFF回路は、入力されたクロック信号CLKの半分の周波数を有する信号を出力することができる。また、本実施の形態ではFF回路の出力としてノード212の電位を出力する例を示しているが、他のノードの電位を出力として用いてもよい。例えば、ノード219もしくはノード220の電位を出力として用いると、入力されたクロック信号CLKとデューティー比がほぼ同じで、半分の周波数を有する信号を出力することができる。

## 【0075】

また、本実施の形態に開示するFF回路は、カウンター回路など他の回路に用いることが可能である。

40

## 【0076】

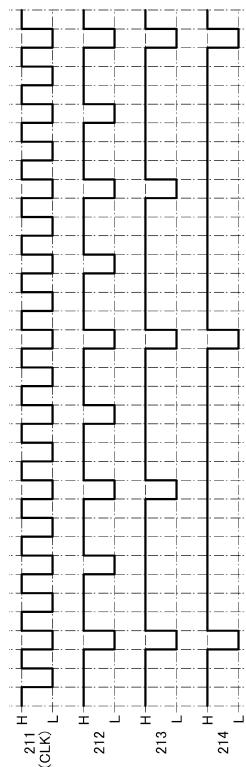

図6は、分周回路200の動作を説明するタイミングチャートであり、端子部211、ノード212、ノード213、及び端子部214における電位の時間変化を示している。端子部211に入力されたクロック信号CLKは、FF回路201により、周波数が1/2倍（周期が2倍）されてノード212に出力される。

## 【0077】

また、端子部211に入力されたクロック信号CLKは、FF回路201及びFF回路202により、周波数が1/4倍（周期が4倍）されてノード213に出力される。

## 【0078】

また、端子部211に入力されたクロック信号CLKは、FF回路201、FF回路20

50

2、及びFF回路203により、周波数が1/8倍（周期が8倍）されて端子部114に出力される。このように、FF回路を1段通過する毎に、クロック信号CLKの周波数が1/2倍される。

#### 【0079】

例えば、FF回路を15段直列接続した分周回路に、32.768kHzの周波数を有するクロック信号CLKを入力すると、1Hzの周波数を有するクロック信号CLKを得ることができる。すなわち、分周回路200は、一定時間ごとに信号を生じさせるタイマーハードとして用いることも可能である。

#### 【0080】

本発明の一態様であるFF回路は、従来のDFF回路よりも少ないトランジスタ数で構成することが可能であり、用いるインバータ数も少ないため、貫通電流による消費電力の増加を抑えることができる。すなわち、従来よりも少ないトランジスタ数で分周回路を作製することができる。よって、占有面積が小さく、消費電力が低減された半導体装置を実現することができる。

10

#### 【0081】

また、OSトランジスタは、シリコンを用いたトランジスタのオフ電流に比べて著しく低く、チャネル幅1μmあたりのオフ電流値を100zA以下、好ましくは10zA以下、更に好ましくは1zA以下にすることができる。

#### 【0082】

すなわち、トランジスタ237として、OSトランジスタを用いることで、トランジスタ237をオフ状態とした時にノード219の電位を安定して維持することができる。特に、FF回路の接続段数が増えると、ノード219の電位を、トランジスタ237をオフ状態として保持する時間が長くなるため、その効果が顕著となる。

20

#### 【0083】

同様に、トランジスタ238として、OSトランジスタを用いることで、トランジスタ238をオフ状態とした時にノード220の電位を安定して維持することができる。

#### 【0084】

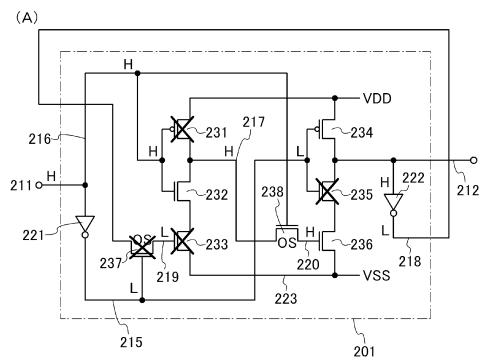

図2(A)に示すFF回路251は、FF回路201と同様の回路構成を有し、OSトランジスタをトランジスタ237、及びトランジスタ238のみでなく、トランジスタ233、及びトランジスタ236にも用いたFF回路である。なお、トランジスタ232や、トランジスタ235にOSトランジスタを用いてもよい。

30

#### 【0085】

トランジスタ232、及びトランジスタ233のどちらか一方もしくは両方にOSトランジスタを用いることで、トランジスタ231をオン状態としてノード217をH電位とする際に、ノード217の電荷がノード223へ漏れ出すことを防ぎ、効率よく電荷の供給を行うことができる。よって、消費電力を低減することが可能となる。

#### 【0086】

また、FF回路の接続段数が増えると、ノード217にH電位が保持される時間も長くなる。このため、トランジスタ232、及びトランジスタ233のどちらか一方もしくは両方に、OSトランジスタを用いることで、ノード217の電位を安定して維持することができる。特に、トランジスタ233は、オフ状態となる時間がトランジスタ232よりも長いため、トランジスタ233にOSトランジスタを用いることが好ましい。

40

#### 【0087】

また、トランジスタ235、及びトランジスタ236のどちらか一方もしくは両方に、OSトランジスタを用いることで、トランジスタ234をオン状態としてノード212をH電位とする際に、ノード212の電荷がノード223へ漏れ出すことを防ぎ、効率よく電荷の供給を行うことができる。よって、消費電力を低減することが可能となる。

#### 【0088】

また、トランジスタ235、及びトランジスタ236のどちらか一方もしくは両方に、OSトランジスタを用いることで、ノード212の電位を安定して維持することができる。

50

特に、トランジスタ 236 は、オフ状態となる時間がトランジスタ 235 よりも長いため、トランジスタ 236 に OS トランジスタを用いることが好ましい。

**【0089】**

また、図 2 (B) および図 2 (C) は、インバータを構成するトランジスタに、OS トランジスタを用いた回路図である。インバータを構成するトランジスタに、OS トランジスタを用いることで、消費電力をより低減することが可能となる。

**【0090】**

半導体装置が有するトランジスタに、OS トランジスタを用いることで、動作が安定し、信頼性の高い半導体装置を実現することができる。また、消費電力が低減された半導体装置を実現することができる。

10

**【0091】**

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

**【0092】**

(実施の形態 2)

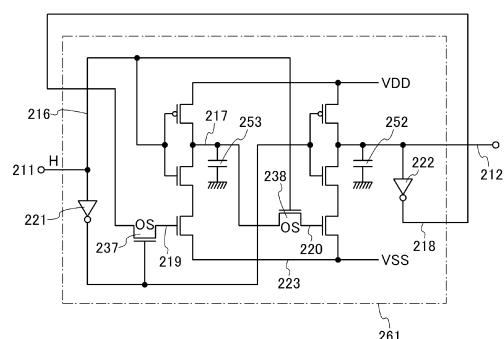

本実施の形態では、実施の形態 1 で説明した FF 回路 201 と異なる構成を有する FF 回路 261 について説明する。

**【0093】**

図 7 は、FF 回路 261 の構成を示す回路図である。FF 回路 261 は、実施の形態 1 で説明した FF 回路 201 のノード 212 及びノード 217 に、容量素子 252 及び容量素子 253 を付加した構成を有する。

20

**【0094】**

FF 回路 261 が有する容量素子 252 の一方の電極はノード 212 に電気的に接続され、他方の電極は共通電位が供給される共通電極に電気的に接続されている。また、容量素子 253 の一方の電極はノード 217 に電気的に接続され、他方の電極は共通電位が供給される共通電極に電気的に接続されている。

**【0095】**

ここでは、容量素子 252 及び容量素子 253 の他方の電極に、共通電位が供給される例について示しているが、該電極に供給される電位は固定電位であればよく、VDD や VSS でもよく、それぞれが異なる電位であってもよい。

30

**【0096】**

容量素子 252 及び容量素子 253 を付加することにより、ノード 212 及びノード 217 がフローティング状態となった時も、ノード 212 及びノード 217 の電位をより安定して維持することが可能となる。よって、半導体装置の信頼性をさらに高めることができる。

**【0097】**

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

**【0098】**

(実施の形態 3)

本実施の形態では、上記実施の形態で説明した分周回路 200 と異なる構成を有する分周回路 300 について説明する。図 8 (A) は、分周回路 300 の構成を示すブロック図であり、FF 回路 301 乃至 FF 回路 303 が、3 段直列に接続されている。

40

**【0099】**

FF 回路 301 乃至 FF 回路 303 は、それぞれ、クロック信号入力部 CK、クロックバー信号入力部 CK バー、入力部 D、出力部 Q、及び出力部 Q バーを有している。FF 回路 301 は、クロック信号入力部 CK が端子部 311 と電気的に接続されている。

**【0100】**

端子部 311 には、特定の周波数を有するクロック信号 CLK が入力される。端子部 311 に入力されたクロック信号 CLK は、クロック信号入力部 CK を介して FF 回路 301 に入力される。また、端子部 311 はインバータ 341 を介してクロックバー信号入力部 CK バーと接続されている。端子部 311 にクロック信号 CLK が入力されると、インバ

50

ータ341からクロック信号CLKの反転信号であるクロックバー信号CLKBが出力される。クロックバー信号CLKBは、クロックバー信号入力部CKバーを介してFF回路301に入力される。

#### 【0101】

FF回路301の出力部Qは、ノード312を介して、FF回路302のクロック信号入力部CKに電気的に接続されている。また、FF回路301の出力部Qバーは、FF回路301の入力部D及びFF回路302のクロックバー信号入力部CKバーと電気的に接続されている。

#### 【0102】

FF回路302の出力部Qは、ノード313を介して、FF回路303のクロック信号入力部CKに電気的に接続されている。また、FF回路302の出力部Qバーは、FF回路302の入力部D及びFF回路303のクロックバー信号入力部CKバーと電気的に接続されている。FF回路303の出力部Qは、端子部314と電気的に接続されている。FF回路303の出力部Qバーは、FF回路303の入力部Dと電気的に接続されている。

10

#### 【0103】

図8(B)は、FF回路301の構成を示す回路図である。

#### 【0104】

図8(B)に示すノード316がクロック信号入力部CKに相当する。また、ノード315がクロックバー信号入力部CKバーに相当する。FF回路301は、図1(B)に示したFF回路201からインバータ221を省略し、外部からクロックバー信号CLKBを入力する点が異なる。なお、二段目以降のFF回路には、前段のFF回路の出力部Qバーから出力される信号をクロックバー信号CLKBとして用いることができる。

20

#### 【0105】

FF回路301では、インバータ221を形成しないため、FF回路201に比べて占有面積を小さくすることができる。すなわち、分周回路300は、分周回路200よりも占有面積を小さくすることができる。なお、その他の回路構成や動作方法は、FF回路201と同様とすることができるため、その説明は割愛する。

#### 【0106】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

#### 【0107】

30

#### (実施の形態4)

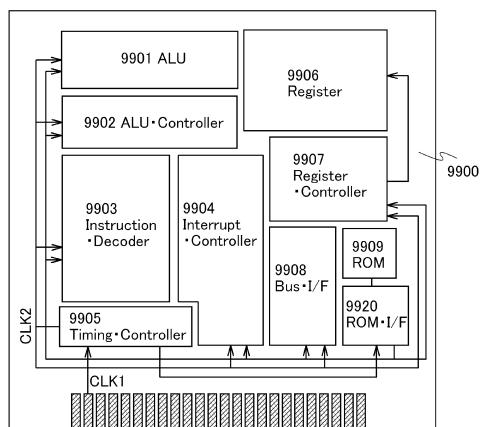

本実施の形態では、本発明の一態様に係る半導体装置の一つである、CPUの構成について説明する。

#### 【0108】

図11に、本実施の形態のCPUの構成を示す。図11に示すCPUは、基板9900上に、ALU9901、ALU・Controller9902、Instruction・Decoder9903、Interrupt・Controller9904、Timing・Controller9905、Register9906、Register・Controller9907、Bus・I/F9908、書き換え可能なROM9909、ROM・I/F9920と、を主に有している。なお、ALUはArithmetic logic unitであり、Bus・I/Fはバスインターフェースであり、ROM・I/FはROMインターフェースである。ROM9909及びROM・I/F9920は、別チップに設けても良い。勿論、図11に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

40

#### 【0109】

Bus・I/F9908を介してCPUに入力された命令は、Instruction・Decoder9903に入力され、デコードされた後、ALU・Controller9902、Interrupt・Controller9904、Register・Controller9907、Timing・Controller9905に入力される。

50

**【0110】**

ALU・Controller9902、Interrupt・Controller9904、Register・Controller9907、Timing・Controller9905は、デコードされた命令に基づき、各種制御を行なう。具体的にALU・Controller9902は、ALU9901の動作を制御するための信号を生成する。また、Interrupt・Controller9904は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。Register・Controller9907は、Register9906のアドレスを生成し、CPUの状態に応じてRegister9906の読み出しや書き込みを行なう。

10

**【0111】**

またTiming・Controller9905は上記実施の形態で示した構成を有する分周回路を含み、ALU9901、ALU・Controller9902、Instruction・Decoder9903、Interrupt・Controller9904、Register・Controller9907の動作のタイミングを制御する信号を生成する。例えばTiming・Controller9905は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部(分周回路)を備えており、クロック信号CLK2を上記各種回路に入力する。

**【0112】**

CPUの構成に、上記実施の形態で示した分周回路を用いることで、CPUの占有面積を小さくすることが可能となり、消費電力の低減を行うことができる。

20

**【0113】**

本実施の形態では、CPUを例に挙げて説明したが、本発明の分周回路はCPUに限定されず、マイクロプロセッサ、画像処理回路、DSP、FPGA等のLSIにも応用可能である。

**【0114】**

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

**【0115】****(実施の形態5)**

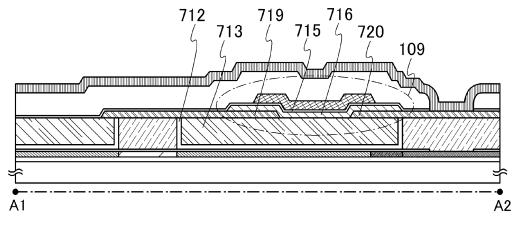

本実施の形態では、OSトランジスタと、チャネルが形成される半導体層にシリコンを用いたトランジスタとを例に挙げて、上記実施の形態に示したFF回路に適用可能なトランジスタの構成と作製方法について、図12乃至図15に示す断面図を用いて説明する。

30

**【0116】**

図12(A)に示すように、基板700上に絶縁膜701と、単結晶の半導体基板から分離された半導体膜702とを形成する。

**【0117】**

基板700として使用することができる素材に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、基板700には、フュージョン法やフロート法で作製されるガラス基板、石英基板、半導体基板、セラミック基板等を用いることができる。ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いると良い。

40

**【0118】**

また、本実施の形態では、半導体膜702が単結晶のシリコンである場合を例に挙げて、説明するが、半導体膜702には非晶質半導体や、単結晶半導体、多結晶半導体、微結晶半導体などの結晶性半導体等を用いることができる。半導体材料としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を挙げることができる。

**【0119】**

以下、トランジスタ732の作製方法について説明する。なお、具体的な単結晶の半導体膜702の作製方法の一例について、簡単に説明する。まず、単結晶の半導体基板である

50

ボンド基板に、電界で加速されたイオンでなるイオンビームを注入し、ボンド基板の表面から一定の深さの領域に、結晶構造が乱されることで局所的に脆弱化された脆化層を形成する。脆化層が形成される領域の深さは、イオンビームの加速エネルギーとイオンビームの入射角によって調節することができる。そして、ボンド基板と、絶縁膜 701 が形成された基板 700 とを、間に当該絶縁膜 701 が挟まるように貼り合わせる。貼り合わせは、ボンド基板と基板 700 とを重ね合わせた後、ボンド基板と基板 700 の一部に、 $1\text{ N}/\text{cm}^2$  以上  $500\text{ N}/\text{cm}^2$  以下、好ましくは  $11\text{ N}/\text{cm}^2$  以上  $20\text{ N}/\text{cm}^2$  以下程度の圧力を加える。圧力を加えると、その部分からボンド基板と絶縁膜 701 とが接合を開始し、最終的には密着した面全体に接合がおよぶ。次いで、加熱処理を行うことで、脆化層に存在する微小ボイドどうしが結合して、微小ボイドの体積が増大する。その結果、脆化層においてボンド基板の一部である単結晶半導体膜が、ボンド基板から分離する。上記加熱処理の温度は、基板 700 の歪み点を越えない温度とする。そして、上記単結晶半導体膜をエッティング等により所望の形状に加工することで、半導体膜 702 を形成することができる。10

#### 【0120】

半導体膜 702 には、しきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどの p 型の導電性を付与する不純物元素、若しくはリン、砒素などの n 型の導電性を付与する不純物元素を添加しても良い。しきい値電圧を制御するための不純物元素の添加は、所定の形状にエッティング加工する前の半導体膜に対して行っても良いし、所定の形状にエッティング加工した後の半導体膜 702 に対して行っても良い。また、しきい値電圧を制御するための不純物元素の添加を、ボンド基板に対して行っても良い。若しくは、不純物元素の添加を、しきい値電圧を大まかに調整するためにボンド基板に対して行った上で、しきい値電圧を微調整するために、所定の形状にエッティング加工する前の半導体膜に対して、又は所定の形状にエッティング加工した後の半導体膜 702 に対して行っても良い。20

#### 【0121】

なお、本実施の形態では、単結晶の半導体膜を用いる例について説明しているが、本発明はこの構成に限定されない。例えば、絶縁膜 701 上に気相成長法を用いて形成された多結晶、微結晶、非晶質の半導体膜を用いても良いし、上記半導体膜を公知の技術により結晶化しても良い。公知の結晶化方法としては、レーザ光を用いたレーザ結晶化法、触媒元素を用いる結晶化法がある。或いは、触媒元素を用いる結晶化法とレーザ結晶化法とを組み合わせて用いることもできる。また、石英のような耐熱性に優れている基板を用いる場合、電熱炉を使用した熱結晶化方法、赤外光を用いたランプ加熱結晶化法、触媒元素を用いる結晶化法、950 度の高温加熱法を組み合わせた結晶化法を用いても良い。30

#### 【0122】

次に、図 12 (B) に示すように、半導体膜 702 上にゲート絶縁膜 703 を形成した後、ゲート絶縁膜 703 上にマスク 705 を形成し、導電性を付与する不純物元素を半導体膜 702 の一部に添加することで、不純物領域 704 を形成する。

#### 【0123】

ゲート絶縁膜 703 は、高密度プラズマ処理、熱処理などを行うことにより半導体膜 702 の表面を酸化又は窒化することで形成することができる。高密度プラズマ処理は、例えば H<sub>e</sub>、A<sub>r</sub>、K<sub>r</sub>、X<sub>e</sub> などの希ガスと酸素、酸化窒素、アンモニア、窒素、水素などの混合ガスとを用いて行う。この場合、プラズマの励起をマイクロ波の導入により行うことで、低電子温度で高密度のプラズマを生成することができる。このような高密度のプラズマで生成された酸素ラジカル (OH ラジカルを含む場合もある) や窒素ラジカル (NH ラジカルを含む場合もある) によって、半導体膜の表面を酸化又は窒化することにより、1 ~ 20 nm、好ましくは 5 ~ 10 nm の絶縁膜が半導体膜に接するように形成できる。例えば、亜酸化窒素 (N<sub>2</sub>O) を A<sub>r</sub> で 1 ~ 3 倍 (流量比) に希釈して、10 ~ 30 Pa の圧力にて 3 ~ 5 kW のマイクロ波 (2.45 GHz) 電力を印加して半導体膜 702 の表面を酸化若しくは窒化させる。この処理により 1 nm ~ 10 nm (好ましくは 2 nm ~ 6 nm) の絶縁膜を形成する。更に亜酸化窒素 (N<sub>2</sub>O) とシラン (SiH<sub>4</sub>) を導入し4050

、10 ~ 30 Pa の圧力にて3 ~ 5 kWのマイクロ波(2.45 GHz)電力を印加して気相成長法により酸化窒化珪素膜を形成してゲート絶縁膜を形成する。固相反応と気相成長法による反応を組み合わせることにより界面準位密度が低く絶縁耐圧の優れたゲート絶縁膜を形成することができる。

#### 【0124】

上述した高密度プラズマ処理による半導体膜の酸化又は窒化は固相反応で進むため、ゲート絶縁膜703と半導体膜702との界面準位密度を極めて低くすることができる。また高密度プラズマ処理により半導体膜702を直接酸化又は窒化することで、形成される絶縁膜の厚さのばらつきを抑えることができる。また半導体膜が結晶性を有する場合、高密度プラズマ処理を用いて半導体膜の表面を固相反応で酸化させることにより、結晶粒界においてのみ酸化が速く進んでしまうのを抑え、均一性が良く、界面準位密度の低いゲート絶縁膜を形成することができる。高密度プラズマ処理により形成された絶縁膜を、ゲート絶縁膜の一部又は全部に含んで形成されるトランジスタは、特性のばらつきを抑えることができる。10

#### 【0125】

また、プラズマCVD法又はスパッタリング法などを用い、酸化珪素、窒化珪素、窒化酸化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸化ジルコニウム、酸化イットリウム、酸化ランタン、酸化セシウム、酸化タンタル、酸化マグネシウム、酸化ハフニウム、ハフニウムシリケート( $HfSi_xO_y$ ( $x > 0$ 、 $y > 0$ ))、窒素が添加されたハフニウムシリケート( $HfSi_xO_y$ ( $x > 0$ 、 $y > 0$ ))、窒素が添加されたハフニウムアルミネート( $HfAl_xO_y$ ( $x > 0$ 、 $y > 0$ ))等を含む膜を、単層で、又は積層させることで、ゲート絶縁膜703を形成しても良い。20

#### 【0126】

なお、本明細書において酸化窒化物とは、その組成として、窒素よりも酸素の含有量が多い物質であり、また、窒化酸化物とは、その組成として、酸素よりも窒素の含有量が多い物質を意味する。

#### 【0127】

ゲート絶縁膜703の厚さは、例えば、1 nm以上100 nm以下、好ましくは10 nm以上50 nm以下とすることができます。本実施の形態では、プラズマCVD法を用いて、酸化珪素を含む単層の絶縁膜を、ゲート絶縁膜703として用いる。30

#### 【0128】

次いで、マスク705を除去した後、図12(C)に示すように、ゲート絶縁膜703の一部を除去して、不純物領域704と重畠する領域にエッチング等により開口部706を形成した後、ゲート電極707及び導電膜708を形成する。

#### 【0129】

ゲート電極707及び導電膜708は、開口部706を覆うように導電膜を形成した後、該導電膜を所定の形状に加工することで、形成することができる。導電膜708は、開口部706において不純物領域704と接している。上記導電膜の形成にはCVD法、スパッタリング法、蒸着法、スピンドル法等を用いることができる。また、導電膜は、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)、マグネシウム(Mg)等を用いることができる。上記金属を主成分とする合金を用いても良いし、上記金属を含む化合物を用いても良い。又は、半導体膜に導電性を付与するリン等の不純物元素をドーピングした、多結晶珪素などの半導体を用いて形成しても良い。40

#### 【0130】

なお、本実施の形態ではゲート電極707及び導電膜708を単層の導電膜で形成しているが、本実施の形態はこの構成に限定されない。ゲート電極707及び導電膜708は積層された複数の導電膜で形成されていても良い。

#### 【0131】

2つの導電膜の組み合わせとして、1層目に窒化タンタル又はタンタルを、2層目にタン50

ゲステンを用いることができる。上記例の他に、窒化タンゲステンとタンゲステン、窒化モリブデンとモリブデン、アルミニウムとタンタル、アルミニウムとチタン等が挙げられる。タンゲステンや窒化タンタルは、耐熱性が高いため、2層の導電膜を形成した後の工程において、熱活性化を目的とした加熱処理を行うことができる。また、2層の導電膜の組み合わせとして、例えば、n型の導電性を付与する不純物元素がドーピングされた珪素とニッケルシリサイド、n型の導電性を付与する不純物元素がドーピングされた珪素とタンゲステンシリサイド等も用いることができる。

#### 【0132】

3つの導電膜を積層する3層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

10

#### 【0133】

また、ゲート電極707及び導電膜708に酸化インジウム、酸化インジウム酸化スズ混合物、酸化インジウム酸化亜鉛混合物、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、又は酸化亜鉛ガリウム等の透光性を有する酸化物導電膜を用いることもできる。

#### 【0134】

なお、マスクを用いずに、液滴吐出法を用いて選択的にゲート電極707及び導電膜708を形成しても良い。液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出又は噴出することで所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。

20

#### 【0135】

また、ゲート電極707及び導電膜708は、導電膜を形成後、誘導結合型プラズマ(I CP: Inductively Coupled Plasma)を用いたドライエッチング法を用い、エッチング条件(コイル型の電極層に印加される電力量、基板側の電極層に印加される電力量、基板側の電極温度等)を適宜調節することにより、所望のテーパー形状を有するようにエッチングすることができる。また、テーパー形状は、マスクの形状によっても角度等を制御することができる。なお、エッチング用ガスとしては、塩素、塩化硼素、塩化珪素もしくは四塩化炭素などの塩素系ガス、四弗化炭素、弗化硫黄もしくは弗化窒素などのフッ素系ガス又は酸素を適宜用いることができる。

#### 【0136】

30

次に、図12(D)に示すように、ゲート電極707及び導電膜708をマスクとして一導電性を付与する不純物元素を半導体膜702に添加することで、ゲート電極707と重なるチャネル形成領域710と、チャネル形成領域710を間に挟む一対の不純物領域709と、不純物領域704の一部に更に不純物元素が添加された不純物領域711とが、半導体膜702に形成される。

#### 【0137】

本実施の形態では、半導体膜702にp型を付与する不純物元素(例えばボロン)を添加する場合を例に挙げる。

#### 【0138】

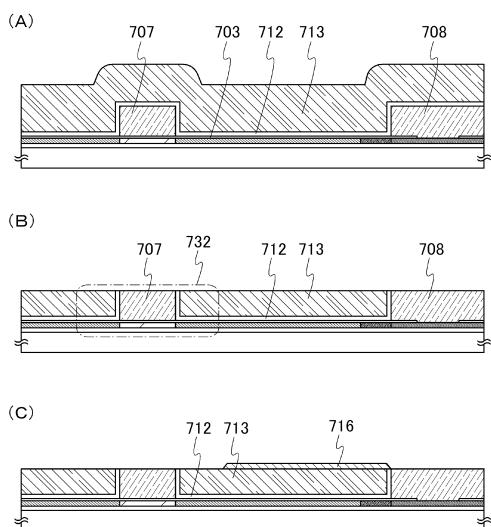

次いで、図13(A)に示すように、ゲート絶縁膜703、ゲート電極707、導電膜708を覆うように、絶縁膜712、絶縁膜713を形成する。具体的には、絶縁膜712、絶縁膜713は、酸化珪素、窒化珪素、窒化酸化珪素、酸化窒化珪素、窒化アルミニウム、酸化アルミニウム、窒化酸化アルミニウム、酸化窒化アルミニウム、酸化ハフニウム、酸化ジルコニアム、酸化イットリウム、酸化ランタン、酸化セシウム、酸化タンタル、または酸化マグネシウムなどの無機の絶縁膜を単層または積層して用いることができる。なお、絶縁膜712、絶縁膜713に誘電率の低い(low-k)材料を用いることで、各種電極や配線の重なりに起因する容量を十分に低減することが可能になる。なお、絶縁膜712、絶縁膜713に、上記材料を用いた多孔性の絶縁膜を適用してもよい。多孔性の絶縁膜では、密度の高い絶縁膜と比較して誘電率が低下するため、電極や配線に起因する寄生容量を更に低減することが可能である。

40

50

**【 0 1 3 9 】**

本実施の形態では、絶縁膜712として酸化窒化珪素、絶縁膜713として窒化酸化珪素を用いる場合を例に挙げる。また、本実施の形態では、ゲート電極707及び導電膜708上に絶縁膜712、絶縁膜713を形成している場合を例示しているが、本発明はゲート電極707及び導電膜708上に絶縁膜を1層だけ形成していても良いし、3層以上の複数の絶縁膜を積層するように形成しても良い。

**【 0 1 4 0 】**

次いで、図13(B)に示すように、絶縁膜712及び絶縁膜713にCMP(化学的機械研磨)処理やエッチング処理を行うことにより、ゲート電極707及び導電膜708の表面を露出させる。なお、後に形成されるトランジスタ731の特性を向上させるために、絶縁膜712、絶縁膜713の表面は可能な限り平坦にしておくことが好ましい。

10

**【 0 1 4 1 】**

以上の工程により、トランジスタ732を形成することができる。

**【 0 1 4 2 】**

次いで、トランジスタ731の作製方法について説明する。まず、図13(C)に示すように、絶縁膜712又は絶縁膜713上に酸化物半導体層716を形成する。

**【 0 1 4 3 】**

酸化物半導体層716は、絶縁膜712及び絶縁膜713上に形成した酸化物半導体膜を所望の形状に加工することで、形成することができる。具体的には、酸化物半導体膜上にフォトリソグラフィ法やインクジェット法などの公知の技術を用いて、加工したいパターン形状に応じたレジストマスクを形成し、ドライエッチング法やウェットエッチング法などの公知の技術を用いて酸化物半導体膜の不要部分を選択的に除去して、酸化物半導体層716を形成すればよい。

20

**【 0 1 4 4 】**

酸化物半導体膜はスパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて形成することができる。上記酸化物半導体膜の膜厚は、2nm以上200nm以下、好ましくは3nm以上50nm以下、更に好ましくは3nm以上20nm以下とする。

**【 0 1 4 5 】**

酸化物半導体膜をスパッタリング法により成膜する場合は、ターゲットとして例えばInとZnを含む金属酸化物を用いることができる。また、スパッタガスとして、希ガス(例えばアルゴン)、酸素、又は希ガスと酸素の混合ガスを用いることができる。スパッタガスとして希ガスと酸素の混合ガスを用いる場合は、酸素ガスの割合を30体積%以上、好ましくは50体積%以上、さらに好ましくは80体積%以上とする。なお、酸化物半導体膜は薄いほど、トランジスタの短チャネル効果が低減される。ただし、薄くしすぎると界面散乱の影響が強くなり、電界効果移動度の低下が起こることがある。

30

**【 0 1 4 6 】**

なお、酸化物半導体膜をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、絶縁膜712及び絶縁膜713の表面に付着している塵埃を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、四フッ化炭素などを加えた雰囲気で行ってもよい。

40

**【 0 1 4 7 】**

酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含む材料を用いることが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また

50

、スタビライザーとしてハフニウム( Hf )を有することが好ましい。また、スタビライザーとしてアルミニウム( Al )を有することが好ましい。

#### 【 0148 】

また、他のスタビライザーとして、ランタノイドである、ランタン( La )、セリウム( Ce )、プラセオジム( Pr )、ネオジム( Nd )、サマリウム( Sm )、ユウロピウム( Eu )、ガドリニウム( Gd )、テルビウム( Tb )、ジスプロシウム( Dy )、ホルミウム( Ho )、エルビウム( Er )、ツリウム( Tm )、イッテルビウム( Yb )、ルテチウム( Lu )のいずれか一種あるいは複数種を有してもよい。

#### 【 0149 】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物である In - Zn 系酸化物、 Sn - Zn 系酸化物、 Al - Zn 系酸化物、 Zn - Mg 系酸化物、 Sn - Mg 系酸化物、 In - Mg 系酸化物、 In - Ga 系酸化物、三元系金属の酸化物である In - Ga - Zn 系酸化物( IGZO とも表記する)、 In - Al - Zn 系酸化物、 In - Sn - Zn 系酸化物、 Sn - Ga - Zn 系酸化物、 Al - Ga - Zn 系酸化物、 Sn - Al - Zn 系酸化物、 In - Hf - Zn 系酸化物、 In - La - Zn 系酸化物、 In - Ce - Zn 系酸化物、 In - Pr - Zn 系酸化物、 In - Nd - Zn 系酸化物、 In - Sm - Zn 系酸化物、 In - Eu - Zn 系酸化物、 In - Gd - Zn 系酸化物、 In - Tb - Zn 系酸化物、 In - Dy - Zn 系酸化物、 In - Ho - Zn 系酸化物、 In - Er - Zn 系酸化物、 In - Tm - Zn 系酸化物、 In - Yb - Zn 系酸化物、 In - Lu - Zn 系酸化物、四元系金属の酸化物である In - Sn - Ga - Zn 系酸化物、 In - Hf - Ga - Zn 系酸化物、 In - Al - Ga - Zn 系酸化物、 In - Sn - Al - Zn 系酸化物、 In - Sn - Hf - Zn 系酸化物、 In - Hf - Al - Zn 系酸化物を用いることができる。また、上記酸化物半導体に SiO<sub>2</sub> を含ませてもよい。

#### 【 0150 】

なお、ここで、例えば、 In - Ga - Zn 系酸化物とは、 In と Ga と Zn を主成分として有する酸化物という意味であり、 In と Ga と Zn の比率は問わない。また、 In と Ga と Zn 以外の金属元素が入っていてもよい。

#### 【 0151 】

また、酸化物半導体として、 InMO<sub>3</sub>( ZnO )<sub>m</sub> ( m > 0 ) で表記される材料を用いてもよい。なお、 M は、 Sn 、 Zn 、 Ga 、 Fe 、 Mn 及び Co から選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、 In<sub>2</sub>SnO<sub>5</sub>( ZnO )<sub>n</sub> ( n > 0 ) で表記される材料を用いてもよい。

#### 【 0152 】

例えば、 In : Ga : Zn = 1 : 1 : 1 あるいは In : Ga : Zn = 2 : 2 : 1 の原子数比の In - Ga - Zn 系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 In : Sn : Zn = 1 : 1 : 1 、 In : Sn : Zn = 2 : 1 : 3 あるいは In : Sn : Zn = 2 : 1 : 5 の原子数比の In - Sn - Zn 系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【 0153 】

しかし、これらに限らず、必要とする半導体特性(電界効果移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

#### 【 0154 】

例えば、 In - Sn - Zn 系酸化物では比較的容易に高い電界効果移動度が得られる。しかしながら、 In - Ga - Zn 系酸化物でも、バルク内欠陥密度を低減することにより電界効果移動度を上げることができる。

#### 【 0155 】

なお、例えば、 In 、 Ga 、 Zn の原子数比が In : Ga : Zn = a : b : c ( a + b + c = 1 ) である酸化物と、原子数比が In : Ga : Zn = A : B : C ( A + B + C = 1 )

10

20

30

40

50

の酸化物の組成が近傍であるとは、a、b、cが、

$(a - A)^2 + (b - B)^2 + (c - C)^2 = r^2$

を満たすことを言う。rは、例えば、0.05とすればよい。他の酸化物でも同様である。

#### 【0156】

また、酸化物半導体としてIn-Zn系酸化物を用いる場合、原子数比で、In/Zn = 0.5 ~ 5.0、好ましくはIn/Zn = 1 ~ 2.0、さらに好ましくはIn/Zn = 1.5 ~ 1.5とする。Znの原子数比を好ましい前記範囲とすることで、トランジスタの電界効果移動度を向上させることができる。ここで、化合物の原子数比がIn : Zn : O = X : Y : Zのとき、Z > 1.5X + Yとする。

10

#### 【0157】

本実施の形態では、In(インジウム)、Ga(ガリウム)、及びZn(亜鉛)を含む金属酸化物ターゲットを用いたスパッタリング法により得られる、膜厚30nmのIn-Ga-Zn系酸化物の薄膜を、酸化物半導体膜として用いる。上記ターゲットとして、例えば、各金属の組成比が、原子数比でIn : Ga : Zn = 1 : 1 : 0.5、In : Ga : Zn = 1 : 1 : 1、またはIn : Ga : Zn = 1 : 1 : 2であるターゲットを用いることができる。また、酸化物半導体を形成するための金属酸化物ターゲットの相対密度は90%以上100%以下、好ましくは95%以上100%未満である。相対密度の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。なお、In-Ga-Zn系酸化物は、IGZOと呼ぶことができる。

20

#### 【0158】

酸化物半導体膜としてIn-Sn-Zn系酸化物の薄膜を用いる場合は、In-Sn-Zn系酸化物をスパッタリング法で成膜するためのターゲットの組成比を、In : Sn : Znが原子数比で、1 : 2 : 2、2 : 1 : 3、1 : 1 : 1、または20 : 45 : 35などとすればよい。

#### 【0159】

なお、In(インジウム)、及びZn(亜鉛)を含むターゲットを用いて酸化物半導体膜を形成する場合、ターゲットの原子数比がIn/Znが0.5以上5.0以下、好ましくは1以上2.0以下、さらに好ましくは1.5以上1.5以下となるようにする。Znの比率を上記範囲に収めることで、電界効果移動度の向上を実現することができる。

30

#### 【0160】

本実施の形態では、減圧状態に保持された成膜室内に基板を保持し、成膜室内の残留水分を除去しつつ水素及び水が除去されたスパッタガスを導入し、上記ターゲットを用いて酸化物半導体膜を成膜する。スパッタガスは高純度化されたガスを用いることが好ましい。例えば、スパッタガスとしてアルゴンを用いる場合は、純度9N、露点-121、含有H<sub>2</sub>O量0.1ppb以下、含有H<sub>2</sub>量0.5ppb以下が好ましく、酸素を用いる場合は、純度8N、露点-112、含有H<sub>2</sub>O量1ppb以下、含有H<sub>2</sub>量1ppb以下が好ましい。

#### 【0161】

酸化物半導体膜は、酸化物半導体の化学量論比に対し、酸素を過剰にすると好ましい。酸素を過剰にすることで酸化物半導体の酸素欠損に起因するキャリアの生成を抑制することができる。

40

#### 【0162】

成膜時に、基板温度を100以上600以下、好ましくは200以上400以下としても良い。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。成膜室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて成膜室内のガスを排気すると、例えば、水素原子

50

、水（H<sub>2</sub>O）など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

#### 【0163】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流（DC）電源0.5kW、スパッタガスとして酸素（酸素流量比率100%）を用いる条件が適用される。なお、パルス直流（DC）電源を用いると、成膜時に発生する塵埃が軽減でき、膜厚分布も均一となるために好ましい。

#### 【0164】

また、スパッタリング装置の成膜室のリークレートを $1 \times 10^{-10} \text{ Pa} \cdot \text{m}^3 / \text{秒}$ 以下とすることで、スパッタリング法による成膜途中における酸化物半導体膜への、アルカリ金属、水素化物等の不純物の混入を低減することができる。また、排気系として上述した吸着型の真空ポンプを用いることで、排気系からのアルカリ金属、水素原子、水素分子、水、水酸基、または水素化物等の不純物の逆流を低減することができる。

#### 【0165】

また、ターゲットの純度を、99.99%以上とすることで、酸化物半導体膜に混入するアルカリ金属、水素原子、水素分子、水、水酸基、または水素化物等を低減することができる。また、当該ターゲットを用いることで、酸化物半導体膜において、リチウム、ナトリウム、カリウム等のアルカリ金属の濃度を低減することができる。

#### 【0166】

なお、酸化物半導体膜に水素、水酸基及び水がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室で絶縁膜712及び絶縁膜713までが形成された基板700を予備加熱し、基板700に吸着した水又は水素などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100以上400以下、好ましくは150以上300以下である。また、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。また、この予備加熱は、後に行われるゲート絶縁膜721の成膜前に、導電膜719、導電膜720まで形成した基板700にも同様に行ってよい。

#### 【0167】

なお、酸化物半導体層716を形成するためのエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。ドライエッチングに用いるエッチングガスとしては、塩素を含むガス（塩素系ガス、例えば塩素（Cl<sub>2</sub>）、三塩化硼素（BCl<sub>3</sub>）、四塩化珪素（SiCl<sub>4</sub>）、四塩化炭素（CCl<sub>4</sub>）など）が好ましい。また、フッ素を含むガス（フッ素系ガス、例えば四弗化炭素（CF<sub>4</sub>）、六弗化硫黄（SF<sub>6</sub>）、三弗化窒素（NF<sub>3</sub>）、トリフルオロメタン（CHF<sub>3</sub>）など）、臭化水素（HBr）、酸素（O<sub>2</sub>）、これらのガスにヘリウム（He）やアルゴン（Ar）などの希ガスを添加したガス、などを用いることができる。

#### 【0168】

ドライエッチング法としては、反応性イオンエッチング（RIE：Reactive Ion Etching）法を用いることができる。また、プラズマ源として、容量結合型プラズマ（CCP：Capacitively Coupled Plasma）、誘導結合型プラズマ（ICP：Inductively Coupled Plasma）、電子サイクロトロン共鳴（ECR：Electron Cyclotron Resonance）プラズマ、ヘリコン波励起プラズマ（HWP：Helicon Wave Plasma）、マイクロ波励起表面波プラズマ（SWP：Surface Wave Plasma）などを用いることができる。エッチングをドライエッチング法で行う場合は、所望の形状にエッチングできるように、エッチング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節する。

#### 【0169】

ウェットエッチングに用いるエッチング液として、磷酸と酢酸と硝酸を混ぜた溶液、クエ

10

20

30

40

50

ン酸やシュウ酸などの有機酸を用いることができる。本実施の形態では、ITO-07N（関東化学社製）を用いる。

**【0170】**

酸化物半導体層716を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

**【0171】**

なお、次工程の導電膜を形成する前に逆スパッタを行い、酸化物半導体層716及び絶縁膜712及び絶縁膜713の表面に付着しているレジスト残渣などを除去することが好ましい。

10

**【0172】**

なお、スパッタ等で成膜された酸化物半導体膜中には、不純物としての水又は水素（水酸基を含む）が多量に含まれていることがある。水又は水素はドナー準位を形成しやすいため、酸化物半導体にとっては不純物である。そこで、本発明の一態様では、酸化物半導体膜中の水又は水素などの不純物を低減（脱水化または脱水素化）するために、酸化物半導体層716に対して、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、又は超乾燥エア（CRDS（キャビティリングダウンレーザー分光法）方式の露点計を用いて測定した場合の水分量が20 ppm（露点換算で-55）以下、好ましくは1 ppm以下、好ましくは10 ppb以下の空気）雰囲気下で、加熱処理を施す。

20

**【0173】**

酸化物半導体層716に加熱処理を施すことで、酸化物半導体層716中の水又は水素を脱離させることができる。具体的には、250以上750以下、好ましくは400以上基板の歪み点未満の温度で加熱処理を行えば良い。例えば、500、3分間以上6分間以下程度で行えばよい。加熱処理にRTA法を用いれば、短時間に脱水化又は脱水素化が行えるため、基板にガラス基板を用いた場合においても、ガラス基板の歪点を超える温度でも処理することができる。

**【0174】**

本実施の形態では、加熱処理装置の一つである電気炉を用いる。

**【0175】**

なお、加熱処理装置は電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA（Gas Rapid Thermal Anneal）装置、LRTA（Lamp Rapid Thermal Anneal）装置等のRTA（Rapid Thermal Anneal）装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

30

**【0176】**

加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水又は水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N（99.9999%）以上、好ましくは7N（99.99999%）以上、（即ち不純物濃度を1 ppm以下、好ましくは0.1 ppm以下）とすることが好ましい。

40

**【0177】**

以上の工程により、酸化物半導体層716中の水素の濃度を低減し、酸化物半導体層716を高純度化することができる。

**【0178】**

酸化物半導体層716を形成した後、イオン注入法により酸化物半導体層716に酸素を

50

導入してもよい。また、酸素の導入は、プラズマドープ法により行ってもよい。具体的には、高周波（R F）を用いて酸素をプラズマ化し、酸素ラジカル、酸素イオンを酸化物半導体層716へ導入する。この時、酸化物半導体層716が形成される基板にバイアスを印加すると好ましい。基板に印加するバイアスを大きくすることで、より深くまで酸素を導入することができる。

#### 【0179】

プラズマドープ法により酸化物半導体層716へ導入される酸素（酸素ラジカル、酸素原子、及び／又は酸素イオン）は、酸素を含むガスを用いてプラズマ発生装置により供給されてもよいし、又はオゾン発生装置により供給されてもよい。

#### 【0180】

酸化物半導体層716に酸素を導入した後、加熱処理（好ましくは200以上600以下、例えば250以上550以下）を行ってもよい。例えば、窒素雰囲気下で450、1時間の加熱処理を行う。なお、上記雰囲気に水、水素などが含まれないことが好ましい。

#### 【0181】

酸化物半導体層716への酸素の導入及び加熱処理によって、不純物の排除工程によって同時に減少してしまう酸化物半導体を構成する主成分材料の一つである酸素を補い酸化物半導体層716をi型（真性）化することができる。

#### 【0182】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

#### 【0183】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い電界効果移動度を得ることができる。

#### 【0184】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の電界効果移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することができる。具体的には、平均面粗さ（Ra）が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。Raは原子間力顕微鏡（AFM：A t o m i c F o r c e M i c r o s c o p e）にて評価可能である。

#### 【0185】

酸化物半導体層716に、結晶性を有する酸化物半導体を用いる場合は、酸化物半導体層716と接する絶縁膜713は、酸化物半導体が結晶成長しやすいように、十分な平坦性を有することが好ましい。また、絶縁膜713と酸化物半導体層716の間に、十分な平坦性を有する絶縁膜を設けてもよい。

#### 【0186】

結晶性を有する酸化物半導体としては、c軸配向し、かつab面、表面または界面の方向から見て三角形状または六角形状の原子配列を有し、c軸においては金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面においてはa軸またはb軸の向きが異なる（c軸を中心に回転した）結晶を含む酸化物半導体（C A A C - O S : C A x i s A l i g n e d C r y s t a l l i n e O x i d e S e m i c o n d u c t o rともいう）を用いることが好ましい。

#### 【0187】

C A A C - O Sとは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有し、かつc軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含む。

#### 【0188】

10

20

30

40

50

C A A C - O S は単結晶ではないが、非晶質のみから形成されているものでもない。また、C A A C - O S は結晶化した部分（結晶部分）を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できることもある。

#### 【 0 1 8 9 】

C A A C - O S を構成する酸素の一部は窒素で置換されてもよい。また、C A A C - O S を構成する個々の結晶部分の c 軸は一定の方向（例えば、C A A C - O S が形成される基板面、C A A C - O S の表面などに垂直な方向）に揃っていてもよい。または、C A A C - O S を構成する個々の結晶部分の a b 面の法線は一定の方向（例えば、C A A C - O S が形成される基板面、C A A C - O S の表面などに垂直な方向）を向いていてもよい。

#### 【 0 1 9 0 】

C A A C - O S は、その組成などに応じて、導体または絶縁体となりうる。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

#### 【 0 1 9 1 】

このようなC A A C - O S の例として、膜状に形成され、膜表面または支持する基板面に垂直な方向から観察すると三角形または六角形の原子配列が認められ、かつその膜断面を観察すると金属原子または金属原子および酸素原子（または窒素原子）の層状配列が認められる酸化物を挙げることもできる。

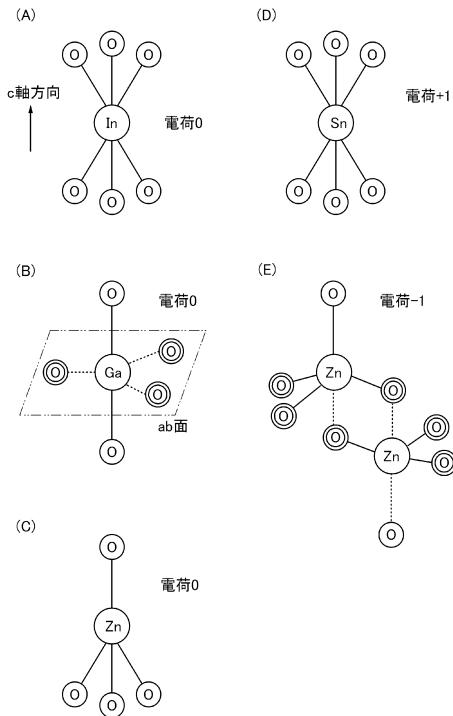

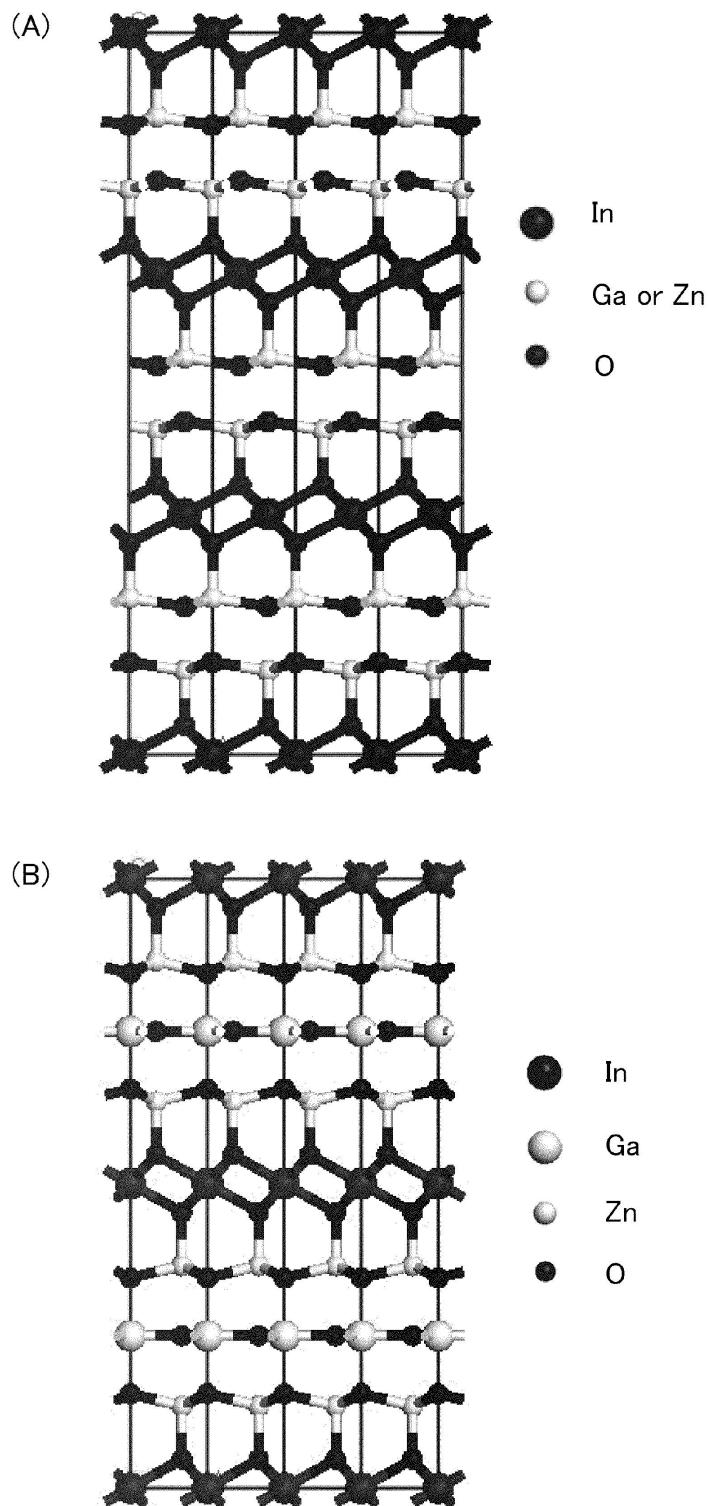

#### 【 0 1 9 2 】

C A A C - O S に含まれる結晶構造の一例について図18乃至図20を用いて詳細に説明する。なお、特に断りがない限り、図18乃至図20は上方向をc軸方向とし、c軸方向と直交する面をa b面とする。なお、単に上半分、下半分という場合、a b面を境にした場合の上半分、下半分をいう。また、図18において、丸で囲まれたOは4配位のOを示し、二重丸で囲まれたOは3配位のOを示す。

#### 【 0 1 9 3 】

図18（A）に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子（以下4配位のO）と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図18（A）の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図18（A）の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図18（A）に示す小グループは電荷が0である。

#### 【 0 1 9 4 】

図18（B）に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子（以下3配位のO）と、Gaに近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもa b面に存在する。図18（B）の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図18（B）に示す構造をとりうる。図18（B）に示す小グループは電荷が0である。

#### 【 0 1 9 5 】

図18（C）に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図18（C）の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図18（C）の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあつてもよい。図18（C）に示す小グループは電荷が0である。

#### 【 0 1 9 6 】

図18（D）に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図18（D）の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図18（D）に示す小グループは電荷が+1となる。

#### 【 0 1 9 7 】

図18（E）に、2個のZnを含む小グループを示す。図18（E）の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図18（E）に示す小グループは電荷が-1となる。

#### 【 0 1 9 8 】

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を

10

20

30

40

50

大グループ(ユニットセルともいう。)と呼ぶ。

#### 【0199】

ここで、これらの小グループ同士が結合する規則について説明する。図18(A)に示す6配位のInの上半分の3個のOは下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは上方向にそれぞれ3個の近接Inを有する。図18(B)に示す5配位のGaの上半分の1個のOは下方向に1個の近接Gaを有し、下半分の1個のOは上方向に1個の近接Gaを有する。図18(C)に示す4配位のZnの上半分の1個のOは下方向に1個の近接Znを有し、下半分の3個のOは上方向にそれぞれ3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。その理由を以下に示す。例えば、6配位の金属原子(InまたはSn)が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)または4配位の金属原子(Zn)のいずれかと結合することになる。

#### 【0200】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

#### 【0201】

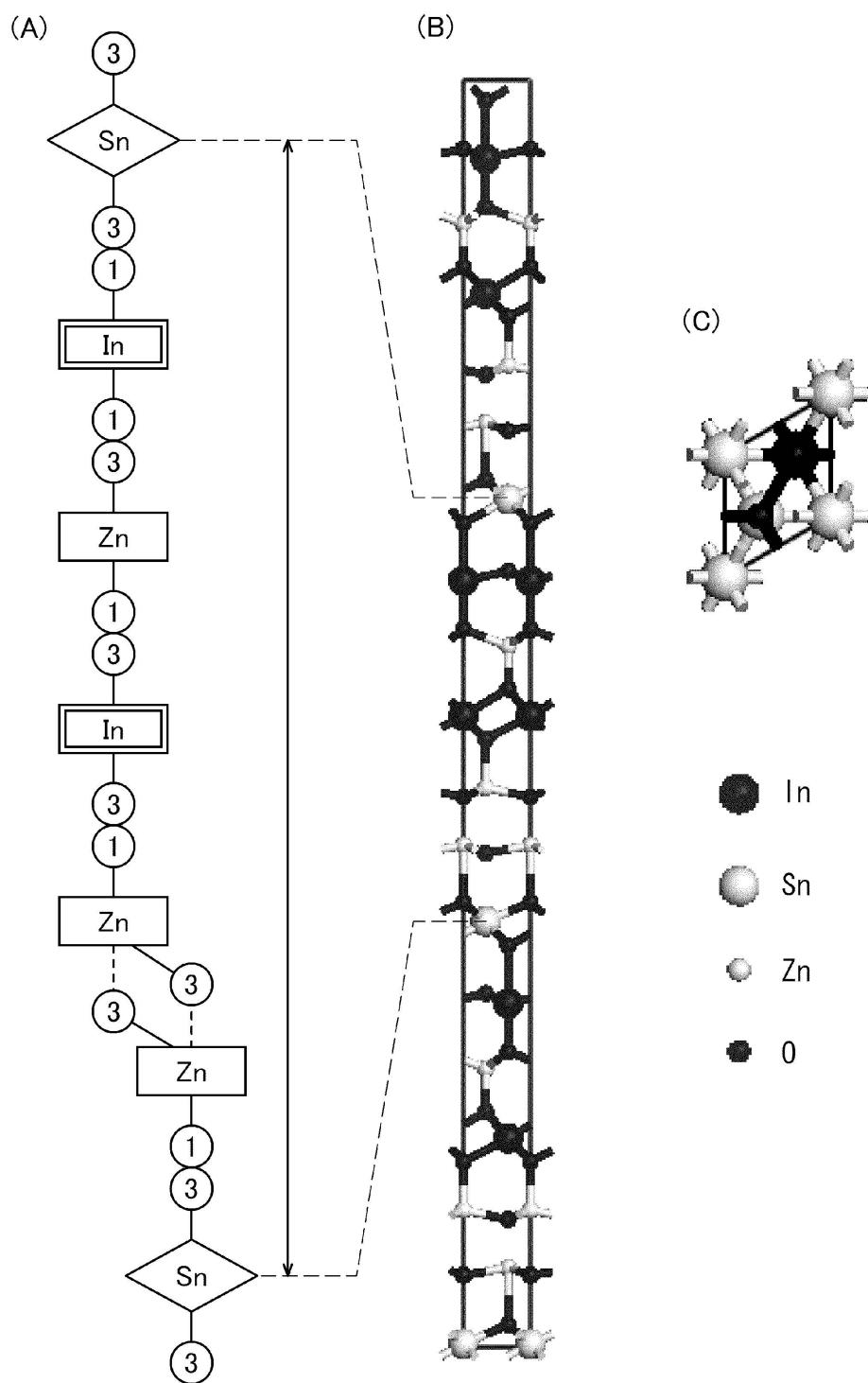

図19(A)に、In-Sn-Zn系酸化物の層構造を構成する中グループのモデル図を示す。図19(B)に、3つの中グループで構成される大グループを示す。なお、図19(C)は、図19(B)の層構造をc軸方向から観察した場合の原子配列を示す。

#### 【0202】

図19(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図19(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図19(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

#### 【0203】

図19(A)において、In-Sn-Zn系酸化物の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

#### 【0204】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ-0.667、-0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷-1が必要となる。電荷-1をとる構造として、図18(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消され

るため、層構造の合計の電荷を0とすることができます。

**【0205】**

具体的には、図19(B)に示した大グループが繰り返されることで、In-Sn-Zn系酸化物の結晶( $In_2SnZn_3O_8$ )を得ることができる。なお、得られるIn-Sn-Zn系酸化物の層構造は、 $In_2SnZn_2O_7$ , ( $ZnO$ )<sub>m</sub>(mは0または自然数。)とする組成式で表すことができる。

**【0206】**

また、このほかにも、四元系金属の酸化物であるIn-Sn-Ga-Zn系酸化物や、三元系金属の酸化物であるIn-Ga-Zn系酸化物(IGZOとも表記する。)、In-Al-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物や、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物や、二元系金属の酸化物であるIn-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物や、In-Ga系酸化物、一元系金属の酸化物であるIn系酸化物、Sn系酸化物、Zn系酸化物などを用いた場合も同様である。

**【0207】**

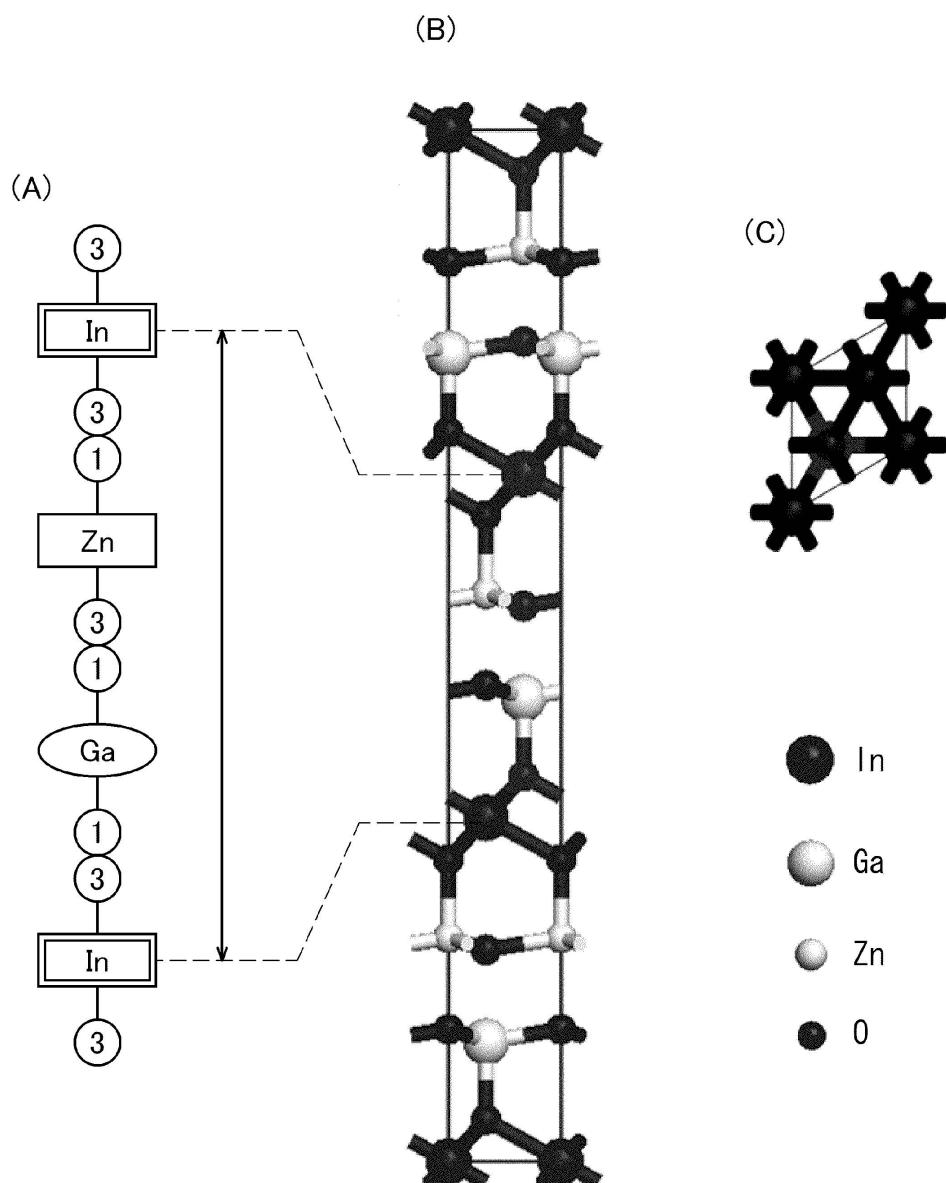

例えば、図20(A)に、In-Ga-Zn系酸化物の層構造を構成する中グループのモデル図を示す。

**【0208】**

図20(A)において、In-Ga-Zn系酸化物の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるInが、4配位のOが1個上半分にあるZnと結合し、そのZnの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にあるGaと結合し、そのGaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にあるInと結合している構成である。この中グループが複数結合して大グループを構成する。

**【0209】**

図20(B)に3つの中グループで構成される大グループを示す。なお、図20(C)は、図20(B)の層構造をc軸方向から観察した場合の原子配列を示している。

**【0210】**

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、ZnおよびGaのいずれかを含む小グループは、電荷が0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

**【0211】**

また、In-Ga-Zn系酸化物の層構造を構成する中グループは、図20(A)に示した中グループに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせた大グループも取りうる。

**【0212】**

具体的には、図20(B)に示した大グループが繰り返されることで、In-Ga-Zn系酸化物の結晶を得ることができる。なお、得られるIn-Ga-Zn系酸化物の層構造は、 $InGaO_3$  ( $ZnO$ )<sub>n</sub>(nは自然数。)とする組成式で表すことができる。

**【0213】**

$n = 1$  ( $InGaZnO_4$ )の場合は、例えば、図21(A)に示す結晶構造を取りうる。なお、図21(A)に示す結晶構造において、図18(B)で説明したように、Ga及びInは5配位をとるため、GaがInに置き換わった構造も取りうる。

**【0214】**

10

20

30

40

50

また、 $n = 2$  ( $InGaZn_2O_5$ ) の場合は、例えば、図21(B)に示す結晶構造を取りうる。なお、図21(B)に示す結晶構造において、図18(B)で説明したように、Ga及びInは5配位をとるため、GaがInに置き換わった構造も取りうる。

#### 【0215】

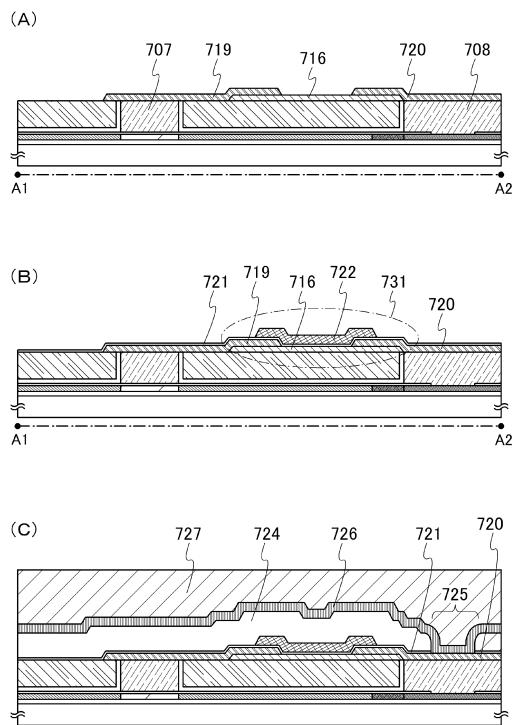

次いで、図14(A)に示すように、ゲート電極707と接し、なおかつ酸化物半導体層716とも接する導電膜719と、導電膜708と接し、なおかつ酸化物半導体層716とも接する導電膜720とを形成する。導電膜719及び導電膜720は、ソース電極又はドレイン電極として機能する。

#### 【0216】

具体的には、導電膜719及び導電膜720は、ゲート電極707及び導電膜708を覆うようにスパッタリング法や真空蒸着法で導電膜を形成した後、該導電膜を所定の形状に加工することで、形成することができる。

#### 【0217】

導電膜719及び導電膜720となる導電膜は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクステン、マグネシウムから選ばれた元素、又は上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、アルミニウム、銅などの金属膜の下側もしくは上側にクロム、タンタル、チタン、モリブデン、タンクステンなどの高融点金属膜を積層させた構成としても良い。また、アルミニウム又は銅は、耐熱性や腐食性の問題を回避するために、高融点金属材料と組み合わせて用いると良い。高融点金属材料としては、モリブデン、チタン、クロム、タンタル、タンクステン、ネオジム、スカンジウム、イットリウム等を用いることができる。

#### 【0218】

また、導電膜719及び導電膜720となる導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、更にその上にチタン膜を成膜する3層構造などが挙げられる。また、Cu-Mg-Al合金、Mo-Ti合金、Ti、Mo、は、酸化膜との密着性が高い。よって、下層にCu-Mg-Al合金、Mo-Ti合金、Ti、或いはMoで構成される導電膜、上層にCuで構成される導電膜を積層し、上記積層された導電膜を導電膜719及び導電膜720に用いることで、酸化膜である絶縁膜と、導電膜719及び導電膜720との密着性を高めることができる。

#### 【0219】

また、導電膜719及び導電膜720となる導電膜としては、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム、酸化スズ、酸化亜鉛、酸化インジウム酸化スズ混合物、酸化インジウム酸化亜鉛混合物又は前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

#### 【0220】

導電膜形成後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

#### 【0221】

なお、導電膜のエッチングの際に、酸化物半導体層716がなるべく除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。エッチング条件によっては、酸化物半導体層716の露出した部分が一部エッチングされることで、溝部(凹部)が形成されることもある。

#### 【0222】

本実施の形態では、導電膜にチタン膜を用いる。そのため、アンモニアと過酸化水素水を含む溶液(アンモニア過水)を用いて、選択的に導電膜をウェットエッチングすることができる。具体的には、31重量%の過酸化水素水と、28重量%のアンモニア水と水とを、体積比5:2:2で混合したアンモニア過水を用いる。或いは、塩素(Cl<sub>2</sub>)、塩化硼素(BCl<sub>3</sub>)などを含むガスを用いて、導電膜をドライエッチングしても良い。

10

20

30

40

50

## 【0223】

なお、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光に多段階の強度をもたせる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことで更に形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

## 【0224】

また、酸化物半導体層716と、ソース電極又はドレイン電極として機能する導電膜719及び導電膜720との間に、ソース領域及びドレイン領域として機能する酸化物導電膜を設けるようにしても良い。酸化物導電膜の材料としては、酸化亜鉛を成分として含むものが好ましく、酸化インジウムを含まないものであることが好ましい。そのような酸化物導電膜として、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、酸化亜鉛ガリウムなどを用いることができる。

## 【0225】

例えば、酸化物導電膜を形成する場合、酸化物導電膜を形成するためのエッチング加工と、導電膜719及び導電膜720を形成するためのエッチング加工とを一括で行うようにしても良い。

## 【0226】

ソース領域及びドレイン領域として機能する酸化物導電膜を設けることで、酸化物半導体層716と導電膜719及び導電膜720の間の抵抗を下げるができるので、トランジスタの高速動作を実現させることができる。また、ソース領域及びドレイン領域として機能する酸化物導電膜を設けることで、トランジスタの耐圧を高めることができる。

## 【0227】

次いで、N<sub>2</sub>O、N<sub>2</sub>、又はArなどのガスを用いたプラズマ処理を行うようにしても良い。このプラズマ処理によって露出している酸化物半導体層の表面に付着した水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

## 【0228】

なお、プラズマ処理を行った後、図14(B)に示すように、導電膜719及び導電膜720と、酸化物半導体層716とを覆うように、ゲート絶縁膜721を形成する。そして、ゲート絶縁膜721において、酸化物半導体層716と重なる位置にゲート電極722を形成する。

## 【0229】

ゲート絶縁膜721は、ゲート絶縁膜703と同様の材料、同様の積層構造を用いて形成することが可能である。なお、ゲート絶縁膜721は、水や、水素などの不純物を極力含まないことが望ましく、単層の絶縁膜であっても良いし、積層された複数の絶縁膜で構成されていても良い。ゲート絶縁膜721に水素が含まれると、その水素が酸化物半導体層716へ侵入し、又は水素が酸化物半導体層716中の酸素を引き抜き、酸化物半導体層716が低抵抗化(n型化)してしまい、寄生チャネルが形成されるおそれがある。

## 【0230】

よって、ゲート絶縁膜721はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。また、ゲート絶縁膜721は、酸素過剰領域を有するのが好ましい。ゲート絶縁膜721が酸素過剰領域を有していると、酸化物半導体層716からゲート絶縁膜721への酸素の移動を防ぐことができ、且つ、ゲート絶縁膜721から酸化物半導体層716への酸素の供給を行うこともできるためである。

## 【0231】

また、ゲート絶縁膜721に、アルカリ金属や、水素及び酸素に対するバリア性の高い材料を用いてもよい。また、ゲート絶縁膜721を、酸素過剰領域を有する絶縁膜とバリア

10

20

30

40

50

性の高い絶縁膜の積層としてもよい。バリア性の高い絶縁膜としては、例えば、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、又は窒化酸化アルミニウム膜などを用いることができる。ゲート絶縁膜721を、酸素過剰領域を有する絶縁膜とバリア性の高い絶縁膜の積層とする場合、酸素過剰領域を有する絶縁膜を酸化物半導体層716に接して形成すればよい。

#### 【0232】

バリア性の高い絶縁膜を用いることで、酸化物半導体層716内、或いは、酸化物半導体層716と絶縁膜の界面とその近傍への不純物の侵入を防ぐとともに、酸化物半導体層中からの酸素脱離を防ぐことができる。

#### 【0233】

本実施の形態では、スパッタリング法で形成された膜厚200nmの酸化珪素膜上に、スパッタリング法で形成された膜厚100nmの窒化珪素膜を積層させた構造を有する、ゲート絶縁膜721を形成する。成膜時の基板温度は、室温以上300℃以下とすればよく、本実施の形態では100℃とする。

10

#### 【0234】

なお、ゲート絶縁膜721を形成した後に、加熱処理を施しても良い。加熱処理は、窒素、超乾燥空気、又は希ガス（アルゴン、ヘリウムなど）の雰囲気下において、好ましくは200℃以上400℃以下、例えば250℃以上350℃以下で行う。上記ガスは、水の含有量が20ppm以下、好ましくは1ppm以下、より好ましくは10ppb以下であることが望ましい。本実施の形態では、例えば、窒素雰囲気下で250℃、1時間の加熱処理を行う。或いは、導電膜719及び導電膜720を形成する前に、水又は水素を低減させるための酸化物半導体層に対して行った先の加熱処理と同様に、高温短時間のRTA処理を行っても良い。酸素を含むゲート絶縁膜721が設けられた後に、加熱処理が施されることによって、酸化物半導体層716に対して行った先の加熱処理により、酸化物半導体層716に酸素欠損が発生していたとしても、ゲート絶縁膜721から酸化物半導体層716に酸素が供与される。

20

#### 【0235】

そして、酸化物半導体層716に酸素が供与されることで、酸化物半導体層716において、ドナーとなる酸素欠損を低減し、化学量論的組成比を満たすことが可能である。その結果、酸化物半導体層716をi型に近づけることができ、酸素欠損によるトランジスタの電気特性のばらつきを軽減し、電気特性の向上を実現することができる。この加熱処理を行うタイミングは、ゲート絶縁膜721の形成後であれば特に限定されず、他の工程、例えば樹脂膜形成時の加熱処理や、透明導電膜を低抵抗化させるための加熱処理と兼ねることで、工程数を増やすことなく、酸化物半導体層716をi型に近づけることができる。

30

#### 【0236】

また、酸素雰囲気下で酸化物半導体層716に加熱処理を施することで、酸化物半導体に酸素を添加し、酸化物半導体層716中においてドナーとなる酸素欠損を低減させても良い。加熱処理の温度は、例えば100℃以上350℃未満、好ましくは150℃以上250℃未満で行う。上記酸素雰囲気下の加熱処理に用いられる酸素ガスには、水、水素などが含まれないことが好ましい。又は、加熱処理装置に導入する酸素ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、（即ち酸素中の不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。

40

#### 【0237】

また、ゲート電極722は、ゲート絶縁膜721上に導電膜を形成した後、該導電膜をエッチング加工することで形成することができる。ゲート電極722は、ゲート電極707、或いは導電膜719及び導電膜720と同様の材料を用いて形成することができる。

#### 【0238】

ゲート電極722の膜厚は、10nm～400nm、好ましくは100nm～200nm

50

とする。本実施の形態では、タングステンターゲットを用いたスパッタリング法により 150 nm のゲート電極用の導電膜を形成した後、該導電膜をエッチングにより所望の形状に加工することで、ゲート電極 722 を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0239】

以上の工程により、トランジスタ 731 が形成される。

#### 【0240】

また、トランジスタ 731 はシングルゲート構造のトランジスタを用いて説明したが、必要に応じて、電気的に接続された複数のゲート電極を有することで、チャネル形成領域を複数有する、マルチゲート構造のトランジスタも形成することができる。10

#### 【0241】

なお、酸化物半導体層 716 に接する絶縁膜（本実施の形態においては、ゲート絶縁膜 721 が該当する。）は、第 13 族元素及び酸素を含む絶縁材料を用いるようにしても良い。酸化物半導体材料には第 13 族元素を含むものが多く、第 13 族元素を含む絶縁材料は酸化物半導体との相性が良く、これを酸化物半導体層に接する絶縁膜に用いることで、酸化物半導体層との界面の状態を良好に保つことができる。

#### 【0242】

第 13 族元素を含む絶縁材料とは、絶縁材料に一又は複数の第 13 族元素を含むことを意味する。第 13 族元素を含む絶縁材料としては、例えば、酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、酸化ガリウムアルミニウムなどがある。ここで、酸化アルミニウムガリウムとは、ガリウムの含有量（原子%）よりアルミニウムの含有量（原子%）が多いものを示し、酸化ガリウムアルミニウムとは、ガリウムの含有量（原子%）がアルミニウムの含有量（原子%）以上のものを示す。20

#### 【0243】

例えば、ガリウムを含有する酸化物半導体層に接して絶縁膜を形成する場合に、絶縁膜に酸化ガリウムを含む材料を用いることで酸化物半導体層と絶縁膜の界面特性を良好に保つことができる。例えば、酸化物半導体層と酸化ガリウムを含む絶縁膜とを接して設けることにより、酸化物半導体層と絶縁膜の界面における水素のパイロアップを低減することができる。なお、絶縁膜に酸化物半導体の成分元素と同じ族の元素を用いる場合には、同様の効果を得ることが可能である。例えば、酸化アルミニウムを含む材料を用いて絶縁膜を形成することも有効である。なお、酸化アルミニウムはバリア性を有する材料であり、水を透過させにくいという特性も有しているため、当該材料を用いることは、酸化物半導体層への水の侵入防止という点においても好ましい。30

#### 【0244】

また、ゲート絶縁膜 721 と同様に、絶縁膜 713 も酸素過剰領域（化学量論的組成比より酸素が多い領域）を有する材料で形成することが好ましい。絶縁膜 713 と酸化物半導体層 716 の間に、酸素過剰領域を有する絶縁膜を形成してもよい。

#### 【0245】

絶縁膜に酸素ドープ処理を行うことにより、酸素過剰領域を有する絶縁膜とすることもできる。酸素ドープとは、酸素をバルクに添加することをいう。なお、当該バルクの用語は、酸素を薄膜表面のみでなく薄膜内部に添加することを明確にする趣旨で用いている。また、酸素ドープには、プラズマ化した酸素をバルクに添加する酸素プラズマドープが含まれる。また、酸素ドープは、イオン注入法、イオンドーピング法、またはプラズマドープ法を用いて行ってもよい。40

#### 【0246】

例えば、酸化物半導体層 716 に接する絶縁膜として酸化ガリウムを用いた場合、酸素雰囲気下による熱処理や、酸素ドープを行うことにより、酸化ガリウムの組成を  $\text{Ga}_2\text{O}_x$  ( $X = 3 + , 0 < X < 1$ ) とすることができます。

#### 【0247】

10

20

30

40

50

また、酸化物半導体層 716 に接する絶縁膜として酸化アルミニウムを用いた場合、酸素雰囲気下による熱処理や、酸素ドープを行うことにより、酸化アルミニウムの組成を  $\text{Al}_2\text{O}_x$  ( $X = 3 + , 0 < X < 1$ ) とすることができる。

#### 【0248】

また、酸化物半導体層 716 に接する絶縁膜として酸化ガリウムアルミニウム（酸化アルミニウムガリウム）を用いた場合、酸素雰囲気下による熱処理や、酸素ドープを行うことにより、酸化ガリウムアルミニウム（酸化アルミニウムガリウム）の組成を  $\text{Ga}_x\text{Al}_{2-x}\text{O}_{3+}$  ( $0 < X < 2 , 0 < X < 1$ ) とすることができる。

#### 【0249】

酸素過剰領域を有する絶縁膜を、酸化物半導体層 716 に接するように形成し、加熱処理を行うことで、絶縁膜中の過剰な酸素が酸化物半導体層に供給され、酸化物半導体層中、又は酸化物半導体層と絶縁膜の界面における酸素欠陥を低減し、酸化物半導体層を i 型化又は i 型に限りなく近くすることができる。 10

#### 【0250】

なお、酸素過剰領域を有する絶縁膜は、酸化物半導体層 716 に接する絶縁膜のうち、上層に位置する絶縁膜又は下層に位置する絶縁膜のうち、どちらか一方のみに用いても良いが、両方の絶縁膜に用いる方が好ましい。酸素過剰領域を有する絶縁膜を、酸化物半導体層 716 に接する絶縁膜の、上層及び下層に位置する絶縁膜に用い、酸化物半導体層 716 を挟む構成とすることで、上記効果をより高めることができる。 20

#### 【0251】

また、酸化物半導体層 716 の上層又は下層に用いる絶縁膜は、上層と下層で同じ構成元素を有する絶縁膜としても良いし、異なる構成元素を有する絶縁膜としても良い。例えば、上層と下層とも、組成が  $\text{Ga}_2\text{O}_x$  ( $X = 3 + , 0 < X < 1$ ) の酸化ガリウムとしても良いし、上層と下層の一方を組成が  $\text{Ga}_2\text{O}_x$  ( $X = 3 + , 0 < X < 1$ ) の酸化ガリウムとし、他方を組成が  $\text{Al}_2\text{O}_x$  ( $X = 3 + , 0 < X < 1$ ) の酸化アルミニウムとしても良い。

#### 【0252】

また、酸化物半導体層 716 に接する絶縁膜は、酸素過剰領域を有する絶縁膜の積層としても良い。例えば、酸化物半導体層 716 の上層に組成が  $\text{Ga}_2\text{O}_x$  ( $X = 3 + , 0 < X < 1$ ) の酸化ガリウムを形成し、その上に組成が  $\text{Ga}_x\text{Al}_{2-x}\text{O}_{3+}$  ( $0 < X < 2 , 0 < X < 1$ ) の酸化ガリウムアルミニウム（酸化アルミニウムガリウム）を形成してもよい。 30

#### 【0253】

次に、図 14 (C) に示すように、ゲート絶縁膜 721、及びゲート電極 722 を覆うように、絶縁膜 724 を形成する。絶縁膜 724 は、PVD 法や CVD 法などを用いて形成することができる。また、酸化珪素、酸化窒化珪素、窒化珪素、酸化ハフニウム、酸化ガリウム、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。なお、絶縁膜 724 には、誘電率の低い材料や、誘電率の低い構造（多孔性の構造など）を用いることが望ましい。絶縁膜 724 の誘電率を低くすることにより、配線や電極などの間に生じる寄生容量を低減し、動作の高速化を図ることができるためである。なお、本実施の形態では、絶縁膜 724 を単層構造としているが、本発明の一態様はこれに限定されず、2 層以上の積層構造としても良い。 40

#### 【0254】

次に、ゲート絶縁膜 721、絶縁膜 724 に開口部 725 を形成し、導電膜 720 の一部を露出させる。その後、絶縁膜 724 上に、上記開口部 725 において導電膜 720 と接する配線 726 を形成する。

#### 【0255】

配線 726 は、PVD 法や、CVD 法を用いて導電膜を形成した後、当該導電膜をエッチング加工することによって形成される。また、導電膜の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素や、上述した

元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、又はこれらを複数組み合わせた材料を用いてもよい。

#### 【0256】

より具体的には、例えば、絶縁膜724の開口を含む領域にPVD法によりチタン膜を薄く(5nm程度)形成した後に、開口部725に埋め込むようにアルミニウム膜を形成する方法を用いることができる。ここで、PVD法により形成されるチタン膜は、被形成面の酸化膜(自然酸化膜など)を還元し、下部電極など(ここでは導電膜720)との接触抵抗を低減させる機能を有する。また、アルミニウム膜のヒロックを防止することができる。また、チタンや窒化チタンなどによるバリア膜を形成した後に、メッキ法により銅膜を形成してもよい。10

#### 【0257】

絶縁膜724に形成する開口部725は、導電膜708と重畳する領域に形成することが望ましい。このような領域に開口部725を形成することで、コンタクト領域に起因する素子面積の増大を抑制することができる。

#### 【0258】

ここで、導電膜708を用いずに、不純物領域704と導電膜720との接続と、導電膜720と配線726との接続とを重畳させる場合について説明する。この場合、不純物領域704上に形成された絶縁膜712、絶縁膜713に開口部(下部の開口部と呼ぶ)を形成し、下部の開口部を覆うように導電膜720を形成した後、ゲート絶縁膜721及び絶縁膜724において、下部の開口部と重畳する領域に開口部(上部の開口部と呼ぶ)を形成し、配線726を形成することになる。下部の開口部と重畳する領域に上部の開口部を形成する際に、エッチングにより下部の開口部に形成された導電膜720が断線してしまうおそれがある。これを避けるために、下部の開口部と上部の開口部が重畳しないように形成することにより、素子面積が増大するという問題がおこる。20

#### 【0259】

本実施の形態に示すように、導電膜708を用いることにより、導電膜720を断線させずに上部の開口部を形成することが可能となる。これにより、下部の開口部と上部の開口部を重畳させて設けることができるため、開口部に起因する素子面積の増大を抑制することができる。つまり、半導体装置の集積度を高めることができる。30

#### 【0260】

次に、配線726を覆うように絶縁膜727を形成する。上述した一連の工程により、FF回路を作製することができる。

#### 【0261】

なお、上記作製方法では、ソース電極及びドレイン電極として機能する導電膜719及び導電膜720が、酸化物半導体層716の後に形成されている。よって、図14(B)に示すように、上記作製方法によって得られるトランジスタ731は、導電膜719及び導電膜720が、酸化物半導体層716の上に形成されている。しかし、トランジスタ731は、ソース電極及びドレイン電極として機能する導電膜が、酸化物半導体層716の下、すなわち、酸化物半導体層716と絶縁膜712及び絶縁膜713の間に設けられても良い。40

#### 【0262】

図15に、ソース電極及びドレイン電極として機能する導電膜719及び導電膜720が、酸化物半導体層716と絶縁膜712及び絶縁膜713の間に設けられている場合の、トランジスタ731の断面図を示す。図15に示すトランジスタ731は、絶縁膜713を形成した後に導電膜719及び導電膜720の形成を行い、次いで酸化物半導体層716の形成を行うことで、得ることができる。

#### 【0263】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することができる。

#### 【0264】

10

20

30

40

50

## (実施の形態 6 )

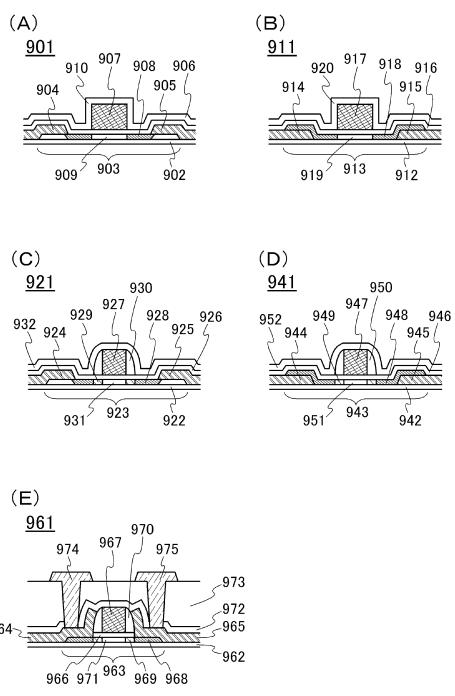

本実施の形態では、実施の形態 4 とは異なる構造を有した酸化物半導体層を用いたトランジスタについて、図 16 に示す断面図を用いて説明する。なお、図 16 ( A ) 乃至図 16 ( E ) は、トップゲート型トランジスタの構造例を示している。また、図 16 ( A ) 、図 16 ( C ) 、及び図 16 ( E ) はプレーナ型(コプレーナ型)トランジスタの構造例を示しており、図 16 ( B ) 、及び図 16 ( D ) はスタガ型トランジスタの構造例を示している。

## 【 0 2 6 5 】

図 16 ( A ) に示すトランジスタ 901 は、下地膜 902 上に形成された、活性層として機能する酸化物半導体層 903 と、酸化物半導体層 903 上に形成されたソース電極 904 及びドレイン電極 905 と、酸化物半導体層 903 、ソース電極 904 及びドレイン電極 905 上のゲート絶縁膜 906 と、ゲート絶縁膜 906 上において酸化物半導体層 903 と重なる位置に設けられたゲート電極 907 と、ゲート電極 907 上において酸化物半導体層 903 を覆う保護絶縁膜 910 とを有する。

10

## 【 0 2 6 6 】

図 16 ( A ) に示すトランジスタ 901 は、ゲート電極 907 が酸化物半導体層 903 の上に形成されているトップゲート型であり、なおかつ、ソース電極 904 及びドレイン電極 905 が酸化物半導体層 903 の上に形成されているトップコンタクト型である。そして、トランジスタ 901 は、ソース電極 904 及びドレイン電極 905 と、ゲート電極 907 とが重なっていない。すなわち、ソース電極 904 及びドレイン電極 905 とゲート電極 907との間には、ゲート絶縁膜 906 の膜厚よりも大きい間隔が設けられている。よって、トランジスタ 901 は、ソース電極 904 及びドレイン電極 905 とゲート電極 907 との間に形成される寄生容量を小さく抑えることができるので、高速動作を実現することができる。

20

## 【 0 2 6 7 】

また、酸化物半導体層 903 は、ゲート電極 907 が形成された後に酸化物半導体層 903 に n 型の導電性を付与するドーパントを添加することで得られる、一対の高濃度領域 908 を有する。また、酸化物半導体層 903 のうち、ゲート絶縁膜 906 を間に挟んでゲート電極 907 と重なる領域がチャネル形成領域 909 である。酸化物半導体層 903 では、一対の高濃度領域 908 の間にチャネル形成領域 909 が設けられている。高濃度領域 908 を形成するためのドーパントの添加は、イオン注入法を用いることができる。ドーパントは、例えばヘリウム、アルゴン、キセノンなどの希ガスや、窒素、リン、ヒ素、アンチモン、ホウ素などを用いることができる。

30

## 【 0 2 6 8 】

例えば、窒素をドーパントとして用いた場合、高濃度領域 908 中の窒素原子の濃度は、 $5 \times 10^{19} / \text{cm}^3$  以上  $1 \times 10^{22} / \text{cm}^3$  以下であることが望ましい。

## 【 0 2 6 9 】

n 型の導電性を付与するドーパントが添加されている高濃度領域 908 は、酸化物半導体層 903 中の他の領域に比べて導電性が高くなる。よって、高濃度領域 908 を酸化物半導体層 903 に設けることで、ソース電極 904 とドレイン電極 905 の間の抵抗を下げることができる。

40

## 【 0 2 7 0 】

また、In-Ga-Zn 系酸化物を酸化物半導体層 903 に用いた場合、窒素を添加した後、300 以上 600 以下で 1 時間程度加熱処理を施すことにより、高濃度領域 908 中の酸化物半導体はウルツ鉱型の結晶構造を有するようになる。高濃度領域 908 中の酸化物半導体がウルツ鉱型の結晶構造を有することで、さらに高濃度領域 908 の導電性を高め、ソース電極 904 とドレイン電極 905 の間の抵抗を下げることができる。なお、ウルツ鉱型の結晶構造を有する酸化物半導体を形成して、ソース電極 904 とドレイン電極 905 の間の抵抗を効果的に下げるためには、窒素をドーパントとして用いた場合、高濃度領域 908 中の窒素原子の濃度を、 $1 \times 10^{20} / \text{cm}^3$  以上 7 atoms % 以下

50

とすることが望ましい。しかし、窒素原子が上記範囲よりも低い濃度であっても、ウルツ鉱型の結晶構造を有する酸化物半導体が得られる場合もある。

#### 【0271】

また、酸化物半導体層903は、CAC-O<sub>S</sub>で構成されていても良い。酸化物半導体層903がCAC-O<sub>S</sub>で構成されている場合、非晶質の場合に比べて酸化物半導体層903の導電率を高めることができるので、ソース電極904とドレイン電極905との間の抵抗を下げることができる。

#### 【0272】

そして、ソース電極904とドレイン電極905との間の抵抗を下げることで、トランジスタ901の微細化を進めて、高いオン電流と、高速動作を確保することができる。また、トランジスタ901の微細化により、当該トランジスタを用いた半導体装置の占める面積を縮小化し、単位面積あたりのトランジスタ数を高めることができる。10

#### 【0273】

図16(B)に示すトランジスタ911は、下地膜912上に形成されたソース電極914及びドレイン電極915と、ソース電極914及びドレイン電極915上に形成された活性層として機能する酸化物半導体層913と、酸化物半導体層913、ソース電極914及びドレイン電極915上のゲート絶縁膜916と、ゲート絶縁膜916上において酸化物半導体層913と重なる位置に設けられたゲート電極917と、ゲート電極917上において酸化物半導体層913を覆う保護絶縁膜920とを有する。

#### 【0274】

図16(B)に示すトランジスタ911は、ゲート電極917が酸化物半導体層913の上に形成されているトップゲート型であり、なおかつ、ソース電極914及びドレイン電極915が酸化物半導体層913の下に形成されているボトムコンタクト型である。そして、トランジスタ911は、トランジスタ901と同様に、ソース電極914及びドレイン電極915と、ゲート電極917とが重なっていないので、ソース電極914及びドレイン電極915とゲート電極917との間に形成される寄生容量を小さく抑えることができ、高速動作を実現することができる。20

#### 【0275】

また、酸化物半導体層913は、ゲート電極917が形成された後に酸化物半導体層913にn型の導電性を付与するドーパントを添加することで得られる、一対の高濃度領域918を有する。また、酸化物半導体層913のうち、ゲート絶縁膜916を間に挟んでゲート電極917と重なる領域がチャネル形成領域919である。酸化物半導体層913では、一対の高濃度領域918の間にチャネル形成領域919が設けられている。30

#### 【0276】

高濃度領域918は、上述した、トランジスタ901が有する高濃度領域908の場合と同様に、イオン注入法を用いて形成することができる。そして、高濃度領域918を形成するためのドーパントの種類については、高濃度領域908の場合を参照することができる。

#### 【0277】

例えば、窒素をドーパントとして用いた場合、高濃度領域918中の窒素原子の濃度は、 $5 \times 10^{19} / \text{cm}^3$ 以上 $1 \times 10^{22} / \text{cm}^3$ 以下であることが望ましい。40

#### 【0278】

n型の導電性を付与するドーパントが添加されている高濃度領域918は、酸化物半導体層913中の他の領域に比べて導電性が高くなる。よって、高濃度領域918を酸化物半導体層913に設けることで、ソース電極914とドレイン電極915との間の抵抗を下げることができる。

#### 【0279】

また、In-Ga-Zn系酸化物を酸化物半導体層913に用いた場合、窒素を添加した後、300以上600以下程度で加熱処理を施すことにより、高濃度領域918中の酸化物半導体はウルツ鉱型の結晶構造を有するようになる。高濃度領域918中の酸化物

10

20

30

40

50

半導体がウルツ鉱型の結晶構造を有することで、さらに高濃度領域 918 の導電性を高め、ソース電極 914 とドレイン電極 915 の間の抵抗を下げることができる。なお、ウルツ鉱型の結晶構造を有する酸化物半導体を形成して、ソース電極 914 とドレイン電極 915 の間の抵抗を効果的に下げるためには、窒素をドーパントとして用いた場合、高濃度領域 918 中の窒素原子の濃度を、 $1 \times 10^{20} / \text{cm}^3$  以上 7 atoms% 以下とすることが望ましい。しかし、窒素原子が上記範囲よりも低い濃度であっても、ウルツ鉱型の結晶構造を有する酸化物半導体が得られる場合もある。

#### 【0280】

また、酸化物半導体層 913 は、CAC-O-S で構成されていても良い。酸化物半導体層 913 が CAC-O-S で構成されている場合、非晶質の場合に比べて酸化物半導体層 913 の導電率を高めることができるので、ソース電極 914 とドレイン電極 915 の間の抵抗を下げることができる。10

#### 【0281】

そして、ソース電極 914 とドレイン電極 915 の間の抵抗を下げることで、トランジスタ 911 の微細化を進めて、高いオン電流と、高速動作を確保することができる。また、トランジスタ 911 の微細化により、当該トランジスタを用いた半導体装置の占める面積を縮小化し、単位面積あたりのトランジスタ数を高めることができる。

#### 【0282】

図 16 (C) に示すトランジスタ 921 は、下地膜 922 上に形成された、活性層として機能する酸化物半導体層 923 と、酸化物半導体層 923 上に形成されたソース電極 924 及びドレイン電極 925 と、酸化物半導体層 923 、ソース電極 924 及びドレイン電極 925 上のゲート絶縁膜 926 と、ゲート絶縁膜 926 上において酸化物半導体層 923 と重なる位置に設けられたゲート電極 927 と、ゲート電極 927 上において酸化物半導体層 923 を覆う保護絶縁膜 932 とを有する。さらに、トランジスタ 921 は、ゲート電極 927 の側部に設けられた、絶縁物で形成されたサイドウォール 930 を有する。20

#### 【0283】

図 16 (C) に示すトランジスタ 921 は、ゲート電極 927 が酸化物半導体層 923 の上に形成されているトップゲート型であり、なおかつ、ソース電極 924 及びドレイン電極 925 が酸化物半導体層 923 の上に形成されているトップコンタクト型である。そして、トランジスタ 921 は、トランジスタ 901 と同様に、ソース電極 924 及びドレイン電極 925 と、ゲート電極 927 とが重なっていないので、ソース電極 924 及びドレイン電極 925 とゲート電極 927 との間に形成される寄生容量を小さく抑えることができ、高速動作を実現することができる。30

#### 【0284】

また、酸化物半導体層 923 は、ゲート電極 927 が形成された後に酸化物半導体層 923 に n 型の導電性を付与するドーパントを添加することで得られる、一対の高濃度領域 928 と、一対の低濃度領域 929 とを有する。また、酸化物半導体層 923 のうち、ゲート絶縁膜 926 を間に挟んでゲート電極 927 と重なる領域がチャネル形成領域 931 である。酸化物半導体層 923 では、一対の高濃度領域 928 の間に一対の低濃度領域 929 が設けられ、一対の低濃度領域 929 の間にチャネル形成領域 931 が設けられている。40 そして、一対の低濃度領域 929 は、酸化物半導体層 923 中の、ゲート絶縁膜 926 を間に挟んでサイドウォール 930 と重なる領域に設けられている。

#### 【0285】

高濃度領域 928 及び低濃度領域 929 は、上述した、トランジスタ 901 が有する高濃度領域 908 の場合と同様に、イオン注入法を用いて形成することができる。そして、高濃度領域 928 を形成するためのドーパントの種類については、高濃度領域 908 の場合を参照することができる。

#### 【0286】

例えば、窒素をドーパントとして用いた場合、高濃度領域 928 中の窒素原子の濃度は、 $5 \times 10^{19} / \text{cm}^3$  以上  $1 \times 10^{22} / \text{cm}^3$  以下であることが望ましい。また、例え50

ば、窒素をドーパントとして用いた場合、低濃度領域 929 中の窒素原子の濃度は、 $5 \times 10^{18} / \text{cm}^3$  以上  $5 \times 10^{19} / \text{cm}^3$  未満であることが望ましい。

#### 【0287】

n型の導電性を付与するドーパントが添加されている高濃度領域 928 は、酸化物半導体層 923 中の他の領域に比べて導電性が高くなる。よって、高濃度領域 928 を酸化物半導体層 923 に設けることで、ソース電極 924 とドレイン電極 925 の間の抵抗を下げることができる。また、低濃度領域 929 をチャネル形成領域 931 と高濃度領域 928 の間に設けることで、短チャネル効果によるしきい値電圧のマイナスシフトを軽減することができる。

#### 【0288】

また、In-Ga-Zn 系酸化物を酸化物半導体層 923 に用いた場合、窒素を添加した後、300 以上 600 以下程度で加熱処理を施すことにより、高濃度領域 928 中の酸化物半導体はウルツ鉱型の結晶構造を有するようになる。またさらに、低濃度領域 929 も、窒素の濃度によっては、上記加熱処理によりウルツ鉱型の結晶構造を有する場合もある。高濃度領域 928 中の酸化物半導体がウルツ鉱型の結晶構造を有することで、さらに高濃度領域 928 の導電性を高め、ソース電極 924 とドレイン電極 925 の間の抵抗を下げることができる。なお、ウルツ鉱型の結晶構造を有する酸化物半導体を形成して、ソース電極 924 とドレイン電極 925 の間の抵抗を効果的に下げるためには、窒素をドーパントとして用いた場合、高濃度領域 928 中の窒素原子の濃度を、 $1 \times 10^{20} / \text{cm}^3$  以上 7 atoms % 以下とすることが望ましい。しかし、窒素原子が上記範囲よりも低い濃度であっても、ウルツ鉱型の結晶構造を有する酸化物半導体が得られる場合もある。

#### 【0289】

また、酸化物半導体層 923 は、CACOS で構成されていても良い。酸化物半導体層 923 が CACOS で構成されている場合、非晶質の場合に比べて酸化物半導体層 923 の導電率を高めることができるので、ソース電極 924 とドレイン電極 925 の間の抵抗を下げることができる。

#### 【0290】

そして、ソース電極 924 とドレイン電極 925 の間の抵抗を下げることで、トランジスタ 921 の微細化を進めて、高いオン電流と、高速動作を確保することができる。また、トランジスタ 921 の微細化により、当該トランジスタを用いた半導体装置の占める面積を縮小化し、単位面積あたりのトランジスタ数を高めることができる。

#### 【0291】

図 16 (D) に示すトランジスタ 941 は、下地膜 942 上に形成されたソース電極 944 及びドレイン電極 945 と、ソース電極 944 及びドレイン電極 945 上に形成された活性層として機能する酸化物半導体層 943 と、酸化物半導体層 943、ソース電極 944 及びドレイン電極 945 上のゲート絶縁膜 946 と、ゲート絶縁膜 946 上において酸化物半導体層 943 と重なる位置に設けられたゲート電極 947 と、ゲート電極 947 上において酸化物半導体層 943 を覆う保護絶縁膜 952 を有する。さらに、トランジスタ 941 は、ゲート電極 947 の側部に設けられた、絶縁物で形成されたサイドウォール 950 を有する。

#### 【0292】

図 16 (D) に示すトランジスタ 941 は、ゲート電極 947 が酸化物半導体層 943 の上に形成されているトップゲート型であり、なおかつ、ソース電極 944 及びドレイン電極 945 が酸化物半導体層 943 の下に形成されているボトムコンタクト型である。そして、トランジスタ 941 は、トランジスタ 901 と同様に、ソース電極 944 及びドレイン電極 945 と、ゲート電極 947 とが重なっていないので、ソース電極 944 及びドレイン電極 945 とゲート電極 947 との間に形成される寄生容量を小さく抑えることができ、高速動作を実現することができる。

#### 【0293】

10

20

30

40

50

また、酸化物半導体層 9 4 3 は、ゲート電極 9 4 7 が形成された後に酸化物半導体層 9 4 3 に n 型の導電性を付与するドーパントを添加することで得られる、一対の高濃度領域 9 4 8 と、一対の低濃度領域 9 4 9 とを有する。また、酸化物半導体層 9 4 3 のうち、ゲート絶縁膜 9 4 6 を間に挟んでゲート電極 9 4 7 と重なる領域がチャネル形成領域 9 5 1 である。酸化物半導体層 9 4 3 では、一対の高濃度領域 9 4 8 の間に一対の低濃度領域 9 4 9 が設けられ、一対の低濃度領域 9 4 9 の間にチャネル形成領域 9 5 1 が設けられている。そして、一対の低濃度領域 9 4 9 は、酸化物半導体層 9 4 3 中の、ゲート絶縁膜 9 4 6 を間に挟んでサイドウォール 9 5 0 と重なる領域に設けられている。

#### 【 0 2 9 4 】

高濃度領域 9 4 8 及び低濃度領域 9 4 9 は、上述した、トランジスタ 9 0 1 が有する高濃度領域 9 0 8 の場合と同様に、イオン注入法を用いて形成することができる。そして、高濃度領域 9 4 8 を形成するためのドーパントの種類については、高濃度領域 9 0 8 の場合を参照することができる。10

#### 【 0 2 9 5 】

例えば、窒素をドーパントとして用いた場合、高濃度領域 9 4 8 中の窒素原子の濃度は、 $5 \times 10^{19} / \text{cm}^3$  以上  $1 \times 10^{22} / \text{cm}^3$  以下であることが望ましい。また、例えば、窒素をドーパントとして用いた場合、低濃度領域 9 4 9 中の窒素原子の濃度は、 $5 \times 10^{18} / \text{cm}^3$  以上  $5 \times 10^{19} / \text{cm}^3$  未満であることが望ましい。

#### 【 0 2 9 6 】

n 型の導電性を付与するドーパントが添加されている高濃度領域 9 4 8 は、酸化物半導体層 9 4 3 中の他の領域に比べて導電性が高くなる。よって、高濃度領域 9 4 8 を酸化物半導体層 9 4 3 に設けることで、ソース電極 9 4 4 とドレイン電極 9 4 5 の間の抵抗を下げることができる。また、低濃度領域 9 4 9 をチャネル形成領域 9 5 1 と高濃度領域 9 4 8 の間に設けることで、短チャネル効果によるしきい値電圧のマイナスシフトを軽減することができる。20

#### 【 0 2 9 7 】

また、In - Ga - Zn 系酸化物を酸化物半導体層 9 4 3 に用いた場合、窒素を添加した後、300 以上 600 以下程度で加熱処理を施すことにより、高濃度領域 9 4 8 中の酸化物半導体はウルツ鉱型の結晶構造を有するようになる。またさらに、低濃度領域 9 4 9 も、窒素の濃度によっては、上記加熱処理によりウルツ鉱型の結晶構造を有する場合もある。高濃度領域 9 4 8 中の酸化物半導体がウルツ鉱型の結晶構造を有することで、さらに高濃度領域 9 4 8 の導電性を高め、ソース電極 9 4 4 とドレイン電極 9 4 5 の間の抵抗を下げることができる。なお、ウルツ鉱型の結晶構造を有する酸化物半導体を形成して、ソース電極 9 4 4 とドレイン電極 9 4 5 の間の抵抗を効果的に下げるためには、窒素をドーパントとして用いた場合、高濃度領域 9 4 8 中の窒素原子の濃度を、 $1 \times 10^{20} / \text{cm}^3$  以上 7 atoms % 以下とすることが望ましい。しかし、窒素原子が上記範囲よりも低い濃度であっても、ウルツ鉱型の結晶構造を有する酸化物半導体が得られる場合もある。30

#### 【 0 2 9 8 】

また、酸化物半導体層 9 4 3 は、CAC - OS で構成されていても良い。酸化物半導体層 9 4 3 が CAC - OS で構成されている場合、非晶質の場合に比べて酸化物半導体層 9 4 3 の導電率を高めることができるので、ソース電極 9 4 4 とドレイン電極 9 4 5 の間の抵抗を下げることができる。40

#### 【 0 2 9 9 】

そして、ソース電極 9 4 4 とドレイン電極 9 4 5 の間の抵抗を下げることで、トランジスタ 9 4 1 の微細化を進めても、高いオン電流と、高速動作を確保することができる。また、トランジスタ 9 4 1 の微細化により、当該トランジスタを用いた半導体装置の占める面積を縮小化し、単位面積あたりのトランジスタ数を高めることができる。

#### 【 0 3 0 0 】

図 16 (E) に示すトランジスタ 9 6 1 は、下地膜 9 6 2 上に形成された、活性層として50

機能する酸化物半導体層 9 6 3 と、酸化物半導体層 9 6 3 上に形成されたソース電極 9 6 4 及びドレイン電極 9 6 5 と、ゲート絶縁膜 9 6 6 上において酸化物半導体層 9 6 3 と重なる位置に設けられたゲート電極 9 6 7 と、ゲート電極 9 6 7 の側部に設けられた、絶縁物で形成されたサイドウォール 9 7 0 と、ゲート電極 9 6 7 上において酸化物半導体層 9 6 3 を覆う保護絶縁膜 9 7 2 と、保護絶縁膜 9 7 2 上に絶縁膜 9 7 3 と、を有する。さらに、トランジスタ 9 6 1 は、保護絶縁膜 9 7 2 、及び絶縁膜 9 7 3 に設けたコンタクトホールを介してソース電極 9 6 4 に電気的に接続する電極 9 7 4 と、ドレイン電極 9 6 5 に電気的に接続する電極 9 7 5 を有する。

#### 【 0 3 0 1 】

絶縁膜 9 7 3 は、酸化シリコン、窒化酸化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル等の無機絶縁材料を含む材料を用いて形成することができる。また、ポリイミド、アクリル等の有機絶縁材料を用いて形成することも可能である。10

#### 【 0 3 0 2 】

また、絶縁膜 9 7 3 の形成後、C M P 処理やエッチング処理などにより、絶縁膜 9 7 3 の表面の段差を軽減するための平坦化処理を行うことが望ましい。絶縁膜 9 7 3 の表面の段差を軽減することで、後の工程において形成される電極や配線などの被覆性を向上させることができ、半導体装置の高集積化が容易となる。さらに、段差乗り越え部分における配線抵抗の増加や、被覆性不良による配線の断線が生じにくくなるため、半導体装置の信頼性を向上させることができる。20

#### 【 0 3 0 3 】

トランジスタ 9 6 1 は、ゲート電極 9 6 7 が酸化物半導体層 9 6 3 の上に形成されているトップゲート型であり、なおかつ、ソース電極 9 6 4 及びドレイン電極 9 6 5 が酸化物半導体層 9 6 3 の上に形成されているトップコンタクト型である。そして、トランジスタ 9 6 1 は、トランジスタ 9 0 1 と同様に、ソース電極 9 6 4 及びドレイン電極 9 6 5 と、ゲート電極 9 6 7 とが重なっていないので、ソース電極 9 6 4 及びドレイン電極 9 6 5 と、ゲート電極 9 6 7 との間に形成される寄生容量を小さく抑えることができ、高速動作を実現することができる。20

#### 【 0 3 0 4 】

また、酸化物半導体層 9 6 3 は、ゲート電極 9 6 7 が形成された後に酸化物半導体層 9 6 3 に n 型の導電性を付与するドーパントを添加することで得られる、一対の高濃度領域 9 6 8 と、一対の低濃度領域 9 6 9 とを有する。また、酸化物半導体層 9 6 3 のうち、ゲート絶縁膜 9 6 6 を間に挟んでゲート電極 9 6 7 と重なる領域がチャネル形成領域 9 7 1 である。酸化物半導体層 9 6 3 では、一対の高濃度領域 9 6 8 の間に一対の低濃度領域 9 6 9 が設けられ、一対の低濃度領域 9 6 9 の間にチャネル形成領域 9 7 1 が設けられている。そして、一対の低濃度領域 9 6 9 は、酸化物半導体層 9 6 3 中の、ゲート絶縁膜 9 6 6 を間に挟んでサイドウォール 9 7 0 と重なる領域に設けられている。30

#### 【 0 3 0 5 】

高濃度領域 9 6 8 及び低濃度領域 9 6 9 は、上述した、トランジスタ 9 0 1 が有する高濃度領域 9 0 8 の場合と同様に、イオン注入法を用いて形成することができる。そして、高濃度領域 9 6 8 を形成するためのドーパントの種類については、高濃度領域 9 0 8 の場合を参照することができる。40

#### 【 0 3 0 6 】

例えば、窒素をドーパントとして用いた場合、高濃度領域 9 6 8 中の窒素原子の濃度は、 $5 \times 10^{19} / \text{cm}^3$  以上  $1 \times 10^{22} / \text{cm}^3$  以下であることが望ましい。また、例えば、窒素をドーパントとして用いた場合、低濃度領域 9 6 9 中の窒素原子の濃度は、 $5 \times 10^{18} / \text{cm}^3$  以上  $5 \times 10^{19} / \text{cm}^3$  未満であることが望ましい。

#### 【 0 3 0 7 】

n 型の導電性を付与するドーパントが添加されている高濃度領域 9 6 8 は、酸化物半導体層 9 6 3 中の他の領域に比べて導電性が高くなる。よって、高濃度領域 9 6 8 を酸化物半導体層 9 6 3 に設けることで、ソース電極 9 6 4 とドレイン電極 9 6 5 の間の抵抗を下げ50

ることができる。また、低濃度領域 9 6 9 をチャネル形成領域 9 7 1 と高濃度領域 9 6 8 の間に設けることで、短チャネル効果によるしきい値電圧のマイナスシフトを軽減することができる。

#### 【 0 3 0 8 】

また、In - Ga - Zn 系酸化物を酸化物半導体層 9 6 3 に用いた場合、窒素を添加した後、300 以上 600 以下程度で加熱処理を施すことにより、高濃度領域 9 6 8 中の酸化物半導体はウルツ鉱型の結晶構造を有するようになる。またさらに、低濃度領域 9 6 9 も、窒素の濃度によっては、上記加熱処理によりウルツ鉱型の結晶構造を有する場合もある。高濃度領域 9 6 8 中の酸化物半導体がウルツ鉱型の結晶構造を有することで、さらに高濃度領域 9 6 8 の導電性を高め、ソース電極 9 6 4 とドレイン電極 9 6 5 の間の抵抗を下げることができる。なお、ウルツ鉱型の結晶構造を有する酸化物半導体を形成して、ソース電極 9 6 4 とドレイン電極 9 6 5 の間の抵抗を効果的に下げるためには、窒素をドーパントとして用いた場合、高濃度領域 9 6 8 中の窒素原子の濃度を、 $1 \times 10^{20} / cm^3$  以上 7 atoms % 以下とすることが望ましい。しかし、窒素原子が上記範囲よりも低い濃度であっても、ウルツ鉱型の結晶構造を有する酸化物半導体が得られる場合もある。

10

#### 【 0 3 0 9 】

また、酸化物半導体層 9 6 3 は、CAC - OS で構成されていても良い。酸化物半導体層 9 6 3 が CAC - OS で構成されている場合、非晶質の場合に比べて酸化物半導体層 9 6 3 の導電率を高めることができるので、ソース電極 9 6 4 とドレイン電極 9 6 5 の間の抵抗を下げることができる。

20

#### 【 0 3 1 0 】

そして、ソース電極 9 6 4 とドレイン電極 9 6 5 の間の抵抗を下げることで、トランジスタ 9 6 1 の微細化を進めても、高いオン電流と、高速動作を確保することができる。また、トランジスタ 9 6 1 の微細化により、当該トランジスタを用いた半導体装置の占める面積を縮小化し、単位面積あたりのトランジスタ数を高めることができる。

#### 【 0 3 1 1 】

なお、酸化物半導体を用いたトランジスタにおいて、ソース領域またはドレイン領域として機能する高濃度領域をセルフアラインプロセスにて作製する方法の一つとして、酸化物半導体層の表面を露出させて、アルゴンプラズマ処理をおこない、酸化物半導体層のプラズマにさらされた領域の抵抗率を低下させる方法が開示されている (S. Jeon et al. "180 nm Gate Length Amorphous InGaZnO Thin Film Transistor for High Density Image Sensor Applications", IEDM Tech. Dig., pp. 504 - 507, 2010.)。

30

#### 【 0 3 1 2 】

しかしながら、上記作製方法では、ゲート絶縁膜を形成した後に、ソース領域またはドレイン領域となるべき部分を露出するべく、ゲート絶縁膜を部分的に除去する必要がある。よって、ゲート絶縁膜が除去される際に、下層の酸化物半導体層も部分的にオーバーエッチングされ、ソース領域またはドレイン領域となるべき部分の膜厚が小さくなってしまう。その結果、ソース領域またはドレイン領域の抵抗が増加し、また、オーバーエッチングによるトランジスタの特性不良が起こりやすくなる。

40

#### 【 0 3 1 3 】

トランジスタの微細化を進めるには、加工精度の高いドライエッチング法を採用する必要がある。しかし、上記オーバーエッチングは、酸化物半導体層とゲート絶縁膜の選択比が十分に確保できないドライエッチング法を採用する場合に、顕著に起こりやすい。

#### 【 0 3 1 4 】

例えば、酸化物半導体層が十分な厚さであればオーバーエッチングも問題にはならないが、チャネル長を 200 nm 以下とする場合には、短チャネル効果を防止する上で、チャネル形成領域となる部分の酸化物半導体層の厚さは 20 nm 以下、好ましくは 10 nm 以下

50

であることが求められる。そのような薄い酸化物半導体層を扱う場合には、酸化物半導体層のオーバーエッチングは、上述したような、ソース領域またはドレイン領域の抵抗が増加、トランジスタの特性不良を生じさせるため、好ましくない。

**【0315】**

しかし、本発明の一態様のように、酸化物半導体層へのドーパントの添加を、酸化物半導体層を露出させず、ゲート絶縁膜を残したまま行うことで、酸化物半導体層のオーバーエッチングを防ぎ、酸化物半導体層への過剰なダメージを軽減することができる。また、加えて、酸化物半導体層とゲート絶縁膜の界面も清浄に保たれる。従って、トランジスタの特性及び信頼性を高めることができる。

**【0316】**

また、酸化物半導体層より下層に位置する下地膜や、保護絶縁膜は、アルカリ金属や、水素及び酸素に対するバリア性の高い材料を用いるのが望ましい。例えば、バリア性の高い絶縁膜として、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、又は窒化酸化アルミニウム膜などを用いることができる。下地膜及び保護絶縁膜をバリア性の高い絶縁膜の単層または積層、もしくは、バリア性の高い絶縁膜と、バリア性の低い絶縁膜の積層としてもよい。

**【0317】**

酸化物半導体層をバリア性の高い絶縁膜で覆うことにより、外部からの不純物の侵入を防ぐとともに、酸化物半導体層中からの酸素脱離を防ぐことができる。よって、トランジスタの信頼性を向上させることができる。

**【0318】**

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

**【0319】**

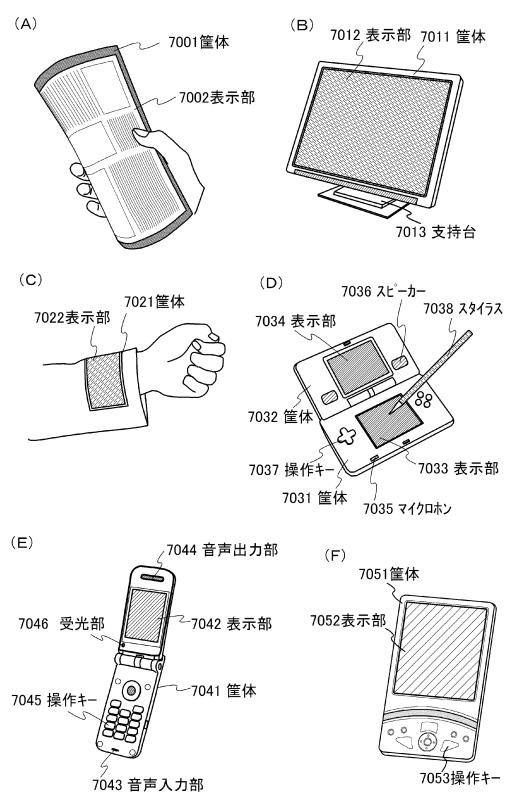

(実施の形態7)

本発明の一態様に係る分周回路を用いることで、信頼性が高い電子機器、消費電力が低減された電子機器を提供することが可能である。特に電力の供給を常時受けることが困難な携帯用の電子機器の場合、本発明の一態様に係る消費電力の低い分周回路をその構成要素に追加することにより、連続使用時間が長くなるといったメリットが得られる。

**【0320】**

本発明の一態様に係る分周回路は、表示装置、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る分周回路を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図17に示す。

**【0321】**

図17(A)は電子書籍であり、筐体7001、表示部7002等を有する。本発明の一態様に係る分周回路は、電子書籍の駆動を制御するための集積回路に用いることができる。電子書籍の駆動を制御するための集積回路に本発明の一態様に係る分周回路を用いることで、消費電力が低減された電子書籍を提供することができる。また、可撓性を有する基板を用いることで、集積回路に可撓性を持たせることができるので、フレキシブルかつ軽くて使い勝手の良い電子書籍を提供することができる。

**【0322】**

図17(B)は表示装置であり、筐体7011、表示部7012、支持台7013等を有する。本発明の一態様に係る分周回路は、表示装置の駆動を制御するための集積回路に用いることができる。表示装置の駆動を制御するための集積回路に本発明の一態様に係る分周回路を用いることで、消費電力が低減された表示装置を提供することができる。なお、

10

20

30

40

50

表示装置には、パーソナルコンピュータ用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

**【0323】**

図17(C)は表示装置であり、筐体7021、表示部7022等を有する。本発明の一態様に係る分周回路は、表示装置の駆動を制御するための集積回路に用いることができる。表示装置の駆動を制御するための集積回路に本発明の一態様に係る分周回路を用いることで、消費電力が低減された表示装置を提供することができる。また、可撓性を有する基板を用いることで、集積回路に可撓性を持たせることができるので、フレキシブルかつ軽くて使い勝手の良い表示装置を提供することができる。よって、図17(C)に示すように、布地などに固定させて表示装置を使用することができ、表示装置の応用の幅が格段に広がる。

10

**【0324】**

図17(D)は携帯型ゲーム機であり、筐体7031、筐体7032、表示部7033、表示部7034、マイクロホン7035、スピーカー7036、操作キー7037、スタイルス7038等を有する。本発明の一態様に係る分周回路は、携帯型ゲーム機の駆動を制御するための集積回路に用いることができる。携帯型ゲーム機の駆動を制御するための集積回路に本発明の一態様に係る分周回路を用いることで、消費電力が低減された携帯型ゲーム機を提供することができる。なお、図17(D)に示した携帯型ゲーム機は、2つの表示部7033と表示部7034とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

20

**【0325】**

図17(E)は携帯電話であり、筐体7041、表示部7042、音声入力部7043、音声出力部7044、操作キー7045、受光部7046等を有する。受光部7046において受信した光を電気信号に変換することで、外部の画像を取り込むことができる。本発明の一態様に係る分周回路は、携帯電話の駆動を制御するための集積回路に用いることができる。携帯電話の駆動を制御するための集積回路に本発明の一態様に係る分周回路を用いることで、消費電力が低減された携帯電話を提供することができる。

**【0326】**

図17(F)は携帯情報端末であり、筐体7051、表示部7052、操作キー7053等を有する。図17(F)に示す携帯情報端末は、モデムが筐体7051に内蔵されているても良い。本発明の一態様に係る分周回路は、携帯情報端末の駆動を制御するための集積回路に用いることができる。携帯情報端末の駆動を制御するための集積回路に本発明の一態様に係る分周回路を用いることで、消費電力が低減された携帯情報端末を提供することができる。

30

**【0327】**

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

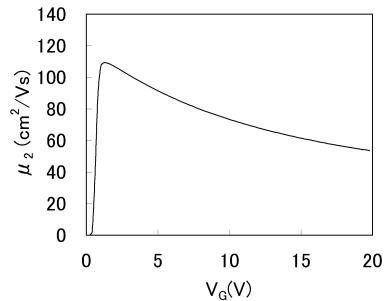

**【実施例1】**

**【0328】**

本実施例では、チャネルが形成される半導体層に、半導体内部の欠陥が無い理想的な酸化物半導体を用いたトランジスタの電界効果移動度について説明する。

40

**【0329】**

酸化物半導体に限らず、実際に測定される絶縁ゲート型トランジスタの電界効果移動度は、さまざまな理由によって本来の移動度よりも低くなる。移動度を低下させる要因としては半導体内部の欠陥や半導体と絶縁膜との界面の欠陥があるが、Levinsonモデルを用いると、半導体内部に欠陥がないと仮定した場合の電界効果移動度を理論的に導き出せる。

**【0330】**

半導体本来の移動度(Hall移動度)を $\mu_0$ 、測定される電界効果移動度を $\mu$ とし、半導体中に何らかのポテンシャル障壁(粒界等)が存在すると仮定すると、以下の式で表現できる。

50

【0331】

【数1】

$$\mu = \mu_0 \exp\left(-\frac{E}{kT}\right)$$

【0332】

ここで、Eはポテンシャル障壁の高さであり、kがボルツマン定数、Tは絶対温度である。また、ポテンシャル障壁が欠陥に由来すると仮定すると、Levinsonモデルでは、以下の式で表される。

10

【0333】

【数2】

$$E = \frac{e^2 N^2}{8\epsilon n} = \frac{e^3 N^2 t}{8\epsilon C_{ox} V_g}$$

【0334】

ここで、eは電気素量、Nはチャネル内の単位面積当たりの平均欠陥密度、 $\epsilon$ は半導体の誘電率、nは単位面積当たりのチャネルに含まれるキャリア数、 $C_{ox}$ は単位面積当たりの容量、 $V_g$ はゲート電圧、tはチャネルの厚さである。なお、厚さ30nm以下の半導体層であれば、チャネルの厚さは半導体層の厚さと同一として差し支えない。

20

線形領域におけるドレイン電流  $I_d$  は、以下の式となる。

【0335】

【数3】

$$I_d = \frac{W \mu V_g V_d C_{ox}}{L} \exp\left(-\frac{E}{kT}\right)$$

【0336】

ここで、Lはチャネル長、Wはチャネル幅であり、ここでは、L = W = 10 μmである。また、 $V_d$ はドレイン電圧である。

30

上式の両辺を  $V_g$  で割り、更に両辺の対数を取ると、以下のようになる。

【0337】

【数4】

$$\ln\left(\frac{I_d}{V_g}\right) = \ln\left(\frac{W \mu V_d C_{ox}}{L}\right) - \frac{E}{kT} = \ln\left(\frac{W \mu V_d C_{ox}}{L}\right) - \frac{e^3 N^2 t}{8kT \epsilon C_{ox} V_g}$$

【0338】

数4の右辺は  $V_g$  の関数である。この式からわかるように、縦軸を  $\ln(I_d / V_g)$  、横軸を  $1 / V_g$  として実測値をプロットして得られるグラフの直線の傾きから欠陥密度Nが求められる。すなわち、トランジスタの  $I_d - V_g$  特性から、欠陥密度を評価できる。酸化物半導体としては、インジウム(Indium)、スズ(Silver)、亜鉛(Zinc)の比率が、In : Sn : Zn = 1 : 1 : 1 のものでは欠陥密度Nは  $1 \times 10^{12} / \text{cm}^2$  程度である。

40

【0339】

このようにして求めた欠陥密度等をもとに数1および数2より  $\mu_0 = 120 \text{ cm}^2 / \text{Vs}$  が導出される。欠陥のあるIn-Sn-Zn酸化物で測定される移動度は  $35 \text{ cm}^2 / \text{Vs}$  程度である。しかし、半導体内部および半導体と絶縁膜との界面の欠陥が無い酸化物半導体の移動度  $\mu_0$  は  $120 \text{ cm}^2 / \text{Vs}$  となると予想できる。

【0340】

ただし、半導体内部に欠陥がなくても、チャネルとゲート絶縁膜との界面での散乱によっ

50

てトランジスタの輸送特性は影響を受ける。すなわち、ゲート絶縁膜界面から  $x$  だけ離れた場所における電界効果移動度  $\mu_1$  は、以下の式で表される。

#### 【0341】

##### 【数5】

$$\frac{1}{\mu_1} = \frac{1}{\mu_0} + \frac{D}{B} \exp\left(-\frac{x}{G}\right)$$

#### 【0342】

ここで、D はゲート方向の電界、B、G は定数である。B および G は、実際の測定結果より求めることができ、上記の測定結果からは、 $B = 4.75 \times 10^7 \text{ cm/s}$ 、 $G = 10 \text{ nm}$ （界面散乱が及ぶ深さ）である。D が増加する（すなわち、ゲート電圧が高くなる）と数5の第2項が増加するため、電界効果移動度  $\mu_1$  は低下することがわかる。

#### 【0343】

半導体内部の欠陥が無い理想的な酸化物半導体をチャネルに用いたトランジスタの電界効果移動度  $\mu_2$  を計算した結果を図22に示す。なお、計算にはシノプシス社製デバイスミュレーションソフト、Sentaurus Deviceを使用し、酸化物半導体のバンドギャップ、電子親和力、比誘電率、厚さをそれぞれ、2.8電子ボルト、4.7電子ボルト、15、15nmとした。これらの値は、スパッタリング法により形成された薄膜を測定して得られたものである。

#### 【0344】

さらに、ゲート、ソース、ドレインの仕事関数をそれぞれ、5.5電子ボルト、4.6電子ボルト、4.6電子ボルトとした。また、ゲート絶縁膜の厚さは100nm、比誘電率は4.1とした。チャネル長およびチャネル幅はともに10μm、ドレイン電圧  $V_d$  は0.1Vである。

#### 【0345】

図22で示されるように、ゲート電圧1V強で移動度  $100 \text{ cm}^2/\text{Vs}$  以上のピークをつけるが、ゲート電圧がさらに高くなると、界面散乱が大きくなり、移動度が低下する。なお、界面散乱を低減するためには、半導体層表面を原子レベルで平坦にすること（Atomic Layer Flatness）が望ましい。

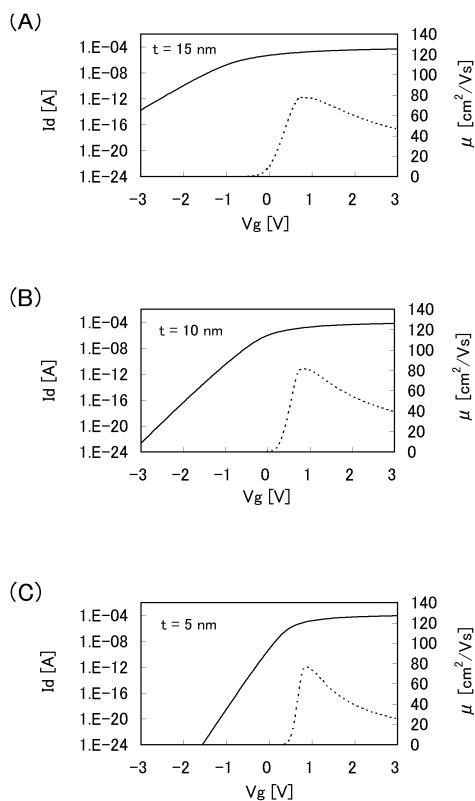

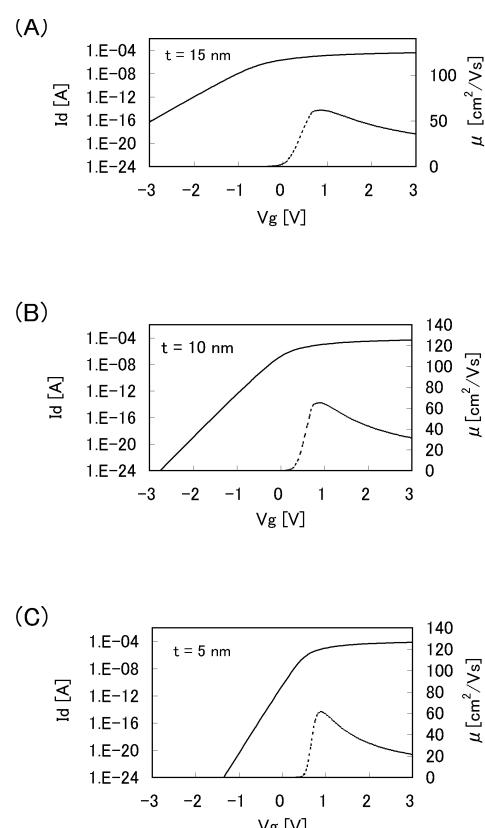

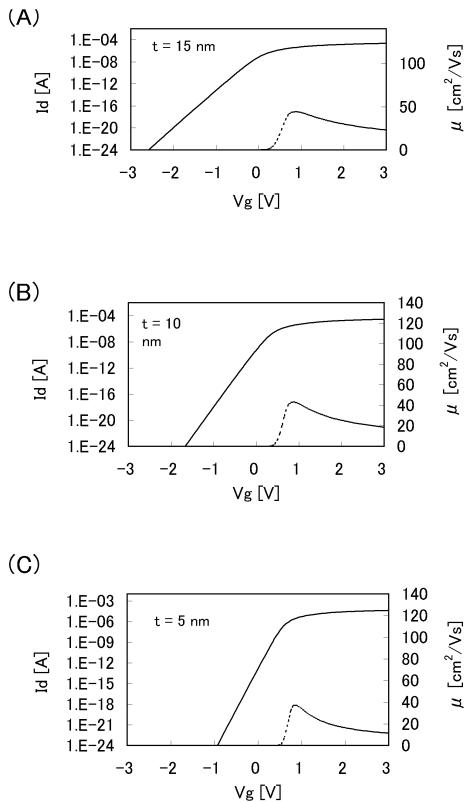

#### 【0346】

このような移動度を有する酸化物半導体を用いて微細なトランジスタを作製した場合の特性を計算した結果を図23乃至図25に示す。なお、計算に用いたトランジスタの断面構造を図26に示す。図26に示すトランジスタは酸化物半導体層に  $n^+$  の導電型を呈する半導体領域1103aおよび半導体領域1103cを有する。半導体領域1103aおよび半導体領域1103cの抵抗率は  $2 \times 10^{-3} \text{ cm}$  とする。

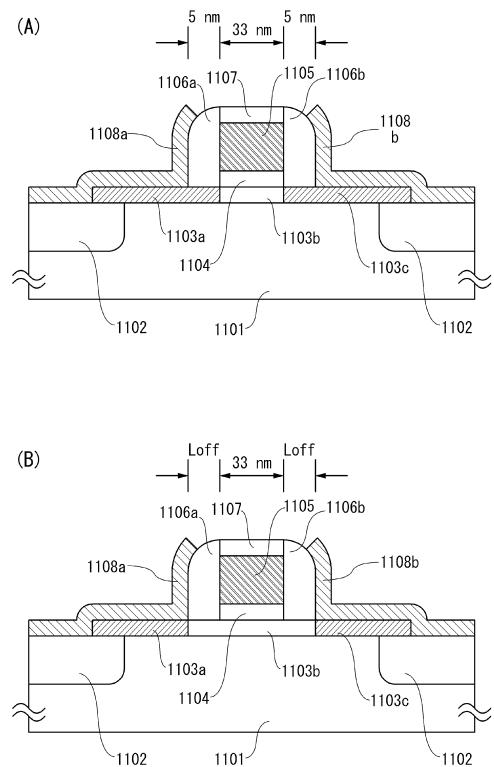

#### 【0347】

図26(A)に示すトランジスタは、下地絶縁層1101と、下地絶縁層1101に埋め込まれるように形成された酸化アルミニウムよりなる埋め込み絶縁物1102の上に形成される。トランジスタは半導体領域1103a、半導体領域1103cと、それらに挟まれ、チャネル形成領域となる真性の半導体領域1103bと、ゲート1105を有する。ゲート1105の幅を33nmとする。

#### 【0348】

ゲート1105と半導体領域1103bの間には、ゲート絶縁膜1104を有し、また、ゲート1105の両側面には側壁絶縁物1106aおよび側壁絶縁物1106b、ゲート1105の上部には、ゲート1105と他の配線との短絡を防止するための絶縁物1107を有する。側壁絶縁物の幅は5nmとする。また、半導体領域1103aおよび半導体領域1103cに接して、ソース1108aおよびドレイン1108bを有する。なお、このトランジスタにおけるチャネル幅を40nmとする。

#### 【0349】

10

20

30

40

50