(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5132169号

(P5132169)

(45) 発行日 平成25年1月30日(2013.1.30)

(24) 登録日 平成24年11月16日(2012.11.16)

(51) Int.Cl.

F 1

|                    |                  |            |      |

|--------------------|------------------|------------|------|

| <b>H01L 29/786</b> | <b>(2006.01)</b> | H01L 29/78 | 616S |

| <b>H01L 21/336</b> | <b>(2006.01)</b> | H01L 29/78 | 616V |

| <b>H01L 21/28</b>  | <b>(2006.01)</b> | H01L 29/78 | 616J |

| <b>H01L 29/417</b> | <b>(2006.01)</b> | H01L 21/28 | 301S |

|                    |                  | H01L 21/28 | L    |

請求項の数 4 (全 50 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2007-74389 (P2007-74389)    |

| (22) 出願日     | 平成19年3月22日 (2007.3.22)        |

| (65) 公開番号    | 特開2007-294913 (P2007-294913A) |

| (43) 公開日     | 平成19年11月8日 (2007.11.8)        |

| 審査請求日        | 平成22年2月3日 (2010.2.3)          |

| (31) 優先権主張番号 | 特願2006-100263 (P2006-100263)  |

| (32) 優先日     | 平成18年3月31日 (2006.3.31)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (74) 代理人  | 100082669<br>弁理士 福田 賢三                         |

| (74) 代理人  | 100095337<br>弁理士 福田 伸一                         |

| (74) 代理人  | 100095061<br>弁理士 加藤 恭介                         |

| (72) 発明者  | 丸山 穂高<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 秋元 健吾<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、下地膜を形成し、

前記下地膜上に、島状半導体膜を形成し、

前記島状半導体膜上に、ゲート絶縁膜を形成し、

前記ゲート絶縁膜上に、ゲート電極を形成し、

前記島状半導体膜の両端部の上に、一対のレジストマスクを形成し、

前記レジストマスクおよび前記ゲート電極をマスクとして、前記島状半導体膜に一導電型を付与する元素を導入することにより、前記島状半導体膜中にチャネル形成領域、前記チャネル形成領域を挟み、前記レジストマスクの下方に位置する一対の接続領域、および前記チャネル形成領域と前記接続領域との間に位置するソース領域またはドレイン領域を形成し、

前記レジストマスクを除去し、

前記ゲート電極の側面にサイドウォールを形成し、

前記島状半導体膜および前記サイドウォールを覆って、金属膜を形成し、

前記島状半導体膜および前記金属膜を加熱することにより、前記接続領域の表面近傍に第1のシリサイド領域を形成するとともに前記ソース領域またはドレイン領域の表面近傍の一部に第2のシリサイド領域を形成し、

前記島状半導体膜、前記ゲート電極および前記サイドウォールを覆う層間絶縁膜を形成し、

10

20

前記層間絶縁膜中に、前記第1のシリサイド領域に到達するコンタクトホールを形成し、

前記層間絶縁膜上に、前記コンタクトホールを介して、前記第1のシリサイド領域に電気的に接続するソース電極またはドレイン電極を形成することを特徴とする半導体装置の作製方法。

**【請求項2】**

基板上に、下地膜を形成し、

前記下地膜上に、第1の島状半導体膜および第2の島状半導体膜を形成し、

前記第1の島状半導体膜および前記第2の島状半導体膜の上に、それぞれ第1のゲート絶縁膜および第2のゲート絶縁膜を形成し、

前記第1のゲート絶縁膜および前記第2のゲート絶縁膜の上に、それぞれ第1のゲート電極および第2のゲート電極を形成し、

前記第1の島状半導体膜の両端部の上に一対の第1のレジストマスクを形成するとともに、前記第2の島状半導体膜および前記第2のゲート電極の上に第2のレジストマスクを形成し、

前記第1のレジストマスク、前記第1のゲート電極および前記第2のレジストマスクをマスクとして、前記第1の島状半導体膜にn型を付与する元素を導入することにより、前記第1の島状半導体膜中に第1のチャネル形成領域、前記第1のチャネル形成領域を挟み、前記第1のレジストマスクの下方に位置する一対の接続領域、および前記第1のチャネル形成領域と前記接続領域との間に位置する第1のソース領域またはドレイン領域を形成し、

前記第1のレジストマスクおよび前記第2のレジストマスクを除去し、

前記第1の島状半導体膜および前記第1のゲート電極の上に第3のレジストマスクを形成し、

前記第3のレジストマスクおよび前記第2のゲート電極をマスクとして、前記第2の島状半導体膜にp型を付与する元素を導入することにより、前記第2の島状半導体膜中に第2のチャネル形成領域、および前記第2のチャネル形成領域を挟む第2のソース領域またはドレイン領域を形成し、

前記第3のレジストマスクを除去し、

前記第1のゲート電極および第2のゲート電極の側面に、それぞれ第1のサイドウォールおよび第2のサイドウォールを形成し、

前記第1の島状半導体膜、前記第1のサイドウォール、前記第2の島状半導体膜、および前記第2のサイドウォールを覆って、金属膜を形成し、

前記第1の島状半導体膜、前記第2の島状半導体膜、および前記金属膜を加熱することにより、前記第1の島状半導体膜において前記接続領域の表面近傍に第1のシリサイド領域を形成するとともに前記第1のソース領域またはドレイン領域の表面近傍の一部に第2のシリサイド領域を形成し、前記第2の島状半導体膜において前記第2のソース領域またはドレイン領域の表面近傍の一部に第3のシリサイド領域を形成し、

前記第1の島状半導体膜、前記第1のゲート電極、前記第1のサイドウォール、前記第2の島状半導体膜、前記第2のゲート電極、および前記第2のサイドウォールを覆う層間絶縁膜を形成し、

前記層間絶縁膜中に、前記第1のシリサイド領域および前記第3のシリサイド領域にそれぞれ達する第1のコンタクトホールおよび第2のコンタクトホールを形成し、

前記層間絶縁膜上に、前記第1のコンタクトホールを介して前記第1のシリサイド領域に電気的に接続する第1のソース電極またはドレイン電極と、前記第2のコンタクトホールを介して前記第3のシリサイド領域に電気的に接続する第2のソース電極またはドレイン電極を形成することを特徴とする半導体装置の作製方法。

**【請求項3】**

請求項1または請求項2において、

前記一導電型を付与する元素は、n型を付与する元素であることを特徴とする半導体裝

10

20

30

40

50

置の作製方法。

【請求項 4】

請求項1乃至請求項3のいずれか1項において、

前記金属膜は、チタン（Ti）、ニッケル（Ni）、コバルト（Co）、タングステン（W）、または白金（Pt）のいずれか1つであることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の作製方法に関するものである。

10

【背景技術】

【0002】

近年、基板上に半導体装置、例えば薄膜トランジスタ（Thin Film Transistor、以下、「TFT」と記す）を製造する技術が大幅に進歩し、例えば、アクティブマトリクス型の表示装置への応用開発が進められている。特に結晶性半導体膜を用いたTFTは、従来の非晶質半導体膜を用いたTFTよりも電界効果移動度（モビリティともいう）が高いので、高速動作が可能である。

【0003】

基板上にTFTを作成する例として、下地膜、活性層、ゲート絶縁膜、ゲート電極、層間絶縁膜、ソース電極またはドレイン電極という順で形成しているものが挙げられる。このTFTの応答速度をさらに上げるためにには、デザインルールを縮小するほか、活性層のソース領域またはドレイン領域にシリサイドを形成し、ソース電極またはドレイン電極との接触抵抗を下げる手段が考えられる。

20

【0004】

このようなシリサイドを形成するためには、一般的に、チタン（Ti）、ニッケル（Ni）、コバルト（Co）、タングステン（W）、白金（Pt）等が用いられる（特許文献1参照）。

【特許文献1】特開平10-98199号公報

【発明の開示】

【発明が解決しようとする課題】

30

【0005】

TFTを作製する工程には、活性層に一導電型を付与する元素を添加し、金属膜を形成後、シリサイド形成を行い、層間絶縁膜を形成し、さらにソース電極またはドレイン電極を形成する工程が含まれる。

【0006】

ところが、ソース電極またはドレイン電極を形成する過程で、層間絶縁膜にコンタクトホールが形成し、その後シリサイドと電気的抵抗が小さくなるよう、シリサイド表面の酸化膜をフッ酸等で除去する工程が含まれる。

【0007】

このシリサイド表面の酸化膜を除去すると、フッ酸等によりシリサイドが消失する可能性があることが分かった。具体的にはn型を付与する元素を添加後、シリサイドを形成し、エッチングによりシリサイド表面の酸化膜（主に酸化珪素）除去を行うと、シリサイドがコンタクトホール底部のみ消失してしまうことが分かった。

40

【0008】

そこで本発明の課題は、コンタクトホール底部のシリサイドを消失させることなく、ソース電極またはドレイン電極とシリサイドの電気的接触を良好にすることにある。

【課題を解決するための手段】

【0009】

本発明は、層間絶縁膜中のコンタクトホールにより露出される活性層中の領域に、n型を付与する元素を添加しないことにより、シリサイドを消失させないことを特徴とする。

50

## 【0010】

本発明は、基板上に、島状半導体膜と、前記島状半導体膜中に、チャネル形成領域と、ソース領域またはドレイン領域と、前記ソース領域またはドレイン領域よりも低濃度で一導電型を付与する不純物を含んでいる接続領域と、前記ソース領域またはドレイン領域の一部の表面近傍と前記接続領域の表面近傍に形成されたシリサイド領域と、前記島状半導体膜上に、ゲート絶縁膜と、前記ゲート絶縁膜上に、ゲート電極と、前記ゲート絶縁膜と前記ゲート電極の側面に形成されたサイドウォールと、前記島状半導体膜、前記ゲート絶縁膜、前記ゲート電極及び前記サイドウォールを覆う層間絶縁膜と、前記層間絶縁膜上に形成され、前記層間絶縁膜中に形成されたコンタクトホールを介して、前記接続領域の表面近傍のシリサイド領域に電気的に接続されるソース電極またはドレイン電極とを有することを特徴とする半導体装置の作製方法に関するものである。 10

## 【0011】

また本発明は、基板上に、第1の島状半導体膜及び第2の島状半導体膜と前記第1の島状半導体膜中に、第1のチャネル形成領域と、nを付与する不純物を含む第1のソース領域またはドレイン領域と、前記第1のソース領域またはドレイン領域よりも低濃度で前記不純物を含んでいる接続領域と、前記第1のソース領域またはドレイン領域の一部の表面近傍と前記接続領域表面近傍に形成された第1のシリサイド領域と、前記第1の島状半導体膜上に、第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に、第1のゲート電極と、前記第1のゲート絶縁膜と前記第1のゲート電極の側面に形成された第1のサイドウォールと、前記第2の島状半導体膜中に、第2のチャネル形成領域と、p型を付与する不純物を含む第2のソース領域またはドレイン領域と、前記第2のソース領域またはドレイン領域の一部の表面近傍に形成された第2のシリサイド領域と、前記第2の島状半導体膜上に、第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に、第2のゲート電極と、前記第2のゲート絶縁膜と前記第2のゲート電極の側面に形成された第2のサイドウォールと、前記第1及び第2の島状半導体膜、前記第1及び第2のゲート絶縁膜、前記第1及び第2のゲート電極及び前記第1及び第2のサイドウォールを覆う層間絶縁膜と、前記層間絶縁膜上に形成され、前記層間絶縁膜中に形成されたコンタクトホールを介して、前記接続領域の表面近傍のシリサイド領域に電気的に接続される第1の電極と、前記層間絶縁膜上に形成され、前記層間絶縁膜中に形成されたコンタクトホールを介して、前記第2のソース領域またはドレイン領域の一方の一部の表面近傍に形成された第2のシリサイド領域に電気的に接続される第2の電極と、前記層間絶縁膜上に形成され、前記層間絶縁膜中に形成されたコンタクトホールを介して、前記第1の電極とは別の、前記接続領域の表面近傍の第1のシリサイド領域に電気的に接続され、かつ、前記第2のソース領域またはドレイン領域の他方の一部の表面近傍に形成された第2のシリサイド領域に電気的に接続される第3の電極とを有することを特徴とする半導体装置の作製方法に関するものである。 20 30

## 【0012】

本発明において、前記シリサイド領域は、チタン(Ti)、ニッケル(Ni)、コバルト(Co)、タンクステン(W)、または白金(Pt)のシリサイドを含むものである。

## 【0013】

また本発明は、基板上に、下地膜を形成し、前記下地膜上に、島状半導体膜を形成し、前記島状半導体膜上に、ゲート絶縁膜を形成し、前記ゲート絶縁膜上に、ゲート電極を形成し、前記島状半導体膜の一部の上に、レジストを形成し、前記レジストをマスクとして、前記島状半導体膜に一導電性を付与する元素を導入し、前記元素を導入することにより、前記島状半導体膜中に、チャネル形成領域と、ソース領域またはドレイン領域と、前記レジストが形成された前記島状半導体膜の一部に接続領域を形成し、前記ゲート絶縁膜及び前記ゲート電極の側面に、サイドウォールを形成し、前記島状半導体膜及び前記サイドウォールを覆って、金属膜を形成し、前記島状半導体膜及び前記金属膜を加熱して、前記ソース領域またはドレイン領域の一部の表面近傍及び前記接続領域の表面近傍に、シリサイド領域を形成し、前記島状半導体膜、前記ゲート絶縁膜、前記ゲート電極及び前記サイドウォールを覆う層間絶縁膜を形成し、前記層間絶縁膜中に、前記接続領域の表面近傍の 40 50

シリサイド領域に到達するコンタクトホールを形成し、前記コンタクトホールを介して、前記接続領域の表面近傍のシリサイド領域に電気的に接続するソース電極またはドレイン電極を形成することを特徴とする半導体装置の作製方法に関するものである。

#### 【0014】

本発明において、前記金属膜は、チタン(Ti)、ニッケル(Ni)、コバルト(Co)、タンゲステン(W)、または白金(Pt)のいずれか1つである。

#### 【0015】

本発明において、前記一導電型を付与する元素は、n型を付与する元素である。

#### 【0016】

なお本明細書において、半導体装置とは、半導体を利用することで機能する素子及び装置全般を指し、液晶表示装置等を含む電気光学装置およびその電気光学装置を搭載した電子機器をその範疇とする。 10

#### 【発明の効果】

#### 【0017】

本発明により、シリサイドをエッチングにより消失させることを防ぎ、ソース電極またはドレイン電極とシリサイドの電気的接触を良好にさせることができる。

#### 【0018】

また本発明により作製された半導体装置は、駆動速度が速く、かつ高い信頼性を有することができる。

#### 【発明を実施するための最良の形態】

#### 【0019】

#### [実施の形態1]

本実施の形態では、図1、図2(A)～図2(C)、図3(A)～図3(D)、図4(A)～図4(C)、図5(A)～図5(B)を用いて、本発明の半導体装置について説明する。 20

#### 【0020】

ただし本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。 30

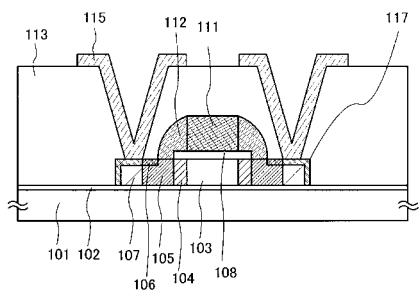

#### 【0021】

図1に本実施の形態の薄膜トランジスタの構成を示す。基板101上に下地膜102が形成され、下地膜102上には活性層である島状半導体膜117が形成されている。

#### 【0022】

島状半導体膜117中には、チャネル形成領域103、低濃度不純物領域(LDD(Lightly Doped Drain)領域ともいう)104、高濃度不純物領域であるソース領域またはドレイン領域105、そして一導電型を有する元素、本実施の形態ではn型を付与する不純物が添加されていない、接続領域107が含まれている。なお低濃度不純物領域104は、必要でないのなら設けなくてもよい。 40

#### 【0023】

ただし、必要であれば、接続領域107にも、シリサイドが消失しない程度に一導電型を有する元素が含まれていても構わない。すなわち、接続領域107は、表面にシリサイドが形成されており、かつ前記ソース領域またはドレイン領域よりも低濃度で一導電型を付与する不純物を含んでいることとなる。

#### 【0024】

島状半導体膜117上には、ゲート絶縁膜108が設けられ、さらにその上にはゲート電極111が形成されている。ゲート電極111の側部には、絶縁膜からなるサイドウォール112が形成されている。

#### 【0025】

10

20

30

40

50

島状半導体膜 117 のソース領域またはドレイン領域 105 の一部の表面近傍、及び接続領域 107 の表面近傍には、シリサイド領域 106 が形成される。シリサイド領域 106 の一方の端部は、サイドウォール 112 の端部と一致していてもよい。

#### 【0026】

図 1 の半導体装置の作製方法の例を、以下に説明する。

#### 【0027】

まず図 2 (A) に示すように、基板 101 上に下地膜 102 を成膜する。基板 101 には、例えばバリウムホウケイ酸ガラスや、アルミニノホウケイ酸ガラスなどのガラス基板、石英基板、ステンレス基板等を用いることができる。また、PET (poly(ethylene terephthalate))、PES (poly(ether sulfone))、PEN (poly(ethylene Naphthalate)) に代表されるプラスチックや、アクリル等の可撓性を有する合成樹脂からなる基板を用いることも可能である。

10

#### 【0028】

下地膜 102 は基板 101 中に含まれるNaなどのアルカリ金属やアルカリ土類金属が、半導体膜中に拡散し、半導体素子の特性に悪影響を及ぼすのを防ぐために設ける。よってアルカリ金属やアルカリ土類金属の半導体膜への拡散を抑えることができる窒化珪素、窒素を含む酸化珪素などの絶縁膜を用いて形成する。本実施の形態では、プラズマCVD 法を用いて酸化珪素膜を 10 ~ 100 nm (好ましくは 20 ~ 70 nm、さらに好ましくは 50 nm)、並びに、窒素を含む酸化珪素膜を 10 nm ~ 400 nm (好ましくは 50 nm ~ 300 nm、さらに好ましくは 100 nm) の膜厚になるように積層して成膜する。

20

#### 【0029】

なお下地膜 102 は窒化珪素、窒素を含む酸化珪素、酸素を含む窒化珪素などの絶縁膜単層であっても、酸化珪素、窒化珪素、窒素を含む酸化珪素、酸素を含む窒化珪素などの絶縁膜を複数積層したものであっても良い。またガラス基板、ステンレス基板またはプラスチック基板のように、アルカリ金属やアルカリ土類金属が多少なりとも含まれている基板を用いる場合、不純物の拡散を防ぐという観点から下地膜を設けることは有効であるが、石英基板など不純物の拡散がさして問題とならない場合は、必ずしも設ける必要はない。

30

#### 【0030】

次に下地膜 102 上に半導体膜 121 を形成する。半導体膜 121 の膜厚は 25 nm ~ 100 nm (好ましくは 30 nm ~ 80 nm) とする。なお半導体膜 121 は、非晶質半導体であっても良いし、多結晶半導体であっても良い。また半導体はシリコン (Si) だけではなくシリコンゲルマニウム (SiGe) も用いることができる。シリコンゲルマニウムを用いる場合、ゲルマニウムの濃度は 0.01 ~ 4.5 atomic % 程度であることが好ましい。本実施の形態では、半導体膜 121 として非晶質珪素膜を 66 nm の厚さで成膜する。

#### 【0031】

次に図 2 (B) に示すように、半導体膜 121 にレーザ照射装置から線状ビーム 125 を照射し、結晶化を行なう。

40

#### 【0032】

レーザ結晶化を行なう場合、レーザ結晶化の前に、レーザに対する半導体膜 121 の耐性を高めるために、500 、 1 時間の加熱処理を半導体膜 121 に加えてよい。

#### 【0033】

レーザ結晶化は、連続発振のレーザ、または擬似 CW レーザとして、発振周波数が 10 MHz 以上、好ましくは 80 MHz 以上のパルス発振レーザを用いることができる。

#### 【0034】

具体的には、連続発振のレーザとして、Ar レーザ、Kr レーザ、CO<sub>2</sub> レーザ、YAG レーザ、YVO<sub>4</sub> レーザ、フォルステライト (Mg<sub>2</sub>SiO<sub>4</sub>) レーザ、YLF レーザ

50

、 $\text{YAlO}_3$ レーザ、 $\text{GdVO}_4$ レーザ、 $\text{Y}_2\text{O}_3$ レーザ、アレキサンドライトレーザ、 $\text{Ti}:$ サファイアレーザ、ヘリウムカドミウムレーザ、多結晶(セラミック)のYAG、 $\text{Y}_2\text{O}_3$ 、 $\text{YVO}_4$ 、 $\text{YAlO}_3$ 、 $\text{GdVO}_4$ にドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザなどが挙げられる。

#### 【0035】

また擬似CWレーザとして、発振周波数が10MHz以上、好ましくは80MHz以上のパルス発振させることができるのであれば、Arレーザ、Krレーザ、エキシマレーザ、 $\text{CO}_2$ レーザ、YAGレーザ、 $\text{Y}_2\text{O}_3$ レーザ、 $\text{YVO}_4$ レーザ、フォルステライト( $\text{Mg}_2\text{SiO}_4$ )レーザ、YLFレーザ、 $\text{YAlO}_3$ レーザ、 $\text{GdVO}_4$ レーザ、アレキサンドライトレーザ、 $\text{Ti}:$ サファイアレーザ、銅蒸気レーザまたは金蒸気レーザ、多結晶(セラミック)のYAG、 $\text{Y}_2\text{O}_3$ 、 $\text{YVO}_4$ 、 $\text{YAlO}_3$ 、 $\text{GdVO}_4$ にドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザのようなパルス発振レーザを用いることができる。10

#### 【0036】

このようなパルス発振レーザは、発振周波数を増加させていくと、いずれは連続発振レーザと同等の効果を示すものである。

#### 【0037】

例えば連続発振が可能な固体レーザを用いる場合、第2高調波～第4高調波のレーザ光を照射することで、大粒径の結晶を得ることができる。代表的には、YAGレーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いるのが望ましい。例えば、連続発振のYAGレーザから射出されたレーザ光を非線形光学素子により高調波に変換して、半導体膜121に照射する。パワー密度は0.01～100MW/cm<sup>2</sup>程度(好ましくは0.1～10MW/cm<sup>2</sup>)とすれば良い。そして走査速度を10～2000cm/sec程度として照射する。20

#### 【0038】

なお、単結晶のYAG、 $\text{YVO}_4$ 、フォルステライト( $\text{Mg}_2\text{SiO}_4$ )、 $\text{YAlO}_3$ 、 $\text{GdVO}_4$ 、若しくは多結晶(セラミック)のYAG、 $\text{Y}_2\text{O}_3$ 、 $\text{YVO}_4$ 、 $\text{YAlO}_3$ 、 $\text{GdVO}_4$ に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザ、Arレーザ、Krレーザ、または $\text{Ti}:$ サファイアレーザは、連続発振をさせることができるものであり、Qスイッチ動作やモード同期などを行うことによってパルス発振をさせることも可能である。10MHz以上の発振周波数でレーザビームを発振させると、半導体膜がレーザによって溶融してから固化するまでの間に、次のパルスが半導体膜に照射される。従って、発振周波数が低いパルスレーザを用いる場合と異なり、半導体膜中において固液界面を連続的に移動させることができるために、走査方向に向かって連続的に成長した結晶粒を得ることができる。30

#### 【0039】

媒質としてセラミック(多結晶)を用いると、短時間かつ低コストで自由な形状に媒質を形成することが可能である。単結晶を用いる場合、通常、直径数mm、長さ数十mmの円柱状の媒質が用いられているが、セラミックを用いる場合はさらに大きいものを作ることが可能である。40

#### 【0040】

発光に直接寄与する媒質中のNd、Ybなどのドーパントの濃度は、単結晶中でも多結晶中でも大きくは変えられないため、濃度を増加させることによるレーザの出力向上にはある程度限界がある。しかしながら、セラミックの場合、単結晶と比較して媒質の大きさを著しく大きくすることができるために大幅な出力が向上する可能性がある。

#### 【0041】

さらに、セラミックの場合では、平行六面体形状や直方体形状の媒質を容易に形成することが可能である。このような形状の媒質を用いて、発振光を媒質の内部でジグザグに進50

行させると、発振光路を長くとることができる。そのため、増幅が大きくなり、大出力で発振させることが可能になる。また、このような形状の媒質から射出されるレーザビームは射出時の断面形状が四角形状であるため、丸状のビームと比較すると、線状ビームに整形するのに有利である。このように射出されたレーザビームを、光学系を用いて整形することによって、短辺の長さ 1 mm 以下、長辺の長さ数 mm ~ 数 m の線状ビームを容易に得ることが可能となる。また、励起光を媒質に均一に照射することにより、線状ビームは長辺方向にエネルギー分布の均一なものとなる。

#### 【0042】

この線状ビームを半導体膜に照射することによって、半導体膜の全面をより均一にアニールすることが可能になる。線状ビームの両端まで均一なアニールが必要な場合は、その両端にスリットを配置し、エネルギーの減衰部を遮光するなどの工夫が必要となる。10

#### 【0043】

上述した半導体膜 121 へのレーザ光の照射により、結晶性がより高められた結晶性半導体膜 122 が形成される。

#### 【0044】

次に、図 2 (C) に示すように結晶性半導体膜 122 を用いて島状半導体膜 117 を形成する。この島状半導体膜 117 は、以降の工程で形成される TFT の活性層となる。

#### 【0045】

次に島状半導体膜にしきい値電圧制御のための不純物を導入する。本実施の形態においてはジボラン ( $B_2H_6$ ) をドープすることによってホウ素 (B) を島状半導体膜中に導入する。20

#### 【0046】

次に島状半導体膜 117 上にゲート絶縁膜 108 を成膜する。ゲート絶縁膜 108 には、例え膜厚 10 ~ 110 nm の酸化珪素、窒化珪素または窒素を含んだ酸化珪素等を用いることができる。また成膜方法は、プラズマ CVD 法、スパッタ法などを用いることができる。本実施の形態では、プラズマ CVD 法で、膜厚 20 nm で成膜した窒素を含む酸化珪素膜を用いてゲート絶縁膜 108 を形成する。

#### 【0047】

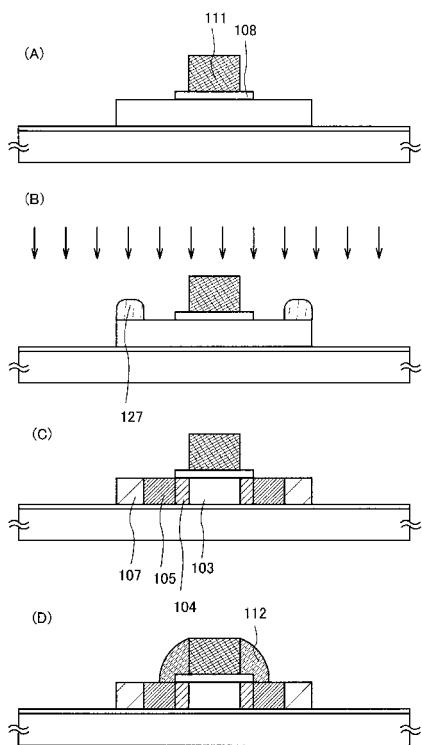

次に、ゲート絶縁膜 108 上に導電膜を成膜した後、導電膜を用いて、ゲート電極 111 を形成する (図 3 (A) 参照)。30

#### 【0048】

ゲート電極 111 は、導電膜を単層または 2 層以上積層させた構造を用いて形成する。導電膜を 2 層以上積層させている場合は、タンタル (Ta)、タングステン (W)、チタン (Ti)、モリブデン (Mo)、アルミニウム (Al) から選ばれた元素、または前記元素を主成分とする合金材料、若しくは化合物材料を積層させてゲート電極 111 を形成してもよい。また、リン (P) 等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてゲート電極を形成してもよい。本実施の形態では、タングステン膜を 400 nm 成膜したものを用いてゲート電極 111 を形成する。

#### 【0049】

ゲート電極 111 は、ゲート配線の一部として形成してもよいし、別にゲート配線を形成して、そのゲート配線にゲート電極 111 を接続してもよい。40

#### 【0050】

次に島状半導体膜 117 の、後に接続領域 107 となる領域上に、レジスト 127 を形成する。これにより接続領域 107 に一導電型を付与する元素を添加させないようする。

#### 【0051】

そして、ゲート電極 111、ゲート絶縁膜 108 及びレジスト 127 をマスクとして用い、島状半導体膜 117 に一導電性を付与する不純物を添加し、ソース領域、ドレイン領域、さらには低濃度不純物領域等を形成する。

#### 【0052】

一導電性を付与する不純物として、n 型を付与する不純物であれば、リン (P) やヒ素50

(A s) を用いればよい。また p 型を付与する不純物であれば、ホウ素 (B) を用いればよい。本実施の形態では、まず、第1の添加工程として、フォスフィン (PH<sub>3</sub>) を用いて、リン (P) を、印加電圧を 40 ~ 120 keV、ドーズ量を  $1 \times 10^{-13} \sim 1 \times 10^{-15}$  cm<sup>-2</sup> として島状半導体膜 117 中に導入する。本実施の形態では、フォスフィンを用いて、印加電圧 60 keV、ドーズ量  $2.6 \times 10^{-13}$  cm<sup>-2</sup> でリンを島状半導体膜 117 中に添加する。この不純物導入の際にチャネル形成領域 103 が形成される。

#### 【0053】

さらに第2の添加工程として、島状半導体膜 117 中に、フォスフィン (PH<sub>3</sub>) を用いて、印加電圧 10 ~ 50 keV、例えば 20 keV、ドーズ量  $5.0 \times 10^{-14} \sim 2.5 \times 10^{-16}$  cm<sup>-2</sup>、例えば  $3.0 \times 10^{-15}$  cm<sup>-2</sup> で、リン (P) を導入する。これにより低濃度不純物領域 104、及びソース領域またはドレイン領域 105 が形成される。さらに、レジスト 127 によって覆われた領域は、一導電型を付与する元素が添加されない接続領域 107 となる。さらにレジスト 127 を除去する (図 3 (C) 参照)。

#### 【0054】

低濃度不純物領域 104 とソース領域またはドレイン領域 105 の境界はゲート絶縁膜 108 の端部に一致している。すなわち低濃度不純物領域 104 の一方の端部、ソース領域またはドレイン領域 105 の一方の端部、及びゲート絶縁膜の端部は一致する。

#### 【0055】

本実施の形態においては、TFT のソース領域またはドレイン領域 105 には、 $1 \times 10^{-19} \sim 5 \times 10^{-21}$  cm<sup>-3</sup> の濃度でリン (P) が含まれることとなる。また TFT の低濃度不純物領域 104 には、 $1 \times 10^{-18} \sim 5 \times 10^{-19}$  cm<sup>-3</sup> の濃度でリン (P) が含まれる。

#### 【0056】

ただし、図 3 (B) に示すレジスト 127 を形成する前の状態で、第1の添加工程を行ってもよい。これにより、低濃度不純物領域 104 の不純物濃度が決まることとなる。次いでレジスト 127 を形成し、第2の添加工程を行ってもよい。これにより、ソース領域またはドレイン領域 105 の不純物濃度が決まることとなる。このような添加工程を行うと、接続領域 107 にも一導電性を付与する不純物元素が含まれることとなる。この場合は、接続領域 107 中の不純物濃度が、後の工程で形成されるシリサイドが消失しない程度であるように、第1の添加工程でのドーズ量及び印加電圧を制御する必要がある。

#### 【0057】

その後図 3 (D) に示すように、ゲート電極 111 及びゲート絶縁膜 108 の側面を覆うように、絶縁膜、いわゆるサイドウォール 112 を形成する。

#### 【0058】

サイドウォール 112 は、プラズマ CVD 法や減圧 CVD (LPCVD) 法を用いて、珪素を有する絶縁膜により形成することができる。本実施の形態では、プラズマ CVD 法により酸化珪素膜を膜厚 50 ~ 200 nm、好ましくは 100 nm で成膜し、次いで酸化珪素膜をエッチングすることにより、テーパー状のサイドウォール 112 を形成する。またサイドウォール 112 は窒素を含む酸化珪素膜を用いて形成してもよい。

#### 【0059】

またサイドウォール 112 の端部はテーパー形状を有さなくともよく、矩形状であってもよい。

#### 【0060】

サイドウォール 112 を形成すると、ゲート電極 111 と、ソース領域またはドレイン領域 105 との間のショートを防ぐことができる。

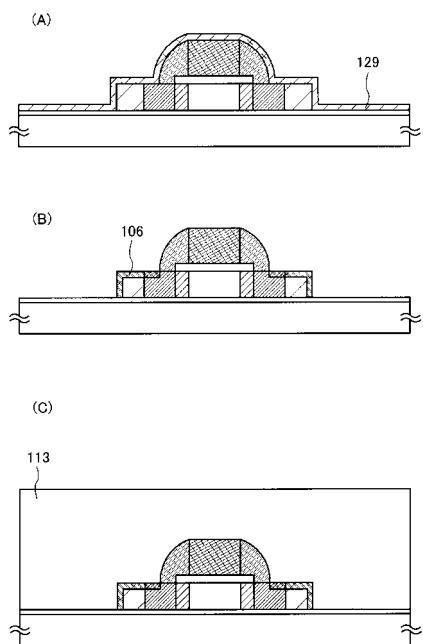

#### 【0061】

次に島状半導体膜 117、ゲート絶縁膜 108、ゲート電極 111 及びサイドウォール 112 を覆って、金属膜 129 を形成する (図 4 (A) 参照)。

#### 【0062】

金属膜 129 として、チタン (Ti)、ニッケル (Ni)、コバルト (Co)、タンゲ

10

20

30

40

50

ステン(W)、白金(Pt)等を用いることができる。本実施の形態では、金属膜129として、ニッケル膜を10nmの厚さで成膜する。

#### 【0063】

次いで、金属膜129を形成した島状半導体膜117を、ファーネスアニール炉を用いる熱アニール法、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用して加熱する。これにより島状半導体膜117中にシリサイド領域106が形成される。特に、島状半導体膜117の、サイドウォール112、ゲート電極111、ゲート絶縁膜108に覆われていない、露出した領域の表面近傍に、シリサイド領域106が形成される。本実施の形態では、ラピッドサーマルアニール法により350以上<sup>10</sup>の温度で加熱することによりシリサイド領域106を形成する。

#### 【0064】

シリサイド領域106を形成したら、未反応の金属膜129を、硫酸や硝酸等の薬液によりエッチングして除去する。

#### 【0065】

次に島状半導体膜117、ゲート絶縁膜108、ゲート電極111及びサイドウォール112を覆って、層間絶縁膜113を形成する(図4(C)参照)。

#### 【0066】

層間絶縁膜113としては、プラズマCVD法またはスパッタ法を用いて、シリコンを含む絶縁膜、例えば酸化珪素膜、窒化珪素膜、窒素を含む酸化珪素膜、またはその積層膜で形成する。もちろん、層間絶縁膜113は窒素を含む酸化珪素膜や窒化珪素膜、またはその積層膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。<sup>20</sup>

#### 【0067】

本実施例では、窒素を含む酸化珪素膜をプラズマCVD法により50nm形成し、レーザ照射方法によって不純物を活性化する。又は窒素を含む酸化珪素膜形成後、窒素雰囲気中550で4時間加熱して、不純物を活性化してもよい。

#### 【0068】

次にプラズマCVD法により窒化珪素膜を100nm形成し、更に酸化珪素膜を600nm形成する。この、窒素を含む酸化珪素膜、酸素を含む窒化珪素膜及び酸化珪素膜の積層膜が層間絶縁膜113である。<sup>30</sup>

#### 【0069】

次に全体を410で1時間加熱し、窒化珪素膜から水素を放出させることにより水素化を行う。

#### 【0070】

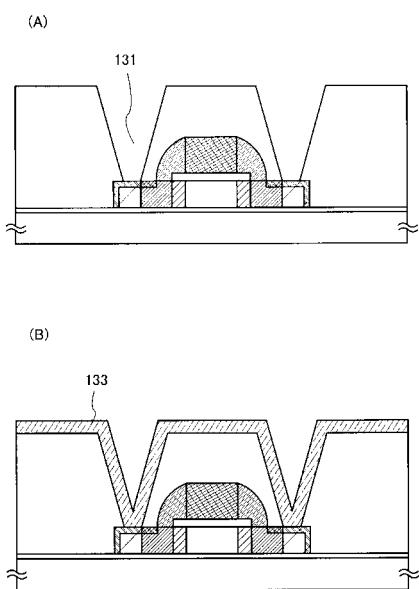

層間絶縁膜113をエッチングして、層間絶縁膜113に、島状半導体膜117に到達するコンタクトホール131を形成する。その際にコンタクトホール131は接続領域107のみに達するようにし、ソース領域またはドレイン領域105を露出させないようにエッチングを行う。すなわち、層間絶縁膜113のエッチングの際には、接続領域107のみにコンタクトホール131が形成されるように、層間絶縁膜113上にレジストを形成する。<sup>40</sup>

#### 【0071】

次いで接続領域107表面の酸化膜(主に酸化珪素を含有)を除去するために、フッ酸で接続領域107表面を洗浄、もしくは水素プラズマ雰囲気中で基板を設置し、接続領域107表面にプラズマ処理を行う。本発明では、この酸化膜除去は接続領域107に対してのみ行う。ソース領域またはドレイン領域105は層間絶縁膜113に覆われているので、ソース領域またはドレイン領域105中のシリサイド領域は除去されない。これによりソース電極またはドレイン電極115と島状半導体膜117との電気的接触を良好にすることができる。

#### 【0072】

次いで層間絶縁膜113上にコンタクトホール131を介して、導電膜133を形成し<sup>50</sup>

(図5(B)参照)、導電膜133を用いて、ソース電極またはドレイン電極115を形成する(図1参照)。ソース電極またはドレイン電極115は、接続領域107中のシリサイド領域に電気的に接続される。

#### 【0073】

本実施の形態では、導電膜133は金属膜を用いる。この金属膜は、アルミニウム(A1)、チタン(Ti)、モリブデン(Mo)、タングステン(W)もしくはシリコン(Si)の元素からなる膜又はこれらの元素を用いた合金膜を用いればよい。

#### 【0074】

本実施の形態では、チタン膜(Ti)、アルミニウム膜(A1)、チタン膜(Ti)をそれぞれ100nm、300nm、100nmに積層したものを用いて、ソース電極またはドレイン電極115を形成する。

#### 【0075】

またこのソース電極またはドレイン電極115を、ニッケル、コバルト、鉄のうち少なくとも1種の元素、及び炭素を含むアルミニウム合金膜で形成してもよい。このようなアルミニウム合金膜は、シリコンと接触してもシリコンとアルミニウムの相互拡散が防止できる。またこのようなアルミニウム合金膜は、透明導電膜、例えばITO(In di um Tin Oxide)膜と接触しても酸化還元反応が起こらないため、両者を直接接觸させることができ。さらにこのようなアルミ合金膜は、比抵抗が低く耐熱性にも優れているので、配線材料としては有用である。

#### 【0076】

またソース電極またはドレイン電極115はそれぞれ、電極と配線を同じ材料で同一工程で形成してもよいし、電極と配線を別々に形成してそれらを接続させてもよい。

#### 【0077】

上記一連の工程によって、本実施の形態の半導体装置を作製することができる。本実施の形態では、n型を付与する元素を添加する際、島状半導体膜117中の、コンタクトホール131の形成される領域はレジストでマスクされ、島状半導体膜117中の、コンタクトホール131の形成される領域には、n型を付与する元素は導入されない。これにより、n型の半導体膜を形成しながら、ソース領域またはドレイン領域105シリサイドを消失させることなく形成し、ソース電極またはドレイン電極115と接続することができる。

#### 【0078】

また、本実施の形態は、必要であれば他の実施の形態及び実施例のいかなる記載とも自由に組み合わせることが可能である。

#### 【0079】

##### [実施の形態2]

本実施の形態では、実施の形態1とは別の構成を有する半導体装置について、図6を用いて説明する。

#### 【0080】

なお本実施の形態では、実施の形態1と同じものは同じ符号で表し、特に記載のないものについては実施の形態1の記載を援用する。

#### 【0081】

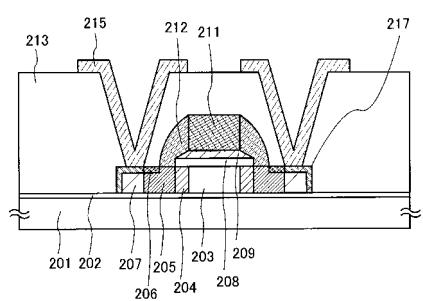

図6に示す半導体装置は、基板201上に下地膜202が形成され、下地膜202上に活性層である島状半導体膜217が形成されている。

#### 【0082】

島状半導体膜217中には、チャネル形成領域203、低濃度不純物領域204、ソース領域またはドレイン領域205、接続領域207が形成されている。さらにソース領域またはドレイン領域205の一部及び接続領域207の表面近傍には、シリサイド領域206が形成されている。

#### 【0083】

島状半導体膜217上には、ゲート絶縁膜208、下層ゲート電極209及び上層ゲー

10

20

30

40

50

ト電極 211 が形成されている。なお、基板 201、下地膜 202、島状半導体膜 217、ゲート絶縁膜 208 は、それぞれ実施の形態 1 の基板 101、下地膜 102、島状半導体膜 117、ゲート絶縁膜 108 と同様の材料、同様の工程にて作製すればよい。

#### 【0084】

また下層ゲート電極 209 及び上層ゲート電極 211 は、以下のようにして形成される。

#### 【0085】

まず実施の形態 1 の図 2 (C) の構成が得られたら、島状半導体膜 217 上に、第 1 の導電膜として、例えば窒化タンタル (TaN) 膜を 10 ~ 50 nm、例えば 30 nm の膜厚で形成する。そして第 1 の導電膜上に第 2 の導電膜として、例えばタンゲステン (W) 膜を 200 ~ 400 nm、例えば 370 nm の膜厚で形成し、第 1 の導電膜及び第 2 の導電膜の積層膜を形成する。10

#### 【0086】

次に第 2 の導電膜を異方性エッティングでエッティングし、上層ゲート電極 211 を形成する。次いで第 1 の導電膜を等方性エッティングでエッティングし、下層ゲート電極 209 を形成する。

#### 【0087】

下層ゲート電極 209 及び上層ゲート電極 211 を形成したら、実施の形態 1 で述べたように接続領域 207 となる領域上にレジストを形成し、ゲート絶縁膜 208、下層ゲート電極 209、上層ゲート電極 211 及びレジストをマスクとして、島状半導体膜 217 に一導電型を付与する元素の導入を行う。これにより、チャネル形成領域 203、低濃度不純物領域 204、ソース領域またはドレイン領域 205 が形成され、レジストで覆われた領域は一導電型を付与する元素が添加されないので、接続領域 207 となる。20

#### 【0088】

さらに、実施の形態 1 の記載を基にして、ゲート絶縁膜 208、下層ゲート電極 209 及び上層ゲート電極 211 の側面を覆うようにして、サイドウォール 212 を形成する。サイドウォール 212 は、サイドウォール 112 と同様の材料及び同様の工程で形成すればよい。

#### 【0089】

次いで、島状半導体膜 217、サイドウォール 212、上層ゲート電極 211 を覆うようにして金属膜を成膜し、加熱処理にて島状半導体膜 217 中に、シリサイド領域 206 を形成する。シリサイド領域 206 の一方の端部は、サイドウォール 212 の端部に一致していてもよい。30

#### 【0090】

さらに不要な金属膜を除去し、層間絶縁膜 213 を形成し、層間絶縁膜 213 をエッティングして、接続領域 207 に達するコンタクトホールを形成する。接続領域 207 表面をフッ酸もしくは水素プラズマで処理して、接続領域 207 表面の酸化膜を除去した後、コンタクトホールを介して接続領域 207 中のシリサイド領域に接続されるソース電極またはドレイン電極 215 を形成する。

#### 【0091】

なお、層間絶縁膜 213、ソース電極またはドレイン電極 215 は、実施の形態 1 の層間絶縁膜 113、ソース電極またはドレイン電極 115 と同様の材料、同様の工程で形成すればよい。40

#### 【0092】

また、本実施の形態は、必要であれば他の実施の形態及び実施例のいかなる記載とも自由に組み合わせることが可能である。

#### 【0093】

#### [実施の形態 3]

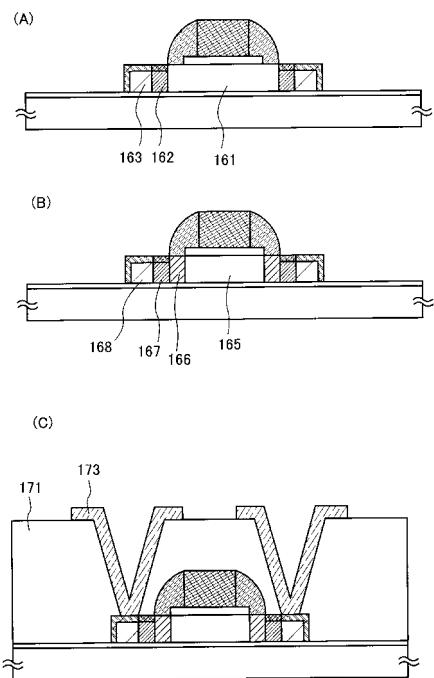

本実施の形態では、実施の形態 1 及び 2 と異なる作製工程により作製される半導体装置について、図 25 (A) ~ 図 25 (D) 及び図 26 (A) ~ 図 26 (C) を用いて説明す50

る。なお本実施の形態では、実施の形態 1 及び 2 と同じものは同じ符号で表し、特に記載のないものについては実施の形態 1 の記載を援用する。

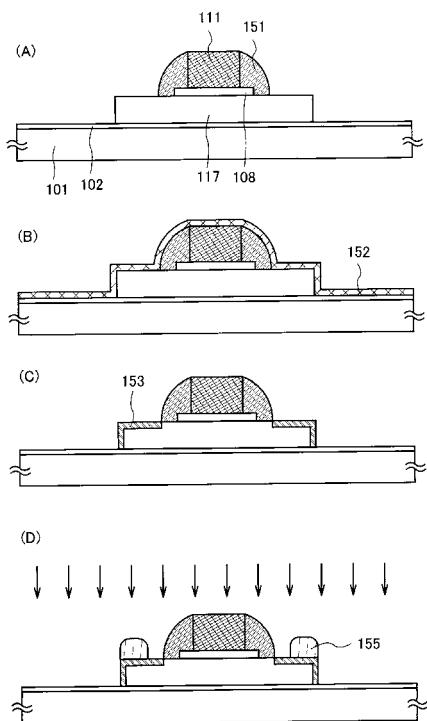

#### 【0094】

薄膜トランジスタを作製する過程において、ソース領域またはドレイン領域に一導電性を付与する元素を添加後、シリサイド領域を形成しようとすると、一導電性を付与する元素がシリサイド領域形成時に再拡散するということが分かっている。これを避けるために、ソース領域またはドレイン領域にシリサイドを形成した後で、一導電性を付与する元素を添加する工程も可能である。その作製方法を以下に説明する。

#### 【0095】

まず実施の形態 1 の記載に基づいて、図 3 (A) までのゲート絶縁膜 108 及びゲート電極 111 までの作製を行う。次いでゲート絶縁膜 108 及びゲート電極 111 の側面に、サイドウォール 151 を形成する(図 25 (A) 参照)。サイドウォール 151 は、実施の形態 1 のサイドウォール 112 と同様に形成すればよい。

10

#### 【0096】

次に、島状半導体膜 117、ゲート絶縁膜 108、ゲート電極 111、サイドウォール 151 を覆って、金属膜 152 を形成する(図 25 (B) 参照)。金属膜 152 は、実施の形態 1 の金属膜 129 と同様の材料、同様の工程で形成すればよい。

#### 【0097】

金属膜 152 を形成後、島状半導体膜 117 及び金属膜 152 を加熱することにより、島状半導体膜 117 中にシリサイド領域 153 を形成する。シリサイド領域 153 の端部は、サイドウォール 151 の端部と一致していてもよい。次いで未反応の金属膜 152 を除去する(図 25 (C) 参照)。

20

#### 【0098】

島状半導体膜 117 の一部の領域上に、レジスト 155 を形成し、レジスト 155、ゲート電極 111 及びサイドウォール 151 をマスクとして、一導電型を付与する元素を島状半導体膜 117 に添加する(図 25 (D) 参照)。本実施例では、一導電性を付与する元素として、n 型を付与する元素でありリン (P) を島状半導体膜 117 に添加する。その後レジスト 155 を除去する。

#### 【0099】

一導電性を付与する元素の導入により、元素がサイドウォール 151 を貫通しない印加電圧で添加された場合は、図 26 (A) で示すように、チャネル形成領域 161、ソース領域またはドレイン領域 162 が形成される。またレジスト 155 が形成された領域の島状半導体膜 117 には、接続領域 163 が形成される。

30

#### 【0100】

また元素がサイドウォール 151 を貫通する程度の印加電圧で添加された場合は、図 26 (B) で示すように、チャネル形成領域 165、低濃度不純物領域 166、ソース領域またはドレイン領域 167 が形成される。またレジスト 155 が形成された領域の島状半導体膜 117 には、接続領域 168 が形成される。

#### 【0101】

図 26 (A) において、シリサイド領域 153 は、ソース領域またはドレイン領域 162 及び接続領域 163 中に形成されている。またシリサイド領域 153 の端部は、ソース領域またはドレイン領域 162 の一方の端部と一致しており、サイドウォール 151 の端部とも一致していてもよい。

40

#### 【0102】

図 26 (B) において、シリサイド領域 153 は、ソース領域またはドレイン領域 167 及び接続領域 168 中に形成されている。またシリサイド領域 153 の端部は、ソース領域またはドレイン領域 167 の一方の端部と一致しており、サイドウォール 151 の端部とも一致していてもよい。

#### 【0103】

ただし、接続領域 168 にも、シリサイドが消失しない程度に一導電性を付与する元素

50

が含まれていてもよい。例えば、レジスト 155 を形成する前に、低濃度不純物領域 166 の不純物濃度を決定する、一導電性を付与する元素の添加工程を行ってもよい。ただしその場合は、シリサイドが消失しない程度の濃度になるように、印加電圧を制御する必要がある。

#### 【0104】

次いで島状半導体膜 117、ゲート絶縁膜 108、ゲート電極 111、サイドウォール 151 を覆って、層間絶縁膜 171 を形成する。実施の形態 1 の記載の基づいて、層間絶縁膜 171 にコンタクトホールを形成する。コンタクトホールは、接続領域 163 のみに到達するように形成し、ソース領域またはドレイン領域 162 には到達しないように形成される。

10

#### 【0105】

コンタクトホールにより露出した接続領域 163 の表面を、フッ酸等で処理して、接続領域 163 中のシリサイド領域上の酸化膜（主に酸化珪素）を除去する。次いで導電膜を形成し、エッチングして、ソース電極またはドレイン電極 173 を形成する（図 26（C）参照）。

#### 【0106】

なお図 26（C）には、図 26（A）に層間絶縁膜 171 及びソース電極またはドレイン電極 173 を形成した構成を示しているが、図 26（B）の構成に上述の作製工程により層間絶縁膜及びソース電極またはドレイン電極を形成することができるのは言うまでもない。

20

#### 【0107】

本実施の形態においても、ソース電極またはドレイン電極 173 が島状半導体膜 117 と電気的に接続するのは、接続領域 163 及び 168 においてのみである。層間絶縁膜 171 中の、ソース電極またはドレイン電極 173 が島状半導体膜 117 と電気的に接続するためのコンタクトホールに達するのも、接続領域 163 及び 168 のみである。このためシリサイド領域 153 は除去されず、良好な電気的接触を得ることが可能となる。

#### 【実施例 1】

#### 【0108】

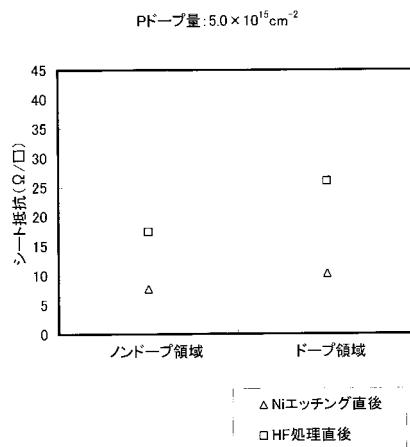

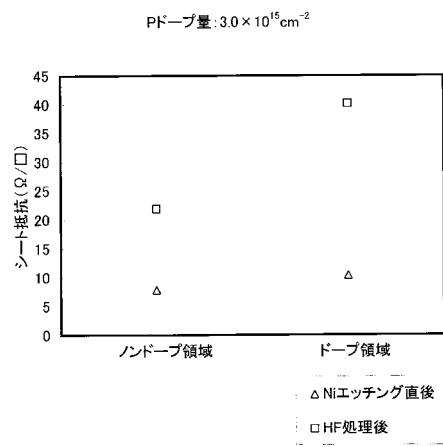

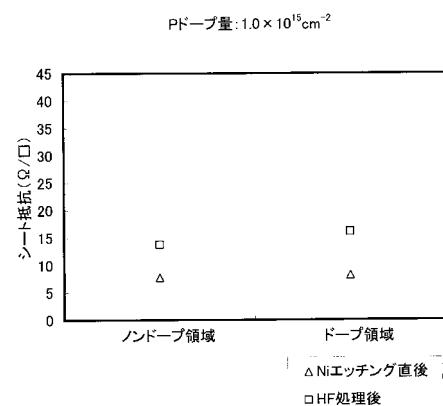

本実施例では、一導電型を付与する元素としてリンを用い、リンを添加したニッケルシリサイドとリンを添加しないニッケルシリサイドで、シート抵抗を測定し、その比較を行った。本実施例を図 22～図 24 を用いて以下に説明する。

30

#### 【0109】

まず、測定に用いた基板について説明する。基板上に成膜した珪素膜に、ニッケルシリサイドを形成し、珪素膜上有る領域にマスクを設け、その後リン（P）を添加した。

#### 【0110】

本実施例では、マスクを設けた領域には、マスクを設けなかった領域に比べてリンは含まれないものとみなし、この領域を接続領域（あるいはノンドープ領域ともいう）とする。一方、マスクを設けなかった領域は、リンが含有されている。本実施例では、リンが含有されている領域をドープ領域と呼ぶ。ただし、接続領域においても、後の工程でシリサイドが消失しない程度の濃度であれば、リンを含有していても構わない。

40

#### 【0111】

図 22～図 24 において、リンを添加後、未反応のニッケルをエッチングにより除去し、ニッケル除去直後に第 1 の測定を行った。さらにフッ酸（HF）でシリサイドを処理して、シリサイド表面の酸化膜（主に酸化珪素）除去を行い、第 2 の測定を行った。

#### 【0112】

また図 22～図 24 で、ドープ領域のリンのドープ量を変化させた。図 22 では、リンのドープ量は、 $5 \times 10^{15} \text{ cm}^{-2}$  であり、図 23 では  $3 \times 10^{15} \text{ cm}^{-2}$  であり、図 24 では  $1 \times 10^{15} \text{ cm}^{-2}$  である。

#### 【0113】

図 22～図 24 のいずれにおいても、接続領域の方がドープ領域よりもシート抵抗が低

50

いことが分かる。またフッ酸でシリサイドを処理した接続領域とドープ領域を比較すると、ドープ領域ではシート抵抗が高く、接続領域ではシート抵抗がはるかに低いことが分かる。つまり本測定により、ドープ領域中のシリサイドがフッ酸処理により消失してしまい、シート抵抗が高くなる、すなわち、導電性が悪くなることが裏付けられた。逆に接続領域では、シリサイドがフッ酸処理により消失しないので、シート抵抗が低い、すなわち導電性がよい。従って電極や配線との電気的接続を行うには、接続領域中のシリサイド領域を用いるとよいことが分かる。

#### 【実施例 2】

##### 【0114】

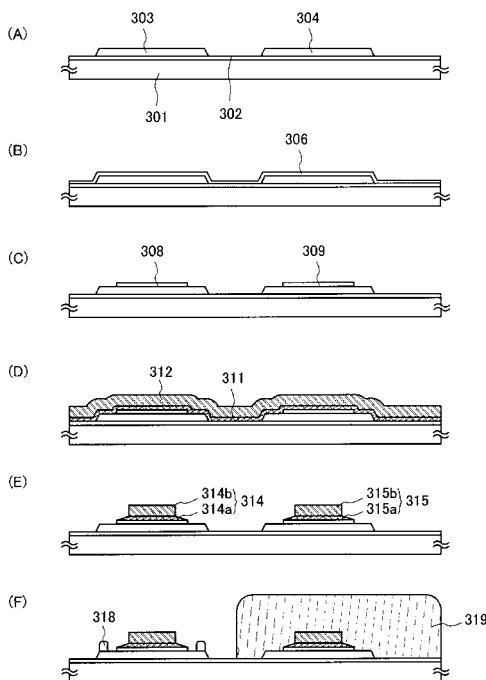

本実施例を図7(A)～図7(F)、図8(A)～図8(E)及び図9(A)～図9(D)を用いて説明する。10

##### 【0115】

まず実施の形態1の記載に基づいて、図2(C)の島状半導体膜までの作製工程を行う。本実施例では、基板301上に、下地膜302を形成し、さらに島状半導体膜303及び304を形成する(図7(A)参照)。

##### 【0116】

なお、基板301、下地膜302並びに島状半導体膜303及び304は、それぞれ実施の形態1の基板101、下地膜102及び島状半導体膜117と同様の材料、同様の工程で形成すればよい。

##### 【0117】

次に島状半導体膜にしきい値電圧制御のための不純物を導入する。本実施例においてはジボラン( $B_2H_6$ )をドープすることによってボロン(B)を島状半導体膜303及び304中に導入する。20

##### 【0118】

次に島状半導体膜303及び304を覆うように絶縁膜306を成膜する(図7(B)参照)。絶縁膜306には、例えば酸化珪素、窒化珪素または窒素を含んだ酸化珪素等を用いることができる。また成膜方法は、プラズマCVD法、スパッタ法などを用いることができる。

##### 【0119】

次に、絶縁膜306を用いて、島状半導体膜303上にゲート絶縁膜308、島状半導体膜304上にゲート絶縁膜309を形成する(図7(C)参照)。30

##### 【0120】

島状半導体膜303及び304、並びにゲート絶縁膜308及び309を覆って、第1の導電膜311及び第2の導電膜312を形成する(図7(D)参照)。

##### 【0121】

第1の導電膜311及び第2の312は、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)から選ばれた元素、または前記元素を主成分とする合金材料、若しくは化合物材料を積層させる。

##### 【0122】

本実施例では、第1の導電膜311として、例えば窒化タンタル(TaN)膜を10～50nm、例えば30nmの膜厚で形成する。そして第1の導電膜312上に第2の導電膜312として、例えばタンゲステン(W)膜を200～400nm、例えば370nmの膜厚で形成し、第1の導電膜311及び第2の導電膜312の積層膜を形成する。40

##### 【0123】

次に第2の導電膜312を異方性エッチングでエッチングし、上層ゲート電極314b及び315bを形成する。次いで第1の導電膜311を等方性エッチングでエッチングし、下層ゲート電極314a及び315aを形成する。以上よりゲート電極314及び315を形成する(図7(E)参照)。

##### 【0124】

ゲート電極314及び315は、ゲート配線の一部として形成してもよいし、別にゲー50

ト配線を形成して、そのゲート配線にゲート電極314及び315を接続してもよい。

#### 【0125】

次いで、島状半導体膜303の、後の工程で接続領域となる領域上に、レジスト318を形成する。また島状半導体膜304、ゲート絶縁膜309及びゲート電極315上に、レジスト319を形成する。

#### 【0126】

そして、ゲート電極314及び315、レジスト318及び319をマスクとして用い、島状半導体膜303に一導電性(*n*型または*p*型の導電性)を付与する不純物を添加し、ソース領域、ドレイン領域、チャネル形成領域、さらには低濃度不純物領域等を形成する(図8(A)参照)。10

#### 【0127】

まず、*n*型を付与する元素としてリンを用い、フォスフィン( $\text{PH}_3$ )を用いて、リン(*P*)を、印加電圧を40~100keV、例えば60keV、ドーズ量を $1 \times 10^{13}$ ~ $1 \times 10^{15} \text{ cm}^{-2}$ 、例えば $2.6 \times 10^{13} \text{ cm}^{-2}$ として島状半導体膜中に導入する。この不純物導入の際に*n*チャネル型TFT356のチャネル形成領域321が形成される。

#### 【0128】

次いで島状半導体膜303中に、フォスフィン( $\text{PH}_3$ )を用いて、印加電圧10~60keV、例えば20keV、ドーズ量 $5.0 \times 10^{14}$ ~ $2.5 \times 10^{16} \text{ cm}^{-2}$ 、例えば $3.0 \times 10^{15} \text{ cm}^{-2}$ で、リン(*P*)を導入する。これにより*n*チャネル型TFTの低濃度不純物領域322、ソース領域またはドレイン領域323が形成される。また島状半導体膜303中の、レジスト318によってマスクされたために、*n*型を付与する元素が導入されない領域を、接続領域324とする。20

#### 【0129】

本実施例においては、*n*チャネル型TFT356のソース領域またはドレイン領域323には、 $1 \times 10^{19}$ ~ $5 \times 10^{21} \text{ cm}^{-3}$ の濃度でリン(*P*)が含まれることとなる。また*n*チャネル型TFT356の低濃度不純物領域322には、 $1 \times 10^{18}$ ~ $5 \times 10^{19} \text{ cm}^{-3}$ の濃度でリン(*P*)が含まれる。

#### 【0130】

ただし、接続領域324にもシリサイドが消失しない程度の濃度でリンが含まれているも構わない。その場合は、実施の形態1で述べたように、低濃度不純物領域322の不純物濃度を決定するリンの添加工程を行い、島状半導体膜303の、接続領域324となる領域を覆うレジスト318を形成し、ソース領域またはドレイン領域323の不純物濃度を決定するリンの添加工程を行えばよい。30

#### 【0131】

次いでレジスト319を除去し、島状半導体膜303、ゲート絶縁膜308及びゲート電極314を覆って、レジスト327を形成する。

#### 【0132】

*p*チャネル型TFT357を作製するために、ジボラン( $\text{B}_2\text{H}_6$ )を用いて印加電圧60~100keV、例えば80keV、ドーズ量 $1 \times 10^{13}$ ~ $5 \times 10^{15} \text{ cm}^{-2}$ 、例えば $3 \times 10^{15} \text{ cm}^{-2}$ の条件で、島状半導体膜304中にホウ素(*B*)を導入する。これにより*p*チャネル型TFTのソース領域またはドレイン領域329、またこの不純物導入の際にチャネル形成領域328が形成される(図8(B)参照)。40

#### 【0133】

なお*p*チャネル型TFT357について、ホウ素の導入に際しては、印加電圧が高いために、下層ゲート電極315a及びゲート絶縁膜309を通して、ソース領域またはドレイン領域329を形成するために十分なホウ素が島状半導体膜304中に添加される。

#### 【0134】

また*p*チャネルTFTでは、後の工程でシリサイド表面の酸化膜をフッ酸等で除去しても、シリサイドが消失しにくいことが分かっている。そのため*p*チャネル型TFT35750

では、接続領域を形成しなくても構わない。しかしもちろん p チャネル型 TFT に接続領域を形成し、ソース電極またはドレイン電極の一部及び接続領域中にシリサイド領域を形成し、接続領域のみにソース電極またはドレイン電極を電気的に接続させても構わない。

#### 【 0 1 3 5 】

p チャネル型 TFT 3 5 7 のソース領域またはドレイン領域 3 2 9 には、 $1 \times 10^{-9}$

$\sim 5 \times 10^{-1} \text{ cm}^{-3}$  の濃度でボロン (B) が含まれる。

#### 【 0 1 3 6 】

次いで、島状半導体膜 3 0 3 及び 3 0 4 、ゲート絶縁膜 3 0 8 及び 3 0 9 、ゲート電極 3 1 4 及び 3 1 5 を覆うように、絶縁膜 3 3 1 を形成する (図 8 (C) 参照)。

#### 【 0 1 3 7 】

絶縁膜 3 3 1 は、プラズマ CVD 法や減圧 CVD (LPCVD) により、酸化珪素や窒素を含む酸化珪素膜を用いて形成することができる。本実施例では、プラズマ CVD 法により酸化珪素膜を膜厚 50 ~ 200 nm、好ましくは 100 nm で成膜する。

#### 【 0 1 3 8 】

次いで絶縁膜 3 3 1 をエッチングすることにより、ゲート絶縁膜 3 0 8 及びゲート電極 3 1 4 の側面にサイドウォール 3 3 3 を形成し、ゲート絶縁膜 3 0 9 及びゲート電極 3 1 5 の側面にサイドウォール 3 3 4 を形成する (図 8 (D) 参照)。サイドウォール 3 3 3 及び 3 3 4 は、テーパー状や矩形状になるように形成し、本実施例では、テーパー状のサイドウォール 3 3 3 及び 3 3 4 を形成する。

#### 【 0 1 3 9 】

次に島状半導体膜 3 0 3 及び 3 0 4 、ゲート絶縁膜 3 0 8 及び 3 0 9 、ゲート電極 3 1 4 及び 3 1 5 、並びにサイドウォール 3 3 3 及び 3 3 4 を覆って、金属膜 3 3 5 を形成する (図 8 (E) 参照)。

#### 【 0 1 4 0 】

金属膜 3 3 5 として、チタン (Ti) 、ニッケル (Ni) 、コバルト (Co) 、タングステン (W) 、白金 (Pt) 等を用いることができる。本実施の形態では、金属膜 3 3 5 として、ニッケル膜を 10 nm の厚さで成膜する。

#### 【 0 1 4 1 】

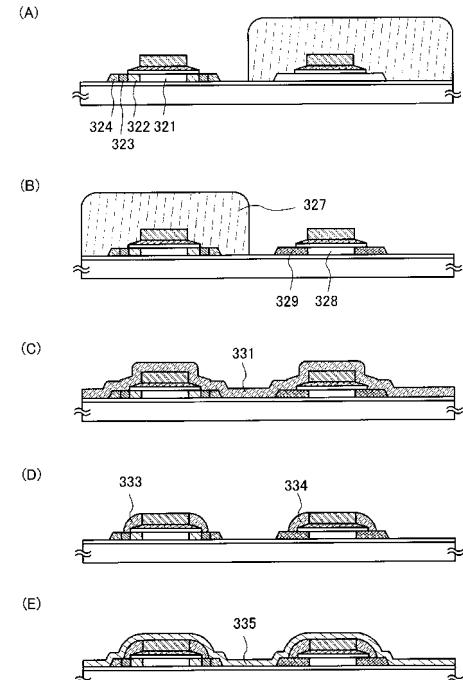

次いで、金属膜 3 3 5 を形成した島状半導体膜 3 0 3 及び 3 0 4 を、ファーネスアニール炉を用いる熱アニール法、レーザーアニール法、またはラピッドサーマルアニール法 (RTA 法) を適用して加熱する。これにより島状半導体膜 3 0 3 中にシリサイド領域 3 4 1 、島状半導体膜 3 0 4 中にシリサイド領域 3 4 2 が形成される。本実施の形態では、ラピッドサーマルアニール法により 350 以上的温度で加熱することによりシリサイド領域 3 4 1 及び 3 4 2 を形成する。

#### 【 0 1 4 2 】

シリサイド領域 3 4 1 及び 3 4 2 を形成したら、未反応の金属膜 3 3 5 を、硫酸や硝酸等の薬液によりエッチングして除去する (図 9 (A) 参照)。

#### 【 0 1 4 3 】

次に島状半導体膜 3 0 3 及び 3 0 4 、ゲート絶縁膜 3 0 8 及び 3 0 9 、ゲート電極 3 1 4 及び 3 1 5 、サイドウォール 3 3 3 及び 3 3 4 を覆って、第 1 層間絶縁膜 3 4 4 を形成する。

#### 【 0 1 4 4 】

第 1 層間絶縁膜 3 4 4 としては、プラズマ CVD 法またはスパッタ法を用いて、シリコンを含む絶縁膜、例えば酸化珪素膜、窒化珪素膜、窒素を含む酸化珪素膜、またはその積層膜で形成する。勿論、第 1 層間絶縁膜 3 4 4 は窒素を含む酸化珪素膜や窒化珪素膜、またはその積層膜に限定されるものではなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。

#### 【 0 1 4 5 】

本実施例では、まず窒素を含む酸化珪素膜をプラズマ CVD 法により 50 nm 形成し、レーザ照射方法によって不純物を活性化する。又は窒素を含む酸化珪素膜形成後、窒素雰

10

20

30

40

50

圧気中 550 で 4 時間加熱して、不純物を活性化してもよい。

【0146】

次に第 1 層間絶縁膜 344 上に、第 2 層間絶縁膜 343 として、プラズマ CVD 法により窒化珪素膜を 50 nm 形成し、更に窒素を含む酸化珪素膜を 600 nm 形成する。この窒化珪素膜及び窒素を含む酸化珪素膜の積層膜が第 2 層間絶縁膜 343 である。

【0147】

次に全体を 410 で 1 時間加熱し、窒化珪素膜から水素を放出させることにより水素化を行う。

【0148】

また第 2 層間絶縁膜 343 上に、さらに絶縁膜を積層してもよい。このような絶縁膜としては、感光性または非感光性の有機材料（ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジストまたはベンゾシクロブテン）、シロキサン、及びそれらの積層構造を用いることができる。有機材料として、ポジ型感光性有機樹脂又はネガ型感光性有機樹脂を用いることができる。

10

【0149】

なおシロキサンとは、シリコン（Si）と酸素（O）との結合で骨格構造で構成され、置換基として、少なくとも水素を含む有機基（例えばアルキル基、芳香族炭化水素）が用いられるものである。また置換基として、フルオロ基を用いてもよい。さらに置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

【0150】

20

また第 2 層間絶縁膜 343 上の絶縁膜として、水分や酸素などを他の絶縁膜と比較して透過させにくい膜を成膜してもよい。代表的には、スパッタ法または CVD 法により得られる窒化珪素膜、酸化珪素膜、酸素を含む窒化珪素膜（組成比 N > O）または窒素を含む酸化珪素膜（組成比 N < O）、炭素を主成分とする薄膜（例えば DLC 膜、CN 膜）などを用いることができる。

【0151】

第 1 層間絶縁膜 344 及び第 2 層間絶縁膜 343 をエッチングして、第 1 層間絶縁膜 344 及び第 2 層間絶縁膜 343 に、島状半導体膜 303 に到達するコンタクトホール 345 及び 346、島状半導体膜 304 に到達するコンタクトホール 347 及び 348 を形成する。

30

【0152】

このとき n チャネル型 TFT 356 の活性層となる島状半導体膜 303 においては、コンタクトホール 345 及び 346 は、接続領域 324 にのみに到達するように形成する。

【0153】

また p チャネル型 TFT 357 の活性層となる島状半導体膜 304 においては、コンタクトホール 347 及び 348 は、シリサイド領域 342 に達すればよい。

【0154】

次いで接続領域 324 表面の酸化膜を除去するために、島状半導体膜 303 及び 304 の、コンタクトホール 345 ~ 348 によって露出した表面をフッ酸で洗浄、もしくは水素プラズマ雰囲気中で基板を設置し、島状半導体膜 303 及び 304 の、コンタクトホール 345 ~ 348 によって露出した表面にプラズマ処理を行う。本実施例ではフッ酸を用いて島状半導体膜 303 及び 304 の、コンタクトホール 345 ~ 348 によって露出した表面を処理する。これによりソース電極またはドレイン電極 351、352 と島状半導体膜 303、ソース電極またはドレイン電極 352、353 と島状半導体膜 304 との電気的接触を良好にすることができる。

40

【0155】

次いで第 2 層間絶縁膜 343 上にコンタクトホール 345 ~ 348 を介して、第 3 の導電膜を形成し、第 3 の導電膜を用いて、ソース電極またはドレイン電極 351 ~ 353 を形成する。

【0156】

50

本実施例として、第3の導電膜は金属膜を用いる。金属膜は、アルミニウム(A1)、チタン(Ti)、モリブデン(Mo)、タンクステン(W)もしくはシリコン(Si)の元素からなる膜又はこれらの元素を用いた合金膜を用いればよい。本実施例では、チタン膜(Ti)、アルミニウム膜(A1)、チタン膜(Ti)をそれぞれ100nm、300nm、100nmに積層したのち、所望の形状になるようにエッチングしてソース電極またはドレイン電極351～353を形成する。

#### 【0157】

またこのソース電極またはドレイン電極351～353を、ニッケル、コバルト、鉄のうち少なくとも1種の元素、及び炭素を含むアルミニウム合金膜で形成してもよい。このようなアルミニウム合金膜は、シリコンと接触してもシリコンとアルミニウムの相互拡散が防止できる。またこのようなアルミニウム合金膜は、透明導電膜、例えばITO(In di um Tin Oxide)膜と接触しても酸化還元反応が起こらないため、両者を直接接触させることができる。さらにこのようなアルミ合金膜は、比抵抗が低く耐熱性にも優れているので、配線材料としては有用である。10

#### 【0158】

またソース電極またはドレイン電極351～353はそれぞれ、電極と配線を同じ材料で同一工程で形成してもよいし、電極と配線を別々に形成してそれらを接続させてもよい。

#### 【0159】

ソース電極またはドレイン電極351は、シリサイド領域341を介して、nチャネル型TFT356のソース領域またはドレイン領域323の一方に電気的に接続されている。ソース電極またはドレイン電極352は、シリサイド領域341を介して、nチャネル型TFT356のソース領域またはドレイン領域323の他方、並びにシリサイド領域342を介して、pチャネル型TFT357のソース領域またはドレイン領域329の一方に電気的に接続されている。またソース電極またはドレイン電極353は、シリサイド領域342を介して、pチャネル型TFT357のソース領域またはドレイン領域329の他方に電気的に接続されている。20

#### 【0160】

上記一連の工程によってnチャネル型TFT356及びpチャネル型TFT357を含むCMOS回路358を含む半導体装置を形成することができる(図9(D)参照)。30

#### 【0161】

また、本実施例は、必要であれば実施の形態のいかなる記載とも自由に組み合わせることが可能である。

#### 【実施例3】

#### 【0162】

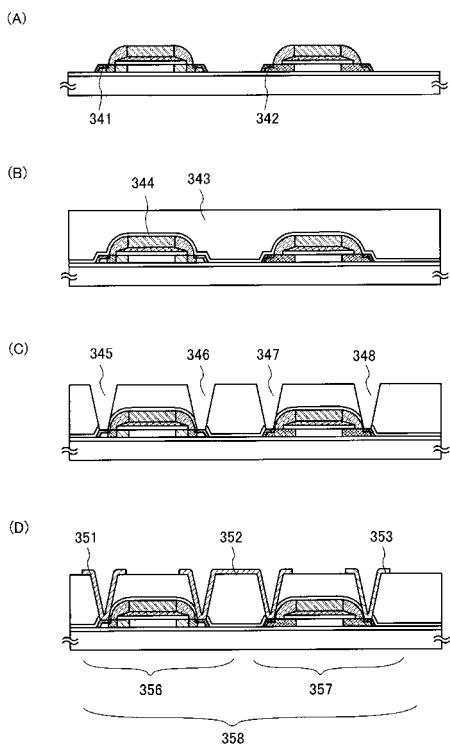

本実施例では、pチャネル型TFTにも接続領域を形成する例について、図10(A)～図10(C)を用いて説明する。なお、実施例2と同じものについては同じ符号で示し、特に符号の付いていないものについては、実施例2の記載を援用する。

#### 【0163】

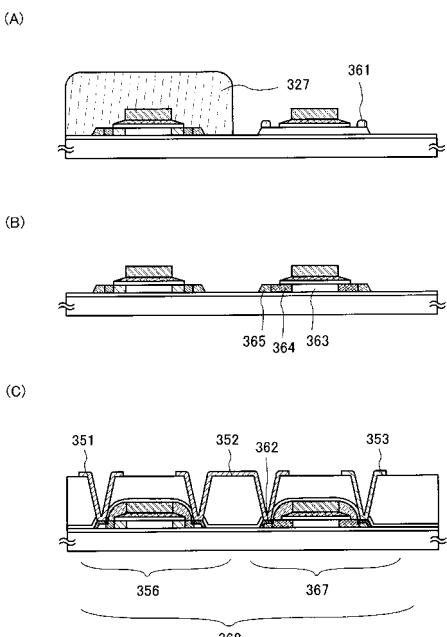

まず実施例2の記載に基づいて、図8(A)のn型を付与する元素を添加する工程までを行う。次いで、pチャネル型TFT367の活性層となる島状半導体膜304中の、接続領域365となる領域上に、レジスト361を形成する。また、nチャネル型TFT356の、活性層となる島状半導体膜303、ゲート絶縁膜308、ゲート電極314を覆って、レジスト327を形成する(図10(A)参照)。40

#### 【0164】

次いで、実施例2の記載に基づき、p型を付与する元素としてホウ素を用い、島状半導体膜304中に、チャネル形成領域363、ソース領域またはドレイン領域364、接続領域365を形成する(図10(B)参照)。

#### 【0165】

次に実施例2の記載を基にして、サイドウォール形成、シリサイド領域形成、層間絶縁

膜形成、コンタクトホール形成、ソース電極またはドレイン電極351～353形成を行う(図10(C)参照)。

#### 【0166】

ソース電極またはドレイン電極352、353、並びに層間絶縁膜344及び343中のコンタクトホール347及び348は、pチャネル型TFT367の接続領域365のシリサイド領域にのみ達しており、ソース領域またはドレイン領域364には達していない。

#### 【0167】

ソース電極またはドレイン電極351は、シリサイド領域341を介して、nチャネル型TFT356のソース領域またはドレイン領域323の一方に電気的に接続されている。ソース電極またはドレイン電極352は、シリサイド領域341を介して、nチャネル型TFT356のソース領域またはドレイン領域323の他方、並びにシリサイド領域362を介して、pチャネル型TFT367のソース領域またはドレイン領域364の一方に電気的に接続されている。またソース電極またはドレイン電極353は、シリサイド領域362を介して、pチャネル型TFT367のソース領域またはドレイン領域364の他方に電気的に接続されている。以上のようにしてCMOS回路368が形成される。

#### 【0168】

また、本実施例は、必要であれば実施の形態及び他の実施例のいかなる記載とも自由に組み合わせることが可能である。

#### 【実施例4】

#### 【0169】

本実施例では、本発明を用いてCPU(中央演算装置:Central Processor Unit)を作製した例を図11(A)～図11(C)、図12(A)～図12(B)、図13、図14及び図15(A)～図15(C)を用いて示す。

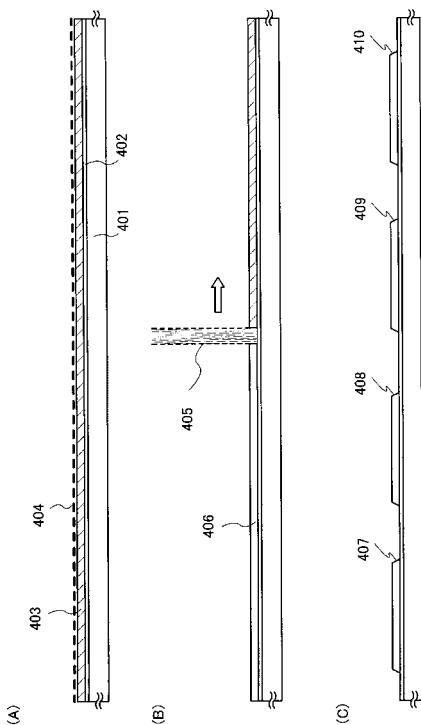

#### 【0170】

図11(A)に示すように、絶縁表面を有する基板401上に下地膜402を形成する。基板401には、例えばバリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、ステンレス基板等を用いることができる。また、PET、PES、PENに代表されるプラスチックや、アクリル等の可撓性を有する合成樹脂からなる基板は、一般的に他の基板と比較して耐熱温度が低い傾向にあるが、作製工程における処理温度に耐え得るのであれば用いることが可能である。

#### 【0171】

下地膜402は基板401中に含まれるNaなどのアルカリ金属やアルカリ土類金属が、半導体膜中に拡散し、半導体素子の特性に悪影響を及ぼすのを防ぐために設ける。よってアルカリ金属やアルカリ土類金属の半導体膜への拡散を抑えることができる酸化珪素や、窒化珪素、窒素を含む酸化珪素などの絶縁膜を用いて形成する。本実施例では、プラズマCVD法を用いてSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>O及びH<sub>2</sub>を反応ガスとして形成される酸素を含む窒化珪素膜を10～200nm(本実施例では50nm)、SiH<sub>4</sub>及びN<sub>2</sub>Oを反応ガスとして形成される酸素を含む窒化珪素膜を50～200nm(本実施例では100nm)の順に積層する。なお下地膜402は単層構造を有してもよく、例えば窒素を含む酸化珪素膜を10～400nm(好ましくは50～300nm)の膜厚になるように形成することができる。

#### 【0172】

ガラス基板、ステンレス基板またはプラスチック基板のように、アルカリ金属やアルカリ土類金属が多少なりとも含まれている基板を用いる場合、不純物の拡散を防ぐという観点から下地膜を設けることは有効であるが、石英基板など不純物の拡散がさして問題となる場合は、必ずしも設ける必要はない。

#### 【0173】

下地膜402上に非晶質半導体膜403を形成する。非晶質半導体膜403の膜厚は25～100nm(好ましくは30～60nm)とする。また非晶質半導体は珪素だけでは

10

20

30

40

50

なくシリコンゲルマニウムも用いることができ、シリコンゲルマニウムを用いる場合、ゲルマニウムの濃度は 0.01 ~ 4.5 atomic % 程度であることが好ましい。本実施例では 66 nm の珪素を主成分とする半導体膜（非晶質珪素膜、アモルファスシリコンとも表記する）を用いる。

#### 【0174】

次に、非晶質半導体膜 403 に触媒元素を添加する。ここで添加とは、少なくとも非晶質半導体膜の結晶化が促進されるように非晶質半導体膜 403 の表面上に触媒元素を形成することをいう。触媒元素を形成することにより、非晶質半導体膜が低温で結晶化できるため好ましい。

#### 【0175】

例えば、非晶質半導体膜 403 上にスピンドローティング法やディップ法等により、結晶化を促進する元素、例えばニッケル、を含む溶液（水溶液や酢酸溶液を含む）を用いて、結晶化を促進する元素を含む膜 404（但し、極めて薄いため膜として観測できない場合もある）を形成する（図 11 (A) 参照）。このとき非晶質半導体膜 403 の表面の濡れ性を改善し、非晶質半導体膜の表面全体に溶液を行き渡らせるため、酸素雰囲気中での UV 光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜（図示しない）を 1 nm ~ 5 nm に成膜することが望ましい。また、イオン注入法によりニッケルイオンを非晶質半導体膜中に注入する、ニッケルを含有する水蒸気雰囲気中で加熱する、ターゲットをニッケル材料としてアルゴンプラズマでスパッタリングすることを行ってもよい。本実施例では、ニッケル酢酸塩 10 ppm を含有した水溶液をスピンドローティング法により非晶質半導体膜 403 上に結晶化を促進する元素を含有させる。

#### 【0176】

その後、非晶質半導体膜 403 にレーザ光（レーザビーム）405 を照射する。

#### 【0177】

またこのようなレーザ照射において、精度よく重ね合わせたり、照射開始位置や照射終了位置を制御するため、マーカーを形成することもできる。マーカーはフォトリソグラフ法を用いて、基板へ形成すればよい。

#### 【0178】

このレーザ照射により、非晶質半導体膜 403 は結晶化し、結晶性半導体膜 406 が形成される（図 11 (B) 参照）。

#### 【0179】

その後、触媒元素を低減、又は除去するためにゲッタリング工程を施す。本実施例では、非晶質半導体膜をゲッタリングシンクとして触媒元素を捕獲する方法を説明する。まず、結晶性半導体膜上に酸素雰囲気中での UV 光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜を形成する。次いでプラズマ CVD 法を用いて、原料ガスに SH<sub>4</sub>、Ar、圧力が 0.3 パスカル、RF パワーが 3 kW、基板温度が 150 ℃ として非晶質半導体膜を 150 nm の膜厚で形成する。

#### 【0180】

その後、窒素雰囲気で 550 ℃ 、4 時間の加熱処理を行い、触媒元素を低減、又は除去する。そして、ゲッタリングシンクとなる非晶質半導体膜、及び酸化膜をフッ酸等により除去し、触媒元素が低減、又は除去された結晶性半導体膜を得ることができる。

#### 【0181】

図 11 (C) に示すように、結晶性半導体膜 406 を用いて、島状半導体膜 407 ~ 410 を得る。島状半導体膜 407 ~ 410 を得るには、結晶性半導体膜 406 にフォトレジストを塗布し、所定のマスク形状を露光し、焼成して、結晶性半導体膜上にマスクを形成する。このマスクを用いて、ドライエッチング法により結晶性半導体膜をエッチングする。ドライエッチング法のガスは、CF<sub>4</sub> と、O<sub>2</sub> を用いることができる。

#### 【0182】

その後、実施の形態 1 ~ 実施の形態 3 及び実施例 2 ~ 実施例 3 と同様の工程によって、

10

20

30

40

50

一導電型を付与する元素を導入する工程、サイドウォール形成、シリサイド領域形成の工程を行う。また本実施例の作製条件、作製工程、成膜材料等について、特に記載のないものは実施例2と同様の作製条件、作製工程、成膜材料等を用いている。

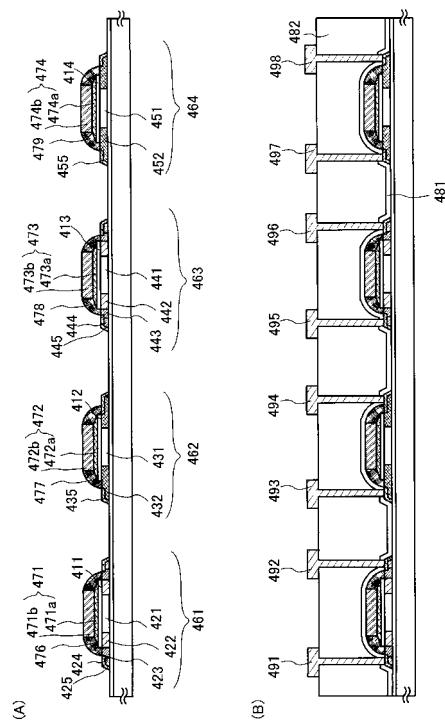

#### 【0183】

ただし、本実施例においては、基板401上にnチャネル型TFT461及び463、pチャネル型TFT462及び464を形成する。図12(A)において、nチャネル型TFT461は下地膜402上に、島状半導体膜407、ゲート絶縁膜411、下層ゲート電極471a及び上層ゲート電極471bからなるゲート電極471を有している。また島状半導体膜407中には、接続領域424、ソース領域またはドレイン領域423、低濃度不純物領域422、及びチャネル形成領域421を有する。ソース領域またはドレイン領域423の一部及び接続領域424には、シリサイド領域425が形成されている。ゲート絶縁膜411、ゲート電極471の側面には、サイドウォール476が形成されている。10

#### 【0184】

また、pチャネル型TFT462は下地膜402上に、島状半導体膜408、ゲート絶縁膜412、下層ゲート電極472a及び上層ゲート電極472bからなるゲート電極472を有している。また島状半導体膜408中には、ソース領域またはドレイン領域432、及びチャネル形成領域431を有する。ソース領域またはドレイン領域432には、シリサイド領域435が形成されている。ゲート絶縁膜412、ゲート電極472の側面には、サイドウォール477が形成されている。20

#### 【0185】

nチャネル型TFT463は下地膜402上に、島状半導体膜409、ゲート絶縁膜413、下層ゲート電極473a及び上層ゲート電極473bからなるゲート電極473を有している。また島状半導体膜409中には、接続領域444、ソース領域またはドレイン領域443、低濃度不純物領域442、及びチャネル形成領域441を有する。ソースドレイン領域またはドレイン領域443には、シリサイド領域445が形成されている。ゲート絶縁膜413、ゲート電極473の側面には、サイドウォール478が形成されている。

#### 【0186】

さらに、pチャネル型TFT464は下地膜402上に、島状半導体膜410、ゲート絶縁膜414、下層ゲート電極474a及び上層ゲート電極474bからなるゲート電極474を有している。また島状半導体膜410中には、ソース領域またはドレイン領域452、及びチャネル形成領域451を有する。ソース領域またはドレイン領域452には、シリサイド領域455が形成されている。ゲート絶縁膜414、ゲート電極474の側面には、サイドウォール479が形成されている。30

#### 【0187】

次に、島状半導体膜407～410、ゲート絶縁膜411～414、ゲート電極471～474を覆うように第1の層間絶縁膜481を形成する。第1の層間絶縁膜481は窒素を有する絶縁膜であればよく、本実施例では、プラズマCVD法により100nmの窒化珪素膜を形成する。40

#### 【0188】

その後、加熱処理を行い、水素化を施す。本実施例では、窒素雰囲気中410で1時間の加熱処理を行う。その結果、窒化珪素から放出される水素により、酸化珪素膜や珪素膜のダングリングボンドを終端する。

#### 【0189】

そして、第1の層間絶縁膜481を覆うように第2の層間絶縁膜482を形成する。第2の層間絶縁膜482は、無機材料(酸化珪素、窒化珪素、酸素を含む窒化珪素など)、感光性または非感光性の有機材料(ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジストまたはベンゾシクロブテン)、シロキサン、及びそれらの積層構造を用いることができる。50

## 【0190】

シロキサンとは、シリコン(Si)と酸素(O)との結合で骨格構造で構成さ、置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられるものである。また置換基として、フルオロ基を用いてもよい。さらには置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

## 【0191】

また第2の層間絶縁膜482として有機材料を用いて形成する場合は、ポジ型感光性有機樹脂又はネガ型感光性有機樹脂を用いることができる。例えば、有機材料としてポジ型の感光性アクリルを用いた場合、フォトリソグラフィ工程による露光処理により感光性有機樹脂をエッティングすると上端部に曲率を有する開口部を形成することができる。本実施例では、原料ガスにSiH<sub>4</sub>、N<sub>2</sub>Oを用いるプラズマCVD法により形成される窒化された酸化珪素膜を600nmの膜厚に形成する。このとき、基板の温度を300～450に加熱し、本実施例では400に加熱する。10

## 【0192】

次いで、第1の層間絶縁膜481、第2の層間絶縁膜482に開口部、いわゆるコンタクトホールを形成し、不純物領域と接続する電極又は配線491～498を形成する。本実施例では電極と配線を一体形成するが、電極と配線を別々に形成して電気的に接続させてもよい。また電極又は配線491～498と同時にゲート電極と接続する配線を形成する。このとき、開口部の直径を1.0μm程度とするため、開口部は垂直に開口するとい。そのため、意図的にレジスト端部がテーパー形状とならないように形成する。またレジストとコンタクトホールを開口する絶縁膜の選択比が高ければ、レジスト端部がテーパー形状となっても構わない。本実施例では、第2の層間絶縁膜482に窒化された酸化珪素膜を用いるため、端部が垂直となるように、つまり意図的にテーパー形状とならないように形成されたレジストマスクを用いて、ドライエッティング法により開口部を形成する。このとき、実際のレジスト端部はテーパー形状となることがある。エッティングガスにCHF<sub>3</sub>、Heを用い、第1のエッティング時間として数sec、例えば3sec、第2のエッティング時間として100～130sec、例えば117sec、第3のエッティング時間として200～270sec、例えば256secとしてエッティングを行う。このとき、開口部のエッティング状況に応じて、エッティングガスの流量を決定することができる。20

## 【0193】

なお第2の層間絶縁膜482に、有機材料やシロキサンを用いる場合、開口部の側面を垂直とするため、レジストマスクよりも高硬度を有するマスク、例えば酸化珪素膜等の無機材料から形成するハードマスクを用いるとよい。30

## 【0194】

その後、レジストマスクをO<sub>2</sub>アッシングやレジスト剥離液により除去する。

## 【0195】

そして開口部に電極又は配線491～498を形成する(図12(B)参照)。配線は、アルミニウム(A1)、チタン(Ti)、モリブデン(Mo)、タンゲステン(W)もしくはシリコン(Si)の元素からなる膜又はこれらの元素を用いた合金膜を用いればよい。本実施例では、チタン膜(Ti)、窒化チタン膜(TiN)、チタンーアルミニウム合金膜(A1-Si)、チタン膜(Ti)をそれぞれ60nm、40nm、300nm、100nmに積層したのち、所望の形状にエッティングして配線、つまりソース電極、ドレイン電極を形成する。40

## 【0196】

またこの電極又は配線491～498を、ニッケル、コバルト、鉄のうち少なくとも1種の元素、及び炭素を含むアルミニウム合金膜で形成してもよい。このようなアルミニウム合金膜は、シリコンと接触してもシリコンとアルミニウムの相互拡散が防止できる。またこのようなアルミニウム合金膜は、透明導電膜、例えばITO(Indium Tin Oxide)膜と接触しても酸化還元反応が起こらないため、両者を直接接觸させることができる。さらにこのようなアルミ合金膜は、比抵抗が低く耐熱性にも優れているので50

、配線材料としては有用である。

#### 【0197】

nチャネル型TFT461の電極又は配線491、並びに電極又は配線492は、ソース領域またはドレイン領域423には達しないように形成される。また第1の層間絶縁膜481及び第2の層間絶縁膜482中に形成され、電極又は配線491、並びに電極又は配線492と島状半導体膜407とを接続するために設けられるコンタクトホールは、ソース領域またはドレイン領域423には達しないように形成される。

#### 【0198】

nチャネル型TFT463の電極又は配線495、並びに電極又は配線496は、ソース領域またはドレイン領域443には達しないように形成される。また第1の層間絶縁膜481及び第2の層間絶縁膜482中に形成され、電極又は配線495、並びに電極又は配線496と島状半導体膜409とを接続するために設けられるコンタクトホールは、ソース領域またはドレイン領域443には達しないように形成される。

10

#### 【0199】

以上のようにして、低濃度不純物領域を有するように形成するLDD構造からなり、ゲート長が $1.0\text{ }\mu\text{m}$ 以下となるnチャネル型の薄膜トランジスタを形成することができる。また、低濃度不純物領域を有さないように形成するいわゆるシングル・ドレイン構造からなり、ゲート長が $1.0\text{ }\mu\text{m}$ 以下となるpチャネル型の薄膜トランジスタが完成する。なおゲート長が $1.0\text{ }\mu\text{m}$ 以下となるTFTをサブミクロンTFTとも表記できる。pチャネル型の薄膜トランジスタは、ホットキャリアによる劣化や短チャネル効果が生じにくいことから、シングル・ドレイン構造とすることができます。

20

#### 【0200】

なお本発明において、pチャネル型の薄膜トランジスタをLDD構造としてもよい。さらにnチャネル型の薄膜トランジスタ、及びpチャネル型の薄膜トランジスタにおいて、LDD構造に代えて、低濃度不純物領域がゲート電極と重なる、いわゆるGOLD構造を有してもよい。

30

#### 【0201】

以上のように形成された薄膜トランジスタを有する半導体装置、本実施例においてはCPUを作製することができ、駆動電圧5Vで、動作周波数30MHzと高速動作が可能となる。

#### 【0202】

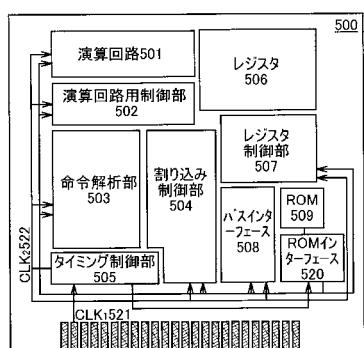

更に本実施例のCPUの構成についてブロック図を用いて説明する。

#### 【0203】

図13に示すCPUは、基板500上に、演算回路(ALU: Arithmetic logic unit)501、演算回路用制御部(ALU Controller)502、命令解析部(Instruction Decoder)503、割り込み制御部(Interrupt Controller)504、タイミング制御部(Timing Controller)505、レジスタ(Register)506、レジスタ制御部(Register Controller)507、バスインターフェース(Bus I/F)508、書き換え可能なROM509、ROMインターフェース(ROM I/F)520とを主に有している。またROM509及びROMインターフェース520は、別チップに設けても良い。

40

#### 【0204】

勿論、図13に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

#### 【0205】

バスインターフェース508を介してCPUに入力された命令は、命令解析部503に入力され、デコードされた後、演算回路用制御部502、割り込み制御部504、レジスタ制御部507、タイミング制御部505に入力される。

#### 【0206】

50

演算回路用制御部 502、割り込み制御部 504、レジスタ制御部 507、タイミング制御部 505は、デコードされた命令に基づき、各種制御を行う。具体的に演算回路用制御部 502は、演算回路 501の駆動を制御するための信号を生成する。また、割り込み制御部 504は、C P Uのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタ制御部 507は、レジスタ 506のアドレスを生成し、C P Uの状態に応じてレジスタ 506の読み出しや書き込みを行う。

#### 【0207】

またタイミング制御部 505は、演算回路 501、演算回路用制御部 502、命令解析部 503、割り込み制御部 504、レジスタ制御部 507の駆動のタイミングを制御する信号を生成する。例えばタイミング制御部 505は、基準クロック信号 C L K<sub>1</sub> 521を元に、内部クロック信号 C L K<sub>2</sub> 522を生成する内部クロック生成部を備えており、クロック信号 C L K<sub>2</sub>を上記各種回路に供給する。10

#### 【0208】

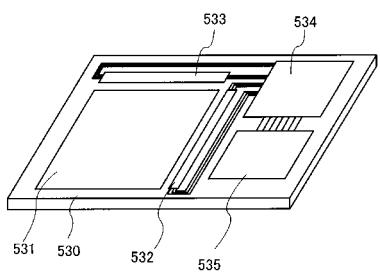

図 14には、画素部と、C P U、その他の回路が同一基板に形成された表示装置、いわゆるシステムオンパネルを示す。基板 530上に画素部 531、画素部 531が有する画素を選択する走査線駆動回路 532と、選択された画素にビデオ信号を供給する信号線駆動回路 533とが設けられている。走査線駆動回路 532、及び信号線駆動回路 533から引き回される配線により C P U 534、その他の回路、例えばコントロール回路 535とが接続されている。なおコントロール回路にはインターフェースが含まれている。そして、基板の端部に F P C 端子との接続部を設け、外部信号とのやりとりを行う。20

#### 【0209】

その他の回路として、映像信号処理回路、電源回路、階調電源回路、ビデオ R A M、メモリ (D R A M、S R A M、P R O M) 等を基板上に設けることができる。またこれら回路は、I C チップにより形成し、基板上に実装してもよい。さらに必ずしも走査線駆動回路 532、及び信号線駆動回路 533を同一基板に形成する必要はなく、例えば走査線駆動回路 532のみを同一基板に形成し、信号線駆動回路 533を I C チップにより形成し、実装してもよい。

#### 【0210】

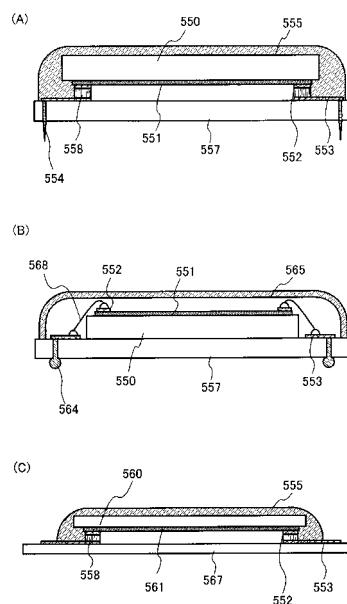

図 15 (A)には、パッケージングされたC P Uの形態を示す。基板 550上に形成されたC P Uの機能を有する薄膜トランジスタアレイ 551を、C P U表面に設けられた電極 (ソース電極やドレイン電極、又はそれらの上に絶縁膜を介して形成された電極等) 552が下側となるフェイスダウン状態とする。基板 550は、ガラス、プラスチックを用いることができる。また銅やその合金で形成される配線 553が設けられた配線基板、例えばプリント基板 557を用意する。プリント基板 557には、接続端子 (ピン) 554が設けられている。そして電極 552と、配線 553とを異方性導電膜 558等を介して接続する。その後、エポキシ樹脂等の樹脂 555で基板 550上方から覆い、パッケージングされたC P Uとして完成する。または中空に保った状態で外周をプラスチックなどで囲んでもよい。30

#### 【0211】

図 15 (B)には、図 15 (A)と異なり、C P U表面に設けられた電極 552が上側となるようにC P Uの機能を有する薄膜トランジスタアレイ 551をフェイスアップ状態とする。そしてプリント基板 557上に基板 550を固定し、電極 552と、配線 553とをワイヤ 568により接続する。このようにワイヤにより接続することをワイヤボンディングという。そして電極 552と、配線 553に接続されるバンプ 564とが接続する。その後、中空に保った状態で外周をプラスチック 565等で囲み、パッケージングされたC P Uとして完成する。40

#### 【0212】

図 15 (C)には、フレキシブル性を有する基板、例えば F P C (F l e x i b l e p r i n t e d c i r c u i t) 上に、C P Uの機能を有する薄膜トランジスタアレイ

10

20

30

40

50

551を固定する例を示す。基板560に形成されたCPUの機能を有する薄膜トランジスタアレイ551を、CPU表面に設けられた電極552が下側となるフェイスダウン状態とする。基板560には、ガラス、石英、金属、バルク半導体、プラスチックを用いることができるが、図15(C)ではフレキシブル性の高いプラスチックを用いると好ましい。また、銅やその合金で形成される配線553が設けられたフレキシブル性を有するFPC567を用意する。そして、電極552と、配線553とを異方性導電膜558を介して接続する。その後、エポキシ樹脂等の樹脂555で基板560上方から覆い、パッケージングされたCPUとして完成する。

#### 【0213】

このようにパッケージングされたCPUは、外部から保護され、さらに携帯しやすくなる。そして所望箇所に、CPUを実装することができ、特に図15(C)のようにフレキシブル性を有すると、実装する位置の自由度が高まる。またパッケージングすることによりCPUの機能を補助することもできる。

#### 【0214】

以上のように、本発明のTFTを用いて、CPU等の半導体装置を作製することができる。薄膜トランジスタにより形成されるCPUは軽量であるため、携帯や実装するときの負担を軽減することができる。また、本実施例で説明したCPUや液晶表示装置やEL表示装置等、様々な表示装置を用いて、システムオンパネルを作製することが可能である。

#### 【0215】

また、本実施例は、必要であれば実施の形態及び他の実施例のいかなる記載とも自由に組み合わせることが可能である。

#### 【実施例5】

#### 【0216】

本実施例では、本発明を用いてIDチップ(IDタグ、ICチップ、ICタグともいう)を作製した例を、図16(A)～図16(B)、図17(A)～図17(B)、図18(A)～図18(B)及び図19(A)～図19(B)を用いて示す。

#### 【0217】

本実施例では、半導体素子として絶縁分離されたTFTを例示するが、集積回路に用いられる半導体素子はこれに限定されず、あらゆる回路素子を用いることができる。例えば、TFTの他に、記憶素子、ダイオード、光電変換素子、抵抗素子、コイル、容量素子、インダクタなどが代表的に挙げられる。

#### 【0218】

まず図16(A)に示すように、スパッタ法を用いて耐熱性を有する基板(第1の基板)601上に剥離層602を形成する。第1の基板601として、例えばバリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板等を用いることができる。また、ステンレス基板を含む金属基板または半導体基板の表面に絶縁膜を形成したものを用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板は、一般的に上記基板と比較して耐熱温度が低い傾向にあるが、作製工程における処理温度に耐え得るのであれば用いることが可能である。

#### 【0219】

剥離層602は、非晶質シリコン、多結晶シリコン、単結晶シリコン、微結晶シリコン(セミアモルファスシリコンを含む)等、シリコンを主成分とする層を用いることができる。剥離層602は、スパッタ法、減圧CVD法、プラズマCVD法等を用いて形成することができる。本実施例では、膜厚50nm程度の非晶質シリコンを減圧CVD法で形成し、剥離層602として用いる。なお剥離層602はシリコンに限定されず、エッチングにより選択的に除去できる材料で形成すれば良い。剥離層602の膜厚は、50～60nmとするのが望ましい。セミアモルファスシリコンに関しては、30～50nmとしてもよい。

#### 【0220】

なおセミアモルファスシリコンに代表されるセミアモルファス半導体とは、非晶質半導

10

20

30

40

50

体と結晶構造を有する半導体（単結晶、多結晶を含む）の中間的な構造の半導体を含む膜である。このセミアモルファス半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を0.5~20nmとして非単結晶半導体中に分散させて存在せしめることが可能である。セミアモルファス半導体は、そのラマンスペクトルが $520\text{ cm}^{-1}$ よりも低波数側にシフトしており、またX線回折ではSi結晶格子に由来するとされる(111)、(220)の回折ピークが観測される。また、未結合手（ダングリングボンド）を终端化させる材料として水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。ここでは便宜上、このような半導体をセミアモルファス半導体（SAS）と呼ぶ。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なセミアモルファス半導体が得られる。

#### 【0221】

またSASは珪素を含む気体をグロー放電分解することにより得ることができる。代表的な珪素を含む気体としては、 $\text{SiH}_4$ であり、その他にも $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ などを用いることができる。また水素や、水素にヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素を加えたガスで、この珪素を含む気体を希釈して用いることで、SASの形成を容易なものとすることができます。希釈率は2倍~1000倍の範囲で珪素を含む気体を希釈することが好ましい。

#### 【0222】

次に、剥離層602上に、下地膜603を形成する。下地膜603は第1の基板601中に含まれるNaなどのアルカリ金属やアルカリ土類金属が、半導体膜中に拡散し、TFTなどの半導体素子の特性に悪影響を及ぼすのを防ぐために設ける。また下地膜603は、後の半導体素子を剥離する工程において、半導体素子を保護する役目も有している。下地膜603は単層であっても複数の絶縁膜を積層したものであっても良い。よってアルカリ金属やアルカリ土類金属の半導体膜への拡散を抑えることができる酸化珪素や、窒化珪素、窒素を含む酸化珪素、酸素を含む窒化珪素などの絶縁膜を用いて形成する。

#### 【0223】

本実施例では、下層下地膜603aとして膜厚100nmの窒素を含む酸化珪素膜、中層下地膜603bとして膜厚50nmの酸素を含む窒化珪素膜、上層下地膜603cとして膜厚100nmの窒素を含む酸化珪素膜を順に積層して下地膜603を形成するが、各膜の材質、膜厚、積層数は、これに限定されるものではない。例えば、下層の窒素を含む酸化珪素膜に代えて、膜厚0.5~3μmのシロキサン系樹脂をスピンドルコート法、スリットコーティング法、液滴吐出法などによって形成しても良い。また、中層の酸素を含む窒化珪素膜に代えて、窒化珪素膜( $\text{Si}_3\text{N}_4$ 等)を用いてもよい。また、上層の窒素を含む酸化珪素膜に代えて、酸化珪素膜を用いてても良い。また、それぞれの膜厚は、0.05~3μmとするのが望ましく、その範囲から自由に選択することができる。

#### 【0224】

或いは、剥離層602に最も近い、下地膜603の下層を窒素を含む酸化珪素膜または酸化珪素膜で形成し、中層をシロキサン系樹脂で形成し、上層を酸化珪素膜で形成しても良い。

#### 【0225】

ここで、酸化珪素膜は、 $\text{SiH}_4$ と $\text{O}_2$ 、又はTEOS(テトラエトキシシラン)と $\text{O}_2$ 等の混合ガスを用い、熱CVD、プラズマCVD、常圧CVD、バイアスECR CVD等の方法によって形成することができる。また、窒化珪素膜は、代表的には、 $\text{SiH}_4$ と $\text{NH}_3$ の混合ガスを用い、プラズマCVDによって形成することができる。また、窒素を含む酸化珪素膜(組成比 $\text{O} > \text{N}$ )、酸素を含む窒化珪素(組成比 $\text{N} > \text{O}$ )は、代表的には、 $\text{SiH}_4$ と $\text{N}_2\text{O}$ の混合ガスを用い、プラズマCVDによって形成することができる。

#### 【0226】

次に、下地膜603上に半導体膜を形成する。半導体膜は、下地膜603を形成した後

10

20

30

40

50

、大気に曝さずに形成することが望ましい。半導体膜の膜厚は 20 ~ 200 nm ( 望ましくは 40 ~ 170 nm 、好ましくは 50 ~ 150 nm ) とする。なお半導体膜は、非晶質半導体であっても良いし、セミアモルファス半導体であっても良いし、多結晶半導体であっても良い。また半導体は珪素だけではなくシリコンゲルマニウムも用いることができる。シリコンゲルマニウムを用いる場合、ゲルマニウムの濃度は 0.01 ~ 4.5 atom % 程度であることが好ましい。

#### 【 0 2 2 7 】

非晶質半導体は、珪素を含む気体をグロー放電分解することにより得ることができる。代表的な珪素を含む気体としては、 SiH<sub>4</sub> 、 Si<sub>2</sub>H<sub>6</sub> が挙げられる。この珪素を含む気体を、水素、水素とヘリウムで希釈して用いても良い。

10

#### 【 0 2 2 8 】

なお上述したようにセミアモルファス半導体は、珪素を含む気体をグロー放電分解することにより得ることができるが、珪素を含む気体中に、 CH<sub>4</sub> 、 C<sub>2</sub>H<sub>6</sub> などの炭化物気体、 GeH<sub>4</sub> 、 GeF<sub>4</sub> などのゲルマニウム化気体、 F<sub>2</sub> などを混入させて、エネルギー バンド幅を 1.5 ~ 2.4 eV 、若しくは 0.9 ~ 1.1 eV に調節しても良い。

#### 【 0 2 2 9 】

例えば、 SiH<sub>4</sub> に H<sub>2</sub> を添加したガスを用いる場合、或いは SiH<sub>4</sub> に F<sub>2</sub> を添加したガスを用いる場合、形成したセミアモルファス半導体を用いて TFT を作製すると、該 TFT のサブスレッショルド係数 ( S 値 ) を 0.35 V / dec 以下、代表的には 0.25 ~ 0.09 V / dec とし、移動度を 10 cm<sup>2</sup> / V sec とすることができる。そして上記セミアモルファス半導体を用いた TFT で、例えば 19 段リングオシレータを形成した場合、電源電圧 3 ~ 5 V において、その発振周波数は 1 MHz 以上、好ましくは 100 MHz 以上の特性を得ることができる。また電源電圧 3 ~ 5 V において、インバータ 1 段あたりの遅延時間は 26 ns 、好ましくは 0.26 ns 以下とすることができます。

20

#### 【 0 2 3 0 】

そして実施の形態 1 ~ 実施の形態 3 及び実施例 2 ~ 実施例 4 の記載に基づいて、一導電性を付与する元素の導入、サイドウォール形成、シリサイド領域形成までの工程を行う。

#### 【 0 2 3 1 】

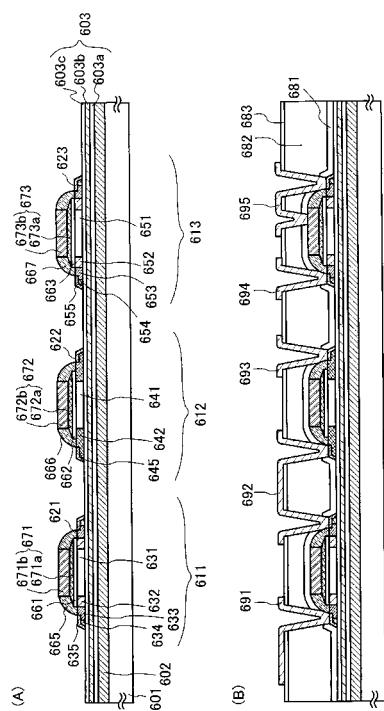

以上により、 n チャネル型 TFT 611 、 p チャネル型 TFT 612 、 n チャネル型 TFT 613 が形成される ( 図 16 ( A ) 参照 ) 。なお、本実施例では、 TFT 611 ~ 613 をトップゲート構造としたが、ボトムゲート構造 ( 逆スタガ構造 ) としてもよい。

30

#### 【 0 2 3 2 】

n チャネル型 TFT 611 は、上層下地膜 603c 上に島状半導体膜 621 、ゲート絶縁膜 661 、下層ゲート電極 671a 及び上層ゲート電極 671b からなるゲート電極 671 を有している。島状半導体膜 621 には、チャネル形成領域 631 、低濃度不純物領域 632 、ソース領域またはドレイン領域 633 、接続領域 634 、シリサイド領域 635 が形成される。シリサイド領域 635 は、ソース領域またはドレイン領域 633 の一部と接続領域 634 中に形成される。またサイドウォール 665 が、ゲート絶縁膜 661 及びゲート電極 671 の側面に形成されている。

#### 【 0 2 3 3 】

40

p チャネル型 TFT 612 は、上層下地膜 603c 上に島状半導体膜 622 、ゲート絶縁膜 662 、下層ゲート電極 672a 及び上層ゲート電極 672b からなるゲート電極 672 を有している。島状半導体膜 622 には、チャネル形成領域 641 、ソース領域またはドレイン領域 642 、シリサイド領域 645 が形成される。シリサイド領域 645 は、ソース領域またはドレイン領域 642 の一部中に形成される。またサイドウォール 666 が、ゲート絶縁膜 662 及びゲート電極 672 の側面に形成されている。

#### 【 0 2 3 4 】

n チャネル型 TFT 613 は、上層下地膜 603c 上に島状半導体膜 623 、ゲート絶縁膜 663 、下層ゲート電極 673a 及び上層ゲート電極 673b からなるゲート電極 673 を有している。島状半導体膜 623 には、チャネル形成領域 651 、低濃度不純物領

50

域 6 5 2、ソース領域またはドレイン領域 6 5 3、接続領域 6 5 4、シリサイド領域 6 5 5 が形成される。シリサイド領域 6 5 5 は、ソース領域またはドレイン領域 6 5 3 の一部と接続領域 6 5 4 中に形成される。またサイドウォール 6 6 7 が、ゲート絶縁膜 6 6 3 及びゲート電極 6 7 3 の側面に形成されている。

#### 【 0 2 3 5 】

さらに、この後、TFT 6 1 1 ~ TFT 6 1 3 を保護するためのパッシベーション膜 6 8 1 を形成しても良い。パッシベーション膜 6 8 1 は、アルカリ金属やアルカリ土類金属の TFT 6 1 1 ~ TFT 6 1 3 への侵入を防ぐことができる、窒化珪素、窒素を含む酸化珪素、窒化アルミニウム、酸化アルミニウム、酸化珪素などを用いるのが望ましい。具体的には、例えば膜厚 6 0 0 nm 程度の窒素を含む酸化珪素膜を、パッシベーション膜として用いることができる。この場合、水素化処理工程は、該窒素を含む酸化珪素膜形成後に 10 行っても良い。上記構成を用いることで、TFT 6 1 1 ~ TFT 6 1 3 が下地膜 6 0 3 とパッシベーション膜 6 8 1 とで覆われるため、Na などのアルカリ金属やアルカリ土類金属が、半導体素子に用いられている半導体膜中に拡散し、半導体素子の特性に悪影響を及ぼすのをより防ぐことができる。

#### 【 0 2 3 6 】

次に TFT 6 1 1 ~ TFT 6 1 3 及びパッシベーション膜 6 8 1 を覆うように、第 1 の層間絶縁膜 6 8 2 を形成する。第 1 の層間絶縁膜 6 8 2 は、ポリイミド、アクリル、ポリアミド等の、耐熱性を有する有機樹脂を用いることができる。また上記有機樹脂の他に、低誘電率材料 (low-k 材料)、シロキサン系材料を出発材料として形成された Si-O-Si 結合を含む樹脂 (以下、シロキサン系樹脂と呼ぶ) 等を用いることができる。 20

#### 【 0 2 3 7 】

シロキサンとは、シリコン (Si) と酸素 (O) との結合で骨格構造で構成され、置換基として、少なくとも水素を含む有機基 (例えばアルキル基、芳香族炭化水素) が用いられるものである。また置換基として、フルオロ基を用いてもよい。さらに置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

#### 【 0 2 3 8 】

第 1 の層間絶縁膜 6 8 2 の形成には、その材料に応じて、スピンコート、ディップ、スプレー塗布、液滴吐出法 (インクジェット法、スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーラー、カーテンコーラー、ナイフコーラー等を採用することができる。また、無機材料を用いてもよく、その際には、酸化珪素、窒化珪素、酸窒化珪素、PSG (リンガラス)、BPSG (リンボロンガラス)、アルミナ膜等を用いることができる。なお、これらの絶縁膜を積層させて、第 1 の層間絶縁膜 6 8 2 を形成しても良い。 30

#### 【 0 2 3 9 】

さらに本実施例では、第 1 の層間絶縁膜 6 8 2 上に、第 2 の層間絶縁膜 6 8 3 を形成する。第 2 の層間絶縁膜 6 8 3 としては、DLC (ダイヤモンドライクカーボン) 或いは窒化炭素 (CN) 等の炭素を有する膜、又は、酸化珪素膜、窒化珪素膜或いは窒素を含む酸化珪素膜等を用いることができる。形成方法としては、プラズマ CVD 法や、大気圧プラズマ CVD 等を用いることができる。あるいは、ポリイミド、アクリル、ポリアミド、レジスト又はベンゾシクロブテン等の感光性又は非感光性の有機材料や、シロキサン系樹脂等を用いてもよい。 40

#### 【 0 2 4 0 】

なお、第 1 の層間絶縁膜 6 8 2 又は第 2 の層間絶縁膜 6 8 3 と、後に形成される配線を構成する導電材料等との熱膨張率の差から生じる応力によって、第 1 の層間絶縁膜 6 8 2 又は第 2 の層間絶縁膜 6 8 3 の膜剥がれや割れが生じるのを防ぐために、第 1 の層間絶縁膜 6 8 2 又は第 2 の層間絶縁膜 6 8 3 中にフィラーを混入させておいても良い。

#### 【 0 2 4 1 】

次に、第 1 の層間絶縁膜 6 8 2 及び第 2 の層間絶縁膜 6 8 3 にコンタクトホールを形成する。そして島状半導体膜 6 2 1 ~ 6 2 3 の、コンタクトホールによって露出した表面を 50

フッ酸で洗浄、もしくは水素プラズマでプラズマ処理する。次いでコンタクトホールを介して、TFT611～TFT613に接続する電極又は配線691～695を形成する。本実施例では電極と配線を一体形成するが、電極と配線を別々に形成して電気的に接続させてもよい。コンタクトホール形成時のエッチングに用いられるガスは、CHF<sub>3</sub>とHeの混合ガスを用いたが、これに限定されるものではない。本実施例では、チタン(Ti)膜、窒化チタン(TiN)膜、珪素を含むアルミニウム(Al-Si)膜、チタン(Ti)膜、窒化チタン(TiN)膜を積層して5層構造とし、スパッタ法によって形成したものを用いて、電極又は配線691～695を形成する。

#### 【0242】

なお、アルミニウム(Al)膜において、珪素(Si)を混入させることにより、配線形成時のレジストベークにおけるヒロックの発生を防止することができる。また、Siの代わりに、0.5%程度のCuを混入させても良い。また、TiやTiNでAl-Si層をサンドイッチすることにより、耐ヒロック性がさらに向上する。なお、エッチング時には、窒素を含む酸化珪素等からなる上記ハードマスクを用いるのが望ましい。なお、配線の材料や、形成方法はこれらに限定されるものではなく、前述したゲート電極に用いられる材料を採用しても良い。

#### 【0243】

またこの電極又は配線691～695を、ニッケル、コバルト、鉄のうち少なくとも1種の元素、及び炭素を含むアルミニウム合金膜で形成してもよい。このようなアルミニウム合金膜は、シリコンと接触してもシリコンとアルミニウムの相互拡散が防止できる。またこのようなアルミニウム合金膜は、透明導電膜、例えばITO(Indium Tin Oxide)膜と接触しても酸化還元反応が起こらないため、両者を直接接觸させることができる。さらにこのようなアルミ合金膜は、比抵抗が低く耐熱性にも優れているので、配線材料としては有用である。

#### 【0244】

なお、電極又は配線691、並びに電極又は配線692はnチャネル型TFT611の接続領域634中のシリサイド領域に、電気的に接続されている。電極又は配線692、並びに電極又は配線693はpチャネル型TFT612のソース領域またはドレイン領域642中のシリサイド領域に電気的に接続されている。電極又は配線694、並びに電極又は配線695はnチャネル型TFT613の接続領域654中のシリサイド領域に、電気的に接続されている。さらに電極又は配線695は、nチャネル型TFT613のゲート電極673にも接続されている。nチャネル型TFT613は、乱数ROMのメモリ素子として用いることができる(図16(B)参照)。

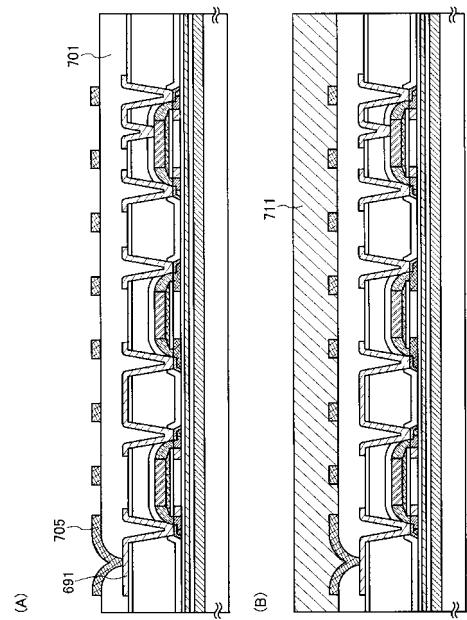

#### 【0245】

次に電極又は配線691～695を覆うように、第2の層間絶縁膜683上に第3の層間絶縁膜701を形成する。第3の層間絶縁膜701は、電極又は配線691が一部露出する様な位置に開口部を有するように形成する。なお第3の層間絶縁膜701は、第1の層間絶縁膜682と同様の材料を用いて形成することが可能である。

#### 【0246】

次に、第3の層間絶縁膜701上にアンテナ705を形成する(図17(A)参照)。アンテナ705は、Ag、Au、Cu、Pd、Cr、Mo、Ti、Ta、W、Al、Fe、Co、Zn、Sn、Niなどの金属、金属化合物を1つまたは複数有する導電材料を用いることができる。そしてアンテナ705は、電極又は配線691と接続されている。なお図17(A)では、アンテナ705が電極又は配線691と直接接続されているが、本発明のIDチップはこの構成に限定されない。例えば別途形成した配線を用いて、アンテナ705と電極又は配線691とを電気的に接続するようにしても良い。

#### 【0247】

アンテナ705は印刷法、フォトリソグラフィ法、蒸着法または液滴吐出法などを用いて形成することができる。本実施例では、アンテナ705が単層の導電膜で形成されているが、複数の導電膜が積層されたアンテナ705を形成することも可能である。例えば、

10

20

30

40

50

Niなどで形成した配線に、Cuを無電解めっきでコーティングして、アンテナ705を形成しても良い。

#### 【0248】

なお液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出して所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。また印刷法にはスクリーン印刷法、オフセット印刷法などが含まれる。印刷法、液滴吐出法を用いることで、露光用のマスクを用いようと、アンテナ705を形成することが可能になる。また、液滴吐出法、印刷法だと、フォトリソグラフィ法と異なり、エッティングにより除去されてしまうような材料の無駄がない。また高価な露光用のマスクを用いなくとも良いので、IDチップの作製に費やされるコストを抑えることができる。

10

#### 【0249】

液滴吐出法または各種印刷法を用いる場合、例えば、CuをAgでコートした導電粒子なども用いることが可能である。なお液滴吐出法を用いてアンテナ705を形成する場合、該アンテナ705の密着性が高まるような処理を、第3の層間絶縁膜701の表面に施すことが望ましい。

#### 【0250】

密着性を高めることができるとする方法として、具体的には、例えば触媒作用により導電膜または絶縁膜の密着性を高めることができる金属または金属化合物を第3の層間絶縁膜701の表面に付着させる方法、形成される導電膜または絶縁膜との密着性が高い有機系の絶縁膜、金属、金属化合物を第3の層間絶縁膜701の表面に付着させる方法、第3の層間絶縁膜701の表面に大気圧下または減圧下においてプラズマ処理を施し、表面改質を行なう方法などが挙げられる。また、上記導電膜または絶縁膜との密着性が高い金属として、チタン、チタン酸化物の他、3d遷移元素であるSc、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Znなどが挙げられる。また金属化合物として、上述した金属の酸化物、窒化物、酸窒化物などが挙げられる。上記有機系の絶縁膜として、例えばポリイミド、シロキサン系樹脂等が挙げられる。

20

#### 【0251】

第3の層間絶縁膜701に付着させる金属または金属化合物が導電性を有する場合、アンテナの正常な動作が妨げられないように、そのシート抵抗を制御する。具体的には、導電性を有する金属または金属化合物の平均の厚さを、例えば1~10nmとなるように制御する、該金属または金属化合物を酸化により部分的に、または全体的に絶縁化すれば良い。或いは、密着性を高めたい領域以外は、付着した金属または金属化合物をエッティングにより選択的に除去しても良い。また金属または金属化合物を、予め基板の全面に付着させのではなく、液滴吐出法、印刷法、ゾル-ゲル法などを用いて特定の領域にのみ選択的に付着させても良い。なお金属または金属化合物は、第3の層間絶縁膜701の表面において完全に連続した膜状である必要はなく、ある程度分散した状態であっても良い。

30

#### 【0252】

そして図17(B)に示すように、アンテナ705を形成した後、アンテナ705を覆うように、第3の層間絶縁膜701上に保護層711を形成する。保護層711は、後に剥離層602をエッティングにより除去する際に、アンテナ705を保護することができる材料を用いる。例えば、水またはアルコール類に可溶なエポキシ系、アクリレート系、シリコン系の樹脂を全面に塗布することで保護層711を形成することができる。

40

#### 【0253】

本実施例では、スピンドルコート法で水溶性樹脂(東亜合成製:VL-WSHL10)を膜厚30μmとなるように塗布し、仮硬化するために2分間の露光を行ったあと、UV光を基板の裏面から2.5分、表面から10分、合計12.5分の露光を行って本硬化させて、保護層711を形成する。なお、複数の有機樹脂を積層する場合、有機樹脂同士では使用している溶媒によって塗布または焼成時に一部溶解してしまったり、密着性が高くなりすぎたりする恐れがある。従って、第3の層間絶縁膜701と保護層711を共に同じ溶媒に可溶な有機樹脂を用いる場合、後の工程において保護層711の除去がスムーズに

50

行なわれるように、第3の層間絶縁膜701を覆うように、無機絶縁膜(窒化珪素膜、酸素を含む窒化珪素膜、窒素を含む酸化珪素膜、窒化アルミニウム膜、または酸素を含む窒化アルミニウム膜、窒素を含む酸化アルミニウム膜)を形成しておくことが好ましい。

#### 【0254】

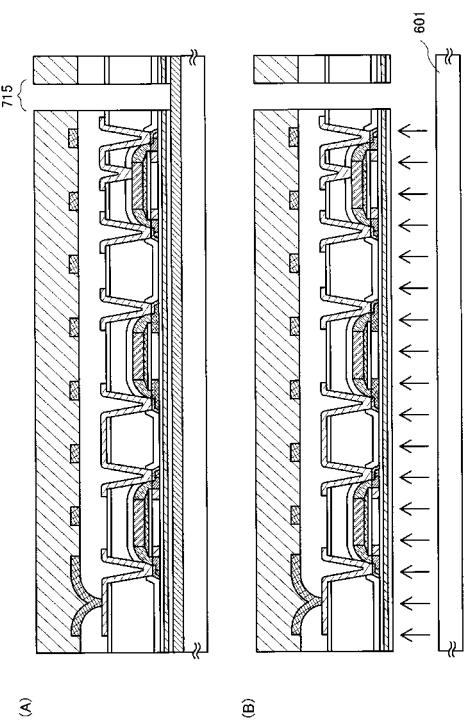

次に図18(A)に示すように、IDチップどうしを分離するために溝715を形成する。溝715は、剥離層602が露出する程度であれば良い。溝715の形成は、ダイシング、スクライビングなどを用いることができる。なお、第1の基板601上に形成されているIDチップを分離する必要がない場合、必ずしも溝715を形成する必要はない。

#### 【0255】

次に図18(B)に示すように、剥離層602をエッティングにより除去する。本実施例では、エッティングガスとしてフッ化ハロゲンを用い、該ガスを溝715から導入する。本実施例では、例えばC<sub>1</sub>F<sub>3</sub>(三フッ化塩素)を用い、温度:350℃、流量:300sccm、気圧:798パスカル(798Pa)、時間:3hの条件で行なう。また、C<sub>1</sub>F<sub>3</sub>ガスに窒素を混ぜたガスを用いても良い。C<sub>1</sub>F<sub>3</sub>等のフッ化ハロゲンを用いることで、剥離層602が選択的にエッティングされ、第1の基板601をTFT611~TFT613から剥離することができる。なおフッ化ハロゲンは、液体であっても液体であってもどちらでも良い。

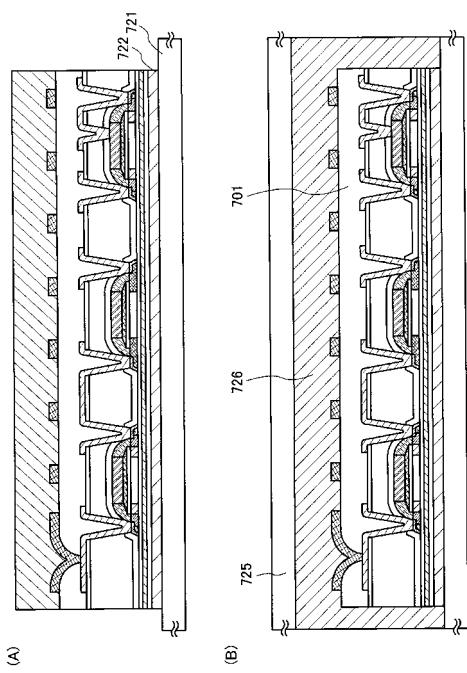

#### 【0256】

次に図19(A)に示すように、剥離されたTFT611~TFT613及びアンテナ705を、接着剤722を用いて第2の基板721に貼り合わせる。接着剤722は、第2の基板721と下地膜603とを貼り合わせることができる材料を用いる。接着剤722は、例えば反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。

#### 【0257】

第2の基板721として、フレキシブルな紙またはプラスチックなどの有機材料を用いることができる。または第2の基板721として、フレキシブル無機材料を用いていても良い。プラスチック基板は、極性基のついたポリノルボルネンからなるARTON(JSR製)を用いることができる。また、ポリエチレンテレフタレート(PET)に代表されるポリエステル、ポリエーテルスルホン(PES)、ポリエチレンナフタレート(PEN)、ポリカーボネット(PC)、ナイロン、ポリエーテルエーテルケトン(PEEK)、ポリスルホン(PSF)、ポリエーテルイミド(PEI)、ポリアリレート(PAR)、ポリブチレンテレフタレート(PBT)、ポリイミド、アクリロニトリルブタジエンスチレン樹脂、ポリ塩化ビニル、ポリプロピレン、ポリ酢酸ビニル、アクリル樹脂などが挙げられる。第2の基板721は集積回路において発生した熱を拡散させるために、2~30W/mK程度の高い熱伝導率を有する方が望ましい。

#### 【0258】

次に図19(B)に示すように、保護層711を除去した後、アンテナ705を覆うように接着剤726を第3の層間絶縁膜701上に塗布し、カバー材725を貼り合わせる。カバー材725は第2の基板721と同様に、フレキシブルな紙またはプラスチックなどの有機材料を用いることができる。接着剤726の厚さは、例えば10~200μmとすれば良い。

#### 【0259】

また接着剤726は、カバー材725と第3の層間絶縁膜701及びアンテナ705とを貼り合わせることができる材料を用いる。接着剤726は、例えば反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。

#### 【0260】

上述した各工程を経て、IDチップが完成する。上記作製方法によって、トータルの膜厚0.3μm以上3μm以下、代表的には2μm程度の飛躍的に薄い集積回路を第2の基板721とカバー材725との間に形成することができる。なお集積回路の厚さは、半導

10

20

30

40

50

体素子自体の厚さのみならず、接着剤722と接着剤726間に形成された各種絶縁膜及び層間絶縁膜の厚さを含めるものとする。またIDチップが有する集積回路の占める面積を、5mm四方(25mm<sup>2</sup>)以下、より望ましくは0.3mm四方(0.09mm<sup>2</sup>)～4mm四方(16mm<sup>2</sup>)程度とすることができる。

#### 【0261】

なお集積回路を、第2の基板721とカバー材725の間のより中央に位置させることで、IDチップの機械的強度を高めることができる。具体的には、第2の基板721とカバー材725の間の距離をdとすると、第2の基板721と、集積回路の厚さ方向における中心との距離が、以下の数1を満たすように、接着剤722、接着剤726の厚さを制御することが望ましい。10

#### 【0262】

##### 【数1】

$$\frac{1}{2}d - 30\mu m < x < \frac{1}{2}d + 30\mu m$$

#### 【0263】

また好ましくは、以下の数2を満たすように、接着剤722、接着剤726の厚さを制御する。

#### 【0264】

##### 【数2】

$$\frac{1}{2}d - 10\mu m < x < \frac{1}{2}d + 10\mu m$$

#### 【0265】

なお図19(B)では、カバー材725を用いる例を示しているが、本発明はこの構成に限定されない。例えば図19(A)に示した工程まで終了としても良い。

#### 【0266】

なお本実施例では、耐熱性の高い第1の基板601と集積回路の間に剥離層を設け、エッチングにより該剥離層を除去することで基板と集積回路とを剥離する方法について示したが、本発明のIDチップの作製方法は、この構成に限定されない。例えば、耐熱性の高い基板と集積回路の間に金属酸化膜を設け、該金属酸化膜を結晶化により脆弱化して集積回路を剥離しても良い。或いは、耐熱性の高い基板と集積回路の間に、水素を含む非晶質半導体膜を用いた剥離層を設け、レーザ光の照射により該剥離層を除去することで基板と集積回路とを剥離しても良い。或いは、集積回路が形成された耐熱性の高い基板を機械的に削除または溶液やガスによるエッチングで除去することで集積回路を基板から切り離しても良い。30

#### 【0267】

またIDチップの可撓性を確保するために、下地膜603に接する接着剤722に有機樹脂を用いる場合、下地膜603として窒化珪素膜または窒素を含む酸化珪素膜を用いることで、有機樹脂からNaなどのアルカリ金属やアルカリ土類金属が半導体膜中に拡散するのを防ぐことができる。40

#### 【0268】

また対象物の表面が曲面を有しており、それにより該曲面貼り合わされたIDチップの第2の基板721が、錐面、柱面など母線の移動によって描かれる曲面を有するように曲がってしまう場合、該母線の方向とTFT611～TFT613のキャリアが移動する方向とを揃えておくことが望ましい。上記構成により、第2の基板721が曲がっても、それによってTFT611～TFT613の特性に影響が出るのを抑えることができる。また、島状の半導体膜が集積回路内において占める面積の割合を、1～30%とすることでも50

、第2の基板721が曲がっても、それによってTFT611～TFT613の特性に影響が出るのをより抑えることができる。

#### 【0269】

なお本実施例では、アンテナを集積回路と同じ基板上に形成している例について説明したが、本発明はこの構成に限定されない。別の基板上に形成したアンテナと集積回路とを、後に貼り合わせることで、電気的に接続するようにしても良い。

#### 【0270】

なお一般的にIDチップで用いられている電波の周波数は、13.56MHz、2.45GHzが多く、該周波数の電波を検波できるようにIDチップを形成することが、汎用性を高める上で非常に重要である。

10

#### 【0271】

また本実施例のIDチップでは、半導体基板を用いて形成されたIDチップよりも電波が遮蔽されにくく、電波の遮蔽により信号が減衰するのを防ぐことができるというメリットを有している。よって、半導体基板を用いずに済むので、IDチップのコストを大幅に低くすることができる。例えば、直径12インチのシリコン基板を用いた場合と、730×920mm<sup>2</sup>のガラス基板を用いた場合とを比較する。前者のシリコン基板の面積は約73000mm<sup>2</sup>であるが、後者のガラス基板の面積は約672000mm<sup>2</sup>であり、ガラス基板はシリコン基板の約9.2倍に相当する。後者のガラス基板の面積は約672000mm<sup>2</sup>では、基板の分断により消費される面積を無視すると、1mm四方のIDチップが約672000個形成できる計算になり、該個数はシリコン基板の約9.2倍の数に相当する。そしてIDチップの量産化を行なうための設備投資は、730×920mm<sup>2</sup>のガラス基板を用いた場合の方が直径12インチのシリコン基板を用いた場合よりも工程数が少なくて済むため、額を3分の1で済ませることができる。さらに本発明では、集積回路を剥離した後、ガラス基板を再び利用できる。よって、破損したガラス基板を補填する、ガラス基板の表面を清浄化する費用を踏まえても、シリコン基板を用いる場合より大幅にコストを抑えることができる。またガラス基板を再利用せずに廃棄していったとしても、730×920mm<sup>2</sup>のガラス基板の値段は、直径12インチのシリコン基板の半分程度で済むので、IDチップのコストを大幅に低くすることができることがわかる。

20

#### 【0272】

従って、730×920mm<sup>2</sup>のガラス基板を用いた場合、直径12インチのシリコン基板を用いた場合よりも、IDチップの値段を約30分の1程度に抑えることができることがわかる。IDチップは、使い捨てを前提とした用途も考えられるので、コストを大幅に低くすることができる本発明のIDチップは上記用途に非常に有用である。

30

#### 【0273】

なお本実施例では、集積回路を剥離して、可撓性を有する基板に貼り合わせる例について説明したが、本発明はこの構成に限定されない。例えばガラス基板のように、集積回路の作製工程における熱処理に耐えうるような、耐熱温度を有している基板を用いる場合、必ずしも集積回路を剥離する必要はない。

#### 【0274】

また、本実施例は、必要であれば実施の形態1～3及び他の実施例のいかなる記載と自由に組み合わせることが可能である。

40

#### 【実施例6】

#### 【0275】

本発明が適用される電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置（カーオーディオコンポ等）、コンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等）、記録媒体を備えた画像再生装置（具体的にはDigital Video Satellite Disc (DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。それらの電子機器の具体例を図20(A)～図20(D)及び図21(A)～図21(D)に示す。

50

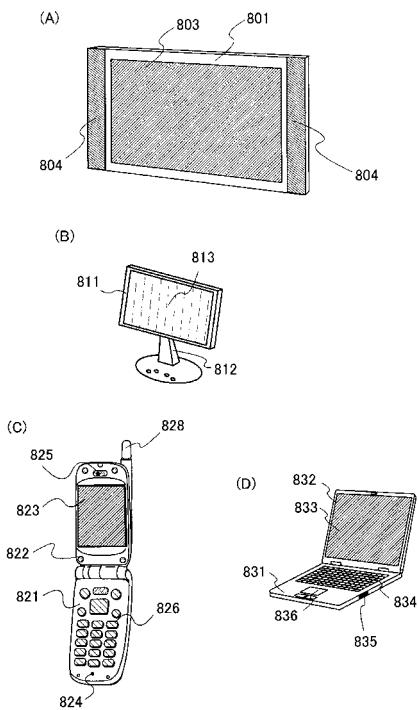

## 【0276】

図20(A)は発光表示装置でありテレビ受像器などがこれに当たる。筐体801、表示部803、スピーカ部804等を含む。本発明は、表示部803及び制御用回路部のTFT等に適用することができる。画素部にはコントラヌスを高めるため、偏光板、または円偏光板を備えるとよい。例えば、封止基板へ1/4板、1/2板、偏光板の順にフィルムを設けるとよい。さらに偏光板上に反射防止膜を設けてもよい。本発明を使用することにより、駆動速度が速く、信頼性のおける発光表示装置を得ることができる。また実施例5により作製されたID Chipを発光表示装置に貼り付けることにより、流通経路などを明確にすることができます。

## 【0277】

10

図20(B)は液晶ディスプレイもしくはOLEDディスプレイであり、筐体811、支持台812、表示部813などによって構成されている。本発明は表示部813及び制御用回路部等のTFTに適用が可能である。本発明を使用することにより、駆動速度が速く、信頼性のおける液晶ディスプレイもしくはOLEDディスプレイを得ることができる。また実施例5により作製されたID Chipを液晶ディスプレイもしくはOLEDディスプレイに貼り付けることにより、流通経路などを明確にすることができます。

## 【0278】

図20(C)は携帯電話であり、本体821、筐体822、表示部823、音声入力部824、音声出力部825、操作キー826、アンテナ828等を含む。本発明は表示部823及び制御用回路部等のTFTに適用することができる。本発明を使用することにより、駆動速度が速く、信頼性のおける携帯電話を得ることができる。また実施例5により作製されたID Chipを携帯電話に貼り付けることにより、流通経路などを明確にすることができます。

20

## 【0279】

図20(D)はノート型パソコンコンピュータであり、本体831、筐体832、表示部833、キーボード834、外部接続ポート835、ポインティングデバイス836等を含む。本発明は、表示部833及び制御用回路部等のTFTに適用することができる。本発明を使用することにより、駆動速度が速く、信頼性のおけるパソコンコンピュータを得ることができる。また実施例5により作製されたID Chipをパソコンコンピュータに貼り付けることにより、流通経路などを明確にすることができます。

30

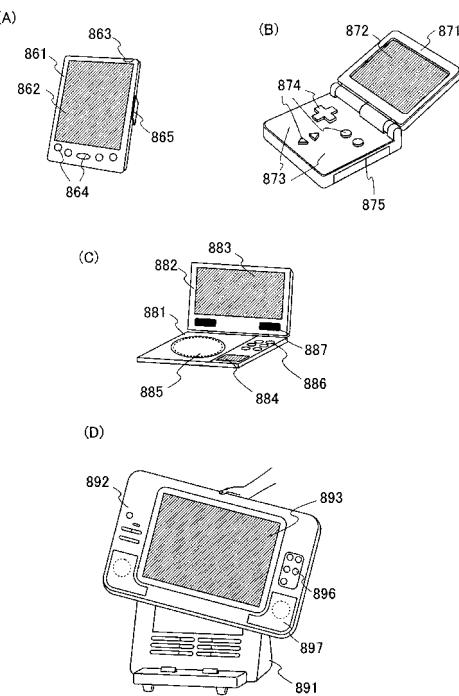

## 【0280】

図21(A)はモバイルコンピュータであり、本体861、表示部862、スイッチ863、操作キー864、赤外線ポート865等を含む。本発明は、表示部862及び制御用回路部等のTFTに適用することができる。本発明を使用することにより、駆動速度が速く、信頼性のおけるモバイルコンピュータを得ることができる。また実施例5により作製されたID Chipをモバイルコンピュータに貼り付けることにより、流通経路などを明確にすることができます。

## 【0281】

図22(B)は携帯型ゲーム機であり、筐体871、表示部872、スピーカ部873、操作キー874、記録媒体挿入部875等を含む。本発明は表示部872及び制御用回路部等のTFTに適用することができる。本発明を使用することにより、駆動速度が速く、信頼性のおける携帯型ゲーム機を得ることができる。また実施例5により作製されたID Chipを携帯型ゲーム機に貼り付けることにより、流通経路などを明確にすることができます。

40

## 【0282】

図22(C)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体881、筐体882、表示部A883、表示部B884、記録媒体(DVD等)読み込み部885、操作キー886、スピーカ部887等を含む。表示部A883は主として画像情報を表示し、表示部B884は主として文字情報を表示する。本発明は表示部A883、表示部B884及び制御用回路部等のTFTに適用することができる。な

50

お、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。本発明を使用することにより、駆動速度が速く、信頼性のにおける画像再生装置を得ることができる。また実施例5により作製されたID Chipを画像再生装置に貼り付けることにより、流通経路などを明確にすることができる。

【0283】

図21(D)は、ワイヤレスでディスプレイのみを持ち運び可能なTVである。筐体892にはバッテリー及び信号受信器が内蔵されており、そのバッテリーで表示部893やスピーカ部897を駆動させる。バッテリーは充電器891で繰り返し充電が可能となっている。また、充電器891は映像信号を送受信することが可能で、その映像信号をディスプレイの信号受信器に送信することができる。筐体892は操作キー896によって制御する。また、図21(D)に示す装置は、操作キー896を操作することによって、筐体892から充電器891に信号を送ることも可能であるため映像音声双方向通信装置とも言える。また、操作キー896を操作することによって、筐体892から充電器891に信号を送り、さらに充電器891が送信できる信号を他の電子機器に受信させることによって、他の電子機器の通信制御も可能であり、汎用遠隔制御装置とも言える。本発明は表示部893及び制御用回路部等のTFTに適用することができる。本発明を使用することにより、駆動速度が速く、信頼性のにおけるTVを得ることができる。また実施例5により作製されたID ChipをTVに貼り付けることにより、流通経路などを明確にすることができる。

【0284】

これらの電子機器に使われる表示装置は、大きさや強度、または使用目的に応じて、ガラス基板だけでなく耐熱性のプラスチック基板を用いることも可能である。それによってよりいっそうの軽量化を図ることができる。

【0285】

なお、本実施例に示した例はごく一例であり、これらの用途に限定するものではないことを付記する。

【0286】

また本実施例は、実施の形態1～3及び他の実施例のいかなる記載とも自由に組み合せて実施することが可能である。

【産業上の利用可能性】

【0287】

本発明は、TFTを有する半導体装置に適用させることができる。本発明のTFTは、シリサイドをエッチングにより消失させることを防ぎ、ソース電極またはドレイン電極とシリサイドの電気的接触を良好にさせることができる。

【0288】

また本発明により作製された半導体装置は、駆動速度が速く、かつ高い信頼性を有することができる。

【図面の簡単な説明】

【0289】

【図1】本発明の半導体装置を示す図。

40

【図2】本発明の半導体装置の作製工程を示す図。

【図3】本発明の半導体装置の作製工程を示す図。

【図4】本発明の半導体装置の作製工程を示す図。

【図5】本発明の半導体装置の作製工程を示す図。

【図6】本発明の半導体装置を示す図。

【図7】本発明の半導体装置の作製工程を示す図。

【図8】本発明の半導体装置の作製工程を示す図。

【図9】本発明の半導体装置の作製工程を示す図。

【図10】本発明の半導体装置の作製工程を示す図。

【図11】本発明のCPUの作製工程を示す図。

50

- 【図12】本発明のCPUの作製工程を示す図。

- 【図13】本発明のCPUの上面図。

- 【図14】本発明のシステムオンパネルを示す図。

- 【図15】本発明のCPUを作製工程を示す図。

- 【図16】本発明のIDチップの作製工程を示す図。

- 【図17】本発明のIDチップの作製工程を示す図。

- 【図18】本発明のIDチップの作製工程を示す図。

- 【図19】本発明のIDチップの作製工程を示す図。

- 【図20】本発明が適用される電子機器の例を示す図。

- 【図21】本発明が適用される電子機器の例を示す図。

- 【図22】一導電性を付与する元素が添加された領域と添加されない領域のシート抵抗の比較を表す図。

- 【図23】一導電性を付与する元素が添加された領域と添加されない領域のシート抵抗の比較を表す図。

- 【図24】一導電性を付与する元素が添加された領域と添加されない領域のシート抵抗の比較を表す図。

- 【図25】本発明の半導体装置の作製工程を示す図。

- 【図26】本発明の半導体装置の作製工程を示す図。

- 【符号の説明】

- |                    |    |

|--------------------|----|

| 【0290】             | 20 |

| 101 基板             |    |

| 102 下地膜            |    |

| 103 チャネル形成領域       |    |

| 104 低濃度不純物領域       |    |

| 105 ソース領域またはドレイン領域 |    |

| 106 シリサイド領域        |    |

| 107 接続領域           |    |

| 108 ゲート絶縁膜         |    |

| 111 ゲート電極          |    |

| 112 サイドウォール        | 30 |

| 113 層間絶縁膜          |    |

| 115 ソース電極またはドレイン電極 |    |

| 117 島状半導体膜         |    |

| 121 半導体膜           |    |

| 122 結晶性半導体膜        |    |

| 125 線状ビーム          |    |

| 127 レジスト           |    |

| 129 金属膜            |    |

| 131 コンタクトホール       |    |

| 133 導電膜            | 40 |

| 151 サイドウォール        |    |

| 152 金属膜            |    |

| 153 シリサイド領域        |    |

| 155 レジスト           |    |

| 161 チャネル形成領域       |    |

| 162 ソース領域またはドレイン領域 |    |

| 163 接続領域           |    |

| 165 チャネル形成領域       |    |

| 166 低濃度不純物領域       |    |

| 167 ソース領域またはドレイン領域 | 50 |

|         |                |    |

|---------|----------------|----|

| 1 6 8   | 接続領域           |    |

| 1 7 1   | 層間絶縁膜          |    |

| 1 7 3   | ソース電極またはドレイン電極 |    |

| 2 0 1   | 基板             |    |

| 2 0 2   | 下地膜            |    |

| 2 0 3   | チャネル形成領域       |    |

| 2 0 4   | 低濃度不純物領域       |    |

| 2 0 5   | ソース領域またはドレイン領域 |    |

| 2 0 6   | シリサイド領域        |    |

| 2 0 7   | 接続領域           | 10 |

| 2 0 8   | ゲート絶縁膜         |    |

| 2 0 9   | 下層ゲート電極        |    |

| 2 1 1   | 上層ゲート電極        |    |

| 2 1 2   | サイドウォール        |    |

| 2 1 3   | 層間絶縁膜          |    |

| 2 1 5   | ソース電極またはドレイン電極 |    |

| 2 1 7   | 島状半導体膜         |    |

| 3 0 1   | 基板             |    |

| 3 0 2   | 下地膜            |    |

| 3 0 3   | 島状半導体膜         | 20 |

| 3 0 4   | 島状半導体膜         |    |

| 3 0 6   | 絶縁膜            |    |

| 3 0 8   | ゲート絶縁膜         |    |

| 3 0 9   | ゲート絶縁膜         |    |

| 3 1 1   | 導電膜            |    |

| 3 1 2   | 導電膜            |    |

| 3 1 4   | ゲート電極          |    |

| 3 1 4 a | 下層ゲート電極        |    |

| 3 1 4 b | 上層ゲート電極        |    |

| 3 1 5   | ゲート電極          | 30 |

| 3 1 5 b | 上層ゲート電極        |    |

| 3 1 5 a | 下層ゲート電極        |    |

| 3 1 8   | レジスト           |    |

| 3 1 9   | レジスト           |    |

| 3 2 1   | チャネル形成領域       |    |

| 3 2 2   | 低濃度不純物領域       |    |

| 3 2 3   | ソース領域またはドレイン領域 |    |

| 3 2 4   | 接続領域           |    |

| 3 2 7   | レジスト           |    |

| 3 2 8   | チャネル形成領域       | 40 |

| 3 2 9   | ソース領域またはドレイン領域 |    |

| 3 3 1   | 絶縁膜            |    |

| 3 3 3   | サイドウォール        |    |

| 3 3 4   | サイドウォール        |    |

| 3 3 5   | 金属膜            |    |

| 3 4 1   | シリサイド領域        |    |

| 3 4 2   | シリサイド領域        |    |

| 3 4 4   | 層間絶縁膜          |    |

| 3 4 3   | 層間絶縁膜          |    |

| 3 4 5   | コンタクトホール       | 50 |

|       |                |    |

|-------|----------------|----|

| 3 4 6 | コンタクトホール       |    |

| 3 4 7 | コンタクトホール       |    |

| 3 4 8 | コンタクトホール       |    |

| 3 5 1 | ソース電極またはドレイン電極 |    |

| 3 5 2 | ソース電極またはドレイン電極 |    |

| 3 5 3 | ソース電極またはドレイン電極 |    |

| 3 5 6 | n チャネル型 TFT    |    |

| 3 5 7 | p チャネル型 TFT    |    |

| 3 5 8 | C MOS 回路       |    |

| 3 6 1 | レジスト           | 10 |

| 3 6 2 | シリサイド領域        |    |

| 3 6 3 | チャネル形成領域       |    |

| 3 6 4 | ソース領域またはドレイン領域 |    |

| 3 6 5 | 接続領域           |    |

| 3 6 7 | p チャネル型 TFT    |    |

| 3 6 8 | C MOS 回路       |    |

| 4 0 1 | 基板             |    |

| 4 0 2 | 下地膜            |    |

| 4 0 3 | 非晶質半導体膜        |    |

| 4 0 4 | 膜              | 20 |

| 4 0 5 | レーザ光           |    |

| 4 0 6 | 結晶性半導体膜        |    |

| 4 0 7 | 島状半導体膜         |    |

| 4 0 8 | 島状半導体膜         |    |

| 4 0 9 | 島状半導体膜         |    |

| 4 1 0 | 島状半導体膜         |    |

| 4 1 1 | ゲート絶縁膜         |    |

| 4 1 2 | ゲート絶縁膜         |    |

| 4 1 3 | ゲート絶縁膜         |    |

| 4 1 4 | ゲート絶縁膜         | 30 |

| 4 2 1 | チャネル形成領域       |    |

| 4 2 2 | 低濃度不純物領域       |    |

| 4 2 3 | ソース領域またはドレイン領域 |    |

| 4 2 4 | 接続領域           |    |

| 4 2 5 | シリサイド領域        |    |

| 4 3 1 | チャネル形成領域       |    |

| 4 3 2 | ソース領域またはドレイン領域 |    |

| 4 3 5 | シリサイド領域        |    |

| 4 4 1 | チャネル形成領域       |    |

| 4 4 2 | 低濃度不純物領域       | 40 |

| 4 4 3 | ソース領域またはドレイン領域 |    |

| 4 4 4 | 接続領域           |    |

| 4 4 5 | シリサイド領域        |    |

| 4 5 1 | チャネル形成領域       |    |

| 4 5 2 | ソース領域またはドレイン領域 |    |

| 4 5 5 | シリサイド領域        |    |

| 4 6 1 | n チャネル型 TFT    |    |

| 4 6 2 | p チャネル型 TFT    |    |

| 4 6 3 | n チャネル型 TFT    |    |

| 4 6 4 | p チャネル型 TFT    | 50 |

|         |               |    |

|---------|---------------|----|

| 4 7 1   | ゲート電極         |    |

| 4 7 1 a | 下層ゲート電極       |    |

| 4 7 1 b | 上層ゲート電極       |    |

| 4 7 2   | ゲート電極         |    |

| 4 7 2 a | 下層ゲート電極       | 10 |

| 4 7 2 b | 上層ゲート電極       |    |

| 4 7 3   | ゲート電極         |    |

| 4 7 3 a | 下層ゲート電極       |    |

| 4 7 3 b | 上層ゲート電極       |    |

| 4 7 4   | ゲート電極         |    |

| 4 7 4 a | 下層ゲート電極       |    |

| 4 7 4 b | 上層ゲート電極       |    |

| 4 7 6   | サイドウォール       |    |

| 4 7 7   | サイドウォール       |    |

| 4 7 8   | サイドウォール       |    |

| 4 7 9   | サイドウォール       |    |

| 4 8 1   | 層間絶縁膜         |    |

| 4 8 2   | 層間絶縁膜         |    |

| 4 9 1   | 電極又は配線        | 20 |

| 4 9 2   | 電極又は配線        |    |

| 4 9 3   | 電極又は配線        |    |

| 4 9 4   | 電極又は配線        |    |

| 4 9 5   | 電極又は配線        |    |

| 4 9 6   | 電極又は配線        |    |

| 4 9 7   | 電極又は配線        |    |

| 4 9 8   | 電極又は配線        |    |

| 5 0 0   | 基板            |    |

| 5 0 1   | 演算回路          |    |

| 5 0 2   | 演算回路用制御部      |    |

| 5 0 3   | 命令解析部         | 30 |

| 5 0 4   | 割り込み制御部       |    |

| 5 0 5   | タイミング制御部      |    |

| 5 0 6   | レジスタ          |    |

| 5 0 7   | レジスタ制御部       |    |

| 5 0 8   | バスインターフェース    |    |

| 5 0 9   | R O M         |    |

| 5 2 0   | R O Mインターフェース |    |

| 5 2 1   | C L K 1       |    |

| 5 2 2   | C L K 2       |    |

| 5 3 0   | 基板            | 40 |

| 5 3 1   | 画素部           |    |

| 5 3 2   | 走査線駆動回路       |    |

| 5 3 3   | 信号線駆動回路       |    |

| 5 3 4   | C P U         |    |

| 5 3 5   | コントロール回路      |    |

| 5 5 0   | 基板            |    |

| 5 5 1   | 薄膜トランジスタアレイ   |    |

| 5 5 2   | 電極            |    |

| 5 5 3   | 配線            |    |

| 5 5 4   | 接続端子          | 50 |

|         |                |    |

|---------|----------------|----|

| 5 5 5   | 樹脂             |    |

| 5 5 7   | プリント基板         |    |

| 5 5 8   | 異方性導電膜         |    |

| 5 6 0   | 基板             |    |

| 5 6 4   | バンプ            |    |

| 5 6 5   | プラスチック         |    |

| 5 6 7   | F P C          |    |

| 5 6 8   | ワイヤ            |    |

| 6 0 1   | 基板             |    |

| 6 0 2   | 剥離層            | 10 |

| 6 0 3   | 下地膜            |    |

| 6 0 3 a | 下層下地膜          |    |

| 6 0 3 b | 中層下地膜          |    |

| 6 0 3 c | 上層下地膜          |    |

| 6 1 1   | T F T          |    |

| 6 1 2   | T F T          |    |

| 6 1 3   | T F T          |    |

| 6 2 1   | 島状半導体膜         |    |

| 6 2 2   | 島状半導体膜         |    |

| 6 2 3   | 島状半導体膜         | 20 |

| 6 3 1   | チャネル形成領域       |    |

| 6 3 2   | 低濃度不純物領域       |    |

| 6 3 3   | ソース領域またはドレイン領域 |    |

| 6 3 4   | 接続領域           |    |

| 6 3 5   | シリサイド領域        |    |

| 6 4 1   | チャネル形成領域       |    |

| 6 4 2   | ソース領域またはドレイン領域 |    |

| 6 4 5   | シリサイド領域        |    |

| 6 5 1   | チャネル形成領域       |    |

| 6 5 2   | 低濃度不純物領域       | 30 |

| 6 5 3   | ソース領域またはドレイン領域 |    |

| 6 5 4   | 接続領域           |    |

| 6 5 5   | シリサイド領域        |    |

| 6 6 1   | ゲート絶縁膜         |    |

| 6 6 2   | ゲート絶縁膜         |    |

| 6 6 3   | ゲート絶縁膜         |    |

| 6 6 5   | サイドウォール        |    |

| 6 6 6   | サイドウォール        |    |

| 6 6 7   | サイドウォール        |    |

| 6 7 1   | ゲート電極          | 40 |

| 6 7 1 a | 下層ゲート電極        |    |

| 6 7 1 b | 上層ゲート電極        |    |

| 6 7 2   | ゲート電極          |    |

| 6 7 2 a | 下層ゲート電極        |    |

| 6 7 2 b | 上層ゲート電極        |    |

| 6 7 3   | ゲート電極          |    |

| 6 7 3 a | 下層ゲート電極        |    |

| 6 7 3 b | 上層ゲート電極        |    |

| 6 8 1   | パッシベーション膜      |    |

| 6 8 2   | 層間絶縁膜          | 50 |

|       |             |    |

|-------|-------------|----|

| 6 8 3 | 層間絶縁膜       |    |

| 6 9 1 | 電極又は配線      |    |

| 6 9 2 | 電極又は配線      |    |

| 6 9 3 | 電極又は配線      |    |

| 6 9 4 | 電極又は配線      |    |

| 6 9 5 | 電極又は配線      |    |

| 7 0 1 | 層間絶縁膜       |    |

| 7 0 5 | アンテナ        |    |

| 7 1 1 | 保護層         |    |

| 7 1 5 | 溝           | 10 |

| 7 2 1 | 基板          |    |

| 7 2 2 | 接着剤         |    |

| 7 2 5 | カバー材        |    |

| 7 2 6 | 接着剤         |    |

| 8 0 1 | 筐体          |    |

| 8 0 3 | 表示部         |    |

| 8 0 4 | スピーカ部       |    |

| 8 1 1 | 筐体          |    |

| 8 1 2 | 支持台         |    |

| 8 1 3 | 表示部         | 20 |

| 8 2 1 | 本体          |    |

| 8 2 2 | 筐体          |    |

| 8 2 3 | 表示部         |    |

| 8 2 4 | 音声入力部       |    |

| 8 2 5 | 音声出力部       |    |

| 8 2 6 | 操作キー        |    |

| 8 2 8 | アンテナ        |    |

| 8 3 1 | 本体          |    |

| 8 3 2 | 筐体          |    |

| 8 3 3 | 表示部         | 30 |

| 8 3 4 | キーボード       |    |

| 8 3 5 | 外部接続ポート     |    |

| 8 3 6 | ポインティングデバイス |    |

| 8 6 1 | 本体          |    |

| 8 6 2 | 表示部         |    |

| 8 6 3 | スイッチ        |    |

| 8 6 4 | 操作キー        |    |

| 8 6 5 | 赤外線ポート      |    |

| 8 7 1 | 筐体          |    |

| 8 7 2 | 表示部         | 40 |

| 8 7 3 | スピーカ部       |    |

| 8 7 4 | 操作キー        |    |

| 8 7 5 | 記録媒体挿入部     |    |

| 8 8 1 | 本体          |    |

| 8 8 2 | 筐体          |    |

| 8 8 3 | 表示部 A       |    |

| 8 8 4 | 表示部 B       |    |

| 8 8 5 | 記録媒体読み込み部   |    |

| 8 8 6 | 操作キー        |    |

| 8 8 7 | スピーカ部       | 50 |

- 8 9 1 充電器

8 9 2 筐体

8 9 3 表示部

8 9 6 操作キー

8 9 7 スピーカ部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

---

フロントページの続き

(51)Int.Cl.

F I

H 01L 29/50

M

審査官 井上 弘亘

(56)参考文献 特開平11-195789 (JP, A)

特開平11-214696 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01L 29 / 786

H 01L 21 / 28

H 01L 21 / 336

H 01L 29 / 417