(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7299711号**

**(P7299711)**

(45)発行日 令和5年6月28日(2023.6.28)

(24)登録日 令和5年6月20日(2023.6.20)

|                         |               |

|-------------------------|---------------|

| (51)国際特許分類              | F I           |

| H 04 N 25/617 (2023.01) | H 04 N 25/617 |

| H 04 N 23/54 (2023.01)  | H 04 N 23/54  |

| H 04 N 25/76 (2023.01)  | H 04 N 25/76  |

| H 04 N 25/779 (2023.01) | H 04 N 25/779 |

| G 02 B 7/02 (2021.01)   | G 02 B 7/02 Z |

請求項の数 17 (全29頁) 最終頁に続く

|          |                                  |          |                                            |

|----------|----------------------------------|----------|--------------------------------------------|

| (21)出願番号 | 特願2019-14424(P2019-14424)        | (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22)出願日  | 平成31年1月30日(2019.1.30)            | (74)代理人  | 100094112<br>弁理士 岡部 譲                      |

| (65)公開番号 | 特開2020-123824(P2020-123824<br>A) | (74)代理人  | 100101498<br>弁理士 越智 隆夫                     |

| (43)公開日  | 令和2年8月13日(2020.8.13)             | (74)代理人  | 100106183<br>弁理士 吉澤 弘司                     |

| 審査請求日    | 令和4年1月27日(2022.1.27)             | (74)代理人  | 100136799<br>弁理士 本田 亜希                     |

|          |                                  | (72)発明者  | 落合 慧<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内     |

|          |                                  | 審査官      | 鈴木 肇                                       |

最終頁に続く

(54)【発明の名称】 光電変換装置及びその駆動方法

**(57)【特許請求の範囲】****【請求項1】**

光電変換部を各々が含む複数の画素が複数の行及び複数の列に渡って配された画素領域と、

前記複数の画素に制御信号を供給する画素制御部と、を有し、

前記画素領域は、第1の読み出し領域と、第2の読み出し領域と、第3の読み出し領域と、第4の読み出し領域と、を有し、

前記第1の読み出し領域に属する第1の画素と前記第2の読み出し領域に属する第2の画素とは、同じ行であって、かつ、互いに異なる列に配され、

前記第3の読み出し領域に属する第3の画素と前記第4の読み出し領域に属する第4の画素とは、同じ列であって、かつ、互いに異なる行に配され、

前記第3の画素が属する行と前記第4の画素が属する行との間に、前記第1の画素及び前記第2の画素が属する行が配され、

前記画素制御部は、第1の期間において前記第1の画素の画素信号と前記第2の画素の画素信号とを読み出す動作を個別に並列して行い、前記第1の期間とは異なる第2の期間において前記第3の画素の画素信号と前記第4の画素の画素信号とを読み出す動作を個別に並列して行うように構成されている

ことを特徴とする光電変換装置。

**【請求項2】**

前記複数の行の各々に少なくとも1つが配されるように、それぞれが対応する行の前記

画素に接続された複数の第1の制御線と、

前記複数の列の各々に少なくとも1つが配されるように、それぞれが対応する列の前記画素に接続された複数の第2の制御線と、

前記複数の列の各々に少なくとも1つが配され、前記画素制御部から前記第1の制御線を介して供給される前記制御信号に応じて、それぞれに対応する列の前記画素からの信号を出力する複数の第1の出力線と、

前記複数の行の各々に少なくとも1つが配され、前記画素制御部から前記第2の制御線を介して供給される前記制御信号に応じて、それぞれに対応する行の前記画素からの信号を出力する複数の第2の出力線と、を更に有する

ことを特徴とする請求項1記載の光電変換装置。

10

#### 【請求項3】

前記画素制御部は、前記第1の画素の画素信号と前記第2の画素の画素信号とを、各々に対応する列の前記第1の出力線を介してそれぞれ読み出し、前記第3の画素の画素信号と前記第4の画素の画素信号とを、各々に対応する行の前記第2の出力線を介してそれぞれ読み出す動作を行うように構成されている

ことを特徴とする請求項2記載の光電変換装置。

#### 【請求項4】

前記複数の行の各々に少なくとも1つが配されるように、それぞれが対応する行の前記画素に接続された複数の第1の制御線と、

前記複数の行の各々に少なくとも1つが配されるように、それぞれが対応する行の前記画素に接続された複数の第2の制御線と、

前記複数の列の各々に少なくとも1つが配され、前記画素制御部から前記第1の制御線を介して供給される前記制御信号に応じて、それぞれに対応する列の前記画素からの信号を出力する複数の第1の出力線と、

前記複数の列の各々に少なくとも1つが配され、前記画素制御部から前記第2の制御線を介して供給される前記制御信号に応じて、それぞれに対応する列の前記画素からの信号を出力する複数の第2の出力線と、を更に有する

ことを特徴とする請求項1記載の光電変換装置。

20

#### 【請求項5】

前記画素制御部は、前記第1の画素の画素信号と前記第2の画素の画素信号とを、各々に対応する列の前記第1の出力線を介してそれぞれ読み出し、前記第3の画素の画素信号を対応する列の前記第1の出力線を介して読み出し、前記第4の画素の画素信号を対応する列の前記第2の出力線を介して読み出す動作を行うように構成されている

ことを特徴とする請求項4記載の光電変換装置。

30

#### 【請求項6】

前記複数の第1の出力線及び前記複数の第2の出力線に接続された読み出し回路を更に有する

ことを特徴とする請求項2乃至5のいずれか1項に記載の光電変換装置。

#### 【請求項7】

前記読み出し回路は、A/D変換部を有する

40

ことを特徴とする請求項6記載の光電変換装置。

#### 【請求項8】

前記読み出し回路は、前記複数の第1の出力線に接続された第1の読み出し回路と、前記複数の第2の出力線に接続された第2の読み出し回路と、を有する

ことを特徴とする請求項6又は7記載の光電変換装置。

#### 【請求項9】

前記複数の画素の各々は、

前記光電変換部で生成された電荷に基づく信号を増幅する増幅部と、

前記第1の制御線に供給される前記制御信号に応じて前記増幅部で増幅された信号を前記第1の出力線に出力する第1の選択トランジスタと、

50

前記第2の制御線に供給される前記制御信号に応じて前記増幅部で増幅された信号を前記第2の出力線に出力する第2の選択トランジスタと、を有することを特徴とする請求項2乃至8のいずれか1項に記載の光電変換装置。

**【請求項10】**

前記第1の読み出し領域及び前記第2の読み出し領域は、第1の方向の視差を検出するための第1焦点検出領域対を構成し、

前記第3の読み出し領域及び前記第4の読み出し領域は、前記第1の方向と交差する第2の方向の視差を検出するための第2焦点検出領域対を構成することを特徴とする請求項1乃至9のいずれか1項に記載の光電変換装置。

**【請求項11】**

前記第1の読み出し領域、前記第2の読み出し領域、前記第3の読み出し領域及び前記第4の読み出し領域の各々は、行及び列が連続する複数の前記画素からなるブロックによって構成されている

ことを特徴とする請求項1乃至10のいずれか1項に記載の光電変換装置。

**【請求項12】**

光電変換部を各々が含む複数の画素が複数の行及び複数の列に渡って配された画素領域を有し、前記画素領域が、第1の読み出し領域と、第2の読み出し領域と、第3の読み出し領域と、第4の読み出し領域と、を有し、前記第1の読み出し領域に属する第1の画素と前記第2の読み出し領域に属する第2の画素とが、同じ行であって、かつ、互いに異なる列に配され、前記第3の読み出し領域に属する第3の画素と前記第4の読み出し領域に属する第4の画素とが、同じ列であって、かつ、互いに異なる行に配され、前記第3の画素が属する行と前記第4の画素が属する行との間に、前記第1の画素及び前記第2の画素が属する行が配された光電変換装置の駆動方法であって、

第1の期間において、前記第1の画素の画素信号と前記第2の画素の画素信号とを個別に並列して読み出し、

前記第1の期間とは異なる第2の期間において、前記第3の読み出し領域に属する画素の画素信号と前記第4の読み出し領域に属する画素の画素信号とを個別に並列して読み出すことを特徴とする光電変換装置の駆動方法。

**【請求項13】**

前記光電変換装置は、前記複数の行の各々に少なくとも1つが配されるように、それぞれが対応する行の前記画素に接続された複数の第1の制御線と、前記複数の列の各々に配され、それぞれに対応する列の前記画素からの信号を出力する複数の第1の出力線と、を更に有し、

前記第1の制御線を介して供給する制御信号により前記第1の画素及び前記第2の画素を駆動し、前記第1の画素の画素信号と前記第2の画素の画素信号とを、前記複数の第1の出力線に個別に並列して読み出す

ことを特徴とする請求項12記載の光電変換装置の駆動方法。

**【請求項14】**

前記光電変換装置は、前記複数の列の各々に少なくとも1つが配されるように、それぞれが対応する列の前記画素に接続された複数の第2の制御線と、前記複数の行の各々に配され、それぞれに対応する行の前記画素からの信号を出力する複数の第2の出力線と、を更に有し、

前記第2の制御線を介して供給する制御信号により、前記第3の画素及び前記第4の画素を駆動し、前記第3の画素の画素信号と前記第4の画素の画素信号とを、各々に対応する行の前記第2の出力線に個別に並列して読み出す

ことを特徴とする請求項12又は13記載の光電変換装置の駆動方法。

**【請求項15】**

前記光電変換装置は、前記複数の行の各々に少なくとも1つが配されるように、それぞれが対応する行の前記画素に接続された複数の第2の制御線と、前記複数の列の各々に配され、それぞれに対応する列の前記画素からの信号を出力する複数の第2の出力線と、を

10

20

30

40

50

更に有し、

前記第2の制御線を介して供給する制御信号により前記第3の画素及び前記第4の画素を駆動し、前記第3の画素の画素信号を対応する列の前記第1の出力線に、前記第4の画素の画素信号を対応する列の前記第2の出力線に、個別に並列して読み出す

ことを特徴とする請求項1\_3記載の光電変換装置の駆動方法。

#### 【請求項16】

請求項1乃至1\_1のいずれか1項に記載の光電変換装置と、

被写体の光学像を画像信号として出力する固体撮像装置と、

前記光電変換装置の出力信号に基づき、前記被写体までの距離を算出する演算部と、

前記演算部で算出された前記距離に基づき、前記被写体の前記光学像が前記固体撮像装置の撮像面に合焦するように光学系を制御する制御信号を出力する制御部と

を有することを特徴とする撮像システム。

#### 【請求項17】

移動体であって、

請求項1乃至1\_1のいずれか1項に記載の光電変換装置と、

前記光電変換装置からの信号に基づく視差画像から、対象物までの距離情報を取得する距離情報取得手段と、

前記距離情報に基づいて前記移動体を制御する制御手段と

を有することを特徴とする移動体。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、光電変換装置及びその駆動方法に関する。

##### 【背景技術】

##### 【0002】

複数の光電変換素子を2次元に配列した光電変換装置は、デジタルカメラの撮像素子や測距、マシンビジョン、画像認識のためのセンシング素子として広く使用されている。高機能化のために、光電変換装置には多様な読み出し方法が適用されている。その1つとして、一対の光電変換素子群から得られた像データを利用する提案がされている。特許文献1には、エリアセンサに設けられた一対の光電変換素子群から得られた像データの相關演算結果を用いて位相差検出型のオートフォーカスを行う固体撮像装置が記載されている。

##### 【先行技術文献】

##### 【特許文献】

##### 【0003】

##### 【文献】特開2000-258682号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

エリアセンサからの像データの読み出し動作中に電源の変動等が生じると、ランダムな縞状のパターンノイズが像データに重畳することがある。一対の光電変換素子群から得られた像データを利用する場合、両者に異なる量のノイズが重畳されると信号処理の精度が低下する可能性がある。

##### 【0005】

例えば、位相差検出型のオートフォーカスセンサは、基準部と参照部から出力される2つの像データの相關演算を行い、位相ずれ量を算出して、三角測距の原理を用いることで被写体までの距離を測定する。そのため、これら2つの像データに異なるパターンノイズが重畳されると、相關演算の結果が不確かなものになり、結果としてオートフォーカスの合焦精度が低下することがあった。

##### 【0006】

10

20

30

40

50

本発明の目的は、対をなす像データに重畳するパターンノイズの影響を抑制しうる光電変換装置及びその駆動方法を提供することにある。

**【課題を解決するための手段】**

**【0007】**

本発明の一観点によれば、光電変換部を各々が含む複数の画素が複数の行及び複数の列に渡って配された画素領域と、前記複数の画素に制御信号を供給する画素制御部と、を有し、前記画素領域は、第1の読み出し領域と、第2の読み出し領域と、第3の読み出し領域と、第4の読み出し領域と、を有し、前記第1の読み出し領域に属する第1の画素と前記第2の読み出し領域に属する第2の画素とは、同じ行であって、かつ、互いに異なる列に配され、前記第3の読み出し領域に属する第3の画素と前記第4の読み出し領域に属する第4の画素とは、同じ列であって、かつ、互いに異なる行に配され、前記第3の画素が属する行と前記第4の画素が属する行との間に、前記第1の画素及び前記第2の画素が属する行が配され、前記画素制御部は、第1の期間において前記第1の画素の画素信号と前記第2の画素の画素信号とを読み出す動作を個別に並列して行い、前記第1の期間とは異なる第2の期間において前記第3の画素の画素信号と前記第4の画素の画素信号とを読み出す動作を個別に並列して行うように構成されている光電変換装置が提供される。10

**【0008】**

また、本発明の更に他の一観点によれば、光電変換部を各々が含む複数の画素が複数の行及び複数の列に渡って配された画素領域と、前記複数の行の各々に少なくとも1つが配されるように、それぞれが対応する行の前記画素に接続された複数の第1の制御線と、前記複数の列の各々に少なくとも1つが配されるように、それぞれが対応する列の前記画素に接続された複数の第2の制御線と、前記複数の列の各々に配され、前記画素制御部から前記第1の制御線を介して供給される前記制御信号に応じて、それぞれに対応する列の前記画素からの信号を出力する複数の第1の出力線と、前記複数の行の各々に配され、前記画素制御部から前記第2の制御線を介して供給される前記制御信号に応じて、それぞれに対応する行の前記画素からの信号を出力する複数の第2の出力線と、前記複数の第1の制御線及び前記複数の第2の制御線に接続され、前記複数の第1の制御線及び前記複数の第2の制御線に前記画素を制御する制御信号を供給する画素制御部と、を有し、前記画素領域は、第1の読み出し領域と、第2の読み出し領域と、第3の読み出し領域と、第4の読み出し領域と、を有し、前記第1の読み出し領域に属する第1の画素と前記第2の読み出し領域に属する第2の画素とは、同じ行であって、かつ、互いに異なる列に配され、前記第3の読み出し領域に属する第3の画素と前記第4の読み出し領域に属する第4の画素とは、同じ列であって、かつ、互いに異なる行に配され、前記第3の画素が属する行と前記第4の画素が属する行との間に、前記第1の画素及び前記第2の画素が属する行が配されている光電変換装置が提供される。20

**【0009】**

また、本発明の更に他の一観点によれば、光電変換部を各々が含む複数の画素が複数の行及び複数の列に渡って配された画素領域を有し、前記画素領域が、第1の読み出し領域と、第2の読み出し領域と、第3の読み出し領域と、第4の読み出し領域と、を有し、前記第1の読み出し領域に属する第1の画素と前記第2の読み出し領域に属する第2の画素とが、同じ行であって、かつ、互いに異なる列に配され、前記第3の読み出し領域に属する第3の画素と前記第4の読み出し領域に属する第4の画素とが、同じ列であって、かつ、互いに異なる行に配され、前記第3の画素が属する行と前記第4の画素が属する行との間に、前記第1の画素及び前記第2の画素が属する行が配された光電変換装置の駆動方法であって、第1の期間において、前記第1の画素の画素信号と前記第2の画素の画素信号とを個別に並列して読み出し、前記第1の期間とは異なる第2の期間において、前記第3の読み出し領域に属する画素の画素信号と前記第4の読み出し領域に属する画素の画素信号とを個別に並列して読み出す光電変換装置の駆動方法が提供される。30

**【発明の効果】**

**【0010】**

50

本発明によれば、対をなす像データに重畳するパターンノイズの影響を抑制し、オートフォーカスの合焦精度を向上することができる。

**【図面の簡単な説明】**

**【0011】**

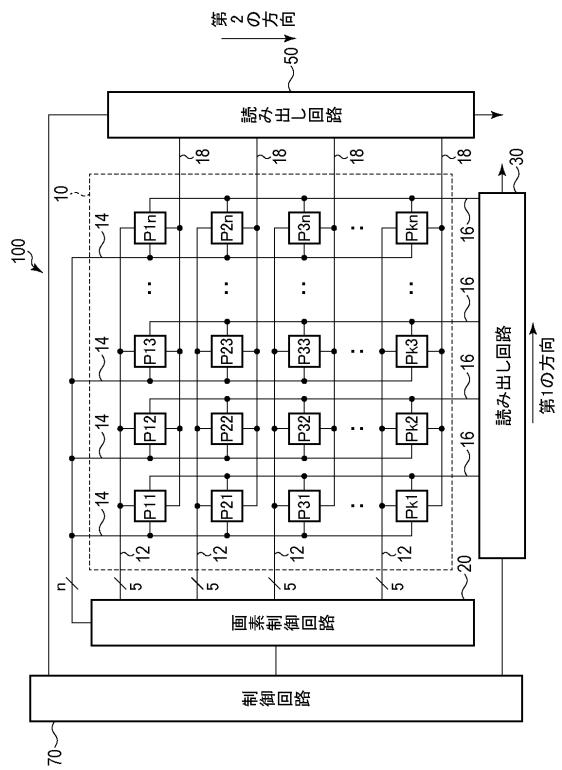

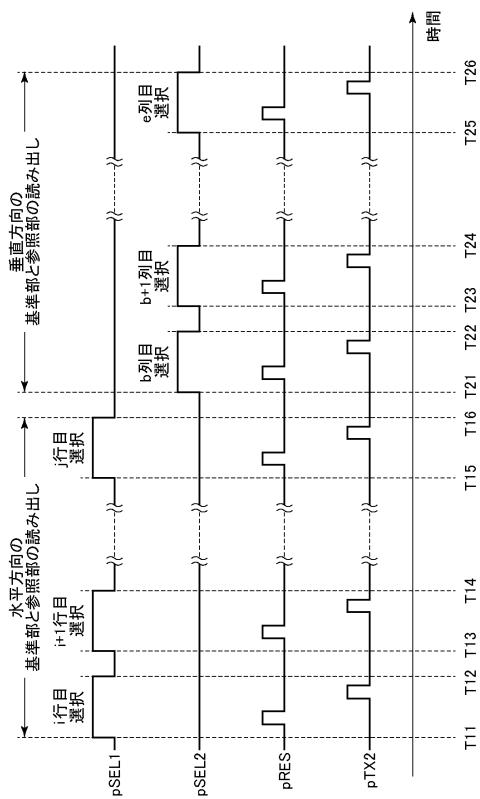

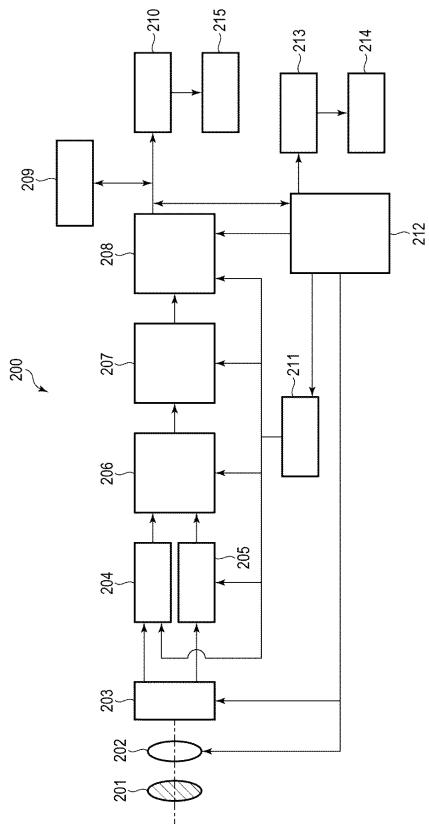

【図1】本発明の第1実施形態による光電変換装置の概略構成を示す図である。

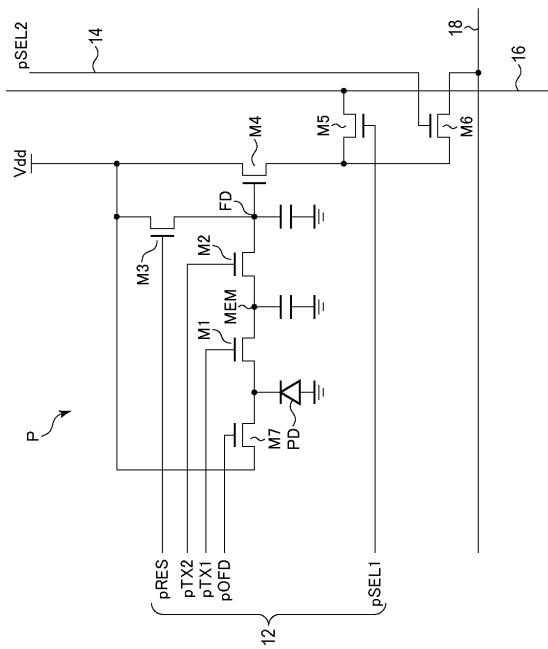

【図2】本発明の第1実施形態による光電変換装置の画素の構成例を示す回路図である。

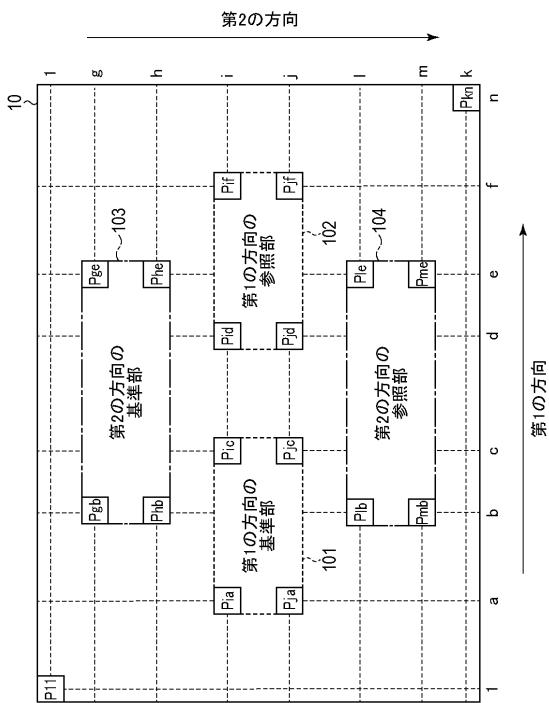

【図3】本発明の第1実施形態による光電変換装置の画素領域に配置される基準部と参照部との位置関係を模式的に示す図である。

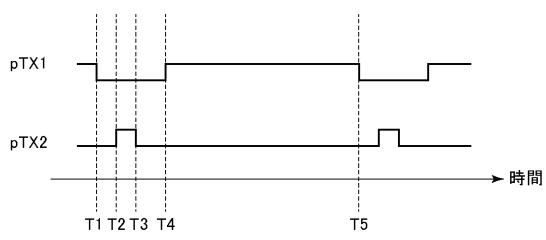

【図4】本発明の第1実施形態による光電変換装置の駆動方法を示すタイミング図（その1）である。10

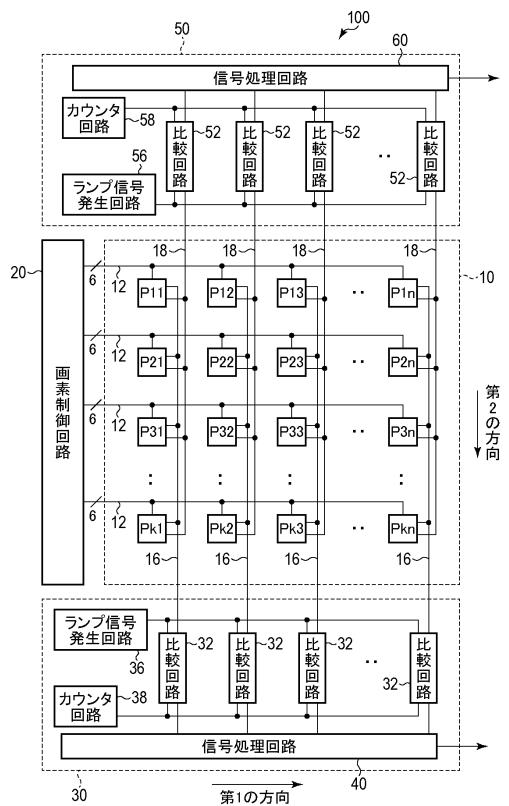

【図5】本発明の第1実施形態による光電変換装置の駆動方法を示すタイミング図（その2）である。

【図6】本発明の第2実施形態による光電変換装置の概略構成を示す図である。

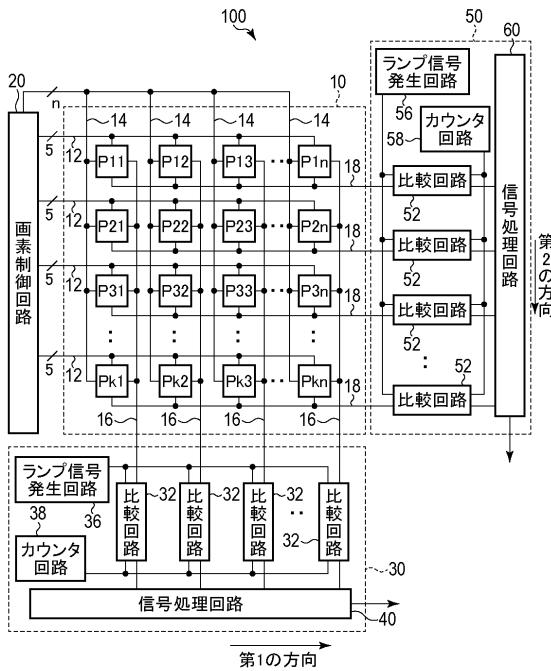

【図7】本発明の第3実施形態による光電変換装置の概略構成を示す図である。

【図8】本発明の第3実施形態による光電変換装置の駆動方法を示すタイミング図である。

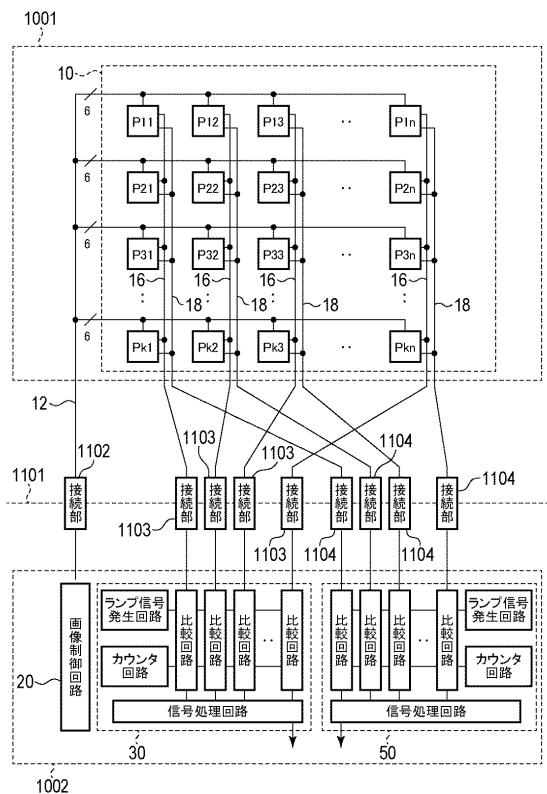

【図9】本発明の第4実施形態による光電変換装置の概略構成を示す図である。

【図10】本発明の第5実施形態による光電変換装置の概略構成を示す図である。

【図11】本発明の第5実施形態による光電変換装置の概略構成を示す図である。

【図12】本発明の第6実施形態による撮像システムの概略構成を示すブロック図である。

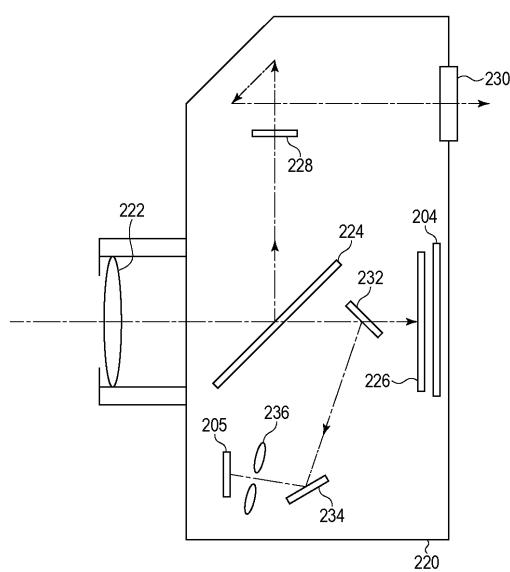

【図13】本発明の第6実施形態による撮像装置の光学系の配置例を示す概略図である。

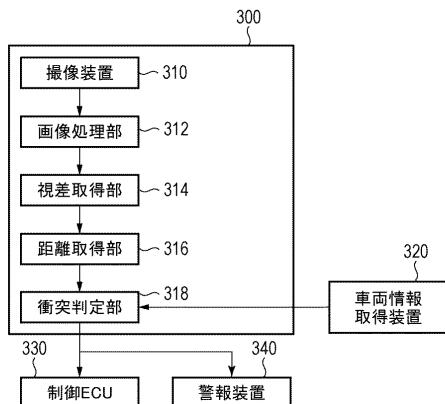

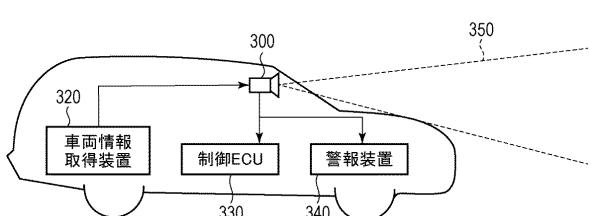

【図14】本発明の第7実施形態による撮像システム及び移動体の構成例を示す図である。

**【発明を実施するための形態】**

**【0012】**

**[第1実施形態]**

本発明の第1実施形態による光電変換装置及びその駆動方法について、図1乃至図5を用いて説明する。図1は、本実施形態による光電変換装置の概略構成を示す図である。図2は、本実施形態による光電変換装置の画素の構成例を示す回路図である。図3は、本実施形態による光電変換装置の画素領域に配置される基準部と参照部との位置関係を模式的に示す図である。図4及び図5は、本実施形態による光電変換装置の駆動方法を示すタイミング図である。20

**【0013】**

はじめに、本実施形態による光電変換装置の概略構成について、図1乃至図3を用いて説明する。

**【0014】**

本実施形態による光電変換装置は、図1に示すように、画素領域10と、画素制御回路20と、読み出し回路30, 50と、制御回路70と、を有する。

**【0015】**

画素領域10には、複数の行及び複数の列に渡って行列状に配された複数の画素Pが設けられている。それぞれの画素Pは、入射光をその光量に応じた電荷に変換する光電変換部を含む。図1にはそれぞれの画素を符号「P」に行番号及び列番号を付記した符号により表している。例えば、第2行第3列に配された画素Pには、「P23」の符号を付している。なお、図1には、k行×n列の画素アレイを示しているが、画素領域10に配される画素アレイの行数及び列数は、特に限定されるものではない。40

**【0016】**

画素領域10の画素アレイの各行には、第1の方向（図1において横方向）に延在して、制御線12と出力線18とが配されている。制御線12は、第1の方向に並ぶ画素Pに接続され、これら画素Pに共通の信号線をなしている。また、出力線18は、第1の方向に並ぶ画素Pに接続され、これら画素Pに共通の信号線をなしている。なお、第1の方向は、行方向と呼ぶことがある。

**【0017】**

10

20

30

40

50

また、画素領域 10 の画素アレイの各列には、第1の方向と交差する第2の方向（図1において縦方向）に延在して、制御線14と、出力線16と、が配されている。制御線14は、第2の方向に並ぶ画素Pに接続され、これら画素Pに共通の信号線をなしている。また、出力線16は、第2の方向に並ぶ画素Pに接続され、これら画素Pに共通の信号線をなしている。なお、第2の方向は、列方向と呼ぶことがある。

#### 【0018】

本実施形態では、複数の制御線14は、複数の列に対応して配される。すなわち、複数の制御線14のそれぞれは、複数の列のうちの対応する1列に接続される。また、複数の出力線18は、複数の行に対応して配される。すなわち、複数の出力線18のそれぞれは、複数の行のうちの対応する1行に接続される。しかし、本実施形態の変形例としては、複数の制御線14は複数の行に対応して配され、複数の出力線18は複数の列に対応して配されてもよい。この変形例では、複数の制御線12が複数の列に対応して配され、複数の出力線16が複数の行に対応して配される。

10

#### 【0019】

各行の制御線12及び各列の制御線14は、画素制御回路20に接続されている。画素制御回路20は、画素Pから信号を読み出す際に画素P内の読み出し回路を駆動するための制御信号を、制御線12, 14を介して画素Pに供給する画素制御部である。画素制御回路20は、シフトレジスタやアドレスデコーダなどの論理回路によって構成され得る。画素Pから読み出される信号は、画素P内の読み出し回路の駆動態様に応じて、対応する列の出力線16又は対応する行の出力線18へと出力される。

20

#### 【0020】

なお、簡単のため、図1は、n本の制御線14が1つのバス配線で画素制御回路20に接続される様を示している。実際には、制御線12と同様に、各制御線14は他の制御線14とは独立に制御信号を伝達する。また、後述の通り、1つの画素Pが制御される複数の対象を含む場合、図1で1つの行に対応して配された制御線12は、複数の制御線を含みうる。本実施形態では、1つの列に対応して配された制御線14は1つの制御線で構成される。しかし、必要に応じて、1つの列に対応して配された制御線14は複数の制御線を含みうる。

20

#### 【0021】

各列の出力線16は、読み出し回路30に接続されている。これにより、画素Pから出力線16に出力された信号は、読み出し回路30に入力されるようになっている。また、各行の出力線18は、読み出し回路50に接続されている。これにより画素Pから出力線18に出力された信号は、読み出し回路50に入力されるようになっている。

30

#### 【0022】

読み出し回路30, 50は、画素Pから読み出された信号に対して所定の処理、例えば、相関二重サンプリング（CDS: Correlated Double Sampling）処理、増幅処理、アナログデジタル変換等の信号処理を実施する回路部である。読み出し回路30, 50は、信号保持部、CDS回路、列アンプ等を含み得る。読み出し回路30, 50は、所定の処理を行った後の画素信号を、光電変換装置100内或いは光電変換装置100の外部の信号処理部（図示せず）に出力する。

40

#### 【0023】

制御回路70は、画素制御回路20、読み出し回路30, 50に、これらの動作やタイミングを制御する制御信号を供給するための回路部である。なお、画素制御回路20、読み出し回路30, 50に供給される制御信号の一部又は総ては、光電変換装置100の外部から供給してもよい。

#### 【0024】

各々の画素Pは、図2に示すように、光電変換部PDと、転送トランジスタM1, M2と、リセットトランジスタM3と、増幅トランジスタM4と、選択トランジスタM5, M6と、電荷排出トランジスタM7と、を有する。

#### 【0025】

50

光電変換部 P D は、例えばフォトダイオードである。光電変換部 P D のフォトダイオードは、アノードが接地電圧ノードに接続され、カソードが転送トランジスタ M 1 のソース及び電荷排出トランジスタ M 7 のソースに接続されている。転送トランジスタ M 1 のドレインは、転送トランジスタ M 2 のソースに接続されている。転送トランジスタ M 1 のドレインと転送トランジスタ M 2 のソースとの間の接続ノードは、容量成分を含み、この容量成分による電荷保持部 M E M を構成する。図 2 には、電荷保持部 M E M の容量成分を、当該ノードに接続された容量素子で表している。

#### 【 0 0 2 6 】

転送トランジスタ M 2 のドレインは、リセットトランジスタ M 3 のソース及び増幅トランジスタ M 4 のゲートに接続されている。転送トランジスタ M 2 のドレイン、リセットトランジスタ M 3 のソース及び増幅トランジスタ M 4 のゲートの接続ノードは、いわゆる浮遊拡散部 F D である。浮遊拡散部 F D は、容量成分（浮遊拡散容量）を含み、この容量成分による電荷の保持部を構成する。図 2 には、浮遊拡散部 F D の容量成分を、F D 部に接続された容量素子で表している。

10

#### 【 0 0 2 7 】

リセットトランジスタ M 3 のドレイン、増幅トランジスタ M 4 のドレイン及び電荷排出トランジスタ M 7 のドレインは、電源電圧ノード（電圧 V d d ）に接続されている。なお、リセットトランジスタ M 3 のドレインに供給される電圧、増幅トランジスタ M 4 のドレインに供給される電圧、電荷排出トランジスタ M 7 のドレインに供給される電圧は、いずれか 2 つ又は 3 つが同じであってもよいし、総て異なっていてもよい。増幅トランジスタ M 4 のソースは、選択トランジスタ M 5 のドレイン及び選択トランジスタ M 6 のドレインに接続されている。選択トランジスタ M 5 のソースは、出力線 1 6 に接続されている。選択トランジスタ M 6 のソースは、出力線 1 8 に接続されている。

20

#### 【 0 0 2 8 】

なお、トランジスタのソースとドレインの呼称は、トランジスタの導電型や着目する機能等に応じて異なることがあり、上述のソースとドレインとは逆の名称で呼ばれることがある。

#### 【 0 0 2 9 】

図 2 の画素構成の場合、画素領域 1 0 の各行に配された制御線 1 2 は、制御信号 p T X 1 , p T X 2 , p R E S , p O F D , p S E L 1 を供給する 5 本の信号線を含む。制御信号 p T X 1 を供給する信号線は、対応する行に属する画素 P の転送トランジスタ M 1 のゲートにそれぞれ接続され、これら画素 P に共通の信号線をなしている。制御信号 p T X 2 を供給する信号線は、対応する行に属する画素 P の転送トランジスタ M 2 のゲートにそれぞれ接続され、これら画素 P に共通の信号線をなしている。制御信号 p R E S を供給する信号線は、対応する行に属する画素 P のリセットトランジスタ M 3 のゲートにそれぞれ接続され、これら画素 P に共通の信号線をなしている。制御信号 p O F D を供給する信号線は、対応する行に属する画素 P の電荷排出トランジスタ M 7 のゲートにそれぞれ接続され、これら画素 P に共通の信号線をなしている。制御信号 p S E L 1 を供給する信号線は、対応する行に属する画素 P の選択トランジスタ M 5 のゲートにそれぞれ接続され、これら画素 P に共通の信号線をなしている。

30

#### 【 0 0 3 0 】

画素領域 1 0 の各列に配された制御線 1 4 は、制御信号 p S E L 2 を供給する信号線を含む。制御信号 p S E L 2 を供給する信号線は、対応する列に属する画素 P の選択トランジスタ M 6 のゲートに接続され、これら画素 P に共通の信号線をなしている。各列に対応する n 本の信号線には、画素制御回路 2 0 からそれぞれ独立した制御信号 p S E L 2 が供給される。

40

#### 【 0 0 3 1 】

画素 P を構成する各トランジスタが N 型トランジスタで構成される場合、画素制御回路 2 0 からハイレベルの制御信号が供給されることにより、対応するトランジスタがオンになる。また、画素制御回路 2 0 からローレベルの制御信号が供給されることにより、対応

50

するトランジスタがオフになる。

**【 0 0 3 2 】**

画素領域 1 0 の各列に配された出力線 1 6 は、対応する列に属する画素 P の選択トランジスタ M 5 のソースに接続されている。また、画素領域 1 0 の各行に配された出力線 1 8 は、対応する行に属する画素 P の選択トランジスタ M 6 のソースに接続されている。

**【 0 0 3 3 】**

光電変換部 P D は、入射光をその光量に応じた量の電荷に変換（光電変換）するとともに、生じた電荷を蓄積する。転送トランジスタ M 1 は、制御信号 p T X 1 によって制御され、オンになることにより、光電変換部 P D が保持する電荷を電荷保持部 M E M に転送する。電荷保持部 M E M は、光電変換部 P D で生成された電荷を、光電変換部 P D とは異なる場所で保持する。

10

**【 0 0 3 4 】**

転送トランジスタ M 2 は、制御信号 p T X 2 によって制御され、オンになることにより、電荷保持部 M E M が保持する電荷を浮遊拡散部 F D に転送する。浮遊拡散部 F D は、電荷保持部 M E M から転送された電荷を保持するとともに、増幅部の入力ノード（増幅トランジスタ M 4 のゲート）でもあるその電圧を、浮遊拡散部 F D の容量と転送された電荷の量とに応じた所定の電圧に設定する。リセットトランジスタ M 3 は、制御信号 p R E S によって制御され、オンになることにより、浮遊拡散部 F D を電圧 V d d に応じた所定の電圧にリセットする。

20

**【 0 0 3 5 】**

選択トランジスタ M 5 は、制御信号 p S E L 1 によって制御され、オンになることにより、出力線 1 6 に信号を出力する画素 P を選択する。また、選択トランジスタ M 6 は、制御信号 p S E L 2 によって制御され、オンになることにより、出力線 1 8 に信号を出力する画素 P を選択する。増幅トランジスタ M 4 は、ドレインに電圧 V d d が供給され、ソースに選択トランジスタ M 5 又は選択トランジスタ M 6 を介して図示しない電流源からバイアス電流が供給される構成となっている。これにより、増幅トランジスタ M 4 は、ゲートを入力ノードとする増幅部（ソースフォロワ回路）を構成している。増幅トランジスタ M 4 は、光電変換部 P D への入射光により生じた電荷に基づく信号を、選択トランジスタ M 5 を介して出力線 1 6 に、或いは、選択トランジスタ M 6 を介して出力線 1 8 に、出力する。

30

**【 0 0 3 6 】**

電荷排出トランジスタ M 7 は、制御信号 p O F D によって制御され、オンになることにより、光電変換部 P D に蓄積された電荷を電源に排出する。すなわち、電荷排出トランジスタ M 7 は、オンになることにより、光電変換部 P D を電圧 V d d に応じた所定の電圧にリセットする。

**【 0 0 3 7 】**

図 2 に示す画素構成によれば、電荷保持部 M E M が電荷を保持している間に光電変換部 P D で生じた電荷は、光電変換部 P D に蓄積することができる。これにより、複数の画素 P の間で露光期間が一致するような撮像動作、いわゆるグローバル電子シャッタ動作を行うことが可能となる。この際、電荷排出トランジスタ M 7 を、総ての画素 P において一括でオフに制御し、光電変換部 P D に蓄積された電荷を同時に排出することで、グローバル電子シャッタ動作における露光の開始時刻を制御することが可能である。また、転送トランジスタ M 1 を、総ての画素 P において一括でオンに制御し、光電変換部 P D に蓄積された電荷を同時に電荷保持部 M E M に転送することで、グローバル電子シャッタ動作における露光の終了時刻を制御することが可能である。ここで、総ての画素 P が同時に露光を開始し、終了する代わりに、対となる領域の画素 P だけが同時に露光を行ってもよい。なお、電子シャッタとは、入射光によって生じた電荷の蓄積を電気的に制御することである。

40

**【 0 0 3 8 】**

このように、本実施形態による光電変換装置は、複数の画素 P が画素領域 1 0 内に行列状に配されたエリアセンサである。本実施形態では、このようなエリアセンサを用いて位

50

相差検出によりオートフォーカスを行うための焦点検出装置を構成する例を示す。

**【 0 0 3 9 】**

相差検出型の焦点検出装置においては、像データを取得するための画素領域 10 が、任意の大きさの基準部と参照部とを含んでいる。そして、基準部から出力される像データと参照部から出力される像データとの相関演算を行ってこれらの間の位相ずれ量を算出し、三角測距の原理を用いて被写体までの距離を測定する。基準部と参照部は、対を成す領域である。そのため、基準部と参照部から出力されるデータは、対をなす像データである。

**【 0 0 4 0 】**

本実施形態による光電変換装置においては、図 3 に示すように、画素領域 10 内に、対となる基準部と参照部とを 2 組、定義する。すなわち、第 1 の組として、第 1 の方向に沿って配された基準部 101 と参照部 102 とが定義されている。また、第 2 の組として、第 2 の方向に沿って配された基準部 103 と参照部 104 とが定義されている。

10

**【 0 0 4 1 】**

基準部 101, 103 及び参照部 102, 104 の各々は、行及び列が連続する複数の画素 P からなるブロックによって構成される読み出し領域である。基準部 101 と参照部 102 とが第 1 の方向に沿った位相差を検出するための焦点検出領域対を構成し、基準部 103 と参照部 104 とが第 2 の方向に沿った位相差を検出するための焦点検出領域対を構成している。基準部と参照部とを 2 組、定義しているのは、被写体の縦方向にも横方向にもピント位置を感知する、いわゆるクロス測距を可能にするためである。基準部 101, 103、参照部 102, 104 の各々の大きさは、これらを構成する画素 P の数に応じて任意に決めることができる。

20

**【 0 0 4 2 】**

基準部 101 (第 1 の読み出し領域) に属する画素のうち少なくとも 1 つの画素 (第 1 の画素) と、参照部 102 (第 2 の読み出し領域) に属する画素のうち少なくとも 1 つの画素 (第 2 の画素) とは、同じ行であって、かつ、互いに異なる列に配されている。基準部 103 (第 3 の読み出し領域) に属する画素のうちの少なくとも 1 つの画素 (第 3 の画素) と、参照部 104 (第 4 の読み出し領域) に属する画素のうちの少なくとも 1 つの画素 (第 4 の画素) とは、同じ列であって、かつ、互いに異なる行に配されている。また、第 1 の画素及び第 2 の画素が属する行は、第 3 の画素が属する行と第 4 の画素が属する行との間に配されている。

30

**【 0 0 4 3 】**

図 1 の例では、第 1 の方向の基準部 101 は、画素 P<sub>i a</sub>, P<sub>i c</sub>, P<sub>j a</sub>, P<sub>j c</sub> を頂点とする矩形状の領域として定義されている。第 1 の方向の参照部 102 は、画素 P<sub>i d</sub>, P<sub>i f</sub>, P<sub>j d</sub>, P<sub>j f</sub> を頂点とする矩形状の領域として定義されている。第 2 の方向の基準部 103 は、画素 P<sub>g b</sub>, P<sub>g e</sub>, P<sub>h b</sub>, P<sub>h e</sub> を頂点とする矩形状の領域として定義されている。第 2 の方向の参照部 104 は、画素 P<sub>l b</sub>, P<sub>l e</sub>, P<sub>m b</sub>, P<sub>m e</sub> を頂点とする矩形状の領域として定義されている。ここで、a, b, c, d, e, f は、2 ~ n - 1 の間の列番号を表す整数であり、この順番で値が大きくなるものとする。また、g, h, i, j, l, m は、2 ~ k - 1 の間の行番号を表す整数であり、この順番で値が大きくなるものとする。

40

**【 0 0 4 4 】**

次に、本実施形態による光電変換装置の駆動方法について、図 4 及び図 5 を用いて説明する。

**【 0 0 4 5 】**

図 4 は、本実施形態の光電変換装置におけるシャッタ動作を示すタイミング図である。シャッタ動作とは、光電変換部 PD における露光期間の開始と終了とを規定する動作である。図 4 には、画素 P の制御信号のうち、転送トランジスタ M1 の制御信号 p<sub>T X 1</sub> と、転送トランジスタ M2 の制御信号 p<sub>T X 2</sub> と、を示している。これら制御信号がハイレベルのとき、対応するトランジスタはオン状態になるものとする。また、これら制御信号がロー レベルのとき、対応するトランジスタはオフ状態になるものとする。

50

**【 0 0 4 6 】**

時刻 T 1において、画素制御回路 20は、各行の制御線 12に供給している制御信号 p TX1を、ハイレベルからローレベルへと制御する。これにより、総ての画素 Pにおいて、転送トランジスタ M1がオフになる。

**【 0 0 4 7 】**

時刻 T 1よりも前の期間において、光電変換部 PDでは、前フレームの露光が行われている。露光とは、光電変換によって生じた電荷が信号として蓄積又は保持されることを意味する。時刻 T 1よりも前に生じた電荷は、光電変換部 PDに保持されている。前フレームの露光の終了は、光電変換部 PDから電荷保持部 MEMへ電荷を転送する転送トランジスタ M1を、総ての画素 Pで同時にオンからオフへと制御する時刻 T 1の動作によって規定される。

10

**【 0 0 4 8 】**

また、時刻 T 1において、光電変換部 PDが保持していた総ての電荷が電荷保持部 MEMに転送される。これにより、光電変換部 PDは、初期状態となり、時刻 T 1から新たに電荷の蓄積を開始する。このように、本実施形態では、転送トランジスタ M1がオフすることで、光電変換部 PDにおける電荷の蓄積が開始する。

**【 0 0 4 9 】**

続く時刻 T 1から時刻 T 4までの期間において、画素制御回路 20は、各行の制御線 12に供給している制御信号 p TX1をローレベルのまま維持する。これにより、時刻 T 1から時刻 T 4の間、転送トランジスタ M1はオフ状態に維持され、この期間の間に光電変換部 PDで生じた電荷は光電変換部 PDに蓄積される。

20

**【 0 0 5 0 】**

時刻 T 1と時刻 T 4との間の時刻 T 2から時刻 T 3の期間において、画素制御回路 20は、各行の制御線 12に供給している制御信号 p TX2を、ローレベルからハイレベルへと制御する。これにより、転送トランジスタ M2がオンになり、そのときに電荷保持部 MEMが保持している電荷、すなわち前フレームの露光期間の間に生じた電荷が、電荷保持部 MEMから浮遊拡散部 FDへと転送される。その結果、増幅部の入力ノードである浮遊拡散部 FDは、その容量と電荷保持部 MEMから転送された電荷の量とに応じた電圧となる。こうして、前フレームの露光期間の間に生じた電荷に基づく信号が、増幅トランジスタ M4から選択トランジスタ M5のドレイン及び選択トランジスタ M6のドレインへと出力される。

30

**【 0 0 5 1 】**

時刻 T 4において、画素制御回路 20は、各行の制御線 12に供給している制御信号 p TX1を、ローレベルからハイレベルへと制御する。これにより、総ての画素 Pにおいて、転送トランジスタ M1がオンになる。これにより、時刻 T 1から時刻 T 4の期間の間に光電変換部 PDで生じた電荷が、電荷保持部 MEMへと転送される。つまり、時刻 T 4以降は、時刻 T 1から時刻 T 4の期間の間に生じた電荷が、電荷保持部 MEMによって保持される。

**【 0 0 5 2 】**

その後、時刻 T 4から、次に転送トランジスタ M1がオフになる時刻 T 5までの期間は、電荷保持部 MEMが、時刻 T 1から時刻 T 4までの期間に生じた電荷と、時刻 T 4から時刻 T 5までの期間に生じた電荷と、の両方を保持する。時刻 T 4から時刻 T 5までの期間において、転送トランジスタ M1はオン状態のまま維持されるため、この期間の間に光電変換部 PDで生じた電荷は、即座に電荷保持部 MEMへと転送される。なお、光電変換部 PDから電荷保持部 MEMに電荷を転送する期間は、任意に設定することができる。

40

**【 0 0 5 3 】**

次いで、時刻 T 5において、画素制御回路 20は、各行の制御線 12に供給している制御信号 p TX1を、ハイレベルからローレベルへと制御する。これにより、総ての画素 Pにおいて、転送トランジスタ M1がオフになる。これにより、1フレームの露光期間が終了する。

50

**【 0 0 5 4 】**

本実施形態の駆動方法では、画素領域 1 0 に配された総ての画素 P において、時刻 T 1 に露光が開始し、時刻 T 5 に露光が終了する。また、時刻 T 5 からは次のフレームの露光が開始し、以降、時刻 T 1 から時刻 T 5 までの動作が繰り返し実行される。

**【 0 0 5 5 】**

なお、上記駆動例では、転送トランジスタ M 1 をオンからオフに制御する動作によって一の露光期間の終了時刻と次の露光期間の開始時刻とを同時に規定しているが、電荷排出トランジスタ M 7 を用いることでこれらを別々に規定することもできる。例えば、時刻 T 1 から時刻 T 5 までの期間において、電荷排出トランジスタ M 7 を一時的にオンにするよう制御する。このようにすることで、電荷排出トランジスタ M 7 をオンからオフに制御するタイミングを、次の露光期間の開始時刻として規定することができる。電荷排出トランジスタ M 7 を用いることで、露光期間の長さの設定の自由度を向上することができる。10

**【 0 0 5 6 】**

図 5 は、本実施形態の光電変換装置における読み出し動作を示すタイミング図である。図 5 には、画素 P の制御信号のうち、選択トランジスタ M 5 の制御信号 p S E L 1 と、選択トランジスタ M 6 の制御信号 p S E L 2 と、リセットトランジスタ M 3 の制御信号 p R E S と、転送トランジスタ M 2 の制御信号 p T X 2 と、を示している。これら制御信号がハイレベルのとき、対応するトランジスタはオン状態になるものとする。また、これら制御信号がローレベルのとき、対応するトランジスタはオフ状態になるものとする。ここでは、第 1 の方向を水平方向と呼び、第 2 の方向を垂直方向と呼ぶものとする。20

**【 0 0 5 7 】**

図 5 に示される制御信号に従って、画素 P の選択、浮遊拡散部 F D のリセット、ノイズ信号の読み出し、電荷の転送及び光信号の読み出しが行われ、読み出し回路 3 0 , 5 0 が備える図示しない C D S 回路によって像データが得られる。

**【 0 0 5 8 】**

本実施形態で説明する駆動例においては、まず、第 1 の期間において、水平方向の基準部 1 0 1 の像データと水平方向の参照部 1 0 2 の像データとの読み出しを同時に行う。その後、第 1 の期間とは異なる第 2 の期間において、垂直方向の基準部 1 0 3 の像データと垂直方向の参照部 1 0 4 の像データとの読み出しを同時に行う。図 5 において、時刻 T 1 1 から時刻 T 1 6 が基準部 1 0 1 の像データ及び参照部 1 0 2 の像データを読み出す期間であり、時刻 T 2 1 から時刻 T 2 6 が基準部 1 0 3 の像データ及び参照部 1 0 4 の像データを読み出す期間である。なお、本実施形態による光電変換装置においては、水平方向の基準部 1 0 1 の像データ、水平方向の参照部 1 0 2 の像データ、垂直方向の基準部 1 0 3 の像データ及び垂直方向の参照部 1 0 4 の像データの読み出しを同時に行うことも可能である。30

**【 0 0 5 9 】**

時刻 T 1 1 から時刻 T 1 2 までの期間は、第 i 行に属する画素 P から信号の読み出しを行う期間である。なお、第 i 行は基準部 1 0 1 及び参照部 1 0 2 の先頭行であり、第 j 行は基準部 1 0 1 及び参照部 1 0 2 の最終行である（図 3 参照）。

**【 0 0 6 0 】**

時刻 T 1 1 から時刻 T 1 2 までの期間において、画素制御回路 2 0 は、第 i 行の制御線 1 2 に供給する制御信号 p S E L 1 をハイレベルに制御する。これにより、第 i 行に属する画素 P の選択トランジスタ M 5 がオンになり、第 i 行に属する画素 P が選択される。すなわち、第 i 行に属する画素 P は、画素信号を、対応する列の出力線 1 6 を介して読み出し回路 3 0 へと出力できる状態となる。40

**【 0 0 6 1 】**

図 5 の時刻 T 1 1 から時刻 T 1 2 までの期間のうち、制御信号 p R E S がハイレベルの期間は、浮遊拡散部 F D のリセット期間である。また、制御信号 p T X 2 がハイレベルの期間は、図 4 の時刻 T 2 から時刻 T 3 までの期間に対応し、電荷保持部 M E M から浮遊拡散部 F D への電荷の転送期間である。リセット期間と転送期間との間に出力線 1 6 に読み

出される画素信号が、浮遊拡散部 FD のリセット電圧に応じた信号（ノイズ信号）である。また、転送期間の後に出力線 16 に読み出される画素信号が、光電変換部 PD で生じた電荷の量に応じた信号（光信号）である。

#### 【 0 0 6 2 】

第 i 行に属する画素 P から読み出し回路 30 へと読み出されたノイズ信号及び光信号は、読み出し回路 30 が備える CDS 回路において差分処理され、第 i 行の像データとなる。

#### 【 0 0 6 3 】

次いで、第 i 行に属する画素 P からの像データの読み出しと同様にして、 $i + 1$  行目から  $j$  行目までの信号の読み出しを繰り返し行う。図 5 には、時刻 T13 から時刻 T14 の間に第  $i + 1$  行に属する画素 P からの信号の読み出しを行い、時刻 T15 から時刻 T16 の間に第  $j$  行に属する画素 P からの信号の読み出しを行う場合を例示している。10

#### 【 0 0 6 4 】

このようにして、水平方向に配された基準部 101 及び参照部 102 に属する総ての画素 P からの画素信号の読み出しを行い、基準部 101 の像データと参照部 102 の像データとを取得する。

#### 【 0 0 6 5 】

なお、基準部 101 及び参照部 102 が配置される  $i$  行目から  $j$  行目には基準部 103 及び参照部 104 を構成する画素 P は存在しないため、基準部 101 及び参照部 102 に対する読み出し動作が基準部 103 及び参照部 104 の画素 P に影響することはない。

#### 【 0 0 6 6 】

時刻 T21 から時刻 T22 までの期間は、第 b 列に属する画素 P から信号の読み出しを行う期間である。なお、第 b 列は基準部 103 及び参照部 104 の先頭列であり、第 e 列は基準部 103 及び参照部 104 の最終列である（図 3 参照）。

#### 【 0 0 6 7 】

時刻 T21 から時刻 T22 までの期間において、画素制御回路 20 は、第 b 列の制御線 14 に供給する制御信号 pSEL2 をハイレベルに制御する。これにより、第 b 列に属する画素 P の選択トランジスタ M6 がオンになり、第 b 列に属する画素 P が選択される。すなわち、第 b 列に属する画素 P は、画素信号を、対応する行の出力線 18 を介して読み出し回路 50 へと出力できる状態となる。

#### 【 0 0 6 8 】

図 5 の時刻 T21 から時刻 T22 までの期間のうち、制御信号 pRES がハイレベルの期間は、浮遊拡散部 FD のリセット期間である。また、制御信号 pTX2 がハイレベルの期間は、図 4 の時刻 T2 から時刻 T3 までの期間に対応し、電荷保持部 MEM から浮遊拡散部 FD への電荷の転送期間である。リセット期間と転送期間との間に出力線 18 に読み出される画素信号が、浮遊拡散部 FD のリセット電圧に応じたノイズ信号である。また、転送期間の後に出力線 18 に読み出される画素信号が、光電変換部 PD で生じた電荷の量に応じた光信号である。30

#### 【 0 0 6 9 】

第 b 列に属する画素 P から読み出し回路 50 へと読み出されたノイズ信号及び光信号は、読み出し回路 50 が備える CDS 回路において差分処理され、第 b 列の像データとなる。

#### 【 0 0 7 0 】

次いで、第 b 列に属する画素 P からの像データの読み出しと同様にして、 $b + 1$  列目から  $e$  列目までの信号の読み出しを繰り返し行う。図 5 には、時刻 T23 から時刻 T24 の間に第  $b + 1$  列に属する画素 P からの信号の読み出しを行い、時刻 T25 から時刻 T26 の間に第  $e$  列に属する画素 P からの信号の読み出しを行う場合を例示している。40

#### 【 0 0 7 1 】

このようにして、垂直方向に配された基準部 103 及び参照部 104 に属する総ての画素 P からの画素信号の読み出しを行い、基準部 103 の像データと参照部 104 の像データとを取得する。

#### 【 0 0 7 2 】

10

20

30

40

50

一般に、CMOSイメージセンサなどの固体撮像装置においては、行列状に配された複数の画素の信号を行単位で順次読み出すことによって全体の像データを取得することが行われている。しかしながら、このような駆動においては、像データの読み出しの際、電源電圧の変動のような経時的に変化するノイズが読み出し回路に混入すると、このノイズに起因するノイズ成分が画素信号に重畠されることによってデータの変動を引き起こすことがある。このデータの変動は行単位で発生するため、固体撮像装置から読み出される像データにおいては、ランダムに発生する水平方向の縞状のパターンノイズとして現れる。

#### 【0073】

図3に示す固体撮像装置において上述のような読み出し動作を行うと、水平方向に生じる上記パターンノイズは、基準部101, 103及び参照部102, 104の像データにそれぞれ重畠する虞がある。10

#### 【0074】

このとき、上記パターンノイズは水平方向に発生するため、水平方向に配された基準部101の像データと参照部102の像データとには、同一量のノイズが重畠することになる。したがって、基準部101の像データと参照部102の像データとの相関演算をする際には、これらに重畠するノイズ成分はキャンセルされ、相関演算の結果に影響を与えることはない。

#### 【0075】

ところが、垂直方向に配された基準部103及び参照部104に対しては異なるタイミングで読み出しが行われるため、基準部103の像データと参照部104の像データとに異なる量のノイズが重畠することがある。この場合、基準部103の像データと参照部104の像データとの相関演算の精度が低下し、これによってオートフォーカスの合焦精度が低下する。20

#### 【0076】

この点、本実施形態の光電変換装置は、図1に示すように、垂直方向に配された出力線16に接続された読み出し回路30と、水平方向に配された出力線18に接続された読み出し回路50と、を有している。したがって、水平方向に配された基準部101及び参照部102に対しては読み出し回路30を用いて像データの読み出しを並列して行うことができ、基準部101の像データに重畠するノイズと参照部102の像データに重畠するノイズとを揃えることができる。また、垂直に配された基準部103及び参照部104に対しては読み出し回路50を用いて像データの読み出しを並列して行うことができ、基準部103の像データに重畠するノイズと参照部104の像データに重畠するノイズとを揃えることができる。30

#### 【0077】

したがって、本実施形態の光電変換装置によれば、水平方向及び垂直方向の両方向に対して精度の高い相関演算をすることができ、オートフォーカスの合焦精度を向上することができます。

#### 【0078】

このように、本実施形態によれば、対をなす像データに重畠するパターンノイズの影響を抑制し、オートフォーカスの合焦精度を向上することができる。40

#### 【0079】

##### [第2実施形態]

本発明の第2実施形態による光電変換装置及びその駆動方法について、図6を用いて説明する。図6は、本実施形態による光電変換装置の概略構成を示すブロック図である。第1実施形態による光電変換装置と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。

#### 【0080】

本実施形態では、読み出し回路30, 50の具体的な構成例とその動作について説明する。その他の構成及び各々の動作は、第1実施形態による光電変換装置と同様である。

#### 【0081】

本実施形態による光電変換装置 100 の読み出し回路 30 は、図 6 に示すように、複数の比較回路 32 と、ランプ信号発生回路 36 と、カウンタ回路 38 と、信号処理回路 40 と、を有する。

#### 【0082】

複数の比較回路 32 は、画素領域 10 の画素アレイの各列に対応して設けられている。複数の比較回路 32 の各々は、対応する列の出力線 16 に接続されている。また、複数の比較回路 32 の各々は、ランプ信号発生回路 36、カウンタ回路 38 及び信号処理回路 40 に接続されている。なお、図 6 では、制御回路 70 の記載を省略している。

#### 【0083】

ランプ信号発生回路 36 は、時間の経過とともにレベルが所定値から徐々に増加し或いは低下する信号（ランプ信号）を生成する回路である。ランプ信号発生回路 36 は、制御回路 70 からの制御信号に応じて、生成したランプ信号を各列の比較回路 32 に出力する。カウンタ回路 38 は、クロック信号を計数し、計数値を示すカウント信号を、各列の比較回路 32 に出力する。

#### 【0084】

各列の比較回路 32 は、対応する列の出力線 16 を介して画素 P から出力されるアナログ信号である画素信号とランプ信号発生回路 36 から出力されるランプ信号とが入力される図示しない差動入力比較器を有する。差動入力比較器は、画素信号の信号レベルとランプ信号の信号レベルとを比較し、これら信号レベルの大小関係が反転したときに、出力信号をハイレベルからローレベル或いはローレベルからハイレベルへと遷移する。比較回路 32 は、差動入力比較器の出力信号のレベルが反転したときにカウンタ回路 38 から受信しているカウント信号が示すカウント値を、画素信号のデジタルデータとして信号処理回路 40 へと出力する。

#### 【0085】

信号処理回路 40 は、CDS 回路等の所定の信号処理回路を有する。信号処理回路 40 は、各列の比較回路 32 から受信したデジタルデータに対してデジタル CDS 処理等の所定の信号処理を施し、像データを生成する。

#### 【0086】

同様に、本実施形態による光電変換装置の読み出し回路 50 は、図 6 に示すように、複数の比較回路 52 と、ランプ信号発生回路 56 と、カウンタ回路 58 と、信号処理回路 60 と、を有する。

#### 【0087】

複数の比較回路 52 は、画素領域 10 の画素アレイの各行に対応して設けられている。複数の比較回路 52 の各々は、対応する行の出力線 18 に接続されている。また、複数の比較回路 52 の各々は、ランプ信号発生回路 56、カウンタ回路 58 及び信号処理回路 60 に接続されている。

#### 【0088】

ランプ信号発生回路 56 は、ランプ信号を生成する回路である。ランプ信号発生回路 56 は、生成したランプ信号を各行の比較回路 52 に出力する。カウンタ回路 58 は、クロック信号を計数し、計数値を示すカウント信号を、各行の比較回路 52 に出力する。

#### 【0089】

各行の比較回路 52 は、対応する行の出力線 18 を介して画素 P から出力されるアナログ信号である画素信号とランプ信号発生回路 56 から出力されるランプ信号とが入力される図示しない差動入力比較器を有する。差動入力比較器は、画素信号の信号レベルとランプ信号の信号レベルとを比較し、これら信号レベルの大小関係が反転したときに、出力信号をハイレベルからローレベル或いはローレベルからハイレベルへと遷移する。比較回路 52 は、差動入力比較器の出力信号のレベルが反転したときにカウンタ回路 58 から受信しているカウント信号が示すカウント値を、画素信号のデジタルデータとして信号処理回路 60 へと出力する。

#### 【0090】

10

20

30

40

50

信号処理回路 60 は、CDS 回路等の所定の信号処理回路を有する。信号処理回路 60 は、各列の比較回路 52 から受信したデジタルデータに対してデジタル CDS 处理等の所定の信号処理を施し、像データを生成する。

#### 【0091】

このように、読み出し回路 30, 50 は、列並列で A/D 変換を行う A/D 変換部を有する。すなわち、本実施形態の光電変換装置は、デジタル出力方式の光電変換装置である。

#### 【0092】

デジタル出力方式の光電変換装置においても、第 1 実施形態の場合と同様、電源電圧の変動のような経時的に変化するノイズが読み出し回路に混入し、このノイズに起因するノイズ成分が画素信号に重畳することがある。具体的な例としては、ランプ信号発生回路 36, 56 の電源のノイズがランプ信号にノイズとして重畳し、その結果、比較回路 32, 52 から出力されるデジタルデータにノイズ成分が重畳することが挙げられる。また、カウンタ回路 38, 58 の電源のノイズがカウント値に揺らぎを生じ、その結果、比較回路 32, 52 から出力されるデジタルデータにノイズ成分が重畳することが挙げられる。

10

#### 【0093】

したがって、本実施形態による光電変換装置においても、第 1 実施形態と同様の読み出し駆動を行うことで、基準部 101 の像データに重畳するノイズと参照部 102 の像データに重畳するノイズとを揃えることができる。また、基準部 103 の像データに重畳するノイズと参照部 104 の像データに重畳するノイズとを揃えることができる。これにより、水平方向及び垂直方向の両方向に対して精度の高い相関演算をすることができ、オートフォーカスの合焦精度を向上することが可能となる。

20

#### 【0094】

このように、本実施形態によれば、対をなす像データに重畳するパターンノイズの影響を抑制し、オートフォーカスの合焦精度を向上することができる。

#### 【0095】

##### [第 3 実施形態]

本発明の第 3 実施形態による光電変換装置及びその駆動方法について、図 7 及び図 8 を用いて説明する。図 7 は、本実施形態による光電変換装置の概略構成を示すブロック図である。図 8 は、本実施形態の光電変換装置における読み出し動作を示すタイミング図である。第 1 及び第 2 実施形態による光電変換装置と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。

30

#### 【0096】

本実施形態の光電変換装置 100 は、図 7 に示すように、画素制御回路 20 から各画素 P に制御信号を供給する制御線として、第 1 の方向に延在する制御線 12 のみを含む点で、第 2 の方向に延在する制御線 14 を更に含む第 1 及び第 2 実施形態とは異なっている。画素領域 10 の各行に配された制御線 12 は、制御信号 p\_T X 1, p\_T X 2, p\_R E S, p\_O F D, p\_S E L 1, p\_S E L 2 を供給する 6 本の信号線を含む。すなわち、本実施形態の制御線 12 は、第 1 及び第 2 実施形態で説明した 5 本の信号線に加え、制御信号 p\_S E L 2 を供給する信号線を更に含む。制御信号 p\_S E L 2 を供給する信号線は、第 1 及び第 2 実施形態では制御線 14 を構成していた信号線である。制御信号 p\_S E L 2 を供給する信号線は、対応する行に属する画素 P の選択トランジスタ M6 のゲートにそれぞれ接続され、これら画素 P に共通の信号線をなしている。換言すると、本実施形態の光電変換装置 100 は、第 1 の方向に延在する複数の制御線 12 と、第 1 の方向に延在する複数の制御線 14 と、を含むとも言える。

40

#### 【0097】

また、本実施形態の光電変換装置は、図 7 に示すように、出力線 16 と出力線 18 とが平行に配されている点においても、第 1 及び第 2 実施形態とは異なっている。すなわち、出力線 16 及び出力線 18 は、いずれも、第 2 の方向（図 7 において縦方向）に延在するように配されている。出力線 16, 18 は、第 2 の方向に並ぶ画素 P に接続され、これら画素 P に共通の信号線をなしている。また、出力線 16, 18 をこのように配置している

50

関係で、読み出し回路 30 及び読み出し回路 50 は、画素領域 10 を挟んで互いに第 2 の方向に位置するように配されている。

#### 【 0 0 9 8 】

なお、第 1 実施形態で述べたように、複数の制御線 14 は、複数の行及び複数の列のうちの一方の各々に配される。また、複数の出力線 18 は、複数の行及び複数の列のうちの他方の各々に配される。本実施形態においては、複数の制御線 12 の一部である複数の制御線 14 は複数の行の各々に配されており、複数の出力線 18 は複数の列の各々に配されている。

#### 【 0 0 9 9 】

本実施形態による光電変換装置におけるその他の構成及び各々の動作は、第 1 又は第 2 実施形態による光電変換装置と同様である。なお、図 7 では、制御回路 70 の記載を省略している。

10

#### 【 0 1 0 0 】

次に、本実施形態による光電変換装置の駆動方法について、図 8 を用いて説明する。本実施形態においても、基準部 101 の像データ及び参照部 102 の像データの読み出しを読み出し回路 30 で行い、基準部 103 の像データ及び参照部 104 の像データの読み出しを読み出し回路 50 で行う。

#### 【 0 1 0 1 】

図 8 は、本実施形態の光電変換装置における読み出し動作を示すタイミング図である。図 8 には、画素 P の制御信号のうち、選択トランジスタ M5 の制御信号 pSEL1 と、選択トランジスタ M6 の制御信号 pSEL2 と、リセットトランジスタ M3 の制御信号 pRES と、転送トランジスタ M2 の制御信号 pTX2 と、を示している。これら制御信号がハイレベルのとき、対応するトランジスタはオン状態になるものとする。また、これら制御信号がローレベルのとき、対応するトランジスタはオフ状態になるものとする。

20

#### 【 0 1 0 2 】

図 8 に示される制御信号に従って、画素 P の選択、浮遊拡散部 FD のリセット、ノイズ信号の読み出し、電荷の転送及び光信号の読み出しが行われる。そして、読み出し回路 30, 50 の信号処理回路 40, 60 が備える図示しない CDS 回路によって像データが得られる。

30

#### 【 0 1 0 3 】

本実施形態では、水平方向の基準部 101 の像データ及び水平方向の参照部 102 の像データの読み出しを同時に行った後、垂直方向の基準部 103 の像データ及び垂直方向の参照部 104 の像データの読み出しを同時に行う例を説明する。図 8 において、時刻 T11 から時刻 T16 が基準部 101 の像データ及び参照部 102 の像データを読み出す期間であり、時刻 T21 から時刻 T26 が基準部 103 の像データ及び参照部 104 の像データを読み出す期間である。

#### 【 0 1 0 4 】

時刻 T11 から時刻 T12 までの期間は、第 i 行に属する画素 P から信号の読み出しを行う期間である。なお、第 i 行は基準部 101 及び参照部 102 の先頭行であり、第 j 行は基準部 101 及び参照部 102 の最終行である（図 3 参照）。

40

#### 【 0 1 0 5 】

時刻 T11 から時刻 T12 までの期間において、画素制御回路 20 は、第 i 行の制御線 12 に供給する制御信号 pSEL1 をハイレベルに制御する。これにより、第 i 行に属する画素 P の選択トランジスタ M5 がオンになり、第 i 行に属する画素 P が選択される。すなわち、第 i 行に属する画素 P は、画素信号を、対応する列の出力線 16 を介して読み出し回路 30 へと出力できる状態となる。

#### 【 0 1 0 6 】

図 8 の時刻 T11 から時刻 T12 までの期間のうち、制御信号 pRES がハイレベルの期間は、浮遊拡散部 FD のリセット期間である。また、制御信号 pTX2 がハイレベルの期間は、図 4 の時刻 T2 から時刻 T3 までの期間に対応し、電荷保持部 MEM から浮遊拡

50

散部 F D への電荷の転送期間である。リセット期間と転送期間との間に出力線 1 6 に読み出される画素信号が、浮遊拡散部 F D のリセット電圧に応じたノイズ信号である。また、転送期間の後に出力線 1 6 に読み出される画素信号が、光電変換部 P D で生じた電荷の量に応じた光信号である。

#### 【 0 1 0 7 】

第 i 行に属する画素 P から読み出し回路 3 0 へと読み出されたノイズ信号及び光信号は、読み出し回路 3 0 が備える C D S 回路において差分処理され、第 i 行の像データとなる。

#### 【 0 1 0 8 】

次いで、第 i 行に属する画素 P からの像データの読み出しと同様にして、i + 1 行目から j 行目までの信号の読み出しを繰り返し行う。図 8 には、時刻 T 1 3 から時刻 T 1 4 の間に第 i + 1 行に属する画素 P からの信号の読み出しを行い、時刻 T 1 5 から時刻 T 1 6 の間に第 j 行に属する画素 P からの信号の読み出しを行う場合を例示している。

#### 【 0 1 0 9 】

このようにして、水平方向に配された基準部 1 0 1 及び参照部 1 0 2 に属する総ての画素 P からの画素信号の読み出しを行い、基準部 1 0 1 の像データと参照部 1 0 2 の像データとを取得する。

#### 【 0 1 1 0 】

なお、基準部 1 0 1 及び参照部 1 0 2 が配置される i 行目から j 行目には基準部 1 0 3 及び参照部 1 0 4 を構成する画素 P は存在しないため、基準部 1 0 1 及び参照部 1 0 2 に対する読み出し動作が基準部 1 0 3 及び参照部 1 0 4 の画素 P に影響することはない。

#### 【 0 1 1 1 】

時刻 T 2 1 から時刻 T 2 2 までの期間は、第 g 行及び第 1 行に属する画素 P から信号の読み出しを行う期間である。なお、第 g 行は基準部 1 0 3 の先頭行であり、第 1 行は参照部 1 0 4 の先頭行である。また、第 h 行は基準部 1 0 3 の最終行であり、第 m 行は参照部 1 0 4 の最終行である（図 3 参照）。

#### 【 0 1 1 2 】

時刻 T 2 1 から時刻 T 2 2 までの期間において、画素制御回路 2 0 は、第 g 行の制御線 1 2 に供給する制御信号 p S E L 1 をハイレベルに制御する。これにより、第 g 行に属する画素 P の選択トランジスタ M 5 がオンになり、第 g 行に属する画素 P が選択される。すなわち、第 g 行に属する画素 P は、画素信号を、対応する列の出力線 1 6 を介して読み出し回路 3 0 へと出力できる状態となる。

#### 【 0 1 1 3 】

同じく時刻 T 2 1 から時刻 T 2 2 までの期間において、画素制御回路 2 0 は、第 1 行の制御線 1 2 に供給する制御信号 p S E L 2 をハイレベルに制御する。これにより、第 1 行に属する画素 P の選択トランジスタ M 6 がオンになり、第 1 行に属する画素 P が選択される。すなわち、第 1 行に属する画素 P は、画素信号を、対応する列の出力線 1 8 を介して読み出し回路 5 0 へと出力できる状態となる。

#### 【 0 1 1 4 】

図 8 の時刻 T 2 1 から時刻 T 2 2 までの期間のうち、制御信号 p R E S がハイレベルの期間は、浮遊拡散部 F D のリセット期間である。また、制御信号 p T X 2 がハイレベルの期間は、図 4 の時刻 T 2 から時刻 T 3 までの期間に対応し、電荷保持部 M E M から浮遊拡散部 F D への電荷の転送期間である。リセット期間と転送期間との間に出力線 1 6 , 1 8 に読み出される画素信号が、浮遊拡散部 F D のリセット電圧に応じたノイズ信号である。また、転送期間の後に出力線 1 6 , 1 8 に読み出される画素信号が、光電変換部 P D で生じた電荷の量に応じた光信号である。

#### 【 0 1 1 5 】

第 g 行に属する画素 P から読み出し回路 3 0 へと読み出されたノイズ信号及び光信号は、読み出し回路 3 0 が備える C D S 回路において差分処理され、第 g 行の像データとなる。また、第 1 行に属する画素 P から読み出し回路 5 0 へと読み出されたノイズ信号及び光信号は、読み出し回路 5 0 が備える C D S 回路において差分処理され、第 1 行の像データ

10

20

30

40

50

となる。

#### 【0116】

この際、第g行に属する画素Pからノイズ信号を読み出すタイミングと第1行に属する画素Pからノイズ信号を読み出すタイミングとを同じにする。また、第g行に属する画素Pから光信号を読み出すタイミングと第1行に属する画素Pから光信号を読み出すタイミングとを同じにする。これにより、第g行に属する画素Pからの読み出した信号に重畠するノイズと第1行に属する画素Pからの読み出した信号とに重畠するノイズとが経時に変化したときの影響を低減することができる。

#### 【0117】

次いで、第g行及び第1行に属する画素Pからの像データの読み出しと同様にして、 $g + 1$ 行目から $h$ 行目までの信号の読み出し及び $1 + 1$ 行目から $m$ 行目までの信号の読み出しを繰り返し行う。図8には、時刻T23から時刻T24の間に第 $g + 1$ 行及び第 $1 + 1$ 行に属する画素Pからの信号の読み出しを行い、時刻T25から時刻T26の間に第 $h$ 行及び第 $m$ 行に属する画素Pからの信号の読み出しを行う場合を例示している。

10

#### 【0118】

なお、図8の駆動例では、基準部103については第g行から第 $h$ 行をこの順番で読み出し、参照部104については第1行から第 $m$ 行をこの順番で読み出したが、一方の領域の行を逆の順番で読み出すようにしてもよい。すなわち、基準部103については第g行から第 $h$ 行をこの順番で読み出し、参照部104については第 $m$ 行から第1行をこの順番で読み出すようにしてもよい。或いは、基準部103については第 $h$ 行から第g行をこの順番で読み出し、参照部104については第1行から第 $m$ 行をこの順番で読み出すようにしてもよい。このように構成することで、画素領域10の中心に対して対称な場所に位置する画素Pを同時に読み出すことができる。

20

#### 【0119】

このようにして、垂直方向に配された基準部103及び参照部104に属する総ての画素Pからの画素信号の読み出しを行い、基準部103の像データと参照部104の像データとを取得する。

#### 【0120】

このように読み出し動作を行うことにより、基準部101の像データと参照部102の像データとに重畠するノイズの量、並びに、基準部103の像データと参照部104の像データとに重畠するノイズの量を、それぞれ同一にすることができます。

30

#### 【0121】

したがって、本実施形態の光電変換装置によれば、水平方向及び垂直方向の両方向に対して精度の高い相関演算をすることができ、オートフォーカスの合焦精度を向上することが可能となる。

#### 【0122】

このように、本実施形態によれば、対をなす像データに重畠するパターンノイズの影響を抑制し、オートフォーカスの合焦精度を向上することができる。

#### 【0123】

##### [第4実施形態]

本発明の第4実施形態による光電変換装置及びその駆動方法について、図9を用いて説明する。図9は、本実施形態による光電変換装置の概略構成を示すブロック図である。第1乃至第3実施形態による光電変換装置と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。

40

#### 【0124】

本実施形態では、第3実施形態による光電変換装置における読み出し回路30, 50の機能を、1つの読み出し回路30によって実現するように構成した光電変換装置を説明する。

#### 【0125】

本実施形態の光電変換装置100は、図9に示すように、画素制御回路20から各画素

50

P に制御信号を供給する制御線として、第 1 の方向に延在する制御線 1 2 のみを含む点で、第 3 実施形態と同様である。また、本実施形態の光電変換装置は、図 9 に示すように、出力線 1 6 と出力線 1 8 とが平行に配されている点においても、第 3 実施形態と同様である。

#### 【 0 1 2 6 】

一方、本実施形態の光電変換装置は、読み出し回路 3 0 が、画素領域 1 0 の画素アレイの各列に対応してそれぞれ 2 つの比較回路 3 2 , 3 4 を有している点で、2 つの読み出し回路 3 0 , 5 0 を有する第 3 実施形態とは異なっている。各列に設けられた比較回路 3 2 は、対応する列に配された出力線 1 6 に接続されている。また、各列に設けられた比較回路 3 4 は、対応する列に配された出力線 1 8 に接続されている。各列の比較回路 3 2 , 3 4 は、ランプ信号発生回路 3 6 、カウンタ回路 3 8 及び信号処理回路 4 0 に接続されている。すなわち、同じ列の比較回路 3 2 , 3 4 には、同じランプ信号発生回路 3 6 から共通のランプ信号が供給され、同じカウンタ回路 3 8 から共通のカウント信号が供給される。

10

#### 【 0 1 2 7 】

本実施形態による光電変換装置におけるその他の構成及び各々の動作は、第 3 実施形態による光電変換装置と基本的に同じである。本実施形態においては、第 3 実施形態で説明した読み出し回路 5 0 の比較回路 5 2 の機能を、読み出し回路 3 0 の比較回路 3 4 が実行することになる。また、第 3 実施形態で説明した読み出し回路 5 0 の信号処理回路 6 0 の機能を、読み出し回路 3 0 の信号処理回路 4 0 が実行することになる。なお、図 9 では、制御回路 7 0 の記載を省略している。

20

#### 【 0 1 2 8 】

本実施形態による光電変換装置における読み出し動作は、図 8 に示した第 3 実施形態のタイミング図と同じであるため、ここでは説明を省略する。

#### 【 0 1 2 9 】

本実施形態においても、第 3 実施形態と同様、基準部 1 0 1 の像データと参照部 1 0 2 の像データとに重畳するノイズの量、並びに、基準部 1 0 3 の像データと参照部 1 0 4 の像データとに重畳するノイズの量を、それぞれ同一にすることができる。また、本実施形態による光電変換装置では、1 つの読み出し回路 3 0 により基準部 1 0 3 の像データと参照部 1 0 4 の像データとを読み出すため、ランプ信号やカウント信号に重畳するノイズの影響を、第 3 実施形態と比較して、更に抑制することが可能である。

30

#### 【 0 1 3 0 】

したがって、本実施形態の光電変換装置によれば、水平方向及び垂直方向の両方向に対して精度の高い相関演算をすることができ、オートフォーカスの合焦精度を向上することができる。

#### 【 0 1 3 1 】

このように、本実施形態によれば、対をなす像データに重畳するパターンノイズの影響を抑制し、オートフォーカスの合焦精度を向上することができる。

#### 【 0 1 3 2 】

##### [ 第 5 実施形態 ]

本発明の第 5 実施形態による光電変換装置及びその駆動方法について、図 1 0 を用いて説明する。図 1 0 は、本実施形態による光電変換装置の構成を示す図である。第 1 乃至第 4 実施形態による光電変換装置と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。

40

#### 【 0 1 3 3 】

図 1 0 は、本実施形態の光電変換装置 1 0 0 が備える、第 1 基板 1 0 0 1 、第 2 基板 1 0 0 2 を示した図である。第 1 基板 1 0 0 1 には、画素領域 1 0 が配されている。画素領域 1 0 には、複数の行及び複数の列に渡って行列状に配された複数の画素 P が設けられている。また、第 2 基板 1 0 0 2 には、画素制御回路 2 0 と、読み出し回路 3 0 , 5 0 と、制御回路 7 0 とが配されている。なお、図 1 0 には、画素領域 1 0 のうちの画素 P と、画素制御回路 2 0 、読み出し回路 3 0 , 5 0 、制御回路 7 0 のみを示しているが、他に複数

50

の制御線 12、複数の出力線 16, 18 が適宜、第 1 基板 1001 に配される。

**【0134】**

画素制御回路 20 は、画素 P から信号を読み出す際に画素 P 内の読み出し回路を駆動するための制御信号を、制御線を介して画素 P に供給する画素制御部である。画素制御回路 20 は、シフトレジスタやアドレスデコーダなどの論理回路によって構成され得る。

**【0135】**

読み出し回路 30, 50 は、画素 P から読み出された信号に対して所定の処理、例えば、CDS 处理、増幅処理、アナログデジタル変換等の信号処理を実施する回路部である。読み出し回路 30, 50 は、信号保持部、CDS 回路、列アンプ等を含み得る。読み出し回路 30, 50 は、所定の処理を行った後の画素信号を、光電変換装置 100 内或いは光電変換装置外部の信号処理部（図示せず）に出力する。10

**【0136】**

制御回路 70 は、画素制御回路 20、読み出し回路 30, 50 に、これらの動作やタイミングを制御する制御信号を供給するための回路部である。なお、画素制御回路 20、読み出し回路 30, 50 に供給される制御信号の一部又は総ては、光電変換装置 100 の外部から供給してもよい。

**【0137】**

図 11 は、平面視における、第 1 基板 1001 が備える画素 P と、第 2 基板 1002 が備える画素制御回路 20、読み出し回路 30, 50 の配置を示した図である。

**【0138】**

本実施形態の撮像装置は、裏面照射型の撮像装置である。画素 P は、不図示の光電変換部を備える。この光電変換部と、接合面 1101 との間に制御線 12 が設けられている。各行の制御線 12 は、制御信号 p TX1, p TX2, p RES, p O F D, p S E L 1, p S E L 2 を供給する 6 本の信号線を含む。制御線 12 は、画素領域 10 の第 1 の方向（図では横方向）に延在している。同様に、光電変換部と、接合面 1101 との間に、出力線 16, 18 が設けられている。出力線 16, 18 は、画素 P の第 2 の方向（図では縦方向）に延在している。20

**【0139】**

制御線 12 は、接続部 1102 を介して、第 2 基板 1002 の画素制御回路 20 と接続される。出力線 16 は、接続部 1103 を介して、第 2 基板 1002 の読み出し回路 30, 50 へ接続される。出力線 18 は、接続部 1104 を介して、第 2 基板 1002 の読み出し回路 50 へ接続される。これにより画素 P から出力線 16 に出力された信号は、読み出し回路 30 に入力され、画素 P から出力線 18 に出力された信号は、読み出し回路 50 に入力されるようになっている。30

**【0140】**

本実施形態では、読み出し回路 30, 50 が第 2 基板 1002 に配されている。しかし、光電変換装置における機能ブロックの構成は、第 3 実施形態と同じである。つまり、本実施形態による光電変換装置におけるその他の構成及び各々の動作は、第 3 実施形態による光電変換装置と同様である。なお、図 11 では制御回路 70 の記載を省略している。また、本実施形態による光電変換装置における読み出し動作は、図 8 に示した第 3 実施形態のタイミング図と同じであるため、ここでは説明を省略する。40

**【0141】**

本実施形態においても、第 3 実施形態と同様、基準部 101 の像データと参照部 102 の像データとに重畠するノイズの量、並びに、基準部 103 の像データと参照部 104 の像データとに重畠するノイズの量を、それぞれ同一にすることができる。

**【0142】**

したがって、本実施形態の光電変換装置によれば、水平方向及び垂直方向の両方向に対して精度の高い相関演算をすることができ、オートフォーカスの合焦精度を向上することが可能となる。

**【0143】**

10

20

30

40

50

このように、本実施形態によれば、対をなす像データに重畳するパターンノイズの影響を抑制し、オートフォーカスの合焦精度を向上することができる。

#### 【0144】

##### [第6実施形態]

本発明の第6実施形態による撮像システムについて、図12及び図13を用いて説明する。第1乃至第5実施形態による光電変換装置と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。図12は、本実施形態による撮像システムの構成例を示すブロック図である。図13は、本実施形態による撮像システムにおける光学系の配置例を示す概略図である。

#### 【0145】

本実施形態による撮像システム200は、図12に示すように、バリア201と、レンズ202と、絞り203と、固体撮像装置204と、AFセンサ205とを有している。レンズ202は、被写体の光学像を結像するための光学系である。バリア201は、レンズ202のプロテクトを行うものである。絞り203は、レンズ202を通過する光の光量を調整するためのものである。固体撮像装置204は、レンズで結像された被写体の光学像を画像信号として取得するためのものである。AFセンサ205は、第1乃至第4実施形態で説明した光電変換装置100である。

10

#### 【0146】

また、撮像システム200は、アナログ信号処理装置206、A/D変換器207、デジタル信号処理部208を更に有している。アナログ信号処理装置206は、固体撮像装置204やAFセンサ205から出力された信号を処理するためのものである。A/D変換器207は、アナログ信号処理装置206から出力された信号をアナログデジタル変換するためのものである。デジタル信号処理部208は、A/D変換器207から出力された画像データに対して各種の補正を行い或いはデータを圧縮する処理を行うためのものである。

20

#### 【0147】

また、撮像システム200は、メモリ部209、外部I/F回路210、タイミング発生部211、全体制御・演算部212、記録媒体制御I/F部213を更に有している。メモリ部209は、画像データを一時記憶するためのものである。外部I/F回路210は、外部コンピュータ215などの外部機器と通信するためのものである。タイミング発生部211は、デジタル信号処理部208などに各種タイミング信号を出力するためのものである。全体制御・演算部212は、各種演算とカメラ全体を制御するためのものである。記録媒体制御I/F部213は、取得した画像データを記録し、又は画像データの読み出しを行うための半導体メモリなどの着脱可能な記録媒体214との間でデータのやりとりを行うためのものである。

30

#### 【0148】

バリア201がオープンされると、被写体からの光学像がレンズ202及び絞り203を介してAFセンサ205に入射される。全体制御・演算部212は、AFセンサ205からの出力信号をもとに、前記した位相差検出の手法により被写体までの距離を算出する。その後、全体制御・演算部212は、演算結果に基づいてレンズ202を駆動し、再び撮像面に合焦しているか否かを判断し、合焦していないと判断したときには、再びレンズ202を駆動するオートフォーカス制御を行う。

40

#### 【0149】

次いで、合焦が確認された後に、固体撮像装置204による電荷蓄積動作が開始される。固体撮像装置204の電荷蓄積動作が終了すると、固体撮像装置204から出力された画像信号は、アナログ信号処理装置206で所定の処理が行われた後、A/D変換器207でアナログデジタル変換される。アナログデジタル変換された画像信号は、デジタル信号処理部208を介して全体制御・演算部212によってメモリ部209に書き込まれる。

#### 【0150】

その後、メモリ部209に蓄積されたデータは、全体制御・演算部212の制御により

50

記録媒体制御 I / F 部 213 を介して記録媒体 214 に記録される。或いは、メモリ部 209 に蓄積されたデータは、外部 I / F 回路 210 を介して、直接に外部コンピュータ 215 などに入力してもよい。

#### 【0151】

図 13 は、本実施形態による撮像システムにおける光学系の配置例を示す概略図である。図 13 に示す光学系の配置例は、2 次結像位相差検出型オートフォーカスシステムを搭載した一眼レフカメラを想定したものである。

#### 【0152】

被写体像は、撮影レンズ 222 を介してカメラボディ 220 の内部に入射する。撮影レンズ 222 は、被写体像を固体撮像装置 204 上に一時結像させるためのレンズである。

撮影レンズ 222 を通過した被写体像は、クイックリターンミラー 224 へと導かれる。クイックリターンミラー 224 は、数十 % 程度の透過率を有するハーフミラーである。これにより、被写体像は、フォーカルプレーンシャッタ 226 を介して固体撮像装置 204 へと導かれるとともに、ファインダースクリーン 228 を介してファインダ 230 へと導かれる。クイックリターンミラー 224 と固体撮像装置 204との間にはサブミラー 232 が配置されており、サブミラー 232 により反射された被写体像を、反射ミラー 234 及び 2 次結像レンズ 236 を介して A F センサ 205 に再結像できるようになっている。

10

#### 【0153】

第 1 乃至第 5 実施形態において説明したように、これまでの実施形態に示した光電変換装置 100 を用いて A F センサ 205 を構成することにより、焦点検出精度を向上することができる。したがって、この A F センサ 205 を用いた本実施形態の撮像システムによれば、より高精細な画像を取得することが可能となる。

20

#### 【0154】

##### [第 7 実施形態]

本発明の第 7 実施形態による撮像システム及び移動体について、図 14 を用いて説明する。図 14 は、本実施形態による撮像システム及び移動体の構成を示す図である。

#### 【0155】

図 14 (a) は、車載カメラに関する撮像システムの一例を示したものである。撮像システム 300 は、撮像装置 310 を有する。撮像装置 310 は、必ずしも画像の取得を目的としたものに限られず、上記第 1 乃至第 5 実施形態のいずれかに記載の光電変換装置 100 を適用することも可能である。撮像システム 300 は、撮像装置 310 により取得された複数の画像データに対し、画像処理を行う画像処理部 312 と、撮像システム 300 により取得された複数の画像データから視差（視差画像の位相差）の算出を行う視差取得部 314 を有する。また、撮像システム 300 は、算出された視差に基づいて対象物までの距離を算出する距離取得部 316 と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部 318 と、を有する。ここで、視差取得部 314 や距離取得部 316 は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部 318 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA (Field Programmable Gate Array) や ASIC (Application Specific Integrated circuit) 等によって実現されてもよいし、これらの組合せによって実現されてもよい。

30

40

#### 【0156】

撮像システム 300 は車両情報取得装置 320 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、撮像システム 300 は、衝突判定部 318 での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御 ECU 330 が接続されている。また、撮像システム 300 は、衝突判定部 318 での判定結果に基づいて、ドライバーへ警報を発する警報装置 340 とも接続

50

されている。例えば、衝突判定部 318 の判定結果として衝突可能性が高い場合、制御 E C U 330 はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置 340 は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

#### 【0157】

本実施形態では、車両の周囲、例えば前方又は後方を撮像システム 300 で撮像する。図 14 (b) に、車両前方（撮像範囲 350）を撮像する場合の撮像システムを示した。車両情報取得装置 320 が、撮像システム 300 ないしは撮像装置 310 に指示を送る。このような構成により、測距の精度をより向上させることができる。

10

#### 【0158】

上記では、他の車両と衝突しないように制御する例を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。更に、撮像システムは、自車両等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体（移動装置）に適用することができる。加えて、移動体に限らず、高度道路交通システム（ITS）等、広く物体認識を利用する機器に適用することができる。

#### 【0159】

##### [変形実施形態]

本発明は、上記実施形態に限らず種々の変形が可能である。

20

#### 【0160】

例えば、いずれかの実施形態の一部の構成を他の実施形態に追加した例や、他の実施形態の一部の構成と置換した例も、本発明の実施形態である。

#### 【0161】

また、上記実施形態では、電荷排出トランジスタ M7 を含む画素 P を示したが、画素 P は必ずしも電荷排出トランジスタ M7 を有する必要はない。この場合、前述のように、転送トランジスタ M1 をオフにするタイミングで露光期間の開始時刻を規定することができる。

#### 【0162】

また、上記第 1 乃至第 5 実施形態では、本発明の光電変換装置を AF センサに適用した例を示したが、本発明の光電変換装置の用途は AF センサに限定されるものではない。例えば、本発明の光電変換装置は、AE センサ等に適用することも可能である。

30

#### 【0163】

また、上記第 6 及び第 7 実施形態に示した撮像システムは、本発明の光電変換装置を適用し得る撮像システム例を示したものであり、本発明の光電変換装置を適用可能な撮像システムは図 12 乃至図 14 に示した構成に限定されるものではない。

#### 【0164】

なお、上記実施形態は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

40

#### 【符号の説明】

#### 【0165】

P … 画素

10 … 画素領域

12, 14 … 制御線

16, 18 … 出力線

20 … 画素制御回路

30, 50 … 読み出し回路

32, 34, 52 … 比較回路

50

3 6 , 5 6 ... ランプ信号発生回路

3 8 , 5 8 ... カウンタ回路

4 0 , 6 0 ... 信号処理回路

7 0 ... 制御回路

1 0 0 ... 光電変換装置

1 0 1 , 1 0 3 ... 基準部

1 0 2 , 1 0 4 ... 参照部

2 0 0 , 3 0 0 ... 撮像システム

### 【図面】

【図 1】

【図 2】

10

20

30

40

50

【図3】

【図4】

10

20

【図5】

【図6】

30

40

50

【図 7】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

(a)

(b)

10

20

30

40

50

---

フロントページの続き

## (51)国際特許分類

|        |                 |     |        |       |

|--------|-----------------|-----|--------|-------|

| G 02 B | 7/34 (2021.01)  | F I | G 02 B | 7/34  |

| G 03 B | 13/36 (2021.01) |     | G 03 B | 13/36 |

| G 03 B | 15/00 (2021.01) |     | G 03 B | 15/00 |

V

## (56)参考文献

特開2018-191040 (JP, A)

特開2009-089143 (JP, A)

特開2012-124791 (JP, A)

特開2018-107724 (JP, A)

特開2018-107747 (JP, A)

特開2013-054333 (JP, A)

## (58)調査した分野 (Int.Cl., DB名)

H 04 N 25 / 617

H 04 N 23 / 54

H 04 N 23 / 60

H 04 N 25 / 76

H 04 N 25 / 779

G 02 B 7 / 02

G 02 B 7 / 34

G 03 B 13 / 36

G 03 B 15 / 00