US 20050130448A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2005/0130448 A1

## (10) Pub. No.: US 2005/0130448 A1 (43) Pub. Date: Jun. 16, 2005

## Olsen et al.

### (54) METHOD OF FORMING A SILICON OXYNITRIDE LAYER

(75) Inventors: Christopher Olsen, Fremont, CA (US);

Faran Nouri, Los Altos, CA (US);

Thai Cheng Chua, San Jose, CA (US)

Correspondence Address: PATENT COUNSEL APPLIED MATERIALS, INC. Legal Affairs Department P.O. Box 450A Santa Clara, CA 95052 (US)

- (73) Assignee: Applied Materials, Inc.

- (21) Appl. No.: 10/736,061

- (22) Filed: Dec. 15, 2003

## **Publication Classification**

- (52) U.S. Cl. ..... 438/786; 257/649

#### (57) **ABSTRACT**

A SiO<sub>x</sub>N<sub>y</sub> gate dielectric and a method for forming a SiO<sub>x</sub>N<sub>y</sub> gate dielectric by heating a structure comprising a silicon oxide film on a silicon substrate in an atmosphere comprising NH<sub>3</sub> and then exposing the structure to a plasma comprising a nitrogen source are provided. In one aspect, the structure is annealed after it is exposed to a plasma comprising a nitrogen source. In another aspect, a SiO<sub>x</sub>N<sub>y</sub> gate dielectric is formed in an integrated processing system by heating a structure comprising a silicon oxide film on a silicon substrate in an atmosphere comprising NH<sub>3</sub> in one chamber of the integrated processing system and then exposing the structure to a plasma comprising a nitrogen source in another chamber of the integrated processing system and then exposing the structure to a plasma comprising a nitrogen source in another chamber of the integrated processing system.

FIG. 6

#### METHOD OF FORMING A SILICON OXYNITRIDE LAYER

#### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] Embodiments of the present invention generally relate to a method of forming a gate dielectric. More particularly, embodiments of the invention relate to a method of forming a silicon oxynitride  $(SiO_xN_y)$  gate dielectric.

[0003] 2. Description of the Related Art

**[0004]** Integrated circuits are composed of many, e.g., millions, of devices such as transistors, capacitors, and resistors. Transistors, such as field effect transistors, typically include a source, a drain, and a gate stack. The gate stack typically includes a substrate, such as a silicon substrate, a gate dielectric, such as silicon dioxide, SiO<sub>2</sub>, on the substrate, and a gate electrode, such as polycrystalline silicon, on the gate dielectric.

**[0005]** As integrated circuit sizes and the sizes of the transistors thereon decrease, the gate drive current required to increase the speed of the transistor has increased. Because the drive current increases as the gate capacitance increases, and capacitance is inversely proportional to the gate dielectric thickness, decreasing the dielectric thickness is one method of increasing the drive current.

[0006] Attempts have been made to reduce the thickness of SiO<sub>2</sub> gate dielectrics below 20 Å. However, it has been found that the use of thin SiO<sub>2</sub> gate dielectrics below 20 Å often results in undesirable effects on gate performance and durability. For example, boron from a boron doped gate electrode can penetrate through a thin SiO<sub>2</sub> gate dielectric into the underlying silicon substrate. Also, there is typically an increase in gate leakage, i.e., tunneling, with thin dielectrics that increases the amount of power consumed by the gate. Thin SiO<sub>2</sub> gate dielectrics may be susceptible to hot carrier damage, in which high energy carriers traveling across the dielectrics may also be susceptible to negative bias temperature instability (NBTI), wherein the threshold voltage or drive current drifts with operation of the gate.

[0007] One method that has been used to address the problems with thin  $SiO_2$  gate dielectrics is to incorporate nitrogen into the  $SiO_2$  layer to form a  $SiO_xN_y$  gate dielectric. Incorporating nitrogen into the  $SiO_2$  layer blocks boron penetration into the underlying silicon substrate and raises the dielectric constant of the gate dielectric, allowing the use of a thicker dielectric layer.

[0008] Heating a silicon oxide layer in the presence of ammonia ( $NH_3$ ) has been used to convert a  $SiO_2$  layer to a  $SiO_xN_y$  layer. However, the conventional methods of heating a silicon oxide layer in the presence of  $NH_3$  in a furnace have typically resulted in non-uniform incorporation of nitrogen across the  $SiO_2$  layer in different parts of the furnace due to air flow when the furnace is opened or closed. Additionally, oxygen or water vapor contamination of the  $SiO_2$  layer may block incorporation of nitrogen into the  $SiO_2$  layer.

[0009] Plasma nitriding (DPN) has also been used to convert a  $SiO_2$  layer to a  $SiO_xN_y$  layer. Gate stacks with a

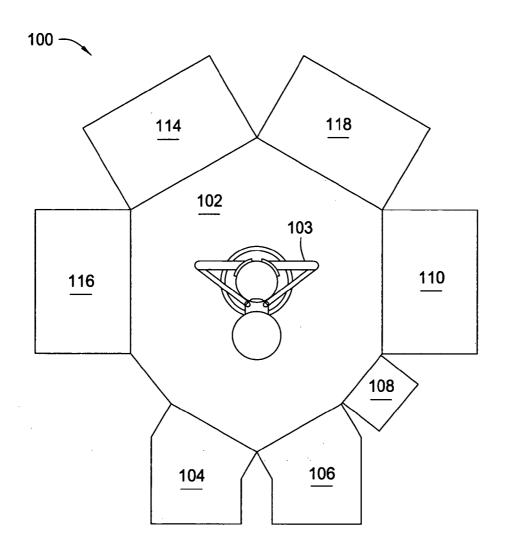

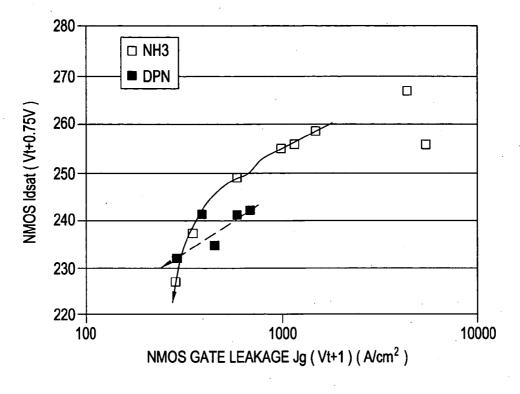

high PMOS drive current and a low gate leakage have been formed using plasma nitriding. However, attempts to form gate stacks with a high N-channel metal-oxide semiconductor (NMOS) drive current and a low gate leakage using plasma nitriding have been unsuccessful at less than 12 Å EOT (equivalent oxide thickness). For example, FIG. 1 shows that heating a silicon oxide layer in the presence of NH<sub>a</sub> results in a higher NMOS drive current at a normalized voltage of the threshold voltage +0.75 V (Idsat(Vt+0.75V)) relative to NMOS gate leakage at a normalized voltage of the threshold voltage +1 V (Jg(Vt+1)) than plasma nitriding the silicon oxide layer. Additionally, FIG. 2 shows that plasma nitriding a silicon oxide layer results in a higher P-channel metal-oxide semiconductor (PMOS) drive current at a normalized voltage of the threshold voltage +0.75 V (Idsat(Vt+0.75V)) relative to NMOS gate leakage at a normalized voltage of the threshold voltage +1 V (Jg(Vt+1))than heating the silicon oxide layer in the presence of NH<sub>3</sub>.

**[0010]** CMOS circuits typically contain both NMOS and PMOS devices. Thus, there remains a need for a method of depositing a  $SiO_xN_y$  gate dielectric that has a high drive current and low leakage current for both PMOS and NMOS devices.

#### SUMMARY OF THE INVENTION

**[0011]** Embodiments of the present invention generally provide a method of forming a  $SiO_xN_y$  gate dielectric, comprising heating a structure comprising a silicon oxide film on a silicon substrate in an atmosphere comprising  $NH_3$  to incorporate nitrogen into the silicon oxide film, and then exposing the structure to a plasma comprising a nitrogen source to form a  $SiO_xN_y$  gate dielectric on the substrate. In one embodiment, the structure is annealed after the structure is exposed to a plasma comprising a nitrogen source.

**[0012]** Embodiments of the invention also provide a method of forming a  $\text{SiO}_x N_y$  gate dielectric in an integrated processing system, comprising heating a structure comprising a silicon oxide film on a silicon substrate in an atmosphere comprising NH<sub>3</sub> in a first processing chamber of the integrated processing system to incorporate nitrogen into the silicon oxide film, transferring the structure to a second processing chamber of the integrated processing system, and then exposing the structure to a plasma comprising a nitrogen source in the second processing chamber to form a  $\text{SiO}_x N_y$  gate dielectric on the substrate. In one embodiment, the silicon oxide film is formed on the substrate in the integrated processing system, and the structure is not removed from the integrated processing system until after the  $\text{SiO}_x N_y$  gate dielectric is formed.

**[0013]** In another embodiment, a  $SiO_xN_y$  gate dielectric, formed by a method comprising heating a structure comprising a silicon oxide film on a silicon substrate in an atmosphere comprising NH<sub>3</sub> to incorporate nitrogen into the silicon oxide film, and then exposing the structure to a plasma comprising a nitrogen source to form a  $SiO_xN_y$  gate dielectric on the substrate, is provided.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0014]** So that the manner in which the above recited features of the present invention can be understood in detail, a more particular description of the invention, briefly summarized above, may be had by reference to embodiments,

some of which are illustrated in the appended drawings. It is to be noted, however, that the appended drawings illustrate only typical embodiments of this invention and are therefore not to be considered limiting of its scope, for the invention may admit to other equally effective embodiments.

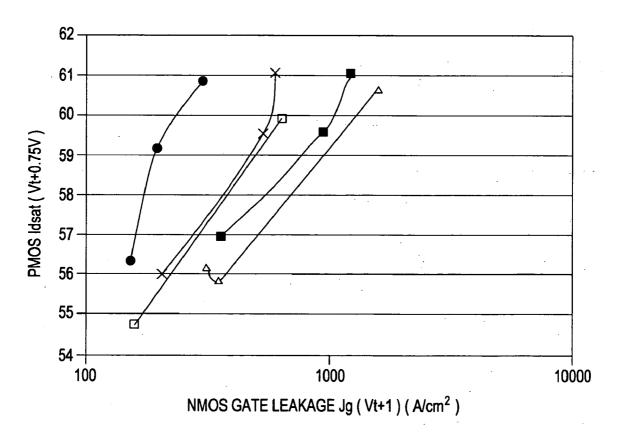

[0015] FIG. 1 is a graph showing NMOS drive current relative to NMOS gate leakage for gate stacks comprising  $SiO_{N_v}$  gate dielectrics.

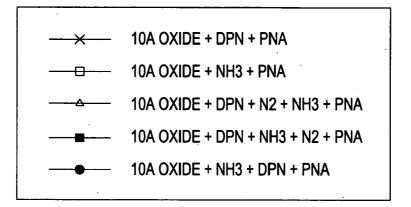

[0016] FIG. 2 is a graph showing PMOS drive current relative to NMOS gate leakage for gate stacks comprising  $SiO_v N_v$  gate dielectrics.

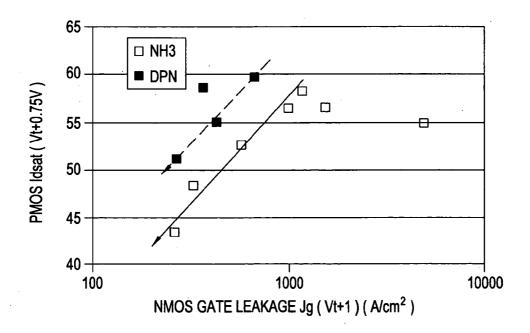

[0017] FIG. 3 is a top schematic view of an integrated processing system.

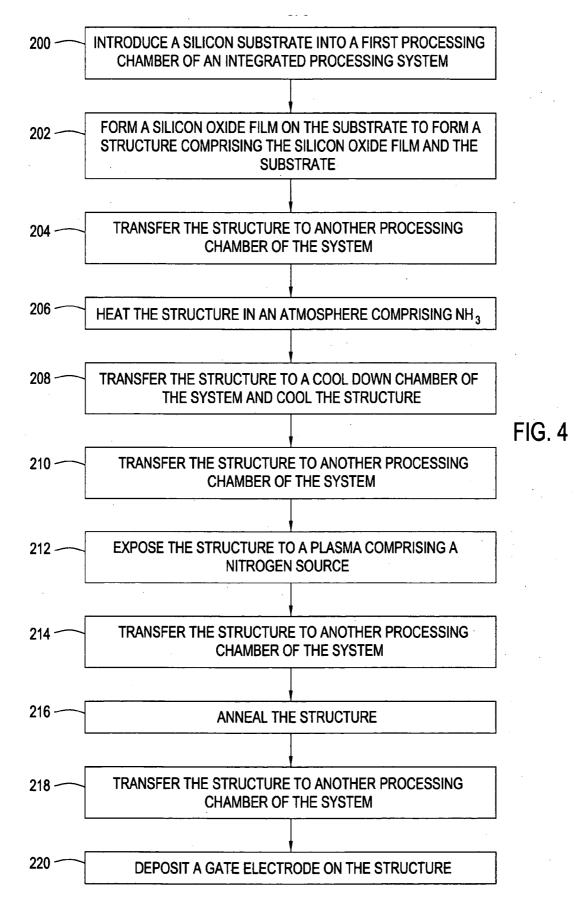

**[0018]** FIG. 4 is a flow chart depicting an embodiment of the invention.

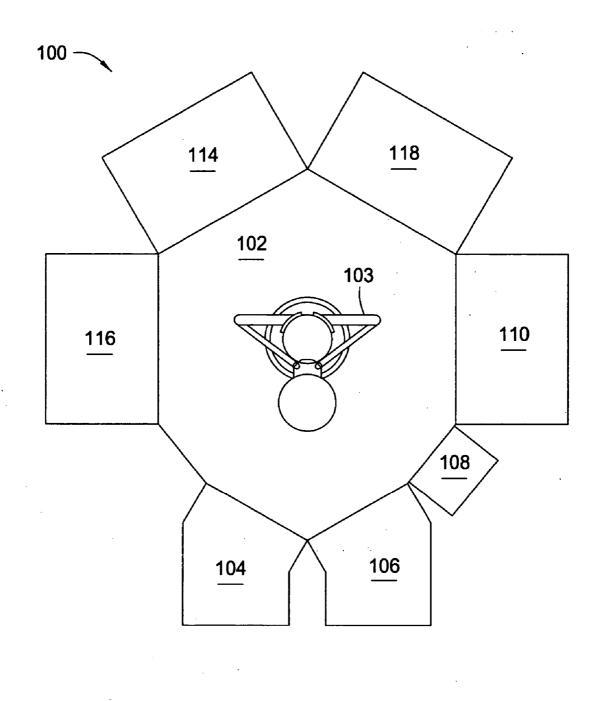

**[0019] FIG. 5** is a top schematic view of an integrated processing system.

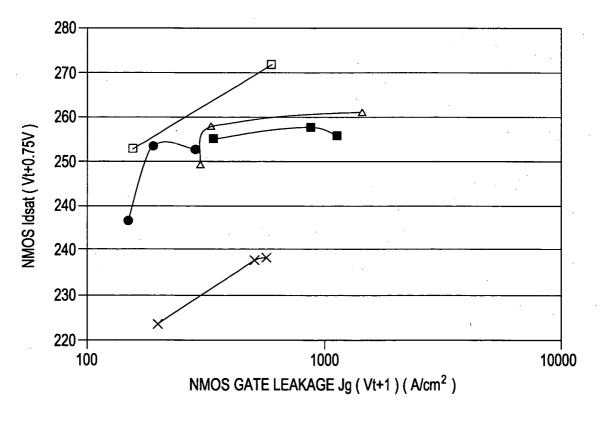

**[0020]** FIG. 6 is a graph showing NMOS drive current relative to NMOS gate leakage for gate stacks comprising  $SiO_{\rm N_v}$  gate dielectrics.

[0021] FIG. 7 is a graph showing PMOS drive current relative to NMOS gate leakage for gate stacks comprising  $SiO_{N_v}$  gate dielectrics.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

**[0022]** Embodiments of the invention include a method for depositing a  $SiO_xN_y$  gate dielectric. Gate stacks including the  $SiO_xN_y$  gate dielectric exhibit desirable electrical properties in both NMOS and PMOS devices.

[0023] In one embodiment, a  $SiO_xN_y$  gate dielectric is formed by heating a structure comprising a silicon oxide film on a silicon substrate in an atmosphere comprising NH<sub>3</sub>. As defined herein, a silicon substrate includes single layer silicon substrates, such as silicon wafers, or structures that include a silicon layer on one or more other layers. The silicon oxide film on the silicon substrate may be formed by exposing the silicon substrate to an atmosphere comprising oxygen to oxidize the top surface of the substrate. The atmosphere comprising oxygen may be an ambient of oxygen (O<sub>2</sub>), hydrogen (H<sub>2</sub>) and O<sub>2</sub>, H<sub>2</sub> and nitrous oxide (N<sub>2</sub>O), O<sub>2</sub> and an inert gas, or combinations thereof. The silicon oxide film may have a thickness of about 4 Å to about 16 Å, for example. In one embodiment, the silicon substrate may be exposed to an atmosphere comprising oxygen at a substrate temperature between about 700° C. and about 1100° C. and at a pressure between about 0.1 Torr and about 800 Torr for a time of between about 1 second and about 120 seconds. Preferably, the temperature is between about 750° C. and about 1000° C., and the pressure is between about 0.5 Torr and about 50 Torr.

[0024] Heating the structure comprising a silicon oxide film in an atmosphere comprising  $NH_3$  incorporates nitrogen into the silicon oxide film such that the top surface of the silicon oxide film is nitrogen-doped. The structure may be heated to a temperature of at least about 700° C. at a pressure of less than about 100 Torr, such as a pressure between about 0.1 Torr and about 100 Torr. Preferably, the structure is heated to a temperature between about 700° C. and about

1100° C., such as about 1050° C., at an NH<sub>3</sub> partial pressure of about 1 Torr. The structure may be heated for a time of between about 1 second and about 120 seconds or for a period of time sufficient to nitrogen dope the top surface of the silicon oxide film. Preferably, substantially no oxygen is incorporated into the structure while heating the structure in an atmosphere comprising NH<sub>3</sub>.

**[0025]** After the structure is heated in an atmosphere comprising  $NH_3$ , the structure is exposed to a plasma comprising a nitrogen source to incorporate more nitrogen into the silicon oxide film, thereby forming the  $SiO_xN_y$  gate dielectric. The nitrogen source may be nitrogen ( $N_2$ ),  $NH_3$ , or combinations thereof. The plasma may further comprise an inert gas, such as helium, argon, or combinations thereof. The pressure during the plasma exposure of the substrate may be between about 1 mTorr and about 30 mTorr, such as between about 1 mTorr and about 10 mTorr.

**[0026]** Preferably, the  $SiO_xN_y$  gate dielectric described herein comprises at least 5 atomic percent nitrogen. In one embodiment, the  $SiO_xN_y$  gate dielectric comprises between about 5 atomic percent nitrogen and about 15 atomic percent nitrogen.

[0027] Optionally, the structure is annealed after exposure to the plasma. In one embodiment, the structure is annealed in an atmosphere comprising  $O_2$ . The partial pressure of  $O_2$ during the anneal may be less than 50 Torr, such as between about 10 mTorr and about 50 Torr. The structure may be annealed at a temperature of between about 700° C. and about 1100° C., such as at a temperature between about 950° C. and about 1100° C. In another embodiment, the structure is annealed in an inert or reducing atmosphere and then annealed in an atmosphere comprising O2 as described above. The structure may be annealed in the inert or reducing atmosphere at a temperature of between about 700° C. and about 1100° C., such as at a temperature between about 950° C. and about 1100° C. For example, the structure may be annealed at a temperature of about 1000° C. in an atmosphere comprising N<sub>2</sub> at an N<sub>2</sub> partial pressure of between about 1 Torr and about 760 Torr.

**[0028]** After the structure is exposed to the plasma and optionally annealed, a gate electrode, such as a polysilicon layer, may be deposited on the  $SiO_xN_y$  gate dielectric to complete a gate stack.

[0029] Integrated Processing Sequence

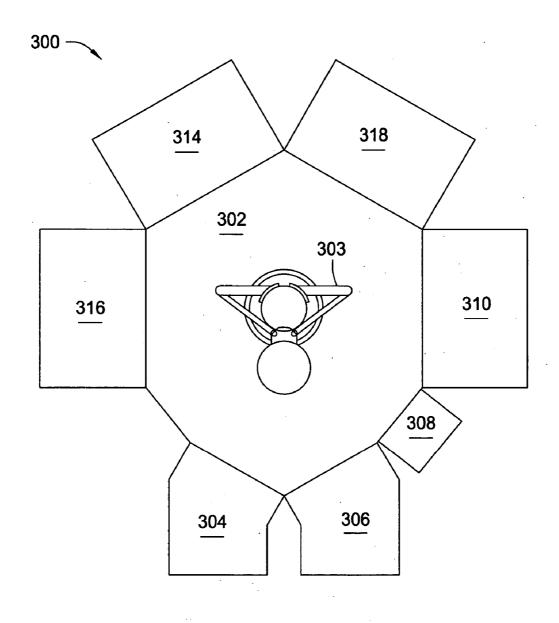

[0030] In a further embodiment, a  $SiO_xN_y$  gate dielectric may be formed on a substrate in an integrated processing system, such as an integrated semiconductor processing system, in a method in which the substrate is not removed from the integrated processing system until after the  $SiO_xN_y$ gate dielectric is formed. An example of an integrated processing system 100 that may be used is the Gate Stack Centura® system, available from Applied Materials, Inc. of Santa Clara, Calif., which is shown in FIG. 3. The integrated processing system 100 may include a central transfer chamber 102, transfer robot 103, load locks 104, 106, a cool down chamber 108, a thermal processing chamber 110, a plasma processing chamber 114, a rapid thermal processing (RTP) chamber 116, and a CVD processing chamber 118. CVD processing chamber 118 may be a low pressure chemical vapor deposition chamber (LPCVD), such as a POLYgen chamber, available from Applied Materials.

[0031] The processing conditions for embodiments in which the SiO<sub>x</sub>N<sub>y</sub> gate dielectric is formed in an integrated processing system may be the same as the processing conditions described above for the formation of the silicon oxide film and the SiO<sub>x</sub>N<sub>y</sub> gate dielectric. For example, in one embodiment a structure comprising a silicon dioxide film on a silicon substrate may be heated in an atmosphere comprising NH<sub>3</sub> in a first processing chamber of the integrated processing system to incorporate nitrogen into the silicon oxide film. Because the substrate is exposed to an atmosphere comprising NH<sub>3</sub> within an enclosed integrated processing system, contaminating oxygen is typically not incorporated into the structure during the heating in an atmosphere comprising NH<sub>3</sub>. The structure may then be transferred to a second processing chamber of the integrated processing system and exposed to a plasma comprising a nitrogen source in the second processing chamber. Optionally, after exposing the structure to the plasma, the structure may be transferred to a third processing chamber of the integrated processing system and annealed in the third processing chamber.

**[0032]** In another embodiment, a substrate is introduced into an integrated processing system and a silicon oxide film, a  $SiO_xN_y$  gate dielectric, and a gate electrode are deposited on the substrate without removing the substrate from the integrated processing system. This embodiment will be described below with respect to **FIGS. 3 and 4**.

[0033] A silicon substrate may be introduced into the integrated processing system 100 via a load lock 102 or 104 and placed in RTP chamber 116, where a silicon oxide film may be formed on the silicon substrate, as shown in steps 200 and 202 of FIG. 4. The structure, including the substrate and the silicon oxide film, may then be transferred to thermal processing chamber 110, where it is heated in an atmosphere comprising NH<sub>3</sub> to incorporate nitrogen into the silicon oxide film, as shown in steps 204 and 206. The structure may then be transferred to cool down chamber 108 and cooled, for example, to less than about 100° C. in about 1 to about 2 minutes, as shown in step 208. The structure may then be transferred to plasma processing chamber 114, where it is exposed to a plasma comprising a nitrogen source to incorporate more nitrogen into the silicon oxide film and form the SiO<sub>2</sub>N<sub>2</sub> gate dielectric, as shown in steps 210 and 212. Optionally, the structure may be transferred to RTP chamber 116 where the structure may be annealed, as shown in steps 214 and 216. The structure may then be transferred to CVD processing chamber 118, as shown in step 218, and a gate electrode, such as a polysilicon layer or an amorphous silicon layer may be deposited on the structure, as shown in step 220. The structure may then be removed from the integrated processing system 100 via a load lock 102 or 104.

[0034] In the embodiment described above with respect to FIGS. 3 and 4, the silicon oxide film is formed on the substrate in RTP chamber 116 in one step and the structure is annealed in the same RTP chamber 116 in another step. In an alternative embodiment, a second RTP chamber is configured on an integrated processing system 300, as shown in FIG. 5, and the silicon oxide film is formed in one RTP chamber in one step and the structure is annealed in a different RTP chamber in another step. The integrated processing system 300 may include a central transfer chamber 302, transfer robot 303, load locks 304, 306, a cool down chamber 308, a thermal processing chamber 310, a plasma

processing chamber **314**, a rapid thermal processing (RTP) chamber **316**, and a RTP chamber **318**.

[0035] A silicon substrate may be introduced into the integrated processing system 300 via a load lock 302 or 304 and placed in RTP chamber 316, where a silicon oxide film may be formed on the silicon substrate. The structure, including the substrate and the silicon oxide film, may then be transferred to thermal processing chamber 310, where it is heated in an atmosphere comprising NH<sub>3</sub> to incorporate nitrogen into the silicon oxide film. The structure may then be transferred to cool down chamber 308 and cooled, for example, to less than about 100° C. in about 1 to about 2 minutes. The structure may then be transferred to plasma processing chamber 314, where it is exposed to a plasma comprising a nitrogen source to incorporate more nitrogen into the silicon oxide film and form the SiO<sub>x</sub>N<sub>y</sub> gate dielectric. Optionally, the structure may then be transferred to RTP chamber 318 where the structure may be annealed. After the structure is annealed, the structure may be transferred out of the integrated processing system 300 via load lock 302 or 304 to a processing chamber (not shown) external to the integrated processing system such as a low pressure chemical vapor deposition chamber (LPCVD), for depositing a gate electrode, such as a polysilicon layer or an amorphous silicon layer.

[0036] While the above embodiments are described with respect to **FIGS. 3 and 5**, it is recognized that other integrated processing systems may be used with the embodiments described herein.

[0037] Performance of  $SiO_xN_y$  Gate Dielectrics in NMOS and PMOS Devices

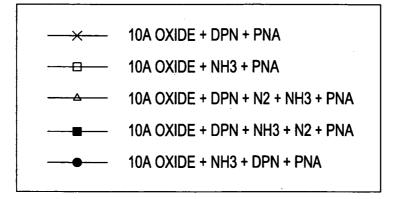

[0038] FIGS. 6 and 7 respectively show the NMOS drive current versus NMOS gate leakage and PMOS drive current versus NMOS gate leakage for gate stacks including a structure comprising a  $\tilde{SiO}_xN_y$  gate dielectric formed according to embodiments of the invention as well as for gate stacks formed according to other methods. The following process sequences were compared in FIGS. 6 and 7: a silicon substrate was oxidized to form a 10 Å silicon oxide layer on the substrate (10 Å oxide), plasma treated in nitrogen atmosphere (decoupled plasma nitridation, DPN), and then annealed (post nitridation anneal, PNA); 10 Å oxide, heated in an atmosphere comprising NH<sub>3</sub> (NH<sub>3</sub>), and then PNA; 10 Å oxide, DPN, heated in an atmosphere comprising  $N_2$  ( $N_2$ ) and then NH<sub>3</sub>, and then PNA; 10 Å oxide, DPN, heated in an atmosphere comprising NH<sub>3</sub>, heated in an atmosphere comprising N2, and then PNA; and 10 Å oxide, NH<sub>3</sub>, DPN, and then PNA, according to an embodiment of the invention. The PNA was performed at 1000° C. for 15 seconds in atmosphere with an  $O_2$  partial pressure of 60 mTorr.

**[0039]** FIG. 6 illustrates that while a process sequence in which a structure is heated in an atmosphere comprising  $NH_3$  and then annealed provides low NMOS gate leakage at a high NMOS drive current, a process sequence in which a structure is heated in an atmosphere comprising  $NH_3$ , treated with a plasma comprising nitrogen, and then annealed, as described in embodiments of the invention, also provides desirable NMOS performance.

**[0040] FIG. 7** illustrates that a process in which a structure is heated in an atmosphere comprising NH<sub>3</sub>, treated with a

plasma comprising nitrogen, and then annealed, as described in embodiments of the invention, provides less NMOS gate leakage at a higher PMOS drive current than the other processes tested.

[0041] Thus, a process in which a structure is heated in an atmosphere comprising  $NH_3$ , treated with a plasma comprising nitrogen, and then annealed, as described in embodiments of the invention, can provide gate stacks that have desirable low gate leakage relative to both NMOS drive currents and PMOS drive currents. Furthermore, a process in which a structure is treated with a plasma comprising nitrogen, heated in an atmosphere comprising  $NH_3$ , and then annealed provides structures that have significantly higher NMOS gate leakages for comparable NMOS and PMOS drive currents.

**[0042]** It is believed that heating the structure in an atmosphere comprising  $NH_3$  prior to treating the structure with a plasma comprising nitrogen smoothens the interface between the gate dielectric and the underlying silicon substrate, resulting in enhanced device performance and reliability. It is also believed that the formation of a slightly thicker oxide film by heating the structure first in an atmosphere comprising  $NH_3$  prior to plasma treating the structure enhances the performance characteristics of a PMOS device.

**[0043]** While the foregoing is directed to embodiments of the present invention, other and further embodiments of the invention may be devised without departing from the basic scope thereof, and the scope thereof is determined by the claims that follow.

What is claimed is:

1. A method of forming a  $SiO_xN_y$  gate dielectric, comprising:

- providing a structure comprising a silicon oxide film formed on a silicon substrate;

- heating the structure in an atmosphere comprising  $\rm NH_3$  to incorporate nitrogen into the silicon oxide film; and then

- exposing the structure to a plasma comprising a nitrogen source to form a  $SiO_xN_y$  gate dielectric on the substrate.

**2**. The method of claim 1, further comprising annealing the structure after the exposing the structure to the plasma.

3. The method of claim 2, wherein the annealing is performed in an atmosphere comprising  $O_2$ .

4. The method of claim 3, wherein the annealing further comprises annealing the structure in an inert or reducing atmosphere before the annealing in an atmosphere comprising  $O_2$ .

5. The method of claim 1, wherein the nitrogen source is selected from the group consisting of  $N_2$ ,  $NH_3$ , and combinations thereof.

6. The method of claim 1, wherein heating the structure comprises heating the structure to a temperature of at least about  $700^{\circ}$  C. at a pressure of less than about 100 Torr.

7. The method of claim 1, wherein exposing the structure to a plasma is performed at a pressure of between about 1 mTorr and about 30 mTorr.

**8**. The method of claim 1, further comprising forming the silicon oxide film by oxidizing a top surface of the silicon substrate.

**9**. The method of claim 1, wherein substantially no oxygen is incorporated into the structure while heating the structure in an atmosphere comprising  $NH_3$ .

10. A method of forming a  $SiO_xN_y$  gate dielectric in an integrated processing system, comprising:

- heating a structure comprising a silicon oxide film formed on a silicon substrate in an atmosphere comprising  $NH_3$ in a first processing chamber of the integrated processing system to incorporate nitrogen into the silicon oxide film;

- transferring the structure to a second processing chamber of the integrated processing system; and then

- exposing the structure to a plasma comprising a nitrogen source in the second processing chamber to form a SiO  $N_v$  gate dielectric on the substrate.

- 11. The method of claim 10, further comprising:

- transferring the structure to a third processing chamber of the integrated processing system; and

- annealing the substrate in the third processing chamber. 12. The method of claim 11, further comprising:

- introducing the silicon substrate into the integrated processing system; and

- forming the silicon oxide film on the substrate in the third processing chamber of the integrated processing system to form the structure comprising a silicon oxide film on a silicon substrate.

- 13. The method of claim 12, further comprising:

- transferring the structure to a fourth processing chamber of the integrated processing system after the annealing the substrate; and

- depositing a polysilicon layer on the  $SiO_xN_y$  gate dielectric in the fifth processing chamber.

- 14. The method of claim 11, further comprising:

- introducing the silicon substrate into the integrated processing system; and

- forming the silicon oxide film on the substrate in a fourth processing chamber of the integrated processing system to form the structure comprising a silicon oxide film on a silicon substrate.

- 15. The method of claim 14, further comprising:

- transferring the structure to a fifth processing chamber external to the integrated processing system after the exposing the structure to the plasma; and

- depositing a polysilicon layer on the  $SiO_xN_y$  gate dielectric in the fifth processing chamber.

16. The method of claim 11, wherein the annealing is performed in an atmosphere comprising  $O_2$ .

17. The method of claim 16, wherein the annealing further comprises annealing the structure in an inert or reducing atmosphere before the annealing in an atmosphere comprising  $O_2$ .

18. The method of claim 10, further comprising transferring the structure to a cool down chamber after the heating and before the transferring the structure to a second processing chamber. 19. A  ${\rm SiO}_{\rm x} N_{\rm y}$  gate dielectric, formed by a method comprising:

- heating a structure comprising a silicon oxide film formed on a silicon substrate in an atmosphere comprising  $NH_3$ to incorporate nitrogen into the silicon oxide film; and then

- exposing the structure to a plasma comprising a nitrogen source to form a  $SiO_xN_y$  gate dielectric on the substrate.

20. The  $SiO_xN_y$  gate dielectric of claim 19, wherein the gate dielectric comprises at least 5% nitrogen.

**21**. The  $SiO_xN_y$  gate dielectric of claim 19, wherein the method further comprises annealing the structure after the exposing the structure to a plasma.

22. The  $SiO_xN_y$  gate dielectric of claim 19, wherein substantially no oxygen is incorporated into the structure while heating the structure in an atmosphere comprising  $NH_3$ .

23. The  $SiO_xN_y$  gate dielectric of claim 19, wherein the nitrogen source is selected from the group consisting of N<sub>2</sub>, NH<sub>3</sub>, and combinations thereof.

24. The  $SiO_xN_y$  gate dielectric of claim 19, wherein the method further comprises forming the silicon oxide film by oxidizing a top surface of the silicon substrate.

**25**. The  $SiO_xN_y$  gate dielectric of claim 19, wherein the method further comprises placing the silicon substrate in an integrated processing system and not removing the structure from the integrated processing system until after the gate dielectric is formed.

**26**. The  $SiO_xN_y$  gate dielectric of claim 25, wherein the method further comprises depositing a polysilicon layer on the substrate, wherein the structure is not removed from the integrated processing system until after the polysilicon layer is deposited.

\* \* \* \* \*