(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-13462

(P2006-13462A)

(43) 公開日 平成18年1月12日(2006.1.12)

(51) Int.CI.

H01L 31/02

(2006.01)

F 1

H01L 31/02

A

テーマコード(参考)

5 F O 8 8

審査請求 未請求 請求項の数 21 O L (全 28 頁)

(21) 出願番号 特願2005-147106 (P2005-147106)

(22) 出願日 平成17年5月19日 (2005.5.19)

(31) 優先権主張番号 特願2004-152160 (P2004-152160)

(32) 優先日 平成16年5月21日 (2004.5.21)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 西 和夫

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 丸山 純矢

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 楠本 直人

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 菅原 裕輔

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】半導体装置及びその作製方法

## (57) 【要約】

## 【課題】

従来、増幅素子を備えた光センサを作製するには、薄膜トランジスタの形成を待って、光電変換層を形成しなければならならず、スループットが悪かった。そこで、本発明では、薄膜トランジスタを形成する工程と光電変換層を形成する工程を平行して行うことにより短時間で作製した半導体装置及びその作製プロセスを提供することを目的とする。

## 【解決手段】

本発明は、第1の基板上に薄膜トランジスタを形成し、第2の基板上に光電変換素子を形成し、薄膜トランジスタと光電変換素子とが内側になるように相対した第1の基板と第2の基板との間に導電膜を狭持させることで、薄膜トランジスタと光電変換素子を電気的に接続させて半導体装置を作製する。これにより、工程数の増加を抑え、スループットの高い半導体装置の作製方法を提供することができる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

第1の基板に近接する薄膜トランジスタと、

第2の基板に近接する光電変換素子と、

相対した前記第1の基板と前記第2の基板との間に挟持された接着剤と導電性粒子を有し、

前記導電性粒子を介して、前記薄膜トランジスタと前記光電変換素子は電気的に接続することを特徴とする半導体装置。

**【請求項 2】**

第1の基板に近接する薄膜トランジスタと、

第2の基板に近接する光電変換素子と、

前記薄膜トランジスタと前記光電変換素子が内側になるように相対した前記第1の基板と前記第2の基板との間に挟持された接着剤と導電性粒子を有し、

前記導電性粒子を介して、前記薄膜トランジスタと前記光電変換素子は電気的に接続することを特徴とする半導体装置。

**【請求項 3】**

請求項1または請求項2において、前記接着剤と前記導電性粒子は異方性導電接着剤であることを特徴とする半導体装置。

**【請求項 4】**

請求項3において、前記異方性導電接着剤は異方性導電性フィルムまたは異方性導電ペーストであることを特徴とする半導体装置。 20

**【請求項 5】**

第1の基板に近接する薄膜トランジスタと、

第2の基板に近接する光電変換素子と、

相対した前記第1の基板と前記第2の基板との間に挟持された、封止材及び金属層を有し、

前記金属層を介して、前記薄膜トランジスタと前記光電変換素子は電気的に接続することを特徴とする半導体装置。

**【請求項 6】**

第1の基板に近接する薄膜トランジスタと、

第2の基板に近接する光電変換素子と、

前記薄膜トランジスタと前記光電変換素子が内側になるように相対した前記第1の基板と前記第2の基板との間に挟持された、封止材及び金属層を有し、

前記金属層を介して、前記薄膜トランジスタと前記光電変換素子は電気的に接続することを特徴とする半導体装置。 30

**【請求項 7】**

請求項1乃至請求項6のいずれか一項において、前記薄膜トランジスタを有する回路は、前記光電変換素子の出力を增幅することを特徴とする半導体装置。

**【請求項 8】**

請求項1乃至請求項7のいずれか一項において、前記光電変換素子はアモルファスシリコンまたは微結晶シリコンからなる光電変換層を有することを特徴とする半導体装置。 40

**【請求項 9】**

請求項1乃至請求項8のいずれか一項において、前記第1の基板は、プラスチック基板または有機樹脂部材からなる基板であることを特徴とする半導体装置。

**【請求項 10】**

請求項1乃至請求項9のいずれか一項において、前記第2の基板は、プラスチック基板または有機樹脂部材からなる基板であることを特徴とする半導体装置。

**【請求項 11】**

請求項1乃至請求項10のいずれか一項において、前記半導体装置は携帯電話であることを特徴とする半導体装置。 50

**【請求項 1 2】**

第1の基板上に薄膜トランジスタを形成し、

第2の基板上に光電変換素子を形成し、

相対させた前記第1の基板と前記第2の基板との間で、前記薄膜トランジスタと前記光電変換素子を電気的に接続させることを特徴とする半導体装置の作製方法。

**【請求項 1 3】**

第1の基板上に薄膜トランジスタを形成し、

第2の基板上に光電変換素子を形成し、

相対させた前記第1の基板と前記第2の基板との間に金属層を挟持させることで、前記薄膜トランジスタと前記光電変換素子を電気的に接続させることを特徴とする半導体装置

10 の作製方法。

**【請求項 1 4】**

第1の基板上に薄膜トランジスタを形成し、

第2の基板上に光電変換素子を形成し、

前記薄膜トランジスタと前記光電変換素子が内側になるように相対させた前記第1の基板と前記第2の基板との間に導電膜を挟持させることで、前記薄膜トランジスタと前記光電変換素子を電気的に接続させることを特徴とする半導体装置の作製方法。

**【請求項 1 5】**

第1の基板上に薄膜トランジスタを形成し、

第2の基板上に光電変換素子を形成し、

前記薄膜トランジスタと前記光電変換素子が内側になるように相対させた前記第1の基板と前記第2の基板との間に金属層及び封止材を挟持させることで、前記薄膜トランジスタと前記光電変換素子を前記金属層を介して電気的に接続させることを特徴とする半導体装置の作製方法。

20

**【請求項 1 6】**

第1の基板上に剥離層を形成し、

前記剥離層上に薄膜トランジスタを形成し、

第2の基板上に光電変換素子を形成し、

前記薄膜トランジスタと前記光電変換素子が内側になるように相対させた前記第1の基板と前記第2の基板との間に導電膜を挟持させることで、前記薄膜トランジスタと前記光電変換素子を電気的に接続させ、

30

前記薄膜トランジスタ及び前記光電変換素子が前記第2の基板に保持された状態で、前記薄膜トランジスタより前記第1の基板を剥離させることを特徴とする半導体装置の作製方法。

**【請求項 1 7】**

第1の基板上に剥離層を形成し、

前記剥離層上に薄膜トランジスタを形成し、

第2の基板上に光電変換素子を形成し、

前記薄膜トランジスタと前記光電変換素子が内側になるように相対させた前記第1の基板と前記第2の基板との間に封止材及び金属層を挟持させることで、前記薄膜トランジスタと前記光電変換素子とを前記金属層を介して電気的に接続させ、

40

前記薄膜トランジスタ及び前記光電変換素子が前記第2の基板に保持された状態で、前記薄膜トランジスタより前記第1の基板を剥離させることを特徴とする半導体装置の作製方法。

**【請求項 1 8】**

請求項16または請求項17において、前記第1の基板を剥離させた後、前記薄膜トランジスタに第3の基板を貼り合わせることを特徴とする半導体装置の作製方法。

**【請求項 1 9】**

請求項18において、前記第3の基板はプラスチック基板または有機樹脂部材からなる基板であることを特徴とする半導体装置の作製方法。

50

**【請求項 20】**

請求項 12 乃至 請求項 19 のいずれか一項において、前記第 1 の基板は、ガラス基板または石英基板であることを特徴とする半導体装置の作製方法。

**【請求項 21】**

請求項 12 乃至 請求項 20 のいずれか一項において、前記薄膜トランジスタを有する回路は、前記光電変換素子の出力を増幅することを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置及びその作製方法に関する。特に光センサを搭載した半導体装置 10 に関する。

**【背景技術】****【0002】**

光センサは、光のセンシングによりスイッチのオン、オフを制御したり、携帯電話等のバックライトの照度を制御したりするのに使用される。さらには、ファクシミリ、複写機、ビデオカメラ、デジタルスチルカメラ等で、映像もしくは画像を電気信号に変換するためのセンサとして広い分野で使用されている。

**【0003】**

光センサは、光電変換層に光が照射されることで光電荷が発生し、電流となり、照射された光の光量に応じた出力をしてことで、光を電気信号に変換する。各光電変換層におけるわずかな光電荷の差を信号として表すことが困難な場合は、光電荷を増幅する回路（以下、増幅回路と示す。）を用いて、そのわずかな差が明確になるよう出力信号を増幅する必要がある。 20

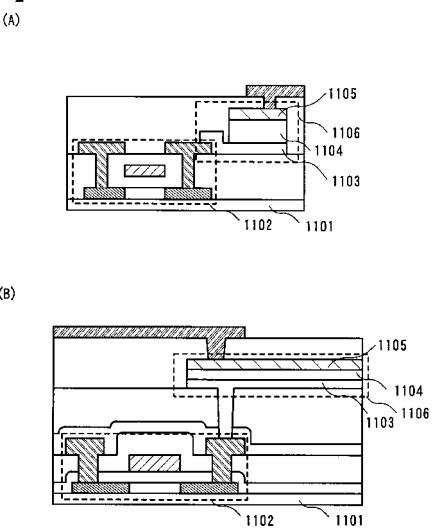

**【0004】**

増幅回路を備えた光センサを作製する場合は、図 11 (A) 及び (B) に示すように、まず基板 1101 上に増幅回路を構成する素子として薄膜トランジスタ 1102 を形成する。その次に、薄膜トランジスタのソース電極またはドレイン電極と接続するように、光電変換素子 1106 のカソード電極 1103 を積層する。その後、カソード電極 1103 上にシリコン層 1104、アノード電極 1105 を形成し、光センサを形成するのが一般的である（例えば、特許文献 1）。 30

**【特許文献 1】特開 2001-265283 号公報（第 13 図参照）****【発明の開示】****【発明が解決しようとする課題】****【0005】**

従来は、図 11 のように、基板 1101 上に薄膜トランジスタ 1102 を形成後、光電変換素子 1106 を形成することで、増幅回路を構成する素子（以下、単に「増幅素子」とも言う）を備える光センサを作製していた。従って、光センサを完成させるまでに時間がかかり、スループットが悪かった。

**【0006】**

加えて、薄膜トランジスタ 1102 の上に積層させて光電変換素子 1106 を形成するため、光電変換素子 1106 は薄膜トランジスタの凹凸の影響を受ける。従って薄膜トランジスタの凹凸がない部分に光電変換素子を設けようとすると受光面積が減少してしまい、光の検出能力が低下するという問題があった。そこで、光の検出能力を高めることが求められていた。 40

**【0007】**

また、増幅回路を薄膜トランジスタで形成する場合は、基板に制約があった。例えばシリコンを用いて半導体膜を形成する場合、シリコンの結晶化や活性化のために、比較的高い温度、例えば 500 以上の加熱工程が必要とされる。このため、基板は耐熱性を持つガラス基板や石英基板に限定される。従って、光センサの部品容積、及び重量が増大してしまうという問題が生じていた。 50

**【 0 0 0 8 】**

また、ガラス基板や石英基板には可撓性がないため、曲面に光センサを実装できず、光センサは平坦な部分にしか設置できなかつた。

**【 0 0 0 9 】**

以上より、本発明は、第1として、半導体装置の作製工程の短縮化や光検出能力の増大を課題とする。第2として、所望の基板上に作製された半導体装置及びその作製方法、薄型で軽量な半導体装置を実現することを課題とする。

**【課題を解決するための手段】****【 0 0 1 0 】**

本発明の特徴の一つは、第1の基板上に薄膜トランジスタを形成し、第2の基板上に光電変換素子を形成する。そして、第1の基板と第2の基板で薄膜トランジスタと光電変換素子を挟むようにして、薄膜トランジスタと光電変換素子の電気的接続をとることで、光センサを有する半導体装置を作製する。また、第1の基板上の薄膜トランジスタは、光電変換素子の出力を増幅する回路を構成することを特徴とする。

**【 0 0 1 1 】**

さらに、上記のように薄膜トランジスタと光電変換素子の電気的接続をした後に、光電変換素子と薄膜トランジスタが第2の基板に保持された状態で、薄膜トランジスタより第1の基板を剥離する。

**【 0 0 1 2 】**

第1の基板を剥離した状態で半導体装置を被実装体に実装しても良い。若しくは、新たに第3の基板として樹脂基板やプリント基板等の可撓性基板を、第1の基板が剥離された半導体装置に貼り合わせてから、半導体装置を被実装体に実装しても良い。

**【 0 0 1 3 】**

上記第1の基板として、耐熱性を有する基板、代表的には、ガラス基板や石英基板等を用いると、増幅回路の薄膜トランジスタを高温で作製できるため、電気特性の良い薄膜トランジスタを得ることができる。しかし、耐熱性がないプラスチック基板又は有機樹脂部材からなる基板であっても、増幅回路として機能する薄膜トランジスタが作製できるのであれば、第1の基板としてプラスチック基板又は有機樹脂部材からなる基板を用いても問題ない。

**【 0 0 1 4 】**

上記第2の基板の材料としては、ガラス、石英、プラスチック又は有機樹脂部材がある。代表的には、P E T (ポリエチレンテレフタレート)、P E N (ポリエチレンナフタレート)、P E S (ポリエーテルスルホン)、ポリプロピレン、ポリプロピレンサルファイド、ポリカーボネート、ポリエーテルイミド、ポリフェニレンサルファイド、ポリフェニレンオキサイド、ポリサルフォン、ポリイミド、またはポリフタールアミドからなるプラスチック基板が挙げられる。また、有機樹脂で形成される部材、代表的にはI Cチップが封止されたパッケージの表面を基板とすることも可能である。また、第2の基板の表面は平面である必要はなく、凹凸面又は曲面であつてもよい。

**【 0 0 1 5 】**

本発明で作製される半導体装置は、増幅回路を構成する素子が形成される第1の基板側からの光をセンシングしても良いし、光電変換素子が形成される第2の基板側からの光をセンシングしても良い。但し第1の基板側からの光を受光する場合は、第1の基板を透光性にすることはもちろんのこと、光電変換層に到達するまでに光が通過する層は透光性の高い材料で形成する必要がある。また、第2の基板側から光を受光する場合は、第2の基板及びカソード電極を透光性の高い材料で形成する。

**【 0 0 1 6 】**

本発明における光電変換素子は、フォトダイオードとして、アノード電極とカソード電極の間に光電変換層を挟んだショットキー型、P I N型もしくはP N型のダイオード、またはアバランシェダイオード等を用いることができる。

**【 0 0 1 7 】**

10

20

30

40

50

本発明により作製される半導体装置は、光センサ、光電変換素子又は太陽電池素子を有する。本発明において、半導体装置とは、非晶質半導体膜を活性層に有する半導体素子又は結晶質半導体膜を活性層に有する半導体素子を含む半導体装置であって、具体的には、光センサ素子、光電変換装置、太陽電池等を有する半導体装置である。

### 【発明の効果】

#### 【0018】

本発明は、薄膜トランジスタを第1の基板上に形成している一方で、光電変換素子を第2の基板上に形成し、これら第1の基板及び第2の基板を対向させ、それら基板の間にあら薄膜トランジスタと光電変換素子との電気的接続をとることで光センサを有する半導体装置を作製する。そのため、従来のように薄膜トランジスタが形成されるのを待って、光電変換素子を形成しなくとも良いので、作製時間の短縮化を図ることが可能となる。10

#### 【0019】

また、薄膜トランジスタと光電変換素子との電気的接続をとった後に基板を剥離できるため、より軽量で薄い半導体装置が得られる。基板を剥離した後にプラスチック基板等の可撓性基板を貼り合わせれば、耐衝撃性が向上し、曲げ、ねじれにも耐えうる可撓性を有する半導体装置が実現できる。可撓性を有する半導体装置は、実装されるものを選ばないため、凹凸面や曲面への実装が可能となる。

#### 【0020】

本発明の半導体装置は、薄膜トランジスタと光電変換素子をそれぞれ独立に形成した後に、それらを電気的に接続して作製される。従って、薄膜トランジスタに起因する凹凸やその他設計上の制限を受けずに光電変換素子を形成できるため、受光面積の広い光電変換素子を増幅回路上に設けることができる。よって、光の検出能力が高い半導体装置を実現することが可能となる。20

### 【発明を実施するための最良の形態】

#### 【0021】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は本実施の形態の記載内容に限定して解釈されるものではない。

#### (実施の形態1)

#### 【0022】

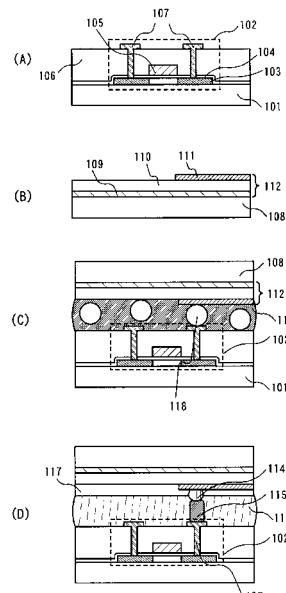

一方の基板には光電変換素子、他方の基板には増幅回路を構成する素子を形成し、光電変換素子と増幅素子を電気的に接続させる形態を図1を用いて説明する。

#### 【0023】

まず、図1(A)の第1の基板101上に増幅素子又は増幅回路を形成する。ここでは増幅素子の代表例として薄膜トランジスタ102を形成する。図1(A)ではトップゲイド型薄膜トランジスタを用いて説明するが、ボトムゲイド型薄膜トランジスタを用いても良い。

#### 【0024】

薄膜トランジスタ102は、半導体層103、ゲート絶縁膜104、ゲート電極105、層間絶縁膜106、ソース電極またはドレイン電極107で構成されている。40

#### 【0025】

また、図1(B)に示すように、第1の基板とは別に、第2の基板108上には、カソード電極109、シリコン層110、アノード電極111で構成される光電変換素子112を形成する。しかし、光電変換素子の構成は本形態に限られず、光を信号として出力する機能を有すればどのような構成であっても良い。

#### 【0026】

次に、薄膜トランジスタと光電変換素子とが内側になるよう第1の基板と第2の基板とを対向させて、薄膜トランジスタと光電変換素子とを電気的に接続させる。この電気的接続は、光電変換素子の出力を薄膜トランジスタで増幅させるために行うものである。電気50

的な接続方法としては、薄膜トランジスタと光電変換素子の間に導電性材料を挟持させる。また、接着剤の機能を有する導電性材料を用いれば、電気的に薄膜トランジスタと光電変換素子を接続させると同時に、基板同士の貼り合わせも行うことができる。具体的な接続方法として、ここでは2つの方法を下記に示す。

#### 【0027】

一つは、導電性を有する接着剤を用いた接続方法である。図1(C)にこの方法で作製した半導体装置を示す。導電性を有する接着剤は、一般的に導電性粒子が分散された樹脂材料であり、これは膜厚方向にしか電気的接続をとらず、面方向の電気的接続はとらないという性質を有する。導電性を有する接着剤として異方性導電接着剤があり、具体的には異方性導電フィルムまたは異方性導電ペーストがある。本形態では異方性導電ペーストを用いる。薄膜トランジスタ102に異方性導電ペースト113を塗布した後に、光電変換素子112と薄膜トランジスタ102が内側になるように、第1の基板101と第2の基板108を貼り合わせる。勿論、異方性導電ペースト113を光電変換素子112に塗布してから、第2の基板108と第1の基板101を貼り合わせても良い。

#### 【0028】

異方性導電ペースト113で貼り合わせた場合は、アノード電極111とソース電極またはドレイン電極107のみを導電性粒子118により電気的に接続させることができるとともに、第1の基板と第2の基板とを接着させることができる。以上の工程により、光センサを有する半導体装置を作製できる。

#### 【0029】

もう一つの方法としては、金属層を用いた接続方法で、その一例として、図1(D)のように半田115を用いる方法がある。半田の場合は、半田と合金を作ることのできる金属、つまり半田と濡れ性のある金属（以下、濡れ性金属と言う）を介して、薄膜トランジスタと光電変換素子を接続させる。従って、薄膜トランジスタ102では、ソース電極またはドレイン電極107を濡れ性金属を用いて形成するか、ソース電極またはドレイン電極107の表面に濡れ性金属膜を形成する。また、光電変換素子では、絶縁膜117を形成し、絶縁膜117に形成したコンタクトホールに電極114を濡れ性金属を用いて形成する。

#### 【0030】

その他、アノード電極111を濡れ性金属で形成したり、アノード電極111の表面のみを濡れ性金属で形成したりして、電極114を形成せずにアノード電極111と半田を直接接続する方法もある。

#### 【0031】

そして、ソース電極またはドレイン電極107と電極114を半田リフロー処理等で半田付けすることで、薄膜トランジスタと光電変換素子とを電気的に接続させる。次に、封止材116を用いて半田115以外の部分を封止して、第1の基板と第2の基板とを接着させる。半田リフロー処理は250度程度の温度をかけて行うため、第1の基板及び第2の基板としては、この温度に耐えうる耐熱性があるのでなければならない。例えば、ガラス基板や石英基板、耐熱性プラスチック基板が好ましい。

#### 【0032】

上述した2つの方法では、薄膜トランジスタと光電変換素子との間に、導電性と接着機能を有する材料を挟持させて、第1の基板と第2の基板とを貼り合わせた。しかし、薄膜トランジスタと光電変換素子との間に挟持されるものは、必ずしも導電性と接着機能を有する必要はなく、少なくとも導電性を有すれば良い。導電性のみを有する材料を挟持する場合は、半導体装置の側面に接着剤を塗布する等の何らかの手段を用いて、両基板を貼り合わせると良い。

#### 【0033】

以上のように、第1の基板上には增幅素子または增幅回路を構成する薄膜トランジスタを形成し、第2の基板上には光電変換素子を形成する。これにより、薄膜トランジスタを形成する工程と光電変換素子を形成する工程の2つの工程を独立に平行して行うことがで

10

20

30

40

50

きる。従って、本発明は短時間で効率よく半導体装置を作製することができる。

【0034】

また、薄膜トランジスタが形成された時点または光電変換素子が形成された時点で、各素子の性能を確認し、確認した上で両素子を電気的に接続させ半導体装置を完成させることができる。従って、欠陥品が作製される割合を抑えることができ、歩留まりを改善することができる。

【0035】

また、光電変換素子を薄膜トランジスタとは別に形成できるため、薄膜トランジスタによる凹凸等の設計上の制限を受けずに受光面を広くとることができる。よって、光電変換素子の光の検出能力を高めることができるとなる。

(実施の形態2)

【0036】

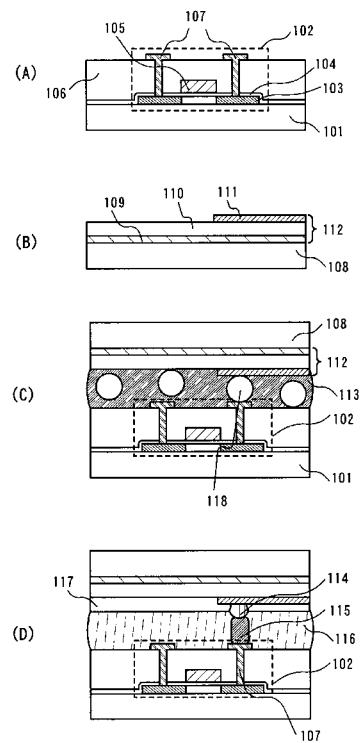

本形態では、実施の形態1で作製した半導体装置から第1の基板を剥離する方法を、図2を用いて説明する。図2において、図1と同一の部分は同じ符号を付し、説明を省略する。

【0037】

まず、第1の基板101上に図1(A)で説明した薄膜トランジスタ102を形成する前に、第1の基板上に剥離層201を形成する。そして、剥離層201上に薄膜トランジスタ102を形成する。

【0038】

このようにして形成した薄膜トランジスタを有する第1の基板と、図1(B)の光電変換素子を有する第2の基板を、導電性を有する接着剤を用いて貼り合わせる。ここでは異方性導電ペーストを用いるが、図1(D)のように半田で貼り合わせても構わない。

【0039】

貼り合わせて、第2の基板108に光電変換素子と薄膜トランジスタが保持された図2(B)の状態になったら、次は、第1の基板101を薄膜トランジスタ102より剥離する。図2(C)では、剥離層と半導体層との界面で剥離されているが、これに限らず、剥離層と第1の基板との界面で剥離されても良いし、剥離層自身が2つに分かれても良い。剥離方法としては、ドライエッティングやウエットエッティングや、又は引っ張り応力を加える等の一般的な方法を用いればよい。

【0040】

この第1の基板が剥離された図2(C)の状態で、薄膜トランジスタ102を備えた光電変換素子を実装したい対象物に直接実装しても良い。または、図2(D)のように、さらに第3の基板203を接着剤202を介して、薄膜トランジスタ102に貼り合わせても良い。このとき、第3の基板側からの光を受光する場合は、第3の基板203及び接着剤202は透光性が高いものを用いる。

【0041】

この剥離工程により第1の基板を半導体装置から剥離できるので、軽く薄い半導体装置を提供できる。さらには第3の基板として樹脂基板等を用いれば、可撓性を有し且つ軽量で薄い半導体装置を提供できる。第3の基板を可撓性基板とすると、可撓性のないガラス基板や石英基板に形成された半導体装置よりも被実装体に対する実装強度を増すことができる。

【0042】

また、第2の基板108とカソード電極109の間に剥離層を設けて、第2の基板を剥離しても良い。さらに、剥離後、接着剤を用いて第4の基板をカソード電極109上に貼り合わせても良い。このとき、第4の基板側からの光を受光する場合は、受光する光を透過させるために、接着剤及び第4の基板は透光性が高いものを用いる。

【0043】

第1の基板、第2の基板ともに剥離をすれば、より薄くて軽い半導体装置を提供できる。

10

20

30

40

50

## 【0044】

一般に、基板を剥離して、新たな基板を貼り合わせる技術を転置技術と呼ぶ。転置をする場合は、基板を剥離している間、光電変換素子や薄膜トランジスタを支持しておく支持基板が必要である。しかし本発明では、わざわざ支持基板を用意しなくとも、第1の基板または第2の基板を支持基板として活用することができる。よって、新たな基板を用意することなく基板の転置ができる、プラスチック基板や有機樹脂部材上に増幅回路を構成する薄膜トランジスタを有する半導体装置を効率よく作製できる。

## 【実施例1】

## 【0045】

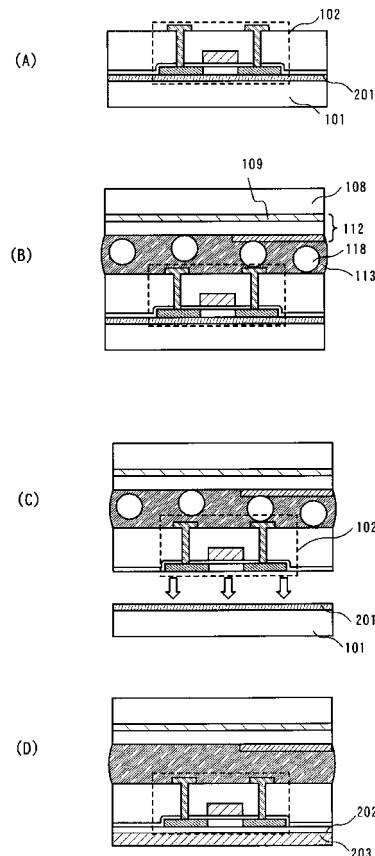

本実施例では、実施の形態1で示した異方性導電ペーストを用いて光電変換素子と増幅素子を電気的に接続させる工程を、より具体的に図3を用いて説明する。

## 【0046】

まず、ガラス基板（第1の基板301）上に素子を形成する。このガラス基板上に下地絶縁膜302の一層目となる酸化膜、ここではスパッタ法で酸化シリコン膜（膜厚150nm～200nm）を形成する。

## 【0047】

次いで、PCVD法で下地絶縁膜302の2層目となる酸化窒化シリコン膜（膜厚100nm）を形成し、さらに大気にふれることなく、水素を含むアモルファスシリコン膜（膜厚54nm）を形成する。なお、酸化窒化シリコン膜は、ガラス基板からのアルカリ金属などの不純物拡散を防止するプロッキング層である。

## 【0048】

次いで、上記アモルファスシリコン膜を公知の技術（固相成長法、レーザー結晶化方法、触媒金属を用いた結晶化方法など）により結晶化させて、ポリシリコン膜を活性層とする薄膜トランジスタ（以下、TFTとも標記する）を用いた素子を形成する。ここでは、触媒金属を用いた結晶化方法を用いてポリシリコン膜を得る。具体的には、重量換算で10ppmのニッケルを含む酢酸塩溶液をスピナーでアモルファスシリコン膜に塗布する。なお、塗布に代えてスパッタ法でニッケル元素をアモルファスシリコン膜全面に散布する方法を用いてもよい。次いで、加熱処理を行い結晶化させて結晶構造を有する半導体膜（ここではポリシリコン膜）を形成する。ここでは熱処理（500、1時間）の後、結晶化のための熱処理（550、4時間）を行って結晶構造を有するシリコン膜を得る。

## 【0049】

次いで、結晶構造を有するシリコン膜表面の酸化膜を希フッ酸等で除去する。その後、結晶化率を高め、結晶粒内に残される欠陥を補修するためのレーザー光（XeCl：波長308nm）の照射を大気中、または酸素雰囲気中で行う。レーザー光には波長400nm以下のエキシマレーザ光や、YAGレーザの第2高調波、第3高調波を用いる。ここでは、繰り返し周波数10～1000Hz程度のパルスレーザー光を用い、当該レーザー光を光学系にてエネルギー密度100～500mJ/cm<sup>2</sup>に集光し、90～95%のオーバーラップ率をもって照射し、シリコン膜表面を走査させればよい。ここでは、繰り返し周波数30Hz、エネルギー密度470mJ/cm<sup>2</sup>でレーザー光の照射を大気中で行なった。なお、大気中、または酸素雰囲気中で行うため、レーザー光の照射により半導体膜表面に酸化膜が形成される。なお、ここではパルスレーザーを用いた例を示したが、連続発振のレーザーを用いてもよく、非晶質半導体膜の結晶化に際し、大粒径に結晶を得るために、連続発振が可能な固体レーザーを用い、基本波の第2高調波～第4高調波を適用するのが好ましい。代表的には、Nd:YVO<sub>4</sub>レーザー（基本波1064nm）の第2高調波（532nm）や第3高調波（355nm）を適用すればよい。連続発振のレーザーを用いる場合には、連続発振のYVO<sub>4</sub>レーザーから射出されたレーザー光を非線形光学素子により出力10Wの高調波に変換する。また、共振器の中にYVO<sub>4</sub>結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または橍円形状のレーザー光に成形して、被処理体である半導体膜に照射する。このときのエネルギー密度は0.01～100MW/cm<sup>2</sup>程度（好ましくは0.1～10M

10

20

30

40

50

$\text{W} / \text{cm}^2$ ) が必要である。そして、 $10 \sim 2000 \text{ cm} / \text{s}$  程度の速度でレーザ光に対して相対的に半導体膜を移動させて照射すればよい。

#### 【0050】

次いで、上記レーザー光の照射により形成された酸化膜上に、オゾン水で酸化膜表面を 120 秒処理して合計  $1 \sim 5 \text{ nm}$  の酸化膜からなるバリア層を形成する。このバリア層は、結晶化するために添加したニッケルを膜中から除去するために形成する。ここではオゾン水を用いてバリア層を形成したが、酸素雰囲気下の紫外線の照射で結晶構造を有する半導体膜の表面を酸化する方法、酸素プラズマ処理により結晶構造を有する半導体膜の表面を酸化する方法、プラズマ CVD 法、スパッタ法、蒸着法などで  $1 \sim 10 \text{ nm}$  程度の酸化膜を堆積してバリア層を形成してもよい。また、バリア層を形成する前にレーザー光の照射により形成された酸化膜を除去してもよい。

#### 【0051】

次いで、バリア層上にスパッタ法にてゲッタリングサイトとなるアルゴン元素を含む非晶質シリコン膜を膜厚  $10 \text{ nm} \sim 400 \text{ nm}$ 、ここでは膜厚  $100 \text{ nm}$  で成膜する。ここでは、アルゴン元素を含む非晶質シリコン膜は、シリコンターゲットを用いてアルゴンを含む雰囲気下で形成する。プラズマ CVD 法を用いてアルゴン元素を含む非晶質シリコン膜を形成する場合は、成膜条件は、モノシランとアルゴンの流量比 ( $\text{SiH}_4 : \text{Ar}$ ) を  $1 : 99$  とし、成膜圧力を  $6.665 \text{ Pa}$  ( $0.05 \text{ Torr}$ ) とし、RF パワー密度を  $0.087 \text{ W} / \text{cm}^2$  とし、成膜温度を  $350^\circ\text{C}$  とする。

#### 【0052】

その後、 $650^\circ\text{C}$  に加熱された炉に入れて 3 分の熱処理を行いゲッタリングして、結晶構造を有する半導体膜中のニッケル濃度を低減する。炉に代えてランプアニール装置を用いてもよい。

#### 【0053】

次いで、バリア層をエッチングストッパーとして、ゲッタリングサイトであるアルゴン元素を含む非晶質シリコン膜を選択的に除去した後、バリア層を希フッ酸で選択的に除去する。なお、ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、酸化膜からなるバリア層をゲッタリング後に除去することが望ましい。

#### 【0054】

なお、触媒元素を用いて結晶化を行わない場合には、上述したバリア層の形成、ゲッタリングサイトの形成、ゲッタリングのための熱処理、ゲッタリングサイトの除去、バリア層の除去などの工程は不要である。

#### 【0055】

次いで、得られた結晶構造を有するシリコン膜（ポリシリコン膜とも呼ばれる）の表面にオゾン水で薄い酸化膜を形成した後、第 1 のフォトマスクを用いてレジストからなるマスクを形成し、所望の形状にエッチング処理して島状に分離された半導体層 303 を形成する。半導体層 303 を形成した後、レジストからなるマスクを除去する。

#### 【0056】

次いで、必要があれば TFT のしきい値を制御するために微量な不純物元素（ボロンまたはリン）のドーピングを行う。ここでは、 $\text{B}_2\text{H}_6$  をプラズマ励起し、質量分離しないで半導体層 303 にボロンを注入する。

#### 【0057】

次いで、フッ酸を含むエッチャントで酸化膜を除去すると同時にシリコン膜の表面を洗浄した後、ゲート絶縁膜 304 となる珪素を主成分とする絶縁膜を形成する。ここでは、プラズマ CVD 法により  $115 \text{ nm}$  の厚さで酸化窒化シリコン膜（組成比 Si = 32%、O = 59%、N = 7%、H = 2%）を形成する。

#### 【0058】

次いで、ゲート絶縁膜 304 上に金属膜を形成した後、第 2 のフォトマスクを用いてパターニングを行い、ゲート電極 305、接続配線 306、接続配線 307、接続配線 308 を形成する。次いで、活性層へのドーピングを行ってソース領域またはドレイン領域の

10

20

30

40

50

形成を行う。

**【0059】**

次いで、CVD法により酸化シリコン膜からなる第1の層間絶縁膜（図示しない）を50nm形成した後、それぞれの半導体層に添加された不純物元素を活性化処理する工程を行う。この活性化工程は、ランプ光源を用いたラピッドサーマルアニール法（RTA法）、或いはYAGレーザーまたはエキシマレーザーを照射する方法、或いは炉を用いた熱処理、或いはこれらの方のうち、いずれかと組み合わせた方法によって行う。

**【0060】**

次いで、水素を含む窒化酸化シリコン膜からなる第2の層間絶縁膜309を形成して熱処理（300～550で1～12時間の熱処理）を行い、半導体層を水素化する工程を行う。この工程は第1の層間絶縁膜に含まれる水素により半導体層のダンギングボンドを終端する工程である。ゲート絶縁膜304の存在に関係なく半導体層303を水素化することができる。

**【0061】**

次いで、第2の層間絶縁膜309上に有機絶縁物材料から成る第3の層間絶縁膜310を形成する。ここでは膜厚0.8μmのアクリル樹脂膜を形成する。

**【0062】**

次いで、第3の層間絶縁膜310上にスパッタ法で膜厚250nm～350nmの無機絶縁膜から成る第4の層間絶縁膜311を形成する。

**【0063】**

次いで、第3のフォトマスクを用いてレジストからなるマスクを形成し、第1～4の層間絶縁膜及びゲート絶縁膜304を選択的にエッチングしてコンタクトホールを形成する。そして、レジストからなるマスクを除去する。

**【0064】**

次いで、金属膜を積層した後、第4のフォトマスクを用いてレジストからなるマスクを形成し、選択的に金属積層膜をエッチングして、配線312、配線313、配線314、薄膜トランジスタのソース電極またはドレイン電極315を形成する。そして、レジストからなるマスクを除去する。なお、金属積層膜は、膜厚100nmのTi膜と、膜厚350nmのSiを微量に含むAl膜と、膜厚100nmのTi膜との3層積層とする。

**【0065】**

以上の工程で、ポリシリコン膜を活性層とするトップゲート型のTFT30、31が作製でき、図3（A）に示す構造が得られる。

**【0066】**

次に、図3（B）に示す光電変換素子を形成する方法を下記に説明する。

**【0067】**

第2の基板321であるフィルム基板に、金属膜、ここでは膜厚100nmの透明導電膜を成膜してカソード電極322を形成する。

**【0068】**

次に、光電変換層としてp型半導体層と、i型（真性）半導体層と、n型半導体層を順次積層する。

**【0069】**

p型半導体層として、PCVD法を用い、電極間隔36mm、成膜圧力266Pa、RFパワー700Wとし、SiH<sub>4</sub>（流量4sccm）と、B<sub>2</sub>H<sub>6</sub>（流量20sccm）と、H<sub>2</sub>（流量773sccm）とを原料ガスとして膜厚50nmのp型微結晶シリコン膜を成膜する。もしくはp型アモルファスシリコン膜でも良い。

**【0070】**

また、i型（真性）半導体層としてPCVD法を用い、電極間隔36mm、成膜圧力133Pa、RFパワー50W～88Wとし、SiH<sub>4</sub>（流量100sccm）と、H<sub>2</sub>（流量1000sccm）とを原料ガスとして膜厚600nmのi型アモルファスシリコン膜を成膜する。

10

20

30

40

50

## 【0071】

また、n型半導体層として、PCVD法を用い、電極間隔33mm、成膜圧力133Pa、RFパワー300Wとし、SiH<sub>4</sub>(流量5sccm)と、PH<sub>3</sub>(流量5sccm)と、H<sub>2</sub>(流量473sccm)とを原料ガスとして膜厚70nmのn型微結晶シリコン膜を成膜する。もしくはn型アモルファスシリコン膜でも良い。

## 【0072】

次に、YAGレーザーによるスクライプで、p型微結晶シリコン膜、i型アモルファスシリコン膜及びn型微結晶シリコン膜の積層膜を選択的に除去する。これは、後に形成するカソード電極と接続する電極が、光電変換層のn型半導体層と接さないようにするためである。

10

## 【0073】

以上により、光電変換層323n、323i、323pを形成する。

## 【0074】

次いで、光電変換層を覆うように絶縁膜324を成膜する。ここでは絶縁膜324としてアクリル樹脂膜を形成する。そして、第5のフォトマスクを用いたレジストからなるマスクを絶縁膜324上に形成し、選択的に絶縁膜324をエッチングまたはYAGレーザーによるスクライプをして、アノード電極とカソード電極に接続する配線のためのコントラクトホールをそれぞれ形成する。特に、カソード電極に接続する配線のためのコントラクトホールは、前の工程により上記p型微結晶シリコン膜、i型アモルファスシリコン膜及びn型微結晶シリコン膜の積層膜を一部除去した部分に形成される。

20

## 【0075】

そして、絶縁膜324上に金属膜を積層した後、第6のフォトマスクを用いたレジストからなるマスクを用いて選択的に金属積層膜をエッチングして、アノード電極325、カソード電極と接続する端子電極326を形成する。

## 【0076】

以上の工程で、第2の基板321上に形成された光電変換素子であるフォトダイオード323が形成でき、図3(B)に示す構造が得られる。

## 【0077】

次に、図3(A)の第1の基板301と図3(B)の第2の基板321を、異方性導電ペースト331を用いて貼り合わせる。このときに基板の位置合わせをして貼り合わせるのが好ましい。例えば、予め第1の基板と第2の基板にそれぞれアライメントマーカーを付けておき、それらマーカーが一致したところで貼り合わせる。位置合わせをした状態で両基板を圧着することで、導電性粒子332により、端子電極326と配線313とが電気的に接続し、アノード電極325と配線312とが電気的に接続する。以上の工程により、光センサの機能を持つ半導体装置が作製される。

30

## 【0078】

本実施例で作製した光センサを有する半導体装置について説明する。

## 【0079】

図3(C)の光センサは、増幅回路を介さずに直接フォトダイオード323に入射する光を受光する。つまり、第2の基板側からの光を受光する。従って、第2の基板321及びカソード電極322は透光性の高い材料で形成される。また、増幅回路を介して第1の基板側からの光を受光するようにしても良い。そのときは、第1の基板及びその他光が透過する層は、透光性の高い材料で形成する。

40

## 【0080】

なお、基本的にはTFT30及び31の半導体層303に光が照射されることによるリーケ電流の増加は、その光が高エネルギーでない限り問題はない。また、第2の基板側からの光を受光する場合は、ゲート電極305や、ソース電極またはドレイン電極315によって半導体層への光は遮光される。仮に半導体層303を遮光したい場合は、絶縁膜324や第4の層間絶縁膜311、第3の層間絶縁膜310、第2の層間絶縁膜309の少なくとも一つに遮光性を持たせて、半導体層303への光の入射を防いでも良い。また、

50

絶縁膜324または第3の層間絶縁膜310の樹脂膜に、黒色顔料またはカーボンを分散させて遮光性を持たせても良い。さらに、貼り合わせ時に用いる導電性を有する接着剤、ここでは異方性導電ペーストに遮光機能を持たせても良い。

#### 【0081】

図3(C)の半導体装置の受光方向とは逆の方向、つまり第1の基板側からの光を受光する場合は、半導体層に入射する光を遮光するため、半導体層の下に遮光膜を設けると良い。

#### 【0082】

また、接続配線306は配線312に接続しており、增幅回路のTFT30のチャネル形成領域にも延在しゲート電極にもなっている。一方で、異方性導電ペースト331中の導電性粒子332を介してアノード電極325とも接続している。10

#### 【0083】

また、接続配線307は配線313と接続し、配線313は、異方性導電ペースト331中の導電性粒子332を介して、カソード電極322と接続する端子電極326と接続する。つまり、接続配線307はカソード電極322と電気的に接続する。一方で、接続配線307はTFT31のソース電極またはドレイン電極315と接続している。

#### 【0084】

図3(D)に、図3(C)で示した2端子の光センサの等価回路図を示す。PIN型のフォトダイオード323の出力値を増幅するために、増幅回路は、TFT30、31を含むカレントミラー回路で構成されている。図3(C)では2個のTFTを図示しているが、実際には出力値を5倍とするためにTFT30(チャネルサイズL/W = 8 μm / 50 μm)を2個並列接続し、TFT31(チャネルサイズL/W = 8 μm / 50 μm)を10個並列接続して設けることもできる。ここでは、100倍とするためにTFT30を1個、TFT31を100個並列接続して設ける。20

#### 【0085】

図3(D)に示した回路を構成しているTFTはN型TFTであるが、P型TFTを用いても良い。

#### 【0086】

図3(D)の光センサは、配線313及び配線314を介して実装され、外部と接続する。配線314は外部電源GNDに接続され、配線313は出力端子へ接続されている。さらに、出力値を増幅させるために増幅回路は、nチャネル型TFTまたはpチャネル型TFTを適宜組み合わせた演算増幅器(オペアンプ)で構成してもよく、その場合は5端子となる。また、オペアンプで増幅回路を構成し、レベルシフタを用いることによって、電源数を削減して4端子とすることもできる。30

#### 【0087】

また、nチャネル型のTFT30、31はシングルゲート構造のトップゲート型TFTの例を示しているが、ダブルゲート構造としてバラツキを低減させてもよい。また、オフ電流値を低減するため、nチャネル型のTFT30、31を低濃度ドレイン(LDD:Lightly Doped Drain)構造としてもよい。このLDD構造はチャネル形成領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との間に低濃度に不純物元素を添加した領域を設けたものであり、この領域をLDD領域と呼んでいる。LDD構造はドレイン近傍の電界を緩和してホットキャリア注入による劣化を防ぐ効果がある。また、ホットキャリアによるオン電流値の劣化を防ぐため、nチャネル型TFT30、31をGOLD(Gate-drain Overlapped LDD)構造としてもよい。ゲート絶縁膜を介してLDD領域をゲート電極と重ねて配置させた構造であるGOLD構造は、LDD構造よりもさらにドレイン近傍の電界を緩和してホットキャリア注入による劣化を防ぐ効果がある。このようなGOLD構造とすることで、ドレイン近傍の電界強度が緩和されてホットキャリア注入を防ぎ、劣化現象の防止に有効である。40

#### 【0088】

10

20

30

40

50

本実施例は、光電変換層の i 型半導体層としてアモルファスシリコンを用いているため、光センサとしては好ましい。それは、アモルファスシリコンを用いる光センサは、可視光領域の波長の中央である 580 ~ 600 nm 近傍において感度が最も高く、人間の視感度に近似したセンシング特性を有するからである。

#### 【0089】

特に、ダイオード型光センサは、応答速度が速く、光の明暗によるダイナミックレンジが大きいという利点がある。しかし、光電荷による電流が小さいため光電荷を増幅する素子が必要になるが、本実施例の光センサはポリシリコンを用いた TFT を増幅素子として有するため、電気特性が高く高速応答可能な光センサが実現できる。つまり、光電変換層をアモルファスシリコンで形成し、増幅素子をポリシリコン TFT で形成する本実施例の光センサは、微弱な電流をも検出するので有効である。

#### 【0090】

なお、上述した理由により、本実施例においては、増幅回路を構成する薄膜トランジスタの活性層をアモルファスシリコン膜を結晶化して得たが、始めから結晶性半導体膜を活性層として形成しても良い。また、光電変換素子の出力を増幅する機能さえあれば、活性層は、微結晶半導体膜や非晶質半導体膜でもよく、その場合は、耐熱温度の低いプラスチック基板や有機樹脂部材からなる基板を第 1 の基板として用いることができる。

#### 【0091】

本実施例は自由に実施の形態 1 及び 2 と組み合わせることができる。

#### 【実施例 2】

#### 【0092】

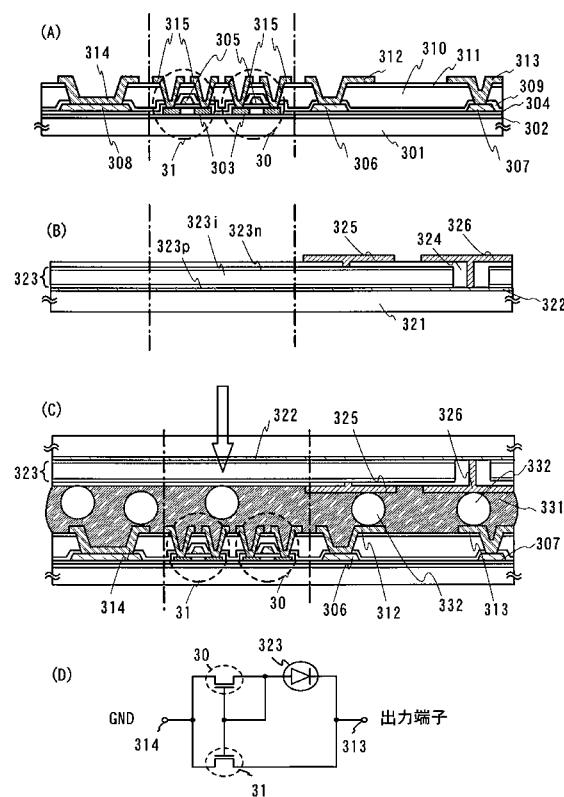

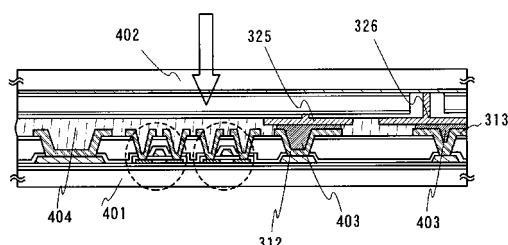

本実施例においては、実施の形態 1 で示した半田による接続方法をより具体的に図 4 を用いて説明する。図 4 において、図 3 と同じ部分には同じ符号を付し、説明を省略する。

#### 【0093】

本実施例も、実施例 1 で示した図 3 (A) のように第 1 の基板上に増幅回路を形成し、図 3 (B) のように第 2 の基板上に光電変換素子を形成することは同様である。

#### 【0094】

但し、半田で光電変換素子と薄膜トランジスタとを貼り合わせる場合は、半田リフロー処理（処理温度 250 度程度）のために加熱するので、第 1 の基板及び第 2 の基板として、半田リフロー処理に耐えうる耐熱性を持つ基板でなければならない。ここでは、第 1 の基板 401 及び第 2 の基板 402 として、共にガラス基板を用いる。

#### 【0095】

また、配線 312、配線 313、アノード電極 325、端子電極 326 は、半田と合金を作ることのできる金属、つまり半田と濡れ性のある金属で形成する必要がある。具体的にはニッケル、銅、金または銀等の金属で形成する。若しくは、配線 312、配線 313、アノード電極 325、端子電極 326 の半田と接する表面部分のみに、ニッケル、銅、金、銀等の金属膜を形成する。

#### 【0096】

そして、図 4 で示すように、増幅回路及びフォトダイオードである光電変換素子が内側になるよう、第 1 の基板と第 2 の基板とを対向させる。このときも、実施例 1 と同様、両基板の位置合わせを行い、半田 403 によって、アノード電極 325 と配線 312 を接続させ、端子電極 326 と配線 313 とを接続させる。

#### 【0097】

半田を付けた後、封止材 404 によって、光電変換素子と増幅回路との間を封止する。封止材 404 としては、有機絶縁物材料からなる封止樹脂を用い、封止すべき空間に流し込む。ここでは、アクリル樹脂膜を用いる。

#### 【0098】

本実施例で作製する半導体装置は、実施例 1 と同様、増幅回路を介さずに直接フォトダイオードへ入射する光を受光する。従って、第 2 の基板及びカソード電極は透光性の高いものが好ましい。また、TFT の半導体層への光照射によるリーク電流の増加を防ぐため

10

20

30

40

50

に、実施例 1 で述べた遮光方法に加え、封止材 404 に遮光性を持たせても良い。なお、第 1 の基板側からの光を受光しても良い。

#### 【0099】

本実施例は、自由に実施の形態 1、2、及び実施例 1 と組み合わせることができる。

#### 【実施例 3】

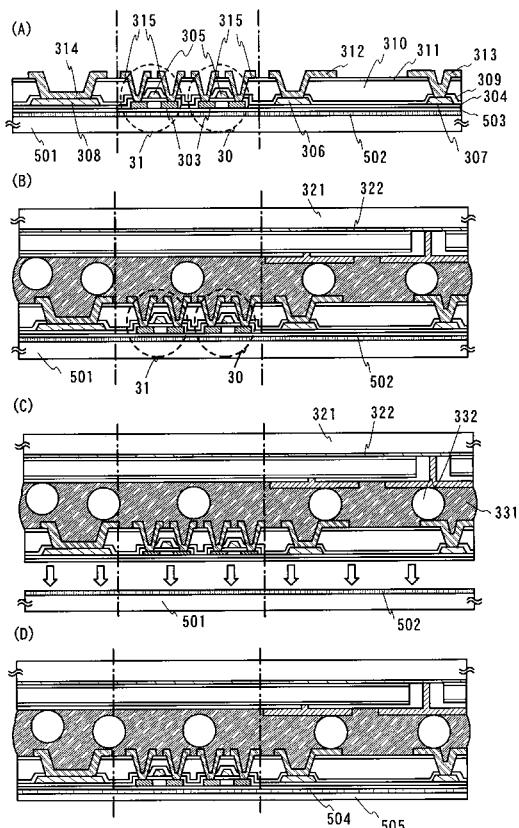

#### 【0100】

本実施例では、実施の形態 2 で示した第 1 の基板と第 2 の基板とを貼り合わせて作製した光センサから、さらに少なくとも一方の基板を剥離し、光センサを転置する方法を、より具体的に図 5 を用いて説明する。特に物理的な手段で基板を剥離する方法について述べる。なお、本実施例は剥離層を形成する以外は、実施例 1 で述べたものと同じ方法で増幅回路や光電変換素子を形成する。よって、図 5 において、図 3 と同じ部分には同じ符号を付し、説明を省略する。10

#### 【0101】

まず、図 5 (A) のガラス基板（第 1 の基板 501）上に増幅回路を構成する薄膜トランジスタを形成する。第 1 の基板 501 上に、剥離層として、スパッタ法で金属膜 502、ここではタンゲステン膜を膜応力が小さい成膜条件である Ar 流量 100 sccm、成膜圧力 2 Pa、成膜パワー 4 kW、基板温度 200°、膜厚 10 nm ~ 200 nm、好ましくは 50 nm ~ 75 nm で形成する。さらに大気にふれることなく、金属膜 502 上に下地絶縁膜 503 の一層目となる酸化物膜、ここではスパッタ法で酸化シリコン膜（膜厚 150 nm ~ 200 nm）を積層形成する。酸化物膜の膜厚は、金属膜の膜厚の 2 倍以上とすることが望ましい。20

#### 【0102】

なお、金属膜 502 と下地絶縁膜 503 の積層形成の際、金属膜 502 と酸化シリコン膜との間にアモルファス状態の酸化金属膜（酸化タンゲステン膜）が 2 nm ~ 5 nm 程度形成され、この酸化金属膜も剥離層の一部となる。後の工程で第 1 の基板を剥離する際、酸化タンゲステン膜中、または酸化タンゲステン膜と酸化シリコン膜との界面、または酸化タンゲステン膜とタンゲステン膜との界面で分離が生じる。なお、タンゲステン膜に代えて、Ti、Ta、Mo、Nd、Ni、Co、Zr、Zn、Ru、Rh、Pd、Os、Ir から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層、またはこれらの積層、或いは、これらの窒化物、例えば、窒化チタン、窒化タンゲステン、窒化タンタル、窒化モリブデンからなる単層、またはこれらの積層を用いることができる。30

#### 【0103】

なお、金属膜 502 や下地絶縁膜一層目の成膜は、スパッタ法により基板端面にも成膜されるため、基板端面に成膜されたタンゲステン膜と酸化タンゲステン膜と酸化シリコン膜とを SF<sub>6</sub> ガスと He ガスを用いたドライエッティング、および O<sub>2</sub> アッシングなどで選択的に除去することが好ましい。この工程は、アモルファスシリコン膜を成膜した後に行う。40

#### 【0104】

次いで、PCVD 法で下地絶縁膜 503 の 2 層目となる酸化窒化シリコン膜（膜厚 100 nm）を形成し、さらに大気にふれることなく、水素を含むアモルファスシリコン膜（膜厚 54 nm）を積層形成する。なお、酸化窒化シリコン膜は、ガラス基板からのアルカリ金属などの不純物拡散を防止するプロッキング層である。40

#### 【0105】

2 層目の酸化窒化シリコン膜の成膜後、水素を含むアモルファスシリコン膜を成膜し結晶化させる。具体的なアモルファスシリコン膜の形成方法、結晶化方法は、実施例 1 と同様である。

#### 【0106】

アモルファスシリコン膜の結晶化をさせるために、410° 以上の熱処理を行うと、金属膜 502 と酸化シリコン膜との間のアモルファス状態の酸化金属膜が結晶化し、結晶構50

造を有する酸化金属膜が得られる。従って、この410以上の熱処理が終了した段階で、比較的小さな力（例えば、人間の手、ノズルから吹付けられるガスの風圧、超音波等）を加えることによって、酸化タンゲステン膜中、または酸化タンゲステン膜と酸化シリコン膜との界面、または酸化タンゲステン膜とタンゲステン膜との界面で分離を生じさせることができる。なお、結晶構造を有する酸化金属膜が得られる温度の熱処理を行うと酸化金属膜の組成が変化するとともに、酸化金属膜の膜厚は若干薄くなる。また、結晶構造を有する酸化タンゲステン膜は複数の結晶構造（WO<sub>2</sub>、WO<sub>3</sub>、WO<sub>x</sub>（2 < X < 3））を有しており、熱処理によってWO<sub>3</sub>は、WO<sub>2</sub>またはWO<sub>x</sub>に組成変化する。

#### 【0107】

その後、実施例1と同様に半導体層303、ゲート絶縁膜304、ゲート電極305と10積層し、第1の基板501上に增幅回路を形成する。

#### 【0108】

以上のように形成した第1の基板501と、図3(B)で示す光電変換素子が形成された第2の基板321を異方性導電ペーストを用いて接着し、図5(B)の状態を得る。ここでは異方性導電ペーストで基板同士を貼り合わせる方法を用いたが、実施例2の図4で示したように、金属層である半田と封止樹脂を用いて貼り合わせた方法でも良い。また、光電変換素子と薄膜トランジスタで挟持されるものは、光電変換素子が形成された第2の基板321と薄膜トランジスタが形成された第1の基板501とを電気的に接続させるのみで、接着機能は有さなくても良い。この場合は、半導体装置の側面に接着剤等を塗布して両基板を接着させれば良い。

#### 【0109】

次いで、第1の基板の剥離を行いやすくするために、金属膜502と酸化金属膜との密着性、或いは酸化金属膜と下地絶縁膜503との密着性を部分的に低下させる処理を行う。密着性を部分的に低下させる処理は、剥離しようとする領域の周縁に沿って酸化金属膜にレーザー光を部分的に照射する処理、或いは、剥離しようとする領域の周縁に沿って外部から局所的に圧力を加えて酸化金属膜の層内または界面の一部分に損傷を与える処理である。具体的にはダイヤモンドペンなどの硬い針を垂直に押しつけて荷重をかけて動かせばよい。好ましくは、スクライバー装置を用い、押し込み量を0.1mm～2mmとし、圧力をかけて動かせばよい。このように、剥離を行う前に剥離現象が生じやすくなるような部分、即ち、きっかけをつくることが重要であり、密着性を選択的（部分的）に低下させる前処理を行うことで、剥離不良がなくなり、さらに歩留まりも向上する。

#### 【0110】

次いで、上記処理により密着性が部分的に低下した領域から剥離し、金属膜502が設けられている第1の基板501を物理的手段により引き剥がす。比較的小さな力（例えば、人間の手、ノズルから吹付けられるガスの風圧、超音波等）で引き剥がすことができる。こうして、下地絶縁膜503を第1の基板501から分離することができる。剥離の状態を図5(C)に示す。

#### 【0111】

次いで、接着剤504によりフィルム基板である第3の基板505と下地絶縁膜503（及び被剥離層）とを接着する（図5(D)）。接着剤504としては、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種接着剤が挙げられる。

#### 【0112】

以上より、フィルム基板である第3の基板505に転置したTFTからなる増幅回路を備える光センサを用意することができる。

#### 【0113】

本実施例では、第1の基板を剥離した後に光センサを転置する方法について述べたが、第2の基板321とカソード電極322の間に本実施例の剥離層を設け、第2の基板を剥離した後に光センサを転置しても良い。もしくは第1の基板と第2の基板ともに剥離した後に光センサを転置しても良い。

10

20

30

40

50

## 【0114】

増幅回路を電気特性（代表的には電界効果移動度）の高いTFTで形成しようとすると、ガラス基板や石英基板等の耐熱温度の高い基板を用いる必要がでてくる。しかし、本実施例を用いれば、ガラス基板等の上に形成された増幅回路をそのままフィルム基板やプラスチック基板、樹脂部材からなる基板等の耐熱温度の低い基板上に転置することができる。これにより、軽量で薄く、可撓性のある光センサを作製することができる。さらに、耐衝撃性が向上し、曲げ、ねじれなどにも耐えうる光センサを実現できる。また、フィルム基板やプラスチック基板、樹脂部材からなる基板上にある光センサは可撓性があるため、実装される場所を選ばず、さらに実装強度が向上する。

## 【0115】

光電変換素子をアモルファスシリコン膜や微結晶シリコン膜で形成する場合、第2の基板としては耐熱性の低い基板から高い基板まで制約無く使うことができる。しかし、増幅回路を電気特性のよいTFTで形成しようとすると、第1の基板を耐熱の高いガラス基板や石英基板等を用いる必要がある。このような場合、本実施例に基づいて、上部に増幅回路が形成される第1の基板を剥離し、フィルム基板やプラスチック基板である第3の基板を転置すれば、一対のフィルム基板や一対のプラスチック基板に挟持された光センサを得ることができる。

## 【0116】

また、半田リフロー処理で第1の基板と第2の基板を貼り合わせる場合、半田リフロー処理温度に起因する基板の制約も出てくる。具体的には、半田リフロー処理は250度程度で行われるため、アモルファスシリコン膜の光電変換素子が形成される第2の基板も、ある程度の耐熱性が必要になってくる。

## 【0117】

従って、半田で貼り合わせて作製された光センサで、第1の基板や第2の基板とともにガラス基板や石英基板の場合、本実施例を適用することで、片方もしくは両方を剥離し、より軽くて薄い基板に光センサを転置することができ、軽量で可撓性のある光センサを作製することができる。

## 【0118】

本実施例は、自由に、実施の形態1、実施の形態2、実施例1及び実施例2と組み合わせることができる。

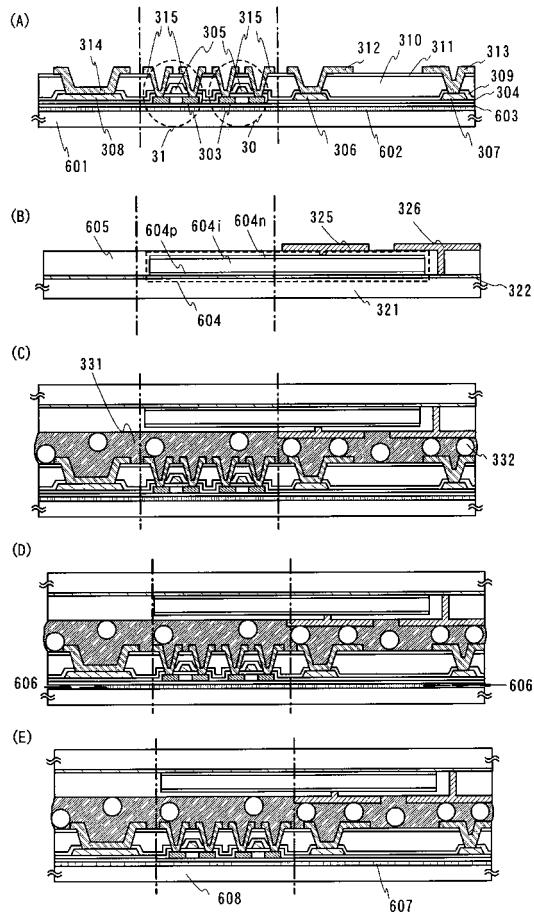

## 【実施例4】

## 【0119】

本実施例では、実施例3の剥離方法とは別の方法で剥離する方法を図6により説明する。特に化学的方法によって剥離する。なお、本実施例は剥離層を形成する以外は、実施例1で述べたものと同じ方法で増幅回路や光電変換素子を形成する。よって、図6において、図3と同じ部分には同じ符号を付し、説明を省略する。

## 【0120】

まず、ガラス基板（第1の基板601）上に増幅回路を構成する薄膜トランジスタを形成する。第1の基板601上に剥離層602を形成する。

## 【0121】

剥離層602としては、珪素を有すればよく、その構造は、非晶質半導体、非晶質状態と結晶状態とが混在したセミアモルファス半導体（SASとも表記する）、及び結晶性半導体のいずれでもよい。なおSASは、非晶質半導体中に0.5nm～20nmの結晶粒を観察することができる微結晶半導体が含まれる。これらの剥離層は、スパッタリング法、又はプラズマCVD法等によって形成することができる。また剥離層は、30nm～1μmの膜厚とすればよく、剥離層の成膜装置が30nm未満の膜を形成できるのであれば、30nm未満の膜厚とすることも可能である。

## 【0122】

また剥離層には、リンやボロン等の元素を添加してもよい。さらに加熱等により当該元素を活性化させてもよい。元素を剥離層に添加することにより、剥離層の反応速度、つま

10

20

30

40

50

りエッチングレートを改善することができる。

【0123】

本実施例では、剥離層602に30nm～1μm、好ましくは30nm～50nmの膜厚を有するSASを用いるが、上述したその他の材料を用いても構わない。

【0124】

また、半導体層がエッティングされないために、剥離層602上に形成される下地絶縁膜603は、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)( $x > y$ )、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)( $x > y$ )( $x, y = 1, 2 \dots$ )等の酸素、又は窒素を有する絶縁膜の単層構造、又はこれらの積層構造を有するとよい。これは第1の基板601の剥離時に用いるエッティングガスに対し、剥離層との十分な選択比がとれるためである。10

【0125】

そのため、下地絶縁膜は、積層構造を有してもよい。本実施例の下地絶縁膜603は酸化珪素膜、酸化窒化珪素膜、酸化珪素膜の3層構造を用いる。第1の基板等からの不純物拡散を考慮すると、下地絶縁膜として酸化窒化珪素膜を用いるのが好ましいが、酸化窒化珪素膜は剥離層、及び半導体層との密着性が低い。そこで、剥離層、半導体層、及び酸化窒化珪素膜との密着性の高い酸化珪素膜により、酸化窒化珪素膜を挟持するようにする。

【0126】

下地絶縁膜603形成以降から、第1の基板上に增幅回路や配線を形成するまでは、実施例1と同一工程であるので、ここでは説明を省略する。20

【0127】

次に、フィルム基板である第2の基板321上に光電変換素子を形成する方法を図6(B)を用いて説明する。第2の基板321上に、カソード電極322、光電変換層としてp型半導体層と、i型(真性)半導体層と、n型半導体層を順次積層するのは実施例1と同様である。

【0128】

次に、光電変換層が全て成膜された後、フォトマスクを用いて形成されたレジストからなるマスクを用いて、アモルファスシリコン膜及び微結晶シリコン膜の積層膜を選択的にエッティングして光電変換層604n、604i、604pを形成する。このときに、次工程で形成される絶縁膜によって光電変換層が三方向覆われるようエッティングする。これは、後の第1の基板の剥離工程において、光電変換層とエッティング剤が反応して光電変換層も一緒にエッティングされるのを防ぐためである。30

【0129】

次いで、光電変換層を覆うように絶縁膜605を成膜した後、絶縁膜中にコンタクトホールを形成し、さらにアノード電極325及びカソード電極322と接続する端子電極326を形成する。

【0130】

以上の工程で、第2の基板321上に形成された光電変換素子であるフォトダイオード604が作製でき、図6(B)に示す構造が得られる。

【0131】

次に、第1の基板601と第2の基板321とを、実施例1のように異方性導電ペーストにより貼り合わせて図6(C)の構成を得る。異方性導電ペースト331により貼り合わせたが、第2の基板321を半田リフロー処理に耐えうる耐熱性を有した基板にすれば、実施例2のような半田による貼り合わせでも良いことはもちろんである。40

【0132】

図6(C)の状態から、剥離層602を除去する。図6(D)に示すように、剥離層602を除去するエッティング剤606を導入する。エッティング剤としては、フッ化ハロゲンを含む気体又は液体を使用することができる。例えばフッ化ハロゲンとしてClF<sub>3</sub>(三フッ化塩素)を使用することができる。なお、ClF<sub>3</sub>は、塩素を200以上でフッ素と反応させることにより、Cl<sub>2</sub>(g) + 3F<sub>2</sub>(g) → 2ClF<sub>3</sub>(g)の過程を経て生50

成することができる。また  $C_1F_3$  は、反応空間の温度によっては液体の場合もあり（沸点 11.75）、その際にはフッ化ハロゲンを含む液体を用いてウェットエッチングを採用することもできる。その他のフッ化ハロゲンを含む気体として、 $C_1F_3$  等に窒素を混合したガスを用いてもよい。

#### 【0133】

また、剥離層 602 をエッチングし、且つ下地絶縁膜 603 をエッチングしないようなエッチング剤であれば、 $C_1F_3$  に限定されるものでなく、またフッ化ハロゲンに限定されるものでもない。例えば、 $CF_4$ 、 $SF_6$ 、 $NF_3$ 、 $F_2$  等のフッ素を含む気体をプラズマ化して用いることもできる。その他のエッチング剤として、テトラメチルアンモニウムハイドロオキサイド（TMAH）のような強アルカリ溶液を用いてもよい。

10

#### 【0134】

さらに、 $C_1F_3$  等のフッ化ハロゲンを含む気体によって化学的に除去する場合、選択的にエッチングされる材料を剥離層として用い、エッチングされない材料を下地膜として用いるという条件に従うならば、剥離層及び下地絶縁膜の組み合わせは、上記材料に限定されるものではない。

#### 【0135】

本実施例では、減圧 CVD 装置を用い、エッチング剤： $C_1F_3$ （三フッ化塩素）ガス、温度：350、流量：300 sccm、気圧：6 Torr、時間：3 h の条件で剥離層を除去することができるが、この条件に限定されるものではない。

20

#### 【0136】

さらに減圧 CVD 装置の側面には加熱手段、例えばヒータを設けてもよい。加熱手段により処理温度を 100 ~ 300 とすると剥離層とエッチング剤の反応速度を高めることができる。その結果、エッチング剤の使用量を少なくすることができ、処理時間を短縮することもできる。

#### 【0137】

このようなエッチング剤の導入により、剥離層を徐々に後退させて、除去することができる。

#### 【0138】

エッチング剤の導入時、半導体層 303 や、フォトダイオード 604 の光電変換層がエッチングされないようにエッチング剤、ガス流量、温度等を設定する。本実施例で用いる  $C_1F_3$  は、珪素を選択的にエッチングする特性があるため、剥離層を選択的に除去することができる。さらに半導体層 303 及び光電変換層がエッチングされないように、下地絶縁膜や光電変換層を覆う絶縁膜には酸素、又は窒素を有する絶縁膜を用いると好ましい。これら剥離層と、下地絶縁膜及び光電変換層を覆う絶縁膜との、エッチング剤に対する反応速度に差があるため、つまりエッチング剤の選択比が高いため、增幅回路や光電変換層を保護しつつ、剥離層を容易に除去することができる。本実施例では、半導体層 303 の上下に設けられた下地絶縁膜及びゲート絶縁膜により、半導体層がエッチング剤と反応することを防止できる。

30

#### 【0139】

その後、第 1 の基板 601 を剥離する。次いで図 6 (E) に示すように、接着剤 607 を用いて、第 2 の基板に支持されたフォトダイオードと增幅回路を第 3 の基板 608 へ接着することができる。第 3 の基板 608 は、可撓性を有するフレキシブル基板が好ましい。フレキシブル基板には、ポリエチレン - テレフタレート (PET)、ポリエチレンナフタレート (PEN)、ポリエーテルスルホン (PES) に代表されるプラスチックや、アクリル、ポリイミド等の可撓性を有する合成樹脂からなる基板を用いることができる。

40

#### 【0140】

接着剤 607 としては、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤等の接着剤又は両面テープ等を用いることができる。

#### 【0141】

フレキシブル基板へ移し替える結果、光センサを有する半導体装置の柔軟性が向上し、

50

破壊強度を高めることができる。またガラス基板である第1の基板上に形成された光センサと比べて、軽量化、薄型化を達成でき、可撓性を高めることができる。

#### 【0142】

本実施例は、自由に、実施の形態1、実施の形態2、実施例1～3と組み合わせることができる。

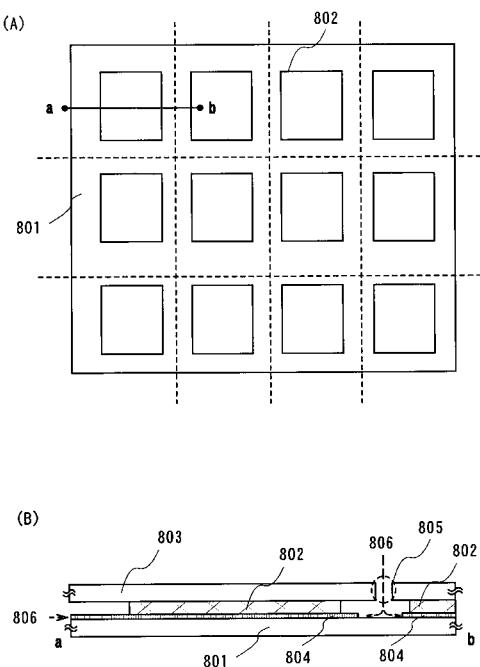

#### 【実施例5】

#### 【0143】

本実施例では、第1の基板上に複数の增幅回路を形成し、第2の基板上に複数の光電変換素子を形成し、これら第1の基板及び第2の基板を貼り合わせる。貼り合わせ後、各光センサにカットして、複数の光センサを有する半導体装置を得る方法を説明する。

10

#### 【0144】

第1の基板上に増幅素子または実施例1の図3(A)で示したような増幅回路を、マトリクス状に複数形成する。一方で、第2の基板上にも、光電変換素子をマトリクス状に複数形成する。そして、これら第1の基板と第2の基板を、実施の形態1、2、実施例1または実施例2で述べた貼り合わせ方法で、貼り合わせることにより、本発明の半導体装置802がマトリクス状に複数作製される。図7(A)は第2の基板803は図示せず、第1の基板801と半導体装置802のみを図示している。そして、基板を破線で示す線に合わせてレーザーやダイヤー等で切ることで、一度に光センサ機能を有する半導体装置を複数作製することができる。

#### 【0145】

また、本実施例で貼り合わせた後、実施例4のように第1の基板を剥離する場合は、第1の基板801に対して剥離層804を選択的に形成すると良い。このようにすると、剥離にかかる時間が短縮される。さらに基板の一部に剥離層に到達する孔805を形成すると良い。これにより、その孔805を通してエッティングガス806が侵入し剥離層と反応するので、反応が速く進行し、エッティング時間をさらに短縮することが可能となる。図7(B)では第2の基板803に孔を開けているが、第1の基板を開けても構わない。また、基板に孔を開ける場合は、半導体装置802同士の間に開けるのが好ましい。

20

#### 【0146】

本実施例は、自由に、実施の形態1、実施の形態2、実施例1～4と組み合わせることができる。

30

#### 【実施例6】

#### 【0147】

本発明で作製した半導体装置をアクティブ型のイメージセンサに適用した場合を説明する。

#### 【0148】

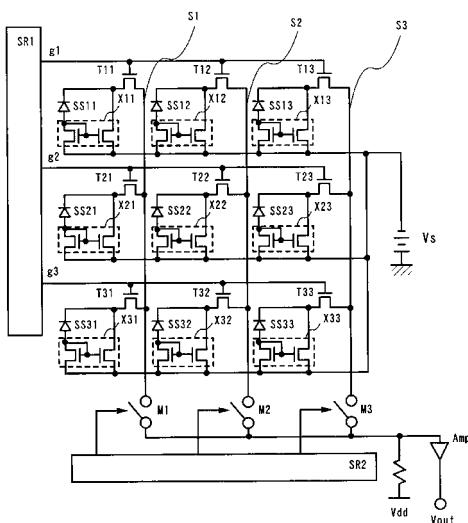

図8は、図3(D)で示した2端子の光センサの等価回路を3×3で配列した場合の等価回路図である。図8を用いて駆動方法を示す。

#### 【0149】

シフトレジスタSR1はゲート信号線g1-g3と接続されている。シフトレジスタSR1はゲート信号線を一本ずつ選択する。まず、ゲート信号線g1が選択されると、g1に接続されている転送用トランジスタT11-T13がオンする。これにより、増幅回路X11-X13で増幅されたダイオードSS11-SS13の信号が、転送用トランジスタT11-T13を通して信号配線S1-S3に出力される。シフトレジスタSR2は転送スイッチM1-M3にそれぞれ接続し、M1-M3を一つずつ選択していく。M1がシフトレジスタSR2によって選択されたとき、S1の信号がバッファアンプ(Amp)で増幅されVoutに出力される。その後、次々と、転送スイッチM2、M3が選択され、S2、S3の信号が増幅され出力される。

40

#### 【0150】

次は、シフトレジスタSR1によりゲート信号線g2が選択され、という手順を繰り返して、各画素、即ちダイオードの信号を読み出していく。

50

## 【0151】

イメージセンサを作製する場合は、光センサの他にシフトレジスタS R 1やS R 2等の周辺回路、及び電荷転送用トランジスタを作製する。これらの周辺回路や電荷転送用トランジスタは、増幅回路のT F Tを作製するのと同時に基板上に作製すると良い。その後、光電変換素子が形成された基板と、周辺回路、電荷転送用トランジスタ及び増幅回路が形成された基板とを貼り合わせてイメージセンサを作製する。

## 【0152】

また、電荷転送用トランジスタと増幅回路は同一基板上に作製して、周辺回路は別に接続させても良い。

## 【0153】

本実施例で作製したイメージセンサは、プラスチック基板上に複数の光センサからなる半導体装置とすることも可能となる。基板を剥離する場合は、図7(B)で示したように、剥離層を選択的に形成したり、剥離層に達する孔を形成したりすると、剥離にかかる時間が短縮され有効である。

## 【0154】

本実施例により形成される半導体装置は、アモルファスシリコン及び微結晶シリコンで形成されたダイオードとポリシリコンで形成されたT F Tの増幅素子からなる光センサを複数有する構成を取ることができる。従って、光電変換層(受光層)の面積が狭くても、即ち小型でも微弱な光を検出可能であり、高感度かつ高精細である。また、プラスチック基板上に形成されているため、従来のものと比べて軽量で薄型化が可能である。また、シフトレジスタ等の駆動回路又は電源線との接続に異方導電性フィルムを用いると、プリント配線基板上に設置されたI Cチップ、駆動回路、電源回路等を構成するパッケージ等の上に設置することができ、光電変換装置の受光面積を拡大すると共に、プリント配線基板の面積を縮小することが可能となる。

## 【0155】

本実施例ではアクティブセンサについて述べたが、本発明で作製した光センサを有する半導体装置をパッシブセンサに適用できることはもちろんである。

## 【0156】

本実施例は、実施の形態1、実施の形態2、実施例1～5と自由に組み合わせができる。

## 【実施例7】

## 【0157】

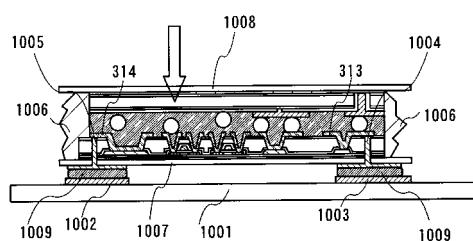

本実施例では、本発明で作製した半導体装置を実装した一例を図9を用いて説明する。実施例1の図3で示した半導体装置を実装する例を示す。よって、図3と同一の部分には同じ符号を付し、説明を省略する。

## 【0158】

図9は、本発明で作製した半導体装置を被実装体、ここではプリント配線基板1001に実装している。プリント配線基板1001には、電極1002及び1003が形成される。また、半導体装置の配線313及び314と接続する電極1004及び1005も形成する。そして電極1002と電極1005、電極1003と電極1004を半田1009により接続して実装する。この構成の場合、基板1007が可撓性基板であると、実装強度が非常に高くなり好ましい。

## 【0159】

また、半導体装置は側面が封止材1006で封止されている。光電変換素子と薄膜トランジスタの間に挟持される導電膜等が接着機能を有さない場合は、この封止材1006に接着機能を持たせれば、基板同士を貼り合わせることができる。

## 【0160】

本実施例では、プリント配線基板1001に基板1007が半田により接着され、実装されている。従って、光電変換素子は基板1008を通過する光を受光する。しかし、実装される形は本実施例に限られず、半導体装置を180度回転させ、基板1008を半田

10

20

30

40

50

によりプリント配線基板 1001 に接着し、基板 1007 を通過した光を受光しても良い。また、半田で実装しなくとも、導電性を有する接着剤を用いて実装しても良い。このときは、導電性を有する接着剤を用いて実装すると同時に半導体装置の側面の封止を行うと良い。

#### 【実施例 8】

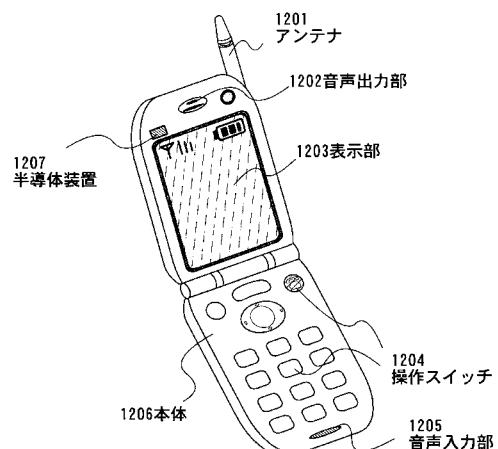

##### 【0161】

本実施例では、本発明を適用して携帯電話を完成させた一例を図 10 に示す。本体 1206、音声出力部 1202、音声入力部 1205、表示部 1203、操作スイッチ 1204、アンテナ 1201、半導体装置 1207 などにより構成されている。本発明の半導体装置 1207 を表示部 1203 の近くに備えることで、携帯電話使用中の周囲の明るさを測定することができ、その測定値により、携帯電話のバックライトの照度を適切に制御することができる。これにより、消費電力の少ない携帯電話を実現できる。

##### 【0162】

本発明の半導体装置 1207 は薄くて軽いため、携帯電話の筐体内に実装しても他の部品の邪魔にならず、また、携帯電話の総重量をほとんど増加させない。

#### 【図面の簡単な説明】

##### 【0163】

【図 1】本発明の実施の形態 1 を示す図。

【図 2】本発明の実施の形態 2 を示す図。

【図 3】本発明の実施例 1 を示す図。

【図 4】本発明の実施例 2 を示す図。

【図 5】本発明の実施例 3 を示す図。

【図 6】本発明の実施例 4 を示す図。

【図 7】本発明の実施例 5 を示す図。

【図 8】本発明の実施例 6 を示す図。

【図 9】本発明の半導体装置の実装方法を示す図。

【図 10】本発明の半導体装置を携帯電話に搭載した図。

【図 11】本発明の従来例を示す図。

#### 【符号の説明】

##### 【0164】

30 T F T

31 T F T

101 第 1 の基板

102 薄膜トランジスタ

103 半導体層

104 ゲート絶縁膜

105 ゲート電極

106 層間絶縁膜

107 ソース電極またはドレイン電極

108 第 2 の基板

109 カソード電極

110 シリコン層

111 アノード電極

112 光電変換素子

113 異方性導電ペースト

114 電極

115 半田

116 封止材

117 絶縁膜

118 導電性粒子

10

20

40

50

|         |                |    |

|---------|----------------|----|

| 2 0 1   | 剥離層            |    |

| 2 0 2   | 接着剤            |    |

| 2 0 3   | 第3の基板          |    |

| 3 0 1   | 第1の基板          |    |

| 3 0 2   | 下地絶縁膜          |    |

| 3 0 3   | 半導体層           |    |

| 3 0 4   | ゲート絶縁膜         |    |

| 3 0 5   | ゲート電極          |    |

| 3 0 6   | 接続配線           |    |

| 3 0 7   | 接続配線           | 10 |

| 3 0 8   | 接続配線           |    |

| 3 0 9   | 第2の層間絶縁膜       |    |

| 3 1 0   | 第3の層間絶縁膜       |    |

| 3 1 1   | 第4の層間絶縁膜       |    |

| 3 1 2   | 配線             |    |

| 3 1 3   | 配線             |    |

| 3 1 4   | 配線             |    |

| 3 1 5   | ソース電極またはドレイン電極 |    |

| 3 2 1   | 第2の基板          |    |

| 3 2 2   | カソード電極         | 20 |

| 3 2 3   | フォトダイオード       |    |

| 3 2 4   | 絶縁膜            |    |

| 3 2 5   | アノード電極         |    |

| 3 2 6   | 端子電極           |    |

| 3 3 1   | 異方性導電ペースト      |    |

| 3 3 2   | 導電性粒子          |    |

| 4 0 1   | 第1の基板          |    |

| 4 0 2   | 第2の基板          |    |

| 4 0 3   | 半田             |    |

| 4 0 4   | 封止材            | 30 |

| 5 0 1   | 第1の基板          |    |

| 5 0 2   | 金属膜            |    |

| 5 0 3   | 下地絶縁膜          |    |

| 5 0 4   | 接着剤            |    |

| 5 0 5   | 第3の基板          |    |

| 6 0 1   | 第1の基板          |    |

| 6 0 2   | 剥離層            |    |

| 6 0 3   | 下地絶縁膜          |    |

| 6 0 4   | フォトダイオード       |    |

| 6 0 5   | 絶縁膜            | 40 |

| 6 0 6   | エッティング剤        |    |

| 6 0 7   | 接着剤            |    |

| 6 0 8   | 第3の基板          |    |

| 8 0 1   | 第1の基板          |    |

| 8 0 2   | 半導体装置          |    |

| 8 0 3   | 第2の基板          |    |

| 8 0 4   | 剥離層            |    |

| 8 0 5   | 孔              |    |

| 8 0 6   | エッティングガス       |    |

| 1 0 0 1 | プリント配線基板       | 50 |

|         |          |    |

|---------|----------|----|

| 1 0 0 2 | 電極       |    |

| 1 0 0 3 | 電極       |    |

| 1 0 0 4 | 電極       |    |

| 1 0 0 5 | 電極       |    |

| 1 0 0 6 | 封止材      |    |

| 1 0 0 7 | 基板       |    |

| 1 0 0 8 | 基板       |    |

| 1 0 0 9 | 半田       |    |

| 1 1 0 1 | 基板       |    |

| 1 1 0 2 | 薄膜トランジスタ | 10 |

| 1 1 0 3 | カソード電極   |    |

| 1 1 0 4 | シリコン層    |    |

| 1 1 0 5 | アノード電極   |    |

| 1 1 0 6 | 光電変換素子   |    |

| 1 2 0 2 | 音声出力部    |    |

| 1 2 0 2 | 音声出力部    |    |

| 1 2 0 3 | 表示部      |    |

| 1 2 0 4 | 操作スイッチ   |    |

| 1 2 0 5 | 音声入力部    |    |

| 1 2 0 6 | 本体       | 20 |

| 1 2 0 7 | 半導体装置    |    |

| 3 2 3 n | 光電変換層    |    |

| 6 0 4 n | 光電変換層    |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

F ターム(参考) 5F088 AA03 AB02 BA01 BA18 BB06 CA02 CB03 CB07 CB11 CB14

EA07 FA05 GA02 JA03 KA02 LA03