## (12) 发明专利

(10) 授权公告号 CN 109477868 B

(45) 授权公告日 2022.04.05

(21) 申请号 201780043151.7

(72) 发明人 R·F·佩恩 L·J·赫勒曼

(22) 申请日 2017.07.17

(74) 专利代理机构 北京纪凯知识产权代理有限公司 11245

(65) 同一申请的已公布的文献号

申请公布号 CN 109477868 A

代理人 赵志刚 赵蓉民

(43) 申请公布日 2019.03.15

(51) Int.CI.

G01R 31/28 (2006.01)

(30) 优先权数据

G06F 11/30 (2006.01)

15/211,782 2016.07.15 US

(85) PCT国际申请进入国家阶段日

2019.01.11

(56) 对比文件

CN 1519577 A, 2004.08.11

(86) PCT国际申请的申请数据

CN 1748154 A, 2006.03.15

PCT/US2017/042403 2017.07.17

CN 1623098 A, 2005.06.01

(87) PCT国际申请的公布数据

CN 101163978 A, 2008.04.16

W02018/014024 EN 2018.01.18

KR 100790238 B1, 2007.12.31

(73) 专利权人 德克萨斯仪器股份有限公司

田勇 等.基于SoC的嵌入式DRAM存储器内建自测试设计.《计算机测量与控制》.2012,

地址 美国德克萨斯州

审查员 蔡文亮

权利要求书2页 说明书7页 附图6页

## (54) 发明名称

用于电子电路的内建自测试的系统和方法

## (57) 摘要

在具有内建自测试的设备(305)的所述示例中,多路复用器(315)至少具有第一输入端子和第二输入端子并且其经耦合以在第一输入端子处接收第一输入信号(A),在第二输入端子处接收第二输入信号(B)以及接收选择信号(S1,S2)。此外,多路复用器(315)经耦合以:响应于选择信号(S1,S2)的第一组合输出(C)第一输入信号(A);响应于选择信号(S1,S2)的第二组合输出(C)第二输入信号(B);以及响应于选择信号(S1,S2)的第三组合输出(C)第一输入信号和第二输入信号(A,B)的模拟求和。

1. 一种带有内建自测试的设备,所述设备包括:

多路复用器,其至少具有第一输入端子和第二输入端子,并且所述多路复用器经耦合以在所述第一输入端子处接收第一输入信号,在所述第二输入端子处接收第二输入信号,接收选择信号,并且:响应于所述选择信号的第一组合输出所述第一输入信号;响应于所述选择信号的第二组合输出所述第二输入信号;以及响应于所述选择信号的第三组合输出所述第一输入信号和所述第二输入信号的模拟求和,其中所述输出的模拟求和用于测试所述设备;以及

发送器,其被配置为响应于第一控制信号而产生预定测试信号模式。

2. 根据权利要求1所述的设备,其还包括:

移相器,其经耦合以响应于第二控制信号选择性地改变到所述发送器的时钟信号的相位,其中,通过选择性地改变所述时钟信号的所述相位来选择性地调整所述第二输入信号的相位。

3. 根据权利要求2所述的设备,其还包括:

至少一个接收器电路,其经耦合以响应于所述多路复用器的输出提供至少一个本地信号;以及

误差检测器,其经耦合以生成至少一个比较信号,以指示所述至少一个本地信号是否与所述至少一个接收器电路的预期输出匹配。

4. 根据权利要求3所述的设备,其中,响应于来自所述误差检测器的所述至少一个比较信号,由控制单元提供所述第一控制信号和所述第二控制信号。

5. 根据权利要求4所述的设备,其中,所述第二输入信号是预定测试信号模式。

6. 根据权利要求5所述的设备,其中,所述预定测试信号模式是伪随机二进制序列模式。

7. 根据权利要求4所述的设备,其还包括:

输入缓冲器,其耦合到所述多路复用器的输出;

其中,所述至少一个接收器电路包括:至少一个内部时钟电路,其耦合到所述输入缓冲器的输出;时钟数据恢复单元,其耦合到所述至少一个内部时钟电路的至少一个输出;以及解复用器,其耦合到所述时钟数据恢复单元的输出;

其中,所述解复用器的输出是所述至少一个本地信号。

8. 一种设备测试的方法,所述方法包括:

生成第一信号;

将所述第一信号提供给多路复用器的第一输入端子;

生成第二信号;

将所述第二信号提供给所述多路复用器的第二输入端子,其中所述第二信号是预定测试信号模式;

利用所述多路复用器,生成第三信号作为所述第一信号和所述第二信号的模拟求和;以及

从所述多路复用器,提供所述第三信号以测试设备。

9. 根据权利要求8所述的方法,其中,生成所述第一信号和所述第二信号包括:

测量所述设备的输出信号;

确定所述设备的所述输出信号是否具有至少一个误差；以及

响应于确定所述设备的所述输出信号不具有至少一个误差，调整以下中的至少一个：所述第一信号的幅值；所述第二信号的幅值；以及所述第二信号的相位。

10. 根据权利要求9所述的方法，其中，确定所述设备的所述输出信号是否具有至少一个误差包括：

确定所述设备的所述输出信号是否与预定模式匹配；以及

响应于确定所述设备的所述输出信号与所述预定模式匹配，确定所述设备的所述输出信号不具有至少一个误差。

11. 根据权利要求10所述的方法，其中，所述预定测试信号模式是伪随机二进制序列模式。

12. 一种集成电路，其包括：

多路复用器，其至少具有第一输入端子和第二输入端子，并且所述多路复用器经耦合以在所述第一输入端子处接收第一输入信号，在所述第二输入端子处接收第二输入信号，接收选择信号，并且：响应于所述选择信号的第一组合输出所述第一输入信号；响应于所述选择信号的第二组合输出所述第二输入信号；以及响应于所述选择信号的第三组合输出所述第一输入信号和所述第二输入信号的模拟求和；

发送器，其耦合至所述多路复用器，以：向所述多路复用器提供所述第二输入信号；并且响应于第一控制信号选择性地改变所述第二输入信号的幅值；

移相器，其耦合至所述发送器，以响应于第二控制信号选择性地改变到所述发送器的时钟信号的相位，其中通过选择性地改变所述时钟信号的所述相位来选择性地调整所述第二输入信号的相位；

至少一个接收器电路，其耦合至所述多路复用器，以响应于所述多路复用器的输出提供至少一个本地信号；

误差检测器，其耦合至所述至少一个接收器电路，以生成至少一个比较信号，以指示所述至少一个本地信号是否与所述至少一个接收器电路的预期输出匹配；以及

控制单元，其耦合至所述误差检测器，以响应于来自所述误差检测器的所述至少一个比较信号提供所述第一输入信号、所述选择信号以及所述第一控制信号和所述第二控制信号。

13. 根据权利要求12所述的集成电路，其中，所述第二输入信号是预定测试信号模式。

14. 根据权利要求13所述的集成电路，其中，所述预定测试信号模式是伪随机二进制序列模式。

15. 根据权利要求12所述的集成电路，其还包括：

输入缓冲器，其耦合到所述多路复用器的输出；

其中，所述至少一个接收器电路包括：至少一个内部时钟电路，其耦合到所述输入缓冲器的输出；时钟数据恢复单元，其耦合到所述至少一个内部时钟电路的至少一个输出；以及解复用器，其耦合到所述时钟数据恢复单元的输出；其中，所述解复用器的输出是所述至少一个本地信号。

## 用于电子电路的内建自测试的系统和方法

### 技术领域

[0001] 本发明总体涉及电子电路，并且更具体地涉及电子电路的内建自测试。

### 背景技术

[0002] 集成电路 (IC) 可以被设计和构建有被配置为执行自测试的附加硬件和软件。内建自测试 (BIST) 系统使集成电路能够测试其自身的功能和操作。在某些情况下，集成电路不需要外部自动化自测试仪器来验证其功能。通常，BIST 系统生成测试信号模式以运行通过 IC 的内部电路，然后收集来自各种内部组件的响应以确定响应是否与预定的预期响应匹配。高数据速率 IC 可以特别受益于周密的表征、生产测试和系统内调试能力。如果需要专用且昂贵 (例如典型成本>10万美元) 的误码率测试仪和示波器，则这样的要求限制了使用现成的低成本的自动化测试仪器 (ATE) 的能力。

[0003] 在许多数字数据通信应用中，通信是双向的，并且在通信链路的两端使用包括发送器和接收器的组合的 IC。这种组合也称为收发器。在收发器中，“环回 (lookback)” 测试功能提供“以设备速度”的功能测试。BIST 可以生成用于发送器的可以被环回到接收器的测试模式。这使得能够在收发器 IC 内以设备速度测试接收器功能。在使用集成电路的其他数字通信应用中，通信在单个方向上，其中上游发送器与下游接收器通信。一个常见的示例是用于显示设备的视频接口，其是没有传输能力的“仅接收”设备。其他设备包括处理器、视频控制器、现场可编程门阵列 (FPGA) 或专用集成电路 (ASIC)，其将数据发送到显示设备。

[0004] 在收发器系统中，环回 BIST 功能仅提供通过/失败指示，并且不提供设备裕量测量。在环回功能中，直接测量接收器实际接收的信号是不实际的，因为“环路”在设备内完成。可以进行的最接近的测量通常是在设备的外部焊盘/引脚处。可以探测这些焊盘/引脚，但不测量附加的信号劣化 (例如由电镀短截线、键合线和/或非理想终端引起的反射)。对于独立接收器，在以设备速度测试接收器功能上存在挑战，因为测试是使用外部连接进行的，这可能会引入噪声和使测试结果偏离的其他干扰。在高速通信系统中，电信号的信号完整性对于无误差、稳健链路是重要的。

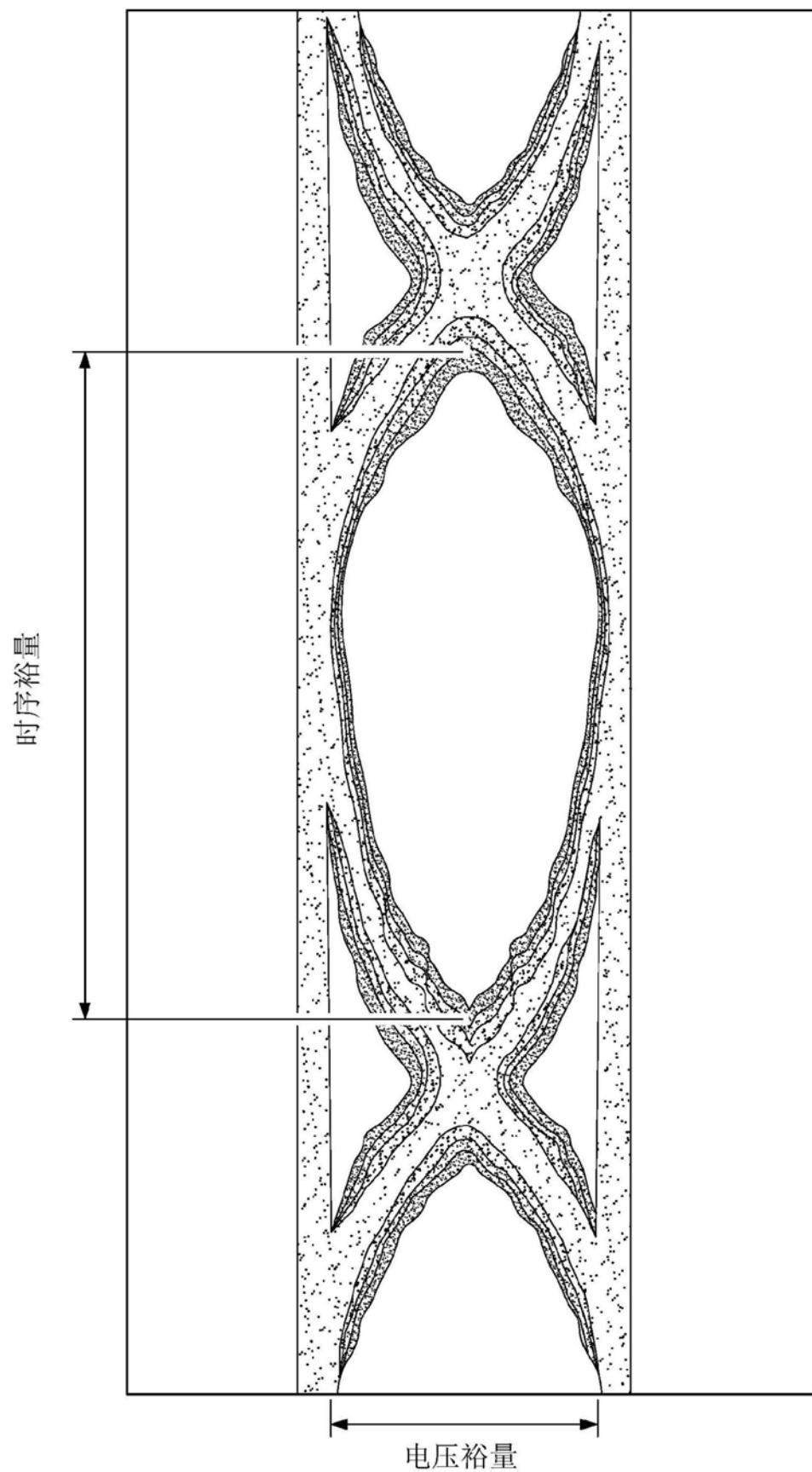

[0005] 图1示出了示例“数据眼 (data eye)”图，其用于评估通信链路的性能。在数据眼图测量中，可以直接测量时序和电压裕量。这通常使用连接到封装 IC 的外部边界或测试连接 (例如，引脚、球或焊盘) 的高速示波器来完成。随着眼在垂直方向上变得更“张开”，接收器可获得更多的电压裕量 (被测量为眼的幅值)。类似地，随着“眼”在水平方向上变得更张开，接收器可获得更多的时序裕量 (被测量为眼的宽度)。

[0006] 该测量具有若干缺点。首先，它使用昂贵的示波器，这可能在测试环境中不可获得，并且同样可能在完成或组装的系统中不可获得。其次，通过在封装 IC 的外部边界进行测量，数据眼图不提供设备内部功能的完整视图。

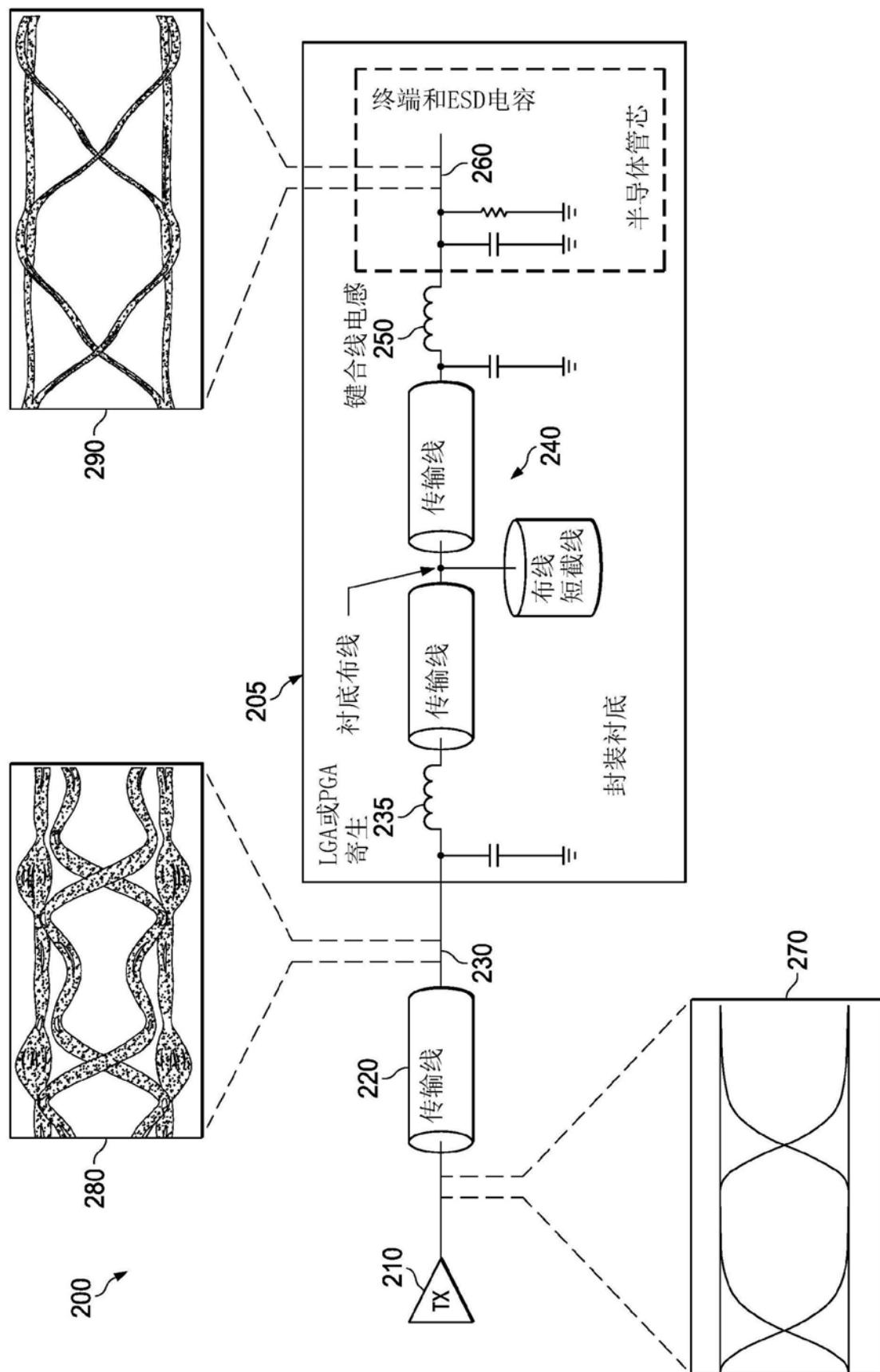

[0007] 图2示出了具有传统测试和测量方法的示例电路200。电路200包括被配置为仅接收数据的接收器电路205 (例如，显示单元)。电路200还包括发送器210。发送器210可以是被配置为向下游发送数据到接收器205的任何电路。来自发送器210的数据行进通过传输线

220(例如,电路板上的电路路径)。接收器205在接收器205电路封装的入口点230处接收数据。入口点230可以是任何电路连接,例如引脚栅格阵列(PGA)、平面栅格阵列(LGA)和类似的其他IC封装连接。IC封装在信号路径中引入寄生电感和电容235。该信号进一步行进通过接收器205的内部布线240并且可以由于各种因素引入进一步的信号异常,例如键合线电感250。该信号最终在IC中在终端点260处被接收。终端点260可以进一步将静电放电(ESD)保护电路、IC键合焊盘和接收器中的IC有源电路产生的寄生电容引入到传入信号。

[0008] 在传统的测试方法中,信号在发送器的出口点和接收器的入口点处被测试,而不在终端点260处测量接收器205内的电压和时序裕量。例如,当信号最初在发送器210的输出处被测量时,它可以图示理想的数据眼图270。然而,当在入口点230和终端点260处进行测量时,数据眼图可以分别表示为如眼图280和290所示。这是由于IC封装和/或IC管芯(die)的非理想性和电学行为引起的进一步的信号损失、反射、滤波和均衡。数据眼图在每个信号点处为电压和时间提供不同的裕量。如图所示,传统测试方法无法提供接收器电压和时序裕量的数据。

## 发明内容

[0009] 在具有内建自测试的设备的所述示例中,多路复用器至少具有第一输入端子和第二输入端子,并且该多路复用器经耦合以在第一输入端子处接收第一输入信号,在第二输入端子处接收第二输入信号以及接收选择信号。此外,多路复用器经耦合以;响应于选择信号的第一组合输出第一输入信号;响应于选择信号的第二组合输出第二输入信号;以及响应于选择信号的第三组合输出第一输入信号和第二输入信号的模拟求和。

## 附图说明

- [0010] 图1(现有技术)是示例“数据眼”图。

- [0011] 图2(现有技术)说明了具有传统测试和测量方法的示例电路。

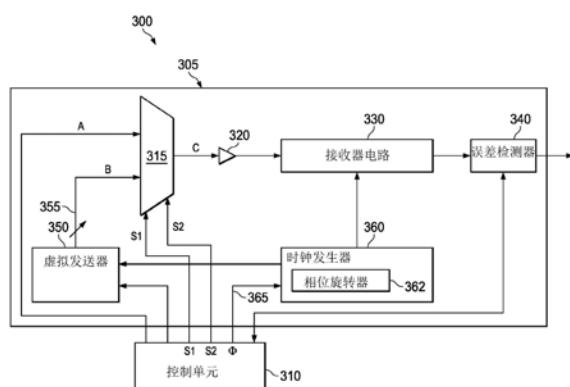

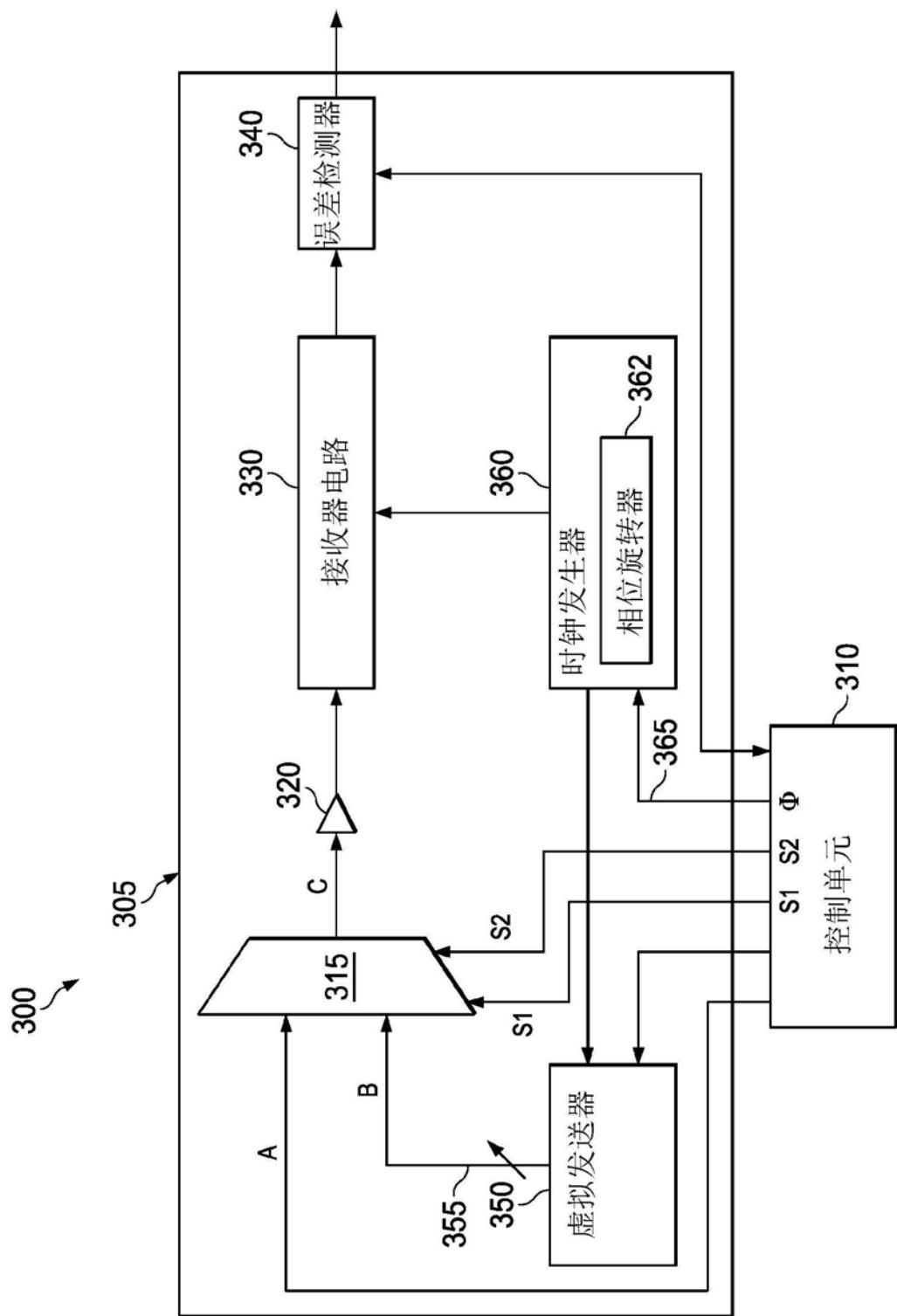

- [0012] 图3A是根据一个实施例的示例内建自测试系统的框图。

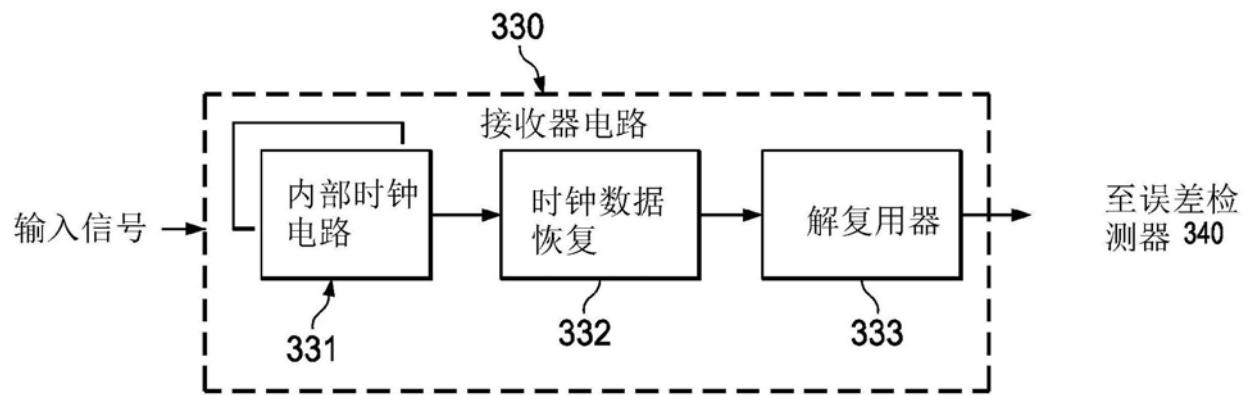

- [0013] 图3B是图3A的系统的接收器电路的示例的框图。

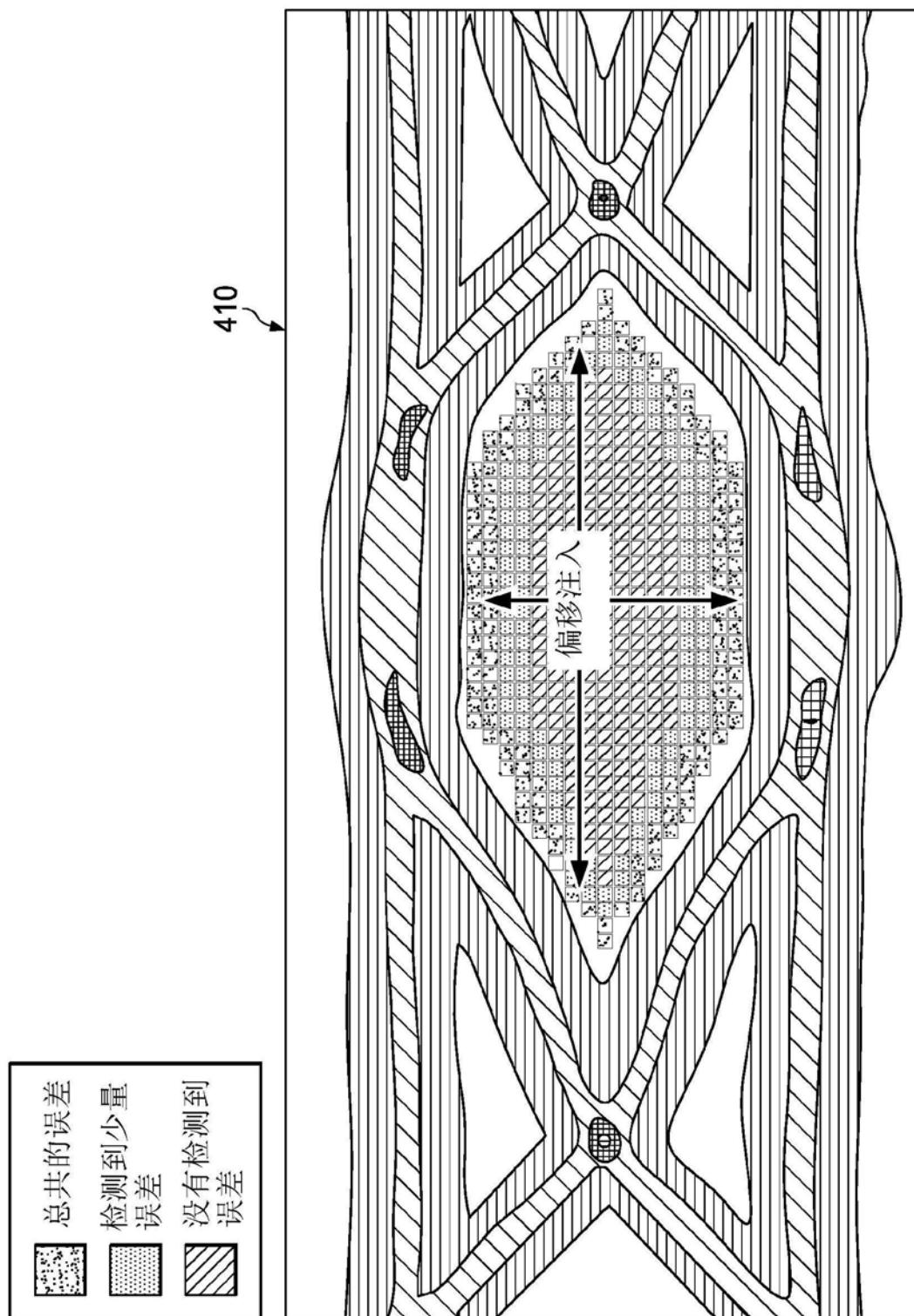

- [0014] 图4A是根据一个实施例的接收器的内建自测试功能的示例数据眼图。

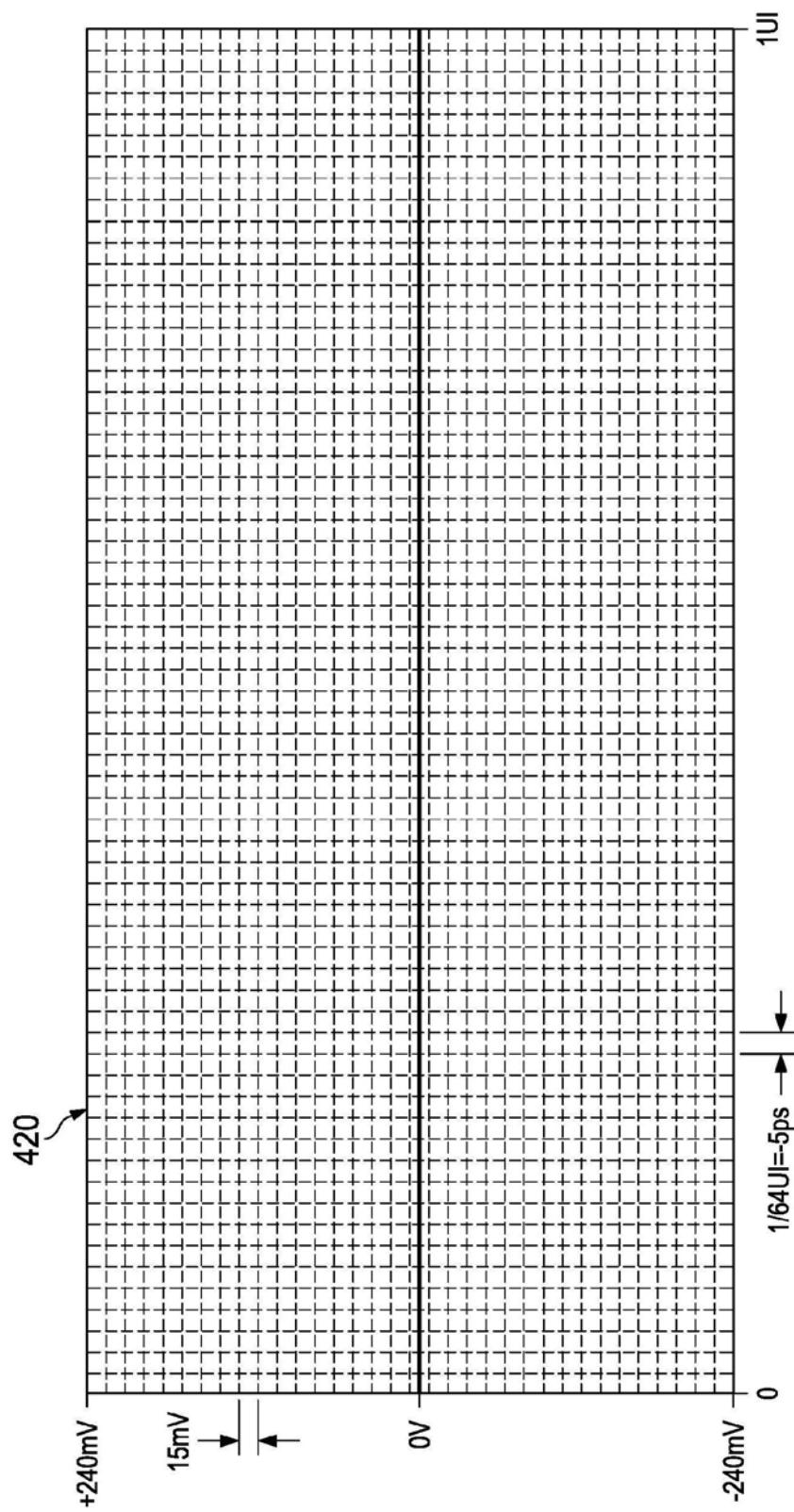

- [0015] 图4B是图4A的示例数据眼图的时序和电压标度的曲线图。

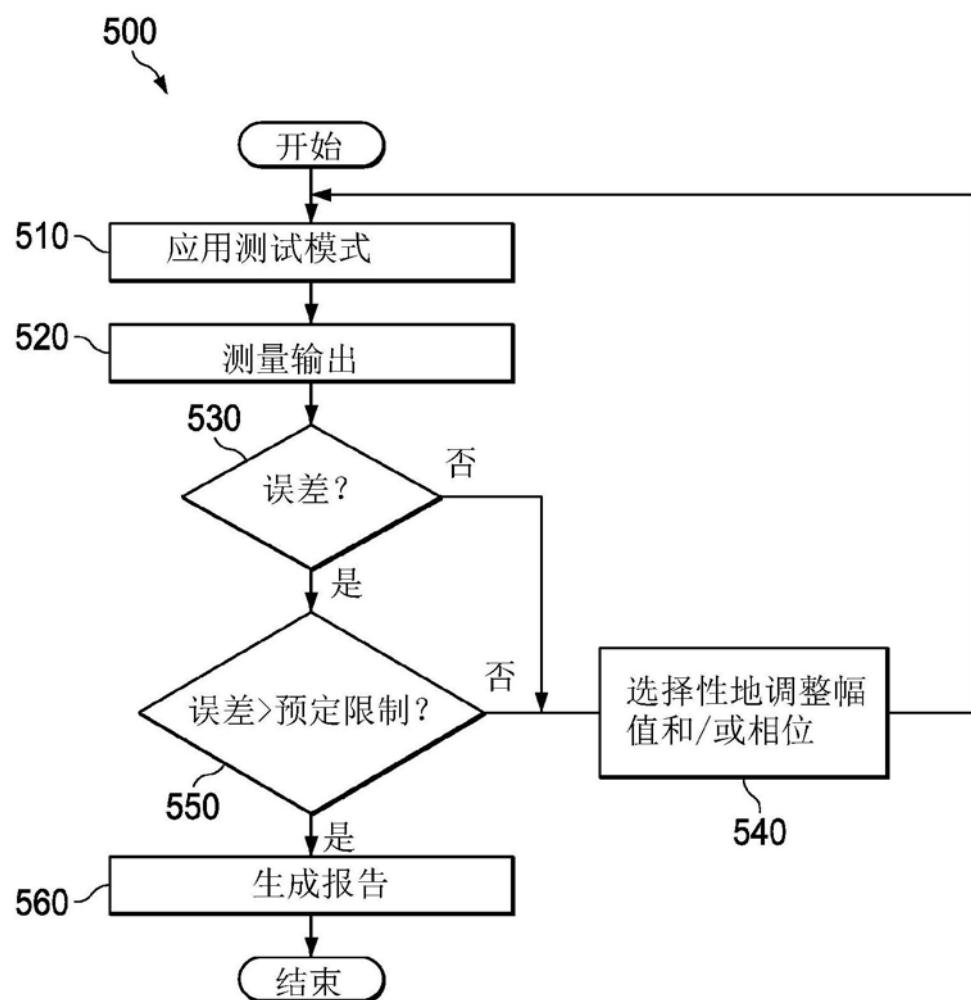

- [0016] 图5是根据一个实施例的用于使用内建自测试系统测量设备的电压和时序裕量的示例过程的流程图。

## 具体实施方式

- [0017] 为了测量IC封装内部的信号完整性(其中接收器感测实际信号),示例实施例测量IC封装内的电压和时序裕量,即使IC封装的高速数据速率超过外部测试硬件的能力。

- [0018] 在用于测试集成电路的系统和方法的所描述的示例中,该系统包括:发送器,其被配置为提供内部可编程输入,其能够修改输入测试信号的幅值和时钟相位以识别误差并准确地确定设备的电压和时序裕量。

- [0019] 图3A示出了根据一个实施例的示例内建自测试系统300。BIST 300包括接收器305和控制单元310。如本文所述,控制单元310可以是被配置为测试接收器305的各种功能并提

供关于功能、电压和时序裕量以及接收器305的各种其他方面的数据的任何计算设备。在该示例中,接收器305的各种组件形成在单个集成电路管芯上。

[0020] 接收器305包括专用多路复用器315。在该示例中,多路复用器315具有: (a) 两个输入端子A和B,其分别用于接收第一输入信号和第二输入信号;以及 (b) 输出端子C,其用于响应于那些输入信号输出输出信号。此外,多路复用器315具有两个选择端子S1和S2,在该示例中其用于从控制单元310接收两个选择信号。

[0021] 在第一示例中,第一输入信号和第二输入信号(分别在输入端子A和B处)是数字信号。在第二示例中,第一输入信号和第二输入信号(分别在输入端子A和B处)是模拟信号。如图3A的示例所示: (a) 从控制单元310接收第一输入信号(在输入端子A处),控制单元310是接收器305的集成电路管芯外部的源;以及 (b) 从虚拟发送器350接收第二输入信号(在输入端子B处),虚拟发送器350是接收器305的集成电路管芯内(内部)的源。

[0022] 多路复用器315响应于选择信号(在端子S1和S2处)输出输出信号(在端子C处),如下表1所示。

[0023] 表1

| [0024] | S1 | S2 | C   |

|--------|----|----|-----|

|        | 0  | 0  | X   |

|        | 0  | 1  | A   |

|        | 1  | 0  | B   |

|        | 1  | 1  | A+B |

[0025] 因此,响应于具有二进制值“11”的选择信号(在端子S1和S2处),多路复用器315: (a) 执行(来自端子A和B)输入信号的模拟求和;以及 (b) 输出模拟求和作为端子C处的输出信号,因此端子C处的输出信号(即,那些输入信号的模拟求和)是连续的模拟信号,即使输入信号(来自端子A和B)是数字信号。与多路复用器315不同,传统的多路复用器响应于其(一个或更多个)选择信号仅输出其输入信号中的一个。

[0026] 响应于具有二进制值“00”的选择信号(在端子S1和S2处),多路复用器315操作端子C以具有如表1所示的“X值”。根据特定实施方式的需要,“X值”是“无效”状态,诸如浮动值(例如,高阻抗)、接地零值、拉高值或其他值。

[0027] 此外,响应于如表1所示的具有二进制值“01”的选择信号(在端子S1和S2处),多路复用器315操作端子C以具有与来自端子A的输入信号相同的值。类似地,响应于如表1所示的具有二进制值“10”的选择信号(在端子S1和S2处),多路复用器315操作端子C以具有与来自端子B的输入信号相同的值。

[0028] 选择信号(在端子S1和S2处)的特定值通过表1中的示例示出,但是多路复用器315可以在其他示例中被配置成响应于那些选择信号的不同值而生成期望的输出C。例如: (a) 在第一替代实施例中,响应于具有二进制值“00”的选择信号(在端子S1和S2处),多路复用器315操作端子C以具有与来自端子A的输入信号相同的值,而不是具有“X值”; (b) 在第二替代实施例中,响应于具有二进制值“00”的选择信号(在端子S1和S2处),多路复用器315操作端子C以具有与来自端子B的输入信号相同的值,而不是具有“X值”;以及 (c) 在第三替代实施例中,响应于具有二进制值“00”的选择信号(在端子S1和S2处),多路复用器315操作端子C以具有与来自多路复用器315的第三端子D(图3A中未示出)的输入信号相同的值,而不是

具有“X值”。

[0029] 此外,在该第三替代实施例中,响应于具有二进制值“11”的选择信号(在端子S1和S2处),多路复用器315: (a) 执行(来自端子A、B和D)输入信号的模拟求和; (b) 输出模拟求和作为端子C处的输出信号,因此端子C处的输出信号(即,那些输入信号的模拟求和)是连续的模拟信号,即使输入信号(来自端子A、B和D)是数字信号。

[0030] 接收器305还包括输入缓冲器/驱动器320,其经耦合以将来自端子C的输出信号驱动到其他信号接收器电路330。误差检测器340经耦合以:接收电路330的输出;将该输出与预定输入信号(例如,来自控制单元310的测试信号)进行比较;以及(c)将该比较的结果提供给控制单元310(并且可选地提供给接收器305的集成电路管芯内或外部的其他单元)。例如,在至少一个实施例中,误差检测器340: (a) 从控制单元310接收预期输出信号的预定模式(pattern); (b) 将该预定模式与电路330的输出进行比较;以及(c) 将该比较的结果提供给控制单元310(并且可选地提供给接收器305的集成电路管芯内或外部的其他单元)。在第一示例中,误差检测器340的输出是该比较的二进制通过/失败指示(并且可选地到接收器305的集成电路管芯内或外部的其他单元)。在第二示例中,误差检测器340的输出是该比较的详细报告。

[0031] 时钟发生器360经耦合以为接收器305操作提供时钟信号。为清楚起见,尽管图3A示出了时钟发生器360仅连接到接收器305内的电路330和虚拟发送器350,但时钟发生器360还耦合到接收器305内的其他组件。如图3A所示,时钟发生器360包括集成相位旋转器(移位器)362。在另一个示例中,移相器在时钟发生器360的外部。时钟发生器360生成时钟频率,以用于接收器305以期望的速度操作。控制单元310经耦合以经由控制信号线365向时钟发生器360提供各种控制信号,例如控制信号,其用于以期望的频率(例如,数据眼图的中心频率)冻结内部时钟;改变/旋转内部时钟信号的相位以确定接收器305的时序裕量以及如本文所解释的其他方面。如果移相器在时钟发生器360外部,则控制单元310经耦合以向该外部移相器提供合适的相移控制信号。

[0032] 虚拟发送器350可配置(例如,可编程)以生成预定测试信号模式。如图3A所示,虚拟发送器350经耦合以经由多路复用器315和缓冲器/驱动器320将那些预定测试信号模式输出到接收器电路330。更具体地,虚拟发送器350经由连接到多路复用器315的输入端子B的信号线355输出那些预定测试信号模式。预定测试信号模式可以是任何形式的伪随机二进制序列(“PRBS”)模式,例如一系列逻辑“1”(例如,正电压)、逻辑“0”(例如,负电压)或被配置为在各种条件下测试接收器305的功能的其他预定信号模式。响应于其从控制单元310接收的适当控制信号,根据其配置(例如,编程),测试信号模式的幅值(amplitude)通过虚拟发送器350连续可变(可调节),这有利地实现接收器305操作的微调。因此,如上所述,控制单元310监视从误差检测器340输出的比较结果。响应于那些比较结果(以及可选地其他因素),控制单元310将合适的控制信号输出到虚拟发送器350,响应于此,该虚拟发送器350调整(连续增加/减少)测试信号模式的幅值,从而确定使接收器305在其最佳能力内工作的电压裕量。

[0033] 接收器305的时序裕量可以通过调整来自时钟发生器360的其内部时钟的相位来确定。例如,控制单元310可最初输出合适的控制信号,用于使时钟发生器360将内部时钟的相位冻结在特定频率(例如,理想数据眼图的中心)处,并且然后旋转/改变内部时钟的相

位,因此控制单元310:通过监视从误差检测器340输出的比较结果来确定那些相位旋转/改变的影响;并且从而测量接收器305的时序裕量。如果移相器在时钟发生器360的外部(如上文的另一个示例中所讨论的),则控制单元310输出合适的控制信号,用于使外部移相器生成用于接收器电路330的任意时钟相位,然后在各个方向上调整相位(例如,提前或延迟)以确定接收器305的时序裕量。

[0034] 控制单元310还经耦合以经由多路复用器315的输入端子A直接输出可配置(例如,可编程)测试信号模式。通过控制单元310适当地控制多路复用器315的端子S1和S2以具有如上所述的二进制值“11”,(来自控制单元310经由输入端子A的)那些测试信号模式可与(来自虚拟发送器350经由输入端子B的)其他测试信号模式组合。通过以这种方式适当地组合这些测试信号模式,控制单元310根据其配置(例如,编程)调整(来自虚拟发送器350经由输入端子B的)其他测试信号模式的幅值,因此控制单元310通过监视从误差检测器340输出的比较结果来确定那些幅值调整的影响。

[0035] 此外,如上所述,控制单元310被配置为输出合适的控制信号,用于使得:(a)虚拟发送器350调整多路复用器315的输入端子B处的测试信号模式的幅值;以及(b)时钟发生器360改变/旋转接收器305的内部时钟信号的相位。因此,通过使接收器305在测试信号模式、幅值和时钟相位的各种组合下操作,控制单元310确定接收器305的更完整的功能概况(profile)。例如,通过监视在这样的测试期间从误差检测器340输出的比较结果,控制单元305可以生成数据眼图以确定接收器305的功能裕量(例如,电压和时序)。

[0036] 图3B示出了接收器电路330(图3A)的示例。在该示例中,接收器电路330包括内部时钟电路331,其经耦合以响应于来自缓冲器/驱动器320的信号提供本地时钟信号(用于各种内部功能单元)。时钟数据恢复单元332经耦合以从电路331的输出恢复数据和时钟信号。解复用器333经耦合以通过对单元332的(一个或更多个)输出进行解复用而将接收器电路330的输出信号提供给误差检测器340。为清楚起见,图3B示出了其组件之间的单独信号线,但是,基于接收器305中使用的多个位线,这些组件可以通过多个信号线进行连接。此外,接收器电路330和接收器305可以包括许多其他内部元件(未示出)。

[0037] 图4A示出了根据一个实施例的接收器(例如接收器305)的BIST功能的示例数据眼图410。可以使用针对测试信号模式的时钟相位和幅值的各种偏移来测量数据眼图410中的眼的“开口”。例如:(a)当测试模式的幅值改变时,眼睛可以在竖直方向上伸展/缩回;以及(b)当时钟的相位改变时,眼可以在水平方向上扩展/缩回。如图4A所示,眼的中心部分可以提供接收器(例如,接收器305)的可接受的工作范围。随着时钟相位和测试幅值被推向眼的边缘,误差率可能会增加,以提供接收器的功能裕量(电压和时序)的详细视图。

[0038] 接收器中的误差检测器(例如,误差检测器340)可以将预期接收的数据模式与实际接收的数据模式进行比较。如果接收器的输入与误差检测器所预期的模式相同,则误差检测器输出无误差的指示。最终,随着虚拟发送器350注入的偏移的电平增大,偏移将大于输入信号,接收器灵敏度将受到损害,并且误差检测器检测到误差。通过监视误差检测器的输出并调整测试模式的幅值,可以确定接收器的灵敏度。

[0039] 如图4A所示,在眼的“中间”,接收器灵敏度和可用信号足以克服由虚拟发送器350注入的任何偏移。最初,随着接近信号幅值的边缘,误差检测器检测到的误差很少。当注入的偏移的幅值增大时,生成大量的误差。使用此调整,可以完全确定和表征接收器灵敏度。

[0040] 图4B示出用于示例数据眼图410(图4A)的时序和电压标度420。对于3.2Gbps的数据速率,64个时序单位步长(每个大约4.88ps)跨越312.5ps的位单位间隔(UI),并且可用于裕量测试。类似地,32个幅值步长(每个15mV)跨越+/-240mV的总电压范围,并且可用于电压裕量测试。通过使接收器305在这些偏移的各种组合下操作,控制单元310测量(在接收信号的数据眼内部的)许多时序和电压偏移点以确定误差检测器340是否接收到无误差数据。例如。控制单元310使用这些测量来评估时钟数据恢复单元332(图3B)的功能。频率和电压的步长或“切片(slices)”对于时序域和电压域中的灵敏度测量都是有用的,从而使控制单元310能够生成数据眼图的“眼”轮廓。通过适当地编程时钟的相位并且添加竖直灵敏度测量(由虚拟发送器350提供),控制单元310映射了“眼”的整个轮廓。为了生成接收器305的给定概况,该示例使用15mV和4.88ps,但是基于给定设备的电压和时钟额定值,可以使用任何数量和大小的步长。

[0041] 图5示出了根据一个实施例的用于使用BIST测量设备(例如,接收器305)的电压和时序裕量的示例过程500。最初在510处,控制单元310将预定测试模式应用于接收器305。如上文结合图3A所讨论的,预定模式可以包括应用来自虚拟发送器350的伪随机二进制序列;应用来自控制单元310的测试模式和/或其组合。在520处,控制单元310(直接地或经由误差检测器340)测量接收器电路330的输出以确定输出是否匹配预期输出信号的预定模式。在至少一个示例中,误差检测器340从控制单元310接收该预定模式,并确定接收器电路330的输出是否匹配该预定模式。在530处,控制单元310(例如,通过接收误差检测器340比较的结果)确定接收器电路330的输出是否包括误差。

[0042] 如果控制单元310(在530处)确定接收器电路330的输出不包括任何误差,则控制单元310使用预定步长(例如上面结合图4A和图4B讨论的时序单位步长和幅值步长)选择性地(在540处)调整测试信号的幅值和/或时钟的相位。如上所述,控制单元310能够基于要用于接收器305的测量模型,单独地或以组合方式和/或可选地利用其他偏移来选择性地调整测试信号的幅值和/或时钟的相位。在以这种方式(在540处)调整幅值和/或相位之后,控制单元310将具有这种调整的幅值和/或相位(并且可选地具有这样的其他偏移)的测试模式(在510处)应用到接收器305以用于下一次测量。

[0043] 如果控制单元310(在530处)确定接收器电路330的输出包括误差,则控制单元310(在550处)确定误差的数量是否超过预定限制。预定限制可以基于数据眼图的“结构”。例如,如果所应用的偏移将“眼”伸展到其外部限制(水平和/或垂直),则误差的数量可能增加。

[0044] 此外,预定限制可以基于设备(例如,接收器305)额定值和信号误差容限。例如,如果设备用于某些基于精度的应用,则即使少量误差可能也是不可接受的,因此可以将预定误差限制设置为保守的低数量。或者,如果设备用于某些高误差容限应用,则可以将预定的误差限制设置为充分高的数量。

[0045] 如果控制单元310(在550处)确定误差的数量未超过预定限制,则控制单元310:(a)使用预定步长选择性地(在540处)调整测试信号的幅值和/或时钟的相位;以及(b)将具有这种调整的幅值和/或相位(以及可选地具有这样的其他偏移)的测试模式(在510处)应用到接收器305以用于下一次测量。或者,如果控制单元310(在550处)确定误差的数量超过预定限制,则这样的数量可以指示接收器305范围的外部边界,因此控制单元310(在560处)

生成其报告。在至少一个示例中,报告包括测量的数据眼图和相关参数,包括: (a) 在测试模式的各个阶段的数据眼图的形状和形式;以及 (b) 这些阶段的信号幅值和/或时钟相位的值。

[0046] 在所描述的实施例中,修改是可能的,并且在权利要求的范围内,其他实施例也是可能的。例如,不一定要求操作以本文所述的特定顺序发生。而且,在一些实施例中可能不需要一些操作。

图1(现有技术)

图2 (现有技术)

图3A

图3B

图5

图4A

图4B