(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-352137

(P2006-352137A)

(43) 公開日 平成18年12月28日(2006.12.28)

| (51) Int.C1.                  | F 1             | テーマコード (参考) |

|-------------------------------|-----------------|-------------|

| <b>HO1L 21/8242 (2006.01)</b> | HO1L 27/10 681C | 5FO33       |

| <b>HO1L 27/108 (2006.01)</b>  | HO1L 27/10 621C | 5FO83       |

| <b>HO1L 21/3205 (2006.01)</b> | HO1L 21/88 Z    |             |

| <b>HO1L 23/52 (2006.01)</b>   |                 |             |

審査請求 未請求 請求項の数 54 O L (全 24 頁)

|              |                              |          |                                                                                   |

|--------------|------------------------------|----------|-----------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2006-166127 (P2006-166127) | (71) 出願人 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区梅灘洞 416 |

| (22) 出願日     | 平成18年6月15日 (2006.6.15)       | (74) 代理人 | 100064908<br>弁理士 志賀 正武                                                            |

| (31) 優先権主張番号 | 10-2005-0052654              | (74) 代理人 | 100089037<br>弁理士 渡邊 隆                                                             |

| (32) 優先日     | 平成17年6月17日 (2005.6.17)       | (74) 代理人 | 100108453<br>弁理士 村山 靖彦                                                            |

| (33) 優先権主張国  | 韓国 (KR)                      | (74) 代理人 | 100110364<br>弁理士 実広 信哉                                                            |

最終頁に続く

(54) 【発明の名称】少なくとも1つの開口部を有する最上部金属層を備える半導体素子及びその製造方法

## (57) 【要約】

【課題】少なくとも1つの開口部を有する最上部金属層を備える半導体素子を提供する。

【解決手段】前記半導体素子はセルアレイ領域を有する半導体基板及び前記セルアレイ領域を有する基板を覆う層間絶縁膜を備える。前記セルアレイ領域内の前記層間絶縁膜上部に最上部金属層が配置される。前記最上部金属層は少なくとも1つの開口部を有する。前記半導体素子の製造方法も提供される。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

セルアレイ領域を有する半導体基板と、

前記セルアレイ領域を有する基板を覆う層間絶縁膜と、

前記セルアレイ領域内の前記層間絶縁膜上部に配置され、少なくとも1つの開口部を有する最上部金属層と、

を含むことを特徴とする半導体素子。

**【請求項 2】**

前記セルアレイ領域は前記半導体基板に形成された複数のメモリセルを含み、前記層間絶縁膜は前記メモリセルを覆うことを特徴とする請求項1記載の半導体素子。

10

**【請求項 3】**

前記メモリセルのそれぞれは前記半導体基板に形成されたセルMOSトランジスタ及び前記セルMOSトランジスタのソース/ドレイン領域のうちいずれか1つに電気的に接続されたセルキャパシタを含むことを特徴とする請求項2記載の半導体素子。

**【請求項 4】**

前記セルアレイ領域内の前記層間絶縁膜上に配置された下部金属配線と、

前記下部金属配線を有する基板上に形成された下部金属層間絶縁膜と、をさらに含み、

前記最上部金属層は前記下部金属層間絶縁膜上部に配置され、前記少なくとも1つの開口部は前記下部金属配線間の前記下部金属層間絶縁膜の少なくとも一部分上に位置することを特徴とする請求項1記載の半導体素子。

20

**【請求項 5】**

前記セルアレイ領域内の前記下部金属層間絶縁膜上に配置され、前記下部金属配線の上部を横切る上部金属配線と、

前記上部金属配線を有する基板上に形成された上部金属層間絶縁膜と、をさらに含み、

前記最上部金属層は前記上部金属層間絶縁膜上部に配置され、前記少なくとも1つの開口部は前記下部金属配線間の前記下部金属層間絶縁膜と前記上部金属配線間の前記上部金属層間絶縁膜との重畠領域のうち少なくとも1つの上部に位置することを特徴とする請求項4記載の半導体素子。

30

**【請求項 6】**

前記少なくとも1つの開口部は前記最上部金属層を貫通する複数の開口部を含むことを特徴とする請求項1記載の半導体素子。

**【請求項 7】**

前記複数の開口部は複数のスリット及び/または複数のホールを含むことを特徴とする請求項6記載の半導体素子。

**【請求項 8】**

前記複数のスリット幅及びそれら間の間隔は0.5μmより大きいか同一であることを特徴とする請求項7記載の半導体素子。

40

**【請求項 9】**

前記複数のホール直径及びそれら間の間隔は0.2μmより大きいか同一であることを特徴とする請求項7記載の半導体素子。

**【請求項 10】**

前記最上部金属層を有する基板を覆うパッシベーション膜をさらに含むことを特徴とする請求項1記載の半導体素子。

**【請求項 11】**

前記パッシベーション膜は順に積層されたシリコン酸化膜及びシリコン窒化膜を含むことを特徴とする請求項10記載の半導体素子。

**【請求項 12】**

セルアレイ領域及び前記セルアレイ領域に隣接した周辺回路領域を有する半導体基板と、

前記セルアレイ領域内の前記半導体基板に形成された複数のメモリセルと、

50

前記周辺回路領域内の前記半導体基板に形成された少なくとも1つの周辺MOSトランジスタと、

前記メモリセル及び前記周辺MOSトランジスタを有する基板を覆う層間絶縁膜と、

前記セルアレイ領域内の前記層間絶縁膜上部に配置され、少なくとも1つの第1開口部を有する第1最上部金属層と、

前記周辺回路領域内の前記層間絶縁膜上部に配置され、前記周辺MOSトランジスタの上部に位置する少なくとも1つの第2開口部を有する第2最上部金属層と、

を含むことを特徴とする半導体素子。

#### 【請求項13】

前記周辺MOSトランジスタは高電圧MOSトランジスタであることを特徴とする請求項12記載の半導体素子。 10

#### 【請求項14】

前記セルアレイ領域内の前記層間絶縁膜上に配置された第1下部金属配線と、

前記第1下部金属配線及び前記層間絶縁膜を覆う下部金属層間絶縁膜と、をさらに含み、前記第1最上部金属層は前記下部金属層間絶縁膜上部に配置され、前記少なくとも1つの第1開口部は前記第1下部金属配線間の前記下部金属層間絶縁膜の少なくとも一部分上に位置することを特徴とする請求項12記載の半導体素子。

#### 【請求項15】

前記周辺回路領域内の前記層間絶縁膜と前記下部金属層間絶縁膜との間に配置された第2下部金属配線をさらに含み、前記第2最上部金属層は前記下部金属層間絶縁膜上部に配置され、前記少なくとも1つの第2開口部は前記第2下部金属配線間の前記下部金属層間絶縁膜の少なくとも一部分上に位置することを特徴とする請求項14記載の半導体素子。 20

#### 【請求項16】

前記セルアレイ領域内の前記下部金属層間絶縁膜上に配置されて前記第1下部金属配線の上部を横切る第1上部金属配線と、

前記第1上部金属配線及び前記下部金属層間絶縁膜を覆う上部金属層間絶縁膜と、をさらに含み、前記第1最上部金属層は前記上部金属層間絶縁膜上部に配置され、前記少なくとも1つの第1開口部は前記第1下部金属配線間の前記下部金属層間絶縁膜と前記第1上部金属配線間の前記上部金属層間絶縁膜との重疊領域のうち、少なくとも1つの上部に位置することを特徴とする請求項14記載の半導体素子。 30

#### 【請求項17】

前記周辺回路領域内の前記下部金属層間絶縁膜と前記上部金属層間絶縁膜との間に配置された第2上部金属配線をさらに含み、前記第2最上部金属層は前記上部金属層間絶縁膜上部に配置され、前記少なくとも1つの第2開口部は前記第2下部金属配線間の前記下部金属層間絶縁膜と前記第2上部金属配線間の前記上部金属層間絶縁膜との重疊領域のうち、少なくとも1つの上部に位置することを特徴とする請求項16記載の半導体素子。

#### 【請求項18】

前記少なくとも1つの第1開口部は前記第1最上部金属層を貫通する複数の第1開口部を含むことを特徴とする請求項12記載の半導体素子。

#### 【請求項19】

前記複数の第1開口部は複数の第1スリット及び/または複数の第1ホールを含むことを特徴とする請求項18記載の半導体素子。 40

#### 【請求項20】

前記複数の第1スリット幅及びそれら間の間隔は0.5μmより大きいか同一であることを特徴とする請求項19記載の半導体素子。

#### 【請求項21】

前記複数の第1ホール直径及びそれら間の間隔は0.2μmより大きいか同一であることを特徴とする請求項19記載の半導体素子。

#### 【請求項22】

前記少なくとも1つの第2開口部は前記第2最上部金属層を貫通する複数の第2開口部

50

を含むことを特徴とする請求項 1 2 記載の半導体素子。

【請求項 2 3】

前記複数の第 2 開口部は複数の第 2 スリット及び / または複数の第 2 ホールを含むことを特徴とする請求項 2 2 記載の半導体素子。

【請求項 2 4】

前記複数の第 2 スリット幅及びそれら間の間隔は  $0.5 \mu m$  より大きいか同一であることを特徴とする請求項 2 3 記載の半導体素子。

【請求項 2 5】

前記複数の第 2 ホール直径及びそれら間の間隔は  $0.2 \mu m$  より大きいか同一であることを特徴とする請求項 2 3 記載の半導体素子。

10

【請求項 2 6】

前記第 1 及び第 2 最上部金属層を有する基板を覆うパッシベーション膜をさらに含むことを特徴とする請求項 1 2 記載の半導体素子。

【請求項 2 7】

前記パッシベーション膜は順に積層されたシリコン酸化膜及びシリコン窒化膜を含むことを特徴とする請求項 2 6 記載の半導体素子。

【請求項 2 8】

セルアレイ領域を有する半導体基板を準備する段階と、

前記半導体基板を覆う層間絶縁膜を形成する段階と、

前記セルアレイ領域内の前記層間絶縁膜上に少なくとも 1 つの開口部を有する最上部金属層を形成する段階と、

を含むことを特徴とする半導体素子の製造方法。

【請求項 2 9】

前記層間絶縁膜を形成する前に前記セルアレイ領域内の前記半導体基板に複数のメモリセルを形成する段階をさらに含むことを特徴とする請求項 2 8 記載の半導体素子の製造方法。

【請求項 3 0】

前記最上部金属層を形成する前に前記セルアレイ領域内の前記層間絶縁膜上に下部金属配線を形成する段階と、

前記下部金属配線を有する基板上に下部金属層間絶縁膜を形成する段階と、をさらに含み、前記最上部金属層は前記少なくとも 1 つの開口部が前記下部金属配線間の前記下部金属層間絶縁膜の少なくとも一部分上に位置するように形成されることを特徴とする請求項 2 8 記載の半導体素子の製造方法。

【請求項 3 1】

前記セルアレイ領域内の前記下部金属層間絶縁膜上に上部金属配線を形成し、前記上部金属配線は前記下部金属配線の上部を横切るように形成する段階と、

前記上部金属配線を有する基板上に上部金属層間絶縁膜を形成する段階と、をさらに含み、前記最上部金属層は前記少なくとも 1 つの開口部が前記下部金属配線間の前記下部金属層間絶縁膜と前記上部金属配線間の前記上部金属層間絶縁膜との重畠領域のうち、少なくとも 1 つの上部に位置するように形成されることを特徴とする請求項 3 0 記載の半導体素子の製造方法。

【請求項 3 2】

前記少なくとも 1 つの開口部は前記最上部金属層を貫通する複数のスリット及び / または複数のホールを具備するように形成されることを特徴とする請求項 2 8 記載の半導体素子の製造方法。

【請求項 3 3】

前記複数のスリットは  $0.5 \mu m$  より大きいか同一の幅を有するように形成されることを特徴とする請求項 3 2 記載の半導体素子の製造方法。

【請求項 3 4】

前記複数のホールは  $0.2 \mu m$  より大きいか同一の直径を有するように形成されること

40

50

を特徴とする請求項 3 2 記載の半導体素子の製造方法。

【請求項 3 5】

前記最上部金属層を有する基板上にパッシベーション膜を形成する段階と、

前記パッシベーション膜を有する基板を熱処理する段階と、

をさらに含むことを特徴とする請求項 2 8 記載の半導体素子の製造方法。

【請求項 3 6】

前記パッシベーション膜はシリコン酸化膜及びシリコン窒化膜を順に積層させて形成することを特徴とする請求項 3 5 記載の半導体素子の製造方法。

【請求項 3 7】

前記基板を熱処理することは少なくとも水素ガスを含む雰囲気ガスを用いて実施することを特徴とする請求項 3 5 記載の半導体素子の製造方法。 10

【請求項 3 8】

セルアレイ領域及び周辺回路領域を有する半導体基板を準備する段階と、

前記セルアレイ領域内の前記半導体基板及び前記周辺回路領域内の前記半導体基板にそれぞれ複数のメモリセル及び少なくとも 1 つの周辺 MOS トランジスタを形成する段階と、

前記メモリセル及び前記周辺 MOS トランジスタを有する基板上に層間絶縁膜を形成する段階と、

前記セルアレイ領域内の前記層間絶縁膜上部及び前記周辺回路領域内の前記層間絶縁膜上部にそれぞれ第 1 最上部金属層及び第 2 最上部金属層を形成する段階と、を含み、前記第 1 最上部金属層は少なくとも 1 つの第 1 開口部を有するように形成され、前記第 2 最上部金属層は前記周辺 MOS トランジスタの上部に位置する少なくとも 1 つの第 2 開口部を有するように形成されることを特徴とする半導体素子の製造方法。 20

【請求項 3 9】

前記周辺 MOS トランジスタは高電圧 MOS トランジスタであることを特徴とする請求項 3 8 記載の半導体素子の製造方法。

【請求項 4 0】

前記セルアレイ領域内の前記層間絶縁膜上に第 1 下部金属配線を形成する段階と、

前記第 1 下部金属配線を有する基板上に下部金属層間絶縁膜を形成する段階と、をさらに含み、前記第 1 最上部金属層は前記少なくとも 1 つの第 1 開口部が前記第 1 下部金属配線間の前記下部金属層間絶縁膜の少なくとも一部分上に位置するように形成されることを特徴とする請求項 3 8 記載の半導体素子の製造方法。 30

【請求項 4 1】

前記セルアレイ領域内の前記下部金属層間絶縁膜上に第 1 上部金属配線を形成し、前記第 1 上部金属配線は前記第 1 下部金属配線の上部を横切るように形成する段階と、

前記第 1 上部金属配線を有する基板上に上部金属層間絶縁膜を形成する段階と、をさらに含み、前記第 1 最上部金属層は前記少なくとも 1 つの第 1 開口部が前記第 1 下部金属配線間の前記下部金属層間絶縁膜と前記第 1 上部金属配線間の前記上部金属層間絶縁膜との重疊領域のうち少なくとも 1 つの上部に位置するように形成されることを特徴とする請求項 4 0 記載の半導体素子の製造方法。 40

【請求項 4 2】

前記セルアレイ領域内の前記層間絶縁膜及び前記周辺回路領域内の前記層間絶縁膜上にそれぞれ第 1 下部金属配線及び第 2 下部金属配線を形成する段階と、

前記第 1 及び第 2 下部金属配線を有する基板上に下部金属層間絶縁膜を形成する段階と、をさらに含み、前記第 1 最上部金属層は前記少なくとも 1 つの第 1 開口部が前記第 1 下部金属配線間の前記下部金属層間絶縁膜の少なくとも一部分上に位置するように形成され、前記第 2 最上部金属層は前記少なくとも 1 つの第 2 開口部が前記第 2 下部金属配線間の前記下部金属層間絶縁膜の少なくとも一部分上に位置するように形成されることを特徴とする請求項 3 8 記載の半導体素子の製造方法。

【請求項 4 3】

10

20

30

40

50

前記セルアレイ領域内の前記下部金属層間絶縁膜及び前記周辺回路領域内の前記下部金属層間絶縁膜上にそれぞれ第1上部金属配線及び第2上部金属配線を形成し、前記第1上部金属配線は前記第1下部金属配線の上部を横切るように形成され、前記第2上部金属配線は前記第2下部金属配線の上部を横切るように形成する段階と、

前記第1及び第2上部金属配線を有する基板上に上部金属層間絶縁膜を形成する段階と、をさらに含み、前記第1最上部金属層は前記少なくとも1つの第1開口部が前記第1下部金属配線間の前記下部金属層間絶縁膜と前記第1上部金属配線間の前記上部金属層間絶縁膜との重畳領域のうち少なくとも1つの上部に位置するように形成され、前記第2最上部金属層は前記少なくとも1つの第2開口部が前記第2下部金属配線間の前記下部金属層間絶縁膜と前記第2上部金属配線間の前記上部金属層間絶縁膜との重畳領域のうち少なくとも1つの上部に位置するように形成されることを特徴とする請求項42記載の半導体素子の製造方法。

10

【請求項44】

前記少なくとも1つの第1開口部は前記第1最上部金属層を貫通する複数の第1スリット及び/または複数の第1ホールを具備するように形成され、前記少なくとも1つの第2開口部は前記第2最上部金属層を貫通する複数の第2スリット及び/または複数の第2ホールを具備するように形成されることを特徴とする請求項38記載の半導体素子の製造方法。

20

【請求項45】

前記第1及び第2スリットは0.5μmより大きいか同一の幅を有するように形成され、前記第1及び第2ホールは0.2μmより大きいか同一の幅を有するように形成されることを特徴とする請求項44記載の半導体素子の製造方法。

30

【請求項46】

前記第1及び第2最上部金属層を有する基板上にパッシベーション膜を形成する段階と、前記パッシベーション膜を有する基板を熱処理する段階と、をさらに含むことを特徴とする請求項38記載の半導体素子の製造方法。

【請求項47】

前記パッシベーション膜はシリコン酸化膜及びシリコン窒化膜を順に積層させて形成することを特徴とする請求項46記載の半導体素子の製造方法。

40

【請求項48】

前記基板を熱処理することは少なくとも水素ガスを含む雰囲気ガスを用いて実施することを特徴とする請求項46記載の半導体素子の製造方法。

【請求項49】

半導体基板と、前記半導体基板上に形成されたゲート電極と、前記半導体基板と前記ゲート電極との間に介在されたゲート絶縁膜と、前記ゲート電極上に配置された金属層間絶縁膜と、前記金属層間絶縁膜上に配置されたパッシベーション膜と、前記パッシベーション膜と前記金属層間絶縁膜との間に介在された最上部導電膜と、を含み、前記最上部導電膜は前記ゲート絶縁膜と整列された少なくとも1つの開口部を具備し、前記開口部は外部の水素原子が前記ゲート絶縁膜と前記半導体基板との間の界面に達する経路を提供することを特徴とする半導体素子。

50

【請求項50】

前記少なくとも1つの開口部は前記ゲート絶縁膜上部に位置することを特徴とする請求項49記載の半導体素子。

【請求項51】

前記最上部導電膜は前記パッシベーション膜と直接接触することを特徴とする請求項49記載の半導体素子。

【請求項52】

50

前記半導体基板の表面に平行な平面内に配置されてそれらとの間の上部開口部を画定する少なくとも一対の平行な上部金属配線と、

前記半導体基板の表面に平行な平面内に配置されてそれらとの間の下部開口部を画定する少なくとも一対の平行な下部金属配線と、をさらに含み、

前記上／下部開口部は互いに重畠して前記半導体基板の表面に垂直となる少なくとも1つの開口領域を画定し、前記最上部導電膜内の前記開口部は前記少なくとも1つの開口領域と整列されて前記水素原子の経路を限定することを特徴とする請求項49記載の半導体素子。

#### 【請求項53】

前記上部金属配線は前記下部金属配線の厚さと異なる厚さを有することを特徴とする請求項52記載の半導体素子。 10

#### 【請求項54】

前記金属層間絶縁膜は流動性酸化膜を含むことを特徴とする請求項49記載の半導体素子。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体素子及びその製造方法に関し、特に、少なくとも1つの開口部を有する最上部金属層を備える半導体素子及びその製造方法に関するものである。

#### 【背景技術】

#### 【0002】

D R A M 素子のような半導体素子は複数のセルを具備する。前記D R A M セルのそれぞれは電気的に直列接続されたセルキャパシタ及びセルトランジスタで構成され、前記セルトランジスタはビットラインに電気的に接続される。前記セルトランジスタは書き込み動作中にオンにされて前記ビットラインに誘導電圧に相応するデータを前記セルキャパシタに伝送する。また、前記セルトランジスタは、読み出し動作中にもオンにされて前記セルキャパシタに保存されたデータを前記ビットラインに伝送する。これとは反対に、前記セルトランジスタは待機モードでオフにされて前記セルキャパシタに保存されたデータを保持する。

#### 【0003】

しかしながら、前記セルトランジスタが待機モードでオフにされても前記セルキャパシタに保存されたデータ（すなわち、電荷）は多様な漏洩電流経路を介して時間が経過とともに消滅される。このような漏洩電流経路は前記セルトランジスタの特性と密接な関係がある。例えば、前記セルトランジスタのゲート絶縁膜の界面トラップ密度が増加したり、前記セルトランジスタのチャネル長が減少したりする場合に、前記セルトランジスタはオフにされても前記セルトランジスタは高い漏洩電流を示す。これによって、前記D R A M 素子はリフレッシュ回路を採用して前記セルキャパシタ内にデータを周期的に書き込む。

#### 【0004】

前記セルトランジスタが高い漏洩電流を示すと、前記リフレッシュ動作の周期は減少されなければならない。この際、前記D R A M 素子の電力消耗は増加する。よって、低電力D R A M 素子を具現するためには前記セルトランジスタの漏洩電流特性を改善させなければならない。

#### 【0005】

前記D R A M 素子を含む大部分の半導体素子は、後半工程（b a c k - e n d p r o c e s s）として水素熱処理（h y d r o g e n a l l o y）工程を用いて製造される。前記水素熱処理工程はM O S トランジスタの欠陥、特に、ゲート絶縁膜の界面トラップ密度を減少させるのに非常に効果的である。よって、前記水素熱処理工程を実施する場合、前記D R A M 素子のリフレッシュ特性は改善できる。前記水素熱処理工程は一般に金属配線及びパッシベーション膜を形成した後に実施される。

10

20

30

40

50

## 【0006】

一方、前記DRAM素子の集積度及び動作速度を改善させるために、多層金属配線技術 (multi-layered metal technique) が広く用いられ、前記セルトランジスタは徐々に縮小されつつある。この場合、前記DRAM素子のセルアレイ領域上部に電源線として用いられる最上部金属層が配置される。前記電源線は一般に平板状を有するように設計されて前記セルアレイ領域の大部分を覆う。これは、前記電源線を介して電流が流れるとき、前記電源線による電圧降下を最小化させることができるためである。この場合、前記水素熱処理工程を実施しても、前記セルアレイ領域を覆う前記平板状の最上部金属層は前記水素熱処理工程間に供給される水素原子が前記セルトランジスタのゲート絶縁膜の界面に達するのを妨害する。よって、前記多層金属配線技術がDRAM素子に適用された場合でも、前記DRAM素子のリフレッシュ特性を改善させるのには限界がある。

10

## 【0007】

金属層を有する半導体素子は、特許文献1に“導電膜を有する樹脂成型型半導体素子”という名称で、原らによって開示されている。原らによると、四角形の半導体基板の端上に金属ガードリングが提供され、前記金属ガードリングを有する基板はパッシベーション膜で覆われる。前記パッシベーション膜を有する基板が樹脂成型膜)を用いるパッケージ工程によって密封されると、前記樹脂成型膜による応力は前記半導体基板における4つのコーナー領域上のパッシベーション膜に集中される。その結果、前記パッシベーション膜内に亀裂が発生する。よって、原らは前記樹脂成型膜の応力を緩和させるために前記4つのコーナー領域上の前記金属ガードリング内にスリットのようなホールを設けた。

20

## 【特許文献1】米国特許第5229642号明細書

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0008】

本発明が解決しようとする技術的課題は、水素熱処理効果 (hydrogen allloy effect) を極大化させるのに好適な金属層を有する半導体素子を提供することにある。

## 【0009】

本発明が解決しようとする他の技術的課題は水素熱処理効果を極大化させることができる金属層を有する半導体素子の製造方法を提供することにある。

30

## 【課題を解決するための手段】

## 【0010】

本発明の一様態によれば、少なくともセルアレイ領域上部に配置された最上部金属層を有する半導体素子が提供される。前記半導体素子はセルアレイ領域を有する半導体基板及び前記セルアレイ領域を有する基板を覆う層間絶縁膜を含む。前記セルアレイ領域内の前記層間絶縁膜上部に最上部金属層が配置される。前記最上部金属層は少なくとも1つの開口部を有する。

## 【0011】

本発明のいくつかの実施形態において、前記セルアレイ領域は前記半導体基板に形成された複数のメモリセルを含むことができる。この場合、前記層間絶縁膜は前記メモリセルを覆う。前記メモリセルのそれぞれは前記半導体基板に形成されたセルMOSトランジスタ及び前記セルMOSトランジスタのソース/ドレイン領域のうちいずれか1つに電気的に接続されたセルキャパシタを含むことができる。

40

## 【0012】

他の実施形態において、前記セルアレイ領域内の前記層間絶縁膜上に下部金属配線が配置され、前記下部金属配線及び前記層間絶縁膜は下部金属層間絶縁膜で覆うことができる。この場合、前記最上部金属層は前記下部金属層間絶縁膜上部に配置され、前記少なくとも1つの開口部は前記下部金属配線との間の前記下部金属層間絶縁膜の少なくとも一部分上に位置することができる。さらに、前記セルアレイ領域内の前記下部金属層間絶縁膜上

50

に上部金属配線が配置することができ、前記上部金属配線及び前記下部金属層間絶縁膜を上部金属層間絶縁膜で覆うことができる。この場合、前記上部金属配線は前記下部金属配線の上部を横切るように配置することができ、前記最上部金属層は前記上部金属層間絶縁膜上部に配置することができる。また、前記少なくとも1つの開口部は、前記下部金属配線間の前記下部金属層間絶縁膜と前記上部金属配線間の前記上部金属層間絶縁膜との重畠領域のうち少なくとも1つの上部に位置することができる。

#### 【0013】

また他の実施形態において、前記少なくとも1つの開口部は前記最上部金属層を貫通する複数の開口部を含むことができる。前記複数の開口部は複数のスリット及び／または複数のホールを含むことができる。前記複数のスリット幅及びそれら間の間隔は0.5μmより大きいか同一とすることができます。前記複数のホール直径及びそれら間の間隔は0.2μmより大きいか同一とすることができます。

10

#### 【0014】

また他の実施形態において、前記最上部金属層を有する基板はパッシベーション膜で覆うことができる。前記パッシベーション膜は順に積層されたシリコン酸化膜及びシリコン窒化膜を含むことができる。

#### 【0015】

本発明の他の様態によれば、前記半導体素子はセルアレイ領域及び前記セルアレイ領域に隣接した周辺回路領域を有する半導体基板を含む。前記セルアレイ領域内の前記半導体基板に複数のメモリセルが提供される。前記周辺回路領域内の前記半導体基板に少なくとも1つの周辺MOSトランジスタ(peripheral MOS transistor)が提供される。前記メモリセル及び前記周辺MOSトランジスタを有する基板は層間絶縁膜で覆われる。前記セルアレイ領域内の前記層間絶縁膜上部に第1最上部金属層が配置され、前記第1最上部金属層は少なくとも1つの第1開口部を有する。前記周辺回路領域内の前記層間絶縁膜上部に第2最上部金属層が配置され、前記第2最上部金属層は前記周辺MOSトランジスタの上部に位置する少なくとも1つの第2開口部を有する。

20

#### 【0016】

本発明の更なる他の様態によれば、少なくともセルアレイ領域上部に配置された最上部金属層を有する半導体素子の製造方法が提供される。この方法はセルアレイ領域を有する半導体基板を準備する段階と、前記半導体基板を覆う層間絶縁膜を形成する段階とを含む。前記セルアレイ領域内の前記層間絶縁膜上に少なくとも1つの開口部を有する最上部金属層を形成する。

30

#### 【0017】

本発明のいくつかの実施形態において、前記層間絶縁膜を形成する前に、前記セルアレイ領域内の前記半導体基板に複数のメモリセルを形成することができる。

#### 【0018】

他の実施形態において、前記最上部金属層を形成する前に前記セルアレイ領域内の前記層間絶縁膜上に下部金属配線を形成することができ、前記下部金属配線を有する基板上に下部金属層間絶縁膜を形成することができる。この場合、前記最上部金属層は前記少なくとも1つの開口部が前記下部金属配線間の前記下部金属層間絶縁膜の少なくとも一部分上に位置するように形成することができる。さらに、前記セルアレイ領域内の前記下部金属層間絶縁膜上に上部金属配線を形成することができ、前記上部金属配線を有する基板上に上部金属層間絶縁膜を形成することができる。前記上部金属配線は前記下部金属配線の上部を横切るように形成されることができ、前記最上部金属層は前記少なくとも1つの開口部が前記下部金属配線間の前記下部金属層間絶縁膜と前記上部金属配線間の前記上部金属層間絶縁膜との重畠領域のうち少なくとも1つの上部に位置するように形成することができる。

40

#### 【0019】

また他の実施形態において、前記少なくとも1つの開口部は、前記最上部金属層を貫通する複数のスリット及び／または複数のホールを具備するように形成することができる。

50

前記複数のスリットは  $0.5 \mu m$  より大きいか同一幅を有するように形成することができ、前記複数のホールは  $0.2 \mu m$  より大きいか同一直径を有するように形成することができる。

【0020】

また他の実施形態において、前記最上部金属層を有する基板上にパッシベーション膜を形成することができ、前記パッシベーション膜を有する基板は熱処理することができる。前記パッシベーション膜はシリコン酸化膜及びシリコン窒化膜を順に積層させて形成することができる。前記熱処理は少なくとも水素ガスを含む雰囲気ガスを用いて実施することができる。

【0021】

本発明の更なる他の様態によれば、前記半導体素子を製造する方法はセルアレイ領域及び周辺回路領域を有する半導体基板を準備する段階を含む。前記セルアレイ領域内の前記半導体基板及び前記周辺回路領域内の前記半導体基板にそれぞれ複数のメモリセル及び少なくとも 1 つの周辺MOSトランジスタを形成する。前記メモリセル及び前記周辺MOSトランジスタを有する基板上に層間絶縁膜を形成する。前記セルアレイ領域内の前記層間絶縁膜上部及び前記周辺回路領域内の前記層間絶縁膜上部にそれぞれ第 1 最上部金属層及び第 2 最上部金属層を形成する。前記第 1 最上部金属層は少なくとも 1 つの第 1 開口部を有するように形成され、前記第 2 最上部金属層は前記周辺MOSトランジスタの上部に位置する少なくとも 1 つの第 2 開口部を有するように形成される。

【0022】

本発明の更なる他の様態によれば、前記半導体素子は半導体基板及び前記半導体基板上に形成されたゲート電極を含む。前記半導体基板と前記ゲート電極との間にゲート絶縁膜が提供され、前記ゲート電極上に金属層間絶縁膜及びパッシベーション膜が順に積層される。前記パッシベーション膜と前記金属層間絶縁膜との間に介在された最上部導電膜が提供される。前記最上部導電膜は前記ゲート絶縁膜と整列された少なくとも 1 つの開口部を具備し、前記開口部は外部の水素原子が前記ゲート絶縁膜と前記半導体基板との界面に達する経路を提供する。

【0023】

本発明のいくつかの実施形態において、前記少なくとも 1 つの開口部は前記ゲート絶縁膜上部に位置することができる。

【0024】

他の実施形態において、前記最上部導電膜は前記パッシベーション膜と直接接觸することができる。

【0025】

さらに他の実施形態において、前記半導体基板の表面に平行な平面内に一対の平行な上部金属配線が配置されることがある。前記上部金属配線はそれら間の上部開口部を画定する。また、前記半導体基板の表面に平行な平面内に一対の平行な下部金属配線が配置されることがある。前記下部金属配線はそれら間の下部開口部を画定する。前記上 / 下部開口部は、互いに重畠して前記半導体基板の表面に垂直である少なくとも 1 つの開口領域を画定し、前記最上部導電膜内の前記開口部は前記少なくとも 1 つの開口領域と整列されて前記水素原子の経路を提供する。前記上部金属配線は前記下部金属配線の厚さと異なる厚さを有することができる。

【0026】

さらに他の実施形態において、前記金属層間絶縁膜は流動性酸化膜 (flowable oxide layer) を含むことができる。

【発明の効果】

【0027】

本発明によれば、セルアレイ領域上部及び / または周辺回路領域上部に形成される最上部金属層を貫通する開口部が提供される。これによって、金属熱処理工程間にセルMOSトランジスタ及び / または周辺MOSトランジスタのゲート絶縁膜の界面に供給される水

10

20

30

40

50

素原子の数量を増加させることができるので、DRAM素子の性能（収率及び／またはリフレッシュ特性）を改善させることができる。

【発明を実施するための最良の形態】

【0028】

以下、添付した図面を参照しながら本発明の好適な実施形態を詳しく説明する。しかしながら、本発明は、ここで説明する実施形態に限られず、他の形態で具体化されることもある。むしろ、ここで紹介される実施形態は開示された発明が完成されていることを示すと共に、当業者に本発明の思想を十分に伝えるために提供するものである。図面において、層及び領域の厚みは明確性をあたえるために誇張して図示されたものである。明細書全体にわたって同じ参照番号は、同様の構成要素を示す。

10

【0029】

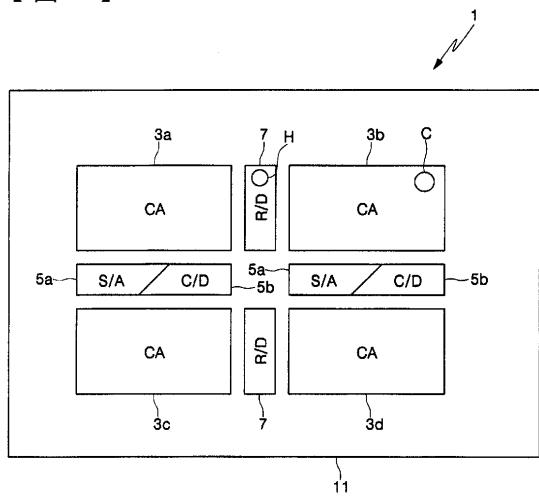

図1は本発明の実施形態に適用可能な半導体記憶素子を示す概略的なブロックダイヤグラムである。

【0030】

図1を参照すると、前記半導体記憶素子1は、セルアレイ領域及び前記セルアレイ領域に隣接した周辺回路領域を有する半導体基板11を具備する。セルアレイ領域は複数のセルブロック、例えば4つのセルブロック3a、3b、3c、3dを含むことができる。前記セルブロックのそれぞれは複数のメモリセル、例えば複数のDRAMセルで構成される。また、前記周辺回路領域は前記セルブロック3a、3b、3c、3d間に半導体基板11または前記セルブロックに隣接した半導体基板11に形成されたローデコーダ7、感知増幅器5a及びコラムデコーダ5bを含むことができる。また、前記ローデコーダ7は高電圧回路領域Hを含むことができる。

20

【0031】

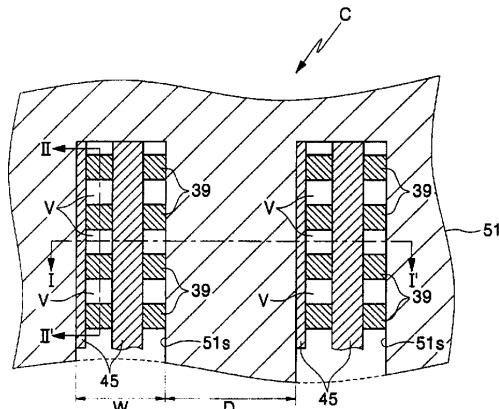

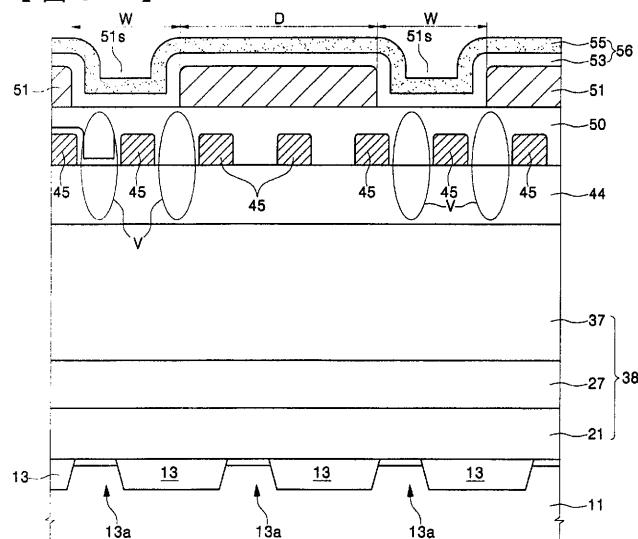

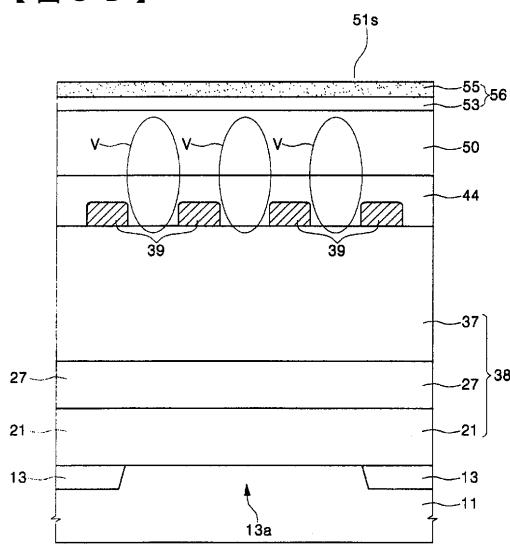

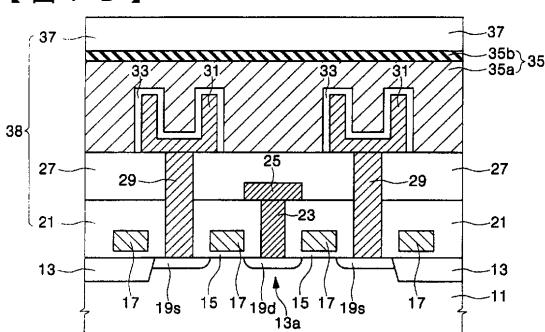

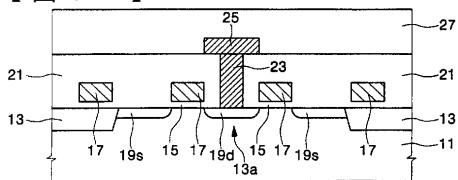

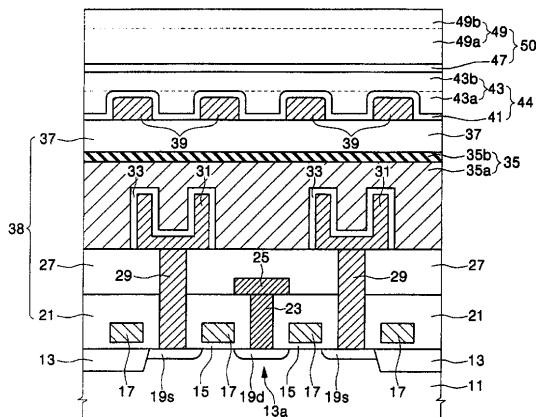

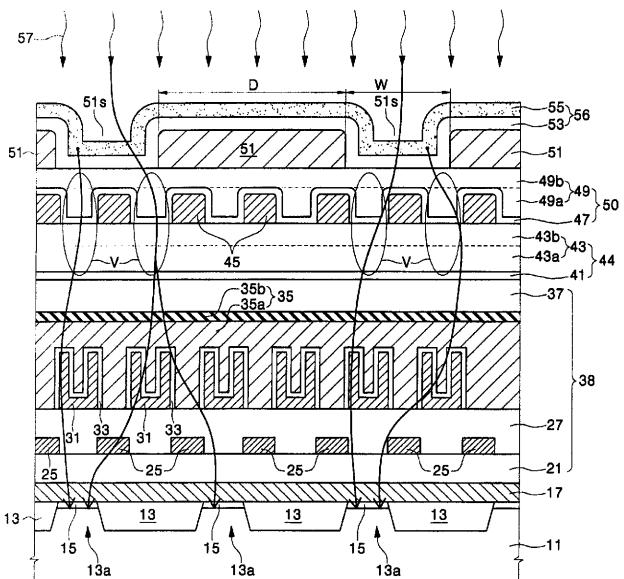

図2は本発明の実施形態による半導体素子を説明する図1のセルブロック3bの一部分Cを示す拡大平面図であり、図3A及び図3Bはそれぞれが図2のI-I'及びII-II'線の断面図である。

【0032】

図2、図3A及び図3Bを参照すると、半導体基板11の所定領域に素子分離膜13が提供されてセル活性領域13aを画定する。前記セル活性領域13aを有する基板上に層間絶縁膜38が提供され、前記層間絶縁膜38上に複数の第1下部金属配線39が配置されることができる。前記層間絶縁膜38は順に積層された下部層間絶縁膜21、中間層間絶縁膜27及び上部層間絶縁膜37を含むことができ、前記第1下部金属配線39はDRAMセルのようなメモリセルのストラッピング(strapping)ワードラインとして用いられることができる。前記第1下部金属配線39及び前記層間絶縁膜38は下部金属層間絶縁膜44で覆われる。

30

【0033】

前記下部金属層間絶縁膜44上に複数の第1上部金属配線45が提供されることができ、前記第1上部金属配線45及び前記下部金属層間絶縁膜44は上部金属層間絶縁膜50で覆われる。前記第1上部金属配線45は前記第1下部金属配線39の上部を横切るように配置することができる。その結果、前記第1下部金属配線39間の前記下部金属層間絶縁膜44と前記第1上部金属配線45間の前記上部金属層間絶縁膜50との重畠領域Vが存在することができる。すなわち、前記第1下部金属配線39間の下部ギャップ領域と前記第1上部金属配線45間の上部ギャップ領域との交差領域にはいかなる金属配線も含まない。

40

【0034】

前記上部金属層間絶縁膜50上に第1最上部金属層51が提供される。前記第1最上部金属層51は図1の周辺回路領域から延長された電源線または高電圧金属配線とすることができます。この場合、前記第1最上部金属層51は平面図から見た場合、広い表面積を有するように設計することができる。これは前記第1最上部金属層51を介して流れる電流による電圧降下を最小化させるためである。しかし、前記第1最上部金属層51が前記セ

50

ルアレイ領域、すなわち前記セルブロック3bの全面を覆うように配置されると、前記第1最上部金属層51は後続の熱処理工程間に前記セル活性領域13aに形成されたDRA MセルのMOSトランジスタに達する水素原子の経路を遮断する。よって、本発明の実施形態において、前記第1最上部金属層51は前記第1最上部金属層51を貫通する少なくとも1つの第1開口部を有することができる。

【0035】

前記少なくとも1つの第1開口部は複数の第1開口部を含む。例えば、前記第1開口部は図2に示すように複数の第1スリット51sを含むことができる。この場合、前記第1スリット51sのそれぞれは0.5μmより大きいか同一幅Wを有することができ、前記第1スリット51s間の間隔Dも0.5μmより大きいか同一とすることができる。本発明の他の実施形態において、前記第1開口部は複数の第1ホール(図示せず)を含むことができる。この場合、前記第1ホール直径及びそれら間の間隔は0.2μmより大きいか同一とすることができる。本発明の更なる他の実施形態において、前記第1開口部は少なくとも1つの第1スリット及び少なくとも1つの第1ホールを含むことができる。いかなる場合においても、前記第1開口部(すなわち、前記第1スリット51s及び/または前記第1ホール)は前記第1下部金属層間絶縁膜44と前記第1上部金属層間絶縁膜50との前記重疊領域Vのうち少なくとも1つの上部に位置するのが好ましい。

【0036】

一方、前記第1上部金属配線45及び前記上部金属層間絶縁膜50が提供されない場合、前記第1開口部は前記第1下部金属配線39間の前記下部金属層間絶縁膜44の少なくとも一部分上に位置するのが好ましい。

【0037】

前記第1最上部金属層51を有する基板はパッシベーション膜56で覆われる。前記パッシベーション膜56は順に積層されたシリコン酸化膜53及びシリコン窒化膜55を含むことができる。

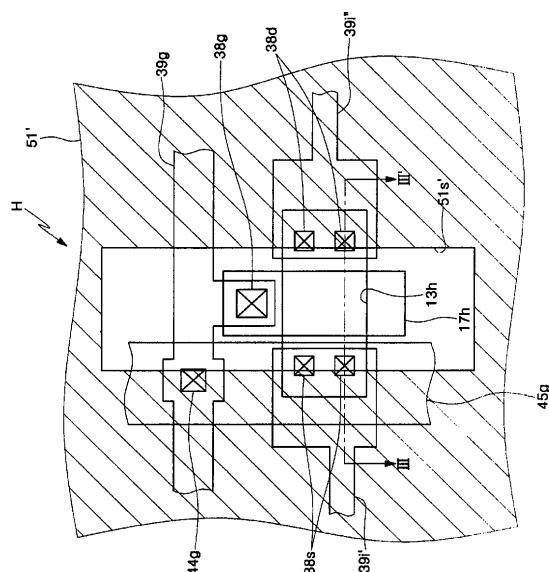

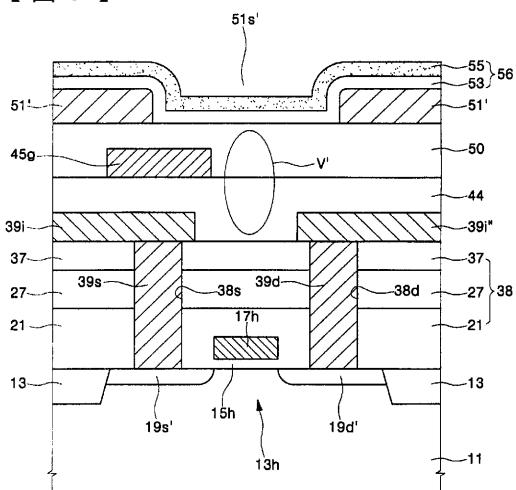

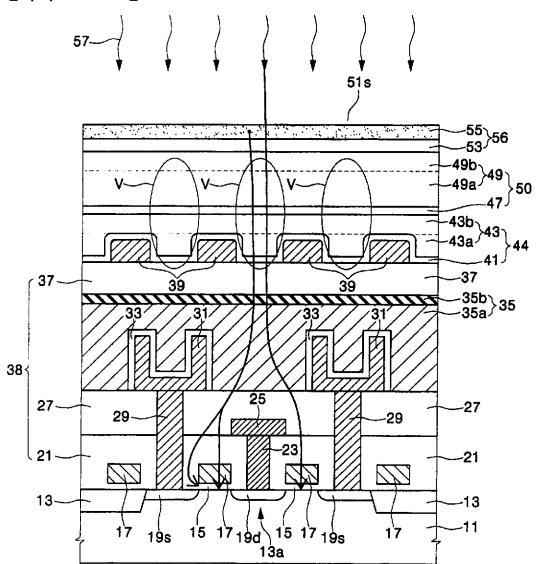

【0038】

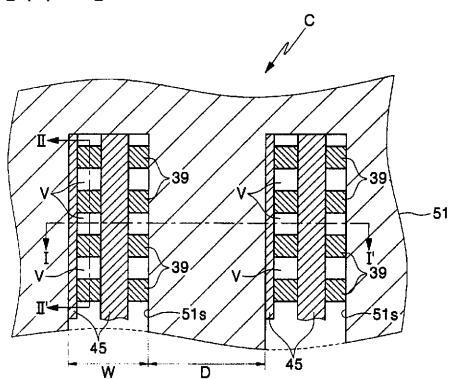

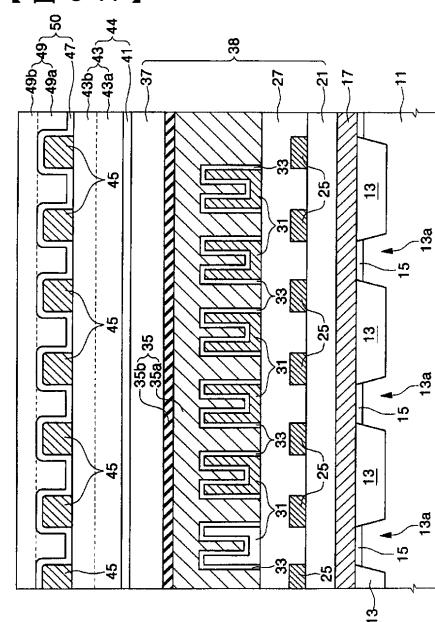

図4は本発明の他の実施形態を説明するための図1における高電圧回路領域Hの一部を示す拡大平面図であり、図5は図4のI—I—I—I—I'線の断面図である。本実施形態は高電圧回路領域を例として説明しているが、本発明は高電圧回路領域に限定されず、感知增幅器(図1の5a)及びコラムデコーダ(図1の5b)のような周辺回路領域にも適用することができる。

【0039】

図4及び図5を参照すると、半導体基板11の所定領域に素子分離膜13が提供されて周辺活性領域13hを画定する。前記周辺活性領域13h内にソース領域19s'及びドレイン領域19d'が提供され、前記ソース/ドレイン領域19s'、19d'間のチャネル領域上部にゲート電極17hが配置される。前記ゲート電極17hは前記チャネル領域からゲート絶縁膜15hによって絶縁される。前記ゲート電極17h及び前記ソース/ドレイン領域19s'、19d'は周辺MOSトランジスタ(peripheral MOS transistor)、例えば、高電圧MOSトランジスタを構成することができる。

【0040】

前記高電圧MOSトランジスタを有する基板上に層間絶縁膜38が提供される。前記層間絶縁膜38は、順に積層された下部層間絶縁膜21、中間層間絶縁膜27及び上部層間絶縁膜37を含むことができる。前記ソース領域19s'及び前記ドレイン領域19d'はそれが前記層間絶縁膜38を貫通するソースコンタクトホール38s及びドレインコンタクトホール38dによって露出されることができる。同様に、前記ゲート電極17hは前記層間絶縁膜38を貫通するゲートコンタクトホール38gによって露出することができる。記ソースコンタクトホール38s及びドレインコンタクトホール38dはそれがソースコンタクトプラグ39s及びドレインコンタクトプラグ39dで埋め込まれることができ、前記ゲートコンタクトホール38gはゲートコンタクトプラグ(図示せず

) で埋め込まれることができる。

【0041】

前記層間絶縁膜 38 上に第2下部金属配線が提供される。前記第2下部金属配線は前記ソースコンタクトプラグ 39s を覆うソース配線 39i' 及び前記ドレインコンタクトプラグ 39d を覆うドレイン配線 39i" を含むことができる。さらに、前記第2下部金属配線は前記ゲートコンタクトプラグを覆うゲート配線 39g を含むことができる。結果的に、前記ソース配線 39i' 及びドレイン配線 39i" はそれぞれが前記ソース領域 19s' 及びドレイン領域 19d' に電気的に接続され、前記ゲート配線 39g は前記ゲート電極 17h に電気的に接続される。前記第2下部金属配線 39i' 、 39i" 、 39g 間のギャップ領域は前記高電圧MOSトランジスタ上部に位置するのが好ましい。例えば、前記第2下部金属配線 39i' 、 39i" 、 39g 間のギャップ領域は前記高電圧MOSトランジスタの少なくともチャネル領域上部に提供されるのが好ましい。前記第2下部金属配線 39i' 、 39i" 、 39g 及び前記層間絶縁膜 38 は下部金属層間絶縁膜 44 で覆われる。

【0042】

前記下部金属層間絶縁膜 44 上に少なくとも1つの第2上部金属配線 45g が配置されることがある。前記第2上部金属配線 45g は前記第2下部金属配線 39i' 、 39i" 、 39g のうちいずれか1つと電気的に接続されることがある。例えば、前記第2上部金属配線 45g は図4に示すように前記下部金属層間絶縁膜 44 を貫通するピアホール 44g を介して前記ゲート配線 39g に電気的に接続されることがある。前記第2上部金属配線 45g は前記第2下部金属配線 39i' 、 39i" 、 39g の上部を横切るように配置することができる。この場合、前記第2上部金属配線 45g も前記高電圧MOSトランジスタの少なくともチャネル領域上部を覆わないように配置されることが好ましい。前記第2上部金属配線 45g 及び前記下部金属層間絶縁膜 44 は上部金属層間絶縁膜 50 で覆われる。

【0043】

前記上部金属層間絶縁膜 50 上に第2最上部金属層 51' が提供される。前記第2最上部金属層 51' は図2、図3A 及び図3B を参照して説明した前記第1開口部 51s と同じ形態を有する少なくとも1つの第2開口部 51s' を具備することができる。この場合、前記第2開口部 51s' は前記高電圧MOSトランジスタの上部に位置するのが好ましい。結果的に、前記高電圧MOSトランジスタの少なくともチャネル領域上部にはいかなる金属配線も存在しない。よって、前記高電圧MOSトランジスタ上に図2、図3A 及び図3B を参照して説明された前記重疊領域V と同じ垂直構造を有する、さらに他の重疊領域V' が提供される。前記重疊領域V' は外部の水素原子が前記高電圧MOSトランジスタに容易に達することのできる経路の役割をする。

【0044】

前記第2最上部金属層 51' を有する基板はパッシベーション膜 56 で覆うことができる。前記パッシベーション膜 56 は順に積層されたシリコン酸化膜 53 及びシリコン窒化膜 55 を含むことができる。

【0045】

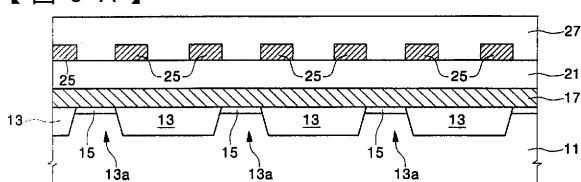

図6Aないし図9A は本発明の実施形態によるDRAM素子の製造方法を説明する図2のI-I' 線の断面図であり、図6Bないし図9B は本発明の実施形態によるDRAM素子の製造方法を説明するための図2のII-II' 線の断面図である。

【0046】

図6A及び図6Bを参照すると、半導体基板 11 の所定領域に素子分離膜 13 を形成してセル活性領域 13a を画定する。前記セル活性領域 13a 上にセルゲート絶縁膜 15 を形成し、前記セルゲート絶縁膜 15 を有する基板上にゲート導電膜を形成する。前記ゲート導電膜をパターニングして前記セル活性領域 13a の上部を横切る複数のワードライン 17 を形成する。続いて、前記ワードライン 17 及び前記素子分離膜 13 をイオン注入マスクとして用いて前記セル活性領域 13a 内に不純物イオンを注入してドレイン領域 19

10

20

30

40

50

d 及びソース領域 19 s を形成する。前記ワードライン 17 及びこれに隣接した前記ソース / ドレイン領域 19 s 、 19 d はセルMOSトランジスタを構成する。

#### 【0047】

前記セルMOSトランジスタを有する基板上に下部層間絶縁膜 21 を形成する。前記下部層間絶縁膜 21 内に前記ドレイン領域 19 d と電気的に接続されたビットラインコンタクトプラグ 23 を形成する。前記下部層間絶縁膜 21 上に複数のビットライン 25 を形成する。前記ビットライン 25 は前記ワードライン 17 の上部を横切るように形成される。また、前記ビットライン 25 は前記ビットラインコンタクトプラグ 23 と接触するように形成される。前記ビットライン 25 を有する基板上に中間層間絶縁膜 27 を形成する。前記下部層間絶縁膜 21 及び前記中間層間絶縁膜 27 はシリコン酸化膜で形成することができる。

10

#### 【0048】

図 7A 及び図 7B を参照すると、前記中間層間絶縁膜 27 及び下部層間絶縁膜 21 をパターニングして前記ソース領域 19 s を露出させるストレージノードコンタクトホールを形成し、前記ストレージノードコンタクトホール内にストレージノードコンタクトプラグ 29 を形成する。前記各ストレージノードコンタクトプラグ 29 上に複数のストレージノード 31 を形成し、前記ストレージノード 31 の表面上に誘電体膜 33 を形成する。前記ストレージノード 31 は多様な形態で形成することができる。例えば、前記ストレージノード 31 は図のようにシリンドラ状に形成することができる。

20

#### 【0049】

前記誘電体膜 33 を有する基板上にプレート電極 35 を形成する。前記プレート電極 35 は図 1 の各セルブロック 3a 、 3b 、 3c 、 3d を覆うように形成することができる。前記プレート電極 35 はポリシリコン膜を含む導電膜で形成することができる。例えば、前記プレート電極 35 はドーピングされたポリシリコン膜 35a 及びチタン窒化膜 35b を順に積層させて形成することができる。この場合、前記チタン窒化膜 35b は 400 ~ 500 の薄い厚さで形成するのが好ましい。これは前記チタン窒化膜 35b が数千の厚い厚さで形成されると、水素原子が前記チタン窒化膜 35b を貫通することができないからである。前記プレート電極 35 を有する基板上に上部層間絶縁膜 37 を形成する。前記上部層間絶縁膜 37 もまたシリコン酸化膜で形成することができる。下部層間絶縁膜 21 、中間層間絶縁膜 27 及び上部層間絶縁膜 37 は層間絶縁膜 38 を構成する。

30

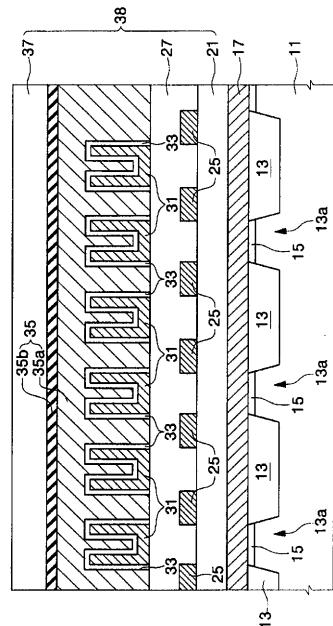

#### 【0050】

図 8A 及び図 8B を参照すると、前記上部層間絶縁膜 37 上に複数の第 1 下部金属配線 39 を形成することができる。前記第 1 下部金属配線 39 はアルミニウム膜のような金属膜で形成することができる。前記アルミニウム膜は純アルミニウム膜（またはアルミニウム合金膜）とすることができます。また、前記第 1 下部金属配線 39 は低い電気抵抗を有するように数千の厚い厚さで形成することができる。例えば、前記第 1 下部金属配線 39 は約 4000 の厚さを有するアルミニウム膜で形成することができる。前記第 1 下部金属配線 39 は前記ワードライン 17 による信号遅延時間 (signal delay time) を減少させるためのストラッピングワードラインとして用いられることができる。この場合、前記第 1 下部金属配線 39 は前記ワードライン 17 に平行線のように形成することができる。

40

#### 【0051】

前記第 1 下部金属配線 39 を有する基板上に下部金属層間絶縁膜 44 を形成する。前記下部金属層間絶縁膜 44 を多様な方法を用いて形成されることがある。例えば、前記下部金属層間絶縁膜 44 は下部キャッピング絶縁膜 41 及び上部キャッピング絶縁膜 43 を順に積層させて形成することができる。前記下部キャッピング絶縁膜 41 は、約 1000 の薄い厚さを有するプラズマ強化のTEOS (plasma-enhanced tetra-ethyl-ortho-silicate ; 以下 “PE-TEOS” と称する。) 膜で形成することができ、前記上部キャッピング絶縁膜 43 は優れたギャップ充填特性を有する高密度プラズマ酸化膜で形成することができる。一方、前記上部キャッピング

50

絶縁膜43は流動性酸化膜(flowable oxide layer)43a及びPE-TEOS膜43bを用いて形成することができる。この場合、前記流動性酸化膜(Fox layer)43aは前記下部キャッピング絶縁膜41上に液状の酸化物を塗布して前記第1下部金属配線39間のギャップ領域を埋め込み前記液状の酸化物を約400の温度で焼き付けることによって形成することができ、前記PE-TEOS膜43bは約3000~4000の厚さで形成することができる。

#### 【0052】

続いて、前記下部金属層間絶縁膜44上に複数の第1上部金属配線45を形成することができる。前記第1上部金属配線45は前記ビットライン25に電気的に接続される金属配線とすることができます。この場合、前記第1上部金属配線45は前記第1下部金属配線39の上部を横切るように形成することができる。前記第1上部金属配線45は前記第1下部金属配線39を形成する方法を用いて形成することができる。しかし、前記第1上部金属配線45は前記第1下部金属配線39と異なる厚さで形成することができる。例えば、前記第1上部金属配線45は約6000の厚さで形成することができる。前記第1上部金属配線45を有する基板上に上部金属層間絶縁膜50を形成する。前記上部金属層間絶縁膜50は前記下部金属層間絶縁膜44を形成する方法を用いて形成することができる。すなわち、前記上部金属層間絶縁膜50は下部キャッピング絶縁膜47及び上部キャッピング絶縁膜49を順に積層させて形成することができる。また、前記上部キャッピング絶縁膜49は流動性酸化膜49a及びPE-TEOS膜49bを含むように形成することができる。

10

20

30

40

#### 【0053】

図9A及び図9Bを参照すると、前記上部金属層間絶縁膜50上に最上部金属層を形成し、前記最上部金属層をパターニングして図1の前記セルブロック3a、3b、3c及び3d上にそれぞれ第1最上部金属層51を形成する。本発明の実施形態によれば、前記第1最上部金属層51のそれぞれは少なくとも1つの第1開口部を有するように形成することができる。前記少なくとも1つの第1開口部は複数の第1スリット51s及び/または複数の第1ホールを含むように形成することができる。前記第1スリット51s及び/または前記第1ホールは前記最上部金属層をパターニングする間に形成することができる。前記第1スリット51sの幅W及びそれら間の間隔Dは0.5μmより大きいか同一とすることことができ、前記第1ホール直径及びそれら間の間隔は0.2μmより大きいか同一とすることができる。

#### 【0054】

前記少なくとも1つの第1開口部が前記第1スリット51sを含むように形成され、前記第1下部金属配線39及び前記第1上部金属配線45が形成される場合、前記第1スリット51sのそれぞれは図9A及び図9Bに示すように前記第1下部金属配線39間の前記下部金属層間絶縁膜44と前記第1上部金属配線45間の前記上部金属層間絶縁膜50との重畠領域Vのうち少なくとも1つの上部に形成されることが好ましい。同様に、前記少なくとも1つの第1開口部が前記第1ホールを含むように形成され、前記第1下部金属配線39及び前記第1上部金属配線45が形成される場合に前記第1ホールのそれぞれも前記重畠領域Vのうち少なくとも1つの上部に形成されることが好ましい。

#### 【0055】

一方、前記第1上部金属配線45及び前記上部金属層間絶縁膜50を形成する工程が省略される場合、前記第1スリット51sまたは前記第1ホールのそれぞれは前記第1下部金属配線39間の前記下部金属層間絶縁膜44の少なくとも一部分上に形成されることが好ましい。

#### 【0056】

前記第1最上部金属層51を有する基板上にパッシベーション膜56を形成する。前記パッシベーション膜56は少なくともシリコン窒化膜を含むように形成することができる。例えば、前記パッシベーション膜56はプラズマシリコン酸化膜53及びプラズマシリコン窒化膜55を順に積層させて形成することができる。この場合、前記プラズマシリコ

50

ン窒化膜 5 5 はシリコンソースガス及び窒素ソースガスを工程ガスとして用いて形成される。前記シリコンソースガスはシラン (  $\text{SiH}_4$  ) ガスとすることができます、前記窒素ソースガスはアンモニア (  $\text{NH}_3$  ) ガスとすることができます。この場合、前記プラズマシリコン窒化膜 5 5 は水素原子を含むことができる。

#### 【 0 0 5 7 】

前記パッシベーション膜 5 6 を有する基板は熱処理工程、すなわち金属熱処理工程 ( metal alloy process ) に支配される。前記金属熱処理工程は、約 400 の温度で水素及び窒素を雰囲気ガス 5 7 として用いて実施することができる。前記金属熱処理工程間に雰囲気ガス内の水素原子は前記第 1 開口部 5 1 s 及び前記重畠領域 V を介して前記セルゲート絶縁膜 1 5 の界面に達することができる。すなわち、前記第 1 開口部 5 1 s は前記水素原子が前記セルゲート絶縁膜 1 5 の界面に達することができる水素経路 ( hydrogen paths ) を提供する。その結果、前記セルゲート絶縁膜 1 5 の界面トラップサイトは前記水素原子で埋め込まれて前記セルゲート絶縁膜 1 5 の界面トラップ密度を著しく減少させる。これによって、前記セルMOSトランジスタの漏洩電流特性はより改善されてDRAM素子のリフレッシュ周期を増加させる。

#### 【 0 0 5 8 】

さらに、前記金属熱処理工程の間に前記パッシベーション膜 5 6 、すなわち前記プラズマシリコン窒化膜 5 5 内の水素原子も前記第 1 開口部 5 1 s を介して前記セルゲート絶縁膜 1 5 の界面に拡散することができる。よって、前記セルMOSトランジスタの漏洩電流特性はさらに改善させることができる。

#### 【 0 0 5 9 】

図 4 及び図 5 に示した高電圧回路領域 H は、図 6 A ないし図 9 A 及び図 6 B ないし図 9 B を参照して説明された実施形態と同じ方法を用いて製造することができる。よって、前記高電圧回路領域 H の製造方法に関する説明は省略する。

#### 【 0 0 6 0 】

##### < 実験例 >

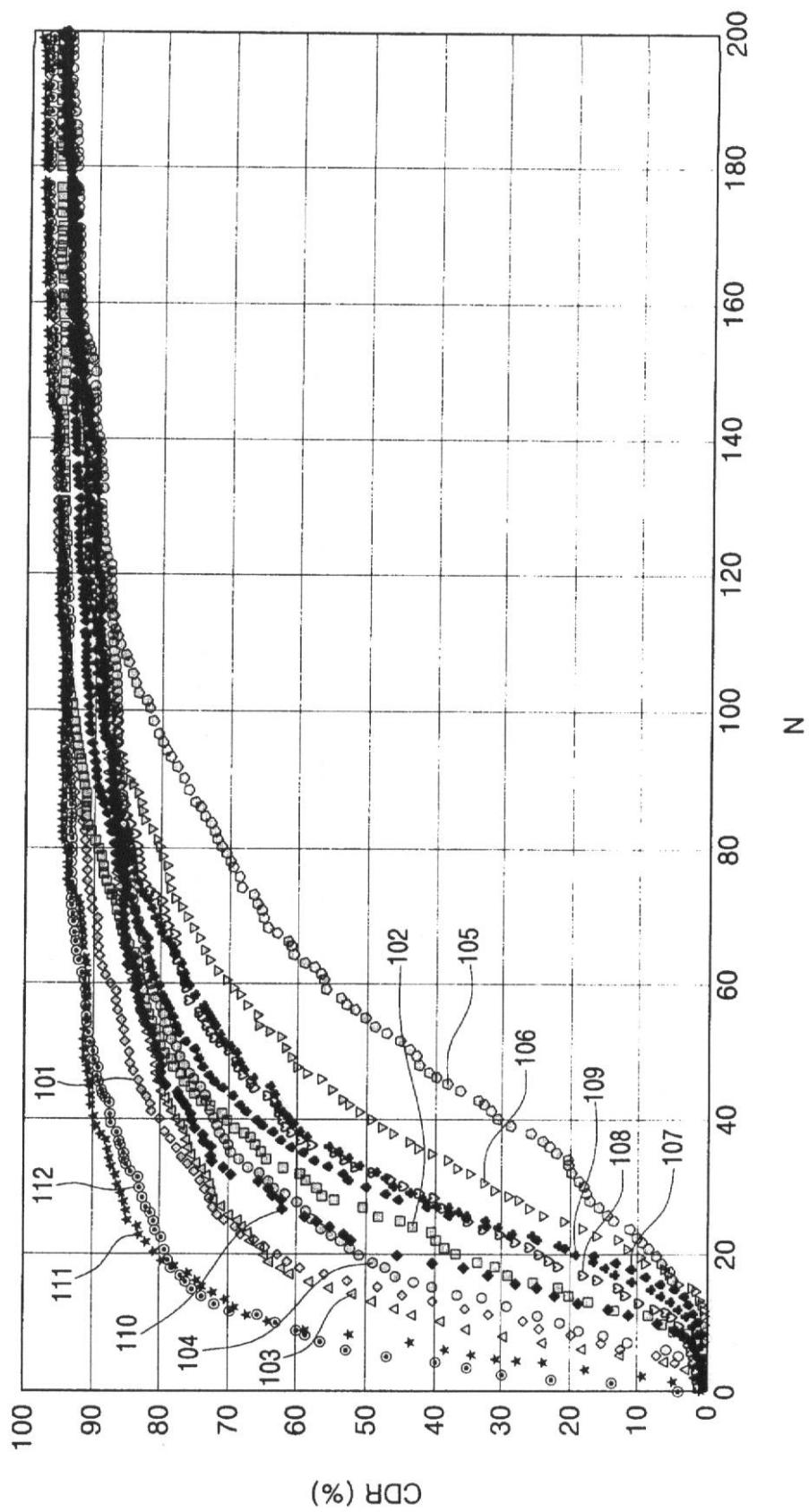

図 10 は本発明の効果を間接的に確認するために製造された 256 メガビットDRAM素子のセルテスト結果を示すグラフである。図 10 において、横軸は不良ビット数 N を示し、縦軸は累積分布率 ( CDR ) を示す。

#### 【 0 0 6 1 】

図 10 において、参考番号 “ 101 ” ないし “ 112 ” で示されたデータは次の表 1 に記載された主要工程条件を用いて製造された試料から得た。また、セルキャパシタの上部電極 ( すなわち、プレート電極はドーピングされたポリシリコン膜及びチタン窒化膜 ( TiN ) ) を順に積層させて形成し、前記チタン窒化膜は 400 の厚さで形成した。ここで、前記セルテストは、マーチテスト ( march test ) プログラム及び 200 msec のリフレッシュ周期を用いて実施された。

#### 【 0 0 6 2 】

10

20

30

【表1】

| 工程パラメータ                  |           | 試料番号 (Sample No.)                                                  |              |                     |

|--------------------------|-----------|--------------------------------------------------------------------|--------------|---------------------|

|                          |           | 101~104                                                            | 105~110      | 111~112             |

| 下部金属配線 (M1)              |           | アルミニウム合金膜 (Al alloy; 4000Å)                                        |              |                     |

| 下部<br>IMD                | 下部キャッピング膜 | PE-TEOS膜 (1000Å)                                                   |              |                     |

|                          | 上部キャッピング膜 | Fox/PE-TEOS (4000Å)                                                | HDP酸化膜       | Fox/PE-TEOS (4000Å) |

| 上部金属配線 (M2)              |           | アルミニウム合金膜 (Al alloy; 6000Å)                                        |              |                     |

| 上部<br>IMD                | 下部キャッピング膜 | PE-TEOS膜 (1000Å)                                                   |              |                     |

|                          | 上部キャッピング膜 | HDP酸化膜                                                             |              |                     |

| セルアレイ領域上の<br>最上部金属層 (M3) |           | アルミニウム合金膜 8000Å、<br>開口部がない平板層<br>(plate layer without<br>openings) | 省略 (skipped) |                     |

| パッシベーション膜                |           | HDP酸化膜 (8000Å) / PECVD SiN膜 (6000Å)                                |              |                     |

| 熱処理                      |           | 400°C、180分、H <sub>2</sub> ガス+N <sub>2</sub> ガス                     |              |                     |

10

20

30

## 【0063】

図10及び表1から分かるように、PE-TEOS膜/流動性酸化膜(Fox)/PE-TEOS膜で構成された下部金属層間絶縁膜及び開口部がない最上部金属層を用いて製造された256メガビットDRAM素子の50%は、10~30個の不良ビットを示し、PE-TEOS膜/HDP酸化膜で構成された下部金属層間絶縁膜及び開口部がない最上部金属層を用いて製造された256メガビットDRAM素子の50%は、20~55個の不良ビットを示した。すなわち、金属層間絶縁膜として流動性酸化膜を採用するDRAM素子が金属層間絶縁膜としてHDP酸化膜を採用するDRAM素子よりもさらに高い収率を示した。これは前記流動性酸化膜が前記HDP酸化膜よりもさらに多孔質であるからと理解される。すなわち、後続の金属熱処理工程中に発生された水素原子が前記HDP酸化膜より前記流動性酸化膜を貫通するのが容易であったと理解される。

## 【0064】

これとは反対に、最上部金属層なしのPE-TEOS膜/流動性酸化膜(Fox)/PE-TEOS膜で構成された下部金属層間絶縁膜を用いて製造した256メガビットDRAM素子の50%は、10個より小さい不良ビット数Nを示した。

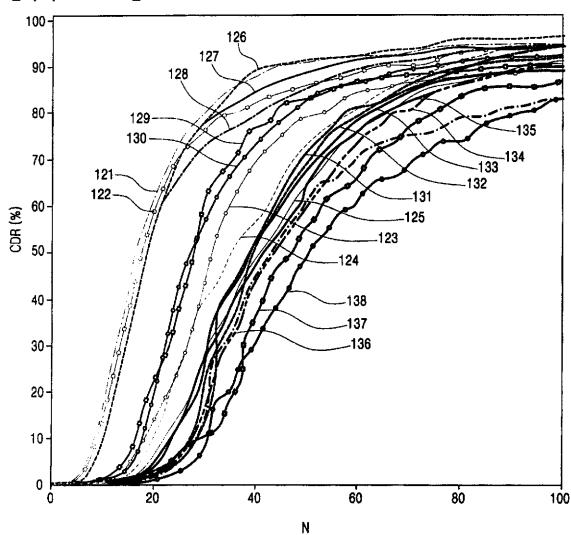

図11は従来技術及び本発明の実施形態により製造された256メガビットDRAM素子のセルテスト結果を示すグラフである。図11のグラフにおいて、横軸は不良ビット数Nを示し、縦軸(ordinate)は累積分布率CDRを示す。

## 【0065】

図11において、参照番号“121”ないし“138”で示されたデータは次の表2に記載された主要工程条件を用いて製造された試料から得た。また、セルキャパシタの上部電極(すなわち、プレート電極)はドーピングされたポリシリコン膜及びチタン窒化膜(TiN)を順に積層させて形成し、前記チタン窒化膜は400の厚さで形成した。さらに、前記256メガビットDRAM素子のそれぞれは複数の単位セルブロックを有するように設計され、前記単位セルブロックのそれぞれは145μmの幅及び273.4μmの長さを有するように設計された。ここで、前記セルテストもテスト(march test)プログラム及び200msecのリフレッシュ周期を用いて実施された。

## 【0066】

40

【表2】

| 工程パラメータ                | 試料番号 (Sample No.)                             |                                        |                   |

|------------------------|-----------------------------------------------|----------------------------------------|-------------------|

|                        | 121~125<br>(本発明)                              | 126~130<br>(本発明)                       | 131~138<br>(従来技術) |

| 下部金属配線 (M1)            | アルミニウム合金膜 (Al alloy; 4000Å)                   |                                        |                   |

| I MD                   | 下部キャッピング膜                                     | PE-TEOS膜 (1000Å)                       |                   |

|                        | 上部キャッピング膜                                     | Fox/PE-TEOS (4000Å)                    |                   |

| 上部金属配線 (M2)            | アルミニウム合金膜 (Al alloy; 6000Å)                   |                                        |                   |

| I MD                   | 下部キャッピング膜                                     | PE-TEOS膜 (1000Å)                       |                   |

|                        | 上部キャッピング膜                                     | HDP酸化膜                                 |                   |

| セルアレイ上の<br>最上部金属層 (M3) | アルミニウム合金膜 (Al alloy; 8000Å)                   |                                        |                   |

| 最上部金属層内の<br>開口部 (スリット) | 幅W; 2 μm<br>間隔D; 8 μm<br>長さ; 252.46 μm        | 幅W; 2 μm<br>間隔D; 4 μm<br>長さ; 252.46 μm | なし                |

| パッシバーション膜              | HDP酸化膜 (8000Å) / PE CVDSiN膜 (6000Å)           |                                        |                   |

| 熱処理<br>(metal alloy)   | 400Å、180分、H <sub>2</sub> ガス+N <sub>2</sub> ガス |                                        |                   |

## 【0067】

図11及び表2から分かるように、スリットなしの平板状の最上部金属層を用いて製造された256メガビットDRAM素子の50%は、約37~50個の不良ビットを示した。一方、10μmのスリットピッチを有する最上部金属層を用いて製造された256メガビットDRAM素子の50%は、約15~35個の不良ビットを示し、6μmのスリットピッチを有する最上部金属層を用いて製造した256メガビットDRAM素子の50%は、約20~30個の不良ビットを示した。

## 【0068】

結果的に、セルアレイ領域上に形成される金属層及び/または金属配線の重畠面積が減少する場合、同一のリフレッシュ周期でのDRAM素子の収率は増加するものとして理解される。すなわち、セルアレイ領域上に配置される最上部金属層の開口部の面積を増加させると、金属熱処理工程中にDRAM素子のセルMOSトランジスタに達する水素原子の数が増加されてセルゲート絶縁膜の界面トラップ密度を著しく減少させることができる。その結果、前記セルMOSトランジスタの漏洩電流特性が改善されて前記DRAM素子のリフレッシュ周期を増加させることができる。

## 【図面の簡単な説明】

## 【0069】

【図1】本発明の実施形態に適用可能な半導体記憶素子の概略的なブロックダイヤグラムである。

【図2】図1のセルアレイ領域の一部分を示す拡大平面図である。

【図3A】図2のI-I'線の断面図である。

【図3B】図2のII-II'線の断面図である。

【図4】図1の周辺回路領域の一部分を示す拡大平面図である。

【図5】図4のIII-III'線の断面図である。

【図6A】本発明の実施形態による半導体素子の製造方法を説明する図2のI-I'線の断面図である。

10

20

30

40

50

【図6B】本発明の実施形態による半導体素子の製造方法を説明する図2のI-I'線の断面図である。

【図7A】本発明の実施形態による半導体素子の製造方法を説明する図2のI-I'線の断面図である。

【図7B】本発明の実施形態による半導体素子の製造方法を説明する図2のI-I'線の断面図である。

【図8A】本発明の実施形態による半導体素子の製造方法を説明する図2のI-I'線の断面図である。

【図8B】本発明の実施形態による半導体素子の製造方法を説明する図2のI-I'線の断面図である。

【図9A】本発明の実施形態による半導体素子の製造方法を説明する図2のI-I'線の断面図である。

【図9B】本発明の実施形態による半導体素子の製造方法を説明する図2のI-I'線の断面図である。

【図10】本発明の効果を間接的に確認するために製造されたDRAM素子のセルテスト結果を示すグラフである。

【図11】従来技術及び本発明の実施形態によって製造されたDRAM素子のセルテスト結果を示すグラフである。

【符号の説明】

【0070】

- 1 半導体記憶素子

- 3 a、3 b、3 c、3 d セルブロック

- 5 a 感知増幅器

- 5 b コラムデコーダ

- 7 ローデコーダ

- 11 半導体基板

- 13 素子分離膜

- 13 a セル活性領域

- 21 下部層間絶縁膜

- 27 中間層間絶縁膜

- 37 上部層間絶縁膜

- 38 層間絶縁膜

- 39 第1下部金属配線

- 44 下部金属層間絶縁膜

- 45 第1上部金属配線

- 50 上部金属層間絶縁膜

- 51 第1最上部金属層

- 51s 第1スリット

- 53 シリコン酸化膜

- 55 シリコン窒化膜

- 56 パッシベーション膜

- H 高電圧回路領域

- V 重畠領域

10

20

30

40

【図1】

【図2】

【図3 A】

【図3 A】

【図3 B】

【図4】

【図5】

【 図 6 A 】

【図7B】

【 図 6 B 】

【図7A】

【 図 8 A 】

【 図 8 B 】

【 図 9 A 】

【 図 9 B 】

【 図 1 1 】

【図10】

---

フロントページの続き

(72)発明者 朴 柱成

大韓民国京畿道龍仁市新鳳洞(番地なし) エルジーエックスアイアパート117棟1002號

(72)発明者 洪 愛蘭

大韓民国京畿道水原市靈通區梅灘洞416番地

F ターム(参考) 5F033 HH04 HH08 HH09 HH33 LL01 MM22 QQ73 RR04 RR06 SS04

SS15 SS22 VV10 VV16 WW01 XX00

5F083 AD24 GA11 JA36 JA56 KA02 KA05 LA03 LA04 LA05 LA17

LA30 MA06 MA17 MA19 MA20 PR18