(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2007년11월28일

(11) 등록번호 10-0780257

(24) 등록일자 2007년11월22일

(51) Int. Cl.

*B24B 1/00* (2006.01)

(21) 출원번호 10-2001-0058025

(22) 출원일자 2001년09월19일

심사청구일자 2006년09월19일

(65) 공개번호 10-2002-0022617

공개일자 2002년03월27일

(30) 우선권주장

JP-P-2000-00284260 2000년09월19일 일본(JP)

(56) 선행기술조사문현

JP10318740 A

(뒷면에 계속)

전체 청구항 수 : 총 91 항

(73) 특허권자

소니 가부시끼 가이샤

일본국 도쿄도 미나토구 코난 1-7-1

(72) 발명자

사토슈조

일본국 도쿄도 시나가와 쿠카타시 나가와 6쵸메 7반 35고

소니가부시끼 가이샤 내

세가와유지

일본국 도쿄도 시나가와 쿠카타시 나가와 6쵸메 7반 35고

소니가부시끼 가이샤 내

(뒷면에 계속)

(74) 대리인

이범래, 이병호, 장훈

심사관 : 김성민

(54) 연마 방법, 연마 장치, 도금 방법 및 도금 장치

**(57) 요 약**

본 발명은 잉여 구리막을 양호한 효율로 제거하여 초기 요철을 쉽게 평탄화할 수 있고, 아래에 위치된 층간 절연 막에 대한 손상을 억제할 수 있는 연마 방법 및 연마 장치와, 평탄한 구리막을 증착할 수 있는 도금 방법 및 도금 장치에 관한 것이다. 연마 방법은 웨이퍼상의 막의 두께에 상당하는 데이터를 측정하는 단계와, 표면 보다 작은 캐소드 부재를 그 영역에 대향시키는 단계와, 표면과 캐소드 부재 사이에 전해액을 개재시키는 단계와, 캐소드로서 캐소드 부재를 사용하고, 애노드로서 상기 막을 사용하여 전압을 인가하는 단계와, 두께에 상당하는 데이터로부터 얻어진 막의 목표량이 제거될 때까지 전해 용리 또는 양극 산화와 퀄레이트화 및 퀄레이트막의 제거를 선택적으로 막의 돌출부들로부터 동한 영역에서 수행하는 단계와, 캐소드 부재를 다른 영역으로 이동하여 전체 표면에 걸쳐 상기 영역들을 평탄화하는 것을 반복하는 단계를 포함한다. 또한, 상술한 바의 역반응에 의해 도금이 수행된다.

**대표도** - 도1a

(72) 발명자

**요시오아키라**

일본국도쿄도시나가와쿠키타시나가와6쵸메7번35고

소니가부시끼가이샤내

**노가미타케시**

일본국도쿄도시나가와쿠키타시나가와6쵸메7번35고

소니가부시끼가이샤내

(56) 선 행 기술조사 문현

KR1020000044860 A

US5865984 A

US5744019 A

US5678320 A

US5620581 A

US5584310 A

US5567300 A

US5516412 A

US5489341 A

## 특허청구의 범위

### 청구항 1

연마될 표면상에 막을 갖는 대상물(object)을 연마하기 위한 연마 방법에 있어서,

상기 대상물 상의 상기 막의 두께에 상당하는 데이터를 측정하는 단계, 및

상기 표면에 비해 상대적으로 작은 캐소드 부재를 상기 표면의 영역에 대향시키고, 적어도 상기 캐소드 부재와 상기 표면의 영역 사이에 전해액을 재시키며, 이 상태에서 캐소드로서 기능하는 상기 캐소드 부재와 애노드로서의 막에 전압을 인가하여, 상기 두께에 상당하는 데이터로부터 얻어진 상기 막의 목표량을 제거할 때까지 우선적으로 상기 막의 돌출부들로부터 상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계를 포함하고,

상기 캐소드 부재를 상기 표면의 다른 영역으로 이동시키고, 상기 막의 목표량이 제거될 때까지 상기 다른 영역에서 상기 막을 전해 연마하여 상기 막을 평탄화하는 공정이 전체 표면에 걸쳐 반복되며, 그로써, 상기 전체 표면에 걸쳐 막의 목표량이 제거되는, 연마 방법.

### 청구항 2

제 1 항에 있어서,

상기 막은 구리막을 포함하는, 연마 방법.

### 청구항 3

제 1 항에 있어서,

상기 두께에 상당하는 데이터 측정 단계 이후, 및 상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계 이전에, 상기 두께에 상당하는 데이터로부터 제거될 상기 막의 양을 산출하는 단계를 더 포함하는, 연마 방법.

### 청구항 4

제 1 항에 있어서,

상기 캐소드 부재는 상기 표면의 한 영역으로부터 다른 영역으로 연속적으로 이동되는, 연마 방법.

### 청구항 5

제 4 항에 있어서,

상기 캐소드 부재의 이동 속도는 상기 두께에 상당하는 데이터로부터 얻어진 제거될 상기 막의 목표량에 따라 제어되는, 연마 방법.

### 청구항 6

제 1 항에 있어서,

상기 캐소드 부재는 상기 표면의 한 영역으로부터 다른 영역으로 단계적으로(stepwise) 이동되는, 연마 방법.

### 청구항 7

제 1 항에 있어서,

상기 막의 두께에 상당하는 데이터로서, 상기 막의 두께가 측정되는, 연마 방법.

### 청구항 8

제 1 항에 있어서,

상기 막의 두께에 상당하는 데이터를 측정하는 단계에서, 상기 캐소드 부재가 상기 표면에 대향하는 영역에서의 상기 막의 두께에 상당하는 데이터가 측정되고,

상기 표면의 다른 영역으로 상기 캐소드 부재를 이동시키고, 상기 다른 영역에서의 상기 막의 두께에 상당하는 데이터를 측정하고, 상기 두께에 상당하는 데이터로부터 얻어진 상기 막의 목표량이 제거될 때까지 상기 다른 영역에서 상기 막의 돌출부로부터 우선적으로 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계가 상기 전체 표면에 걸쳐 반복되는, 연마 방법.

### 청구항 9

제 8 항에 있어서,

상기 막의 두께에 상당하는 데이터를 측정하는 단계에서, 상기 막의 두께에 상당하는 데이터로서, 상기 캐소드 부재가 상기 표면에 대향하는 영역에서의 상기 전해 연마의 전류가 측정되고,

상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계에서, 상기 전해 연마의 전류에 의해 결정된 상기 막의 목표량이 제거될 때까지 상기 전해 연마가 수행되는, 연마 방법.

### 청구항 10

제 9 항에 있어서,

상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계에서, 상기 전해 연마의 전류가 특정 값이 될 때의 시점에서 남아있는 상기 막의 목표량이 0이 되도록 결정되고, 상기 표면의 상기 영역에서의 상기 전해 연마가 종료되는, 연마 방법.

### 청구항 11

제 1 항에 있어서,

상기 캐소드 부재는 상기 표면의 상기 영역에서의 상기 막의 요철에 대응하는 상기 막의 오목부보다 돌출부에 더 강한 전계를 인가할 수 있도록 성형되고,

상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계에서, 상기 전계를 인가함으로써, 상기 막이 우선적으로 상기 막의 돌출부로부터 상기 표면의 상기 영역에서 전해 용리에 의해 전해 연마 및 평탄화되는, 연마 방법.

### 청구항 12

제 11 항에 있어서,

상기 표면은 상기 표면의 상기 영역에서의 돌출 및 오목 패턴을 반복함으로써 형성된 돌출 및 오목 패턴을 갖고,

상기 캐소드 부재를 단계적으로 상기 표면의 다른 영역으로 이동시키고, 이들 다른 영역들에서 상기 막의 요철에 대응하는 상기 막의 상기 오목부보다 상기 돌출부에 더 강한 전계를 인가함으로써, 우선적으로 상기 막의 돌출부로부터 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계가 전체 표면에 걸쳐 반복되는, 연마 방법.

### 청구항 13

제 1 항에 있어서,

상기 캐소드 부재는 서로 절연된 상태로 배열되어 있는 다수의 영역들로 분할되고, 전체로서의 상기 캐소드 부재가 상기 전체 표면에 대향하며,

상기 분할된 캐소드 부재에 대한 전압 인가 위치를 변화시킴으로써, 상기 표면에 대향하는 상기 캐소드 부재의 위치를 한 영역으로부터 다른 영역으로 변화시킬 때와 실질적으로 대등한 효과가 얻어지는, 연마 방법.

### 청구항 14

제 13 항에 있어서,

상기 캐소드 부재는 다수의 동심원 영역들로 분할되고,

상기 전체 표면은 동심원 영역들로 분할된 상기 캐소드 부재의 내측으로부터 외측으로 전압 인가 위치를 변화시킴으로써 전해 연마되는, 연마 방법.

### 청구항 15

제 1 항에 있어서,

상기 표면에 비해 상대적으로 작은 캐소드 부재를 상기 표면의 상기 영역에 대향하도록 했을 때, 상기 캐소드 부재로부터 특정 거리에 이격 설치된 애노드 부재가 상기 표면에 대향하게 되며, 전해액이 적어도 상기 표면의 상기 영역과 상기 캐소드 부재의 사이 및 상기 표면과 상기 애노드 부재의 사이에 개재되고, 상기 캐소드 부재 및 애노드 부재에 전압이 인가되어 캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 실체로 전압이 인가되는, 연마 방법.

### 청구항 16

제 15 항에 있어서,

상기 애노드 부재는 상기 표면상의 물질 보다 귀한 금속을 포함하는, 연마 방법.

### 청구항 17

제 1 항에 있어서,

상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계에서, 상기 전해 연마와 동시에 화학 기계 연마가 수행되어 상기 전해 연마와 상기 화학 기계 연마를 조합한 복합 연마에 의해 막을 평탄화하는, 연마 방법.

### 청구항 18

제 1 항에 있어서,

캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 전압이 인가될 때, 직류 전압이 인가되는, 연마 방법.

### 청구항 19

제 18 항에 있어서,

직각 펄스(rectangular pulse) 전압이 인가되는, 연마 방법.

### 청구항 20

제 15 항에 있어서,

상기 캐소드 부재와 애노드 부재에 전압이 인가될 때, 교류 전압이 인가되는, 연마 방법.

### 청구항 21

제 1 항에 있어서,

상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계에서, 상기 영역에서의 상기 전해 연마의 전해 전류가 동시에 측정되는, 연마 방법.

### 청구항 22

제 21 항에 있어서,

캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 인가된 전압은 상기 전해 전류를 일정하게 유지하도록 제어되는, 연마 방법.

### 청구항 23

제 21 항에 있어서,

상기 표면의 상기 영역에서의 상기 막의 평탄화의 진행은 상기 전해 전류를 통해 관리되는, 연마 방법.

#### 청구항 24

연마될 표면상에 막을 갖는 대상물을 연마하는 연마 방법에 있어서,

상기 대상물 상의 상기 막의 두께에 상당하는 데이터를 측정하는 단계;

상기 표면에 비해 상대적으로 작은 캐소드 부재를 상기 표면의 영역에 대향시키고, 적어도 상기 캐소드 부재와 상기 표면의 상기 영역 사이에 칠레이트제(chelating agent)를 포함하는 전해액을 개재시키며, 이 상태에서 캐소드로서 기능하는 상기 캐소드 부재와 애노드로서의 상기 막에 전압을 인가하여, 양극 산화에 의해 상기 막의 표면을 산화시키고, 상기 산화된 물질의 칠레이트막을 형성하는 단계; 및

상기 막의 요철에 대응하는 상기 칠레이트막의 돌출부를 선택적으로 제거하여 상기 표면에서 돌출부의 막을 노출시키도록 하는 단계를 포함하고,

상기 표면의 한 영역으로부터 다른 영역으로 상기 캐소드 부재를 이동시키는 단계, 칠레이트막 형성 단계 및 칠레이트막 제거 단계는 전체 표면을 평탄화하기 위해 상기 전체 표면에 걸쳐 두께에 상당하는 데이터로부터 결정된 상기 막의 목표량이 제거될 때까지 반복되는, 연마 방법.

#### 청구항 25

제 24 항에 있어서,

상기 막은 구리막을 포함하는, 연마 방법.

#### 청구항 26

제 24 항에 있어서,

상기 전해액은 계면활성제를 더 포함하는, 연마 방법.

#### 청구항 27

제 24 항에 있어서,

상기 두께에 상당하는 데이터를 측정하는 단계 이후 및 상기 표면의 상기 영역에 상기 칠레이트막을 형성하는 단계 이전에, 상기 두께에 상당하는 데이터로부터 제거될 상기 막의 목표량을 산출하는 단계를 더 포함하는, 연마 방법.

#### 청구항 28

제 24 항에 있어서,

상기 캐소드 부재는 상기 표면의 한 영역으로부터 다른 영역으로 연속적으로 이동되는, 연마 방법.

#### 청구항 29

제 28 항에 있어서,

상기 캐소드 부재의 이동 속도는 상기 두께에 상당하는 데이터로부터 얻어진 제거될 상기 막의 목표량에 따라 제어되는, 연마 방법.

#### 청구항 30

제 24 항에 있어서,

상기 캐소드 부재는 상기 표면의 한 영역으로부터 다른 영역으로 단계적으로 이동되는, 연마 방법.

#### 청구항 31

제 24 항에 있어서,

상기 막의 두께에 상당하는 데이터로서, 상기 막의 두께가 측정되는, 연마 방법.

**청구항 32**

제 24 항에 있어서,

상기 막의 두께에 상당하는 데이터 측정 단계에서, 상기 캐소드 부재가 상기 표면에 대향하는 영역에서의 상기 막의 두께에 상당하는 데이터가 측정되고,

상기 표면의 다른 영역들로 상기 캐소드 부재를 이동시키는 단계, 상기 다른 영역들에서의 상기 막의 두께에 상당하는 데이터를 측정하는 단계, 상기 킬레이트막 형성 단계, 및 상기 킬레이트막 제거 단계는 상기 전체 표면에 걸쳐 반복되는, 연마 방법.

**청구항 33**

제 32 항에 있어서,

상기 막의 두께에 상당하는 데이터 측정 단계에서, 상기 막의 두께에 상당하는 데이터로서, 상기 캐소드 부재가 상기 표면에 대향하는 영역에서의 상기 양극 산화의 전해 전류가 측정되고,

상기 양극 산화의 전해 전류 측정 단계, 상기 킬레이트막 형성 단계, 및 상기 킬레이트막 제거 단계는 상기 양극 산화의 전해 전류에 의해 결정된 상기 막의 목표량이 제거될 때까지 상기 전체 표면에 걸쳐 반복되는, 연마 방법.

**청구항 34**

제 33 항에 있어서,

상기 표면의 영역의 상기 양극 산화의 전해 전류를 측정하는 단계, 상기 킬레이트막 형성 단계, 및 상기 킬레이트막 제거 단계를 상기 전체 표면에 걸쳐 반복할 때, 상기 양극 산화의 전해 전류가 특정값이 되는 시점에서 남아있는 상기 막의 목표량을 0으로 결정하고, 상기 표면의 상기 영역에서의 상기 킬레이트막 형성 단계와 상기 킬레이트막 제거 단계가 종료되는, 연마 방법.

**청구항 35**

제 24 항에 있어서,

상기 캐소드 부재는 상기 표면의 상기 영역에서의 상기 막의 요철에 대응하는 상기 막의 오목부보다 돌출부에 더 강한 전계를 인가할 수 있도록 성형되고,

상기 표면의 상기 영역에서의 상기 킬레이트막 형성 단계와 상기 킬레이트막 제거 단계에서, 상기 전계를 인가함으로써, 우선적으로 상기 막의 돌출부로부터 상기 킬레이트막이 형성 및 제거되어 상기 막을 평탄화하는, 연마 방법.

**청구항 36**

제 35 항에 있어서,

상기 표면은 상기 표면의 상기 영역에서의 돌출 및 오목 패턴을 반복함으로써 형성된 돌출 및 오목 패턴을 갖고,

상기 캐소드 부재를 단계적으로 상기 표면의 다른 영역들로 이동시키고, 상기 다른 영역들에서의 상기 막의 요철에 대응하는 상기 막의 오목부보다 돌출부에 더 강한 전계를 인가함으로써, 상기 막을 킬레이트화하는 단계와, 상기 형성된 킬레이트막을 우선적으로 상기 막의 돌출부로부터 제거하여 상기 막을 평탄화하는 단계가 상기 전체 표면에 걸쳐 반복되는, 연마 방법.

**청구항 37**

제 24 항에 있어서,

상기 캐소드 부재는 서로 절연된 상태로 배열되는 다수의 영역들로 분할되고, 전체로서의 상기 캐소드 부재가 상기 전체 표면에 대향하며,

상기 분할된 캐소드 부재에 대한 전압 인가 위치를 변화시킴으로써, 상기 표면에 대향하는 상기 캐소드 부재의

위치를 한 영역으로부터 다른 영역으로 변화시킬 때와 실질적으로 대등한 효과가 얻어지는, 연마 방법.

### 청구항 38

제 37 항에 있어서,

상기 캐소드 부재는 다수의 동심원 영역들로 분할되고,

동심원 영역들로 분할된 상기 캐소드 부재의 내측으로부터 외측으로 전압 인가 위치를 변화시킴으로써, 상기 막의 전체 표면이 양극 산화 및 킬레이트화에 의해 산화되는, 연마 방법.

### 청구항 39

제 24 항에 있어서,

상기 표면에 비해 상대적으로 작은 캐소드 부재를 상기 표면의 상기 영역에 대향하도록 형성했을 때, 상기 캐소드 부재로부터 특정 거리에 이격 설치된 애노드 부재가 상기 표면에 대향하게 되며, 전해액이 적어도 상기 표면의 상기 영역과 상기 캐소드 부재 사이 및 상기 표면과 상기 애노드 부재의 사이에 개재되고, 상기 캐소드 부재와 상기 애노드 부재에 전압이 인가되어 캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 실제로 상기 전압이 인가되는, 연마 방법.

### 청구항 40

제 39 항에 있어서,

상기 애노드 부재는 상기 표면상의 물질 보다 귀한 금속을 포함하는, 연마 방법.

### 청구항 41

제 24 항에 있어서,

상기 표면의 상기 영역에서의 상기 킬레이트막을 제거하는 단계에서, 상기 막의 요철에 대응하는 상기 킬레이트막의 돌출부가 와이핑(wiping)에 의해 선택적으로 제거되는, 연마 방법.

### 청구항 42

제 24 항에 있어서,

상기 표면의 상기 영역에서의 상기 킬레이트막을 제거하는 단계에서, 상기 킬레이트막은 진동을 인가함으로써 제거되는, 연마 방법.

### 청구항 43

제 24 항에 있어서,

상기 표면의 상기 영역에서의 상기 킬레이트막을 제거하는 단계에서, 상기 킬레이트막은 제트(jet)를 인가함으로써 제거되는, 연마 방법.

### 청구항 44

제 24 항에 있어서,

캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 전압이 인가될 때, 직류 전압이 인가되는, 연마 방법.

### 청구항 45

제 44 항에 있어서,

직각 펄스 전압이 인가되는, 연마 방법.

### 청구항 46

제 39 항에 있어서,

상기 캐소드 부재와 상기 애노드 부재에 전압이 인가될 때, 교류 전압이 인가되는, 연마 방법.

#### 청구항 47

제 24 항에 있어서,

상기 표면의 상기 영역에서 상기 양극 산화에 의해 상기 막을 산화시키는 단계에서, 상기 영역에서의 상기 양극 산화의 전해 전류가 동시에 측정되는, 연마 방법.

#### 청구항 48

제 47 항에 있어서,

캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 인가된 상기 전압이 상기 전해 전류를 일정하게 유지하도록 제어되는, 연마 방법.

#### 청구항 49

제 47 항에 있어서,

상기 표면의 상기 영역에서의 상기 막의 평탄화의 진행은 상기 전해 전류를 통해 관리되는, 연마 방법.

#### 청구항 50

연마될 표면상에 막을 갖는 대상물을 연마하는 연마 장치에 있어서,

상기 대상물을 유지하기 위한 테이블,

상기 대상물 상의 상기 막의 두께에 상당하는 데이터를 측정하는 측정 수단,

상기 표면의 영역에 대향하도록 배열된, 상기 표면에 비해 상대적으로 작은 캐소드 부재,

적어도 상기 캐소드 부재와 상기 표면의 상기 영역 사이에 전해액을 공급하는 전해액 공급 수단,

캐소드로서 기능하는 상기 캐소드 부재와 애노드로서 기능하는 상기 막에 전압을 인가하는 전원,

상기 막이 상기 표면의 상기 영역에서 전해 용리에 의해 전해 연마될 때, 두께에 상당하는 데이터로부터 얻어진 막의 목표량이 제거될 때까지 전압 인가를 제어하는 제어 수단, 및

상기 전체 표면에 걸쳐 막의 목표량을 제거하기 위해 상기 표면의 다른 영역들로 상기 캐소드 부재를 이동시키는 이동 수단을 포함하는, 연마 장치.

#### 청구항 51

제 50 항에 있어서,

상기 막은 구리막을 포함하는, 연마 장치.

#### 청구항 52

제 50 항에 있어서,

상기 두께에 상당하는 데이터로부터 제거될 상기 막의 목표량을 산출하는 연산 유닛을 더 포함하는, 연마 장치.

#### 청구항 53

제 50 항에 있어서,

상기 측정 수단은 상기 막의 두께를 측정하는, 연마 장치.

#### 청구항 54

제 50 항에 있어서,

상기 측정 수단은 상기 캐소드 부재가 상기 표면에 대향하는 영역에서의 상기 전해 연마의 전해 전류를 측정하

고,

상기 제어 수단은 상기 표면의 상기 영역에서 상기 전해 연마의 전해 전류에 의해 결정되는 막의 목표량이 제거될 때까지 인가될 전압을 제어하는, 연마 장치.

### 청구항 55

제 54 항에 있어서,

상기 제어 수단은 상기 전해 연마의 전해 전류가 특정값이 되는 시점에 남아있는 상기 막의 목표량을 0으로 결정하고, 상기 표면의 상기 영역에서의 전해 연마가 종료되도록 제어하는, 연마 장치.

### 청구항 56

제 50 항에 있어서,

상기 캐소드 부재는 상기 표면의 상기 영역에서의 상기 막의 요철에 대응하는 상기 막의 오목부보다 돌출부에 더 강한 전계를 인가할 수 있도록 성형되고,

상기 전계를 인가함으로써, 상기 막이 우선적으로 상기 막의 돌출부로부터 상기 표면의 상기 영역에서 전해 용리에 의해 전해 연마 및 평탄화되는, 연마 장치.

### 청구항 57

제 50 항에 있어서,

상기 캐소드 부재는 서로 절연되어 배열되는 다수의 영역들로 분할되고, 전체로서 상기 캐소드 부재는 전체 표면에 대향하며,

상기 분할된 캐소드 부재에 대한 전압 인가 위치를 변화시킴으로써, 상기 표면에 대향하는 상기 캐소드 부재의 위치를 한 영역으로부터 다른 영역으로 변화시킬 때와 실질적으로 동일한 효과가 얻어지는, 연마 장치.

### 청구항 58

제 57 항에 있어서,

상기 캐소드 부재는 다수의 동심원 영역들로 분할되는, 연마 장치.

### 청구항 59

제 50 항에 있어서,

상기 표면에 대향하며 상기 캐소드 부재로부터 특정 거리 이격 배치되어 있는 애노드 부재를 더 포함하고,

상기 전해액 공급 수단은 상기 표면의 상기 영역과 상기 캐소드 부재 사이 및 상기 표면과 상기 애노드 부재 사이에 전해액을 공급하고,

상기 전원은 상기 캐소드 부재 및 상기 애노드 부재에 전압을 인가하는, 연마 장치.

### 청구항 60

제 59 항에 있어서,

상기 애노드 부재는 상기 표면상의 물질 보다 귀한 금속을 포함하는, 연마 장치.

### 청구항 61

제 50 항에 있어서,

화학 기계 연마를 위한 연마 수단을 더 포함하고,

상기 전해 연마로 상기 막을 평탄화하는 동시에, 상기 막의 상기 영역에서 화학 기계 연마를 수행하는, 연마 장치.

## 청구항 62

제 50 항에 있어서,

상기 전원은 캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 직류 전압을 인가하는, 연마 장치.

## 청구항 63

제 62 항에 있어서,

상기 전원은 직각 펄스 전압을 인가하는, 연마 장치.

## 청구항 64

제 59 항에 있어서,

상기 전원은 상기 캐소드 부재와 상기 애노드 부재에 교류 전압을 인가하는, 연마 장치.

## 청구항 65

제 50 항에 있어서,

상기 영역에서의 상기 전해 연마의 전해 전류를 측정하기 위한 전류계를 더 포함하는, 연마 장치.

## 청구항 66

제 65 항에 있어서,

상기 제어 수단은 상기 전해 전류가 일정하게 유지되도록 상기 표면과 상기 캐소드 부재에 인가되는 전압을 제어하는, 연마 장치.

## 청구항 67

연마될 표면상에 막을 갖는 대상물을 연마하는 연마 장치에 있어서,

상기 대상물을 유지하는 테이블,

상기 대상물 상의 막의 두께에 상당하는 데이터를 측정하는 측정 수단,

상기 표면의 영역에 대향하도록 배열된, 상기 표면에 비해 상대적으로 작은 캐소드 부재,

킬레이트제를 포함하는 전해액을 적어도 상기 표면의 상기 영역과 상기 캐소드 부재 사이에 공급하는 전해액 공급 수단,

캐소드로서 기능하는 상기 캐소드 부재와 애노드로서의 상기 막에 전압을 인가하는 전원,

상기 막의 표면이 상기 표면의 상기 영역에서 양극 산화에 의해 산화되고, 상기 산화된 물질의 킬레이트막이 형성될 때까지 전압 인가를 제어하는 제어 수단,

상기 킬레이트막을 제거하는 킬레이트막 제거 수단, 및

전체 표면에 걸쳐 상기 두께에 상당하는 데이터로부터 얻어진 상기 막의 목표량을 제거하기 위해 상기 표면의 다른 영역들로 상기 캐소드 부재를 이동시키는 이동 수단을 포함하는, 연마 장치.

## 청구항 68

제 67 항에 있어서,

상기 막은 구리막을 포함하는, 연마 장치.

## 청구항 69

제 67 항에 있어서,

상기 킬레이트막 제거 수단은 상기 막의 요철에 대응하는 상기 킬레이트막의 돌출부를 선택적으로 제거하는, 연

마 장치.

### 청구항 70

제 67 항에 있어서,

상기 전해액 공급 수단은 전해액으로서 계면활성제를 더 포함하는 전해액을 공급하는, 연마 장치.

### 청구항 71

제 67 항에 있어서,

상기 두께에 상당하는 데이터로부터 제거될 상기 막의 목표량을 산출하기 위한 연산 유닛을 더 포함하는, 연마 장치.

### 청구항 72

제 67 항에 있어서,

상기 측정 수단은 상기 막의 두께를 측정하는, 연마 장치.

### 청구항 73

제 67 항에 있어서,

상기 측정 수단은 상기 캐소드 부재가 상기 표면에 대향하는 영역에서 양극 산화의 전해 전류를 측정하고,

상기 제어 수단은 상기 표면의 상기 영역에서 상기 양극 산화의 전해 전류에 의해 결정된 막의 목표량을 제거할 때까지 인가될 상기 전압을 제어하는, 연마 장치.

### 청구항 74

제 73 항에 있어서,

상기 제어 수단은 상기 양극 산화의 전해 전류가 특정값이 되는 시점에서 남아있는 상기 막의 목표량을 0으로 결정하고, 상기 표면의 상기 영역에서의 상기 양극 산화를 종료하도록 제어하는, 연마 장치.

### 청구항 75

제 67 항에 있어서,

상기 캐소드 부재는 상기 표면의 상기 영역에서의 상기 막의 요철에 대응하는 상기 막의 오목부보다 돌출부에 더 강한 전계를 인가할 수 있도록 성형되고,

상기 전계를 인가함으로써, 상기 막은 우선적으로 상기 막의 돌출부로부터 상기 표면의 상기 영역에서 양극 산화에 의해 산화되고 킬레이트화되어 상기 막을 평탄화하는, 연마 장치.

### 청구항 76

제 67 항에 있어서,

상기 캐소드 부재는 서로 절연되어 배열된 다수의 영역들로 분할되고, 전체로서의 상기 캐소드 부재는 상기 전체 표면에 대향하며,

상기 분할된 캐소드 부재에 대한 전압 인가 위치를 변화시킴으로써, 상기 표면에 대향하는 상기 캐소드 부재의 위치를 한 영역으로부터 다른 영역으로 이동시킬 때와 실질적으로 동일한 효과가 얻어지는, 연마 장치.

### 청구항 77

제 76 항에 있어서,

상기 캐소드 부재는 다수의 동심원 영역들로 분할되는, 연마 장치.

### 청구항 78

제 67 항에 있어서,

상기 표면에 대향하고 상기 캐소드 부재로부터 특정 거리 이격 배치되어 있는 애노드 부재를 포함하고,

상기 전해액 공급 수단은 상기 표면의 상기 영역과 상기 캐소드 부재 사이 및 상기 표면과 상기 애노드 부재 사이에 전해액을 공급하며,

상기 전원은 상기 캐소드 부재 및 애노드 부재에 전압을 인가하는, 연마 장치.

#### 청구항 79

제 78 항에 있어서,

상기 애노드 부재는 상기 표면상의 물질보다 귀한 금속을 포함하는, 연마 장치.

#### 청구항 80

제 67 항에 있어서,

상기 킬레이트막 제거 수단으로서 상기 막의 요철에 대응하는 상기 킬레이트막의 돌출부를 선택적으로 제거하는 와이핑 수단을 포함하는, 연마 장치.

#### 청구항 81

제 67 항에 있어서,

상기 킬레이트막 제거 수단은 진동 인가 수단을 포함하는, 연마 장치.

#### 청구항 82

제 67 항에 있어서,

상기 킬레이트막 제거 수단은 제트를 발생시키는 수단과, 상기 킬레이트막에 상기 제트를 인가하는 인가 수단을 포함하는, 연마 장치.

#### 청구항 83

제 67 항에 있어서,

상기 전원은 캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 직류 전압을 인가하는, 연마 장치.

#### 청구항 84

제 83 항에 있어서,

상기 전원은 직각 펠스 전압을 인가하는, 연마 장치.

#### 청구항 85

제 78 항에 있어서,

상기 전원은 상기 캐소드 부재와 상기 애노드 부재에 교류 전압을 인가하는, 연마 장치.

#### 청구항 86

제 67 항에 있어서,

상기 영역에서의 상기 양극 산화의 전해 전류를 측정하는 전류계를 더 포함하는, 연마 장치.

#### 청구항 87

제 86 항에 있어서,

상기 제어 수단은 상기 전해 전류를 일정하게 유지하기 위해 상기 표면과 상기 캐소드 부재에 인가되는 전압을 제어하는, 연마 장치.

## 청구항 88

대상물의 표면상에 도금막을 증착하는 도금 방법에 있어서,

상기 대상물 상의 상기 도금막의 두께 데이터 또는 표면의 표면 높이 데이터를 측정하는 단계, 및

상기 표면에 비해 상대적으로 작은 애노드 부재를 상기 표면의 영역에 대향시키고, 적어도 상기 표면의 상기 영역과 상기 애노드 부재 사이에 전해 도금액을 개재시키면서, 애노드로서 기능하는 상기 애노드 부재와 캐소드로서의 상기 표면에 전압을 인가하고, 상기 측정 시간에 상기 도금막의 상기 두께 데이터 또는 상기 표면 높이 데이터로부터 유도된 상기 도금막의 목표량이 증착될 때까지 상기 표면의 상기 영역에 도금에 의해 상기 도금막을 증착하는 단계를 포함하고;

상기 애노드 부재를 상기 표면의 다른 영역으로 이동시키고, 상기 다른 영역에서 도금에 의한 도금막 증착하는 공정을 전체 표면에 걸쳐 반복하는, 도금 방법.

## 청구항 89

제 88 항에 있어서,

상기 도금막은 구리막을 포함하는, 도금 방법.

## 청구항 90

대상물의 표면상에 도금막을 증착하는 도금 장치에 있어서,

상기 대상물을 유지하는 테이블,

상기 대상물 상의 상기 도금막의 두께 데이터 또는 표면의 표면 높이 데이터를 측정하는 측정 수단,

상기 표면의 영역에 대향하도록 배열된, 상기 표면에 비해 상대적으로 작은 애노드 부재,

적어도 상기 표면의 상기 영역과 상기 애노드 부재 사이에 전해 도금액을 공급하는 전해 도금액 공급 수단,

애노드로서 기능하는 상기 애노드 부재와 캐소드로서의 상기 표면에 전압을 인가하는 전원,

상기 표면의 상기 영역에서의 측정시에 상기 도금 두께 데이터 또는 상기 표면 높이 데이터로부터 유도된 상기 도금막의 목표량이 도금에 의해 형성될 때까지 전압의 인가를 제어하는 제어 수단, 및

상기 애노드 부재를 상기 표면의 다른 영역으로 이동시키는 이동 수단을 포함하는, 도금 장치.

## 청구항 91

제 90 항에 있어서,

상기 도금막은 구리막을 포함하는, 도금 장치.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

<44> 본 발명은 반도체 디바이스 제조에 사용되는 연마(polishing) 방법, 연마 장치, 도금(plating) 방법 및 도금 장치에 관한 것으로서, 특히, 다마센(damascene) 프로세스에서의 구리막 또는 다른 막의 연마 방법 및 연마 장치와, 구리막 등을 형성하는 프로세스들에서 사용되는 도금 방법 및 도금 장치에 관한 것이다.

<45> 반도체 디바이스의 크기 감소와 집적도의 향상에 따라서, 상호접속부들의 소형화와, 상호접속 피치의 감소 및 상호접속부들의 중첩에 진보가 이루어져 왔다. 따라서, 반도체 디바이스들의 제조 프로세스에서 다층 상호접속 기술의 중요성이 커지고 있다.

<46> 한편, 종래에는 다층 상호접속 구조를 가진 반도체 디바이스의 상호접속 물질로서 빈번히 알루미늄이 사용되어

왔지만, 최근의  $0.25\mu\text{m}$  이하의 설계 규칙(design rule)에서 신호들의 전달 지연을 억제하기 위해, 상호접속 물질의 알루미늄을 구리로 대체하기 위한 상호접속 프로세스가 개발되고 있다. 상호접속부들에 구리를 사용할 때, 저저항과, 높은 전자 이동 공차라는 두가지 장점을 얻을 수 있다.

<47> 상호접속부에 구리를 사용하는 프로세스에서, 예를 들어, 충간 절연막 내에 먼저 형성된 홈형(groove-like) 상호접속 패턴에 금속을 매립하고, 화학 기계 연마(CMP, chemical machine polishing)에 의해 잉여 금속막을 제거하여 상호접속부들을 형성하는 다마센 프로세스라고 하는 상호접속 프로세스가 주로 사용되고 있다. 다마센 프로세스는 상호접속부들의 에칭이 불필요하고, 또한, 부가적인 상부 충간 절연막이 그 자체에 의해 평탄화되어, 프로세스가 단순해질 수 있다는 특성들을 가지고 있다.

<48> 또한, 상호접속부들을 위한 홈들뿐만 아니라, 접촉 홀들도 충간 절연막내에 홈으로써 형성되고, 상호접속부들 및 접촉 홀들이 동시에 금속으로 매립되는 이중 다마센 프로세스에 의해, 상호접속 단계들의 현저한 감소가 가능하게 된다.

<49> 여기서, 도면들을 참조하여 이중 다마센 프로세스에 의해 구리 상호접속부들을 형성하기 위한 프로세스의 예를 이하 설명한다.

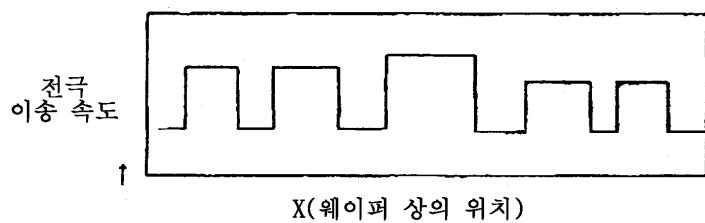

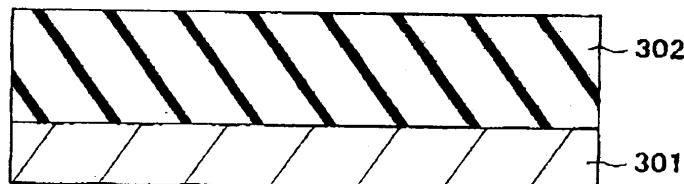

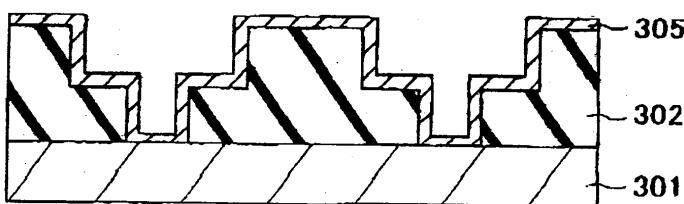

<50> 먼저, 도 34a에 도시된 바와 같이, 예를 들어, 실리콘 산화물로 제조된 충간 절연막(302)이 실리콘 또는 다른 반도체 기판(301)상에 예를 들어 저압 화학 기상 증착(CVD)에 의해 형성되고, 상기 반도체 기판상에는 도시되지 않은 불순물 확산 영역이 적절히 형성된다.

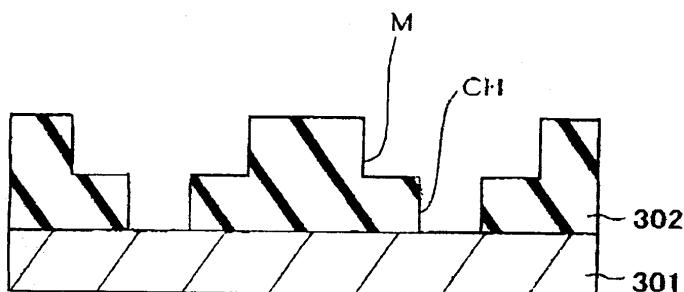

<51> 다음에, 도 34b에 도시된 바와 같이, 반도체 기판(301)의 불순물 확산 영역과 소통하는 접촉 홀들(CH)과, 기판(301)의 불순물 확산 영역에 전기적으로 접속되도록 상호접속부들의 미리 결정된 패턴을 형성하게 될 홈들(M)이 공지된 포토리소그래피 및 에칭을 사용하여 형성된다.

<52> 다음에, 도 34c에 도시된 바와 같이, 배리어 금속막(barrier metal film)(305)이 충간 절연막(302)의 표면상에, 및 접촉 홀들(CH)과 홈들(M) 내에 형성된다. 이 배리어 금속막(305)은 Ta, Ti, TaN 또는 TiN과 같은 물질로 널리 공지된 스퍼터링에 의해 형성된다. 상호접속 물질이 구리이고, 충간 절연막(302)이 실리콘 산화물일 때, 구리가 실리콘 산화물에 대해 큰 확산 계수를 갖기 때문에, 이는 쉽게 산화된다. 배리어 금속막(305)은 이를 방지하기 위해 제공된다.

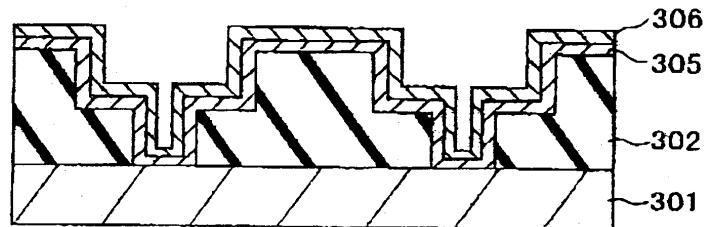

<53> 다음에, 도 35a에 도시된 바와 같이, 시드막(seed film)((306)이 널리 공지된 스퍼터링에 의해 미리 결정된 두께로 배리어 금속막(305) 상에 형성된다.

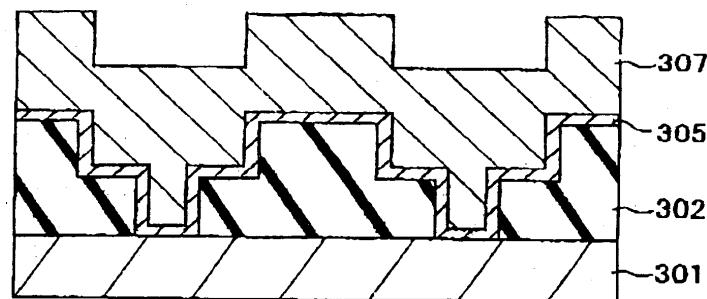

<54> 그후, 도 35b에 도시된 바와 같이, 구리막(307)이 시드막(306)상에 성장 및 형성되어, 접촉 홀들(CH)과 홈들(M)이 구리에 의해 매립되게 된다. 구리막(307)은, 예를 들어, 도금, CVD, 스퍼터링 등에 의해 형성된다.

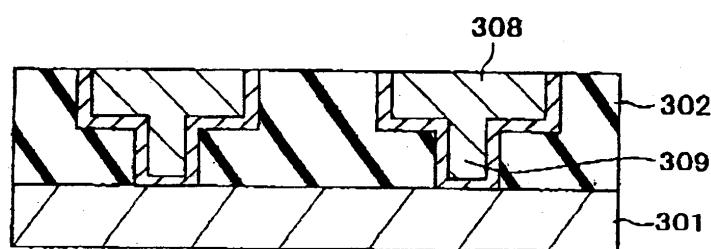

<55> 다음에, 도 35c에 도시된 바와 같이, 평탄화를 위해 충간 절연막(302)상의 잉여 구리막(307) 및 배리어 금속막(305)이 CMP에 의해 제거된다.

<56> 상술한 단계들로 인하여, 구리 상호접속부들(308) 및 접촉 홀들(309)이 형성된다.

<57> 상술한 프로세스를 상호접속부들(308) 상에서 반복함으로써, 다층 상호접속부들이 형성될 수 있다.

### 발명이 이루고자 하는 기술적 과제

<58> 본 발명에 의해 해결될 문제점들을 요약하면, 이중 다마센 프로세스를 사용한 구리 상호접속부 형성 프로세스에서 CMP에 의해 잉여 구리막(307)을 제거하는 단계에서, 종래의 CMP를 사용하는 평탄화 기술이 연마를 위해 연마 도구와 구리막 사이에 미리 결정된 압력을 가하는 것을 수반하기 때문에, 대규모의 손상이 반도체 기판에 주어지게 되는 문제가 발생된다.

<59> 특히, 예를 들어, 폴리이미드 막 또는 다른 유기 절연막 또는 플루오린을 포함하는 실리콘 산화물로 구성된 SiOF 막, 또는, 다공성 실리카나 다른 젤 절연막 같은 무기 절연막과 같은 낮은 유전율을 갖는 절연막이 반도체 디바이스의 동작 속도를 상승시키기 위해 상호접속부들 내에서 기생 커패시턴스를 감소시킬 목적으로 충간 절연막에 사용되는 경우에, 일반적으로 이들 절연막들은 낮은 기계적 강도를 가지기 때문에, CMP 프로세스에서의 상술한 손상이 더 이상 무시할만한 것이 아니게 되며, 충간 절연막의 균열들과 반도체 기판으로부터 충간 절연막의 분리를 초래할 수 있다.

<60> 또한, 충간 절연막(302), 구리막(307) 및 배리어 금속막(305) 사이에서 제거 성능이 다르고, 따라서, 다이싱

(dishing), 침식(erosion)(박화(thinning)), 리세스들 등이 상호접속부들(308)내에 쉽게 발생한다는 문제점이 존재해 왔다.

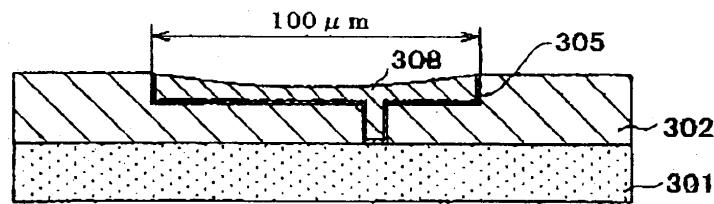

<61> 다이싱은 도 36에 도시된 바와 같이,  $0.18\mu\text{m}$  설계 규칙에서, 예를 들어, 약  $100\mu\text{m}$ 의 폭을 갖는 상호접속부(308)의 경우에, 상호접속부의 중앙부가 과도하게 제거되고 침하하게 되는 현상이다. 다이싱이 발생하는 경우에, 상호접속부(308)의 단면적은 불충분하게 된다. 이는 열악한 상호접속 저항 등을 유발한다. 이 다이싱은 상대적으로 연성인 구리 또는 알루미늄이 상호접속 물질로 사용될 때 발생하기 쉽다.

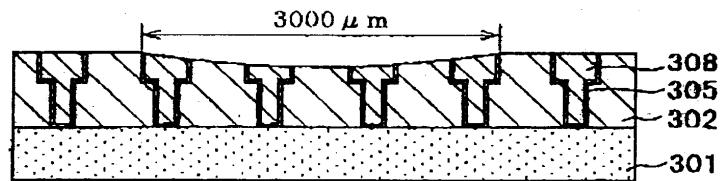

<62> 침식은 도 37에 도시된 바와 같이,  $1.0\mu\text{m}$ 의 폭을 갖는 상호접속부들이, 예를 들어,  $3000\mu\text{m}$ 의 범위로 50%의 밀도에서 형성되는 경우 등의 높은 패턴 밀도를 가진 부분이 과도하게 제거되는 현상이다. 침식이 발생할 때, 상호접속부들의 단면적은 불충분해지게 된다. 이는 열악한 상호접속 저항 등을 유발한다.

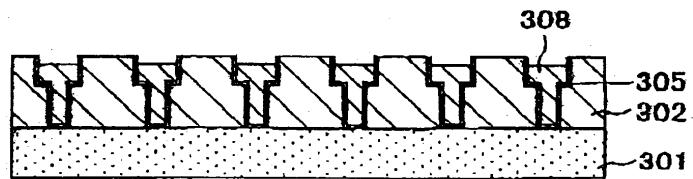

<63> 리세스는 도 38에 도시된 바와 같이, 상호접속부(308)가 층간 절연막(302)과 상호접속부(308) 사이의 경계면에서 높이가 더 낮아져서 단차를 초래하게 되는 현상이다. 이 경우에도 마찬가지로, 상호접속부의 단면적이 불충분하게 되어 열악한 상호접속 저항 등을 초래하게 된다.

<64> 또한, CMP로 잉여 구리막(307)을 평탄화 및 제거하는 단계에서, 구리막을 효과적으로 제거할 필요가 있다. 단위 시간당 제거량, 즉, 연마율은, 예를 들어,  $500\text{nm}/\text{min}$  이상일 필요가 있다.

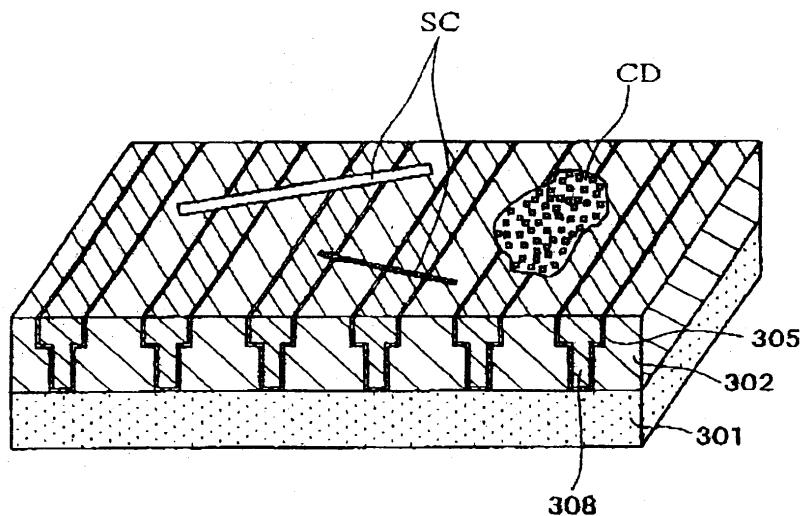

<65> 이 연마율을 얻기 위해서, 웨이퍼상의 연마 압력을 증가시킬 필요가 있다. 연마 압력이 증가될 때, 도 39에 도시된 바와 같이, 스크레치(scratch)(SC)와 화학적 손상(CD)이 상호접속부 표면에 발생하기 쉽다. 특히, 이들은 연성인 구리에서 쉽게 발생된다. 이 때문에, 이들은 상호접속부들의 개구, 단락, 열악한 상호접속 저항 및 다른 결함들을 초래하게 된다. 또한, 연마 압력이 증가되면, 스크레치들, 층간 절연막의 분리, 다이싱, 침식 및 리세스들의 양도 더 커지게 된다.

<66> 본 발명의 제 1 목적은 양호한 잉여 구리막 제거 효율로, 초기 요철을 용이하게 평탄화할 수 있고, 구리 상호접속부들을 갖는 반도체 디바이스 제조 프로세스에서 연마에 의해 구리막을 평탄화할 때 구리막 아래의 층간 절연막에 대한 손상을 억제할 수 있는 연마 방법 및 연마 장치를 제공하는 것이다.

<67> 한편, 상술한 연마 프로세스의 전 프로세스(pre-process)인 구리 매립 전해도금 프로세스에서, 기본적으로, 전체면에 걸쳐 균일한 두께의 막을 형성하는 것은 어렵다. 현재의 상태에서, 막들은 일반적으로 약 3 내지 5%의 두께 변화도로 형성된다. CMP 프로세스는 이 상태로부터 상호접속부들을 형성하도록 수행된다. CMP에 의한 제거량의 균일성이 0%가 되는 경우에도, 전체 표면상의 잉여 구리가 제거될 때까지 CMP가 수행되는 경우에, 도금막 형성의 변화도의 범위로 과연마(over-polishing)가 발생되고, 순차적으로, 동일한 범위로 다이싱, 침식 및 리세스가 불가피해진다. 예를 들어,  $10,000\text{\AA}$ 의 구리막이 깊이가  $5000\text{\AA}$ 인 상호접속부를 형성하도록 도금되는 경우를 가정하면, 두께의 변화도는 3 내지 5%, 즉, 300 내지  $500\text{\AA}$ 이다.  $300$  내지  $500\text{\AA}$ 의 과연마에 의해 유발된 리세스는  $5000\text{\AA}$ 의 상호접속부에 대하여 단면적의 6 내지 10%의 손실에 대응한다. 이는 상호접속부들의 형성 시 무시하기에는 너무 크다.

<68> 따라서, 상술한 문제를 해결하기 위해서, 본 발명의 제 2 목적은 평탄한 구리막을 증착할 수 있고, 반도체 디바이스의 상호접속부를 형성하는 프로세스에 적용될 수 있는 도금 방법 및 도금 장치를 제공하는 것이다.

### 발명의 구성 및 작용

<69> 제 1 목적을 달성하기 위해서, 본 발명의 제 1 양상에 따르면, 연마될 표면상에 막을 갖는 대상물(object)을 연마하기 위한 연마 방법에 있어서, 상기 대상물 상의 상기 막의 두께에 상당하는 데이터를 측정하는 단계, 및 상기 표면에 비해 상대적으로 작은 캐소드 부재를 상기 표면의 영역에 대향시키고, 적어도 상기 캐소드 부재와 상기 표면의 영역 사이에 전해액을 재시키며, 이 상태에서 캐소드로서 기능하는 상기 캐소드 부재와 애노드로서의 상기 막에 전압을 인가하여, 상기 두께에 상당하는 데이터로부터 얻어진 상기 막의 목표량을 제거할 때까지 우선적으로 상기 막의 돌출부들로부터 상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마(electrolytic polishing) 및 평탄화하는 단계를 포함하고, 상기 캐소드 부재를 상기 표면의 다른 영역으로 이동시키고, 상기 막의 목표량이 제거될 때까지 상기 다른 영역에서 상기 막을 전해 연마하여 상기 막을 평탄화하는 단계가 전체 표면에 걸쳐 반복되며, 그로써, 상기 전체 표면에 걸쳐 막의 목표량이 제거되는 연마 방법이 제공된다.

<70> 상기 막은 구리막을 포함하는 것이 바람직하다.

- <71> 본 연마 방법은 상기 두께에 상당하는 데이터 측정 단계 이후, 및 상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계 이전에, 상기 두께에 상당하는 데이터로부터 제거될 상기 막의 양을 산출하는 단계를 더 포함하는 것이 바람직하다.

- <72> 상기 캐소드 부재는 상기 표면의 한 영역으로부터 다른 영역으로 연속적으로 이동되는 것이 바람직하다.

- <73> 상기 캐소드 부재의 이동 속도는 상기 두께에 대응하는 데이터로부터 얻어진 제거될 상기 막의 목표량에 따라 제어되는 것이 더 바람직하다.

- <74> 상기 캐소드 부재는 상기 표면의 한 영역으로부터 다른 영역으로 단계적으로(stepwise) 이동되는 것이 바람직하다.

- <75> 상기 막의 두께에 상당하는 데이터로서, 상기 막의 두께가 측정되는 것이 바람직하다.

- <76> 상기 막의 두께에 상당하는 데이터를 측정하는 단계에서, 상기 캐소드 부재가 상기 표면에 대향하는 영역에서의 상기 막의 두께에 상당하는 데이터가 측정되고, 상기 표면의 다른 영역으로 상기 캐소드 부재를 이동시키고, 상기 다른 영역에서의 상기 막의 두께에 상당하는 데이터를 측정하고, 상기 두께에 상당하는 데이터로부터 얻어진 상기 막의 목표량이 제거될 때까지 상기 다른 영역에서 상기 막의 돌출부로부터 우선적으로 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계가 상기 전체 표면에 걸쳐 반복되는 것이 바람직하다.

- <77> 상기 막의 두께에 상당하는 데이터를 측정하는 단계에서, 상기 막의 두께에 상당하는 데이터로서, 상기 캐소드 부재가 상기 표면에 대향하는 영역에서의 상기 전해 연마의 전류가 측정되고, 상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계에서, 상기 전해 연마의 전류에 의해 결정된 상기 막의 목표량이 제거될 때까지 상기 전해 연마가 수행되는 것이 더 바람직하다.

- <78> 상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계에서, 상기 전해 연마의 전류가 특정 값이 될 때의 시점에서 남아있는 상기 막의 목표량이 0이 되도록 결정되고, 상기 표면의 상기 영역에서의 상기 전해 연마가 종료되는 것이 더 바람직하다.

- <79> 상기 캐소드 부재는 상기 표면의 상기 영역에서의 상기 막의 요철에 대응하는 상기 막의 오목부보다 돌출부에 더 강한 전계를 인가할 수 있도록 성형되는 것이 바람직하다. 상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계에서, 상기 전계를 인가함으로써, 상기 막이 우선적으로 상기 막의 돌출부로부터 상기 표면의 상기 영역에서 전해 용리에 의해 전해 연마 및 평탄화된다.

- <80> 상기 표면은 상기 표면의 상기 영역에서의 돌출 및 오목 패턴을 반복함으로써 형성된 돌출 및 오목 패턴을 갖는 것이 더 바람직하다. 상기 캐소드 부재를 단계적으로 상기 표면의 다른 영역으로 이동시키고, 이를 다른 영역들에서 상기 막의 요철에 대응하는 상기 막의 상기 오목부보다 상기 돌출부에 더 강한 전계를 인가함으로써, 우선적으로 상기 막의 돌출부로부터 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계가 전체 표면에 걸쳐 반복된다.

- <81> 상기 캐소드 부재는 서로 절연된 상태로 배열되어 있는 다수의 영역들로 분할되고, 전체로서의 상기 캐소드 부재가 상기 전체 표면에 대향하는 것이 바람직하다. 상기 분할된 캐소드 부재에 대한 전압 인가 위치를 변화시킴으로써, 상기 표면에 대향하는 상기 캐소드 부재의 위치를 한 영역으로부터 다른 영역으로 변화시킬 때와 실질적으로 대등한 효과가 얻어진다.

- <82> 상기 캐소드 부재는 다수의 동심원 영역들로 분할되고, 상기 전체 표면은 동심원 영역들로 분할된 상기 캐소드 부재의 내측으로부터 외측으로 전압 인가 위치를 변화시킴으로써 전해 연마되는 것이 더 바람직하다.

- <83> 상기 표면에 비해 상대적으로 작은 캐소드 부재를 상기 표면의 상기 영역에 대향하도록 했을 때, 상기 캐소드 부재로부터 특정 거리에 이격 설치된 애노드 부재가 상기 표면에 대향하게 되며, 전해액이 적어도 상기 표면의 상기 영역과 상기 캐소드 부재의 사이 및 상기 표면과 상기 애노드 부재의 사이에 개재되고, 상기 캐소드 부재 및 애노드 부재에 전압이 인가되어 캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 실제로 전압이 인가되는 것이 바람직하다.

- <84> 상기 애노드 부재는 상기 표면상의 물질 보다 귀한 금속을 포함하는 것이 더 바람직하다.

- <85> 상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계에서, 상기 전해 연마와 동시에 화학 기계 연마가 수행되어 상기 전해 연마와 상기 화학 기계 연마를 조합한 복합 연마에 의해 막을 평

탄화하는 것이 바람직하다.

- <86> 캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 전압이 인가될 때, 직류 전압이 인가되는 것이 바람직하다.

- <87> 직각 펄스(rectangular pulse) 전압이 인가되는 것이 더 바람직하다.

- <88> 또한, 애노드 부재가 상기 캐소드 부재로부터 특정 거리 이격되도록 설정되어 상기 표면에 대향하게 되는 경우에, 상기 상기 캐소드 부재와 애노드 부재에 전압이 인가될 때, 교류 전압이 인가되는 것이 바람직하다.

- <89> 상기 표면의 상기 영역에서 전해 용리에 의해 상기 막을 전해 연마 및 평탄화하는 단계에서, 상기 영역에서의 상기 전해 연마의 전해 전류가 동시에 측정되는 것이 바람직하다.

- <90> 캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 인가된 전압은 상기 전해 전류를 일정하게 유지하도록 제어되는 것이 더 바람직하다.

- <91> 또한, 상기 표면의 상기 영역에서의 상기 막의 평탄화의 진행은 상기 전해 전류를 통해 관리되는 것이 더 바람직하다.

- <92> 본 발명의 연마 방법에 따르면, 대상물 상의 막의 두께에 상당하는 데이터가 측정되고, 상기 표면에 비해 상대적으로 작은 캐소드 부재가 상기 표면의 영역에 대향하게 되며, 적어도 상기 표면의 상기 영역과 상기 캐소드 부재 사이에 전해액이 개재되고, 캐소드로서 기능하는 캐소드 부재와 애노드로서의 막에 전압이 인가되고, 상기 막은 두께에 상당하는 데이터로부터 얻어진 막의 목표량이 제거될 때까지, 우선적으로 상기 막의 돌출부들로부터 상기 표면의 상기 영역에서 전해 용리에 의해 전해 연마되어 상기 막을 평탄화시킨다.

- <93> 여기서, 전체 표면에 걸쳐 막의 목표량을 제거하기 위해서, 캐소드 부재를 상기 막의 다른 영역으로 이동시키는 단계와, 상기 막의 목표량이 제거될 때까지 상기 다른 영역들에서 막을 전해 연마 및 평탄화하는 단계가 전체 표면에 걸쳐 반복된다.

- <94> 본 발명의 연마 방법에 따르면, 표면상에 도금된 막의 두께의 변화도를 앞서 측정한 후에 얻어진 조건들 하에서 필요 제거량의 분포를 설정하고, 이에 따라 상호접속부들의 형성을 위해 필요에 따라 상기 막을 연마함으로써 정확한 양만큼 제거하는 것이 가능하다.

- <95> 또한, 표면상에 중첩된 부분 제거량들로 구성된, 전체 표면에 걸친 실제 제거량 분포가 상술한 미리 설정된 제거량 분포와 부합되도록 상기 캐소드 부재를 이동시킴으로써, 상기 막이 상호접속부들의 형성을 위해 필요에 따라 연마에 의해 정확한 양만큼 제거될 수 있다.

- <96> 또한, 상기 표면상의 상기 막은 CMP법과는 달리 전해 용리에 의한 연마에 의해 제거되기 때문에, 더 이상 상기 막 상에 압력을 가할 필요가 없고, 따라서, 상기 막의 균열의 발생 또는 하부 충간 절연막에 대한 손상이 억제될 수 있다.

- <97> 또한, 전해 용리에 의한 연마에 의한 상술한 제거에서, 상기 막의 표면상에 형성된 요철들에서 돌출부들만이 선택적으로 전해 용리되어, 효과적인 평탄화가 달성될 수 있다.

- <98> 상술한 바와 같이, 본 발명의 연마 방법에 따르면, 연마에 의해 막을 평탄화할 때, 초기 요철은 용이하게 평탄화될 수 있고, 잉여 구리막 제거의 양호한 효율을 얻을 수 있으며, 하부 충간 절연막에 대한 손상을 억제할 수 있다.

- <99> 또한, 제 1 목적을 달성하기 위해, 본 발명의 제 2 양상에 따르면, 연마될 표면상에 막을 갖는 대상물을 연마하는 연마 방법에 있어서, 상기 대상물 상의 상기 막의 두께에 상당하는 데이터를 측정하는 단계; 상기 표면에 비해 상대적으로 작은 캐소드 부재를 상기 표면의 영역에 대향시키고, 적어도 상기 캐소드 부재와 상기 표면의 상기 영역 사이에 칼레이트제(chelating agent)를 포함하는 전해액을 개재시키며, 이 상태에서 캐소드로서 기능하는 상기 캐소드 부재와 애노드로서의 상기 막에 전압을 인가하여, 양극 산화에 의해 상기 막의 표면을 산화시키고, 상기 산화된 물질의 칼레이트막을 형성하는 단계; 및 상기 막의 요철에 대응하는 상기 칼레이트막의 돌출부를 선택적으로 제거하여 상기 표면에서 돌출부의 막을 노출시키도록 하는 단계를 포함하고, 상기 표면의 한 영역으로부터 다른 영역으로 상기 캐소드 부재를 이동시키는 단계, 칼레이트막 형성 단계 및 칼레이트막 제거 단계는 전체 표면을 평탄화하기 위해 상기 전체 표면에 걸쳐 두께에 상당하는 데이터로부터 결정된 상기 막의 목표량이 제거될 때까지 반복되는, 연마 방법이 제공된다.

- <100> 상기 막은 구리막을 포함하는 것이 바람직하다.

- <101> 상기 전해액은 계면활성제를 더 포함하는 것이 바람직하다.

- <102> 본 발명의 연마 방법은 상기 두께에 상당하는 데이터를 측정하는 단계 이후 및 상기 표면의 상기 영역에 상기 퀄레이트막을 형성하는 단계 이전에, 상기 두께에 상당하는 데이터로부터 제거될 상기 막의 목표량을 산출하는 단계를 더 포함하는 것이 바람직하다.

- <103> 상기 캐소드 부재는 상기 표면의 한 영역으로부터 다른 영역으로 연속적으로 이동되는 것이 바람직하다.

- <104> 상기 캐소드 부재의 이동 속도는 상기 두께에 상당하는 데이터로부터 얻어진 제거될 상기 막의 목표량에 따라 제어되는 것이 더욱 바람직하다.

- <105> 상기 캐소드 부재는 상기 표면의 한 영역으로부터 다른 영역으로 단계적으로 이동되는 것이 바람직하다.

- <106> 상기 막의 두께에 상당하는 데이터로서, 상기 막의 두께가 측정되는 것이 바람직하다.

- <107> 상기 막의 두께에 상당하는 데이터 측정 단계에서, 상기 캐소드 부재가 상기 표면에 대향하는 영역에서의 상기 막의 두께에 상당하는 데이터가 측정되고, 상기 표면의 다른 영역들로 상기 캐소드 부재를 이동시키는 단계, 상기 다른 영역들에서의 상기 막의 두께에 상당하는 데이터를 측정하는 단계, 상기 퀄레이트막 형성 단계, 및 상기 퀄레이트막 제거 단계는 상기 전체 표면에 걸쳐 반복되는 것이 바람직하다.

- <108> 상기 막의 두께에 상당하는 데이터 측정 단계에서, 상기 막의 두께에 상당하는 데이터로서, 상기 캐소드 부재가 상기 표면에 대향하는 영역에서의 상기 양극 산화의 전해 전류가 측정되고, 상기 양극 산화의 전해 전류 측정 단계, 상기 퀄레이트막 형성 단계, 및 상기 퀄레이트막 제거 단계는 상기 양극 산화의 전해 전류에 의해 결정된 상기 막의 목표량이 제거될 때까지 상기 전체 표면에 걸쳐 반복되는 것이 더 바람직하다.

- <109> 상기 표면의 영역의 상기 양극 산화의 전해 전류를 측정하는 단계, 상기 퀄레이트막 형성 단계, 및 상기 퀄레이트막 제거 단계를 상기 전체 표면에 걸쳐 반복할 때, 상기 양극 산화의 전해 전류가 특정값이 되는 시점에서 남아있는 상기 막의 목표량을 0으로 결정하고, 상기 표면의 상기 영역에서의 상기 퀄레이트막 형성 단계와 상기 퀄레이트막 제거 단계가 종료되는 것이 더 바람직하다.

- <110> 상기 캐소드 부재는 상기 표면의 상기 영역에서의 상기 막의 요철에 대응하는 상기 막의 오목부보다 돌출부에 더 강한 전계를 인가할 수 있도록 성형되는 것이 바람직하다. 상기 표면의 상기 영역에서의 상기 퀄레이트막 형성 단계와 상기 퀄레이트막 제거 단계에서, 상기 전계를 인가함으로써, 우선적으로 상기 막의 돌출부들로부터 상기 퀄레이트막이 형성 및 제거되어 상기 막을 평탄화한다.

- <111> 상기 표면은 상기 표면의 상기 영역에서의 돌출 및 오목 패턴을 반복함으로써 형성된 돌출 및 오목 패턴을 갖는 것이 더 바람직하다. 상기 캐소드 부재를 단계적으로 상기 표면의 다른 영역들로 이동시키고, 상기 다른 영역들에서의 상기 막의 요철에 대응하는 상기 막의 오목부보다 돌출부에 더 강한 전계를 인가함으로써, 상기 막을 퀄레이트화하는 단계와, 상기 형성된 퀄레이트막을 우선적으로 상기 막의 돌출부로부터 제거하여 상기 막을 평탄화하는 단계가 상기 전체 표면에 걸쳐 반복된다.

- <112> 상기 캐소드 부재는 서로 절연된 상태로 배열되는 다수의 영역들로 분할되고, 전체로서의 상기 캐소드 부재가 상기 전체 표면에 대향하는 것이 바람직하다. 상기 분할된 캐소드 부재에 대한 전압 인가 위치를 변화시킴으로써, 상기 표면에 대향하는 상기 캐소드 부재의 위치를 한 영역으로부터 다른 영역으로 변화시킬 때와 실질적으로 대등한 효과가 얻어진다.

- <113> 상기 캐소드 부재는 다수의 동심원 영역들로 분할되고, 동심원 영역들로 분할된 상기 캐소드 부재의 내측으로부터 외측으로 전압 인가 위치를 변화시킴으로써, 상기 막의 전체 표면이 양극 산화 및 퀄레이트화에 의해 산화되는 것이 더 바람직하다.

- <114> 상기 표면에 비해 상대적으로 작은 캐소드 부재를 상기 표면의 상기 영역에 대향하도록 형성했을 때, 상기 캐소드 부재로부터 특정 거리에 이격 설치된 애노드 부재가 상기 표면에 대향하게 되며, 전해액이 적어도 상기 표면의 상기 영역과 상기 캐소드 부재 사이 및 상기 표면과 상기 애노드 부재의 사이에 개재되고, 상기 캐소드 부재와 상기 애노드 부재에 전압이 인가되어 캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 실제로 상기 전압이 인가되는 것이 바람직하다.

- <115> 상기 애노드 부재는 상기 표면상의 물질 보다 귀한 금속을 포함하는 것이 더 바람직하다.

- <116> 상기 표면의 상기 영역에서의 상기 킬레이트막을 제거하는 단계에서, 상기 막의 요철에 대응하는 상기 킬레이트막의 돌출부가 와이핑(wiping)에 의해 선택적으로 제거되는 것이 바람직하다.

- <117> 대안적으로, 상기 표면의 상기 영역에서의 상기 킬레이트막을 제거하는 단계에서, 상기 킬레이트막은 진동을 인가함으로써 제거되는 것이 바람직하다.

- <118> 대안적으로, 상기 표면의 상기 영역에서의 상기 킬레이트막을 제거하는 단계에서, 상기 킬레이트막은 제트(jet)를 인가함으로써 제거되는 것이 바람직하다.

- <119> 캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 전압이 인가될 때, 직류 전압이 인가되는 것이 바람직하다.

- <120> 각각 펄스 전압이 인가되는 것이 더 바람직하다.

- <121> 또한, 상기 캐소드 부재로부터 특정 거리 이격 배치되어 있는 애노드 부재가 상기 표면에 대해 대향하게 되는 경우에, 상기 캐소드 부재와 애노드 부재에 전압이 인가될 때, 교류 전압이 인가되는 것이 바람직하다.

- <122> 상기 표면의 상기 영역에서 상기 양극 산화에 의해 상기 막을 산화시키는 단계에서, 상기 영역에서의 상기 양극 산화의 전해 전류가 동시에 측정되는 것이 더 바람직하다.

- <123> 캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 인가된 상기 전압이 상기 전해 전류를 일정하게 유지하도록 제어되는 것이 더 바람직하다.

- <124> 상기 표면의 상기 영역에서의 상기 막의 평탄화의 진행은 상기 전해 전류를 통해 관리되는 것이 더 바람직하다.

- <125> 상술한 본 발명의 도금 방법에 따르면, 대상물 상의 막의 두께에 상당하는 데이터가 측정되고, 상기 표면에 비해 상대적으로 작은 캐소드 부재가 상기 표면의 영역에 대향하게 되며, 적어도 상기 표면의 상기 영역과 상기 캐소드 부재 사이에 킬레이트제를 포함하는 전해액이 개재되며, 상기 막의 표면이 양극 산화에 의해 산화되고, 캐소드로서 기능하는 캐소드 부재와 애노드로서의 막에 전압을 인가함으로써 산화된 물질의 킬레이트막이 형성된다. 또한, 상기 킬레이트막의 돌출부들은 그 표면에서 돌출부의 상기 막을 노출시키기 위해 상기 막의 요철에 대응하여 선택적으로 제거된다.

- <126> 여기서, 상기 표면의 한 영역으로부터 다른 영역으로 상기 캐소드 부재를 이동시키는 단계, 킬레이트막 형성 단계, 킬레이트막 제거 단계는 상기 전체 표면에 걸친 두께에 상당하는 데이터로부터 결정된 막의 목표량이 제거될 때까지 반복되어 전체 표면이 평탄화된다.

- <127> 상술한 본 발명의 연마 방법에 따르면, 상기 표면상의 막상에 형성된 요철면이 상기 표면의 영역에서 양극 산화에 의해 부분적으로 산화되고, 처리액(processing solution)으로서 공급된 킬레이트제와 반응하여 킬레이트화된다. 따라서, 용이하게 제거될 수 있는 낮은 기계적 강도를 가진 킬레이트막이 형성된다. 킬레이트막의 돌출부를 제거하는 경우에, 더 노출된 구리가 양극 산화에 의해 산화된 이후 킬레이트화되기 때문에, 상기 킬레이트막의 돌출부를 제거하는 단계를 반복함으로써 상기 막의 평탄성이 달성될 수 있다.

- <128> 또한, 처리액에 계면활성제가 첨가되는 경우에, 요철면상의 킬레이트막은 미셀화되어(micelled) 복합 미셀을 형성하고, 또한, 이는 선택적으로 돌출부로부터 용이하게 제거될 수 있다.

- <129> 상기 캐소드 부재의 전기적 작용이 연장되는 범위내에서, 상기 킬레이트막의 전기 저항이 구리보다 크기 때문에, 상기 홈 내에 남아있는 제거되지 않은 킬레이트막으로 피복된 구리는 도통에 의한 양극 산화에 의해 산화되기 어렵고, 따라서, 이 영역의 킬레이트화는 매우 느리며, 앞선 킬레이트막의 제거에 의해 노출된 구리막의 돌출부에서만 양극 산화에 의해 킬레이트막이 형성된다.

- <130> 또한, 상기 전류는 전해액을 통해 공급되기 때문에, 상기 캐소드의 캐소드 부재와 애노드 상의 막 사이의 전위차가 일정한 경우에, 전극들 사이의 거리가 짧을수록 전류 밀도는 더 커지게 된다. 따라서, 킬레이트막의 제거 이후에 노출된 막에서, 상기 막의 보다 많이 돌출하는 부분은 캐소드로서 사용된 캐소드 부재에 대한 전극 거리가 더 짧고, 따라서, 보다 높은 전류 밀도를 갖게되며, 결과적으로, 양극 산화 속도가 더 높고, 킬레이트화가 더 빠르다.

- <131> 또한, 상기 요철면상에 형성된 킬레이트막의 체적이 원래 구리 보다 크기 때문에, 요철면상의 단자는 원래 구리의 표면상의 단자에 비해 더 커지게 된다. 따라서, 돌출부에 의해 수신되는 와이핑 등으로 인한 기계적 제거 에너지는 크다.

- <132> 따라서, 캐소드 부재의 전기적 작용이 연장하는 범위 내에서, 막의 돌출부들은 선택적으로 제거될 수 있고, 효과적으로 평탄화될 수 있다.

- <133> 또한, 표면상에 도금된 막의 두께의 변화도를 이전에 측정함으로써 얻어진 조건들에 의해 필요한 제거량의 분포를 설정하는 것이 가능하고, 이에 따라, 상호접속부들의 형성을 위해 필요에 따라 연마에 의해 정확한 양만큼 막을 제거할 수 있다.

- <134> 또한, 표면상에 중첩된 부분적 제거량들로 구성된 전체 표면에 걸친 제거량들의 실제 분포를 사전 설정된 제거량 분포와 일치시키도록 상기 캐소드 부재를 이동시킴으로써, 상호접속부들의 형성을 위해 필요에 따라 연마에 의해 전체 표면에 걸쳐 정확한 양만큼 막을 제거할 수 있다.

- <135> 또한, 상기 표면상의 막이 CMP법과는 달리 양극 산화, 킬레이트화 및 킬레이트막의 제거에 의한 연마에 의해 제거되기 때문에, 상기 막상에 압력을 가할 필요가 없고, 따라서, 막의 크랙들(cracks)의 발생이나 하부 충간 절연막에 대한 손상이 억제될 수 있다.

- <136> 상술한 바와 같이, 본 발명의 연마 방법에 따르면, 연마에 의해 막이 평탄화될 때, 초기 요철들은 용이하게 평탄화될 수 있고, 잉여 구리막의 양호한 제거 효율을 얻을 수 있으며, 하부 충간 절연막에 대한 손상이 억제될 수 있다.

- <137> 또한, 제 1 목적을 달성하기 위해, 본 발명의 제 3 양상에 따르면, 연마될 표면상에 막을 갖는 대상물을 연마하는 연마 장치에 있어서, 상기 대상물을 유지하기 위한 테이블, 상기 대상물 상의 상기 막의 두께에 상당하는 데이터를 측정하는 측정 수단, 상기 표면의 영역에 대향하도록 배열된, 상기 표면에 비해 상대적으로 작은 캐소드 부재, 적어도 상기 캐소드 부재와 상기 표면의 상기 영역 사이에 전해액을 공급하는 전해액 공급 수단, 캐소드로서 기능하는 상기 캐소드 부재와 애노드로서 기능하는 상기 막에 전압을 인가하는 전원, 상기 막이 상기 표면의 상기 영역에서 전해 용리에 의해 전해 연마될 때, 두께에 상당하는 데이터로부터 얻어진 막의 목표량이 제거될 때까지 전압 인가를 제어하는 제어 수단, 및 상기 전체 표면에 걸쳐 막의 목표량을 제거하기 위해 상기 표면의 다른 영역들로 상기 캐소드 부재를 이동시키는 이동 수단을 포함하는, 연마 장치가 제공된다.

- <138> 상기 막은 구리막을 포함하는 것이 바람직하다.

- <139> 본 발명의 연마 장치는 상기 두께에 상당하는 데이터로부터 제거될 상기 막의 목표량을 산출하는 연산 유닛을 더 포함하는 것이 바람직하다.

- <140> 상기 측정 수단은 상기 막의 두께를 측정하는 것이 바람직하다.

- <141> 상기 측정 수단은 상기 캐소드 부재가 상기 표면에 대향하는 영역에서의 상기 전해 연마의 전류를 측정하고, 상기 제어 수단은 상기 표면의 상기 영역에서 상기 전해 연마의 전류에 의해 결정되는 막의 목표량이 제거될 때까지 인가될 전압을 제어하는 것이 바람직하다.

- <142> 상기 제어 수단은 상기 전해 연마의 전류가 특정값이 되는 시점에 남아있는 상기 막의 목표량을 0으로 결정하고, 상기 표면의 상기 영역에서의 전해 연마가 종료되도록 제어하는 것이 더 바람직하다.

- <143> 상기 캐소드 부재는 상기 표면의 상기 영역에서의 상기 막의 요철에 대응하는 상기 막의 오목부보다 돌출부에 더 강한 전계를 인가할 수 있도록 성형되는 것이 바람직하다. 상기 전계를 인가함으로써, 상기 막이 우선적으로 상기 막의 돌출부로부터 상기 표면의 상기 영역에서 전해 용리에 의해 전해 연마 및 평탄화된다.

- <144> 상기 캐소드 부재는 서로 절연되어 배열되는 다수의 영역들로 분할되고, 전체로서 상기 캐소드 부재는 전체 표면에 대향하는 것이 바람직하다. 상기 분할된 캐소드 부재에 대한 전압 인가 위치를 변화시킴으로써, 상기 표면에 대향하는 상기 캐소드 부재의 위치를 한 영역으로부터 다른 영역으로 변화시킬 때와 실질적으로 동일한 효과가 얻어진다.

- <145> 상기 캐소드 부재는 다수의 동심원 영역들로 분할되는 것이 더 바람직하다.

- <146> 본 발명의 연마 장치는 상기 표면에 대향하며 상기 캐소드 부재로부터 특정 거리 이격 배치되어 있는 애노드 부재를 더 포함하고, 상기 전해액 공급 수단은 상기 표면의 상기 영역과 상기 캐소드 부재 사이 및 상기 표면과 상기 애노드 부재 사이에 전해액을 공급하고, 상기 전원은 상기 캐소드 부재 및 상기 애노드 부재에 전압을 인가하는 것이 바람직하다.

- <147> 상기 애노드 부재는 상기 표면상의 물질 보다 귀한 금속을 포함하는 것이 더 바람직하다.

- <148> 본 발명의 연마 장치는 화학 기계 연마를 위한 연마 수단을 더 포함하고, 상기 전해 연마로 상기 막을 평탄화하는 동시에, 상기 막의 상기 영역에서 화학 기계 연마를 수행하는 것이 바람직하다.

- <149> 상기 전원은 캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 직류 전압을 인가하는 것이 바람직하다.

- <150> 상기 전원은 직각 펠스 전압을 인가하는 것이 더 바람직하다.

- <151> 또한, 상기 캐소드 부재로부터 특정 거리에 이격 배치되어 있는 애노드 부재가 상기 표면에 대향하게 되는 경우에, 상기 전원은 상기 캐소드 부재와 상기 애노드 부재에 교류 전압을 인가하는 것이 바람직하다.

- <152> 본 발명의 연마 장치는 상기 영역에서의 상기 전해 연마의 전류를 측정하기 위한 전류계를 더 포함하는 것이 바람직하다.

- <153> 상기 제어 수단은 상기 전해 전류가 일정하게 유지되도록 상기 표면과 상기 캐소드 부재에 인가되는 전압을 제어하는 것이 더 바람직하다.

- <154> 본 발명의 상기 연마 장치에 따르면, 본 발명의 연마 방법에 의해 상기 표면상의 막이 연마될 수 있다. 연마에 의해 막을 평탄화할 때, 초기 요철이 용이하게 평탄화되고, 잉여 구리막의 양호한 제거 효율이 얻어지며, 하부 충간 절연막에 대한 손상이 억제될 수 있다.

- <155> 또한, 상기 목적을 달성하기 위해, 본 발명의 제 4 양상에 따르면, 연마될 표면상에 막을 갖는 대상물을 연마하는 연마 장치에 있어서, 상기 대상물을 유지하는 테이블, 상기 대상물 상의 막의 두께에 상당하는 데이터를 측정하는 측정 수단, 상기 표면의 영역에 대향하도록 배열된, 상기 표면에 비해 상대적으로 작은 캐소드 부재, 킬레이트체를 포함하는 전해액을 적어도 상기 표면의 상기 영역과 상기 캐소드 부재 사이에 공급하는 전해액 공급 수단, 캐소드로서 기능하는 상기 캐소드 부재와 애노드로서의 상기 막에 전압을 인가하는 전원, 상기 막의 표면이 상기 표면의 상기 영역에서 양극 산화에 의해 산화되고, 상기 산화된 물질의 킬레이트막이 형성될 때까지 전압 인가를 제어하는 제어 수단, 상기 킬레이트막을 제거하는 킬레이트막 제거 수단, 및 전체 표면에 걸쳐 두께에 상당하는 데이터로부터 얻어진 상기 막의 목표량을 제거하기 위해 상기 표면의 다른 영역들로 상기 캐소드 부재를 이동시키는 이동 수단을 포함하는, 연마 장치가 제공된다.

- <156> 상기 막은 구리막을 포함하는 것이 바람직하다.

- <157> 상기 킬레이트막 제거 수단은 상기 막의 요철에 대응하는 상기 킬레이트막의 돌출부를 선택적으로 제거하는 것이 바람직하다.

- <158> 상기 전해액 공급 수단은 전해액으로서 계면활성제를 더 포함하는 전해액을 공급하는 것이 바람직하다.

- <159> 본 발명의 연마 장치는 상기 두께에 상당하는 데이터로부터 제거될 상기 막의 목표량을 산출하기 위한 연산 유닛을 더 포함하는 것이 바람직하다.

- <160> 상기 측정 수단은 상기 막의 두께를 측정하는 것이 바람직하다.

- <161> 대안적으로, 상기 측정 수단은 상기 캐소드 부재가 상기 표면에 대향하는 영역에서 양극 산화의 전해 전류를 측정하고, 상기 제어 수단은 상기 표면의 상기 영역에서 상기 양극 산화의 전해 전류에 의해 결정된 막의 목표량을 제거할 때까지 인가될 상기 전압을 제어한다.

- <162> 상기 제어 수단은 상기 양극 산화의 전해 전류가 특정값이 되는 시점에서 남아있는 상기 막의 목표량을 0으로 결정하고, 상기 표면의 상기 영역에서의 상기 양극 산화를 종료하도록 제어하는 것이 더 바람직하다.

- <163> 상기 캐소드 부재는 상기 표면의 상기 영역에서의 상기 막의 요철에 대응하는 상기 막의 오목부보다 돌출부에 더 강한 전계를 인가할 수 있도록 성형되는 것이 바람직하다. 상기 전계를 인가함으로써, 상기 막은 우선적으로 상기 막의 돌출부로부터 상기 표면의 상기 영역에서 양극 산화에 의해 산화되고 킬레이트화되어 상기 막을 평탄화한다.

- <164> 상기 캐소드 부재는 서로 절연되어 배열된 다수의 영역들로 분할되고, 전체로서의 상기 캐소드 부재는 상기 전체 표면에 대향하는 것이 바람직하다. 상기 분할된 캐소드 부재에 대한 전압 인가 위치를 변화시킴으로써, 상기 표면에 대향하는 상기 캐소드 부재의 위치를 한 영역으로부터 다른 영역으로 이동시킬 때와 실질적으로 동일한 효과가 얻어진다.

- <165> 상기 캐소드 부재는 다수의 동심원 영역들로 분할되는 것이 더 바람직하다.

- <166> 본 발명의 연마 장치는 상기 표면에 대향하고 상기 캐소드 부재로부터 특정 거리 이격 배치되어 있는 애노드 부재를 포함하고, 상기 전해액 공급 수단은 상기 표면의 상기 영역과 상기 캐소드 부재 사이 및 상기 표면과 상기 애노드 부재 사이에 전해액을 공급하며, 상기 전원은 상기 캐소드 부재 및 애노드 부재에 전압을 인가하는 것이 바람직하다.

- <167> 상기 애노드 부재는 상기 표면상의 물질 보다 귀한 금속을 포함하는 것이 더 바람직하다.

- <168> 본 발명의 연마 장치는 상기 킬레이트막 제거 수단으로서 상기 막의 요철에 대응하는 상기 킬레이트막의 돌출부를 선택적으로 제거하는 와이핑 수단을 포함하는 것이 바람직하다.

- <169> 대안적으로, 상기 킬레이트막 제거 수단은 진동 인가 수단을 포함하는 것이 바람직하다.

- <170> 대안적으로, 상기 킬레이트막 제거 수단은 제트를 발생시키는 수단과, 상기 킬레이트막에 상기 제트를 인가하는 인가 수단을 포함하는 것이 바람직하다.

- <171> 상기 전원은 캐소드로서의 상기 캐소드 부재와 애노드로서의 상기 표면에 직류 전압을 인가하는 것이 바람직하다.

- <172> 상기 전원은 직각 펄스 전압을 인가하는 것이 보다 바람직하다.

- <173> 또한, 상기 캐소드 부재로부터 특정 거리에 이격 배치된 애노드 부재가 상기 표면에 대향하게 되는 경우에, 상기 전원은 상기 캐소드 부재와 상기 애노드 부재에 교류 전압을 인가하는 것이 바람직하다.

- <174> 본 발명의 연마 장치는 상기 영역에서의 상기 양극 산화의 전해 전류를 측정하는 전류계를 더 포함하는 것이 바람직하다.

- <175> 상기 제어 수단은 상기 전해 전류를 일정하게 유지하기 위해 상기 표면과 상기 캐소드 부재에 인가되는 전압을 제어하는 것이 더 바람직하다.

- <176> 본 발명의 상기 연마 장치에 따르면, 표면상의 상기 막은 본 발명의 연마 방법에 의해 처리될 수 있다. 연마에 의해 막이 평탄화될 때, 초기 요철은 용이하게 평탄화될 수 있고, 잉여 구리막의 양호한 제거 효율을 얻을 수 있으며, 하부 충간 절연막에 대한 손상이 억제될 수 있다.

- <177> 상기 제 2 목적을 달성하기 위해서, 본 발명의 제 5 양상에 따르면, 대상물의 표면상에 도금막을 증착하는 도금 방법에 있어서, 상기 대상물을 상의 상기 도금막의 두께 데이터 또는 표면의 표면 높이 데이터를 측정하는 단계, 및 상기 표면에 비해 상대적으로 작은 애노드 부재를 상기 표면의 영역에 대향시키고, 적어도 상기 표면의 상기 영역과 상기 애노드 부재 사이에 전해 도금액을 개재시키면서, 애노드로서 기능하는 상기 애노드 부재와 캐소드로서의 상기 표면에 전압을 인가하고, 상기 측정 시간에 상기 도금막의 상기 두께 데이터 또는 상기 표면 높이 데이터로부터 유도된 상기 도금막의 목표량이 증착될 때까지 상기 표면의 상기 영역에 도금에 의해 상기 도금막을 증착하는 단계를 포함하고; 상기 애노드 부재를 상기 표면의 다른 영역으로 이동시키고, 상기 다른 영역에서 도금에 의한 도금막 증착을 전체 표면에 걸쳐 반복하는, 도금 방법이 제공된다.

- <178> 상기 도금막은 구리막을 포함하는 것이 바람직하다.

- <179> 본 발명의 도금 방법에 따르면, 도금될 표면의 표면 높이를 미리 측정함으로써, 또는, 도금 동안 도금 두께 데이터를 측정함으로써 얻어진 조건들하에서 필요 증착량의 분포를 설정하는 것이 가능하고, 이에 따라 필요한 도금막을 정확한 양만큼 형성하는 것이 가능하다.

- <180> 또한, 상기 표면상에 중첩된 부분적 증착량들로 구성된 전체 표면에 걸친 증착량들의 실제 분포가 사전에 설정된 증착량들의 분포와 일치되도록 상기 애노드 부재를 이동시킴으로써, 도금막은 전체 표면에 걸쳐 정확한 양만큼 형성될 수 있다.

- <181> 상술한 바와 같이, 반도체 디바이스의 상호접속부들의 형성 프로세스에서, 평탄한 도금막이 증착될 수 있다.

- <182> 또한, 제 2 목적을 달성하기 위해, 본 발명의 제 6 양상에 따르면, 대상물의 표면상에 도금막을 증착하는 도금 장치에 있어서, 상기 대상물을 유지하는 테이블, 상기 대상물을 상의 상기 도금막의 두께 데이터 또는 표면의 표면 높이 데이터를 측정하는 측정 수단, 상기 표면의 영역에 대향하도록 배열된, 상기 표면에 비해 상대적으로 작은 애노드 부재, 적어도 상기 표면의 상기 영역과 상기 애노드 부재 사이에 전해 도금액을 공급하는 전해 도

금액 공급 수단, 애노드로서 기능하는 상기 애노드 부재와 캐소드로서의 상기 표면에 전압을 인가하는 전원, 상기 표면의 상기 영역에서의 측정시에 상기 도금 두께 데이터 또는 상기 표면 높이 데이터로부터 유도된 상기 도금막의 목표량이 도금에 의해 형성될 때까지 전압의 인가를 제어하는 제어 수단, 및 상기 애노드 부재를 상기 표면의 다른 영역으로 이동시키는 이동 수단을 포함하는, 도금 장치가 제공된다.

<183> 상기 도금막은 구리막을 포함하는 것이 바람직하다.

<184> 본 발명의 도금 장치에 따르면, 미리 도금될 표면의 표면 높이를 측정하거나, 도금 동안 도금 두께 데이터를 측정함으로써 얻어진 조건들하에 필요한 증착량의 분포를 설정하는 것이 가능하고, 이에 따라, 필요한 도금막을 정확한 양만큼 형성하는 것이 가능하다.

<185> 또한, 상기 표면상에 중첩된 부분 증착량들로 구성된 전체 표면에 걸친 증착량의 실제 분포가 상기 사전에 설정된 증착량의 분포와 일치되도록 상기 애노드 부재를 이동시킴으로써, 전체 표면에 걸쳐 정확한 양만큼 도금막을 형성하는 것이 가능하다.

<186> 상술한 바와 같이, 반도체 디바이스의 상호접속부 형성 프로세스에서, 평탄한 도금막을 증착할 수 있다.

<187> 첨부된 도면들을 참조로 주어진 양호한 실시예들에 대한 하기의 상세한 설명으로부터 본 발명의 상술한 목적들 및 특징들을 보다 명확하게 알 수 있을 것이다.

<188> 하기에, 첨부된 도면을 참조로 본 발명의 연마 방법, 연마 장치, 도금 방법 및 도금 장치를 설명한다.

#### 제 1 실시예

<190> 구리 상호접속부들을 가진 반도체 디바이스내에, 이중 다마센 프로세스에 의해 구리 상호접속부들을 형성하는 프로세스에 본 발명을 적용하는 경우에 대하여 설명한다.

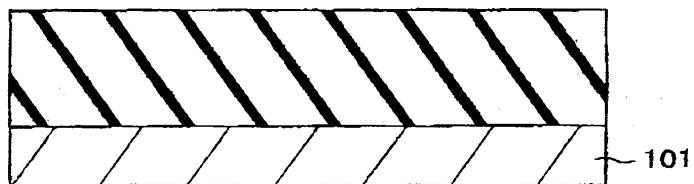

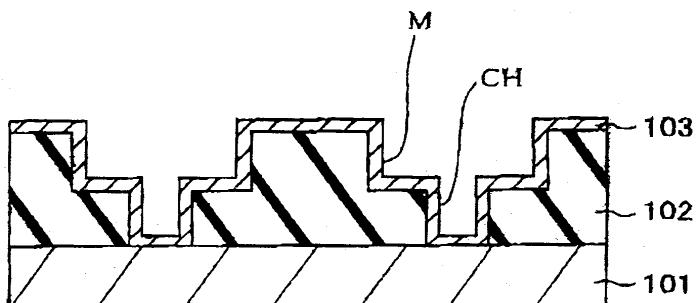

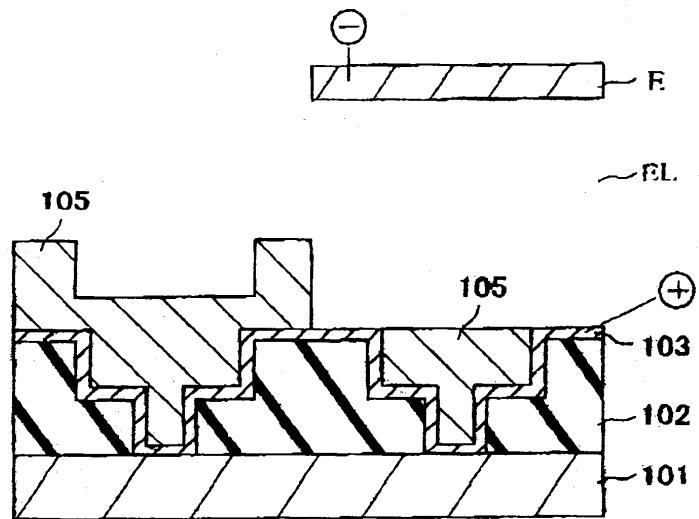

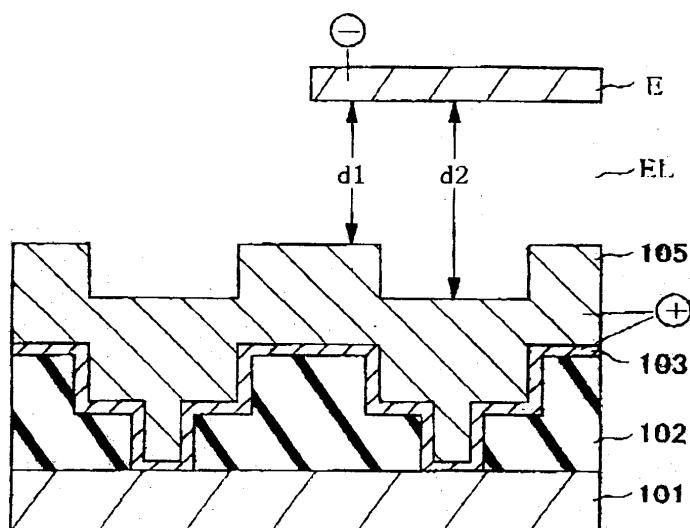

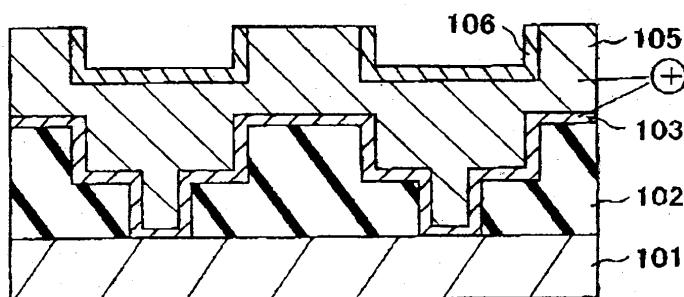

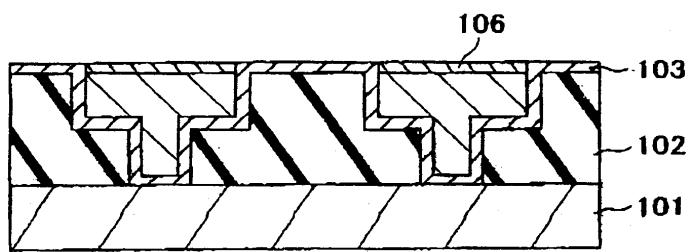

<191> 먼저, 도 1a에 도시된 바와 같이, 예를 들어, 실리콘 산화물( $\text{SiO}_2$ )로 제조된 예를 들어, 충간 절연막(102)이, 저압 화학 기상 증착(CVD)에 의해 실리콘 또는 다른 반도체 기판(101)상에 형성되고, 상기 반도체 기판상에는 도시되지 않은 불순물 확산 영역이, 반응원으로서 예를 들어, 테트라에틸 오르소실리케이트(TEOS, tetraethyl orthosilicate)를 사용하여 적절히 형성되어 있다.

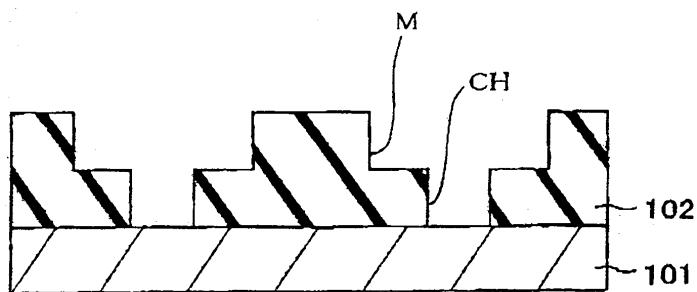

<192> 다음에, 도 1b에 도시된 바와 같이, 반도체 기판(101)의 불순물 확산 영역 및 상호접속 홈들(M)과 소통하는 접촉 홀들(CH)이 공지된 포토리소그래피 및 에칭에 의해 형성된다. 상호접속부 용도의 홈들(M)의 깊이는 예를 들어, 약 800nm이며, 폭은 예를 들어, 약 250nm 내지 100 $\mu\text{m}$ 이다.

<193> 다음에, 도 1c에 도시된 바와 같이, 배리어 금속막(103)이 충간 절연막(102)의 표면상에, 그리고, 접촉 홀들(CH) 및 상호접속 홈들(M)의 내부에 형성된다. 이 배리어 금속막(103)은 스퍼터링 시스템, 진공 기상 증착 시스템 등을 사용하여, 물리 기상 증착(PVD)에 의해 Ta, Ti, W, Co, TaN, TiN, WN, CoW 또는 CoWP 같은 물질로 예를 들어, 약 25nm의 두께로 형성된다.

<194> 상기 배리어 금속막(103)은 상호접속부들을 구성하는 물질이 충간 절연막(102)내로 확산되는 것을 방지하고, 충간 절연막(102)과의 접합성을 향상시키기 위해 제공된다. 특히, 본 실시예에서와 같이, 상호접속 물질이 구리이고, 충간 절연막(102)이 실리콘 산화물인 경우에, 구리가 실리콘 산화물내로의 큰 확산 계수를 갖기 때문에, 이는 쉽게 산화될 수 있다. 이는 반드시 방지되어야만 한다.

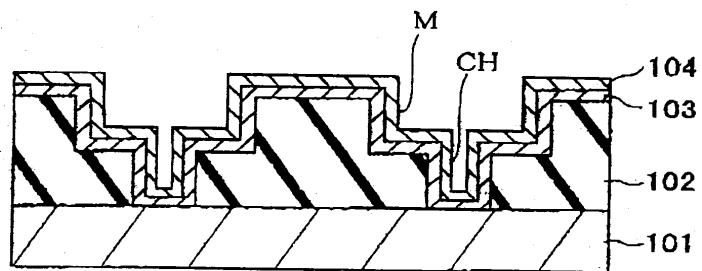

<195> 다음에, 도 2a에 도시된 바와 같이, 구리 상호접속부들을 형성하는 물질과 동일한 물질로 제조된 시드막(104)이 공지된 스퍼터링에 의해, 예를 들어, 약 150nm의 두께로 배리어 금속막(103)상에 형성된다. 이 시드막(104)은 상호 접속 홈들과, 접촉 홀들을 구리로 매립할 때, 구리 입자들의 성장을 가속시키도록 형성된다.

<196> 다음에, 도 2b에 도시된 바와 같이, 구리로 제조된 상호접속층(105)이 접촉 홀들(CH)과 상호접속 홈들(M)을 매립하도록 예를 들어, 약 1200nm 내지 1600nm의 두께로 배리어 금속막상에 형성된다. 이 상호접속층(105)은 전해 도금 또는 무전해 도금에 의해 형성되는 것이 바람직하지만, CVD, PVD, 스퍼터링 등에 의해 상호접속층(105)을 형성하는 것도 가능하다. 시드막(104)은 상호접속층(105)과 일체로 형성된다는 것을 인지하여야 한다.

<197> 접촉 홀들(CH)과 상호접속 구멍들(M)을 매립하는 것에 의해, 상기 상호접속층(105)의 표면상에 예를 들어, 약 800nm의 높이를 가진 요철(unevenness)이 유발된다.

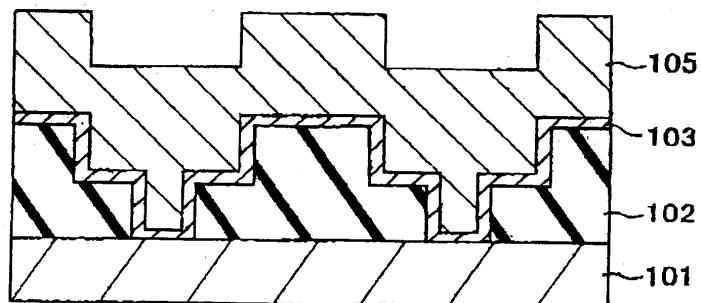

<198> 상술한 프로세스는 종래 기술에서와 동일한 방식으로 수행되지만, 본 발명의 연마 방법에서는, 화학 기계 연마에 의해서가 아니라, 상기 표면 보다 작은 캐소드 부재를 사용하는 전해 용리(electrolytic elution)에 의해,

충간 절연막(102)상에 존재하는 잉여 금속막(102)이 제거되게 된다.

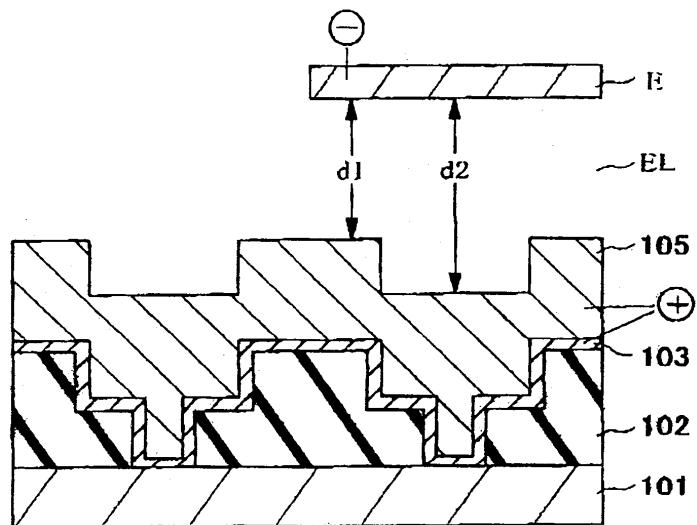

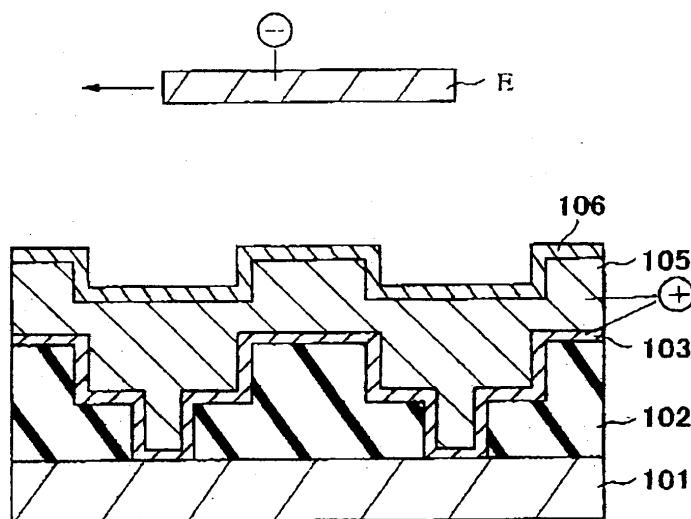

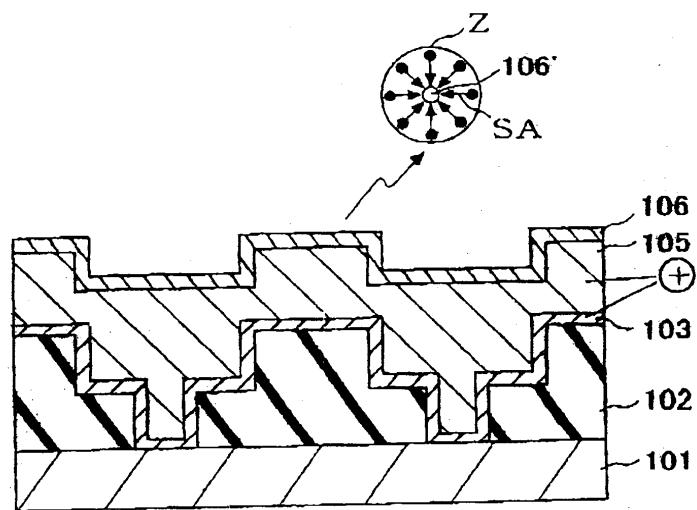

<199> 즉, 도 3a에 도시된 바와 같이, 상호접속층(105)에 비해 상대적으로 작은 캐소드 부재(E)가 표면의 영역, 즉, 상호접속층(105)에 대향하도록 배열되고, 전해액(EL)이 적어도 상기 상호접속층(105)과 캐소드 부재(E) 사이에 개재된다.

<200> 상술한 전해액의 조성으로서, 예를 들어, 인산, 질산, 염화암모니아, 황산, 염화수소산 등이나 이들의 혼합물이 사용될 수 있다.

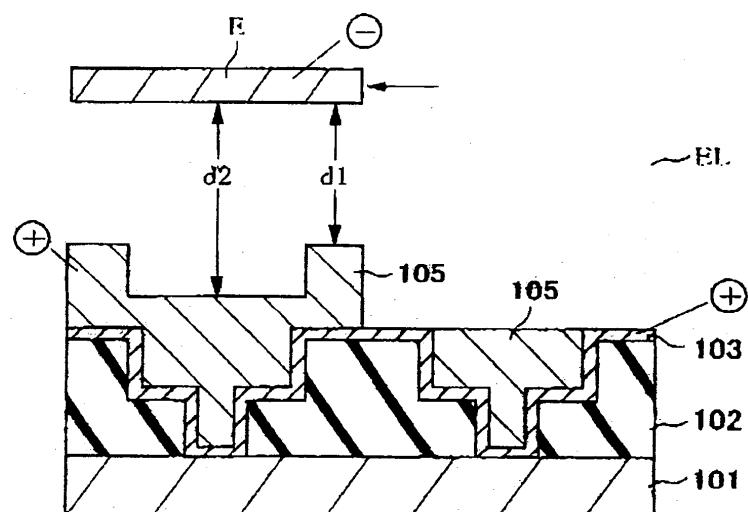

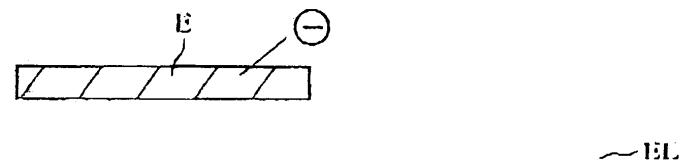

<201> 상술한 상태에서, 도 3b에 도시된 바와 같이, 캐소드로서의 캐소드 부재(E)와, 애노드로서의 상호접속층(105)에 전압이 인가되어, 상호접속층(105)의 상기 영역내의 전해 용리에 의해 상기 상호접속층(105)을 전해 연마(poliish) 및 평탄화(flatten)한다.

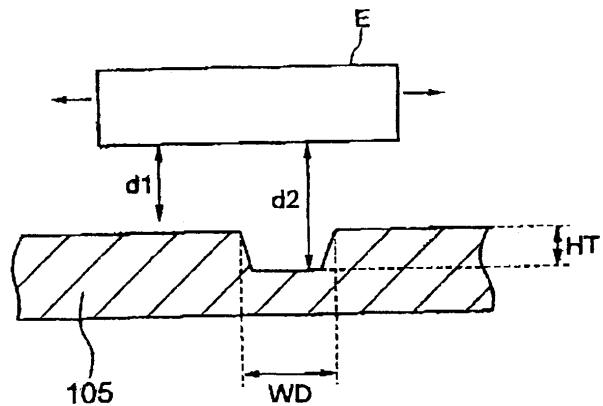

<202> 이때, 전해액을 통해 전류가 인가되기 때문에, 애노드의 상호접속층(105)과 캐소드 부재(E) 사이의 전위차가 일정한 경우에, 전극들 사이의 거리가 짧아질수록 전류 밀도는 커지게 된다. 따라서, 그 표면상에 요철을 가진 상호접속층(105)의 돌출부와 캐소드 부재(E) 사이의 거리(d1)는 상기 상호접속층(105)의 오목부와 캐소드 부재(E) 사이의 거리(d2) 보다 짧고, 따라서, 전류 밀도는 더 높다. 결과적으로, 전해 용리의 속도는 더 높고, 상호접속층(105)의 돌출부가 선택적으로 제 1 전해 연마된다.

<203> 상술한 상호접속층(105)의 영역내의 전해 연마는 상기 상호접속층(105)의 목표량이 제거될 때까지 수행된다. 여기서, 상기 영역내의 상호접속층(105)의 제거의 목표량은 상호접속층(105)에 대하여, 두께 측정기(thick meter)에 의해 측정된 두께 데이터로부터 독립적인 단계에서 먼저 산출되게 된다. 선택적으로, 상술한 전해 연마 단계 동안에 이것이 측정 및 산출될 수 있다. 또한, 전해 연마 단계내의 전해 용리의 전해 전류를 측정하는 것이 가능하고, 상기 상호접속층(105)의 제거의 잔여량에 관련한 양으로서 상기 전해 전류를 사용할 수 있다.

<204> 다음에, 도 4a에 도시된 바와 같이, 캐소드 부재(E)는 전해 연마에 의한 상호접속층(105)의 평탄화 프로세스가 완료된 영역으로부터 다른 영역으로 이동된다. 이 다른 영역에서는 상기 상호접속층(105)이 제거되지 않았기 때문에, 상기 캐소드 부재(E)는 돌출부에 대해서는 거리 d1으로, 오목부에 대해서는 거리 d2로, 요철을 구비한 상호접속층(105)에 대향하게 된다.

<205> 다음에, 도 3b에 도시된 바와 같이, 그 앞의 영역에서의 전해 연마에 의한 상호접속층(105)의 평탄화 프로세스와 유사하게, 도 4b에 도시된 바와 같은 전해 연마에 의해 상호접속층(105)이 상기 다른 영역에서 평탄화 된다.

<206> 또한, 이 단계에서, 상술한 바와 동일하게, 상기 상호접속층(105)은 선택적으로 돌출부들로부터 전해 연마된다. 상술한 바와 유사하게, 상술한 상호 접속층(105)의 나머지 영역에서의 전해 연마가 상기 나머지 영역에서 상호 접속층(105)의 목표량이 제거될 때까지 수행되게 된다.

<207> 후속하는 단계에서, 접촉 훌들 및 상호접속 홈들의 외측에 중착된 배리어 금속막이 제거된다.

<208> 상술한 단계들로 인하여, 반도체 디바이스에 적합한 구리 상호접속부들과 접촉 훌 접속부들이 이중 다마센 프로세스에 의해 동시에 형성된다.

<209> 구리 상호접속부들을 가진 반도체 디바이스에서 이중 다마센 프로세스에 의해 구리 상호접속부들을 형성하는 프로세스에 상기 연마 방법을 적용하는 것에 따라서, 상기 표면상에 도금된 구리막의 두께의 변동을 이전에 측정함으로써 얻어진 조건들하에서 제거 필요량의 분포를 설정하고, 이에 따라서, 상호접속부들의 형성을 위한 필요에 따라 정확한 양만큼 연마에 의해 구리막을 제거하는 것이 가능하다.

<210> 또한, 상기 표면상에 중첩된 부분 제거량을 포함하는 전체 표면에 걸친 제거량의 실제 분포가 상술한 사전설정된 제거량 분포에 부합되도록 캐소드 부재를 이동시킴으로써, 상호접속부들의 형성을 위해 필요에 따라 전체 표면에 걸쳐 연마함으로써 정확한 양만큼 구리막을 제거하는 것이 가능하다.

<211> 또한, 상기표면상의 구리막이 CMP법과는 달리 전해 용리에 의해 연마되어 제거되기 때문에, 더 이상 막상에 압력을 가할 필요가 없고, 따라서, 구리막의 균열들의 발생 또는 하부 충간 절연막에 대한 손상이 억제될 수 있다.

<212> 또한, 상술한 연마 및 전해 용리에 의한 제거에서, 단지 돌출부들만이 상기 구리막의 표면상에 형성된 요철에서 선택적으로 전해 용리되고, 따라서, 효과적인 평탄화가 달성될 수 있다.

<213> 상술한 바와 같이, 본 발명의 연마 방법에 따라서, 연마에 의해 구리막을 평탄화할 때, 최초의 요철은 용이하게

평탄화될 수 있고, 잉여 구리막의 제거에서 양호한 효율을 얻을 수 있으며, 더 낮은 충간 절연막에 대한 손상이 억제될 수 있다.

#### <214> 제 2 실시예

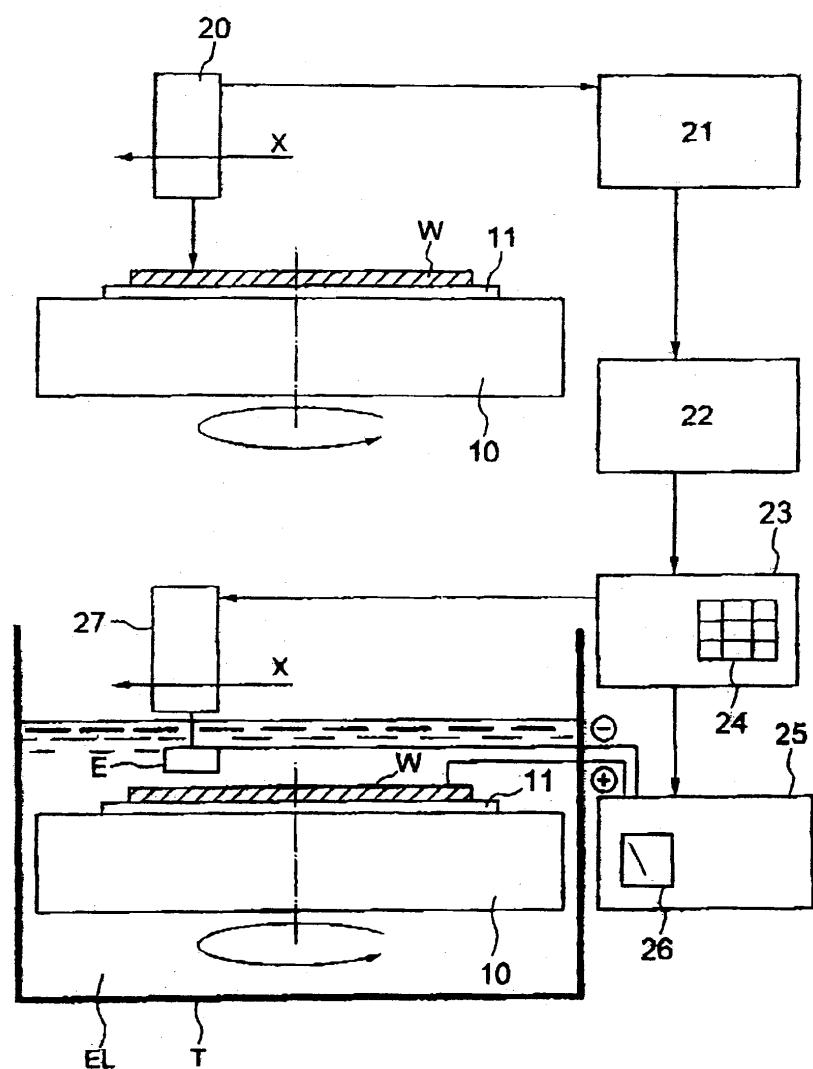

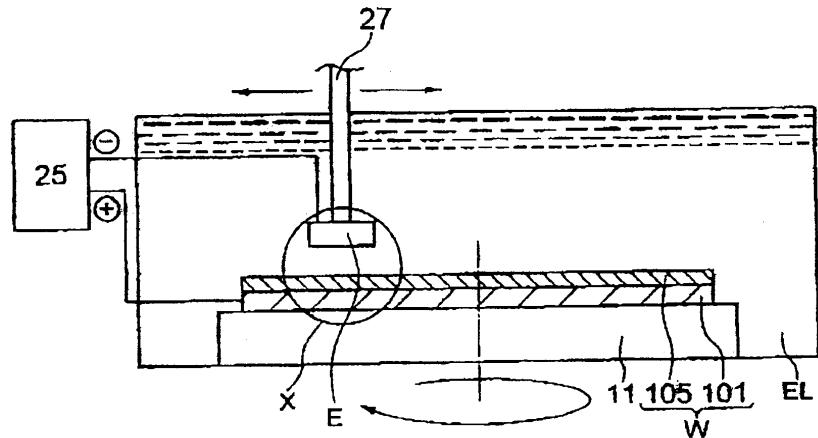

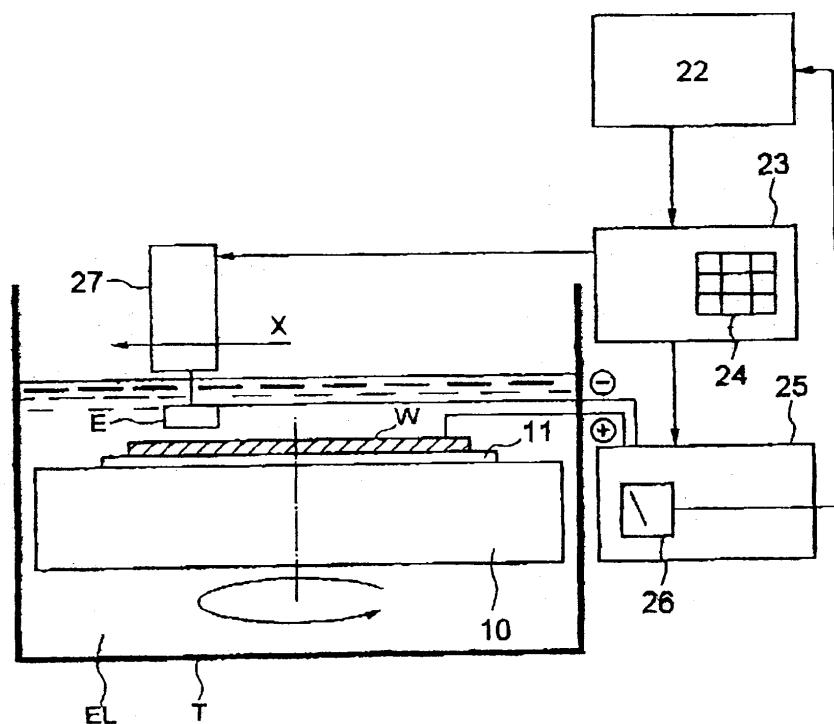

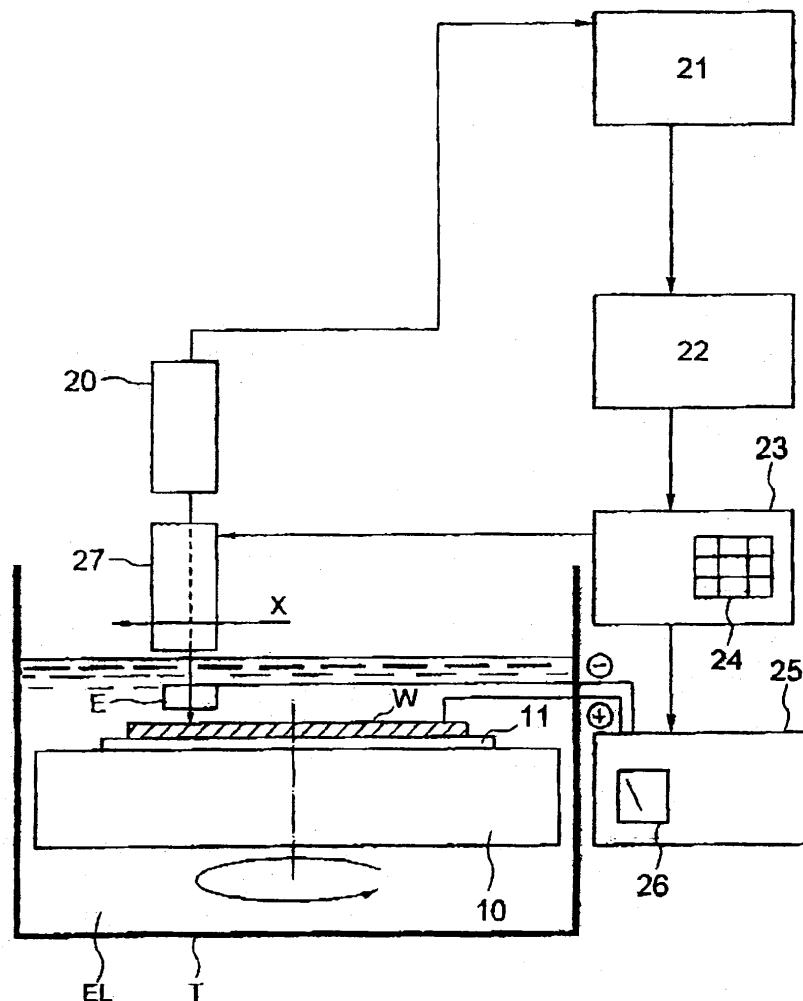

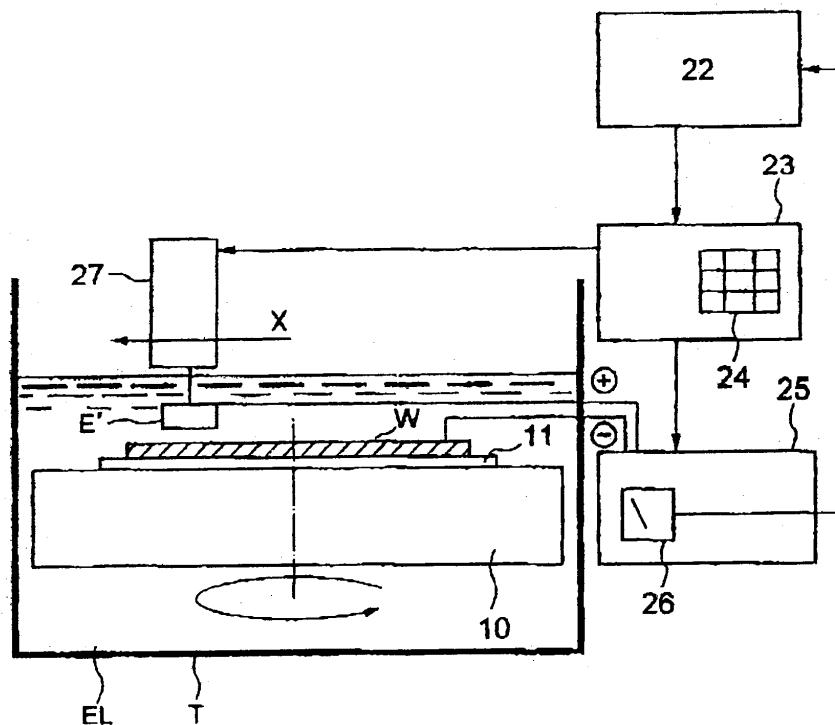

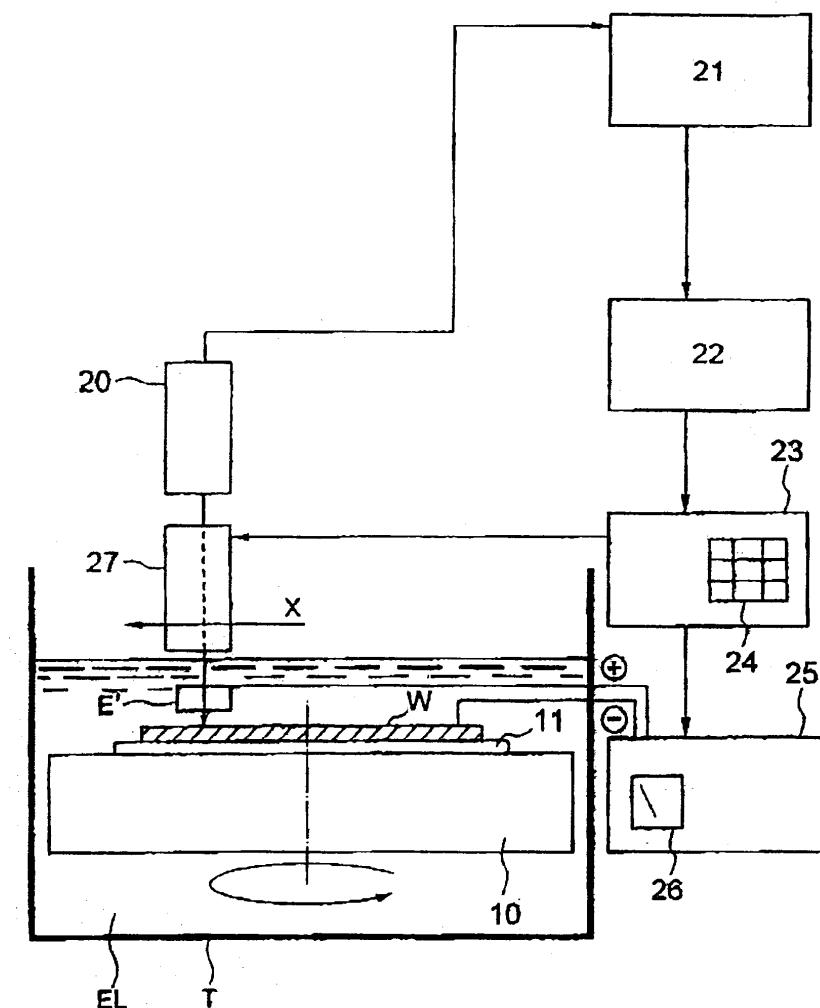

<215> 도 5는 상호접속층의 전해 연마의 상술한 단계에 사용되는 연마 장치의 개략도이다.

<216> 즉, 본 실시예의 연마 장치는 그 표면상에 구리막을 가지는 연마될 웨이퍼(W)(이하, "웨이퍼"라고도 지칭함)를 지지하기 위한 테이블(10)과, 상기 테이블(10)상에 제공된 진공 척(vacuum chuck) 같은 고정 수단(securig means)(11)과, 측정 헤드(20)를 구비한 측정 수단(21)과, 연산 유닛(22)과, 제어기(23)와, 제어 패널(24)과, 전원(25)과, 전류계(226)와, 캐소드 부재(E)와, 상기 캐소드 부재(E)의 이동 기구(27) 및 전해액(EL)을 저장하기 위한 전해조 탱크(electrolytic bath tank)(T)를 포함한다.

<217> 비록, 도면에 예시되지는 않았지만, 상기 연마 장치는 청정실내에 설치되고, 연마될 웨이퍼를 저장한 웨이퍼 카세트를 청정실의 내 또는 외로 로딩 및 언로딩하기 위한 로딩/언로딩 포트가 청정실내에 제공된다. 또한, 이 로딩/언로딩 포트를 통해 청정실내에 로딩된 웨이퍼 카세트와, 상기 연마 장치 사이에 웨이퍼를 전달하기 위한 웨이퍼 운송 로봇이 상기 로딩/언로딩 포트와 연마 장치 사이에 배열된다.

<218> 예를 들어, 웨이퍼(W)는 회전 테이블(10)상의 진공 척 같은 고정 수단(11)에 의해 고정된다. 고정 수단으로서, 진공 척에 부가하여, 에지 클램프(edge clamp) 또는 기계적 클램프(mechanical clamp)를 사용할 수도 있다. 에지 클램프의 경우에, 상기 웨이퍼의 가장자리부를 접지하는 클램프부를 통해 애노드로서 기능하는 웨이퍼에 전류가 공급될 수 있다.

<219> 구리막의 두께, 또는 상기 두께에 상당하는 데이터는 측정 헤드(20)를 구비한 측정 수단(21)에 의해 측정된다. 예를 들어, 4 프로브형 시트 저항 측정기(four-probe type sheet resistance meter)로 시트 저항을 측정하고 이를 공지된 시트 저항을 사용하여 두께로 환산시키는 방법이나, 와전류형 검출기(eddy current type detector) 또는 정전용량형 검출기(electrostatic capacitance type detector)에 의해 두께에 상당하는 데이터를 측정하는 방법을 사용하여, 상기 테이블(10)을 회전시키면서 한 방향(도 5의 X-방향)으로 상기 측정 헤드(20)를 스캔시킴으로써 상기 구리막의 두께가 측정될 수 있다.

<220> 획득된 상기 구리막의 두께에 상당하는 데이터로부터, 상기 연산 유닛(22)은 구리막의 목표 제거량을 산출하고, 이를 제어기(23)로 출력한다.

<221> 상기 제어기(23)는 이 입력으로부터 구리막의 목표 제거량을 설정하고, 이 설정에 따라서, 전원(25)으로부터의 전압과, 캐소드 부재(E)의 이동 기구(27)를 제어한다. 또한, 상기 제어기(23)는 제어 패널(24)로부터의 외부 입력을 수신할 수 있다.

<222> 전해 용리에 의한 전해 연마의 단계에서, 웨이퍼(W)는 테이블(10)과 함께 전해조 탱크(T)내의 전해액(EL)내에 침적(immersed)된다.

<223> 상기 웨이퍼(W)의 표면 보다 상대적으로 작은 캐소드 부재(E)는 상기 표면의 한 영역에 대향하도록 배열된다. 예를 들어, 상기 캐소드 부재(E)는 무산소 구리(oxygen-free copper)로 구성된 200nm 직경을 가진 원판이고, 전해액(EL)내에서 웨이퍼와 평행하게 배열된다.

<224> 상기 웨이퍼의 가장자리에서, 예를 들어, 가장자리로부터 2mm 떨어진 장소들에서 접지된 클램프부를 통한 컨덕턴스에 의해, 직류 전압 또는 펄스 전압이 전원(25)에 의해, 애노드로서의 웨이퍼 표면, 즉, 애노드로서 구리막 및 캐소드로서의 캐소드 부재(E)에 인가된다.

<225> 전원은 항상 정전압을 출력하는 저전압 전원이 아니며, 전압을 특정 사이클에 의한 펄스로 출력하기 위한 내장 스위칭 조절 회로(built-in switching regulator circuit)를 구비한 DC 전원인 것이 바람직하다.

<226> 보다 명확하게, 특정 사이클에 의해 펄스 전압을 출력하는 전원이 사용되며, 적절하게 펄스폭을 변화시킬 수 있다. 예를 들어, 반도체 디바이스의 전압 공차에 따라서, 출력 전압이 100 내지 150V 또는 30V이면서, 그 최대 출력 전류가 2 내지 3A(예를 들어, 2.2A)이고 그 펄스폭이 1, 2, 3, 5, 10, 20 또는 30μs인 전원을 사용할 수 있다.

<227> 상기 펄스 전압의 전압 및 펄스폭은 구리막의 가장 효과적인 제거를 가능하게 하도록 웨이퍼와 캐소드 부재 사이의 거리 및 전해액의 전기 저항에 의해 선택될 수 있다.

- <228> 상술한 바와 같은 짧은 폭을 가진 펠스 전압을 출력하는 것은 펠스당 양극 산화의 양을 매우 작게 한다. 즉, 이는 기포들, 미립자들 등이 개재되어 있을 때 발생하는 전기 저항의 급변화로 인한 스파크 방전 또는 웨이퍼의 표면의 요철과 접촉하는 경우에, 전극들 사이의 거리의 급변화에 의해 유발되는 방전으로 인한, 목표 제거량에 비해 구리막의 급작스럽고 큰 양극 산화를 방지하고, 가능한 작은 양의 연속성을 달성하는데 유효하다.

- <229> 또한, 출력전압이 출력 전류에 비해 상대적으로 높기 때문에, 전극 거리를 설정할 때, 특정 기계적 안전 계수(safety margin)를 설정하는 것이 가능하다. 즉, 전극 거리가 다소 변화되는 경우에도, 출력 전압이 높기 때문에, 전류값의 변화가 작다.

- <230> 이런 전압이 인가되는 경우에, 제 1 실시예에서 설명한 바와 같이, 상기 표면의 한 영역에서 전해 연마가 수행된다.

- <231> 예를 들어, 캐소드 부재(E)는 테이블(10)을 회전시키면서, 이동 기구(27)에 의해 일 방향(도 5의 X-방향)으로 스캔되고, 그래서, 전해 용리에 의해 전체 표면을 전해 연마한다. 캐소드 부재(E)는 이동 기구(27)를 연속적으로 또는 단계적으로 이동시킴으로써 이동될 수 있다.

- <232> 상기 전원에 의해 캐소드 및 애노드에 인가된 전압과, 이동 기구(27)는 구리막의 사전설정된 목표 제거량에 따라 제어기(23)에 의해 제어된다.

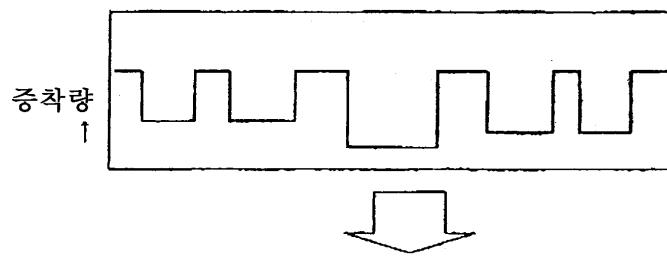

- <233> 예를 들어, 이동 기구(27)가 연속적으로 캐소드 부재(27)를 이동할 때, 캐소드 부재(E)의 이동 속도는 사전 설정된 구리막의 목표 제거량에 따라 제어될 수 있다. 이동 속도가 낮은 영역에서, 상기 캐소드 부재(E)는 보다 긴 시간 동안 표면에 대향하게 되고, 전해 용리의 시간이 길어지며, 보다 많은 양의 구리막이 전해 용리에 의해 전해 연마될 수 있다. 한편, 이동 속도가 높은 영역에서, 캐소드 부재(E)가 표면에 대향하는 시간이 짧아지고, 전해 용리의 시간이 짧아지며, 구리막의 전해 용리의 양이 보다 작아지게된다.

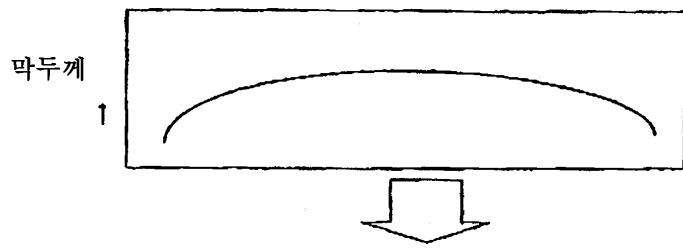

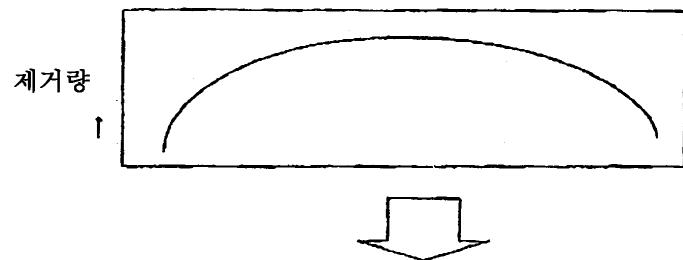

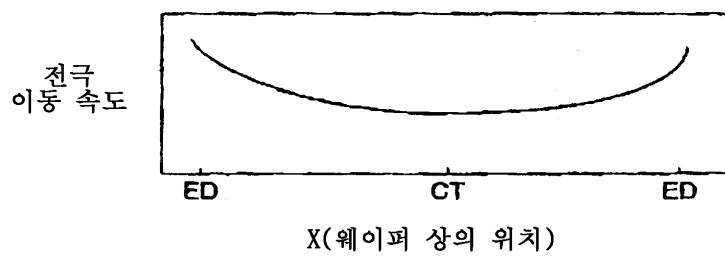

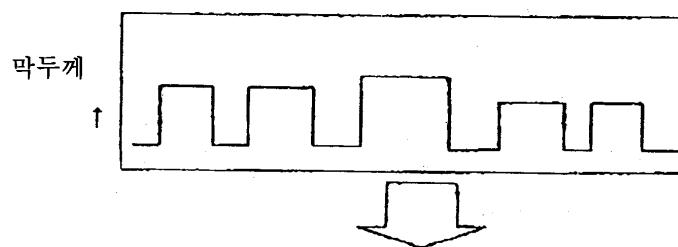

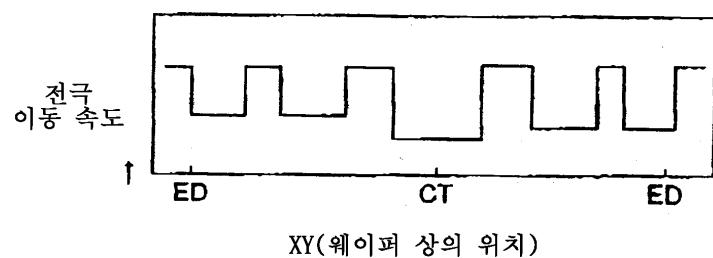

- <234> 예를 들어, 구리막의 측정 결과가 도 6a에 그려진 것일 때, 즉, 막이 주앙부(CT)에서 두껍고, 가장자리부(ED)에서 얇은 두께 프로파일을 갖는 경우에, 상기 구리막의 목표 제거량은 도 6b의 프로파일에 도시된 바와 같이 가장자리 ED에서 작고, 중앙부(CT)에서 커지도록 설정된다. 상기 제어기(23)는 예를 들어, 도 6c에 도시된 바와 같이 목표 제거량의 프로파일이 중앙부(CT)에서 빠르게 이동하고, 가장자리(ED)에서 느리게 이동하는 것을 만족시키도록, 상기 캐소드 부재(E)의 이동 속도를 제어한다.

- <235> 또한, 전류계(26)에 의해 전해 용리의 전류를 모니터링하는 것이 가능하고, 예를 들어, 제어기가 상기 전류가 일정하도록 전압을 제어하게하는 것을 가능하게 한다.

- <236> 도 5에 도시된 연마 장치가 전해 용리를 수행하는 전해조 탱크의 내측을 세부적으로 설명하기 위한 도면이고, 도 7b는 도 7a의 X 부분의 확대도이다.

- <237> 연마될 표면으로서 상호접속층(105)이 형성되어 있는 기판(101)으로 이루어진 웨이퍼(W)는 진공 척 같은 고정 수단에 의해 고정되어 있고, 구동되어 회전한다. 캐소드 부재(E)는 웨이퍼(W)의 한 영역에서 표면과 평행하도록 배열되어 있다. 구리의 전해 용리를 위한 전해액(EL)이 상기 상호접속층(105)과 캐소드 부재(E) 사이에 개재된다.

- <238> 여기서, 상기 구리의 전해 용리를 위한 전해액으로서, 예를 들어, 인산, 질산, 염화암모니아, 황산, 염화수소산 등이나 이들의 혼합물이 사용될 수 있다.

- <239> 도시되지 않은 구동 기구가 상기 웨이퍼(W)를 회전시키면서, 전원(25)은 캐소드로서의 캐소드 부재(E)와, 애노드로서의 배리어 금속막(도시되지 않음) 및 상호접속층(105)에 전압을 공급한다. 이동 기구(27)는 특정 방향으로 캐소드 부재(E)를 이동시킨다.

- <240> 여기서, 도 7b에 도시된 바와 같이, 극미하게 전해적으로 동작되는 범위내의 상호접속층(105)의 표면상의 돌출부와 캐소드 부재(E) 사이의 거리(d1)는 상호접속층(105)의 표면상의 오목부와 상기 캐소드 부재(E) 사이의 거리(d2) 보다 짧고, 따라서, 캐소드 부재(E)와 상호접속층(105) 사이의 전위차가 일정할 때, 돌출부에서의 전류 밀도는 오목부에서의 전류 밀도 보다 크고, 따라서, 전해 용리가 촉진된다.

- <241> 여기서, 캐소드 부재(E)와 웨이퍼 사이의 거리가 너무 작으면, 캐소드 부재와 웨이퍼 사이에 개재된 전해액의 유동 작용(flow action)이 충분히 기능하지 않고, 그래서, 이 거리를 특정값, 예를 들어, 2mm 등 보다 큰 것으로 설정하는 것이 바람직하다.

- <242> 이 스케일은 약 0.5 내지  $1.5\mu\text{m}$ 의 요철의 높이(HT)와, 약 0.1 내지  $100\mu\text{m}$ 의 폭(WD)을 가진 상호접속부의 레벨의

범위에서 작용한다.

<243> 그러나, 극미하게, 때때로 구리막의 표면은 양극 산화 및 패시베이션에 의해서 산화된다. 패시베이션막 (passivation film)(도시되지 않음)은 구리보다 더 높은 전기 저항을 갖는다. 따라서, 패시베이션막이 상기 구리막의 표면상에 형성된 이후에, 상기 구리막으로부터 전해액을 통해 캐소드 부재를 통과하는 전류의 값은 하강하고, 전해 용리는 그 범위만큼 억제된다.

<244> 패시베이션막이 상술한 바와같이 구리막의 표면상에 형성될 때, 이 부분을 선택적으로 제거하도록 상기 패시베이션막 부분상에 부분적으로 보다 높은 전압을 인가하는 것이 가능하다. 새로 노출된 구리 표면이 강하게 패시베이션되지만, 상기 표면은 패시베이션막을 제거하기 위해 패시베이션된 영역(passivated region)에 보다 높은 전압을 반복적으로 인가함으로써 성공적으로 연마될 수 있다.

<245> 또한, 본 실시예의 연마 장치의 전원(25)은 전원(25)을 통해 유동(floating)하는 전해 전류를 모니터링할 수 있는 전류계(26)를 포함한다. 상기 모니터링된 전류 신호는 제어기(23)로 출력될 수 있다. 또한, 전류계(26) 대신, 전원은 전기 저항을 검출하는 수단으로서 기능하는 저항계를 포함할 수 있다. 그 기능은 전류 검출 수단과 동일하다.

<246> 또한, 제어기(23)는 전원(25)의 전류계로부터의 전류값 신호로부터 결정된 전류값에 기초하여 평탄화 장치의 동작을 제어할 수 있다. 특히, 이는 전류값 신호로부터 결정된 전류값에 기초하여 전압 인가를 정지하도록 평탄화 장치의 동작을 제어할 수 있다.

<247> 제어기(23)에 접속된 제어 패널(24)은 조작자가 다양한 데이터를 입력하는 것을 가능하게 하기 위한 것이다. 예를 들어, 이는 모니터링된 전류값 신호를 디스플레이한다.

<248> 전류계로 전해 전류를 모니터링함으로써, 평탄화 프로세스가 제어될 수 있고, 상기 평탄화 프로세스의 진행 상태가 정확하게 파악될 수 있다.

<249> 예를 들어, 상술한 바와 같이 전극에 의한 스캐닝 작용을 가능하게 하는 하드웨어 구성에서, 상기 전극은 표면의 특정 지점에 고정되고, 전류값의 변화가 모니터링되며, 상기 전류값이 감소되기 시작할 때 상기 전극이 움직인다. 이 동작은 반복되어 전체 표면을 스캔한다.

<250> 패시베이션막이 상술한 바와 같이 형성되는 경우에, 전류값은 패시베이션막의 형성을 따라 감소되고, 그 제거를 따라 증가된다. 이 변화는 반복된다.

<251> 상술한 연마에서, 전체 구리막이 전해 작용에 의해 제거되고, 배리어 금속막의 표면이 노출되는 경우에, 배리어 금속막의 전기 저항은 구리막의 전기 저항 보다 높기 때문에, 상기 전류값은 패시베이션막이 제거된 이후 감소되기 시작한다. 전류값이 감소되기 시작할 때, 전압은 양극 산화로 인해 패시베이션의 진행이 정지되도록 인가가 중단된다. 상기 구리막의 초기 요철의 평탄화는 이와 같은 프로세스에 의해 달성된다.

<252> 다음에, 접촉 홀들 및 상호접속 흄들 외측에 중착된 배리어 금속막이 제거되고, 그에 의해, 구리 상호접속부들이 다마센 프로세스에 의해 형성된다.

<253> 본 실시예에 따른 연마 장치에 따라서, 물질이 전기화학적으로만 제거되기 때문에, 상기 물질은 종래의 화학 기계 연마에 비해 극도로 낮은 연마 압력에 의해 막을 평탄화하도록 제거될 수 있다. 단순한 기계적 연마와 비교하는 경우에도, 이는 스크레치들을 감소시키고, 단차들을 감소시키며 다이싱 및 침식 등을 감소시키는 다양한 장점이 있다. 또한, 기계적 접촉이 없는 평탄화 기능은 스크레치 감소에 극도의 우월성을 제공한다.

<254> 또한, 평탄화가 극도로 낮은 압력에서 이루어질 수 있기 때문에, 낮은 기계적 강도들을 가지고 있으면서, 종래의 화학 기계 연마에 의해 파괴되기 쉬운, 낮은 유전율을 갖는 유기막(organic film)이나 낮은 유전율을 갖는 다공성 절연막(porous insulation film)이 충간 절연막으로 사용될 때 특히 유용하다.

<255> 종래 기술의 화학 기계 연마에서, 알루미나 입자들(alumina particles) 등을 함유하는 슬러리(slurry)를 사용할 때, 알루미나 입자들은 때때로 CMP 프로세스에 기여한 이후, 소모되지 않고 남아있거나 구리막의 표면내에 매립될 수 있다. 그러나, 본 발명의 연마 방법에서는, 연마입자들을 포함하지 않는 전해액을 사용한 평탄화 방법이 가능하기 때문에, 상호접속부들을 형성하는 동안 어떠한 입자들도 구리막에 남아있거나 구리막내에 매립되지 않는다.

<256> 또한, 표면상에 도금된 구리막의 두께의 변화도(variability)를 미리 측정함으로써 얻어진 조건들 하에서 필요한 제거량의 분포를 설정하는 것이 가능하고, 이에 따라, 상호접속부들의 형성을 위한 필요에 따라 연마에 의해

구리막의 양을 정확한 양으로 제거하는 것이 가능하다. 특히, 상기 표면상에 중첩된 부분적 제거량들로 구성된 전체 표면에 걸친 제거량들의 실제 분포가 사전설정된 제거량들의 분포와 일치되도록 캐소드 부재를 이동시킴으로써, 상호접속부들 형성에 필요한 정확한 양만큼 전체 표면에 걸쳐 연마에 의해 구리막을 제거하는 것이 가능하다.

<257> 상술한 바와 같이, 본 발명의 연마 장치에 따라서, 연마에 의해 구리막을 평탄화할 때, 초기 요철은 용이하게 평탄화될 수 있고, 잉여 구리막의 양호한 제거 효율을 얻을 수 있으며, 하부 충간 절연막에 대한 손상이 억제될 수 있다.

#### 제 3 실시예

<259> 제 1 및 제 2 실시예들에서, 캐소드 부재들이 평면들을 가지고, 표면의 한 영역에서 균일한 전계를 제공할 수 있는 경우에 대하여 설명하였지만, 웨이퍼상에 형성된 상호접속 패턴, 즉, 웨이퍼의 표면의 요철 패턴에 대응하는 전압 인가면상의 요철의 패턴을 가진 캐소드 부재를 사용하는 것도 가능하다.

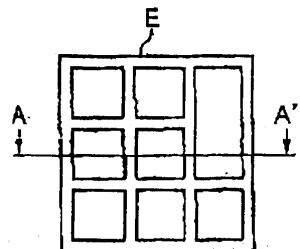

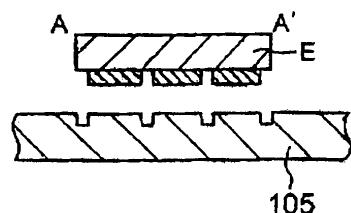

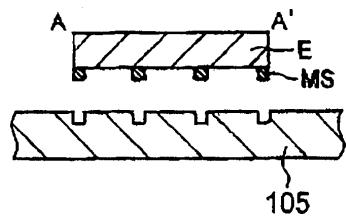

<260> 도 8a는 본 실시예에 따른 캐소드 부재의 예의 평면도이며, 도 8b는 도 8a의 A-A' 평면을 따른 캐소드 부재의 단면도이다. 이들은 캐소드 부재가 연마될 표면, 즉, 상호접속층에 대향하게될 때의 구성을 도시하고 있다.

<261> 즉, 캐소드 부재(E)는 웨이퍼의 표면, 즉, 상호접속층(105)의 요철 패턴에 대응하는 형태이며, 상기 상호접속층(105)의 돌출부에 대응하는 부분들은 돌출되어 강한 전계를 제공하고, 상호접속층(105)의 오목부들에 대응하는 부분들은 함몰되어 있어 약한 전계를 제공한다.

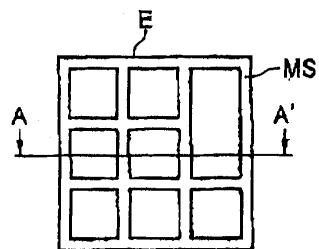

<262> 또한, 도 8c는 본 실시예에 따른 캐소드 부재의 다른 예를 도시하는 평면도이고, 도 8d는 A-A' 라인을 따른 단면도이다. 이들은 캐소드 부재가 연마될 표면, 즉, 상호접속층(105)에 대향하게될 때의 구성을 도시하고 있다.

<263> 즉, 캐소드 부재(E)는 상기 웨이퍼의 표면, 즉, 상호접속층(105)의 표면의 요철 패턴에 대응하여 형성되어, 상호접속층(105)의 오목부들에 대응하는 부분들에서 마스크(MS)가 형성되어 약한 전계를 제공하고, 상호접속층(105)의 돌출부에 대응하는 부분들에서는 캐소드 부재(E)의 표면이 노출되어 강한 전계를 제공한다.

<264> 웨이퍼의 표면의 요철 패턴에 대응하는 전압 인가면상의 요철 패턴을 가진 이런 캐소드 부재를 사용할 때, 상기 캐소드 부재는 상기 웨이퍼의 미리 결정된 영역들에서 각 상호접속 패턴에 대해 배치된다. 연마가 완료되었을 때, 캐소드 부재은 인접 영역으로 단계적으로 이동된다.

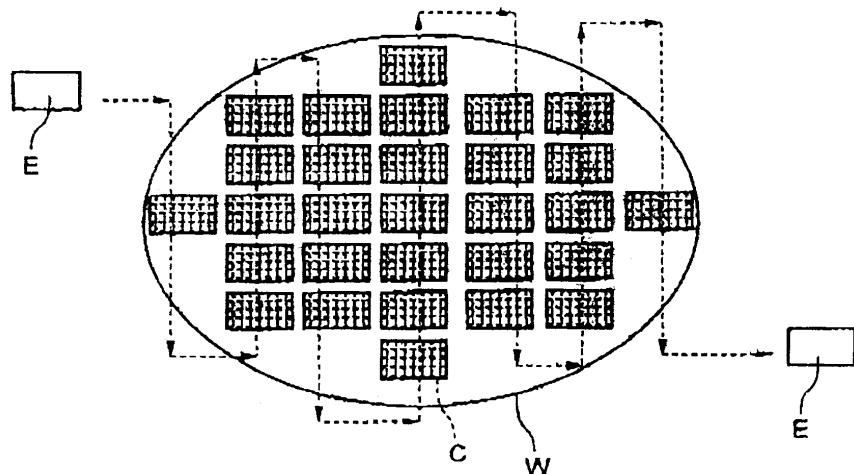

<265> 이 경우에, 웨이퍼는 연마 동안 회전 구동되지 않으며, 전해액내에 정지되어 있게된다. 예를 들어, 도 8e에 도시된 바와 같이, 스텝퍼 정렬기의 노출에서와 동일한 절차에 의해, 상기 캐소드 부재(E)는 X- 및 Y-방향으로 단계적으로 이동되어 상기 웨이퍼의 전체 표면이 프로세싱될 때까지 웨이퍼(W)상의 각 단위 반도체칩(C)을 연마한다.

<266> 구리막의 두께나 두께에 상당하는 데이터를 측정하기 위한 측정 헤드를 가진 측정 수단이나, 구리막의 획득된 두께에 상당하는 데이터로부터 구리막의 목표 제거량을 산출하기 위한 산출 유닛 같은 상기 장치의 나머지 부분들의 동작 및 구성은 제 1 및 제 2 실시예에서와 동일한 방식으로 형성될 수 있다. 제 1 및 제 2 실시예에서와 동일한 효과가 얻어질 수 있다.

#### 제 4 실시예

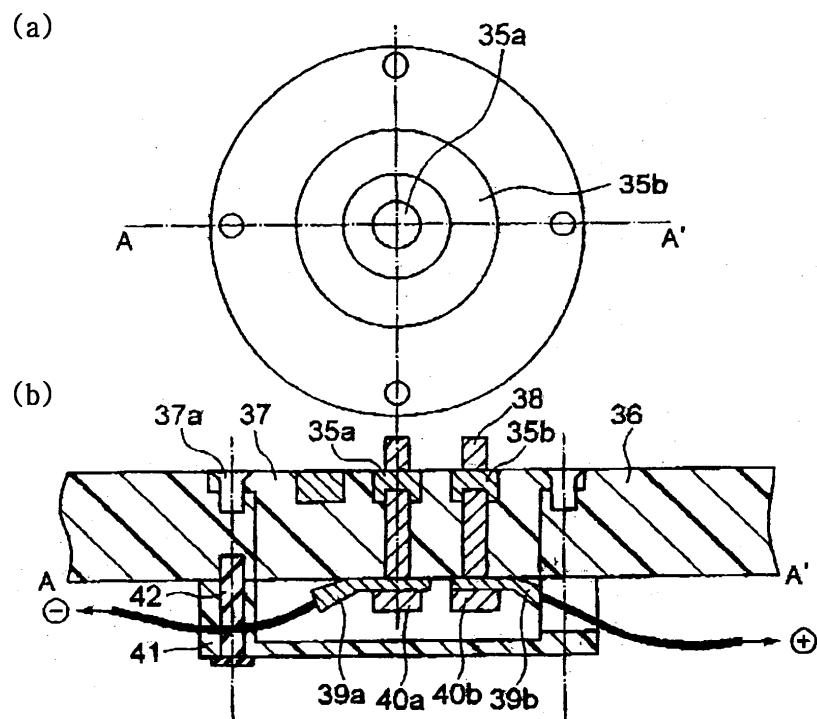

<268> 제 1 및 제 2 실시예에서, 캐소드 부재가 기계적 이동을 위한 기구를 구비하였지만, 서로 절연되도록 배열되어 전체 표면 전부에 대향하는 다수의 영역들로 분할된 캐소드 부재를 사용하는 것도 가능하다. 분할된 캐소드 부재에 대한 전압 인가 위치를 변화시킴으로써, 표면에 대향한 캐소드 부재의 위치를 한 영역으로부터 다른 영역으로 변화시킬때와 실질적으로 동일한 효과를 얻을 수 있다.

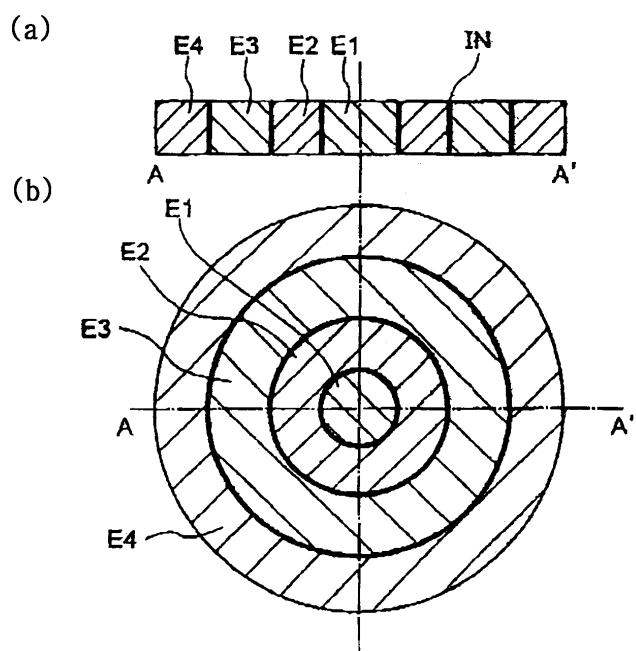

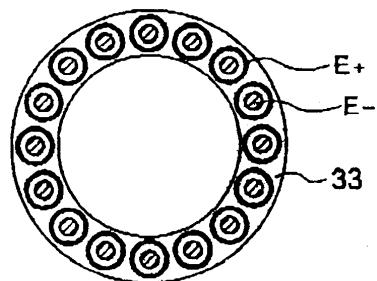

<269> 즉, 예를 들어, 도 9의 (a)에 단면도로, 그리고, 도 9의 (b)에 평면도로 도시된 바와 같이, 상기 캐소드 부재는 다수의 동심원 영역들(도 9의 (a) 및 도 9의 (b)에서는 4개, 즉, E1, E2, E3, E4)로 분할된 캐소드 부재로 이루어질 수 있다. 두 개의 이웃하는 영역들은 절연체(IN)에 의해 서로로부터 절연된 상태로 유지된다. 상기 캐소드 부재는 전체로서 전체 표면에 대향한다.

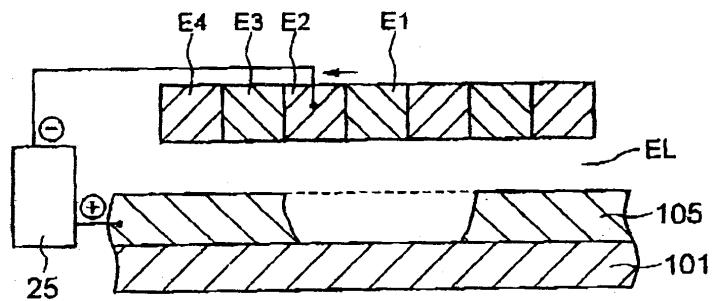

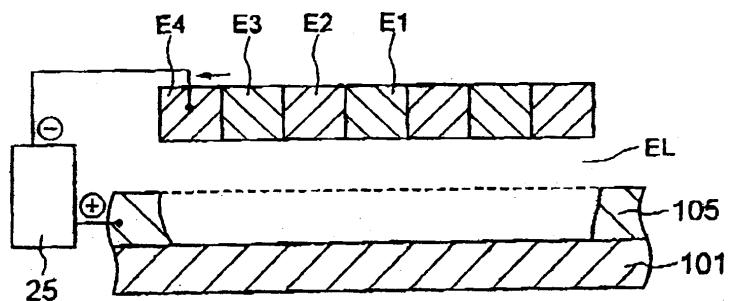

<270> 다수의 동심원 영역들(E1, E2, E3, E4)를 사용하는 전해 용리에 의한 전해 연마를 위해서, 도 10a에 도시된 바와 같이, 상기 영역들(E1, E2, E3, E4)은 전체로서 상기 연마될 기판으로서의 상호접속층(105)을 가진 기판(101)으로 구성된 웨이퍼에 대향하도록 배열되어 있으며, 그 사이에 전해액(EL)이 개재되어 있다. 캐소드로서 접속된 최내부 영역(E1)과 애노드로서 접속된 웨이퍼의 가장자리부에 있는 상호접속층(105)으로, 전원(25)에 의

해 미리 결정된 전압이 인가된다. 결과적으로, 상기 영역 E1에 대향하는 상호접속층(105)의 부분이 연해 용리에 의해 전해 연마된다.

<271> 상기 영역 E1에 대향하는 상호접속층(105)이 연마가 종료된 이후에, 도 10b에 도시된 바와 같이, 캐소드로서 접속된 제 2 최내부 영역(E2)에 미리 결정된 전압이 인가된다. 상기 영역 E2에 대향한 상기 상호접속층(105)의 부분이 전해 용리에 의해 전해 연마된다.

<272> 이 방식으로, 내부로부터 외부 동심원 영역들(E1, E2, E3, E4)로 전압 인가 위치를 변화시킴으로써, 도 10c에 도시된 바와 같이, 상기 상호접속층(105)에 어떠한 아일랜드형 부분들도 남기지 않고 전체 표면이 균일하게 연마될 수 있다.

<273> 구리막의 두께나 두께에 상당하는 데이터를 측정하기 위한 측정 헤드를 가진 측정 수단이나, 구리막의 획득된 두께에 상당하는 데이터로부터 구리막의 목표 제거량을 산출하기 위한 산출 유닛 같은 상기 장치의 나머지 부분들의 동작 및 구성은 제 1 및 제 2 실시예에서와 동일한 방식으로 형성될 수 있다. 제 1 및 제 2 실시예에서와 동일한 효과가 얻어질 수 있다.

#### 제 5 실시예

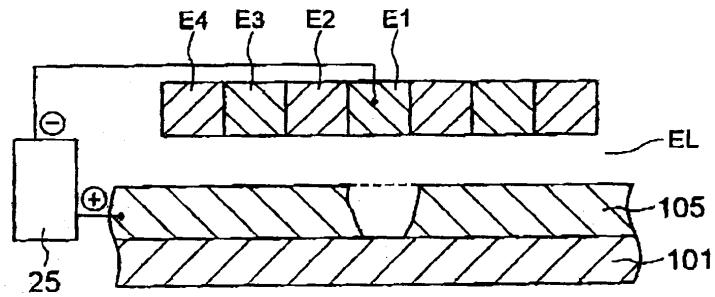

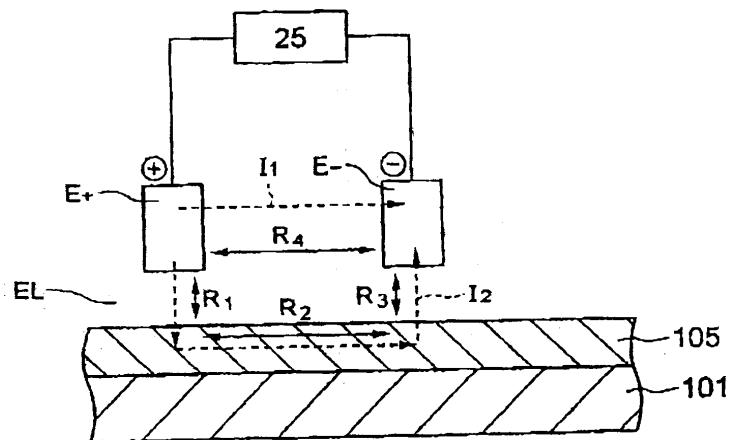

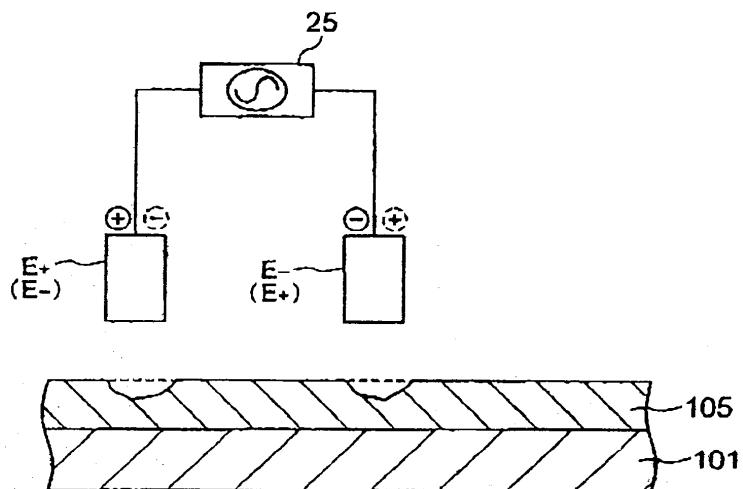

<275> 제 1 및 제 2 실시예에서, 캐소드로서 캐소드 부재를 사용하고, 애노드로서 상호접속층을 사용하여 전해 용리를 위한 연마 장치를 구성하는 것을 설명하였다. 본 실시예에서는, 도 11a에 도시된 바와 같이, 상기 캐소드 부재(E<sub>-</sub>)가 연마될 표면으로서의 상호접속층이 형성된 기판(101)으로 구성된 웨이퍼의 상호접속층(105)에 대향하게 되고, 애노드 부재(E<sub>+</sub>)가 특정 거리만큼 캐소드부재(E<sub>-</sub>)로부터 이격 배치되어 상기 상호접속층(105)에 대향하게 되며, 적어도 상기 상호접속층(105)과 캐소드 부재(E<sub>-</sub>) 사이와, 상기 상호접속층(105)과 상기 애노드 부재(E<sub>+</sub>)의 사이에 전해액이 개재되며, 상기 캐소드 부재(E<sub>-</sub>)와 애노드 부재(E<sub>+</sub>)로 전압이 인가된다.

<276> 이때, 상기 캐소드 부재(E<sub>-</sub>)와 애노드 부재(E<sub>+</sub>) 사이의 거리는 충분히 길게 설정되고, 상기 상호접속층(105)과 캐소드 부재(E<sub>-</sub>) 및 상기 상호접속층(105)과 애노드 부재(E<sub>+</sub>) 사이의 거리는 충분히 짧게 설정된다.

<277> 따라서, 상기 상호접속층(105)과 애노드 부재(E<sub>+</sub>) 사이의 저항(R1)과, 상기 캐소드 부재(E<sub>-</sub>)에 대향한 상호접속층(105)의 부분들과 상기 애노드 부재(E<sub>+</sub>) 각각의 사이의 저항(R2) 및 상기 상호접속층(105)과 상기 캐소드 부재(E<sub>-</sub>) 사이의 저항(R3)의 합은 애노드 부재(E<sub>+</sub>)와 캐소드 부재(E<sub>-</sub>) 사이의 직접 저항(R4) 보다 작고, 상호접속층(105)을 통한 애노드 부재(E<sub>+</sub>)로부터 캐소드 부재(E<sub>-</sub>)로의 전류(I<sub>2</sub>)는 애노드 부재(E<sub>+</sub>)로부터 직접적으로 캐소드 부재(E<sub>-</sub>)로의 전류(I<sub>1</sub>) 보다 크며, 그래서, 애노드로서의 연마될 표면, 즉, 상호접속층(105)과 캐소드로서의 캐소드 부재(E<sub>-</sub>)에 전압을 인가하였을 때와 동일한 효과가 얻어진다.

<278> 결과적으로, 도 11b에 도시된 바와 같이, 전해 용리가 상기 캐소드 부재(E<sub>-</sub>)에 대향한 상호접속층(105)의 부분의 표면에서 발생된다.

<279> 상술한 애노드 부재가 연마될 표면, 즉, 구리 보다 용이하게 이온화될 수 있는 경우에, 상기 애노드 부재는 상술한 전해 용리 작용에 의해 전해 용리되어 단부가 상승되게 될 것이다. 따라서, 애노드 부재로서 구리보다 귀한 금속을 사용하는 것이 바람직하다. 예를 들어, 백금이나 백금 피복 티타늄으로 구성된 전극을 사용할 수 있다.

<280> 상술한 캐소드 부재(E<sub>-</sub>)와 상기 애노드 부재(E<sub>+</sub>)를 사용하는 상기 표면의 전체 표면에 걸친 전해 용리를 위하여, 상기 캐소드 부재(E<sub>-</sub>)와 상기 애노드 부재(E<sub>+</sub>)에 대향하는 영역은 한 영역으로부터 다른 영역으로 이동된다.

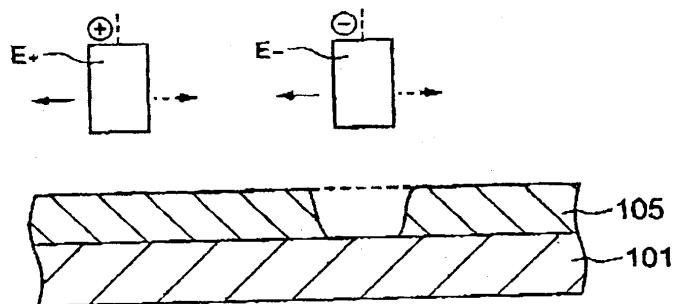

<281> 여기서, 캐소드 부재(E<sub>-</sub>)와 애노드 부재(E<sub>+</sub>) 사이의 상호접속층(105)이 완전히 용리되는 경우에, 상기 상호접속층(105)을 통과하는 전류는 사라지고, 전해 용리 작용은 정지되며, 전해 용리는 더 이상 상기 표면 전체면에 걸쳐 수행되지 않는다.

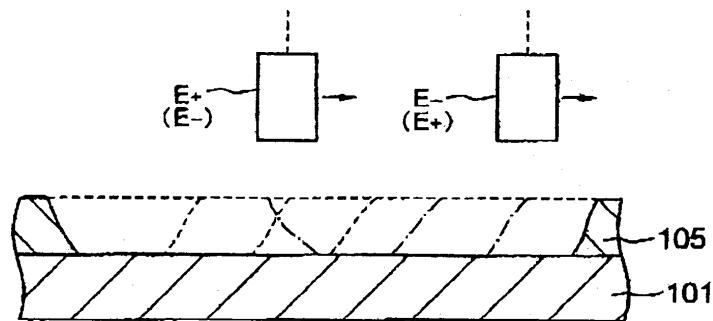

<282> 이를 방지하기 위하여, 도 12a에 도시된 바와 같이, 상기 캐소드 부재(E<sub>-</sub>)와 애노드 부재(E<sub>+</sub>) 사이에 교류 전압을 인가하는 것이 바람직하다. 이 경우에, 상기 캐소드 및 애노드는 서로간에 교번되기 때문에, 전해 용리는 각 전극에 대향하는 위치들에서 발생하게 되고, 두 개의 캐소드들이 특정 부분에 있은 모든 상호접속층(105)이 완전히 용리되기 이전에 이동되며, 그에 의해, 도 12b에 도시된 바와 같이, 전해 용리에 의해 웨이퍼의 전체면을

전해 연마하는 것이 가능하다.

<283> 구리막의 두께나 두께에 상당하는 데이터를 측정하기 위한 측정 헤드를 가진 측정 수단이나, 구리막의 획득된 두께에 상당하는 데이터로부터 구리막의 목표 제거량을 산출하기 위한 산출 유닛 같은 상기 장치의 나머지 부분들의 동작 및 구성은 제 1 및 제 2 실시예에서와 동일한 방식으로 형성될 수 있다. 제 1 및 제 2 실시예에서와 동일한 효과가 얻어질 수 있다.

#### 제 6 실시예

<285> 제 2 실시예에서, 구리막의 두께 또는 상기 두께에 상당하는 데이터가 먼저 측정 헤드를 구비한 측정 수단에 의해 측정되고, 제거될 구리막의 양의 프로파일이 획득된, 구리막의 두께에 상당하는 데이터로부터 산출되며, 캐소드 부재가 이에 기초하여 이동하였지만, 본 실시예는 전해 용리 동안 두께에 상당하는 데이터를 측정하는 전해 용리에 의한 전해 연마 방법을 제공하며, 특히, 두께에 상당하는 데이터로서 전해 연마의 전해 전류를 측정하는 방법을 제공한다.

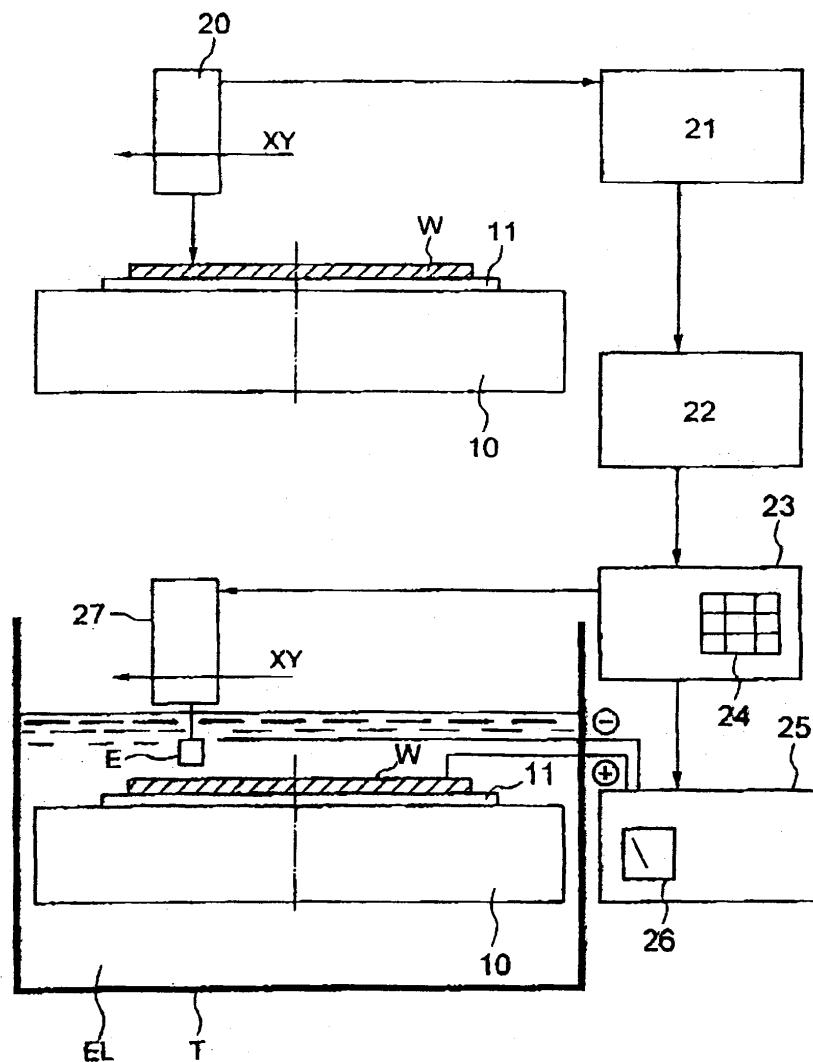

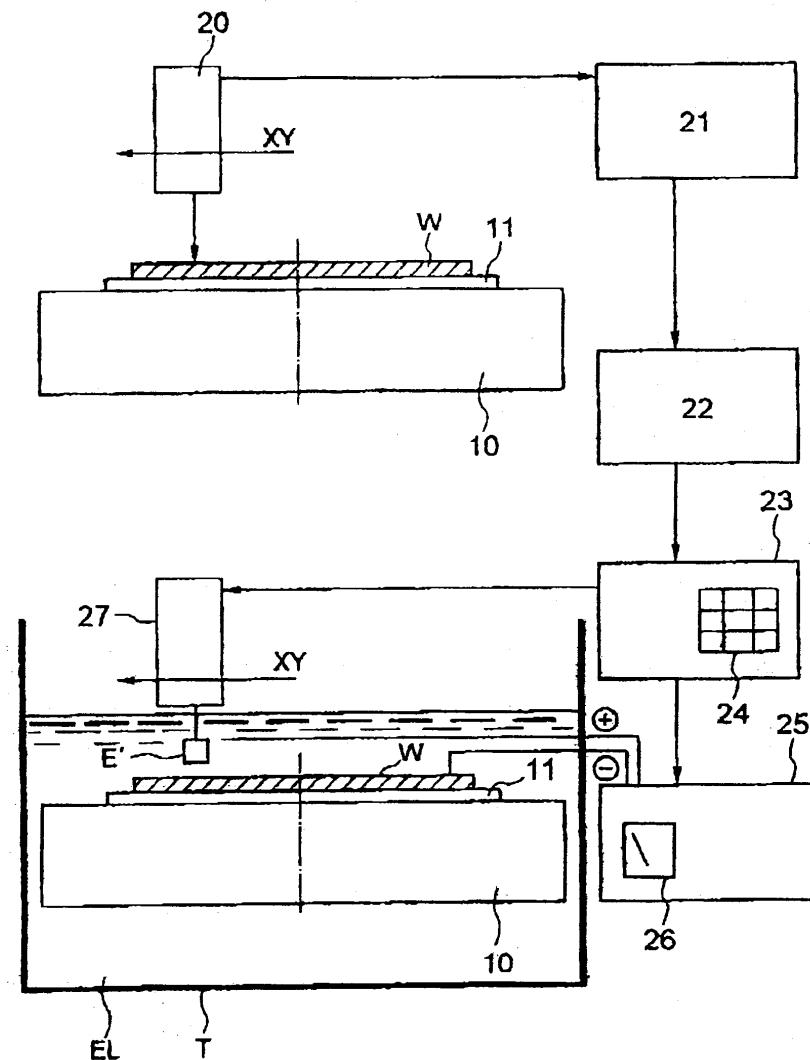

<286> 도 13a는 본 실시예에 따른 연마 장치의 개략도이다.

<287> 즉, 본 실시예의 연마 장치는 그 표면상에 구리막을 가진 연마될 웨이퍼(W)(이하, "웨이퍼"라고도 지칭함)를 지지하는 테이블(10)과, 상기 테이블(10)상에 제공된 진공 척 같은 고정 수단(11)과, 연산 유닛(22)과, 제어기(23)와, 제어 패널(24)과, 전원(25)과, 전류계(26)와, 캐소드 부재(E)와, 캐소드 부재(E)를 이동시키는 이동 기구(27) 및 전해액(EL)을 저장하기 위한 전해조 탱크(T)를 포함한다.

<288> 예를 들어, 상기 웨이퍼(W)는 회전 테이블(10)상의 진공 척 같은 고정 수단(11)에 의해 고정되고, 상기 테이블과 함께 전해조 탱크(T)내의 전해액(EL)내에 침적된다.

<289> 예를 들어, 상기 웨이퍼(W)의 표면 보다 상대적으로 작은 캐소드 부재(E)는 상기 표면의 한 영역에 대향하도록 배열되며, 상기 테이블은 회전된다. 직류 전압 또는 펄스 전압 같은 미리 결정된 전압이 전원(25)에 의해 애노드로서 사용되는 웨이퍼의 표면, 즉, 구리막과, 캐소드로서의 캐소드 부재(E)에 인가된다.

<290> 이런 전압이 인가되는 경우에, 제 1 실시예에서 상술한 바와 마찬가지로, 상기 표면의 영역은 전해 연마된다.

<291> 이때, 전해 전류가 전류계(26)에 의해 모니터링되고, 연산 유닛(22)으로 출력된다. 상기 입력 전류값으로부터, 연산 유닛(22)은 구리의 잔여 목표 제거량을 연산하고, 이를 제어기(23)로 출력한다.

<292> 상기 제어기(23)는 이 입력으로부터 구리막의 목표 제거량을 설정하고, 이에 따라 상기 전원(25)으로부터의 전압 출력과, 상기 캐소드 부재(E)의 이동 기구(27)를 제어한다. 또한, 상기 제어기(23)는 상기 제어 패널(24)로부터 외부 입력을 수신할 수 있다.

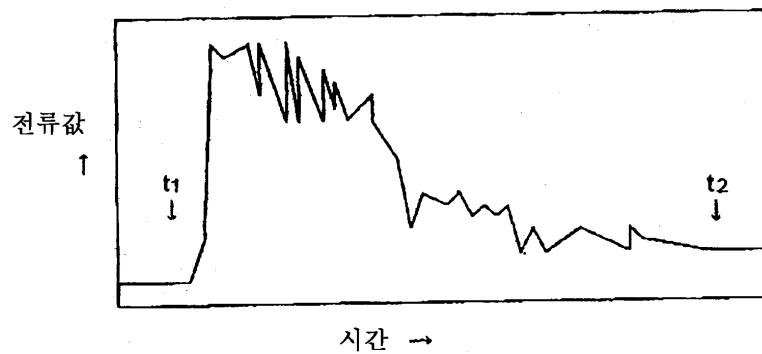

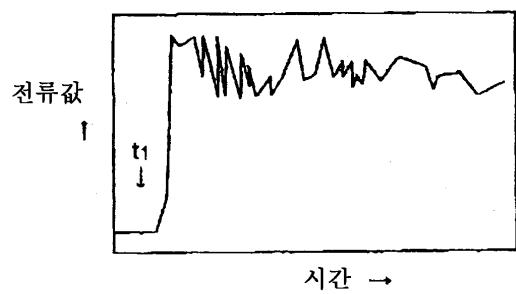

<293> 선택적으로, 전해 전류는 전류계(26)에 의해 모니터링될 수 있고, 전류값이 특정값이 되는 시점에서 제거될 구리막의 목표량을 0으로 결정하고, 상기 표면의 상기 영역에서의 전해 연마를 완료하며, 상기 캐소드 부재(E)는 이동 기구에 의해 이 영역으로부터 다른 영역으로 이동된다.

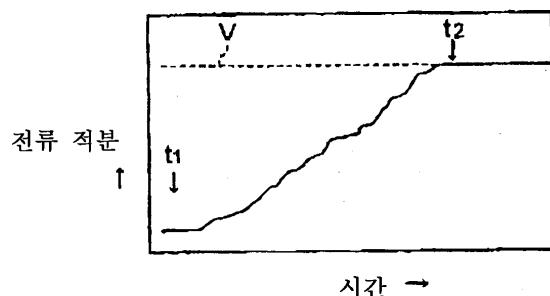

<294> 예를 들어, 도 13b의 그래프에 도시된 바와 같이, 전해 용리 반응이 시간  $t_1$ 에서 시작하는 경우에, 전류값은 급작스럽게 상승하여 최대값에 도달한다. 반응이 진행되는 동안 구리막의 잔여량이 감소된다. 이와 함께, 전류값은 점진적으로 하강된다.

<295> 상호접속 흄들 외측의 구리막이 제거되었을 때, 전해 용리 반응은 느려지기 시작하고, 전류값은 상기 피크 값에 비해 충분히 작아지며, 그래서, 작은 변화를 가진 평탄한 영역이 설정되게 된다. 시간  $t_2$ 에서, 구리막의 잔여 목표량이 0으로 결정되고, 상기 표면의 상기 영역의 전해 연마가 완료된다.

<296> 상기 장치의 잔여부의 구성 및 동작은 제 1 및 제 2 실시예들과 동일하게 형성될 수 있다. 제 1 및 제 2 실시예에서와 동일한 효과가 달성될 수 있다.

<297> 또한, 본 실시예는 제 3 내지 제 5 실시예의 연마 장치에도 적용될 수 있다.

#### 제 7 실시예

<299> 상기 제 2 실시예에서, 구리막의 두께 또는 상기 두께에 상당하는 데이터가 이전에 측정 헤드를 구비한 측정 수단에 의해 측정되고, 제거될 구리막의 양의 프로파일이 획득된 구리막의 두께에 상당하는 데이터로부터 산출되며, 상기 캐소드 부재가 이에 기초하여 이동되는 것을 설명하였지만, 본 실시예는 상기 두께에 상당하는 데이터

를 측정하는 동안 전해 용리에 의해 전해 연마를 수행하는 방법이다.

<300> 도 14는 본 실시예에 따른 연마 장치의 개략도이다.

<301> 즉, 본 실시예의 연마 장치는 그 표면상에 구리막을 가진 연마될 웨이퍼(W; 하기에는 "웨이퍼"라고도 지칭함)를 지지하는 테이블(10)과, 상기 테이블(10)상에 제공된 진공 척 같은 고정 수단(11)과, 측정 헤드(20)를 구비한 측정 수단(21)과, 연산 유닛(22)과, 제어기(23)와, 제어 패널(24)과, 전원(25)과, 전류계(26)와, 캐소드 부재(E)와, 캐소드 부재(E)를 이동시키는 이동 기구(27) 및 전해액(EL)을 저장하기 위한 전해조 탱크(T)를 포함한다.

<302> 예를 들어, 상기 웨이퍼(W)는 회전 테이블(10)상의 진공 척 같은 고정 수단(11)에 의해 고정되고, 상기 테이블과 함께 전해조 탱크(T)내의 전해액(EL)내에 침적된다. 상기 측정 헤드(20)와 캐소드 부재(E)는 상기 표면의 한 영역에 대향하도록 배열된다.

<303> 먼저, 상기 테이블(10)을 회전 구동하는 동안, 상기 표면의 한 영역에서의 구리막의 두께 또는 상기 두께에 상당하는 데이터가 측정 헤드(20)를 구비한 측정 수단(21)에 의해 측정된다. 구리막의 두께는 예를 들어, 4프로브형 시트 저항계를 사용한 시트 저항 측정 방법을 사용하고, 공지된 시트 저항을 사용하여 이를 두께로 변환하거나, 와전류형 검출기 또는 정전 용량형 검출기를 사용하여 두께에 상당하는 데이터를 측정하는 방법을 사용하여 측정될 수 있다.

<304> 연산 유닛(22)은 획득된 구리막의 두께에 상당하는 데이터로부터 제거될 구리막의 목표량을 산출하고, 이를 제어기(23)로 출력한다.

<305> 상기 제어기(23)는 이 입력으로부터 제거될 구리막의 목표량을 설정하고, 이에 따라, 상기 전원(25)으로부터의 전압 출력과, 상기 캐소드 부재(E)의 이동 기구(27)를 제어한다. 또한, 제어기(23)는 상기 제어 패널(24)로부터의 외부 입력을 수신할 수 있다.

<306> 직류 전압 또는 펄스 전압과 같은 미리 결정된 전압이 전원(25)에 의해 공급되고, 애노드로서 웨이퍼 표면, 즉, 상호접속층(105) 및 캐소드로서 캐소드 부재(E)를 사용한다. 이런 전압이 인가되는 경우에, 제 1 실시예에서 상술한 바와 마찬가지로, 상기 표면의 영역은 전해 연마된다.

<307> 여기서, 측정 수단(21)이 두께 또는 두께에 상당하는 데이터를 측정하는 동안, 전해 용리에 의해 상기 표면이 전해 연마된다. 상기 두께 또는 두께에 상당하는 데이터의 측정의 결과로부터 구리막의 목표량이 제거된 것으로 판정되었을 때, 상기 캐소드 부재(E)는 이동 기구(27)에 의해 연속적으로 또는 단계적으로 이동된다. 이때, 상기 측정 헤드(20)도 상기 캐소드 부재(E)를 따라 이동된다.

<308> 상기 표면의 전체 표면이 상술한 단계들을 전체 표면에 걸쳐 수행함으로써 전해 용리에 의해 균일하게 전해 연마될 수 있다.

<309> 상기 장치의 잔여부의 구성 및 동작은 제 1 및 제 2 실시예들과 동일하게 형성될 수 있다. 제 1 및 제 2 실시예와 동일한 효과가 달성될 수 있다.

<310> 또한, 본 실시예는 제 3 내지 제 5 실시예의 연마 장치에도 적용될 수 있다.

#### 제 8 실시예

<312> 도 15는 본 실시예에 따른 연마 장치의 개략도이다. 이는 제 2 실시예에 따른 연마 장치와 실질적으로 동일하지만, 캐소드 부재(E)가 상기 표면의 요철의 크기의 범위 보다 작다. 또한, 상기 측정 헤드(20)와 이동 기구(27)는 연마될 표면의 평면내에서 이차원적으로 이동될 수 있다. 여기서, 상기 테이블(10)의 회전구동기구는 불필요하다.

<313> 상술한 연마 장치에서, 제 2 실시예와 동일한 방식으로, 구리막의 두께 또는 상기 두께에 상당하는 데이터가 먼저 측정 헤드를 구비한 측정 수단에 의해 이차원적으로 측정되고, 제거될 구리막의 목표량의 프로파일이 상기 획득된 두께에 상당하는 데이터로부터 산출되며, 캐소드 부재의 이동은 상기 전해 용리의 제어를 위해, 이에 기초한 표면의 평면내에서 이차원적으로 제어된다. 상기 캐소드 부재(E)가 상기 표면의 요철의 크기의 범위 보다 작기 때문에, 상기 소형 캐소드 부재의 이동과 상기 표면의 요철에 따른 전압의 인가가 가능하다.

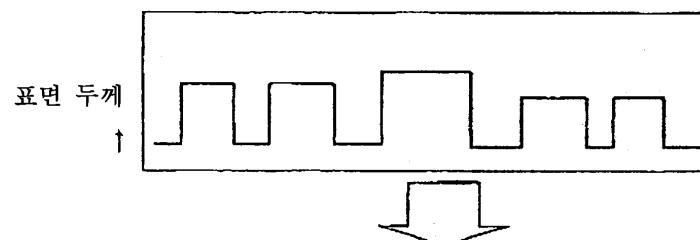

<314> 예를 들어, 구리막의 두께 측정의 결과가 도 16a의 그래프(도면에서, 상기 평면에서 일 방향에 대한 프로파일이 일차원적으로 도시되어 있음)에 도시된 바와 같을 때, 즉, 미세 돌출 및 오목 영역들이 웨이퍼의 가장자리부

(ED)로부터 중앙부(CT)로 형성되어 있을 때, 상기 제거될 구리막의 목표량은 도 16a의 프로파일과 동일한 도 16b에 도시된 바와 같이 설정된다. 캐소드 부재(E)의 이동 속도는 도 16c에 도시된 바와 같이, 큰 제거량의 부분에서는 느리게 움직이고, 작은 제거량의 부분에서는 빠르게 움직이도록 제어된다.

- <315> 상기 장치의 나머지 부분들의 구조 및 동작은 제 1 및 제 2 실시예에서와 동일하게 형성될 수 있다. 제 1 및 제 2 실시예들에서 달성되는 바와 동일한 효과들이 얻어진다.

- <316> 또한, 본 실시예는 제 3 내지 제 5 실시예의 연마 장치에도 적용될 수 있다.

- <317> 제 9 실시예

- <318> 상술한 제 1 내지 제 8 실시예에서, 상기 표면은 전해 용리 단독에 의해 연마된다. 본 실시예에서는 화학 기계 연마(CMP)에 의한 연마가 또한 조합되고, 그에 의해, 전해 연마와 화학 기계 연마가 조합된 복합 연마에 의한 연마가 가능하다.

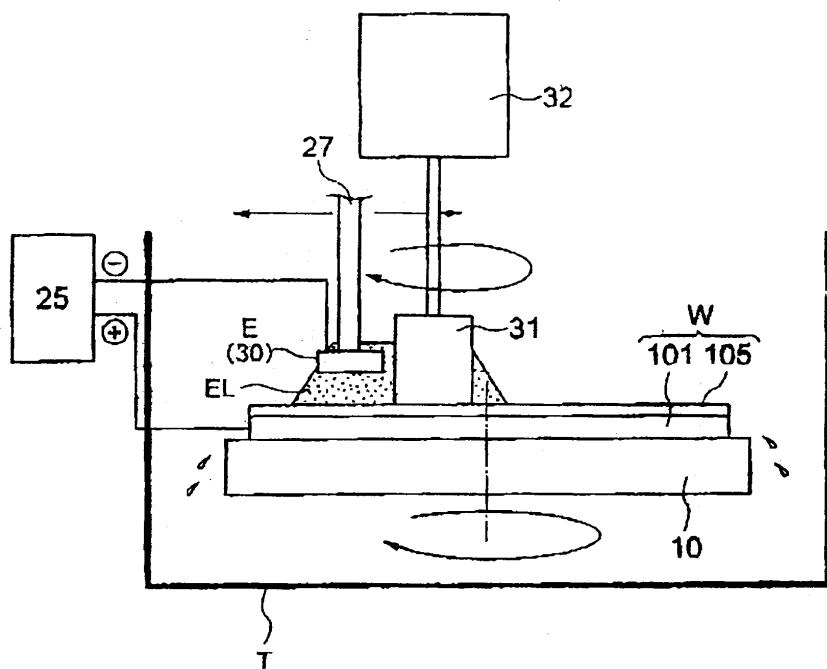

- <319> 본 실시예에 따른 연마 장치는 도 5의 하부에서 전해조 탱크(T)의 내부가 도 17에 도시된 연마 장치로 대체된 점을 제외하면, 도 5에 도시된 것과 실질적으로 동일하다.

- <320> 즉, 연마될 표면으로서 상호접속층(105)이 형성되어 있는 기판(101)으로 구성된 웨이퍼(W)는 진공 척, 에지 클램프 또는 기계적 클램프 같은 고정 수단에 의해 고정되며, 회전 구동된다. 웨이퍼(W)의 한 영역에서, 전해액을 공급하는 노즐(30)로서도 기능하면서, 이동 기구(27)에 의해 이동될 수 있는 캐소드 부재(E)가 상기 표면과 평행하게 배열된다.

- <321> 구리의 전해 용리를 위해 전해액 공급 노즐로부터 공급된 전해액(EL)은 상기 캐소드 부재(E)와 상호접속층(105) 사이에 개재된다.

- <322> 직류 전압 또는 펄스 전압 같은 미리 결정된 전압이 전원(25)에 의해 애노드로서 사용되는 웨이퍼의 표면, 즉, 상호접속층(105)과, 캐소드로서의 캐소드 부재(E)에 인가될 때, 제 1 실시예에서 설명한 바와 같이, 상기 표면의 한 영역이 전해 연마된다.

- <323> 전해액이 상기 전해액 공급 노즐(30)에 의해 공급되는 영역에서, 스크러버(scrubber)(31)를 포함하는 연마 헤드(32)가 제공된다. 상기 연마 헤드(32)는 그 위에 압력을 가하면서, 상기 스크러버(31)를 회전하도록 구동할 수 있다. 또한, 상기 스크러버(31)는 연마 헤드의 이동으로 인해 이동하지만, 상기 캐소드 부재(E)의 이동과 링크되어 이동한다. 또한, 연마 헤드(32)는 상기 연마 헤드(32)의 이동으로 인해 스크러버(31)에 압력을 가할 수 있다.

- <324> 여기서, 예를 들어 상기 스크러버는 폴리비닐 아세탈 발포체(polyvinyl acetal foam), 폴리우레탄 발포체(polyurethane foam) 등으로 제조된다. 일반적인 CMP 프로세스에 사용되는 물질로 제조된 스크러버가 채택될 수 있다.

- <325> 여기서, 예를 들어, 구리를 위한 전해액으로서, 알루미늄 산화물, 실리콘 산화물, 세륨 산화물 또는 지르코늄 산화물 같은 연마 입자를 함유한 연마 슬러리를 추가로 포함하는 제 1 또는 제 2 실시예에서 설명된 전해액들을 사용하는 것이 가능하다. 이들 연마 입자들을 포함함으로써, 화학 기계 연마가 효과적으로 수행될 수 있다.

- <326> 예를 들어, 본 실시예에 따른 연마 장치는 전해 용리에 의한 연마를 위한 도시되지 않은 제어기에 의해 제거되는 전원(25)으로부터 상기 캐소드 부재(E)와, 상호접속층(105) 사이에 전압을 공급하고, 연마 슬러리 같은 연마 입자를 함유한 전해액을 사용하는 화학 기계 연마에 의해 연마 효율을 향상 또는 보조하도록 연마할 수 있다.

- <327> 상기 캐소드 부재(E)와 스크러버(31)는 상기 이동 기구(27)에 의해 링크되고, 상기 웨이퍼의 전체 표면에 걸쳐 연속적으로 또는 단계적으로 이동되기 때문에, 전체 표면은 전해 용리에 의한 전해 연마와 화학 기계 연마의 복합 연마에 의해 균일하게 연마될 수 있다.

- <328> 낮은 기계적 강도를 가지면서, 종래의 화학 기계 연마에 의해 쉽게 파손되는, 낮은 유전율의 유기 물질이나 낮은 유전율의 다공성 물질을 충간 절연막으로 사용하는 웨이퍼의 연마시에, 높은 압력을 가하는 화학 기계 연마는 바람직하지 못하다. 그러나, 본 실시예에서는 전해 연마와 화학 연마가 조합되어 있기 때문에, 연마 압력이 화학 기계 연마만을 사용하는 연마에 비해 감소될 수 있다. 따라서, 앞선 실시예들과 유사하게, 구리막의 스크레이치들 및 하부 충간 절연막에 대한 손상이 억제될 수 있다.

- <329> 본 실시예에서도 마찬가지로, 제 2 실시예에서와 동일한 방식으로, 때때로, 상기 구리막의 표면이 양극 산화에

의해 산화되고, 패시베이션된다. 이 경우에, 패시베이션된 부분은 화학 기계 연마에 의한 부분적인 스크러빙(scrubbing)을 위한 시간을 연장시킴으로써 화학 기계 연마에 의해서, 또는, 상기 패시베이션 막부상에 높은 전압을 인가함으로써, 선택적으로 제거될수 있다. 비록, 새로 노출된 구리 표면은 강하게 패시베이션되지만, 상기 표면은 패시베이션 막을 제거하기 위한 기계적 스크러빙을 반복함으로써, 성공적으로 연마될 수 있다.

<330> 이때, 전해 전류의 값은 패시베이션막의 제거와 함께 증가하고, 패시베이션막의 형성과 함께 감소된다.

<331> 구리막의 두께나 두께에 상당하는 데이터를 측정하기 위한 측정 헤드를 가진 측정 수단이나, 구리막의 획득된 두께에 상당하는 데이터로부터 구리막의 목표 제거량을 산출하기 위한 산출 유닛 같은 상기 장치의 나머지 부분들의 동작 및 구성은 제 1 내지 제 8 실시예들에서와 동일한 방식으로 형성될 수 있다. 제 1 내지 제 8 실시예들에서와 동일한 효과가 얻어질 수 있다.

### 제 10 실시예

<333> 본 실시예에 따른 연마 장치는 제 9 실시예와 동일한 방식으로 전해 연마와 화학 기계 연마를 조합한 복합 연마를 위한 장치이다.

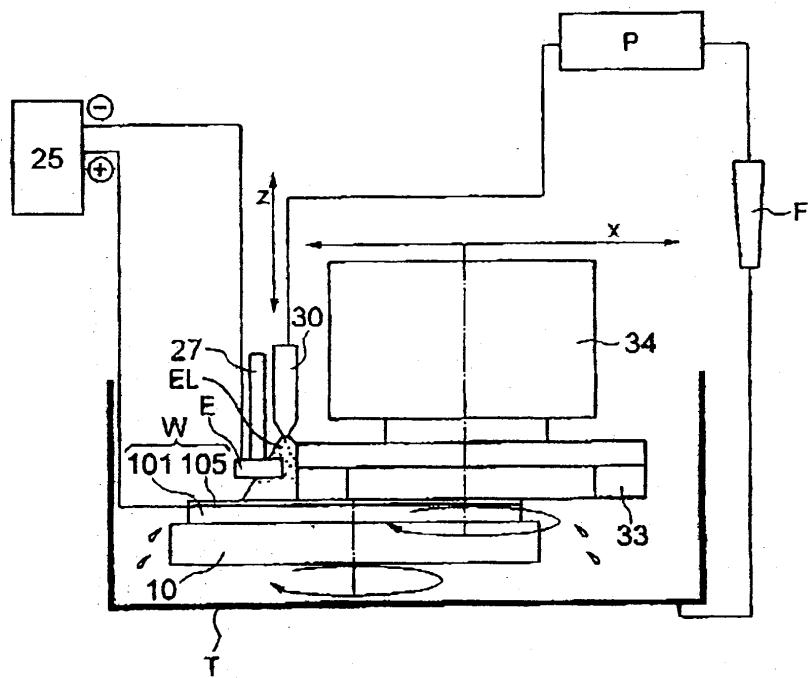

<334> 본 실시예에 따른 연마 장치는 도 5의 하부에서 전해조 탱크(T)의 내부가 도 18에 도시된 연마 장치로 대체된 점을 제외하면, 도 5에 도시된 것과 실질적으로 동일하다.

<335> 즉, 연마될 표면으로서 상호접속층(105)이 형성되어 있는 기판(101)으로 구성된 웨이퍼(W)는 진공 척, 에지 클램프 또는 기계적 클램프 같은 고정 수단에 의해 고정되며, 회전 구동된다. 에지 클램프의 경우에, 전류는 웨이퍼의 가장자리부를 접지하는 클램프부를 통해 애노드로서 기능하는 웨이퍼로 전류가 전달될 수 있다.

<336> 웨이퍼(W)의 한 영역에서, 이동 기구(27)에 의해 이동될 수 있는 캐소드 부재(E)가 상기 표면과 평행하게 배열된다. 또한, 이 영역내에 전해액 공급 노즐(30)이 배열되며, 상기 캐소드 부재(E)와 링크되어 이동된다. 구리의 전해 용리를 위해 전해액 공급 노즐로부터 공급된 전해액(EL)은 상기 캐소드 부재(E)와 상호접속층(105) 사이에 개재된다.

<337> 도면에 도시된 바와 같은 하나의 노즐에 부가하여, 상기 웨이퍼의 대향 측면에서 대칭인 다수의 노즐들을 제공하는 것이나, 복수개를 임의의 위치에 제공하는 것이 가능하다는 것을 인지하여야 한다.

<338> 직류 전압 또는 펄스 전압 같은 미리 결정된 전압이 전원(25)에 의해 애노드로서 사용되는 웨이퍼의 표면, 즉, 상호접속층(105)과, 캐소드로서의 캐소드 부재(E)에 공급될 때, 제 1 실시예에서 설명한 바와 같이, 상기 표면의 한 영역이 전해 연마된다.

<339> 상기 캐소드 부재(E)와 상기 웨이퍼(W) 사이의 거리가 너무 짧은 경우에, 상기 캐소드 부재와 상기 웨이퍼 사이에 개재된 전해액의 유통 작용이 충분하게 기능하지 않으며, 그래서, 이 거리를 특정값 보다 크게 설정하는 것이 바람직하다.

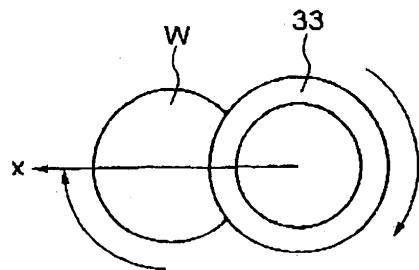

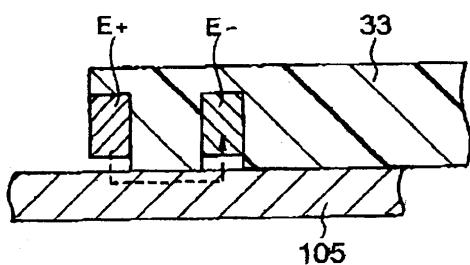

<340> 전해액이 상기 전해액 공급 노즐(30)에 의해 공급되는 영역에서, 연마 링 훈(33)을 구비한 샤프트(34)가 제공된다.

<341> 도 18b에 도시된 바와 같이, 상기 샤프트(34)는 웨이퍼(W)의 회전 방향과 동일한 방향으로 회전하도록 연마 링 훈(33)을 구동할 수 있다.

<342> 상기 연마 링 훈(33)도 도면에서 X-방향으로 상기 샤프트(34)의 이동으로 인해 이동할 수 있지만, 이는 캐소드 부재(E)의 이동과 링크된다. 또한, 도면에서 Z-방향으로의 샤프트(34)의 이동에 의해서 연마 링 훈(33)에 압력이 가해져 기계적 스크러빙 압력(mechanical scrubbing pressure)을 제공할 수 있다.

<343> 예를 들어, 상기 연마 링 훈(33)은 폴리비닐 아세탈 밸포체, 폴리우레탄 밸포체 등으로 제조된다. 일반적인 CMP 프로세스에 사용되는 연마 링 훈들이 채용될 수 있다. 예를 들어, 연마 링 훈(33)의 크기는 외부 직경 200mm, 내부 직경 160mm 및 두께 20mm이다.

<344> 여기서, 예를 들어, 구리를 위한 전해액으로서, 알루미늄 산화물, 실리콘 산화물, 세륨 산화물 또는 지르코늄 산화물 같은 연마 입자를 함유한 연마 슬러리를 추가로 포함하는 제 1 또는 제 2 실시예에서 설명된 전해액들을 사용하는 것이 가능하다. 이를 연마 입자들을 포함함으로써, 화학 기계 연마가 효과적으로 수행될수 있다.

<345> 예를 들어, 본 실시예에 따른 연마 장치는 전해 용리에 의한 연마를 위한 도시되지 않은 제어기에 의해 제거되는 전원(25)으로부터 상기 캐소드 부재(E; 전해액 공급 노즐 30)와, 상호접속층(105) 사이에 전압을 공급하고,

연마 슬러리 같은 연마 입자를 함유한 전해액을 사용하는 화학 기계 연마에 의해 연마 효율을 향상 또는 보조하도록 연마할 수 있다.

<346> 캐소드 부재(E)와, 전해액 공급 노즐(30) 및 연마 링 훈(33)은 이동 기구(27) 등에 의해 링크될 수 있고, 웨이퍼의 전체 표면에 걸쳐 연속적으로, 또는 단계적으로 이동될 수 있으며, 상기 전체 표면은 전해 용리에 의한 전해 연마와, 화학 기계 연마의 복합 연마에 의해 균일하게 연마될 수 있다.

<347> 본 실시예에 따른 연마 장치는 전해조 탱크(T)의 저면에 존재하는 전해액이 필터(F)를 경유하여 제트 펌프(P)에 의해 빨아 올려질 수 있고, 전해액 공급 노즐(30)에 의해 다시 공급될 수 있다. 이때, 전해액에 불필요한 성분들을 제거하고, 부족한 성분들을 추가하는 것이 가능하다.

<348> 또한, 제 2 실시예에서 설명된 바와 동일한 전원(25)이 사용될 수 있다.

<349> 또한, 제 2 실시예에서와 동일한 방식으로, 전류계에 의해 전해 전류를 검출하고, 상술한 전류계로부터의 전류값에 기초하여 캐소드 부재를 이동시키거나 전압의 인가를 정지시키는 것 같이 연마 장치의 동작을 제어할 수 있다.

<350> 비록, 도면에 예시되지는 않았지만, 상기 연마 장치는 청정실내에 설치된다. 청정실의 내 또는 외로 연마될 웨이퍼를 저장한 웨이퍼 카세트를 로딩 및 언로딩하기 위한 로딩/언로딩 포트가 청정실내에 제공된다. 또한, 이로딩/언로딩 포트를 통해 청정실내에 로딩된 웨이퍼 카세트와 상기 연마 장치 사이에서 웨이퍼를 전달하기 위한 웨이퍼 운송 로봇이 상기 로딩/언로딩 포트와 연마 장치 사이에 배열된다.

<351> 구리막의 두께나 두께에 상당하는 데이터를 측정하기 위한 측정 헤드를 가진 측정 수단이나, 구리막의 획득된 두께에 상당하는 데이터로부터 구리막의 목표 제거량을 산출하기 위한 산출 유닛 같은 상기 장치의 나머지 부분들의 동작 및 구성은 제 1 내지 제 8 실시예들에서와 동일한 방식으로 형성될 수 있다. 제 1 내지 제 8 실시예들에서와 동일한 효과가 얻어질 수 있다.

#### 제 11 실시예

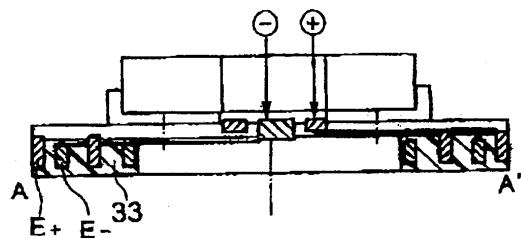

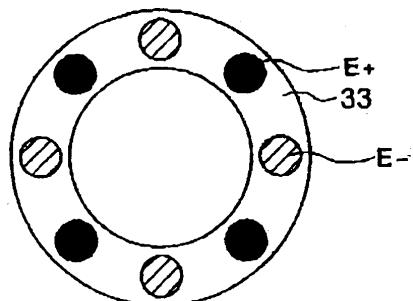

<353> 본 실시예에 따른 연마 장치는 제 10 실시예의 것과 실질적으로 동일하지만, 제 5 실시예에서와 동일한 방식으로, 도 19a의 개략적인 단면도와, 도 19b의 평면도(도 19a의 A-A'선을 따라 취한 단면에 대응함)에 도시된 바와 같이, 캐소드 부재들(E)로부터 특정 거리만큼 이격 배치된 링형 애노드 부재들(E<sub>r</sub>)이 연마될 표면에 대향하도록 배열된다. 예를 들어, 상기 캐소드 부재들(E)과 애노드 부재들(E<sub>r</sub>)은 크고 작은 직경들을 가진 링형 전극들로부터 형성된다. 이들 링들은 동심이며, 교대로 배열되어 있다.

<354> 캐소드 부재들(E)과 애노드 부재들(E<sub>r</sub>)은 양자 모두가 연마 링 훈(33) 내에 매립된다.

<355> 상기 연마 장치로 연마하기 위해서, 도시되지 않은 전해액 공급 노즐로부터 전해액이 공급되고, 연마될 표면, 즉, 상호접속층(105)과 캐소드 부재들(E)의 사이 및 상호접속층(105)과 애노드 부재들(E<sub>r</sub>)의 사이에 개재되고, 미리 결정된 양전압 또는 음전압이 도시되지 않은 전원에 의해 연마 링 훈(33)의 중앙에 있는 링형 단자(35b)와 단자(35a)를 통해 캐소드 부재들(E)과 애노드 부재들(E<sub>r</sub>)로 공급된다.

<356> 이때, 도 19c에 도시된 바와 같이, 캐소드 부재들(E)과 애노드 부재들(E<sub>r</sub>) 사이의 거리가 충분히 길게 설정되고, 상호접속층(105)과 애노드 부재들(E<sub>r</sub>) 사이의 거리와, 상호접속층(105)과 캐소드 부재들(E) 사이의 거리가 이에 비해 충분히 짧게 설정되는 경우에, 전류는 애노드 부재들(E<sub>r</sub>)로부터 캐소드 부재들(E)로 상호접속층(105)을 통해 흐르고, 따라서, 캐소드로서의 캐소드 부재들(E)과, 애노드로서의 상기 표면의 상기 영역들, 즉, 캐소드 부재들(E)에 대향하는 상호접속층(105)에 전압을 공급하는 경우와 동일한 효과들이 얻어질 수 있다.

<357> 결과적으로, 상기 캐소드 부재들(E)에 대향한 상호접속층(105)의 부분들의 표면으로부터 전해 용리에 의한 전해 연마가 가능하다.

<358> 또한, 연마 링 훈(33)에 의한 스크러빙에 의한 화학 기계 연마에 의해 연마하는 것이 가능하다. 이는 연마 효율을 개선 또는 보조한다.

<359> 전해액 공급 노즐과 연마 링 훈(33)을 링크시키고, 상술한 동작과 동시에, 이들을 상기 표면의 전체 표면에 걸

쳐 연속적으로, 또는 단계적으로 이동시킴으로써, 전체 표면이 전해 용리에 의한 전해 연마와, 화학 기계 연마의 복합 연마에 의해 균일하게 연마될 수 있다.

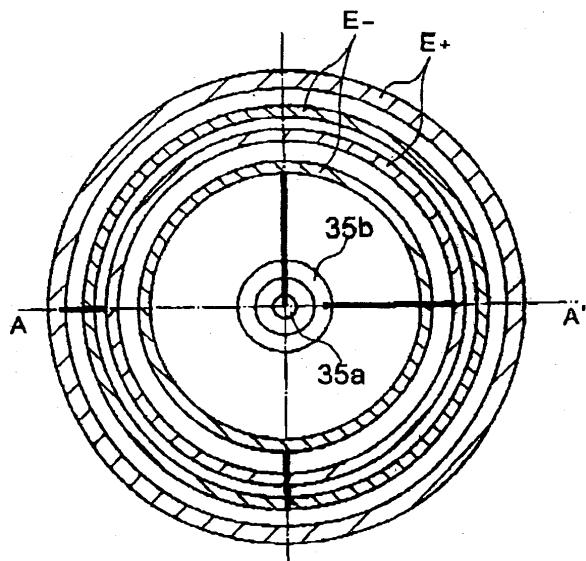

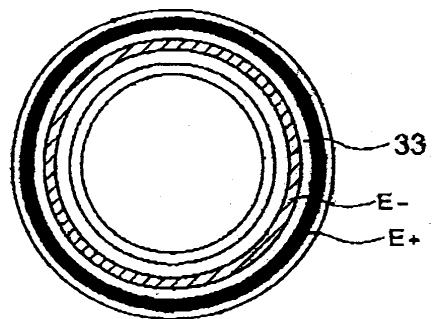

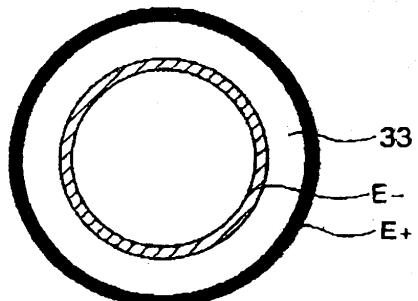

- <360> 상기 연마 링 휠(33) 내에 매립된 애노드 부재들( $E_+$ )과 캐소드 부재들( $E_-$ )에 전압을 공급하기 위한 배선 구조의 예는 도 20의 (a)의 평면도와, 상기 도 20의 (a)의 A-A 선을 따른 단면도인 도 20의 (b)에 도시되어 있다.

- <361> 즉, 도시되지 않은 영역내에 캐소드 부재들( $E_-$ )과 애노드 부재들( $E_+$ )이 매립된 연마 링 휠(33)을 유지하기 위해 휠 홀더(36)의 중앙에 제공된 개구내로 폴리 염화 비닐 등으로 이루어진 단자 홀더(37)가 장착되고, 플라스틱 또는 다른 스크류들(37a)에 의해 고정된다.

- <362> 상기 단자(35a) 및 링형 단자(35b)는 단자 홀더(37) 내에 매립된다. 슬립 링(slip ring)에 의해 전원으로부터 돌출 접촉 프로브(38)를 경유하여 전압이 공급된다.

- <363> 단자 홀더(37)의 후방측에는 단자들(39a, 39b)이 단자 홀더(37)를 관통하는 도전성 스크류들(40a, 40b)을 경유하여 단자 35b와 링형 단자 35b에 접속된다. 상기 단자들(39a, 39b)은 도시되지 않은 영역에서, 캐소드 부재들( $E_-$ )과 애노드 부재들( $E_+$ )에 접속된다.

- <364> 상기 단자들(39a, 39b)의 영역은 플라스틱 덮개(41)에 의해 보호된다. 상기 플라스틱 덮개(41)는 플라스틱 스크류들(plastic screws)(42)에 의해 휠 홀더(36)에 고정된다.

- <365> 상술한 캐소드 부재들( $E_-$ )과 애노드 부재들( $E_+$ )이 파묻혀 있는 연마 링 휠의 레이아웃의 예가 하기에 도시되어 있다.

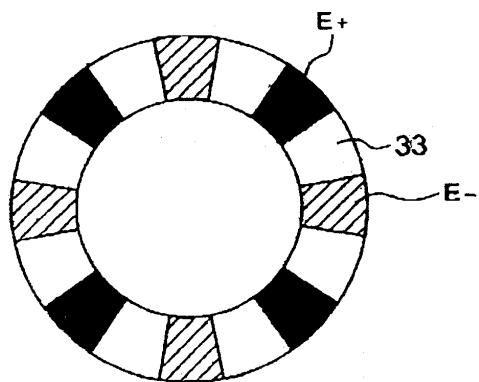

- <366> 도 21a는 하나의 대직경 애노드 부재( $E_+$ )가 소직경 캐소드 부재( $E_-$ ) 둘레에 배열되어 있는 구조를 도시하고 있다.

- <367> 도 21b는 도 21a와 마찬가지로, 하나의 대직경 애노드 부재( $E_+$ )가 연마 링 휠(33) 둘레에 배열되어 있고, 소직경 캐소드 부재( $E_-$ )가 연마 링 휠(33)내측에 배열되어 있는 구조를 도시하고 있다.

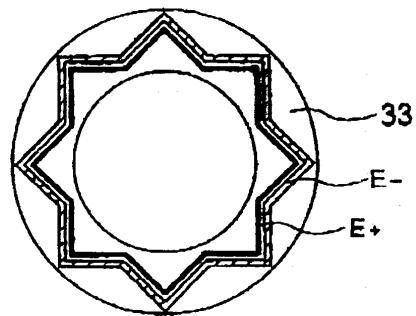

- <368> 도 21c는 상기 캐소드 부재( $E_-$ )와 애노드 부재( $E_+$ )가 별 형상(star shapes)로 배열되어 있는 구조를 도시하고 있다.

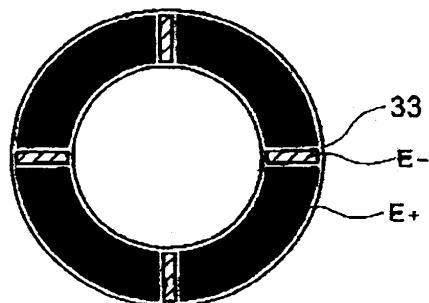

- <369> 도 22a는 캐소드 부재들( $E_-$ )이 연마 링 휠(33)의 중앙에서 수직으로 교차하는 2개의 라인들상에 배열되어 있고, 애노드 부재들( $E_+$ )이 나머지 영역들에 배열되어 있는 구조를 도시하고 있다.

- <370> 도 22b는 애노드 부재들( $E_+$ )에 의해 둘러싸여진 원형 캐소드 부재들( $E_-$ )의 패턴들이 연마 링 휠(33)의 영역상에 배열되어 있는 구조를 도시하고 있다.

- <371> 도 22c는 원형 캐소드 부재들( $E_-$ )과 애노드 부재들( $E_+$ )이 상기 연마 링 휠(33)의 영역상에 교대로 배열되어 있는 구조를 도시하고 있다.

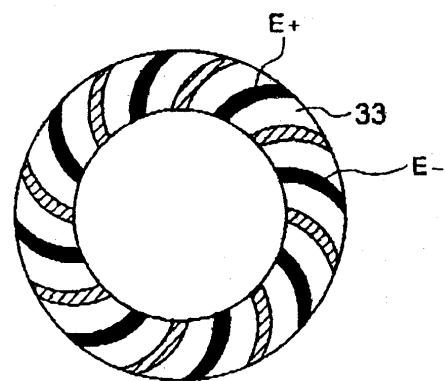

- <372> 도 23a는 상기 연마 링 휠(33)의 영역이 직경방향으로 구획들로 분할되고, 캐소드 부재들( $E_-$ )과 애노드 부재들( $E_+$ )이 교대로 이 구획들에 배열되어 있는 구조를 도시하고 있다.

- <373> 도 23b는 캐소드 부재들( $E_-$ )과 애노드 부재들( $E_+$ )이 상기 연마 링 휠(33)의 영역상에 나선형으로 교대로 배열되어 있는 구조를 도시하고 있다.

- <374> 본 실시예에서, 애노드 부재들의 물질과 같은 나머지 구성은 제 5 실시예의 구성과 유사하다. 또한, 예를 들어, 구리막의 두께나 그 두께에 상당하는 데이터를 측정하기 위한 측정 헤드가 제공된 측정 수단, 및 구리막의 획득된 두께에 상당하는 데이터로부터 구리막의 목표 제거량을 산출하기 위한 산출 유닛의 동작 및 구성은 제 1 및 제 2 실시예들에서와 동일한 방식으로 이루어질 수 있다. 제 1 및 제 2 실시예들에서와 동일한 효과가 얻어질 수 있다.

- <375> 제 12 실시예

- <376> 다음에, 본 발명의 연마 방법 및 장치를 사용하여 구리 상호접속부들을 가진 반도체 디바이스에서 이중 다마센

프로세스에 의해 구리 상호접속부들을 형성하는 프로세스를 설명한다.

<377> 먼저, 도 2b까지의 단계들과 동일한 방식으로, 충간 절연막(102)이 반도체 기판(101)상에 형성되고, 접촉 홀들과 상호접속 흄들(M)이 형성되고, 그후, 배리어 금속막(103)과 충간 접속층(105)이 형성된다.

<378> 상호접속층(105)의 표면은 접촉 홀들(CH)과 상호접속 흄들(M)을 매립하면서 유발된, 예를 들어, 약 800nm의 높이를 가진 요철이 형성되어 있다.

<379> 상기 프로세스는 종래기술과 동일한 방식으로 수행되지만, 본 발명의 연마 방법에서는 충간 절연막(102)상에 존재하는 상호접속층(105)의 잉여부들이 화학 기계 연마에 의해 제거되지 않고, 연마될 표면에 비해 작은 크기의 캐소드 부재를 사용한 양극 산화와, 킬레이트제를 사용한 산화된 구리의 킬레이트화에 의해 제거된다.

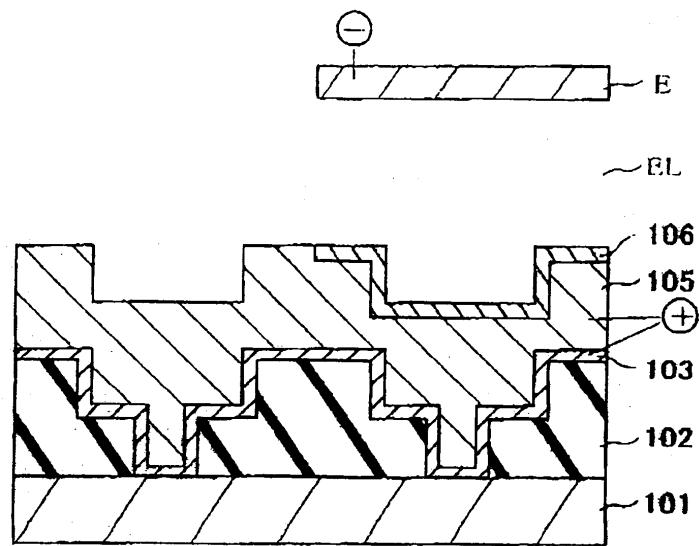

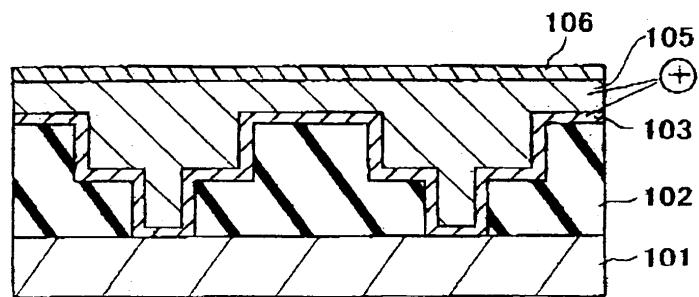

<380> 즉, 도 24a에 도시된 바와 같이, 연마될 표면, 즉, 상호접속층(105)에 비해 상대적으로 작은 크기의 캐소드 부재(E)가 상기 상호접속층(105)의 한 영역에 대향하도록 배열되고, 킬레이트제를 포함하는 전해액(EL)이 적어도, 상기 상호접속층(105)의 상기 영역과 캐소드 부재(E) 사이에 개재된다.

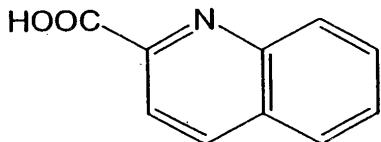

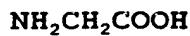

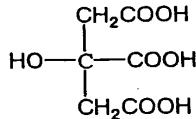

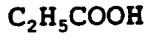

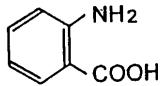

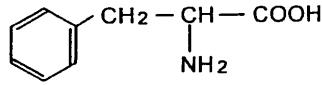

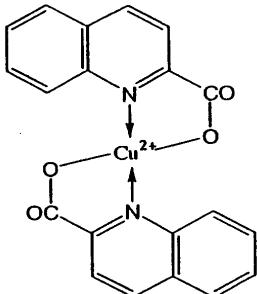

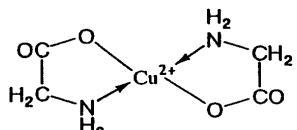

<381> 여기서, 킬레이트제로서, 예를 들어, 화학식 1의 퀴날디니산(quinaldinic acid)과, 화학식 2의 글리신(glycine)과, 화학식 3의 시트릭산(citric acid)과, 화학식 4의 옥살릭산(oxalic acid)과, 화학식 5의 프로피오닉산(propionic acid)과, 화학식 6의 안트라닐릭산(anthranilic acid)과, 화학식 7의 페닐랄라닌(phenylalanine) 등이 사용될 수 있다.

(1)

(2)

(3)

(4)

(5)

(6)

(7)

<389> 다음에, 캐소드로서 캐소드 부재(E)와, 애노드로서 상호접속층(105) 및 배리어 금속층(103)을 사용하여 전압이 공급된다.

<390> 이때, 캐소드 부재(E)에 대향한 영역에서, 애노드, 즉, 구리막(105)은 양극 산화에 의해 산화되어 CuO를 형성한다. 여기서, 상호접속층(105)의 표면상의 돌출부와 캐소드 부재(E) 사이의 거리(d1)는 상호접속층(105)의 표면상의 오목부와, 캐소드 부재(E) 사이의 거리(d2) 보다 짧고, 따라서, 캐소드 부재(E)와 상호접속층(105) 사이의 전위차가 일정할 때, 상기 돌출부에서의 전류 밀도가 상기 오목부에서의 전류 밀도 보다 크며, 따라서, 양극 산화가 가속된다.

<391> 도 24b에 도시된 바와 같이, 산화 구리막(CuO; 105)의 표면은 전해액내의 킬레이트제에 의해 킬레이트화된다.

<392> 퀼레이트제로서 퀴날딕산이 사용되었을 때, 화학식 8의 퀼레이트화 화합물로 이루어진 막이 형성된다. 글리신이 사용되었을 때, 화학식 9의 퀼레이트 화합물로 이루어진 막이 형성된다.

(8)

(9)

&lt;393&gt;

&lt;395&gt;

&lt;396&gt;

&lt;397&gt;

&lt;398&gt;

&lt;399&gt;

&lt;400&gt;

&lt;401&gt;

&lt;402&gt;

&lt;403&gt;

&lt;404&gt;

&lt;405&gt;

&lt;406&gt;

&lt;407&gt;

이들 퀼레이트 막들(106)은 구리보다 높은 전기 저항과, 매우 낮은 기계적 강도를 가지며, 그러므로, 부서지기 쉬운 막들이다.

이 방식으로 퀼레이트막(106)이 상호접속층(105)의 표면상에 형성되면, 구리막(105)으로부터 전해액(EL)을 경유하여 캐소드 부재(E)로의 전류값은 상기 영역에서 감소된다.

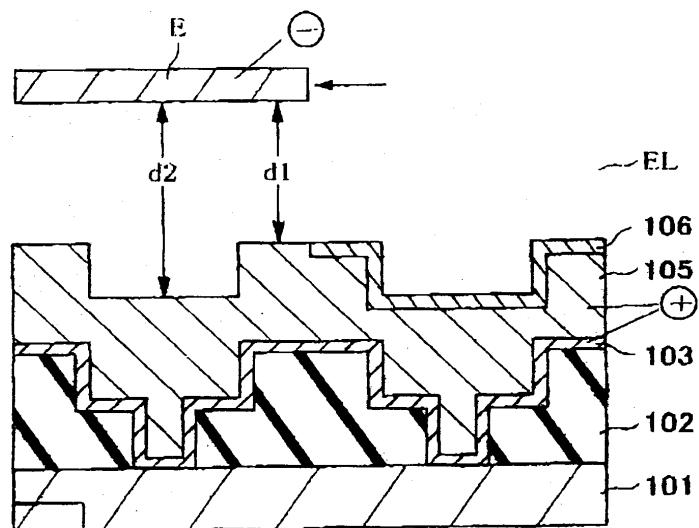

다음에, 도 25a에 도시된 바와 같이, 상기 캐소드 부재(E)는 상기 상호접속층(105)의 표면의 퀼레이트화가 완료된 영역으로부터 다른 영역으로 이동된다.

이 다른 영역에서는, 상기 상호접속층(105)이 퀼레이트화되지 않았기 때문에, 상기 캐소드 부재(E)가 돌출부에 대한 거리가 d1이고, 오목부에 대한 거리가 d2인 상태로, 요철을 가진 상호접속층(105)과 대향한다.

다음에, 도 24b에 도시된 바와 같이, 상호접속층(105)의 이전 영역에서의 양극 산화 및 퀼레이트화와 동일하게, 도 25b에 도시된 바와 같이 상기 다른 영역에서 상호접속층(105)이 양극 산화에 의해 산화되고, 퀼레이트화된다.

마찬가지로 이 단계에서, 상술한바와 동일하게, 상기 상호접속층(105)은 선택적으로 상기 돌출부들로부터 양극 산화에 의해 산화된다. 상기 상호접속층(105)의 모든 다른 영역들이 양극 산화에 의해 산화되고 퀼레이트화될 때까지 상술한 바와 유사하게 상기 상호접속층의 다른 영역들에서 양극 산화 및 퀼레이트화가 수행되게 된다.

다음에, 도 26a에 도시된 바와 같이, 상기 상호접속층(105)의 표면상에 형성된 퀼레이트막(106)의 돌출부들이 와이핑, 기계적 연마 등에 의해 선택적으로 제거된다.

상기 퀼레이트막(106)의 돌출부들을 기계적 연마에 의해 제거할 때, 상기 전해액(EL)은 제 10 실시예에서 설명한 바와 같은 연마 슬러리를 포함할 수도 있다.

또한, 상기 퀼레이트막(106)의 기계적 강도가 매우 낮기 때문에, 기판(101)에 진동을 인가하거나, 전해액을 분사하는 것에 의해서도 용이하게 제거될 수 있다.

이때, 낮은 전기 저항의 상호접속층(105)의 돌출부들이 전해액에 노출되어 있기 때문에, 상기 상호접속층(105)으로부터 전해액(EL)을 경유하여 캐소드 부재(E)로 흐르는 전류값은 증가된다.

다음에, 도 26b에 도시된 바와 같이, 캐소드 부재(E)가 상기 표면의 한 영역에 대향하게 되고, 전압이 인가되면, 전해액에 노출된 상호접속층(105)의 돌출부들은 낮은 전기 저항과 캐소드 부재(E)대 대한 짧은 거리를 가지고 있기 때문에, 이들은 양극 산화에 의해 강하게 산화되며, 산화된 구리는 퀼레이트화된다.

이 방식에서, 캐소드 부재(E)는 이동되고, 상기 양극 산화 및 퀼레이트화가 동일한 방식으로 다른 영역들에서 수행되어 상호접속층(105)의 전체 표면을 다시 양극 산화 및 퀼레이트화하게 된다.

다음에, 퀼레이트막(106)의 돌출부들은 앞서 언급한 와이핑, 기계 연마 등에 의해 선택적으로 제거되고, 노출된 구리막(105)은 강하게 산화 및 퀼레이트화되며, 퀼레이트막(106)의 돌출부들은 선택적으로 제거된다. 이 단계들

이 그후 반복된다.

<408> 상호접속층(105)으로부터 전해액(EL)을 경유하여 캐소드 부재(E)로 흐르는 전류는 각각 킬레이트막(106)의 제거 및 형성과 함께 반복적으로 상승 및 하강한다.

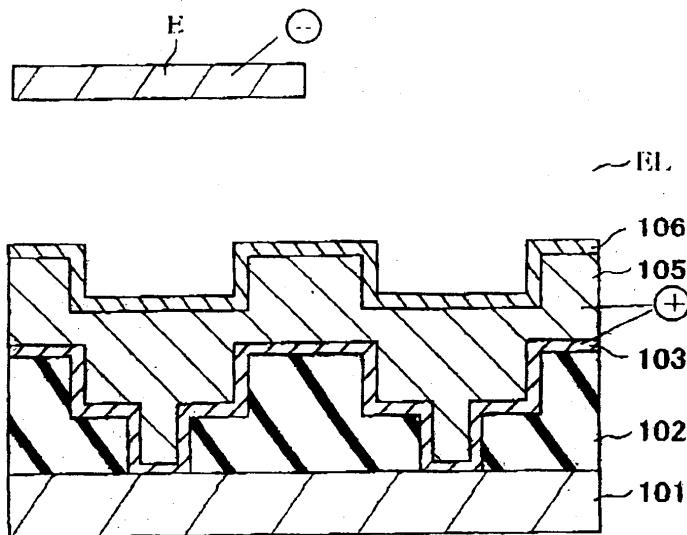

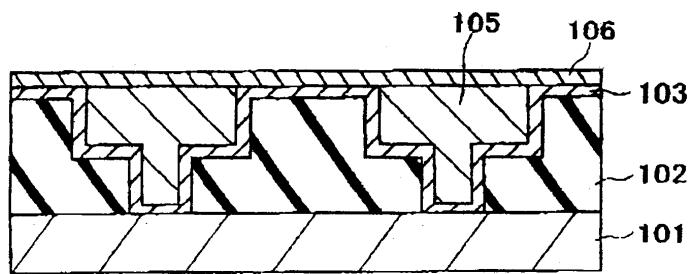

<409> 캐소드 부재(E)를 이동시키면서 전체 표면에 걸쳐 양극 산화 및 킬레이트화의 단계와, 상기 킬레이트막의 돌출부들의 선택적인 제거 단계를 반복함으로써, 도 27a에 도시된 바와 같이, 상호접속층(105)이 평탄화된다.

<410> 다음에, 도 27b에 도시된 바와 같이, 배리어 금속막(103)상의 상호접속층(105)의 잉여부들이 완전히 사라질 때까지, 양극 산화에 의한 킬레이트막의 형성 단계 및 킬레이트막의 제거 단계가 상기 평탄화된 상호접속층(105)의 전체 표면에 걸쳐 계속된다.

<411> 다음에, 도 27c에 도시된 바와 같이, 전체 상호접속층(105)의 특정량이 예를 들어, 상술한 와이핑, 기계적 연마 등에 의해 제거되고, 배리어 금속막(103)의 표면을 노출시킨다.

<412> 양극 산화에 의한 킬레이트막의 형성 및 킬레이트막의 제거를 통한 상호접속층(105)의 평탄화 연마는 상기 상호접속층(105)의 목표량이 제거될 때까지 수행된다.

<413> 여기서, 한 영역에서 제거될 상호접속층(105)의 목표량은 상호접속층(105)에 대한 두께 측정기에 의해 측정된 두께 데이터로부터 독립적 단계에서 먼저 산출되거나, 상술한 전해 연마 단계 동안 측정 및 산출된다.

<414> 또한, 양극 산화의 전해 전류를 측정하고, 제거될 상호접속층(105)의 잔여량에 관한 양으로서 상기 전해 전류를 사용하는 것이 가능하다.

<415> 예를 들어, 상기 킬레이트막(106)의 제거 이후에, 상기 전해 전류가 모니터링되는 경우에, 상기 킬레이트막(106)의 제거 이후의 상기 전류는 상호접속층(105) 보다 높은 전기 저항을 가진 배리어막(103)이 노출될 때 감소하기 시작한다.

<416> 따라서, 킬레이트막의 제거 이후 전류가 감소하기 시작하는 시점에서, 전압의 인가를 중단하여 양극 산화에 의한 킬레이트화를 정지시킨다.

<417> 다음에, 상기 접촉 홀들 및 상호접속 홈들의 외측에 증착된 배리어 금속막이 제거된다.

<418> 상술한 단계들로 인하여, 반도체 디바이스에 적합한 접촉 홀 접속부들 및 구리 상호접속부들이 이중 다마센 프로세스에 의해 동시에 형성된다.

<419> 구리 상호접속부들을 가진 반도체 디바이스에서 이중 다마센 프로세스에 의한 구리 상호접속부들의 형성 프로세스에 사용된 본 실시예의 연마 방법에 따라서, 상기 표면상에 도금된 막의 두께의 변화도를 먼저 측정함으로써 얻어진 조건들에 의해 필요한 제거량의 분포를 설정하고, 이에 따라, 상호접속부들의 형성을 위한 필요에 따라 정확한 양만큼 연마에 의해 상호접속막을 제거하는 것이 가능하다.

<420> 또한, 상기 표면상에 중첩된 킬레이트화로 인한 부분적 제거량들로 구성된 전체 표면의 제거량들의 실제 분포가 사전설정된 제거량들의 분포화 일치되도록 상기 캐소드 부재를 이동시킴으로써, 상호접속부들의 형성을 위한 필요에 따라 전체 표면에 걸쳐 정확한 양만큼 연마에 의해 상호접속막을 제거하는 것이 가능하다.

<421> 또한, 종래의 CMP법과는 달리, 상기 표면상의 상호접속막이 양극 산화에 의한 킬레이트막의 형성과 킬레이트막의 제거에 의해 연마 및 제거되기 때문에, 더 이상 상기 막상에 압력을 가할 필요가 없으므로, 막의 균열의 발생 또는 하부 층간 절연막에 대한 손상이 억제된다.

<422> 또한, 와이핑에 의해 킬레이트막을 제거할 때, 상호접속층에 가해지는 압력은 종래의 화학 기계 연마에서 보다 현저히 작으므로, 상호접속층의 균열의 발생 또는 하부 층간 절연막에 대한 손상이 억제될 수 있다.

<423> 공급된 전해액내에 연마 슬러리를 포함시킴으로써, 화학 기계 연마에 의해 킬레이트막을 연마하여 연마 효율을 향상 또는 보조하는 것이 가능하다.

<424> 또한, 양극 산화에 의한 킬레이트막의 형성과 상기 킬레이트막의 제거에 의한 연마 및 제거의 단계에서, 상기 상호접속층의 표면상에 형성된 요철의 돌출부들이 선택적으로 제거될 수 있으므로, 상기 표면이 효과적으로 평탄화된다.

<425> 상술한 바와 같이, 본 발명의 연마 방법에 따라서, 연마에 의해 막을 평탄화할 때, 초기 요철은 용이하게 평탄화되고, 잉여 구리막의 양호한 제거 효율을 얻을 수 있으며, 하부 층간 절연막에 대한 손상이 억제될 수 있다.

- <426> 또한, 본 실시예에서, 상기 전해액에 폴리옥시에틸렌알킬에테르(polyoxyethylenealkylether), 알킬벤젠설포네이트(alkylbenzenesulfonate) 또는 다른 계면활성제를 추가하는 것이 바람직하다.

- <427> 도 28에 도시된 바와 같이, 전해액내의 계면활성제(SA)는 상기 구리 상호접속층의 표면상에 형성된 불용성 킬레이트막(106)을 둘러싸고, 미셀화한다. 형성된 불용성 복합 미셀들(insoluble complex micelles)(Z)은 상호접속층의 표면으로부터 용이하게 분리될 수 있고, 그래서, 상기 킬레이트막의 제거가 미셀화된 불용성 복합물들로 인해 보다 용이해진다. 또한, 돌출부들의 선택적인 제거가 보다 용이해진다.

- <428> 상기 상호접속층 연마의 프로세스를 위한 연마 장치에서, 제 2 내지 제 11 실시예들에 설명된 것들과 실질적으로 동일한 장치가 사용될 수 있다.

- <429> 상술한 연마 장치들의 것들과의 차이점은 킬레이트제를 함유하는 전해액 또는 추가로 계면활성제를 함유하는 전해액이 공급될 전해액으로서 사용되고, 캐소드 부재에 대향하는 연마될 표면이 전해 용리되는 것이 아니라 양극 산화된다는 것이다. 연마될 표면의 표면층이 양극 산화에 의해 산화될 때, 산화된 표면은 전해액내의 킬레이트제와 반응하여 킬레이트막을 형성한다. 그후, 상기 표면은 낮은 기계적 강도의 킬레이트막을 상술한 방법들에 의해 제거함으로써 연마되게 된다.

- <430> 또한, 예를 들어, 이 프로세스는, 애노드가 특정 거리로 캐소드 부재로부터 이격되도록 배열되어 있는 도 11에 도시된 장치나, 연마 링 훈을 채용하는 도 18에 도시된 바와 같은 장치에도 적용될 수 있다.

- <431> 그러나, 스크리버 또는 연마 링 훈을 구비한 장치에서 다공성 실리카와 같은 낮은 기계적 강도의 절연막상의 상호접속층을 연마할 때, 스크리버 또는 연마 링 훈에 의한 통상적인 화학 기계 연마에서와 같이 압력을 가하는 것은 바람직하지 못하다. 와이핑의 압력의 범위로 압력을 제한하는 것이 바람직하다.

- <432> 또한, 예를 들어, 제 10 실시예에서와 같이, 제트 펌프(P)에 의해 필터(F)를 경유하여 전해조 탱크(T)의 기저에 있는 전해액을 빨아 올려서 이를 다시 전해액 공급 노즐(30)에 의해 공급할 때, 불용성 킬레이트 또는 미셀들이나 전해액내의 다른 불필요한 성분들을 제거하고, 퀴날덕산 또는 소모되어 불충분해진 다른 성분들을 추가하는 것이 가능하다.

- <433> 본 실시예에서는, 상술한 바와 같이, 제 2 내지 제 11 실시예들에 설명된 연마 장치들을 사용하는 것이 가능하다. 제 2 내지 제 11 실시예들에서 얻어지는 바와 동일한 효과들이 얻어질 수 있다.

- <434> 제 13 실시예

- <435> 도 29는 상기 상호접속층의 형성 프로세스에 사용되는 도금 장치의 구조의 개략도이다.

- <436> 즉, 본 실시예의 도금 장치는 구리막이 그 위에 증착되게 될 도금될 웨이퍼(W; 하기에, "웨이퍼"라고도 지칭함)를 지지하기 위한 테이블(10)과, 상기 테이블(10)상에 제공된 진공 척 같은 고정 수단(11)과, 연산 유닛(22)과, 제어기(23)와, 제어 패널(24)과, 전원(25)과, 전류계(26)와, 애노드 부재(E')와, 상기 애노드 부재(E')의 이동 기구(27) 및 전해 도금액(electrolytic plating solution)(EL)을 저장하는 전해 도금조 탱크(T)를 포함한다.

- <437> 예를 들어, 상기 웨이퍼(W)는 회전 테이블(10)상의 진공 척 같은 고정 수단(11)에 의해 고정된다. 고정 수단으로서, 진공 척에 부가하여, 에지 클램프나 기계적 클램프를 사용할 수도 있다. 에지 클램프를 사용하는 경우에, 상기 웨이퍼의 가장자리부를 접지하는 클램프부를 통해 캐소드로서 기능하는 웨이퍼에 전류가 공급될 수 있다.

- <438> 상기 웨이퍼(W)는 테이블(10)과 함께 전해 도금조 탱크(T)내의 전해도금액(EL)내에 침적된다.

- <439> 예를 들어, 테이블(10)이 회전 구동되는 동안, 상기 웨이퍼(W)의 표면 보다 상대적으로 작은 애노드 부재(E')는 상기 표면의 한 영역에 대향하도록 배열된다. 직류 전압 또는 펄스 전압 같은 미리 결정된 전압이 전원에 의해, 캐소드로서의 웨이퍼의 표면, 즉, 배리어 금속막과, 애노드로서의 애노드 부재(E')에 공급된다.

- <440> 이런 전압이 인가되는 경우에, 상기 표면의 상기 영역은 도금된다.

- <441> 이때, 전해 도금 전류가 전류계(26)에 의해 모니터링되고, 연산 유닛(22)으로 출력된다. 상기 연산 유닛(22)은 상기 입력 전류값을 점증적으로 가산(적분)하고, 상기 얻어진 전류의 적분값을 제어기(23)로 출력한다.

- <442> 상기 제어기(23)는 상기 전류의 적분값을 사전설정된 값과 비교하고, 상기 사전설정된 값이 도달되었을 때, 필요한 두께의 구리막이 형성된 것으로 판단한다. 그후, 상기 도금된면의 상기 영역에서의 도금 처리를 종료하고, 이동 기구(27)를 제어하여, 상기 애노드 부재(E')를 이 영역으로부터 다른 영역으로 이동시킨다.

- <443> 또한, 상기 제어기(23)는 상기 제어 패널(24)로부터의 외부 입력을 수신할 수 있다.

- <444> 예를 들어, 도 30a에 도시된 바와 같이 전해 도금 전류의 프로파일을 보면, 시간  $t_1$ 에서 전해 도금 반응이 시작할 때 전류값이 급작스럽게 증가하고, 그후, 변동의 범위내에서 안정해진다.

- <445> 도 30b는 상기 전류의 적분에 의해 얻어진 그래프이다. 상기 전류의 적분값은 증착 두께에 실질적으로 비례한다. 시간  $t_1$ 에서 전해 도금 반응이 시작되고, 전류의 적분값이 점진적으로 상승되며, 단조적으로 증가된다. 여기서, 적분값이 미리 결정된 두께에 상당하는 사전설정된 값(V)에 도달하는 시점에서, 전압의 인자가 중단되어 이 영역에서의 도금을 정지시킨다.

- <446> 이 방식에서, 상기 테이블이 회전되는 동안, 상기 애노드 부재(E')가 이동 기구(27)에 의해 일 방향(도 29의 X-방향)으로 스캔되게되어 전체 표면을 전해도금하게 된다. 상기 애노드 부재(E')는 이동 기구(27)에 의해 연속적으로 또는 단계적으로 이동될 수 있다.