(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.<sup>6</sup>

H01L 29/78

H01L 21/336

**H01L 21/60**

(45) 공고일자 2000년04월15일

(11) 등록번호 10-0254025

(24) 등록일자 2000년01월28일

(21) 출원번호 10-1992-0008675

(65) 공개번호 특 1992-0022562

(22) 출원일자 1992년05월22일

(43) 공개일자 1992년12월19일

(30) 우선권주장 707,365 1991년05월30일 미국(US)

(73) 특허권자 아메리칸 텔리폰 앤드 텔레그라프 캠퍼니 존 제이. 키세인

미합중국, 뉴욕 10013-2412, 뉴욕, 애비뉴 오브디아메리카즈 32

(72) 발명자 리쿠오-후야

미합중국, 펜실베니아 18106, 웨스코스빌, 로워 맥컨지 타운쉽, 컨트리 클럽 로드 1308

성잔메

미합중국, 펜실베니아 18103, 엘린타운, 로워 맥컨지 타운쉽, 반사이드 로드 1109

(74) 대리인 이병호

**심사관 : 오세준****(54) 반도체 집적 회로 제조 방법****요약**

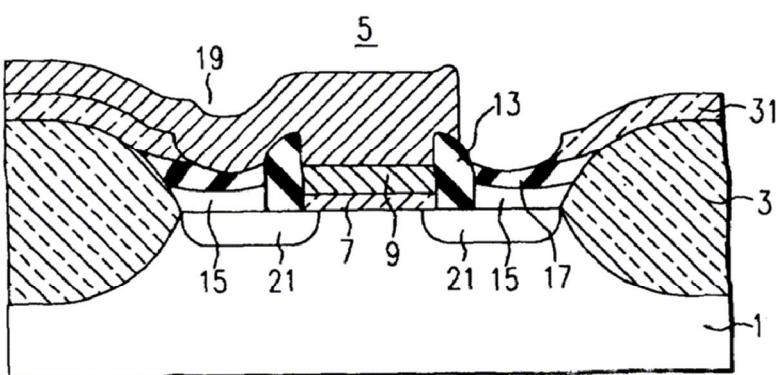

전계 효과 트랜지스터와의 게이트 접촉부(19)는 질화물 상부층(11)을 가진 게이트 구조(5)와 필드 산화물 영역(3) 사이에 폴리실리콘 플러그(15)를 형성함으로써 소스/드레인 영역(21) 위에 열려 있다. 접촉부(19)는 게이트구조(5)와 폴리실리콘 플러그(15)를 산화, 에칭하여 형성된다. 산화물 층(31)은 에칭 전증착된다. 상기 에칭 단계에 의해 게이트 접촉부가 개방되나 플러그(15)내 실리콘을 노출하지는 못하는데, 이것은 폴리실리콘 플러그(15)의 상이한 산화율과 게이트 구조(5) 상부의 물질이 상이한 두께를 가지는 산화물층을 만들기 때문이다. 질화물은 제거되고 접촉부가 게이트 구조(5)에 형성된다.

**대표도****형세서**

[발명의 명칭]

반도체 집적회로 제조 방법

[도면의 간단한 설명]

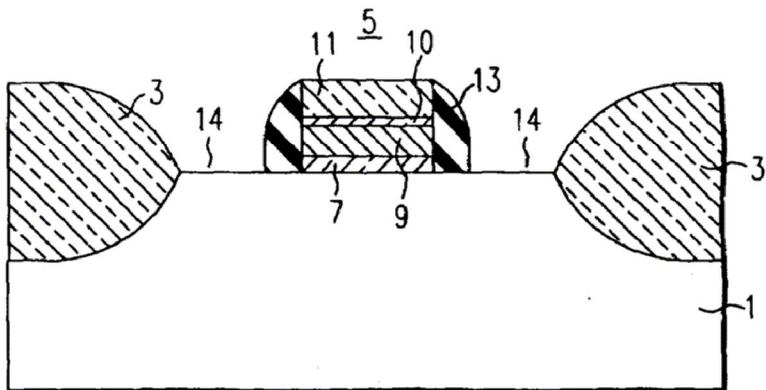

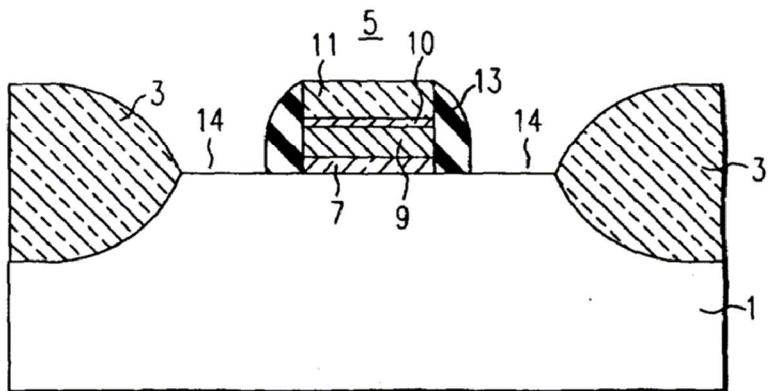

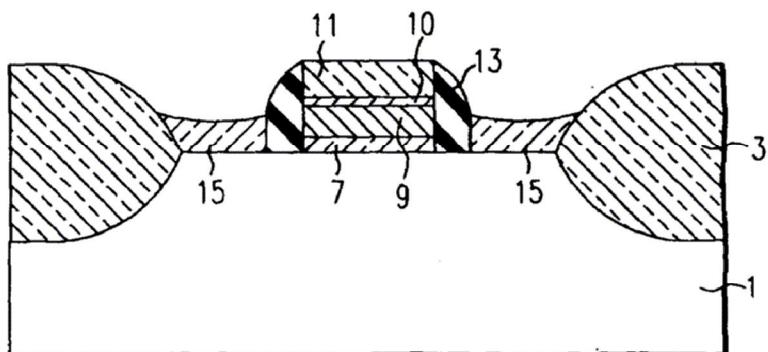

제 1 도 내지 제 6 도는 본 발명에 의한 제조 공정의 여러 단계에서의 집적 회로 부분의 단면도

\* 도면의 주요부분에 대한 부호의 설명

1 : 기판

3 : 절연 영역

5 : 게이트 구조

7 : 산화물

## 13 : 절연 측벽

## [발명의 상세한 설명]

본 발명은 자기 정렬된 게이트 접촉부를 형성하는 집적 회로의 제조방법에 관한 것이다.

집적 회로에 존재하는 구성 요소들의 수가 증대함에 따라, 개개의 집적회로 칩들이 매우 크게 되지 않도록 개개의 구성 요소들의 사이즈를 축소하기 위한 연구가 당업자들에 의해서 행해졌다. 전계 효과 트랜지스터와 같은 통상의 구성 요소와 관련해서, 이러한 연구는 소스/드레인 영역 또는 채널 길이의 사이즈, 즉 소스 및 드레인 영역간 간격을 축소하는 것이며, 이렇게 함으로써 보다 작은 트랜지스터 제조가 가능케 된다. 칩 사이즈를 축소하기 위한 또 다른방법은 트랜지스터 소자들과의 보다 콤팩트한 전기적 접촉을 이용하는 것이다. 예를 들어, 게이트 구조는 개개의 디바이스들을 전기적으로 분리하는 필드산화물상의 런너(runner) 이외의 소스/드레인 영역 근방에서 접촉될 수 있다.

예를 들면, 디바이스 및 피쳐(feature) 사이즈의 축소를 도모하는 연구들의 설명에 대해서는 1989년 4월 18일에 특허 허여된 Lynch 등의 미국 특허 제 4,822,754호와 1989년 7월 4일에 특허 허여된 Lee 등의 미국 특허 제 4,844,776호를 참조하라.

피쳐 사이즈를 축소하는 것, 즉 디바이스 규격을 간단히 축적 설계하는 것 이외에, 디바이스들 또는 집적 회로 구성 요소들의 구조적 변경들은 여러이유로 인하여 바람직하다. 예를 들면 소스/드레인 영역은 통상 실리콘 기판내로의 이온 주입(임플란트) 또는 불순물을 확산에 의해 형성된다. 기판이란 용어는 최하부에 놓여 있으며 다른 물질을 지지하는 물질을 의미하는데 사용된다. 이처럼 기판이란 용어는 에피택셜층을 포함하는 것을 의미한다.

불순물 주입된 소스/드레인 구조와 관련한 어떤 문제점은 최소한 이론적으로 융기된 소스/드레인 영역이라 칭해지는 영역에 의해서 제거되거나 완화될 수 있다.

반도체 집적회로들은 절연 영역 사이의 기판과 게이트 구조상에 절연영역을 형성하는 것을 포함하는 방법에 의해서 제조된다. 게이트 구조 및 절연영역들 사이에는 영역들이 있다. 게이트 구조는 전도층, 절연 측벽과 제 1 물질로 이루어진 절연 상부 층을 가진다. 제 2 물질을 포함하는 플러그는 게이트 구조 및 절연 영역 사이에 형성되고, 게이트 구조의 노출 표면과 플러그가 산화된다. 양호한 실시예에 있어서, 산화물 층은 표면상에 증착된다. 즉 블랜켓(blanket) 증착된다. 종래의 패턴화를 이용하여 게이트 구조의 선택부분을 노출하고, 이 패턴화에 이어서 제 1 물질의 상부상에서 산화물 부분을 제거하나 제 2 물질의 상부상에서 즉, 플러그상에서 약간의 산화물을 남기는 예정 공정이 행해진다. 제 1 물질의 약간은 제거될 수 있다. 게이트 구조의 노출된 부분상의 제 1 물질의 잔류 부분은 예정에 의해 제거됨으로써, 전도물질이 노출된다. 이제 전기 접촉부가 절연 영역까지 연장하는 게이트 구조에서 형성된다. 플러그상의 산화물을 의해 전기 접촉부는 소스/드레인 영역에 형성되지 않으며, 게이트 구조의 여전히 덮혀진 부분상에 형성되는 게이트를 교차하는 국부적 상호 접속이 이루어진다.

또 다른 양호한 실시예에 있어서, 제 1 및 제 2 물질의 두 산화물을 사이의 차이 또는 산화 후 예정 선택도 사이의 차이가 있다. 일실시예에 있어서, 절연 영역들은 필드 산화물을 영역들을 포함한다. 또 다른 양호한 실시예에 있어서, 제 1물질은 실리콘 질화물(silicon nitride)을 포함하며, 제 2 물질은 실리콘을 포함한다. 또 다른 실시예에 있어서, 폴리실리콘 플러그로 불순물이 주입(임플란트)됨으로써, 불순물 영역이 형성되고, 이 산화 단계에 의해 불순물은 전계 효과 트랜지스터의 소스/드레인 영역을 형성하는 기판으로 불순물이 확산된다. 또 다른 바람직한 실시예에 있어서, 전도 물질을 노출하기 위해 사용된 예정은 제 1 및 제 2 물질과 제 2 물질상의 산화물을 사이에서 높은 선택도를 가진다. 그러나, 또 다른 바람직한 실시예에 있어서, 게이트 구조는 제 2 물질층을 가지며, 이 층은 제 1 물질층과 전도층 사이에 존재한다.

이후, 본 발명의 보다 상세한 설명을 위해 첨부된 도면을 참조하여 설명하기로 한다.

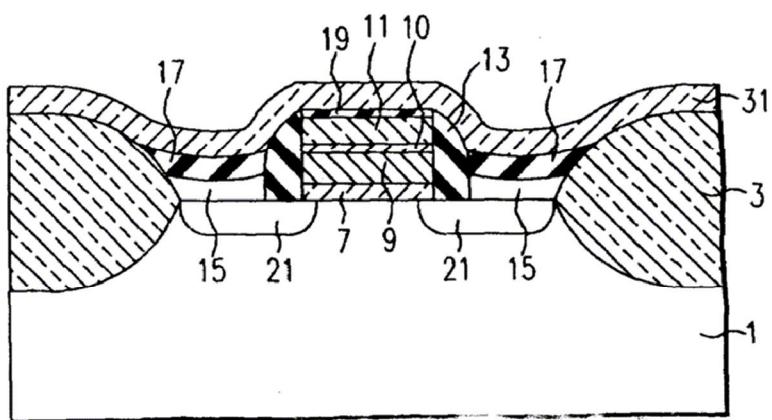

제 1 도에는 기판(1), 절연 영역(3), 얇은 산화물(7), 제 1 물질 및 절연 측벽(13)을 포함하는 폴리실리콘 층(9, 10, 11)을 가진 게이트 구조(5)가 도시되어 있다. 얇은 산화물(7)은 게이트 유전체이고, 폴리실리콘 층(9)은 전도체이다. 양호한 실시예에 있어서, 제 1 물질은 질화물이다. 도시한 대로, 게이트 구조(5)는 절연 영역(3)들 사이에 있으며, 영역(3)들과 게이트 구조(5) 사이에서 영역(14)을 형성하도록 놓여진다. 절연 영역(3)들은 서로 디바이스를 전기적으로 분리하며, 예를 들어 필드 산화물을 영역이다. 다른 절연 물질, 예를 들어 실리콘 질화물이 사용될 수 있지만, 측벽(13)은 실리콘 산화물을 포함할 수 있다. 기판(1)은 실리콘을 포함한다. 층(10)은 얇은 산화물이며, 원한다면 층은 생략 가능하다. 도시된 구조는 당업자에 의해 용이하게 제조 가능하다.

제 2 물질을 포함하는 플러그(15)는 게이트 구조(5)와 필드 산화물을 영역(3) 사이의 영역(14)들에서 형성된다. 제 2 물질은 예를 들어 폴리실리콘을 포함한다. 제 1 및 제 2 물질은 상이한 산화물을 또는 상이한 예정 선택도를 가져야 만 한다. 플러그(15)는 노출된 게이트 구조(5)의 상부 표면을 남기는 예치백에 의해 행해진 폴리실리콘의 블랜켓 증착에 의해 형성되거나 대안적으로 폴리실리콘은 소망 레벨에서 게이트 구조(5) 및 필드 산화물을 영역(3) 사이의 노출된 실리콘상에 선택적으로 증착된다. 원하는 것 보다 폴리실리콘이 더 많이 증착되면, 과잉 폴리실리콘은 예정에 의해 제거 가능하다. 최종 구조가 제 2도에 도시된다.

선택적으로, 소스/드레인 영역에 대한 불순물이 주입되거나 폴리실리콘 내에 넣어지며, 이에 따라 불순물 영역이 형성된다. 원하는 디바이스 파라미터들을 고려한 후 당업자에 의해 적절한 에너지 및 농도가 용이하게 선택될 것이다. 선택적으로, 불순물이 소스/드레인, 즉 불순물 영역을 형성하도록 기판내로 직접 주입될 수 있다. 이제 산화 단계가 실행된다. 산화단계에서 폴리실리콘 플러그(15)의 노출 표면과 제 1 물질, 예를 들어 산화물을 영역(17, 19)을 형성하는 게이트 구조(5)의 상부상에 질화물 층(11)의 노출 표면을 산화하며, 공지된 바와같이, 폴리실리콘은 질화물이 산화하는 것보다 신속히 산화한다. 즉 제 1 및 제 2 물질은 상이한 산화물을 가지며, 폴리실리콘 플러그의 상부에 형성된 산화물 영역은 제 1 물질, 즉

질화물 층에 형성된 산화물 영역보다 두껍다. 후자 산화물 영역은 산소 질화물(oxynitride) 층으로 불리워진다. 이 층은 초기 층보다 최소 5% 두꺼운 것이 바람직하다. 대안적으로, 건식 산화 단계(dry oxidation step)가 행해진다. 이 산화법은 산소 질화물을 생성하지 못한다. 건식 산화가 이용되거나, 산소 질화물 층이 너무 얕으면, 산화물 층(31)은 블랜킷 증착된다. TEOS 등의 공지의 증착 산화물이 사용 가능하다. 이 층이 양호하게 존재한다. 그 결과의 구조가 제 3도에 도시된다.

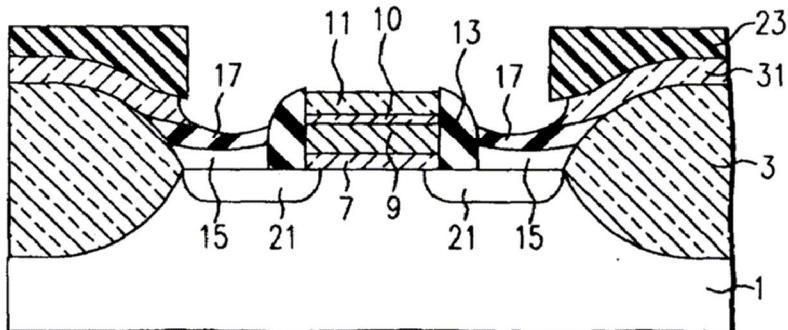

이제 구조의 노출 표면이 예를 들어 레지스트상에서 스피닝(spinning)에 의해 레지스트와 함께 피복된다. 다음에 레지스트는 패턴화되어 게이트 구조(5)의 상부의 적어도 일부분을 노출하는 원도우를 형성한다. 도시된 원도우는 게이트 구조의 원도우보다 크다. 불순물 영역에서 산화물 표면 부분은 통상 노출된다. 통상의 레지스트 및 리소그래픽 패턴화 기술이 사용 가능하다. 습식 또는 건식 중 어느 하나의 에칭을 이용하여 게이트 구조(5)의 상부에서 산소 질화물과 증착 산화물(31)을 제거하고, 게이트 구조에서 하부 질화물층(11)을 노출한다. 통상, 플러그에서 열적 산화물 부분 또한 제거된다. 그러나, 질화물과 폴리실리콘의 상이한 산화율이 폴리실리콘상에서 보다 두꺼운 산화물을 형성하고 증착된 산화물로 인하여, 산화물 층(17) 부분이 영역(21)위에 남게 된다. 전기적 접촉에 필요한 게이트 구조 부분만이 노출된다. 즉, 증착된 산화물이 게이트 구조의 잔류 부분을 덮음을 알 수 있다. 노출된 부분은 불순물 영역 위에 있을 수 있다. 당업자는 공지의 기술을 사용하여 폴리실리콘 플러그(15)상의 모든 산화물이 제거되기 전 예침을 종료할 것이다.

레지스트가 스트립되고, 어느 잔류 레지스트는 종래의 세정기술(cleaning technique)을 사용하여 제거된다. 산화물과 질화물 사이에서 고선택도를 가진 에칭이 이용되어 전도층(9)이 노출되도록 게이트 구조(5)의 상부에서 질화물을 제거한다. 고선택도를 가짐으로써 증착 산화물이 남아 있지 않으며, 게이트 구조의 상부에서 산화물을 제거하지 않을지라도, 약간의 산화물은 폴리실리콘 플러그(15)의 상부에 남아 있게 된다. 절연 측벽(13)상부의 적은 부분이 이 단계에서 제거될 수 있다. 그 결과의 구조가 제 5도에 도시된다. 산화물 층(10)이 존재하면, 산화물 층은 전도층이 노출되도록 제거되어야 한다. 이 층은 플러그가 산화물 층으로 도포되어 남아 있는 플러그상의 산화물 층과 비교하여 비교적 얇다.

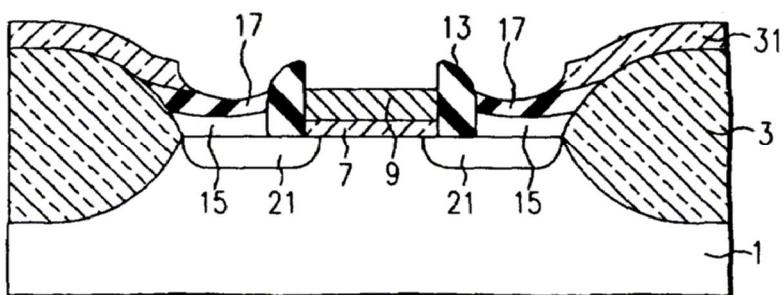

통상의 금속 증착 및 패턴화 기술은 게이트 구조(5)에서 전기적 접촉부(19)를 형성하기 위해 이용된다. 전기적 접촉부(19)는 소스/드레인 영역(21)을 교차한다. 게이트 원도우가 소스/드레인 영역에 대해 오정렬되고 도시된 바와같이 게이트 구조보다 크다면 플러그상의 잔류 산화물에 의해 소스/드레인 영역에서 전기적 접촉부가 만들어 지지 않는다. 약간의 오정렬이 존재하나, 플러그상의 산화물과 절연 측벽은 소스/드레인 영역과의 원치 않는 접촉을 방지한다. 그 결과의 구조가 제 6 도에 도시된다.

이제 기술된 공정에 관한 여러 코멘트가 적합하다. 절연 측벽에 의해 인해 폴리실리콘 플러그(15)와 게이트 구조(5) 사이에 전기적 접촉이 방지됨을 알 수 있다. 질화물 예침으로 야기된 어느 손상은 폴리실리콘 플러그(15)에만 한정되며, 기판 또는 플러그 내부에 있는 소스/드레인 접합에는 미치지 않는다. 주입 단계와 함께 산화 단계가 얇은 소스/드레인 영역을 생성하기 위해 사용된다.

다른 실시예들이 또한 가능하다는 것은 당업자에게는 자명한 것이다. 예를 들어, 질화물 이외의 물질이 게이트 구조에서 사용 가능하다.

## (57) 청구의 범위

### 청구항 1

기판(1)위에 절연 영역(3)들을 형성하는 단계와,

상기 절연 영역(3)들 사이에서 상기 기판(1)상에 게이트 구조체(5)를 형성함으로써 상기 게이트 구조(5) 및 상기 절연 영역(3)들 사이에 영역(14)들을 형성하는 단계로, 상기 게이트 구조(5)는 절연 측벽(13), 전도층(9) 및 제 1 물질을 포함하는 절연 상부층(11)을 가지며, 상기 영역(14)들은 소스 및 드레인 영역을 포함하며, 상기 게이트 구조(5)는 상기 소스 및 상기 드레인 영역 사이에 있는 상기 형성 단계와

상기 게이트 구조(5) 및 상기 절연 영역(3)들 사이에 폴리실리콘 플러그(15)들을 제조하는 단계와,

불순물들을 상기 폴리실리콘 플러그들내로 주입하는 단계와,

상기 폴리실리콘 플러그(15)들의 표면들과 상기 절연 상부층(11)을 산화함으로써 상기 불순물들로 하여금 상기 기판내로 확산케 하여 전계 효과 트랜지스터를 형성케 하는 형성 단계로, 상기 게이트 구조는 상기 소스와 상기 드레인 영역 사이에 있는 상기 형성 단계와,

게이트 구조(5)의 상부의 적어도 일 부분을 노출하기 위해 패턴화 하는 단계와,

상기 절연 상부층(11) 상부의 산화물과 상기 절연 상부층(11)을 제거하기 위해 예침함으로써 상기 전도층(9) 부분을 노출하고 폴리실리콘 플러그(15) 상부에 있는 산화물은 남게 하는 단계와,

상기 게이트 구조(5)에서 상기 소스/드레인 영역(21) 위에서 연장하고 상기 절연 영역(3)들 위에 놓여있는 영역까지 연장하는 전기적 접촉부(9)를 형성하는 단계를 포함하는 반도체 집적 회로 제조 방법.

### 청구항 2

제 1 항에 있어서, 상기 산화 단계 후 산화물을 포함하는 층(31)을 증착하는 단계를 더 포함하는 반도체 집적 회로 제조 방법.

### 청구항 3

제 2 항에 있어서,

상기 제 1 물질은 실리콘 질화물을 포함하는 반도체 집적 회로 제조 방법.

## 청구항 4

제 1 항에 있어서,

상기 케이트 구조(5)와의 상기 전기적 접촉부(19)는 상기 영역들 위에 있는 반도체 집적 회로 제조 방법.

## 도면

## 도면1

## 도면2

## 도면3

도면4

도면5

도면6