(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5329053号

(P5329053)

(45) 発行日 平成25年10月30日(2013.10.30)

(24) 登録日 平成25年8月2日(2013.8.2)

(51) Int.Cl.

F 1

G02F 1/1343 (2006.01)

G02F 1/1368 (2006.01)G02F 1/1343

G02F 1/1368

請求項の数 6 (全 27 頁)

(21) 出願番号 特願2007-137346 (P2007-137346)

(22) 出願日 平成19年5月24日 (2007.5.24)

(65) 公開番号 特開2007-316641 (P2007-316641A)

(43) 公開日 平成19年12月6日 (2007.12.6)

審査請求日 平成22年5月24日 (2010.5.24)

(31) 優先権主張番号 10-2006-0046551

(32) 優先日 平成18年5月24日 (2006.5.24)

(33) 優先権主張国 韓国(KR)

(31) 優先権主張番号 10-2006-0071630

(32) 優先日 平成18年7月28日 (2006.7.28)

(33) 優先権主張国 韓国(KR)

(73) 特許権者 512187343

三星ディスプレイ株式会社

Samsung Display Co., Ltd.

大韓民国京畿道龍仁市器興区三星二路95

95, Samsung 2 Ro, Gih

eung-Gu, Yongin-City,

Gyeonggi-Do, Korea

(74) 代理人 100121382

弁理士 山下 託嗣

(72) 発明者 金仁雨

大韓民国京畿道龍仁市器興區靈德洞テヨン

アパート205-1404

最終頁に続く

(54) 【発明の名称】表示基板

## (57) 【特許請求の範囲】

## 【請求項1】

第1領域と第2領域を有する基板上に前記第1及び第2領域にかけて形成されたストレージ電極と、

前記ストレージ電極上に前記基板を覆うように形成され、前記ストレージ電極が形成された領域で開口部を有する絶縁膜パターンと、

前記絶縁膜パターン上に形成され、前記第1及び第2領域にそれぞれ位置し、前記ストレージ電極上において互いに離間している2つの画素電極を含み、

一の画素電極の他の画素電極と対向する辺において、前記ストレージ電極の延在方向に沿って他の画素電極から遠ざかる向きに凹んでいる凹部が前記ストレージ電極の領域上に形成されており、

前記絶縁膜パターンの開口部は、前記ストレージ電極と前記画素電極との間に層に設けられており、前記凹部と重畳して設けられており、

前記第1及び前記第2領域はそれぞれ異なる画素領域に属していることを特徴とする表示基板。

## 【請求項2】

前記第1及び第2領域は、映像情報に対応される互いに異なる電圧が印加されることを特徴とする請求項1に記載の表示基板。

## 【請求項3】

前記2つの画素電極は前記ストレージ電極の長さ方向に対して傾斜し、相互対称である

方向に屈曲する形状を有することを特徴とする請求項 1 に記載の表示基板。

【請求項 4】

前記凹部は、前記ストレージ電極の長さ方向の縁部に沿ってそれぞれ形成されており、かつ、前記ストレージ電極の長さ方向の中心線に対して対称な一組の第 1 凹部及び第 2 凹部を有することを特徴とする請求項 3 に記載の表示基板。

【請求項 5】

前記絶縁膜パターンは有機絶縁膜を含むことを特徴とする請求項 1 に記載の表示基板。

【請求項 6】

前記有機絶縁膜は各画素領域で前記開口部を定義することを特徴する請求項 5 に記載の表示基板。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は表示基板とその製造方法及びこれを有する液晶表示装置に係り、より詳細には工程上のエラーを防止し、かつ高画質の映像を表示することができる表示基板とその製造方法及びこれを有する液晶表示装置に関する。

【背景技術】

【0002】

一般的に、液晶表示装置、プラズマ表示装置、有機電界発光表示装置のように映像を表示する表示装置は基板を含んでいる。この基板には複数の画素領域が定義されている。画素領域は映像を表示する最小単位を示し、各表示装置には複数の画素領域が互いに区分されるように定義されている。

20

各画素領域はそれぞれ同一の構造を有しており、1つの画素領域には表示される映像に対応する電圧が印加される画素電極を備えている。画素電極は基板上に透明導電膜を蒸着した後、これをパターニングして形成される。基板と画素電極との間には、絶縁膜のような中間膜を介在させることができ、中間膜が平坦でなく、表面に段差が形成された場合には、この段差によって、最初設計された画素電極とは異なるものが形成される恐れがある。

【発明の開示】

【発明が解決しようとする課題】

30

【0003】

本発明の目的は、工程上のエラーを防止することができる表示基板を提供することにある。

本発明の他の目的は前記表示基板の製造方法を提供することにある。本発明の他の目的は、上述した表示基板を利用して高画質の映像を表示することができる液晶表示装置を提供することにある。

【課題を解決するための手段】

【0004】

本発明の一実施形態に係る表示基板は、ストレージ電極、透明絶縁膜パターン、第 1 及び第 2 画素電極を含む。前記ストレージ電極は第 1 領域と第 2 領域とを有する基板上に前記第 1 及び第 2 領域にかけて形成される。前記透明絶縁膜パターンは前記ストレージ電極上に前記基板を覆うように形成され、前記ストレージ電極が形成された領域で開口部を有する。前記第 1 及び第 2 画素電極は前記透明絶縁膜パターン上に形成され、前記第 1 及び第 2 領域にそれぞれ位置する。前記第 1 及び第 2 画素電極のうちの少なくとも 1 つは前記ストレージ電極が形成された領域上で少なくとも 1 つの凹部が形成される。そして、前記第 1 及び第 2 領域はそれぞれ異なる画素領域に属しており、前記開口部及び前記凹部は、前記ストレージ電極が形成された領域上において互いに対応する位置にある。

40

【0005】

本発明の他の実施形態に係る表示基板は、ストレージ電極、透明絶縁膜パターン、第 1

50

及び第2画素電極を含む。前記ストレージ電極は第1領域と第2領域とを有する基板上に前記第1及び第2領域にかけて形成される。前記透明絶縁膜パターンは前記ストレージ電極上に形成され、前記第1領域の前記ストレージ電極上で第1開口部を有し、前記第2領域の前記ストレージ電極上で第2開口部を有する。前記第1及び第2画素電極は前記透明絶縁膜パターン上に形成され、前記第1及び第2領域にそれぞれ位置する。

#### 【0006】

本発明の一実施形態に係る表示基板の製造方法は次の過程を含む。第1領域と第2領域とを有する基板上に前記第1及び第2領域にかけて位置するストレージ電極を形成する。前記基板上で前記ストレージ電極から離隔されるようにゲート電極を形成し、前記ゲート電極上で互いに離間するソース電極とドレイン電極とを形成する。前記ソース電極とドレイン電極上に前記ストレージ電極が形成された領域で開口部を有する透明絶縁膜パターンを形成する。前記透明絶縁膜パターン上の前記第1及び第2領域にそれぞれ第1画素電極と第2画素電極を形成する。前記第1及び第2画素電極のうちの少なくとも1つは前記ストレージ電極が形成された領域上で少なくとも1つの凹部が形成される。

10

#### 【0007】

本発明の他の実施形態に係る表示基板の製造方法は次の過程を含む。第1領域と第2領域とを有する基板上に前記第1及び第2領域にかけて位置するストレージ電極を形成する。前記基板上において前記ストレージ電極から離間するようにゲート電極を形成し、前記ゲート電極上において互いに離間するソース電極とドレイン電極とを形成する。前記ソース電極とドレイン電極上に前記第1領域の前記ストレージ電極上で第1開口部を有し、前記第2領域の前記ストレージ電極上で第2開口部を有する透明絶縁膜パターンを形成する。前記透明絶縁膜パターン上の前記第1及び第2領域にそれぞれ第1画素電極と第2画素電極とを形成する。

20

#### 【0008】

本発明の実施形態に係る液晶表示装置は第1基板及び第2基板、液晶層、ストレージ電極、透明絶縁膜パターン、画素電極、共通電極を含む。前記第1及び第2基板は互いに向き合う。前記液晶層は前記第1及び第2基板の間に介在して、液晶が配列される。前記ストレージ電極は前記第1基板上に形成される。前記透明絶縁膜パターンは前記ストレージ電極上に形成され、前記ストレージ電極が形成された領域で開口される。前記画素電極は前記透明絶縁膜パターン上に形成される。前記共通電極は前記第2基板上に形成され、前記液晶の配列方向を制御する方向制御手段を有する。前記方向制御手段は前記ストレージ電極の端に位置し、前記ストレージ電極の長さ方向と並んでおり、互いに対称の1対からなる。

30

#### 【発明の効果】

#### 【0009】

本実施形態によると、互いに区分された画素電極を形成し、表示装置の動作特性の向上する効果がある。また区分された画素電極を形成する工程において、工程上のエラーによってこれらが電気的に短絡することを防止できる効果がある。

#### 【発明を実施するための最良の形態】

#### 【0010】

40

以下、添付の図面を参照して本発明の実施形態を詳細に説明する。ただし、本発明はここで説明される実施形態に限定されず、多様な形態に応用及び変形可能である。以下の実施形態は本発明によって開示された技術思想をより明確にし、さらに本発明が属する分野で平均的な知識を持った当業者に本発明の技術思想を十分に伝達するために提供されるものである。したがって、本発明の範囲が下述する実施形態によって限定されると解釈されなければならない。また実施形態とともに提示された図面において、相及び領域の大きさは明確な説明を強調するために簡略化、または誇張されたものであり、図面において、同一の参照番号は同一の構成要素を示す。

#### 【0011】

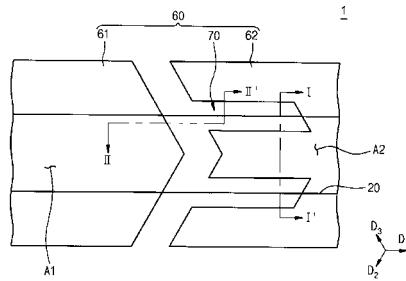

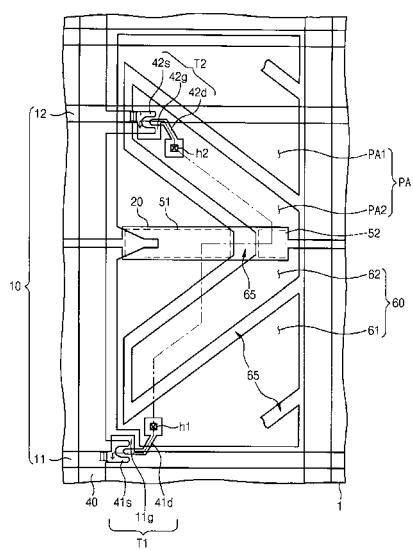

図1Aは本発明の一実施形態に係る表示基板の平面図である。

50

図1Aに示すように、第1領域A1と第2領域A2とを有する基板1を用意する。基板1上にはストレージ電極20と画素電極60が形成されている。ストレージ電極20は第1領域A1と第2領域A2にかけて形成されている。

画素電極60は、互いに離間して形成され、それぞれ第1領域A1と第2領域A2に位置する第1画素電極61と第2画素電極62とを含んでいる。画素電極60は映像が表示される最小単位である画素領域に対応している。第1及び第2画素電極61、62は互いに異なる画素領域に属する構成とすることができます、また同一の画素領域に属する構成とすることができる。第1及び第2画素電極61、62が互いに異なる画素領域に属する場合、第1及び第2画素電極61、62には互いに異なる映像情報に対応して異なる電圧がそれぞれ印加される。同一の画素領域に属する場合、第1及び第2画素電極61、62には同一の映像情報に対応し、高画質の映像を表示するために相互に補償するため異なる電圧がそれぞれ印加される。10

#### 【0012】

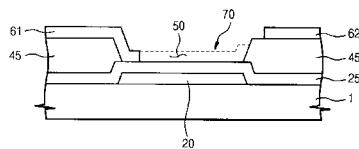

ストレージ電極20の長さ方向を第1方向D1とすると、画素電極60はこの第1方向D1に対して所定の傾きを有し相互に対称である第2及び第3方向D2、D3に向かって曲がる形状で形成される。第1領域A1と第2領域A1との境界において、第1画素電極61は第1方向D1に突き出た凸辺を有し、第2画素電極62はこの凸辺に対応するよう<sup>20</sup>に第1方向D1に向かって凹んでいる凹辺を有する。第2画素電極62の凹辺には第1方向D1に向かって凹んでいる凹部70が形成されている。凹部70は、ストレージ電極20の端部において互いに向き合うように1対で形成されている。

#### 【0013】

ここで、前述とは逆に、凹部70が形成された凹辺を有するように第1画素電極61を形成し、第2画素電極62が凸辺を有するように形成することもできる。また凹部70は、ストレージ電極20上に少なくとも1つ以上を形成すれば良く、その形状や個数において制限はない。ただ、本実施形態の表示基板が液晶表示装置に用いられる場合には凹部70がストレージ電極20の端部に一対で形成されることが液晶の配列制御に有利である。これに対する詳細な説明は今後液晶表示装置に関する実施形態において説明する。

#### 【0014】

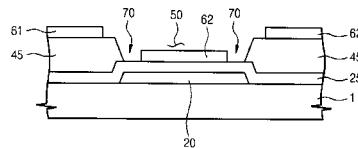

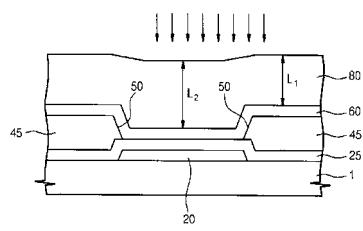

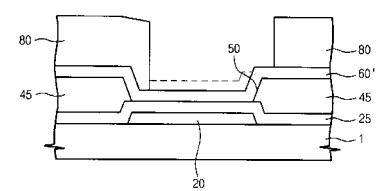

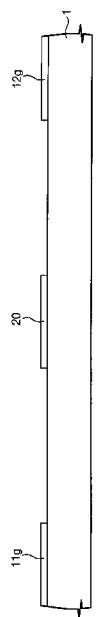

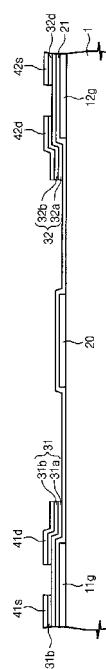

図1Bは図1AのI-I'ラインに沿って切断した断面図である。

図1Bに示すように、ストレージ電極20上には絶縁膜が形成される。絶縁膜は二重膜からなり、下層膜はストレージ電極20をカバーする透明な無機膜25で形成される。上層膜はストレージ電極20上で開口部50を有するようにパターニングされた透明な有機膜45で形成される。有機膜45上には画素電極60が形成される。30

#### 【0015】

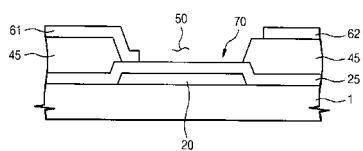

図1Cは図1AのII-II'ラインに沿って切断した断面図である。

第1画素電極61と第2画素電極62はストレージ電極20上で互いに離間して形成されており、この離間する間隔は凹部70によってさらに増加する。上述のように、凹部70によって間隔が増加することによって、画素電極60を形成する時、第1及び第2画素電極61、62が相互に電気的に短絡されることを防止することができる。これについては、以後上述の構造を有する表示基板の製造方法を通じて説明する。40

#### 【0016】

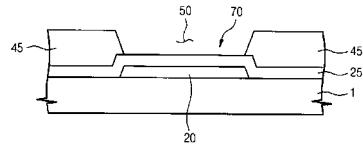

図2A～図2Dは図1Cの表示基板を製造する過程を説明する断面図である。

図2Aに示すように、基板1上にストレージ電極20が形成される。ストレージ電極20は銅、アルミニウム、銀、クロム系列の金属、またはこれらの合金を蒸着して導電膜を形成した後、導電膜をエッチングして形成される。

ストレージ電極20上に無機膜25が形成される。無機膜25は、例えば窒化シリコン膜でプラズマ化学気相蒸着法を用いて基板1の全面を覆うように形成される。無機絶縁膜25上に有機膜45が形成される。有機膜45は、例えばアクリル成分の樹脂を塗布した後、これをパターニングして開口部50を有するように形成される。

#### 【0017】

50

20

30

40

50

図2Bに示すように、有機膜45上に透明導電膜60'が形成される。透明導電膜60'は酸化亜鉛インジウムや酸化柱石インジウムをスパッタリングで蒸着して形成することができる。この場合、透明導電膜60'は均一の厚さで形成され、開口部50が形成された領域における段差によって表面高低が一定ではない。

透明導電膜60'上に感光膜80'が塗布される。感光膜80'はスピンドルティング方法で塗布され、この場合、透明導電膜60'の表面高低に関わらず、感光膜80'の表面が全般に平坦に形成され、領域別の厚さは一定にならない。

#### 【0018】

感光膜80'に対する露光が行われる。感光膜80'がポジティブタイプの場合を例として説明すると、前述の露光の際、透明導電膜60'で除去される部分に対応する領域の感光膜80'が露光される。この露光される領域において、感光膜80'に到達する光(矢印として表示)の強度は一定であるが、当該領域での感光膜80'の厚さは一定ではない。したがって、露光された領域のうち、感光膜80'の厚さが厚い領域では光が感光膜80'の底面まで及ばない可能性がある。

#### 【0019】

例えば、有機膜45が形成された領域上において光が到達しなければならない経路は‘L1’に該当し、開口部50が形成された領域において光が到達しなければならない経路は‘L1’より長い‘L2’になる。

図2Cに示すように、感光膜80'のうち露光された部分を現像により除去することにより、感光膜パターン80が形成される。感光膜パターン80によって、ストレージ電極20の一部と、これに隣接して形成された透明導電膜60'が露出する。

#### 【0020】

図2Cにおいて点線で表示されたものは、露光の時、光が到達せずに、感光膜80'が設定と異なり、一部残留してもよい部分を示したものである。

図2Dに示すように、感光膜パターン80をエッチングマスクとして用いて透明導電膜60'をエッチングすることで、互いに離間した第1及び第2画素電極61、62を含む画素電極60を形成する。このエッチングの時、凹部70が形成され、第1及び第2画素電極61、62の間の間隔は凹部70の形成のために広くなる。

#### 【0021】

図2Dにおいて点線として表示されたものは、露光の時、光が到達せずに、感光膜80'が設定と異なり、一部残留することによって、その下部の透明導電膜80'が残留してもよい部分を示す。この部分は凹部70が形成された領域と重畠する。これによって、凹部70が形成されない場合に、第1及び第2画素電極61、62が相互に連結して電気的に短絡(short)してもよいことが分かる。すなわち、凹部70は画素電極60形成の時、第1及び第2画素電極61、62の間の短絡を遮断して工程上の不良を防止する役割を果たす。

#### 【0022】

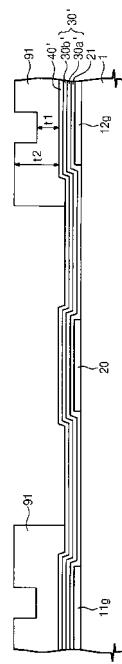

図3Aは本発明の他の実施形態に係る表示基板の平面図である。

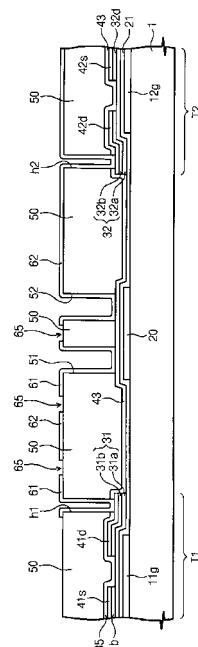

図3Aに示す表示基板は、基板1、ゲートライン10、データライン40、薄膜トランジスタT1、T2、画素電極60を備えている。ゲートライン10とデータライン40は基板1上で互いに交差して複数形成されている。この複数のゲートライン10とデータライン40が交差しながら複数の画素領域PAが定義される。複数の画素領域PAのそれぞれは互いに同一の構造を有するので、以下では1つの画素領域PAを基準にして説明する。

#### 【0023】

画素領域PAは第1領域PA1と第2領域PA2に区分され、このような領域区分に対応して画素電極60は第1画素電極61と第2画素電極62とを含む。第1画素電極61は第1領域PA1に位置し、第2画素電極62は第2領域PA2で第1画素電極61と離間した位置に配置される。第1画素電極61は所定領域が切開されており、この切開された部分と第1及び第2画素電極61、62との間の離間する間隔として、画素電極60が

10

20

30

40

50

切開部パターン 6 5 を有するようになる。

**【 0 0 2 4 】**

画素電極 6 0 には電圧が印加され、第 1 及び第 2 画素電極 6 1、6 2 には、相互間に動作特性を補償するためのそれぞれ異なる電圧が印加される。このために、第 1 及び第 2 画素電極 6 1、6 2 にそれぞれ対応するように第 1 薄膜トランジスタ T 1 と第 2 薄膜トランジスタ T 2 が設けられている。

第 1 薄膜トランジスタ T 1 は第 1 ゲート電極 1 1 g、第 1 ソース電極 4 1 s 及び第 1 ドレイン電極 4 1 d を含んでいる。第 1 ゲート電極 1 1 g は第 1 ゲートライン 1 1 から分岐されて形成されている。第 1 ソース電極 4 1 s はデータライン 4 0 から分岐されて形成されている。第 1 ドレイン電極 4 1 d は第 1 ソース電極 4 1 s から離間して形成され、第 1 コンタクトホール h 1 を通じて第 1 画素電極 6 1 と電気的に接続されている。10

**【 0 0 2 5 】**

第 2 薄膜トランジスタ T 2 は第 2 ゲート電極 1 2 g、第 2 ソース電極 4 2 s 及び第 2 ドレイン電極 4 2 d を含んでいる。第 2 ゲート電極 1 2 g は第 2 ゲートライン 1 2 から分岐されて形成されている。第 2 ソース電極 4 2 s はデータライン 4 0 から分岐されて形成されている。第 2 ドレイン電極 4 2 d は第 2 ソース電極 4 2 s から離間しており、第 2 コンタクトホール h 2 を通じて第 2 画素電極 6 2 と電気的に接続されている。

**【 0 0 2 6 】**

画素領域 PA の中心部にはストレージ電極 2 0 が形成されている。ストレージ電極 2 0 は第 1 画素領域 PA 1 と第 2 画素領域 PA 2 にかけて一体に形成されている。ストレージ電極 2 0 上には透明絶縁膜パターン（図 3 B の符号 5 0 参照）が形成されて基板 1 の全面を覆っている。透明絶縁膜パターンには開口部 5 1、5 2 が形成されている。開口部 5 1、5 2 は第 1 領域 PA 1 のストレージ電極 2 0 上に形成される第 1 開口部 5 1 と第 2 領域 PA 2 のストレージ電極 2 0 上に形成される第 2 開口部 5 2 とを含んでいる。透明絶縁膜パターンは開口部 5 1、5 2 が形成された領域を除いて、第 1 及び第 2 画素電極 6 1、6 2 の境界を含む所定の領域でストレージ電極 2 0 をカバーする。20

**【 0 0 2 7 】**

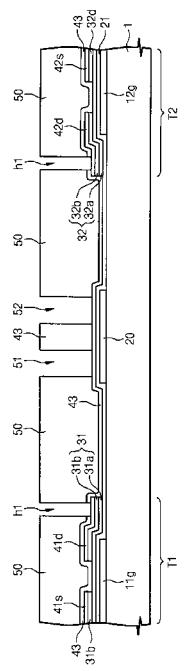

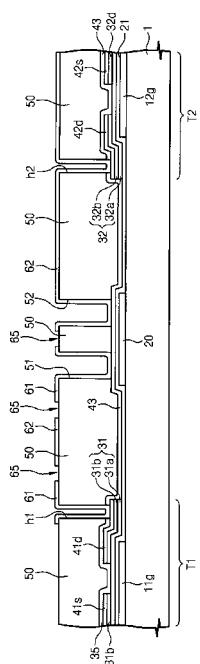

図 3 B 図 3 A の I I I - I I I ' ラインに沿って切断した断面図である。

図 3 B に示すように、基板 1 上の所定領域にそれぞれ互いに離間するように第 1 ゲート電極 1 1 g、ストレージ電極 2 0 及び第 2 ゲート電極 1 2 g が形成されている。第 1 ゲート電極 1 1 g、ストレージ電極 2 0 及び第 2 ゲート電極 1 2 g 上には基板 1 の全面を覆うようにゲート絶縁膜 2 1 が形成されている。30

**【 0 0 2 8 】**

ゲート絶縁膜 2 1 上には、第 1 ゲート電極 1 1 g をカバーするように第 1 半導体パターン 3 1、第 1 ソース電極 4 1 s 及び第 1 ドレイン電極 4 1 d が形成されており、これらを通じて第 1 薄膜トランジスタ T 1 が形成されている。第 1 半導体パターン 3 1 は、第 1 アクティブパターン 3 1 a とその上部の第 1 オミックコンタクトパターン 3 1 b とを含んでおり、第 1 オミックコンタクトパターン 3 1 b は第 1 ソース電極 4 1 s 及び第 1 ドレイン電極 4 1 d に沿って相互間に分離するように形成されている。40

**【 0 0 2 9 】**

また、ゲート絶縁膜 2 1 上には第 2 ゲート電極 1 2 g をカバーするように第 2 半導体パターン 3 2、第 2 ソース電極 4 2 s 及び第 2 ドレイン電極 4 2 d が形成されており、これらを通じて第 2 薄膜トランジスタ T 2 が形成されている。第 2 半導体パターン 3 2 は第 2 アクティブパターン 3 2 a とその上部の第 2 オミックコンタクトパターン 3 2 b を含んでおり、第 2 オミックコンタクトパターン 3 2 b は第 2 ソース電極 4 2 s 及び第 2 ドレイン電極 4 2 d に沿って相互間に分離するように形成されている。

**【 0 0 3 0 】**

第 1 薄膜トランジスタ T 1 と第 2 薄膜トランジスタ T 2 上には、基板 1 の全面を覆うように保護膜 4 3 が形成されており、保護膜 4 3 上には透明絶縁膜パターン 5 0 が形成されている。保護膜 4 3 と透明絶縁膜パターン 5 0 は第 1 及び第 2 コンタクトホール h 1、h 50

2を有している。第1コンタクトホールh1を通じて第1ドレイン電極41dの所定の領域が露出し、第2コンタクトホールh2を通じて第2ドレイン電極42dの所定の領域が露出する。

#### 【0031】

透明絶縁膜パターン50上には画素電極60が形成される。第1画素電極61は第1領域PA1に形成されて第1薄膜トランジスタT1と電気的に接続される。第2画素電極62は第2領域PA2に形成されて第2薄膜トランジスタT2と電気的に接続される。第1及び第2画素電極61、62はストレージ電極20上で透明絶縁膜パターン50にカバーされる部分で境界を成す。

#### 【0032】

ストレージ電極20と第1及び第2画素電極61、62、その間のゲート絶縁膜21と保護膜43によってストレージキャパシタが形成される。透明絶縁膜パターン50は数マイクロメーター程度で厚く形成され、開口部51、52が形成された領域で透明絶縁膜パターン50が除去されて、ストレージ電極20と第1及び第2画素電極61、62との間の離隔距離が減少する。その結果、ストレージキャパシタのキャパシタンスが増加して動作特性が向上することができる。

#### 【0033】

ただ、ストレージ電極20上的一部分は透明絶縁膜パターン50によってカバーされ、これは第1及び第2画素電極61、62を形成する際に、これらが相互に電気的に短絡することを防止するためのものである。

これに対する詳細な説明は、以下、上記の構造を有する表示基板の製造方法を通じて説明する。

#### 【0034】

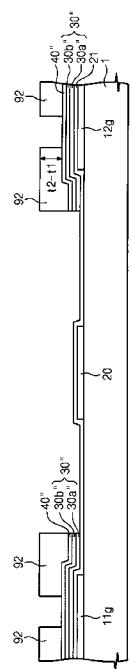

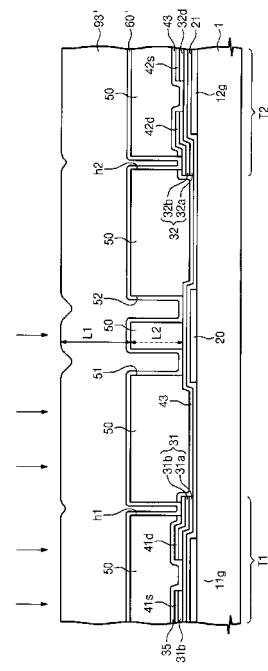

図4A～図4Gは図3Bの表示基板の製造方法を説明する断面図である。

図4Aに示すように、基板1上にゲート導電膜を形成した後、これをパターニングして第1ゲート電極11g、ストレージ電極20及び第2ゲート電極12gを形成する。ゲート導電膜は銅、アルミニウム、銀、クロム系列の金属、またはこれらの合金を蒸着して形成することができ、エッティング液を利用した湿式エッティング法によってゲート導電膜をエッチングすることができる。

#### 【0035】

図4Bに示すように、第1ゲート電極11g、ストレージ電極20及び第2ゲート電極12g上にゲート絶縁膜21を形成する。ゲート絶縁膜21は無機系化合物、例えば窒化シリコン膜でプラズマ化学気相蒸着法を利用して基板1の全面を覆うように形成することができる。

この後、ゲート絶縁膜21上に半導体膜30' とデータ導電膜40'を形成する。半導体膜30'は非晶質シリコン膜でプラズマ化学気相蒸着法を利用して基板1の全面を覆うように形成することができる。半導体膜30'はアクティブ膜30a' とその上部のオミックコンタクト膜30b' とを含む。オミックコンタクト膜30b'は不純物イオンを含む。データ導電膜40'はゲート導電膜と同一の方法で形成することができる。

#### 【0036】

データ導電膜40'上に第1感光膜パターン91が形成される。第1感光膜パターン91はデータ導電膜40'上にフォトレジスト成分の感光膜をコーティングした後、これを露光及び現像することで形成できる。

第1感光膜パターン91は位置によって異なる厚さを有する。第1感光膜パターン91は第1及び第2ゲート電極11g、12g上で第1厚さt1を有し、第1及び第2ゲート電極11g、12gの端部と、ここに接する領域では第1厚さt1より厚い第2厚さt2を有する。第1感光膜パターン91によってストレージ電極20上に形成されたデータ導電膜40'が露出する。

#### 【0037】

上述のように、領域別に異なる厚さを有するように、感光膜に対して露光する際に、ス

10

20

30

40

50

リットマスクまたはハーフトーンマスクをフォトマスクとして用いる。スリットマスクまたはハーフトーンマスクは投光領域と不投光領域の他に中間投光領域を有する。中間投光領域ではスリットの間隔を調節するか、または中間トーンを有する物質を利用して、一部の光が透過して感光膜が露光される。感光膜がポジティブタイプの場合、中間投光領域に対応する部分では感光膜全体の中間の厚さを有するパターンを形成することができる。

#### 【0038】

図4Cに示すように、第1感光膜パターン91をエッチングマスクとして利用してデータ導電膜40' と半導体膜30' がエッチングされる。データ導電膜40' はゲート導電膜と同一方法でエッチングすることができ、その結果、データ導電膜パターン40" が形成される。次に、半導体膜30' がエッチングすることにより予備半導体膜パターン30" 10 を形成する。予備半導体膜パターン30" は予備アクティブパターン30a" と予備オミックコンタクトパターン30b" とを含む。予備半導体膜パターン30" とデータ導電膜パターン40" は同一のパターンで形成されて、平面上で相互に重畠する。

#### 【0039】

第1感光膜パターン91を第1厚さt1だけ均一に除去して第2感光膜パターン92を形成する。第2感光膜パターン92は第2厚さt2と第1厚さt1との差に該当する厚さを有し、第1及び第2ゲート電極11g、12gをカバーするデータ導電膜パターン40" を露出する。

図4Dに示すように、第2感光膜パターン92をエッチングマスクとして用いてデータ導電膜パターン40" をエッチングする。その結果、第1ゲート電極11g上に第1ソース電極41sと第1ドレイン電極41dが形成され、第2ゲート電極12g上に第2ソース電極42sと第2ドレイン電極42dとが形成される。また予備半導体膜パターン30" を再びエッチングし、第1半導体パターン31と第2半導体パターン32とを形成する。再びエッチングする際に、第1半導体パターン31から2つの部分に分離した第1オミックコンタクトパターン31bが形成され、第2半導体パターン32から2つの部分に分離した第2オミックコンタクトパターン32bが形成される。 20

#### 【0040】

このように、第1及び第2半導体パターン31、32を形成し、それぞれ第1薄膜トランジスタT1と第2薄膜トランジスタT2を完成する。第1及び第2薄膜トランジスタT1、T2を完成する際に、第1及び第2半導体パターン31、32と第1及び第2ソース電極41s、42sと第1及び第2ドレイン電極41d、42dは同一のフォトマスクを利用し形成することができ、その結果、工程手続きとそれによる費用を減少することができる。 30

#### 【0041】

図4Eに示すように、第1薄膜トランジスタT1と第2薄膜トランジスタT2上に保護膜43と透明絶縁膜パターン50を形成する。保護膜43はゲート絶縁膜21と同一の方法で形成することができる。透明絶縁膜パターン50は有機膜、例えばアクリル成分の樹脂を塗布した後、これをパターニングして形成することができる。

保護膜43と透明絶縁膜パターン50は、第1及び第2コンタクトホールh1、h2を有するようにパターニングされる。また透明絶縁膜パターン50はストレージ電極20上で第1及び第2開口部51、52を有するようにパターニングされる。 40

#### 【0042】

保護膜43と透明絶縁膜パターン50は次のように同一のフォトマスクを利用して形成することができる。すなわち、保護膜43と有機膜とを塗布した後、フォトリソグラフィ及び現像工程を進行し、第1及び第2コンタクトホールh1、h2が形成される領域では、保護膜43が露出するように透明絶縁膜のすべての厚さを除去し、ストレージ電極20上の第1及び第2開口部51、52が形成される領域では、保護膜43が露出しないように透明絶縁膜が所定の厚さで残るようにする。以後、乾式エッチングを進行すれば、露出した保護膜43が除去されて第1及び第2コンタクトホールh1、h2が形成される。同時にストレージ電極20上では所定厚さ残った透明絶縁膜を除去することによって開口部 50

51、52が形成される。

**【0043】**

図4Fに示すように、透明絶縁膜パターン50上に透明導電膜60'を形成する。透明導電膜60'はスパッタリングで蒸着して形成することができ、蒸着の時、透明導電膜160'は均一の厚さで形成されるため、表面高低は一定ではない。

透明導電膜60'上に感光膜93'を塗布する。感光膜93'はスピンドルティング方法で塗布することができ、透明導電膜60'の表面高低に関わらず、感光膜93'はほぼ平坦に形成することができる。その結果、感光膜93'は領域別で厚さが一定にならない。

**【0044】**

感光膜93'に対する露光が行われる。感光膜93'がポジティブタイプの場合、透明導電膜60'で除去される部分に対応する感光膜93'を露光する。この露光される領域において、感光膜93'に到達する光(矢印として表示)の強度は一定であるが、該当する領域での感光膜93'の厚さは一定ではない。したがって、露光する領域のうち、感光膜93'の厚さが厚い領域では光が感光膜93'の底面まで及ぶないようにすることもできる。

**【0045】**

例えば、ストレージ電極20上の透明絶縁膜パターン50がカバーする領域における光の経路は‘L1’まで到達することとなる。もしこの領域の透明絶縁膜パターン50に開口を設ける場合には、光の経路は‘L2’だけ増加する位置まで到達する必要がある。

図4Gに示すように、感光膜93'において露光された部分を現像工程により除去し、残っている部分をエッチングマスクで透明導電膜60'をエッチングして画素電極60'を形成する。画素電極60'は第1及び第2画素電極61、62を含み、第1及び第2画素電極61、62はストレージ電極20上で境界を成して互いに分離する。

**【0046】**

ところが、図4Fに示したように、感光膜93'において露光された領域のうち、その厚さが厚い領域では光が感光膜93'の底面まで到達せずに、感光膜93'の一部が残る場合がある。このようにして感光膜93'が残る領域では、その下部の透明導電膜60'が残ることとなる。もし、ストレージ電極20上の透明絶縁膜パターン50が完全に開口されている場合は、該当領域において感光膜93'が完全に露光されずに、透明導電膜60'が残るようになる。

**【0047】**

上記のような場合、エッチングの際に、第1及び第2画素電極61、62が互いに電気的に短絡する場合がある。本実施形態では、ストレージ電極20が第1及び第2画素電極61、62の境界に該当する所定の領域で透明絶縁膜パターン50によりカバーすることにより、第1及び第2画素電極61、62が互いに電気的に短絡することを防止する。

一方、上記した短絡が発生しない範囲内で、透明絶縁膜パターン50がストレージ電極20をカバーする領域の大きさをより小さくすることができる。この場合、ストレージキャバシタのキャパシタンスがより向上して、動作特性を向上することができる。具体的にカバーされる領域で透明絶縁膜パターン50の厚さを少し減らすか、または該当の領域で第1及び第2開口部51、52に沿って透明絶縁膜パターン50が緩慢に傾くように形成する方案は多様に提案されており、これらを適宜適用することができる。

**【0048】**

以下では例示的な観点において、上記のような表示基板が用いられた表示装置の1つである液晶表示装置に対して説明する。

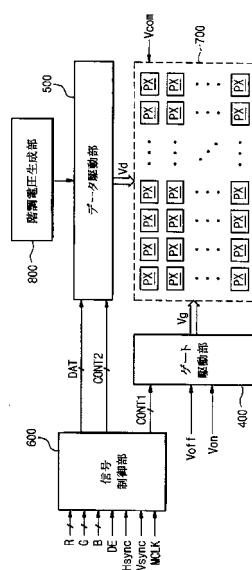

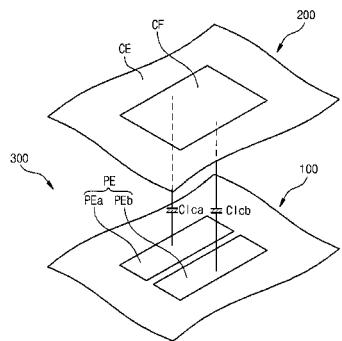

図5は本発明の一実施形態に係る液晶表示装置のブロック図であり、図6は本発明の一実施形態に係る液晶表示装置の2つの副画素に対する等価回路図である。

図5に示したように、本発明の一実施形態に係る液晶表示装置は液晶表示板組立(liquid crystal panel assembly)700、これと接続されたゲート駆動部400及びデータ駆動部500、データ駆動部500に接続された階調電圧生成部800、及びこれらを制御する信号制御部600を含む。

**【0049】**

10

20

30

40

50

等価回路において、液晶表示板組立体 700 は、複数の信号線（図示しない）とこれに接続されており、ほぼ行列の形態で配列された複数の画素（pixel）PX を含む。一方、図 6 に示したように、液晶表示板組立体 700 は互いに向い合う下部及び上部表示板 100、200 とその間に介在する液晶が配列される液晶層 300 を含む。

信号線はゲート信号（“走査信号”ともいう）を伝達する複数のゲートライン（図示しない）とデータ信号を伝達する複数のデータライン（図示しない）とを含む。ゲートラインはほぼ行方向に延在して、互いにほぼ平行であり、データラインはほぼ列方向に延在して、互いにほぼ平行である。

#### 【0050】

各画素 PX は一对の副画素を含み、各副画素は液晶キャパシタ（liquid crystal cell capacitor）C1ca、C1cb を含む。2つの副画素のうちの少なくとも1つはゲートライン、データライン及び液晶キャパシタ C1ca、C1cb と接続されたスイッチング素子（図示しない）を含む。10

液晶キャパシタ C1ca / C1cb は下部表示板 100 の副画素電極 PEa / PEb と上部表示板 200 の共通電極 CE を2つの端子とし、副画素電極 PEa / PEb と共に電極 CE との間の液晶層 300 は誘電体として機能する。一对の副画素電極 PEa、PEb は互いに分離しており、1つの画素電極 PE を成す。共通電極 CE は上部表示板 200 の全面に形成されており、共通電圧 Vcom が印加される。液晶層 300 はマイナスの誘電率異方性を有し、液晶層 300 の液晶分子は電場がない状態でその長軸が下部及び上部表示板 100、200 の表面に対して垂直になるように配向することができる。20

#### 【0051】

一方、色表示を実現するためには、各画素 PX が基本色（primary color）のうちの1つを固有に表示する空間分割方式、各画素 PX が時間に応じて交互に基本色を表示する時間分割方式などを用いて、所望する色相が認識されるように構成する。基本色の例として、赤色、緑色、青色の光の三原色を用いることができる。図 6 は空間分割の一例として、各画素 PX が上部表示板 200 の領域に基本色のうちの1つを示す色フィルター CF を備える場合を示す。図 6 とは異なり、色フィルター CF を、下部表示板 100 の副画素電極 PEa、PEb の上または下に形成することもできる。

#### 【0052】

表示板 100、200 の外面には偏光子（polarizer）（図示しない）をそれぞれ取り付け、2つの偏光子の偏光軸が直交するように構成できる。この場合、電場が形成されなかった時、液晶層 300 に入射した光は外部に透過しない。反射型液晶表示装置の場合には2つの偏光子のうちの1つを省略することができる。30

図 5 に示すように、階調電圧生成部 800 は画素 PX の透過率と係わる複数の階調電圧（または基準階調電圧）を生成する。

#### 【0053】

ゲート駆動部 400 は、液晶表示板組立体 700 のゲートラインと接続されてゲートオン電圧 Von とゲートオフ電圧 Voff との組み合わせからなるゲート信号 Vg をゲートラインに印加する。

データ駆動部 500 は液晶表示板組立体 700 のデータラインと接続されており、階調電圧生成部 800 からの階調電圧を選択し、これをデータ信号としてデータラインに印加する。階調電圧生成部 800 がすべての階調に対する電圧を提供するのではなく、所定数の基準階調電圧のみを提供し、データ駆動部 500 が階調電圧生成部 800 から提供された基準階調電圧を分圧して、すべての階調に対する階調電圧を生成してこの中からデータ信号を選択するように構成することもできる。40

#### 【0054】

信号制御部 600 はゲート駆動部 400 及びデータ駆動部 500 などを制御する。

このような駆動装置 400、500、600、800 のそれぞれは、少なくとも1つの集積回路チップの形態で液晶表示板組立体 700 上に直接装着することができ、FPC 膜（flexible printed circuit film）（図示しない）上に50

装着して、TCP (tape carrier package) の形態で液晶表示板組立体 700 に付着することもでき、または、別途の印刷回路基板 (printed circuit board) (図示しない) 上に装着することもできる。これとは異なり、これら駆動装置 400、500、600、800 を、液晶表示板組立体 700 に集積することもできる。また、駆動装置 400、500、600、800 を單一チップに集積する構成とすることもできる。これらのうちの少なくとも 1つまたはこれらをなす少なくとも 1つの回路素子を單一チップの外に配置することもできる。

#### 【0055】

次に、図 7～図 13C、そして上述した図 5 及び図 6 を参照して本発明の一実施形態に係る液晶表示板組立体に対して詳細に説明する。

10

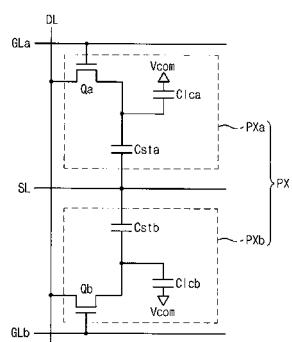

図 7 は本発明の一実施形態に係る液晶表示板組立体の一画素に対する等価回路図である。

図 7 に示すように、この実施形態における一画素中には、複数対のゲートライン GL a、GL b、複数のデータライン DL 及び複数のストレージライン SL を含む信号線と、ここに接続された複数の画素 PX を備えている。

#### 【0056】

各画素 PX は、一对の副画素 PX a、PX b を含み、各副画素 PX a、PX b はそれぞれ該当のゲートライン GL a、GL b 及びデータライン DL に接続されているスイッチング素子 Q a、Q b と、ここに接続された液晶キャパシタ C1ca、C1cb と、スイッチング素子 Q a、Q b 及びストレージ電極では SL に接続されているストレージキャパシタ Csta、Cstb を含む。

20

#### 【0057】

各スイッチング素子 Q a、Q b は下部表示板 100 に設けられている薄膜トランジスタなどの三端子素子として、その制御端子はゲートライン GL a、GL b に接続されており、入力端子はデータライン DL に接続されており、出力端子は液晶キャパシタ C1ca、C1cb 及びストレージキャパシタ Csta、Cstb に接続されている。

液晶キャパシタ C1ca、C1cb の補助的な役割を果たすストレージキャパシタ Csta、Cstb は、下部表示板 100 に設けられたストレージ電極線 SL と画素電極 PE とが絶縁体を間に重畠して配置され、ストレージ電極線 SL には共通電圧 Vcom などの決められた電圧が印加される。しかしそれでキャパシタ Csta、Cstb は副画素電極 PE a、PE b が絶縁体を媒介にして、直上の前端ゲートラインと重畠して配置することができる。

30

#### 【0058】

液晶キャパシタ C1ca、C1cb などについては、上述したので、詳細な説明は略する。

このような液晶表示板組立体を含む液晶表示装置では、信号制御部 600 が 1つの画素 PX に対する入力映像信号 R、G、B を受信して 2つの副画素 PX a、PX b に対する出力映像信号 DAT に変換してデータ駆動部 500 に送ることができる。これとは異なり、階調電圧生成部 800 で、2つの副画素 PX a、PX b に対する階調電圧集合を別に作って、これを交互にデータ駆動部 500 に提供するか、データ駆動部 500 でこれを交互に選択することによって、2つの副画素 PX a、PX b に互いに異なる電圧を印加することができる。ただ、この時、2つの副画素 PX a、PX b の合成ガンマ曲線が正面での基準ガンマ曲線に近くなるように映像信号を補正するか、階調電圧集合を作るのが好ましい。例えば、正面での合成ガンマ曲線はこの液晶表示板組立体に最適になるように決められた正面での基準ガンマ曲線と一致するようにし、側面での合成ガンマ曲線は正面での基準ガンマ曲線と一番近くなるようにする。

40

#### 【0059】

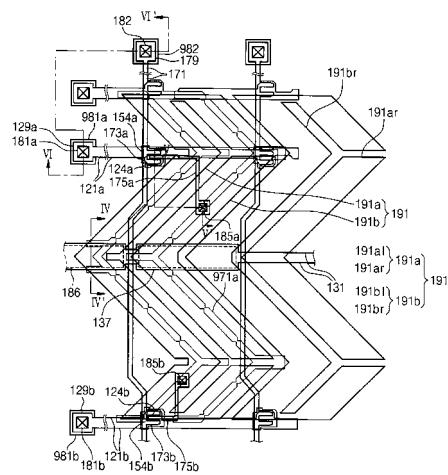

図 7 に示した液晶表示板組立体の一例について、図 8～図 11、及び上述した図 7 を参考して詳細に説明する。

図 8 は本発明の一実施形態に係る液晶表示板組立体の配置図であり、図 9～図 11 はそ

50

それぞれ図8に示した液晶表示板組立体をIV-IV'、V-V'及VI-VI'線に沿って切断した断面図である。

#### 【0060】

図8～図11に示すように、本実施形態に係る液晶表示板組立体は互いに向い合う下部表示板100と上部表示板200及びこれら表示板100、200の間に介在する液晶層300を含む。

まず、下部表示板100について説明する。

透明なガラスまたはプラスチックなどで製造された絶縁基板110上に、複数対の第1及び第2ゲートライン121a、121b及び複数のストレージ電極線(storage electrode lines)131を含む複数のゲート導電体を形成する。 10

#### 【0061】

第1及び第2ゲートライン121a、121bはゲート信号を伝達し、主に図の横方向に延在し、それぞれ画素の上側及び下側に位置する。

第1ゲートライン121aは、図の下方に突き出した複数の第1ゲート電極(gate electrode)124aと、異なる層またはゲート駆動部400との接続のために幅が広く形成された端部129aを含む。第2ゲートライン121bは、図の上方に突き出した複数の第2ゲート電極124bと、異なる層またはゲート駆動部400との接続のために幅が広く形成された端部129bを含む。ゲート駆動部400を基板110上に集積する場合、ゲートライン121a、121bを延長して、これと直接接続することができる。 20

#### 【0062】

ストレージ電極線131は共通電圧Vcomなどの所定の電圧が印加され、主に図の横方向に延在している。ストレージ電極線131は、それぞれ第1ゲートライン121a及び第2ゲートライン121bの間に位置している。各ストレージ電極線131は、図の上下に幅が拡張された複数のストレージ電極(storage electrode)137を含んでいる。しかし、ストレージ電極137を含めたストレージ電極線131の形状及び配置は様々な形態に変形することができる。

#### 【0063】

ゲート導電体121a、121b、131は、アルミニウムAlやアルミニウム合金などのアルミニウム系列金属、銀Agや銀合金などの銀系列金属、銅Cuや銅合金など銅系列金属、モリブデン(Mo)やモリブデン合金などのモリブデン系列金属、クロム(Cr)、タンタル(Ta)及びチタン(Ti)などで形成することができる。しかし、これらは物理的性質が異なる2つの導電膜(図示しない)を含む多重膜構造とすることもできる。このうち、1つの導電膜は信号遅延や電圧降下を減らすように比抵抗(resistivity)が低い金属、例えば、アルミニウム系列金属、銀系列金属、銅系列金属などで製造することができる。これとは異なり、他の導電膜は他の物質、特に酸化亜鉛インジウムIZO及び酸化錫インジウムITOとの物理的、化学的、電気的接触特性が優れた物質、たとえば、モリブデン系列金属、クロム、タンタル、チタンなどで形成することができる。このような組み合わせの例として、クロム下部膜とアルミニウム(合金)上部膜及びアルミニウム(合金)下部膜とモリブデン(合金)上部膜がある。しかし、ゲート導電体121a、121b、131はその他多様な金属または導電体で形成することができる。 40

#### 【0064】

ゲート導電体121a、121b、131の側面は基板110面に対して傾いており、その勾配角は約30°～約80°とすることが好ましい。

ゲート導電体121a、121b、131上には窒化シリコンSiNxまたは酸化シリコンSiOxなどからなるゲート絶縁膜(gate insulating layer)140が形成されている。

#### 【0065】

ゲート絶縁膜140上には水素化非晶質シリコン(hydrogenated amorphous silicon)(以下、非晶質シリコンは略称a-Siとして記載する

10

20

30

40

50

) または多結晶シリコン (polysilicon) などからなる複数の第1及び第2島型半導体154a、154bが形成されている。第1及び第2島型半導体154a、154bはそれぞれ第1及び第2ゲート電極124a、124b上に位置している。

#### 【0066】

島型半導体154a、154b上には、島型抵抗性接触部材(ohmic contact)163a、165aが形成されている。抵抗性接触部材163a、165aは、燐などのn型不純物が高濃度でドーピングされているn+水素化非晶質シリコンなどの物質で形成するか、あるいはシリサイド(silicide)で形成することができる。第1及び第2島型抵抗性接触部材163a、165aは対をなし、島型半導体154a、154b上に配置されている。

10

#### 【0067】

半導体154a、154bと抵抗性接触部材163a、165aの側面も基板110面に対して傾いており、勾配角は30°～80°程度である。

抵抗性接触部材163a、165a及びゲート絶縁膜140上には複数のデータライン(data line)171と複数対の第1及び第2ドレイン電極(drain electrode)175a、175bを含むデータ導電体が形成されている。

#### 【0068】

データライン171はデータ信号を伝達し、通常、図の縦方向に延在しており、ゲートライン121a、121b及びストレージ電極線131と交差する。各データライン171は全体にかけて一直線ではなく、少なくとも二度曲がるように形成されている。

20

各データライン171は、第1及び第2ゲート電極124a、124bに向かってそれぞれ突き出した形状の複数対の第1及び第2ソース電極(source electrode)173a、173bと、異なる層またはデータ駆動部500との接続のために幅が拡張された端部179を含む。データ駆動部500を基板110上に集積する場合、データライン171を延長してこれと直接接続することができる。

#### 【0069】

第1及び第2ドレイン電極175a、175bは互いに分離しており、データライン171とも分離している。

第1及び第2ドレイン電極175a、175bは第1及び第2ゲート電極124a、124bを中心に第1及び第2ソース電極173a、173bと向き合い、棒型の端部分は曲がった第1及び第2ソース電極173a、173bで一部囲まれている。

30

#### 【0070】

第1及び第2ゲート電極124a、124b、第1及び第2ソース電極173a、173b及び第1及び第2ドレイン電極175a、175bは第1及び第2半導体154a、154bとともに第1及び第2薄膜トランジスタ(thin film transistor; TFT)Qa、Qbを構成しており、第1及び第2薄膜トランジスタQa、Qbのチャンネル(channel)は、第1及び第2ソース電極173a、173bと第1及び第2ドレイン電極175a、175bとの間の第1及び第2半導体154a、154bに形成されている。

#### 【0071】

データ導電体171、175a、175bは、モリブデン、クロム、タンタル及びチタンなど耐火性金属(refractory metal)またはこれらの合金で形成することが好ましく、耐火性金属膜(図示しない)と低抵抗導電膜(図示しない)とを含む多重膜構造とすることもできる。多重膜構造の例では、クロムまたはモリブデン(合金)下部膜とアルミニウム(合金)上部膜の二重膜、モリブデン(合金)下部膜とアルミニウム(合金)中間膜とモリブデン(合金)上部膜の三重膜とすることができる。しかし、データ導電体171、175a、175bはその他にも多様な金属または導電体で構成することができる。

40

#### 【0072】

データ導電体171、175a、175bもその側面が基板110面に対して30°～

50

80°程度の勾配角で傾いた構成であることが好ましい。

抵抗性接触部材163a、165aは、その下の半導体154a、154bとその上のデータ導電体171、175a、175bとの間のみに存在しており、これらの間の接触抵抗を低くする。半導体154a、154bはソース電極とドレイン電極との間だけでなく、データ導電体171、175a、175bで覆わない露出された部分がある。

#### 【0073】

データ導電体171、175a、175b及び露出された半導体154a、154b部分の上には透明な絶縁膜パターンで構成される保護膜( passivation layer )180が形成されている。保護膜180は無機絶縁物または有機絶縁物などで形成され、平坦な表面とすることができます。有機絶縁物は4.0以下の誘電定数であることが好ましく、感光性( photosensitivity )を有するものを用いることもできる。しかし、保護膜180は有機膜の優れた絶縁特性を示し、さらに露出した半導体154a、154bの部分に悪い影響が及ばないように下部無機膜と上部有機膜の二重膜構造にすることができる。

#### 【0074】

保護膜180には、データライン171の端部分179と第1及び第2ドレイン電極175a、175bの一方部分をそれぞれ露出する複数のコンタクトホール( contact hole )182、185a、185bが形成されており、保護膜180とゲート絶縁膜140には、ゲートライン121a、121bの端部分129a、129bをそれぞれ露出する複数のコンタクトホール181a、181bが形成されている。また保護膜180はストレージ電極137上で形成された開口部186を有する。

#### 【0075】

保護膜180上には、複数の画素電極( pixel electrode )191及び複数の接触補助部材( contact assistant )981a、981b、982が形成されている。これらは透明な導電物質やアルミニウム、銀、クロムまたはその合金などの反射性金属により形成することができる。

各画素電極191は互いに分離している一対の第1及び第2副画素電極191a、191bを含んでいる。

#### 【0076】

第1副画素電極191aは、それぞれコンタクトホール185aを通じてそれぞれの第1ドレイン電極175aと接続されており、第2副画素電極191bはコンタクトホール185bを通じてそれぞれの第2ドレイン電極175bと接続されている。

画素電極191は、保護膜180を挟んでデータライン171と重畳している。1つのデータライン171は隣り合う画素電極191と全て重畳する。

#### 【0077】

次に、図12、図13A、図13B及び図13Cを参照して、このような液晶表示板組み立て体の画素電極の詳細構造に対して説明する。

図12は本発明の様々な実施形態による液晶表示板組み立て体において1つの画素電極の概略的な配置図であり、図13A～図13Cは図12に示した各副画素電極の基本になる電極片の平面図である。

#### 【0078】

図12に示したように、本発明の実施形態に係る液晶表示板組み立て体の各画素電極( pixel electrode )191は互いに分離している一対の第1及び第2副画素電極191a、191bを含んでいる。第1副画素電極191aと第2副画素電極191bは行方向に隣接し、切開部( cutout )991a、991bを有している。共通電極270( 図6参照 )は第1及び第2副画素電極191a、191bと向い合う切開部971a、971bを有している。

#### 【0079】

第1及び第2副画素電極191a、191bのそれぞれは、少なくとも図13Aに示した平行四辺形の電極片196の1つと図13Bに示した平行四辺形の電極片197の1つ

10

20

30

40

50

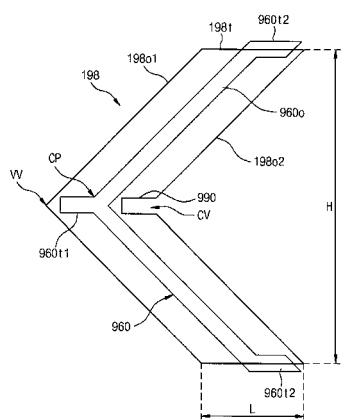

を含んでいる。図13A及び図13Bに示した電極片196、197を上下に連結すれば、図13Cに示した基本電極198になり、各副画素電極191a、191bはこのような基本電極198に基づく構造を有する。

#### 【0080】

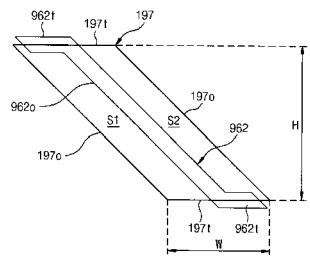

図13A及び図13Bに示したように、電極片196、197のそれぞれは一対の斜辺(*oblique edge*)196o、197o及び一対の横辺(*transverse edge*)196t、197tを有しており、ほぼ平行四辺形である。各斜辺196o、197oは横辺196t、197tに対して斜角(*oblique angle*)をなし、斜角の大きさはほぼ45°～135°であることが好ましい。便宜上横辺196t、197tを中心に垂直の状態で傾いた方向(“傾斜方向”)によって区分して、図13Aのように右側に傾いた場合を“右傾斜”といい、図13Bのように左に傾いた場合を“左傾斜”と言う。10

#### 【0081】

電極片196、197において、横辺196t、197tの長さ、すなわち幅Wと横辺196t、197tとの間の距離、すなわち高さHは、表示板組み立て体700の大きさに応じて自由に決めることができる。また各電極片196、197において横辺196t、197tは他の部分との関係を考慮して折れるか飛び出すなどの変形可能性があるため、このような変形の全てを含んで平行四辺形と呼ぶ。

#### 【0082】

共通電極270には、電極片196、197と向き合う切開部961、962が形成されており、電極片196、197は切開部961、962を中心に2つの副領域S1、S2に区画される。切開部961、962には少なくとも1つのノッチ(*notch*)がある。切開部961、962は電極片196、197の斜辺196o、197oと平行に形成された斜線部961o、962oと、斜線部961o、962oと鈍角をなしながら電極片196、197の横辺196t、197tと重畠する横部961t、962tを含む。20

#### 【0083】

各副領域S1、S2は切開部961、962の斜線部961o、962o及び電極片196、197の斜辺196t、197tにより定義される2つの主辺(*primary edge*)を有する。主辺の間の距離、すなわち副領域の幅は約25～40μm程度であることが好ましい。30

図13Cに示した基本電極198は右傾斜電極片196と左傾斜電極片197が結合して構成される。右傾斜電極片196と左傾斜電極片197の角度はほぼ直角であることが望ましく、2つの電極片196、197は一部だけで連結される。連結されない部分は切開部990を構成するものであり、基本電極198の折れ曲がった部分における凹んだ側に位置して形成される。このような切開部990は省略することが可能である。

#### 【0084】

連結された2つの電極片196、197の外方側に位置する(図の上下端に位置する)横辺196t、197tが基本電極198の横辺198tを構成し、2つの電極片196、197の対応する斜辺196o、197oは互いに連結されて基本電極198の屈曲辺(*curved edge*)198o1、198o2を形成する。40

屈曲辺198o1、198o2は、横辺198tと鈍角、例えば約135°を形成して接続する凸辺(*convex edge*)198o1及び横辺198tと鋭角、例えば約45°を形成して接続する凹辺(*concave edge*)198o2を含む。屈曲辺198o1、198o2は、一対の斜辺196o、197oがほぼ直角を形成して接続されるため、その折れた角度はほぼ直角である。

#### 【0085】

切開部960は、凹辺198o2上の凹頂点CVから凸辺198o1上の凸頂点VVに向かってほぼ基本電極198の中心まで延長される構成とすることができる。

また、共通電極270の切開部961、962は互いに連結されて1つの切開部96050

を構成する。この時、切開部 961、962 で重複する横部 961t、962t は、一体となって 1 つの横部 960t1 を構成する。この新たな形態の切開部 960 は次のように説明することができる。

#### 【0086】

切開部 960 は、屈曲点 CP を有する屈曲部 960o、屈曲部 960o の屈曲点 CP に連結されている中央横部 960t1、及び屈曲部 960o の両端に連結されている一対の縦断横部 960t2 を含む。切開部 960 の屈曲部 960o は直角に接続する一対の斜線部からなり、基本電極 198 の屈曲辺 198o1、198o2 とほぼ平行であり、基本電極 198 を左辺部と右辺部に二等分する。切開部 960 の中央横部 960t1 は屈曲部 960o と鈍角、例えば約 135° を形成し、ほぼ基本電極 198 の凸頂点 VV に向かって延長されている。縦断横部 960t2 は基本電極 198 の横辺 198t に整列されており、屈曲部 960o と鈍角、例えば約 135° を形成する。10

#### 【0087】

基本電極 198 と切開部 960 は基本電極 198 の凸頂点 VV と凹頂点 CV を連結する仮想の直線（“横中心線”といい）に対してほぼ反転対称である。

図 12 に示した各画素電極 191において、第 1 副画素電極 191a の大きさは第 2 副画素電極 191b の大きさより小さい。特に、第 2 副画素電極 191b の高さ（図の上下方向のサイズ：以下、高さと記載する）が第 1 副画素電極 191a の高さより大きく、両副画素電極 191b の幅（これら画素電極を構成する各電極片の左右方向の幅）は実質的に同一である。第 2 副画素電極 191b の電極片の数は第 1 副画素電極 191b の電極片の数より多い。20

#### 【0088】

第 1 副画素電極 191a は左傾斜電極片 197 と右傾斜電極片 196 からなり、図 13 C に示した基本電極 198 と実質的に同一の構造を有する。

第 2 副画素電極 191b は 2 つ以上の左傾斜電極片 197 と 2 つ以上の右傾斜電極片 196 の組み合わせからなり、図 13 C に示した基本電極 198 とこれに結合された左傾斜及び右傾斜電極片 196、197 を含む。

#### 【0089】

図 12 に示した第 2 副画素電極 191b は全部で 6 個の電極片 191b1 ~ 191b6 からなり、このうち 2 つの電極片 191b5、191b6 は第 1 副画素電極 191a の上下に配置されている。画素電極 191b は三回折れた構造を有し、一回折れた構造に比べて 縦方向にさらに優れている画質の映像が表示される。また、第 1 副画素電極 191a の電極片 191a1、191a2 と第 2 副画素電極 191b の電極片 191b5、191b6 が隣接する位置において、共通電極 270 の切開部 961、962 の横部 961t、962t が一体となって 1 つの横部を構成していることから、開口率がさらに増加する。30

#### 【0090】

中間の電極片 191a1、191a2、191b1、191b2 とその上下に配置された電極片 191b3 ~ 191b6 の高さが互いに異なる。例えば、上下電極片 191b3 ~ 191b6 の高さが中間電極片 191a1、191a2、191b1、191b2 の約 1 / 2 であり、これによって第 1 副画素電極 191a と第 2 副画素電極 191b の面積比はほぼ 1 : 2 になる。このように、上下電極片 191b3 ~ 191b6 の高さを調節すれば、所望の面積比を得ることができる。40

#### 【0091】

図 12 において、第 1 及び第 2 副画素電極 191a、191b の位置関係及び折れた方向を変更することが可能であり、図 12 の画素電極 191 を上下左右に反転対称移動するか、回転移動することで変形することができる。

図 8 ~ 図 13 C に示すように、第 1 及び第 2 副画素電極 191a、191b と上部表示板 200 の共通電極 270 は、その間の液晶層 300 部分とともにそれぞれ第 1 及び第 2 液晶キャパシタ C1c a、C1c b を構成し、薄膜トランジスタ Qa、Qb がターンオフした後にも印加された電圧を維持する。50

## 【0092】

第1及び第2副画素電極191a、191bはゲート絶縁膜140を挟んでストレージ電極137と重畳して、それぞれ第1及び第2ストレージキャパシタCsta、Cstbで構成され、第1及び第2ストレージキャパシタCsta、Cstbは第1及び第2液晶キャパシタC1ca、C1cbの電圧維持能力を強化する。この時、保護膜180には開口部186が形成されているため、画素電極191とストレージ電極137との間にはゲート絶縁膜140のみが存在し、画素電極191とストレージ電極線131との距離が短くなるため、電圧維持能力が向上する。

## 【0093】

接触補助部材981a、981b、982はそれぞれコンタクトホール181a、181b、182を通じてゲートライン121a、121bの端部129a、129b及びデータライン171の端部179と接続される。接触補助部材981a、981b、982はゲートライン121a、121bの端部129a、129b及びデータライン171の端部179と外部装置との接着性を補強して、これらを保護する。

## 【0094】

図9及び図10に示すように、上部表示板200の断面構造に関して説明する。

透明なガラスまたはプラスチックなどからなる絶縁基板210上に遮光部材(*light blocking member*)220が形成されている。遮光部材220は画素電極191の境界に対応する部分と薄膜トランジスタに対応する部分とをカバーし、画素電極191の間の光漏れを防ぎ、画素電極191と向き合う開口領域を定義する。

20

## 【0095】

基板210及び遮光部材220上には、さらに複数の色フィルタ230が形成されている。色フィルタ230は遮光部材220で囲まれた領域内に大部分が存在し、画素電極191の列方向に沿って延長されて配置される。各色フィルタ230はレッド、グリーン及びブルーの三原色のうちの1つを表示することができる。

色フィルタ230及び遮光部材220上にはオーバーコート(*overcoat*)250が形成されている。オーバーコート250は(有機)絶縁物で形成することができ、色フィルタ230が露出されることを防止し、平坦面を提供する。このオーバーコート250は省略することも可能である。

30

## 【0096】

オーバーコート250上には共通電極270が形成されている。

共通電極270には複数の切開部971a、971bが形成されている。

表示板100、200の内側面には配向膜(*alignment layer*)911、921が形成されており、これらは垂直配向膜とすることができます。

表示板100、200の外側面には偏光子(*polarizer*)912、922が具備されており、両偏光子912、922の偏光軸は直交し、このうちの1つの偏光軸はゲートライン121a、121bに対して平行であることがほしい。反射型液晶表示装置の場合には2つの偏光子912、922のうちの1つを省略することができる。

## 【0097】

液晶表示装置は偏光子912、922、位相遅延膜、表示板100、200及び液晶層300に光を供給する照明部(*backlight unit*:図示せず)を含むことができる。

40

液晶層300はマイナスの誘電率異方性を有し、液晶層300の液晶分子は電場がない状態でその長軸が2つの表示板100、200の表面に対して垂直になるように配向されている。

## 【0098】

以下、このような液晶表示装置の動作について詳細に説明する。

信号制御部600は外部のグラフィック制御器(図示せず)から入力映像信号R、G、B及びこの表示を制御する入力制御信号を受信して液晶表示板組み立て体700の動作条件に従って処理し、ゲート制御信号CONT1及びデータ制御信号CONT2などを生成

50

した後、それぞれゲート駆動部 400 及びデータ駆動部 500 に送る。

#### 【0099】

ゲート駆動部 400 は信号制御部 600 からのゲート制御信号 C O N T 1 に応じてゲートオン電圧 V<sub>on</sub> をゲートラインに印加して、このゲートラインに接続されたスイッチング素子をターンオンさせる。これによって、データラインに印加されたデータ信号が、ターンオンしたスイッチング素子を通じて該当する画素 P X に印加される。

この時、1つの画素電極 191 を構成する第1副画素電極 191 a と第2副画素電極 191 b は別個のスイッチング素子と連結されており、2つの副画素には互いに異なる時間に同一のデータラインを通じて別個のデータ電圧が印加される。一方、第1副画素電極 191 a と第2副画素電極 191 b は別個のスイッチング素子と接続されており、同一の時間に互いに異なるデータラインを通じて別個のデータ電圧を印加することができる。また、第1副画素電極 191 a はスイッチング素子（図示せず）と接続されており、第2副画素電極 191 b が第1副画素電極 191 a と容量性結合されている場合には、第1副画素電極 191 a を含む副画素のみにスイッチング素子を通じてデータ電圧が印加され、第2副画素電極 191 b を含む副画素には第1副画素電極 191 a の電圧変化に応じて変化する電圧を印加するように構成できる。この時、面積が相対的に小さい第1副画素電極 191 a の電圧が面積が相対的に大きい第2副画素電極 191 b の電圧より高く設定される。

#### 【0100】

画素 P X に印加されたデータ信号の電圧と共通電圧 V<sub>com</sub>との差は液晶キャパシタの充電電圧、すなわち画素電圧として示す。液晶分子は画素電圧の大きさに応じてその配列が異なり、これによって液晶層 300 を通過する光の偏光が変化する。このような偏光の変化は表示板組み立て体 300 に取り付けられた偏光子によって光の透過率の変化として示し、これを通じて画素 P X は映像信号 D A T の階調が示される輝度を表示する。

#### 【0101】

液晶分子の傾斜角度は電気場の強さによって変わり、2つの液晶キャパシタ C1c a、C1c b の電圧が互いに異なるので、液晶分子の傾斜角度が異なり、これによって2つの副画素の輝度が異なる。したがって第1液晶キャパシタ C1c a の電圧と第2液晶キャパシタ C1c b の電圧を適切に調節すれば、側面から見る映像と正面から見る映像とを最も近似させることができ、すなわち側面ガンマ曲線と正面ガンマ曲線とを最も禁じさせることができ、これによって側面視認性を向上させることができる。

#### 【0102】

また、高い電圧が印加される第1副画素電極 191 a の面積を第2副画素電極 191 b の面積より小さくすれば、側面ガンマ曲線を正面ガンマ曲線にさらに近似させることができる。特に第1及び第2副画素電極 191 a、191 b の面積比が約 1:2 ~ 1:3 である場合、側面ガンマ曲線が正面ガンマ曲線により近似し、側面視認性が向上する。

液晶分子の傾斜方向は一次的に電場生成電極 191、270 の切開部 971 a、971 b と副画素電極 191 a、191 b の辺が主電場を歪曲して作る水平成分によって決定される。このような主電場の水平成分は切開部 971 a、971 b の辺と副画素電極 191 a、191 b の辺にほぼ垂直である。

#### 【0103】

切開部 971 a、971 b によって分割された副領域上の液晶分子は、大部分が周辺に対して垂直方向に傾くため、傾斜方向は、ほぼ 4 つの方向になる。このように液晶分子の傾斜方向を多様にすることにより、液晶表示装置の基準視野角が大きくなる。

切開部 971 a、971 b が形成された領域と同一の領域で、切開部 971 a、971 b に代えて共通電極 270 上に突起を形成する場合、この突起が切開部 971 a、971 b と同様に作用する。すなわち、突起によって電場が歪曲し、液晶表示装置の基準視野角を大きくすることができる。

#### 【0104】

一方、副画素電極 191 a、191 b の間の電圧差によって副次的に生成される副電場 (secondary electric field) の方向は副領域の主辺と垂直で

10

20

30

40

50

ある。したがって、副電場の方向と主電場の水平成分の方向とを一致させる。その結果、副画素電極 191a、191b の間の副電場は、液晶分子の傾斜方向を決定するために提供される。

#### 【0105】

前述したように、共通電極 270 の切開部は中央横部 960t1、屈曲部 960o 及び縦断横部 960t2 を含む。図 8 に示すように、中央横部 960t1 がストレージ電極 137 と完全に重畠するように位置する場合、該当する中央横部 960t1 はストレージ電極 137 のエッジに沿って分離された一対で形成することができる。中央横部 960t1 は、屈曲部 960o を構成する互いに対称の一対の斜線部が接する地点に位置する。この斜線部が接する地点で、液晶分子は斜線部の右傾斜部分と左傾斜部分の両方の影響に受け 10て、その配列方向が乱れる。中央横部 960t1 は上記のような現像を防止し、液晶分子の配列方向を制御する手段として作用する。

#### 【0106】

ところが、図 9 に示すように、ストレージ電極 137 が形成された領域では共通電極 270 から開口部 186 が形成された領域までの離間距離が増加する。したがって、該当する領域での液晶分子に対する制御機能が弱くなり、中央横部 960t1 において正常に作用できなくなるおそれがある。このような点を防止するために、図 8 および図 9 に示すように、ストレージ電極 137 が形成された領域と重畠するように位置する中央横部 960t1 は、ストレージ電極 137 のエッジ部分に一対で形成する。

#### 【0107】

図 14 を参考して本発明の他の実施形態による液晶表示板組み立て体について説明する。

。

図 14 は本発明の他の実施形態による液晶表示板組み立て体の一部を示す配置図である。

。

本実施形態による液晶表示板組み立て体も互いに向き合う下部表示板（図示せず）と上部表示板（図示せず）及びこれら 2 つの表示板の間に介された液晶層（図示しない）を含む。

#### 【0108】

本実施形態による液晶表示板組み立て体の垂直構造は図 8 ~ 図 13C に示した液晶表示板組み立て体の層状構造とほぼ類似であり、共通的な部分に対する詳細な説明は省略する

。

下部表示板に対して説明すれば、絶縁基板（図示せず）上に複数のゲートライン（図示せず）及びストレージ電極線 131 を含む複数のゲート導電体が形成されている。ストレージ電極線 131 はストレージ電極 137 を含む。ゲート導電体上にはゲート絶縁膜（図示せず）が形成されている。ゲート絶縁膜の上には島型半導体（図示せず）が形成されており、その上には複数の抵抗性接触部材（図示せず）が形成されている。抵抗性接触部材及びゲート絶縁膜上には複数のデータライン 171 を含むデータ導電体が形成されている。データ導電体 171 及び露出した半導体部分上には開口部 186 を有する保護膜（図示せず）が形成されており、保護膜及びゲート絶縁膜には複数のコンタクトホール（図示せず）及び開口部 186 が形成されている。保護膜上には複数の画素電極 191 と複数の接触補助部材（図示せず）が形成されている。

40

#### 【0109】

上部表示板に対して説明すれば、絶縁基板（図示せず）上に遮光部材（図示せず）、複数の色フィルタ（図示せず）、オーバーコート（図示せず）、共通電極（図示せず）、及び配向膜（図示せず）が形成されている。

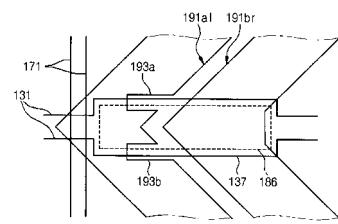

画素電極 191 は凹辺を有する第 1 副画素 191a1 と凸辺を有する第 2 副画素 191b1 に区分され、凹辺の角部には少なくとも 1 つの凹部 193a、193b が形成されている。第 1 副画素 191a1 の 2 つの凹部 193a、193b は開口部 186 の側面に沿って形成されている。これによって、隣り合う第 1 及び第 2 副画素 191a1、191b1 の間隔を充分に確保して、第 1 及び第 2 副画素 191a1、191b1 間に電気的に短絡が

50

発生することを防止することができる。

**【0110】**

凹部193a、193bは少なくとも1つ形成されれば良く、その形状や個数に対する制限はない。但し、凹部193a、193bは画素電極191の所定部分を切開することによって形成することができるため、前述の実施形態において共通電極280の中央横部960t1と同様に液晶分子の方向を制御する手段として用いることができる。この場合、前記中央横部960t1と同一の原理によって、ストレージ電極137と重畠される領域では凹部193a、193bがストレージ電極20のエッジに一対で形成されることが好ましい。

**【0111】**

図15を参考して本発明の他の実施形態による液晶表示板組み立て体について説明する。

図15は本発明の他の実施形態による液晶表示板組み立て体の一部を示す配置図である。

本実施形態による液晶表示板組み立て体も互いに向き合う下部表示板(図示せず)と上部表示板(図示せず)及びこれら2つの表示板の間に介された液晶層(図示せず)を含む。

**【0112】**

本実施形態による液晶表示板組み立て体の垂直構造は図8～図13Cに示した液晶表示板組み立て体の層状構造とほぼ類似であり、共通的な部分に対する詳細な説明は省略する。

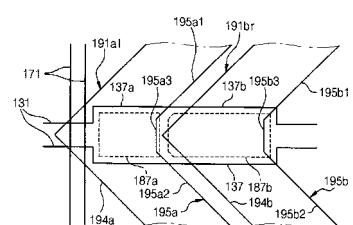

図15に示すように、左側に配置されている画素電極191の第1副画素電極191a1及び右側に配置されている画素電極191の第2副画素電極191b1は、行方向に隣り合うように配置されている。第1及び第2副画素電極191a1、191b1はそれぞれ凸辺194a、194bを有する。また第1及び第2副画素電極191a1、191b1は、2つの斜辺195a1、195a2、195b1、195b2及び2つの斜辺の間を連結する縦辺195a3、195b3からなる凹辺195a、195bを有する。

**【0113】**

ストレージ電極線131は、画素電極191の中央部を横切るように形成される。すなわちストレージ電極線131を中心には上下対称になる。1つのストレージ電極137は隣り合う2つの画素電極191に部分的に重畠している。より詳細には、ストレージ電極137は、左側に位置する画素電極191の第1副画素電極191a1及び右側に位置する画素電極191の第2副画素電極191b1と重畠する。ストレージ電極137は第1副画素電極191a1と重畠する第1部分137a及び第2副画素電極191b1と重畠する第2部分137bを含む。

**【0114】**

ストレージ電極137と画素電極191との間には保護膜が形成され、保護膜は第1開口部187aと第2開口部187bとを有する。第1開口部187aはストレージ電極137の第1部分137aを露出し、第2開口部187bはストレージ電極137の第2部分137bを露出する。第1及び第2開口部186、187は第1副画素電極191a1及び第2副画素電極191b1と重畠する部分で分離されている。これによって、第1及び第2開口部187a、187bの段差部位に第1及び第2副画素電極191a1、191b1間の短絡(short)が発生することを防止できる。

**【0115】**

第2開口部187bの頂点のうち第2副画素電極191b1の凸辺に近い2つの頂点は面取りがされており、面取りがされている斜辺は第2副画素電極191b1の凸辺と平行である。これによって、ストレージキャパシタの容量が低下することを防止できる。

以上、例示的な観点からいくつの実施形態を見たが、該当の技術分野の通常の知識を有する当業者であれば、特許請求の範囲に記載された本発明の思想及び領域から逸脱しない範囲内で本発明を多様に修正及び変更できることを理解できる。

**【図面の簡単な説明】****【0116】**

【図1A】本発明の一実施形態に係る表示基板の平面図である。

【図1B】図1AのI-I'ラインに沿って切断した断面図である。

【図1C】図1AのII-II'ラインに沿って切断した断面図である。

【図2A】図1Cの表示基板を製造する過程を説明する断面図である。

【図2B】図1Cの表示基板を製造する過程を説明する断面図である。

【図2C】図1Cの表示基板を製造する過程を説明する断面図である。

【図2D】図1Cの表示基板を製造する過程を説明する断面図である。

【図3A】本発明の他の実施形態に係る表示基板の平面図である。

10

【図3B】図3AのIII-III'ラインに沿って切断した断面図である。

【図4A】図3Bの表示基板の製造方法を説明する断面図である。

【図4B】図3Bの表示基板の製造方法を説明する断面図である。

【図4C】図3Bの表示基板の製造方法を説明する断面図である。

【図4D】図3Bの表示基板の製造方法を説明する断面図である。

【図4E】図3Bの表示基板の製造方法を説明する断面図である。

【図4F】図3Bの表示基板の製造方法を説明する断面図である。

【図4G】図3Bの表示基板の製造方法を説明する断面図である。

【図5】本発明の一実施形態に係る液晶表示装置のブロック図である。

【図6】本発明の一実施形態に係る液晶表示装置の2つの副画素に対する等価回路図である。

20

【図7】本発明の一実施形態に係る液晶表示板組立体の一画素に対する等価回路図である。

【図8】本発明の一実施形態に係る液晶表示板組立体の配置図である。

【図9】図4に示した液晶表示板組立体をIV-IV'、V-V'及びVI-VI'ラインに沿って切断した断面図である。

【図10】図4に示した液晶表示板組立体をIV-IV'、V-V'及びVI-VI'ラインに沿って切断した断面図である。

【図11】図4に示した液晶表示板組立体をIV-IV'、V-V'及びVI-VI'ラインに沿って切断した断面図である。

30

【図12】図4に示した液晶表示板組立体の画素電極及び共通電極の配置図である。

【図13A】図12に示した各副画素電極の基本となる電極片の平面図である。

【図13B】図12に示した各副画素電極の基本となる電極片の平面図である。

【図13C】図12に示した各副画素電極の基本となる電極片の平面図である。

【図14】本発明の他の実施形態に係る液晶表示板組立体の一部を示す配置図である。

【図15】本発明の他の実施形態に係る液晶表示板組立体の一部を示す配置図である。

【図1A】

【図1B】

【図1C】

【図2A】

【図2B】

【図2C】

【図2D】

【図3A】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図4G】

【図5】

【図6】

【図7】

【 四 8 】

【図9】

【図10】

【図 1 1】

【図12】

【図13A】

【図13B】

【図13C】

【図14】

【図15】

---

フロントページの続き

(72)発明者 金 東 奎

大韓民国京畿道龍仁市豊徳川2洞サムソン5次アパート523-1305

(72)発明者 李 正 浩

大韓民国ソウル麻浦區孔徳1洞サムソンレミアン2次アパート186-268

(72)発明者 宋 榮 九

大韓民国京畿道水原市靈通區靈通洞ビヨクジョクゴル9団地アパートサムソンアパート921-1

201

(72)発明者 朴 錦

大韓民国忠清南道天安市瓦村洞173番地シンドン・ア ファミリエ109-1505

(72)発明者 朴 昂 ウック

大韓民国忠清南道牙山市湯井面虎山里ホンギックアパート103-501

(72)発明者 朴 仁 浩

大韓民国忠清南道天安市斗井洞ウソンアパート105-1207

(72)発明者 李 庸 羽

大韓民国ソウル龍山區厚岩洞143-36

(72)発明者 秋 ミン 亨

大韓民国京畿道城南市壽井區福井洞668-2番地401號

(72)発明者 鄭 敬 錫

大韓民国全羅北道益山市銅山洞ジェイルアパート2次203-606

審査官 清水 督史

(56)参考文献 特開2006-023744(JP,A)

特開2006-201344(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1343

G 02 F 1 / 1368