(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6619559号

(P6619559)

(45) 発行日 令和1年12月11日(2019.12.11)

(24) 登録日 令和1年11月22日(2019.11.22)

|                          |               |         |

|--------------------------|---------------|---------|

| (51) Int.Cl.             | F 1           |         |

| HO 1 L 21/8242 (2006.01) | HO 1 L 27/108 | 3 2 1   |

| HO 1 L 27/108 (2006.01)  | HO 1 L 29/78  | 6 1 8 B |

| HO 1 L 29/786 (2006.01)  | HO 1 L 29/78  | 6 2 0   |

| HO 1 L 21/8234 (2006.01) | HO 1 L 29/78  | 6 1 3 B |

| HO 1 L 27/088 (2006.01)  | HO 1 L 27/108 | 6 7 1 Z |

請求項の数 3 (全 76 頁) 最終頁に続く

|                    |                               |           |                                                |

|--------------------|-------------------------------|-----------|------------------------------------------------|

| (21) 出願番号          | 特願2015-48995 (P2015-48995)    | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日           | 平成27年3月12日(2015.3.12)         | (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (65) 公開番号          | 特開2015-222807 (P2015-222807A) | (72) 発明者  | 塙野入 豊<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (43) 公開日           | 平成27年12月10日(2015.12.10)       | (72) 発明者  | 熱海 知昭<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査請求日              | 平成30年3月9日(2018.3.9)           | (72) 発明者  | 長塚 修平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号       | 特願2014-52263 (P2014-52263)    |           |                                                |

| (32) 優先日           | 平成26年3月14日(2014.3.14)         |           |                                                |

| (33) 優先権主張国・地域又は機関 | 日本国(JP)                       |           |                                                |

| (31) 優先権主張番号       | 特願2014-52864 (P2014-52864)    |           |                                                |

| (32) 優先日           | 平成26年3月16日(2014.3.16)         |           |                                                |

| (33) 優先権主張国・地域又は機関 | 日本国(JP)                       |           |                                                |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

記憶回路および回路が同一の基板上に設けられ、

前記記憶回路は、第1のトランジスタと、前記第1のトランジスタの上方に位置する容量素子と、前記容量素子上方に位置する第2のトランジスタと、を有し、

前記第1のトランジスタは、第1のゲートと第2のゲートとを有し、

前記第1のトランジスタの第1のゲートには、前記第2のトランジスタのソースまたはドレインのいずれか一方と、前記容量素子の一方の電極と、が電気的に接続され、

前記容量素子の一方の電極および他方の電極は、前記第1のトランジスタの第1ゲートの上方に位置し、

前記容量素子の一方の電極は、前記第1のトランジスタの第1のゲートと重なる領域と、前記第1のトランジスタの第2のゲートと重なる領域と、前記第2のトランジスタのゲートと重なる領域と、を有し、

前記回路は、第3のトランジスタと、第4のトランジスタと、を有し、

前記第3のトランジスタと、前記第4のトランジスタとは、互いに直列に接続され、

前記第1乃至第4のトランジスタは、それぞれ、酸化物半導体膜にチャネルが形成されることを特徴とする半導体装置。

## 【請求項 2】

請求項1において、

前記第1のトランジスタのチャネル長方向と、前記第2のトランジスタのチャネル長方

向とは、互いに異なる方向であることを特徴とする半導体装置。

**【請求項 3】**

請求項 1 又は 2 において、

前記第 1 のトランジスタは、第 1 の半導体膜と、第 2 の半導体膜と、第 3 の半導体膜とが順に積層された領域を有し、

前記第 1 のトランジスタのソース電極として機能する導電膜と、前記第 2 のトランジスタのドレイン電極として機能する導電膜とは、前記第 2 の半導体膜と前記第 3 の半導体膜の間に設けられることを特徴とする半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

10

**【0001】**

本発明の一態様は、半導体を利用した回路システムやその他の半導体装置に関する。または、本発明の一態様は、半導体装置のための駆動方法、または作製方法に関する。

**【0002】**

本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関する。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関する。特に、本発明の一態様は、半導体装置、表示装置、発光装置、蓄電装置、記憶装置、それらの駆動方法、またはそれらの製造方法に関する。

**【0003】**

20

本明細書等において、半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。撮像装置、表示装置、液晶表示装置、発光装置、電気光学装置、発電装置（薄膜太陽電池、有機薄膜太陽電池等を含む）、及び電子機器は、半導体装置を有している場合がある。

**【0004】**

本明細書等において、回路システムとは、容量素子、トランジスタ、抵抗素子、記憶素子、配線等の半導体装置を有する回路全般のことを指す。または、回路システムには、半導体装置を駆動させる駆動回路、電源回路等が含まれていてもよい。または、回路システムには、インバータ回路、NAND回路、AND回路、NOR回路、OR回路、バッファ、レベルシフタ、XOR回路、XNOR回路、AND-NOR回路、OR-NAND回路、AND-OR-INN回路、OR-AND-INN回路、アナログスイッチ、フリップフロップ、セット可能なフリップフロップ、リセット可能なフリップフロップ、セットおよびリセット可能なフリップフロップ、加算器、半加算器、マルチプレクサ、デマルチプレクサ、レジスタ、スキャンレジスタ、リテンションレジスタ、アイソレータ、およびデコーダ等の 1 つまたは複数が含まれてもよい。

30

**【背景技術】**

**【0005】**

半導体材料を用いてトランジスタを構成する技術が注目されている。該トランジスタは集積回路（I C）や画像表示装置（単に表示装置とも表記する）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体材料としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

40

**【0006】**

例えば、酸化物半導体として酸化亜鉛、またはIn-Ga-Zn酸化物を用いてトランジスタを作製する技術が開示されている（特許文献 1 及び特許文献 2 参照）。

**【0007】**

また、近年では電子機器の高性能化、小型化、または軽量化に伴い、微細化されたトランジスタなどの半導体素子を高密度に集積した集積回路の要求が高まっている。

**【先行技術文献】**

**【特許文献】**

50

**【0008】**

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

**【発明の概要】****【発明が解決しようとする課題】****【0009】**

本発明の一態様は、良好な電気特性を有するトランジスタを有する回路システムを提供することを課題の一つとする。または、本発明の一態様は、良好な電気特性を有するトランジスタと、静電容量が小さい容量素子とを有する回路システムを提供することを課題の一つとする。または、本発明の一態様は、微細化に適したトランジスタを有する回路システムを提供することを課題の一つとする。または、本発明の一態様は、スイッチング速度(動作速度ともいう)が向上する回路システムを提供することを課題の一つとする。または、本発明の一態様は、書き込み速度が向上する回路システムを提供することを課題の一つとする。または、本発明の一態様は、読み出し速度が向上する回路システムを提供することを課題の一つとする。または、本発明の一態様は、消費電力の小さい回路システムを提供することを課題の一つとする。または、本発明の一態様は、保持特性の良好な記憶素子を有する回路システムを提供することを課題の一つとする。または、新規な回路システムを提供することを課題の一つとする。または、新規な半導体装置を提供することを課題の一つとする。

**【0010】**

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

**【課題を解決するための手段】****【0011】**

本発明の一態様は、容量素子と、容量素子と電気的に接続されるトランジスタと、を有する半導体装置において、容量素子の静電容量は、0.1fF以上10fF未満であり、トランジスタは、酸化物半導体膜を有し、室温動作時において、半導体装置の書き込み時間が0.1n秒以上5n秒未満である半導体装置である。

**【0012】**

本発明の一態様は、記憶回路および回路が同一の基板に作製されている半導体装置であつて、記憶回路は、容量素子、第1のトランジスタ、および第2のトランジスタを有し、第1のトランジスタのゲートには、容量素子および第2のトランジスタのソースまたはドレインのいずれか一方が電気的に接続され、回路は、第3のトランジスタと、第4のトランジスタと、を有し、第3のトランジスタと、第4のトランジスタとは、互いに直列に接続され、第1のトランジスタおよび第3のトランジスタは、シリコンを含む活性層を有し、第2のトランジスタおよび第4のトランジスタは、酸化物半導体膜で形成された活性層を有する半導体装置である。

**【0013】**

本発明の一態様は、記憶回路および回路が同一の基板に作製されている半導体装置であつて、記憶回路は、容量素子、第1のトランジスタ、および第2のトランジスタを有し、第1のトランジスタのゲートには、容量素子、および第2のトランジスタのソースまたはドレインのいずれか一方が電気的に接続され、回路は、第3のトランジスタと、第4のトランジスタと、を有し、第3のトランジスタと、第4のトランジスタとは、互いに直列に接続され、第1乃至第4のトランジスタは、酸化物半導体膜で形成された活性層を有する半導体装置である。

**【0014】**

上記各態様において、酸化物半導体膜で形成された活性層を有するトランジスタは、チャネル長が1nm以上100nm未満である領域を有すると好ましい。また、上記各態様

10

20

30

40

50

において、酸化物半導体膜は、酸素と、Inと、Znと、M(Mは、Ti、Ga、Y、Zr、La、Ce、Nd、またはHf)とを有することが好ましい。また、上記各態様において、酸化物半導体膜は結晶部を有すると好ましい。また、上記各態様において、酸化物半導体膜は、c軸配向した結晶部を有すると好ましい。

**【発明の効果】**

**【0015】**

本発明の一態様により、良好な電気特性を有するトランジスタを有する回路システムを提供することができる。または、本発明の一態様により、良好な電気特性を有するトランジスタと、静電容量が小さい容量素子とを有する回路システムを提供することができる。または、本発明の一態様により、微細化に適したトランジスタを有する回路システムを提供することができる。または、本発明の一態様により、スイッチング速度(動作速度ともいう)が向上する回路システムを提供することができる。または、本発明の一態様により、書き込み速度が向上する回路システムを提供することができる。または、本発明の一態様により、読み出し速度が向上する回路システムを提供することができる。または、本発明の一態様により、消費電力の小さい回路システムを提供することができる。または、本発明の一態様により、保持特性の良好な記憶素子を有する回路システムを提供することができる。または、新規な回路システムを提供することができる。または、新規な半導体装置を提供することができる。

10

**【0016】**

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

20

**【図面の簡単な説明】**

**【0017】**

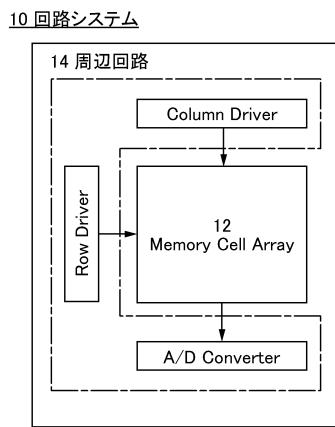

**【図1】**回路システムの一例を説明するブロック図。

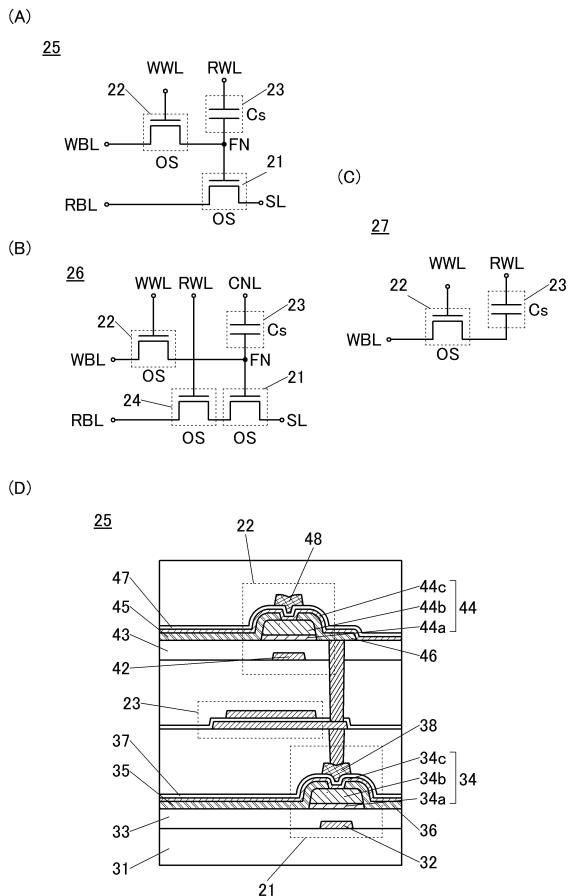

**【図2】(A)-(C)**：記憶装置の一例を示す回路図。(D)：同断面図。

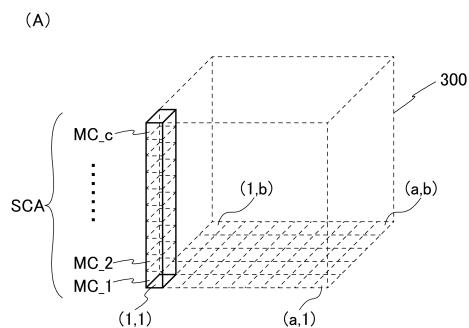

**【図3】(A)**：メモリセルアレイの一例を示す模式図。(B)：メモリセルの一例を示す回路図。

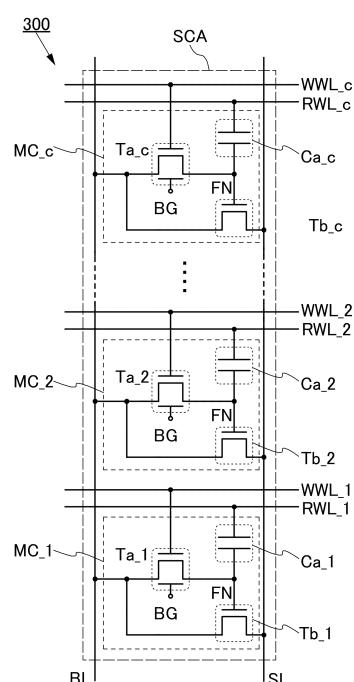

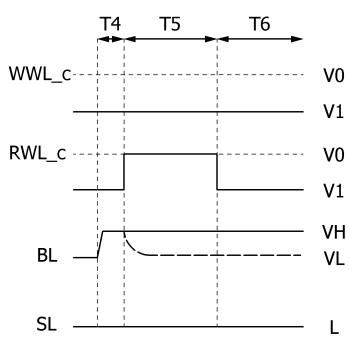

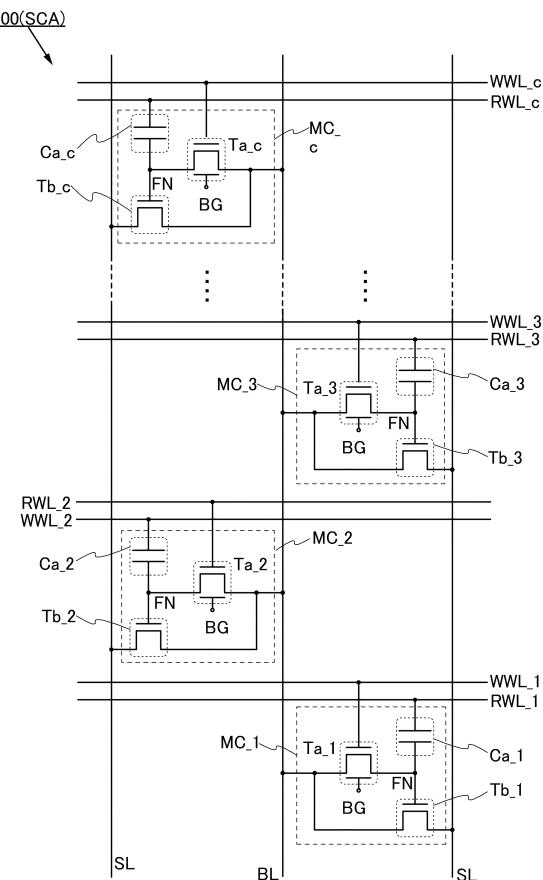

**【図4】**メモリセルアレイの一例を示す回路図。

30

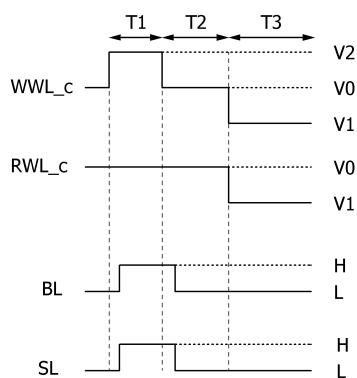

**【図5】(A)、(B)**：メモリセルアレイの動作の一例を示すタイミングチャート。

**【図6】**メモリセルアレイの一例を示す回路図。

**【図7】**メモリセルアレイの一例を示す回路図。

**【図8】**メモリセルアレイの一例を示す断面図。

**【図9】**メモリセルアレイの一例を示す断面図。

**【図10】**図9の部分拡大図。

**【図11】**メモリセルアレイの一例を示す断面図。

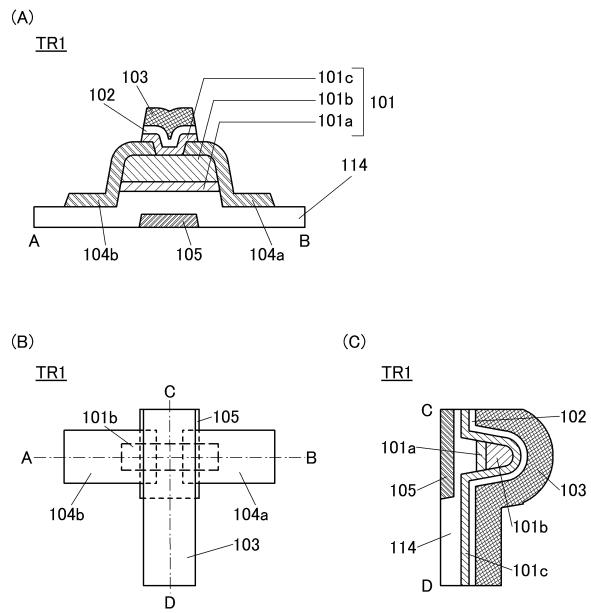

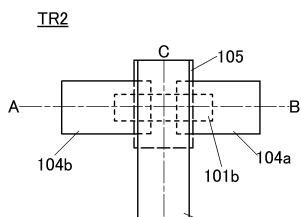

**【図12】(B)**：トランジスタの一例を示す上面図。(A)、(C)：同断面図。

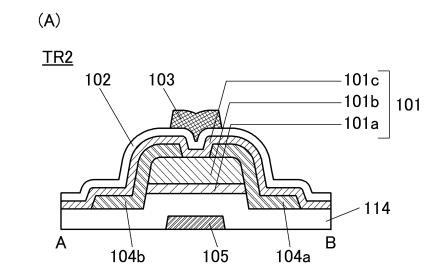

**【図13】(B)**：トランジスタの一例を示す上面図。(A)、(C)：同断面図。

**【図14】(A)-(D)**：トランジスタの一例を示す断面図。

40

**【図15】(A)-(D)**：メモリセルアレイの作製方法の一例を示す断面図。

**【図16】(A)-(C)**：メモリセルアレイの作製方法の一例を示す断面図。

**【図17】(A)-(C)**：メモリセルアレイの作製方法の一例を示す断面図。

**【図18】**メモリセルアレイの作製方法の一例を示す断面図。

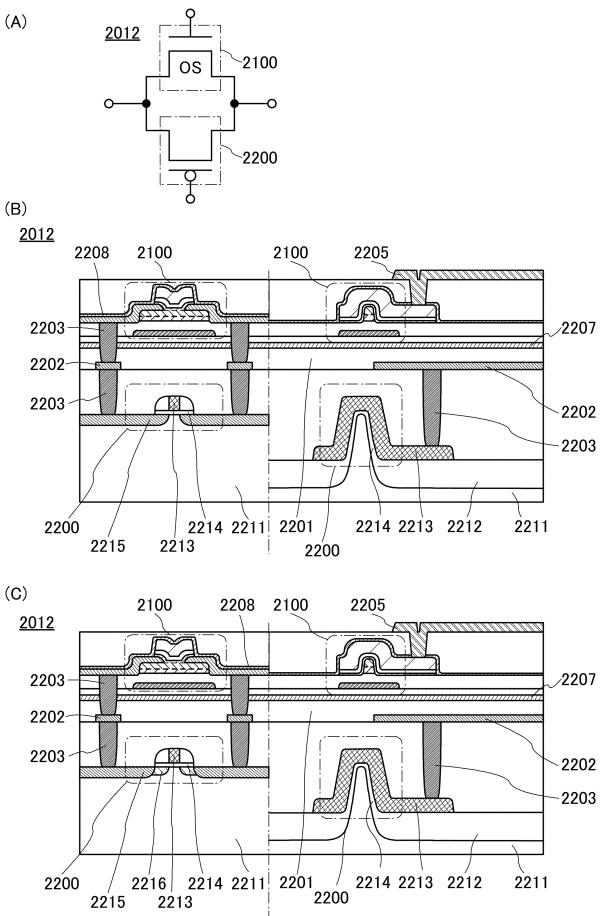

**【図19】(A)**：半導体装置の一例を示す回路図。(B)、(C)：図19(A)の半導体装置の構成例を示す断面図。

**【図20】(A)**：半導体装置の一例を示す回路図。(B)、(C)：図20(A)の半導体装置の構成例を示す断面図。

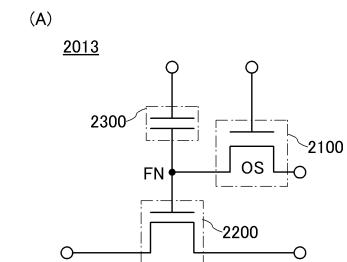

**【図21】(A)**：半導体装置の一例を示す回路図。(B)：図21(A)の半導体装置の構成例を示す断面図。

50

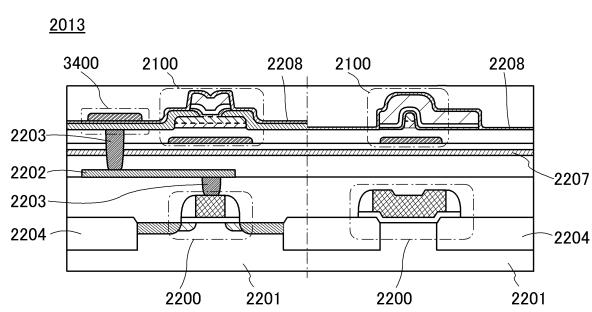

- 【図22】(a) - (i) : 半導体装置の一例を示す回路図。

- 【図23】(A) : 半導体装置の構成例を示す断面図。 (B)、(C) : 半導体装置の一例を示す回路図。

- 【図24】(A) : 半導体装置の構成例を示す断面図。 (B)、(C) : 半導体装置の一例を示す回路図。

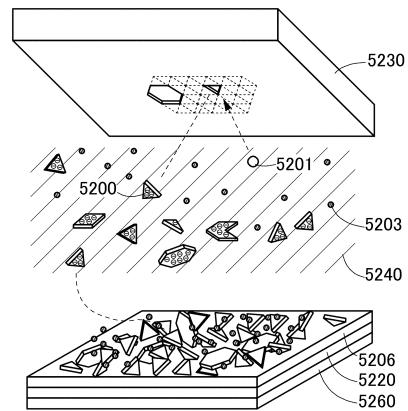

- 【図25】R F デバイスの一例を示す図。

- 【図26】(A) - (F) : R F デバイスの使用例を示す図。

- 【図27】C P U の一例を示す図。

- 【図28】記憶回路の一例を示す回路図。

- 【図29】(A) - (F) : 電子機器の一例を示す図。 10

- 【図30】絶縁膜及び酸化物半導体膜の積層構造におけるバンド構造を示す図。

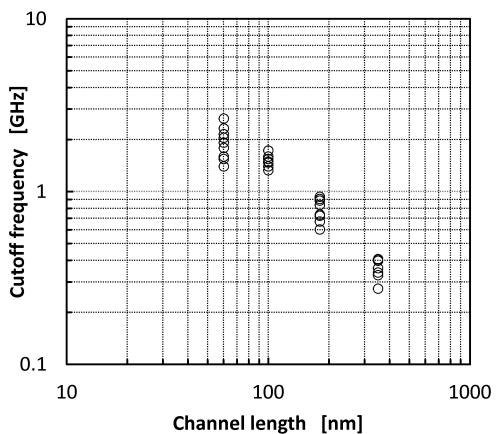

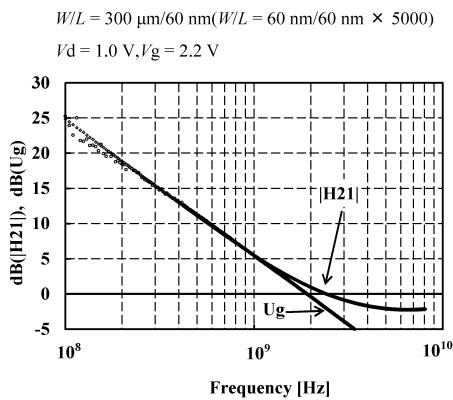

- 【図31】O S トランジスタの遮断周波数の測定結果を示す図。

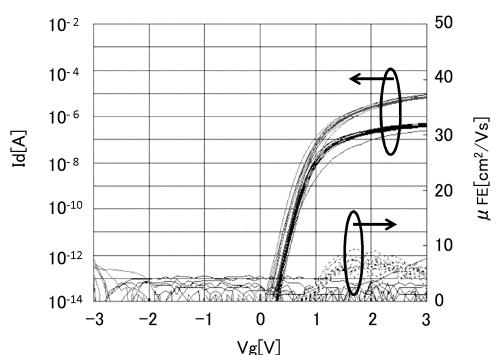

- 【図32】作製したトランジスタの  $V_g$  -  $I_d$  特性を示す図。

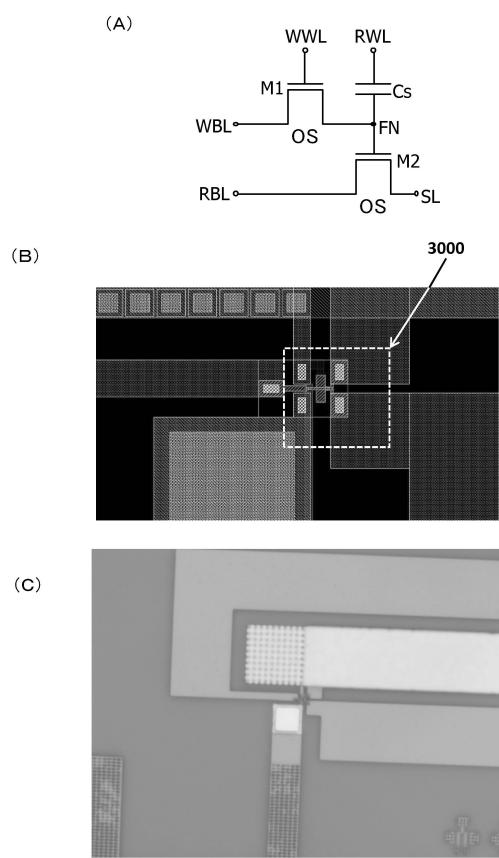

- 【図33】(A) : 作製した回路システムの回路図。 (B) : 同レイアウト図。 (C) : 同光学顕微鏡写真。

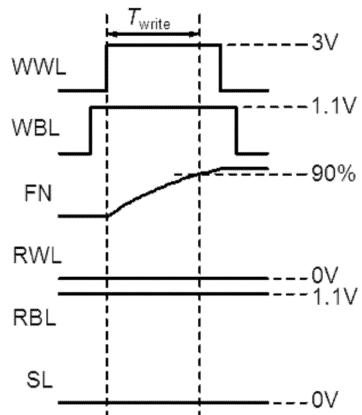

- 【図34】作製した回路システムの書き込み動作時の動作波形を示す模式図。

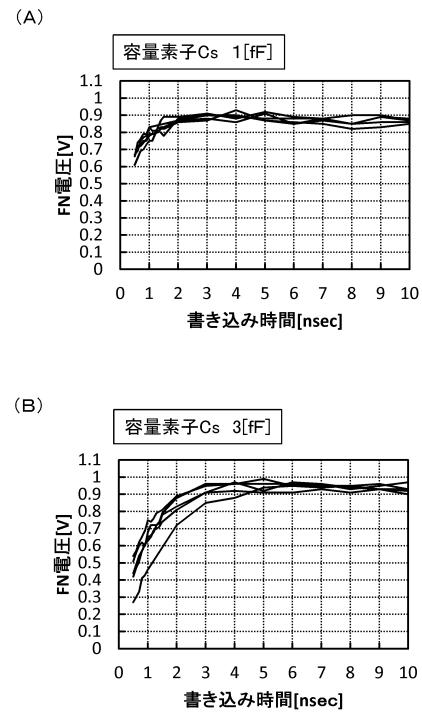

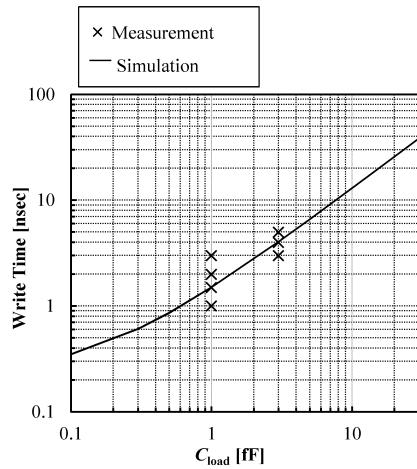

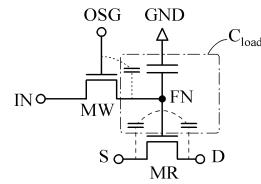

- 【図35】作製した回路システムのフローティングノードの電圧と書き込み時間との関係を示す図。

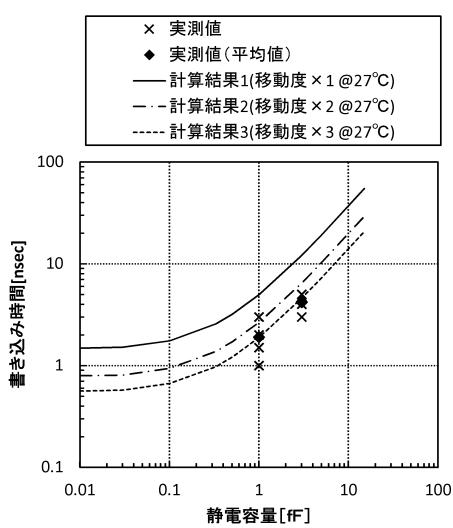

- 【図36】作製した回路システムの書き込み時間と静電容量との関係を示す図。

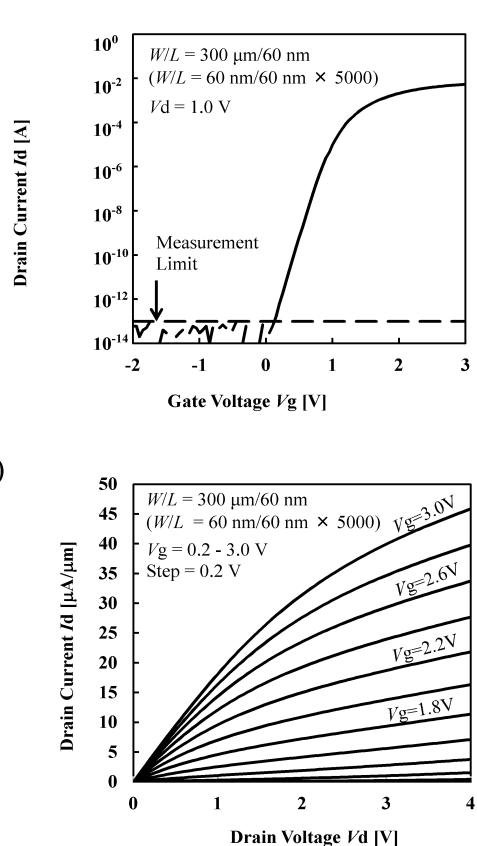

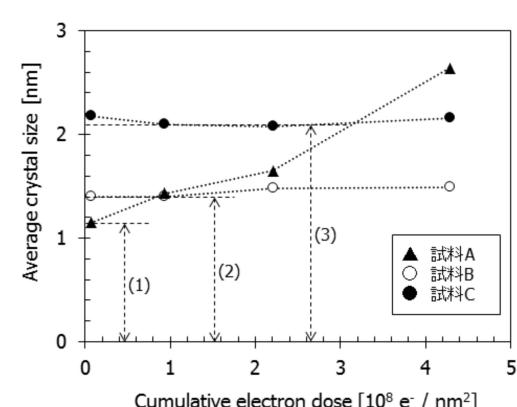

- 【図37】C AAC - O S (C Axis Aligned Crystalline 20

Oxide Semiconductor) 膜を用いたトランジスタ (C AAC - O S

F E T) の D C 特性。 (A) : ドレイン電流 ゲート電圧 ( $I_d$  -  $V_g$ ) 特性の測定結果。

(B) : ドレイン電流 ドレイン電圧 ( $I_d$  -  $V_d$ ) 特性の測定結果。

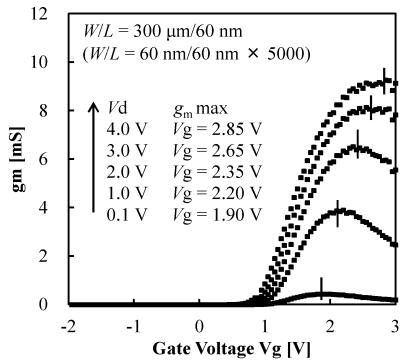

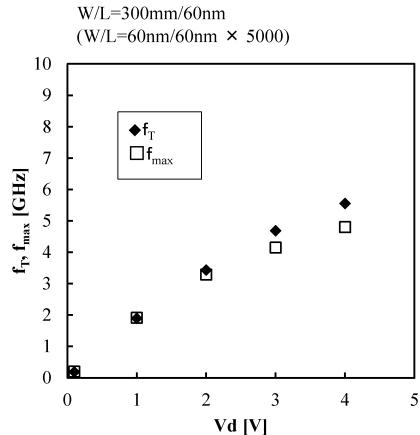

- 【図38】C AAC - O S F E T の相互コンダクタンス  $g_m$  特性の測定結果を示す図。

- 【図39】C AAC - O S F E T の周波数に対する高周波利得の測定結果を示す図。

- 【図40】C AAC - O S F E T の  $V_d$  と遮断周波数および最大発振周波数の関係を示す図。

- 【図41】作製した記憶回路の回路図。

- 【図42】図41の記憶回路の負荷容量  $C_{load}$  と書き込み時間の関係を示す図。

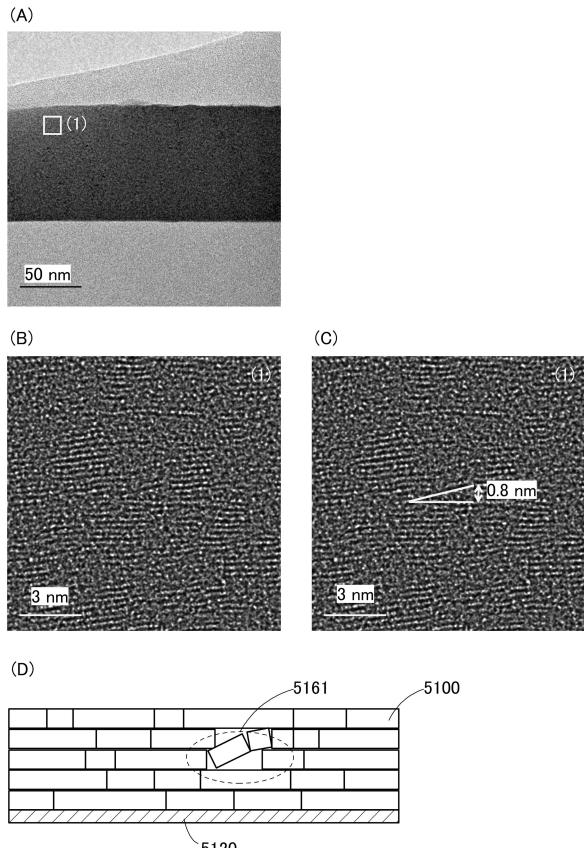

- 【図43】C AAC - O S の断面における C s 補正高分解能 T E M 像、および C AAC - 30

O S の断面模式図。

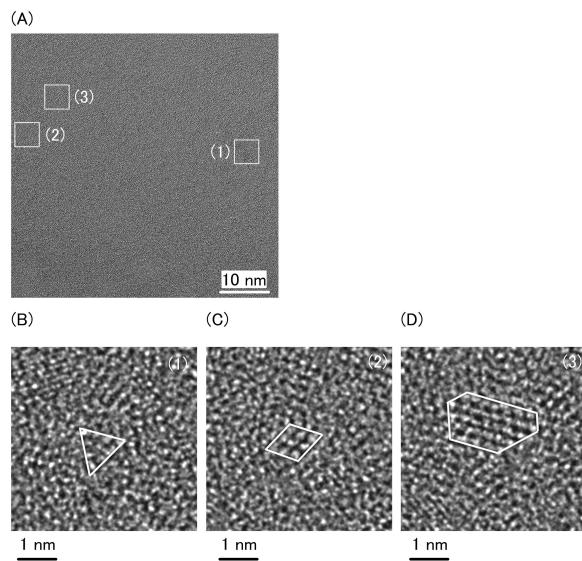

- 【図44】C AAC - O S の平面における C s 補正高分解能 T E M 像。

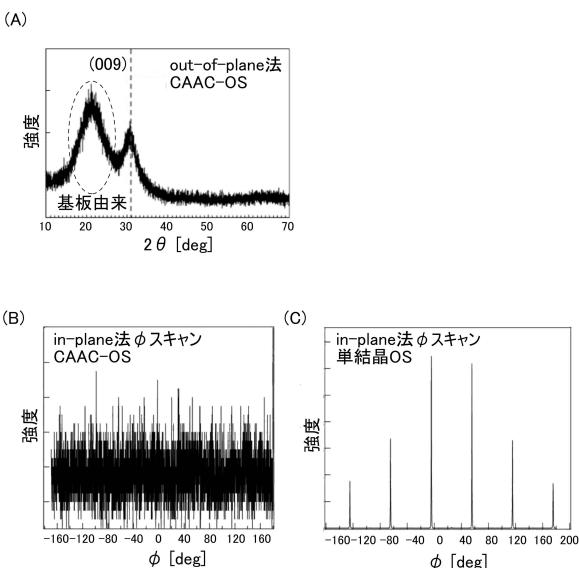

- 【図45】C AAC - O S および単結晶酸化物半導体の X R D による構造解析を説明する図。

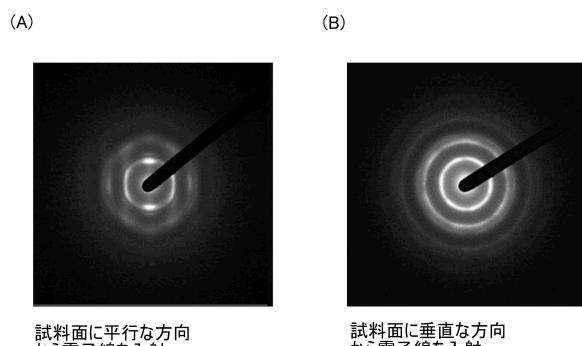

- 【図46】C AAC - O S の電子回折パターンを示す図。

- 【図47】In - Ga - Zn 酸化物の電子照射による結晶部の変化を示す図。

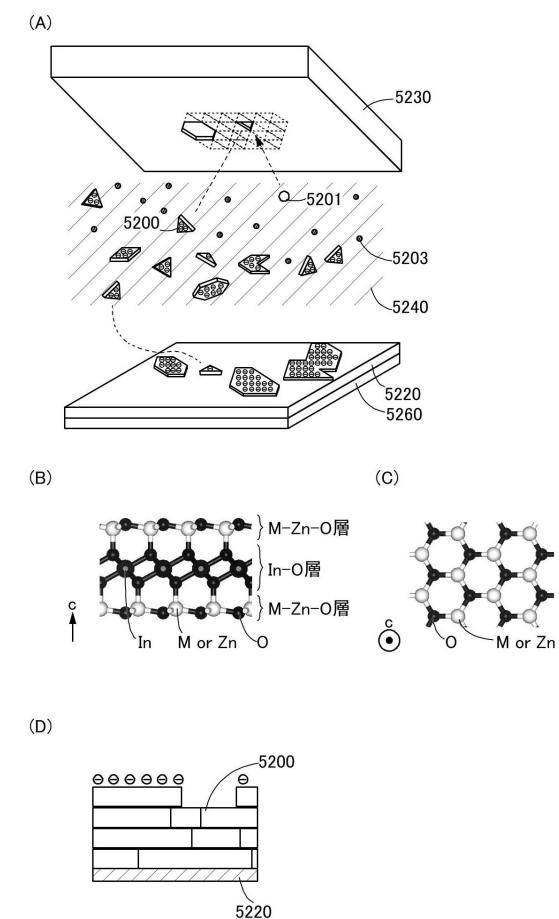

- 【図48】C AAC - O S の成膜方法を説明する図。

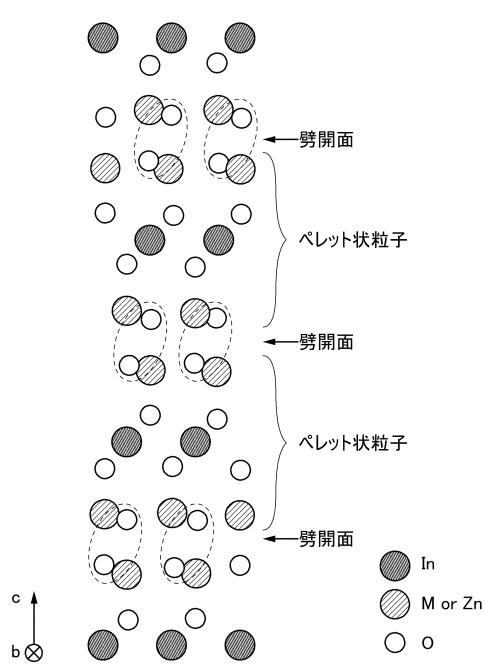

- 【図49】In M Z n O<sub>4</sub> の結晶を説明する図。

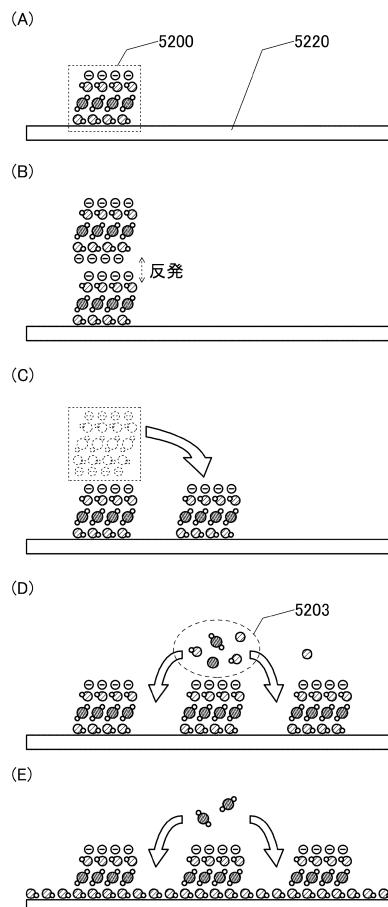

- 【図50】C AAC - O S の成膜方法を説明する図。

- 【図51】C AAC - O S の成膜方法を説明する図。 40

- 【図52】n c - O S の成膜方法を説明する図。

- 【発明を実施するための形態】

- 【0018】

- 実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

- 【0019】

- 以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。また、同様の機能 50

を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

【0020】

本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0021】

本明細書等における「第1」、「第2」等の序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではない。

【0022】

本明細書等において、「平行」とは、二つの直線が -10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。10

【0023】

トランジスタは半導体素子の一種であり、電流や電圧の増幅や、導通または非導通を制御するスイッチング動作などを実現することができる。本明細書等におけるトランジスタは、IGFET (Insulated Gate Field Effect Transistor) や薄膜トランジスタ (TFT: Thin Film Transistor) を含む。また、トランジスタは、ゲート、ソース、およびドレインと呼ばれる3つの端子を有する。本明細書等において、トランジスタのゲート以外の2つの端子について、これらをトランジスタの第1端子、第2端子と呼ぶ場合がある。20

【0024】

例えば、本明細書等において、XとYとが接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とを含むものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも含むものとする。

【0025】

ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

【0026】

XとYとが電気的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に1個以上接続されることが可能である。なお、スイッチは、オンオフが制御される機能を有している。つまり、スイッチは、導通状態（オン状態）、または、非導通状態（オフ状態）になり、電流を流すか流さないかを制御する機能を有している。または、スイッチは、電流を流す経路を選択して切り替える機能を有している。30

【0027】

XとYとが機能的に接続されている場合の一例としては、XとYとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（DA変換回路、AD変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフタ回路など）、電圧源、電流源、切り替え回路、增幅回路（信号振幅または電流量などを大きく出来る回路、オペアンプ、差動增幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制御回路など）が、XとYとの間に1個以上接続されることが可能である。なお、一例として、XとYとの間に別の回路を挟んでいても、Xから出力された信号がYへ伝達される場合は、XとYとは機能的に接続されているものとする。40

【0028】

なお、XとYとが接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟んで接続されてい50

る場合)と、XとYとが機能的に接続されている場合(つまり、XとYとの間に別の回路を挟んで機能的に接続されている場合)と、XとYとが直接接続されている場合(つまり、XとYとの間に別の素子又は別の回路を挟まずに接続されている場合)とを含むものとする。つまり、電気的に接続されている、と明示的に記載する場合は、単に、接続されている、とのみ明示的に記載されている場合と同じであるとする。

#### 【0029】

なお、例えば、トランジスタのソース(又は第1端子など)が、Z1を介して(又は介さず)、Xと電気的に接続され、トランジスタのドレイン(又は第2端子など)が、Z2を介して(又は介さず)、Yと電気的に接続されている場合や、トランジスタのソース(又は第1端子など)が、Z1の一部と直接的に接続され、Z1の別の一部がXと直接的に接続され、トランジスタのドレイン(又は第2端子など)が、Z2の一部と直接的に接続され、Z2の別の一部がYと直接的に接続されている場合では、以下のように表現することが出来る。10

#### 【0030】

例えば、「XとYとトランジスタのソース(又は第1端子など)とドレイン(又は第2端子など)とは、互いに電気的に接続されており、X、トランジスタのソース(又は第1端子など)、トランジスタのドレイン(又は第2端子など)、Yの順序で電気的に接続されている。」と表現することができる。または、「トランジスタのソース(又は第1端子など)は、Xと電気的に接続され、トランジスタのドレイン(又は第2端子など)はYと電気的に接続され、X、トランジスタのソース(又は第1端子など)、トランジスタのドレイン(又は第2端子など)、Yは、この順序で電気的に接続されている」と表現することができる。または、「Xは、トランジスタのソース(又は第1端子など)とドレイン(又は第2端子など)とを介して、Yと電気的に接続され、X、トランジスタのソース(又は第1端子など)、トランジスタのドレイン(又は第2端子など)、Yは、この接続順序で設けられている」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続の順序について規定することにより、トランジスタのソース(又は第1端子など)と、ドレイン(又は第2端子など)とを、区別して、技術的範囲を決定することができる。なお、これらの表現方法は、一例であり、これらの表現方法に限定されない。ここで、X、Y、Z1、Z2は、対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など)であるとする。20

#### 【0031】

##### (実施の形態1)

本実施の形態では、本発明の一態様の回路システムについて、図1乃至図18を用いて説明する。ここでは、回路システムの一例として記憶装置について説明する。

#### 【0032】

##### <回路システムの構成例>

図1は、回路システムの一例を示すブロック図である。

#### 【0033】

図1に示す回路システム10は、メモリセルアレイ12、および周辺回路14を有する。周辺回路14はメモリセルアレイ12と電気的に接続されている。周辺回路14には、行選択ドライバ( Row Driver )、列選択ドライバ( Column Driver )、及びA/Dコンバータ( A/D Converter )等が設けられる。また、周辺回路14には、論理回路等を設けてもよい。40

#### 【0034】

なお、メモリセルアレイ12と、メモリセルアレイ12に電気的に接続する周辺回路14(ここでは、行選択ドライバ、列選択ドライバ、及びA/Dコンバータ)を含む構成を、記憶装置と称してもよい。

#### 【0035】

ここで、図2を用いて、本発明の一態様の回路システムに用いることのできる記憶回路の一例を説明する。50

## 【0036】

図2(A)は、記憶装置の一例を示す回路図である。図2(A)に示す記憶回路25は、トランジスタ21、トランジスタ22、および容量素子23を有する。記憶回路25は、電力が供給されない状況でもデータの保持が可能であり、且つ、書き込み回数にも制限が無い。また、記憶回路25は、例えば、図1に示すメモリセルアレイ12のメモリセルに適用することが可能である。

## 【0037】

トランジスタ21及びトランジスタ22は、具体的には、酸化物半導体を有する半導体層にチャネルが形成されるトランジスタ(以下、"OSトランジスタ"と呼ぶ場合がある。)である。なお、図2(A)に示すように、OS(Oxide Semiconductor)を付記しているものは、酸化物半導体層を有するトランジスタであることを表している。他の図面でも同様である。また、図2(A)には、トランジスタ21及びトランジスタ22の双方ともOSトランジスタである例示しているが、これに限定されず、トランジスタ21またはトランジスタ22の少なくとも一方がOSトランジスタであればよい。トランジスタ22がOSトランジスタであることが非常に好適である。トランジスタ22にOSトランジスタを適用することで、記憶回路25の消費電力を低減することが可能となる。具体的には、トランジスタ22のオフ電流を小さくできるため、長期間にわたり記憶内容を保持することが可能となる。つまり、リフレッシュ動作を必要としない、または、リフレッシュ動作の頻度を極めて少なくすることが可能となるため、消費電力を十分に低減された記憶回路25を提供することができる。

10

20

## 【0038】

また、図2(A)に示す記憶回路25は、データの書き込みに高い電圧が不要であるため、素子の劣化が起こりにくい。例えば、従来のフラッシュメモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行わないため、絶縁体の劣化といった問題が生じない。すなわち、図2(A)に示す記憶回路25は、従来のフラッシュメモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上した半導体装置である。また、トランジスタ22の導通状態、非導通状態によって、データの書き込みが行われるため、高速な動作が可能となる。

## 【0039】

また、記憶回路25の容量素子23の静電容量は、0.1fF以上10fF未満であることが好ましい。容量素子23の静電容量を上記の範囲とすることで、書き込み速度を向上させることができる。言い換えると、書き込み時間を短時間とすることができる。具体的には、室温動作時において、書き込み時間を0.1nsec以上5nsec未満とすることができる。または、室温動作時において、書き込み速度の周波数を、0.2GHzを超えて10GHz以下とすることができる。または室温動作時において、書き込み時間を、ビット速度(bit rateともいう)に換算して、400Mbps(bit per second)以上20Gbps以下とすることができる。

30

## 【0040】

ここでは、書き込み時間とは、記憶回路25の容量素子23を充電することで、データを書き込む場合に容量素子23を90%充電するのに要する時間のことであり、別言すると、ノードFNの電位を、ローレベルの電位からデータ書き込み用のビット線(配線WB-L)の電位の90%まで上昇させるのに要する時間のことを言う。

40

## 【0041】

書き込み速度は、記憶回路の書き込みトランジスタが非導通状態から導通状態となる時間で表してもよい。或いは、書き込み速度は書き込みトランジスタの電流利得が1以上となる最大の周波数(遮断周波数)で表してもよい。なお、記憶回路25では、トランジスタ22が書き込みトランジスタとなる。

## 【0042】

トランジスタ21およびトランジスタ22のいずれか一方または双方は、チャネル長が1nm以上100nm未満の領域を有することが好ましく、チャネル長が5nm以上60

50

$n\text{m}$ 以下の領域を有することがさらに好ましい。トランジスタのチャネル長を上述の範囲とすることで、微細化された記憶装置、または該記憶装置を有する回路面積が小さい回路システム、または該記憶装置を有する消費電力が低い回路システムを提供することができる。

#### 【0043】

図2(A)に示す記憶回路25は、配線WBL(書き込みビット配線ともいう)、配線RBL(読み出しビット配線ともいう)、配線WWL(書き込みワード配線ともいう)、配線RWL(読み出しワード配線ともいう)、および配線SL(ソース線ともいう)と電気的に接続されている。配線RBLはトランジスタ21の第1端子と電気的に接続され、配線SLはトランジスタ21の第2端子と電気的に接続されている。また、配線WBLはトランジスタ22の第1端子と電気的に接続され、配線WWLはトランジスタ22のゲート電極と電気的に接続されている。また、トランジスタ21のゲート電極は、トランジスタ22の第2端子、および容量素子23の第1端子(第1電極)と電気的に接続され、配線RWLは容量素子23の第2端子(第2電極)と電気的に接続されている。10

#### 【0044】

また、図2(A)において、容量素子23の電極とトランジスタ21のゲート電極とが電気的に接続されているノードをノードFNと呼ぶ。符号“FN”は電気的に浮遊状態になることが可能なノードであることを示している。なお、本明細書等において、ノードとは、素子間を電気的に接続するために設けられる配線上のいずれかの箇所のことである。20

#### 【0045】

図2(A)に示す記憶回路25では、トランジスタ21のゲート電極(ノードFN)の電位を長期間保持することが可能である。以下に、記憶回路25の書き込み、保持、読み出しについて説明する。

#### 【0046】

データの書き込みは、まず、配線WWLの電位をトランジスタ22がオン状態となる電位にする。これにより、トランジスタ22がオン状態となり、トランジスタ21のゲート電極および容量素子23の第1端子に配線WBLの電位が与えられる。すなわち、容量素子23には所定の電荷が与えられる。ここでは、配線WBLには、ローレベルまたはハイレベルの二つの電位レベルの何れか一方を与えることとする。容量素子23には配線WBLの電位レベルに対応する電荷が与えられる。次に、配線WWLの電位をトランジスタ22がオフ状態となる電位にする。トランジスタ22をオフ状態となることにより、ノードFNが電気的に浮遊状態となり、容量素子23に与えられた電荷が保持される。このようにして、図2(A)に示す記憶回路25に書き込みを行う。30

#### 【0047】

トランジスタ22のオフ電流は極めて小さいため、容量素子23に与えられた電荷は長期間にわたって保持される。したがって、電源が供給されない状態でもデータの保持が可能となる。

#### 【0048】

データの読み出しについて説明する。配線RBLに所定の電位(定電位)を与えた状態で、配線RWLに適切な電位(読み出し電位)を与えると、容量素子23に保持された電荷量に応じて、配線SLは異なる電位をとる。トランジスタ21をnチャネル型とすると、トランジスタ21のゲート電極にハイレベル電位が与えられている場合の見かけのしきい値 $V_{th\_H}$ は、一般に、トランジスタ21のゲート電極にローレベルの電位が与えられている場合の見かけのしきい値 $V_{th\_L}$ より低くなる。ここで、見かけのしきい値電圧とは、トランジスタ21を「オン状態」とするために必要な配線RWLの電位をいうものとする。したがって、配線RWLの電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、トランジスタ21のゲート電極に与えられた電位を判別できる。例えば、書き込みにおいて、トランジスタ21のゲート電極にハイレベル電位が与えられていた場合には、配線RWLの電位が $V_0 (> V_{th\_H})$ となれば、トランジスタ21は「オン状態」となる。ローレベル電位が与えられていた場合には、配線RWLの電位が $V_0 (<$ 40

$V_{t h\_L}$ ) とっても、トランジスタ 21 は「オフ状態」のままである。このため、配線 RBL の電位を判別することで、保持されているデータを読み出すことができる。

#### 【0049】

なお、記憶回路 25 をアレイ状に配置して用いる場合、所望の記憶回路 25 のデータのみを読み出せることが必要になる。このようにデータを読み出さない場合には、容量素子 23 に保持された電荷量にかかわらずトランジスタ 21 が「オフ状態」となるような電位、つまり、 $V_{t h\_H}$  より小さい電位を配線 RWL に与えればよい。または、データを読み出す場合には、容量素子 23 に保持された電荷量にかかわらずトランジスタ 21 が「オン状態」となるような電位、つまり、 $V_{t h\_L}$  より大きい電位を配線 RWL に与えればよい。

10

#### 【0050】

図 2(A) は、2 トランジスタのゲインセル構造の一例である。メモリセルの構造は、図 2(A) に限定されない。例えば、図 2(B) に示す記憶回路 26 や、図 2(C) に示す記憶回路 27 をメモリセルに適用することが可能である。

#### 【0051】

図 2(B) に示す記憶回路 26 は、3 トランジスタのゲインセル構造の一例である。記憶回路 26 において、トランジスタ 24 は読み出し用トランジスタとして機能し、配線 RWL にゲートが電気的に接続されている。容量素子 23 の第 1 端子はノード FN と電気的に接続され、第 2 端子は配線 CNL と電気的に接続されている。記憶回路 26 も記憶回路 25 と同様に駆動することができる。データの読み出し時に、必要に応じて、配線 CNL の電位を制御して、ノード FN の電位を上昇させるようにすればよい。

20

#### 【0052】

図 2(C) に示す記憶回路 27 は、トランジスタ 21 を設けていない点で記憶回路 25 と相違している。記憶回路 27 も記憶回路 25 と同様に駆動することができる。記憶回路 27 のデータの読み出し動作を説明する。トランジスタ 22 がオン状態となると、浮遊状態である配線 WBL と容量素子 23 とが導通し、配線 WBL に付随する配線容量と容量素子 23 の間で電荷が再分配される。その結果、配線 WBL の電位が変化する。配線 WBL の電位の変化量は、容量素子 23 に蓄積された電荷量（または容量素子 23 の第 1 端子の電位）によって、異なる値をとる。

#### 【0053】

30

例えば、容量素子 23 の第 1 端子（ノード FN）の電位を V、容量素子 23 の容量を C、配線 WBL に付随する配線容量を CB、電荷が再分配される前の配線 WBL の電位を VB0 とし、配線 RWL の電位を 0 [V]、配線 WBL に付随する配線容量の他方の電極の電位を 0 [V] とすると、電荷が再分配された後の配線 WBL の電位は、 $(CB \times VB_0 + C \times V) / (CB + C)$  となる。したがって、記憶回路 27 の状態が、容量素子 23 の第 1 端子の電位 V が  $V_1$  と  $V_0$  ( $V_1 > V_0$ ) の 2 状態をとるとすると、電位  $V_1$  を保持している場合の配線 WBL の電位 ( $= (CB \times VB_0 + C \times V_1) / (CB + C)$ ) は、電位  $V_0$  を保持している場合の配線 WBL の電位 ( $= (CB \times VB_0 + C \times V_0) / (CB + C)$ ) よりも高くなることがわかる。よって、配線 WBL の電位を所定の電位と比較することで、データを読み出すことができる。

40

#### 【0054】

図 2(D) に示す記憶回路 25 のデバイス構造の一例を図 2(D) に示す。図 2(D) には、記憶回路 25 のトランジスタ 21、22 のチャネル長の方向の断面を図示している。なお、実際の記憶回路 25 において、トランジスタ 21 とトランジスタ 22 のチャネル長方向が一致していなくてもよい。これは、他の図面においても同様である。

#### 【0055】

図 2(D) に示す記憶回路 25 は、基板 31 上のトランジスタ 21 と、トランジスタ 21 の上方の容量素子 23 と、トランジスタ 21 及び容量素子 23 上のトランジスタ 22 と、を有する。トランジスタ 21 は、基板 31 上の導電膜 32 と、導電膜 32 上の絶縁膜 33 と、絶縁膜 33 上の半導体膜 34a と、半導体膜 34a 上の半導体膜 34b と、半導体

50

膜34bと電気的に接続される導電膜35と、半導体膜34bと電気的に接続される導電膜36と、導電膜35、半導体膜34b、及び導電膜36上の半導体膜34cと、半導体膜34c上の絶縁膜37と、絶縁膜37上の導電膜38と、を有する。

#### 【0056】

トランジスタ21において、導電膜32は、バックゲート電極としての機能を有する。また、絶縁膜33は、半導体膜34の下地膜としての機能、及びゲート絶縁膜としての機能を有する。また、導電膜35、36は、ソース電極及びドレイン電極としての機能を有する。また、絶縁膜37は、ゲート絶縁膜としての機能を有する。また、導電膜38は、ゲート電極としての機能を有する。

#### 【0057】

トランジスタ22は、導電膜42と、導電膜42上の絶縁膜43と、絶縁膜43上の半導体膜44aと、半導体膜44a上の半導体膜44bと、半導体膜44bと電気的に接続される導電膜45と、半導体膜44bと電気的に接続される導電膜46と、導電膜45、半導体膜44b、及び導電膜46上の半導体膜44cと、半導体膜44c上の絶縁膜47と、絶縁膜47上の導電膜48と、を有する。

#### 【0058】

トランジスタ22において、導電膜42は、バックゲート電極としての機能を有する。また、絶縁膜43は、半導体膜44の下地膜としての機能、及びゲート絶縁膜としての機能を有する。また、導電膜45、46は、ソース電極及びドレイン電極としての機能を有する。また、絶縁膜47は、ゲート絶縁膜としての機能を有する。また、導電膜48は、ゲート電極としての機能を有する。図2(D)には、トランジスタ21及びトランジスタ22がバックゲート電極を有する構成を例示しているが、これに限定されず、バックゲート電極を設けない構成としてもよい。

#### 【0059】

図2(D)に示すように、トランジスタ21、容量素子23、及びトランジスタ22の構成要素の少なくとも一部を重ねて配置させることで、回路面積の小さい回路システムとすることができます。

#### 【0060】

次に、図2(D)に示す記憶回路25を複数有する半導体装置の一例について、図3乃至図7を用いて説明する。

#### 【0061】

<メモリセルアレイの構成例>

図3(A)は、メモリセルアレイの一例を示す模式図である。図3(A)に示すメモリセルアレイ300には、サブアレイSCAが、平面において横a個×縦b個(a、bは自然数)のアレイ状に配置されている。各サブアレイSCAは、積層されているc個(cは自然数)のメモリセルMCからなる。このように、メモリセルアレイ300はメモリセルMCが3次元的に配列されている構造を有する。

#### 【0062】

明細書、図面において、同じ要素(信号、配線、素子、回路等)を区別するため、"\_\_\_\_1"、"[L1]"などの行番号、列番号、順序等を表す識別記号を用語に付ける場合がある。例えば、"MC\_j"とは、サブアレイSCAの第j(jは1からcまでの自然数)のメモリセルMCであることを表している。

#### 【0063】

メモリセルMCは、記憶回路25～27(図2)と同様な回路構成とすることができます。図3(B)にメモリセルMC\_jの回路図の一例を示す。図3(B)に示すメモリセルMC\_jは、トランジスタTa\_j、トランジスタTb\_j及び容量素子Ca\_jを有する。図3(B)に示すメモリセルMC\_jは、図2(A)に示す記憶回路25の変形例である。ここで、"Ta\_j"の符号は、トランジスタTaがメモリセルMC\_jの構成要素であることを示している。他の図面でも、このような符号を用いる場合がある。

#### 【0064】

10

20

30

40

50

トランジスタ T a\_j の第 1 端子は配線 B\_L と電気的に接続され、第 2 端子はトランジスタ T b\_j のゲート電極と電気的に接続されている。トランジスタ T a\_j のゲート電極は配線 W\_W\_L\_j に電気的に接続されている。トランジスタ T b\_j の第 1 端子は配線 B\_L と電気的に接続され、第 2 端子は配線 S\_L と電気的に接続されている。容量素子 C\_a\_j の第 1 端子（第 1 電極）はトランジスタ T b\_j のゲート電極と電気的に接続され、第 2 端子（第 2 電極）は配線 R\_W\_L\_j と電気的に接続される。

#### 【 0 0 6 5 】

トランジスタ T a\_j は、バックゲート電極（B\_G）を有する。例えば、バックゲート電極にソース電極よりも低い電位または高い電位を印加することができるため、トランジスタ T a\_j のしきい値電圧をプラス方向またはマイナス方向へ変動させることができる。<sup>10</sup> n チャネル型トランジスタのしきい値電圧をプラス方向に変動させることで、ゲート電位が 0 V であってもトランジスタが非導通状態（オフ状態）となる、ノーマリーオフが実現できる場合がある。なお、バックゲート電極に印加する電位は、可変であってもよいし、固定であってもよい。バックゲート電極に印加する電位を可変にする場合、電位を制御する回路をバックゲート電極に接続してもよい。また、バックゲート電極は、トランジスタ T a\_j のゲート電極と接続してもよい。バックゲート電極とゲート電極とを接続し、同じ電位を印加することにより、オン電流の増加、初期特性バラつきの低減、-GBT (-Gate Bias - Temperature) ストレス試験の劣化の抑制、及び異なるドレイン電圧におけるオン電流の立ち上がり電圧の変動の抑制が可能である。トランジスタ T a\_j のオン電流を増加させることにより、例えばメモリセルアレイ 300 の書き込み時間を短縮することができる。<sup>20</sup>

#### 【 0 0 6 6 】

また、図 3 (B) には図示しないが、トランジスタ T b\_j も、バックゲート電極を有してもよい。バックゲート電極を設けることで、トランジスタ T b\_j のオン電流を増加させることができあり、オン電流の増加により、例えばメモリセルアレイ 300 の読み出し速度を高めることができる。

#### 【 0 0 6 7 】

ここでは、配線 W\_W\_L\_j に与えられるワード信号を制御することで、ノード F\_N の電位が配線 B\_L の電位に応じた電位にすることを、メモリセル M\_C\_j にデータを書き込む、という。また、配線 R\_W\_L\_j に与えられる読み出し信号を制御することで、配線 B\_L の電位をノード F\_N の電位に応じた電位にすることを、メモリセル M\_C\_j からデータを読み出す、という。<sup>30</sup>

#### 【 0 0 6 8 】

配線 B\_L には、2 値、または多値のデータに対応する電位が与えられる。多値のデータは、k ビット（k は 2 以上の自然数）のデータである。具体的には、2 ビットのデータであれば 4 値のデータであり、配線 B\_L に入力される信号は 4 種類の電位レベルを有することになる。配線 R\_W\_L\_j には、読み出し信号が与えられる。読み出し信号は、メモリセル M\_C\_j からデータを選択的に読み出すために、ノード F\_N の電位を制御するための信号である。また、配線 W\_W\_L\_j には、ワード信号が与えられる。ワード信号は、配線 B\_L の電位をノード F\_N に与えるために、トランジスタ T a\_j を導通状態とする信号である。<sup>40</sup>

#### 【 0 0 6 9 】

ノード F\_N は、容量素子 C\_a\_j の第 1 電極、トランジスタ T a\_j の第 2 端子、及びトランジスタ T b\_j のゲート電極を接続する配線上のいずれかのノードに相当する。例えば、ノード F\_N に液晶素子や有機 EL (Electroluminescence) 素子などの表示素子を電気的に接続してもよい。上記表示素子を有する場合、メモリセル M\_C\_j の一部を表示装置の画素として機能させることができる。

#### 【 0 0 7 0 】

ノード F\_N の電位は、配線 B\_L に与えられるデータに基づく電位である。ノード F\_N は、トランジスタ T a\_j を非導通状態とすることで電気的に浮遊状態になり、また、容量<sup>50</sup>

素子 C a \_ j によって配線 R W L \_ j とトランジスタ T b \_ j が容量結合している。そのため、配線 R W L \_ j の電位を変化させることで、ノード F N の電位を変化させることができる。配線 R W L \_ j に与えられる読み出し信号の電位を変化させると、ノード F N の電位は元の電位に読み出し信号の電位の変化分が加わった電位となる。

#### 【 0 0 7 1 】

トランジスタ T a \_ j は、導通状態と非導通状態とを切り換えることで、データの書き込みを制御するスイッチとしての機能を有する。また、トランジスタ T a \_ j は、非導通状態を維持することで、書き込んだデータに基づく電位を保持する機能を有する。ここでは、トランジスタ T a \_ j は n チャネル型のトランジスタとする。

#### 【 0 0 7 2 】

なお、トランジスタ T a \_ j は、非導通状態においてソース電極とドレイン電極との間を流れる電流（オフ電流）が低いトランジスタが用いられることが好適である。ここでは、オフ電流が低いとは、室温において、ソース電極とドレイン電極との間の電圧を 10 V とし、チャネル幅 1 μmあたりの規格化されたオフ電流が 10 z A 以下であることをいう。このようにオフ電流が少ないトランジスタとしては、半導体層に酸化物半導体を有するトランジスタが挙げられる。

#### 【 0 0 7 3 】

トランジスタ T a \_ j にオフ電流の小さいトランジスタを用いることによって、電気的に浮遊状態とされているノード F N の電位を長期間に渡って保持することができる。したがって、メモリセル M C \_ j のリフレッシュ頻度を低減することができるため、消費電力の少ない半導体装置を実現することができる。

#### 【 0 0 7 4 】

例えば、ノード F N に保持された電位を 85 において 10 年間 ( $3 \cdot 15 \times 10^8$  秒) 保持するためには、トランジスタ T a \_ j は、容量 1 fFあたり、規格化されたオフ電流値が 4.3 yA (ヨクトアンペア : 1 yA は  $1 \times 10^{-24}$  A) 未満であることが好ましい。この場合、ノード F N の許容される電位の変動が 0.5 V 以内であることが好ましい。または、95 において、規格化されたオフ電流が 1.5 yA 未満であることが好ましい。

#### 【 0 0 7 5 】

図 3 (B) に示すメモリセル M C \_ j の構成では、トランジスタ T a \_ j の非導通状態を維持することで、ノード F N の電位を保持している。そのため、ノード F N での電荷の移動を伴った電位の変動を抑えることが可能なスイッチとして、トランジスタ T a \_ j はオフ電流が少ないトランジスタであることが特に好ましい。

#### 【 0 0 7 6 】

よって、トランジスタ T a \_ j をオフ電流が少ないトランジスタとして、メモリセルアレイ 300 を不揮発性のメモリとすることができる。つまり、一旦、メモリセル M C \_ j に書き込まれたデータは、再度、トランジスタ T a \_ j を導通状態とするまで、ノード F N に保持し続けることができる。

#### 【 0 0 7 7 】

トランジスタ T b \_ j は、ノード F N の電位に従って、ソース電極とドレイン電極との間に電流 I d を流す機能を有する。図 3 (B) に示すメモリセル M C \_ j の構成では、トランジスタ T b \_ j のソース電極とドレイン電極との間に流れる電流 I d は、配線 B L と配線 S L との間に流れる電流である。トランジスタ T b \_ j は、例えばシリコンを活性層に用いたトランジスタ（以下、Siトランジスタと呼ぶ）を用いてもよく、また酸化物半導体を活性層に用いた OSトランジスタを用いてもよい。ここでは、トランジスタ T b \_ j は OSトランジスタであり、かつ n チャネル型のトランジスタとする。

#### 【 0 0 7 8 】

トランジスタ T a \_ j 及びトランジスタ T b \_ j は、一例として、スイッチング速度の速い n チャネル型トランジスタを用いることができる。例えば、トランジスタのスイッチング速度は、0.1 n 秒以上 5 n 秒未満である。一例として、チャネル領域が酸化物半導

10

20

30

40

50

体（好ましくはIn、Ga、及びZnを含む酸化物）を含むOSトランジスタを用いることで、上記のスイッチング速度を実現することができる。なお、トランジスタのスイッチング速度とは、一つのトランジスタが非導通状態から導通状態となる時間を表す。或いは、トランジスタのスイッチング速度とは、トランジスタを増幅器として用いる場合に、電流利得が1以上となる最大の周波数（遮断周波数）に対応する速度で表しても良い。

#### 【0079】

<メモリセルアレイの回路構成例1>

ここで、図3(B)に示すメモリセルMC\_jを3次元的に配列し、メモリセルアレイ300とする場合の一例を図4に示す。図4は、メモリセルアレイ300の一例を示す回路図であり、サブアレイSCAの一例を示す回路図でもある。図4に示すように、サブアレイSCAはc個のメモリセルMCを有し、各メモリセルMCは、それぞれ、配線BL及び配線SLを共有している。10

#### 【0080】

<メモリセルアレイの動作例>

次に、図4に示すメモリセルアレイ300の動作を説明する。図5は、図4に示すメモリセルアレイ300の動作の一例を説明するタイミングチャートである。図5のタイミングチャートは、配線WWL\_c、配線RWL\_c、ノードFN、配線BL、及び配線SLに与えられる各信号の変化を示すものである。

#### 【0081】

まず、図5(A)を用いて、書き込みの動作を説明する。ここでは2値のデータの書き込みについて説明を行うが、メモリセルアレイ300は2値のデータの書き込みに限定されず、多値のデータを書き込むこともできる。図5(A)に示すタイミングチャートには、書き込み期間T1、休止期間T2、及び非選択期間T3を示す。20

#### 【0082】

書き込み期間T1では、まず配線WWL\_cに電位V2が与えられる。次いで、配線BLに2値のデータに応じた電位、つまりハイ(H)レベルの電位またはロー(L)レベルの電位が与えられる。また、配線SLには、配線BLと同じレベルの電位を与える。配線BLがHレベルの時、配線SLにもHレベルの電位が与えられる。配線BLがLレベルの時、配線SLにも、Lレベルの電位が与えられる。

#### 【0083】

休止期間T2では、配線BL及び配線SLにLレベルの電位が与えられ、配線RWL\_c及び配線WWL\_cには電位V0が与えられる。ここで、例えば電位V0は接地電位とし、電位V2は正の電位とすればよい。また、電位V2の絶対値は、Hレベルの電位よりも大きいことが好ましく、例えば、Hレベルの電位+トランジスタTa\_cのしきい値電圧よりも大きく、且つHレベルの電位+トランジスタTa\_cのしきい値電圧の3倍未満とすればよい。

#### 【0084】

非選択期間T3では、配線RWL\_c及び配線WWL\_cに電位V1が与えられる。電位V1は例えば負の電位とすればよい。電位V1の絶対値は、Hレベルの電位よりも大きいことが好ましく、例えば、Hレベルの電位+トランジスタTb\_cのしきい値電圧よりも大きく、且つHレベルの電位+トランジスタTb\_cのしきい値電圧の3倍未満とすればよい。また、配線BL及び配線SLにはLレベルの電位が与えられる。40

#### 【0085】

次に、図5(B)を用いて、読み出しの動作について説明する。図5(B)に示すタイミングチャートには、配線BLの電位をプリチャージする期間T4、データを読み出すために配線BLの放電を行う期間T5、非選択の期間T6を示している。

#### 【0086】

図5(B)に示す期間T4では、配線BLをプリチャージする。このとき、配線WWL\_cに電位V1が与えられる。また、配線RWL\_cは、電位V1が与えられる。ここで、V1は、V0よりも低い電位である。例えば、V0を接地電位とし、V1を負の電位と50

すればよい。また、ノード F N では、データに対応する電位が保持されている。また、配線 B L は、H レベルの電位 (V H) が与えられる。また、配線 S L は、L レベルの電位が与えられる。ここで、電位 V 1 の絶対値は、H レベルの電位より大きいことが好ましく、例えば、H レベルの電位 + トランジスタ T b\_c のしきい値電圧よりも大きく、且つ H レベルの電位 + トランジスタ T b\_c のしきい値電圧の 3 倍未満にすればよい。

#### 【0087】

期間 T 4 では、配線 B L は、H レベルの電位 V H が与えられた後、電気的に浮遊状態となる。すなわち、配線 B L は、電荷の充電又は放電により電位の変動が生じる状態となる。この浮遊状態は、配線 B L に電位を与えるスイッチをオフにすることで実現できる。

#### 【0088】

次いで、図 5 (B) に示す期間 T 5 では、データを読み出すためにノード F N の電位により配線 B L の放電を行う。このとき、配線 W W L\_c は、期間 T 4 に引き続き、電位 V 1 が与えられる。配線 S L は、前の期間に引き続き、L レベルの電位が与えられる。配線 R W L\_c は、電位 V 0 の電位が与えられるため、ノード F N の電位が上昇する。ノード F N の電位により、トランジスタ T b\_c の導通状態が変化する。ノード F N に H レベルの電位が書き込まれている場合には、トランジスタ T b\_c が導通状態となり、配線 B L の電位は低下し、電位 V L となる。ノード F N に L レベルの電位が書き込まれている場合には、トランジスタ T b\_c が非導通状態のため、配線 B L の電位は H レベルの状態が維持される。

#### 【0089】

次いで、図 5 (B) に示す期間 T 6 では、配線 R W L\_c の電位を V 1 とし、メモリセル M C\_c を非選択の状態にする。これで、メモリセル M C\_c からデータを読み出す動作が完了する。

#### 【0090】

<メモリセルアレイの回路構成例 2、3 >

メモリセルアレイ 300 の他の回路構成例を図 6 及び図 7 に示す。図 6 及び図 7 は、メモリセルアレイ 300 の一例を示す回路図であり、サブアレイ SCA の回路図である。

#### 【0091】

図 6 の回路構成例は、図 4 の変形例である。図 4 の例と異なる点は、奇数番のメモリセル M C と偶数番のメモリセル M C とが異なる配線 S L に電気的に接続されていること、配線 B L に対して、奇数番のメモリセル M C と偶数番のメモリセル M C が互い違いに接続されていることである。そのため、サブアレイ SCA の集積度を高めることができる。または、面積あたりの記憶容量を高めることができる。図 7 に示すサブアレイ SCA では、c 個のメモリセル M C が 1 つの配線 S L を共有している。このため、配線 S L の本数を少なくすることができる。

#### 【0092】

<メモリセルの積層構造例 1 >

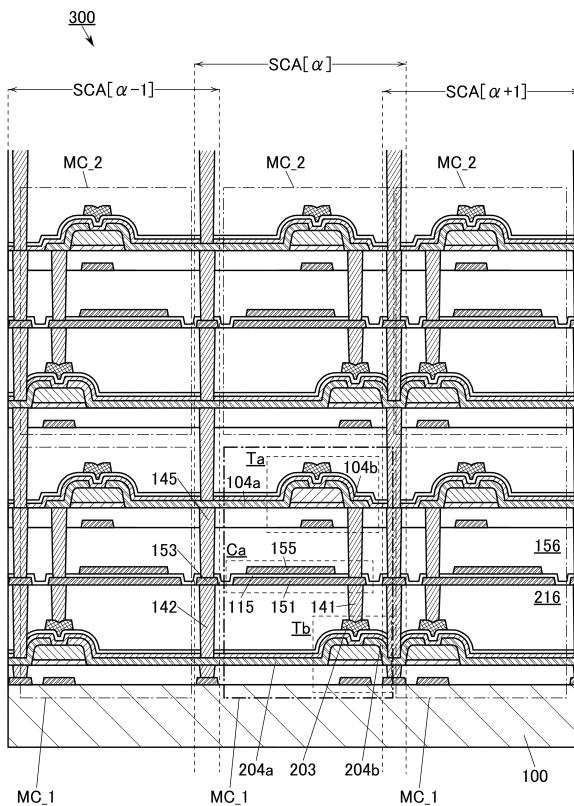

図 8 はメモリセルアレイの一例を示す断面図である。図 8 の例は、図 4 の回路構成を有するサブアレイ SCA でメモリセルアレイを構成した例に相当する。

#### 【0093】

図 8 には、隣接する 3 つのサブアレイ (SCA [-1], SCA [ ], SCA [+1]) を図示している。サブアレイ SCA が互いに隣接するとは、図 3 (A) に示す x-y 平面において x 座標、y 座標の一方が 1 異なり、他方が同じであることを示す。例えば、3 つのサブアレイ (SCA [-1], SCA [ ], SCA [+1]) の y 座標が等しい場合、サブアレイ SCA [ ] の x 座標が k (k は 2 以上 a 以下の整数) であれば、サブアレイ SCA [-1] の x 座標は k - 1 であり、サブアレイ SCA [+1] の x 座標は k + 1 である。

#### 【0094】

図 8 には、サブアレイ (SCA [-1], SCA [ ], SCA [+1]) のメモリセル M C\_1 及びメモリセル M C\_2 を示している。図示しないが、各サブアレイのメ

10

20

30

40

50

モリセルMC\_2の上には、それぞれ、メモリセルMC\_3が積層され、順にメモリセルMC\_cまで積層される。メモリセルMCの積層数を多くすることで、回路面積を増加させずに、メモリセルアレイ300の集積度を高めることができる。

#### 【0095】

以下、図8に示すメモリセルアレイ300のデバイス構造について説明する。図8において、図面の明瞭化のため、メモリセルアレイ300を構成する一部の要素（トランジスタTa等）の符号には、識別記号”\_1”を付けていない。明細書中では、識別符号”\_1”等を付して、または付けずに、メモリセルアレイ300の構造を説明する場合がある。他の図面についても同様である。

#### 【0096】

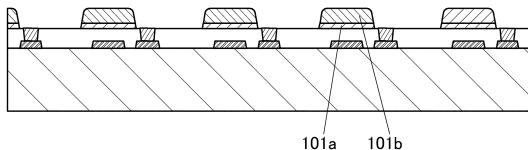

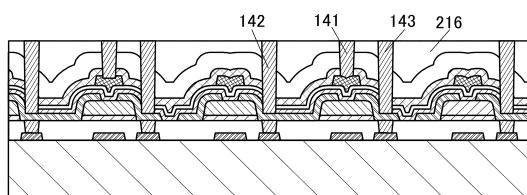

各メモリセルMCは、トランジスタTa及びトランジスタTbは、酸化物半導体材料を含んで構成される。トランジスタTbの上には容量素子Caが設けられている。トランジスタTbと容量素子Caの間には絶縁膜216が設けられている。容量素子Caの少なくとも一部は、トランジスタTbと重なるように設けられることが好ましい。絶縁膜115は、導電膜151及び導電膜155に挟まれ、容量素子Caを形成する。導電膜204a、導電膜204bは、それぞれ、トランジスタTbのソース電極またはドレイン電極として機能する。導電膜151は、プラグ141を介してトランジスタTbのゲート電極203と電気的に接続される。

#### 【0097】

容量素子Caの上にはトランジスタTaが設けられている。容量素子CaとトランジスタTaの間には絶縁膜156が設けられている。トランジスタTaの少なくとも一部は、容量素子Caと重なるように設けられることが好ましい。導電膜104a、導電膜104bはそれぞれ、トランジスタTaのソース電極またはドレイン電極として機能する。

#### 【0098】

導電膜204a、204bは配線SL（図示しない）に電気的に接続される。導電膜204aは、プラグ142、導電膜153、及びプラグ145等を介して導電膜104aと電気的に接続される。導電膜204a及び導電膜104aは配線BL（図示しない）に電気的に接続されている。プラグ142、導電膜153、及びプラグ145等を配線BLとして機能させてもよい。

#### 【0099】

隣接する2つのメモリセルMC\_jは、プラグ142、導電膜153等を共有する。具体的には、サブアレイSCA[ ]のメモリセルMC\_jは、サブアレイSCA[-1]のメモリセルMC\_jと、プラグ142、プラグ145および導電膜153を共有する。隣接する2つのサブアレイSCAでプラグや導電層を共有することにより、メモリセルアレイ300の集積度を高めることができる。

#### 【0100】

また、隣接するMC\_jにおいて導電膜104aおよび導電膜204bが共有されている。具体的には、サブアレイSCA[-1]とサブアレイSCA[ ]のそれぞれのトランジスタTaは、導電膜104aを共有する。サブアレイSCA[ ]とサブアレイSCA[+1]のそれぞれのトランジスタTbは導電膜204aを共有する。このように導電膜を共有することにより、メモリセルアレイ300の集積度を高めることができる。

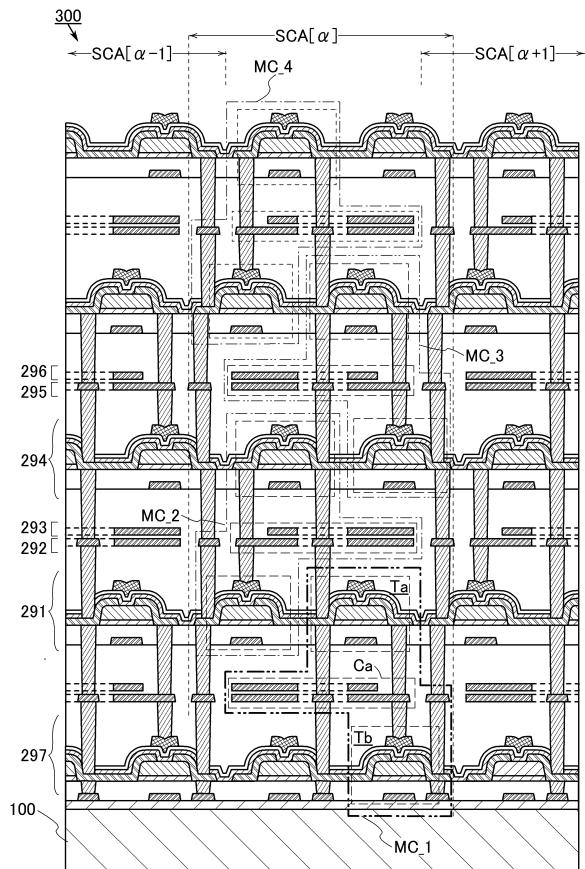

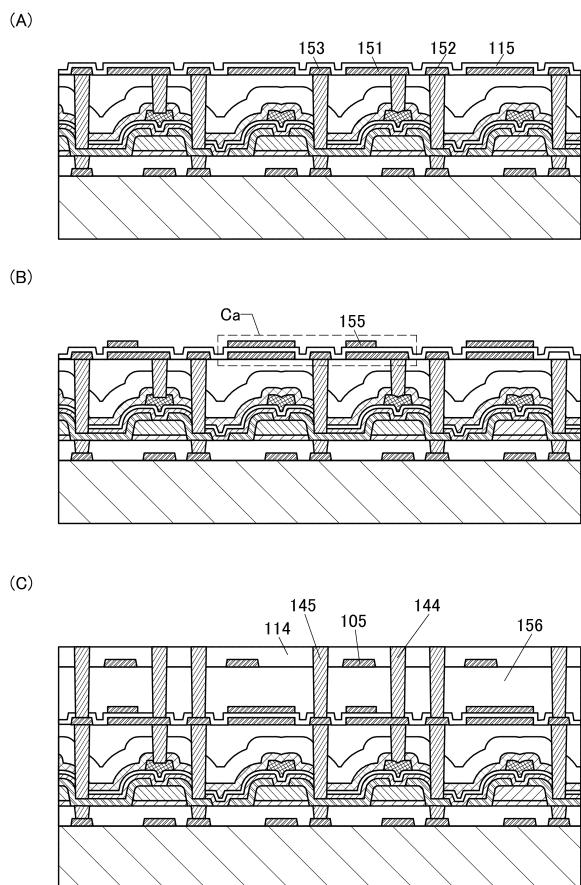

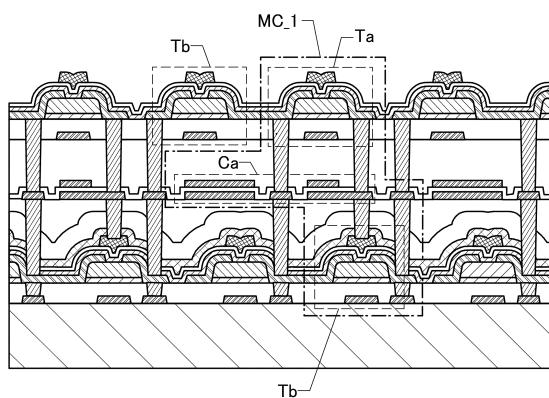

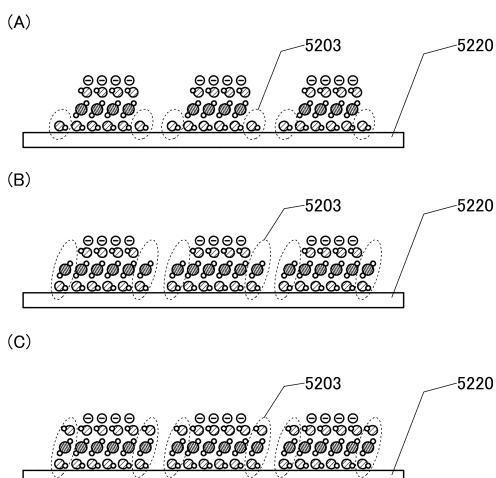

#### 【0101】

##### <メモリセルの積層構造例2>

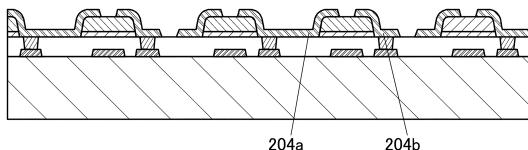

図9及び図10に、図8示すメモリセルアレイ300の変形例を示す。図10は図9の一部を拡大した図である。図9に示すメモリセルアレイ300は基板100上に形成され、層291乃至層297を有する。また、層291はトランジスタを有する。また、層292及び層293は導電膜を有する。また、層294はトランジスタを有する。また、層295及び層296は導電膜を有する。また、層297はトランジスタを有する。

#### 【0102】

図8に示すメモリセルアレイ300のサブアレイSCAでは、トランジスタTb、容量

10

20

30

40

50

素子C a、トランジスタT a、トランジスタT b、容量素子C a、トランジスタT aの順に積層されている。これに対し、図9に示すサブアレイSCAでは、メモリセルMCを互い違いに配置することによりトランジスタT b、容量素子C a、トランジスタT a、容量素子C a、トランジスタT bの順に積層される。よって、工程を簡略化することができる。

#### 【0103】

メモリセルMCにおいて、トランジスタT bの上には容量素子C aが設けられ、容量素子C a上にトランジスタT aが設けられている。容量素子C aは、トランジスタT bと重なる領域を有し、また、トランジスタT aと重なる領域を有することが好ましい。また、容量素子C aの一部は、隣接するメモリセルMCのトランジスタT bと重なる領域を有していてもよい。図9に示すようなデバイス構造とすることで、メモリセルアレイ300の集積度を高めることができる。10

#### 【0104】

具体的には、サブアレイSCA [ ]において、メモリセルMC\_2とメモリセルMC\_3は左右対称の構造を有する。そのため、容量素子C aは、トランジスタT a、およびトランジスタT bと重なっている。このような構造とすることにより、サブアレイSCAにおいて、メモリセルMCを互い違いに配置することができ、1つ下のメモリセルMCのトランジスタT a上に容量素子を形成することができ、集積度を高めることができる。図8に示すメモリセルアレイ300と比べて工程を簡略化することができる。20

#### 【0105】

また、サブアレイSCA [ ]において、c個のメモリセルMCを互い違いに配置することにより、上下に隣接する2つのメモリセルMCでは、それぞれ、トランジスタT aとトランジスタT bとが同じ層に形成される。このように、上下に隣接するメモリセルの有するトランジスタが同一層に形成されることで、メモリセルアレイ300を構成する層の数が削減されるため、より少ない工程でメモリセルアレイ300を作製することができる。少ない工程で作製することにより、歩留まりを高めることができる。また、積層される層数が増えるのに伴い、例えば、絶縁膜、導電膜、半導体膜等が有する膜応力により、膜の剥がれや割れなどが生じる可能性がある。よって、積層される膜の数を少なくすることにより、膜剥がれ等による半導体装置の故障を低減することができる。30

#### 【0106】

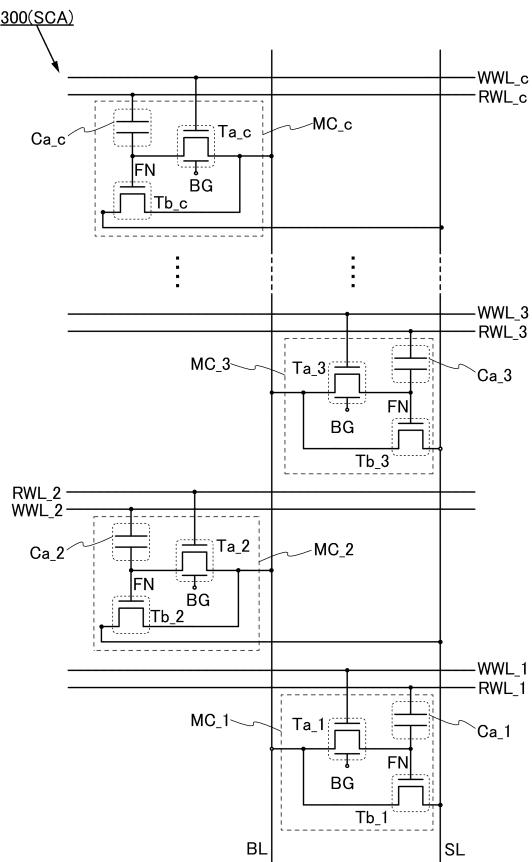

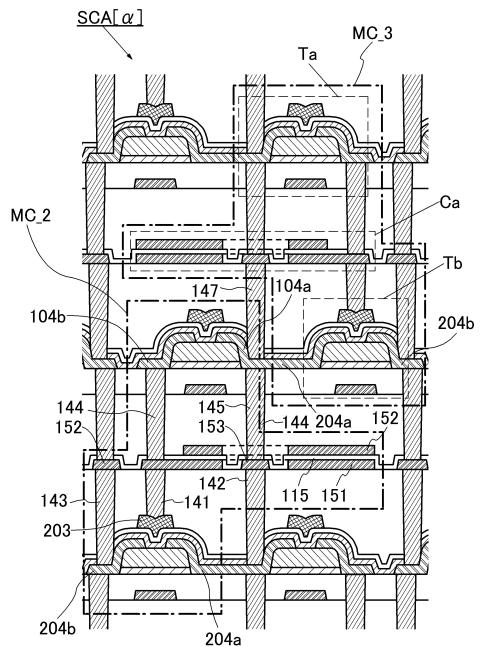

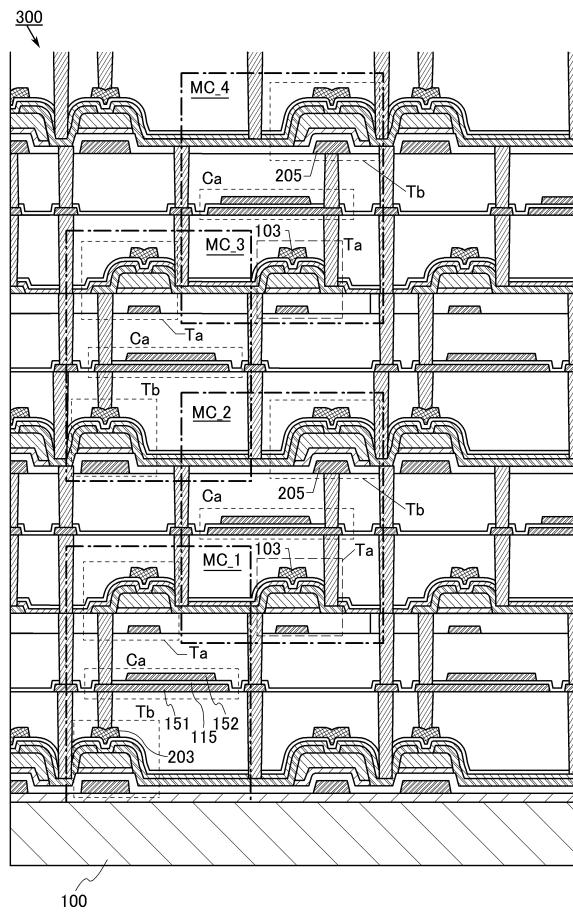

##### <メモリセルの積層構造例3>

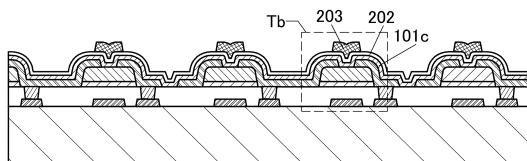

図11にメモリセルアレイの一例を示す。図11に示すメモリセルアレイ300は、図8及び図9に示すメモリセルアレイ300の変形例である。

#### 【0107】

図11に示すメモリセルアレイ300は、メモリセルMCが互い違いに配置されている点で図9と共に通する。次の点で相違する。メモリセルMCでは、トランジスタT aの上に容量素子C aが位置し、容量素子C aの上にトランジスタT bが位置している。また、奇数番目のメモリセルMC（図11中では、MC\_1、MC\_3）では、トランジスタT bのゲート電極203が容量素子C aと電気的に接続されている。偶数番目のメモリセルMC（図11中ではメモリセルMC\_2及びメモリセルMC\_4）では、導電膜205が、容量素子C aと電気的に接続されている。導電膜205は、トランジスタT bのバックゲート電極として機能する。40

#### 【0108】

つまり、図11の例では、jが奇数のメモリセルMC\_jと、偶数のメモリセルMC\_jとで構造が異なる。また、図11の例では、トランジスタT aとトランジスタT bを同一の層に形成する必要がなく、トランジスタT aの有する半導体膜とトランジスタT bの有する半導体膜が異なる半導体膜から形成することができる。そのため、トランジスタT aとトランジスタT bのそれぞれの半導体膜を、例えば構成元素や原子数比の異なる酸化物半導体膜で形成することが容易である。

#### 【0109】

10

20

30

40

50

以上がメモリセルアレイ 300 の構成例についての説明である。次に、メモリセルアレイ 300 が有するトランジスタ T<sub>a</sub> 及びトランジスタ T<sub>b</sub> の構造について説明する。

#### 【0110】

<トランジスタの構成例 1>

図 12 (B) は、トランジスタの構成の一例を示す上面図であり、図 12 (A) は、図 12 (B) の A - B 線断面図であり、図 12 (C) は図 12 (B) の C - D 線断面図である。図 12 に示すトランジスタ TR1 は OS トランジスタであり、メモリセル MC のトランジスタ T<sub>a</sub> に相当するトランジスタの例である。トランジスタ TR1 は、トランジスタ T<sub>b</sub> にも適用が可能である。

#### 【0111】

トランジスタ TR1 は、半導体膜 101、導電膜 104a、導電膜 104b、ゲート絶縁膜 102、ゲート電極 103、導電膜 105、および絶縁膜 114 を有する。

#### 【0112】

半導体膜 101 は、絶縁膜 114 の上面に接する半導体膜 101a、半導体膜 101a の上面に接する半導体膜 101b、および半導体膜 101b の上面に接する半導体膜 101c を有する。図 12 (A) の例では、半導体膜 101 は、半導体膜 101a、半導体膜 101b および半導体膜 101c の積層構造である。ただし、半導体膜 101 は、上記積層構造に限定されず、単層で形成してもよい。ゲート電極 103、ゲート絶縁膜 102 および半導体膜 101c の端部が概略一致する。これは、ゲート絶縁膜 102 および半導体膜 101c を形成するためのエッチング工程で、ゲート電極 103 がマスクとして機能するからである。

#### 【0113】

導電膜 104a 及び導電膜 104b は、それぞれ、ソース電極またはドレイン電極として機能する。導電膜 104a 及び導電膜 104b は、半導体膜 101b の上面と接し、且つ、その上面で離間されている。半導体膜 101c は、半導体膜 101b、導電膜 104a 及び導電膜 104b のそれぞれの上面と接する。ゲート電極 103 はゲート絶縁膜 102 を介して半導体膜 101 と対向し、導電膜 105 は絶縁膜 114 を介して半導体膜 101 と対向する。導電膜 105 はトランジスタ TR1 のバックゲート電極として機能する。

#### 【0114】

別言すると、半導体膜 101a は、絶縁膜 114 と半導体膜 101b の間に設けられている。また、半導体膜 101c は、半導体膜 101b とゲート絶縁膜 102 の間に設けられている。また、導電膜 104a および導電膜 104b は、半導体膜 101b の上面に接し、半導体膜 101c の下面と接する。半導体膜 101b の側面は、導電膜 104a および導電膜 104b と接する。

#### 【0115】

なお、導電膜 105 を設けない構成としてもよい。または、図示しないが、導電膜 105 は、ゲート電極 103 と電気的に接続する構成としてもよい。例えば、導電膜 105 をゲート電極 103 と電気的に接続し、同じ電位を印加する構成とした場合、オン電流の増加、初期特性バラつきの低減、-GBT (-Gate Bias-Temperature) ストレス試験の劣化の抑制、及び異なるドレイン電圧におけるオン電流の立ち上がり電圧の変動の抑制が可能である。トランジスタ TR1 のオン電流を増加させることにより、例えばメモリセルアレイ 300 の読み出し速度を高めることができる。

#### 【0116】

また、ゲート電極 103 の電界によって、半導体膜 101b を電気的に取り囲むことができる（導電膜の電界によって、半導体膜を電気的に取り囲むトランジスタの構造を、surrounded channel (s-channel) 構造とよぶ。）。トランジスタ TR1 は s-channel 構造のデバイスである。そのため、半導体膜 101b の全体（バルク）にチャネルが形成される場合がある。s-channel 構造では、トランジスタのソース電極 - ドレイン電極間に大電流を流すことができ、導通時の電流（オン電流）を高くすることができます。

10

20

30

40

50

## 【0117】

上述の s - c h a n n e l 構造は、高いオン電流が得られるため、微細化された O S トランジスタに適した構造といえる。また、O S トランジスタを微細化できるため、該 O S トランジスタを有する半導体装置は、集積度の高い、高密度化された半導体装置とすることが可能となる。例えば、O S トランジスタは、チャネル長が 1 nm 以上 1 0 0 nm 未満、さらに好ましくはチャネル長が 5 nm 以上 6 0 nm 以下の領域を有すると好ましい。

## 【0118】

なお、チャネル長とは、例えば、トランジスタの上面図において、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソース（ソース領域またはソース電極）とドレイン（ドレン領域またはドレン電極）との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書等では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。10

## 【0119】

また、チャネル幅とは、例えば、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソース（ソース領域またはソース電極）とドレイン（ドレン領域またはドレン電極）とが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。20

## 【0120】

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅（以下、実効的なチャネル幅と呼ぶ。）と、トランジスタの上面図において示されるチャネル幅（以下、見かけ上のチャネル幅と呼ぶ。）と、が異なる場合がある。例えば、立体的な構造を有するトランジスタでは、実効的なチャネル幅が、トランジスタの上面図において示される見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつ立体的な構造を有するトランジスタでは、半導体の上面に形成されるチャネル領域の割合に対して、半導体の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、上面図において示される見かけ上のチャネル幅よりも、実際にチャネルの形成される実効的なチャネル幅の方が大きくなる。30

## 【0121】

また、立体的な構造を有するトランジスタにおいては、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるために、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

## 【0122】

そこで、本明細書等では、トランジスタの上面図において、半導体とゲート電極とが重なる領域における、ソース（ソース領域またはソース電極）とドレイン（ドレン領域またはドレン電極）とが向かい合っている部分の長さである見かけ上のチャネル幅を、「囲い込みチャネル幅（S C W : S u r r o u n d e d C h a n n e l W i d t h ）」と呼ぶ場合がある。また、本明細書等では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書等では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面 T E M 像などを取得して、その画像を解析することなどによって、値を決定することができる。4050

## 【0123】

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。

## 【0124】

以下、図12に示すトランジスタTR1が有する各構成要素の詳細について説明する。

## 【0125】

<下地膜として機能する絶縁膜>

絶縁膜114は、酸化物を含むことが好ましい。特に加熱により酸素を脱離する酸化物材料を含むことが好ましい。また、半導体膜101は、絶縁膜114上に設けられること10が好ましい。

## 【0126】

加熱により酸素を脱離する酸化物材料として、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物を用いることが好ましい。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物膜は、昇温脱離ガス分光法(TDS: Thermal Desorption Spectroscopy)分析にて、酸素原子に換算しての酸素の脱離量が $1.0 \times 10^{18}$  atoms/cm<sup>3</sup>以上、好ましくは $3.0 \times 10^{20}$  atoms/cm<sup>3</sup>以上である酸化物膜である。なお、上記TDS分析時における膜の表面温度としては100以上700以下、または100以上500以下の範囲が好ましい。

## 【0127】

加熱により酸素を脱離する酸化物材料として、例えば、酸化シリコンまたは酸化窒化シリコンを含む材料を用いることが好ましい。または、金属酸化物を用いることもできる。金属酸化物として、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等を用いる事ができる。なお、本明細書中において、酸化窒化シリコンとは、その組成として窒素よりも酸素の含有量が多い材料を指し、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多い材料を示す。

## 【0128】

半導体膜101として酸化物半導体を用いた場合、絶縁膜114から脱離した酸素が酸化物半導体に供給され、酸化物半導体中の酸素欠損を低減することが可能となる。その結果、トランジスタTR1の電気特性の変動を抑制し、信頼性を高めることができる。

## 【0129】

また、絶縁膜114の上面は平坦化処理、例えば、CMP(Chemical Mechanical Polishing)法等を用いた平坦化処理により平坦化されていることが好ましい。

## 【0130】

<半導体膜>

半導体膜101は、シリコンよりもバンドギャップの大きな半導体を含むことが好ましい。好適には、半導体膜101は酸化物半導体を含んで構成される。シリコンよりもバンドギャップが広く、且つキャリア密度の小さい半導体材料を用いると、トランジスタのオフ状態における電流を低減できるため好ましい。半導体膜101としてこのような材料を用いることで、電気特性の変動が抑制され、信頼性の高いトランジスタを実現できる。

## 【0131】

より具体的には、半導体膜101としては、酸化物半導体膜を用いると好ましい。例えば、半導体膜101bとして、In:Ga:Zn = 1:1:1, 2:1:3, 3:1:2、または4:2:3の原子数比のIn-Ga-Zn酸化物を用いた場合、半導体膜101aまたは半導体膜101cとして、In:Ga:Zn = 1:3:2, 1:3:4, 1:3:6, 1:6:4, 1:6:8, 1:6:10, 1:9:6、または1:2:3などの原子数比のIn-Ga-Zn酸化物を用いることができる。なお、半導体膜101b、半導体膜101aおよび半導体膜101cの原子数比はそれぞれ、誤差として上記の原子数比4050

のプラスマイナス 20 % の変動を含む。また、半導体膜 101a と半導体膜 101c は、組成の同じ材料を用いてもよいし、異なる組成の材料を用いてもよい。

### 【0132】

また、半導体膜 101b として In - M - Zn 酸化物を用いた場合、半導体膜 101b となる半導体膜を成膜するために用いるターゲットは、該ターゲットが含有する金属元素の原子数比を  $In : M : Zn = x_1 : y_1 : z_1$  としたときに、 $x_1 / y_1$  の値が 1 / 3 以上 6 以下、好ましくは 1 以上 6 以下であり、 $z_1 / y_1$  が 1 / 3 以上 6 以下、好ましくは 1 以上 6 以下の原子数比の酸化物を用いることが好ましい。なお、 $z_1 / y_1$  を 6 以下とすることで、後述する CAC - OS 膜が形成されやすくなる。ターゲットの金属元素の原子数比の代表例としては、 $In : M : Zn = 1 : 1 : 1$ 、 $2 : 1 : 3$ 、 $3 : 1 : 2$  などがある。10

### 【0133】

また、半導体膜 101a、半導体膜 101c として In - M - Zn 酸化物を用いた場合、半導体膜 101a、半導体膜 101c となる半導体膜を成膜するために用いるターゲットは、該ターゲットが含有する金属元素の原子数比を  $In : M : Zn = x_2 : y_2 : z_2$  としたときに、 $x_2 / y_2 < x_1 / y_1$  であり、 $z_2 / y_2$  の値が 1 / 3 以上 6 以下、好ましくは 1 以上 6 以下の原子数比の酸化物を用いることが好ましい。なお、 $z_2 / y_2$  を 6 以下とすることで、後述する CAC - OS 膜が形成されやすくなる。ターゲットの金属元素の原子数比の代表例としては、 $In : M : Zn = 1 : 3 : 4$ 、 $1 : 3 : 6$ 、 $1 : 3 : 8$  などがある。20

### 【0134】

半導体膜 101c を酸化ガリウム膜で形成することが好ましい。酸化ガリウム膜はインジウム拡散を防ぐ、プロッキング機能を有する。そのため、半導体膜 101c を酸化ガリウム膜で形成することで半導体膜 101a、半導体膜 101b からゲート絶縁膜 102 へのインジウム拡散を防ぐことができ、トランジスタ TR1 のオフ電流を低減することができる。

### 【0135】

酸化物半導体をスパッタリング法で成膜する場合、ターゲットの原子数比からずれた原子数比の膜が形成される場合がある。特に、亜鉛は、ターゲットの原子数比よりも膜の原子数比が小さくなる場合がある。具体的には、ターゲットに含まれる亜鉛の原子数比の 40 atom % 以上 90 atom % 程度以下となる場合がある。30

### 【0136】

<ソース電極及びドレイン電極として機能する導電膜>

導電膜 104a、導電膜 104b は、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニア、モリブデン、銀、タンタル、またはタンゲステンなどの金属、またはこれを主成分とする合金を単層構造または積層構造として用いる。例えば、シリコンを含むアルミニウム膜の単層構造、チタン膜上にアルミニウム膜を積層する二層構造、タンゲステン膜上にアルミニウム膜を積層する二層構造、銅 - マグネシウム - アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、タンゲステン膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。40

### 【0137】

<ゲート絶縁膜>

ゲート絶縁膜 102 は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたは Ga - Zn 系金属酸化物、窒化シリコンなどを用いればよく、積層または単層で設ける。50

## 【0138】

また、ゲート絶縁膜102として、ハフニウムシリケート( $HfSiO_x$ )、窒素が添加されたハフニウムシリケート( $HfSi_xO_yN_z$ )、窒素が添加されたハフニウムアルミニート( $HfAl_xO_yN_z$ )、酸化イットリウムなどのhigh-k材料を用いてもよい。

## 【0139】

また、ゲート絶縁膜102として、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどの酸化物絶縁膜、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物絶縁膜、または上記材料を混合した膜を用いて形成することができる。10

## 【0140】

また、ゲート絶縁膜102として、絶縁膜114と同様に、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いることが好ましい。

## 【0141】

なお、特定の材料をゲート絶縁膜に用いると、特定の条件でゲート絶縁膜に電子を捕獲せしめて、しきい値電圧を増大させることもできる。例えば、酸化シリコンと酸化ハフニウムの積層膜のように、ゲート絶縁膜の一部に酸化ハフニウム、酸化アルミニウム、酸化タンタルのような電子捕獲準位の多い材料を用い、より高い温度(半導体装置の使用温度あるいは保管温度よりも高い温度、あるいは、125以上450以下、代表的には150以上300以下)の下で、ゲート電極の電位をソース電極やドレイン電極の電位より高い状態を、1秒以上、代表的には1分以上維持することで、半導体層からゲート電極に向かって、電子が移動し、そのうちのいくらかは電子捕獲準位に捕獲される。20

## 【0142】

このように電子捕獲準位に必要な量の電子を捕獲させたトランジスタは、しきい値電圧がプラス側にシフトする。ゲート電極の電圧の制御によって電子の捕獲する量を制御することができ、それに伴ってしきい値電圧を制御することができる。また、電子を捕獲せしめる処理は、トランジスタの作製過程に行なえばよい。

## 【0143】

例えば、トランジスタのソース電極あるいはドレイン電極に接続する配線メタルの形成後、あるいは、前工程(ウェハー処理)の終了後、あるいは、ウェーハーダイシング工程後、パッケージ後等、工場出荷前のいずれかの段階で行うとよい。いずれの場合にも、その後に125以上の温度に1時間以上さらされないことが好ましい。30

## 【0144】

## &lt;ゲート電極&gt;

ゲート電極103は、例えばアルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた金属、または上述した金属を成分とする合金か、上述した金属を組み合わせた合金等を用いて形成される。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属を用いてよい。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体、ニッケルシリサイド等のシリサイドを用いてよい。また、ゲート電極103は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化タンタル膜または窒化タングステン膜上にタングステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた一または複数の金属を組み合わせた合金膜、もしくは窒化膜を用いてよい。40

## 【0145】

また、ゲート電極103は、インジウム錫酸化物、酸化タングステンを含むインジウム

50

酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属の積層構造とすることもできる。

## 【0146】

また、ゲート電極103とゲート絶縁膜の間に、In-Ga-Zn酸化窒化物半導体膜、In-Sn酸化窒化物半導体膜、In-Ga酸化窒化物半導体膜、In-Zn酸化窒化物半導体膜、Sn酸化窒化物半導体膜、In酸化窒化物半導体膜、金属窒化膜(InN、ZnN等)等を設けてよい。これらの膜は5eV以上、好ましくは5.5eV以上の仕事関数を有し、酸化物半導体の電子親和力よりも大きい値であるため、酸化物半導体を用いたトランジスタのしきい値電圧をプラスにシフトすることができ、所謂ノーマリーオフ特性のスイッチング素子を実現できる。例えば、In-Ga-Zn酸化窒化物半導体膜を用いる場合、少なくとも半導体膜101より高い窒素濃度、具体的には7原子%以上のIn-Ga-Zn酸化窒化物半導体膜を用いる。

## 【0147】

<バックゲート電極として機能する導電膜>

導電膜105は、ゲート電極103と同様の材料を用いればよい。

## 【0148】

<トランジスタの構成例2-6>

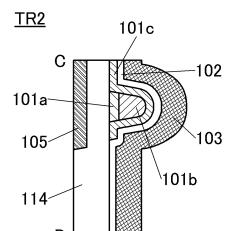

次に、図12に示すトランジスタTR1とは異なる構成例を説明する。図13および図14にトランジスタTR1の変形例を示す。

## 【0149】

図12に示すトランジスタTR1は、ゲート絶縁膜102と半導体膜101cの端部が概略一致するように加工されている。図13に示すTR2は、半導体膜101cの端部がゲート絶縁膜102よりも内側に位置するように加工されている。図13(B)はトランジスタTR2の上面図である。図13(A)は図13(B)のA-B線断面図であり、図13(C)は、同C-D断面図である。

## 【0150】

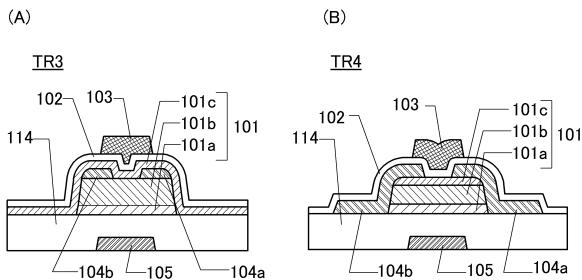

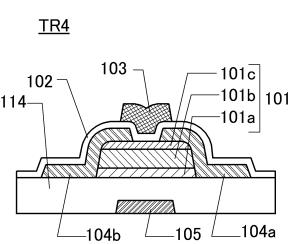

図14に示すトランジスタは、メモリセルMCのトランジスタTa、およびトランジスタTbに適用が可能である。図14はトランジスタのチャネル長方向の断面図である。

## 【0151】

図14(A)に示すトランジスタTR3はトランジスタTR2の変形例であり、導電膜104aと導電膜104bの構造が異なる。例えば、トランジスタTR3は次のような工程を経て作製することができる。半導体膜101aおよび半導体膜101bを形成するため、2層の半導体膜を形成し、半導体膜の積層膜上に、導電膜104a及び導電膜104bとなる導電膜を形成する。導電膜上にレジストマスクを形成し、上記導電膜をエッチングして導電膜でなるマスクを形成する。このマスクを用いて、半導体膜の積層膜をエッチングして、半導体膜101aと半導体膜101bを形成する。次にマスクを加工し導電膜104aおよび導電膜104bを形成する。

## 【0152】

図14(B)に示すトランジスタTR4はトランジスタTR2の変形例である。トランジスタTR4では、導電膜104a及び導電膜104bの下面に接して半導体膜101cが設けられている。このような構成とすることで、半導体膜101a、半導体膜101b及び半導体膜101cを構成するそれぞれの膜の成膜時において、大気に触れさせることなく連続的に成膜することができるため、各々の界面欠陥を低減することができる。

## 【0153】

図14(C)に示すトランジスタTR5はトランジスタTR4の変形例である。トランジスタTR5では、絶縁膜116に開口部を設けてプラグ118aおよびプラグ118bを形成し、該プラグをトランジスタのソース電極及びドレイン電極としている。

## 【0154】

10

20

30

40

50

図14(D)に示すトランジスタTR6はトランジスタTR5の変形例である。トランジスタTR6では、半導体膜101に低抵抗領域171aおよび低抵抗領域171bが設けられている。例えば、該低抵抗領域の形成は以下のように行う。絶縁膜114上に半導体膜101を形成する。次に、ゲート絶縁膜102およびゲート電極103を形成する。次に、ゲート電極103をマスクとして、低抵抗領域171aおよび低抵抗領域171bを形成する。低抵抗領域171a、171bは、キャリア密度の高い領域である。

#### 【0155】

キャリア密度を高める方法として、たとえば不純物の添加や、酸素欠損の形成等が挙げられる。例えばキャリア密度を高める方法として、イオン注入を用いて元素を添加すればよい。用いることのできる元素としては、例えばアルゴン、ホウ素、炭素、マグネシウム、アルミニウム、シリコン、リン、カルシウム、スカンジウム、チタン、バナジウム、クロム、マンガン、鉄、コバルト、ニッケル、ガリウム、ゲルマニウム、ヒ素、イットリウム、ジルコニウム、ニオブ、モリブデン、インジウム、スズ、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステンから選択された一種以上を添加することが好みしい。低抵抗領域171aおよび低抵抗領域171bは、上述の不純物元素を $5 \times 10^{19}$ atoms/cm<sup>3</sup>以上、好ましくは $1 \times 10^{20}$ atoms/cm<sup>3</sup>以上、さらに好ましくは $2 \times 10^{20}$ atoms/cm<sup>3</sup>以上、より好ましくは $5 \times 10^{20}$ atoms/cm<sup>3</sup>以上含む領域である。

#### 【0156】

低抵抗領域171a及び低抵抗領域171bは、不要な水素をトラップすることができる可能性がある。不要な水素を低抵抗領域171a及び低抵抗領域171bにトラップすることによりチャネル領域の水素濃度を低くすることができる。

#### 【0157】

以上が、トランジスタTaおよびトランジスタTbに適用することが可能なトランジスタの構成例の説明である。

#### 【0158】

##### <メモリセルの作製方法例>

以下では、図15乃至図18を参照して、図9に示すメモリセルアレイ300の作製方法の一例について説明する。ここでは、トランジスタTa、トランジスタTbに図13に示すトランジスタTR2が適用されている。

#### 【0159】

基板100を準備する。基板100としては、例えば単結晶シリコン基板(p型の半導体基板、またはn型の半導体基板を含む)、炭化シリコンや窒化ガリウムを材料とした化合物半導体基板、またはガラス基板などを用いることができる。また、基板100として、SOI基板を用いてもよい。以下では、基板100として単結晶シリコンを用いた場合について説明する。

#### 【0160】

次に、基板100上に導電膜105等となる導電膜を形成する。導電膜105等となる導電膜の形成方法としては、例えばスパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いることができる。次に、レジストマスクを形成し、導電膜105等となる導電膜の不要な部分をエッチングにより除去する。その後レジストマスクを除去し、導電膜105等を形成する。

#### 【0161】

次に、基板100、導電膜105上に絶縁膜114を成膜する。絶縁膜114は、例えばスパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いて形成することができる。特に、当該絶縁膜をCVD法、好ましくはPECVD法によって成膜すると、被覆性を向上させることができるため好ましい。またプラズマによるダメージを減らすには、熱CVD法、MOCVD法あるいはALD法が好ましい。

#### 【0162】

10

20

30

40

50

また、絶縁膜114に酸素を過剰に含有させるためには、例えば酸素雰囲気下にて絶縁膜114の成膜を行えばよい。または、成膜後の絶縁膜114に酸素を導入して酸素を過剰に含有する領域を形成してもよく、双方の手段を組み合わせてもよい。

#### 【0163】

例えば、成膜後の絶縁膜114に酸素（少なくとも酸素ラジカル、酸素原子、酸素イオンのいずれかを含む）を導入して酸素を過剰に含有する領域を形成する。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理などを用いることができる。

#### 【0164】

酸素導入処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、酸素、一酸化二窒素、二酸化窒素、二酸化炭素、一酸化炭素などを用いることができる。また、酸素導入処理において、酸素を含むガスに希ガスを含ませてもよい。または、水素等を含ませてもよい。例えば、二酸化炭素、水素およびアルゴンの混合ガスを用いるとよい。

#### 【0165】

また、絶縁膜114を成膜した後、その上面の平坦性を高めるためにCMP法等を用いた平坦化処理を行ってもよい。

#### 【0166】

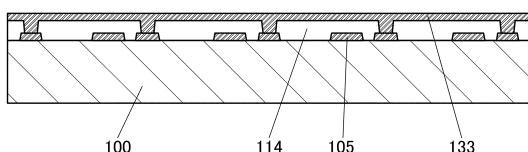

次に、絶縁膜114の上にトランジスタTbのソース電極またはドレイン電極等に接続するためのプラグを形成する。まず、絶縁膜114に開口部を設ける。次に、該開口部を埋めるように、プラグとなる導電膜133を成膜する（図15（A））。

#### 【0167】

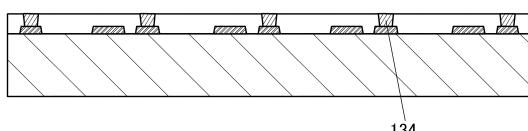

次に、絶縁膜114の表面が露出するように、導電膜133に平坦化処理を行い、プラグ134を形成する（図15（B））。

#### 【0168】

次に、絶縁膜114上に半導体膜101a等となる半導体膜と、半導体膜101b等となる半導体膜を順に成膜する。当該半導体膜は、大気に触れさせることなく連続して成膜することが好ましい。半導体膜101aとなる半導体膜、および半導体膜101bとなる半導体膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて成膜すればよい。

#### 【0169】

なお、半導体膜101a等となる半導体膜、および半導体膜101b等となる半導体膜として、In-Ga-Zn酸化物膜をMOCVD法によって成膜する場合、原料ガスとしてトリメチルインジウム、トリメチルガリウムおよびジメチル亜鉛などを用いればよい。なお、上記原料ガスの組み合わせに限定されず、トリメチルインジウムに代えてトリエチルインジウムなどを用いてもよい。また、トリメチルガリウムに代えてトリエチルガリウムなどを用いてもよい。また、ジメチル亜鉛に代えてジエチル亜鉛などを用いてもよい。

#### 【0170】

半導体膜101a及び半導体膜101bとなる半導体膜を成膜後、加熱処理を行うことが好ましい。該加熱処理は、250以上650以下、好ましくは300以上500

以下の温度で、不活性ガス雰囲気、酸化性ガスを10ppm以上含む雰囲気、または減圧状態で行えばよい。また、加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上含む雰囲気で行ってもよい。加熱処理は、半導体膜を成膜した直後に行ってもよいし、半導体膜を加工して島状の半導体膜101a、半導体膜101b等を形成した後に行ってもよい。加熱処理により、絶縁膜114から半導体膜に酸素が供給され、半導体膜中の酸素欠損を低減することができる。

#### 【0171】

その後、レジストマスクを形成し、不要な部分をエッチングにより除去する。その後レジストマスクを除去することにより、島状の半導体膜101a、半導体膜101b等の積層構造を形成する（図15（C））。

10

20

30

40

50

## 【0172】

なお、半導体膜のエッティングの際に、絶縁膜114の一部がエッティングされ、半導体膜101a、半導体膜101b等に覆われていない領域における絶縁膜114が薄膜化する場合がある。したがって、当該エッティングにより絶縁膜114が消失しないよう、予め厚く形成しておくことが好ましい。

## 【0173】

その後、導電膜204a、204bとなる導電膜を成膜する。該導電膜の成膜は、スパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いて形成することができる。次に、レジストマスクを形成し、導電膜204a、204bとなる導電膜の不要な部分をエッティングにより除去する。その後レジストマスクを除去し、導電膜204a、導電膜204b等を形成する(図15(D))。

10

## 【0174】

ここで、上記導電膜のエッティングの際に、半導体膜101bや絶縁膜114の上部の一部などがエッティングされ、導電膜204aや導電膜204bと重ならない部分が薄膜化することがある。したがって、半導体膜101bとなる半導体膜等の厚さを、エッティングされる深さを考慮して予め厚く形成しておくことが好ましい。

## 【0175】

次に、ゲート絶縁膜202、半導体膜101cを形成する。なお、ゲート絶縁膜202及び半導体膜101c形成後に、レジストマスクを形成し、エッティングによりゲート絶縁膜202及び半導体膜101cを加工してもよい。次にゲート電極203となる導電膜を形成する。その後、レジストマスクを形成し、エッティングにより該導電膜を加工し、ゲート電極203を形成する。その後レジストマスクを除去する。この段階でトランジスタTbが形成される(図16(A))。

20

## 【0176】

半導体膜101cとなる半導体膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて成膜すればよい。

## 【0177】

なお、半導体膜101cとなる半導体膜として、In-Ga-Zn酸化物膜をMOCVD法によって成膜する場合、原料ガスとしてトリメチルインジウム、トリメチルガリウムおよびジメチル亜鉛などを用いればよい。なお、上記原料ガスの組み合わせに限定されず、トリメチルインジウムに代えてトリエチルインジウムなどを用いてもよい。また、トリメチルガリウムに代えてトリエチルガリウムなどを用いてもよい。また、ジメチル亜鉛に代えてジエチル亜鉛などを用いてもよい。

30

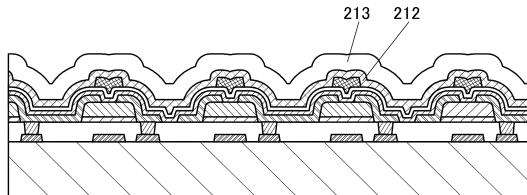

## 【0178】

なお、図8乃至図11には図示していないが、トランジスタTb上に絶縁膜212及び絶縁膜213を形成してもよい(図16(B))。

## 【0179】

絶縁膜212は、例えばスパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いて形成することができる。また、絶縁膜212の成膜後、加熱処理を行うことが好ましい。該加熱処理により、絶縁膜114等から半導体膜101bに対して酸素を供給し、半導体膜101b中の酸素欠損を低減することができる。また、絶縁膜212を2層以上の積層構造としてもよい。その場合には、例えば絶縁膜212を2層の積層構造とし、下層に例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよい。

40

## 【0180】

絶縁膜213は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよく、積層または単層で設ける。

50

**【0181】**

次に、絶縁膜213上に絶縁膜216を形成する。絶縁膜216は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよく、積層または単層で設ける。絶縁膜216は、例えばスパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いて形成することができる。また絶縁膜216として有機樹脂などの有機絶縁材料を用いる場合には、スピンドルコート法などの塗布法を用いて形成してもよい。また、絶縁膜216を形成した後にその上面に対して平坦化処理を行うことが好ましい。

**【0182】**

10

次に、絶縁膜216、絶縁膜213、絶縁膜212、ゲート絶縁膜202及び半導体膜101等に開口部を設け、開口部を埋め込むようにプラグ141、プラグ142、プラグ143等となる導電膜を形成し、絶縁膜216の表面が露出するように平坦化処理を行い、プラグ141、プラグ142、プラグ143等を形成する(図16(C))。

**【0183】**

次に、絶縁膜216及びプラグ141等の上に、導電膜を形成し、マスク形成してエッチングを行い、導電膜151、152、153等を形成する。その後、絶縁膜115を形成する(図17(A))。絶縁膜115は、容量素子Caの絶縁膜として機能することができる。絶縁膜115に用いることのできる材料等は、例えばゲート絶縁膜102の記載を参照すればよい。

20

**【0184】**

次に、絶縁膜115上に、導電膜155等を形成する。導電膜155等に用いることのできる材料等は、例えば導電膜105の記載を参照すればよい。このようにして、容量素子Caを形成することができる(図17(B))。

**【0185】**

次に、導電膜155及び絶縁膜115上に、絶縁膜156を形成する。絶縁膜156の上面は平坦化されていてもよい。絶縁膜156については、絶縁膜216の記載を参照する。次に、絶縁膜156上に、導電膜105等を形成する。次に、絶縁膜114を形成する。次に、絶縁膜156及び絶縁膜114に開口部を設け、開口部を埋め込むように導電膜を形成し、絶縁膜114が露出するように導電膜の表面を平坦化し、プラグ144、プラグ145等を形成する(図17(C))。

30

**【0186】**

次に、トランジスタTa等を形成する(図18参照)。

**【0187】**

トランジスタTaの形成については、トランジスタTbの記載を参照すればよい。また、図18に示すように、メモリセルMC\_1の有するトランジスタTaと、メモリセルMC\_2の有するトランジスタTbを同じ工程で形成することができる。

**【0188】**

以上の工程を繰り返すことで、図9に示すメモリセルアレイ300を作製することができる。

40

**【0189】**

以上、本実施の形態で示す構成、方法は、他の実施の形態で示す構成、方法と適宜組み合わせて用いることができる。

**【0190】**

(実施の形態2)

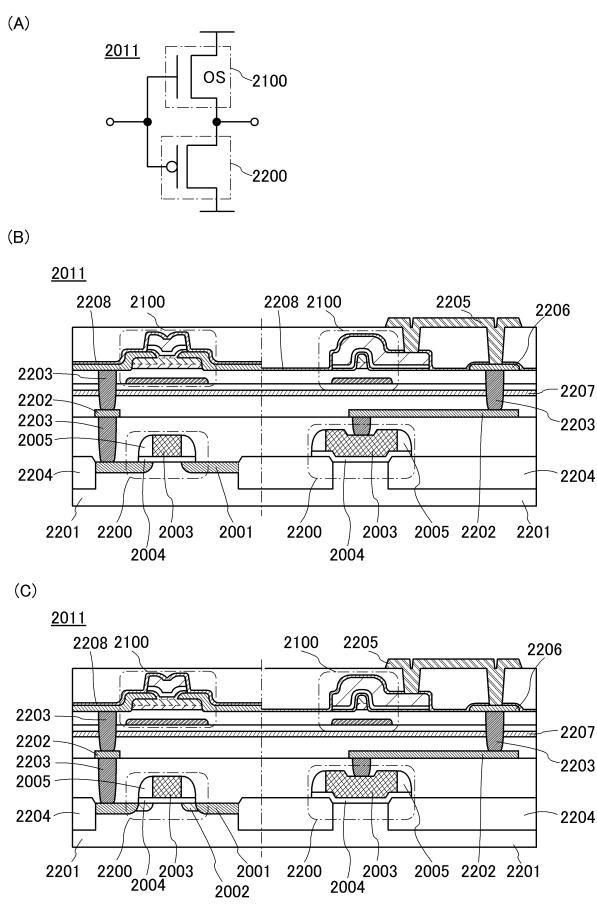

図19乃至図21を参照して、本実施の形態では、本発明の一態様の回路システムに用いることのできる回路の構成例について詳細に説明する。

**【0191】**

<CMOS回路>

図19(A)に示す回路2011は、pチャネル型のトランジスタ2200とnチャネ

50

ル型のトランジスタ 2100 を直列に接続し、且つそれぞれのゲートを接続した、いわゆる CMOS で構成したインバータ回路である。図 19 (B) に回路 2011 のデバイス構造の一例を示す。

#### 【0192】

図 19 (B) は回路 2011 の構成例を示す断面図である。回路 2011 は、基板 2201 と、トランジスタ 2200 と、トランジスタ 2100 と、配線 2202 と、プラグ 2203 と、配線 2206 と、配線 2205 と、素子分離層 2204 と、絶縁膜 2207 と、絶縁膜 2208 と、を有している。また、トランジスタ 2200 は、ソース領域又はドレイン領域として機能する不純物領域 2001 と、ゲート電極 2003 と、ゲート絶縁膜 2004 と、側壁絶縁層 2005 と、を有している。

10

#### 【0193】

図 19 (B) に示す回路 2011 は、下部に第 1 の半導体材料を用いたトランジスタ 2200 を有し、上部に第 2 の半導体材料を用いたトランジスタ 2100 を有している。図 19 (B) では、第 2 の半導体材料を用いたトランジスタ 2100 として、実施の形態 1 で例示した OS トランジスタが適用されている。なお、一点鎖線より左側がトランジスタ 2100 及びトランジスタ 2200 のチャネル長方向の断面、右側がトランジスタ 2100 及びトランジスタ 2200 のチャネル幅方向の断面である。図示のように、2 種類のトランジスタを積層することにより、回路の占有面積が低減され、より高密度に複数の回路を配置することができる。

#### 【0194】

第 1 の半導体材料と第 2 の半導体材料は異なる禁制帯幅を持つ材料とすることが好ましい。例えば、第 1 の半導体材料を酸化物半導体以外の半導体材料（シリコン（歪シリコン含む）、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、ガリウムヒ素、アルミニウムガリウムヒ素、インジウムリン、窒化ガリウム、有機半導体など）とし、第 2 の半導体材料を酸化物半導体とすることができる。酸化物半導体以外の材料として単結晶シリコンなどを用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、先の実施の形態で例示したトランジスタを適用することで、優れたサブスレッショルド特性が得られ、微細なトランジスタとすることが可能である。また、スイッチ速度が速いため高速動作が可能であり、オフ電流が低いためリーク電流が小さい。

20

#### 【0195】

トランジスタ 2200 は、n チャネル型のトランジスタまたは p チャネル型のトランジスタのいずれであってもよく、回路によって適切なトランジスタを用いればよい。図 19 (A) の回路 2011 では、トランジスタ 2200 は p チャネル型である。

30

#### 【0196】

また、図 19 (C) に示すように、トランジスタ 2200 に不純物領域 2002 を設けてよい。不純物領域 2002 は、LDD (Lightly Doped Drain) 領域やエクステンション領域として機能する。不純物領域 2001 の不純物濃度は、不純物領域 2002 よりも高い。ゲート電極 2003 及び側壁絶縁層 2005 をマスクとして用いて、不純物領域 2001 及び不純物領域 2002 を自己整合的に形成することができる。特に、トランジスタ 2200 を n チャネル型とする場合は、ホットキャリアによる劣化を抑制するため、不純物領域 2002 を設けることが好ましい。

40

#### 【0197】

また、トランジスタ 2200 としてシリサイド（サリサイド）を有するトランジスタや、側壁絶縁層 2005 を有さないトランジスタを用いてもよい。シリサイド（サリサイド）を有する構造であると、ソース領域およびドレイン領域がより低抵抗化でき、半導体装置の高速化が可能である。また、低電圧で動作できるため、半導体装置の消費電力を低減することが可能である。

#### 【0198】

図 19 (B) ではトランジスタ 2100 にバックゲート電極を設けた構成を示しているが、バックゲート電極を設けない構成であってもよい。

50

## 【0199】

基板2201としては、シリコンや炭化シリコンを材料とした単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムを材料とした化合物半導体基板や、SOI(Silicon on Insulator)基板などを用いることができる。半導体基板を用いて形成されたトランジスタは、高速動作が容易である。なお、基板2201としてp型の単結晶シリコン基板を用いた場合、基板2201の一部にn型を付与する不純物元素を添加してn型のウェルを形成し、n型のウェルが形成された領域にp型のトランジスタを形成することも可能である。n型を付与する不純物元素としては、リン(P)、砒素(As)等を用いることができる。p型を付与する不純物元素としては、ボロン(B)等を用いることができる。

10

## 【0200】

また、基板2201は導電基板、または絶縁基板上に半導体膜を設けたものでもよい。該導電基板としては、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タングステン基板、タングステン・ホイルを有する基板などが挙げられる。該絶縁基板として、例えば、ガラス基板、石英基板、プラスチック基板、可撓性基板、貼り合わせフィルム、纖維状の材料を含む紙、又は基材フィルムなどが挙げられる。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミニオホウケイ酸ガラス、又はソーダライムガラスなどがある。可撓性基板の一例としては、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)に代表されるプラスチック、又はアクリル等の可撓性を有する合成樹脂などがある。貼り合わせフィルムの一例としては、ポリプロピレン、ポリエステル、ポリフッ化ビニル、又はポリ塩化ビニルなどがある。基材フィルムの一例としては、ポリエステル、ポリアミド、ポリイミド、アラミド、エポキシ、無機蒸着フィルム、又は紙類などがある。

20

## 【0201】

なお、ある基板を用いて半導体素子を形成し、その後、別の基板に半導体素子を転置してもよい。半導体素子が転置される基板の一例としては、上述した基板に加え、紙基板、セロファン基板、アラミドフィルム基板、ポリイミドフィルム基板、石材基板、木材基板、布基板(天然纖維(絹、綿、麻)、合成纖維(ナイロン、ポリウレタン、ポリエステル)若しくは再生纖維(アセテート、キュプラ、レーヨン、再生ポリエステル)などを含む)、皮革基板、又はゴム基板などがある。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、又は薄型化を図ることができる。

30

## 【0202】

トランジスタ2200は、素子分離層2204により、基板2201に形成される他のトランジスタと分離されている。素子分離層2204は、酸化アルミニウム、酸化窒化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタルなどから選ばれた一種以上含む絶縁体を用いることができる。

40

## 【0203】

ここで、下層に設けられるトランジスタ2200にシリコン系半導体材料を用いた場合、トランジスタ2200の半導体膜の近傍に設けられる絶縁膜中の水素はシリコンのダンギリングボンドを終端し、トランジスタ2200の信頼性を向上させる効果がある。一方、上層に設けられるトランジスタ2100に酸化物半導体を用いた場合、トランジスタ2100の半導体膜の近傍に設けられる絶縁膜中の水素は、酸化物半導体中にキャリアを生成する要因の一つとなるため、トランジスタ2100の信頼性を低下させる要因となる場合がある。したがって、シリコン系半導体材料を用いたトランジスタ2200の上層に酸化物半導体を用いたトランジスタ2100を積層して設ける場合、これらの間に水素の拡散を防止する機能を有する絶縁膜2207を設けることは特に効果的である。絶縁膜2207により、下層に水素を閉じ込めてトランジスタ2200の信頼性が向上するこ

50

とに加え、下層から上層に水素が拡散することが抑制されることでトランジスタ 2100 の信頼性も同時に向上させることができる。

#### 【0204】

絶縁膜 2207 としては、例えば酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム、イットリア安定化ジルコニア (YSZ) 等を用いることができる。

#### 【0205】

また、酸化物半導体膜を含んで構成されるトランジスタ 2100 を覆うように、トランジスタ 2100 上に水素の拡散を防止する機能を有する絶縁膜 2208 を形成することができる。

10 絶縁膜 2208 としては、絶縁膜 2207 と同様の材料を用いることができ、特に酸化アルミニウムを適用することが好ましい。酸化アルミニウム膜は、水素、水分などの不純物および酸素の双方に対して膜を透過させない遮断 (ブロッキング) 効果が高い。したがって、トランジスタ 2100 を覆う絶縁膜 2208 として酸化アルミニウム膜を用いることで、トランジスタ 2100 に含まれる酸化物半導体膜からの酸素の脱離を防止するとともに、酸化物半導体膜への水および水素の混入を防止することができる。

#### 【0206】

プラグ 2203 は、銅 (Cu)、タンゲステン (W)、モリブデン (Mo)、金 (Au)、アルミニウム (Al)、マンガン (Mn)、チタン (Ti)、タンタル (Ta)、ニッケル (Ni)、クロム (Cr)、鉛 (Pb)、錫 (Sn)、鉄 (Fe)、コバルト (Co) の低抵抗材料からなる単体、もしくは合金、またはこれらを主成分とする化合物を含む導電膜の単層または積層とすることが好ましい。特に、耐熱性と導電性を両立するタンゲステンやモリブデンなどの高融点材料を用いることが好ましい。また、アルミニウムや銅などの低抵抗導電性材料で形成することが好ましい。さらに、Cu - Mn 合金を用いると、酸素を含む絶縁体との界面に酸化マンガンを形成し、酸化マンガンが Cu の拡散を抑制する機能を持つので好ましい。

20

#### 【0207】

配線 2202 及び配線 2205、銅 (Cu)、タンゲステン (W)、モリブデン (Mo)、金 (Au)、アルミニウム (Al)、マンガン (Mn)、チタン (Ti)、タンタル (Ta)、ニッケル (Ni)、クロム (Cr)、鉛 (Pb)、錫 (Sn)、鉄 (Fe)、コバルト (Co) の低抵抗材料からなる単体、もしくは合金、またはこれらを主成分とする化合物を含む導電膜の単層または積層とすることが好ましい。特に、耐熱性と導電性を両立するタンゲステンやモリブデンなどの高融点材料を用いることが好ましい。また、アルミニウムや銅などの低抵抗導電性材料で形成することが好ましい。さらに、Cu - Mn 合金を用いると、酸素を含む絶縁体との界面に酸化マンガンを形成し、酸化マンガンが Cu の拡散を抑制する機能を持つので好ましい。

30

#### 【0208】

配線 2206 は、トランジスタ 2100 のソース電極またはドレイン電極と同じ材料で形成することができる。

#### 【0209】

なお、図 19 (B)、(C)において、符号及びハッチングパターンが与えられていない領域は絶縁体で構成された領域を表している。これらの領域には、酸化アルミニウム、窒化酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタルなどから選ばれた一種以上含む絶縁体を用いることができる。また、当該領域には、ポリイミド樹脂、ポリアミド樹脂、アクリル樹脂、シロキサン樹脂、エポキシ樹脂、フェノール樹脂等の有機樹脂を用いることもできる。これは、後述する図 20 (B)、(C)、および図 21 (B) も同様である。

40

#### 【0210】

トランジスタ 2100 やトランジスタ 2200 の電極を適宜接続することにより、様々

10

20

30

40

50

な回路を構成することができる。図20、図21に他の例を示す。

### 【0211】

#### <アナログスイッチ>

図20(A)に示す回路2012は、トランジスタ2100とトランジスタ2200のそれぞれのソースとドレインを接続した回路構成を有し、いわゆるアナログスイッチとして機能させることができる。図20(B)は回路2012のデバイス構造の一例を示す断面図である。図19(B)に示すトランジスタ2200は、プレーナ型のトランジスタとしたが、トランジスタ2200には、様々なタイプのトランジスタとすることができます。例えば、FIN(フィン)型、TRI-GATE(トライゲート)型などの立体構造のトランジスタなどとすることができます。そのような例を、図20(B)に示す。

10

### 【0212】

図20(B)に示すように、半導体基板2211の上に、絶縁膜2212が設けられている。半導体基板2211は、先端の細い凸部(フィンともいう)を有する。なお、凸部の上には、絶縁膜が設けられていてもよい。その絶縁膜は、凸部を形成するときに、半導体基板2211がエッティングされないようにするためのマスクとして機能するものである。なお、凸部は、先端が細くなくてもよく、例えば、略直方体の凸部であってもよいし、先端が太い凸部であってもよい。半導体基板2211の凸部の上には、ゲート絶縁膜2214が設けられ、その上には、ゲート電極2213が設けられている。半導体基板2211には、ソース領域又はドレイン領域として機能する不純物領域2215が形成されている。また、図20(C)に示すように、不純物領域2216を設けてもよい。不純物領域2216はLDD領域やエクステンション領域として機能する。

20

### 【0213】

#### <記憶回路>

本発明の一態様であるトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数に制限が無い半導体装置(記憶装置)の一例を説明する。

### 【0214】

図21(A)に示す回路2013は、第2の半導体材料を用いたトランジスタ2100と第1の半導体材料を用いたトランジスタ2200、および容量素子2300を有している。回路2013は、図2(A)の記憶回路25と同様の回路構成を有し、同様の機能を有する。そのため、回路2013の構成の説明は、記憶回路25の説明を援用する。図21(A)の例では、トランジスタ2200をnチャネル型としている。

30

### 【0215】

トランジスタ2100は、酸化物半導体を有する半導体層にチャネルが形成されるトランジスタである。トランジスタ2100は、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作を必要としない、或いは、リフレッシュ動作の頻度が極めて少ない半導体装置とすることが可能となるため、消費電力を十分に低減することができる。

### 【0216】

また、トランジスタ2100は、実施の形態1で例示したトランジスタを適用することで、優れたサブスレッシュルド特性が得られ、微細なトランジスタとすることが可能である。また、スイッチ速度が速いため高速動作が可能である。一方、トランジスタ2200は、酸化物半導体以外の半導体材料として単結晶シリコンなどを用いたトランジスタであり、微細なトランジスタや高速動作が可能である。これらを組み合わせることで、小型の半導体装置を実現できる。また、高速な書き込み動作、読み出し動作が可能となる。

40

### 【0217】

図21(B)に回路2013のデバイス構造の一例を示す。回路2013では、トランジスタ2200は、nチャネル型でもpチャネル型でもよい。トランジスタ2200がpチャネル型である場合は不純物領域2002を設けてもよいし、設けなくてもよい。また、トランジスタ2100は、バックゲート電極を設けない構成であってもよい。

50

**【0218】**

図19乃至図21の例では、基板2201及び半導体基板2211にバルク状のものを用いたが、本発明の一態様はこれに限定されない。例えば、SOI基板を用いることもできる。

**【0219】**

以上、本実施の形態で示す構成、方法は、他の実施の形態で示す構成、方法と適宜組み合わせて用いることができる。

**【0220】****(実施の形態3)**

本実施の形態では、本発明の一態様の回路システムに適用可能な回路の一例について、

10

図22を用いて説明する。

**【0221】**

活性層に酸化物半導体を用いたトランジスタ、または活性層にシリコンを用いたトランジスタを用いた回路の例を図22(a)乃至図22(i)に示す。以下では、活性層に酸化物半導体を用いたトランジスタをOSトランジスタと呼び、シリコンを活性層に用いたトランジスタをSiトランジスタと呼ぶ。また、pチャネル型のSiトランジスタをp-Siトランジスタと呼び、nチャネル型のSiトランジスタをn-Siトランジスタと呼ぶ。なお、OSトランジスタの導電型は、特段の断りがない場合、nチャネル型である。また、便宜上、図22には、pチャネル型トランジスタをPMOSと、nチャネル型トランジスタNMOSと記載している。

20

**【0222】**

製造を容易にしつつ集積度を高め、かつ短チャネル効果の小さいOSトランジスタのメリットを活かすためには、OSトランジスタのチャネル長は1nm以上100nm未満であることが好ましく、5nm以上、60nm以下とすることがより好ましい。Siトランジスタにおいても、OSトランジスタと同一基板に形成するためには、Siトランジスタのチャネル長は1nm以上100nm未満であることが好ましい。または、チャネル長は、5nm以上60nm以下、または5nm以上30nm以下がより好ましい。

**【0223】**

図22(a)、図22(b)に示す回路は、トランジスタ700を有し、例えばスイッチ回路として機能する。トランジスタ700はOSトランジスタである。図22(b)に示すトランジスタ700は、第1のゲート(トップゲート、もしくはフロントゲート)と第2のゲート(バックゲート)を有するデュアルゲート型のOSトランジスタであり、第1のゲートと第2のゲートを別々に制御することで、オン特性の改善、及びオフ特性の改善が可能である。

30

**【0224】**

図22(c)に示す回路は、トランジスタ700と、トランジスタ701と、ノードFNを有しており、ノードFNで電位を保持することで、記憶回路25(図2(A))と同様に、記憶回路として機能することができる。図22(c)の例では、トランジスタ700はOSトランジスタである。トランジスタ701は、p-Siトランジスタでもよいし、n-Siトランジスタでもよいし、OSトランジスタでもよい。

40

**【0225】**

図22(d)に示す回路は、トランジスタ700と、トランジスタ701と、容量素子705と、ノードFNを有している。図22(d)に示す回路は、記憶回路25(図2(A))と回路構成が同様であり、記憶回路として機能することができる。ここでは、トランジスタ700はデュアルゲート型のOSトランジスタである。トランジスタ701は、p-Siトランジスタでもよいし、n-Siトランジスタでもよいし、OSトランジスタでもよい。p-Siトランジスタとする場合は、データ入力のシーケンスが図5のタイミングチャートと異なる。

**【0226】**

図22(c)や図22(d)の回路では、トランジスタ700、701がOSトランジ

50

スタである場合、基板はシリコン基板を用いる必要はなく、ガラスや石英ガラスなどの透明基板や金属基板等を用いることが可能となる。

#### 【0227】

微細化を行う上で、nチャネル型トランジスタはLDDや歪形成など、pチャネル型トランジスタに比べて複雑な工程を必要とする。OSトランジスタは、LDDや歪形成などの複雑な工程が必要ない。そのため、図22(c)や図22(d)の回路では、トランジスタ701をp-Siトランジスタとし、トランジスタ700をOSトランジスタとすることで、製造工程の簡略化が可能となる。

#### 【0228】

OSトランジスタは、900以上 10 の高温プロセスを必要としないため、Siトランジスタよりも集積化に適している。また、OSトランジスタは他の半導体素子と積層することが可能であり、OSトランジスタを回路に適用することで、3次元的に素子が集積された集積度の高い半導体装置を提供することが可能である。つまり、OSトランジスタは、Siトランジスタよりも低温プロセスで形成可能であるため、Siトランジスタ上にOSトランジスタを積層することで、信頼性が高く、高性能な半導体装置を提供することが可能である。

#### 【0229】

図22(e)の回路は、図22(d)の変形例であり、トランジスタ701の代わりに、直列に電気的に接続されたトランジスタ702とトランジスタ703を有する。例えば、トランジスタ702の第1端子は、高電源電位( $V_{DD}$ )が与えられる配線または電極に電気的に接続され、トランジスタ703の第2端子は、接地電位(GND)が与えられる配線または電極に電気的に接続する。トランジスタ700は、デュアルゲート型のOSトランジスタであり、トランジスタ702はp-Siトランジスタであり、トランジスタ703はn-Siトランジスタである。トランジスタ702及びトランジスタ703はCMOSインバータ回路を構成している。トランジスタ700の作製は低温プロセスで行うことができ、一般的なSiトランジスタの製造プロセスとの整合性も高いため、トランジスタ702及びトランジスタ703上にトランジスタ700を形成することは容易である。

#### 【0230】

図22(f)に、CMOSインバータ回路の例を示す。トランジスタ700はOSトランジスタであり、トランジスタ702はp-Siトランジスタである。トランジスタ700の作製は低温プロセスで行うことができ、一般的なSiトランジスタの製造プロセスとの整合性も高いため、トランジスタ702上にトランジスタ700を形成することは容易である。

#### 【0231】

図22(g)に示す回路は、トランジスタ700と、トランジスタ701と、トランジスタ704と、ダイオード706と、ノードFNを有する。トランジスタ701とトランジスタ704は直列に電気的に接続されている。トランジスタ701のゲートは、トランジスタ700を介して、ダイオード706の入力端子と電気的に接続されている。ダイオード706の入力端子、トランジスタ700のゲート、トランジスタ701の第1端子、およびトランジスタ704の第2端子は、図示されていない、互いに異なる配線または電極に電気的に接続されている。トランジスタ700と、トランジスタ701と、トランジスタ704と、ダイオード706と、ノードFNで構成される回路は、図22(c)等の回路と同様に、記憶回路として機能することができる。ダイオード706の入力端子および出力端子間の電位に応じたデータをノードFNで保持させることができる。ダイオード706をフォトダイオードとすることで、センサ素子として機能させることができる。この場合、図22(g)に示す回路は、光センサ回路として機能させることができる。ノードFNに、フォトダイオード(ダイオード706)を流れる光電流に応じた電位を保持させることができる。

#### 【0232】

10

20

30

40

50

図22(g)に示す回路に適用されるセンサ素子は、光センサ素子に限定されるものではなく、様々なセンサを用いることができる。例えば、センサ素子には、力、変位、位置、速度、加速度、角速度、回転数、距離、光(例えは、可視光、赤外線)、電磁波(例えは、脳波)、磁気、温度、化学物質、音、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、又はにおい等を測定する、または検出して、その結果を電圧信号または電流信号に変換する機能を有する素子が用いられる。例えは、フォトダイオード(706)の代わりに、温度特性が異なる2つの抵抗素子を直列に接続した温度センサ素子を設けてもよい。

#### 【0233】

図22(g)の回路において、トランジスタ700はOSトランジスタである。トランジスタ701およびトランジスタ704は、p-Siトランジスタでもよいし、n-Siトランジスタでもよいし、OSトランジスタでもよい。ダイオード706は、例えは、シリコンを用いたフォトダイオードでも良い。トランジスタ701およびトランジスタ704がSiトランジスタの場合、トランジスタ700の作製は低温プロセスで行うことができ、一般的なSiトランジスタの製造プロセスとの整合性も高いため、トランジスタ701およびトランジスタ704上にトランジスタ700を形成することは容易である。

#### 【0234】

また、図22(g)の回路において、トランジスタ701及びトランジスタ704の一方にSiトランジスタを用い、他方にOSトランジスタを用いる場合、Siトランジスタの高速特性とOSトランジスタの低リーキ特性を組み合わせた回路を形成することが可能である。

#### 【0235】

また、図22(g)の回路において、トランジスタ701及びトランジスタ704がOSトランジスタである場合、更に工程を簡略化することが可能となる。後述する実施例1、および実施例3で示すように、テクノロジーノードが微細であれば、OSトランジスタはSiトランジスタに同等の周波数特性を得ることが可能なため、上述のような構成でも高速動作と低リーキ特性を組み合わせた回路を形成することが可能である。

#### 【0236】

図22(h)に示す回路は、直列に電気的に接続されたトランジスタ700とトランジスタ704を有する。トランジスタ700は、第1のゲートが第1端子に電気的に接続され、第2端子は図示されていない配線または電極に電気的に接続されている。第1のゲートと第2端子を互いに電気的に接続してもよい。トランジスタ704の第1端子は、図示されていない配線または電極に電気的に接続されている。図22(h)は、Enhancement/Depletion型のインバータ回路として機能することが可能である。トランジスタ700はデュアルゲート型のOSトランジスタであり、第2のゲート電位を可変とすることで、図22(h)に示す回路(インバータ回路)の特性を制御することができる。トランジスタ704は、OSトランジスタまたはn-Siトランジスタとすることができる。

#### 【0237】

図22(i)に示す回路は、図22(h)の回路と同様に、直列に電気的に接続されたトランジスタ700とトランジスタ704とを有する。図22(i)に示す回路は、トランジスタ700のゲートが図示されていない配線または電極に電気的に接続されている点が、図22(h)の回路と異なる。図22(i)に示す回路は、Enhancement/Enhancement型のインバータとして機能することが可能である。トランジスタ700のゲート電位は固定としてもよいし、可変としても良い。トランジスタ700はOSトランジスタである。トランジスタ704は、OSトランジスタまたはn-Siトランジスタとすることができる。

#### 【0238】

図22(h)および図22(i)において、トランジスタ704をSiトランジスタとする場合は、図22(c)等に示す回路と同様に、トランジスタ704上にトランジスタ

10

20

30

40

50

700を作製することができる。

**【0239】**

なお、図22(a)乃至図22(i)の回路図に用いられるOSトランジスタには、必要に応じて、第2のゲート電極を設けてもよいし、設けなくてもよい。

**【0240】**

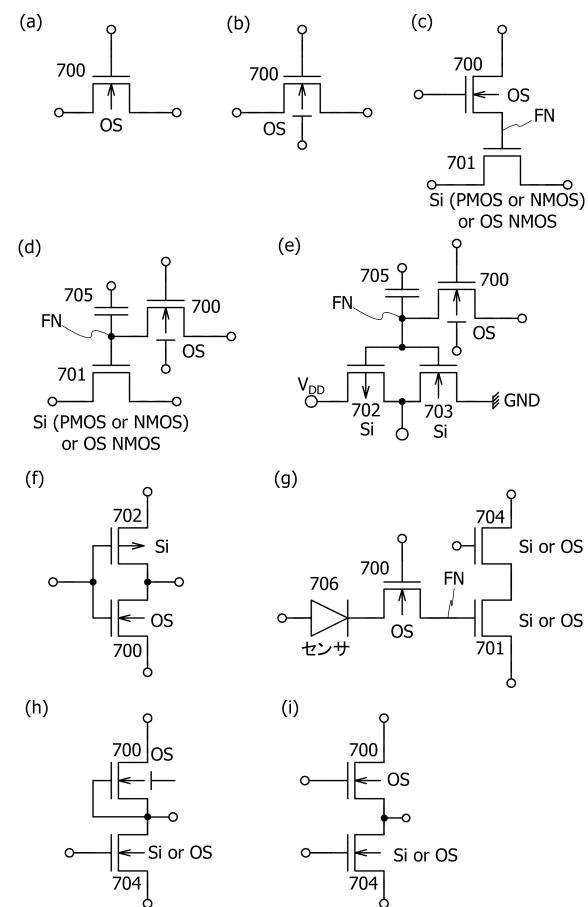

図22(a)乃至図22(i)に示す回路(半導体装置)を全て同一基板上に作製することが可能である。そのため、異なる機能、性能等を有する複数の回路を、同一基板上に作製することができる。例として、図22(d)と図22(f)に示す回路を同一基板上に作製した場合の半導体装置を図23(A)に示し、図22(d)と図22(i)に示す回路を同一基板上に作製した場合の半導体装置を図24(A)に示す。

10

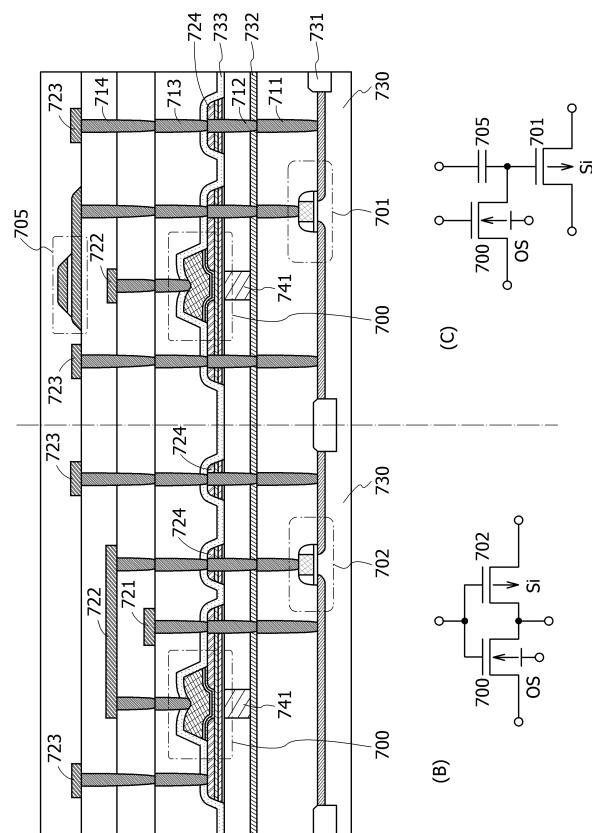

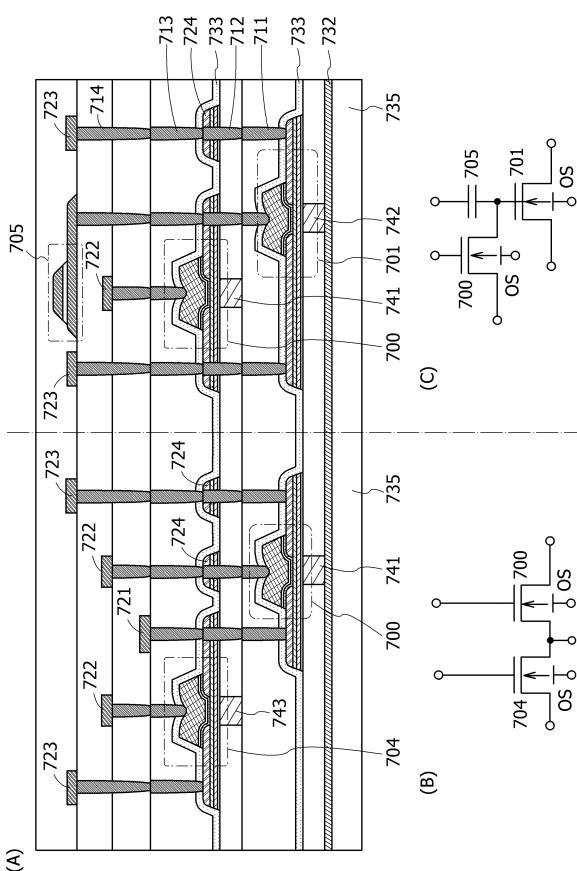

**【0241】**

図23(A)は半導体装置の構成の一例を示す断面図である。左側に、図23(B)の回路を示し、右側に図23(C)の回路を示している。図23(B)の回路図は図22(f)の回路図に相当し、図23(C)の回路図は図22(d)の回路図に相当する。図23(A)に示す半導体装置は、トランジスタ700がOSトランジスタであり、トランジスタ701及びトランジスタ702はp-Siトランジスタである例を示している。また、図23(A)には、各トランジスタのチャネル長方向の断面構造を示している。

**【0242】**

図23(A)に示す半導体装置は、トランジスタ700と、トランジスタ701と、トランジスタ702と、容量素子705と、基板730と、素子分離層731と、絶縁膜732と、絶縁膜733と、プラグ711と、プラグ712と、プラグ713と、プラグ714と、配線721と、配線722と、配線723と、配線724と、および、配線741とを有している。なお、図23(A)において、同一の層に形成されている複数のプラグのうち、ある一つのプラグのみに符号を記載し、それ以外のプラグには、煩雑さを避けるために符号の記載を省略している。

20

**【0243】**

基板730の詳細は、図19(B)の基板2201の記載を参照し、素子分離層731の詳細は、図19(B)の素子分離層2204を参照し、絶縁膜732の詳細は、図19(B)の絶縁膜2207の記載を参照し、絶縁膜733の詳細は、図19(B)の絶縁膜2208の記載を参照し、プラグ711乃至プラグ714の詳細は、図19(B)のプラグ2203の記載を参照し、配線721乃至723の詳細は、図19(B)の配線2202の記載を参照する。

30

**【0244】**

配線741は、トランジスタ700の第2のゲート電極としての機能を有する。配線741は、配線721乃至配線723に用いることができる材料で形成してもよい。なお、場合によっては、配線741を省略してもよい。配線724は、トランジスタ700のソース電極またはドレイン電極と、同一の材料で形成することができる。

**【0245】**

図23(A)において、符号及びハッチングパターンが与えられていない領域は絶縁体で構成された領域を表している。これらの領域には、酸化アルミニウム、窒化酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタルなどから選ばれた一種以上含む絶縁体を用いることができる。また、当該領域には、ポリイミド樹脂、ポリアミド樹脂、アクリル樹脂、シロキサン樹脂、エポキシ樹脂、フェノール樹脂等の有機樹脂を用いることもできる。

40

**【0246】**

半導体装置を、図23(A)のような構成にすることで、記憶回路(トランジスタとフローティングノードを含む)とその周辺回路を同一基板上に作製することができる。また、OSトランジスタは、900以上の熱処理が不要なため、より低温なプロセスで回路

50

を作製することが可能である。また、微細化されたOSトランジスタは、活性層にシリコンを用いたnチャネル型のトランジスタと同等の周波数特性を示し、OSトランジスタとp-Siトランジスタを組み合わせたCMOS回路は高速動作が可能である。

#### 【0247】

図24(A)は半導体装置の構成例を示す断面図であり、左側に図24(B)に示す回路を示し、右側に図24(C)に示す回路を示す。図24(B)の回路図は図22(i)の回路図に相当し、図24(C)の回路図は図22(d)の回路図に相当する。図24(A)に示す半導体装置は、トランジスタ700、トランジスタ701及びトランジスタ704にOSトランジスタを用いた例を示している。図24(A)は、各トランジスタのチャネル長方向の断面図である。

10

#### 【0248】

図24(A)に示す半導体装置は、トランジスタ700と、トランジスタ701と、トランジスタ704と、容量素子705と、基板735と、絶縁膜732と、絶縁膜733と、プラグ711と、プラグ712と、プラグ713と、プラグ714と、配線721と、配線722と、配線723と、配線724と、配線741と、配線742と、および、配線743とを有している。なお、図24(A)において、同一の層に形成されている複数のプラグのうち、ある一つのプラグのみに符号を与え、それ以外のプラグは、煩雑さを避けるために符号を省略している。

#### 【0249】

基板735の詳細は、図19(B)の基板2201の記載を参照する。また、基板735の中に他のデバイスが形成されていてもよい。その場合は、基板735の表面が平坦になるようにCMP法等で平坦化処理を行うことが好ましい。

20

#### 【0250】

絶縁膜732の詳細は、図19(B)の絶縁膜2207の記載を参照し、絶縁膜733の詳細は、図19(B)の絶縁膜2208の記載を参照し、プラグ711乃至プラグ714の詳細は、図19(B)のプラグ2203の記載を参照し、配線721乃至723の詳細は、図19(B)の配線2202の記載を参照する。

#### 【0251】

配線741はトランジスタ700の第2のゲート電極としての機能を有し、配線742はトランジスタ701の第2のゲート電極としての機能を有し、配線743はトランジスタ704の第2のゲート電極としての機能を有している。配線741乃至配線743は、配線721乃至配線723に用いることができる材料で形成することができる。なお、場合によっては、配線741乃至配線743を省略してもよい。

30

#### 【0252】

配線724は、トランジスタ700及びトランジスタ704のソース電極またはドレイン電極と同じ材料で形成することができる。

#### 【0253】

なお、図24(A)において、符号及びハッチングパターンが与えられていない領域は絶縁体で構成された領域を表している。これらの領域には、酸化アルミニウム、窒化酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタルなどから選ばれた一種以上含む絶縁体を用いることができる。また、当該領域には、ポリイミド樹脂、ポリアミド樹脂、アクリル樹脂、シロキサン樹脂、エポキシ樹脂、フェノール樹脂等の有機樹脂を用いることもできる。

40

#### 【0254】

半導体装置を、図24(A)のような構成にすることで、記憶回路(トランジスタとフローティングノードを含む)とその周辺回路を同一基板上に作製することができる。また、OSトランジスタは、900以上の中熱処理が不要なため、より低温なプロセスで半導体装置を作製することが可能である。また、OSトランジスタは他の半導体素子と積層す

50

ることが可能であり、3次元的に素子を配置することができ、集積度の高い半導体装置を作製することができる。また、微細化されたOSトランジスタは、活性層にシリコンを用いたnチャネル型のトランジスタと同等の周波数特性を示し、OSトランジスタで作製した回路は高速動作が可能である。

#### 【0255】

また、OSトランジスタにおける電子移動度のチャネル長依存性は、Siトランジスタにおける電子移動度のチャネル長依存性ほど影響が大きくない。また、OSトランジスタは、チャネル長を10μmから100nmまで微細化しても、電界効果移動度の明確な低下がみられない。

#### 【0256】

そのため、OSトランジスタをチャネル長が10μm以下のトランジスタに用いる場合、Siトランジスタとの電界効果移動度の差はトランジスタのチャネル長を10μm以上としたときよりも小さくなる。OSトランジスタを100nm以下のチャネル長のトランジスタに用いる場合、Siトランジスタの30分の1程度、好ましくは10分の1程度、より好ましくは3分の1程度の電界効果移動度まで差を縮めることができる。

#### 【0257】

また、OSトランジスタをチャネル長が約100nmのトランジスタに用いる場合、Siトランジスタと同程度の電界効果移動度を実現することが可能だと考えられる。そのため、微細加工されたOSトランジスタでは、Siトランジスタと同等のスイッチング速度、周波数特性を実現することが可能である。

#### 【0258】

また、OSトランジスタは、オフ電流が低い特性を有する。OSトランジスタを用いた回路においては、オフ電流が低いことで電荷を保持するための容量を小さくすることができる。

#### 【0259】

本実施の形態の構成は、他の実施の形態および実施例と適宜組み合わせができる。

#### 【0260】

##### (実施の形態4)

本実施の形態では、上記実施の形態で例示したメモリセルアレイ300等の記憶装置を含むRFデバイスについて説明する。ここで記憶装置はメモリセルアレイに接続する行選択ドライバ、列選択ドライバ、及びA/Dコンバータ等を含んでもよい。

#### 【0261】

本実施の形態におけるRFデバイスは、内部に記憶回路を有し、記憶回路に必要な情報を記憶し、非接触手段、例えば無線通信を用いて外部と情報の授受を行うものである。このような特徴から、RFデバイスは、物品などの個体情報を読み取ることにより物品の識別を行う個体認証システムなどに用いることが可能である。なお、これらの用途に用いるためには極めて高い信頼性が要求される。

#### 【0262】

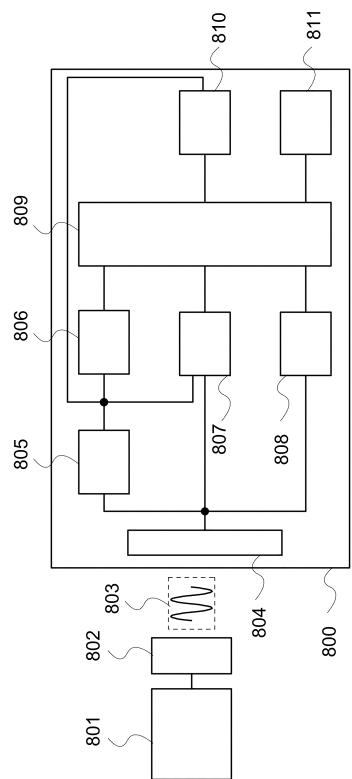

図25は、RFデバイスの構成例を示すブロック図である。図25に示すRFデバイス800は、アンテナ804、整流回路805、定電圧回路806、復調回路807、変調回路808、論理回路809、記憶回路810、およびROM811を有している。

#### 【0263】

復調回路807に含まれる整流作用を示すトランジスタに逆方向電流を十分に抑制することが可能な材料、例えば、酸化物半導体、が用いられた構成としてもよい。これにより、逆方向電流に起因する整流作用の低下を抑制し、復調回路の出力が飽和することを防止できる。つまり、復調回路の入力に対する復調回路の出力を線形に近づけることができる。なお、データの伝送形式は、一対のコイルを対向配置して相互誘導によって交信を行う電磁結合方式、誘導電磁界によって交信する電磁誘導方式、電波を利用して交信する電波方式の3つに大別される。本実施の形態に示すRFデバイス800は、そのいずれの方式

10

20

30

40

50

に用いることも可能である。

#### 【0264】

次に各回路の構成について説明する。アンテナ804は、通信器801（質問器、リーダ／ライタなどともいう）に接続されたアンテナ802との間で無線信号803の送受信を行うためのものである。整流回路805は、アンテナ804で無線信号を受信することにより生成される入力交流信号を整流、例えば、半波2倍圧整流し、後段に設けられた容量素子により、整流された信号を平滑化することで入力電位を生成するための回路である。なお、整流回路805の入力側または出力側には、リミッタ回路を設けてもよい。リミッタ回路とは、入力交流信号の振幅が大きく、内部生成電圧が大きい場合に、ある電力以上の電力を後段の回路に入力しないように制御するための回路である。

10

#### 【0265】

定電圧回路806は、入力電位から安定した電源電圧を生成し、各回路に供給するための回路である。なお、定電圧回路806は、内部にリセット信号生成回路を有していてもよい。リセット信号生成回路は、安定した電源電圧の立ち上がりを利用して、論理回路809のリセット信号を生成するための回路である。

#### 【0266】

復調回路807は、入力交流信号を包絡線検出することにより復調し、復調信号を生成するための回路である。また、変調回路808は、アンテナ804より出力するデータに応じて変調をおこなうための回路である。

#### 【0267】

論理回路809は復調信号を解析し、処理を行うための回路である。記憶回路810は、入力された情報を保持する回路であり、ロウデコーダ、カラムデコーダ、記憶領域などを有する。また、ROM811は、固有番号（ID）などを格納し、処理に応じて出力を行うための回路である。

20

#### 【0268】

なお、上述の各回路は、必要に応じて、適宜、取捨することができる。

#### 【0269】

ここで、先の実施の形態で説明した記憶回路を、記憶回路810に適用することができる。本発明の一態様の記憶回路は、電源が遮断された状態であっても情報を保持できるため、RFデバイスに好適に用いることができる。さらに本発明の一態様の記憶回路は、データの書き込みに必要な電力（電圧）が従来の不揮発性メモリに比べて著しく小さいため、データの読み出し時と書き込み時の最大通信距離の差を生じさせないことも可能である。さらに、データの書き込み時に電力が不足し、誤動作または誤書き込みが生じることを抑制することができる。

30

#### 【0270】

また、本発明の一態様の記憶回路は、不揮発性のメモリとして用いることが可能であるため、ROM811に適用することもできる。その場合には、生産者がROM811にデータを書き込むためのコマンドを別途用意し、ユーザが自由に書き換えできないようにしておくことが好ましい。生産者が出荷前に固有番号を書込んだのちに製品を出荷することで、作製したRFデバイスすべてについて固有番号を付与するのではなく、出荷する良品にのみ固有番号を割り当てることが可能となり、出荷後の製品の固有番号が不連続になることがなく出荷後の製品に対応した顧客管理が容易となる。

40

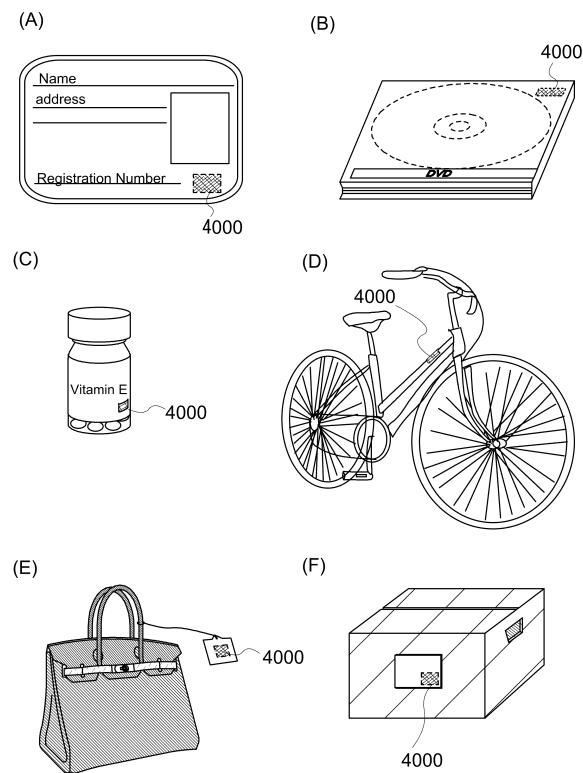

#### 【0271】

次に、図26を参照して、RFデバイスの使用例について説明する。RFデバイスの用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類（運転免許証や住民票等、図26（A））、包装用容器類（包装紙やボトル等、図26（C））、記録媒体（DVDやビデオテープ等、図26（B））、乗り物類（自転車等、図26（D））、身の回り品（鞄や眼鏡等）、食品類、植物類、動物類、人体、衣類、生活用品類、薬品や薬剤を含む医療品、または電子機器（液晶表示装置、EL表示装置、テレビジョン装置、または携帯電話）等の物品、若しくは各物品に取り付ける荷札（図26（E））、図

50

26(F)等に設けて使用することができる。

**【0272】**

本発明の一態様に係るRFデバイス4000は、表面に貼る、または埋め込むことにより、物品に固定される。例えば、本であれば紙に埋め込み、有機樹脂からなるパッケージであれば当該有機樹脂の内部に埋め込み、各物品に固定される。本発明の一態様に係るRFデバイス4000は、小型、薄型、軽量を実現するため、物品に固定した後もその物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、または証書類等に本発明の一態様に係るRFデバイス4000を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、または電子機器等に本発明の一態様に係るRFデバイスを取り付けることにより、検品システム等のシステムの効率化を図ることができる。また、乗り物類であっても、本発明の一態様に係るRFデバイスを取り付けることにより、盗難などに対するセキュリティ性を高めることができる。10

**【0273】**

以上のように、本発明の一態様に係るRFデバイスを本実施の形態に挙げた各用途に用いることにより、情報の書き込みや読み出しを含む動作電力を低減できるため、最大通信距離を長くとることが可能となる。また、電力が遮断された状態であっても情報を極めて長い期間保持可能であるため、書き込みや読み出しの頻度が低い用途にも好適に用いることができる。20

**【0274】**

以上、本実施の形態で示す構成、方法は、他の実施の形態で示す構成、方法と適宜組み合わせて用いることができる。

**【0275】**

(実施の形態5)

本実施の形態では、少なくとも実施の形態で説明したメモリセルアレイ300等を含む記憶装置を含むCPUについて説明する。ここで記憶装置はメモリセルアレイに接続する行選択ドライバ、列選択ドライバ、及びA/Dコンバータ等を含んでもよい。

**【0276】**

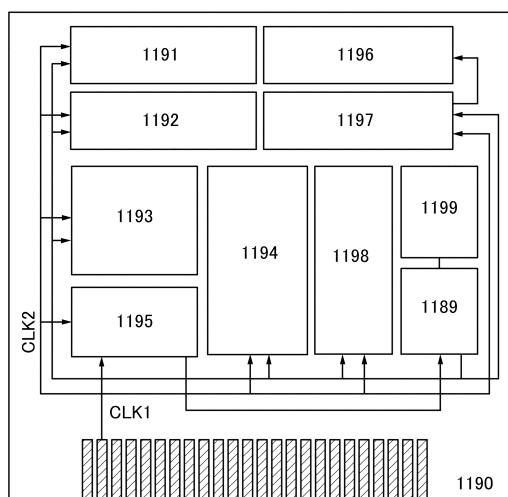

図27は、先の実施の形態で説明した記憶装置や、その他の半導体装置を少なくとも一部に用いたCPUの一例の構成を示すブロック図である。30

**【0277】**

図27に示すCPUは、基板1190上に、ALU1191(ALU: Arithmetic logical unit、演算回路)、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース1198(Bus I/F)、書き換え可能なROM1199、およびROMインターフェース1189(ROM I/F)を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けてもよい。もちろん、図27に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。例えば、図27に示すCPUまたは演算回路を含む構成を一つのコアとし、当該コアを複数含み、それぞれのコアが並列で動作するような構成としてもよい。また、CPUが内部演算回路やデータバスで扱えるビット数は、例えば8ビット、16ビット、32ビット、64ビットなどとすることができる。40

**【0278】**

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。50

**【0279】**

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう。

**【0280】**

また、タイミングコントローラ1195は、ALU1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、内部クロック信号CLK2を上記各種回路に供給する。

**【0281】**

図27に示すCPUでは、レジスタ1196に、メモリセルが設けられている。レジスタ1196のメモリセルとして、先の実施の形態に示したトランジスタを用いることができる。

10

20

**【0282】**

図27に示すCPUにおいて、レジスタコントローラ1197は、ALU1191からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジスタ1196が有するメモリセルにおいて、フリップフロップによるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。フリップフロップによるデータの保持が選択されている場合、レジスタ1196内のメモリセルへの、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ1196内のメモリセルへの電源電圧の供給を停止することができる。

**【0283】**

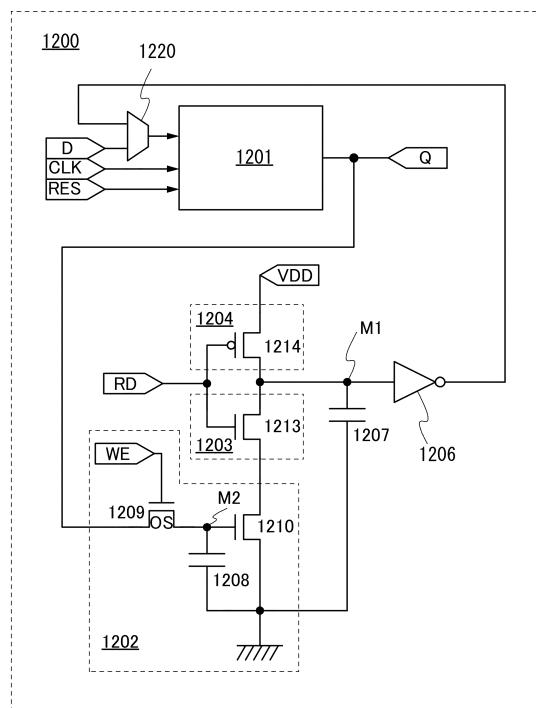

30

図28は、レジスタ1196として用いることのできる記憶素子の回路図の一例である。記憶回路1200は、電源遮断で記憶データが揮発する回路1201と、電源遮断で記憶データが揮発しない回路1202と、スイッチ1203と、スイッチ1204と、論理素子1206と、容量素子1207と、選択機能を有する回路1220と、を有する。回路1202は、容量素子1208と、トランジスタ1209と、トランジスタ1210と、を有する。なお、記憶回路1200は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の素子をさらに有していても良い。トランジスタ1209は酸化物半導体層にチャネルが形成されるトランジスタであることが好ましい。

**【0284】**

ここで、回路1202には、先の実施の形態で説明した記憶装置を用いることができる。記憶回路1200への電源電圧の供給が停止した際、回路1202のトランジスタ1209のゲートには接地電位(0V)、またはトランジスタ1209がオフする電位が入力され続ける構成とする。例えば、トランジスタ1209のゲートが抵抗等の負荷を介して接地される構成とする。

40

**【0285】**

スイッチ1203は、一導電型(例えば、nチャネル型)のトランジスタ1213を用いて構成され、スイッチ1204は、一導電型とは逆の導電型(例えば、pチャネル型)のトランジスタ1214を用いて構成した例を示す。ここで、スイッチ1203の第1端子はトランジスタ1213のソースとドレインの一方に対応し、スイッチ1203の第2端子はトランジスタ1213のソースとドレインの他方に対応し、スイッチ1203はト

50

ランジスタ1213のゲートに入力される制御信号RDによって、第1端子と第2端子の間の導通または非導通（つまり、トランジスタ1213のオン状態またはオフ状態）が選択される。スイッチ1204の第1端子はトランジスタ1214のソースとドレインの一方に対応し、スイッチ1204の第2端子はトランジスタ1214のソースとドレインの他方に対応し、スイッチ1204はトランジスタ1214のゲートに入力される制御信号RDによって、第1端子と第2端子の間の導通または非導通（つまり、トランジスタ1214のオン状態またはオフ状態）が選択される。

#### 【0286】

トランジスタ1209のソースとドレインの一方は、容量素子1208の一対の電極のうちの一方、およびトランジスタ1210のゲートと電気的に接続される。ここで、接続部分をノードM2とする。トランジスタ1210のソースとドレインの一方は、低電源電位を供給することのできる配線（例えばGND線）に電気的に接続され、他方は、スイッチ1203の第1端子（トランジスタ1213のソースとドレインの一方）と電気的に接続される。スイッチ1203の第2端子（トランジスタ1213のソースとドレインの他方）はスイッチ1204の第1端子（トランジスタ1214のソースとドレインの一方）と電気的に接続される。スイッチ1204の第2端子（トランジスタ1214のソースとドレインの他方）は電源電位VDDを供給することのできる配線と電気的に接続される。スイッチ1203の第2端子（トランジスタ1213のソースとドレインの他方）と、スイッチ1204の第1端子（トランジスタ1214のソースとドレインの一方）と、論理素子1206の入力端子と、容量素子1207の一対の電極のうちの一方と、は電気的に接続される。ここで、接続部分をノードM1とする。容量素子1207の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位（GND等）または高電源電位（VDD等）が入力される構成とすることができます。容量素子1207の一対の電極のうちの他方は、低電源電位を供給することのできる配線（例えばGND線）と電気的に接続される。容量素子1208の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位（GND等）または高電源電位（VDD等）が入力される構成とすることができます。容量素子1208の一対の電極のうちの他方は、低電源電位を供給することのできる配線（例えばGND線）と電気的に接続される。

#### 【0287】

なお、容量素子1207および容量素子1208は、トランジスタや配線の寄生容量等を積極的に利用することによって省略することも可能である。

#### 【0288】

トランジスタ1209の第1ゲート（第1のゲート電極）には、制御信号WEが入力される。スイッチ1203およびスイッチ1204は、制御信号WEとは異なる制御信号RDによって第1端子と第2端子の間の導通状態または非導通状態を選択され、一方のスイッチの第1端子と第2端子の間が導通状態のとき他方のスイッチの第1端子と第2端子の間は非導通状態となる。

#### 【0289】

トランジスタ1209のソースとドレインの他方には、回路1201に保持されたデータに対応する信号が入力される。図28では、回路1201から出力された信号が、トランジスタ1209のソースとドレインの他方に入力される例を示した。スイッチ1203の第2端子（トランジスタ1213のソースとドレインの他方）から出力される信号は、論理素子1206によってその論理値が反転された反転信号となり、回路1220を介して回路1201に入力される。

#### 【0290】

なお、図28では、スイッチ1203の第2端子（トランジスタ1213のソースとドレインの他方）から出力される信号は、論理素子1206および回路1220を介して回路1201に入力する例を示したがこれに限定されない。スイッチ1203の第2端子（トランジスタ1213のソースとドレインの他方）から出力される信号が、論理値を反転

10

20

30

40

50

させられることなく、回路 1201 に入力されてもよい。例えば、回路 1201 内に、入力端子から入力された信号の論理値が反転した信号が保持されるノードが存在する場合に、スイッチ 1203 の第 2 端子（トランジスタ 1213 のソースとドレインの他方）から出力される信号を当該ノードに入力することができる。

#### 【0291】

また、図 28において、記憶回路 1200 に用いられるトランジスタのうち、トランジスタ 1209 以外のトランジスタは、酸化物半導体以外の半導体でなる層または基板 1190 にチャネルが形成されるトランジスタとすることができる。例えば、シリコン層またはシリコン基板にチャネルが形成される Si トランジスタとすることができる。また、記憶回路 1200 に用いられるトランジスタ全てを、チャネルが酸化物半導体層で形成される OS トランジスタとすることもできる。または、記憶回路 1200 は、トランジスタ 1209 以外にも、OS トランジスタを含んでいてもよく、残りのトランジスタは酸化物半導体以外の半導体でなる層または基板 1190 にチャネルが形成されるトランジスタとすることもできる。10

#### 【0292】

図 28における回路 1201 には例えばフリップフロップ回路を用いることができる。また、論理素子 1206 には例えばインバータやクロックドインバータ等を用いることができる。

#### 【0293】

本発明の一態様の半導体装置では、記憶回路 1200 に電源電圧が供給されない間は、回路 1201 に記憶されていたデータを、回路 1202 に設けられた容量素子 1208 によって保持することができる。20

#### 【0294】

また、OS トランジスタはオフ電流が極めて小さい。例えば、OS トランジスタのオフ電流は、結晶性を有するシリコンにチャネルが形成されるトランジスタのオフ電流に比べて著しく低い。そのため、トランジスタ 1209 を OS トランジスタとすることによって、記憶回路 1200 に電源電圧が供給されない間も容量素子 1208 に保持された信号は長期間にわたり保たれる。こうして、記憶回路 1200 は電源電圧の供給が停止した間も記憶内容（データ）を保持することが可能である。

#### 【0295】

また、スイッチ 1203 およびスイッチ 1204 を設けることによって、プリチャージ動作を行うことを特徴とする記憶素子であるため、電源電圧供給再開後に、回路 1201 が元のデータを保持しなおすまでの時間を短くすることができる。30

#### 【0296】

また、回路 1202 において、容量素子 1208 によって保持された信号はトランジスタ 1210 のゲートに入力される。そのため、記憶回路 1200 への電源電圧の供給が再開された後、容量素子 1208 によって保持された信号を、トランジスタ 1210 の状態（オン状態、またはオフ状態）に変換して、回路 1202 から読み出すことができる。それ故、容量素子 1208 に保持された信号に対応する電位が多少変動していても、元の信号を正確に読み出すことが可能である。40

#### 【0297】

このような記憶回路 1200 を、プロセッサが有するレジスタやキャッシュメモリなどの記憶装置に用いることで、電源電圧の供給停止による記憶装置内のデータの消失を防ぐことができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰することができる。よって、プロセッサ全体、もしくはプロセッサを構成する一つ、または複数の論理回路において、短い時間でも電源停止を行うことができるため、消費電力を抑えることができる。

#### 【0298】

本実施の形態では、記憶回路 1200 を CPU に用いる例として説明したが、記憶回路 1200 は、DSP (Digital Signal Processor)、カスタム

L S I 、 P L D ( P r o g r a m m a b l e L o g i c D e v i c e ) 等の L S I 、 R F デバイス ( R a d i o F r e q u e n c y D e v i c e ) にも応用可能である。

#### 【 0 2 9 9 】

例えば、本明細書等において、様々な基板を用いて、トランジスタを形成することが出来る。基板の種類は、特定のものに限定されることはない。その基板の一例としては、半導体基板（例えば単結晶基板又はシリコン基板）、S O I 基板、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タングステン基板、タングステン・ホイルを有する基板、可撓性基板、貼り合わせフィルム、繊維状の材料を含む紙、又は基材フィルムなどがある。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、又はソーダライムガラスなどがある。可撓性基板、貼り合わせフィルム、基材フィルムなどの一例としては、以下のものがあげられる。例えば、ポリエチレンテレフタレート ( P E T ) 、ポリエチレンナフタレート ( P E N ) 、ポリエーテルサルファン ( P E S ) に代表されるプラスチックがある。または、一例としては、アクリル等の合成樹脂などがある。または、一例としては、ポリプロピレン、ポリエステル、ポリフッ化ビニル、又はポリ塩化ビニルなどがある。または、一例としては、ポリアミド、ポリイミド、アラミド、エポキシ、無機蒸着フィルム、又は紙類などがある。特に、半導体基板、単結晶基板、又はS O I 基板などを用いてトランジスタを製造することによって、特性、サイズ、又は形状などのばらつきが少なく、電流能力が高く、サイズの小さいトランジスタを製造することができる。このようなトランジスタによって回路を構成すると、回路の低消費電力化、又は回路の高集積化を図ることができる。10

#### 【 0 3 0 0 】

また、基板として、可撓性基板を用い、可撓性基板上に直接、トランジスタを形成してもよい。または、基板とトランジスタの間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板より分離し、他の基板に転載するためには用いることができる。その際、トランジスタは耐熱性の劣る基板や可撓性の基板にも転載できる。なお、上述の剥離層には、例えば、タングステン膜と酸化シリコン膜との無機膜の積層構造の構成や、基板上にポリイミド等の有機樹脂膜が形成された構成等を用いることができる。20

#### 【 0 3 0 1 】

つまり、ある基板を用いてトランジスタを形成し、その後、別の基板にトランジスタを転置し、別の基板上にトランジスタを配置してもよい。トランジスタが転置される基板の一例としては、上述したトランジスタを形成することが可能な基板に加え、紙基板、セロファン基板、アラミドフィルム基板、ポリイミドフィルム基板、石材基板、木材基板、布基板（天然繊維（絹、綿、麻）、合成繊維（ナイロン、ポリウレタン、ポリエステル）若しくは再生繊維（アセテート、キュプラ、レーヨン、再生ポリエステル）などを含む）、皮革基板、又はゴム基板などがある。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、又は薄型化を図ることができる。30

#### 【 0 3 0 2 】

以上、本実施の形態で示す構成、方法は、他の実施の形態で示す構成、方法と適宜組み合わせて用いることができる。40

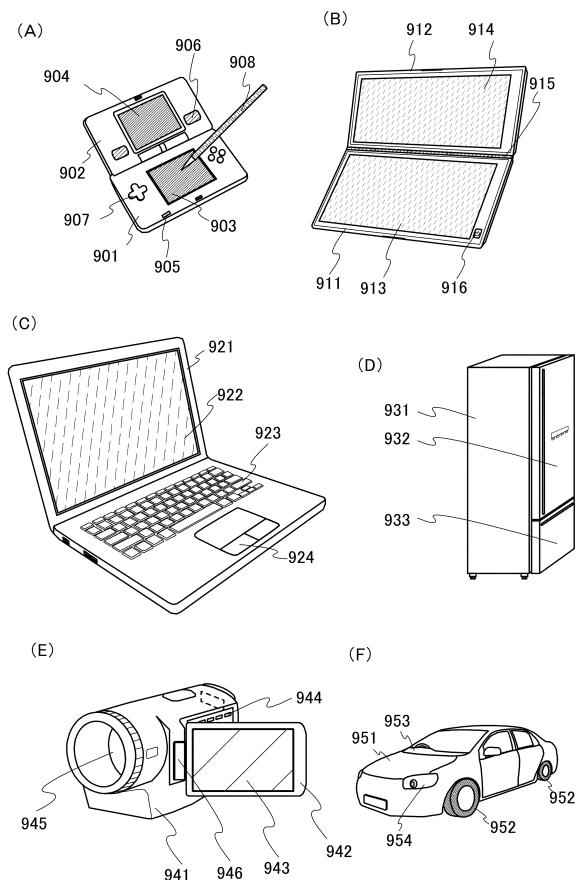

#### 【 0 3 0 3 】

##### ( 実施の形態 6 )

本発明の一態様に係る半導体装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはD V D : D i g i t a l V e r s a t i l e D i s c 等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯データ端末、電子書籍、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレ50

イ)、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンタ、プリンタ複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図29に示す。

#### 【0304】

図29(A)に示す携帯型ゲーム機は、筐体901、筐体902、表示部903、表示部904、マイクロフォン905、スピーカー906、操作キー907、スタイルス908等を有する。なお、図29(A)に示した携帯型ゲーム機は、2つの表示部903と表示部904とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

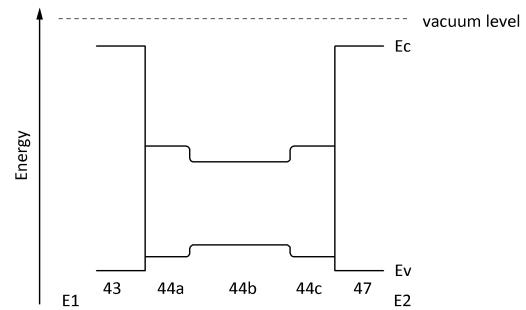

10