(12)发明专利申请

(10)申请公布号 CN 109216170 A

(43)申请公布日 2019.01.15

(21)申请号 201810783756.6

阿尔图尔·科利奇

(22)申请日 2015.02.02

乔治·安德鲁·安东内利

(30)优先权数据

(74)专利代理机构 上海胜康律师事务所 31263

61/934,514 2014.01.31 US

代理人 樊英如 张静

(62)分案原申请数据

(51)Int.Cl.

201510053668.7 2015.02.02

H01L 21/033(2006.01)

(71)申请人 朗姆研究公司

H01L 21/3213(2006.01)

地址 美国加利福尼亚州

G03F 7/16(2006.01)

(72)发明人 杰弗里·马克斯

G03F 7/004(2006.01)

理查德·A·戈奇奥

G03F 1/76(2012.01)

丹尼斯·M·豪斯曼

C23C 18/18(2006.01)

阿德里安·拉瓦伊

C23C 18/16(2006.01)

托马斯·尼斯利

C23C 18/14(2006.01)

斯利士·K·雷迪

权利要求书1页 说明书8页 附图3页

巴德里·N·瓦拉达拉简

(54)发明名称

结合真空的硬掩模工艺和装置

(57)摘要

本发明涉及结合真空的硬掩模工艺和装置，具体而言，用于形成金属硬掩模的结合真空的无光致抗蚀剂的方法和装置可以提供低于30纳米图案的分辨率。在半导体衬底上沉积对图案化剂敏感的含金属(例如，金属盐或有机金属化合物)膜。含金属膜然后通过在真空中暴露于图案化剂而被直接图案化(即，不使用光致抗蚀剂)，从而形成所述金属掩模。例如，所述含金属膜是感光性的，图案化使用低于30nm波长的光的光刻(诸如EUV光刻)来进行。

1. 一种形成金属掩模的无光致抗蚀剂的方法,其包括:

在半导体衬底上沉积EUV敏感的含金属膜;以及

在真空环境中通过波长范围为10至20纳米之间的EUV曝光直接以低于30纳米的分辨率图案化所述含金属膜;以及

显影图案以形成所述金属掩模。

2. 根据权利要求1所述的方法,其中,所述含金属膜是金属盐。

3. 根据权利要求2所述的方法,其中,所述金属盐是金属卤化物。

4. 根据权利要求3所述的方法,其中,所述金属是锡(Sn)。

5. 一种用于进行无光致抗蚀剂的金属掩模的形成的装置,所述装置包括:

含金属膜沉积模块;

含金属膜图案化模块;

连接所述沉积模块和所述图案化模块的真空传送模块。

6. 根据权利要求5所述的装置,其中:

所述沉积模块包括用于沉积感光性金属卤化物膜或有机金属化合物膜的反应器室;以及

所述图案化模块包括具有低于30nm的波长的辐射源的光刻工具。

7. 根据权利要求6所述的装置,其中,所述图案化模块是EUV光刻工具。

8. 根据权利要求6所述的装置,其中,所述图案化模块具有选自由光子、电子、质子、离子和中性物质组成的组中的图案化剂的源,使得所述含金属膜能通过暴露于所述图案化剂进行图案化。

9. 根据权利要求6所述的装置,其还包括用于将衬底从所述图案化模块传送到所述真空传送模块的入装载锁,以及用于将衬底从所述真空传送模块传送到所述图案化模块的出装载锁;且其中所述出装载锁用作除气模块。

10. 根据权利要求6所述的装置,其还包括控制器,该控制器包括用于进行无光致抗蚀剂的金属掩模形成的指令,所述指令包括用于以下操作的指令:

在所述含金属膜沉积模块中,在半导体衬底上沉积EUV敏感的含金属膜;

将所述衬底在真空下传送到所述含金属膜图案化模块;以及

在所述含金属膜图案化模块中,在真空环境中通过EUV曝光直接图案化所述含金属膜以形成所述金属掩模。

## 结合真空的硬掩模工艺和装置

[0]本申请是申请号为201510053668.7、申请日为2015.02.02、发明名称为“结合真空的硬掩模工艺和装置”的申请的分案申请。

### 相关申请的交叉引用

[0001] 本申请要求于2014年1月31日提交的、名称为“VACUUM-INTEGRATED HARDMASK PROCESSES”的美国临时专利申请No. 61/934,514的优先权，在此通过参考引入其全部内容并用于所有目的。

### 技术领域

[0002] 本发明总体涉及半导体处理领域。具体地，本发明涉及用于形成金属硬掩模而不使用光致抗蚀剂的结合真空的工艺。

### 背景技术

[0003] 在半导体处理中膜的图案化在半导体的生产和制造中往往是关键步骤。图案化包括光刻。在常规的光刻中，如193nm的光刻，图案通过下列步骤印刻：通过从光子源发射光子到掩模并将图案印在感光性光致抗蚀剂上，从而造成光致抗蚀剂中的化学反应，在显影之后，去除光致抗蚀剂的某些部分以形成图案。

[0004] 先进的技术节点(如国际半导体技术发展路线图所定义)包括节点22纳米、16纳米、以及小于16纳米。在16纳米节点中，例如，在镶嵌结构中典型的通孔或线的宽度通常不超过约30纳米。先进半导体集成电路(IC)和其它器件的特征的尺寸缩放推动光刻提高分辨率。

### 发明内容

[0005] 本发明的方面涉及用于形成金属硬掩模的结合真空的无光致抗蚀剂的方法和装置。这样的方法和装置可以提供低于30纳米的图案化分辨率。通常，在半导体衬底沉积含金属(例如，金属盐或有机金属化合物)膜，该含金属膜对例如光子、电子、质子、离子或中性物质之类图案化剂敏感，使得所述膜可通过暴露于这些物质中的一种进行图案化。然后通过在真空环境中暴露于图案化剂将含金属膜直接图案化(即，不使用光致抗蚀剂)，以形成金属掩模。例如，所述含金属膜是感光性的，图案化使用光学光刻(诸如EUV光刻)进行。

[0006] 在一种实施方案中，在半导体衬底上沉积EUV敏感含金属膜。然后含金属膜通过在真空气氛中EUV曝光而被直接图案化，从而形成金属硬掩模。以这种方式，提供了将膜形成(冷凝/沉积)和光学光刻的步骤结合的结合真空的金属硬掩模工艺和相关的结合真空的硬件，导致EUV光刻(EUVL)性能大大改善-例如线边缘粗糙度降低。通过使用含金属的硬掩模，并通过使用EUV光子通量直接图案化含金属膜，该方法完全不需要光致抗蚀剂。

[0007] 在另一实施方案中，用于进行无光致抗蚀剂的金属硬掩模形成的装置可以结合真空以进行所描述的工艺。该装置包括含金属膜沉积模块，含金属膜图案化模块，以及连接所述沉积模块和所述图案化模块的真空传送模块。

具体而言,本发明的一些方面可以阐述如下:

1.一种形成金属掩模的无光致抗蚀剂的方法,其包括:

在半导体衬底上沉积EUV敏感的含金属膜;以及

在真空环境中通过波长范围为10至20纳米之间的EUV曝光直接以低于30纳米的分辨率图案化所述含金属膜;以及

显影图案以形成所述金属掩模。

2.根据条款1所述的方法,其中,所述含金属膜是金属盐。

3.根据条款2所述的方法,其中,所述金属盐是金属卤化物。

4.根据条款3所述的方法,其中,所述金属是锡(Sn)。

5.根据条款3所述的方法,其中,所述金属是铪(Hf)。

6.根据条款1所述的方法,其中,所述含金属膜是有机金属化合物。

7.根据条款6所述的方法,其中,所述有机金属化合物的所述金属是锡(Sn)。

8.根据条款1所述的方法,其中,所述半导体衬底是包括部分形成的集成电路的硅晶片,所述方法还包括:

在所述沉积之前,提供所述半导体衬底在第一反应器室中用于沉积含金属膜;和

在所述沉积之后,在真空下将所述衬底传送到光刻处理室以进行图案化。

9.根据条款8所述的方法,其还包括在进入所述光刻处理室之前,对所述衬底除气。

10.根据条款9所述的方法,其中,所述除气包括降低所述衬底周围的压强至不大于 $1E-8$ 托。

11.根据条款1所述的方法,其还包括通过在所述金属掩模上选择性沉积进行的图案扩增。

12.根据条款11所述的方法,其中,所述选择性沉积包括无电沉积。

13.根据条款1所述的方法,其中,所述EUV曝光具有13.5纳米的波长。

14.根据条款1所述的方法,其还包括在随后蚀刻下面的半导体衬底期间将所述掩模用作图案传输层。

15.根据条款1所述的方法,其中,所述图案的显影包括加热所述衬底以挥发所述含金属膜的未暴露区域。

16.一种用于进行无光致抗蚀剂的金属掩模的形成的装置,所述装置包括:

含金属膜沉积模块;

含金属膜图案化模块;

连接所述沉积模块和所述图案化模块的真空传送模块。

17.根据条款16所述的装置,其中:

所述沉积模块包括用于沉积感光性金属卤化物膜或有机金属化合物膜的反应器室;以及

所述图案化模块包括具有低于30nm的波长的辐射源的光刻工具。

18.根据条款17所述的装置,其中,所述图案化模块是EUV光刻工具。

19.根据条款17所述的装置,其中,所述图案化模块具有选自由光子、电子、质子、离子和中性物质组成的组中的图案化剂的源,使得所述含金属膜能通过暴露于所述图案化剂进行图案化。

20. 根据条款17所述的装置,其还包括用于将衬底从所述图案化模块传送到所述真空传送模块的入装载锁,以及用于将衬底从所述真空传送模块传送到所述图案化模块的出装载锁;且其中所述出装载锁用作除气模块。

21. 根据条款17所述的装置,其还包括控制器,该控制器包括用于进行无光致抗蚀剂的金属掩模形成的指令,所述指令包括用于以下操作的指令:

在所述含金属膜沉积模块中,在半导体衬底上沉积EUV敏感的含金属膜;

将所述衬底在真空下传送到所述含金属膜图案化模块;以及

在所述含金属膜图案化模块中,在真空环境中通过EUV曝光直接图案化所述含金属膜以形成所述金属掩模。

[0008] 在下文将参照有关附图更加详细地说明本发明的这些特征和优点以及其它特征和优点。

## 附图说明

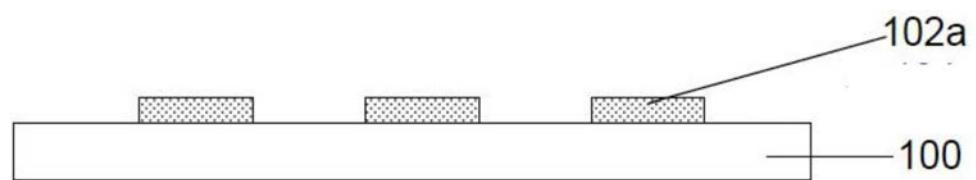

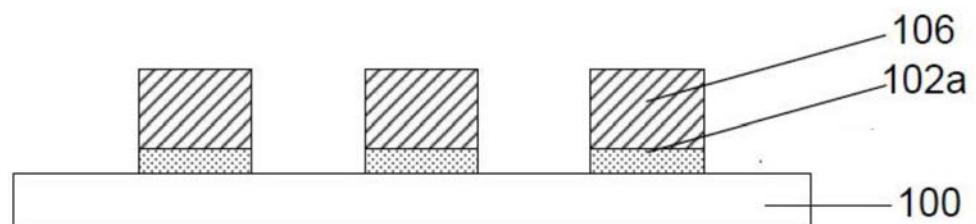

[0009] 图1A-E示出了用于结合真空的无光致抗蚀剂的硬掩模形成工艺的代表性的工艺流程。

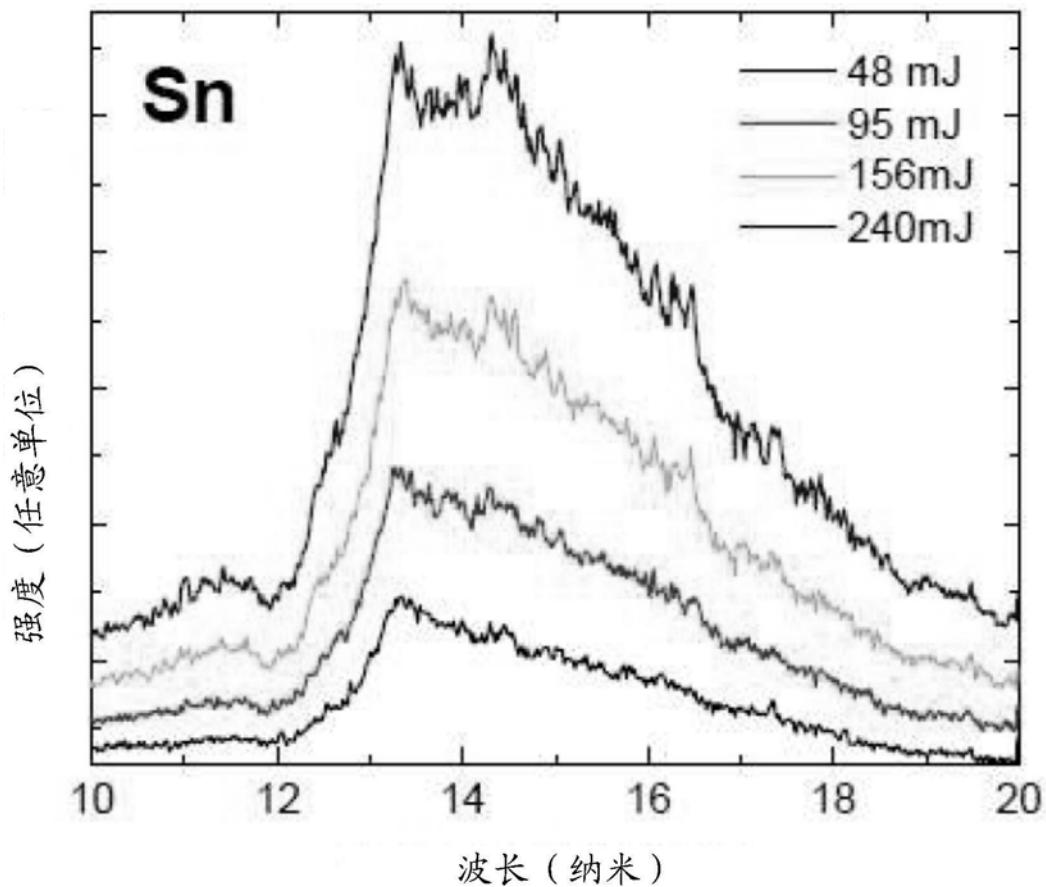

[0010] 图2提供使用激励的Sn液滴的EUV源的发光光谱。

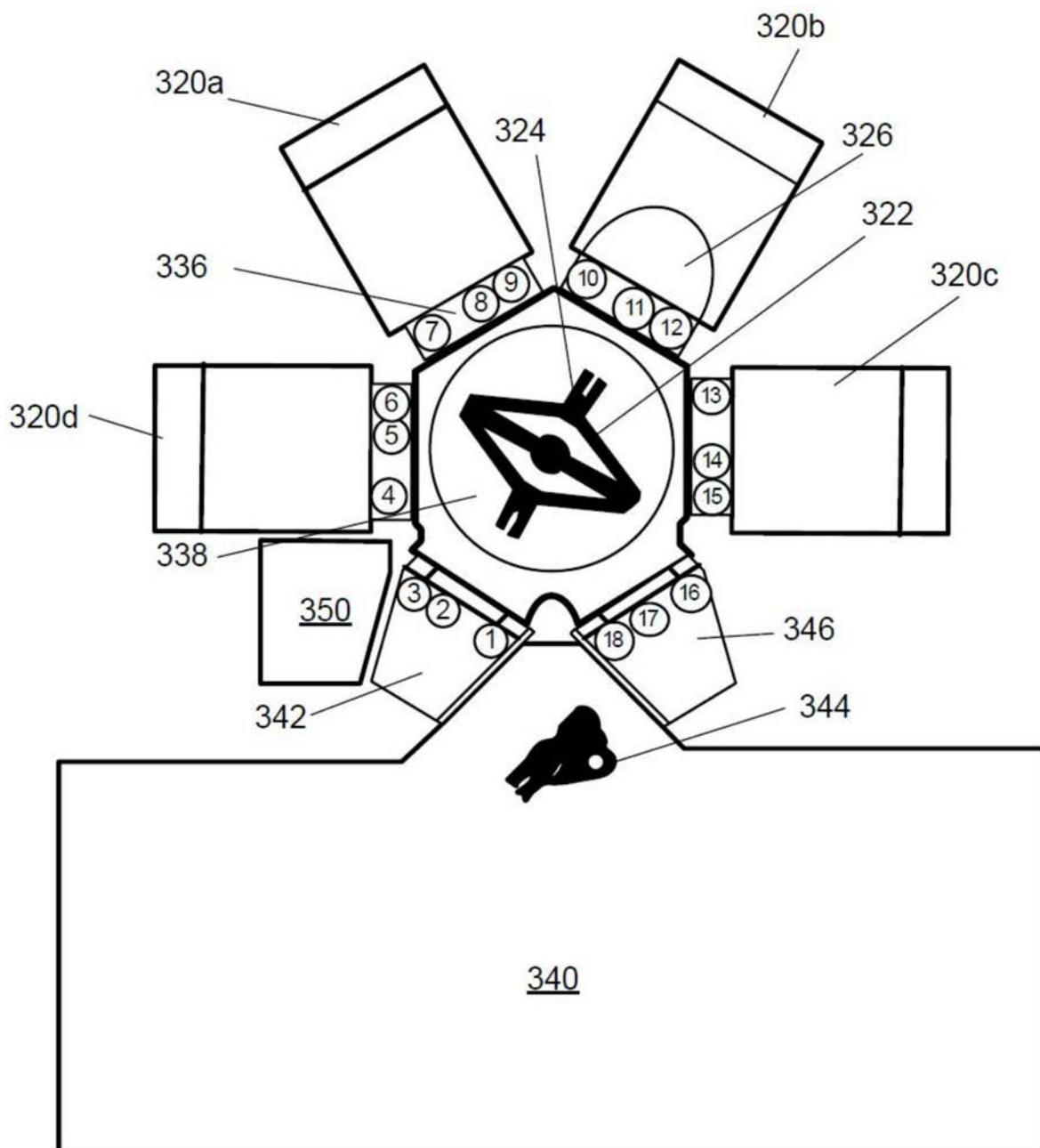

[0011] 图3描绘了半导体工艺集群结构体系,其具有与真空传送模块接口的金属沉积模块和图案化模块,适合于实施本文中所描述的结合真空的工艺。

## 具体实施方式

[0012] 现在将详细地参考本发明的具体实施方式。具体实施方式的实例示于附图中。虽然本发明将结合这些具体实施方式描述,但应当理解,这并不意味着将本发明限制于这些具体实施方式。相反,它旨在覆盖可以被包括在本发明的精神和范围内的替换、修改和等同方案。在以下的描述中,许多具体细节被阐述以便提供本发明的充分理解。本发明可以在没有这些具体细节的一些或全部的情况下实施。在其他实例中,公知的处理操作未被详细描述,以便不会不必要地混淆本发明。

### 介绍

[0013] 极紫外(EUV)光刻技术可通过调节到用目前的光刻方法可达到的较小的成像源的波长从而延伸光刻技术超越它的光学限制以图案化小的关键尺寸的特征。约13.5nm的波长的EUV光源可用于前缘光刻工具,也称为扫描器。极紫外辐射在包括石英和水蒸汽的大范围的固体和流体材料中被强烈吸收,并且在真空下操作也如此。

[0014] EUV光刻通常利用使用常规的光致抗蚀剂工艺图案化的有机硬掩模(例如,PECVD非晶氢化碳可灰化的硬掩模)。在光致抗蚀剂曝光期间,EUV辐射被吸收在抗蚀剂以及下方的衬底中,产生高能光电子(约100电子伏),并进而产生侧向扩散几纳米的低能二次电子(约10电子伏特)。这些电子增加在抗蚀剂中化学反应的程度,从而提高其EUV剂量的灵敏度。然而,性质上是随机的二次电子图案被叠加在光学图像上。这种不必要的二次电子曝光导致分辨率的损失、在图案化的抗蚀剂中可观察到线边缘粗糙度(LER)变化和线宽变化。在随后的图案转印蚀刻过程中这些缺陷被复制到要图案化的材料中。

[0015] 不同于如光致抗蚀剂之类绝缘体,金属不容易受到二次电子曝光效果的影响,因

为二次电子可以通过与传导电子一起散射很快失去能量并热能化。用于这种过程的合适的金属元素可以包括但不限于：铝、银、钯、铂、铑、钌、铱、钴、钌、锰、镍、铜、铪、钽、钨、镓、锗、锡、锑，或它们的任意组合。

[0016] 然而，在用于将覆盖金属膜图案化成掩模的光致抗蚀剂中的电子散射仍会导致不可接受的影响，如LER。

[0017] 公开了结合膜形成(沉积/冷凝)与光学光刻的结合真空的金属硬掩模工艺和相关的结合真空的硬件，导致EUV光刻(EUVL)性能大大改善-例如线边缘粗糙度降低。通过使用含金属的硬掩模膜，并通过使用EUV光子通量直接图案化含金属膜，该工艺完全避免了对光致抗蚀剂的需求。

[0018] 在各种实施方式中，沉积(例如，冷凝)工艺(例如，在如Lam Vector®之类PECVD工具中进行的ALD或MOCVD)可以被用于形成含金属膜薄膜，这种含金属膜如光敏的金属盐或含金属的有机化合物(有机金属化合物)，其在EUV(例如，在10-20纳米的数量级的波长)中，例如在EUV光源(例如，13.5纳米=91.8电子伏特)的波长下，具有强的吸收性。该膜一经EUV曝光就光分解并形成金属掩模，该金属掩模在随后的蚀刻过程中是图案传输层(例如，在导体蚀刻工具中，如Lam 2300®Kiyo®)。

[0019] 含金属膜可在集成有光刻平台(例如，晶片步进机，如荷兰费尔德霍芬的ASML提供TWINSCAN NXE: 3300B®平台)的室中沉积并在真空下传送，以便在曝光之前不发生反应。与光刻工具集成是通过以下事实促进的：考虑到由周围的气体(如H<sub>2</sub>O, O<sub>2</sub>等)对入射光子的强的光吸收，EUVL也需要大大降低的压强。

[0020] 在一些实施方式中，如果因为光学或机械原因需要，则可以在EUV曝光/分解步骤之后进行选择性的膜沉积，以增加掩模材料的厚度；这种工艺被称为图案扩增。在这样的背景下来看，初始的硬掩模然后用作在其上形成最终掩模的种子层，类似于使用用于无电(ELD)或电化学(ECD)沉积的金属籽晶层。

#### 结合真空的无光致抗蚀剂金属硬掩模形成工艺

[0021] 图1A-E示出了用于结合真空的无光致抗蚀剂的硬掩模形成工艺的代表性的工艺流程。通常，对例如光子、电子、质子、离子或中性物质之类图案化剂敏感的含金属膜可通过暴露于这些物质中的一种进行图案化，在半导体衬底上沉积该含金属膜。然后，含金属膜通过在真空环境下暴露于图案化剂而被直接图案化(即，不使用光致抗蚀剂)，从而形成金属掩模。本说明书中主要提及由极紫外光刻(EUV光刻(EUVL)，特别是具有采用激励的锡液滴的EUV源的EUVL)图案化的含金属膜，特别是其中的金属是锡的含金属膜。这样的膜在本文中称为EUV敏感膜。然而，应当理解，其他包括不同的含金属膜和图案化剂/技术的实施方案是可能的。

[0022] 合乎期望的硬掩模金属将是强有力的吸收体并将有相对宽的吸收曲线、高熔点、低延展性/高物理稳定性并容易地沉积。为了本公开的目的，需要注意的是，发射给定能量的光子的材料也将吸收具有该能量的光子。强烈被吸收光将导致所需分解或以其他方式将使膜敏感，以使暴露区可以用热、湿化学过程等去除。图2提供了使用激励的Sn液滴的EUV源的发光光谱。见，R.W.Coon等人，“Comparison of EUV spectral and ion emission features from laser produced Sn and Li plasmas”，Proc.Of SPIE Vol.7636 73636-1(2010)；R.C.Spitzer,等人，“Conversion efficiencies from laser-produced plasmas

in the extreme ultraviolet region”, 79J.Appl.Phys., 2251 (1996); 以及 H.C.Gerritsen 等人, “Laser-generated plasma as soft x-ray source”, J.Appl.Phys. 59 2337 (1986), 在此就其涉及各种金属的发射/吸收特性的公开内容通过引用并入本文。所发射的光子为约 13.5 纳米或 91.8 电子伏特。因此, 锡是用于这种应用的理想的硬掩模金属。

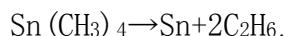

[0023] 参照图 1A, 示出待图案化的半导体衬底 100。在典型的例子中, 半导体衬底 100 是包括部分形成的集成电路的硅晶片。

[0024] 图 1B 示出了含金属膜 102, 其对沉积在半导体衬底 100 上的图案化剂敏感。含金属膜可以是对暴露于图案化剂敏感的金属盐(例如金属卤化物)或有机金属化合物, 使得含金属膜被分解成碱金属或呈现出对随后的显影工艺敏感。合适的图案化剂可以是光子、电子、质子、离子或中性物质, 使得所述含金属膜 102 可通过暴露于这些物质中的一种经由分解成碱金属或呈现对随后的显影工艺敏感而被图案化。如下面进一步说明的, 有效的金属和图案化剂组合的一个具体的实例是通过 EUV 光刻图案化的沉积为金属卤化物(例如,  $\text{SnBr}_4$ )或有机金属(例如,  $\text{Sn}(\text{CH}_3)_4$ )的 Sn。在一般情况下, 在沉积之前, 半导体衬底 100 被放置在反应器室中用于在真空下沉积含金属膜。

[0025] 含金属膜 102 覆盖层可以通过从适当的前体(例如, 在非等离子体 CVD 反应器, 例如可从加州佛利蒙市的朗姆研究公司购得的 Altus® CVD 工具)冷凝来形成。例如, 锡溴化物,  $\text{SnBr}_4$ , 具有 205°C 的标准沸点和在 760 托下的 31°C 的熔点, 在 10°C 蒸气压为 10 托。它可以冷凝到衬底上以形成固态  $\text{SnBr}_4$  膜, 厚度依赖于曝光时间和衬底温度, 例如为约 5 至 200 纳米, 例如 10 纳米。这种经由冷凝的沉积的合适的工艺条件包括介于约 0 和 30°C 之间的沉积温度, 例如约 20°C, 和小于 20 托的反应器压强, 例如在 20°C 下维持 14 和 15 托之间。保持在介于约 100 和 1000 sccm 之间的前体流率使得能控制沉积速率。

[0026] Sn 金属的替代来源可以是有机金属。例如, 四甲基锡( $\text{Sn}(\text{CH}_3)_4$ )具有 75°C 的标准沸点和在 760 托的 -54°C 的熔点。它也可以被冷凝在衬底上, 形成固态的  $(\text{Sn}(\text{CH}_3)_4)$  膜, 厚度依赖于曝光时间和衬底温度, 例如为约 5 至 200 埃, 例如 100 埃。该经由冷凝的沉积的合适的工艺条件包括介于约 -54°C 至 30°C 之间, 例如约 20°C 的沉积温度, 和小于 20 托的反应器压强, 例如维持在约 1 托在 20°C 下。保持在介于约 100 和 1000 sccm 之间的前体流率使得能控制沉积速率。

[0027] 用于形成金属掩模的另一种合适的金属是铪(Hf)。氯化铪,  $\text{HfCl}_4$ (在 190°C 下, 1 托的蒸气压, 具有 432°C 的熔点)可以冷凝到衬底上以形成固态的  $\text{HfCl}_4$  晶体膜, 厚度取决于曝光时间和衬底温度, 例如约 50 至 2000 nm, 例如, 1000 nm。该通过冷凝的沉积的合适的工艺条件包括介于约 0 至 300°C 之间的沉积温度, 例如约 100°C, 以及小于 10 托的反应器压强, 例如保持在 100°C 下介于 0.1 至 1 托之间。保持在介于约 10 和 100 sccm 之间的前体流率使得能控制沉积速率。

[0028] 为了防止由于水蒸气造成的劣化, 在真空环境下进行含 Sn 膜和含 Hf 膜的形成和传送。然后, 所形成的膜传送至 EUV 图案化工具并通过无需使用光致抗蚀剂的直接曝光进行图案化, 如图 1C-D 所示。

[0029] 应当注意的是, EUVL 工具通常相比于沉积工具在更高的真空下操作。如果是这种情况的话, 合乎理想的是提高在从沉积传送到图案化工具的过程中的衬底的环境真空度,

以允许衬底和沉积的含金属膜在进入图案化工具之前脱气。这使得图案化工具的光学器件不受到衬底脱气的污染。

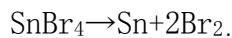

[0030] 参照图1C,对于通过EUVL图案化的金属卤化物Sn系含金属膜,分解化学过程按下式进行:

光子直接分解 $\text{SnBr}_4$ 成Sn(锡金属)和溴气( $\text{Br}_2$ )。可替代地,反应物 $\text{X}_2$ (例如,其中X为Cl、I或H)可用于促进反应途径 $\text{SnBr}_4 + \text{X}_2 \rightarrow \text{SnX}_4 + 2\text{Br}_2$ ,通过光分解最终形成Sn,特别是其中 $\text{SnX}_4$ 比易凝结的 $\text{SnBr}_4$ 较容易光激活。在两种情况下,副产物( $\text{Br}_2$ )和反应物( $\text{X}_2$ )需要控制,如保持真空。

[0031] 对于通过EUVL图案化的有机金属Sn系含金属膜,光子直接分解 $\text{Sn}(\text{CH}_3)_4$ 成Sn(锡金属)和乙烷气体,分解化学过程按下式进行:

[0032] 对于通过EUVL图案化的金属卤化物Hf系含金属膜,分解化学过程按下式进行:

光子直接分解 $\text{HfCl}_4$ 成Hf金属和氯气( $\text{Cl}_2$ )。替代地,反应物 $\text{X}_2$ (例如,其中X为Br、I或H)可以用于促进反应途径 $\text{HfCl}_4 + \text{X}_2 \rightarrow \text{HfX}_4 + 2\text{Cl}_2$ ,通过光分解最终形成Hf,特别是其中 $\text{HfX}_4$ 比易凝结的 $\text{HfCl}_4$ 较容易光激活。在两种情况下,副产物( $\text{Cl}_2$ )和反应物( $\text{X}_2$ )需要密闭度,如真空。

[0033] 如图1C所示,图案化导致金属掩模的暴露的含金属膜区域102a和要通过图案显影去除的材料的未暴露区域102b。

[0034] 参照图1D,该图案随后可显影。图案的显影可通过下述方式而简单地发生:加热衬底以挥发含金属膜的未暴露区域102b,使得仅暴露的区域102a保持为完全成形的金属掩模。应当注意的是,因为将形成热稳定和环境稳定的图案化的金属掩模,所以这种图案显影操作可不需要结合真空。在图案化工具之外进行图案显影也可能合乎期望,以避免用含金属膜分解的任何不相容的副产物污染该工具的光学器件。

[0035] 参照图1E,作为可选的步骤,可以进行图案扩增。例如可以在图1C和/或1D中所描绘的操作之后,在图案化的衬底上执行选择性ALD或无电沉积(ELD),从而用额外的选择性沉积金属106增加该金属掩模的厚度。这可以有用于减少掩模的光传输,或使其机械上更加稳固。例如,通过无电沉积工艺的调整可以完成这样的扩增,例如在美国专利No.6,911,067, No.6,794,288, No.6,902,605和No.4,935,312中所描述的,其公开内容在这方面通过引用并入本文。

[0036] 例如,以这种方式初始1nm的籽晶可以被放大到10nm。如参照图1D所讨论的图案显影,这种操作可以不需要结合真空,因为在扩增之前热稳定和环境稳定的图案化的金属掩模已经形成。

### 替代的工艺实施方式

[0037] 作为金属盐或有机金属含金属膜沉积的替代方案,含金属的EUV敏感膜可以通过有机金属CVD的多步骤工艺用合适的前体(例如,在非等离子体CVD反应器中,诸如可以从加州佛利蒙市的朗姆(Lam)研究公司购得的Altus®CVD工具或PECVD反应器,例如Vector®PECVD工具)沉积。例如,烷基和氨基的前体的等离子体沉积,诸如 $\text{CH}_4/\text{H}_2$ 等离子体沉积后进行氨( $\text{NH}_3/\text{H}_2$ )等离子体沉积,可在半导体衬底上产生氨基丙基三乙氧基硅烷(APTES)的氨基

官能化的自组装单层(SAM)。这样的胺终端表面使得能够保形无电沉积(ELD)。然后SAM可以被输送到EUV图案化工具并被图案化。例如根据在本领域中已知的方法通过ELD,例如通过PdCl<sub>2</sub>/H<sub>2</sub>O溶液曝光,以提供Pd催化剂,随后通过Ni或Co的ELD,然后铜(Cu)的ELD,在给定的参数的情况下,使该图案化的SAM选择性生长,导致金属基掩模形成,而无需使用光致抗蚀剂。为此目的,这样的基于SAM的方法也可用于作为参考图1E描述的ELD技术的替代方案的图案扩增。

[0038] 还应当注意的是,虽然本公开主要引用EUVL用作为图形化技术,但替代的实施方式可以使用电子、离子或中性物质的聚焦束以直接将图案刻写到覆盖掩模上,这些步骤也是在真空中进行的。如果副产物凝结于EUVL系统的反射光学器件,则可以使用原位室清洁。

### 装置

[0039] 图3描绘了具有与真空传送模块接口的结合真空的金属沉积和图案化模块的半导体工艺集群工具结构体系,其适合于执行本文所描述的结合真空的工艺。在多个存储设施中“传送”晶片的传送模块和处理模块的配置可以被称为“集群工具结构”系统。按照特定工艺的要求,金属沉积模块和图案化模块是结合真空的。真空传送模块(VM)338与可以被单独优化以执行各种制造工艺的四个处理模块320a-320d接口。举例而言,处理模块320a-320d可被实施来执行冷凝、沉积、蒸发、ELD、蚀刻,和/或其它半导体工艺。例如,模块320a可以是适于进行如本文所述的含金属膜的沉积的非等离子体CVD反应器,例如可从加州佛利蒙市的朗姆研究公司购得的Altus®CVD工具。模块320b可以是PECVD工具,如Lam Vector®。但是应当理解的是,该图不一定按比例绘制。

[0040] 气锁342和346,也被称为装载锁或传送模块,其与VM 338和图案化模块340接口。例如,合适的图案化模块可以是由荷兰费尔德霍芬的ASML公司提供的TWINSCAN NXE:3300B®平台。这个工具结构体系允许工件(如具有沉积的含金属膜的衬底)在真空下被传输,以便在暴露之前不发生反应。沉积模块与光刻工具集成是通过以下事实促进的:考虑到由周围的气体(如H<sub>2</sub>O,O<sub>2</sub>等)对入射光子的强的光吸收,EUVL也需要大大降低的压强。

[0041] 气锁342可以是“出”装载锁,指的是将衬底从服务于沉积模块620a的VM 338传输出来到达图案化模块340,并且气锁346可以是“进”装载锁,指的是将衬底从图案化模块340传输回进到VM338。进装载锁346也可提供到所述工具的外部的用于衬底进出的接口。每个处理模块具有使模块接口到VM 338的刻面。例如,沉积工艺模块320a具有刻面336。在每个刻面内部,传感器,例如,如图所示传感器1-18,用于当晶片326在各站之间移动时检测晶片326的通过。图案化模块340以及气锁342和346可以被类似地配备有其他刻面和传感器(未示出)。

[0042] 主VM机械手322在包括气锁342和346的模块之间传送晶片326。在一个实施方式中,机械手322具有一个臂,在另一实施方式中,机械手322具有两个臂,每个臂具有端部执行器324以拾取晶片(例如晶片326)用于运输。前端机械手344,用于将晶片326从出气锁342传输到图案化模块340,从图案化模块340传输进入进气锁346。前端机械手344还可以在进装载锁和工具的用于衬底进出的外部之间传输晶片326。因为进气锁模块346具有将大气与真空之间的环境相匹配的能力,所以晶片326能够在不被损坏的情况下在两种压强环境之间移动。

[0043] 应当注意的是,EUVL工具通常比沉积工具在更高的真空下工作。如果是这种情况,

合乎期望的是在从沉积到图案化工具的传输过程中提高衬底的环境真空,以允许在衬底和沉积的含金属膜进入图案化工具之前进行脱气。出气锁342可以通过将传输的晶片保持在不高于图案化模块340中的压强的较低的压强下持续一段时间以及排出任何抽气来提供这个功能,以使图案化工具340的光学元件不受到来自衬底抽气的污染。抽气出气锁的合适的压强不大于1E-8毫。

[0044] 在一些实施方式中,系统控制器350(其可以包括一个或多个物理或逻辑控制器)控制群集工具和/或它的单独的模块的操作的部分或全部。应当注意的是,控制器可以相对于集群结构体系是本地的,或可以位于生产工厂中的集群结构体系的外部,或在远程位置并通过网络连接到集群结构体系。系统控制器350可以包括一个或多个存储器设备和一个或多个处理器。该处理器可以包括中央处理单元(CPU)或计算机、模拟和/或数字输入/输出连接,步进电机控制器板、以及其他类似部件。用于执行适当的控制操作的指令在处理器上执行。这些指令可以存储在与控制器相关联的存储器设备,或者它们可以通过网络提供。在某些实施方式中,系统控制器执行系统控制软件。

[0045] 该系统控制软件可以包括用于控制工具或模块操作的任何方面的数量和/或应用的时序的指令。系统控制软件可以以任何合适的方式进行配置。例如,可以编写各种处理工具组件子程序或控制的对象,以控制进行各种处理工具工艺所需要的处理工具组件的操作。系统控制软件可以以任何合适的计算可读编程语言进行编码。在一些实施方式中,系统控制软件包括用于控制上述的各种参数的输入/输出控制(IOC)的排序指令。例如,半导体制造过程的各阶段可包括用于由系统控制器执行的一个或多个指令。例如,设定用于冷凝、沉积、蒸发、图案化和/或蚀刻阶段的工艺条件的指令可以被包括在相应的配方阶段中。

## 结论

[0046] 本文所述的结合真空的膜沉积和光刻工艺及装置提供EUV敏感金属膜沉积,并随后在真空环境中通过EUV曝光直接图案化,以防止它们的分解或劣化。EUVL是在真空中完成的,以避免入射的13.5nm的光通量因受到环境气体的光吸收而劣化。其中描述结合真空的硬掩模工艺的优点尤其是:EUV系统的真空操作开辟了使用对氧和水分敏感的化合物的可能性;在装置中结合真空的沉积系统与EUV系统使得能够使用这些材料。金属前体的光分解产生非线性反应,其中光分解通过金属膜的增加的吸收而增强。金属在高能量的二次电子的热化方面比光致抗蚀剂好,从而改善对比度或LER。直接使用金属膜作为掩模或用图案扩增允许非常薄的膜,并减少所需的曝光时间。对于蚀刻来说金属膜是较好的硬掩模,并从掩模的角度来说减少了所需的厚度。此外,按照本文中所描述工艺可以继续进行与EUV真空和光学元件相容的材料、具有用于金属沉积的适当剂量阈值的有机金属前体、以及具有多个光分解事件以消除在一定空间中的成核点的成核膜的进一步的发展和优化。

[0047] 应当理解,本文所述的示例和实施方式仅用于说明性的目的,并且根据所述的示例和实施方式的各种修改或变化,将启发本领域的技术人员。虽然为了清楚起见省略了各种细节,但可以实现各种设计替代方案。因此,这些实施例应被认为是说明性的而非限制性的,并且本发明并不限于本文给出的细节,而是可以在所附权利要求的范围内进行修改。

图1A

图1B

图1C

图1D

图1E

图2

图3