(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-208564

(P2012-208564A)

(43) 公開日 平成24年10月25日(2012.10.25)

(51) Int.Cl.

**G06F 1/26 (2006.01)**

**G06F 9/445 (2006.01)**

**H04N 5/225 (2006.01)**

F 1

GO6F 1/00

GO6F 9/06

H04N 5/225

334B

61OK

F

テーマコード (参考)

5B011

5B376

5C122

審査請求 未請求 請求項の数 10 O L (全 14 頁)

(21) 出願番号

(22) 出願日

特願2011-71743 (P2011-71743)

平成23年3月29日 (2011.3.29)

(71) 出願人 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100103056

弁理士 境 正寿

(72) 発明者 橋本 征二

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

F ターム (参考) 5B011 MB11

5B376 AE09 AE38 EA08 EA11 FA01

FA11 GA05

5C122 DA03 DA04 EA52 EA68 GF05

HA60 HA71 HA72 HA76 HB01

HB02 HB09

## (54) 【発明の名称】プログラム処理装置

## (57) 【要約】

【構成】ジャイロセンサ56はデジタルカメラ10の動きを検出する。第1メモリ電源スイッチ52、第2メモリ電源スイッチ54、およびサブCPU44は、ジャイロセンサ56の検知に応答してSDRAM32に電源を供給する。サブCPU44は、メインCPU26によって実行されるプログラムを第1メモリ電源スイッチ52、第2メモリ電源スイッチ54、およびサブCPU44の供給処理に関連してSDRAM32にロードする。主電源スイッチ50およびサブCPU44は、サブCPU44のロード処理の後の電源オン操作に応答してメインCPU26に電源を供給する。

【効果】プログラムが実行可能となるまでの期間短縮および電力浪費の抑制。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

装置の動きを検出する検出手段、

前記検出手段の検知に応答して内部メモリに電源を供給する第1供給手段、

プロセッサによって実行されるプログラムを前記第1供給手段の供給処理に関連して前記内部メモリにロードするロード手段、および

前記ロード手段のロード処理の後の電源オン操作に応答して前記プロセッサに前記電源を供給する第2供給手段を備える、プログラム処理装置。

**【請求項 2】**

前記電源オン操作が実行されることなく前記ロード手段のロード処理から指定期間が経過したとき前記内部メモリへの前記電源の供給を停止する第1メモリ電源停止手段をさらに備える、請求項1記載のプログラム処理装置。 10

**【請求項 3】**

前記検出手段によって検出された動きの発生パターンが1または2以上の既定パターンのいずれかと一致したとき前記第1供給手段の供給処理を制限する第1制限手段をさらに備える、請求項1または2記載のプログラム処理装置。

**【請求項 4】**

電源オフ操作に応答して前記プロセッサへの電源の供給を停止するプロセッサ電源停止手段、および

前記プロセッサ電源停止手段の停止処理から指定期間が経過したとき前記内部メモリへの前記電源の供給を停止する第2メモリ電源停止手段をさらに備える、請求項1ないし3のいずれかに記載のプログラム処理装置。 20

**【請求項 5】**

供給制限操作に応答して前記第1供給手段の供給処理を制限する第2制限手段をさらに備える、請求項1ないし4のいずれかに記載のプログラム処理装置。

**【請求項 6】**

前記内部メモリは揮発性メモリに相当する、請求項1ないし5のいずれかに記載のプログラム処理装置。

**【請求項 7】**

請求項1ないし6のいずれかに記載のプログラム処理装置を備える、電子カメラ。 30

**【請求項 8】**

前記プログラムはファームウェアに相当する、請求項7記載の電子カメラ。

**【請求項 9】**

装置の動きを検出する検出手段を備えるプログラム処理装置の第1プロセッサに、

前記検出手段の検知に応答して内部メモリに電源を供給する第1供給ステップ、

第2プロセッサによって実行されるプログラムを前記第1供給ステップの供給処理に関連して前記内部メモリにロードするロードステップ、および

前記ロードステップのロード処理の後の電源オン操作に応答して前記第2プロセッサに前記電源を供給する第2供給ステップを実行させるための、プログラム処理プログラム。

**【請求項 10】**

装置の動きを検出する検出手段を備えるプログラム処理装置によって実行されるプログラム処理方法であって、

前記検出手段の検知に応答して内部メモリに電源を供給する第1供給ステップ、

プロセッサによって実行されるプログラムを前記第1供給ステップの供給処理に関連して前記内部メモリにロードするロードステップ、および

前記ロードステップのロード処理の後の電源オン操作に応答して前記プロセッサに前記電源を供給する第2供給ステップを備える、プログラム処理方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

10

20

30

40

50

この発明は、プログラム処理装置に関し、特にプロセッサによってプログラムが実行される、プログラム処理装置に関する。

【背景技術】

【0002】

この種の処理装置の一例が、特許文献1に開示されている。この背景技術によれば、電子機器は、非常時稼動部および常時稼動部により構成される。非常時稼動部は、CPU(中央演算処理装置)、プログラム格納メモリ、主記憶装置、動作部および起動時刻指示部を備える。常時稼動部は、タイマ、起動準備指示部および起動時刻メモリを備える。起動準備指示部は、角速度を検知するジャイロセンサ等からなるセンサの出力信号に基づいて、起動準備指示を常時稼動部のリモコン受信部に送信する。リモコン受信部は、起動準備指示部から送信される起動準備指示を受信し、その起動準備指示をCPUに与える。リモコン受信部は、起動準備指示を受信した場合に、CPUに起動準備指示を与える。それにより、非常時稼動部の電源がオンになり、CPUが起動準備を実行する。起動準備には、プログラム格納メモリに格納された圧縮されたプログラムを展開する動作、プログラム格納メモリに格納されたプログラムを主記憶装置に転送する動作およびCPUによりプログラムの一部を実行する動作のうち一部または全部が含まれる。

10

【先行技術文献】

【特許文献】

【0003】

【特許文献1】国際公開第2004/092934号

20

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかし、背景技術では、起動準備指示が与えられたときに非常時稼動部の電源がオンとなるので、CPU等の非常時稼動部の構成要素全てに電力が供給される可能性がある。このため、CPUによるプログラムの実行が可能となるまでの期間を短縮しようとするあまり、非常時稼動部の不要な起動に起因して電力が浪費される恐れがある。

【0005】

それゆえに、この発明の主たる目的は、プログラムが実行可能となるまでの期間を短縮することができるとともに、プログラム処理装置の不要な起動に起因する電力の浪費を抑制することができる、プログラム処理装置を提供することである。

30

【課題を解決するための手段】

【0006】

この発明に従うプログラム処理装置(10:実施例で相当する参照符号。以下同じ)は、装置の動きを検出する検出手段(56)、検出手段の検知に応答して内部メモリ(32)に電源を供給する第1供給手段(52, 54, S17~S19)、プロセッサ(26)によって実行されるプログラムを第1供給手段の供給処理に関連して内部メモリにロードするロード手段(S21~S23)、およびロード手段のロード処理の後の電源オン操作に応答してプロセッサに電源を供給する第2供給手段(50, S41)を備える。

【0007】

好ましくは、電源オン操作が実行されることなくロード手段のロード処理から指定期間が経過したとき内部メモリへの電源の供給を停止する第1メモリ電源停止手段(S31~S33)をさらに備える。

【0008】

好ましくは、検出手段によって検出された動きの発生パターンが1または2以上の既定パターンのいずれかと一致したとき第1供給手段の供給処理を制限する第1制限手段(S7~S11)をさらに備える。

【0009】

好ましくは、電源オフ操作に応答してプロセッサへの電源の供給を停止するプロセッサ電源停止手段(S59)、およびプロセッサ電源停止手段の停止処理から指定期間が経過した

40

50

とき内部メモリへの電源の供給を停止する第2メモリ電源停止手段(S65)をさらに備える。

**【0010】**

好ましくは、供給制限操作に応答して第1供給手段の供給処理を制限する第2制限手段(28b, S13)をさらに備える。

**【0011】**

好ましくは、内部メモリは揮発性メモリに相当する。

**【0012】**

好ましくは、上述のプログラム処理装置は電子カメラに設けられる。

**【0013】**

さらに好ましくは、プログラムはファームウェアに相当する。

**【0014】**

この発明に従うプログラム処理プログラムは、装置の動きを検出する検出手段(56)を備えるプログラム処理装置(10)の第1プロセッサ(44)に、検出手段の検知に応答して内部メモリ(32)に電源を供給する第1供給ステップ(52, 54, S17~S19)、第2プロセッサ(26)によって実行されるプログラムを第1供給ステップの供給処理に関連して内部メモリにロードするロードステップ(S21~S23)、およびロードステップのロード処理の後の電源オン操作に応答して第2プロセッサに電源を供給する第2供給ステップ(50, S41)を実行させるための、プログラム処理プログラムである。

**【0015】**

この発明に従うプログラム処理方法は、装置の動きを検出する検出手段(56)を備えるプログラム処理装置(10)によって実行されるプログラム処理方法であって、検出手段の検知に応答して内部メモリ(32)に電源を供給する第1供給ステップ(52, 54, S17~S19)、プロセッサ(26)によって実行されるプログラムを第1供給ステップの供給処理に関連して内部メモリにロードするロードステップ(S21~S23)、およびロードステップのロード処理の後の電源オン操作に応答してプロセッサに電源を供給する第2供給ステップ(50, S41)を備える。

**【発明の効果】**

**【0016】**

装置の動きが検出されると、内部メモリに電源が供給されるとともに内部メモリにプログラムがロードされる。また、ロードされたプログラムを実行するプロセッサには、ロード処理の後の電源オン操作に応答して電源が供給される。したがって、その後プロセッサによってプログラムが実行される際にプログラムを内部メモリにロードする必要がなく、プログラムが実行可能となるまでの期間を短縮することができる。また、プログラム処理装置の不要な起動に起因する電力の浪費を抑制することができる。

**【0017】**

この発明の上述の目的、その他の目的、特徴および利点は、図面を参照して行う以下の実施例の詳細な説明から一層明らかとなろう。

**【図面の簡単な説明】**

**【0018】**

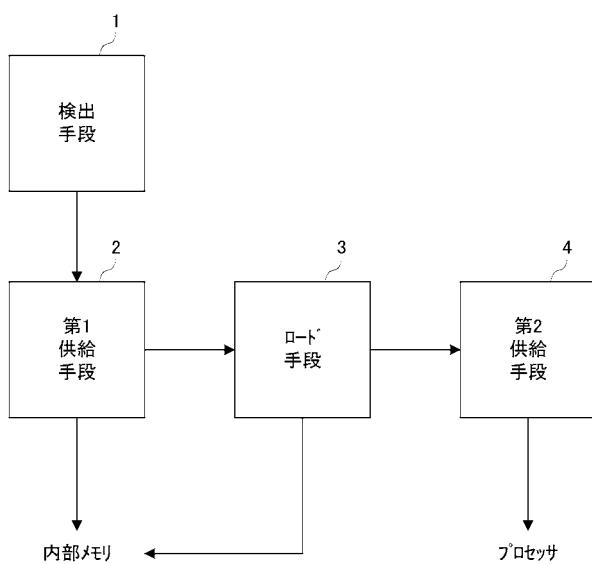

**【図1】**この発明の一実施例の基本的構成を示すブロック図である。

**【図2】**この発明の一実施例の構成を示すブロック図である。

**【図3】**サブCPU44によって参照されるレジスタの構成の一例を示す図解図である。

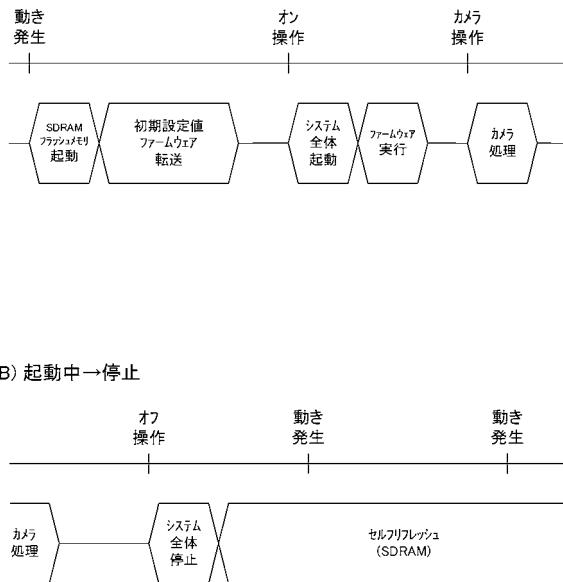

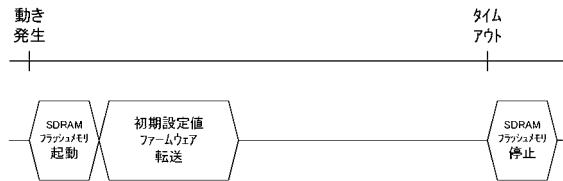

**【図4】**(A)は図2に示した実施例の動作の一部を示すタイミング図であり、(B)は図2に示した実施例の動作の他の一部を示すタイミング図である。

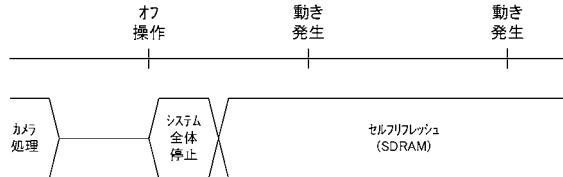

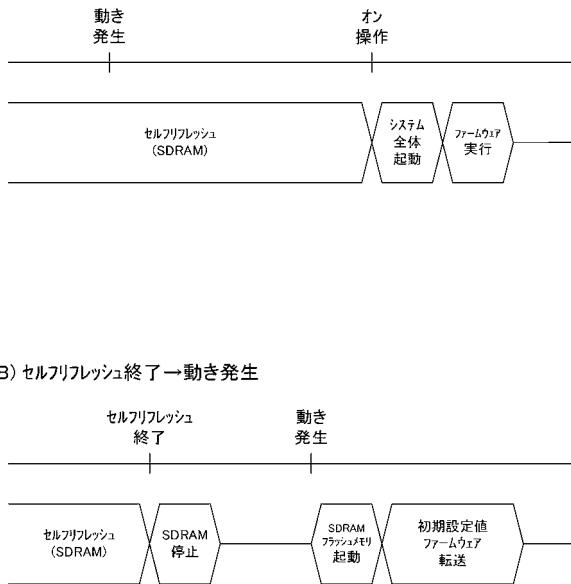

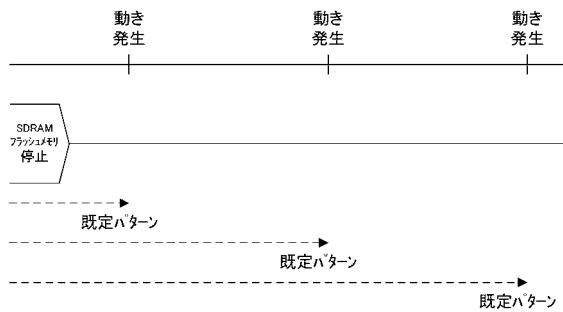

**【図5】**(A)は図2に示した実施例の動作のその他の一部を示すタイミング図であり、(B)は図2に示した実施例の動作のさらにその他の一部を示すタイミング図である。

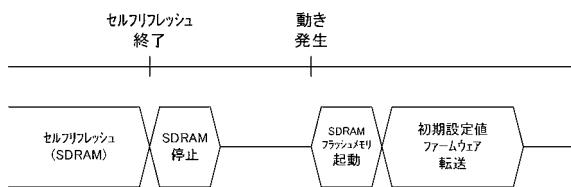

**【図6】**(A)は図2に示した実施例の動作の他の一部を示すタイミング図であり、(B)は図2に示した実施例の動作のその他の一部を示すタイミング図である。

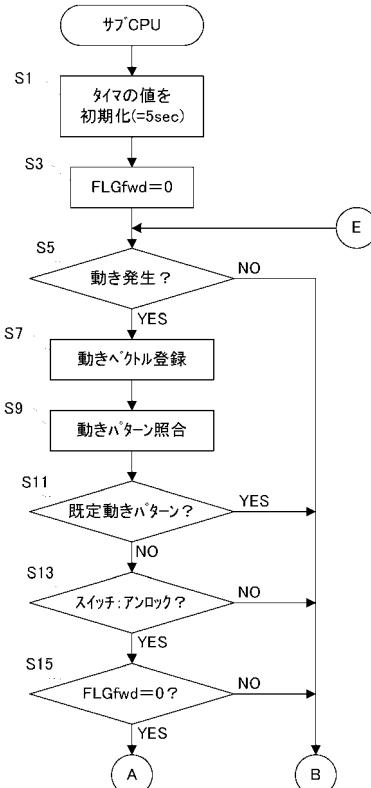

**【図7】**図2に示した実施例に適用されるサブCPUの動作の一部を示すフロー図である

10

20

30

40

50

。

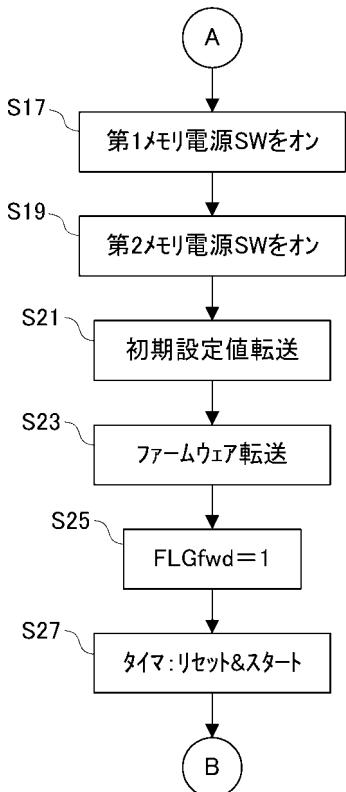

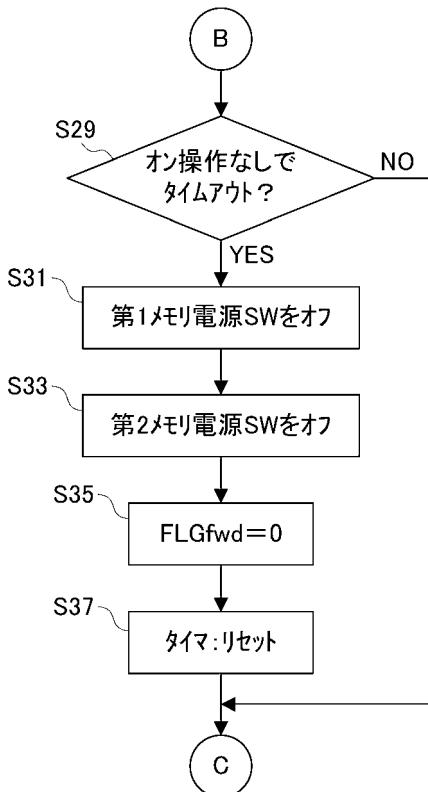

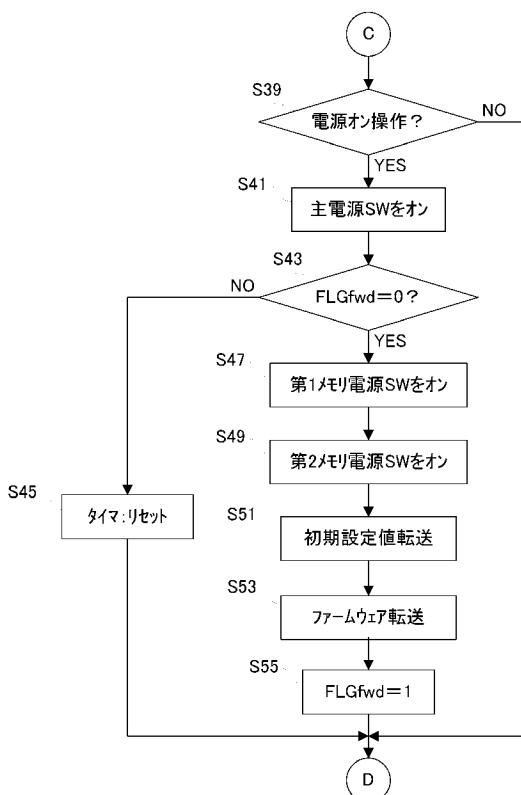

【図 8】図 2 に示した実施例に適用されるサブ C P U の動作の他の一部を示すフロー図である。

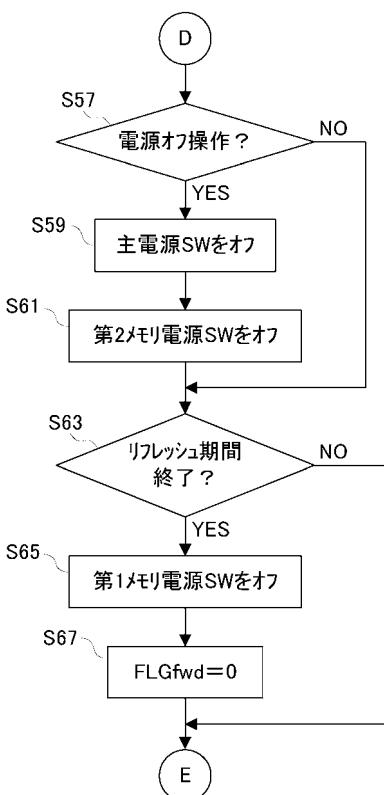

【図 9】図 2 に示した実施例に適用されるサブ C P U の動作のその他の一部を示すフロー図である。

【図 10】図 2 に示した実施例に適用されるサブ C P U の動作のさらにその他の一部を示すフロー図である。

【図 11】図 2 に示した実施例に適用されるサブ C P U の動作の他の一部を示すフロー図である。

【図 12】図 2 に示した実施例に適用される C P U の動作の一部を示すフロー図である。 10

【発明を実施するための形態】

【0 0 1 9】

以下、この発明の実施の形態を図面を参照しながら説明する。

【基本的構成】

【0 0 2 0】

図 1 を参照して、この実施例のプログラム処理装置は、基本的に次のように構成される。検出手段 1 は装置の動きを検出する。第 1 供給手段 2 は、検出手段 1 の検知に応答して内部メモリに電源を供給する。ロード手段 3 は、プロセッサによって実行されるプログラムを第 1 供給手段 2 の供給処理に関連して内部メモリにロードする。第 2 供給手段 4 は、ロード手段 3 のロード処理の後の電源オン操作に応答してプロセッサに電源を供給する。 20

【0 0 2 1】

装置の動きが検出されると、内部メモリに電源が供給されるとともに内部メモリにプログラムがロードされる。また、ロードされたプログラムを実行するプロセッサには、ロード処理の後の電源オン操作に応答して電源が供給される。したがって、その後プロセッサによってプログラムが実行される際にプログラムを内部メモリにロードする必要がなく、プログラムが実行可能となるまでの期間を短縮することができる。また、プログラム処理装置の不要な起動に起因する電力の浪費を抑制することができる。

【実施例】

【0 0 2 2】

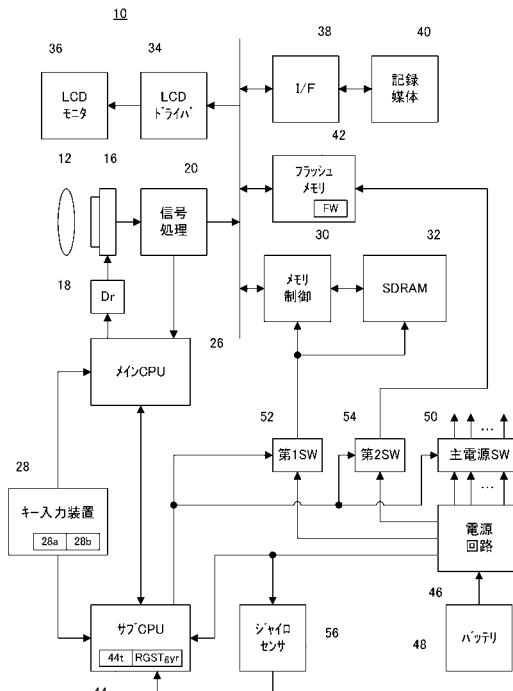

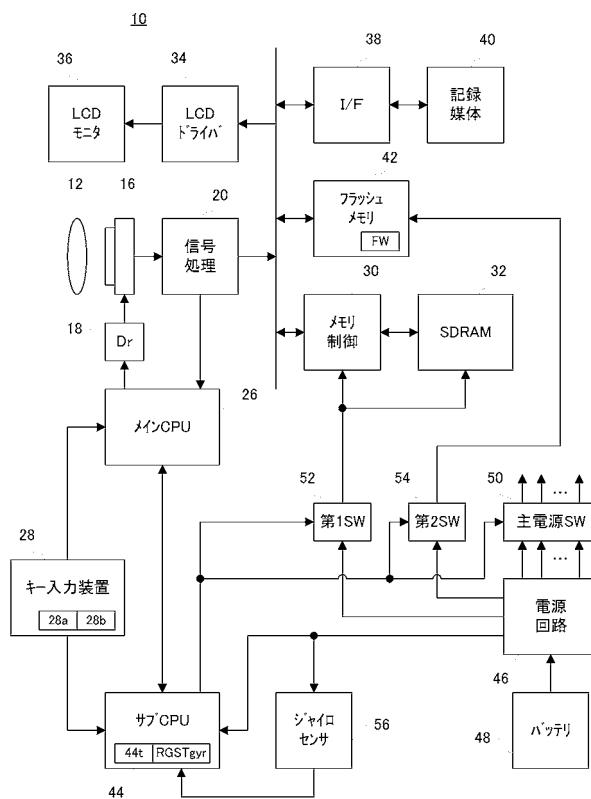

図 2 を参照して、この実施例のディジタルカメラ 1 0 は、電源回路 4 6 を含む。電源回路 4 6 は、互いに異なる電圧値を各々が示す複数の直流電源をバッテリ 4 8 に基づいて生成する。 30

【0 0 2 3】

生成された複数の直流電源の一部はサブ C P U 4 4 およびジャイロセンサ 5 6 に直接的に与えられ、生成された複数の直流電源の他の一部は主電源スイッチ 5 0 , 第 1 メモリ電源スイッチ 5 2 , および第 2 メモリ電源スイッチ 5 4 を介してシステム全体に与えられる。したがって、サブ C P U 4 4 およびジャイロセンサ 5 6 は常時起動されるのに対して、システム全体を構成する要素の起動 / 停止は以下のようによく制御される。システム全体のうち、メモリ制御回路 3 0 および S D R A M 3 2 は第 1 メモリ電源スイッチ 5 2 のオン / オフに応答して起動 / 停止され、フラッシュメモリ 4 2 は第 2 メモリ電源スイッチ 5 4 のオン / オフに応答して起動 / 停止される。システム全体を構成する他の要素は、主電源スイッチ 5 0 のオン / オフに応答して起動 / 停止される。 40

【0 0 2 4】

フラッシュメモリ 4 2 は、ディジタルカメラ 1 0 のファームウェアおよびファームウェアの実行に必要な初期設定値を保持する。

【0 0 2 5】

ジャイロセンサ 5 6 は、ディジタルカメラ 1 0 に動きが発生したか否かを検知し、動きの発生が検知されると検知された動きを表す動きベクトルを出力する。ジャイロセンサ 5 6 から出力された動きベクトルは、サブ C P U 4 4 によって取り込まれ、図 3 に示すレジスタ R G S T g y r に登録される。レジスタ R G S T g y r には複数回の動き発生にそれ 50

それ対応する複数の動きベクトルが保持される。なお、ジャイロセンサ56によって検知される動きには、振動、移動、回転、および回動等が含まれる。

#### 【0026】

デジタルカメラ10の操作者は通常、デジタルカメラ10を手に取って電源オン操作を行う。したがって、ジャイロセンサ56から動きベクトルが出力されたとき、デジタルカメラ10が電源オン操作のために操作者によって動かされたと判断される。このとき、サブCPU44は、第1メモリ電源スイッチ52および第2メモリ電源スイッチ54をそれぞれ制御して、メモリ制御回路30、SDRAM32、およびフラッシュメモリ42を起動する。

#### 【0027】

サブCPU44は次に、デジタルカメラ10のファームウェアおよびファームウェアの実行に必要な初期設定値をフラッシュメモリ42からSDRAM32に転送する（図4（A）参照）。転送が完了するとサブCPU44は、タイマ44tのリセット＆スタートを実行する。タイマ値は例えば5秒とする。

#### 【0028】

タイマ44tにタイムアウトが発生する前にキー入力装置28上の電源ボタン28aによって電源オン操作が行われると、システム全体のうち起動されていなかった残りの要素を、サブCPU44は主電源スイッチ50を制御して起動する。起動されたメインCPU26は、SDRAM32に保持されたファームウェアを実行する。

#### 【0029】

なお、デジタルカメラ10が動かされることなく電源オン操作が行われた場合、動きベクトルがジャイロセンサ56から出力されず、電源オン操作の前に上述の転送処理が実行されない。この場合、SDRAM32およびフラッシュメモリ42を含むシステム全体の起動後に、サブCPU44は、デジタルカメラ10のファームウェアおよびファームウェアの実行に必要な初期設定値をフラッシュメモリ42からSDRAM32に転送する。このようにしてSDRAM32に保持されたファームウェアは、起動されたメインCPU26によって実行される。

#### 【0030】

ファームウェアの実行に従って、メインCPU26においてメインタスクが起動される。起動されたメインタスクの下でメインCPU26は、キー入力装置28に設けられたモード変更ボタン28mdの状態（つまり現時点の動作モード）を判別し、撮像モードに対応して撮像タスクを起動する一方、再生モードに対応して再生タスクを起動する。

#### 【0031】

撮像タスクが起動されるとメインCPU26は、動画取り込み処理のためにドライバ18を起動する。ドライバ18は、周期的に発生する垂直同期信号Vsyncに応答して、撮像面を露光し、撮像面で生成された電荷をラスタ走査様で読み出す。イメージセンサ16からは、被写界を表す生画像データが繰り返し出力される。

#### 【0032】

信号処理回路20は、イメージセンサ16から出力された生画像データに白バランス調整、色分離、YUV変換などの処理を施し、これによって作成されたYUV形式の画像データをメモリ制御回路30を通してSDRAM32に書き込む。LCDドライバ34は、SDRAM32に格納された画像データをメモリ制御回路30を通して読み出し、読み出された画像データに基づいてLCDモニタ36を駆動する。この結果、被写界のリアルタイム動画像（スルー画像）がLCDモニタ36に表示される。

#### 【0033】

シャッターボタン28shが全押しされると、メインCPU26は撮像タスクの下で静止画取り込み処理および記録処理を実行する。静止画取り込み処理によって取り込まれた1フレームの画像データは、記録処理に関連して起動したI/F38によってファイル形式で記録媒体40に記録される。

#### 【0034】

10

20

30

40

50

再生タスクが起動されるとメインCPU26は、再生タスクの下で記録媒体40に記録された最新の画像ファイルを再生画像ファイルとして指定し、指定画像ファイルに注目した再生処理が実行される。この結果、指定画像ファイルの画像データに対応する光学像がLCDモニタ36に表示される。

#### 【0035】

操作者によるキー入力装置28の操作によって、メインCPU26は、後続の画像ファイルまたは先行する画像ファイルを再生画像ファイルとして指定する。指定画像ファイルは上述と同様の再生処理を施され、この結果、LCDモニタ36の表示が更新される。

#### 【0036】

図4(B)を参照して、電源ボタン28aによって電源オフ操作が行われたときは、メインCPU26は実行中のタスクを終了し、SDRAM32にセルフリフレッシュ命令を発行する。SDRAM32は、自らの内部カウンタを用いたリフレッシュの実行を開始する。システム全体のうちメモリ制御回路30およびSDRAM32を除いた一部は、サブCPU44による主電源スイッチ50および第2メモリ電源スイッチ54の制御に従って停止される。

10

#### 【0037】

SDRAM32によるセルフリフレッシュは、既定期間内において繰り返し実行される。既定期間は例えば1時間とする。セルフリフレッシュの実行期間内は、ファームウェアおよびファームウェアの実行に必要な初期設定値がSDRAM32に保持されている。したがって、SDRAM32のセルフリフレッシュの実行期間内にジャイロセンサ56から動きベクトルが出力された場合、サブCPU44は上述の転送処理を実行しない(図4(B)参照)。また、図5(A)を参照して、SDRAM32のセルフリフレッシュの実行期間内に電源ボタン28aによって電源オン操作が行われた場合、上述の転送処理が実行されることなく、システム全体のうち起動されていなかった残りの要素が起動され、メインCPU26においてファームウェアが実行される。

20

#### 【0038】

図5(B)を参照して、SDRAM32によるセルフリフレッシュの実行期間が終了すると、サブCPU44は、第1メモリ電源スイッチ52を制御してメモリ制御回路30およびSDRAM32を停止する。SDRAM32の停止に従って、ファームウェアおよびファームウェアの実行に必要な初期設定値は、SDRAM32から消失する。したがって、SDRAM32のセルフリフレッシュの実行期間終了後にジャイロセンサ56から動きベクトルが出力された場合、上述の通りサブCPU44は、SDRAM32およびフラッシュメモリ42を起動する。サブCPU44は次に、ファームウェアおよびファームウェアの実行に必要な初期設定値をフラッシュメモリ42からSDRAM32に転送し、タイム44tのリセット&スタートを実行する。タイム44tにタイムアウトが発生する前にキー入力装置28上の電源ボタン28aによって電源オン操作が行われると、システム全体のうち起動されていなかった残りの要素が起動され、メインCPU26においてファームウェアが実行される(図4(A)参照)。

30

#### 【0039】

電源ボタン28aによって電源オン操作が行われることなくタイム44tにタイムアウトが発生したとき、ジャイロセンサ56によって検知されたディジタルカメラ10の動きは、電源オン操作のためではないものと判断される。したがって、サブCPU44は、第1メモリ電源スイッチ52および第2メモリ電源スイッチ54をそれぞれ制御してメモリ制御回路30、SDRAM32、およびフラッシュメモリ42を停止する(図6(A)参照)。

40

#### 【0040】

このように、電源オン操作が行われるか否かに関わらず、ディジタルカメラ10の動き発生に従って動きベクトルがジャイロセンサ56から出力される。例えば、ディジタルカメラ10が操作者によって携帯されたとき、乗り物による移動および操作者の歩行等によって繰り返される振動の発生に従って、ジャイロセンサ56は、ディジタルカメラ10の

50

動きを検知する毎に動きベクトルを出力する。このような周期的な振動による動きベクトルの出力パターンは、1または2以上の既定動きパターンとして準備される。

#### 【0041】

レジスタRGSTgyrに動きベクトルが新たに登録されると、サブCPU44は、レジスタRGSTgyrに登録された複数の動きベクトルの発生パターンを1または2以上の既定動きパターンの各々と照合する。この結果、動きベクトルの発生パターンがいずれかの既定動きパターンと一致したとき、サブCPU44は、電源オン操作が行われないものと判断し、上述の転送処理を実行しない(図6(B)参照)。

#### 【0042】

レジスタRGSTgyrには複数回の動き発生にそれぞれ対応する複数の動きベクトルが保持されるが、最新の動きベクトルの登録時から遡ってパターン照合に必要な期間内に登録された1または2以上の動きベクトルが、確保されなければよい。動きベクトルを確保する期間は例えば15秒間とする。

10

#### 【0043】

また、上述の転送処理を制限するためのロックスイッチ28bがキー入力装置28に設けられている。操作者の操作によってロックスイッチ28bの状態がロックまたはアンロックのいずれかに設定される。動きベクトルがジャイロセンサ56から出力されたとき、ロックスイッチ28bがアンロック状態の場合に限り転送処理が実行され、ロックスイッチ28bがロック状態の場合は転送処理が実行されない。なお、ロックスイッチ28bがロック状態の場合、ジャイロセンサ56への電源の供給を停止するようにしてもよい。

20

#### 【0044】

サブCPU44は、図7～図10に示すフロー図に従う処理を実行する。また、メインCPU26は、図11に示すメインタスクを含む複数のタスクを並列的に実行する。なお、メインタスクを含むメインCPU26で実行されるタスクに対応する制御プログラムは、上述のファームウェアとしてフラッシュメモリ42に記憶される。

#### 【0045】

図7を参照して、ステップS1ではタイマ44tの値を“5秒”に初期化し、ステップS3ではフラグFLGfwdに“0”を初期設定する。ジャイロセンサ56による動きベクトルの出力に従って、ステップS5ではデジタルカメラ10に動きが発生したか否かを判別する。判別結果がNOであればステップS29に進む一方、判別結果がYESであればステップS7に進む。

30

#### 【0046】

ステップS7では、ジャイロセンサ56から出力された動きベクトルをレジスタRGSTgyrに登録する。ステップS9では、レジスタRGSTgyrに登録された複数の動きベクトルの発生パターンを1または2以上の既定動きパターンの各々と照合する。

#### 【0047】

ステップS11では、ステップS9の照合処理の結果、動きベクトルの発生パターンがいずれかの既定動きパターンと一致したか否かを判別する。判別結果がYESであれば、電源オン操作が行われないものと判断してステップS29に進む。一方、判別結果がNOであればステップS13に進む。

40

#### 【0048】

ステップS13ではロックスイッチ28bがアンロック状態であるか否かを判別し、判別結果がNOであればステップS29に進む一方、判別結果がYESであればステップS15に進む。ステップS15では、フラグFLGfwdに“0”が設定されているか否かを判別し、判別結果がNOであればステップS29に進む一方、判別結果がYESであればステップS17に進む。

#### 【0049】

ステップS17では第1メモリ電源スイッチ52を制御してメモリ制御回路30およびSDRAM32を起動し、ステップS19では第2メモリ電源スイッチ54を制御してフラッシュメモリ42を起動する。

50

**【0050】**

ステップS21では、デジタルカメラ10のファームウェアの実行に必要な初期設定値をフラッシュメモリ42からSDRAM32に転送する。ステップS23では、デジタルカメラ10のファームウェアをフラッシュメモリ42からSDRAM32に転送する。

**【0051】**

ステップS25ではフラグFLG fwdに“1”を設定し、ステップS27ではタイマ44tのリセット&スタートを実行する。ステップS29では、電源オン操作が行われることなくタイマ44tにタイムアウトが発生したか否かを判別し、判別結果がNOであればステップS39に進む一方、判別結果がYESであればステップS31～ステップS37の処理を経てステップS39に進む。

10

**【0052】**

ステップS31では第1メモリ電源スイッチ52を制御してメモリ制御回路30およびSDRAM32を停止し、ステップS33では第2メモリ電源スイッチ54を制御してフラッシュメモリ42を停止する。ステップS35ではフラグFLG fwdに“0”を設定し、ステップS37ではタイマ44tのリセットを実行する。

20

**【0053】**

ステップS39では電源ボタン28aによって電源オン操作が行われたか否かを判別し、判別結果がNOであればステップS57に進む一方、判別結果がYESであればステップS41で主電源スイッチ50をオンにする。

20

**【0054】**

ステップS43ではフラグFLG fwdに“0”が設定されているか否かを判別し、判別結果がNOであればステップS45の処理を経てステップS57に進む一方、判別結果がYESであればステップS47～ステップS55の処理を経てステップS57に進む。ステップS45ではタイマ44tのリセットを実行する。

30

**【0055】**

ステップS47では第1メモリ電源スイッチ52を制御してメモリ制御回路30およびSDRAM32を起動し、ステップS49では第2メモリ電源スイッチ54を制御してフラッシュメモリ42を起動する。

**【0056】**

ステップS51では、デジタルカメラ10のファームウェアの実行に必要な初期設定値をフラッシュメモリ42からSDRAM32に転送する。ステップS53では、デジタルカメラ10のファームウェアをフラッシュメモリ42からSDRAM32に転送する。ステップS55ではフラグFLG fwdに“1”を設定する。

30

**【0057】**

ステップS57では電源ボタン28aによって電源オフ操作が行われたか否かを判別し、判別結果がNOであればステップS63に進む一方、判別結果がYESであればステップS59～ステップS61の処理を経てステップS63に進む。

**【0058】**

ステップS59およびステップS61では主電源スイッチ50および第2メモリ電源スイッチ54をそれぞれ制御して、システム全体のうちメモリ制御回路30およびSDRAM32を除いた一部を停止する。SDRAM32は、自らの内部カウンタを用いたリフレッシュの実行を開始する。

40

**【0059】**

ステップS63ではSDRAM32のセルフリフレッシュの実行期間が終了したか否かを判別し、判別結果がNOであればステップS5に戻る一方、判別結果がYESであればステップS65～ステップS67の処理を経てステップS5に戻る。ステップS65では第1メモリ電源スイッチ52を制御してメモリ制御回路30およびSDRAM32を停止し、ステップS67ではフラグFLG fwdに“0”を設定する。

**【0060】**

50

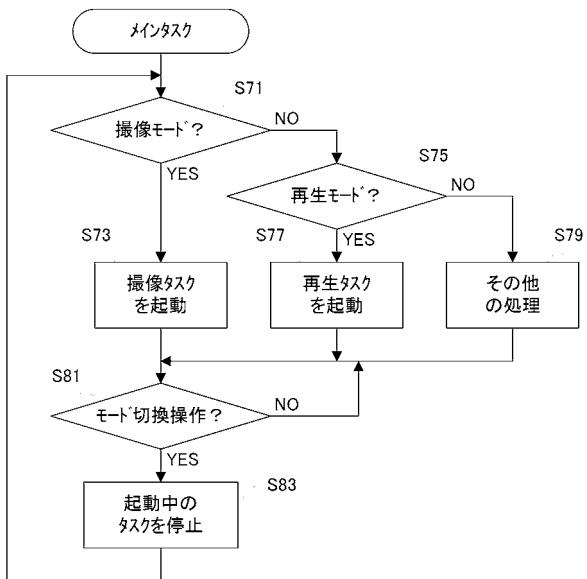

図12を参照して、ステップS71では現時点の動作モードが撮像モードであるか否かを判別し、ステップS75では現時点の動作モードが再生モードであるか否かを判別する。ステップS71の判別結果がYESであれば、ステップS73で撮像タスクを起動する。ステップS75の判別結果がYESであれば、ステップS77で再生タスクを起動する。ステップS71の判別結果およびステップS75の判別結果のいずれもがNOであれば、ステップS79でその他の処理を実行する。

#### 【0061】

ステップS73、ステップS77、またはステップS79の処理が完了すると、モード変更ボタン28mdが操作されたか否かをステップS81で繰り返し判別する。判別結果がNOからYESに更新されると、起動中のタスクをステップS83で停止し、その後にステップS71に戻る。10

#### 【0062】

以上の説明から分かるように、ジャイロセンサ56はデジタルカメラ10の動きを検出する。第1メモリ電源スイッチ52、第2メモリ電源スイッチ54、およびサブCPU44は、ジャイロセンサ56の検知に応答してSDRAM32に電源を供給する。サブCPU44は、メインCPU26によって実行されるプログラムを第1メモリ電源スイッチ52、第2メモリ電源スイッチ54、およびサブCPU44の供給処理に関連してSDRAM32にロードする。主電源スイッチ50およびサブCPU44は、サブCPU44のロード処理の後の電源オン操作に応答してメインCPU26に電源を供給する。20

#### 【0063】

動きが検出されると、内部メモリに電源が供給されるとともに内部メモリにプログラムがロードされる。また、ロードされたプログラムを実行するプロセッサには、ロード処理の後の電源オン操作に応答して電源が供給される。したがって、その後プロセッサによってプログラムが実行される際にプログラムを内部メモリにロードする必要がなく、プログラムが実行可能となるまでの期間を短縮することができる。また、プログラム処理装置の不要な起動に起因する電力の浪費を抑制することができる。

#### 【0064】

なお、この実施例では、デジタルカメラ10のファームウェア等をフラッシュメモリ42からSDRAM32に転送するようにした。しかし、デジタルカメラ10のファームウェア等が記録媒体40に保持されるようにし、記録媒体40からSDRAM32に転送するようにしてもよい。30

#### 【0065】

また、この実施例では、電源オン操作が行われることなくタイマ44tにタイムアウトが発生したとき、SDRAM32およびフラッシュメモリ42を停止するようにした。しかし、フラッシュメモリ42の停止は、ファームウェア等の転送処理の完了後直ちに実行するようにしてもよい。

#### 【0066】

また、この実施例では、デジタルスチルカメラを用いて説明したが、本発明は、デジタルビデオカメラ、パーソナルコンピュータ、携帯電話端末、スマートフォン、またはデジタルオーディオプレーヤーなどの揮発性メモリが用いられる他の機器にも適用することができる。40

#### 【符号の説明】

#### 【0067】

- 10 ... デジタルカメラ

- 26 ... メインCPU

- 32 ... SDRAM

- 44 ... サブCPU

- 50 ... 主電源スイッチ

- 52 ... 第1メモリ電源スイッチ

- 54 ... 第2メモリ電源スイッチ

10

20

30

40

50

5 6 ... ジャイロセンサ

【 四 1 】

【 図 2 】

【図3】

RGSTgyr

| 1 | 2 | 3 | 4 | 5 | ... |

|---|---|---|---|---|-----|

|   |   |   |   |   |     |

【図4】

(A) 停止→起動

(B) 起動中→停止

【図5】

(A) 停止→起動(セルフリフレッシュ期間内)

(B) セルフリフレッシュ終了→動き発生

【図6】

(A) 動き発生→操作なし

(B) 既定動きパターン

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図12】