Office de la Propriété Intellectuelle du Canada

\*

Canadian Intellectual Property Office

CA 2903860 C 2018/04/03

(11)(21) 2 903 860

(12) BREVET CANADIEN CANADIAN PATENT

(13) **C**

- (86) Date de dépôt PCT/PCT Filing Date: 2014/03/17

- (87) Date publication PCT/PCT Publication Date: 2014/09/18

- (45) Date de délivrance/Issue Date: 2018/04/03

- (85) Entrée phase nationale/National Entry: 2015/09/02

- (86) N° demande PCT/PCT Application No.: US 2014/030890

- (87) N° publication PCT/PCT Publication No.: 2014/146019

- (30) Priorité/Priority: 2013/03/15 (US61/788,926)

- (51) Cl.Int./Int.Cl. *H03M 1/12* (2006.01), *A61N 1/36* (2006.01), *A61N 1/372* (2006.01), *H03M 1/46* (2006.01)

- (72) Inventeur/Inventor: LEE, EDWARD K. F., US

- (73) Propriétaire/Owner: ALFRED E. MANN FOUNDATION FOR SCIENTIFIC RESEARCH, US

- (74) Agent: SMART & BIGGAR

(54) Titre: CONVERTISSEUR ANALOGIQUE-NUMERIQUE PAR APPROXIMATIONS SUCCESSIVES AVEC SURVEILLANCE HAUTE TENSION

(54) Title: HIGH VOLTAGE MONITORING SUCCESSIVE APPROXIMATION ANALOG TO DIGITAL CONVERTER

#### (57) Abrégé/Abstract:

A successive approximation ADC made of a low voltage configurable differential amplifier and low voltage logic circuits which can convert a high voltage analog input to a digital equivalent. The differential amplifier can be configured as either an op amp or a

CA 2903860 C 2018/04/03

(11)(21) 2 903 860

(13) **C**

#### (57) Abrégé(suite)/Abstract(continued):

comparator depending upon the mode of operation. An input capacitor C1 is switchably coupled to an electrode selected for voltage sampling. A switched capacitor array C2 is coupled across the differential amplifier input and output. A SAR coupled to the switched capacitor array provides a digital output corresponding to the sampled analog voltage. During a sampling interval and a charge transfer interval, the differential amplifier is configured as an op amp. During the transfer interval, the voltage on the input capacitor multiplied by the ratio C1/C2 is transferred to the switched capacitor array. During an analog to digital conversion interval, the ADC converts the analog voltage to an equivalent digital output.

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

## (10) International Publication Number WO 2014/146019 A3

(51) International Patent Classification:

**H03M 1/12** (2006.01) **A61N 1/372** (2006.01) **A61N 1/36** (2006.01) **H03M 1/46** (2006.01)

(21) International Application Number:

PCT/US2014/030890

(22) International Filing Date:

17 March 2014 (17.03.2014)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/788,926 15 March 2013 (15.03.2013)

US

- (71) Applicant: ALFRED E. MANN FOUNDATION FOR SCIENTIFIC RESEARCH [US/US]; P. O. Box 905, Santa Clarita, California 91380 (US).

- (72) Inventor: LEE, Edward K. F.; 1819 Catlin Street, Fullerton, California 92833 (US).

- (74) Agent: CHRISTIANSEN, Richard B.; Kilpatrick Townsend & Stockton LLP, Two Embarcadero Center, Eighth Floor, San Francisco, California 94111 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY,

BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Published**:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

- (88) Date of publication of the international search report:

5 March 2015

#### (54) Title: HIGH VOLTAGE MONITORING SUCCESSIVE APPROXIMATION ANALOG TO DIGITAL CONVERTER

FIG. 1

(57) Abstract: A successive approximation ADC made of a low voltage configurable differential amplifier and low voltage logic circuits which can convert a high voltage analog input to a digital equivalent. The differential amplifier can be configured as either an op amp or a comparator depending upon the mode of operation. An input capacitor C1 is switchably coupled to an electrode selected for voltage sampling. A switched capacitor array C2 is coupled across the differential amplifier input and output. A SAR coupled to the switched capacitor array provides a digital output corresponding to the sampled analog voltage. During a sampling interval and a charge transfer interval, the differential amplifier is configured as an op amp. During the transfer interval, the voltage on the input capacitor multiplied by the ratio C1/C2 is transferred to the switched capacitor array. During an analog to digital conversion interval, the ADC converts the analog voltage to an equivalent digital output.

# HIGH VOLTAGE MONITORING SUCCESSIVE APPROXIMATION ANALOG TO DIGITAL CONVERTER

This application claims the benefit of U.S. Provisional Application No. 61/788,926, filed on March 15, 2013.

### Field of the Invention

The present invention relates to a successive approximation analog to digital converter capable of a broad range of uses and in particular to high voltage stimulation electrode monitoring especially in functional electrical stimulation (FES) applications.

## Background of the Invention

Typically in FES applications, current pulses generated in a programmable current generator are applied to nerve tissue for stimulating the tissue through a plurality of selectable electrodes. For many applications, due to the required current pulse amplitudes and the impedance of the stimulated tissue and of the electrodes, a high compliance voltage is required for the stimulators. Compliance voltage is the voltage available at an electrode that can be used to force current to flow through the electrode and still maintain control of the electrode voltage.

In many applications measurements of the electrode voltages are necessary for maintaining the operational integrity of the stimulator circuits. Such samples would be required for example in the measurements and determination of tissue and electrode impedances as well as detecting the existence or absence of shorts or open circuits involving the electrodes. To accommodate digital processing circuitry typically utilized in biomedical devices, digitizing the analog signals normally sensed by the electrodes is often required. However, analog-to-digital converters (ADCs) are often designed using low voltage transistors for minimizing die area as well as power consumption. As a result, the

high electrode voltages cannot be digitized directly. Attenuation of the electrode voltage to the input voltage range of the ADC is required.

A common technique to achieve attenuation is to use resistor voltage dividers to divide the high electrode voltage to a lower voltage. However, this technique is not suitable for an FES application since it will draw out current from the stimulator and hence, affecting the stimulation pulse amplitude as well as the output impedance of the stimulator. To alleviate these problems, a voltage buffer between the stimulator and the voltage divider can be added [See Lee, E., "High Voltage Tolerant Stimulation Monitoring Circuit in Conventional CMOS Process", Proc. Of the IEEE 2009 Int. Custom Integrated Circuits Conference (CICC), pp. 93-96, Sept. 2009]. However, such a voltage buffer is difficult to design due to the requirement for a high-voltage rail-to-rail operational amplifier (op amp).

Another possible technique is to use two switched-capacitors (SCs) as two separate resistors to form a voltage divider. In this way, no DC current is drawn out from the stimulator. However, the charge injection of the switches and the nonlinear parasitic capacitances at connection node of the two SCs will affect the accuracy of the attenuation gain as well as the linearity of the divider. Furthermore, an ADC usually has considerable input capacitance. When the ADC input is connected to the SC divider, it will affect the actual attenuation factor of the attenuator. Therefore, instead of using a simple SC voltage divider, a SC amplifier with a voltage gain equal to the required attenuation factor is typically used [See Lee, E., Dai, R., Reeves, N., and Yun, X., "A 36V Biphasic Stimulator with Electrode Monitoring Circuit", Proc. of the 2012 IEEE Int.

Symposium on Circuits and Systems, pp1087-1090, May 2012]. The SC amplifier is not only used for driving the ADC but can also be used for eliminating the parasitic capacitance effects and possibly the charge injection effects. However, this design requires additional power to power the SC amplifier.

Among different ADC architectures, successive approximation ADCs using a SC array digital to analog converter is a popular architecture for biomedical applications since it requires low power consumption for the sampling rate required in most biomedical devices. Based on this type of ADC, one can

combine the attenuation function into the ADC. An additional switched-capacitor can be added in series with the SC array at the input of the original ADC architecture [Thomas Paul Kearney, "Programmable Input Range SAR ADC", U. S. Patent No. 6,731, 232]. By properly controlling the clock phases, attenuation can be achieved. Since now the input capacitance of the ADC (capacitance of the SC array) becomes part of the attenuator, no buffer or SC amplifier is required to drive the ADC input. However, the accuracy of the attenuation factor is still affected due to the nonlinear parasitic capacitances and charge injections of the switches. In some instances, what is needed therefore may be a new and novel successive approximation ADC architecture to remedy the deficiencies existing in the art as discussed above.

## **Summary of the Invention**

One non-limiting embodiment of the present invention includes a differential amplifier configurable as either an op amp or a comparator depending upon the particular mode of operation of the ADC. An input capacitor having a capacitance value of C1 is switchably coupled to an electrode selected for voltage sampling and a second input (negative input) of the differential amplifier. A reference voltage is applied to a first input (positive input) of the differential amplifier. A switched capacitor array having a total capacitance value of C2 is coupled across the second input and the differential amplifier output. The switched capacitor array may be a binary weighted array used for ADC purposes. A successive approximation register is coupled to the switched capacitor array and the differential amplifier output and provides a digital output corresponding to the sampled electrode analog voltage.

In some instances during a sampling interval, the input capacitor is charged to the sampled electrode analog voltage. Concurrently, the differential amplifier is configured as an op amp such that a virtual ground is established at the second input which provides for a path for charging the input capacitor up to the sampled electrode analog voltage.

In some instances during a transfer interval, the voltage on the input capacitor multiplied by the ratio C1/C2 is transferred to the switched capacitor array while the differential amplifier is maintained as being configured as an op amp.

In some instances during an analog to digital conversion interval, the differential amplifier is configured as a comparator and the switched capacitor array, the successive approximation register and the comparator undertake the conversion of the electrode analog voltage to an equivalent digital output.

In one embodiment the present disclosure relates to a peripherally-implantable neurostimulation system. The peripherally implantable neurostimulation system can include a plurality of leads that can each include at least one electrode, an analog-to-digital converter that can include, for example, a successive approximation analog-to-digital converter and an integral switched capacitor amplifier. In some embodiments, the successive approximation analog-to-digital converter and the integral switched capacitor amplifier can share a common differential amplifier. In some embodiments, the system includes a pulse generator that can generate one or several electrical pulses. In some embodiments, the pulse generator is connected to the leads such that the electrical pulses are transmitted to the at least one electrode.

In some embodiments, the peripherally-implantable neurostimulation system can include a successive approximation register. In some embodiments of the peripherally-implantable neurostimulation system, the successive approximation register can include a logic signal generator, which logic signal generator can generate a first signal directing the differential amplifier to operate as an opamp during a first period, and a second signal directing the differential amplifier to operate as a comparator during a second period. In some embodiments, the peripherally-implantable neurostimulation system can include an input capacitor between the leads and the analog-to-digital converter, which input capacitor can be charged during the first period. In some embodiments, the input capacitor can be discharged during the first period and subsequent to the

charging of the input capacitor, and the charge the can be transferred to a switched capacitor array.

In one embodiments, the present disclosure relates to an implantable electrical stimulation system. The implantable electrical stimulation system can include a pulse generator that can generate one or several electrical pulses, an electrode array that can output the one or several electrical pulses, an analog-to-digital converter that can convert an analog signal associated with at least one of the electrodes of the electrode array to a digital signal, and that can include a reconfigurable differential amplifier, and a controller that can reconfigure the differential amplifier between an operational amplifier mode and a comparator mode.

In some embodiments of the implantable electrical stimulation system, the analog-to-digital converter can include a successive approximation analog-to-digital converter and a switched capacitor amplifier that share a common differential amplifier. In some embodiments, the implantable electrical stimulation system can include a successive approximation register.

In some embodiments of the implantable electrical stimulation system, the controller can generate a first signal directing the reconfigurable differential amplifier to operate as an opamp during a first period, and a second signal directing the differential amplifier to operate as a comparator during a second period. In some embodiments, the implantable electrical stimulation system can include an input capacitor connecting the leads and the analog-to-digital converter, which input capacitor can be charged during the first period. In some embodiments, the input capacitor is discharged during the first period and subsequent to the charging of the input capacitor, and the charge can be transferred to a switched capacitor array.

In one embodiment, the present disclosure relates to a method of treating neuropathic pain. The method of treating neuropathic pain can include delivering at least one electrical pulse to a body tissue proximate or at a nerve by an implanted pulse generator and at least one electrode, sensing an analog attribute of the at least one electrical pulse using a differential amplifier

10

15

20

25

configured in an operational amplifier mode, and converting the sensed analog attribute to a digital signal using the differential amplifier configured in a comparator mode.

In some embodiments of the method of treating neuropathic pain, delivering the at least one electrical pulse can include delivering at least one electrical pulse to a peripheral body tissue proximate to or at a peripheral nerve. In some embodiments, the electrical pulse can have a first property, which first property can indicate the presence or absence of a short or open circuit and/or the voltage of the at least one electrode. In some embodiments, the method of treating neuropathic pain can include delivering a second electrical pulse having a second property. In some embodiments, the second property of the second electrical pulse can be based on the first property of the electrical pulse and the digital signal.

According to one aspect of the present invention, there is provided an analog to digital converter (ADC) comprising: a switched capacitor array, wherein the capacitor array has a total capacitance value of C2; a differential amplifier selectably configurable as either an operational amplifier or a comparator, said differential amplifier having first and second inputs and an output, wherein the first input is coupled to a reference voltage and wherein the switched capacitor array is coupled across the second input and the output of the differential amplifier; an input capacitor switchably coupled between the differential amplifier second input and an analog voltage source adapted to provide an analog voltage signal to be converted to a digital output signal, said input capacitor having a capacitance value of C1; a successive approximation register coupled to the switched capacitor array and the differential amplifier output and configured to provide the digital output signal; and a logic signal generator configured to provide timing control logic signals arranged to: (a) charge the input capacitor to the value of the analog voltage signal and configure the differential amplifier as an operational amplifier during a sampling interval such that a virtual ground is established at the differential amplifier second input for facilitating charge transfer from the input capacitor to the switched capacitor array; (b) 10

15

20

25

transfer the analog voltage signal on the input capacitor multiplied by the ratio C1/C2 to the capacitor array during a transfer interval; and (c) configure the differential amplifier as a comparator for comparing the reference voltage to the voltage on the switched capacitor array, wherein the capacitors in the switched capacitor array are switched for converting the voltage on the capacitor array to digital output bits for storage in the successive approximation register according to the comparator output in a successive approximation protocol during an analog to digital conversion interval to thereby provide the digital output signal.

According to another aspect of the present invention, there is provided a method of converting an analog signal to a digital equivalent signal utilizing an analog to digital converter, said converter comprising: a differential amplifier configurable as either an op amp or a comparator, said differential amplifier having first and second inputs and an output, wherein a reference voltage is coupled to the first input; a capacitor array coupled across the second input and the output, said capacitor array having a total capacitance value of C2; an input capacitor switchably coupled between a source of analog signals and the second input, said input capacitor having a capacitance value of C1; a successive approximation register coupled to the switched capacitor array and the differential amplifier output; and a logic signal generator configured to provide timing control logic signals to: define a sampling interval, define a transfer interval and define an analog to digital conversion interval respectively, the method comprising: sampling the analog signal onto the input capacitor during the sampling interval wherein the differential amplifier is configured as an op amp; transferring the sampled signal on the input capacitor multiplied by the ratio C1/C2 during the transfer interval to the switched capacitor array, wherein the differential amplifier is configured as an op amp; and configuring the differential amplifier as a comparator and converting the voltage on the capacitor array to digital output bits for storage in the successive approximation register according to the comparator output in a successive approximation protocol during an analog to digital conversion interval to thereby provide the digital equivalent signal.

According to still another aspect of the present invention, there is provided an implantable neurostimulation system comprising: a plurality of leads, wherein each of the plurality of leads comprises at least one electrode; an analog-to-digital converter comprising a successive approximation analog-to-digital converter and an integral switched capacitor amplifier, wherein the successive approximation analog-to-digital converter and the integral switched capacitor amplifier share a common differential amplifier; and a pulse generator configured to generate one or several electrical pulses, wherein the pulse generator is connected to the leads such that the electrical pulses are transmitted to the at least one electrode.

According to yet another aspect of the present invention, there is provided an implantable electrical stimulation system comprising: a pulse generator configured to generate one or several electrical pulses; an electrode array configured to output the one or several electrical pulses; an analog-to-digital converter configured to convert an analog signal associated with at least one of the electrodes of the electrode array to a digital signal, the analog-to-digital converter including a reconfigurable differential amplifier; and a controller configured to reconfigure the differential amplifier between an operational amplifier mode and a comparator mode.

## **Brief Description of the Drawings**

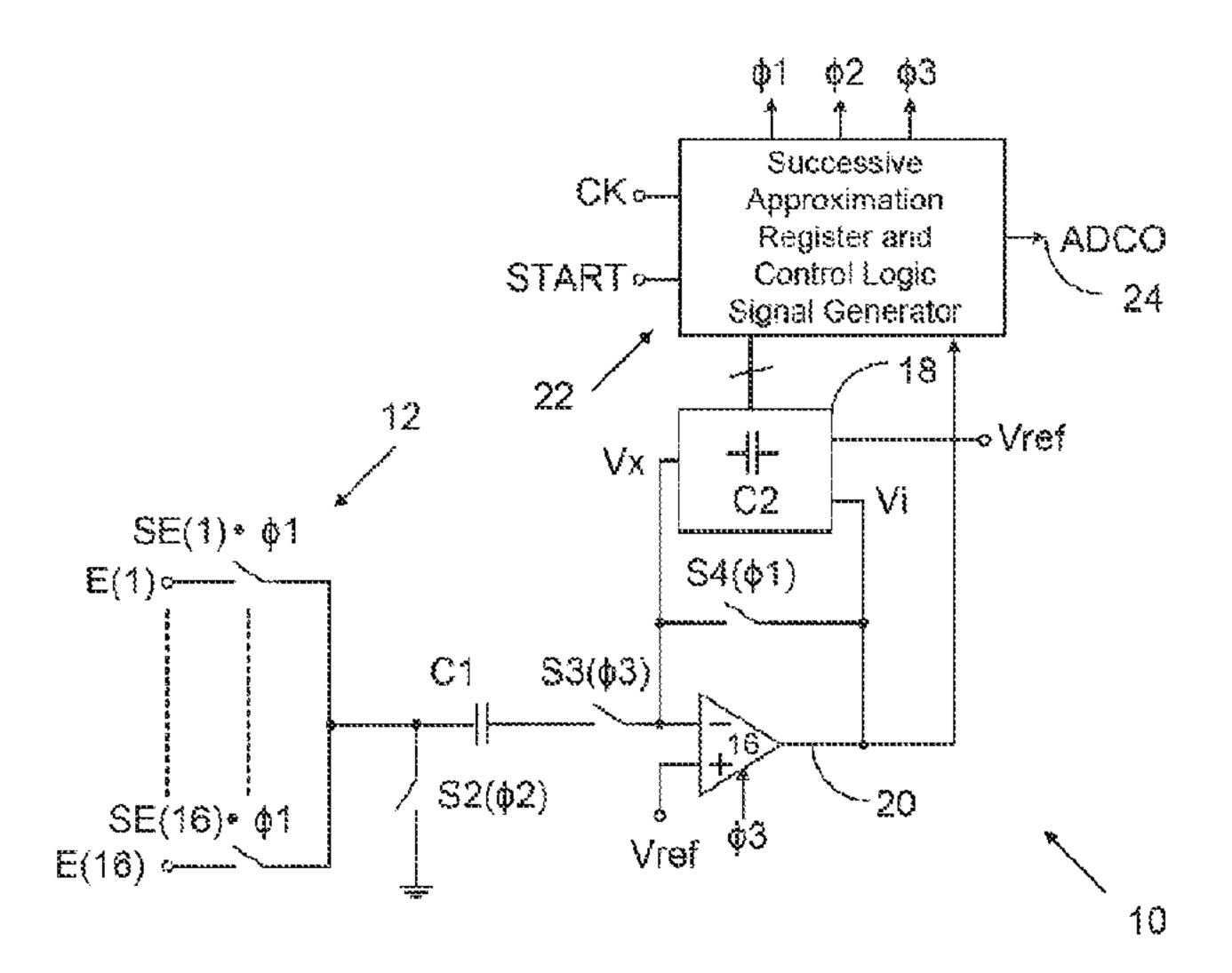

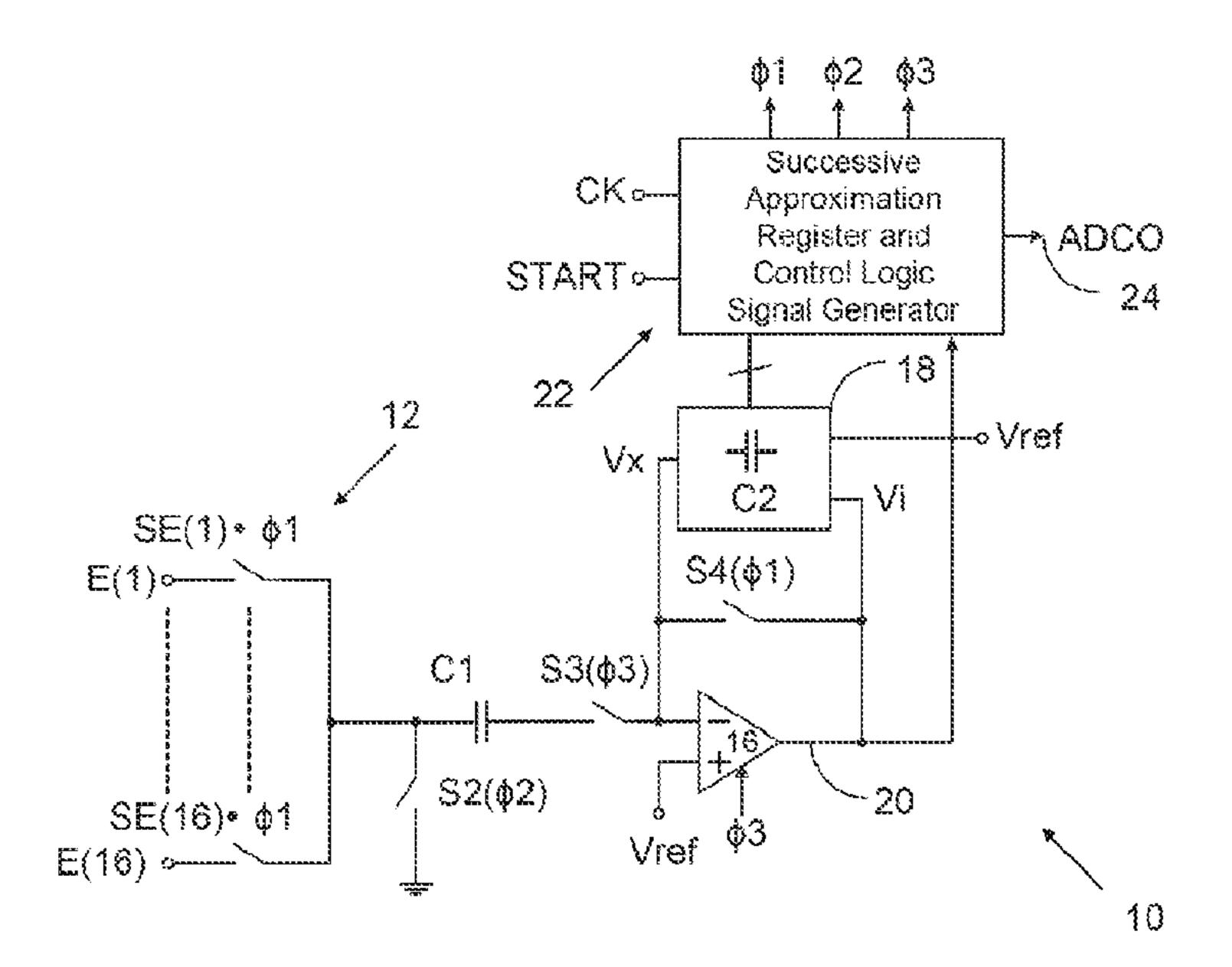

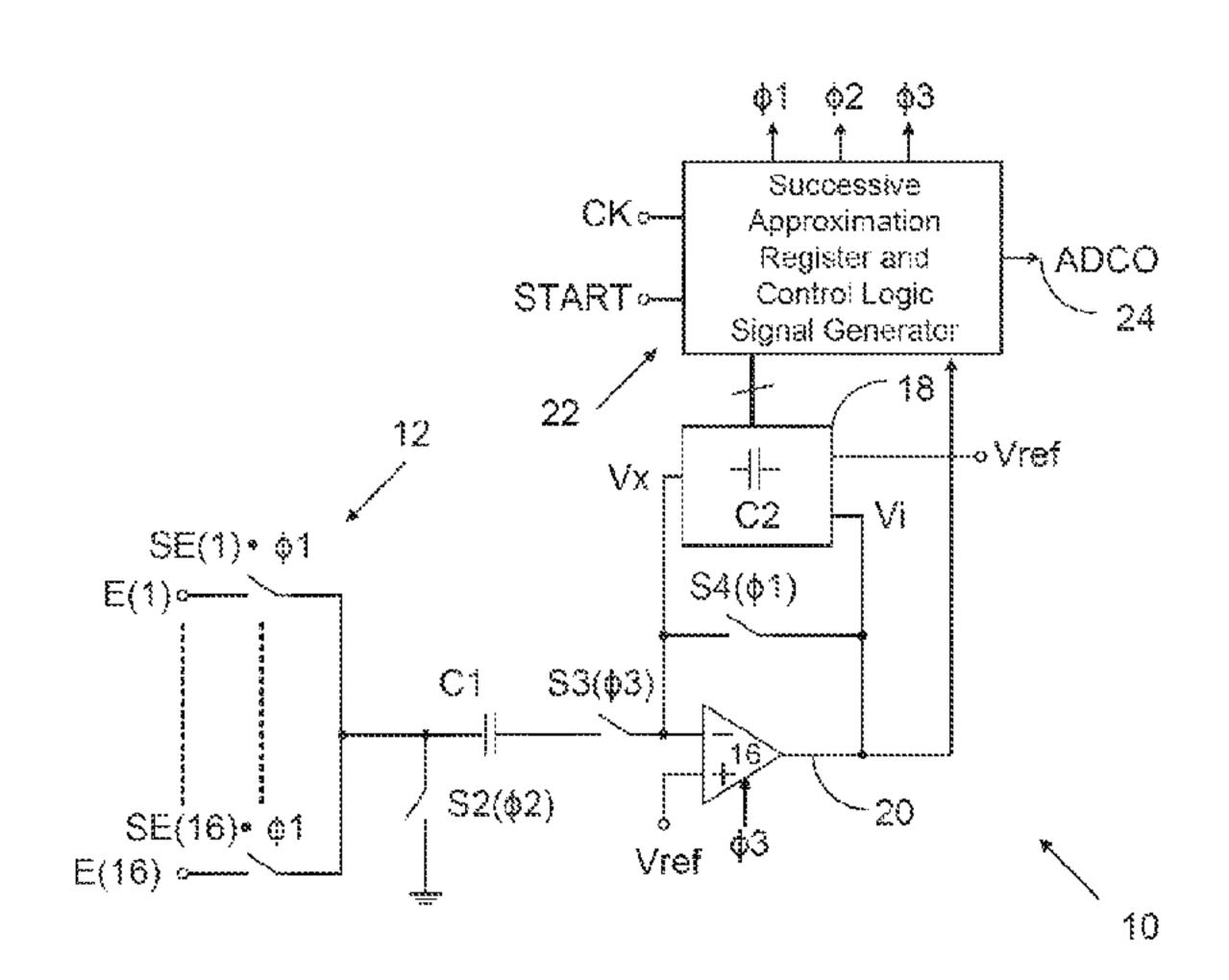

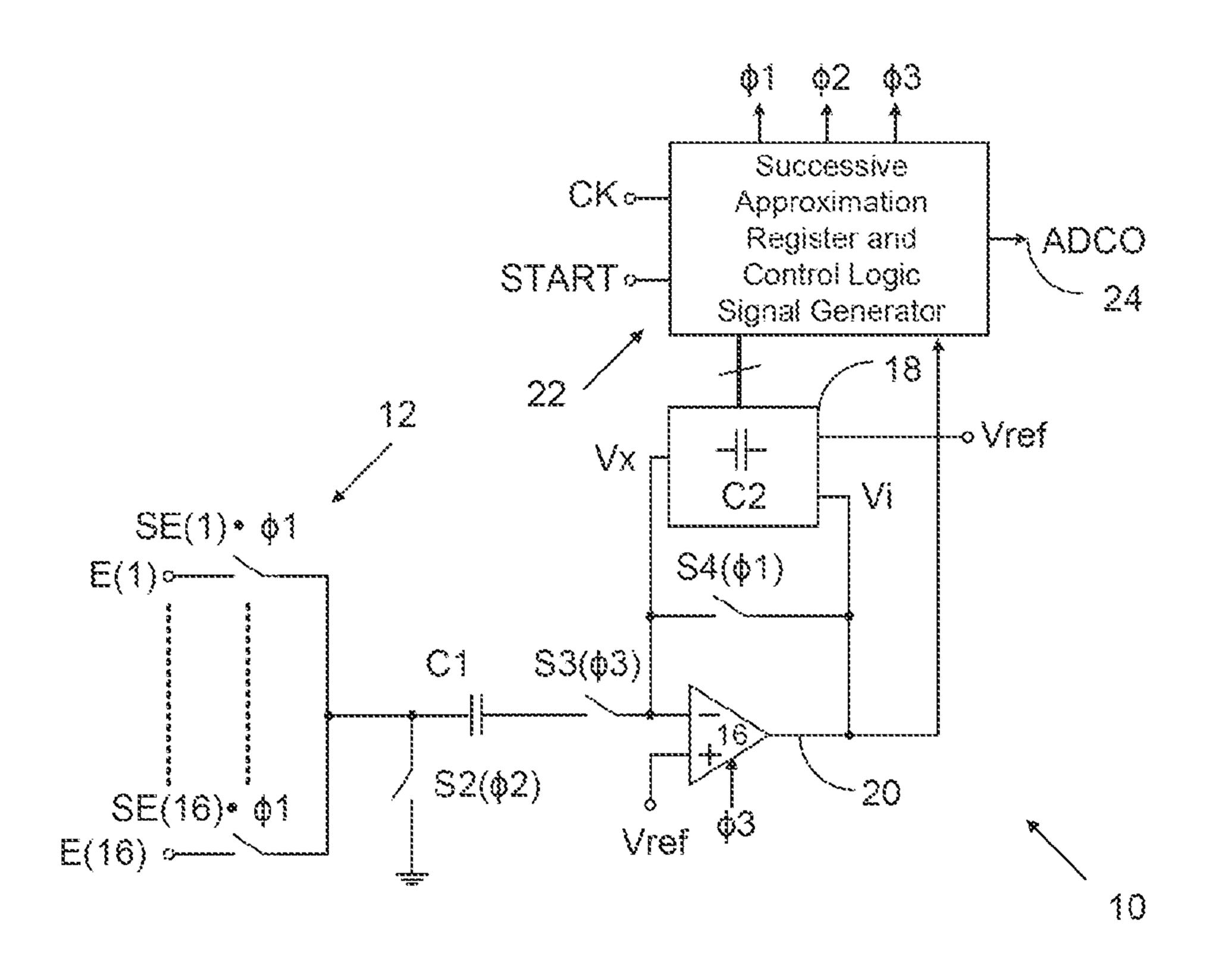

- Fig. 1 is a circuit diagram of an embodiment of the ADC of the present invention;

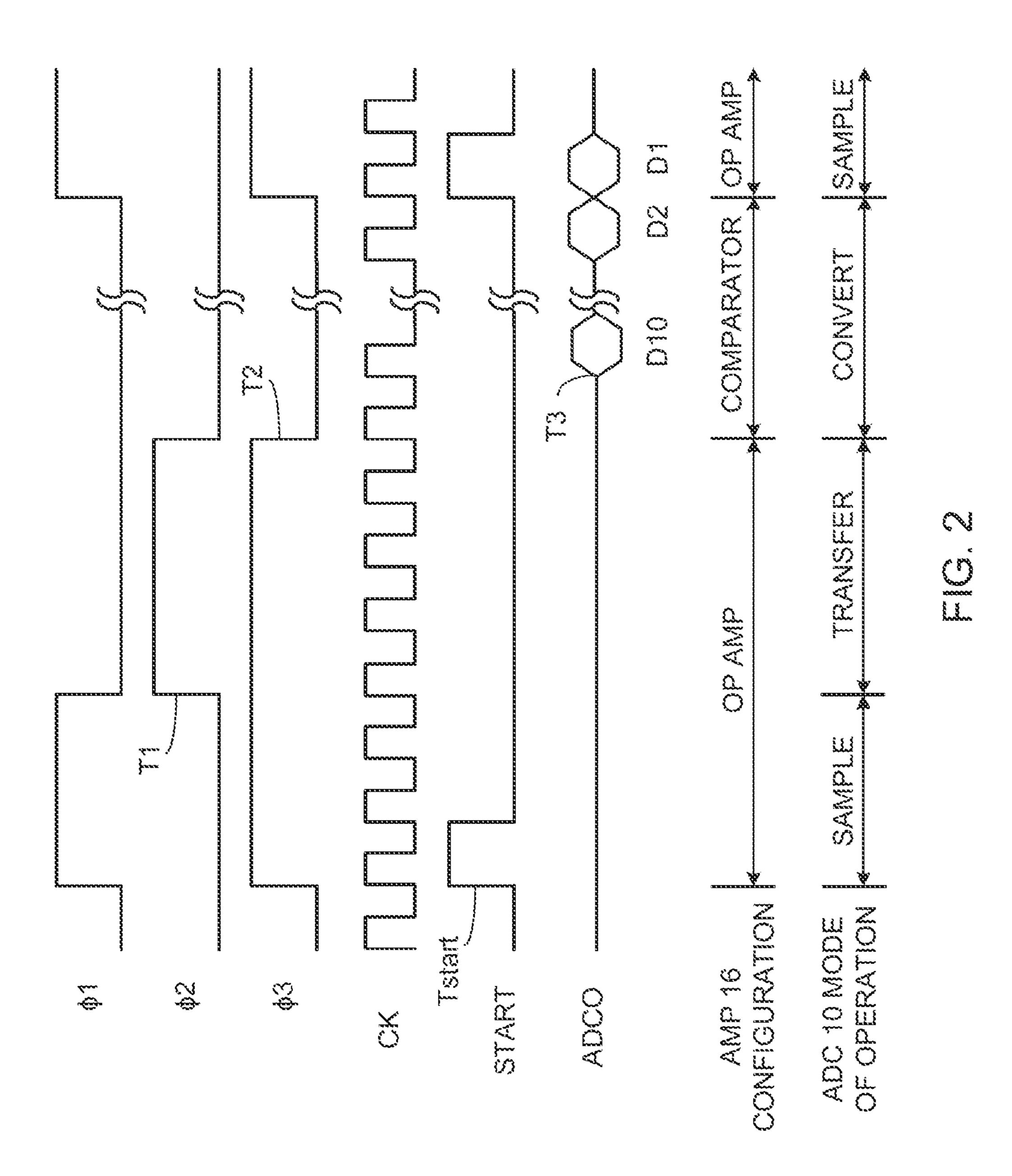

- Fig. 2 is a timing diagram of timing control logic signals;

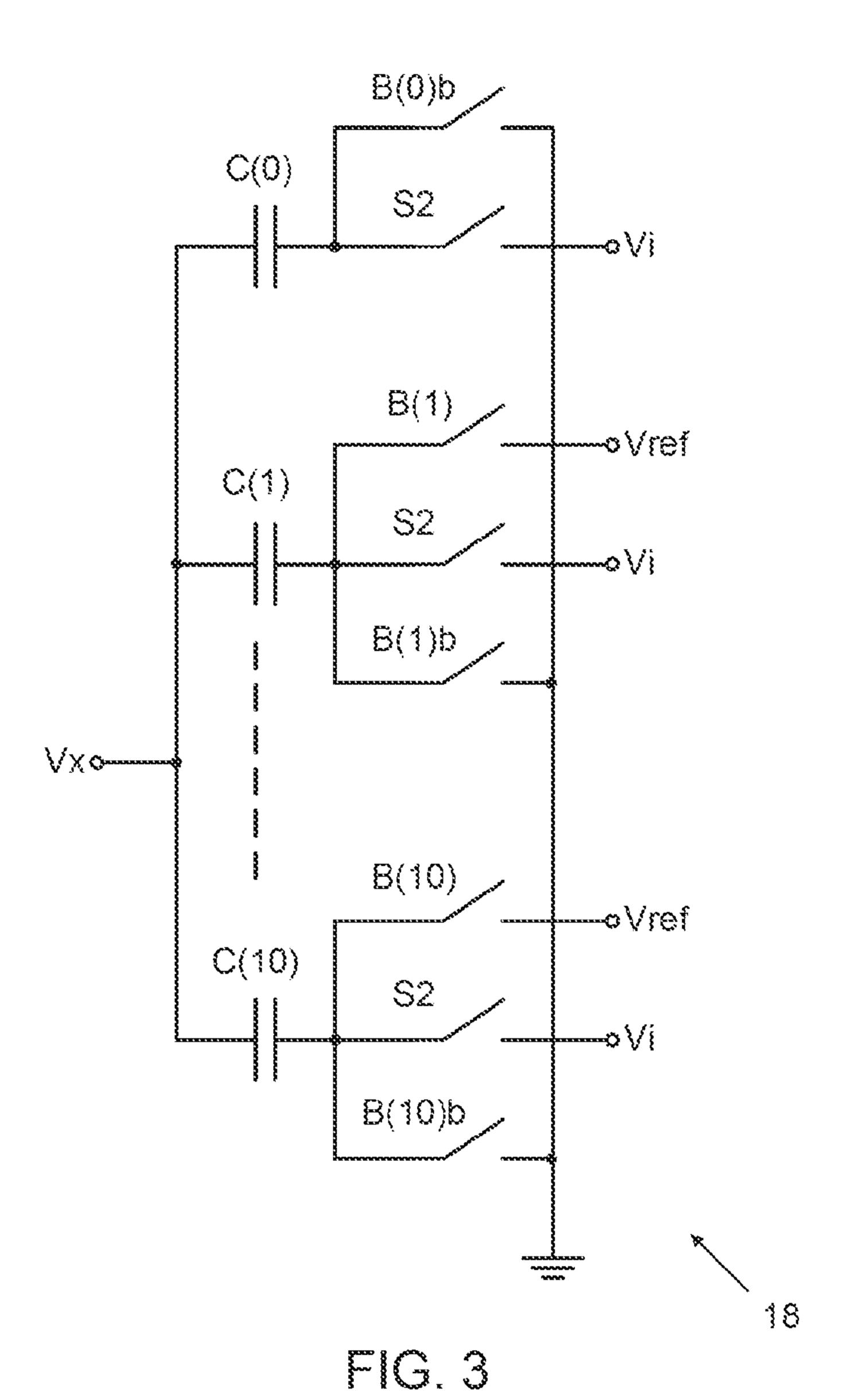

- Fig. 3 is a simplified circuit diagram of a conventional switched capacitor array; and

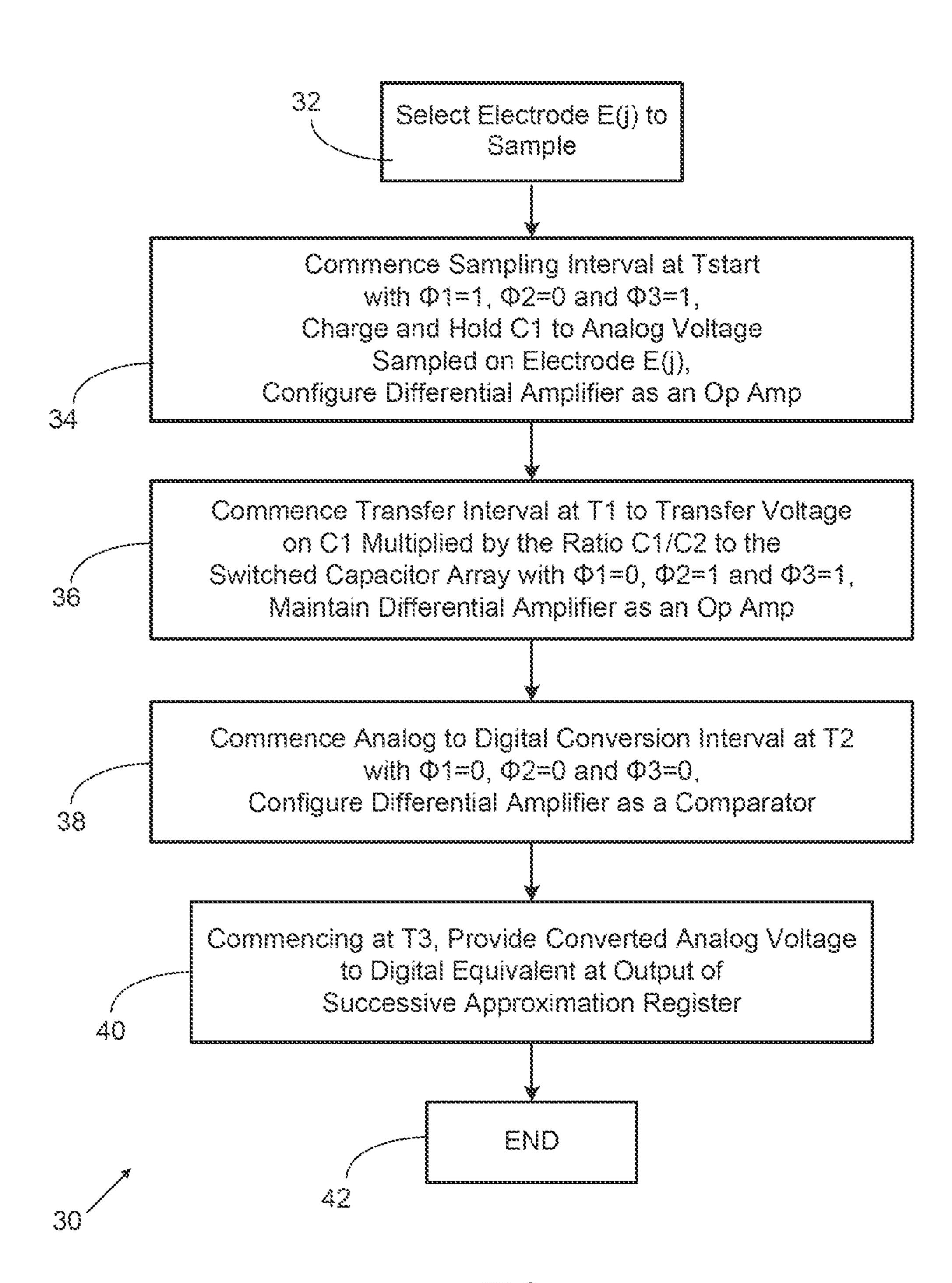

- Fig. 4 is a simplified flow chart of the steps involved in the operation of the present invention.

5

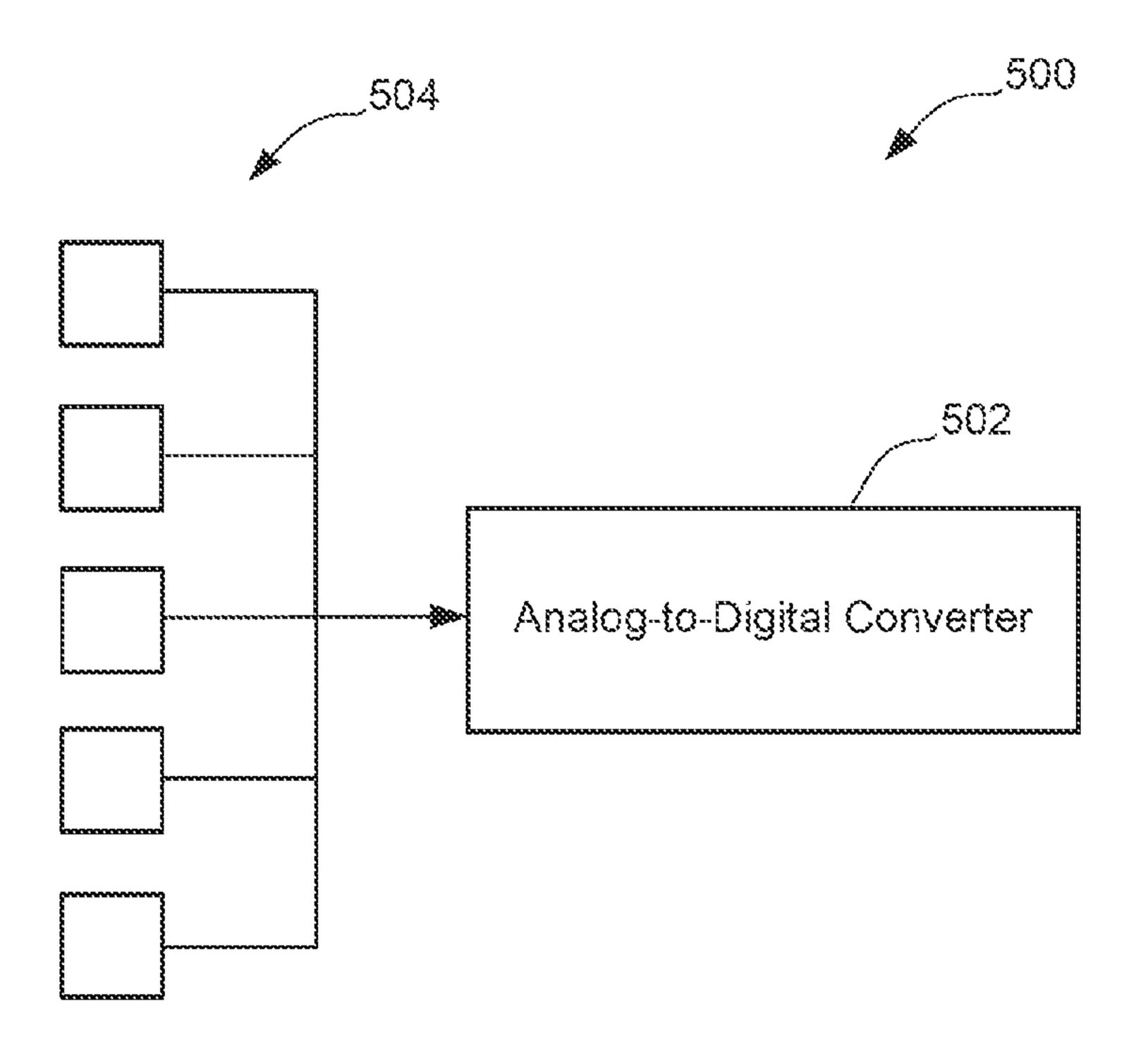

Fig. 5 is a schematic illustration of one embodiment of a sensing system.

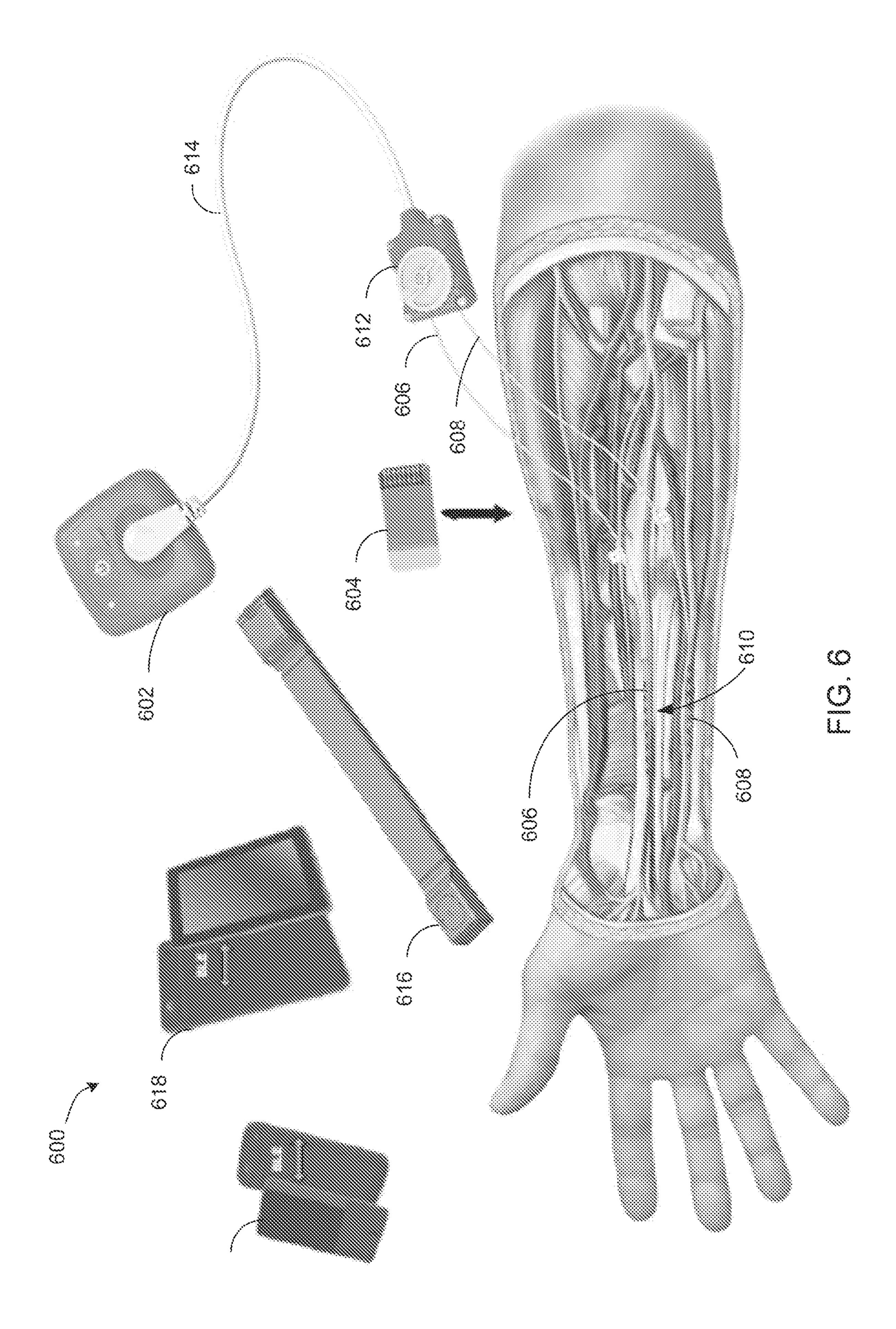

Fig. 6 is a schematic illustration of one embodiment of a peripherally-implantable neurostimulation system.

## Detailed Description of the Invention

Referring now to Fig.1, there is shown an overall circuit/block diagram 10 of an embodiment of one embodiment of an analog-to-digital converter (ADC).

Specifically, depicted in Fig. 1 is a ten bit ADC architecture that is configured to selectively measure/sample the voltage appearing at sixteen different electrodes. It is to be understood however, that ADC architectures involving fewer or greater than ten bits and sampling of voltages for fewer or greater than sixteen electrodes are within the contemplation of the invention. The electrode voltages to be digitally converted are analog in nature and are individually selected from the electrode array 12 and voltage samples are taken during a sample interval defined when the signal Φ1 is high (See Fig. 2). The selection of the electrode of interest may be determined either by a clinician or programmed in a voltage sample protocol implemented in a processor (not shown). As shown in Fig. 1, the notation SE(j)•Φ1 represents a switch array SE(j) configured as an "and" function switch such that when the E(j) electrode is selected for voltage sample and during the sample interval defined by signal Φ1, the switch SE(j), considered a first switch, is closed and the voltage at the E(j) electrode is measured. In the instance described, the notation (j) is selectable from 1 to 16, however, other embodiments may have more or fewer switches.

The switch array SE(j) is coupled to one input (negative input) of a configurable differential amplifier 16 through a series circuit arrangement with capacitor C1 and a switch S3. A reference voltage Vref is coupled to the other input (positive input) of differential amplifier 16. A second switch S2 is coupled between ground and the interconnection of the switch array SE(j) and capacitor C1. The state of switch S2 is controlled by the signal  $\Phi$ 2 and the state of switch S3 is controlled by the signal  $\Phi$ 3.

A switched capacitor array C2 (18), as shown in Fig. 3, is coupled across an input (negative input) and the output 20 of differential amplifier 16. More specifically, capacitor array 18 may be configured in a binary weighted switched capacitor arrangement so that each capacitor in the array is switchable through a corresponding series switch to be in parallel between a common first port identified as Vx and a common second port identified as Vi. The state of each corresponding series switch S2 is defined by the signal  $\Phi2$  such that when  $\Phi2$  is high, all of the capacitors in the array are connected in parallel between the first

and second port. In such case, the total capacitance value C2 of the capacitor array 18 is equal to the sum of the capacitance values of all the capacitors in the array. Furthermore, each capacitor is switchable between the first port and a reference voltage identified as Vref in Fig. 3 through a corresponding series switch so that for a 10 bit switched capacitor array, switch B(10) couples the eleventh capacitor C(10) in the array to Vref and switch B(10)b couples the eleventh capacitor C(10) to ground. A similar switching regime is provided for each remaining capacitor in the switched capacitor array 18.

Furthermore, in one embodiment, the 10 bit switched capacitor array 18 of Fig. 3 includes eleven capacitors C(0) to C(11). Capacitor C(0) connected to switch B(0)b, is considered a "dummy" capacitor. The remaining ten capacitors each contribute to forming the ten bit switched capacitor array processing. In terms of a switching protocol for the "B" switches shown in Fig. 3. The following truth table defines the states of the switches as a function of the signals  $\Phi 1$ ,  $\Phi 2$  and  $\Phi 3$ .

#### TRUTH TABLE FOR "B" SWITCHES IN SWITCHED CAPACITOR ARRAY C2

For  $\Phi 1=1$ , B(k)=1 and B(k)b=0 For  $\Phi 2=1$ , B(k)=0 and B(k)b=0 For  $\Phi 3=0$ , B(k) and B(k)b are complementary

For the above table, "k" varies from 0 to 10

An example of a DAC capacitor array for "n" bits can be found in a technical paper entitled "Capacitor Array Structure and Switch Control for Energy-Efficient SAR Analog-to-Digital Converters" by Jeong-Sup Lee and In-Cheol Park, IEEE Circuits and Systems, 2008. ISCAS 2008. May, 18-21, 2008, pp. 236-239. Another reference to switched capacitor arrays appears in "Analog Integrated Circuit Design", by David Johns and Ken Martin, John Wiley & Sons,

1997, pp. 492-496 and therefore operation of the switched capacitor array need not be described in detail.

A conventional successive approximation register (SAR) 22 is coupled to the switched capacitor array 18 and to the output 20 of differential amplifier 16. Timing control logic signals Φ1, Φ2 and Φ3 as well as clocking signals CK and a start signal START are generated by a logic signal generator (not shown) contained within SAR 22 and applied for conventional SAR operation. Including the logic signal generator in the SAR 22 tends to reduce overall circuit area but having a logic signal generator outside of the SAR 22 as an independent circuit block is also within the contemplation of the invention. The logic signal generator generates the timing signals Φ1, Φ2 and Φ3 for overall circuit operation. As is shown in Fig. 2, when the signal START goes high or logic "1", the sequence of signals Φ1, Φ2 and Φ3 commence. The output 24 of the SAR 22 is identified as ADCO which represents the converted analog to digital output signal. A switch S4 controlled by signal Φ1 is coupled across the output 20 and the negative input of differential amplifier 16 which causes the differential amplifier 16 to function as op amp 16 when Φ1 goes high or at logic "1". Additionally, and as is shown in Fig. 1, the signal Φ3 is connected directly to differential amplifier 16 in a manner such that when Φ3 is high or logic "1", differential amplifier 16 is caused to function as an op amp and when Φ3 is low or logic "0" differential amplifier 16 is caused to function as a comparator.

Fig. 2 shows a time line indicating the time intervals during which differential amplifier 16 is configured either as an op amp or a comparator. Also shown in Fig. 2 is a time line indicating the three modes of operation of ADC 10: sampling, transferring or converting an analog input to a digital output. In some embodiments, the three modes of operation of the ADC 10 can correspond to a plurality of periods. In one embodiment, for example, the operation of the ADC 10 can be divided into a first period, wherein sampling and transferring occur, and a second mode, wherein converting of the analog input to the digital output occurs. In one such embodiment, the sampling can occur in a first portion of the first period and the transferring can occur in a second portion of the first period. In

one embodiment, for example, the modes of operation of the ADC 10 can be divided into a first period including the sampling, a second period including the transferring, and a third period including the converting of the analog input to the digital output.

In operation, a particular electrode is selected for voltage sampling and switch SE(j), where "j" represents the number of the particular selected electrode, is high or at logic "1". During the sample interval, that is, when the signal Φ1 is high or at logic "1", the voltage appearing at the selected electrode E(i) is sampled on capacitor C1. During the sample interval, charge transfers from the selected electrode output to capacitor C1 which causes capacitor C1 to charge up to the electrode output voltage. As noted above, during the sample interval, the configurable differential amplifier 16 functions as an op amp with unity gain feedback by virtue of switch S4 being closed (Φ1 being high). By configuring the differential amplifier as an op amp during a sample interval, a virtual ground is established at the differential amplifier second input for facilitating charge transfer from the input capacitor C1 to the switched capacitor array. Furthermore, any voltage offsets (designated as Vos) attributable to op amp 16 are also sampled on capacitor C1. At the same time, the switches B(1) to B(10) are closed such that all the capacitors in the switched capacitor array 18 are coupled to voltage Vref. During the sampling interval, signal Φ2 is low so that switch S2 is open and signal Φ3 is high so that switch S3 is closed.

During the transfer interval, that is when the signal  $\Phi 2$  is high or logic "1", all the capacitors in the switched capacitor array 18 are coupled to Vi (Fig. 3) which is also coupled to the output 20 of op amp 16. The charge on capacitor C1, as a result of the voltage on C1, is transferred to the switched capacitor array 18 identified as capacitor C2 in Fig. 1, and the voltage across capacitor C2 designated as VC2 is equal to the offset voltage Vos minus the voltage, designated as VE(j), on the "j" electrode, multiplied by the ratio C1/C2 or:  $VC2 = -VE(j) \cdot (C1/C2) + Vos$ . The voltage VC2 is measured between the first port Vx and the second port Vi of the switched capacitor array 18. As is to be noted and importantly, the voltage appearing on the selected electrode is attenuated by

the factor C1/C2 when the capacitance value of capacitor C2 is greater than the capacitance value of capacitor C1. In those instances when it is desired to amplify rather than attenuate the voltage appearing on the selected electrode, the capacitance value of capacitor C1 may be set to be greater than the capacitance value of capacitor C2 so that the ratio of the capacitors equals the desired amplification factor.

It is also to be noted that the symbol C2 has a dual usage such that for purposes of forming the factor C1/C2, the symbol C2 represents the total capacitance value of all the capacitors in the switched capacitor array and for purposes of describing circuit operation, the symbol C2 represents circuit block 18 of Figs. 1 and 3.

During the transfer interval, the signal  $\Phi 1$  is low so that switch S4 is open and signal  $\Phi 3$  is high so that switch S3 is closed. It is to be noted that during the transfer interval, the capacitors in the switched capacitor array are coupled between the differential amplifier output and the negative input, and are in a feedback loop due to  $\Phi 2$  being high, and differential amplifier 16 remains configured as an op amp.

This new and novel arrangement provides for the measurement of large electrode voltages by first attenuating the high electrode voltage range to a lower voltage range across capacitor C2. The attenuation factor is given precisely by the ratio of capacitors C1 and C2, which (unlike the prior art discussed previously) is not affected by any parasitic capacitance associated with capacitors C1 and C2. Since the voltage across capacitor C2 has a lower voltage range, low voltage circuits including logic circuits can be used for digitizing the voltage across capacitor C2. In addition, since low voltage circuits utilizing low voltage transistors that require small die areas are used, high voltage transistors (that occupy large die areas) are only required for switch S2 as well as the input switch array coupled between the electrode inputs and capacitor C1. As a result, this reduces the overall ADC die area when compared to circuits using high voltage transistors.

During the analog to digital conversion interval, that is when the signal Φ3 is low or logic "0", the differential amplifier 16 is configured as a comparator and the voltage VC2 is converted to digital bits (D1 to D10 assuming a 10 bit ADC architecture) in a manner similar to a conventional successive approximation ADC, by switching the capacitors in the switched capacitor array 18 between Vref and ground according to the comparison results generated by comparator 16. For the example 10 bit ADC, although a processor is not shown in the drawings, it is to be understood that a processor configured to undertake the switching activity in the switched capacitor array as well as processing in the successive approximation register (SAR) 22 is within the contemplation of the invention and well within the capabilities of those skilled in the art and therefore is not described here in detail. Upon completion of a successive approximation process during the analog to digital conversion interval, SAR 22 provides the analog to digital converted output at SAR output 24. It is also to be understood that whether done in SAR 22 or after the ADCO (SAR output 24) is generated, the actual converted voltage must be upscaled by the inverse of the attenuation factor C1/C2 or downscaled by the gain factor C1/C2 as the case may be, in order to obtain an accurate conversion of the selected electrode voltage.

With regard to the offset voltage Vos, it is considered that the voltage is unchanged during the sample interval and transfer interval due to proper design of the differential amplifier 16. Moreover, the offset voltage of differential amp 16 is cancelled by the offset voltage stored on capacitor C2.

With reference to Fig. 2 and Fig. 4 there are shown a logic signal timing diagram and a flow chart of the ADC process 30 respectively, to convert a sampled selected electrode voltage to its digital equivalent at the output 24 of the SAR 22. At block 32 an electrode from the plurality of electrodes is selected for corresponding analog voltage sampling. At block 34 a voltage sampling interval commences at Tstart and the electrode voltage E(j) is sampled and held on capacitor C1 and the differential amplifier is configured as an op amp. At block 36 a transfer interval commences at T1 and the voltage on C1 multiplied by the ratio C1/C2 is transferred to the switched capacitor array and the differential amplifier is maintained as an op

amp. At block 38 an analog to digital conversion commences at T2 and the differential amplifier is configured as a comparator. At T3, at block 40 the converted analog voltage as a digital equivalent is provided at the successive approximation register (SAR 22) output. In some embodiments, information received from the successive approximation register (SAR 22) output can be used to determine the impedance of the electrode and/or tissue surrounding the electrode. In some embodiments, this can be used to determine and/or detect the presence or absence of shorts or open circuits in and/or relating to the electrodes. The process is repeated for other selected electrodes whose analog voltage is to be sampled and converted into a digital equivalent.

In some non-limiting embodiments, the afore described ADC architecture may be incorporated into an implantable electrical stimulation system, such as a peripherally implantable system for treating neuropathic pain.

Approximately 8% of the Western (EU and US) population is affected by Neuropathic pain (chronic intractable pain due to nerve damage). In about 5% of people, this pain is severe. There are at least 200,000 patients that have chronic intractable pain involving a nerve. Neuropathic pain can be very difficult to treat with only half of patients achieving partial relief. Thus, determining the best treatment for individual patients remains challenging. Conventional treatments include certain antidepressants, anti-epileptic drugs and opioids. However, side effects from these drugs can be detrimental. In some of these cases, electrical stimulation, including FES, can provide effect treatment of this pain without the drug-related side effects.

A spinal cord stimulator, which is one type of FES device, is a device used to deliver pulsed electrical signals to the spinal cord to control chronic pain. Because electrical stimulation is a purely electrical treatment and does not cause side effects similar to those caused by drugs, an increasing number of physicians and patients favor the use of electrical stimulation over drugs as a treatment for pain. The exact mechanisms of pain relief by spinal cord stimulation (SCS) are unknown. The scientific background of the SCS trials was based initially on the Gate Control Theory of pain that was first described by Melzack and Wall in 1965. The theory posits that pain is transmitted by two kinds of afferent nerve fibers. One is the larger

myelinated  $A\delta$  fiber, which carries quick, intense-pain messages. The other is the smaller, unmyelinated "C" fiber, which transmits throbbing, chronic pain messages. A third type of nerve fiber, called  $A\beta$ , is "non-nociceptive," meaning it does not transmit pain stimuli. The gate control theory asserts that signals transmitted by the  $A\delta$  and C pain fibers can be thwarted by the activation/stimulation of the non-nociceptive  $A\beta$  fibers and thus inhibit an individual's perception of pain. Thus, neurostimulation provides pain relief by blocking the pain messages before they reach the brain.

At the present time, SCS is used mostly in the treatment of failed back surgery syndrome, a complex regional pain syndrome that has refractory pain due to ischemia. SCS complications have been reported in 30% to 40% of all SCS patients. This increases the overall costs of patient pain management and decreases the efficacy of SCS. Common complications include: infection, hemorrhaging, injury of nerve tissue, placing device into the wrong compartment, hardware malfunction, lead migration, lead breakage, lead disconnection, lead erosion, pain at the implant site, generator overheating, and charger overheating. The occurrence rates of common complications are surprisingly high: 9.5% are accounted for lead extension connection issues, 6% are due to lead breakage, 22.6% of cases are associated with lead migration and 4.5% experienced infection.

Peripheral neuropathy may be either inherited or acquired. Causes of acquired peripheral neuropathy include physical injury (trauma) to a nerve, viruses, tumors, toxins, autoimmune responses, nutritional deficiencies, alcoholism, diabetes, and vascular and metabolic disorders. Acquired peripheral neuropathies are grouped into three broad categories: those caused by systemic disease, those caused by trauma, and those caused by infections or autoimmune disorders affecting nerve tissue. One example of an acquired peripheral neuropathy is trigeminal neuralgia, in which damage to the trigeminal nerve (the large nerve of the head and face) causes episodic attacks of excruciating, lightning-like pain on one side of the face.

A high percentage of patients with peripheral neuropathic pain do not benefit from SCS for various reasons. However, many of these patients can receive

acceptable levels of pain relief via direct electrical stimulation to the corresponding peripheral nerves. This therapy is called peripheral nerve stimulation (PNS). There is, however, no FDA approved PNS devices in the US market. Standard spinal cord stimulator (SCS) devices are often used off label by pain physicians to treat this condition. It is estimated that about 15% of SCS devices have been used off-label for PNS.

As current commercially-available SCS systems were designed for stimulating the spinal cord and not for peripheral nerve stimulation, there are more device complications associated with the use of SCS systems for PNS than for SCS. Current SCS devices (generators) are large and bulky. In the event that an SCS is used for PNS, the SCS generator is typically implanted in the abdominal or in the lower back above the buttocks and long leads are tunneled across multiple joints to reach the target peripheral nerves in the arms, legs or face. The excessive tunneling and the crossing of joints leads to increased post-surgical pain and higher device failure rates. Additionally, rigid leads can lead to skin erosion and penetration, with lead failure rates nearing 100% within 3 years of implantation. Most complications result in replacement surgery and even multiple replacement surgeries in some cases.

One embodiment of a sensing system 500 of a peripherally-implantable neurostimulation system is shown in Fig. 5. In some embodiments, components of the sensing system 500 can be located in other components of the peripherally-implantable neurostimulation system, or can be shared with other components of the peripherally implantable neurostimulation system. In some embodiments, the sensing system 500 can be configured to determine one or several voltages, which can include, measuring/sampling voltage at one or several electrodes. In the embodiment depicted in Fig. 5, the sensing system 500 includes an analog-to-digital converter 502 that is connected to a plurality of electrodes 504. In some embodiments, the analog-to-digital converter 502 can be any circuit configured to sense the full-range of voltages at the electrodes 504 and/or to sense a desired portion of the full-range of the voltages at the electrodes 504, and can be, for example, circuit 10 depicted in Fig. 1.

In some embodiments, the analog-to-digital converter 502 can include one or several space saving features. In one embodiment, for example, the analog-todigital converter 502 can include one or several switched capacitors, which can be, for example, part of a switched capacitor amplifier. In one embodiment, the switched capacitor amplifier can be combined with a successive approximation analog-to-digital converter, which successive approximation analog-to-digital converter can include a comparator. The combination of the switched capacitor amplifier and the successive approximation analog-to-digital converter is shown in Fig. 1. As seen in Fig. 1, the switched capacitor amplifier is created during time intervals and/or periods when the differential amplifier 16 operates as an opamp. In one such embodiment, the switched capacitor amplifier and the successive approximation analog-to-digital converter can share a common differential amplifier configurable as either an opamp or as a comparator. In one such embodiment, the comparator of the successive approximation analog-to-digital converter can be used as an opamp when the analog-to-digital converter 502 is sampling, and the comparator of the successive approximation analog-to-digital converter can be used as a comparator for the digitization of the measured voltage.

As seen in Fig. 5, the analog-to-digital converter 502 can be connected to a plurality of electrodes 504. In some embodiments, the electrodes 504 can be part of the electrode array 12 shown in Figure 1. In some embodiments, the electrodes 504 can comprise a conductive portion of one or more leads, such as, for example, a conductive portion of an anodic lead and/or a cathodic lead. In some embodiments, a single electrode 504 can be located on a lead, and in some embodiments, a plurality of electrodes 504 can be located on one lead. The electrodes 504 can, in some embodiments, be placed on, or implanted in a body adjacent to, for example, a nerve. In some embodiments, information identifying the presence or absence of a short or open circuit and/or indicating the voltage of one or several electrodes 504 can be used to alter the creation of one or several electrical pulses and/or pulse patterns.

One embodiment of a peripherally-implantable neurostimulation system 600 is shown in Fig. 6. In some embodiments, the peripherally-implantable

neurostimulation system 600 can be used in treating patients with, for example, chronic, severe, refractory neuropathic pain originating from peripheral nerves. In some embodiments, the peripherally-implantable neurostimulation system 600 can be used to either stimulate a target peripheral nerve or the posterior epidural space of the spine.

The peripherally-implantable neurostimulation system 600 can include one or several pulse generators. The pulse generators can comprise a variety of shapes and sizes, and can be made from a variety of materials. In some embodiments, the one or several pulse generators can generate electrical pulses that are delivered to a nerve to control pain. In some embodiments, a pulse generator can be an external pulse generator 602 or an implantable pulse generator 604. In some embodiments, an external pulse generator 602 can be used to evaluate the suitability of a patient for treatment with the peripherally-implantable neurostimulation system 600 and/or for implantation of an implantable pulse generator 604.

The implantable pulse generator 604 can be sized and shaped, and made of material so as to allow implantation of the implantable pulse generator 604 inside of a body. In some embodiments, the implantable pulse generator 604 can be sized and shaped so as to allow placement of the implantable pulse generator 604 at any desired location in a body, and in some embodiments, placed proximate to a peripheral nerve such that leads (discussed below) are not tunneled across joints and/or such that extension cables are not needed. In some embodiments, the pulse generator, and specifically the implantable pulse generator 604 and/or the external pulse generator 602 can incorporate the sensing system of Fig. 5, and specifically, circuit 10 of Figure 1.

In some embodiments, the electrical pulses generated by the pulse generator can be delivered to one or several nerves 610 and/or to tissue proximate to one or several nerves 610 via one or several leads. The leads can include conductive portions, referred to as electrodes, and non-conductive portions. The leads can have a variety of shapes, can be in a variety of sizes, and can be made

from a variety of materials, which size, shape, and materials can be dictated by the application or other factors.

In some embodiments, the leads can include an anodic lead 606 and/or a cathodic lead 608. In some embodiments, the anodic lead 606 and the cathodic lead 608 can be identical leads, but can receive pulses of different polarity from the pulse generator.

In some embodiments, the leads can connect directly to the pulse generator, and in some embodiments, the leads can be connected to the pulse generator via a connector 612 and a connector cable 614. The connector 612 can comprise any device that is able to electrically connect the leads to the connector cable 614. Likewise, the connector cable can be any device capable of transmitting distinct electrical pulses to the anodic lead 606 and the cathodic lead 608.

In some embodiments, the peripherally-implantable neurostimulation system 600 can include a charger 616 that can be configured to recharge the implantable pulse generator 604 when the implantable pulse generator 604 is implanted within a body. The charger 616 can comprise a variety of shapes, sizes, and features, and can be made from a variety of materials. In some embodiments, the charger 616 can recharge the implantable pulse generator 604 via an inductive coupling.

In some embodiments, one or several properties of the electrical pulses can be controlled via a controller. In some embodiments, these properties can include, for example, the frequency, strength, pattern, duration, or other aspects of the timing and magnitude of the electrical pulses. In one embodiment, these properties can include, for example, a voltage, a current, or the like. In one embodiment, a first electrical pulse can have a first property and a second electrical pulse can have a second property. This control of the electrical pulses can include the creation of one or several electrical pulse programs, plans, or patterns, and in some embodiments, this can include the selection of one or several pre-existing electrical pulse programs, plans, or patterns. In the embodiment depicted in Fig. 6, the peripherally-implantable neurostimulation system 600 includes a controller that is a clinician programmer 618. The clinician programmer 618 can be used to create one or several pulse programs, plans, or patterns and/or to select one or several of the

created pulse programs, plans, or patterns. In some embodiments, the clinician programmer 618 can be used to program the operation of the pulse generators including, for example, one or both of the external pulse generator 602 and the implantable pulse generator 604. The clinician programmer 618 can comprise a computing device that can wiredly and/or wirelessly communicate with the pulse generators. In some embodiments, the clinician programmer 618 can be further configured to receive information from the pulse generators indicative of the operation and/or effectiveness of the pulse generators and the leads.

In some embodiments, the controller of the peripherally-implantable neurostimulation system 600 can include a patient remote 620. The patient remote 620 can comprise a computing device that can communicate with the pulse generators via a wired or wireless connection. The patient remote 620 can be used to program the pulse generator, and in some embodiments, the patient remote 620 can include one or several pulse generation programs, plans, or patterns created by the clinician programmer 618. In some embodiments, the patient remote 620 can be used to select one or several of the pre-existing pulse generation programs, plans, or patterns and to select, for example, the duration of the selected one of the one or several pulse generation programs, plans, or patterns.

Advantageously, the above outlined components of the peripherallyimplantable neurostimulation system 600 can be used to control and provide the generation of electrical pulses to mitigate patient pain.

While the invention has been described by means of specific embodiments and applications thereof, it is understood that numerous modifications and variations could be made thereto by those skilled in the art without departing from the scope of the invention. It is therefore to be understood that within the scope of the claims, the invention may be practiced otherwise than as specifically described herein. For example, although certain electronic devices were described as being coupled to specific positive and negative inputs of the differential amplifier it is to be understood that other connection assignments for such electronic devices is contemplated by the invention with corresponding adjustments made to logic signal timing and signal processing to achieve desired ADC operation.

### CLAIMS:

1. An implantable neurostimulation system comprising:

a plurality of leads, wherein each of the plurality of leads comprises at least one electrode;

an analog-to-digital converter comprising a successive approximation analog-to-digital converter and an integral switched capacitor amplifier, wherein the successive approximation analog-to-digital converter and the integral switched capacitor amplifier share a common differential amplifier; and

a pulse generator configured to generate one or several electrical pulses, wherein the pulse generator is connected to the leads such that the electrical pulses are transmitted to the at least one electrode.

- 2. The implantable neurostimulation system of claim 1, further comprising a successive approximation register.

- 3. The implantable neurostimulation system of claim 2, wherein the successive approximation register comprises a logic signal generator.

- 4. The implantable neurostimulation system of claim 3, wherein the logic signal generator is configured to generate a first signal directing the differential amplifier to operate as an opamp during a first period, and a second signal directing the differential amplifier to operate as a comparator during a second period.

- The implantable neurostimulation system of claim 4, further comprising an input capacitor between the leads and the analog-to-digital converter, wherein the input capacitor is charged during the first period.

- 6. The implantable neurostimulation system of claim 5, wherein the input capacitor is discharged during the first period and subsequent to the charging of the input capacitor, and wherein the charge is transferred to a switched capacitor array.

25

7. An implantable electrical stimulation system comprising:

a pulse generator configured to generate one or several electrical pulses;

an electrode array configured to output the one or several electrical pulses;

an analog-to-digital converter configured to convert an analog signal associated with at least one of the electrodes of the electrode array to a digital signal, the analog-to-digital converter including a reconfigurable differential amplifier; and

a controller configured to reconfigure the differential amplifier between an operational amplifier mode and a comparator mode.

- 8. The implantable electrical stimulation system of claim 7, wherein the analog-to-digital converter comprises a successive approximation analog-to-digital converter and a switched capacitor amplifier that share a common differential amplifier.

- 15 9. The implantable electrical stimulation system of claim 8, further comprising a successive approximation register.

- 10. The implantable electrical stimulation system of claim 7, wherein the controller is configured to generate a first signal directing the reconfigurable differential amplifier to operate as an opamp during a first period, and a second signal directing the differential amplifier to operate as a comparator during a second period.

- The implantable electrical stimulation system of claim 10, further comprising an input capacitor connecting the leads and the analog-to-digital converter, wherein the input capacitor is charged during the first period.

- 12. The implantable electrical stimulation system of claim 11, wherein the input capacitor is discharged during the first period and subsequent to the charging of

the input capacitor, and wherein the charge is transferred to a switched capacitor array.

FIG. 1

FIG. 4

FIG. 5

PCT/US2014/030890