(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3961392号

(P3961392)

(45) 発行日 平成19年8月22日(2007.8.22)

(24) 登録日 平成19年5月25日(2007.5.25)

(51) Int.C1.

F 1

H 03K 17/00 (2006.01)

G 11C 17/06 (2006.01)H 03K 17/00

G 11C 17/06

E

D

請求項の数 14 (全 10 頁)

(21) 出願番号 特願2002-298312 (P2002-298312)

(22) 出願日 平成14年10月11日 (2002.10.11)

(65) 公開番号 特開2003-142994 (P2003-142994A)

(43) 公開日 平成15年5月16日 (2003.5.16)

審査請求日 平成16年6月28日 (2004.6.28)

(31) 優先権主張番号 09/976744

(32) 優先日 平成13年10月13日 (2001.10.13)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 398038580

ヒューレット・パッカード・カンパニー

HEWLETT-PACKARD COMPANY

アメリカ合衆国カリフォルニア州パロアルト ハノーバー・ストリート 3000

(74) 代理人 100087642

弁理士 古谷 聰

(74) 代理人 100076680

弁理士 溝部 孝彦

(72) 発明者 ジョシュ・エヌ・ホーガン

アメリカ合衆国カリフォルニア州94022, ロスアルトス, キングスウッド・ウェイ・620

最終頁に続く

(54) 【発明の名称】ダイオードベースのマルチブレクサ

## (57) 【特許請求の範囲】

## 【請求項1】

整数  $M > 1$  および  $N > 1$  としたとき、 $M$  個のラッチからなるマルチブレクサであって、各ラッチが  $N$  個の段を有し、前記段の各々がデータ入力、電源入力およびデータ出力を有し、前記段の各々が、前記データ出力に接続された電荷蓄積素子、前記データ入力と前記電力供給入力との間に接続された第1のダイオード、および前記電力供給入力と前記データ出力との間に接続された第2のダイオードを含み、

各段が、クロック入力、および該クロック入力と前記電源入力との間に接続された第3のダイオードを更に有し、前記段のクロック入力が互いに接続される、マルチブレクサ。

## 【請求項2】

整数  $M > 1$  および  $N > 1$  としたとき、 $M$  個のラッチからなるマルチブレクサであって、各ラッチが  $N$  個の段を有し、前記段の各々がデータ入力、電源入力およびデータ出力を有し、前記段の各々が、前記データ出力に接続された電荷蓄積素子、前記データ入力と前記電力供給入力との間に接続された第1のダイオード、および前記電力供給入力と前記データ出力との間に接続された第2のダイオードを含み、

各段が、データクリア入力、および該データクリア入力と前記データ出力との間に接続された第4のダイオードのダイオードを更に有し、前記段のデータクリア入力が互いに接続される、マルチブレクサ。

## 【請求項3】

各ラッチが  $N$  段のデータ入力によって形成された  $N$  ビット幅の入力を有し、各ラッチが

N段のデータ出力によって形成されたNビット幅の出力を有する、請求項1又は請求項2に記載のマルチプレクサ。

【請求項4】

前記ラッチのうちの少なくとも1つを一度に有効にするための論理回路を更に含む、請求項1又は請求項2に記載のマルチプレクサ。

【請求項5】

入力データによって前記第1のダイオードが順方向にバイアスされるか逆方向にバイアスされるかが決まり、それによって、前記第1のダイオードが順方向にバイアスされた場合、前記ラッチが第1の論理状態に設定され、前記第1のダイオードが逆方向にバイアスされた場合、前記ラッチが第2の論理状態に設定される、請求項1又は請求項2に記載のマルチプレクサ。

10

【請求項6】

ダイオードベースのメインメモリと、

前記メインメモリ用の、ダイオードベースのアドレス論理回路と、

前記メインメモリおよび前記アドレス論理回路のうちのいずれか一方のためのマルチプレクサであって、複数のラッチを有し、整数N>1としたときに、各ラッチがN個の段を有し、各段がデータ入力、電源入力、およびデータ出力を有し、各段が前記データ出力に接続された電荷蓄積素子、前記データ入力と前記電源入力との間に接続された第1のダイオード、および前記電源入力と前記データ出力との間に接続された第2のダイオードを含む、マルチプレクサと

20

からなる固体メモリ素子。

【請求項7】

前記アドレス論理回路用のアドレスラインを更に含み、該アドレスラインが前記段のデータ出力に接続される、請求項6に記載の固体メモリ素子。

【請求項8】

各ラッチがNビットの出力を有し、前記アドレス論理回路が複数のグループに分割され、異なるNビット出力が異なるグループに対応する、請求項7に記載の固体メモリ素子。

【請求項9】

前記メインメモリ用のデータラインを更に含み、該データラインが前記段のデータ出力に接続される、請求項6に記載の固体メモリ素子。

30

【請求項10】

各ラッチがNビットの出力を有し、前記メインメモリが複数のグループに分割され、異なるNビット出力が異なるグループに対応する、請求項9に記載の固体メモリ素子。

【請求項11】

前記メインメモリおよび前記アドレス論理回路を形成するための土台となる基板であつて、前記ラッチに対してタイミング信号を生成するための論理回路を含む基板と、

前記基板上に形成され、前記タイミング信号に応じて前記ラッチを有効にするため、ゲートとを更に含む、請求項6に記載の固体メモリ素子。

【請求項12】

各段が、クロック入力、および該クロック入力と前記電源入力との間に接続された第3のダイオードを更に有し、前記段のクロック入力が互いに接続される、請求項6に記載の固体メモリ素子。

40

【請求項13】

各段が、データクリア入力、および該データクリア入力と前記データ出力との間に接続された第3のダイオードを更に有し、前記段のデータクリア入力が互いに接続される、請求項6に記載の固体メモリ素子。

【請求項14】

前記メインメモリおよび前記アドレス論理回路のうちの他方のための第2のマルチプレクサを更に含む、請求項6に記載の固体メモリ素子。

【発明の詳細な説明】

50

**【0001】****【発明の属する技术分野】**

本発明は、マルチプレクサに関するものである。本発明は、ワンタイム・プログラマブル(OTP)固体メモリにも関連する。

**【0002】****【従来の技术】**

PDA、ハンドヘルド式コンピュータ、デジタルカメラ、及び、デジタルミュージックプレーヤなどの携帯用装置には、データ、デジタル画像、及び、MP3ファイルなどを記憶するためのメモリが含まれる。これらの携帯用装置には、さまざまな種類の記憶装置を利用することができる。従来の記憶装置の種類には、フラッシュメモリ、小型ハードディスク、コンパクトディスク、及び、磁気テープなどが含まれる。しかし、これらの種類の記憶装置は、いずれも物理的サイズが大きい、記憶容量が少ない、比較的コストが高い、堅牢性に乏しい、アクセス時間が遅い、電力消費が多いといった1以上の制約がある。

10

**【0003】**

特許文献1には、ダイオードベースのOTP固体メモリが開示されている。従来のメモリに比べると、ダイオードベースのメモリは、耐衝撃性が高く、消費電力が少なく、アクセス時間が短く、転送速度が適当で、記憶容量が十分である。ダイオードベースのメモリは、携帯用装置の標準的な携帯用インターフェイス(例えばP-CMCIA、CF)に適している。

20

**【0004】**

ダイオードベースのOTP固体メモリ装置には、多数のデータライン及びアドレスラインが含まれる場合がある。マルチプレクサを用いると、これらのデータライン及びアドレスラインの数を減らすことができる。

**【0005】**

マルチプレクサは、TTLなどのトランジスタ論理回路をベースにする場合がある。しかしながら、ダイオードベースのOTP固体メモリ装置においてトランジスタに必要な層を作成すると、メモリ装置のコスト及び複雑性が増すことになる。

**【特許文献1】**

米国特許出願第09/875,356号明細書

30

**【0006】****【発明が解决しようとする課題】**

本発明の目的は、ダイオードベースのOTPメモリ装置のマルチプレクサにおいてトランジスタの利用を回避することである。

**【0007】****【課題を解决するための手段】**

本発明の態様の1つによれば、マルチプレクサには複数の段(ステージ)が含まれる。各段には、データ出力に接続された記憶装置、データ入力と電源入力との間に接続された第1のダイオード、及び、電源入力とデータ出力との間に接続された第2のダイオードが含まれる。

40

**【0008】**

本発明の他の態様及び利点については、本発明の原理を例示した添付の図面に関連して検討すれば、下記の詳細な説明から明らかになるであろう。

**【0009】**

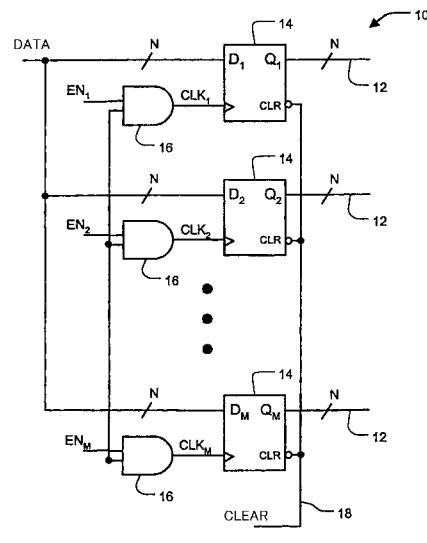

図1を参照すると、マルチプレクサ10には、M個のダイオードベースのラッチ14が含まれる(整数M>1)。ラッチ14の入力(D<sub>1</sub>~D<sub>M</sub>)は並列に接続され、各ラッチ14が同じNビット・ワード(DATA)を受信するようになっている。各ラッチ14は、Nビット幅の出力ライン12を備えている(整数N>1)。マルチプレクサ10は、Nビット・ワード(DATA)を受信し、そのNビット・ワード(DATA)をM個の出力ライン12のうちのいずれか1つへ転送することができる。

**【0010】**

50

クロック信号 (C L K<sub>1</sub>、C L K<sub>2</sub>、. . . 、C L K<sub>M</sub>) がラッチ 14 のクロック入力に供給される。例えば、クロック信号 C L K<sub>1</sub> が第 1 のラッチ 14 に供給される。クロック信号 C L K<sub>1</sub> が高のとき、第 1 のラッチ 14 はデータ・ワード (D A T A) を記憶する。クロック信号 C L K<sub>1</sub> が低になると、この記憶されたデータが第 1 のラッチ 14 の出力ライン 12 で得られるようになる。

#### 【0011】

信号発生器 (図 1 には図示せず) により、基準クロック (C L K) 及び許可信号 (E N<sub>1</sub>、E N<sub>2</sub>、. . . 、E N<sub>M</sub>) が生成される。各許可信号 (E N<sub>1</sub>、E N<sub>2</sub>、. . . 、E N<sub>M</sub>) は、ラッチ 14 に対応する。マルチプレクサ 10 には更に、基準クロック (C L K) 及び許可信号 (E N<sub>1</sub>、E N<sub>2</sub>、. . . 、E N<sub>M</sub>) からクロック信号 (C L K<sub>1</sub>、C L K<sub>2</sub>、. . . 、C L K<sub>M</sub>) を生成するためのゲート 16 も含まれる。例えば、基準クロック (C L K) 及び第 1 の許可信号 (E N<sub>1</sub>) が高のとき、第 1 のラッチ 14 はデータ・ワード (D A T A) を記憶する。ゲート 16 は、E C L 技術をベースにしたものでもよいし、トランジスタを利用しない他の技術をベースしたものでもよい。

#### 【0012】

マルチプレクサ 10 には、ラッチ 14 に記憶されているデータをクリアするためのライン 18 も含まれる。信号発生器によりデータクリア信号 (C L E A R) が生成され、データクリアライン 18 へ供給される。

#### 【0013】

図 1 に示すマルチプレクサによれば、入力ラインが約 M : 1 に減少する。従って、M = 3 2 のラッチを備えたマルチプレクサにより、入力ラインが約 32 : 1 に減少する。

#### 【0014】

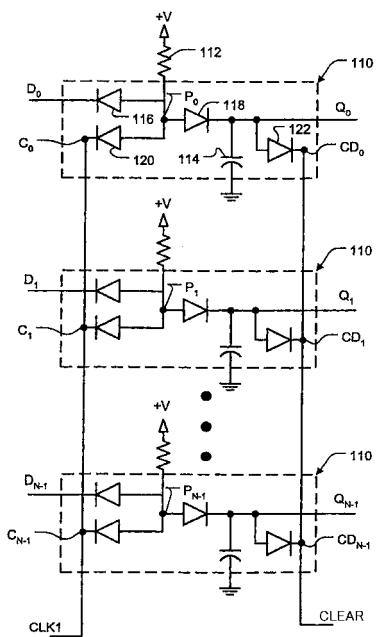

図 2 は、ダイオードベースのラッチ 14 をさらに詳細に示している。ラッチ 14 には、それぞれデータ入力 (D<sub>n</sub>)、電源入力 (P<sub>n</sub>)、及び、データ出力 (Q<sub>n</sub>) を備えた N 個の段 110 が含まれる (0 ≤ n ≤ (N - 1))。第 1 の段 110 のデータ入力 (D<sub>0</sub>) はデータ・ワード (D A T A) の最初のビットを受信し、2 番目の段のデータ入力 (D<sub>1</sub>) はデータ・ワード (D A T A) の 2 番目のビットを受信し、N 番目の段のデータ入力 (D<sub>N-1</sub>) はデータ・ワード (D A T A) の N 番目のビットを受信する。これらの N 個の段 110 の N 個のデータ出力 (Q<sub>0</sub> ~ Q<sub>N-1</sub>) は、N ビットのデータライン 12 に接続される。各段 110 毎に、プルアップ抵抗器 112 が電源入力 (P<sub>n</sub>) と電圧源 (+ V) との間に接続される。

#### 【0015】

各段 110 には、データ出力 (Q<sub>n</sub>) に接続された電荷蓄積素子 (例えばコンデンサ) 114、データ入力 (D<sub>n</sub>) と電源入力 (P<sub>n</sub>) との間に接続された第 1 のダイオード 116、及び、電源入力 (P<sub>n</sub>) とデータ出力 (Q<sub>n</sub>) との間に接続された第 2 のダイオード 118 が含まれる。第 1 のダイオード 116 の陰極はデータ入力 (D<sub>n</sub>) に接続され、第 1 のダイオード 116 の陽極は電源入力 (P<sub>n</sub>) に接続される。第 2 のダイオード 118 の陰極はデータ出力 (Q<sub>n</sub>) に接続され、第 2 のダイオード 118 の陽極は電源入力 (P<sub>n</sub>) に接続される。

#### 【0016】

各段 110 には更に、クロック入力 (C<sub>n</sub>)、及び、クロック入力 (C<sub>n</sub>) と電源入力 (P<sub>n</sub>) との間に接続された第 3 のダイオード 120 が設けられる。段 110 のクロック入力 (C<sub>0</sub> ~ C<sub>N-1</sub>) は同じクロック信号 (例えば、C L K<sub>1</sub>) を受信するように互いに接続される。

#### 【0017】

各段 110 には、データクリア入力 (C D<sub>n</sub>)、及び、データクリア入力 (C D<sub>n</sub>) とデータ出力 (Q<sub>n</sub>) との間に接続された第 4 のダイオード 122 がさらに設けられる。段 110 のデータクリア入力 (C D<sub>0</sub> ~ C D<sub>N-1</sub>) は同じデータ・クリア信号 (C L E A R) を受信するように互いに接続される。

#### 【0018】

10

20

30

40

50

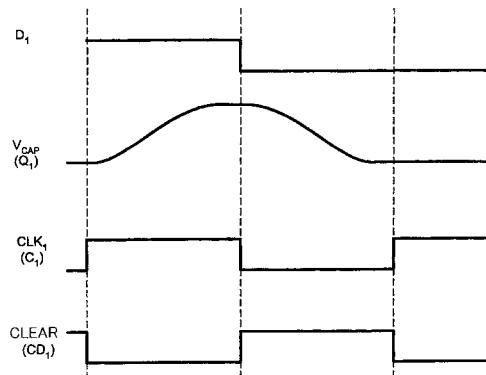

更に図3を参照する。次に、下記の例に従って、第2の段110の動作について説明する。初期状態は次の通りである。クロック信号がデアサートされ、クリア信号がアサートされている。第3及び第4のダイオード120及び122には順バイアスがかかっており、その間、電流が電源から第3のダイオード120を流れ、コンデンサ114が第4のダイオード122を通して放電される。

#### 【0019】

動作の開始時には、クロック信号( $CLK_1$ )がアサートされ、データクリア信号( $CLEAR$ )がデアサートされる。第3及び第4のダイオード120, 122が逆バイアス状態になる。データ・ワード・ビット( $D_1$ )が高の場合、第1のダイオード116が逆バイアス状態になり、第2のダイオード118が順バイアス状態になる。電流がブル・アップ抵抗器112及び第2のダイオード118を通して流れ、コンデンサ114を充電する。コンデンサ電圧( $V_{CAP}$ )が上昇する。10

#### 【0020】

データは、クロック信号( $CLK_1$ )の立ち下がりエッジで読み出される。高のコンデンサ電圧( $V_{CAP}$ )がデータ出力( $Q_1$ )で読み出される。この高の電圧は、高のデータ状態に対応する。

#### 【0021】

データの読み出しが終わると、データクリア信号( $CLEAR$ )が再びアサートされる。この結果、第3及び第4のダイオード120, 122が順バイアス状態になり、電流が電源から第3のダイオード120を通して流れ、コンデンサ114が第4のダイオード122を通して放電される。コンデンサ電圧( $V_{CAP}$ )が低下する。20

#### 【0022】

次のクロックサイクル開始時には、クロック信号( $CLK_1$ )がアサートされ、データクリア信号( $CLEAR$ )がデアサートされる。第3及び第4のダイオード120, 122が逆バイアス状態になる。データ・ワード・ビット( $D_1$ )が低の場合、第1のダイオード116が順バイアス状態になる。電流が第1のダイオード116を通して流れ、コンデンサ114は充電されない。従って、コンデンサ電圧( $V_{CAP}$ )は上昇しない。

#### 【0023】

データは、クロック信号( $CLK_1$ )の立ち下がりエッジで読み出される。データ出力( $Q_1$ )の低のコンデンサ電圧( $V_{CAP}$ )は、低のデータ状態に対応する。30

#### 【0024】

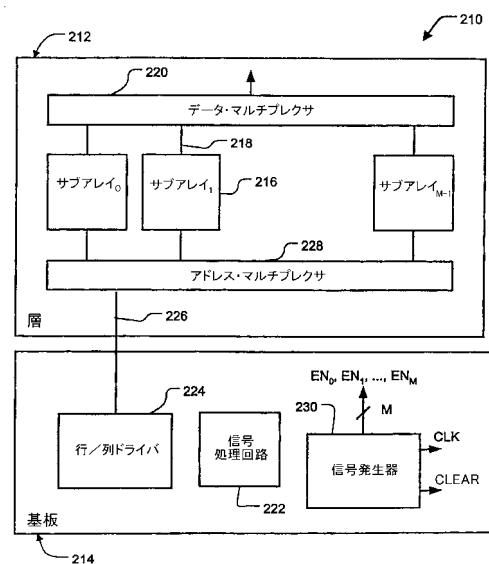

図4は、ダイオードベースのOTPメモリ装置210を示している。シリコン基板214上に、1以上の記憶階層(memory level)212がスタックされる。各階層には、M個のサブアレイ216が含まれる。各サブアレイ216については後でさらに詳細に説明する。データはサブアレイ216からデータライン218へ読み出され、データライン218を介してデータ・マルチブレクサ220(図1に示すマルチブレクサ10と同じ構成にすることができる)へ供給される。データ・マルチブレクサ220の出力は、基板214上の信号処理回路222へ供給される。

#### 【0025】

アドレスは行/列ドライバ224により復号され、復号されたアドレスがアドレス・マルチブレクサ228(図1に示すマルチブレクサ10と同じ構成にすることができる)により適当なアドレス・ライン226に対して多重化される。行/列ドライバ224も基板214上に設けられる。40

#### 【0026】

基板214上の信号発生器230により、許可信号( $EN_1, EN_2, \dots, EN_M$ )、基準クロック( $CLK$ )、及び、データクリア信号( $CLEAR$ )が生成される。これらのタイミング信号は、アドレスを復号することによって生成することができる。

#### 【0027】

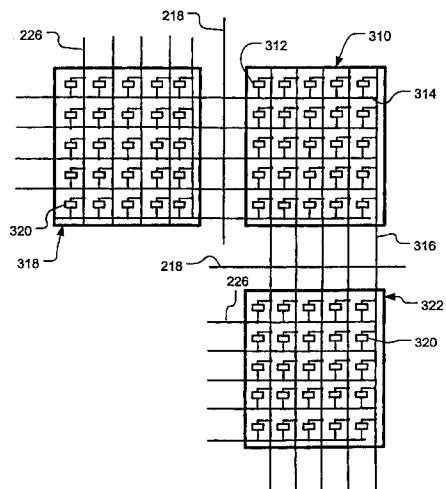

次に、図5を参照する。サブアレイ216は、OTPメモリ要素312の交差点抵抗器アレイ310、メモリ要素312の行の方向に延びるワードライン314、及び、メモリ要

素312の列の方向に延びるビットライン316を含む。メモリ要素312の各行毎に1本のワードライン314を設け、メモリ要素312の各列毎に1本のビットライン316を設けることができる。各メモリ要素312は、ワードライン314とビットライン316との交差点に配置される。

【0028】

OTP行デコーダ318は、アドレス・マルチプレクサ228により行アドレス・ライン226に供給されたアドレスを復号することによって、ワードライン314を選択する。行デコーダ318は、複数のOTPアドレス要素320を含む。行デコーダ318の各アドレス要素320は、ワードライン314と行アドレスライン226との交差点に配置される。

10

【0029】

OTP列デコーダ322は、アドレス・マルチプレクサ228により列アドレス・ライン226に供給されたアドレスを復号することによって、列ライン(ビットライン)316を選択する。列デコーダ322は、複数のOTPアドレス要素320を含む。列デコーダ322の各アドレス要素320は、ビットライン316と列アドレス・ライン226との交差点に配置される。

【0030】

メモリ要素312及びアドレス要素320は、いずれもダイオードを含む。

【0031】

データは、行/列ドライバ224及び信号発生器230へアドレスを供給することにより、メモリ装置210に書き込むことができる。信号発生器230はこのアドレスを復号し、アドレス・マルチプレクサ228にサブアレイを選択させる。行/列ドライバ224はこのアドレスを復号し、復号されたアドレスをアドレス・マルチプレクサ228へ送信し、従って選択されたサブアレイへ送信する。選択されたサブアレイのアドレス論理回路は、この復号されたアドレスを受信し(アドレスライン226を介して)、ワードライン314及びビットライン316を選択する。選択されたワードライン314及びビットライン316に書き込み電流が流れ、それらの交差点にあるメモリ要素312に書き込み電流が流れる。書き込み電流の大きさは、選択されたメモリ要素312の抵抗状態を変化させるのに十分なものとする。

20

【0032】

メモリ要素312の抵抗状態は、行/列ドライバ224にアドレスを供給することによって検知することができる。アドレス・マルチプレクサ228は、復号されたアドレスを選択されたサブアレイに送信する。この復号されたアドレスに応じてワードライン314及びビットライン316が選択される。検知電流が選択されたワードライン314及びビットライン316を流れ、従って、それらの交差点にあるメモリ要素312を流れる。検知電流の大きさは、選択されたメモリ要素312の抵抗状態を示すものである。この検知電流はデジタル値に変換され、データ・マルチプレクサがこのデジタル値を基板214上の信号処理回路222へ送信する。実際にはサブアレイから出力される全てのデータがまとめて送信されるが、選択されたアドレスに対応するメモリのビットしか有効ではない。

30

【0033】

本発明は、上記の説明及び例示の特定の実施形態に制限されることはない。本発明は、特許の範囲の範囲より規定されるものとする。

40

【0034】

以下においては、本発明の種々の構成要件の組み合わせからなる例示的な実施態様を示す。

1. 整数M > 1およびN > 1としたとき、N個の段(110)を有するM個のラッチ(14)からなるマルチプレクサであって、

前記段の各々はデータ入力(D<sub>n</sub>)、電源入力(P<sub>n</sub>)およびデータ出力(Q<sub>n</sub>)を有し、前記段の各々は、前記データ出力(Q<sub>n</sub>)に接続された電荷記憶装置(114)、前記データ入力(D<sub>n</sub>)と前記電力供給入力(P<sub>n</sub>)との間に接続された第1のダイオード(116)、およ

50

び、前記電力供給入力 (P<sub>n</sub>) と前記データ出力 (Q<sub>n</sub>) との間に接続された第2のダイオード(18)を含む、マルチプレクサ(10)。

2. 前記ラッチ(14)の各々は、該ラッチのN個の段(110)のデータ入力 (D<sub>n</sub>) により形成されたNビット幅の入力を有し、

前記ラッチ(14)の各々は、該ラッチのN個の段(110)のデータ出力 (Q<sub>n</sub>) により形成されたNビット幅の出力を有する、請求項1のマルチプレクサ(10)。

3. 少なくとも1つの前記ラッチ(14)を一時に有効にするための論理(16)をさらに含む、請求項1のマルチプレクサ(10)。

4. 前記段(110)の各々は、クロック入力 (C<sub>n</sub>)、および、該クロック入力 (C<sub>n</sub>) と前記電源供給入力 (P<sub>n</sub>) との間に接続された第3のダイオード(120)をさらに含み、前記段(110)のクロック入力 (C<sub>n</sub>) が互いに接続されている、請求項1のマルチプレクサ(10)。 10

5. 前記段(110)の各々は、クリアデータ入力 (C D<sub>n</sub>)、および、該クリアデータ入力 (C D<sub>n</sub>) と前記データ出力 (Q<sub>n</sub>) との間に接続された第3のダイオード(122)をさらに含み、前記段(110)のクリアデータ入力 (C D<sub>n</sub>) が互いに接続されている、請求項1のマルチプレクサ(10)。

6. 入力データによって前記第1のダイオード(116)が順方向にバイアスされるか逆方向にバイアスされるかが決まり、前記第1のダイオード(116)が順方向にバイアスされる場合には前記ラッチが第1の論理状態に設定され、前記第1のダイオード(116)が逆方向にバイアスされる場合には前記ラッチが第2の論理状態に設定される、請求項1のマルチプレクサ(10)。 20

【0035】

#### 【発明の効果】

本発明は、上記のように構成することにより、トランジスタを利用することなくダイオードベースのOTPメモリ装置のマルチプレクサを構成することができる。

#### 【図面の簡単な説明】

【図1】本発明によるマルチプレクサを例示した図である。

【図2】本発明によるマルチプレクサ用のラッチを例示した図である。

【図3】本発明によるマルチプレクサに関するタイミング図である。

【図4】本発明によるサブ・アレイ及びマルチプレクサを含むダイオードベースのメモリ装置を例示した図である。 30

【図5】サブアレイを例示した図である。

#### 【符号の説明】

10 マルチプレクサ

12 出力ライン

14 ラッチ

16 論理回路

110 段

114 電荷蓄積装置

116 第1のダイオード

118 第2のダイオード

120 第3のダイオード

122 第4のダイオード

C<sub>n</sub> クロック入力

C D<sub>n</sub> データクリア入力

D<sub>n</sub> データ入力

P<sub>n</sub> 電源入力

Q<sub>n</sub> データ出力

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

審査官 清水 稔

(56)参考文献 特開平11-027111(JP, A)

実開平06-044246(JP, U)

特開平01-263562(JP, A)

特開2000-059223(JP, A)

国際公開第00/000983(WO, A1)

特開昭63-283314(JP, A)

特開平05-211301(JP, A)

特公昭44-004138(JP, B1)

実開昭52-126711(JP, U)

実開昭64-013816(JP, U)

Tanaka, K. et.al., High speed 8:1 multiplexer and 1:8 demultiplexer ICs using GaAs DCF

L circuit, Gallium Arsenide Integrated Circuit (GaAs IC) Symposium, 1991. Technical D

igest 1991., 13th Annual , 1991年10月23日, p.229 - 232

(58)調査した分野(Int.Cl., DB名)

H03K 17/00

G11C 17/06