(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3615010号

(P3615010)

(45) 発行日 平成17年1月26日(2005.1.26)

(24) 登録日 平成16年11月12日(2004.11.12)

(51) Int.C1.<sup>7</sup>

F 1

H03K 19/20

H03K 19/20

H03K 19/0948

H03K 19/21

H03K 19/21

H03K 19/094

B

請求項の数 4 (全 45 頁)

(21) 出願番号

特願平9-33853

(22) 出願日

平成9年2月18日(1997.2.18)

(65) 公開番号

特開平10-233678

(43) 公開日

平成10年9月2日(1998.9.2)

審査請求日

平成16年1月20日(2004.1.20)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(73) 特許権者 000237617

富士通ヴィエルエスアイ株式会社

愛知県春日井市高蔵寺町2丁目1844番

2

(74) 代理人 100068755

弁理士 恩田 博宣

(72) 発明者 外園 久和

愛知県春日井市高蔵寺町二丁目1844番

2 富士通ヴィエルエスアイ株式会社内

審査官 彦田 克文

最終頁に続く

(54) 【発明の名称】論理回路

## (57) 【特許請求の範囲】

## 【請求項1】

高電位側電源に接続されているPチャネルMOSトランジスタ及び該PチャネルMOSトランジスタと低電位側電源との間に接続されているNチャネルMOSトランジスタを含む複数のMOSトランジスタで構成され、複数の入力信号に基づいて所定論理の出力信号を出力する論理回路であって、

前記複数の入力信号の内の一つの入力信号が前記複数のMOSトランジスタの内の一つのNチャネルMOSトランジスタのソース又はドレインに入力され、

前記複数の入力信号の内の他の入力信号が前記複数のMOSトランジスタのゲートに入力され、

前記一つの入力信号と、一つの電源とのいずれかのレベルを出力信号として出力する論理回路であり、

前記出力信号を前記高電位側電源の電圧と前記低電位側電源の電圧との範囲でフル振幅動作させる出力信号安定化回路を備えることを特徴とする論理回路。

## 【請求項2】

高電位側電源に接続されているPチャネルMOSトランジスタ及び該PチャネルMOSトランジスタと低電位側電源との間に接続されているNチャネルMOSトランジスタを含む複数のMOSトランジスタで構成され、n個の入力信号(nは2以上の整数)に基づいて所定論理の出力信号を出力する論理回路であって、

前記複数の入力信号の内の一つの入力信号が前記複数のMOSトランジスタの内の一つの

NチャネルMOSトランジスタのソース又はドレインに入力され、

前記複数の入力信号の内の他の入力信号が前記複数のMOSトランジスタのゲートに入力され、

2n-2個のトランジスタで所望論理の出力信号を出力する論理回路であり、

前記出力信号を前記高電位側電源の電圧と前記低電位側電源の電圧との範囲でフル振幅動作させる出力信号安定化回路を備えることを特徴とする論理回路。

【請求項3】

高電位側電源に接続されているPチャネルMOSトランジスタ及び該PチャネルMOSトランジスタと低電位側電源との間に接続されているNチャネルMOSトランジスタを含む複数のMOSトランジスタで構成され、複数の入力信号に基づいて所定論理の出力信号を出力する論理回路であって、

前記複数の入力信号の内の一つの入力信号が前記複数のMOSトランジスタの内の一つのNチャネルMOSトランジスタのソース又はドレインに入力され、

前記複数の入力信号の内の他の入力信号が前記複数のMOSトランジスタのゲートに入力され、

高電位側電源及び低電位側電源が供給されるインバータ回路を使用することなく所望論理の出力信号を出力する論理回路であり、

前記出力信号を前記高電位側電源の電圧と前記低電位側電源の電圧との範囲でフル振幅動作させる出力信号安定化回路を備えることを特徴とする論理回路。

【請求項4】

前記論理回路は、所望論理の反転信号を出力する論理回路とし、

前記出力信号安定化回路は、

前記反転信号を反転させて出力するインバータ回路と、

前記インバータ回路の出力信号に基づいて前記反転信号を電源電圧レベルとするMOSトランジスタと

を備えることを特徴とする請求項1、請求項2又は請求項3記載の論理回路。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は、論理回路に関するものである。

マイコンあるいはASIC等の半導体装置には、多数の論理回路が使用されている。近年の半導体装置の高集積化及び低消費電力化にともない、このような論理回路の素子数の削減及び低消費電力化がますます必要となっている。

【0002】

【従来の技術】

(第一の従来例)

図15は、CMOS構成の2入力NOR回路の従来例を示す。入力信号A1は、CMOSインバータ回路1aに入力され、そのインバータ回路1aの出力信号であるノードN1は、CMOSインバータ回路1bに入力される。

【0003】

前記インバータ回路1bを構成するPチャネルMOSトランジスタのソースは、PチャネルMOSトランジスタTr1を介して高電位側電源Vccに接続される。前記トランジスタTr1のゲートには、入力信号A2が入力される。

【0004】

前記インバータ回路1bの出力信号は、出力端子Toから出力信号Xとして出力される。前記出力端子Toは、NチャネルMOSトランジスタTr2を介して低電位側電源Vssに接続され、同トランジスタTr2のゲートには前記入力信号A2が入力される。

【0005】

このように構成された2入力NOR回路の動作を説明すると、入力信号A1, A2がともにLレベル、すなわち「0」となると、トランジスタTr1はオンされるとともに、トランジ

10

20

30

40

50

ンジスタTr2はオフされる。

【0006】

また、ノードN1はHレベルとなり、インバータ回路1bを構成するPチャネルMOSトランジスタはオフされるとともに、NチャネルMOSトランジスタはオンされるため、トランジスタTr1のオン動作に関わらず、出力信号XはLレベルとなる。

【0007】

入力信号A1が「0」、入力信号A2がHレベル、すなわち「1」となると、トランジスタTr1がオフされるとともに、トランジスタTr2がオンされる。また、ノードN1がHレベルとなる。従って、出力信号XはLレベルとなる。

【0008】

入力信号A1が「1」、入力信号A2が「0」となると、トランジスタTr1がオンされるとともに、トランジスタTr2がオフされる。また、ノードN1がLレベルとなる。従って、出力信号XがHレベルとなる。

【0009】

入力信号A1, A2がともに「1」となると、トランジスタTr1がオフされるとともに、トランジスタTr2がオンされる。また、ノードN1がLレベルとなる。従って、出力信号XがLレベルとなる。

【0010】

上記のような動作により、この論理回路は図17に示す真理値に基づく動作を行い、入力信号A1の反転信号であるノードN1と入力信号A2とのNOR論理を出力信号Xとして出力し、図16に示すシンボルで表記されるNOR回路2を構成する。

【0011】

上記のようなNOR回路2では、NOR論理を出力するための4個のトランジスタと、入力信号A1を反転させるためのインバータ回路1aを構成する2個のトランジスタとから、計6個のトランジスタを必要とする。すなわち、入力数をnとすれば、4n-2個のトランジスタを必要とする。

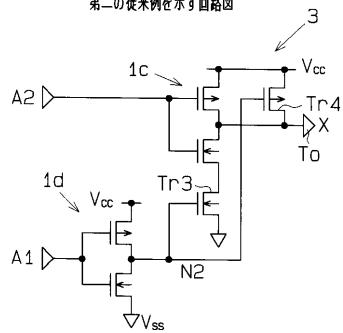

(第二の従来例)

図18は、CMOS構成の2入力NAND回路の従来例を示す。入力信号A2は、CMOSインバータ回路1cに入力され、そのインバータ回路1cから出力端子Toに出力信号Xが出力される。

【0012】

入力信号A1は、CMOSインバータ回路1dに入力され、そのインバータ回路1dの出力信号、すなわちノードN2は、NチャネルMOSトランジスタTr3及びPチャネルMOSトランジスタTr4のゲートに入力される。

【0013】

前記トランジスタTr3は、前記インバータ回路1cを構成するNチャネルMOSトランジスタと電源Vssとの間に介在される。前記トランジスタTr4は、前記出力端子Toと電源Vccとの間に介在される。

【0014】

このように構成された2入力NAND回路の動作を説明すると、入力信号A1, A2がともに「0」となると、ノードN2はHレベルとなり、トランジスタTr3がオンされるとともに、トランジスタTr4がオフされる。また、インバータ回路1cを構成するPチャネルMOSトランジスタがオンされるとともに、NチャネルMOSトランジスタがオフされるため、トランジスタTr3のオン動作に関わらず、出力信号XはHレベルとなる。

【0015】

入力信号A1が「0」、入力信号A2が「1」となると、ノードN2がHレベルとなり、トランジスタTr3がオンされるとともに、トランジスタTr4がオフされる。また、インバータ回路1cを構成するPチャネルMOSトランジスタがオフされるとともに、NチャネルMOSトランジスタがオンされるため、出力信号XはLレベルとなる。

【0016】

10

20

30

40

50

入力信号 A 1 が「1」、入力信号 A 2 が「0」となると、ノード N 2 が L レベルとなり、トランジスタ T r 3 がオフされるとともに、トランジスタ T r 4 がオンされる。また、インバータ回路 1 c を構成する P チャネルMOSトランジスタがオンされて、出力信号 X が H レベルとなる。

【0017】

入力信号 A 1 , A 2 がともに「1」となると、ノード N 2 が L レベルとなり、トランジスタ T r 3 がオフされるとともに、トランジスタ T r 4 がオンされる。従って、インバータ回路 1 c の動作に関わらず、出力信号 X が H レベルとなる。

【0018】

上記のような動作により、この論理回路は図 2 0 に示す真理値に基づく動作を行い、入力信号 A 1 の反転信号であるノード N 2 と入力信号 A 2 との N A N D 論理を出力信号 X として出力し、図 1 9 に示すシンボルで表記される N A N D 回路 3 を構成する。 10

【0019】

上記のような N A N D 回路 3 では、 N A N D 論理を出力するための 4 個のトランジスタと、入力信号 A 1 を反転させるためのインバータ回路 1 d を構成する 2 個のトランジスタとから、計 6 個のトランジスタを必要とする。すなわち、入力数を n とすれば、  $4n - 2$  個のトランジスタを必要とする。

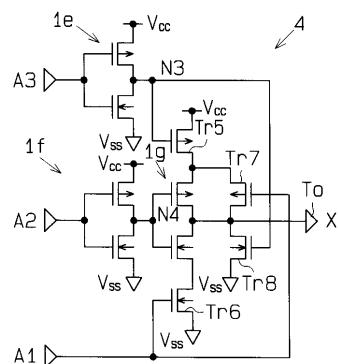

(第三の従来例)

図 2 1 は、 C M O S 構成の 2 w i d e · 2 A N D · 3 入力 · A N D · O R · インバータ回路の従来例を示す。入力信号 A 3 は、 C M O S インバータ回路 1 e に入力され、そのインバータ回路 1 e の出力信号すなわちノード N 3 は、 P チャネルMOSトランジスタ T r 5 及び N チャネルMOSトランジスタ T r 8 のゲートに入力される。 20

【0020】

入力信号 A 2 は、 C M O S インバータ回路 1 f に入力され、そのインバータ回路 1 f の出力信号すなわちノード N 4 は、インバータ回路 1 g に入力される。前記インバータ回路 1 g の出力信号は、出力端子 T o から出力信号 X として出力される。

【0021】

前記トランジスタ T r 5 は、前記インバータ回路 1 g と電源 V c c との間に介在される。前記トランジスタ T r 8 は、出力端子 T o と電源 V s s との間に介在される。入力信号 A 1 は、 N チャネルMOSトランジスタ T r 6 及び P チャネルMOSトランジスタ T r 7 のゲートに入力される。前記トランジスタ T r 6 は、前記インバータ回路 1 g と電源 V s s との間に介在され、前記トランジスタ T r 7 は、前記トランジスタ T r 5 のドレインと、前記出力端子 T o との間に介在される。 30

【0022】

このように構成された A N D · O R · インバータ回路 4 は、図 2 3 に示す真理値に基づく動作を行う。すなわち、入力信号 A 1 , A 2 , A 3 がともに「0」となると、トランジスタ T r 6 がオフされるとともに、トランジスタ T r 7 がオンされる。ノード N 3 は H レベルとなるため、トランジスタ T r 5 はオフされ、トランジスタ T r 8 はオンされる。従って、インバータ回路 1 g は不活性状態となり、トランジスタ T r 8 のオン動作により出力信号 X は L レベルとなる。 40

【0023】

入力信号 A 1 , A 2 , A 3 が「1 , 0 , 0」となると、トランジスタ T r 6 がオンされるとともに、トランジスタ T r 7 がオフされる。ノード N 3 は H レベルとなるため、トランジスタ T r 5 はオフされ、トランジスタ T r 8 はオンされる。ノード N 4 は H レベルとなるため、インバータ回路 1 g の動作及びトランジスタ T r 8 のオン動作により、出力信号 X は L レベルとなる。

【0024】

入力信号 A 1 , A 2 , A 3 が「0 , 1 , 0」となると、トランジスタ T r 6 がオフされるとともに、トランジスタ T r 7 がオンされる。ノード N 3 は H レベルとなるため、トランジスタ T r 5 はオフされ、トランジスタ T r 8 はオンされる。従って、インバータ回路 1 50

g は不活性状態となり、トランジスタ T<sub>r</sub> 8 のオン動作により出力信号 X は L レベルとなる。

【 0 0 2 5 】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「 1 , 1 , 0 」となると、トランジスタ T<sub>r</sub> 6 がオンされるとともに、トランジスタ T<sub>r</sub> 7 がオフされる。ノード N<sub>3</sub> は H レベルとなるため、トランジスタ T<sub>r</sub> 5 はオフされ、トランジスタ T<sub>r</sub> 8 はオンされる。ノード N<sub>4</sub> は L レベルとなるが、トランジスタ T<sub>r</sub> 5 がオフされているため、インバータ回路 1<sub>g</sub> は不活性状態となる。従って、トランジスタ T<sub>r</sub> 8 のオン動作により出力信号 X は L レベルとなる。

【 0 0 2 6 】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「 0 , 0 , 1 」となると、トランジスタ T<sub>r</sub> 6 がオフされるとともに、トランジスタ T<sub>r</sub> 7 がオンされる。ノード N<sub>3</sub> は L レベルとなるため、トランジスタ T<sub>r</sub> 5 はオンされ、トランジスタ T<sub>r</sub> 8 はオフされる。ノード N<sub>4</sub> は H レベルとなるが、トランジスタ T<sub>r</sub> 6 がオフされているため、インバータ回路 1<sub>g</sub> は不活性状態となる。従って、トランジスタ T<sub>r</sub> 5 , T<sub>r</sub> 7 のオン動作により出力信号 X は H レベルとなる。

【 0 0 2 7 】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「 1 , 0 , 1 」となると、トランジスタ T<sub>r</sub> 6 がオンされるとともに、トランジスタ T<sub>r</sub> 7 がオフされる。ノード N<sub>3</sub> は L レベルとなるため、トランジスタ T<sub>r</sub> 5 はオンされ、トランジスタ T<sub>r</sub> 8 はオフされる。ノード N<sub>4</sub> は H レベルとなり、トランジスタ T<sub>r</sub> 6 のオン動作及びインバータ回路 1<sub>g</sub> の動作により、出力信号 X は L レベルとなる。

【 0 0 2 8 】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「 0 , 1 , 1 」となると、トランジスタ T<sub>r</sub> 6 がオフされるとともに、トランジスタ T<sub>r</sub> 7 がオンされる。ノード N<sub>3</sub> は L レベルとなるため、トランジスタ T<sub>r</sub> 5 はオンされ、トランジスタ T<sub>r</sub> 8 はオフされる。ノード N<sub>4</sub> は L レベルとなり、トランジスタ T<sub>r</sub> 5 , T<sub>r</sub> 7 のオン動作及びインバータ回路 1<sub>g</sub> の動作により、出力信号 X は H レベルとなる。

【 0 0 2 9 】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「 1 , 1 , 1 」となると、トランジスタ T<sub>r</sub> 6 がオンされるとともに、トランジスタ T<sub>r</sub> 7 がオフされる。ノード N<sub>3</sub> は L レベルとなるため、トランジスタ T<sub>r</sub> 5 はオンされ、トランジスタ T<sub>r</sub> 8 はオフされる。ノード N<sub>4</sub> は L レベルとなり、トランジスタ T<sub>r</sub> 5 のオン動作及びインバータ回路 1<sub>g</sub> の動作により、出力信号 X は H レベルとなる。

【 0 0 3 0 】

上記のような動作により、この論理回路は図 2 3 に示す真理値に基づく動作を行い、入力信号 A<sub>1</sub> と入力信号 A<sub>2</sub> の反転信号との A N D 論理信号と、入力信号 A<sub>3</sub> の反転信号との N O R 論理が出力信号 X として出力し、図 2 2 に示すシンボルで表記される A N D · O R · インバータ回路 4 を構成する。

【 0 0 3 1 】

上記のような A N D · O R · インバータ回路 4 では、A N D · O R · 反転論理を出力するための 6 個のトランジスタと、入力信号 A<sub>2</sub> , A<sub>3</sub> を反転させるためのインバータ回路 1<sub>e</sub> , 1<sub>f</sub> を構成する 4 個のトランジスタとから、計 10 個のトランジスタを必要とする。

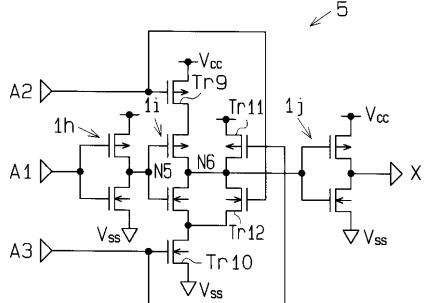

(第四の従来例)

図 2 4 は、C M O S 構成の 2 w i d e · 2 O R · 3 入力 · O R · A N D 回路の従来例を示す。入力信号 A<sub>1</sub> は、C M O S インバータ回路 1<sub>h</sub> に入力され、そのインバータ回路 1<sub>h</sub> の出力信号すなわちノード N<sub>5</sub> は C M O S インバータ回路 1<sub>i</sub> に入力される。

【 0 0 3 2 】

前記インバータ回路 1<sub>i</sub> の出力信号すなわちノード N<sub>6</sub> は、C M O S インバータ回路 1<sub>j</sub> を介して出力信号 X として出力される。

入力信号 A<sub>2</sub> は、P チャネルM O S トランジスタ T<sub>r</sub> 9 及びN チャネルM O S トランジス

タTr12 のゲートに入力される。入力信号A3は、NチャネルMOSトランジスタTr10 及びPチャネルMOSトランジスタTr11 のゲートに入力される。

【0033】

前記トランジスタTr9は、インバータ回路1iと電源Vccとの間に介在され、前記トランジスタTr10 は、インバータ回路1iと電源Vssとの間に介在される。

【0034】

前記トランジスタTr11 は、前記ノードN6と電源Vccとの間に介在され、前記トランジスタTr12 は、ノードN6と前記トランジスタTr10 のドレインとの間に介在される。

【0035】

このように構成されたOR・AND回路は、第三の従来例と同様に、図23に示す真理値に基づく動作を行う。すなわち、入力信号A1, A2, A3がともに「0」となると、ノードN5はHレベルとなる。トランジスタTr9はオンされ、トランジスタTr12 はオフされる。また、トランジスタTr10 はオフされ、トランジスタTr11 はオンされる。

【0036】

トランジスタTr10 がオフされているので、インバータ回路1iは不活性状態となり、トランジスタTr11 のオン動作に基づいて、ノードN6がHレベルとなる。従って、出力信号XはLレベルとなる。

【0037】

入力信号A1, A2, A3が「1, 0, 0」となると、ノードN5はLレベルとなる。トランジスタTr9はオンされ、トランジスタTr12 はオフされる。また、トランジスタTr10 はオフされ、トランジスタTr11 はオンされる。

【0038】

トランジスタTr11 のオン動作及びトランジスタTr9のオン動作に基づくインバータ回路1iの動作によりノードN6はHレベルとなる。従って、出力信号XはLレベルとなる。

【0039】

入力信号A1, A2, A3が「0, 1, 0」となると、ノードN5はHレベルとなる。トランジスタTr9はオフされ、トランジスタTr12 はオンされる。また、トランジスタTr10 はオフされ、トランジスタTr11 はオンされる。

【0040】

トランジスタTr10 のオフ動作により、インバータ回路1iは不活性状態となり、トランジスタTr11 のオン動作によりノードN6はHレベルとなる。従って、出力信号XはLレベルとなる。

【0041】

入力信号A1, A2, A3が「1, 1, 0」となると、ノードN5はLレベルとなる。トランジスタTr9はオフされ、トランジスタTr12 はオンされる。また、トランジスタTr10 はオフされ、トランジスタTr11 はオンされる。

【0042】

トランジスタTr9のオフ動作により、インバータ回路1iは不活性状態となり、トランジスタTr11 のオン動作によりノードN6はHレベルとなる。従って、出力信号XはLレベルとなる。

【0043】

入力信号A1, A2, A3が「0, 0, 1」となると、ノードN5はHレベルとなる。トランジスタTr9はオンされ、トランジスタTr12 はオフされる。また、トランジスタTr10 はオンされ、トランジスタTr11 はオフされる。

【0044】

トランジスタTr10 のオン動作により、インバータ回路1iは活性化され、ノードN6はLレベルとなる。従って、出力信号XはHレベルとなる。

10

20

30

40

50

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「1 , 0 , 1」となると、ノード N<sub>5</sub> は L レベルとなる。トランジスタ T<sub>r 9</sub> はオンされ、トランジスタ T<sub>r 12</sub> はオフされる。また、トランジスタ T<sub>r 10</sub> はオンされ、トランジスタ T<sub>r 11</sub> はオフされる。

【0045】

トランジスタ T<sub>r 9</sub> のオン動作により、インバータ回路 1<sub>i</sub> は活性化され、ノード N<sub>6</sub> は H レベルとなる。従って、出力信号 X は L レベルとなる。

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「0 , 1 , 1」となると、ノード N<sub>5</sub> は H レベルとなる。トランジスタ T<sub>r 9</sub> はオフされ、トランジスタ T<sub>r 12</sub> はオンされる。また、トランジスタ T<sub>r 10</sub> はオンされ、トランジスタ T<sub>r 11</sub> はオフされる。

【0046】

トランジスタ T<sub>r 10</sub> のオン動作により、インバータ回路 1<sub>i</sub> は活性化され、ノード N<sub>6</sub> は L レベルとなる。従って、出力信号 X は H レベルとなる。

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> がともに「1」となると、ノード N<sub>5</sub> は L レベルとなる。トランジスタ T<sub>r 9</sub> はオフされ、トランジスタ T<sub>r 12</sub> はオンされる。また、トランジスタ T<sub>r 10</sub> はオンされ、トランジスタ T<sub>r 11</sub> はオフされる。

【0047】

トランジスタ T<sub>r 9</sub> のオフ動作により、インバータ回路 1<sub>i</sub> は不活性状態となり、トランジスタ T<sub>r 12</sub> , T<sub>r 10</sub> のオン動作によりノード N<sub>6</sub> は L レベルとなる。従って、出力信号 X は H レベルとなる。

【0048】

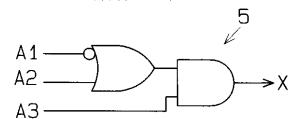

上記のような動作により、この論理回路は第三の従来例と同様に図 2 3 に示す真理値に基づく動作を行い、入力信号 A<sub>1</sub> の反転信号と入力信号 A<sub>2</sub> との OR 論理信号と、入力信号 A<sub>3</sub> との AND 論理を出力信号 X として出力し、図 2 5 に示すシンボルで表記される OR · AND 回路 5 を構成する。

【0049】

上記のような OR · AND 回路 5 では、OR · AND 論理を出力するための 8 個のトランジスタと、入力信号 A<sub>1</sub> を反転させるためのインバータ回路 1<sub>h</sub> を構成する 2 個のトランジスタとから、計 10 個のトランジスタを必要とする。

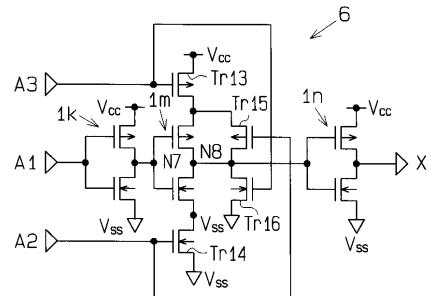

(第五の従来例)

図 2 6 は、CMOS 構成の 2 wide · 2 AND · 3 入力 · AND · OR 回路の従来例を示す。入力信号 A<sub>1</sub> は、CMOS インバータ回路 1<sub>k</sub> に入力され、そのインバータ回路 1<sub>k</sub> の出力信号すなわちノード N<sub>7</sub> は CMOS インバータ回路 1<sub>m</sub> に入力される。

【0050】

前記インバータ回路 1<sub>m</sub> の出力信号すなわちノード N<sub>8</sub> は、CMOS インバータ回路 1<sub>n</sub> を介して出力信号 X として出力される。

入力信号 A<sub>3</sub> は、P チャネル MOS トランジスタ T<sub>r 13</sub> 及び N チャネル MOS トランジスタ T<sub>r 16</sub> のゲートに入力される。入力信号 A<sub>2</sub> は、N チャネル MOS トランジスタ T<sub>r 14</sub> 及び P チャネル MOS トランジスタ T<sub>r 15</sub> のゲートに入力される。

【0051】

前記トランジスタ T<sub>r 13</sub> は、インバータ回路 1<sub>m</sub> と電源 V<sub>cc</sub> との間に介在され、前記トランジスタ T<sub>r 14</sub> は、インバータ回路 1<sub>m</sub> と電源 V<sub>ss</sub> との間に介在される。

【0052】

前記トランジスタ T<sub>r 15</sub> は、ノード N<sub>8</sub> と前記トランジスタ T<sub>r 13</sub> のドレインとの間に介在され、前記トランジスタ T<sub>r 16</sub> は、ノード N<sub>8</sub> と電源 V<sub>ss</sub> との間に介在される。

【0053】

このように構成された AND · OR 回路は、図 2 8 に示す真理値に基づく動作を行う。すなわち、入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> がともに「0」となると、ノード N<sub>7</sub> は H レベルとなる。トランジスタ T<sub>r 13</sub> はオンされ、トランジスタ T<sub>r 16</sub> はオフされる。また、トランジスタ T<sub>r 14</sub> はオフされ、トランジスタ T<sub>r 15</sub> はオンされる。

10

20

30

40

50

## 【0054】

トランジスタTr14がオフされているので、インバータ回路1mは不活性状態となり、トランジスタTr13, Tr15のオン動作に基づいて、ノードN8がHレベルとなる。従って、出力信号XはLレベルとなる。

## 【0055】

入力信号A1, A2, A3が「1, 0, 0」となると、ノードN7はLレベルとなる。トランジスタTr13はオンされ、トランジスタTr16はオフされる。また、トランジスタTr14はオフされ、トランジスタTr15はオンされる。

## 【0056】

トランジスタTr15のオン動作及びトランジスタTr13のオン動作に基づくインバータ回路1mの動作によりノードN8はHレベルとなる。従って、出力信号XはLレベルとなる。 10

## 【0057】

入力信号A1, A2, A3が「0, 1, 0」となると、ノードN7はHレベルとなる。トランジスタTr13はオンされ、トランジスタTr16はオフされる。また、トランジスタTr14はオンされ、トランジスタTr15はオフされる。

## 【0058】

トランジスタTr14のオン動作により、インバータ回路1mは活性状態となり、ノードN8はLレベルとなる。従って、出力信号XはHレベルとなる。

入力信号A1, A2, A3が「1, 1, 0」となると、ノードN7はLレベルとなる。トランジスタTr13はオンされ、トランジスタTr16はオフされる。また、トランジスタTr14はオンされ、トランジスタTr15はオフされる。 20

## 【0059】

トランジスタTr13のオン動作により、インバータ回路1mは活性状態となり、ノードN8はHレベルとなる。従って、出力信号XはLレベルとなる。

入力信号A1, A2, A3が「0, 0, 1」となると、ノードN7はHレベルとなる。トランジスタTr13はオフされ、トランジスタTr16はオンされる。また、トランジスタTr14はオフされ、トランジスタTr15はオンされる。

## 【0060】

トランジスタTr14のオフ動作により、インバータ回路1mは不活性状態となり、トランジスタTr16のオン動作によりノードN8はLレベルとなる。従って、出力信号XはHレベルとなる。 30

## 【0061】

入力信号A1, A2, A3が「1, 0, 1」となると、ノードN7はLレベルとなる。トランジスタTr13はオフされ、トランジスタTr16はオンされる。また、トランジスタTr14はオフされ、トランジスタTr15はオンされる。

## 【0062】

トランジスタTr13のオフ動作により、インバータ回路1mは不活性化され、トランジスタTr16のオン動作によりノードN8はLレベルとなる。従って、出力信号XはHレベルとなる。 40

## 【0063】

入力信号A1, A2, A3が「0, 1, 1」となると、ノードN7はHレベルとなる。トランジスタTr13はオフされ、トランジスタTr16はオンされる。また、トランジスタTr14はオンされ、トランジスタTr15はオフされる。

## 【0064】

トランジスタTr14のオン動作により、インバータ回路1mは活性化され、かつトランジスタTr16がオンされて、ノードN8はLレベルとなる。従って、出力信号XはHレベルとなる。

## 【0065】

入力信号A1, A2, A3がともに「1」となると、ノードN7はLレベルとなる。トラ 50

ンジスタTr13はオフされ、トランジスタTr16はオンされる。また、トランジスタTr14はオンされ、トランジスタTr15はオフされる。

【0066】

トランジスタTr13のオフ動作により、インバータ回路1mは不活性状態となり、トランジスタTr16のオン動作によりノードN8はLレベルとなる。従って、出力信号XはHレベルとなる。

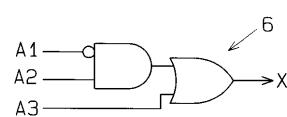

【0067】

上記のような動作により、この論理回路は図28に示す真理値に基づく動作を行い、入力信号A1の反転信号と入力信号A2とのAND論理信号と、入力信号A3とのOR論理を出力信号Xとして出力し、図27に示すシンボルで表記される2wide·2AND·3 10

入力·AND·OR回路6を構成する。

【0068】

上記のようなAND·OR回路6では、AND·OR論理を出力するための8個のトランジスタと、入力信号A1を反転させるためのインバータ回路1kを構成する2個のトランジスタとから、計10個のトランジスタを必要とする。

(第六の従来例)

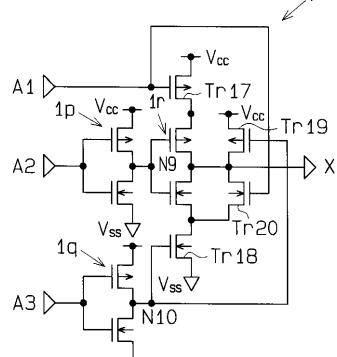

図29は、CMOS構成の2wide·2OR·3入力·OR·AND·インバータ回路の従来例を示す。入力信号A1は、PチャネルMOSトランジスタTr17及びNチャネルMOSトランジスタTr20のゲートに入力される。

【0069】

入力信号A2は、CMOSインバータ回路1pに入力され、そのインバータ回路1pの出力信号すなわちノードN9はCMOSインバータ回路1rに入力される。前記インバータ回路1rの出力信号は、出力信号Xとして出力される。

【0070】

入力信号A3は、CMOSインバータ回路1qに入力され、そのインバータ回路1qの出力信号すなわちノードN10は、PチャネルMOSトランジスタTr19及びNチャネルMOSトランジスタTr18のゲートに入力される。

【0071】

前記トランジスタTr17は、インバータ回路1rと電源Vccとの間に介在され、前記トランジスタTr18は、インバータ回路1rと電源Vssとの間に介在される。

【0072】

前記トランジスタTr19は、電源Vccと前記インバータ回路1rの出力端子との間に介在され、前記トランジスタTr20は、インバータ回路1rの出力端子と前記トランジスタTr18のドレインとの間に介在される。

【0073】

このように構成されたOR·AND·インバータ回路7は、前記第五の従来例と同様に、図28に示す真理値に基づく動作を行う。すなわち、入力信号A1, A2, A3がともに「0」となると、ノードN9, N10はHレベルとなる。トランジスタTr17はオンされ、トランジスタTr20はオフされる。また、トランジスタTr18はオンされ、トランジスタTr19はオフされる。

【0074】

トランジスタTr18がオンされているので、インバータ回路1rは活性状態となる。従って、出力信号XはLレベルとなる。

入力信号A1, A2, A3が「1, 0, 0」となると、ノードN9, N10はHレベルとなる。トランジスタTr17はオフされ、トランジスタTr20はオンされる。また、トランジスタTr18はオンされ、トランジスタTr19はオフされる。

【0075】

トランジスタTr18のオン動作によりインバータ回路1rが活性状態となり、かつトランジスタTr20のオン動作により、出力信号XはLレベルとなる。

入力信号A1, A2, A3が「0, 1, 0」となると、ノードN9はLレベル、ノードN 50

10はHレベルとなる。トランジスタTr17はオンされ、トランジスタTr20はオフされる。また、トランジスタTr18はオンされ、トランジスタTr19はオフされる。

【0076】

トランジスタTr17のオン動作により、インバータ回路1rは活性状態となり、出力信号XはHレベルとなる。

入力信号A1, A2, A3が「1, 1, 0」となると、ノードN9はLレベルとなり、ノードN10はHレベルとなる。トランジスタTr17はオフされ、トランジスタTr20はオンされる。また、トランジスタTr18はオンされ、トランジスタTr19はオフされる。

10

【0077】

トランジスタTr17のオフ動作により、インバータ回路1mは不活性状態となり、トランジスタTr18, Tr20のオン動作により出力信号XはLレベルとなる。

【0078】

入力信号A1, A2, A3が「0, 0, 1」となると、ノードN9はHレベルとなり、ノードN10はLレベルとなる。トランジスタTr17はオンされ、トランジスタTr20はオフされる。また、トランジスタTr18はオフされ、トランジスタTr19はオンされる。

【0079】

トランジスタTr18のオフ動作により、インバータ回路1rは不活性状態となり、トランジスタTr19のオン動作により、出力信号XはHレベルとなる。

20

入力信号A1, A2, A3が「1, 0, 1」となると、ノードN9はHレベルとなり、ノードN10はLレベルとなる。トランジスタTr17はオフされ、トランジスタTr20はオンされる。また、トランジスタTr18はオフされ、トランジスタTr19はオンされる。

【0080】

トランジスタTr18のオフ動作により、インバータ回路1rは不活性化され、トランジスタTr19のオン動作により出力信号XはHレベルとなる。

入力信号A1, A2, A3が「0, 1, 1」となると、ノードN9, N10はLレベルとなる。トランジスタTr17はオンされ、トランジスタTr20はオフされる。また、トランジスタTr18はオフされ、トランジスタTr19はオンされる。

30

【0081】

トランジスタTr17のオン動作により、インバータ回路1rは活性化され、かつトランジスタTr19のオン動作により出力信号XはHレベルとなる。

入力信号A1, A2, A3がともに「1」となると、ノードN9, N10はLレベルとなる。トランジスタTr17はオフされ、トランジスタTr20はオンされる。また、トランジスタTr18はオフされ、トランジスタTr19はオンされる。

【0082】

トランジスタTr17のオフ動作により、インバータ回路1rは不活性状態となり、トランジスタTr19のオン動作により、出力信号XはHレベルとなる。

40

上記のような動作により、この論理回路は前記第五の従来例と同様に、図28に示す真理値に基づく動作を行い、入力信号A1と入力信号A2の反転信号とのOR論理信号と、入力信号A3の反転信号とのAND論理を反転させて、出力信号Xとして出力し、図30に示すシンボルで表記される2 wide · 2 OR · 3 入力 · OR · AND · インバータ回路7を構成する。

【0083】

上記のようなOR · AND · インバータ回路7では、OR · AND · 反転論理を出力するための6個のトランジスタと、入力信号A2, A3を反転させるためのインバータ回路1p, 1qを構成する4個のトランジスタとから、計10個のトランジスタを必要とする。

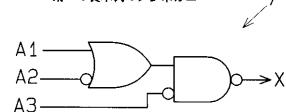

(第七の従来例)

50

図31は、CMOS構成の3入力AND回路の従来例を示す。入力信号A1は、CMOSインバータ回路1sに入力され、そのインバータ回路1sの出力信号であるノードN11は、NチャネルMOSトランジスタTr24及びPチャネルMOSトランジスタTr26のゲートに入力される。

【0084】

入力信号A2は、NチャネルMOSトランジスタTr23及びPチャネルMOSトランジスタTr25のゲートに入力される。

入力信号A3は、PチャネルMOSトランジスタTr21及びNチャネルMOSトランジスタTr22のゲートに入力される。

【0085】

前記トランジスタTr21のソースは、電源Vccに接続され、ドレインはノードN12に接続される。

前記トランジスタTr22のドレインは、前記ノードN12に接続され、ソースは前記トランジスタTr23のドレインに接続される。前記トランジスタTr23のソースは、前記トランジスタTr24のドレインに接続され、同トランジスタTr24のソースは電源Vssに接続される。

【0086】

前記トランジスタTr25のソースは、電源Vccに接続され、ドレインはノードN12に接続される。前記トランジスタTr26のソースは、電源Vccに接続され、ドレインはノードN12に接続される。

【0087】

前記ノードN12は、CMOSインバータ回路1tに入力され、そのインバータ回路1tから出力信号Xが出力される。

このように構成されたAND回路8は、図33に示す真理値に基づく動作を行う。すなわち、入力信号A1, A2, A3がともに「0」となると、ノードN11はHレベルとなる。トランジスタTr24はオンされ、トランジスタTr26はオフされる。トランジスタTr23はオフされ、トランジスタTr25はオンされる。また、トランジスタTr21はオンされ、トランジスタTr22はオフされる。従って、ノードN12はHレベルとなり、出力信号XはLレベルとなる。

【0088】

入力信号A1, A2, A3が「1, 0, 0」となると、ノードN11はLレベルとなる。トランジスタTr24はオフされ、トランジスタTr26はオンされる。トランジスタTr23はオフされ、トランジスタTr25はオンされる。また、トランジスタTr21はオンされ、トランジスタTr22はオフされる。従って、ノードN12はHレベルとなり、出力信号XはLレベルとなる。

【0089】

入力信号A1, A2, A3が「0, 1, 0」となると、ノードN11はHレベルとなる。トランジスタTr24はオンされ、トランジスタTr26はオフされる。トランジスタTr23はオンされ、トランジスタTr25はオフされる。また、トランジスタTr21はオンされ、トランジスタTr22はオフされる。従って、ノードN12はHレベルとなり、出力信号XはLレベルとなる。

【0090】

入力信号A1, A2, A3が「1, 1, 0」となると、ノードN11はLレベルとなる。トランジスタTr24はオフされ、トランジスタTr26はオンされる。トランジスタTr23はオンされ、トランジスタTr25はオフされる。また、トランジスタTr21はオンされ、トランジスタTr22はオフされる。従って、ノードN12はHレベルとなり、出力信号XはLレベルとなる。

【0091】

入力信号A1, A2, A3が「0, 0, 1」となると、ノードN11はHレベルとなる。トランジスタTr24はオンされ、トランジスタTr26はオフされる。トランジス

10

20

30

40

50

トランジスタ Tr 23 はオフされ、トランジスタ Tr 25 はオンされる。また、トランジスタ Tr 21 はオフされ、トランジスタ Tr 22 はオンされる。従って、ノード N12 は H レベルとなり、出力信号 X は L レベルとなる。

【0092】

入力信号 A1, A2, A3 が「1, 0, 1」となると、ノード N11 は L レベルとなる。トランジスタ Tr 24 はオフされ、トランジスタ Tr 26 はオンされる。トランジスタ Tr 23 はオフされ、トランジスタ Tr 25 はオンされる。また、トランジスタ Tr 21 はオフされ、トランジスタ Tr 22 はオンされる。従って、ノード N12 は H レベルとなり、出力信号 X は L レベルとなる。

【0093】

入力信号 A1, A2, A3 が「0, 1, 1」となると、ノード N11 は H レベルとなる。トランジスタ Tr 24 はオンされ、トランジスタ Tr 26 はオフされる。トランジスタ Tr 23 はオンされ、トランジスタ Tr 25 はオフされる。また、トランジスタ Tr 21 はオフされ、トランジスタ Tr 22 はオンされる。従って、ノード N12 は L レベルとなり、出力信号 X は H レベルとなる。

【0094】

入力信号 A1, A2, A3 がともに「1」となると、ノード N11 は L レベルとなる。トランジスタ Tr 24 はオフされ、トランジスタ Tr 26 はオンされる。トランジスタ Tr 23 はオンされ、トランジスタ Tr 25 はオフされる。また、トランジスタ Tr 21 はオフされ、トランジスタ Tr 22 はオンされる。従って、ノード N12 は H レベルとなり、出力信号 X は L レベルとなる。

【0095】

上記のような動作により、この論理回路は図 33 に示す真理値に基づく動作を行い、入力信号 A1 の反転信号及び入力信号 A2, A3 の AND 論理信号を出力信号 X として出力し、図 32 に示すシンボルで表記される 3 入力 AND 回路 8 を構成する。

【0096】

上記のような AND 回路 8 では、AND 論理を出力するための 8 個のトランジスタと、入力信号 A1 を反転させるためのインバータ回路 1s を構成する 2 個のトランジスタとから、計 10 個のトランジスタを必要とする。

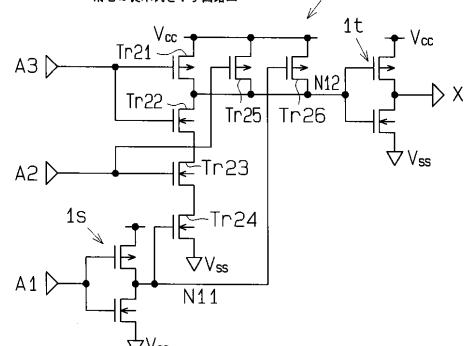

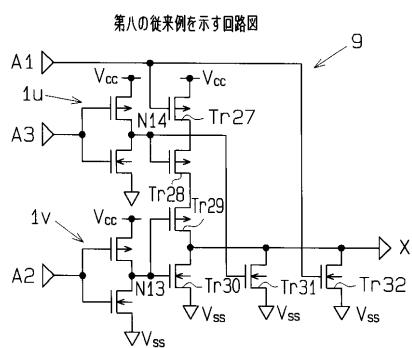

(第八の従来例)

図 34 は、CMOS 構成の 3 入力 NOR 回路の従来例を示す。入力信号 A1 は、P チャネル MOS トランジスタ Tr 27 及び N チャネル MOS トランジスタ Tr 32 のゲートに入力される。

【0097】

入力信号 A2 は、CMOS インバータ回路 1v に入力され、その出力信号であるノード N13 は、P チャネル MOS トランジスタ Tr 29 及び N チャネル MOS トランジスタ Tr 30 のゲートに入力される。

【0098】

入力信号 A3 は、CMOS インバータ回路 1u に入力され、その出力信号であるノード N14 は、P チャネル MOS トランジスタ Tr 28 及び N チャネル MOS トランジスタ Tr 31 のゲートに入力される。

【0099】

前記トランジスタ Tr 27 のソースは、電源 Vcc に接続され、ドレインは前記トランジスタ Tr 28 のソースに接続される。前記トランジスタ Tr 28 のドレインは、前記トランジスタ Tr 29 のソースに接続され、そのトランジスタ Tr 29 のドレインは、前記トランジスタ Tr 30 のドレインに接続される。前記トランジスタ Tr 30 のソースは電源 Vss に接続される。

前記トランジスタ Tr 31 のドレインは、前記トランジスタ Tr 29, Tr 30 のドレインに接続され、トランジスタ Tr 31 のソースは電源 Vss に接続される。前記トランジスタ Tr 32 のドレインは、前記トランジスタ Tr 29, Tr 30 のドレ

10

20

30

40

50

インに接続され、トランジスタ Tr 32 のソースは電源 Vss に接続される。

【0100】

このように構成された NOR 回路 9 は、前記第七の従来例と同様に、図 33 に示す真理値に基づく動作を行う。すなわち、入力信号 A1, A2, A3 がともに「0」となると、ノード N13, 14 は H レベルとなる。トランジスタ Tr 27 はオンされ、トランジスタ Tr 32 はオフされる。

【0101】

トランジスタ Tr 30 はオンされ、トランジスタ Tr 29 はオフされる。トランジスタ Tr 28 はオフされ、トランジスタ Tr 31 はオンされる。従って、出力信号 X は L レベルとなる。

10

【0102】

入力信号 A1, A2, A3 が「1, 0, 0」となると、ノード N13, 14 は H レベルとなる。トランジスタ Tr 27 はオフされ、トランジスタ Tr 32 はオンされる。

【0103】

トランジスタ Tr 30 はオンされ、トランジスタ Tr 29 はオフされる。トランジスタ Tr 28 はオフされ、トランジスタ Tr 31 はオンされる。従って、出力信号 X は L レベルとなる。

【0104】

入力信号 A1, A2, A3 が「0, 1, 0」となると、ノード N13 は L レベル、ノード N14 は H レベルとなる。トランジスタ Tr 27 はオンされ、トランジスタ Tr 32 はオフされる。

20

【0105】

トランジスタ Tr 30 はオフされ、トランジスタ Tr 29 はオンされる。トランジスタ Tr 28 はオフされ、トランジスタ Tr 31 はオンされる。従って、出力信号 X は L レベルとなる。

【0106】

入力信号 A1, A2, A3 が「1, 1, 0」となると、ノード N13 は L レベル、ノード N14 は H レベルとなる。トランジスタ Tr 27 はオフされ、トランジスタ Tr 32 はオンされる。

【0107】

トランジスタ Tr 30 はオフされ、トランジスタ Tr 29 はオンされる。トランジスタ Tr 28 はオフされ、トランジスタ Tr 31 はオンされる。従って、出力信号 X は L レベルとなる。

30

【0108】

入力信号 A1, A2, A3 が「0, 0, 1」となると、ノード N13 は H レベル、ノード N14 は L レベルとなる。トランジスタ Tr 27 はオンされ、トランジスタ Tr 32 はオフされる。

【0109】

トランジスタ Tr 30 はオンされ、トランジスタ Tr 29 はオフされる。トランジスタ Tr 28 はオンされ、トランジスタ Tr 31 はオフされる。従って、出力信号 X は L レベルとなる。

40

【0110】

入力信号 A1, A2, A3 が「1, 0, 1」となると、ノード N13 は H レベル、ノード N14 は L レベルとなる。トランジスタ Tr 27 はオフされ、トランジスタ Tr 32 はオンされる。

【0111】

トランジスタ Tr 30 はオンされ、トランジスタ Tr 29 はオフされる。トランジスタ Tr 28 はオンされ、トランジスタ Tr 31 はオフされる。従って、出力信号 X は L レベルとなる。

【0112】

50

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「0 , 1 , 1」となると、ノード N<sub>13</sub> , 14 は L レベルとなる。トランジスタ T<sub>r 27</sub> はオンされ、トランジスタ T<sub>r 32</sub> はオフされる。

【0113】

トランジスタ T<sub>r 30</sub> はオフされ、トランジスタ T<sub>r 29</sub> はオンされる。トランジスタ T<sub>r 28</sub> はオンされ、トランジスタ T<sub>r 31</sub> はオフされる。従って、出力信号 X は H レベルとなる。

【0114】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> がともに「1」となると、ノード N<sub>13</sub> , 14 は L レベルとなる。トランジスタ T<sub>r 27</sub> はオフされ、トランジスタ T<sub>r 32</sub> はオンされる。

【0115】

トランジスタ T<sub>r 30</sub> はオフされ、トランジスタ T<sub>r 29</sub> はオンされる。トランジスタ T<sub>r 28</sub> はオンされ、トランジスタ T<sub>r 31</sub> はオフされる。従って、出力信号 X は L レベルとなる。

【0116】

上記のような動作により、この論理回路は図 33 に示す真理値に基づく動作を行い、入力信号 A<sub>2</sub> , A<sub>3</sub> の反転信号及び入力信号 A<sub>1</sub> の NOR 論理信号を出力信号 X として出力し、図 35 に示すシンボルで表記される 3 入力 NOR 回路 9 を構成する。

【0117】

上記のような NOR 回路 9 では、NOR 論理を出力するための 6 個のトランジスタと、入力信号 A<sub>2</sub> , A<sub>3</sub> を反転させるためのインバータ回路 1v , 1u を構成する 4 個のトランジスタとから、計 10 個のトランジスタを必要とする。

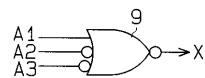

(第九の従来例)

図 36 は、CMOS 構成の 3 入力 OR 回路の従来例を示す。入力信号 A<sub>1</sub> は、インバータ回路 1w に入力され、そのインバータ回路 1w の出力信号であるノード N<sub>15</sub> は、P チャネル MOS トランジスタ T<sub>r 35</sub> 及び N チャネル MOS トランジスタ T<sub>r 36</sub> のゲートに入力される。

【0118】

入力信号 A<sub>2</sub> は、P チャネル MOS トランジスタ T<sub>r 34</sub> 及び N チャネル MOS トランジスタ T<sub>r 37</sub> のゲートに入力される。

入力信号 A<sub>3</sub> は、P チャネル MOS トランジスタ T<sub>r 33</sub> 及び N チャネル MOS トランジスタ T<sub>r 38</sub> のゲートに入力される。

【0119】

前記トランジスタ T<sub>r 33</sub> のソースは、電源 V<sub>cc</sub> に接続され、ドレインは前記トランジスタ T<sub>r 34</sub> のソースに接続される。前記トランジスタ T<sub>r 34</sub> のドレインは、前記トランジスタ T<sub>r 35</sub> のソースに接続され、そのトランジスタ T<sub>r 35</sub> のドレインは、前記トランジスタ T<sub>r 36</sub> のドレインすなわちノード N<sub>16</sub> に接続される。前記トランジスタ T<sub>r 36</sub> のソースは電源 V<sub>ss</sub> に接続される。

【0120】

前記トランジスタ T<sub>r 37</sub> , T<sub>r 38</sub> のドレインは、ノード N<sub>16</sub> に接続され、同トランジスタ T<sub>r 37</sub> , T<sub>r 38</sub> のソースは電源 V<sub>ss</sub> に接続される。ノード N<sub>16</sub> は、CMOS インバータ回路 1x に入力され、そのインバータ回路 1x から出力信号 X が出力される。

【0121】

このように構成された OR 回路 10 は、図 38 に示す真理値に基づく動作を行う。すなわち、入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> がともに「0」となると、ノード N<sub>15</sub> は H レベルとなる。トランジスタ T<sub>r 36</sub> はオンされ、トランジスタ T<sub>r 35</sub> はオフされる。

【0122】

トランジスタ T<sub>r 34</sub> はオンされ、トランジスタ T<sub>r 37</sub> はオフされる。トランジスタ T<sub>r 33</sub> はオンされ、トランジスタ T<sub>r 38</sub> はオフされる。従って、ノード N<sub>16</sub> は L レベルとなり、出力信号 X は H レベルとなる。

## 【0123】

入力信号 A1, A2, A3 が「1, 0, 0」となると、ノード N15 は L レベルとなる。トランジスタ Tr36 はオフされ、トランジスタ Tr35 はオンされる。トランジスタ Tr34 はオンされ、トランジスタ Tr37 はオフされる。トランジスタ Tr33 はオンされ、トランジスタ Tr38 はオフされる。従って、ノード N16 は H レベルとなり、出力信号 X は L レベルとなる。

## 【0124】

入力信号 A1, A2, A3 が「0, 1, 0」となると、ノード N15 は H レベルとなる。トランジスタ Tr36 はオンされ、トランジスタ Tr35 はオフされる。トランジスタ Tr34 はオフされ、トランジスタ Tr37 はオンされる。トランジスタ Tr33 10 はオンされ、トランジスタ Tr38 はオフされる。従って、ノード N16 は L レベルとなり、出力信号 X は H レベルとなる。

## 【0125】

入力信号 A1, A2, A3 が「1, 1, 0」となると、ノード N15 は L レベルとなる。トランジスタ Tr36 はオフされ、トランジスタ Tr35 はオンされる。トランジスタ Tr34 はオフされ、トランジスタ Tr37 はオンされる。トランジスタ Tr33 はオンされ、トランジスタ Tr38 はオフされる。従って、ノード N16 は L レベルとなり、出力信号 X は H レベルとなる。

## 【0126】

入力信号 A1, A2, A3 が「0, 0, 1」となると、ノード N15 は H レベルとなる。トランジスタ Tr36 はオンされ、トランジスタ Tr35 はオフされる。トランジスタ Tr34 はオンされ、トランジスタ Tr37 はオフされる。トランジスタ Tr33 20 はオフされ、トランジスタ Tr38 はオンされる。従って、ノード N16 は L レベルとなり、出力信号 X は H レベルとなる。

## 【0127】

入力信号 A1, A2, A3 が「1, 0, 1」となると、ノード N15 は L レベルとなる。トランジスタ Tr36 はオフされ、トランジスタ Tr35 はオンされる。トランジスタ Tr34 はオンされ、トランジスタ Tr37 はオフされる。トランジスタ Tr33 30 はオフされ、トランジスタ Tr38 はオンされる。従って、ノード N16 は L レベルとなり、出力信号 X は H レベルとなる。

## 【0128】

入力信号 A1, A2, A3 が「0, 1, 1」となると、ノード N15 は H レベルとなる。トランジスタ Tr36 はオンされ、トランジスタ Tr35 はオフされる。トランジスタ Tr34 はオフされ、トランジスタ Tr37 はオンされる。トランジスタ Tr33 はオフされ、トランジスタ Tr38 はオンされる。従って、ノード N16 は L レベルとなり、出力信号 X は H レベルとなる。

## 【0129】

入力信号 A1, A2, A3 がともに「1」となると、ノード N15 は L レベルとなる。トランジスタ Tr36 はオフされ、トランジスタ Tr35 はオンされる。トランジスタ Tr34 はオフされ、トランジスタ Tr37 はオンされる。トランジスタ Tr33 40 はオフされ、トランジスタ Tr38 はオンされる。従って、ノード N16 は L レベルとなり、出力信号 X は H レベルとなる。

## 【0130】

上記のような動作により、この論理回路は図 38 に示す真理値に基づく動作を行い、入力信号 A1 の反転信号及び入力信号 A2, A3 の OR 論理信号を出力信号 X として出力し、図 37 に示すシンボルで表記される 3 入力 OR 回路 10 を構成する。

## 【0131】

上記のような OR 回路 10 では、OR 論理を出力するための 8 個のトランジスタと、入力信号 A1 を反転させるためのインバータ回路 1w を構成する 2 個のトランジスタとから、計 10 個のトランジスタを必要とする。

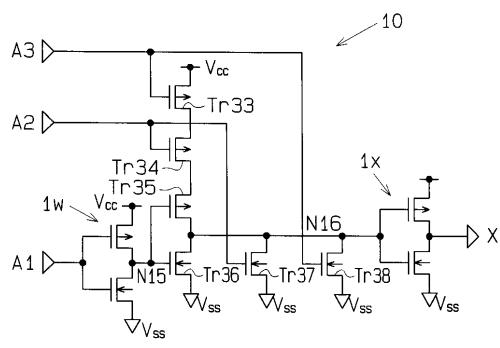

(第十の従来例)

図39は、CMOS構成の3入力NAND回路の従来例を示す。入力信号A1は、PチャネルMOSトランジスタTr39 及びNチャネルMOSトランジスタTr40 のゲートに入力される。

【0132】

入力信号A2は、CMOSインバータ回路1yに入力され、そのインバータ回路1yの出力信号であるノードN17は、NチャネルMOSトランジスタTr41 及びPチャネルMOSトランジスタTr43 のゲートに入力される。

【0133】

入力信号A3は、CMOSインバータ回路1zに入力され、そのインバータ回路1zの出力信号であるノードN18は、NチャネルMOSトランジスタTr42 及びPチャネルMOSトランジスタTr44 のゲートに入力される。 10

【0134】

前記トランジスタTr39 のソースは、電源Vccに接続され、ドレインは前記トランジスタTr40 のドレインに接続される。前記トランジスタTr40 のソースは、前記トランジスタTr41 のドレインに接続され、そのトランジスタTr41 のソースは、前記トランジスタTr42 のドレインに接続される。前記トランジスタTr42 のソースは電源Vssに接続される。

【0135】

前記トランジスタTr43 , Tr44 のソースは、電源Vccに接続され、ドレインは前記トランジスタTr39 , Tr40 のドレインに接続される。そして、前記トランジスタTr39 , Tr40 , Tr43 , Tr44 のドレインから出力信号Xが出力される。 20

【0136】

このように構成されたNAND回路11は、前記第九の従来例と同様に、図38に示す真理値に基づく動作を行う。すなわち、入力信号A1 , A2 , A3がともに「0」となると、ノードN17 , 18はHレベルとなる。トランジスタTr39 はオンされ、トランジスタTr40 はオフされる。

【0137】

トランジスタTr41 はオンされ、トランジスタTr43 はオフされる。トランジスタTr42 はオンされ、トランジスタTr44 はオフされる。従って、出力信号XはHレベルとなる。 30

【0138】

入力信号A1 , A2 , A3が「1 , 0 , 0」となると、ノードN17 , 18はHレベルとなる。トランジスタTr39 はオフされ、トランジスタTr40 はオンされる。

【0139】

トランジスタTr41 はオンされ、トランジスタTr43 はオフされる。トランジスタTr42 はオンされ、トランジスタTr44 はオフされる。従って、出力信号XはLレベルとなる。

【0140】

入力信号A1 , A2 , A3が「0 , 1 , 0」となると、ノードN17はLレベル、ノードN18はHレベルとなる。トランジスタTr39 はオンされ、トランジスタTr40 はオフされる。 40

【0141】

トランジスタTr41 はオフされ、トランジスタTr43 はオンされる。トランジスタTr42 はオンされ、トランジスタTr44 はオフされる。従って、出力信号XはHレベルとなる。

【0142】

入力信号A1 , A2 , A3が「1 , 1 , 0」となると、ノードN17はLレベル、ノードN18はHレベルとなる。トランジスタTr39 はオフされ、トランジスタTr40 50

はオンされる。

【0143】

トランジスタTr41はオフされ、トランジスタTr43はオンされる。トランジスタTr42はオンされ、トランジスタTr44はオフされる。従って、出力信号XはHレベルとなる。

【0144】

入力信号A1, A2, A3が「0, 0, 1」となると、ノードN17はHレベル、ノードN18はLレベルとなる。トランジスタTr39はオンされ、トランジスタTr40はオフされる。

【0145】

トランジスタTr41はオンされ、トランジスタTr43はオフされる。トランジスタTr42はオフされ、トランジスタTr44はオンされる。従って、出力信号XはHレベルとなる。

【0146】

入力信号A1, A2, A3が「1, 0, 1」となると、ノードN17はHレベル、ノードN18はLレベルとなる。トランジスタTr39はオフされ、トランジスタTr40はオンされる。

【0147】

トランジスタTr41はオンされ、トランジスタTr43はオフされる。トランジスタTr42はオフされ、トランジスタTr44はオンされる。従って、出力信号XはHレベルとなる。

【0148】

入力信号A1, A2, A3が「0, 1, 1」となると、ノードN17, 18はLレベルとなる。トランジスタTr39はオンされ、トランジスタTr40はオフされる。

【0149】

トランジスタTr41はオフされ、トランジスタTr43はオンされる。トランジスタTr42はオフされ、トランジスタTr44はオンされる。従って、出力信号XはHレベルとなる。

【0150】

入力信号A1, A2, A3がともに「1」となると、ノードN17, 18はLレベルとなる。トランジスタTr39はオフされ、トランジスタTr40はオンされる。

【0151】

トランジスタTr41はオフされ、トランジスタTr43はオンされる。トランジスタTr42はオフされ、トランジスタTr44はオンされる。従って、出力信号XはHレベルとなる。

【0152】

上記のような動作により、この論理回路は前記第九の従来例と同様に、図38に示す真理値に基づく動作を行い、入力信号A1及び入力信号A2, A3の反転信号のNAND論理信号を出力信号Xとして出力し、図40に示すシンボルで表記される3入力NAND回路11を構成する。

【0153】

上記のようなNAND回路11では、NAND論理を出力するための6個のトランジスタと、入力信号A2, A3を反転させるためのインバータ回路1y, 1zを構成する4個のトランジスタとから、計10個のトランジスタを必要とする。

【0154】

【発明が解決しようとする課題】

上記各従来例では、2入力の場合には6個のトランジスタを必要とし、3入力の場合には10個のトランジスタを必要とする。一般的には、入力数をnとすれば、4n-2個のトランジスタを必要とする。従って、各回路の素子数が多く、このような論理回路を多数使用する半導体集積回路装置のチップ面積が増大する。

10

20

40

50

## 【0155】

また、各従来例では少なくとも1つのインバータ回路を備えており、これらのインバータ回路の入力信号の反転動作時には、電源Vccから電源Vssへ貫通電流が流れる。

## 【0156】

従って、このような論理回路を多数使用する半導体集積回路装置の消費電力が増大するという問題点がある。

この発明の目的は、素子数を削減して回路面積を縮小し得る論理回路を提供することにある。また、論理回路を構成するインバータ回路の数を削減して、消費電力を低減し得るCMOS論理回路を提供することにある。

## 【0157】

10

## 【課題を解決するための手段】

請求項1では、高電位側電源に接続されているPチャネルMOSトランジスタ及び該PチャネルMOSトランジスタと低電位側電源との間に接続されているNチャネルMOSトランジスタを含む複数のMOSトランジスタで論理回路が構成され、複数の入力信号に基づいて所定論理の出力信号が出力される。複数の入力信号の内の一つの入力信号が前記複数のMOSトランジスタの内の一つのNチャネルMOSトランジスタのソース又はドレインに入力され、前記複数の入力信号の内の他の入力信号が前記複数のMOSトランジスタのゲートに入力されて、前記一つの入力信号と一つの電源とのいずれかのレベルを出力信号として出力する。前記出力信号を高電位側電源と低電位側電源との範囲でフル振幅で動作させる出力信号安定化回路が備えられる。

20

## 【0158】

請求項2では、高電位側電源に接続されているPチャネルMOSトランジスタ及び該PチャネルMOSトランジスタと低電位側電源との間に接続されているNチャネルMOSトランジスタを含む複数のMOSトランジスタで論理回路が構成され、n個(nは2以上の整数)の入力信号に基づいて所定論理の出力信号が出力される。複数の入力信号の内の一つの入力信号が前記複数のMOSトランジスタの内の一つのNチャネルMOSトランジスタのソース又はドレインに入力され、前記複数の入力信号の内の他の入力信号が前記複数のMOSトランジスタのゲートに入力されて、2n-2個のトランジスタで所望論理の出力信号を出力する。前記出力信号を高電位側電源と低電位側電源との範囲でフル振幅で動作させる出力信号安定化回路が備えられる。

30

## 【0159】

請求項3では、高電位側電源に接続されているPチャネルMOSトランジスタ及び該PチャネルMOSトランジスタと低電位側電源との間に接続されているNチャネルMOSトランジスタを含む複数のMOSトランジスタで論理回路が構成され、複数の入力信号に基づいて所定論理の出力信号が出力される。複数の入力信号の内の一つの入力信号が前記複数のMOSトランジスタの内の一つのNチャネルMOSトランジスタのソース又はドレインに入力され、前記複数の入力信号の内の他の入力信号が前記複数のMOSトランジスタのゲートに入力されて、高電位側電源及び低電位側電源が供給されるインバータ回路を使用することなく所望論理の出力信号を出力する。前記出力信号を高電位側電源と低電位側電源との範囲でフル振幅で動作させる出力信号安定化回路が備えられる。

40

## 【0160】

請求項4では、前記論理回路を、所望論理の反転信号を出力する論理回路とし、前記出力信号安定化回路は、前記反転信号を反転させて出力するインバータ回路と、前記インバータ回路の出力信号に基づいて前記反転信号を電源電圧レベルとするMOSトランジスタとを備える。

## 【0161】

## (作用)

請求項1では、一つの入力信号と、一つの電源とのいずれかのレベルが、他の入力信号に基づく所望論理の出力信号として出力され、その出力信号が出力信号安定化回路によりフル振幅で出力される。

50

## 【0162】

請求項2では、入力信号の数をnとしたとき、2n-2個のトランジスタで、前記一つの入力信号と、一つの電源とのいずれかのレベルが、前記入力信号に基づく所望論理の出力信号として出力され、その出力信号が出力信号安定化回路によりフル振幅で出力される。

## 【0163】

請求項3では、インバータ回路を使用することなく、前記一つの入力信号と、一つの電源とのいずれかのレベルが、前記入力信号に基づく所望論理の出力信号として出力され、その出力信号が出力信号安定化回路によりフル振幅で出力される。

## 【0164】

請求項4では、前記論理回路から所望論理の反転信号が出力され、その反転信号が前記出力信号安定化回路により反転され、かつ電源電圧レベルとされる。

## 【0165】

## 【発明の実施の形態】

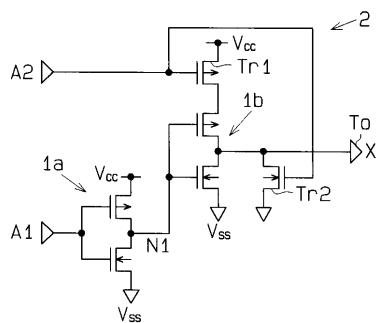

## (第一の実施の形態)

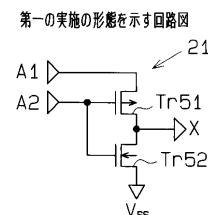

図2は、この発明を具体化したCMOS論理回路の第一の実施の形態を示す。この実施の形態は、前記第一の従来例と同様に2入力NOR回路を構成する。

## 【0166】

入力信号A1は、PチャネルMOSトランジスタTr51のソース(ドレイン)に入力され、入力信号A2は前記トランジスタTr51及びNチャネルMOSトランジスタTr52のゲートに入力される。

## 【0167】

前記トランジスタTr52のソースは、電源Vssに接続され、ドレインは前記トランジスタTr51のドレイン(ソース)に接続される。そして、前記トランジスタTr52のドレイン及びトランジスタTr51のドレイン(ソース)から出力信号Xが出力される。

## 【0168】

このように構成された2入力NOR回路21では、入力信号A1, A2がともに「0」となると、トランジスタTr51がオンされるとともに、トランジスタTr52がオフされる。従って、入力信号A1がトランジスタTr51を介して出力信号Xとして出力されるので、出力信号XはLレベルとなる。

## 【0169】

入力信号A1が「0」、入力信号A2が「1」となると、トランジスタTr51がオフされるとともに、トランジスタTr52がオンされる。従って、出力信号XはLレベルとなる。

## 【0170】

入力信号A1が「1」、入力信号A2が「0」となると、トランジスタTr51がオンされるとともに、トランジスタTr52がオフされる。従って、入力信号A1がトランジスタTr51を介して出力信号Xとして出力されるので、出力信号XはHレベルとなる。

## 【0171】

入力信号A1, A2がともに「1」となると、トランジスタTr51がオフされるとともに、トランジスタTr52がオンされる。従って、出力信号XはLレベルとなる。

## 【0172】

上記のような動作により、この論理回路は前記第一の従来例と同様に、図17に示す真理値に基づく動作を行い、入力信号A1の反転信号と入力信号A2とのNOR論理信号を出力信号Xとして出力し、図16に示すシンボルで表記される2入力NOR回路を構成する。

## 【0173】

上記のような2入力NOR回路21では、次に示す作用効果を得ることができる。

(イ) 2個のMOSトランジスタにより、2入力NOR回路21が構成されるので、前記

10

20

30

40

50

第一の従来例に比して素子数を削減することができる。従って、回路面積を縮小することができる。

(ロ) インバータ回路を必要としないので、入力信号 A1, A2 の反転時にも電源 Vcc から電源 Vss への貫通電流は生じない。従って、消費電力を低減することができる。

(ハ) 上記のような 2 入力 NOR 回路 21 を多数搭載する半導体集積回路装置のチップ面積を縮小することができる。

(ニ) 上記のような 2 入力 NOR 回路 21 を多数搭載する半導体集積回路装置の消費電力を低減することができる。

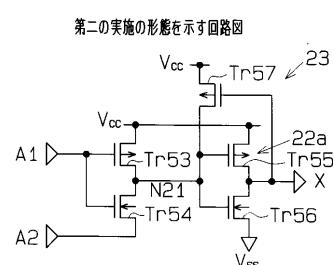

(第二の実施の形態)

図 3 は、この発明を具体化した CMOS 論理回路の第二の実施の形態を示し、前記第一の 10 実施の形態と同様に 2 入力 NOR 回路を構成する。

【0174】

前記 2 入力 NOR 回路 21 では、トランジスタ Tr51 がオンされ、かつ入力信号 A1 が「0」となって、出力信号 X が L レベルとなるとき、その出力信号 X は入力信号 A1 よりトランジスタ Tr51 のしきい値分高いレベルまでしか低下しない。従って、入力信号 A1 として電源 Vss レベルが入力されても、L レベルの出力信号 X を電源 Vss レベルまで引き下げることができない。この実施の形態は、出力信号 X を電源 Vcc レベルと電源 Vss レベルとの間で確実にフル振幅動作させる構成としたものである。

【0175】

入力信号 A2 は、N チャネル MOS トランジスタ Tr54 のソース(ドレイン)に入力 20 される。入力信号 A1 は、前記トランジスタ Tr54 及び P チャネル MOS トランジスタ Tr53 のゲートに入力される。

【0176】

前記トランジスタ Tr53 のソースは、電源 Vcc に接続され、ドレインは前記トランジスタ Tr54 のドレイン(ソース)に接続され、ノード N21 を構成する。

前記ノード N21 は、インバータ回路 22a に入力され、そのインバータ回路 22a から出力信号 X が出力される。また、出力信号 X は P チャネル MOS トランジスタ Tr57 のゲートに入力され、そのトランジスタ Tr57 のソースは電源 Vcc に接続され、ドレインはノード N21 に接続される。

【0177】

このように構成された 2 入力 NOR 回路 23 では、入力信号 A1, A2 がともに「0」となると、トランジスタ Tr53 がオンされるとともに、トランジスタ Tr54 がオフされて、ノード N21 が H レベルとなる。従って、出力信号 X は L レベルとなる。

【0178】

入力信号 A1 が「0」、入力信号 A2 が「1」となると、トランジスタ Tr53 がオンされるとともに、トランジスタ Tr54 がオフされて、ノード N21 が H レベルとなる。従って、出力信号 X は L レベルとなる。

【0179】

入力信号 A1 が「1」、入力信号 A2 が「0」となると、トランジスタ Tr53 がオフされるとともに、トランジスタ Tr54 がオンされて、ノード N21 が L レベルとなる。従って、出力信号 X は H レベルとなる。

【0180】

入力信号 A1, A2 がともに「1」となると、トランジスタ Tr53 がオフされるとともに、トランジスタ Tr54 がオンされて、ノード N21 が H レベルとなり、出力信号 X が L レベルとなる。

【0181】

このとき、ノード N21 は入力信号 A1 よりトランジスタ Tr54 のしきい値分低いレベルまでしか上昇しないが、インバータ回路 22a の出力信号 X と電源 Vcc との電位差がトランジスタ Tr57 のしきい値以上となれば、トランジスタ Tr57 がオンされて、ノード N21 がほぼ電源 Vcc レベルまで引き上げられる。従って、出力信号 X は電

10

20

30

40

50

源 V<sub>SS</sub> レベルまで確実に引き下げられるので、出力信号 X を電源 V<sub>CC</sub> レベルと電源 V<sub>SS</sub> レベルとの間で確実にフル振幅動作させることができる。

#### 【 0182 】

上記のような動作により、この論理回路は前記第一の従来例と同様に、図 17 に示す真理値に基づく動作を行い、入力信号 A<sub>1</sub> の反転信号と入力信号 A<sub>2</sub> との NOR 論理信号を出力信号 X として出力し、図 16 に示すシンボルで表記される 2 入力 NOR 回路を構成する。

#### 【 0183 】

上記のような 2 入力 NOR 回路 23 では、次に示す作用効果を得ることができる。

(イ) 5 個の MOS トランジスタにより、2 入力 NOR 回路 23 が構成されるので、前記第一の従来例に比して素子数を削減することができる。従って、回路面積を縮小することができる。

(ロ) 上記のような 2 入力 NOR 回路 23 を多数搭載する半導体集積回路装置のチップ面積を縮小することができる。

(ハ) トランジスタ Tr57 及びインバータ回路 22a で構成される出力信号安定化回路の動作により、第一の実施の形態に比して、入力信号 A<sub>1</sub>, A<sub>2</sub> の振幅が小さくなつても、出力信号 X を高電位側電源 V<sub>CC</sub> と低電位側電源 V<sub>SS</sub> との間でフル振幅動作させることができる。

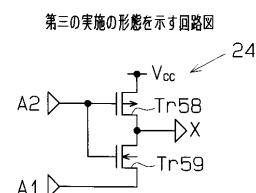

#### ( 第三の実施の形態 )

図 4 は、この発明を具体化した CMOS 論理回路の第三の実施の形態を示す。この実施の形態は、前記第二の従来例と同様に 2 入力 NAND 回路を構成する。

#### 【 0184 】

入力信号 A<sub>1</sub> は、N チャネル MOS トランジスタ Tr59 のソース (ドレイン) に入力され、入力信号 A<sub>2</sub> は前記トランジスタ Tr59 及び P チャネル MOS トランジスタトランジスタ Tr58 のゲートに入力される。

#### 【 0185 】

前記トランジスタ Tr58 のソースは、電源 V<sub>CC</sub> に接続され、ドレインは前記トランジスタ Tr59 のドレイン (ソース) に接続される。そして、前記トランジスタ Tr58 のドレイン及びトランジスタ Tr59 のドレイン (ソース) から出力信号 X が出力される。

#### 【 0186 】

このように構成された 2 入力 NAND 回路 24 では、入力信号 A<sub>1</sub>, A<sub>2</sub> がともに「0」となると、トランジスタ Tr58 がオンされるとともに、トランジスタ Tr59 がオフされる。従って、出力信号 X は H レベルとなる。

#### 【 0187 】

入力信号 A<sub>1</sub> が「0」、入力信号 A<sub>2</sub> が「1」となると、トランジスタ Tr58 がオフされるとともに、トランジスタ Tr59 がオンされる。従って、入力信号 A<sub>1</sub> がトランジスタ Tr59 を介して出力信号 X として出力されるので、出力信号 X は L レベルとなる。

#### 【 0188 】

入力信号 A<sub>1</sub> が「1」、入力信号 A<sub>2</sub> が「0」となると、トランジスタ Tr58 がオンされるとともに、トランジスタ Tr59 がオフされる。従って、出力信号 X は H レベルとなる。

#### 【 0189 】

入力信号 A<sub>1</sub>, A<sub>2</sub> がともに「1」となると、トランジスタ Tr58 がオフされるとともに、トランジスタ Tr59 がオンされる。従って、出力信号 A<sub>1</sub> がトランジスタ Tr59 を介して出力信号 X として出力されるので、出力信号 X は H レベルとなる。

#### 【 0190 】

このとき、入力信号 A<sub>1</sub>, A<sub>2</sub> が電源 V<sub>CC</sub> レベルであっても、出力信号 X は入力信号 A<sub>2</sub> よりトランジスタ Tr59 のしきい値分低いレベルとなる。

上記のような動作により、この論理回路は前記第一の従来例と同様に、図20に示す真理値に基づく動作を行い、入力信号A1の反転信号と入力信号A2とのNAND論理信号を出力信号Xとして出力し、図19に示すシンボルで表記される2入力NAND回路を構成する。

#### 【0191】

上記のような2入力NAND回路24では、次に示す作用効果を得ることができる。

(イ) 2個のMOSトランジスタにより、2入力NAND回路24が構成されるので、前記第二の従来例に比して素子数を削減することができる。従って、回路面積を縮小することができる。

(ロ) インバータ回路を必要としないので、入力信号A1, A2の反転時にも電源Vcc 10から電源Vssへの貫通電流は生じない。従って、消費電力を低減することができる。

(ハ) 上記のような2入力NAND回路24を多数搭載する半導体集積回路装置のチップ面積を縮小することができる。

(二) 上記のような2入力NAND回路24を多数搭載する半導体集積回路装置の消費電力を低減することができる。

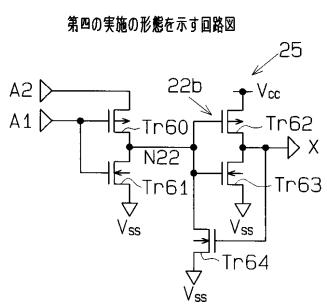

#### (第四の実施の形態)

図5は、この発明を具体化したCMOS論理回路の第四の実施の形態を示し、前記第三の実施の形態と同様に2入力NOR回路を構成する。

#### 【0192】

前記第三の実施の形態の2入力NOR回路24では、トランジスタTr59 20がオンされ、かつ入力信号A1が「1」となって、出力信号XがHレベルとなるとき、その出力信号Xは入力信号A2よりトランジスタTr59 のしきい値分低いレベルまでしか上昇しない。

#### 【0193】

従って、Hレベルの入力信号A1, A2として電源Vccレベルが入力されても、Hレベルの出力信号Xを電源Vccレベルまで引き上げることができない。この実施の形態は、出力信号Xを電源Vccレベルと電源Vssレベルとの間で確実にフル振幅動作させる構成としたものである。

#### 【0194】

入力信号A1は、PチャネルMOSトランジスタTr60 及びNチャネルMOSトランジスタTr61 のゲートに入力される。前記トランジスタTr60 のソース(ドレイン)には、入力信号A2が入力され、同トランジスタTr60 のドレイン(ソース)は、前記トランジスタTr61 のドレインに接続されて、ノードN22を構成する。前記トランジスタTr61 のソースは電源Vssに接続される。

#### 【0195】

前記ノードN22は、インバータ回路22bに入力され、そのインバータ回路22bから出力信号Xが出力される。また、出力信号XはNチャネルMOSトランジスタTr64のゲートに入力され、同トランジスタTr64 のドレインはノードN22に接続され、ソースは電源Vssに接続される。そして、インバータ回路22b及びトランジスタTr64 とで出力信号安定化回路が構成される。

#### 【0196】

このように構成された2入力NAND回路25では、入力信号A1, A2がともに「0」となると、トランジスタTr60 がオンされるとともに、トランジスタTr61 がオフされて、入力信号A2がトランジスタTr60 を介してノードN22に出力されるため、ノードN22がLレベルとなる。従って、出力信号XはHレベルとなる。

#### 【0197】

このとき、ノードN22は入力信号A1よりトランジスタTr60 のしきい値分高いレベルまでしか低下しないが、インバータ回路22bの出力信号Xと電源Vssとの電位差がトランジスタTr64 のしきい値以上となれば、トランジスタTr64 がオンされて、ノードN22がほぼ電源Vssレベルまで引き下げられる。従って、出力信号Xは電

源Vccレベルまで確実に引き上げられる。

【0198】

入力信号A1が「0」、入力信号A2が「1」となると、トランジスタTr60がオンされるとともに、トランジスタTr61がオフされて、入力信号A2がトランジスタTr60を介してノードN22に出力されるため、ノードN22がHレベルとなる。従って、出力信号XはLレベルとなる。

【0199】

入力信号A1が「1」、入力信号A2が「0」となると、トランジスタTr60がオフされるとともに、トランジスタTr61がオンされて、ノードN22がLレベルとなる。従って、出力信号XはHレベルとなる。

10

【0200】

入力信号A1, A2がともに「1」となると、トランジスタTr60がオフされるとともに、トランジスタTr61がオンされて、ノードN22がLレベルとなる。従って、出力信号XはHレベルとなる。

【0201】

上記のような動作により、この論理回路は前記第三の従来例と同様に、図20に示す真理値に基づく動作を行い、入力信号A1の反転信号と入力信号A2とのNAND回路論理信号を出力信号Xとして出力し、図19に示すシンボルで表記される2入力NAND回路を構成する。

【0202】

上記のような2入力NAND回路25では、次に示す作用効果を得ることができる。

20

(イ) 5個のMOSトランジスタにより、2入力NAND回路25が構成されるので、前記第二の従来例に比して素子数を削減することができる。従って、回路面積を縮小することができる。

(ロ) 上記のような2入力NAND回路25を多数搭載する半導体集積回路装置のチップ面積を縮小することができる。

(ハ) 出力信号安定化回路を備えたことにより、第三の実施の形態に比して、入力信号A1, A2の振幅が小さくなっても、出力信号Xを高電位側電源Vccと低電位側電源Vssとの間でフル振幅動作させることができる。

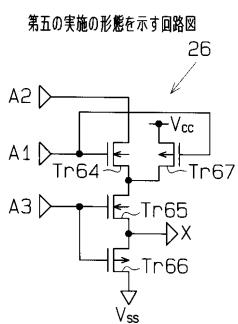

(第五の実施の形態)

30

図6は、この発明を具体化したCMOS論理回路の第五の実施の形態を示す。この実施の形態は、前記第三の従来例と同様に2wide・2AND・3入力・AND・OR・インバータ回路を構成する。

【0203】

入力信号A1は、NチャネルMOSトランジスタTr64及びPチャネルMOSトランジスタTr67のゲートに入力され、入力信号A2は同トランジスタTr64のドレイン(ソース)に入力される。

【0204】

入力信号A3は、NチャネルMOSトランジスタTr65及びPチャネルMOSトランジスタTr66のゲートに入力される。前記トランジスタTr65のドレイン(ソース)は、前記トランジスタTr64のソース(ドレイン)に接続され、同トランジスタTr65のソース(ドレイン)は、前記トランジスタTr66のソースに接続される。前記トランジスタTr66のドレインは電源Vssに接続される。そして、前記トランジスタTr66のソースから出力信号Xが出力される。

40

【0205】

前記トランジスタTr67のソースは電源Vccに接続され、ドレインは前記トランジスタTr65のドレイン(ソース)に接続される。

このように構成されたAND・OR・インバータ回路26は、図23に示す真理値に基づく動作を行う。すなわち、入力信号A1, A2, A3がともに「0」となると、トランジスタTr64, Tr65がオフされるとともに、トランジスタTr66, Tr67

50

がオンされる。従って、出力信号XはLレベルとなる。

【0206】

入力信号A1, A2, A3が「1, 0, 0」となると、トランジスタTr64, Tr66がオンされるとともに、トランジスタTr65, Tr67がオフされる。従って、出力信号XはLレベルとなる。

【0207】

入力信号A1, A2, A3が「0, 1, 0」となると、トランジスタTr64, Tr65がオフされるとともに、トランジスタTr66, Tr67がオンされる。従って、出力信号XはLレベルとなる。

【0208】

入力信号A1, A2, A3が「1, 1, 0」となると、トランジスタTr64, Tr66がオンされるとともに、トランジスタTr65, Tr67がオフされる。従って、出力信号XはLレベルとなる。

【0209】

入力信号A1, A2, A3が「0, 0, 1」となると、トランジスタTr64, Tr66がオフされるとともに、トランジスタTr65, Tr67がオンされる。従って、出力信号XはHレベルとなる。このとき、出力信号Xは入力信号A3よりトランジスタTr65のしきい値分低いレベルとなる。

【0210】

入力信号A1, A2, A3が「1, 0, 1」となると、トランジスタTr64, Tr65がオンされるとともに、トランジスタTr66, Tr67がオフされる。すると、Lレベルの入力信号A2がトランジスタTr64, Tr65を介して出力信号Xとして出力されるため、出力信号XはLレベルとなる。

【0211】

入力信号A1, A2, A3が「0, 1, 1」となると、トランジスタTr64, Tr66がオフされるとともに、トランジスタTr65, Tr67がオンされる。従って、出力信号XはHレベルとなる。このとき、出力信号Xは入力信号A3よりトランジスタTr65のしきい値分低いレベルとなる。

【0212】

入力信号A1, A2, A3が「1, 1, 1」となると、トランジスタTr64, Tr65がオンされるとともに、トランジスタTr66, Tr67がオフされる。すると、Hレベルの入力信号A2がトランジスタTr64, Tr65を介して出力信号Xとして出力されるため、出力信号XはHレベルとなる。

【0213】

このとき、出力信号Xは入力信号A2よりトランジスタTr64, Tr65のしきい値分低いレベルが出力される。

上記のような動作により、この論理回路は図23に示す真理値に基づく動作を行い、入力信号A1と入力信号A2の反転信号とのAND論理信号と、入力信号A3の反転信号とのNOR論理を出力信号Xとして出力し、図22に示すシンボルで表記されるAND・OR・インバータ回路を構成する。

【0214】

上記のようなAND・OR・インバータ回路26では、次に示す作用効果を得ることができる。

(イ) 4個のMOSトランジスタにより、2wide・2AND・3入力・AND・OR・インバータ回路26が構成されるので、前記第三の従来例に比して素子数を削減することができる。従って、回路面積を縮小することができる。

(ロ) インバータ回路を必要としないので、入力信号A1～A3の反転時にも電源Vccから電源Vssへの貫通電流は生じない。従って、消費電力を低減することができる。

(ハ) 上記のような2wide・2AND・3入力・AND・OR・インバータ回路26を多数搭載する半導体集積回路装置のチップ面積を縮小することができる。

10

20

30

40

50

(二) 上記のような 2 wide · 2 AND · 3 入力 · AND · OR · インバータ回路 26 を多数搭載する半導体集積回路装置の消費電力を低減することができる。

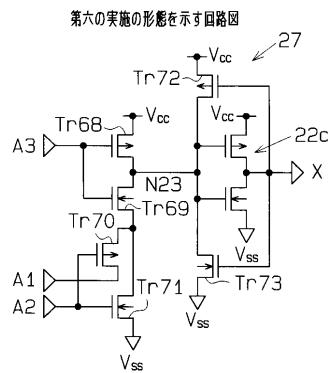

(第六の実施の形態)

図 7 は、この発明を具体化した CMOS 論理回路の第六の実施の形態を示し、前記第五の実施の形態と同様に 2 wide · 2 AND · 3 入力 · AND · OR · インバータ回路を構成する。

【0215】

前記第五の実施の形態では、H レベルの入力信号 A3 よりトランジスタ Tr65 のしきい値分低いレベルが H レベルの出力信号 X として出力される場合、あるいは H レベルの入力信号 A2 よりトランジスタ Tr64, Tr65 のしきい値分低いレベルが出力信号 X として出力される場合がある。

【0216】

従って、H レベルの入力信号 A1 ~ A3 として電源 Vcc レベルが入力されても、H レベルの出力信号 X を電源 Vcc レベルまで引き上げることができない。この実施の形態は、出力信号 X を電源 Vcc レベルと電源 Vss レベルとの間で確実にフル振幅動作させる構成としたものである。

【0217】

入力信号 A1 は、P チャネル MOS トランジスタ Tr70 のドレイン (ソース) に入力され、入力信号 A2 は前記トランジスタ Tr70 及び N チャネル MOS トランジスタ Tr71 のゲートに入力される。

【0218】

入力信号 A3 は、P チャネル MOS トランジスタ Tr68 及び N チャネル MOS トランジスタ Tr69 のゲートに入力される。

前記トランジスタ Tr68 のソースは、電源 Vcc に接続され、ドレインは前記トランジスタ Tr69 のドレイン (ソース) に接続されて、ノード N23 を構成する。

【0219】

前記トランジスタ Tr69 のソース (ドレイン) は、前記トランジスタ Tr70 のソース (ドレイン) 及び前記トランジスタ Tr71 のドレインに接続され、そのトランジスタ Tr71 のソースは電源 Vss に接続される。

【0220】

ノード N23 は、CMOS インバータ回路 22c に入力され、そのインバータ回路 22c から出力信号 X が出力される。前記出力信号 X は、P チャネル MOS トランジスタ Tr72 及び N チャネル MOS トランジスタ Tr73 のゲートに入力される。

【0221】

前記トランジスタ Tr72 のソースは電源 Vcc に接続され、ドレインはノード N23 に接続される。前記トランジスタ Tr73 のドレインは、ノード N23 に接続され、ソースは電源 Vss に接続される。そして、インバータ回路 22c 及びトランジスタ Tr72, Tr73 とで出力信号安定化回路が構成される。

【0222】

このように構成された AND · OR · インバータ回路 27 は、図 23 に示す真理値に基づく動作を行う。すなわち、入力信号 A1, A2, A3 がともに「0」となると、トランジスタ Tr68, Tr70 がオンされるとともに、トランジスタ Tr69, Tr71 がオフされる。

【0223】

すると、ノード N23 は H レベルとなり、出力信号 X は L レベルとなる。また、トランジスタ Tr72 がオンされるとともに、トランジスタ Tr73 がオフされて、ノード N23 がほぼ電源 Vcc レベルとなる。

【0224】

入力信号 A1, A2, A3 が「1, 0, 0」となると、トランジスタ Tr68, Tr70 がオンされるとともに、トランジスタ Tr69, Tr71 がオフされる。

10

20

30

40

50

すると、ノードN23はHレベルとなり、出力信号XはLレベルとなる。また、トランジスタTr72がオンされるとともに、トランジスタTr73がオフされて、ノードN23がほぼ電源Vccレベルとなる。

【0225】

入力信号A1, A2, A3が「0, 1, 0」となると、トランジスタTr68, Tr71がオンされるとともに、トランジスタTr69, Tr70がオフされる。

すると、ノードN23はHレベルとなり、出力信号XはLレベルとなる。また、トランジスタTr72がオンされるとともに、トランジスタTr73がオフされて、ノードN23がほぼ電源Vccレベルとなる。

【0226】

入力信号A1, A2, A3が「1, 1, 0」となると、トランジスタTr68, Tr71がオフされるとともに、トランジスタTr69, Tr70がオフされる。

すると、ノードN23はHレベルとなり、出力信号XはLレベルとなる。また、トランジスタTr72がオンされるとともに、トランジスタTr73がオフされて、ノードN23がほぼ電源Vccレベルとなる。

【0227】

入力信号A1, A2, A3が「0, 0, 1」となると、トランジスタTr69, Tr70がオフされるとともに、トランジスタTr68, Tr71がオフされる。

すると、入力信号A1がトランジスタTr70, Tr69を介してノードN23に出力されて、ノードN23はLレベルとなる。このとき、ノードN23は入力信号A1よりトランジスタTr70のしきい値分高いレベル以下には下がらないが、出力信号Xが電源VssよりトランジスタTr73のしきい値分以上高いレベルとなれば、トランジスタTr73がオンされて、ノードN23がほぼ電源Vssレベルとなる。従って、インバータ回路22cの動作により、出力信号Xはほぼ電源Vccレベルまで引き上げられて、Hレベルとなる。

【0228】

入力信号A1, A2, A3が「1, 0, 1」となると、トランジスタTr69, Tr70がオフされるとともに、トランジスタTr68, Tr71がオフされる。すると、入力信号A1がトランジスタTr70, Tr69を介してノードN23に出力されて、ノードN23はHレベルとなる。

【0229】

このとき、ノードN23は入力信号A1よりトランジスタTr69のしきい値分低下したレベル以上には上昇しないが、出力信号Xが電源VccよりトランジスタTr72のしきい値分以上低いレベルとなれば、トランジスタTr72がオンされて、ノードN23はほぼ電源Vccレベルとなる。従って、インバータ回路22cの動作により、出力信号Xはほぼ電源Vssレベルまで引き下げられてLレベルとなる。

【0230】

入力信号A1, A2, A3が「0, 1, 1」となると、トランジスタTr69, Tr71がオフされるとともに、トランジスタTr68, Tr70がオフされる。

すると、ノードN23はほぼ電源Vssレベルまで引き下げられて、Lレベルとなり、出力信号XはHレベルとなる。また、トランジスタTr72がオフされるとともに、トランジスタTr73がオンされて、ノードN23がほぼ電源Vssレベルとなる。

【0231】

入力信号A1, A2, A3が「1, 1, 1」となると、トランジスタTr69, Tr71がオフされるとともに、トランジスタTr68, Tr70がオフされる。

すると、ノードN23は上記と同様にLレベルとなり、出力信号XはHレベルとなる。また、トランジスタTr72がオフされるとともに、トランジスタTr73がオンされて、ノードN23がほぼ電源Vssレベルとなる。

【0232】

上記のような動作により、この論理回路は図23に示す真理値に基づく動作を行い、入力

10

20

30

40

50

信号A1と入力信号A2の反転信号とのAND論理信号と、入力信号A3の反転信号とのNOR論理を出力信号Xとして出力し、図22に示すシンボルで表記されるAND・OR・インバータ回路を構成する。

【0233】

上記のようなAND・OR・インバータ回路27では、次に示す作用効果を得ることができる。

(イ) 8個のMOSトランジスタにより、2wide・2AND・3入力・AND・OR・インバータ回路27が構成されるので、前記第三の従来例に比して素子数を削減することができる。従って、回路面積を縮小することができる。

(ロ) 上記のような2wide・2AND・3入力・AND・OR・インバータ回路27を多数搭載する半導体集積回路装置のチップ面積を縮小することができる。 10

(ハ) 出力信号安定化回路の動作により、第五の実施の形態に比して、入力信号A1～A3の振幅が小さくなっても、出力信号Xを高電位側電源Vccと低電位側電源Vssとの間でフル振幅動作させることができる。

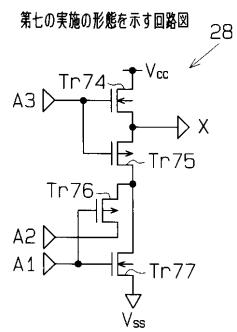

(第七の実施の形態)

図8は、この発明を具体化したCMOS論理回路の第七の実施の形態を示す。この実施の形態は、前記第五の従来例と同様に2wide・2AND・3入力・AND・OR回路を構成する。

【0234】

入力信号A2は、PチャネルMOSトランジスタTr76のドレイン(ソース)に入力され、入力信号A1は前記トランジスタTr76及びNチャネルMOSトランジスタTr77のゲートに入力される。 20

【0235】

入力信号A3は、PチャネルMOSトランジスタTr75及びNチャネルMOSトランジスタTr74のゲートに入力される。

前記トランジスタTr74のドレインは、電源Vccに接続され、ソースは前記トランジスタTr75のソース(ドレイン)に接続されるとともに、出力信号Xを出力する。

【0236】

前記トランジスタTr75のドレイン(ソース)は、前記トランジスタTr76のソース(ドレイン)及び前記トランジスタTr77のドレインに接続され、そのトランジスタTr77のソースは電源Vssに接続される。 30

【0237】

このように構成されたAND・OR回路28は、図28に示す真理値に基づく動作を行う。すなわち、入力信号A1, A2, A3がともに「0」となると、トランジスタTr75, Tr76がオンされるとともに、トランジスタTr74, Tr77がオフされる。従って、入力信号A2がトランジスタTr75, Tr76を介して出力信号Xとして出力されるため、出力信号XはLレベルとなる。

【0238】

このとき、出力信号Xは入力信号A2よりトランジスタTr75, Tr76のしきい値分上昇したレベルまでしか低下しない。従って、入力信号A1～A3として電源Vssレベルが入力されても、Lレベルの出力信号Xは、電源Vssレベルより高いレベルとなる。 40

【0239】

入力信号A1, A2, A3が「1, 0, 0」となると、トランジスタTr75, Tr77がオンされるとともに、トランジスタTr74, Tr76がオフされる。従って、出力信号XはLレベルとなる。このとき、出力信号Xは電源VssよりトランジスタTr75のしきい値分高いレベルまでしか低下しない。

【0240】

入力信号A1, A2, A3が「0, 1, 0」となると、トランジスタTr75, Tr76がオンされるとともに、トランジスタTr74, Tr77がオフされる。従って 50

、入力信号 A 2 が出力信号 X として出力されるため、出力信号 X は H レベルとなる。

【 0 2 4 1 】

入力信号 A 1 , A 2 , A 3 が「 1 , 1 , 0 」となると、トランジスタ Tr 75 , Tr 77 がオンされるとともに、トランジスタ Tr 74 , Tr 76 がオフされる。従って、出力信号 X は L レベルとなる。このとき、出力信号 X は電源 V ss よりトランジスタ Tr 75 のしきい値分高いレベルまでしか低下しない。

【 0 2 4 2 】

入力信号 A 1 , A 2 , A 3 が「 0 , 0 , 1 」となると、トランジスタ Tr 74 , Tr 76 がオンされるとともに、トランジスタ Tr 75 , Tr 77 がオフされる。従って、出力信号 X は H レベルとなる。 10

【 0 2 4 3 】

入力信号 A 1 , A 2 , A 3 が「 1 , 0 , 1 」となると、トランジスタ Tr 74 , Tr 77 がオンされるとともに、トランジスタ Tr 75 , Tr 76 がオフされる。従って、出力信号 X は H レベルとなる。

【 0 2 4 4 】

入力信号 A 1 , A 2 , A 3 が「 0 , 1 , 1 」となると、トランジスタ Tr 74 , Tr 76 がオンされるとともに、トランジスタ Tr 75 , Tr 77 がオフされる。従って、出力信号 X は H レベルとなる。

【 0 2 4 5 】

入力信号 A 1 , A 2 , A 3 が「 1 , 1 , 1 」となると、トランジスタ Tr 74 , Tr 77 がオンされるとともに、トランジスタ Tr 75 , Tr 76 がオフされる。従って、出力信号 X は H レベルとなる。 20

【 0 2 4 6 】

上記のような動作により、この論理回路は図 2 8 に示す真理値に基づく動作を行い、入力信号 A 1 の反転信号と入力信号 A 2 との AND 論理信号と、入力信号 A 3 との OR 論理を出力信号 X として出力し、図 2 7 に示すシンボルで表記される AND · OR 回路を構成する。

【 0 2 4 7 】

上記のような AND · OR 回路 2 8 では、次に示す作用効果を得ることができる。

(イ) 4 個の MOS トランジスタにより、 2 wide · 2 AND · 3 入力 · AND · OR 回路 2 8 が構成されるので、前記第五の従来例に比して素子数を削減することができる。従って、回路面積を縮小することができる。 30

(ロ) インバータ回路を必要としないので、入力信号 A 1 ~ A 3 の反転時にも電源 V cc から電源 V ss への貫通電流は生じない。従って、消費電力を低減することができる。

(ハ) 上記のような 2 wide · 2 AND · 3 入力 · AND · OR 回路 2 8 を多数搭載する半導体集積回路装置のチップ面積を縮小することができる。

(二) 上記のような 2 wide · 2 AND · 3 入力 · AND · OR 回路 2 8 を多数搭載する半導体集積回路装置の消費電力を低減することができる。

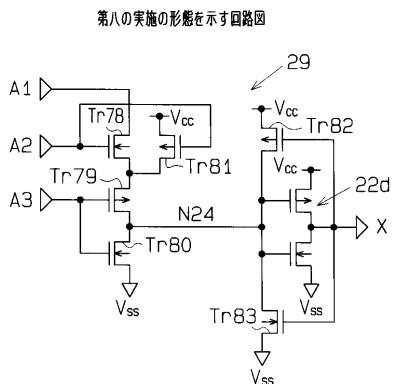

(第八の実施の形態)

図 9 は、この発明を具体化した CMOS 論理回路の第八の実施の形態を示し、前記第七の実施の形態と同様に 2 wide · 2 AND · 3 入力 · AND · OR 回路を構成する。 40

【 0 2 4 8 】

前記第七の実施の形態では、 L レベルの入力信号 A 1 ~ A 3 を電源 V ss レベルとしても、 L レベルの出力信号 X を電源 V ss レベルまで引き下げることができない場合がある。この実施の形態は、 L レベルの出力信号 X を電源 V ss レベルまで引き下げて、出力信号 X を電源 V cc レベルと電源 V ss レベルとの間で確実にフル振幅動作させる構成としたものである。

【 0 2 4 9 】

入力信号 A 2 は、 N チャネル MOS トランジスタ Tr 78 及び P チャネル MOS トランジスタ Tr 81 のゲートに入力され、入力信号 A 1 は同トランジスタ Tr 78 のドレ 50

イン(ソース)に入力される。

【0250】

入力信号A3は、NチャネルMOSトランジスタTr80及びPチャネルMOSトランジスタTr79のゲートに入力される。前記トランジスタTr79のソース(ドレイン)は、前記トランジスタTr78のソース(ドレイン)に接続され、同トランジスタTr79のドレイン(ソース)は、前記トランジスタTr80のドレインに接続されて、ノードN24を構成する。前記トランジスタTr80のソースは電源Vssに接続される。

【0251】

前記トランジスタTr81のソースは電源Vccに接続され、ドレインは前記トランジスタTr79のソース(ドレイン)に接続される。 10

前記ノードN24は、CMOSインバータ回路22dに入力され、そのインバータ回路22dから出力信号Xが出力される。出力信号Xは、PチャネルMOSトランジスタTr82及びNチャネルMOSトランジスタTr83のゲートに入力される。

【0252】

前記トランジスタTr82のソースは電源Vccに接続され、ドレインはノードN24に接続される。前記トランジスタTr83のドレインはノードN24に接続され、ソースは電源Vssに接続される。そして、インバータ回路22dと、トランジスタTr82, Tr83とで出力信号安定化回路が構成される。

【0253】

このように構成された2wide・2AND・3入力・AND・OR回路29では、前記第五の従来例と同様に、図28に示す真理値に基づいて動作する。すなわち、入力信号A1, A2, A3がともに「0」となると、トランジスタTr81, Tr79がオンされるとともに、トランジスタTr78, Tr80がオフされる。 20

【0254】

すると、ノードN24はほぼ電源VccレベルとなってHレベルとなり、インバータ回路22dの動作により、出力信号Xは電源Vssレベルまで低下して、Lレベルとなる。また、トランジスタTr82がオンされるとともに、トランジスタTr83がオフされ、ノードN24がほぼ電源Vccレベルとなる。

【0255】

入力信号A1, A2, A3が「1, 0, 0」となると、トランジスタTr81, Tr79がオンされるとともに、トランジスタTr78, Tr80がオフされる。 30

すると、ノードN24はHレベルとなり、同様に出力信号XはLレベルとなる。

【0256】

入力信号A1, A2, A3が「0, 1, 0」となると、トランジスタTr78, Tr79がオンされるとともに、トランジスタTr81, Tr80がオフされる。

すると、Lレベルの入力信号A1がトランジスタTr78, Tr79を介してノードN24に出力されるため、ノードN24はLレベルとなる。

【0257】

このとき、ノードN24は入力信号A1よりトランジスタTr79のしきい値分高いレベル以下には低下しない。 40

ノードN24がLレベルとなると、インバータ回路22dの動作により、出力信号XはHレベルとなる。すると、トランジスタTr82がオフされるとともに、トランジスタTr83がオンされて、ノードN24がほぼ電源Vssレベルとなる。従って、Hレベルの出力信号Xは電源Vccレベルまで引き上げられる。

【0258】

入力信号A1, A2, A3が「1, 1, 0」となると、トランジスタTr78, Tr79がオンされるとともに、トランジスタTr81, Tr80がオフされる。

すると、Hレベルの入力信号A1がトランジスタTr78, Tr79を介してノードN24に出力されるため、ノードN24はHレベルとなる。 50

## 【0259】

このとき、ノードN24は入力信号A1よりトランジスタTr79のしきい値分低いレベル以上には上昇しない。

ノードN24がHレベルとなると、インバータ回路22dの動作により、出力信号XはLレベルとなる。すると、トランジスタTr82がオンされるとともに、トランジスタTr83がオフされて、ノードN24がほぼ電源Vccレベルとなる。従って、Lレベルの出力信号Xは電源Vssレベルまで引き下げられる。

## 【0260】

入力信号A1, A2, A3が「0, 0, 1」となると、トランジスタTr81, Tr80がオンされるとともに、トランジスタTr78, Tr79がオフされる。10

すると、ノードN24はLレベルとなり、出力信号XはHレベルとなる。また、トランジスタTr82がオフされるとともに、トランジスタTr83がオンされて、ノードN24がほぼ電源Vssレベルとなる。

入力信号A1, A2, A3が「1, 0, 1」となると、トランジスタTr81, Tr80がオンされるとともに、トランジスタTr78, Tr79がオフされる。

## 【0261】

すると、ノードN24はLレベルとなり、出力信号XはHレベルとなる。また、トランジスタTr82がオフされるとともに、トランジスタTr83がオンされて、ノードN24がほぼ電源Vssレベルとなる。

## 【0262】

入力信号A1, A2, A3が「0, 1, 1」となると、トランジスタTr78, Tr80がオンされるとともに、トランジスタTr81, Tr79がオフされる。20

すると、ノードN24はLレベルとなり、出力信号XはHレベルとなる。また、トランジスタTr82がオフされるとともに、トランジスタTr83がオンされて、ノードN24がほぼ電源Vssレベルとなる。

## 【0263】

入力信号A1, A2, A3が「1, 1, 1」となると、トランジスタTr78, Tr80がオンされるとともに、トランジスタTr81, Tr79がオフされる。

すると、ノードN24はLレベルとなり、出力信号XはHレベルとなる。また、トランジスタTr82がオフされるとともに、トランジスタTr83がオンされて、ノードN24がほぼ電源Vssレベルとなる。30

## 【0264】

上記のような動作により、この論理回路は図28に示す真理値に基づく動作を行い、入力信号A1の反転信号と入力信号A2とのAND論理信号と、入力信号A3とのOR論理を出力信号Xとして出力し、図27に示すシンボルで表記されるAND・OR回路を構成する。

## 【0265】

上記のようなAND・OR回路29では、次に示す作用効果を得ることができる。

(イ) 8個のMOSトランジスタにより、2wide・2AND・3入力・AND・OR回路29が構成されるので、前記第五の従来例に比して素子数を削減することができる。40

従って、回路面積を縮小することができる。

(ロ) 上記のような2wide・2AND・3入力・AND・OR回路29を多数搭載する半導体集積回路装置のチップ面積を縮小することができる。

(ハ) 出力信号安定化回路を備えたことにより、第七の実施の形態に比して、入力信号A1～A3の振幅が小さくなっても、出力信号Xを高電位側電源Vccと低電位側電源Vssとの間でフル振幅動作させることができる。

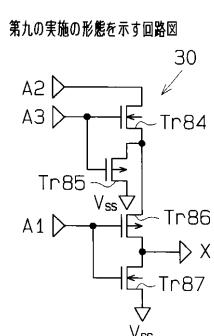

## (第九の実施の形態)

図10は、この発明を具体化したCMOS論理回路の第九の実施の形態を示す。この実施の形態は、前記第七の従来例と同様に3入力AND回路を構成する。

## 【0266】

入力信号 A 1 は、N チャネルMOS トランジスタ Tr 8 7 及びP チャネルMOS トランジスタ Tr 8 6 のゲートに入力される。入力信号 A 2 は、N チャネルMOS トランジスタ Tr 8 4 のドレイン(ソース)に入力される。

【0267】

入力信号 A 3 は、前記トランジスタ Tr 8 4 及びP チャネルMOS トランジスタ Tr 8 5 のゲートに入力される。前記トランジスタ Tr 8 4 のソース(ドレイン)は、前記トランジスタ Tr 8 5 のソース及び前記トランジスタ Tr 8 6 のソース(ドレイン)に接続される。

【0268】

前記トランジスタ Tr 8 5 のドレインは、電源 Vss に接続される。前記トランジスタ Tr 8 6 のドレイン(ソース)は、前記トランジスタ Tr 8 7 のドレインに接続され、同トランジスタ Tr 8 7 のソースは電源 Vss に接続される。そして、前記トランジスタ Tr 8 7 のドレインから出力信号 X が出力される。 10

【0269】

このように構成されたAND回路30は、図33に示す真理値に基づく動作を行う。すなわち、入力信号 A 1 , A 2 , A 3 がともに「0」となると、トランジスタ Tr 8 5 , Tr 8 6 がオンされるとともに、トランジスタ Tr 8 4 , Tr 8 7 がオフされる。従って、出力信号 X は L レベルとなる。

【0270】

このとき、出力信号 X は、電源 Vss よりトランジスタ Tr 8 6 , Tr 8 5 のしきい値分高いレベルが出力される。従って、入力信号 A 1 , A 3 に L レベルの入力信号として電源 Vss レベルを入力しても、出力信号 X は電源 Vss レベルまで下がらない。 20

【0271】

入力信号 A 1 , A 2 , A 3 が「1, 0, 0」となると、トランジスタ Tr 8 5 , Tr 8 7 がオンされるとともに、トランジスタ Tr 8 4 , Tr 8 6 がオフされる。従って、出力信号 X は L レベルとなる。このとき、L レベルの出力信号 X はほぼ電源 Vss レベルまで低下する。

【0272】

入力信号 A 1 , A 2 , A 3 が「0, 1, 0」となると、トランジスタ Tr 8 5 , Tr 8 6 がオンされるとともに、トランジスタ Tr 8 4 , Tr 8 7 がオフされる。従って、出力信号 X は L レベルとなる。このとき、上記と同様に出力信号 X は電源 Vss レベルまで低下しない。 30

【0273】

入力信号 A 1 , A 2 , A 3 が「1, 1, 0」となると、トランジスタ Tr 8 5 , Tr 8 7 がオンされるとともに、トランジスタ Tr 8 4 , Tr 8 6 がオフされる。従って、出力信号 X は L レベルとなる。

【0274】

入力信号 A 1 , A 2 , A 3 が「0, 0, 1」となると、トランジスタ Tr 8 4 , Tr 8 6 がオンされるとともに、トランジスタ Tr 8 5 , Tr 8 7 がオフされる。従って、入力信号 A 2 がトランジスタ Tr 8 4 , Tr 8 6 を介して出力信号 X として出力されるため、出力信号 X は L レベルとなる。 40

【0275】

このとき、出力信号 X は、入力信号 A 2 よりトランジスタ Tr 8 6 のしきい値分高いレベル以上となる。従って、L レベルの入力信号 A 1 として電源 Vss レベルを入力しても、L レベルの出力信号 X は電源 Vss レベルまで低下しない。

【0276】

入力信号 A 1 , A 2 , A 3 が「1, 0, 1」となると、トランジスタ Tr 8 4 , Tr 8 7 がオンされるとともに、トランジスタ Tr 8 5 , Tr 8 6 がオフされる。従って、出力信号 X は L レベルとなる。

【0277】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「0 , 1 , 1」となると、トランジスタ Tr<sub>84</sub> , Tr<sub>86</sub> がオンされるとともに、トランジスタ Tr<sub>85</sub> , Tr<sub>87</sub> がオフされる。従って、入力信号 A<sub>2</sub> がトランジスタ Tr<sub>84</sub> , Tr<sub>86</sub> を介して出力信号 X として出力されるため、出力信号 X は H レベルとなる。

【0278】

このとき、出力信号 X は、入力信号 A<sub>2</sub> よりトランジスタ Tr<sub>84</sub> のしきい値分低いレベル以下となる。従って、H レベルの入力信号 A<sub>2</sub> として電源 V<sub>cc</sub> レベルを入力しても、H レベルの出力信号 X は電源 V<sub>cc</sub> レベルまで上昇しない。

【0279】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「1 , 1 , 1」となると、トランジスタ Tr<sub>84</sub> , Tr<sub>87</sub> がオフされるとともに、トランジスタ Tr<sub>85</sub> , Tr<sub>86</sub> がオフされる。従って、出力信号 X は L レベルとなる。

【0280】

上記のような動作により、この論理回路は図 33 に示す真理値に基づく動作を行い、入力信号 A<sub>1</sub> の反転信号と入力信号 A<sub>2</sub> , A<sub>3</sub> との AND 論理信号を出力信号 X として出力し、図 32 に示すシンボルで表記される AND 回路を構成する。

【0281】

上記のような AND 回路 30 では、次に示す作用効果を得ることができる。

(イ) 4 個の MOS トランジスタにより、3 入力 AND 回路 30 が構成されるので、前記第七の従来例に比して素子数を削減することができる。従って、回路面積を縮小することができる。

(ロ) インバータ回路を必要としないので、入力信号 A<sub>1</sub> ~ A<sub>3</sub> の反転時にも電源 V<sub>cc</sub> から電源 V<sub>ss</sub> への貫通電流は生じない。従って、消費電力を低減することができる。

(ハ) 上記のような 3 入力 AND 回路 30 を多数搭載する半導体集積回路装置のチップ面積を縮小することができる。

(二) 上記のような 3 入力 AND 回路 30 を多数搭載する半導体集積回路装置の消費電力を低減することができる。

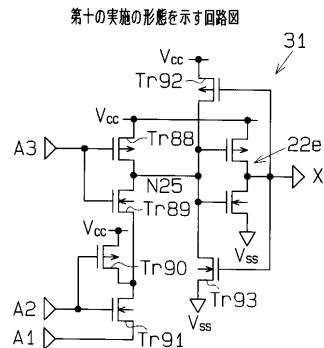

(第十の実施の形態)

図 11 は、この発明を具体化した CMOS 論理回路の第十の実施の形態を示し、前記第九の実施の形態と同様に 3 入力 AND 回路を構成する。

【0282】

前記第九の実施の形態では、L レベル出力信号 X を電源 V<sub>ss</sub> レベルまで引き下げることができない場合及び H レベルの出力信号 X を電源 V<sub>cc</sub> レベルまで引き上げることができない場合がある。

【0283】

この実施の形態は、出力信号 X を電源 V<sub>cc</sub> レベルと電源 V<sub>ss</sub> レベルとの間で確実にフル振幅動作させる構成としたものである。

入力信号 A<sub>3</sub> は、P チャネル MOS トランジスタ Tr<sub>88</sub> 及び N チャネル MOS トランジスタ Tr<sub>89</sub> のゲートに入力される。

【0284】

入力信号 A<sub>2</sub> は、P チャネル MOS トランジスタ Tr<sub>90</sub> 及び N チャネル MOS トランジスタ Tr<sub>91</sub> のゲートに入力される。

前記トランジスタ Tr<sub>88</sub> のソースは、電源 V<sub>cc</sub> に接続され、ドレインは前記トランジスタ Tr<sub>89</sub> のドレイン(ソース)に接続されて、ノード N<sub>25</sub> を構成する。前記トランジスタ Tr<sub>89</sub> のソース(ドレイン)は、前記トランジスタ Tr<sub>91</sub> のドレイン(ソース)に接続され、同トランジスタ Tr<sub>91</sub> のソース(ドレイン)に入力信号 A<sub>1</sub> が入力される。

【0285】

前記トランジスタ Tr<sub>90</sub> のソースは電源 V<sub>cc</sub> に接続され、ドレインは前記トランジスタ Tr<sub>91</sub> のドレイン(ソース)に接続される。

10

20

30

40

50

前記ノードN25は、CMOSインバータ回路22eに入力され、そのインバータ回路22eから出力信号Xが出力される。出力信号Xは、PチャネルMOSトランジスタTr92及びNチャネルMOSトランジスタTr93のゲートに入力される。

【0286】

前記トランジスタTr92のソースは電源Vccに接続され、ドレインはノードN25に接続される。前記トランジスタTr93のドレインはノードN25に接続され、ソースは電源Vssに接続される。そして、インバータ回路22eと、トランジスタTr92, Tr93とで出力信号安定化回路が構成される。

【0287】

このように構成された3入力AND回路31では、前記第七の従来例と同様に、図33に示す真理値に基づいて動作する。すなわち、入力信号A1, A2, A3がともに「0」となると、トランジスタTr88, Tr90がオンされるとともに、トランジスタTr89, Tr91がオフされる。

【0288】

すると、ノードN25はほぼ電源VccレベルとなってHレベルとなり、出力信号XはLレベルとなる。また、トランジスタTr92がオンされるとともに、トランジスタTr93がオフされて、ノードN25がほぼ電源Vccレベルとなる。

【0289】

入力信号A1, A2, A3が「1, 0, 0」となると、トランジスタTr88, Tr90がオンされるとともに、トランジスタTr89, Tr91がオフされる。すると、同様に出力信号XはLレベルとなり、ノードN25がほぼ電源Vccレベルとなる。

【0290】

入力信号A1, A2, A3が「0, 1, 0」となると、トランジスタTr88, Tr91がオンされるとともに、トランジスタTr89, Tr90がオフされる。すると、ノードN25はHレベルとなり、出力信号XはLレベルとなる。また、トランジスタTr92がオンされるとともに、トランジスタTr93がオフされて、ノードN25がほぼ電源Vccレベルとなる。

【0291】

入力信号A1, A2, A3が「1, 1, 0」となると、トランジスタTr88, Tr91がオンされるとともに、トランジスタTr89, Tr90がオフされる。すると、ノードN25はHレベルとなり、出力信号XはLレベルとなる。また、トランジスタTr92がオンされるとともに、トランジスタTr93がオフされて、ノードN25がほぼ電源Vccレベルとなる。

【0292】

入力信号A1, A2, A3が「0, 0, 1」となると、トランジスタTr89, Tr90がオンされるとともに、トランジスタTr88, Tr91がオフされる。すると、ノードN25はHレベルとなる。このとき、ノードN25は電源VccよりトランジスタTr89のしきい値分低いレベル以上には上昇しない。

【0293】

ノードN25がHレベルとなると、インバータ回路22eの動作により、出力信号XはLレベルとなる。すると、トランジスタTr92がオンされるとともに、トランジスタTr93がオフされて、ノードN25がほぼ電源Vccレベルとなる。従って、Lレベルの出力信号Xは電源Vssレベルまで引き下げられる。

【0294】

入力信号A1, A2, A3が「1, 0, 1」となると、トランジスタTr89, Tr90がオンされるとともに、トランジスタTr88, Tr91がオフされる。そして、「1, 0, 1」の場合と同様に出力信号XがLレベルとなる。

【0295】

入力信号A1, A2, A3が「0, 1, 1」となると、トランジスタTr89, Tr91がオフされるとともに、トランジスタTr88, Tr90がオンされる。すると、ノードN25は電源VccよりトランジスタTr89のしきい値分高いレベル以上には上昇しない。

1 がオンされるとともに、トランジスタTr88, Tr90 がオフされる。すると、Lレベルの入力信号A1がトランジスタTr89, Tr91を介してノードN25に出力されるため、ノードN25はLレベルとなり、出力信号XはHレベルとなる。また、トランジスタTr92 がオフされるとともに、トランジスタTr93 がオンされて、ノードN25がほぼ電源Vssレベルとなる。従って、Hレベルの出力信号Xは電源Vccレベルまで引き上げられる。

【0296】

入力信号A1, A2, A3が「1, 1, 1」となると、トランジスタTr89, Tr91 がオンされるとともに、トランジスタTr88, Tr90 がオフされる。

すると、Hレベルの入力信号A1がトランジスタTr89, Tr91を介してノードN25に出力されるため、ノードN25はHレベルとなり、出力信号XはLレベルとなる。

【0297】

このとき、ノードN25は、入力信号A2からトランジスタTr91, Tr89 のしきい値分低下したレベル以上には上昇しないが、ノードN25がHレベルとなって、出力信号XがLレベルとなると、トランジスタTr92 がオンされるとともに、トランジスタTr93 がオフされて、ノードN25がほぼ電源Vccレベルとなり、出力信号Xは電源Vssレベルまで引き下げられる。

【0298】

上記のような動作により、この論理回路は図33に示す真理値に基づく動作を行い、入力信号A1の反転信号と入力信号A2, A3とのAND論理を出力信号Xとして出力し、図32に示すシンボルで表記されるAND回路を構成する。

【0299】

上記のようなAND回路31では、次に示す作用効果を得ることができる。

(イ) 8個のMOSトランジスタにより、3入力AND回路31が構成されるので、前記第七の従来例に比して素子数を削減することができる。従って、回路面積を縮小することができる。

(ロ) 上記のような3入力AND回路31を多数搭載する半導体集積回路装置のチップ面積を縮小することができる。

(ハ) 出力信号安定化回路を備えたことにより、第九の実施の形態に比して、入力信号A1～A3の振幅が小さくなっても、出力信号Xを高電位側電源Vccと低電位側電源Vssとの間でフル振幅動作させることができる。

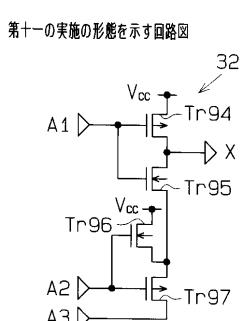

(第11の実施の形態)

図12は、この発明を具体化したCMOS論理回路の第十一の実施の形態を示す。この実施の形態は、前記第九の従来例と同様に3入力OR回路を構成する。

【0300】

入力信号A1は、PチャネルMOSトランジスタTr94 及びNチャネルMOSトランジスタTr95 のゲートに入力される。入力信号A2は、NチャネルMOSトランジスタTr96 及びPチャネルMOSトランジスタTr97 のゲートに入力される。

【0301】

入力信号A3は、前記トランジスタTr97 のドレイン(ソース)に入力される。

前記トランジスタTr94 のソースは、電源Vccに接続され、ドレインは前記トランジスタTr95 のドレイン(ソース)に接続される。

【0302】

前記トランジスタTr95 のソース(ドレイン)は、前記トランジスタTr97 のソース(ドレイン)及び前記トランジスタTr96 のソースに接続される。前記トランジスタTr96 のドレインは電源Vccに接続される。そして、前記トランジスタTr94 のドレインから出力信号Xが出力される。

【0303】

このように構成されたOR回路32は、図38に示す真理値に基づく動作を行う。すなわ

20

30

40

50

ち、入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> がともに「0」となると、トランジスタ Tr 94 , Tr 97 がオンされるとともに、トランジスタ Tr 95 , Tr 96 がオフされる。従って、出力信号 X は H レベルとなる。

【0304】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「1 , 0 , 0」となると、トランジスタ Tr 95 , Tr 97 がオンされるとともに、トランジスタ Tr 94 , Tr 96 がオフされる。すると、入力信号 A<sub>3</sub> がトランジスタ Tr 95 , Tr 97 を介して出力信号 X として出力されるため、出力信号 X は L レベルとなる。

【0305】

このとき、出力信号 X は、入力信号 A<sub>3</sub> よりトランジスタ Tr 97 のしきい値分高いレベルとなる。従って、入力信号 A<sub>2</sub> , A<sub>3</sub> に L レベルの入力信号として電源 V<sub>ss</sub> レベルを入力しても、出力信号 X は電源 V<sub>ss</sub> レベルまで下がらない。 10

【0306】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「0 , 1 , 0」となると、トランジスタ Tr 94 , Tr 96 がオンされるとともに、トランジスタ Tr 95 , Tr 97 がオフされる。従って、出力信号 X は H レベルとなる。

【0307】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「1 , 1 , 0」となると、トランジスタ Tr 95 , Tr 96 がオンされるとともに、トランジスタ Tr 94 , Tr 97 がオフされる。従って、出力信号 X は H レベルとなる。 20

【0308】

このとき、出力信号 X は、電源 V<sub>cc</sub> よりトランジスタ Tr 95 , Tr 96 のしきい値分低いレベルが出力される。従って、入力信号 A<sub>1</sub> , A<sub>2</sub> が電源 V<sub>cc</sub> であっても、出力信号 X は電源 V<sub>cc</sub> レベルまで上がらない。

【0309】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「0 , 0 , 1」となると、トランジスタ Tr 94 , Tr 97 がオンされるとともに、トランジスタ Tr 95 , Tr 96 がオフされる。従って、出力信号 X は H レベルとなる。

【0310】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「1 , 0 , 1」となると、トランジスタ Tr 95 , Tr 97 がオンされるとともに、トランジスタ Tr 94 , Tr 96 がオフされる。すると、入力信号 A<sub>3</sub> がトランジスタ Tr 95 , Tr 97 を介して出力信号 X として出力されるため、出力信号 X は H レベルとなる。 30

【0311】

このとき、出力信号 X は、入力信号 A<sub>3</sub> よりトランジスタ Tr 95 のしきい値分低いレベル以上には上昇しない。従って、H レベルの入力信号 A<sub>1</sub> , A<sub>3</sub> として電源 V<sub>cc</sub> レベルが入力されても、出力信号 X は電源 V<sub>cc</sub> レベルまで上昇しない。

【0312】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「0 , 1 , 1」となると、トランジスタ Tr 94 , Tr 96 がオンされるとともに、トランジスタ Tr 95 , Tr 97 がオフされる。従って、出力信号 X は H レベルとなる。 40

【0313】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「1 , 1 , 1」となると、トランジスタ Tr 95 , Tr 96 がオンされるとともに、トランジスタ Tr 94 , Tr 97 がオフされる。従って、出力信号 X は H レベルとなる。

【0314】

このとき、出力信号 X は、電源 V<sub>cc</sub> よりトランジスタ Tr 95 , Tr 96 のしきい値分低いレベルが出力される。

上記のような動作により、この論理回路は図 38 に示す真理値に基づく動作を行い、入力信号 A<sub>1</sub> の反転信号と入力信号 A<sub>2</sub> , A<sub>3</sub> との OR 論理信号を出力信号 X として出力し、 50

図37に示すシンボルで表記されるOR回路を構成する。

【0315】

上記のようなOR回路32では、次に示す作用効果を得ることができる。

(イ) 4個のMOSトランジスタにより、3入力OR回路32が構成されるので、前記第九の従来例に比して素子数を削減することができる。従って、回路面積を縮小することができる。

(ロ) インバータ回路を必要としないので、入力信号A1～A3の反転時にも電源Vccから電源Vssへの貫通電流は生じない。従って、消費電力を低減することができる。

(ハ) 上記のような3入力OR回路32を多数搭載する半導体集積回路装置のチップ面積を縮小することができる。

(二) 上記のような3入力OR回路32を多数搭載する半導体集積回路装置の消費電力を低減することができる。

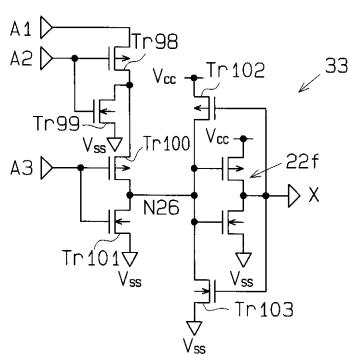

(第一二の実施の形態)

図13は、この発明を具体化したCMOS論理回路の第十二の実施の形態を示し、前記第十一の実施の形態と同様な論理を出力する。

【0316】

前記第十一の実施の形態では、Hレベルの出力信号Xが出力されるとき、その出力レベルが電源Vccレベルまで上昇しないときがある。また、Lレベルの出力信号Xが出力されるとき、その出力レベルが電源Vssレベルまで低下しないときがある。

【0317】

この実施の形態は、入力信号を出力信号Xとして出力するとき、出力信号Xを電源Vccレベルと電源Vssレベルとの間で確実にフル振幅動作させる構成としたものである。

【0318】

入力信号A1は、PチャネルMOSトランジスタTr98のソース(ドレイン)に入力される。

入力信号A2は、前記トランジスタTr98及びNチャネルMOSトランジスタTr99のゲートに入力される。

【0319】

入力信号A3は、PチャネルMOSトランジスタTr100及びNチャネルMOSトランジスタTr101のゲートに入力される。

前記トランジスタTr98のドレイン(ソース)は、前記トランジスタTr99のドレイン及び前記トランジスタTr100のソース(ドレイン)に接続され、同トランジスタTr99のソースは電源Vssに接続される。

【0320】

前記トランジスタTr100のドレイン(ソース)は、前記トランジスタTr101のドレインに接続されて、ノードN26が構成され、前記トランジスタTr101のソースは電源Vssに接続される。

【0321】

前記ノードN26は、CMOSインバータ回路22fに入力され、そのインバータ回路22fから出力信号Xが出力される。

前記出力信号Xは、PチャネルMOSトランジスタTr102及びNチャネルMOSトランジスタTr103のゲートに入力される。前記トランジスタTr102のソースは電源Vccに接続され、ドレインはノードN26に接続される。前記トランジスタTr103のドレインは、ノードN26に接続され、ソースは電源Vssに接続される。そして、インバータ回路22fと、トランジスタTr102, Tr103とで出力信号安定化回路が構成される。

【0322】

このように構成された論理回路33では、前記第九の従来例と同様に、図38に示す真理値に基づいて動作する。すなわち、入力信号A1, A2, A3がともに「0」となると、トランジスタTr98, Tr100がオンされるとともに、トランジスタTr99, Tr101がオ

10

20

30

40

50

Tr 101 がオフされる。

【0323】

すると、ノードN26には入力信号A1がトランジスタTr98, Tr100を介して出力されるため、ノードN26はLレベルとなる。このとき、ノードN26には、入力信号A1よりトランジスタTr100, Tr98のしきい値分高いレベルが出力される。

【0324】

ノードN26がLレベルとなると、出力信号XがHレベルとなって、トランジスタTr102がオフされるとともに、トランジスタTr103がオンされる。すると、ノードN26はほぼ電源Vssレベルまで低下し、出力信号Xはほぼ電源Vccレベルとなる。

【0325】

入力信号A1, A2, A3が「1, 0, 0」となると、トランジスタTr98, Tr100がオンされるとともに、トランジスタTr99, Tr101がオフされる。

すると、ノードN26には入力信号A1がトランジスタTr98, Tr100を介して出力されるため、ノードN26はHレベルとなる。このとき、Hレベルの入力信号A1として電源Vccレベルが入力されれば、ノードN26はほぼ電源Vccレベルとなる。そして、ノードN26がHレベルとなると、出力信号XはLレベルとなって、トランジスタTr102がオンされるとともに、トランジスタTr103がオフされる。

【0326】

入力信号A1, A2, A3が「0, 1, 0」となると、トランジスタTr99, Tr100がオンされるとともに、トランジスタTr98, Tr101がオフされる。

すると、ノードN26はトランジスタTr100, Tr99を介して電源Vssに接続されるため、Lレベルとなる。

【0327】

このとき、ノードN26は電源VssよりトランジスタTr100のしきい値分高いレベル以下には下がらない。

ノードN26がLレベルとなると、インバータ回路22fの動作により、出力信号XはHレベルとなって、トランジスタTr102がオフされるとともに、トランジスタTr103がオンされる。すると、ノードN26はほぼ電源Vssレベルとなり、出力信号Xはほぼ電源Vccレベルとなる。

【0328】

入力信号A1, A2, A3が「1, 1, 0」となると、トランジスタTr99, Tr100がオンされるとともに、トランジスタTr98, Tr101がオフされて、上記と同様にノードN26がLレベルとなり、出力信号XがHレベルとなる。

【0329】

入力信号A1, A2, A3が「0, 0, 1」となると、トランジスタTr98, Tr101がオフされるとともに、トランジスタTr99, Tr100がオフされて、ノードN26がLレベル、すなわちほぼ電源Vssレベルとなる。

【0330】

ノードN26がLレベルとなると、出力信号XがHレベルとなり、トランジスタTr102がオフされるとともに、トランジスタTr103がオンされる。従って、出力信号Xはほぼ電源Vccレベルとなる。

【0331】

入力信号A1, A2, A3が「1, 0, 1」となると、トランジスタTr98, Tr101がオフされるとともに、トランジスタTr99, Tr100がオフされて、ノードN26がLレベル、すなわちほぼ電源Vssレベルとなる。従って、上記と同様に出力信号XはHレベルとなり、ほぼ電源Vccレベルとなる。

【0332】

入力信号A1, A2, A3が「0, 1, 1」となると、トランジスタTr99, Tr101がオフされるとともに、トランジスタTr98, Tr100がオフされて、ノードN26がLレベル、すなわちほぼ電源Vssレベルとなる。従って、上記と同様に出力信

10

20

30

40

50

号 X は H レベルとなり、ほぼ電源 V<sub>cc</sub> レベルとなる。

【 0 3 3 3 】

入力信号 A<sub>1</sub> , A<sub>2</sub> , A<sub>3</sub> が「 1 , 1 , 1 」となると、トランジスタ Tr 99 , Tr 101 がオンされるとともに、トランジスタ Tr 98 , Tr 100 がオフされて、ノード N<sub>26</sub> が L レベル、すなわちほぼ電源 V<sub>ss</sub> レベルとなる。従って、上記と同様に出力信号 X は H レベルとなり、ほぼ電源 V<sub>cc</sub> レベルとなる。

【 0 3 3 4 】

上記のような動作により、この論理回路は図 38 に示す真理値に基づく動作を行い、入力信号 A<sub>1</sub> の反転信号と入力信号 A<sub>2</sub> , A<sub>3</sub> との OR 論理を出力信号 X として出力し、図 37 に示すシンボルで表記される OR 回路を構成する。

10

【 0 3 3 5 】

上記のような OR 回路 33 では、次に示す作用効果を得ることができる。

(イ) 8 個の MOS トランジスタにより、3 入力 OR 回路 33 が構成されるので、前記第九の従来例に比して素子数を削減することができる。従って、回路面積を縮小することができる。

(ロ) 上記のような 3 入力 OR 回路 33 を多数搭載する半導体集積回路装置のチップ面積を縮小することができる。

(ハ) 出力信号安定化回路を備えたことにより、第十一の実施の形態に比して、入力信号 A<sub>1</sub> ~ A<sub>3</sub> の振幅が小さくなっても、出力信号 X を高電位側電源 V<sub>cc</sub> と低電位側電源 V<sub>ss</sub> との間でフル振幅動作させることができる。

20

【 0 3 3 6 】

上記のような各実施の形態において、2 入力の論理回路は、第一及び第三の実施の形態に示すように、2 個のトランジスタで構成することができる。また、第五、第七、第九、第十一の実施の形態に示すように、3 入力の論理回路は、4 個のトランジスタを必要とする。一般的には、入力数を n とすれば、( 2n - 2 ) 個のトランジスタで構成することができる。

【 0 3 3 7 】

第一及び第三の実施の形態に対応する 2 入力の第一及び第二の従来例では、6 個のトランジスタを必要とする。第五、第七、第九、第十一の実施の形態に対応する 3 入力の論理回路では、10 個のトランジスタを必要とする。一般的には、入力数を n とすれば、( 4n - 2 ) 個のトランジスタを必要とする。

30

【 0 3 3 8 】

従って、上記各実施の形態では、対応する従来例に対し、素子数を削減することができる。

また、第一及び第三の実施の形態に対し、出力信号 X の振幅を電源 V<sub>cc</sub> と電源 V<sub>ss</sub> との間でフル振幅動作させるための出力信号安定化回路を備えた第二及び第四の実施の形態では、5 個のトランジスタを必要とする。第五、第七、第九、第十一の実施の形態に対し、出力信号安定化回路を備えた第六、第八、第十、第十二の実施の形態では、8 個のトランジスタを必要とする。

【 0 3 3 9 】

40

一般的には、入力数を n としたとき、n = 2 であれば 5 個、n = 3 であれば 2n + 2 個のトランジスタを必要とする。

従って、出力信号安定化回路を備えても、対応する従来例に対し、素子数を削減することができる。

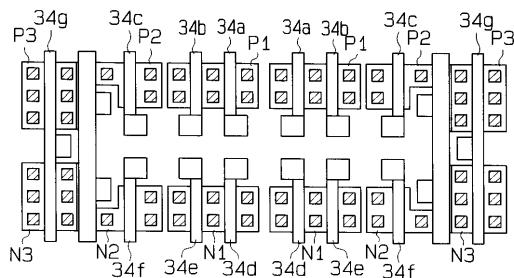

【 0 3 4 0 】

図 14 は前記第六、第八、第十、第十二の実施の形態の各論理回路を構成するトランジスタをチップ上にレイアウトするレイアウトパターンを示す。

領域 P<sub>1</sub> ~ P<sub>3</sub> は、それぞれ p 型拡散領域が形成され、領域 N<sub>1</sub> ~ N<sub>3</sub> は、それぞれ n 型拡散領域が構成される。領域 P<sub>1</sub> 上に形成された 2 本のゲート電極 34a , 34b により、領域 P<sub>1</sub> 上に 2 つの P チャネル MOS トランジスタが形成され、領域 P<sub>2</sub> 上に形成され

50

たゲート電極 34c により 1 つの P チャネル MOS トランジスタが形成される。

【0341】

領域 N1 上に形成された 2 本のゲート電極 34d, 34e により、領域 N1 上に 2 つの P チャネル MOS トランジスタが形成され、領域 N2 上に形成されたゲート電極 34f により 1 つの P チャネル MOS トランジスタが形成される。

【0342】

また、領域 P3, N3 上にまたがるゲート電極 34g により、インバータ回路が構成される。

このような構成により、3 個ずつの P チャネル MOS トランジスタ及び N チャネル MOS トランジスタと、一つのインバータ回路とからなる論理回路のバルクが形成され、一つの論理回路を構成するレイアウトパターンが、線対称状に、かつ規則的に多数レイアウトされる。

【0343】

そして、各領域に形成されたコンタクトホール 35 とゲート電極 34a ~ 34g 及び電源が配線（図示しない）により適宜接続されると、第六、第八、第十、第十二の実施の形態の各論理回路を構成することができる。

【0344】

このような構成とすることにより、前記第六、第八、第十、第十二の実施の形態の各論理回路を構成するバルクパターンを共通として、小さな面積で効率よくレイアウトすることができる。

【0345】

【発明の効果】

以上詳述したように、この発明は素子数を削減して回路面積を縮小し得る論理回路を提供することができる。また、論理回路を構成するインバータ回路の数を削減して、消費電力を低減し得る論理回路を提供することができる。

【図面の簡単な説明】

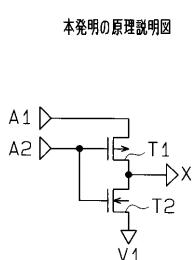

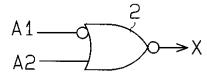

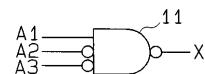

【図 1】本発明の原理説明図である。

【図 2】第一の実施の形態を示す回路図である。

【図 3】第二の実施の形態を示す回路図である。

【図 4】第三の実施の形態を示す回路図である。

【図 5】第四の実施の形態を示す回路図である。

【図 6】第五の実施の形態を示す回路図である。

【図 7】第六の実施の形態を示す回路図である。

【図 8】第七の実施の形態を示す回路図である。

【図 9】第八の実施の形態を示す回路図である。

【図 10】第九の実施の形態を示す回路図である。

【図 11】第十の実施の形態を示す回路図である。

【図 12】第十一の実施の形態を示す回路図である。

【図 13】第十二の実施の形態を示す回路図である。

【図 14】トランジスタのレイアウトの一例を示す説明図である。

【図 15】第一の従来例を示す回路図である。

【図 16】第一の従来例のシンボル図である。

【図 17】第一の従来例の真理値を示す説明図である。

【図 18】第二の従来例を示す回路図である。

【図 19】第二の従来例のシンボル図である。

【図 20】第二の従来例の真理値を示す説明図である。

【図 21】第三の従来例を示す回路図である。

【図 22】第三の従来例のシンボル図である。

【図 23】第三の従来例の真理値を示す説明図である。

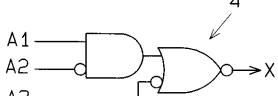

【図 24】第四の従来例を示す回路図である。

10

20

30

40

50

- 【図25】第四の従来例のシンボル図である。

- 【図26】第五の従来例を示す回路図である。

- 【図27】第五の従来例のシンボル図である。

- 【図28】第五の従来例の真理値を示す説明図である。

- 【図29】第六の従来例を示す回路図である。

- 【図30】第六の従来例のシンボル図である。

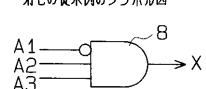

- 【図31】第七の従来例を示す回路図である。

- 【図32】第七の従来例のシンボル図である。

- 【図33】第七の従来例の真理値を示す説明図である。

- 【図34】第八の従来例を示す回路図である。

- 【図35】第八の従来例のシンボル図である。

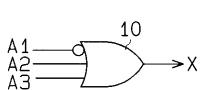

- 【図36】第九の従来例を示す回路図である。

- 【図37】第九の従来例のシンボル図である。

- 【図38】第九の従来例の真理値を示す説明図である。

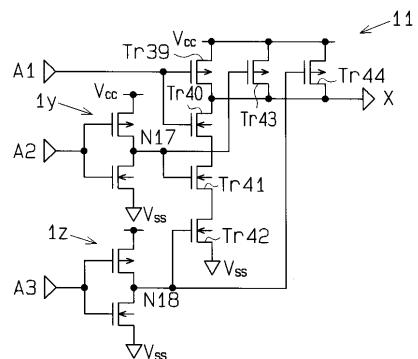

- 【図39】第十の従来例を示す回路図である。

- 【図40】第十の従来例のシンボル図である。

## 【符号の説明】

T 1 P チャネルMOSトランジスタ

T 2 N チャネルMOSトランジスタ

A 1, A 2 入力信号

X 出力信号

V 1 電源

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

第十二の実施の形態を示す回路図

【図14】

トランジスタのレイアウトの一例を示す説明図

【図18】

第二の従来例を示す回路図

【図19】

第二の従来例のシンボル図

【図20】

第二の従来例の真理値を示す説明図

| A1 | A2 | X |

|----|----|---|

| 0  | 0  | H |

| 0  | 1  | L |

| 1  | 0  | H |

| 1  | 1  | H |

【図15】

第一の従来例を示す回路図

【図16】

第一の従来例のシンボル図

【図17】

第一の従来例の真理値を示す説明図

| A1 | A2 | X |

|----|----|---|

| 0  | 0  | L |

| 0  | 1  | L |

| 1  | 0  | H |

| 1  | 1  | L |

【図21】

第三の従来例を示す回路図

【図22】

第三の従来例のシンボル図

第二の従来例の真理値を示す説明図

| A1 | A2 | X |

|----|----|---|

| 0  | 0  | H |

| 0  | 1  | L |

| 1  | 0  | H |

| 1  | 1  | H |

【図23】

第三の従来例の真理値を示す説明図

| A1 | A2 | A3 | X |

|----|----|----|---|

| 0  | 0  | 0  | L |

| 1  | 0  | 0  | L |

| 0  | 1  | 0  | L |

| 1  | 1  | 0  | L |

| 0  | 0  | 1  | H |

| 1  | 0  | 1  | L |

| 0  | 1  | 1  | H |

| 1  | 1  | 1  | H |

【図24】

第四の従来例を示す回路図

【図28】

第五の従来例の真理値を示す説明図

| A1 | A2 | A3 | X |

|----|----|----|---|

| 0  | 0  | 0  | L |

| 1  | 0  | 0  | L |

| 0  | 1  | 0  | H |

| 1  | 1  | 0  | L |

| 0  | 0  | 1  | H |

| 1  | 0  | 1  | H |

| 0  | 1  | 1  | H |

| 1  | 1  | 1  | H |

【図29】

第六の従来例を示す回路図

【図25】

第四の従来例のシンボル図

【図26】

第五の従来例を示す回路図

【図27】

第五の従来例のシンボル図

【図30】

第六の従来例のシンボル図

【図31】

第七の従来例を示す回路図

【図32】

第七の従来例のシンボル図

【図33】

第七の従来例の真理値を示す説明図

| A1 | A2 | A3 | X |

|----|----|----|---|

| 0  | 0  | 0  | L |

| 1  | 0  | 0  | L |

| 0  | 1  | 0  | L |

| 1  | 1  | 0  | L |

| 0  | 0  | 1  | L |

| 1  | 0  | 1  | L |

| 0  | 1  | 1  | H |

| 1  | 1  | 1  | L |

【図34】

【図37】

【図35】

第八の従来例のシンボル図

【図36】

第九の従来例を示す回路図

【図38】

第九の従来例のシンボル図

第九の従来例の真理値を示す説明図

| A1 | A2 | A3 | X |

|----|----|----|---|

| 0  | 0  | 0  | H |

| 1  | 0  | 0  | L |

| 0  | 1  | 0  | H |

| 1  | 1  | 0  | H |

| 0  | 0  | 1  | H |

| 1  | 0  | 1  | H |

| 0  | 1  | 1  | H |

| 1  | 1  | 1  | H |

【図39】

第十の従来例を示す回路図

【図40】

第十の従来例のシンボル図

---

フロントページの続き

(56)参考文献 特開平05-300007(JP, A)

特開平04-253366(JP, A)

特開昭56-062427(JP, A)

特開昭53-081061(JP, A)

特開昭60-030215(JP, A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H03K 19/20

H03K 19/0948

H03K 19/21