(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년05월03일

(11) 등록번호 10-1260632

(24) 등록일자 2013년04월26일

|                       |                                           |                 |

|-----------------------|-------------------------------------------|-----------------|

| (51) 국제특허분류(Int. Cl.) | G11C 16/06 (2006.01) G11C 16/26 (2006.01) |                 |

|                       | G11C 16/10 (2006.01) G11C 16/30 (2006.01) |                 |

| (21) 출원번호             | 10-2012-7027496                           | (분할)            |

| (22) 출원일자(국제)         | 2006년09월29일                               |                 |

|                       | 심사청구일자                                    | 2012년11월14일     |

| (85) 번역문제출일자          | 2012년10월22일                               |                 |

| (65) 공개번호             | 10-2012-0135327                           |                 |

| (43) 공개일자             | 2012년12월12일                               |                 |

| (62) 원출원              | 특허                                        | 10-2008-7010560 |

|                       | 원출원일자(국제)                                 | 2006년09월29일     |

|                       | 심사청구일자                                    | 2011년03월31일     |

| (86) 국제출원번호           | PCT/CA2006/001609                         |                 |

| (87) 국제공개번호           | WO 2007/036050                            |                 |

|                       | 국제공개일자                                    | 2007년04월05일     |

| (30) 우선권주장            |                                           |                 |

(73) 특허권자

**모사이드 테크놀로지스 인코퍼레이티드**

캐나다 케이2케이 2엑스1 온타리오 오타와 스위트

203 하인스 로드 11

(72) 발명자

**오, 학준**

캐나다, 온타리오 케이2티 1제이3, 카나타, 캠비

어 크레센트 21

**편, 홍, 범**

캐나다, 온타리오 케이2엠, 2이1, 카나타, 리버그

린 크레센트 16

**김, 진기**

캐나다, 온타리오 케이2케이 3에이치6, 카나타,

아이언사이드코트 46

(74) 대리인

**하약특허법인**

11/324,023 2005년12월30일 미국(US)

(뒷면에 계속)

(56) 선행기술조사문현

JP1993210981 A

전체 청구항 수 : 총 14 항

### 심사관 : 학석경

#### (54) 발명의 명칭 출력 제어 메모리

### (57) 요약

반도체 메모리에서 직렬 데이터 링크 인터페이스의 출력 포트로의 데이터 전송을 제어하는 장치, 시스템 및 방법이 개시된다. 일예로, 플래시 메모리 장치는 복수의 직렬 데이터 링크, 복수의 메모리 뱅크, 및 메모리 장치가 메모리 장치의 직렬 데이터 출력 포트에 직렬 데이터를 전송할 수 있게 하는 제어 입력 포트를 가질 수 있다. 다른 예에서, 플래시 메모리 장치는 단일 직렬 데이터 링크, 단일 메모리 뱅크, 직렬 데이터 입력 포트, 출력 인에 이를 신호를 수신하기 위한 제어 입력 포트를 가질 수 있다. 플래시 메모리 장치는, 메모리 장치 사이에서 직렬로 통신하기 위해 반향 신호 라인을 사용하는 데이지-체인 구성(daisy-chain configuration)으로 캐스케이딩될 수 있다.

## 대표도 - 도2a

(30) 우선권주장

60/722,368 2005년09월30일 미국(US)

60/847,790 2006년09월27일 미국(US)

---

## 특허청구의 범위

### 청구항 1

반도체 장치로서,

복수의 플래시 메모리 뱅크로서, 각 플래시 메모리 뱅크는 각각의 행 디코딩 회로 및 각각의 감지 증폭기 회로를 갖는, 복수의 플래시 메모리 뱅크;

메모리 뱅크 상태 지시자를 저장하기 위한 레지스터로서, 각 메모리 뱅크 상태 지시자는 상기 복수의 플래시 메모리 뱅크 각각이 사용중인지 여부를 나타내기 위한 것인, 레지스터; 및

인터페이스로서, i) 상기 인터페이스의 입력 포트에서 어드레스 및 명령 데이터 모두를 공통으로 수신하고; ii) 상기 플래시 메모리 뱅크를 어드레스하며; 또한, iii) 중첩되는 시간 주기에서 상기 플래시 메모리 뱅크 중 적어도 2개에서 수행되는 동작을 개시하도록 동작가능한, 인터페이스를 포함하며,

상기 인터페이스 및 상기 플래시 메모리 뱅크는 상기 반도체 장치의 단일 칩에서 제공되는, 반도체 장치.

### 청구항 2

청구항 1에 있어서, 상기 인터페이스는 직렬로 데이터를 통신하도록 동작가능한, 반도체 장치.

### 청구항 3

청구항 1에 있어서, 상기 인터페이스는 출력 데이터 포트를 포함하는, 반도체 장치.

### 청구항 4

청구항 3에 있어서, 상기 입력 포트는 일방향(unidirectional) 입력 데이터 포트이고, 상기 출력 데이터 포트는 일방향 출력 데이터 포트인, 반도체 장치.

### 청구항 5

청구항 1에 있어서, 상기 동작 중 하나는 상기 플래시 메모리 뱅크 중 적어도 하나에서 개시되는 한편 상기 동작 중 제2의 이전 동작은 상기 플래시 메모리 뱅크 중 다른 뱅크에서 실행되고 있는, 반도체 장치.

### 청구항 6

청구항 1에 있어서, 상기 동작은 페이지 판독, 프로그램 및 소거 동작 중 적어도 2개를 포함하는, 반도체 장치.

### 청구항 7

청구항 1에 있어서, 상기 동작은 데이터 전송 동작을 포함하는, 반도체 장치.

### 청구항 8

청구항 1에 있어서, 상기 동작은 페이지 판독, 프로그램 및 소거 동작 중 적어도 1개, 및 데이터 전송 동작을 포함하는, 반도체 장치.

### 청구항 9

청구항 1에 있어서, 상기 복수의 플래시 메모리 뱅크는 2개의 플래시 메모리 뱅크보다 많은, 반도체 장치.

### 청구항 10

청구항 9에 있어서, 상기 2개의 플래시 메모리 뱅크보다 많은 플래시 메모리 뱅크는 적어도 4개의 플래시 메모리 뱅크인, 반도체 장치.

### 청구항 11

청구항 1 내지 10 중 어느 하나의 청구항에 있어서, 상기 인터페이스는 상기 플래시 메모리 뱅크 중 임의의 뱅

크에서 임의의 어드레스를 액세스하기 위해 독립적으로 제어가능한, 반도체 장치.

### 청구항 12

청구항 11에 있어서, 상기 인터페이스는, 상기 플래시 메모리 뱅크 중 임의의 뱅크에서 임의의 행을 액세스하기 위해, 또한 독립적으로 제어가능한, 반도체 장치.

### 청구항 13

청구항 11에 있어서, 상기 인터페이스는, 상기 플래시 메모리 뱅크 중 임의의 뱅크에서 임의의 열을 액세스하기 위해, 또한 독립적으로 제어가능한, 반도체 장치.

### 청구항 14

청구항 1 내지 10 중 어느 하나의 청구항에 있어서, 상기 플래시 메모리 뱅크는 NAND 플래시 메모리 뱅크인, 반도체 장치.

## 명세서

### 기술 분야

[0001] 본 발명은 반도체 메모리 장치에 관한 것이다. 더욱 상세하게, 본 발명은 반도체 플래시 메모리 장치의 속도 및/또는 용량을 개선하기 위한 메모리 구조에 관한 것이다.

### 배경 기술

[0002] 디지털 카메라, 휴대용 디지털 정보단말, 휴대용 오디오/비디오 재생기 및 이동 단말기와 같은 이동 전자 장치는 대용량 메모리, 바람직하게는 용량 및 속도 성능이 더욱 증가하고 있는 비휘발성 메모리를 계속해서 필요로 한다. 예컨대 현재 이용 가능한 오디오 재생기는 오디오/비디오 데이터를 저장하기 위해 256Mbytes와 40Gbytes 사이의 메모리를 가질 수 있다. 데이터가 전원이 꺼진 경우에도 유지되어, 배터리 수명을 연장하므로, 플래시 메모리 및 하드디스크 드라이브와 같은 비휘발성 메모리가 선호된다.

[0003] 현재, 하드디스크 드라이브는 20 내지 40Gbytes의 데이터를 저장할 수 있는 고밀도이지만, 상대적으로 부피가 크다. 그러나 고체-상태 드라이브로도 알려져 있는 플래시 메모리는 고밀도, 비휘발성 및 하드디스크 드라이브에 비해 작은 크기를 가짐으로 인해 인기를 끌고 있다. 플래시 메모리 기술은 EEPROM 및 EEPROM 기술을 기초로 한다. 용어 "플래시"는, 다수의 메모리 셀이 각 바이트가 개별적으로 소거되었던 EEPROM과 차별화되어 한번에 소거될 수 있기 때문에 선택되었다. 멀티-레벨 셀(MLC)의 출현은 단일 레벨 셀에 비해 플래시 메모리 밀도를 더 증가시킨다. 당업자는 플래시 메모리가 NOR 플래시나 NAND 플래시로 구성될 수 있으며, 이때 NAND 플래시는 더욱 간소한 메모리 어레이 구조로 인해 소정의 면적당 더 높은 밀도를 가짐을 이해할 것이다. 더 논의하기 위해, 플래시 메모리에 대한 인용은 NOR 또는 NAND 또는 다른 타입의 플래시 메모리 중 어느 하나인 것으로 이해되어야 한다.

[0004] 기존의 플래시 메모리 모듈은 다수의 현재의 가전 장치에 충분한 속도로 동작하지만, 그러한 메모리 모듈은 높은 데이터 레이트(rate)가 요구되는 다른 장치에서 사용하기에는 아마도 적당하지 않을 것이다. 예컨대 고선명 동화상을 레코딩하는 이동 멀티미디어 장치는 아마도 적어도 10MB/s의 프로그래밍 처리량을 갖는 메모리 모듈을 필요로 할 것이며, 이러한 처리량은 7MB/s의 전형적인 프로그래밍 데이터 레이트를 갖는 현재의 플래시 메모리 기술로는 얻을 수 없다. 복수-레벨 셀 플래시는 셀을 프로그램하는데 필요한 복수-단계 프로그래밍 시퀀스로 인해 1.5MB/s와 같이 훨씬 더 느린 속도를 갖는다.

[0005] 플래시 메모리의 프로그래밍 및 판독 처리량은 플래시 메모리의 동작 주파수를 증가시킴으로써 직접적으로 증가 할 수 있다. 예컨대 대략 20~30MHz인 현재 동작 주파수는 대략 200MHz까지 한 자릿수(an order of magnitude) 만큼 증가할 수 있다. 이 방법은 간단한 것처럼 보이지만, 그러한 고 주파수에서 신호 품질에 상당한 문제가 있으며, 이로 인해 플래시 메모리의 동작 주파수가 실질적으로 제한된다. 특히, 플래시 메모리는 요구되는 구성에 따라 8 또는 16개에 달하는 병렬 입/출력(I/O) 핀의 세트를 사용하여 다른 소자와 통신하며, 상기 핀은 명령 지시를 수신하고, 입력 데이터를 수신하며 및 출력 데이터를 제공한다. 이것은 흔히 병렬 인터페이스라고 알려져 있다. 고속 동작으로 인해, 예컨대 신호 품질을 저하하는 혼신(cross-talk), 신호 왜곡(skew) 및 신호 감쇄와 같이 잘 알려져 있는 통신 저하 효과가 발생할 것이다.

## 발명의 내용

### 해결하려는 과제

[0006] 그러한 병렬 인터페이스는 데이터를 관리 및 기록하기 위해 다수의 핀을 사용한다. 입력 핀 및 와이어(wire)의 수가 증가함에 따라, 불필요한 효과의 수도 증가한다. 이들 효과는 심벌간 간섭, 신호 왜곡 및 혼신을 포함한다. 심벌간 간섭은 와이어를 따라 일주하는 신호의 감쇄 및 복수 개의 요소가 이 와이어에 연결될 때 발생하는 반사 신호(reflections)로 인해 생긴다. 신호 왜곡은 신호가 다른 길이 및/또는 특징을 갖는 와이어를 따라 일주하고 종점에 다른 시간에 도달할 때 발생한다. 혼신은 근접해 있는 와이어 상의 신호의 원치 않는 결합을 지칭한다. 메모리 장치의 동작 속도가 증가할수록 혼신은 더욱 문제가 된다.

[0007] 그러므로 메모리 모듈에 액세스하는데 필요한 입력 핀과 와이어의 개수를 최소화하면서, 메모리 용량 및/또는 동작 속도를 증가시킨 이동 전자 장치 및 고체 구동 애플리케이션에서 사용하기 위한 메모리 모듈이 당업계에서 필요하게 되었다.

### 과제의 해결 수단

[0008] 다음은 본 발명의 여러 양상을 기본적으로 이해하기 위한 본 발명의 일부 실시예의 간략화된 개요이다. 이러한 개요는 본 발명의 광범위한 개관(extensive overview)이 아니다. 이것은 본 발명의 핵심 즉 중요한 요소를 식별하거나 본 발명의 범주를 정하기 위한 것이 아니다. 이것의 유일한 목적은, 후술될 상세한 설명의 서론으로서 간략한 형태로 본 발명의 일부 실시예를 제공하는 것이다.

[0009] 본 발명의 실시예에 따라, 반도체 메모리 장치는 메모리, 직렬 입력 데이터를 메모리에 전송하는 직렬 데이터 링크 및 입력 제어 신호를 포함한다. 제어 회로는 직렬 데이터 링크 인터페이스와 메모리 사이의 데이터 전송을 제어한다. 본 발명의 원리에 부합하여, 메모리는 단일 메모리 뱅크나 복수의 메모리 뱅크일 수 있다. 직렬 데이터 링크 인터페이스는 메모리 뱅크에 전송되도록 직렬 입력 데이터를 병렬 데이터로 변환할 수 있다. 또한, 직렬 링크 인터페이스는 메모리 뱅크로부터 전달받은 병렬 데이터를 직렬 출력 데이터로 변환할 수 있다. 본 발명의 여러 다른 양상이 또한 본 명세서 전반에 걸쳐서 개시되어 있다.

### 발명의 효과

[0010] 본 발명의 원리에 따라, 플래시 메모리 시스템은 복수의 직렬로 연결된 플래시 메모리 장치를 가질 수 있다. 이러한 시스템의 플래시 메모리 장치는 직렬 입력 데이터 포트, 직렬 데이터 출력 포트, 다수의 제어 입력 포트 및 다수의 제어 출력 포트를 포함한다. 플래시 메모리 장치는 외부 소스로부터 직렬 입력 데이터 및 제어 신호를 수신하고 데이터 및 제어 신호를 외부 장치에 제공하도록 구성된다. 이 외부 소스 및 외부 장치는 시스템 내의 다른 플래시 메모리 장치일 수 있다. 본 발명의 일부 실시예에서, 플래시 메모리 장치 각각은 고유한 장치 식별자를 포함할 수 있다. 장치는 장치가 타겟 장치인지를 판정하도록 타겟 장치 정보를 장치의 고유한 장치 식별 번호와 상관시키기 위해 직렬 입력 데이터의 타겟 장치 정보 필드를 분석하도록 구성될 수 있다. 장치는 수신된 임의의 추가 입력 데이터를 처리하기 전에 타겟 장치 정보 필드를 분석할 수 있다. 만약 메모리 장치가 타겟 장치가 아니라면, 장치는 직렬 입력 데이터를 무시함으로써, 추가 처리 시간 및 자원을 절약할 수 있다.

[0011] 본 발명의 실시예에 따라, 메모리 장치 및 방법은, SIP(Serial Input Port) 및 SOP(Serial Output Port)인 직렬 입출력 핀의 단일 세트를 입/출력 포트 각각의 인에이블링/디스에이블링을 위한 두 제어 신호, 즉 IPE(Input Port Enable) 및 OPE(Output Port Enable)와 함께 완전히 직렬화한다(serialize). 이점은 메모리 제어기에게 최대한의 융통성을 갖는 데이터 통신을 제공한다. 본 발명의 메모리 장치는, IPE가 '높은(High)' 논리 상태에 있을 때만 장치의 SIP 포트를 거쳐서 정보 신호 스트림을 수신하며, 장치는 또한, OPE가 '높은' 논리 상태에 있을 때만 장치의 SOP 포트를 거쳐서 출력 데이터 신호 스트림을 송신한다. IPE가 '높은' 상태(프리-러닝(free-running) 직렬 클록 신호(SCLK: Serial Clock Signal)의 상승 에지에서 참조됨)가 될 때, SIP 포트는 장치 어드레스 바이트, 명령 바이트, 열 어드레스 바이트, 행 어드레스 바이트 및/또는 입력 데이터 바이트인 연속적인 직렬 입력 스트림 바이트를 각 동작의 경우에 대한 미리 결정된 수의 클록 사이클 동안에 수신하기 시작한다. 만약 IPE가 '낮은' 상태가 된다면, SIP 포트는 입력 신호 스트리밍 바이트를 수신하는 것을 정지한다. OPE 신호가 '높은' 상태가 될 때, SOP 포트는 프리-러닝 직렬 클록 신호(SCLK)의 상승 에지에서 참조된 데이터를 출력하기 시작한다. 만약 OPE가 '낮은' 상태가 되면, SOP는 데이터 출력을 정지한다. 그러므로, 메모리 제어기는 메모리 장치와 제어기 자신의 통신을 제어하기 위한 더 큰 융통성을 가질 수 있다.

[0012] 또한, 장치가 시스템에서 직렬로 연결될 때, 장치는 수신된 IPE 및 OPE 신호를 외부 장치에 "반향(echo)"하는 출력 제어 포트를 더 포함할 수 있다. 이로 인해 시스템은 (방송/멀티-드롭(multi-drop) 캐스케이딩 방식에 대비하여) 테이지-체인 캐스케이딩 방식을 형성하기 위해 점-대-점 방식으로 연결된 신호 포트(예컨대, SIP/SOP, IPE/IPEQ, OPE/OPEQ, SCLK1/SCLK0)를 갖게 된다. 이들 시스템은 제한된 하드웨어의 물리적인 장치 선택 핀을 사용하기보다는 고유한 장치 식별 및 타겟 장치 선택 어드레스 방식을 사용할 수 있어서, 전체 시스템은 시스템의 전체 성능을 희생하지 않고도 메모리 밀도 면에서 가능한 한 많이 쉽게 확장될 수 있다.

[0013] 본 발명은 예를 들어 예시되어 있으며, 유사한 참조번호가 유사한 요소를 지시하는 첨부하는 도면으로 제한되지 않는다.

### 도면의 간단한 설명

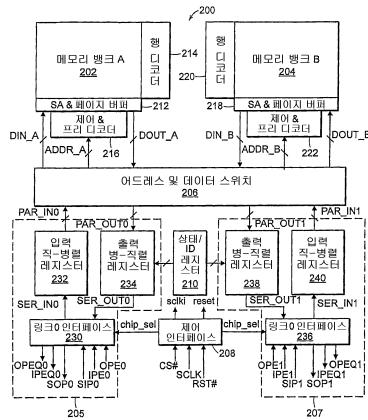

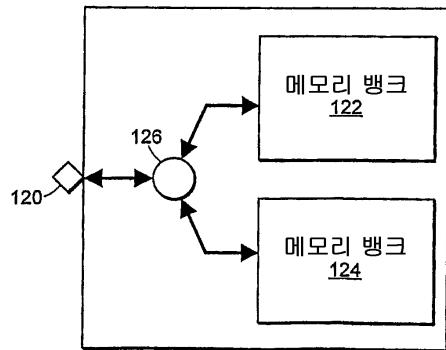

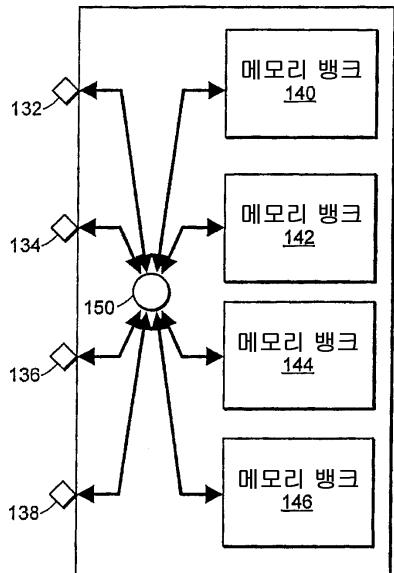

[0014] 도 1a, 도 1b 및 도 1c는 본 발명의 여러 양상에 따라 동시에 동작할 수 있는 예시적인 메모리 장치를 도시하는 높은 수준의 도면이다.

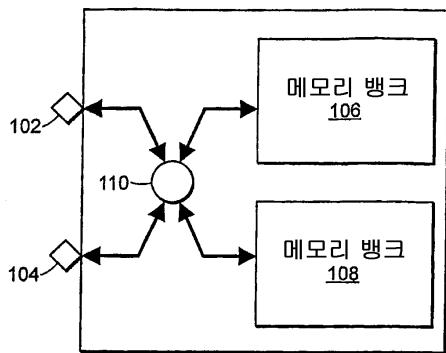

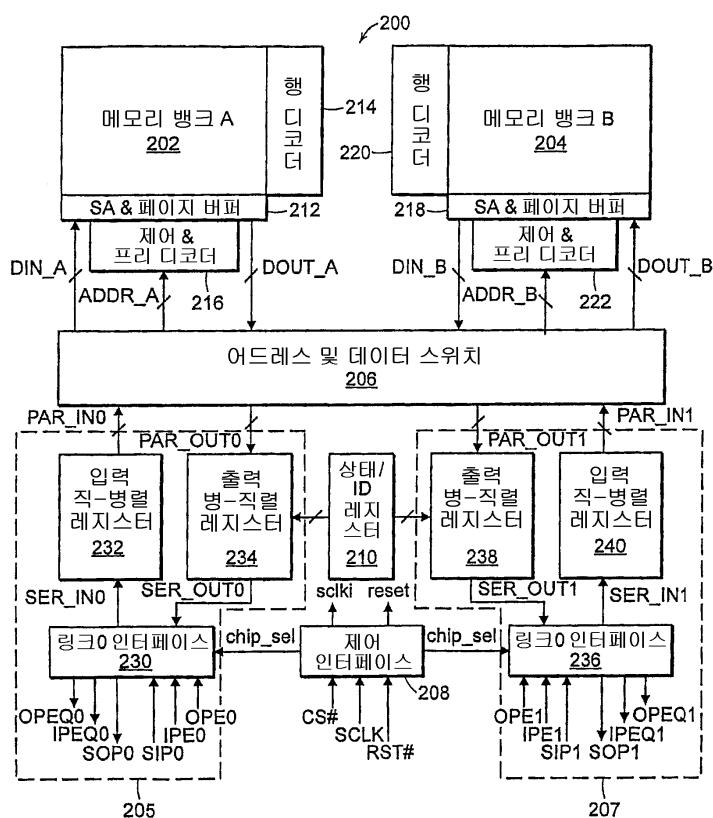

도 2a는 본 발명의 양상에 따른 예시적인 메모리 장치의 높은 수준의 블록도이다.

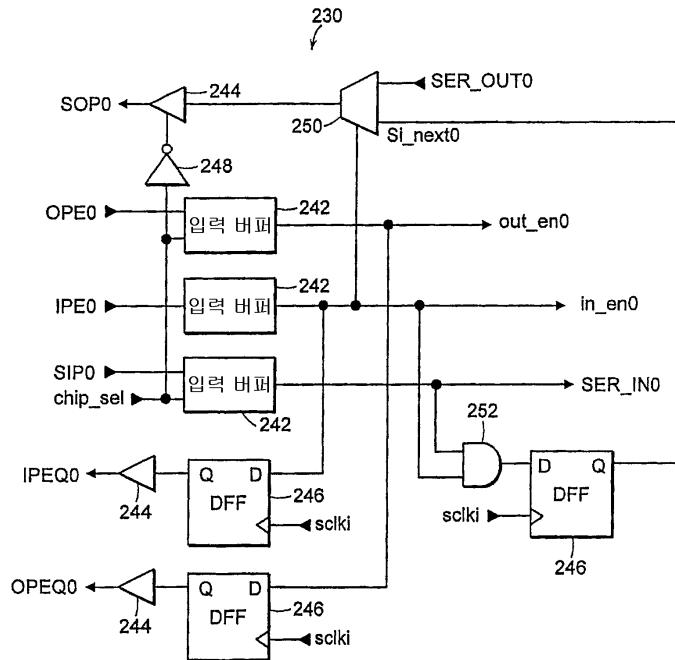

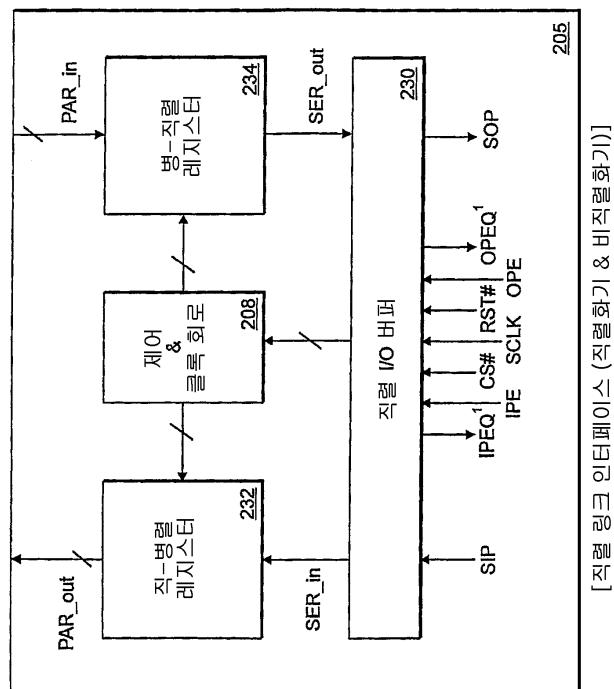

도 2b는 본 발명의 실시예에 따른 도 2a에 도시된 직렬 데이터 링크의 개략도이다.

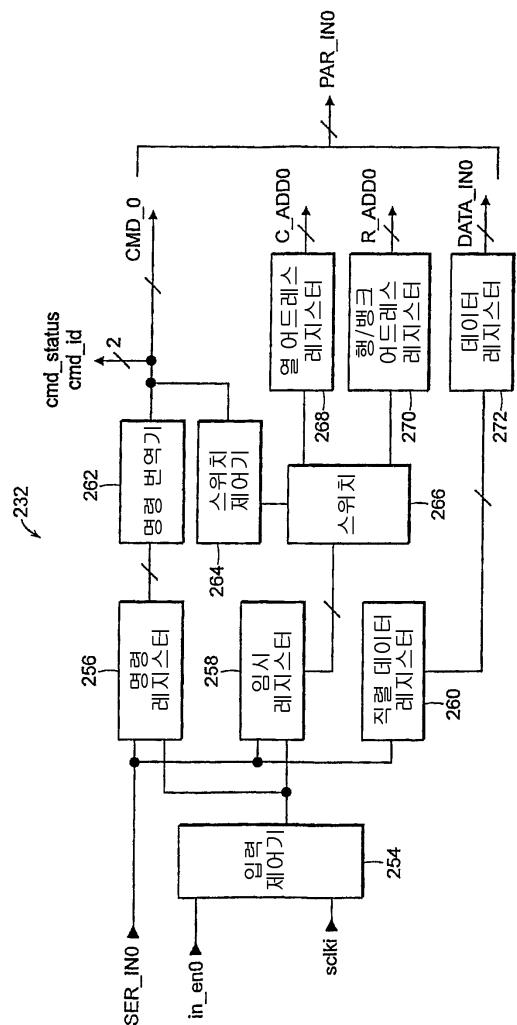

도 2c는 본 발명의 실시예에 따른 도 2a에 도시된 입력 직-병렬 레지스터 블록의 개략도이다.

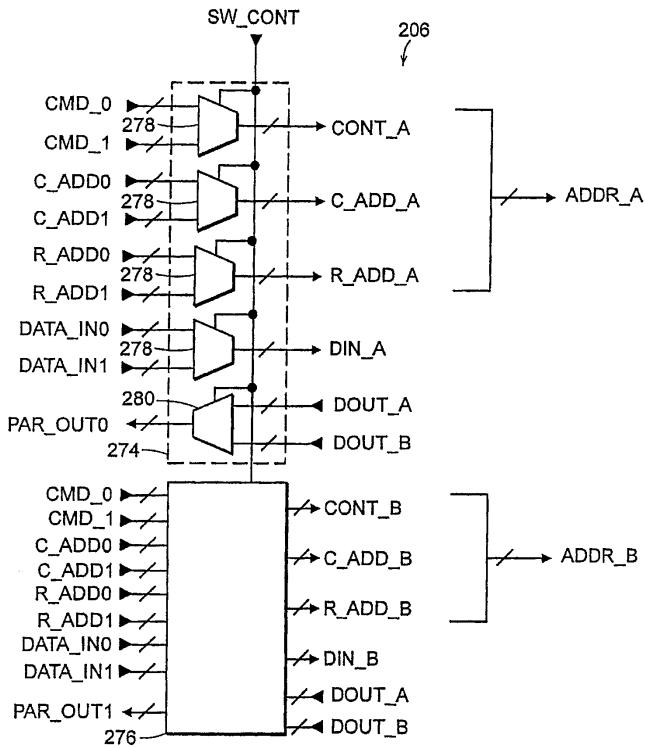

도 2d는 본 발명의 실시예에 따른 도 2a에 도시된 경로 스위치 회로의 개략도이다.

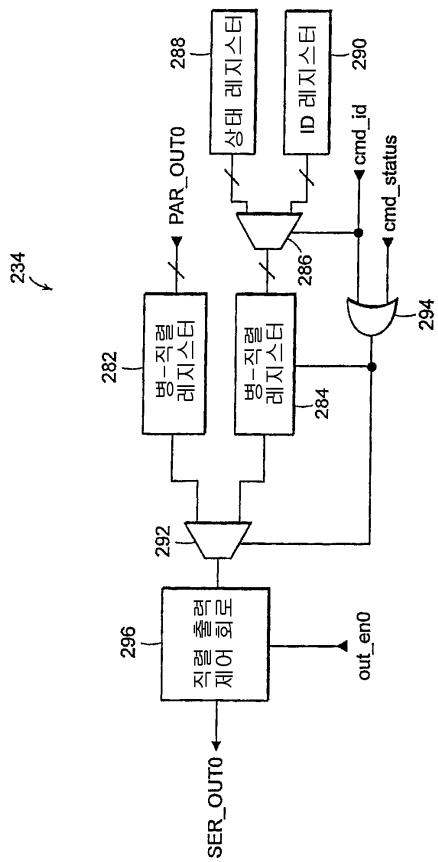

도 2e는 본 발명의 실시예에 따른 도 2a에 도시된 출력 병-직렬 레지스터 블록의 개략도이다.

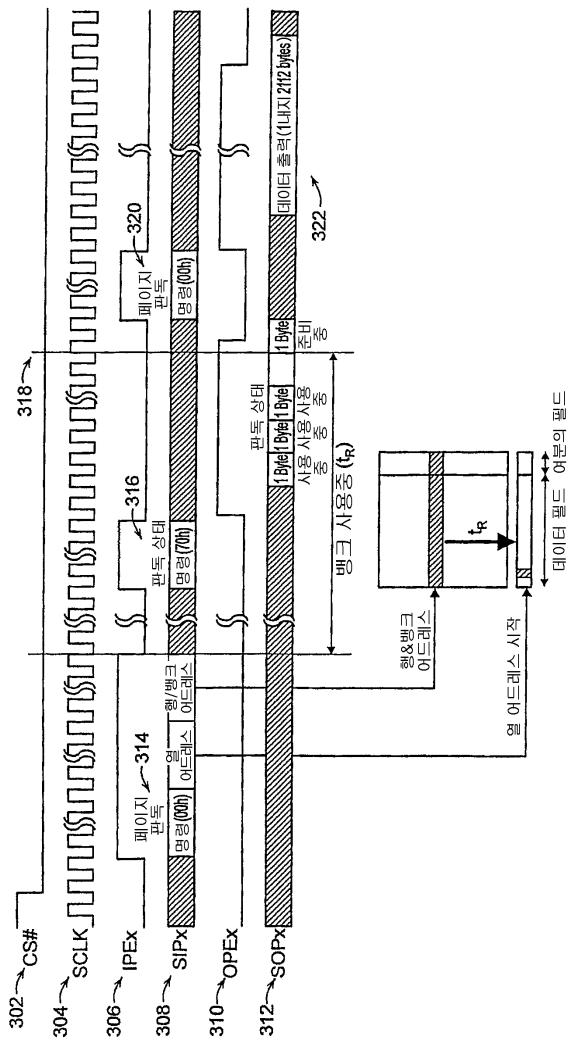

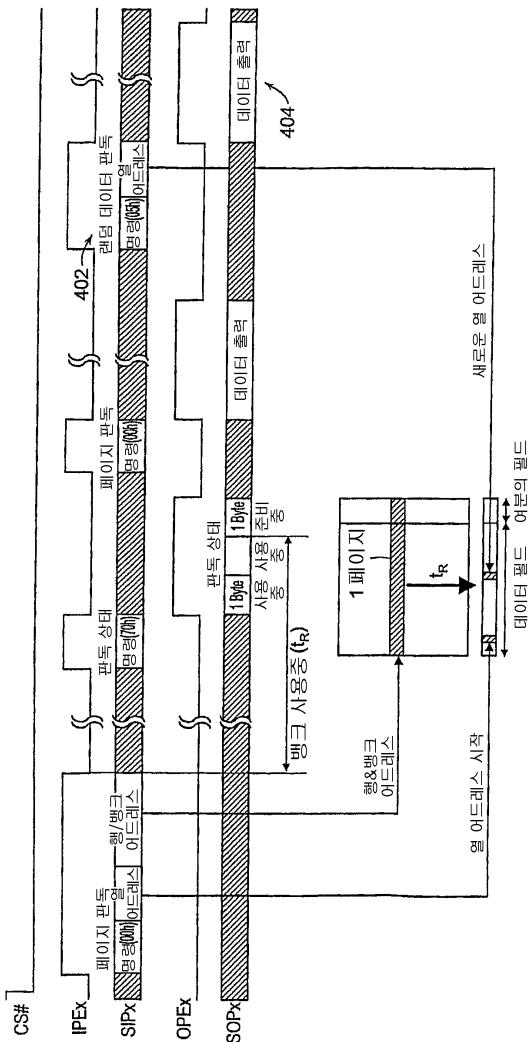

도 3a, 도 4, 도 5a, 도 6a 및 도 7은 본 발명의 여러 양상에 따른 메모리 장치에 의해 실행된 메모리 동작에 대한 타이밍 도이다.

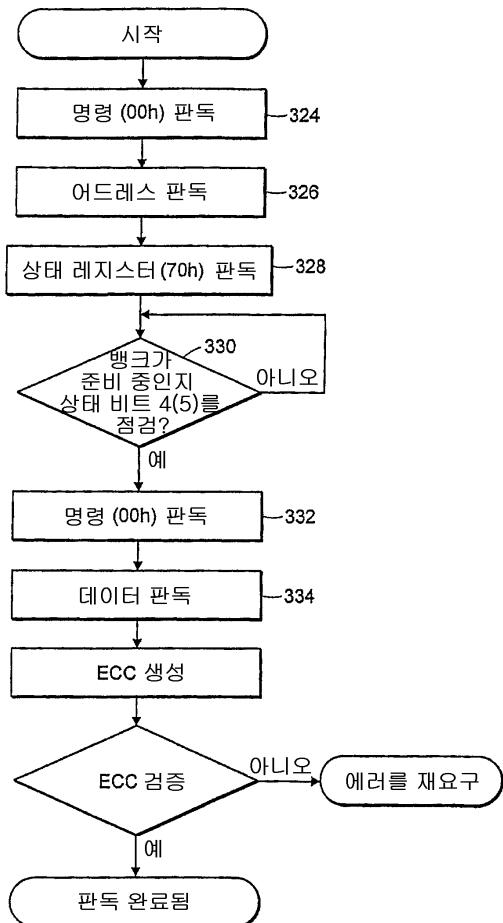

도 3b, 도 5b 및 도 6b는 본 발명의 여러 양상에 따른 장치에서 도 3a, 도 5a 및 도 6a 각각의 메모리 동작을 예시한 흐름도이다.

도 8a, 도 8b 및 도 8c는 본 발명의 여러 양상에 따른 메모리 장치에서 실행된, 동시 메모리 동작에 대한 타이밍 도이다.

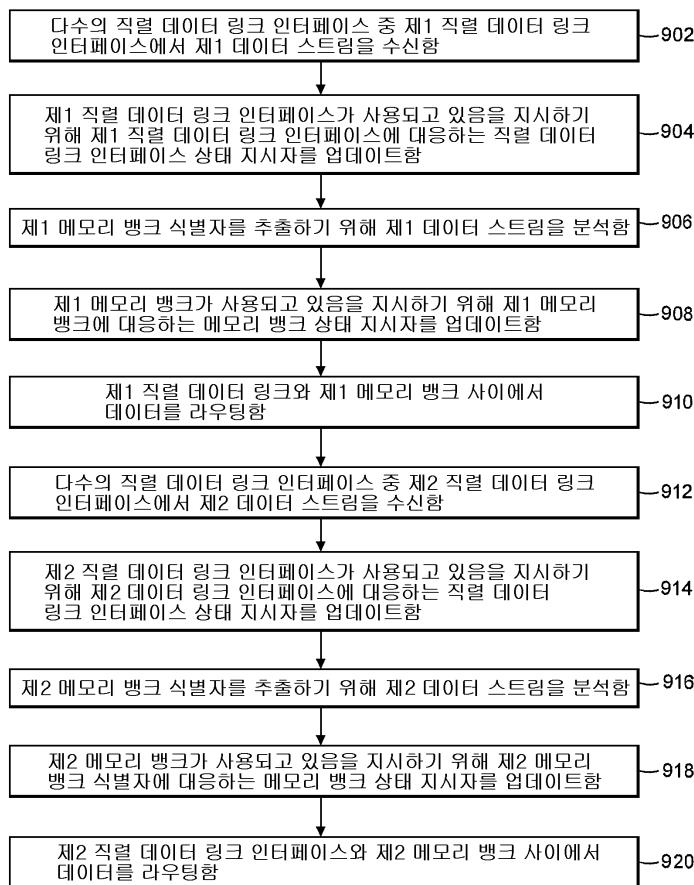

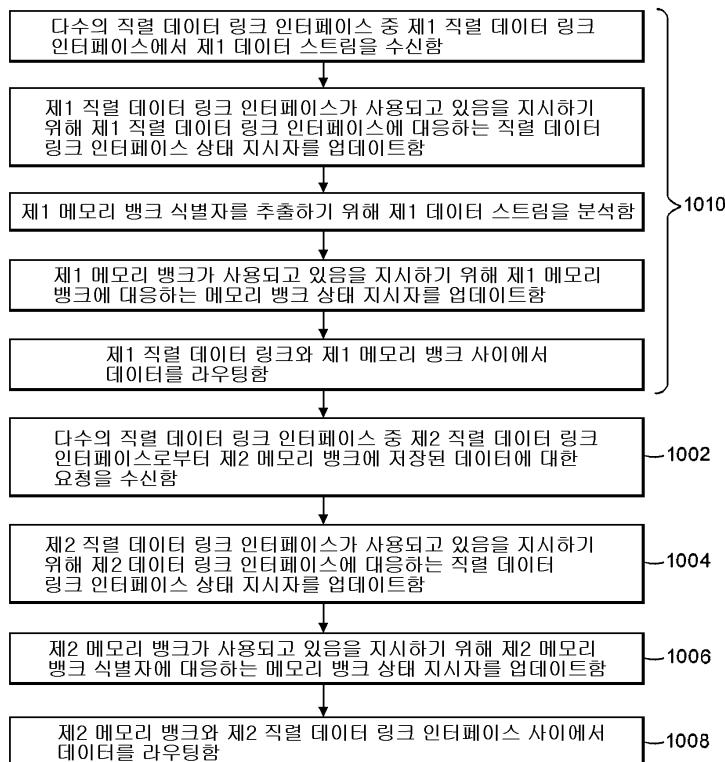

도 9 및 도 10은 본 발명의 여러 양상에 따른 다수의 직렬 데이터 링크 인터페이스와 다수의 메모리 뱅크 사이에서의 데이터 전송을 제어하는 방법을 도시한 흐름도이다.

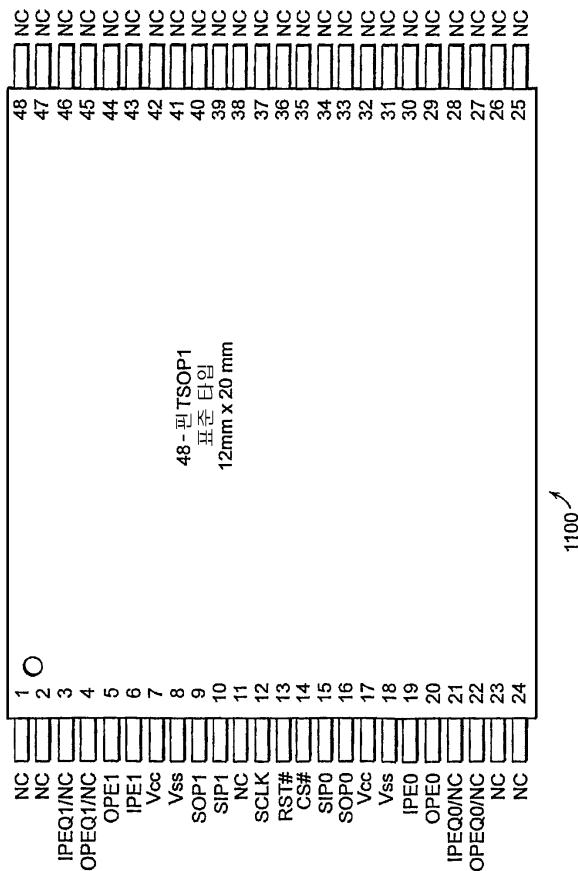

도 11은 본 발명의 여러 양상에 따른 장치 내의 메모리 장치의 핀-아웃(pin-out) 구성의 블록도이다.

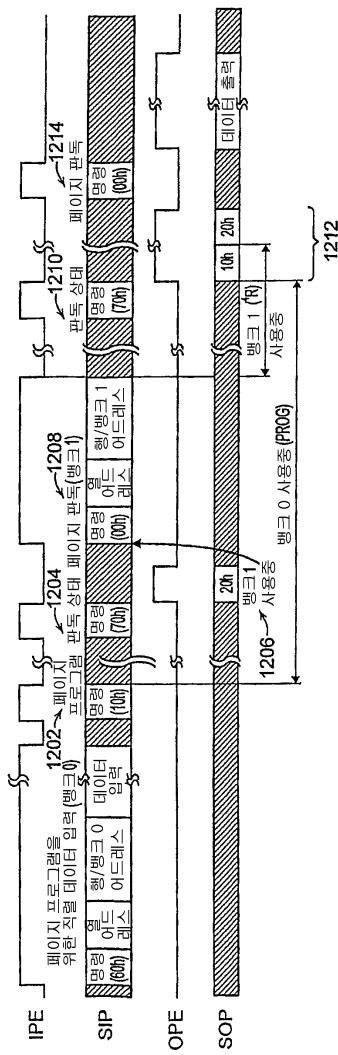

도 12는 본 발명에 따른 가상의 복수의 링크 특성의 여러 양상이 장착된 메모리 장치에서 실행된 메모리 동작에 대한 타이밍 도이다.

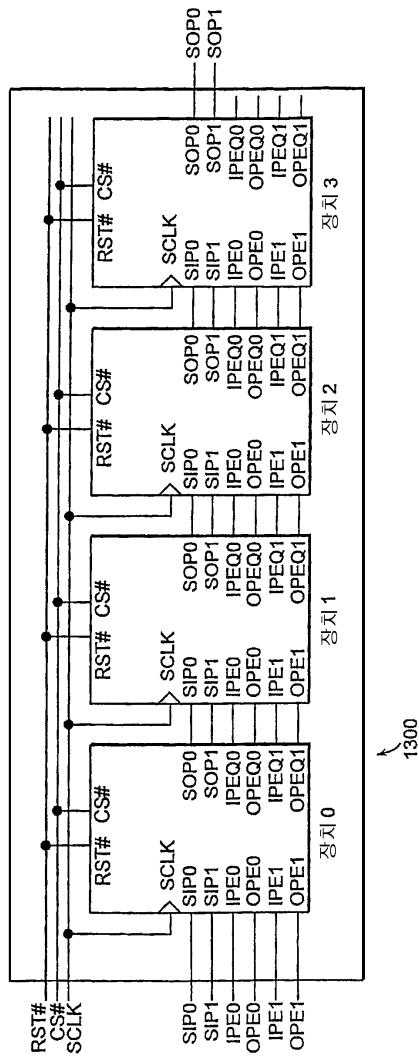

도 13a는 본 발명의 여러 양상에 따른 다수의 메모리 장치의 캐스케이딩된 구성의 높은 수준의 블록도이다.

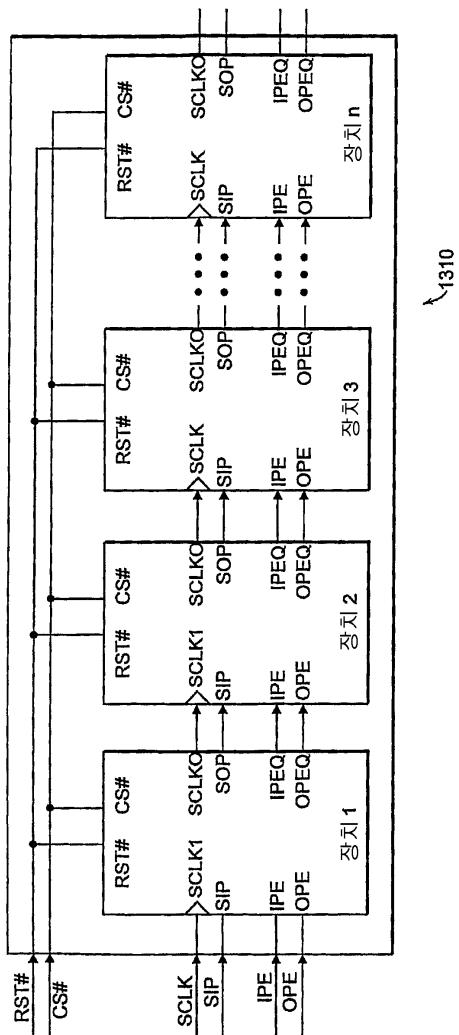

도 13b는 본 발명의 여러 양상에 따른 다수의 메모리 장치의 대안의 캐스케이딩된 구성의 높은 수준의 블록도이다.

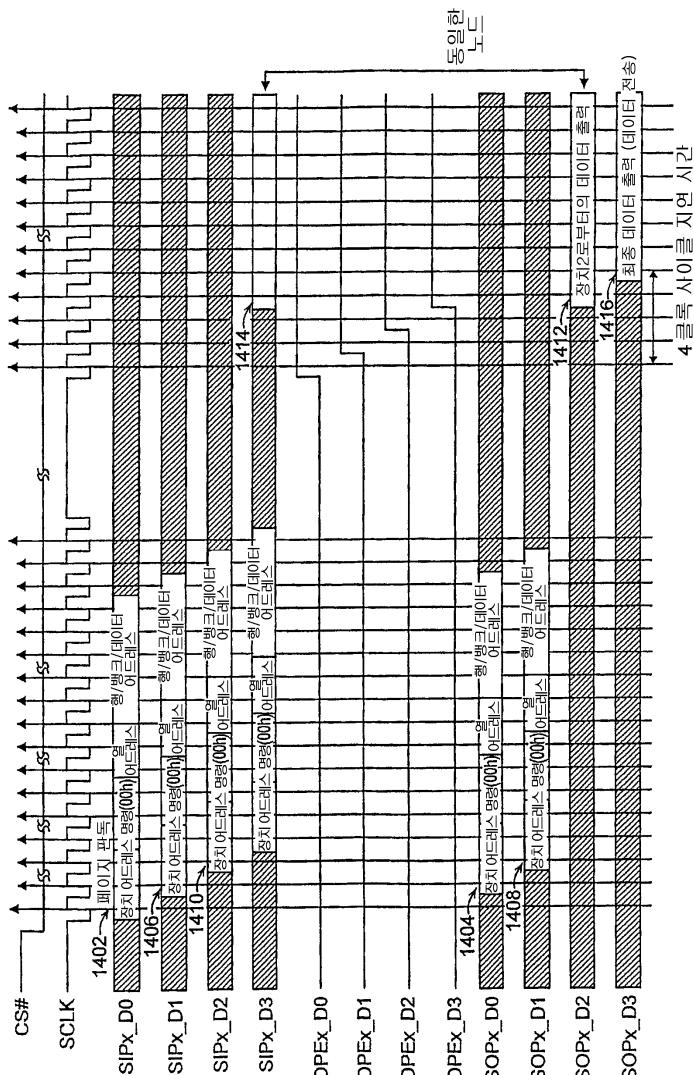

도 14는 본 발명의 양상에 따른 캐스케이딩된 구성에서 메모리 장치상에서 실행된 메모리 동작에 대한 간략화된 타이밍 도이다.

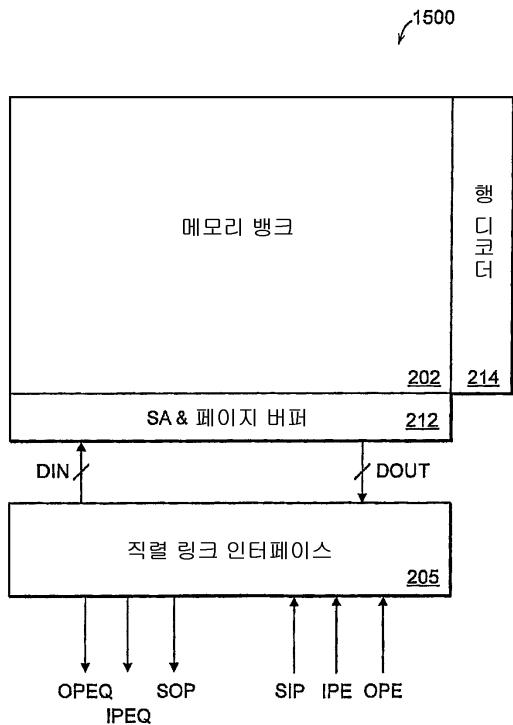

도 15a는 본 발명의 양상에 따른 예시적인 메모리 장치의 높은 수준의 블록도이다.

도 15b는 도 15a에 예시된 메모리 장치에서 사용될 수 있는 직렬 링크 인터페이스의 더욱 상세한 블록도이다.

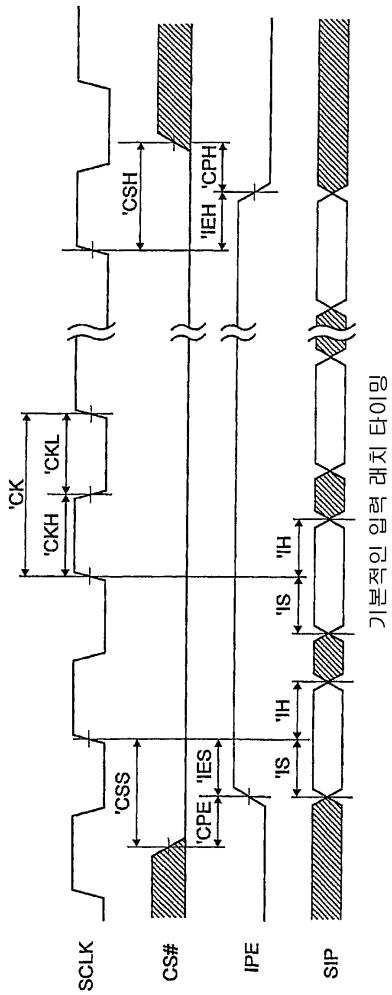

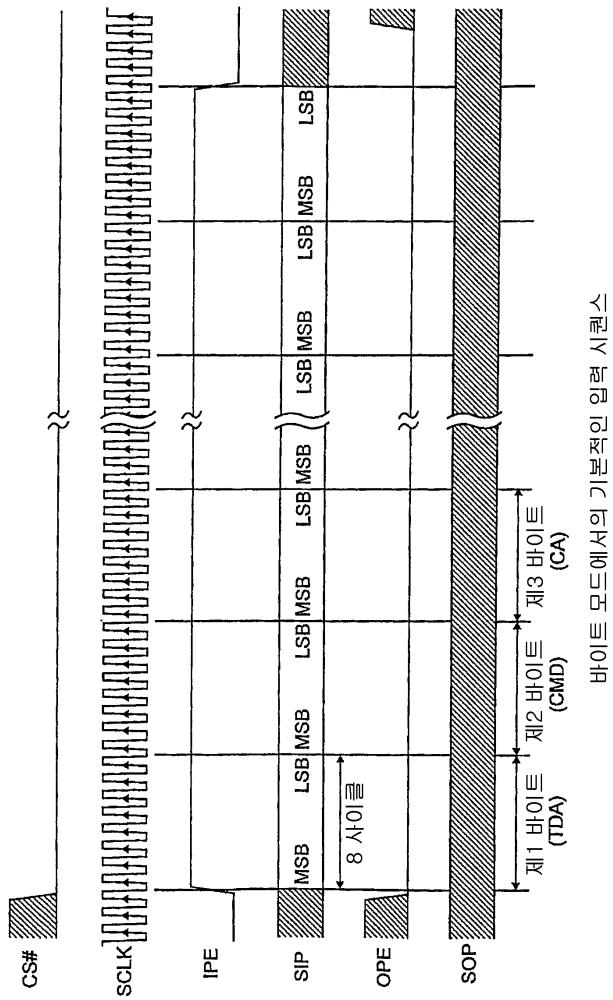

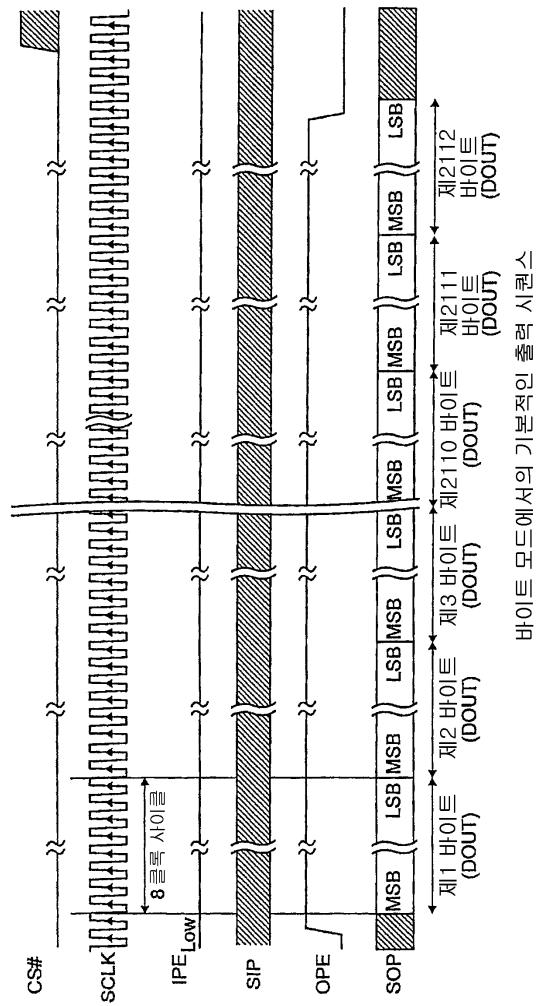

도 16a 및 도 16b는 입력 래치 타이밍 및 입력 시퀀스 타이밍 바이트 모드 각각에 대한 타이밍 도이다.

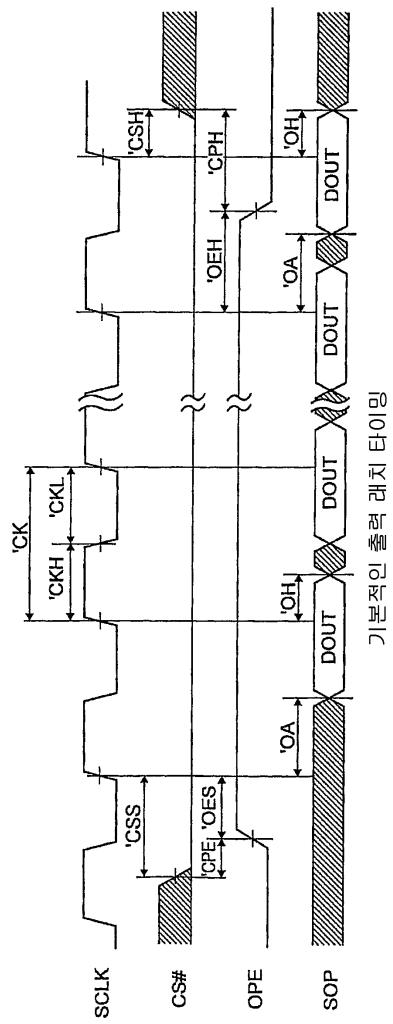

도 17a 및 도 17b는 출력 래치 타이밍 및 출력 시퀀스 타이밍 바이트 모드 각각에 대한 타이밍 도이다.

### 발명을 실시하기 위한 구체적인 내용

[0015] 반도체 메모리에 대한 직렬 데이터 인터페이스가 개시된다. 직렬 데이터 인터페이스는 중앙 제어 로직과 통신하는 하나 이상의 직렬 데이터 링크를 포함할 수 있으며, 여기서 각 직렬 데이터 링크는 명령 및 데이터를 직렬로 수신할 수 있고, 출력 데이터를 직렬로 제공할 수 있다. 각 직렬 데이터 링크는 데이터를 프로그래밍 및 판독하

기 위해 메모리 내의 임의의 메모리 뱅크에 액세스할 수 있다. 직렬 인터페이스의 적어도 한 가지 장점은 밀도마다 동일한 표준 핀-아웃(pin-out)을 갖고, 그에 따라 기판 재설계 없이도 더 높은 밀도로의 양립 가능한 장래의 업그레이드를 가능하게 하는 낮은-핀-계수(low-pin-count) 장치이다.

[0016] 도 1a 및 도 1b는 본 발명의 여러 양상에 따른 동시 동작을 지원하는 예시적인 메모리 장치를 도시한 높은 수준의 도면이다. 도 1a는 복수의 직렬 데이터 링크 인터페이스(102 및 104)와 복수의 메모리 뱅크(106 및 108)를 갖는 메모리 장치를 도시한다. 현재 도시한 배치를 본 명세서에서 이중 포트 구성이라고 지칭한다. 각 직렬 데이터 링크 인터페이스는 도 2a와 관련하여 더 상세하게 후술될 관련 입/출력 핀 및 데이터 입력 및 데이터 출력 회로를 갖는다. 직렬 데이터 링크 인터페이스를 통해 전송된 데이터는 직렬 방식(예컨대 단일-비트-폭 데이터스 트림)으로 통과한다. 메모리 장치 내의 데이터 링크 인터페이스(102 및 104) 각각은 독립적이며, 데이터를 임의의 메모리 뱅크(106 및 108) 내외부로 전송할 수 있다. 예컨대 직렬 데이터 링크(102)는 데이터를 메모리 뱅크(106)나 메모리 뱅크(108) 내외부로 전송할 수 있다. 유사하게, 직렬 데이터 링크(104)는 데이터를 메모리 뱅크(106) 및 메모리 뱅크(108) 내외부로 전송할 수 있다. 도시된 두 개의 직렬 데이터 링크 인터페이스는 독립적이므로, 이들은 데이터를 분리된 메모리 뱅크 내외부로 동시에 전송할 수 있다. 링크는, 본 명세서에 사용된 바와 같이 하나 이상의 메모리 뱅크 내외부로의 데이터 전송 경로를 제공하고, 그러한 데이터 전송을 제어하는 회로를 지칭한다. 제어 모듈(110)은 각 직렬 데이터 링크 인터페이스(102 및 104)와 각 메모리 뱅크(106 및 108) 사이의 데이터 교환을 제어하기 위한 명령으로 구성 가능하다. 예컨대, 제어 모듈(110)은 직렬 데이터 링크 인터페이스(104)가 데이터를 메모리 뱅크(108)에 기록하는 동시에 직렬 데이터 링크 인터페이스(102)가 데이터를 메모리 뱅크(106)로부터 판독할 수 있도록 구성될 수 있다. 이러한 특성은 시스템 설계에 대한 향상된 융통성과 향상된 장치 이용(예컨대, 버스 이용 및 코어 이용)을 제공한다. 후에 도시될 바와 같이, 제어 모듈(110)은 제어 회로, 레지스터 및 스위치 회로를 포함할 수 있다.

[0017] 도 1b는 단일 직렬 데이터 링크 인터페이스(120)가 제어 모듈(126)을 통해 복수의 메모리 뱅크(122 및 124)에 링크된 실시예를 도시한다. 현재 도시된 이러한 배치를 본 명세서에서는 단일 포트 구성이라고 지칭하며, 이러한 배치는 도 1a에 도시된 이중 포트 구성보다 더 적은 메모리 장치 입/출력 핀을 사용한다. 제어 모듈(126)은 두 개의 동작 프로세스나 스레드(thread)를 실행하거나 수행하도록 구성되어, 직렬 데이터 링크 인터페이스(120)는 파이프라인 방식(pipelined fashion)으로 데이터를 메모리 뱅크(122 및 124)와 교환할 수 있다. 예컨대 데이터가 메모리 뱅크(122)내에 기록되고 있는 동안에, 데이터 링크 인터페이스(120)는 메모리 뱅크(124)로부터 데이터를 판독하고 있을 수 있다. 본 발명의 여러 양상에 따라 및 더 상세하게 후술될 바와 같이, 메모리 장치는 도 1b에 예시된 단일 링크 구성을 사용하여 복수의 링크 동작을 에뮬레이트(emulate)한다. 복수의 뱅크 구성과 연계하여, 본 명세서에서 또한 가상의 복수의 링크라고도 지칭되는 이러한 단일 링크를 사용하면, 다른 뱅크가 사용중 상태에 있을 수 있는 동안에, 임의의 이용 가능한 뱅크에 액세스할 수 있다. 그 결과, 메모리 장치는 링크 중재 회로(link arbitration circuitry)를 거쳐 다른 이용 가능한 뱅크에 액세스함으로써 단일 링크 구성을 더 잘 이용할 수 있다.

[0018] 도 1a 및 도 1b에 도시된 메모리 장치는 단지 예시할 목적으로 두 개의 메모리 뱅크를 포함한다. 당업자는 본 명세서에서 개시된 본 발명의 여러 양상이 확장성이 있고, 복수의 메모리 뱅크 및 복수의 직렬 데이터 링크 인터페이스를 이용할 수 있게 한다는 점을 인식할 것이다. 단일 메모리 장치는 예컨대 2, 4, 또는 그 이상의 메모리 뱅크를 포함할 수 있다. 도 1c는 네 개의 독립적인 직렬 데이터 링크(132, 134, 136 및 138)가 제어 모듈(150)의 제어 하에서 네 개의 메모리 뱅크(140, 142, 144 및 146)와 데이터를 교환하도록 구성된 실시예를 도시한다. 가상의 복수의 링크 구성을 사용하면, 단 하나의 링크만 필요하며, 따라서 나머지 링크(예컨대, 도 1a의 이중 링크나 도 1c의 4중 링크 핀아웃 구성에서)는 사용되지 않으며, NC(No Connection: 연결 안 됨)로 간주될 수 있다. 종래의 병렬 인터페이스 구조에 비해 직렬 데이터 링크 인터페이스의 적어도 한 가지 장점은, 링크 융통성과 큰 밀도를 유지하면서도 메모리 장치상에서 핀의 개수가 감소한다는 점이다. 예컨대, 종래의 플래시 메모리 장치는 패키지의 복수의 측에 걸쳐서 48개의 핀을 필요로 할 수 있지만, 본 발명의 양상에 따른 메모리 장치는 도 11에 예시된 바와 같이 표준 패키지(1100)의 단일 측 상에서 더 소수의 핀(예컨대 11개의 핀)을 사용할 수 있다. 대안적으로, 필요한 내부 접착 패드의 수가 더 적기 때문에, 다른 더 작은 타입의 패키지가 대신 사용될 수 있다.

[0019] 도 2a는 본 발명의 일실시예에 따른 도 1a에 도시된 메모리 장치의 더욱 상세한 개략도를 예시한다. 메모리 장치(200)의 각 메모리 뱅크의 구조는 NAND 플래시 메모리 코어 구조와 같거나 유사할 수 도 있다. 도 2a는 본 발명에 관련된 이들 회로를 예시하며, 도 2a를 간략화하기 위해 특정한 회로 블록을 의도적으로 생략한다. 예컨대 플래시 메모리 코어 구조로 구현된 메모리 장치(200)는 메모리 셀을 프로그래밍하고 소거하는데 필요한 고전압

생성기 회로를 포함할 것이다. 코어 구조(또는 코어 회로)는, 본 명세서에서 사용된 바와 같이 디코딩 및 데이터 전송 회로와 같은 메모리 셀 어레이 및 관련 액세스 회로를 포함하는 회로를 지칭한다. 표준 메모리 구조가 잘 알려져 있으므로, 선택된 구조와 관련된 고유한 동작도 잘 알려져 있으며, 이점은 당업자에 의해 이해되어야 한다. 임의의 알려진 비휘발성 또는 휘발성 메모리 구조가 본 발명의 대안적인 실시예에서 사용될 수 있음이 당업자에 의해 또한 이해되어야 한다.

- [0020] 메모리 장치(200)는 메모리 뱅크 A(202) 및 메모리 뱅크 B(204)와, 메모리 뱅크(202 및 204) 양자에 연결된 어드레스 및 제어 경로 스위치 회로(206)와, 각 메모리 뱅크와 관련되며 데이터를 스위치 회로(206)에 제공하고, 데이터를 스위치 회로(206)로부터 수신하기 위한 동일한 인터페이스 회로(205 및 207)와 같이 그 각자의 데이터, 제어 및 어드레싱 회로를 구비한 복수의 동일한 메모리 뱅크를 포함한다. 메모리 뱅크(202 및 204)는 바람직하게는 예컨대 플래시 메모리와 같은 비휘발성 메모리이다. 논리적으로, 메모리 뱅크(202)에 의해 수신되고 제공된 신호는 문자 "A"로 표시되는 반면, 메모리 뱅크(204)에 의해 수신되고 제공된 신호는 문자 "B"로 표시된다. 유사하게, 인터페이스 회로(205)에 의해 수신되고 제공된 신호는 숫자 "0"으로 표시되는 반면, 인터페이스 회로(207)에 의해 수신되고 제공된 신호는 숫자 "1"로 표시된다. 각 인터페이스 회로(205/207)는 액세스 데이터를 직렬 데이터스트림으로 수신하며, 여기서 액세스 데이터는 예컨대 동작을 프로그래밍하기 위한 명령, 어드레스 정보 및 입력 데이터를 포함할 수 있다. 판독 동작에서, 인터페이스 회로는 판독 명령 및 어드레스 데이터에 응답하여, 출력 데이터를 직렬 데이터스트림으로서 제공할 것이다. 메모리 장치(200)는 클록 신호(sclk) 및 reset)와 같은 글로벌 신호를 메모리 뱅크(202 및 204) 양자의 회로와 각 인터페이스 회로(205 및 207)에 제공하는 제어 인터페이스(208)와 상태/ID 레지스터 회로(210)와 같은 글로벌 회로를 더 포함한다. 이제, 전술한 회로에 대해 다음에서 추가로 논의할 것이다.

- [0021] 메모리 뱅크(202)는, 출력 데이터(DOUT\_A)를 제공하며, 입력 프로그램 데이터(DIN\_A)를 수신하기 위한 감지 증폭기 및 페이지 버퍼 회로 블록(212)과 행 디코더 블록(214)과 같은 잘 알려진 메모리 주변 회로를 포함한다. 당업자는 블록(212)이 또한 열 디코더 회로를 포함할 것임을 이해할 것이다. 제어 및 프리디코더 회로 블록(216)은 어드레스 신호 및 제어 신호를 신호 라인(ADDR\_A)을 통해 수신하며, 프리디코딩된 어드레스 신호를 행 디코더(214)와 감지 증폭기 및 페이지 버퍼 회로 블록(212)에 제공한다.

- [0022] 메모리 뱅크(204)에 대한 주변 회로는 메모리 뱅크(202)에 대해 이전에 기재한 것과 동일하다. 메모리 뱅크 B의 회로는 출력 데이터(DOUT\_B)를 제공하고, 입력 프로그램 데이터(DIN\_B)를 수신하기 위한 감지 증폭기 및 페이지 버퍼 회로 블록(218)과, 행 디코더 블록(220)과, 제어 및 프리디코더 회로 블록(222)을 포함한다. 제어 및 프리디코더 회로 블록(222)은 어드레스 신호 및 제어 신호를 신호 라인(ADDR\_B)을 통해 수신하고, 프리디코딩된 어드레스 신호를 행 디코더(220)와 감지 증폭기 및 페이지 버퍼 회로 블록(222)에 제공한다. 각 메모리 뱅크 및 그 대응하는 주변 회로는 잘 알려진 구조로 구성될 수 있다.

- [0023] 일반적인 동작에서, 각 메모리 뱅크는 특정한 명령 및 어드레스와 필요한 경우 입력 데이터에 응답한다. 예컨대 메모리 뱅크(202)는 판독 명령 및 판독 어드레스에 응답하여 출력 데이터(DOUT\_A)를 제공할 것이며, 프로그램 명령 및 프로그램 어드레스에 응답하여 입력 데이터를 프로그래밍할 수 있다. 각 메모리 뱅크는 예컨대 소거 명령과 같은 다른 명령에 응답할 수 있다.

- [0024] 현재 도시된 실시예에서, 경로 스위치(206)는 메모리 뱅크(202 및 204)와 인터페이스 회로(205 및 207) 사이에서 신호를 통과시키기 위해 두 모드 중 하나로 동작할 수 있는 이중 포트 회로이다. 제 1 모드는 메모리 뱅크(202) 및 인터페이스 회로(205)의 신호가 서로에게 전달되는 직접 전송 모드이다. 동시에, 메모리 뱅크(204) 및 인터페이스 회로(207)의 신호는 직접 전송 모드로 서로에게 전달된다. 제 2 모드는 메모리 뱅크(202) 및 인터페이스 회로(207)의 신호가 서로에게 전달되는 교차-전송 모드이다. 동시에, 메모리 뱅크(204)와 인터페이스 회로(205)의 신호가 서로에게 전달된다. 경로 스위치(206)의 단일 포트 구성이 후술될 것이다.

- [0025] 전술된 바와 같이, 인터페이스 회로(205 및 207)는 데이터를 직렬 데이터스트림으로서 수신하고 제공한다. 이는 칩의 핀-아웃 요구량을 감소시키기 위한 것일 뿐만 아니라 높은 동작 주파수에서 전체 신호 처리량을 증가시키기 위한 것이다. 메모리 뱅크(202 및 204)의 회로는 통상 병렬 어드레스 및 데이터용으로 구성되므로, 변환 회로가 필요하다.

- [0026] 인터페이스 회로(205)는 직렬 데이터 링크(230), 입력 직-병렬 레지스터 블록(232), 및 출력 병-직렬 레지스터 블록(234)을 포함한다. 직렬 데이터 링크(230)는 직렬 입력 데이터(SIPO), 입력 인에이블 신호(IPE0) 및 출력 인에이블 신호(OPE0)를 수신하고, 직렬 출력 데이터(SOPO), 입력 인에이블 반향(echo) 신호(IPEQ0) 및 출력 인에이블 반향 신호(OPEQ0)를 제공한다. 신호(SIPO)(및 SIP1)는 어드레스, 명령 및 입력 데이터를 각각 포함할 수

있는 직렬 데이터스트림이다. 직렬 데이터 링크(230)는 SIP0에 대응하는 버퍼링된 직렬 입력 데이터(SER\_IN0)를 제공하며, 직렬 출력 데이터(SER\_OUT0)를 출력 병-직렬 레지스터 블록(234)으로부터 수신한다. 입력 직-병렬 레지스터 블록(232)은 SER\_IN0를 수신하고, 이를 신호의 병렬 세트(PAR\_IN0)로 변환한다. 출력 병-직렬 레지스터 블록(234)은 출력 데이터(PAR\_OUT0)의 병렬 세트를 수신하여, 이를 직렬 출력 데이터(SER\_OUT0)로 변환하며, 이것은 후속해서 데이터스트림(SOP0)으로서 제공된다. 출력 병-직렬 레지스터 블록(234)은 PAR\_OUT0 데이터 대신 그 내부에 저장된 데이터를 출력하기 위해 상태/ID 레지스터 회로(210)로부터 데이터를 또한 수신할 수 있다. 이 특정한 특성의 더 상세한 내용은 후술될 것이다. 더나아가, 직렬 데이터 링크(230)는 다른 메모리 장치(200)와의 제어 신호 및 데이터 신호의 데이터 채인 캐스케이딩을 수용하도록 구성된다.

[0027] 직렬 인터페이스 회로(207)는 인터페이스 회로(205)와 동일하게 구성되며, 직렬 데이터 링크(236), 입력 직-병렬 레지스터 블록(240) 및 출력 병-직렬 레지스터 블록(238)을 포함한다. 직렬 데이터 링크(236)는 직렬 입력 데이터(SIP1), 입력 인에이블 신호(IPE1) 및 출력 인에이블 신호(OPE1)를 수신하며, 직렬 출력 데이터(SOP1), 입력 인에이블 반향(echo) 신호(IPEQ1) 및 출력 인에이블 반향 신호(OPEQ1)를 제공한다. 직렬 데이터 링크(236)는 SIP1에 대응하는, 버퍼링된 직렬 입력 데이터(SER\_IN1)를 제공하며, 출력 병-직렬 레지스터 블록(238)으로부터 직렬 출력 데이터(SER\_OUT1)를 수신한다. 입력 직-병렬 레지스터 블록(238)은 SER\_IN1을 수신하고, 이를 신호의 병렬 세트(PAR\_IN1)로 변환한다. 출력 병-직렬 레지스터 블록(240)은 출력 데이터의 병렬 세트(PAR\_OUT1)를 수신하며, 이를 직렬 출력 데이터(SER\_OUT1)로 변환하며, 이러한 데이터(SER\_OUT1)는 후속해서 데이터스트림(SOP1)으로서 제공된다. 출력 병-직렬 레지스터 블록(240)은 또한 PAR\_OUT1 데이터 대신에 그 내부에 저장된 데이터를 출력하기 위해 상태/ID 레지스터 회로(210)로부터 데이터를 수신할 수 있다. 직렬 데이터 링크(230)에서와 같이, 직렬 데이터 링크(236)는 다른 메모리 장치(200)와의 제어 신호 및 데이터 신호의 데이터 채인 캐스케이딩을 수용하도록 구성된다.

[0028] 제어 인터페이스(208)는 표준 입력 버퍼 회로를 포함하며, 각각 CS#, SCLK 및 RST#에 대응하는 내부 칩 선택 신호(chip\_sel), 내부 클록 신호(sclki) 및 내부 리셋 신호(reset)를 생성한다. 신호(chip\_sel)가 주로 직렬 데이터 링크(230 및 236)에 의해 사용되는 반면, reset 및 sclki는 메모리 장치(200)를 통해 다수의 회로에 의해 사용된다.

[0029] 도 2b는 본 발명의 실시예에 따른 직렬 데이터 링크(230)의 개략도이다. 직렬 데이터 링크(230)는 입력 신호(OPE0, IPE0 및 SIP0)를 수신하기 위한 입력 버퍼(242), 신호(SOP0, IPEQ0 및 OPEQ0)를 구동하기 위한 출력 구동기(244), 신호(out\_en0 및 in\_en0)를 클록 아웃하기 위한(clocking out) 플립-플롭 회로(246), 인버터(248) 및 멀티플렉서(MUX)(250)를 포함한다. 신호(OPE0 및 SIP0)에 대한 입력 버퍼는 chip\_sel에 응답하여 인에이블되며, 신호(SOP0)에 대한 출력 구동기는 인버터(248)를 통해 반전된 chip\_sel에 응답하여 인에이블된다. 신호(out\_en0)는 도 2e에서 추후에 도시될 출력 버퍼를 인에이블하며, 신호(SER\_OUT0)를 제공한다. 신호(in\_en0)는 SER\_IN0 데이터, 신호(in\_en0, out\_en0 및 SER\_IN0)를 래치하기 위해 입력 직-병렬 레지스터 블록(232)을 인에이블한다.

[0030] 직렬 데이터 링크(230)는 메모리 장치(200)를 다른 메모리 장치와 데이터 채인 캐스케이딩 할 수 있게 하는 회로를 포함한다. 더욱 상세하게는, 직렬 입력 데이터 스트림(SIP0), 및 인에이블 신호(OPE0 및 IPE0)는 직렬 데이터 링크(230)를 거쳐 다른 메모리 장치의 대응하는 편에 전달될 수 있다. SER\_IN0는 AND 논리 게이트(252)에 의해 수신되고, in\_en0가 활성 고 논리 레벨(active high logic level)에 있을 때 그 대응하는 플립-플롭(246)에 전달된다. 동시에 활성 고 논리 레벨의 in\_en0은 Si\_next0을 출력 구동기(244)에 전달하도록 MUX(250)를 제어할 것이다. 유사하게 IPE0 및 OPE0은 각각의 플립-플롭(246)을 거쳐 IPEQ0 및 OPEQ0에 클록 아웃될 수 있다. 직렬 데이터 링크(230)를 기술하였지만, 직렬 데이터 링크(236)는 도 2b에서 직렬 데이터 링크(230)에 대해 도시된 바와 동일하게 상호 연결되는 동일한 소자를 포함한다.

[0031] 도 2c는 입력 직-병렬 레지스터 블록(232)의 개략도이다. 이 블록은 클록 신호(sclki), 인에이블 신호(in\_en0) 및 입력 데이터스트림(SER\_IN0)을 수신하며, SER\_IN0을 데이터의 병렬 그룹으로 변환한다. 특히 SER\_IN0는 명령(CMD\_0), 열 어드레스(C\_ADD0), 행 어드레스(R\_ADD0) 및 입력 데이터(DATA\_IN0)를 제공하도록 변환될 수 있다. 본 발명의 현재 개시한 실시예는 바람직하게는 예컨대 200MHz와 같은 고주파수에서 동작한다. 이 속도에서 직렬 입력 데이터스트림은 수신된 명령이 디코딩될 수 있는 것보다 더 빠른 속도로 수신될 수 있다. 직렬 입력 데이터스트림이 레지스터 세트에서 초기에 버퍼링되는 것이 바로 이 때문이다. 현재 도시한 개략도는 또한 입력 직-병렬 레지스터 블록(240)에도 적용되며, 여기서 유일한 차이점은 신호 지시어의 명칭이다.

[0032] 입력 직-병렬 레지스터 블록(232)은 in\_en0 및 sclki를 수신하기 위한 입력 제어기(254), 명령 레지스터(256),

임시 레지스터(258) 및 직렬 데이터 레지스터(260)를 포함한다. 직렬 입력 데이터스트림의 데이터 구조가 미리 결정되므로, 입력 데이터스트림의 특정한 수의 비트가 앞서 언급한 레지스터에 분배될 수 있다. 예컨대 명령에 대응하는 비트가 명령 레지스터(256)에 저장될 수 있고, 행 및 열 어드레스에 대응하는 비트가 임시 레지스터(258)에 저장될 수 있으며, 입력 데이터에 대응하는 비트가 직렬 데이터 레지스터(260)에 저장될 수 있다. 직렬 입력 데이터스트림의 비트 분배는 입력 제어기(254)에 의해 제어될 수 있고, 이 제어기(254)는 각 미리 결정된 수의 비트가 수신된 이후 제어 신호를 인에이블하는 적절한 레지스터를 생성하기 위한 카운터를 포함한다. 다시 말해, 세 개의 레지스터 각각은 직렬 입력 데이터스트림의 미리 결정된 데이터 구조에 따라 직렬 입력 데이터스트림의 데이터 비트를 수신하고 저장하도록 순차적으로 인에이블될 수 있다.

[0033] 명령 번역기(262)는 명령 레지스터(256)로부터 명령 신호를 병렬로 수신하며, 디코딩된 명령(CMD\_0)을 생성한다. 명령 번역기(262)는 수신된 명령을 디코딩하기 위해 상호연결된 논리 게이트 또는 펌웨어로 구현된 표준 회로이다. 도 4에 도시된 바와 같이, CMD\_0는 신호(cmd\_status 및 cmd\_id)를 포함할 수 있다. 스위치 제어기(264)는 간단한 스위치 회로(266)를 제어하기 위해 CMD\_0으로부터 하나 이상의 신호를 수신한다. 스위치 회로(266)는 임시 레지스터(258)에 저장된 모든 데이터를 병렬로 수신하며, 디코딩된 명령(CMD\_0)에 따라 열 어드레스 레지스터(268) 및 행/뱅크 레지스터(270) 중 하나 또는 양자에 데이터를 로딩한다. 이러한 디코딩은, 임시 레지스터가 열 및 행/뱅크 어드레스 데이터 양자를 항상 포함할 수는 없기 때문에 바람직하게 수행된다. 예컨대 블록 소거 명령을 가진 직렬 입력 데이터스트림이 행 어드레스만을 사용할 것이며, 그러한 경우 임시 레지스터(258)에 저장된 관련 비트만이 행/뱅크 레지스터(270)에 로딩된다. 열 어드레스 레지스터(268)는 병렬 신호(C\_ADD0)를 제공하며, 행/뱅크 어드레스 레지스터(270)는 병렬 신호(R\_ADD0)를 제공하며, 데이터 레지스터(272)는 동작을 프로그래밍하기 위해 병렬 신호(DATA\_IN0)를 제공한다. 집합적으로 CMD\_0, C\_ADD0, R\_ADD0 및 Data\_IN0(옵션)는 병렬 신호(PAR\_IN0)를 형성한다. 병렬 신호 각각의 비트 폭은 특정되어 있지 않으며, 이는 원하는 폭이 특정한 표준을 지키도록 주문제작 또는 맞춰질 수 있는 설계 파라미터이기 때문이다.

[0034] 플래시 코어 구조 구현을 위한 메모리 장치(200)의 일부 동작의 예가 아래 표 1에 기재되어 있다. 표 1은 CMD\_0에 대한 가능한 OP(동작) 코드와, 열 어드레스(C\_ADD0), 행/뱅크 어드레스(R\_ADD0) 및 입력 데이터(DATA\_IN0)의 대응하는 상태를 나열한다.

표 1

| 동작                       | OP 코드<br>(1바이트) | 열 어드레스<br>(2바이트) | 행/뱅크 어드레스<br>(3바이트) | 입력 데이터<br>(1바이트에서 2112<br>바이트까지) |

|--------------------------|-----------------|------------------|---------------------|----------------------------------|

| 페이지 판독                   | 00h             | 유효               | 유효                  | -                                |

| 랜덤 데이터 판독                | 05h             | 유효               | -                   | -                                |

| 복사를 위한 페이지<br>판독         | 35h             | -                | 유효                  | -                                |

| 복사를 위한 타겟 어<br>드레스 입력    | 8Fh             | -                | 유효                  | -                                |

| 직렬 데이터 입력                | 80h             | 유효               | 유효                  | 유효                               |

| 랜덤 데이터 입력                | 85h             | 유효               | -                   | 유효                               |

| 페이지 프로그램                 | 10h             | -                | -                   | -                                |

| 블록 소거                    | 60h             | -                | 유효                  | -                                |

| 판독 상태                    | 70h             | -                | -                   | -                                |

| 판독 ID                    | 90h             | -                | -                   | -                                |

| 기록 구성 레지스터               | A0h             | -                | -                   | 유효(1바이트)                         |

| 기록 DN(Device<br>Name) 기입 | B0h             | -                | -                   | -                                |

| 리셋                       | FFh             | -                | -                   | -                                |

| 뱅크 선택                    | 20h             | -                | 유효(뱅크)              | -                                |

[0036] 표 1: 명령 세트

[0037] 더나아가 표 2는 입력 데이터스트림의 바람직한 입력 시퀀스를 기재한다. 명령, 어드레스 및 데이터는 최상위 비트로부터 시작해서 메모리 장치(200)의 내외부로 직렬로 시프트된다. 명령 시퀀스는 1-바이트 명령 코드(표 2의 "cmd")로 시작한다. 명령에 따라, 1-바이트 명령 코드 다음에는 열 어드레스 바이트(표 2의 "ca"), 행 어드레스 바이트(표 2의 "ra"), 뱅크 어드레스 바이트(표 2의 "ba"), 데이터 바이트(표 2의 "data") 및/또는 이들의

조합이 따르거나 어떤 것도 따르지 않는다.

표 2

| [0038] | 동작                       | 1 <sup>st</sup><br>바이트 | 2 <sup>nd</sup><br>바이<br>트 | 3 <sup>rd</sup><br>바이<br>트 | 4 <sup>th</sup><br>바이<br>트 | 5 <sup>th</sup><br>바이<br>트 | 6 <sup>th</sup><br>바이<br>트 | 7 <sup>th</sup><br>바이<br>트 | .. | 2115 <sup>th</sup><br>바이트 | .. | 2118 <sup>th</sup><br>바이트 |

|--------|--------------------------|------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----|---------------------------|----|---------------------------|

|        | 페이지 판독                   | cmd                    | ca                         | ca                         | ba/ra                      | ra                         | ra                         | -                          | -  | -                         | -  | -                         |

|        | 랜덤 테이터<br>판독             | cmd                    | ca                         | ca                         | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

|        | 복사를 위한<br>페이지 판독         | cmd                    | ba/ra                      | ra                         | ra                         | -                          | -                          | -                          | -  | -                         | -  | -                         |

|        | 복사를 위한<br>타겟 어드레<br>스 입력 | cmd                    | ba/ra                      | ra                         | ra                         | -                          | -                          | -                          | -  | -                         | -  | -                         |

|        | 직렬 테이터<br>입력             | cmd                    | ca                         | ca                         | ba/ra                      | ra                         | ra                         | data                       | -  | data                      | -  | data                      |

|        | 랜덤 테이터<br>입력             | cmd                    | ca                         | ca                         | data                       | data                       | data                       | data                       | -  | data                      | -  | -                         |

|        | 페이지 프로<br>그램             | cmd                    | -                          | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

|        | 블록 소거                    | cmd                    | ba/ra                      | ra                         | ra                         | -                          | -                          | -                          | -  | -                         | -  | -                         |

|        | 판독 상태                    | cmd                    | -                          | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

|        | 판독 ID                    | cmd                    | -                          | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

|        | 기록 구성 레<br>지스터           | cmd                    | data                       | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

|        | 기록 DN<br>기입              | cmd                    | -                          | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

|        | 리셋                       | cmd                    | -                          | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

|        | 뱅크 선택                    | cmd                    | ba                         | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

[0039] 표 2: 바이트 모드에서의 입력 시퀀스

[0040] 도 2d는 도 2a에 도시된 경로 스위치(206)의 개략도이다. 스위치(206)는 동일하게 구성된 두 개의 스위치 부-회로(274 및 276)로 논리적으로 분리된다. 스위치 부-회로(274)는 인터페이스 회로(205)나 인터페이스 회로(207) 중 어느 하나의 명령, 어드레스 및 입력 데이터를 메모리 뱅크(202)의 회로에 선택적으로 전달하는 네 개의 입력 멀티플렉서(278)를 포함한다. 이들 신호는 예컨대 PAR\_IN0로서 앞서 도 2c에서 그룹화되었다. 스위치 부-회로(274)는 메모리 뱅크(202)나 메모리 뱅크(204) 중 어느 하나로부터 출력 데이터를 인터페이스 회로(205)에 선택적으로 전달하기 위해 하나의 출력 멀티플렉서(280)를 포함한다. 스위치 부-회로(276)는 인터페이스 회로(205)나 인터페이스 회로(207) 중 어느 하나의 명령, 어드레스 및 입력 데이터를 메모리 뱅크(204) 회로에 선택적으로 전달하는 네 개의 입력 멀티플렉서(미도시됨)를 포함한다. 스위치 부-회로(276)는 메모리 뱅크(202)나 메모리 뱅크(204) 중 어느 하나로부터 출력 데이터를 인터페이스 회로(207)에 선택적으로 전달하기 위해 하나의 출력 멀티플렉서(미도시됨)를 포함한다.

[0041] 스위치 부-회로(274 및 276) 양자는 스위치 제어 신호(SW\_CONT)의 상태에 따라 직접 전송 모드나 교차-전송 모드로 동시에 동작할 수 있다. 경로 스위치 회로(206)는 현재 이중 포트 구성으로 도시되며, 이것은 메모리 뱅크(202 및 204) 양자가 인터페이스 회로(205 및 207) 중 어느 하나를 거쳐서 동시에 액세스될 수 있음을 의미한다.

[0042] 본 발명의 다른 실시예에 따라 도 1b에 앞서 예시된 바와 같이, 경로 스위치(206)는 인터페이스 회로(205 및 207) 중 단 하나만 활성 상태인 단일 포트 모드로 동작할 수 있다. 사용되지 않은 인터페이스 회로와 관련된 입/출력 패드가 더 이상 필요하지 않으므로, 이 구성은 메모리 장치(200)의 핀-아웃 영역 요건을 더 감소시킬 수 있다. 단일 포트 구성에서, 스위치 부-회로(274 및 276)는 SW\_CONT 선택 신호에 응답하여 남아 있을 수 있는 각 출력 멀티플렉서(280)를 제외하고는 직접 전송 모드로만 동작하도록 설정된다.

[0043] 인터페이스 회로(205)만이 활성 상태인 단일 포트 실시예에서, 추가 경로 스위치(미도시됨)가 스위치(266) 및 직렬 데이터 레지스터(260)의 출력으로부터 입력 직-병렬 레지스터 블록(232 또는 240) 중 어느 하나의 대응하는 열, 행/뱅크 및 데이터 레지스터에 데이터를 선택적으로 전달하기 위해 입력 병-직렬 레지스터 블록(232)(또

는 블록(234))에 포함된다. 효과적으로, 이 추가 경로 스위치는 스위치(206)와 유사할 수 있다. 그러므로 입력-직-병렬 레지스터 블록(232 및 240) 양자의 열, 행/뱅크 및 데이터 레지스터에는 교대로 발생하는 메모리 뱅크 액세스나 실질적으로 동시에 액세스하기 위한 데이터가 로딩될 수 있다.

[0044] 도 2e는 출력 병-직렬 레지스터 블록(234)의 개략도이다. 출력 병-직렬 레지스터 블록(238)이 동일하게 구성됨을 주목해야 한다. 출력 병-직렬 레지스터 블록(234)은 메모리 뱅크로부터 액세스된 데이터나 레지스터에 앞서 저장된 상태 데이터 중 어느 하나를 제공한다. 더욱 상세하게, 사용자나 시스템은 직렬 데이터 링크(230 또는 236) 중 어느 하나의 상태를 요청할 수 있다. 출력된 상태 데이터에서 지정된 비트 위치(예컨대 비트 4)의 '1'의 값은 특정한 직렬 데이터 링크 인터페이스가 사용 중임을 지시할 수 있다. 고정된 데이터는 칩 식별 데이터를 더 포함할 수 있으며, 이 식별 데이터는 상태 데이터와 함께 메모리 장치(200)의 전원을 켜면 디폴트 상태로 미리 로딩될 수 있다. 상태 데이터는 시스템에 의해 인식 가능한 미리 선택된 임의의 비트 패턴을 갖도록 구성될 수 있다. 비록 도시되지 않았지만, 도 2e는 하나 이상의 미리 결정된 조건에 기초하여 레지스터(284)에 저장된 하나 이상의 비트를 업데이트하기 위한 추가 제어 회로를 포함할 수 있다. 예컨대, 하나 이상의 상태 비트는 경과한 클록 사이클의 총수를 기초로 해서 또는 메모리 장치(200)의 여러 회로 블록으로부터 수신된 하나 이상의 플래그 신호의 조합을 기초로 해서 변화할 수 있다.

[0045] 출력 병-직렬 레지스터 블록(234)은 경로 스위치(206)로부터 출력 데이터(PAR\_OUT0)를 수신하기 위한 제 1 병-직렬 레지스터(282)와, 멀티플렉서(286)로부터 고정된 데이터를 수신하기 위한 제 2 병-직렬 레지스터(284)를 포함한다. 멀티플렉서(286)는 신호(cmd\_id)에 응답하여 상태 레지스터(288)에 저장된 상태 데이터나 ID 레지스터(290)에 저장된 칩 식별 데이터 중 하나를 선택적으로 전달한다. 출력 멀티플렉서(292)는 cmd\_id나 cmd\_status 중 어느 하나가 활성상태임에 응답하여 OR 게이트(294)를 통해서 제 1 병-직렬 레지스터(282)나 제 2 병-직렬 레지스터(284) 중 어느 하나로부터 데이터를 전달한다. 마지막으로, out\_en0에 의해 인에이블된 직렬 출력 제어 회로(296)는 SER\_OUT0을 제공한다.

[0046] 당업자는 상태 지시자의 크기 및 위치가 본 발명의 여러 양상에 따라 변경될 수 있음을 인식할 것이다. 예컨대, 직렬 데이터 링크 인터페이스 상태 지시자는 다른 타입의 상태 지시자(예컨대, 메모리 뱅크 상태 지시자)와 결합할 수 있고/거나 물리적으로 레지스터 블록 외부에(예컨대 링크 중재 모듈이나 제어 모듈(238)에) 위치할 수 있다. 다른 예에서 직렬 데이터 링크 인터페이스 상태 지시자는 1-비트 레지스터이다.

[0047] 도 15a는 본 발명의 양상에 따른 예시적인 메모리 장치의 높은 수준의 블록도이다. 메모리 장치(1500)에서 메모리 뱅크(202)의 구조는 NAND 플래시 메모리 코어 구조와 동일하거나 이와 유사할 수 있다. 특정한 회로 블록은 도 15a를 간략화하기 위해 생략되었다. 예컨대, 플래시 메모리 코어 구조로 구현된 메모리 장치(1500)는 메모리 셀을 프로그래밍하고 소거하는데 필요한 고전압 생성기 회로를 포함할 것이다. 코어 구조(또는 코어 회로)는, 본 명세서에서 사용되는 경우, 디코딩 및 데이터 전송 회로와 같은 메모리 셀 어레이 및 관련 액세스 회로를 포함하는 회로를 지칭한다. 표준 메모리 구조가 잘 알려져 있으므로, 선택된 구조와 관련된 고유한 동작도 잘 알려져 있으며, 이점은 당업자에게 이해되어야 한다. 임의의 알려진 비휘발성 또는 휘발성 메모리 구조가 본 발명의 대안적인 실시예에서 사용될 수 있음도 또한 당업자에게 이해되어야 한다.

[0048] 메모리 장치(1500)는 메모리 뱅크(202)와, 직렬 입력 데이터를 메모리 뱅크에 전송하는 직렬 데이터 링크 인터페이스(205)를 포함한다. 메모리 뱅크(202)는 출력 데이터(DOUT)를 제공하고 입력 프로그램 데이터(DIN)를 수신하기 위한 감지 증폭기 및 페이지 버퍼 회로 블록(212)과, 행 디코더 블록(214)과 같은 잘 알려져 있는 메모리 주변 회로를 포함한다. 당업자는, 블록(212)이 또한 열 디코더 회로를 포함할 것임을 이해할 것이다. 도 15a에 도시된 바와 같이, 직렬 링크 인터페이스(205)는 직렬 입력 포트(SIP), 직렬 출력 포트(SOP), 입력 인에이블 제어 포트(IPE), 출력 인에이블 제어 포트(OPE), 입력 인에이블 반향(echo) 제어 포트(IPEQ) 및 출력 인에이블 반향 제어 포트(OPEQ)를 포함한다. 당업자는, 직렬 링크 인터페이스(205)가 칩 선택(CS#) 핀, 클록 신호 입력(SCLK), 또는 리셋 선택(RST#) 핀과 같은 다른 장치 포트를 또한 포함할 수 있음을 이해할 것이다.

[0049] 도 15b는 도 15a에 예시된 메모리 장치에서 사용될 수 있는 직렬 링크 인터페이스의 더욱 상세한 블록도이다. 도 2a의 메모리 장치(200)와 유사하게, 인터페이스 회로(205)는 직렬 데이터 링크(230), 입력-직-병렬 레지스터 블록(232) 및 출력 병-직렬 레지스터 블록(234)을 포함한다. 직렬 데이터 링크 인터페이스(230)는 직렬 입력 데이터(SIP), 입력 인에이블 신호(IPE) 및 출력 인에이블 신호(OPE)를 수신하며, 직렬 출력 데이터(SOP), 입력 인에이블 반향 신호(IPEQ) 및 출력 인에이블 반향 신호(OPEQ)를 제공한다. 신호(SIP)는, 어드레스, 명령 및 입력 데이터를 각각 포함할 수 있는 직렬 데이터스트림이다. 직렬 데이터 링크(230)는 SIP에 대응하는, 버퍼링된 직렬 입력 데이터(SER\_in)를 제공하며, 병-직렬 레지스터 블록(234)의 출력으로부터 직렬 출력 데이터(SER\_out)를

수신한다. 직-병렬 레지스터 블록(232)의 입력은 SER\_in을 수신하고, 이를 신호의 병렬 세트(PAR\_in)로 변환한다. 병-직렬 레지스터 블록(234)의 출력은 출력 데이터의 병렬 세트(PAR\_in)를 수신하여, 이를 직렬 출력 데이터(SER\_out)로 변환하며, 변환된 데이터(SER\_out)는 후속해서 데이터스트림(SOP)으로서 제공된다. 더나아가, 입력 인에이블 신호(IPE), 출력 인에이블 신호(OPE), 입력 인에이블 반향 신호(IPEQ) 및 출력 인에이블 반향 신호(OPEQ)는 제어 신호 및 데이터 신호를 다른 메모리 장치(1500)와 데이터-체인 캐스케이딩하도록 직렬 데이터 링크(230)를 구성하는데 사용된다. 제어 모듈(208)은 직렬 데이터 링크 인터페이스와 메모리 뱅크 사이의 데이터 전송을 제어한다.

[0050] 도 3a, 4, 5A, 6A 및 7은 본 발명의 여러 양상에 따라 메모리 장치(200)에 의해 실행된 일부 메모리 동작에 대한 예시적인 타이밍 도를 예시한다. 메모리 장치(200)에 의해 실행된 일부 메모리 명령은 페이지 판독, 랜덤 데이터 판독, 복사를 위한 페이지 판독, 복사를 위한 타겟 어드레스 입력, 직렬 데이터 입력, 랜덤 데이터 입력, 페이지 프로그램, 블록 소거, 판독 상태, 판독 ID, 기록 구성 레지스터, 기록 장치 이름 기입, 리셋 및/또는 뱅크 선택을 포함하며, 이들로 제한되지 않는다. 타이밍 도에 대한 다음의 논의가 앞선 도면에 도시된 메모리 장치(200)의 앞서 기술한 실시예와, 표 1 및 2를 참고하여 이루어질 것이다.

[0051] 도 3a의 타이밍 도에 도시된 예에서, "페이지 판독" 메모리 명령(314)은 본 발명에 따라 메모리 장치(200)의 직렬 데이터 링크(230)에서 수신된다. 게다가, 도 3b는 도 3a의 타이밍 도에서 "페이지 판독" 메모리 명령(314)의 동작에 필적하는 간략화된 흐름도를 도시한다. 실제로, 도 3b에 예시된 단계는 도 3a의 타이밍 도와 연계하여 논의될 것이다. 예컨대, 단계(324)에서, "페이지 판독" 메모리 명령(314)은 메모리 장치(200)의 직렬 데이터 링크(230)에서 판독된다.

[0052] 이 예에서 인입되는 데이터스트림은 (제 1 바이트에서) 명령 데이터, (제 2 및 제 3 바이트에서) 열 어드레스 데이터, 및 (제 4, 제 5 및 제 6 바이트에서) 행 및 뱅크 어드레스 데이터를 포함하는 6-바이트 직렬 데이터스트림(즉, 직렬 입력 데이터)이다. 후술될 바와 같이, 타겟 장치 어드레싱에 있어서, 직렬 데이터스트림은 타겟 장치 어드레스('tda')를 식별케 하며 비트 스트림에서 명령 데이터 앞에 오는 추가적인 바이트를 포함할 수 있다. 뱅크 어드레스는 경로 스위치(206)를 통한 뱅크(202나 204) 중 어느 하나로의 액세스를 판정하는데 사용될 수 있다. 당업자는 서로 다른 메모리 명령이 서로 다른 데이터스트림을 가질 수 있음을 이해할 것이다. 예컨대, "랜덤 데이터 판독" 메모리 명령은 단지 세 바이트의 미리 결정된 데이터스트림: (제 1 바이트에서) 명령 데이터와 (제 2 및 제 3 바이트에서) 열 어드레스 데이터를 갖는다. 후자의 예에서, 직렬 입력 데이터의 어드레스 필드는 열 어드레스 데이터만을 포함하며, 2 바이트 길이를 가졌다. 한편, 전자의 예에서, 어드레스 필드는 5 바이트 길이를 가졌다. 당업자는 여기서 개시한 전체 내용을 살펴본 후 다수의 메모리 명령 및 미리 결정된 데이터스트림이 본 발명의 여러 양상에 따라 분명하다는 점을 인식할 것이다.

[0053] 도 3a에서 예시된 바와 같이 "페이지 판독" 메모리 명령을 수반하는 예를 계속해서 다루면, 칩 선택(CS#) 신호(302)가 낮은 상태로 설정되고 입력 포트 인에이블(IPEX) 신호(306)에 응답하여 높은 상태로 설정되는 동안, 직렬 입력(SIPx) 포트(308)는 직렬 클록(SCLK) 신호(304)의 제 1 상승 에지(the first rising edge) 상에서 샘플링된다(예기서 'x'는 링크 0 인터페이스(232)나 링크 1 인터페이스(234)와 같이 링크 인터페이스 번호를 나타내는 플레이스홀더 placeholder 역할을 한다). (단계(328)에서) 판독된 데이터는 "페이지 판독" 메모리 명령(314)에 대응하는 데이터스트림이다. CS# 신호(302)는 메모리 장치(200)로의 입력이며, 특히 메모리 장치(200)가 활성 상태인지(예컨대 CS#이 낮은 상태일 때)를 지시하는데 사용된다. IPEX 신호(306)는 인입된 데이터스트림이 특정한 링크 인터페이스에서 수신될 것인지(예컨대 IPEX가 높은 상태일 때) 특정한 링크 인터페이스가 인입된 데이터스트림을 무시할 것인지(예컨대 IPEX가 낮은 상태일 때)를 지시한다. 인입된 데이터스트림은 링크 인터페이스의 SIPx(308)에서 메모리 장치에 수신된다. 마지막으로, 시스템 클록(SCLK) 신호(304)는 메모리 장치(200)로의 입력이며, 메모리 장치(200)의 다수의 회로에 의해 실행된 여러 동작을 동기화하는데 사용된다. 본 발명의 여러 양상에 따른 메모리 장치가 그러한 클록 신호와 동기화될 수 있거나(예컨대 동작 및 데이터 전송이 클록 신호의 상승 및/또는 하강 에지에서 발생할 때) 비동기성(즉, 동기성이 아님)일 수 있음이 당업자에게 분명할 것이다. 대안적으로 2배의 전송 속도(DDR: Double Data Rate) 구현시, SCLK 클록 신호의 상승 및 하강 에지 양자는 정보를 래치하는 데 사용될 수 있다. 도 3a의 예에서, 그러나 입력 데이터는 SCLK의 하강 에지 상에서 래치되며 출력 데이터(322)가 SCLK의 상승 에지 이후 직렬 출력 핀(312)(SOPx) 상에 나타난다.

[0054] "페이지 판독"의 상태는 도 3a에 도시된 바와 같이 SOPx 핀(312) 상에서 점검될 수 있어서, "준비" 지시가 나타나는 시간(318)까지 "뱅크 사용중" 결과가 SOPx 상에 제공될 것이며, 출력 데이터가 시간(322) 동안에 곧 나타날 것이다. 비록 도 3a가 "판독 상태"가 후속되는 "페이지 판독"을 예시할지라도, "판독 상태"가 없는 "페이지 판독"도 본 발명의 양상에 따라 생각해 볼 수 있음을 주목해야 한다. 그러한 실시예에서, 출력 데이터가 준비될

때까지 어떠한 데이터도 SOPx 핀 상에 제공되지 않을 것이다.

[0055] SIPx에 의해 샘플링된 명령 데이터가 도 2c에서 적절한 레지스터(예컨대 명령 레지스터(256))에 기록된다. 제 1 바이트가 명령 데이터가 되도록 인입된 데이터스트림을 설계하는 옵션의 적어도 하나의 이점은 데이터가 추가로 처리하지 않고도 명령 레지스터에 전송될 수 있다는 것이다. 데이터스트림의 후속한 바이트는 메모리 명령 타입에 따른 어드레스 데이터 및/또는 입력 데이터일 수 있다. 당업자는 본 발명의 여러 양상에 따라 메모리 장치에 의해 인식된 메모리 명령 세트가 워드-단위로(즉, 16bits) 또는 임의의 I/O 폭으로 한정될 수 있음을 인식할 것이다. 도 3a에서, 명령 데이터(즉, "페이지 판독"(314)에 대응하는 00h) 다음에 5 바이트의 어드레스 데이터: 2 바이트의 열 어드레스 데이터와 3 바이트의 행/뱅크 어드레스 데이터가 온다. 어드레스 데이터가 도 2c에서 어드레스 레지스터(258)에 기록된다. 어드레스 데이터는 판독될 메모리 뱅크(202)에 저장된 데이터의 위치를 찾는데 사용된다. 프리-디코더 회로(216), 열 디코더 내장 회로(column decoder in circuit)(212) 및 행 디코더(214)는 판독될 데이터를 선택하기 위해 이 프로세스 동안에 사용된다. 예컨대, 프리-디코더 모듈(214)은 어드레스 정보를 미리 디코딩하는데 사용된다. 후속해서, 열 디코더 내장 회로(212) 및 행 디코더(214)는 어드레스 데이터에 대응하는 비트라인 및 워드라인을 활성화하는데 사용된다. "페이지 판독" 명령의 경우, 복수의 비트라인은 원드 라인에 대응하여 활성화된다. 후속해서, 메모리 뱅크(202)에 저장된 데이터는 감지 증폭기에 의해 감지된 후 페이지 레지스터 내장 회로(212)에 전송된다. 페이지 레지스터 내의 데이터는 도 3a에서 시간(318)까지 이용 가능하지 않을 수 있다. 즉, 출력 핀(SOPx)은 "사용중"을 지시할 것이다. 경과한 시간의 양은 전송 시간( $t_R$ )으로 지칭된다. 전송 시간 기간은 (도 3a에서) 시간(318)에 종료되며,  $t_R$ 의 지속기간 동안 지속된다.

[0056] 전송 시간 기간이 경과하기 전에, 메모리 뱅크 상태 지시자는 특정한 메모리 뱅크(예컨대 메모리 뱅크(202))가 "사용중"임을 지시하도록 설정된다. 도 3a의 예시적인 메모리 뱅크 상태 지시자는 메모리 뱅크(202)(즉, 뱅크 0)가 "사용중"이거나 "준비중"임을 지시하는 비트 중 하나(예컨대 비트 4)를 가진 1-바이트 필드이다. 메모리 뱅크 상태 지시자는 도 2e의 상태 레지스터(288)에 저장된다. 메모리 뱅크 상태 지시자는 메모리 뱅크가 인입된 데이터스트림으로부터 식별된 후 업데이트된다(예컨대 비트 4가 '0'으로 설정된다). 메모리 동작이 완료되면, 뱅크 상태 지시자는 메모리 뱅크가 더 이상 "사용중"이 아님(즉, '준비중'임)을 지시하도록 업데이트된다(예컨대 비트 4가 '1'로 설정된다). SOPx 출력 핀뿐만 아니라 뱅크 상태 지시자도 더 상세하게 후술될 바와 같이 "사용중" 상태를 지시할 것임을 주목해야 한다. 당업자는 비록 메모리 뱅크 상태 지시자가 도 3a에서 1-바이트 필드로서 도시된다 하더라도, 그 크기가 반드시 그렇게 제한될 필요가 없음을 인식할 것이다. 더 큰 상태 지시자의 적어도 하나의 이점은 더 다수 양의 메모리 뱅크의 상태를 모니터할 수 있다는 것이다. 게다가, 이 상태 지시자는 다른 타입의 상태(예컨대 메모리 뱅크가 "페이지 프로그램"과 같은 메모리 동작이 실행된 이후 "통과" 또는 "실패" 상태에 있는지)를 모니터하는데 사용될 수 있다. 게다가, 각 비트가 서로 다른 메모리 뱅크의 상태를 지시하도록 구현되고 있는 이러한 예의 상태 지시자는 단지 예시적인 것임이 당업자에게 분명할 것이다. 예컨대, 비트 조합의 값은 (예컨대, 논리 게이트 및 기타 회로를 사용하여) 메모리 뱅크의 상태를 지시하는데 사용될 수 있다. 메모리 뱅크 상태 지시자에 대응하는 "판독 상태" 명령의 동작은 아래에서 도 7과 관련하여 논의될 것이다.

[0057] 도 3a의 예에서 메모리 뱅크 상태 지시자는 (단계(328)에서) "판독 상태" 메모리 명령(316)을 사용하여 판독된다. 종종 전송 시간 동안에, "판독 상태" 명령(316)이 레지스터 블록(224)에서 명령 레지스터에 전달된다. "판독 상태" 명령은 메모리 장치(200)에게 메모리 뱅크(202)의 상태를 모니터하여 메모리 뱅크(202)로부터 페이지 레지스터(216)로의 데이터 전송이 완료된 때를 판정할 것을 지시한다. "판독 상태" 명령은 제어 모듈(238)로부터 데이터 경로 제어 모듈(230)을 거쳐 전달되거나, 데이터 경로 제어 모듈(230)에 의해 직접 전달된다. "판독 상태" 명령이 발급되면(예컨대, 명령 번역기(228) 및/또는 제어 모듈(238)로 전달되면), 출력 포트 인에이블(OPEx) 신호(310)가 높은 상태로 구동되며, 메모리 뱅크 상태 지시자의 내용이 직렬 출력(SOPx) 포트(312)를 거쳐 출력된다. IPEx 신호(306)와 유사하게, OPEx 신호(310)는 높은 상태로 설정될 때 직렬 출력 포트 버퍼(예컨대, 데이터 출력 레지스터)를 인에이블한다. 도 3a의 시간(318)에, SOPx 내의 상태 지시자 데이터는 메모리 뱅크(202)가 (단계(330)에서) "사용중" 상태에서 "준비중" 상태로 변경되었음을 지시한다. OPEx 신호(310)는 상태 지시자의 내용이 더 이상 필요하지 않으므로 낮은 상태로 복귀한다.

[0058] 다음으로, 도 3a에서 IPEx 신호는 높은 상태로 설정되고, 후행하는 어드레스 데이터가 없는 "페이지 판독" 명령(320)이 데이터 레지스터로부터 출력 핀(SOPx)로 데이터를 제공하기 위해 (단계(332)에서) 레지스터 블록(224)의 명령 레지스터에 재발급된다. 후속해서, OPEx 신호가 높은 상태로 설정되고(및 IPEx가 낮은 상태로 복귀하고), 페이지 레지스터(216)의 내용이 SOPx(312)에 전송된다. 출력 데이터는 (단계(334)에서) 메모리 장치(200)로부터 링크 인터페이스(230)를 거쳐 제공된다. 여러 정정 회로(도면에서 미도시됨)는 출력 데이터를 점검

하고, 에러가 검출된다면 판독 에러를 지시할 수 있다. 당업자는 페이지 판독 명령의 상태 및 재확인 모니터링이 시스템에 의해 자동으로 이뤄질 수 있음을 이해할 것이다. 도 3a는 단지 본 발명의 양상에 따른 메모리 장치 동작의 일례이며, 본 발명은 그렇게 제한되지 않는다. 예컨대, 다른 메모리 명령 및 타이밍 도를 본 발명이 여러 양상에 따라 상상할 수 있다.

[0059] 예컨대, 도 4에서 "페이지 판독" 명령 다음에 오는 "랜덤 데이터 판독" 명령에 대한 간략화된 타이밍 도가 예시되어 있다. "랜덤 데이터 판독" 명령은 "페이지 판독" 명령이나 "랜덤 데이터 판독" 명령에 후속하여 하나 또는 복수의 열 어드레스에서 추가적인 데이터의 판독을 가능케 한다. "랜덤 데이터 판독" 명령(402)에 대한 데이터 스트림은 세 개의 바이트: (제 1 바이트에서) 명령 데이터와, (제 2 및 제 3 바이트에서) 열 어드레스 데이터로 구성된다. 데이터가 "페이지 판독" 명령에서 선택된 동일한 행으로부터 판독될 것이므로, 어떠한 행 어드레스 데이터도 필요치 않다. 보통의 "페이지 판독" 명령이 완료된 이후 발급된 "랜덤 데이터 판독" 명령으로 인해 결국 현재의 페이지(즉, 더 이른 명령 동안의 페이지 판독)로부터 데이터(404) 중 일부가 출력되게 된다. "랜덤 데이터 판독" 명령에 대한 적어도 하나의 이점은 데이터가 메모리 뱅크(202)에 대응하는 회로(212)의 페이지 레지스터에 이미 존재하므로 미리 선택된 페이지로부터 데이터가 출력될 수 있는 효율이 증가한다는 것이다.

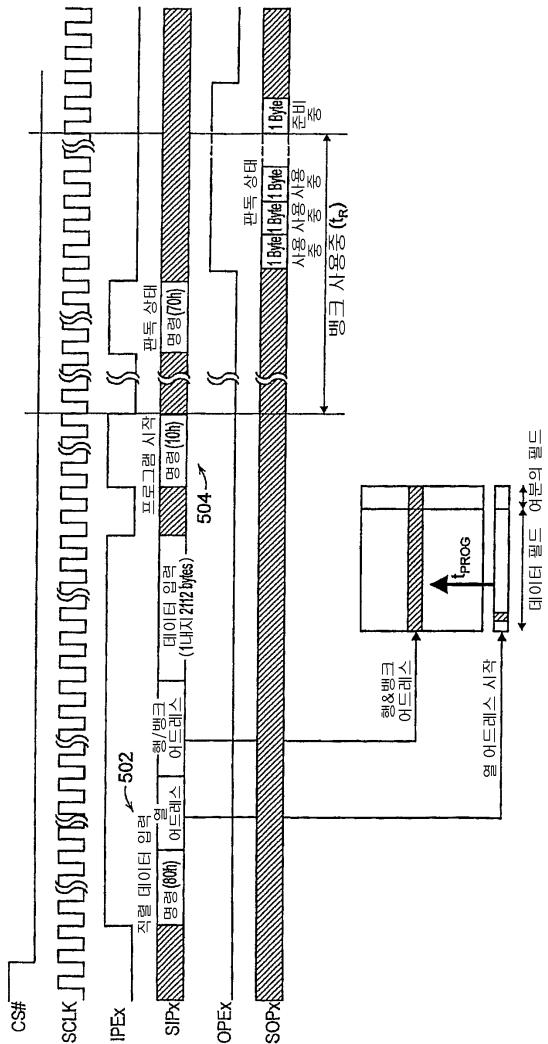

[0060] 도 5a에 관해, "페이지 프로그램" 명령에 대한 타이밍 도가 예시된다. 도 2a에 예시된 실시예가 직렬 데이터 입출력 링크 구조를 사용하므로, 페이지 프로그래밍을 시작하기 전에, 프로그램 데이터가 먼저 뱅크 페이지 레지스터 내로 로딩되어야 한다. 이것은 "직렬 데이터 입력 명령"으로 달성된다. "직렬 데이터 입력" 명령(502)은 데이터의 페이지(예컨대 2,2112바이트)까지 페이지 버퍼 내장 회로(212)에 로딩되는 직렬 데이터 로딩 기간으로 구성된다. 데이터 레지스터를 로딩하는 프로세스가 완료된 후, 뱅크 레지스터로부터 적절한 메모리 뱅크로 데이터를 전송하기 위해 "페이지 시작" 명령(504)이 발급된다. 명령(504)이 발급되면, 내부 기록 상태 머신(state machine)이 적절한 알고리즘을 수행하고, 동작을 프로그래밍하고 검증하기 위해 타이밍을 제어한다. 그러므로 본 발명의 실시예에 따라, "페이지 시작" 명령은 두 개의 단계: 직렬 데이터 입력 단계와 검증 단계로 나눠진다. "페이지 프로그램" 명령을 성공적으로 완료하면, 메모리 뱅크 상태 지시자는 성공적인 동작을 지시하기 위해 ("실패"와 대조되는) "통과" 결과를 제공할 것이다. 다른 면에서, 도 5a의 예에서 수반하는 타이밍 도 및 단계는 더 상세하게 전술했던 도 3a의 타이밍도 및 단계와 유사하다.

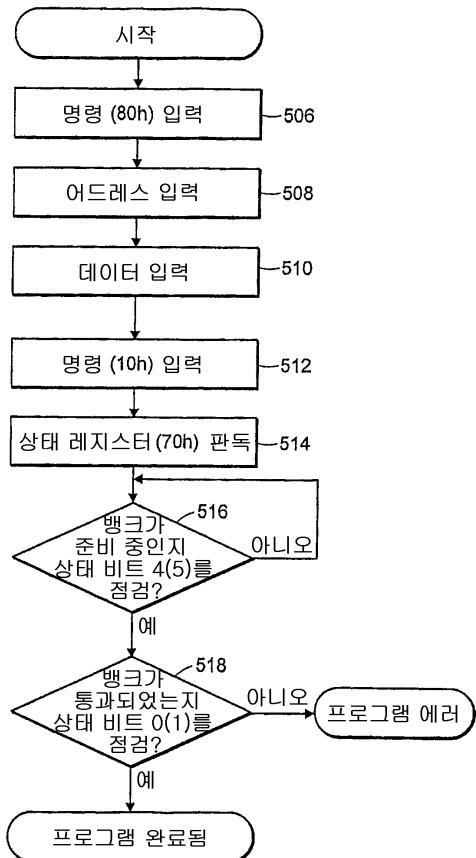

[0061] 게다가, 도 5b는 도 5a의 타이밍 도에서 "페이지 프로그램" 명령의 동작에 필적하는 간략화된 흐름도를 도시한다. 단계(506)에서, "직렬 데이터 입력" 명령(502)은 직렬 입력 포트(SIP) 라인에 입력된다. 이 예에서 SIP 라인에 대한 데이터스트림 입력은 (제 1 바이트에서) 명령 데이터로 시작하는 복수-바이트 직렬 데이터스트림(즉, 직렬 입력 데이터)이다. 다음으로, (직렬 데이터스트림의 제 2 및 제 3 바이트에서) 열 어드레스 데이터와 (직렬 데이터스트림의 제 4, 제 5 및 제 6 바이트에서) 행 어드레스/뱅크 데이터는 (단계(508)에서) SIP 라인에 입력된다. 입력 데이터는 (단계(510)에서) 직렬 데이터스트림의 후속한 바이트에서 SIP 라인에 입력된다. 단계(512)에서, "프로그램 시작" 명령(504)이 발급된다. 다음으로, 동작의 상태를 모니터하기 위해, "판독 상태" 명령이 (단계(514)에서) SIP 라인에 기록된다. 이로 인해, 결국 메모리 장치는 메모리 뱅크 상태 레지스터의 상태 비트를 모니터링하게 된다. 상태 비트가 메모리 뱅크가 (단계(516)에서) 준비중이며, 메모리 뱅크가 (단계(518)에서) "통과"를 지시함을 지시하면, "페이지 프로그램" 명령이 성공적으로 실행되었다.

[0062] 게다가, "복사를 위한 페이지 판독" 및 "복사를 위한 타겟 어드레스 입력" 메모리 명령이 본 발명의 양상에 따라 메모리 장치에 의해 실행된 다른 동작이다. 만약 "복사를 위한 페이지 판독" 명령이 직렬 링크 인터페이스의 명령 레지스터에 기록된다면, 메모리 위치의 내부 소스 어드레스가 (3바이트 단위로) 기록된다. 소스 어드레스가 입력되면, 메모리 장치는 특정한 소스 어드레스에서 메모리 뱅크의 내용을 데이터 레지스터에 전송한다. 후속하여, (3-바이트 뱅크/행 어드레스 시퀀스를 가진) "복사를 위한 타겟 어드레스 입력" 메모리 명령이 페이지 복사 동작을 위한 타겟 메모리 어드레스를 명시하는데 사용된다. 그러면, "페이지 프로그램" 명령이 내부 제어 논리가 자동으로 페이지 데이터를 타겟 어드레스에 기록하게 하는데 사용될 수 있다. "판독 상태" 명령은 후속해서 명령의 성공적인 수행을 확인하는데 사용될 수 있다. 다른 메모리 동작이 여기서 개시된 전체 내용을 살펴본 후 당업자에게 분명하게 될 것이다.

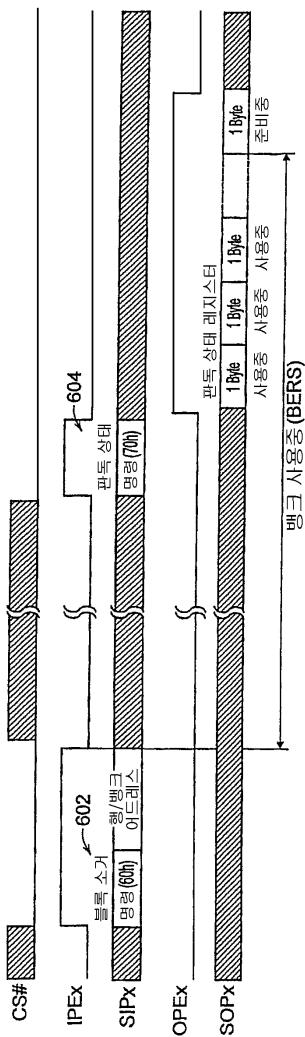

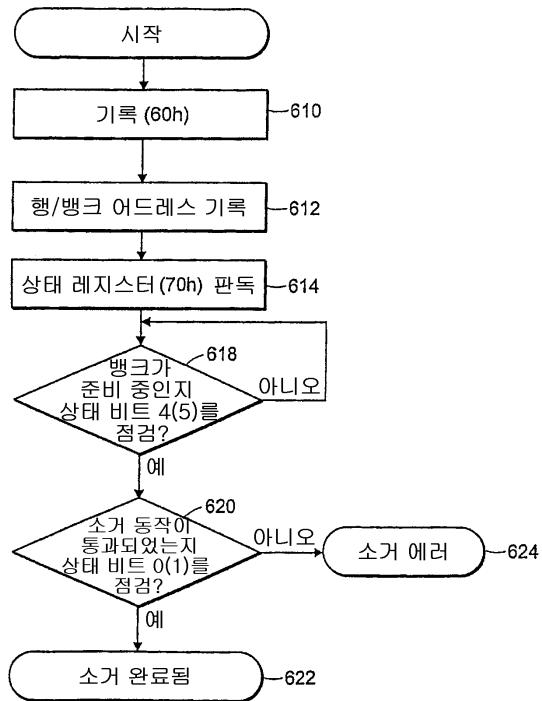

[0063] 도 6a에 관해서, "소거"(또는 "블록 소거") 명령에 대한 타이밍도가 예시된다. 게다가, 도 6b는 도 6a의 타이밍 도에서 "소거" 명령의 동작에 필적하는 간략화된 흐름도를 도시한다. 당업자는 소거가 통상 블록 레벨에서 발생한다는 점을 알고 있다. 예컨대, 플래시 메모리 장치(200)는 각 뱅크에서 블록당 64 2,112-바이트(2,048+64 바이트)로 구성된 2,048개의 소거 가능한 블록을 가질 수 있다. 각 블록은 132K바이트(128K+4K바이트)이다. "소거" 명령은 한 번에 한 블록 상에서 동작한다. 블록 소거는, "소거" 명령(즉, '60h'의 명령 데이터)에 대응하는, 단계(610)에서의 명령 데이터(602)를 단계(612)에서의 행 및 뱅크 어드레스를 위한 세 개의 바이트와 함

께 SIPx를 통해 명령 레지스터에 기록함으로써 시작된다. 명령 및 어드레스 입력이 완료된 이후, 내부 소거 상태 머신은 속성 알고리즘을 자동으로 수행하고, 모든 필요한 타이밍을 제어하여 동작을 소거하고 검증한다. "소거" 동작이 메모리 블록의 모든 메모리 위치에 '1'의 논리 값을 기록 즉 프로그래밍함으로써 수행될 수 있음을 주의해야 한다.  $t_{BERS}$ (즉, 블록 소거 시간)가 완료될 때를 판정하도록 소거 상태를 모니터링하기 위해, "판독 상태" 명령(604)(예컨대, 70h에 대응하는 명령 데이터)이 단계(614)에서 발급될 수 있다. "판독 상태" 명령 이후, 모든 판독 사이클은 새로운 명령이 주어질 때까지 메모리 뱅크 상태 레지스터로부터 올 것이다. 이 예에서, 메모리 뱅크 상태 레지스터의 적절한 비트(예컨대, 비트 4)는 대응하는 메모리 뱅크의 상태(예컨대, 사용중 또는 준비중)를 반영한다. 뱅크가 단계(618)에서 준비중이 될 때, 메모리 뱅크 상태 레지스터의 적절한 비트(예컨대, 비트 0)가 단계(622)에서 소거 동작이 통과되었는지(즉, 성공적으로 실행되었는지) 또는 단계(624)에서 실패했는지를 판정하기 위해 단계(620)에서 점검된다. 일부 면에서, 도 6a의 예에서 수반하는 타이밍 도 및 단계는 더 상세하게 상술했던 도 3a의 타이밍 도 및 단계와 유사하다.

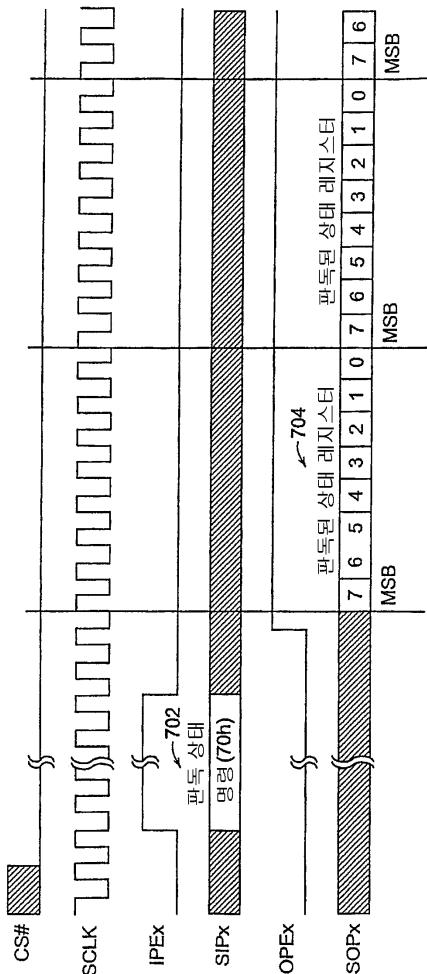

[0064] 도 7을 참조하면, 메모리 뱅크 상태 지시자는 "판독 상태" 메모리 명령을 사용하여 판독된다. "판독 상태" 명령(즉, '70h')이 702에서 도 2c의 명령 레지스터(256)에 전송될 때, 메모리 장치(200)에게는, 특히 메모리 뱅크(202)로부터 페이지 버퍼 내장 회로(212)로의 데이터 전송이 성공적으로 완료된 때를 판정하기 위해 메모리 뱅크(202)의 상태를 모니터링할 것이 지시된다. "판독 상태" 명령이 발급되면(예컨대, 명령 해석기(262)에 전달되면), 출력 포트 인에이블(OPEX) 신호가 높은 상태로 구동되고, 메모리 뱅크 상태 지시자의 내용이 직렬 출력(SOPx) 포트를 거쳐 704에서 출력된다. OPEX 신호는 높은 상태로 설정될 때 직렬 출력 포트 버퍼(예컨대, 데이터 출력 레지스터)를 인에이블한다. 도 7의 예에서, 메모리 뱅크 상태 지시자는 특히 메모리 뱅크(예컨대, 메모리 뱅크(202))가 "사용중"이거나 "준비중"인지 및/또는 메모리 뱅크 상에서 실행된 동작(예컨대 "소거" 명령)이 "통과"했는지 "실패"했는지를 지시하는 각 비트를 가진 1-바이트(즉, 8-비트) 필드이다. 당업자는, 비록 메모리 뱅크 상태 지시자가 도 7에서 1-바이트 필드로서 도시된다 하더라도, 그 크기가 반드시 그렇게 제한되지 않을 것임을 이해할 것이다. 더 큰 상태 지시자의 적어도 하나의 이점은 더 다수 양의 메모리 뱅크의 상태를 모니터링할 수 있다는 것이다. 게다가, 비록 이 예의 상태 지시자가 각 비트가 서로 다른 메모리 뱅크의 상태를 지정하도록 구현되었다 하더라도 본 발명이 그렇게 제한되지 않음이 당업자에게 분명할 것이다. 예컨대, 비트 조합의 값은 (예컨대, 논리 게이트 및 기타 회로를 사용하여) 메모리 뱅크의 상태를 지시하는데 사용될 수 있다.

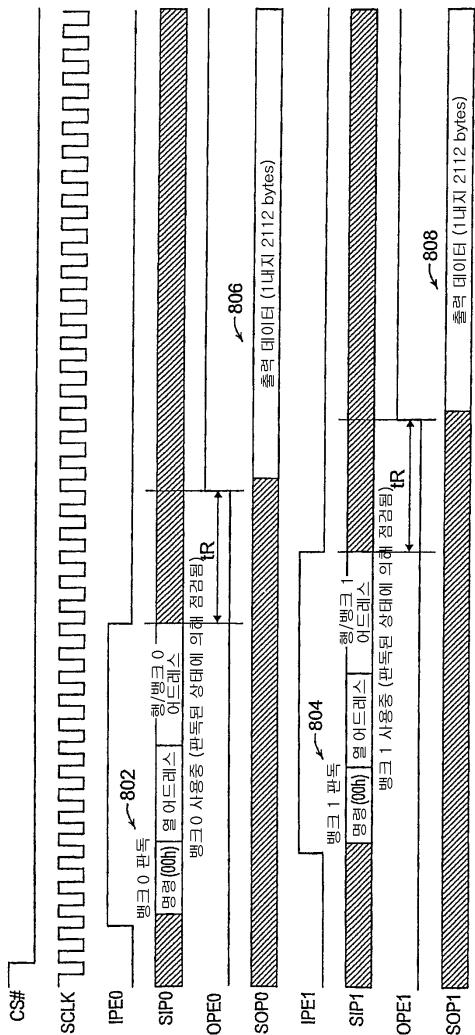

[0065] 도 8a, 8B 및 8C는 이중 독립 직렬 데이터 링크(230 및 236)를 사용하여 동시 동작을 실행하는데 사용되는 본 발명의 양상에 따른 메모리 장치에 대한 타이밍 도를 예시한다. 본 발명의 양상에 따른 메모리 장치에 의해 실행된 일부 동시 동작은 동시 판독, 동시 프로그래밍, 동시 소거, 프로그래밍 동안의 판독, 소거 동안의 판독, 및 소거 동안의 프로그래밍을 포함하며, 이들로 제한되지 않는다. 도 8a는 뱅크 A(뱅크(202))와 뱅크 B(뱅크(204)) 상에서 실행되는 동시 "페이지 판독" 동작을 예시한다. 도 8a에서, 뱅크 A는 "뱅크 0"으로 표시되는 반면, 도 8b에서, 뱅크 B는 "뱅크 1"로 표시된다. 여기서 개시한 전체 내용을 살펴보면, 다른 동시 동작은 당업자에게 분명하게 될 것이다.

[0066] 도 8a를 참조하면, 메모리 장치(200)에서 서로 다른 메모리 뱅크에 관련된 동시 "페이지 판독" 동작(802 및 804)이 수행된다. 이중 데이터 링크 인터페이스(230, 236)를 가진 메모리 장치(200)에서, "페이지 판독"(802)이 데이터 링크 인터페이스(230)(즉, 링크 0)를 거쳐서 계류 중인 반면, "페이지 판독" 명령(804)이 데이터 링크 인터페이스(236)(즉, 링크 1)를 거쳐 발급된다. 비록 도 8a가 뱅크 1 상의 "페이지 판독" 이전에 시작하는 뱅크 0 상의 "페이지 판독"을 도시할지라도, 두 개의 "페이지 판독" 동작은 실질적으로 동시에 시작하여 동시에 동작할 수 있다. "페이지 판독" 명령 각각으로부터 출력된 데이터(806 및 808)는 그 각자의 데이터 링크 인터페이스를 거쳐서 동시에 전달된다. 그러므로 메모리 장치(200)의 각 데이터 링크 인터페이스는 메모리 뱅크 중 임의의 하나에 액세스하고 독립적으로 동작할 수 있다. 이러한 특성의 적어도 하나의 이점은 시스템 설계 용통성이 더 크다는 것과, 장치 이용(예컨대 버스 이용 및 코어 이용)이 개선된다는 것이다.

[0067] 도 8a에서 메모리 뱅크로부터 데이터 링크 인터페이스로 출력된 데이터의 경로는 앞서 논의한 도 3a의 경로와 유사하다. 예컨대, 메모리 뱅크(204)로부터 출력된 데이터는 S/A 및 페이지 버퍼(218)로부터 예컨대 뱅크 어드레스에 의해 제어된 경로 스위치(206)를 거쳐 출력 병-직렬 레지스터 블록(240)과 직렬 데이터 링크 인터페이스(236)(즉, 링크 1)로 전해진다. 메모리 뱅크(202 및 204)와 직렬 데이터 링크 인터페이스(230 및 236) 각각 사이의 동시 데이터 전송은 서로 독립적으로 발생할 것이다. 뱅크 어드레스는 경로 스위치(206)를 제어할 수 있으므로, 직렬 데이터 링크 인터페이스(236)는 대신 뱅크(202)에 액세스할 수 있다. 메모리 장치(200)의 데이터 링크 인터페이스의 수는 메모리 장치(200) 상의 포트나 핀의 수로 제한되지 않는다. 또한, 메모리 장치(200)에서 링크 인터페이스의 수도 메모리 장치에서 메모리 뱅크의 수에 의해 제한되지 않는다. 예컨대, 각 데이터 링크

인터페이스는 단일 입력 스트림 및/또는 단일 출력 스트림을 처리할 수 있다.

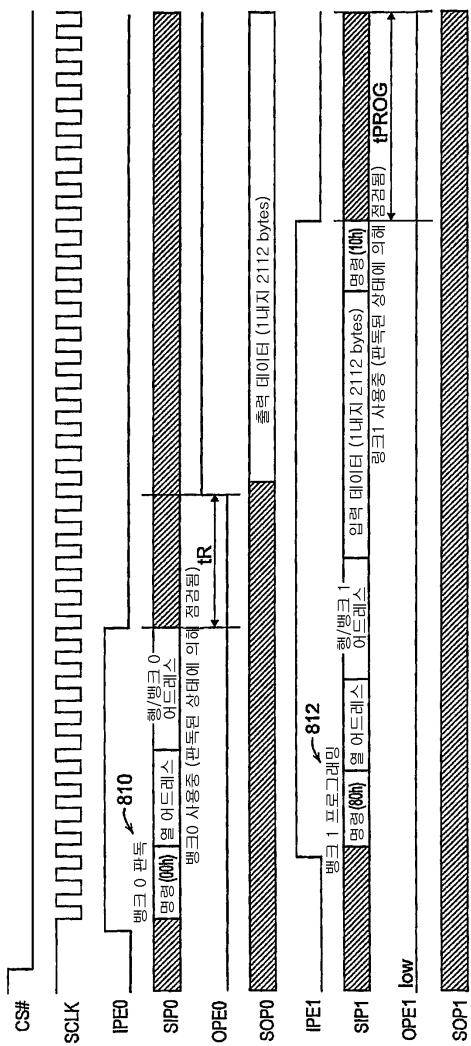

[0068] 더나아가, 본 발명의 여러 양상에 따라, 도 8b는 동시에 실행된 메모리 장치(200)에서 서로 다른 메모리 뱅크에 관련된 "페이지 판독" 명령(810) 및 "페이지 프로그램" 명령(812)의 타이밍 도를 예시한다. 이 예에서, 판독 동작("페이지 판독"(810))은 직렬 데이터 링크 인터페이스(230)를 거쳐서 다수의 메모리 뱅크(예컨대, 메모리 뱅크(202)) 중 하나 상에서 실행되고 있다. 한편, 동시에, 기록 동작("페이지 프로그램"(812))은 직렬 데이터 링크 인터페이스(236)를 거쳐 다수의 메모리 뱅크 중 다른 하나(예컨대, 메모리 뱅크(204))에서 실행되고 있다. 본 발명의 여러 양상에 따라, 메모리 장치(200)에서의 각 링크는 메모리 뱅크 중 어느 하나에 액세스하고 독립적으로 동작할 수 있다.

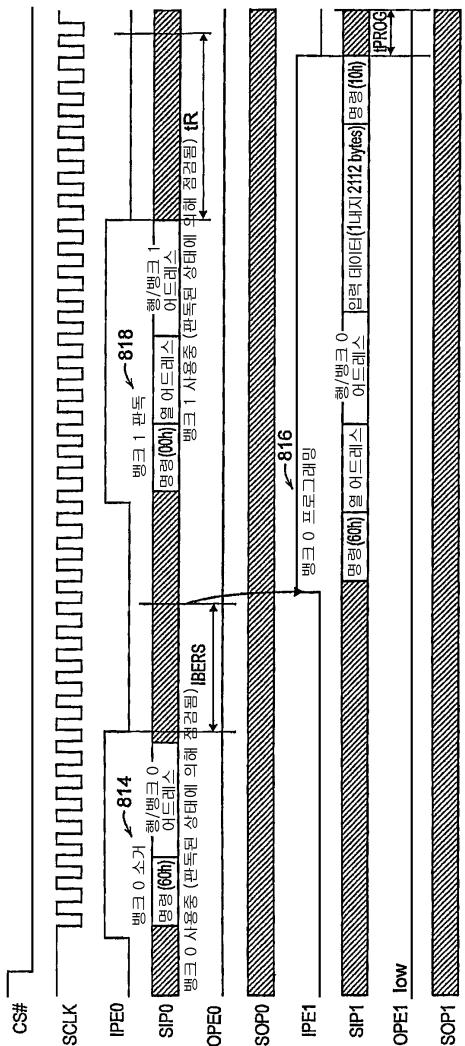

[0069] 도 8c는 동시 메모리 동작을 실행하는 두 개의 직렬 데이터 링크 인터페이스와 두 개의 메모리 뱅크를 가진 메모리 장치(200)의 예시적인 타이밍 도이다. 첫째, 메모리 뱅크 0(뱅크(202))에 관련된 "소거" 명령(814)이 직렬 인터페이스 링크 0(직렬 데이터 링크(230))으로부터 발급된다. 링크 0(직렬 데이터 링크(230)) 및 메모리 뱅크 0(뱅크(202))가 "소거" 명령(814)을 사용중인 동안, "페이지 프로그램" 명령은 메모리 장치에 수신되고 링크 1(직렬 데이터 링크(236))을 사용하는 데 관련된다. 그에 따라 "페이지 프로그램" 명령(816)은 직렬 데이터 링크 인터페이스 1(직렬 데이터 링크(236))로부터 메모리 뱅크 0(뱅크(202)) 상에서 실행된다. 한편, 동시에, 판독 명령(818)이 직렬 데이터 인터페이스 0(직렬 데이터 링크(230))에 의해 메모리 뱅크 1(뱅크(204)) 상에서 실행된다. 데이터는 메모리 명령(814) 동안에 직렬 데이터 링크 인터페이스 0(직렬 데이터 링크(230))과 링크 0(뱅크(202)) 사이와, 메모리 명령(818) 동안의 동일한 링크 인터페이스 0(직렬 데이터 링크(230))와 링크 1(뱅크(204)) 사이에 전송된다. 그러므로 본 발명의 양상에 따라, 메모리 장치(200)에서 각 링크는 메모리 뱅크(즉, 사용중이지 않은 메모리 뱅크) 중 임의의 하나에 독립적으로 액세스한다.

[0070] 여기서 개시한 전체 내용을 살펴본 후, 도 8a, 8B 및 8C가 본 발명에 따라 고안한 동시 메모리 동작의 일부 예를 단지 예시한다는 것이 당업자에게 분명할 것이다. 동시 동작의 다른 예는 동시 소거, 프로그래밍 동안의 판독, 소거 동안의 판독, 소거 동안의 프로그래밍, 프로그래밍 동안의 소거 및/또는 동시 프로그래밍을 포함하며, 이들로 제한되지 않는다. 당업자는 흐름도에 기재된 단계의 순서에 대한 서술이 이를 단계를 그러한 특정한 순서로만 제한하는 것으로 해석되지 않아야 함을 인식할 것이다. 예컨대, 판독 및 프로그램 명령은 판독 상태 명령을 갖거나 갖지 않고 발급될 수 있다.

[0071] 도 9는 본 발명의 양상에 따른 다수의 직렬 링크 인터페이스와 다수의 메모리 뱅크 사이의 두 개의 동시 기록 동작을 더욱 일반적으로 기술한다. 도 9는 본 발명의 실시예에 따라 직렬 데이터 링크 인터페이스를 통해 데이터를 메모리 뱅크에 기록하는 방법을 예시한다. 먼저, 단계(902)에서, 데이터스트림이 직렬 데이터 링크 인터페이스에서 수신된다. 이 데이터스트림은 레지스터에 저장될 명령, 어드레스 및 데이터를 포함한다. 다음으로, 단계(904)에서, 제 1 직렬 데이터 링크 인터페이스에 대응하는 직렬 데이터 링크 인터페이스 상태 지시자가 제 1 직렬 데이터 링크 인터페이스가 사용중임을 지시하기 위해 업데이트된다. 단계(904)는 상태 레지스터에서 비트 값을 변화시키는 단계를 포함한다. 단계(904)에서의 업데이트는 특정한 인터페이스가 사용중임을 지시한다. 단계(906)에서, 데이터스트림은 제 1 메모리 뱅크 식별자를 추출하기 위해 분석된다. 메모리 뱅크 식별자는 메모리 장치에서 메모리 뱅크를 고유하게 식별한다. 메모리 뱅크 식별자는 데이터스트림의 어드레스 필드나 다른 필드 내에 포함될 수 있다. 다음으로, 메모리 뱅크 식별자를 추출하기 위해 데이터스트림을 분석한 후, 단계(908)에서, 대응하는 메모리 뱅크 상태 지시자가 업데이트된다. 단계(904 및 908)에서 발생한 이러한 업데이트는 예컨대 상태/ID 레지스터(210) 내에서 제어 회로에 의해 생성된 제어 신호에 의해 구동될 수 있다. 이를 제어 신호는 간략화하기 위해 여기에 포함된 타이밍 도에서 생략되었다. 결국, 단계(910)에서 데이터의 경로는 제 1 직렬 데이터 링크와 제 1 메모리 뱅크 사이에서 지정된다. 데이터는 먼저 메모리 뱅크 페이지 레지스터에 기록된 후 후속하여 메모리 뱅크로 프로그래밍되므로, 단계(910)는 이 일반적인 설명에서 간략화되었다는 점을 주목해야 한다.

[0072] 한편, 다른 기록 데이터 동작이 도시된 동작(902)과 동시에 서로 다른 직렬 데이터 링크 인터페이스를 통해 서로 다른 메모리 뱅크 상에서 실행된다. 달리 말해, 제 2 메모리 동작이 제 2 직렬 데이터 링크 인터페이스와 제 2 메모리 뱅크 사이에 경로가 지정된 제 2 데이터스트림을 사용하여 동시에 실행된다. 먼저, 제 2 데이터스트림이 단계(912)에서 다수의 직렬 데이터 링크 인터페이스 중 제 2 인터페이스에서 수신된다. 단계(912 및 902)에서 언급된 직렬 데이터 링크 인터페이스는 모두 동일한 메모리 장치의 일부분이다. 단계(914)에서, 제 2 데이터 링크 인터페이스에 대응하는 직렬 데이터 링크 인터페이스 상태 지시자는 제 2 직렬 데이터 링크 인터페이스가 사용되고 있음을 지시하기 위해 업데이트된다. 다음으로, 제 2 데이터스트림이 단계(916)에서 제 2 메모리 뱅크 식별자를 추출하기 위해 분석된다. 제 2 메모리 뱅크 식별자에 대응하는 메모리 뱅크 상태 지시자는, 제 2 메모

리 뱅크가 단계(918)에서 사용되고 있으며, 단계(920)에서 데이터의 경로가 "페이지 프로그램" 명령과 관련하여 전술된 바와 같이 제 2 메모리 뱅크의 관련 페이지 레지스터를 통해 제 2 직렬 데이터 링크 인터페이스와 제 2 메모리 뱅크 사이에서 지정됨을 지시하기 위해 업데이트된다. 도 9에서, 데이터 전송이 발생했다면, 즉, 직렬 데이터 링크 인터페이스가 지정된 메모리 뱅크로 기록될 모든 데이터를 수신했다면, 각 직렬 데이터 링크 인터페이스에 대응하는 직렬 데이터 링크 인터페이스 지시자는 관련 링크가 이제 이용 가능함을 지시하도록 리셋될 것인 반면, 메모리 뱅크 지시자는 모든 관련 데이터가 프로그래밍될 때까지 사용중 상태로 남아 있을 것이며, 모든 관련 데이터가 프로그래밍된 이후에 메모리 뱅크 지시자는 관련 뱅크가 이용 가능하게 되었음을 지시할 것이다.

[0073] 도 10은 도 9에서 단계(902 내지 910)에 도시된 데이터 기록과 동시에 데이터가 메모리 뱅크로부터 판독될 때 실행될 수 있는 예시적인 단계(단계(1010)로 지정됨)를 포함한다. 도 10은 도 7에 도시된 동시 메모리 동작을 완료하는데 실행될 수 있는 일부 단계의 예를 예시한다. 먼저, 단계(1002)에서, 제 2 메모리 뱅크에 저장된 데이터에 대한 판독 요청이 다수의 직렬 데이터 링크 인터페이스 중 제 2 인터페이스로부터 수신된다. 단계(1004)에서, 제 2 데이터 링크 인터페이스에 대응하는 직렬 데이터 링크 인터페이스 상태 지시자는 제 2 직렬 데이터 링크 인터페이스가 사용중임을 지시하기 위해 업데이트된다. 제 2 메모리 뱅크 식별자에 대응하는 메모리 뱅크 상태 지시자는 제 2 메모리 뱅크가 단계(1006)에서 사용중임을 지시하기 위해 업데이트된다. 마지막으로, 단계(1008)에서, 데이터의 경로가 제 2 메모리 뱅크와 제 2 직렬 데이터 링크 인터페이스 사이에서 지정된다. 도 10에 도시된 단계 중 하나 이상이 동시에 실행될 수 있다.

[0074] 도 1b로 돌아가서, 도시된 메모리 장치는 가상의 복수의 링크를 사용하는 단일 데이터 링크 인터페이스(120) 구성을 포함한다. 도 1b는 전술된 입력 직-병렬 레지스터(232)의 구성으로 구현될 수 있다. 더욱 일반적으로, 도 1b의 실시예는 메모리 장치(200)로 구현될 수 있지만, 두 직렬 데이터 링크 중 하나만이 사용된다. 종래의 플레이시 메모리에서, I/O 핀은 동작이 완료될 때까지 점거된 상태이다. 그러므로 장치 사용중 상태 동안에 어떠한 동작도 어서트(assert)될 수 없으며, 이것은 장치 이용 가능성을 감소시키며, 전체 성능을 저하시킨다. 도 1b에 도시된 예에서, "판독 상태" 동작에 의해 점검된 임의의 이용 가능한 메모리 뱅크가 두 메모리 뱅크 중 하나에서 동작이 초기화된 이후 액세스될 수 있다. 후속해서, 메모리 장치는 추가 스위치 경로를 거쳐서 이용 가능한 메모리 뱅크에 액세스하기 위해 직렬 데이터 링크를 사용할 수 있다. 그러므로 본 발명의 이 양상에 따라, 단일 링크가 복수의 메모리 뱅크에 액세스하기 위해 사용될 수 있다. 이 가상의 복수의 링크 구성은 단일 링크를 사용하여 복수의 링크 동작을 애뮬레이트한다.

[0075] 도 12는 뱅크 0에서 "페이지 프로그램"과 뱅크 1에서 "페이지 판독"이 수행되게 될 가상의 복수의 링크 구성을 사용하여 메모리 동작을 실행하는 두 개의 메모리 뱅크를 갖는 메모리 장치의 타이밍 도를 예시한다. 먼저, 메모리 뱅크 0에 관련된 "페이지 프로그램" 명령(1202)이 발급된다. "페이지 프로그램" 명령은 이미 전술하였지만, 개괄적으로 설명하면, "직렬 데이터 입력" 명령이 먼저 뱅크 0의 페이지 레지스터에 뱅크 0으로 프로그래밍될 데이터를 로딩하기 위해 실행된다. 후속해서, "페이지 프로그램 명령"이 발급되고, 데이터가 페이지 레지스터로부터 뱅크 0으로 기록된다. "판독 상태" 명령(1204)이 발급될 때, 장치는 뱅크 1이 "준비중"(및 뱅크 0은 "사용중")임을 지시한다(1206). 결과적으로, 본 발명에 따른 가상의 복수의 링크 구성은 기초로 해서, 메모리 뱅크 0이 사용 중인 동안에, 메모리 뱅크 1에 관련된 "페이지 판독" 명령(1208)은 발급될 수 있다(발급된다). "페이지 판독" 명령은 전술되었다. "판독 상태" 명령(1210)은 메모리 뱅크의 상태를 판정하기 위해 발급될 수 있다(그리고 도 12에서는 발급되는 것으로 도시되어 있다.). "판독 상태" 명령의 결과는 간격(1212) 동안에 메모리 뱅크 0 및 메모리 뱅크 1 양자가 준비 중임을 지시한다. 마지막으로, 결국 직렬 출력 핀(SOP) 상에 출력될 뱅크 1의 "페이지 판독" 명령에 대응하는 메모리 어드레스의 내용이 될 (뱅크 1에 대한) "페이지 판독" 명령(1214)이 발급된다. 뱅크 0 상의 "페이지 프로그램" 동작이 발생하고 있는 동안, 직렬 데이터 인터페이스 링크 핀(SIP)이 뱅크 1을 "준비중"인 것으로 식별케 하는 "판독 상태" 명령을 수신하는데 이용 가능함을 주목해야 한다. 유사하게, 뱅크 1 상의 "페이지 판독" 명령이 초기화되면, SIP 핀은 뱅크 0 및 1 양자가 이제 준비 중임을 지시하는 "판독 상태" 명령에 다시 이용 가능하다. 그 결과, 단일 직렬 데이터 인터페이스 링크가 양 뱅크를 액세스하고 양 뱅크의 상태를 점검하는데 사용될 수 있다. 도 12에 구현된 가상의 복수의 링크 특성의 양상은 링크가 심지어 더 이른 메모리 동작이 계류중인 동안에도 이용 가능함을 예시한다. 이러한 특성으로부터 얻는 적어도 하나의 이점은 가상의 복수의 링크 구성으로 인해 핀의 총수가 감소한다는 것이다. 다른 이점은 메모리 장치의 성능이 증가한다는 것이다.

[0076] 게다가, 가상의 복수의 링크 특성의 양상이 이중 또는 4중-링크 구성을 갖는 메모리 장치로 구현될 때, 링크 중 하나를 제외한 모두가 비활성 상태인 것으로 간주하는 것이 바람직할 수 있다. 예컨대 (도 1c에서) 4중-링크 구

성에서 네 개의 링크 중 세 개가 사용되지 않을 수 있고, NC(No Connection: 연결 안 됨)로 지정될 수 있다. 그러한 구현의 적어도 하나의 이점은 링크 융통성 및 이용 가능성을 유지하면서도 메모리 장치상의 핀의 수를 감소시킨다는 것이다.

[0077] 본 발명의 여러 양상에 따라, 도 13a는 복수의 메모리 장치(200)를 직렬로 연결하기 위한 데이지-체인 캐스케이드 구성(1300)을 예시한다. 특히, 장치 0은 다수의 데이터 입력 포트(SIP0, SIP1), 다수의 데이터 출력 포트(SOP0, SOP1), 다수의 제어 입력 포트(IPE0, IPE1) 및 다수의 제어 출력 포트(OPE0, OPE1)로 구성된다. 이들 데이터와 제어 신호는 외부 소스(예컨대 메모리 제어기(미도시됨))로부터 메모리 장치(1300)로 전달된다. 게다가, 본 발명에 따라, 제 2 플래시 메모리 장치(장치 1)는 장치 0과 동일한 타입의 포트로 구성될 수 있다. 장치 1은 장치 0에 직렬로 연결될 수 있다. 예컨대, 장치 1은 장치 0으로부터 데이터 및 제어 신호를 수신할 수 있다. 하나 이상의 추가 장치는 또한 유사한 방식으로 장치 0 및 장치 1과 나란하게 직렬로 연결될 수 있다. 캐스케이드 구성에서 최종 장치(예컨대 장치 3)는 미리 결정된 지연시간 이후 데이터 및 제어 신호를 다시 메모리 제어기에 제공한다. 각 메모리 장치(200)(예컨대 장치 0, 1, 2, 3)는 IPE0, IPE1, OPE0 및 OPE1(즉, 제어 출력 포트)의 반향(echo)(IPEQ0, IPEQ1, OPEQ0, OPEQ1)을 후속한 장치에 출력한다. 도 2b에서 전술된 회로는 신호가 어떻게 하나의 장치로부터 후속한 데이터 체인 방식으로 연결된 장치로 전달될 수 있는지를 예시한다. 게다가, 단일 클록 신호는 다수의 직렬로 연결된 메모리 장치 각각에 통신된다.

[0078] 전술한 캐스케이드 구성에서, 캐스케이딩된 메모리 장치(1300)의 장치 동작은 비-캐스케이딩된 메모리 장치(200)에서와 동일하다. 당업자는 메모리 장치(1300)의 전체 지연시간이 캐스케이드 구성에서 증가할 수 있음을 인식할 것이다. 예컨대 도 14는 메모리 장치(1300)에서 수신되고 메모리 장치(1300)의 장치 2 내의 메모리 뱅크에 관련된 "페이지 판독" 메모리 명령(1402)에 대한 매우-간략화된 타이밍 도를 도시한다. 메모리 명령은 메모리 장치(1300)에서 수신되고 장치 0 및 장치 1을 거쳐 장치 2로 전달된다. 예컨대, "페이지 판독" 명령(1402)에 대응하는 데이터스트림은 메모리 장치(1300)의 장치 0의 SIP0 라인으로부터 장치 0의 회로를 거쳐서 전송될 것이며, 장치 0의 SOP0 라인에서 출력된다. 장치 0의 출력은 도 14의 간략화된 타이밍 도의 1404에서 SOPx\_D0 출력 라인 상에 반영된다. "SOPx\_D0"는 장치 0 상의 직렬 출력 포트 0에 대응한다. 유사하게, 데이터스트림은 후속해서 (1406에서) 장치 1 상의 SIPx\_D1에서 수신되며, 장치 1을 거쳐서 전달되어 1408에서 SOPx\_D1 라인 상에서 장치 1에 의해 출력된다. 다음으로, 데이터스트림은 1410에서 장치 2 상의 SIPx\_D2에서 수신된다. 이 예에서, "페이지 판독" 명령은 메모리 장치(200)의 회로에 대해 기술된 것과 유사한 방식으로 장치 2의 메모리 뱅크에 관련되므로, 장치 2의 회로는 "페이지 판독" 명령을 수신하고, 장치 2의 메모리 뱅크로부터 1412에서 장치 2 상의 SOPx\_D2 출력 라인으로의 요청된 데이터의 전송을 제어한다. 장치 2에 의해 출력된 데이터는 1414에서 장치 3에 수신되며 장치 3을 거쳐서 전송되어 메모리 장치(1300)로부터 출력된다. 당업자는 도 14의 간략화한 타이밍 도로부터 네 개의 클록 사이클의 미리 결정된 지연시간이 이러한 캐스케이드 구성으로 인해 초래되었음을 인식할 것이다.

[0079] 한편, 캐스케이드 구성으로 인해 장치 처리량을 희생하지 않고 거의 무제한의 장치가 연결될 수 있다. 본 발명의 양상은 복수-칩 패키지 방법 및 고체 상태 대용량 저장 장치 구현에 유리할 수 있다. 캐스케이딩된 장치(1300)에서 인입되는 데이터스트림은 비-캐스케이딩된 메모리 장치(200)의 데이터스트림과 유사하지만, 데이터스트림의 제 1 바이트 앞에는 1-바이트 장치 식별자가 올 수 있다. 예컨대, 제 1 바이트에서 "0000"의 값은 장치 0을 지시할 수 있는 반면, "0001"의 값은 장치 1을 지시할 수 있다. 당업자는 장치 식별자가 반드시 1 바이트로 제한될 필요가 있기보다는 원하는 경우 증가하거나 감소할 수 있음을 이해할 것이다. 또한, 장치 식별자는 데이터스트림에서 반드시 제 1 바이트 위치에 있을 필요가 없다. 예컨대, 식별자의 크기는 캐스케이드 구성에서 더 많은 장치를 수용하고, 데이터스트림의 어드레스 필드와 함께 놓일 수 있도록 증가할 수 있다.

[0080] 본 발명에 따른 일실시예에서, 메모리 장치(200)는 하나의 모놀리식(monolithic) 4Gb 칩을 사용한다. 다른 실시 예에서, 메모리 장치는 8Gb를 위한 한 쌍의 적층 칩을 사용한다. 다른 실시예에서, 메모리 장치(1300)는 16Gb를 구성하기 위해 4개의 칩의 적층을 사용한다. 본 발명의 다양한 양상에 따른 플래시 메모리 장치는 비휘발성을 요구하는 고체 상태 파일 저장 및 다른 휴대용 장치와 같은 대형 비휘발성 저장 장치에 대한 개선된 방법일 수 있다. 메모리 장치(1300)는 시스템에 더 큰 확장성 및 융통성을 통합하기 위해 거의 무제한의 링크된 장치에 대한 새로운 플래시 장치 캐스케이드 방식으로부터 이익을 얻을 수 있다. 직렬 인터페이스는 더 높은 클록 속도, 더 우수한 신호 무결성(integrity) 및 더 낮은 전력 소모라는 신호 성능 개선을 제공할 것이다. 직렬 인터페이스는 또한 패키지 구성을 변경하지 않고도 무제한으로 확장 가능한 I/O 폭을 제공한다. 더나아가 본 발명에 따른 메모리 장치의 1-측 패드 구조는 더 소수의 I/O를 가지며 칩 패키지 크기를 크게 감소시킨다.

[0081] 도 13b는 도 15a에 예시된 다수의 메모리 장치(1500)를 사용하는 데이지-체인 캐스케이드 구성에서 장치 연결의

시스템 구현에 관한 다른 예를 도시한다. 도 15a 및 도 15b에 대해 전술한 바와 같이, 메모리 장치는 단일 직렬 입력 포트(SIP), 단일 직렬 출력 포트(SOP), 한 쌍의 입력 인에이블(IPE) 및 출력 인에이블(OPE) 포트, 및 그에 대응하는 한 쌍의 입력 인에이블 반향(IPEQ) 및 출력 인에이블 반향(OPEQ) 포트를 포함한다. 이 캐스케이드 구성에서, 직렬 클록 출력 포트(SCLKO)가 모든 장치에 추가된다. 아울러, 직렬 클록 입력 포트 이름은 직렬 클록 출력 포트(SCLKO)와 구별하기 위해 SCLKI로 변경된다. 위상 동기 루프(PLL)나 디지털-위상 동기 루프(DLL) 회로와 같은 추가적인 회로는 SCLKI와 SCLKO 신호 사이의 임의의 위상 차이를 매칭(즉, 동기화)시키기 위해 모든 장치에서 사용될 수 있다.

- [0082] 플래시 코어 구조 구현을 위한 캐스케이딩된 메모리 장치의 일부 동작의 예가 아래의 표 3에 기재되어 있다. 표 3은 타겟 장치 어드레스(TDA), 가능한 OP(동작) 코드, 및 열 어드레스, 행/뱅크 어드레스 및 입력 데이터의 대응하는 상태를 나열한다.

표 3

| 동작                | 타겟 장치 어드레스 (1바이트) | OP 코드 (1바이트) | 열 어드레스 (2바이트) | 행/뱅크 어드레스(3바이트) | 입력 데이터 (1바이트에서 2112바이트까지) |

|-------------------|-------------------|--------------|---------------|-----------------|---------------------------|

| 페이지 판독            | tda               | 00h          | 유효            | 유효              | -                         |

| 랜덤 데이터 판독         | tda               | 05h          | 유효            | -               | -                         |

| 복사를 위한 페이지 판독     | tda               | 35h          | -             | 유효              | -                         |

| 복사를 위한 타겟 어드레스 입력 | tda               | 8Fh          | -             | 유효              | -                         |

| 직렬 데이터 입력         | tda               | 80h          | 유효            | 유효              | 유효                        |

| 랜덤 데이터 입력         | tda               | 85h          | 유효            | -               | 유효                        |

| 페이지 프로그램          | tda               | 10h          | -             | -               | -                         |

| 블록 소거             | tda               | 60h          | -             | 유효              | -                         |

| 판독 상태             | tda               | 70h          | -             | -               | -                         |

| 판독 ID             | tda               | 90h          | -             | -               | -                         |

| 기록 구성 레지스터        | tda               | A0h          | -             | -               | 유효(1바이트)                  |

| 기록 DN 기입          | 00h               | B0h          | -             | -               | -                         |

| 리셋                | tda               | FFh          | -             | -               | -                         |

| 뱅크 선택             | tda               | 20h          | -             | 유효(뱅크)          | -                         |

- [0084] 표 3: 명령 세트

- [0085] 본 발명의 일부 실시예에서, 도 13a의 시스템(1300)에서나, 도 13b의 시스템(1310)에서의 각 장치는 직렬 입력 데이터에서 타겟 장치 어드레스(tda)로서 사용될 수 있는 고유한 장치 식별자를 보유할 수 있다. 직렬 입력 데이터를 수신할 때, 플래시 메모리 장치는 직렬 입력 데이터에서 타겟 장치 어드레스 필드를 분석하고, 타겟 장치 어드레스를 장치의 고유한 장치 식별 번호와 상관시킴으로써 이 장치가 타겟 장치인지를 판정한다.

- [0086] 표 4는 도 13a 및 도 13b와 연계하여 기술된 시스템을 포함하는 본 발명의 실시예에 따른 입력 데이터스트림의 바람직한 입력 시퀀스를 도시한다. 명령, 어드레스 및 데이터는 최상위 비트로부터 시작해서 메모리 장치(1500) 내외로 직렬로 시프트된다. 입력 포트 인에이블(IPE: Input Port Enable)이 높은 상태(HIGH)인 동안에, 직렬 입력 신호(SIP)는 직렬 클록(SCLK)의 상승 에지에서 샘플링된다. 명령 시퀀스는 1-바이트 타겟 장치 어드레스 ("tda")와 1-바이트 동작 코드(교환 가능하게는 명령 코드(표 3에서 "cmd")로도 지칭됨)로 시작한다. 최상위 비트에서 1-바이트 타겟 장치 어드레스를 갖는 직렬 입력 신호에서부터 시작함으로써, 장치는 수신된 임의의 추가 입력 데이터를 처리하기 전에 타겟 장치 어드레스 필드를 분석할 수 있다. 만약 메모리 장치가 타겟 장치가 아니라면, 처리하기 전에 직렬 입력 데이터를 다른 장치에 전송할 수 있으며, 그에 따라 추가 처리 시간 및 차원을 절약할 수 있다.

표 4

[0087]

| 동작                       | 1 <sup>st</sup><br>바이트 | 2 <sup>nd</sup><br>바이트 | 3 <sup>rd</sup><br>바이<br>트 | 4 <sup>th</sup><br>바이<br>트 | 5 <sup>th</sup><br>바이<br>트 | 6 <sup>th</sup><br>바이<br>트 | 7 <sup>th</sup><br>바이<br>트 | 8 <sup>th</sup><br>바이<br>트 | .. | 2116 <sup>th</sup><br>바이트 | .. | 2119 <sup>th</sup><br>바이트 |

|--------------------------|------------------------|------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----|---------------------------|----|---------------------------|

| 페이지 판독                   | tda                    | cmd                    | ca                         | ca                         | ra                         | ra                         | ra                         | -                          | -  | -                         | -  | -                         |

| 랜덤 데이터<br>판독             | tda                    | cmd                    | ca                         | ca                         | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

| 복사를 위한<br>페이지 판독         | tda                    | cmd                    | ra                         | ra                         | ra                         | -                          | -                          | -                          | -  | -                         | -  | -                         |

| 복사를 위한<br>타겟 어드레<br>스 입력 | tda                    | cmd                    | ra                         | ra                         | ra                         | -                          | -                          | -                          | -  | -                         | -  | -                         |

| 직렬 데이터<br>입력             | tda                    | cmd                    | ca                         | ca                         | ra                         | ra                         | ra                         | data                       | .. | data                      | .. | data                      |

| 랜덤 데이터<br>입력             | tda                    | cmd                    | ca                         | ca                         | data                       | data                       | data                       | data                       | .. | data                      | -  | -                         |

| 페이지 프로<br>그램             | tda                    | cmd                    | -                          | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

| 블록 소거                    | tda                    | cmd                    | ra                         | ra                         | ra                         | -                          | -                          | -                          | -  | -                         | -  | -                         |

| 판독 상태                    | tda                    | cmd                    | -                          | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

| 판독 ID                    | tda                    | cmd                    | -                          | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

| 기록 구성 레<br>지스터           | tda                    | cmd                    | data                       | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

| 기록 DN 기입                 | tda                    | cmd                    | -                          | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

| 리셋                       | tda                    | cmd                    | -                          | -                          | -                          | -                          | -                          | -                          | -  | -                         | -  | -                         |

[0088]

표 4: 바이트 모드에서의 입력 시퀀스

[0089]

1-바이트 tda는 장치로 시프트되며, 그 다음에 1-바이트 cmd 코드가 온다. 최상위 비트(MSB)는 SIP 상에서 시작하며, 각 비트는 직렬 클록(SCLK)의 상승 에지에서 래치된다. 명령에 따라, 1-바이트 명령 코드 다음에는 열 어드레스 바이트, 행 어드레스 바이트, 뱅크 어드레스 바이트, 데이터 바이트 및/또는 이들의 조합이 오거나 아무 것도 오지 않는다.

[0090]

본 발명의 실시예에서, 플래시 장치상의 신호 버스는 완전히 다중화된다. 명령, 어드레스 및 데이터 입/출력은 동일한 핀을 공유할 수 있다. 예컨대, 명령 시퀀스는 통상 1-바이트 타겟 장치 어드레스 래치 사이클, 1-바이트 명령 래치 사이클, 어드레스 래치 사이클(예컨대, 열 어드레스를 위한 2-바이트 및 행 어드레스를 위한 3-바이트) 및 필요한 경우 1 바이트 이상(2,112 바이트까지) 데이터 입력 래치 사이클로 구성된다. 명령 지시의 모든 세트 다음에는, IPE가 높은 상태에서 낮은 상태로 전이한 후 두 개의 추가 클록 사이클이 온다. 데이터-체인 캐스케이딩된 구성의 경우, 낮은 상태로의 IPE 전이 후 클록 사이클 지연은 그러한 구성에서 캐스케이딩된 수에 의존할 수 있다. 본 발명의 실시예에서, 직렬 입력 시퀀스는 "바이트 단위"이며, 이것은 IPE 및 SIP가 8-클록 사이클 단위에 대해 유효해야 함을 의미한다. 만약 IPE가 완전한 바이트(즉, 8 클록 사이클)의 완성 이전에 높은 상태에서 낮은 상태로 전이한다면, 대응하는 명령 및/또는 어드레스 시퀀스는 장치에 의해 무시될 것이다. 데이터 입력 시퀀스의 경우에, 입력 데이터의 마지막 불완전 바이트는 무시될 것이지만, 입력 데이터의 이전 완전 바이트(들)는 유효할 것이다.

[0091]

도 16a, 16B, 17A 및 17B는 본 발명의 메모리 장치에서 직렬 데이터의 입력 및 출력 래치 타이밍에 관한 타이밍 도의 예를 예시한다.

[0092]

도 16a는 본 발명의 원리에 부합하는 기본적인 입력 래치 타이밍을 예시한다. 직렬 입력 포트(SIP)에서 데이터를 수신할 때, TDA/명령/어드레스/데이터-입력이 SIP 포트를 거쳐서 주장되고, CS#이 낮은 상태이고 IPE가 높은 상태일 때 SCLK의 상승 에지에서 얻어진다. 도 16b는 바이트 모드에서 입력 시퀀스를 상세하게 예시한 클록 도이다. 입력 데이터는 장치 내부로 시프트되어야 하고, 최상위 비트(MSB)가 먼저 SIP 상에 시프트되며, 각 비트는 SCLK의 상승 에지에서 래치되어야 한다.

[0093]

도 17a는 본 발명의 원리에 부합하는 기본적인 출력 래치 타이밍을 예시한다. 장치로부터 직렬 출력 포트(SOP)를 거쳐서 데이터를 전달할 경우, 데이터는, CS#이 낮은 상태이고 OPE가 높은 상태일 때 SCLK의 상승 에지 상에

서 SOP 포트를 거쳐서 주장된다. SOP 상의 직렬 데이터 출력은 SCLK의 상승 에지에서 외부로 시프트된다. 도 17b는 바이트 모드에서 출력 시퀀스를 상세하게 예시한 클록도이다. 출력 데이터는 장치로부터 시프트되고, 최상위 비트(MSB)가 먼저 SOP 상에 시프트되며, 각 비트는 SCLK의 상승 에지에서 동기화된다.

[0094] 전술한 바와 같이, 메모리 장치는 이중-뱅크 메모리일 수 있으며, 여기서 각 뱅크는 임의의 직렬 링크에 의해 액세스될 수 있다. 대안적으로, 본 발명의 다른 실시예에서, 메모리 장치는 단일 메모리 뱅크와 단일 직렬 인터페이스를 포함할 수 있다. 메모리 장치의 직렬 인터페이스는, 풍부한 특성의 동작(feature-rich operation)을 지원하면서도, 종래의 병렬 인터페이스 방식에 비해 데이터 처리량을 크게 개선한다. 예컨대, 프로그램 동작은 (2K+64) 바이트 페이지 상에서 200 $\mu$ s 동안 실행될 수 있고, 소거 동작은 (128K+4K) 바이트 블록 상에서 1.5ms 동안 실행될 수 있다. 온-칩 기록 제어기가 펄스 반복(사용되는 경우)을 포함하는 모든 프로그램 및 소거 기능과, 데이터의 내부 겹침 및 마지닝(margining)을 자동화하는데 사용될 수 있다. 기록-겹침 시스템에서, 실시간 매핑-아웃 알고리즘을 구비한 ECC(Error Correcting Code)가 메모리 장치에서 100K 프로그램/소거 사이클의 확장된 신뢰도를 개선하는데 사용될 수 있다.

[0095] 본 발명의 여러 양상의 유용성은 당업자에게 분명함에 틀림없다. 본 명세서에서 임의의 예 및 모든 예나 예시적인 표현(예컨대 "와 같은")의 사용은 단지 발명을 더 예시하기 위한 것이며, 달리 청구되지 않는다면 발명의 범주를 제한하지 않는다. 명세서의 어떠한 표현도 청구되지 않은 어떠한 요소를 발명의 실행에 필요한 것으로 지적하는 것으로 해석되지 않아야 한다.

[0096] 본 발명은 본 발명의 바람직한 및 예시적인 실시예 측면에서 종종 기재되었다. 본 개시물을 살펴봄으로써 당업자에게는 첨부된 청구항의 범주와 사상 내에서 다른 실시예, 변경 및 변형이 있을 것이다.

## 도면

### 도면1a

### 도면1b

## 도면1c

## 도면2a

## 도면2b

## 도면2c

도면2d

도면2e

### 도면3a

## 도면3b

## 도면4

### 도면5a

## 도면5b

## 도면6a

## 도면6b

## 도면7

### 도면8a

## 도면8b

## 도면8c

## 도면9

## 도면10

## 도면11

1100 ↗

도면12

### 도면13a

도면13b

1310

### 도면14

도면15a

도면15b

[직렬 링크 인터페이스 (직렬회기 &amp; 비직렬회기)]

### 도면16a

### 도면16b

## 바이트 모드에서의 기본적인 입력 시퀀스

도면17a

도면17b

바이트 모드에서의 기본적인 출력 시퀀스