(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5567794号

(P5567794)

(45) 発行日 平成26年8月6日(2014.8.6)

(24) 登録日 平成26年6月27日(2014.6.27)

(51) Int.Cl.

F 1

|        |        |           |

|--------|--------|-----------|

| HO 1 L | 27/12  | (2006.01) |

| HO 1 L | 21/02  | (2006.01) |

| HO 1 L | 21/322 | (2006.01) |

| HO 1 L | 21/20  | (2006.01) |

|        |        |

|--------|--------|

| HO 1 L | 27/12  |

| HO 1 L | 21/322 |

| HO 1 L | 21/20  |

B

Z

請求項の数 9 (全 39 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2009-149861 (P2009-149861) |

| (22) 出願日     | 平成21年6月24日 (2009.6.24)       |

| (65) 公開番号    | 特開2010-34535 (P2010-34535A)  |

| (43) 公開日     | 平成22年2月12日 (2010.2.12)       |

| 審査請求日        | 平成24年6月13日 (2012.6.13)       |

| (31) 優先権主張番号 | 特願2008-167618 (P2008-167618) |

| (32) 優先日     | 平成20年6月26日 (2008.6.26)       |

| (33) 優先権主張国  | 日本国 (JP)                     |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (74) 代理人  | 100103159<br>弁理士 加茂 裕邦                         |

| (72) 発明者  | 笛川 慎也<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 倉田 求<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

審査官 綿引 隆

最終頁に続く

(54) 【発明の名称】 S O I 基板の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

単結晶半導体基板の表面に絶縁膜を形成し、

前記絶縁膜を介して前記単結晶半導体基板にイオンビームを照射することにより、前記単結晶半導体基板中に脆化領域を形成し、

前記単結晶半導体基板の前記脆化領域が形成された側の前記絶縁膜と支持基板の一方の面とを貼り合わせ、

熱処理を行うことにより、前記脆化領域において前記単結晶半導体基板を分離して、単結晶半導体層が貼り合わされた前記支持基板と前記単結晶半導体基板の一部とに分離し、

前記単結晶半導体層に対してレーザ光を照射して、前記単結晶半導体層の欠陥または凹凸を低減し、

前記単結晶半導体層の表面をエッチングし、

前記単結晶半導体層の表面に対して O H 遊離基を含むプラズマ処理を行い、前記単結晶半導体層の欠陥をさらに低減することを特徴とする S O I 基板の作製方法。

## 【請求項 2】

単結晶半導体基板の表面に絶縁膜を形成し、

前記絶縁膜を介して前記単結晶半導体基板にイオンビームを照射することにより、前記単結晶半導体基板中に脆化領域を形成し、

前記単結晶半導体基板の前記脆化領域が形成された側の前記絶縁膜と支持基板の一方の面とを貼り合わせ、

10

20

熱処理を行うことにより、前記脆化領域において前記単結晶半導体基板を分離して、単結晶半導体層が貼り合わされた前記支持基板と前記単結晶半導体基板の一部とに分離し、

前記単結晶半導体層に対してレーザ光を照射して、前記単結晶半導体層の欠陥または凹凸を低減し、

前記単結晶半導体層の表面をエッチングし、

前記単結晶半導体層の表面に対してOH遊離基を含むプラズマ処理を行い、前記単結晶半導体層の欠陥をさらに低減し、

前記単結晶半導体層に熱処理を行うことを特徴とするSOI基板の作製方法。

#### 【請求項3】

単結晶半導体基板の表面に絶縁膜を形成し、

10

前記絶縁膜を介して前記単結晶半導体基板にイオンビームを照射することにより、前記単結晶半導体基板中に脆化領域を形成し、

前記単結晶半導体基板の前記脆化領域が形成された側の前記絶縁膜と支持基板の一方の面とを貼り合わせ、

熱処理を行うことにより、前記脆化領域において前記単結晶半導体基板を分離して、単結晶半導体層が貼り合わされた前記支持基板と前記単結晶半導体基板の一部とに分離し、

前記単結晶半導体層に対してレーザ光を照射して、前記単結晶半導体層の欠陥または凹凸を低減し、

前記単結晶半導体層の表面をエッチングし、

前記単結晶半導体層に熱処理を行い、

20

前記単結晶半導体層の表面に対してOH遊離基を含むプラズマ処理を行い、前記単結晶半導体層の欠陥をさらに低減することを特徴とするSOI基板の作製方法。

#### 【請求項4】

単結晶半導体基板の表面に第1の絶縁膜を形成し、

前記第1の絶縁膜を介して前記単結晶半導体基板にイオンビームを照射することにより、前記単結晶半導体基板中に脆化領域を形成し、

前記第1の絶縁膜上に第2の絶縁膜を形成し、

前記第1の絶縁膜及び前記第2の絶縁膜を間に挟んで、前記単結晶半導体基板と向かい合うように、支持基板の一方の面と貼り合わせ、

熱処理を行うことにより、前記脆化領域において前記単結晶半導体基板を分離して、単結晶半導体層が貼り合わされた前記支持基板と前記単結晶半導体基板の一部とに分離し、

前記単結晶半導体層に対してレーザ光を照射して、前記単結晶半導体層の欠陥または凹凸を低減し、

前記単結晶半導体層の表面をエッチングし、

前記単結晶半導体層の表面に対してOH遊離基を含むプラズマ処理を行い、前記単結晶半導体層の欠陥をさらに低減することを特徴とするSOI基板の作製方法。

#### 【請求項5】

単結晶半導体基板表面に第1の絶縁膜を形成し、

前記第1の絶縁膜を介して前記単結晶半導体基板にイオンビームを照射することにより、前記単結晶半導体基板中に脆化領域を形成し、

40

支持基板に対してバイアス電圧を印加してプラズマ処理を行うことにより、前記支持基板を平坦化し、

平坦化された前記支持基板上にスパッタリング法を用いてアルミニウムを含む第2の絶縁膜を形成し、

前記第1の絶縁膜及び前記第2の絶縁膜を間に挟んで、前記単結晶半導体基板と向かい合うように前記支持基板の一方の面と貼り合わせ、

熱処理を行うことにより、前記脆化領域において前記単結晶半導体基板を分離して、単結晶半導体層が貼り合わされた前記支持基板と前記単結晶半導体基板の一部とに分離し、

前記単結晶半導体層に対してレーザ光を照射して、前記単結晶半導体層の欠陥または凹凸を低減し、

50

前記単結晶半導体層の表面をエッティングし、

前記単結晶半導体層の表面に対してO H遊離基を含むプラズマ処理を行い、前記単結晶半導体層の欠陥をさらに低減することを特徴とするSOI基板の作製方法。

**【請求項6】**

請求項1乃至請求項5のいずれか一において、

前記O H遊離基を含むプラズマ処理は、前記単結晶半導体層が貼り合わされた前記支持基板を加熱しながら行うことを特徴とするSOI基板の作製方法。

**【請求項7】**

請求項6において、

前記加熱された前記支持基板の温度は、100以上280以下であることを特徴とするSOI基板の作製方法。 10

**【請求項8】**

請求項6において、

前記加熱された前記支持基板の温度は、220以上280以下であることを特徴とするSOI基板の作製方法。

**【請求項9】**

請求項1乃至請求項8のいずれか一において、

前記O H遊離基を含むプラズマ処理は、プラズマ発生室と反応室が分離したプラズマ処理装置で行うことを特徴とするSOI基板の作製方法。

20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、SOI(Silicon on Insulator)基板及びその作製方法、並びに当該SOI基板を用いた半導体装置及びその作製方法に関する。

**【背景技術】**

**【0002】**

近年、バルク状のシリコンウエハに代わり、絶縁表面に薄い単結晶半導体膜が存在するSOI(Silicon on Insulator)基板を使った集積回路が開発されている。SOI基板を使うことで、トランジスタのドレインと基板間における寄生容量が低減されるため、SOI基板は半導体集積回路の性能を向上させるものとして注目されている。 30

**【0003】**

SOI基板を製造する方法の1つに、スマートカット(登録商標)法が知られている。スマートカット法によるSOI基板の作製方法の概要を以下に説明する。まず、シリコンウエハにイオン注入法を用いて水素イオンを注入することにより表面から所定の深さに脆化領域を形成する。次に、酸化シリコン膜を介して、水素イオンが注入されたシリコンウエハを別のシリコンウエハに接着させる。その後、熱処理を行うことにより、脆化領域において、水素イオンを注入したシリコンウエハが薄膜状に分離し、シリコンウエハ上に単結晶シリコン層を形成することができる。また、スマートカット法は水素イオン注入剥離法と呼ぶこともある。 40

**【0004】**

また、このようなスマートカット法を用いて単結晶シリコン層をガラスからなるベース基板上に形成する方法が提案されている(例えば、特許文献1参照)。ガラス基板はシリコンウエハよりも大面積化が可能であり且つ安価な基板であるため、主に、液晶表示装置等の製造に用いられている。ガラス基板をベース基板として用いることにより、大面積で安価なSOI基板を作製することが可能となる。

**【先行技術文献】**

**【特許文献】**

**【0005】**

40

50

【特許文献 1】特開 2004 - 87606 号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、ガラス基板に接着された薄い単結晶シリコン層は、水素イオンの注入及び脆化領域においての分離により、内部には結晶欠陥が残存し、表面には脆化領域やダメージが残存するなど表面の平坦性が劣化した状態となっている。従来、シリコンウエハに接着された単結晶シリコン層の結晶性の回復には、1000℃以上の温度で熱処理を行うことで結晶性の回復を行っていたが、歪み点が700℃以下のガラス基板に接着された単結晶シリコン層の結晶性の回復には、このような高温のプロセスを用いることができない。

10

【0007】

また、高性能な半導体素子を作製するには、単結晶シリコン層表面の凹凸を抑えることが要求されている。SOI基板からトランジスタを作製する場合、半導体層上にゲート絶縁膜を介してゲート電極が形成されるため、半導体層表面の凹凸が大きいと、絶縁耐圧性の高いゲート絶縁膜を形成することが困難となる。また、絶縁耐圧性を高めるために薄いゲート絶縁膜が必要となるが、半導体層表面の凹凸が大きいと、ゲート絶縁膜との界面準位密度が高くなるなどの原因により、電界効果移動度が低下し、しきい値電圧値の大きさが増加するなど、半導体素子の性能が低下する。

【0008】

本発明の一態様は、上述した問題に鑑みてなされたものであり、単結晶半導体層の平坦性を高め、結晶欠陥を減少させることのできる技術的手段を提供することを目的の一とする。また、耐熱性の低い基板が単結晶半導体層の支持基板に用いられたとしても、単結晶半導体層の平坦性を高め、結晶欠陥を減少させることのできる技術的手段を提供することを目的の一とする。また、結晶性及び平坦性の高い単結晶半導体層を歩留まり良く作製することのできる技術的手段を提供することを目的の一とする。

20

【課題を解決するための手段】

【0009】

上記目的を達成するため、本発明の一態様では表面に絶縁膜が形成され、表面から所定の深さの領域に脆化領域が形成された単結晶半導体基板と、支持基板とを絶縁膜を介して貼り合わせた後、熱処理を行い脆化領域において分離することにより、支持基板上に絶縁膜を介して単結晶半導体層を形成し、単結晶半導体層にレーザ光を照射し、前記単結晶半導体層の表面をエッチングし、前記単結晶半導体層の表面にプラズマ処理を行うことを特徴とするSOI基板の作製方法を提供する。

30

【0010】

プラズマ処理は、単結晶半導体層の表面を、OH遊離基を含むプラズマに曝すことによって行なうことが好ましい。OH遊離基を含むプラズマに曝すことによって、欠陥や歪み、ダングリングボンドなどにOH遊離基が作用して、OH遊離基でダングリングボンドを終端化させることができる。その結果、単結晶半導体層の結晶欠陥を減少させることができる。

40

【0011】

本発明の一態様は、単結晶半導体基板の表面に絶縁膜を形成し、絶縁膜を介して単結晶半導体基板にイオンビームを照射することにより、単結晶半導体基板の一方の面から所定の深さの領域に脆化領域を形成し、単結晶半導体基板の脆化領域が形成された側の絶縁膜と支持基板の一方の面とを貼り合わせ、熱処理を行うことにより、前記脆化領域において前記単結晶半導体基板を分離して、単結晶半導体層が貼り合わされた前記支持基板と単結晶半導体基板の一部とに分離し、単結晶半導体層に対してレーザ光を照射し、単結晶半導体層の表面をエッチングし、単結晶半導体層の表面にプラズマ処理を行い、単結晶半導体層に熱処理を行うことを特徴としている。

【0012】

また、本発明の一態様は、単結晶半導体基板の表面に絶縁膜を形成し、絶縁膜を介して单

50

結晶半導体基板にイオンビームを照射することにより、単結晶半導体基板の一方の面から所定の深さの領域に脆化領域を形成し、単結晶半導体基板の脆化領域が形成された側の絶縁膜と支持基板の一方の面とを貼り合わせ、熱処理を行うことにより、脆化領域において単結晶半導体基板を分離して、単結晶半導体層が貼り合わされた支持基板と単結晶半導体基板の一部とに分離し、単結晶半導体層に対してレーザ光を照射し、単結晶半導体層の表面をエッティングし、単結晶半導体層に熱処理を行い、単結晶半導体層の表面にプラズマ処理を行うことを特徴としている。

#### 【0013】

単結晶半導体層の表面に行うプラズマ処理は、支持基板を加熱しながら行うことが好ましい。支持基板の温度は、100以上280以下、好ましくは220以上280以下とするとよい。

10

#### 【0014】

単結晶半導体層の表面に行うプラズマ処理は、プラズマ発生室と反応室が分離したプラズマ処理装置で行うことが好ましい。

#### 【0015】

本明細書における「単結晶」とは、結晶面、又は結晶軸が揃っている結晶であり、それを構成している原子又は分子が空間的に規則正しい配列になっているものをいう。もっとも、単結晶は原子が規則正しく配列することによって構成されるものであるが、一部にこの配列の乱れがある格子欠陥を含むもの、意図的に非意図的に格子歪みを有するものも含まれる。

20

#### 【0016】

また、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路及び電子機器は全て半導体装置に含まれる。

#### 【0017】

また、本明細書中において表示装置とは、発光装置や液晶表示装置を含む。発光装置は発光素子を含み、液晶表示装置は液晶素子を含む。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL（Electro Luminescence）素子、有機EL素子等が含まれる。

#### 【発明の効果】

#### 【0018】

本発明の一態様を適用することで、耐熱性の低い支持基板を用いた場合であっても、十分に平坦性を高め、結晶欠陥を減少させることができる。また、このようなSOI基板を用いて、優れた特性の半導体装置を作製することができる。

30

#### 【図面の簡単な説明】

#### 【0019】

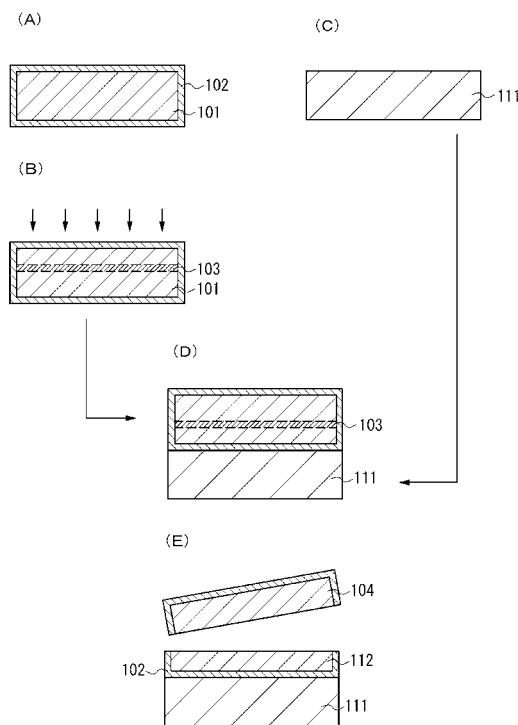

【図1】実施の形態1に係るSOI基板の作製方法を説明する図。

【図2】実施の形態1に係るSOI基板の作製方法を説明する図。

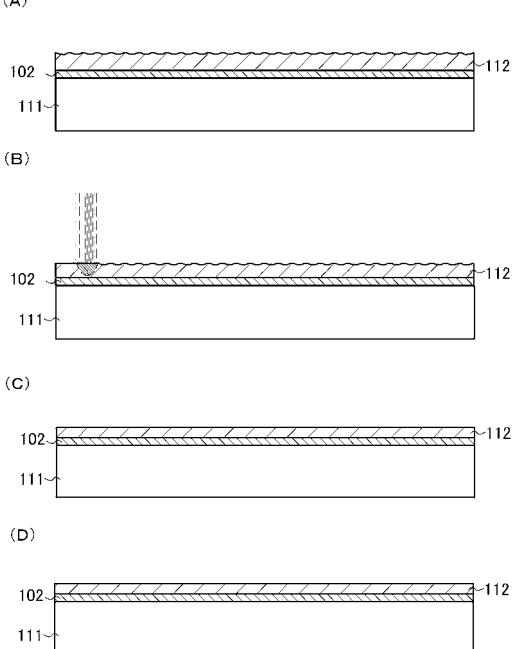

【図3】プラズマ処理装置の一例を示す概要構成図。

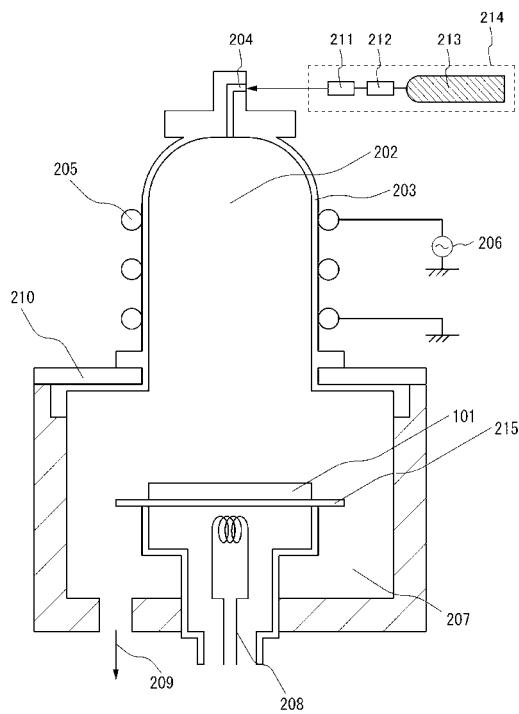

【図4】実施の形態2に係るSOI基板の構成を説明する図。

【図5】実施の形態2に係るSOI基板の構成を説明する図。

40

【図6】実施の形態2に係るSOI基板の構成を説明する図。

【図7】実施の形態3に係る半導体装置の作製方法を説明する図。

【図8】実施の形態3に係る半導体装置の作製方法を説明する図。

【図9】SOI基板により得られるマイクロプロセッサの構成を示すブロック図。

【図10】SOI基板により得られるRFCPUの構成を示すブロック図。

【図11】(A)液晶表示装置の画素の平面図。(B)J-K切断線による図11(A)の断面図。

【図12】(A)エレクトロルミネンス表示装置の画素の平面図。(B)J-K切断線による図12(A)の断面図。

【図13】本発明の一態様が適用される電子機器を示す図。

50

【図14】本発明の一態様が適用される携帯電話を示す図。

【図15】実施例1に係るSOI基板の構成を説明する図。

【図16】単結晶シリコン層のライフタイム評価測定結果を示すグラフ。

【図17】実施例2に係る半導体装置の構成を説明する図。

【図18】実施例2に係る半導体装置の電流電圧特性を示す図。

【発明を実施するための形態】

【0020】

以下に、本発明の実施の形態及び実施例を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を変更し得ることは当業者であれば容易に理解される。従って、本実施の形態及び実施例の記載内容に限定して解釈されるものではない。なお、実施の形態及び実施例を説明するための全図において、同一部分の又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。10

【0021】

(実施の形態1)

本実施の形態では、絶縁膜を介して単結晶半導体層が支持基板に固定されているSOI基板の作製方法について説明する。

【0022】

まず、単結晶半導体基板101を準備する。単結晶半導体基板101は、所望の大きさ、形状に加工されている。単結晶半導体基板101は、例えば、単結晶シリコン基板、ゲルマニウム基板、ガリウムヒ素やインジウムリン等の化合物半導体基板等が挙げられる。市販のシリコン基板としては、直径5インチ(125mm)、直径6インチ(150mm)、直径8インチ(200mm)、直径12インチ(300mm)サイズの円形のものが代表的である。また、直径18インチ(450mm)サイズの円形のものも用いることができる。なお、形状は円形に限らず矩形状に加工したシリコン基板を用いることも可能である。以下の説明では、単結晶半導体基板101として、単結晶シリコン基板を用いる場合について説明する。20

【0023】

単結晶半導体基板101上に絶縁膜102を形成する(図1(A))。絶縁膜102は、単層構造又は2層以上の積層構造とすることができます。絶縁膜102を構成する膜には、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、酸化ゲルマニウム膜、窒化ゲルマニウム膜、酸化窒化ゲルマニウム膜、窒化酸化ゲルマニウム膜などのシリコン又はゲルマニウムを組成に含む膜を用いることができる。また、酸化アルミニウム、酸化タンタル、酸化ハフニウムなどの金属の酸化物でなる絶縁膜、窒化アルミニウムなどの金属の窒化物でなる絶縁膜、酸化窒化アルミニウム膜などの金属の酸化窒化物でなる絶縁膜、窒化酸化アルミニウム膜などの金属の窒化酸化物でなる絶縁膜を用いることもできる。30

【0024】

絶縁膜102を構成する絶縁膜は、化学気相法(CVD; Chemical Vapour Deposition)、スパッタリング法、原子エピタキシ(ALE)法、単結晶半導体基板101を酸化する、又は窒化するなどの方法により形成することができる。CVD法は、減圧CVD法、熱CVD法、プラズマ励起CVD法(以下、PECVD法という)などがある。PECVD法は、350℃以下の低温処理であり、また他のCVD法よりも成膜速度が大きいので好ましい。40

【0025】

絶縁膜102には、ナトリウムが単結晶半導体層112に侵入することを防止するためのバリア層となる絶縁膜を少なくとも1層含むことが好ましい。バリア層は、1層でも2層以上でもよい。支持基板111にアルカリ金属若しくはアルカリ土類金属などの半導体装置の信頼性を低下させる不純物を含むような基板(代表的には、ガラス基板)を用いた場合、支持基板111が加熱されると、このような不純物が支持基板111から単結晶半導50

体層 112 に拡散するおそれがある。よって、バリア層を形成することで、このようなアルカリ金属若しくはアルカリ土類金属などの半導体装置の信頼性を低下させる不純物が単結晶半導体層 112 に移動することを防止することができる。バリア層として機能する膜には、窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、又は窒化酸化アルミニウム膜などがある。絶縁膜 102 として 2 層以上の積層構造にする場合には、このような膜を絶縁膜 102 に含ませることで、絶縁膜 102 をバリア層として機能させることができる。

#### 【 0026 】

絶縁膜 102 を単層構造とする場合は、バリア層として機能する膜で絶縁膜 102 を形成することが好ましい。この場合、厚さ 5 nm 以上 200 nm 以下の窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、又は窒化酸化アルミニウム膜で、単層構造の絶縁膜 102 を形成することができる。10

#### 【 0027 】

また、絶縁膜 102 を単層構造とする場合、単結晶半導体基板 101 に酸化処理を行い、単結晶半導体基板 101 の表面に酸化膜を形成したものを用いることができる。この酸化膜を形成するための熱酸化処理は、ドライ酸化で行うこともできるが、酸化雰囲気中にハロゲン元素を含むガスを添加することが好ましい。ハロゲン元素を含んだ酸化膜を絶縁膜 102 として形成することができる。ハロゲン元素を含むガスとして、HCl、HF、NF<sub>3</sub>、HBr、Cl、ClF、BCl<sub>3</sub>、F、Br<sub>2</sub>、DCE ( dichloroethylene ) などから選ばれた一種類又は複数種類のガスを用いることができる。また、ジクロロエチレンとして、トランス - 1, 2 - ジクロロエチレンを用いる場合は、トランス - 1, 2 - ジクロロエチレンは熱分解する温度が低いため、熱酸化処理の温度を低温で行いたい場合に有効となる。なお、トランス - 1, 2 - ジクロロエチレンにかえて、シス - 1, 2 - ジクロロエチレン、1, 1 - ジクロロエチレンや、これらの中から二種類以上のガスの混合ガスを用いてもよい。20

#### 【 0028 】

本実施の形態では、例えば、酸素に対し HCl を 0.5 ~ 10 体積 % ( 好ましくは 3 体積 % ) の割合で含む雰囲気中で、700 以上の温度で熱処理を行う。950 以上 1100 以下の加熱温度で熱酸化を行うとよい。処理時間は、0.1 ~ 6 時間、好ましくは 0.5 ~ 1 時間とすればよい。形成される酸化膜の膜厚は、10 nm ~ 1000 nm ( 好ましくは、50 nm ~ 200 nm ) 、例えば、100 nm の膜厚とすることができます。30

#### 【 0029 】

このような温度範囲で酸化処理を行うことで、ハロゲン元素によるゲッタリング効果を得ることができる。ゲッタリング効果としては、特に、金属などの不純物を除去する効果がある。すなわち、ハロゲン元素の作用により金属などの不純物が揮発性の塩化物となって気相中へ離脱して、単結晶半導体基板 101 から除去される。また、酸化雰囲気中に含まれるハロゲン元素により、単結晶半導体基板 101 の表面の未結合手が終端されるため、酸化膜と単結晶半導体基板 101 との界面の局在準位密度が低減できる。

#### 【 0030 】

また、ハロゲン元素を含む雰囲気での熱酸化処理により、絶縁膜 102 として用いる酸化膜にハロゲン元素を含ませることができる。ハロゲン元素を  $1 \times 10^{16} / \text{cm}^3 \sim 5 \times 10^{21} / \text{cm}^3$  の濃度で含ませることにより、単結晶半導体基板 101 において、金属などの不純物を捕獲して単結晶半導体層 112 の汚染を防止する保護膜としての機能させることができる。40

#### 【 0031 】

絶縁膜 102 として用いる酸化膜にハロゲン元素を含ませるためには、フッ化物ガス又はフッ素ガスを含む PECVD 装置のチャンバーで、酸化膜を形成してもよい。このようなチャンバーに酸化膜形成用のプロセスガスを供給し、このプロセスガスを励起してプラズマを生成し、当該プラズマに含まれる活性種の化学反応により、単結晶半導体基板 101 上に酸化膜を形成する。50

**【 0 0 3 2 】**

次に、絶縁膜 102 を介して、単結晶半導体基板 101 にイオンを照射することにより、イオンを単結晶半導体基板 101 に導入し、単結晶半導体基板 101 の一方の面から所定の深さの領域に脆化領域 103 を形成する（図 1（B））。

**【 0 0 3 3 】**

脆化領域 103 が形成される深さは、イオンの加速電圧と入射角によって調節することができる。イオンの平均侵入深さとほぼ同じ深さの領域に脆化領域 103 が形成される。単結晶半導体基板 101 にイオンが導入される深さで、後の工程において単結晶半導体基板 101 から分離される単結晶半導体層 112 の厚さが決定する。脆化領域 103 が形成される深さは、10 nm 以上 500 nm 以下であり、好ましい深さの範囲は、50 nm 以上 10 200 nm 以下である。

**【 0 0 3 4 】**

イオンを単結晶半導体基板 101 に導入するには、イオンドーピング装置を用いることができる。イオンドーピング装置は、ソースガスを励起し、プラズマを生成し、プラズマ中からイオンを引き出し、質量分離せずにイオンを被処理物に導入する。イオンドーピング装置を用いることにより、単結晶半導体基板 101 に対して均一なドーピングを行うことができる。なお、質量分離装置を備えているイオンドーピング装置では、プラズマ中のイオン種を質量分離し、ある特定の質量のイオン種を被処理体に照射することができる。

**【 0 0 3 5 】**

イオンの照射の際に用いるガスとしては、水素ガス、希ガス等があるが、本実施の形態では水素ガスを用いることが好ましい。イオンドーピング法で水素ガスを用いた場合、生成するイオン種は、 $H^+$ 、 $H_2^+$ 、及び $H_3^+$ であるが、 $H_3^+$ が最も多く照射されることが好ましい。 $H_3^+$ は、 $H^+$ 、 $H_2^+$ よりもイオンの照射効率がよく、照射時間の短縮を図ることができる。また、後の工程において剥離層に亀裂が生じやすくなる。

20

**【 0 0 3 6 】**

次に、支持基板 111 を準備する（図 1（C））。支持基板 111 は、絶縁体でなる基板を用いる。具体的には、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、石英基板、セラミック基板、サファイア基板等が挙げられる。本実施の形態では、ガラス基板を用いる場合について説明する。支持基板 111 として大面積化が可能で安価なガラス基板を用いることにより、シリコンウエハを用いる場合と比較して低コスト化を図ることができる。

30

**【 0 0 3 7 】**

支持基板 111 を用いるに際し、支持基板 111 の表面をあらかじめ洗浄することが好ましい。具体的には、支持基板 111 を塩酸過酸化水素水混合溶液（H P M）、硫酸過酸化水素水混合溶液（S P M）、アンモニア過酸化水素水混合溶液（A P M）、希フッ酸（D H F）、オゾン水等を用いて超音波洗浄を行う。例えば、支持基板 111 の表面に塩酸過水を用いて超音波洗浄を行うことが好ましい。このような洗浄処理を行うことによって、支持基板 111 表面の平坦化や残存する研磨粒子を除去することができる。

**【 0 0 3 8 】**

次に、絶縁膜 102、脆化領域 103 が形成された単結晶半導体基板 101 と支持基板 111 を洗浄する。この洗浄工程は、純水中での超音波洗浄で行うことができる。超音波洗浄はメガヘルツ超音波洗浄（メガソニック洗浄）が好ましい。超音波洗浄の後、単結晶半導体基板 101 及び支持基板 111 の一方又は双方をオゾン添加水で洗浄することが好ましい。オゾン添加水で洗浄することによって、有機物の除去と、絶縁膜 102 表面及び支持基板 111 の親水性を向上させる表面活性化処理を行うことができる。また、オゾン添加水の他、酸素添加水、水素添加水、又は純水等で洗浄処理をしてもよい。このような洗浄処理をすることで、接合面を親水性にすることができる、接合面のOH基を増大させることができる。OH基の増大により水素結合による接合をより強固にすることができる。

40

**【 0 0 3 9 】**

また、絶縁膜 102 の表面及び支持基板 111 の活性化処理には、オゾン添加水による洗

50

淨の他、原子ビーム若しくはイオンビームの照射処理、プラズマ処理、若しくは、ラジカル処理で行うことができる。原子ビーム若しくはイオンビームを利用する場合は、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。このような表面処理により、400 以下の温度であっても異種材料間を接合することが容易となる。

#### 【0040】

次に、単結晶半導体基板101の表面と支持基板111の表面とを対向させ、絶縁膜102の表面と支持基板111とを密着させる(図1(D))。絶縁膜102と支持基板111とを密着させることにより、ファン・デル・ワールス力で基板同士が引き合う。次に、単結晶半導体基板101の一端の一箇所に300~15000N/cm<sup>2</sup>程度の圧力を加える。この圧力は、1000~5000N/cm<sup>2</sup>が好ましい。絶縁膜102の表面にできるSi-OHと支持基板111の表面にできるSi-OHとが圧力をかけた部分から水素結合で接着し始め、接着部分が絶縁膜102のほぼ全面に及ぶ。その結果、支持基板111に単結晶半導体基板101が接着される。この接着工程は、加熱処理を伴わず、常温で行うことができるため、ガラス基板のように耐熱温度が700 以下の低耐熱性の基板を支持基板111に用いることが可能である。

#### 【0041】

支持基板111に単結晶半導体基板101を接着させた後、支持基板111と絶縁膜102との接着界面での結着力を増加させるための加熱処理を行うことが好ましい。この処理温度は、脆化領域103に亀裂を生じさせない温度とし、200 以上450 以下の温度範囲で処理することができる。このような温度範囲で熱処理を行うことにより、脱水縮合反応が起こり、水分子が離脱して酸素原子を介した結合(Si-O-Si)となる。したがって、支持基板111と絶縁膜102との接合界面での結着力を強固にすることができます。

#### 【0042】

次に、加熱処理を行い脆化領域103において分離(劈開、分割とも記す)することにより、単結晶半導体層が接着された支持基板と単結晶半導体基板の一部とに分離する。図1(E)は、単結晶半導体基板101から、単結晶半導体層112を分離する工程を説明する図である。

#### 【0043】

加熱処理を行うことで、温度上昇によって脆化領域103に形成されている微小な空孔には、イオンドーピングで添加したH原子が気体として析出し、過剰なH原子はH<sub>2</sub>ガスとなり、微小な空孔内部の圧力が上昇する。圧力の上昇により、脆化領域103の微小な空孔に体積変化が起こって脆化領域103に亀裂が生じ、脆化領域103に単結晶半導体基板101を分離するための分離面が生じる。絶縁膜102は、支持基板111に接合しているので、支持基板111には単結晶半導体基板101から分離された単結晶半導体層112が固定される。単結晶半導体層112を単結晶半導体基板101から分離するための加熱処理の温度は、支持基板111の歪み点を超えない温度とする。

#### 【0044】

この加熱処理には、RTA(Rapid Thermal Anneal)装置、抵抗加熱炉、マイクロ波加熱装置を用いることができる。RTA装置には、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置を用いることができる。この加熱処理で、単結晶半導体層112が貼り付けられた支持基板111の温度が550 以上650 以下の範囲に上昇させることが好ましい。

#### 【0045】

このように、熱処理を行い脆化領域103において分離することにより、支持基板111上に、絶縁膜102を介して単結晶半導体層112を設けることができる(図1(E))。また、単結晶半導体層112を分離した単結晶半導体基板104を再利用することで、作製に係るコストを削減することが可能である。図1(E)に示す熱処理工程は、加熱温

10

20

30

40

50

度が 700 以下と比較的低温であるため、単結晶半導体基板 101 への熱によるダメージを抑制することができ、単結晶半導体基板 101 を再利用する場合に有効である。

#### 【0046】

以上の工程により、支持基板 111 上に絶縁膜 102 を介して単結晶半導体層 112 が設けられた SOI 基板を作製することができる。

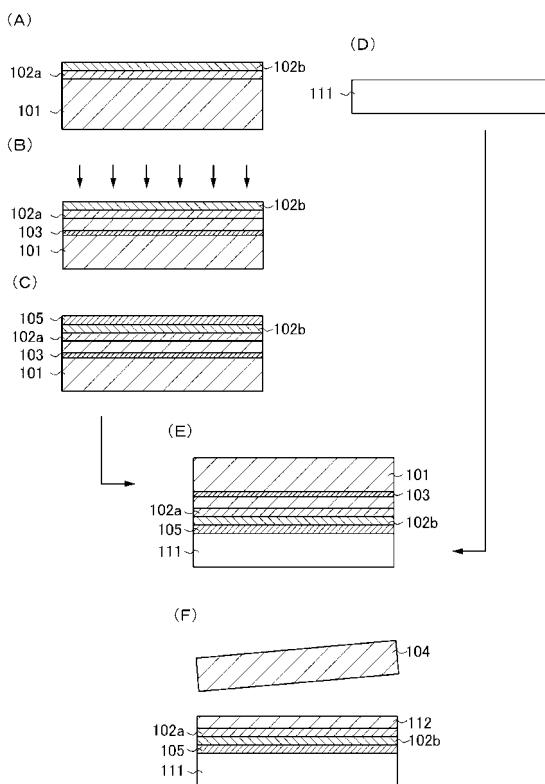

#### 【0047】

図 2 (A) に示す単結晶半導体層 112 は、脆化領域 103 の形成のためのイオン添加工程や分離工程により、内部には結晶欠陥が残存し、表面には脆化領域 103 やダメージが残存するなど表面の平坦性が劣化した状態となっている。また、単結晶半導体層 112 の分離がスムーズに行われないと、単結晶半導体層 112 の表面が荒れたり、単結晶半導体層 112 の膜厚がばらついたり、単結晶半導体層 112 に微細なクラックが生じたりといった問題が生じる。このような平坦性の損なわれた単結晶半導体層 112 の表面に薄く、且つ、高い絶縁耐圧のゲート絶縁層を形成することは困難である。また、単結晶半導体層 112 に結晶欠陥が存在する場合には、ゲート絶縁層との界面における局在準位密度が高くなるなど、トランジスタの性能及び信頼性に悪影響を与えててしまう。なお、図 2 (A)において、単結晶半導体層 112 の表面の凹凸形状は、表面が粗く、平坦性が悪いことを特徴的に示しているだけであり、実際の形状はこれに限定されない。

#### 【0048】

そこで、単結晶半導体層 112 の平坦性を高め、結晶欠陥を減少させるための処理を行う。単結晶半導体層 112 の平坦性を高め、結晶欠陥を減少させるための処理は、エッチング処理及びレーザ光の照射いずれか一方又は双方を組み合わせて行うことができる。例えば、ドライエッティング又はウェットエッティングの一方又は双方を組み合わせたエッティング処理（エッチバック処理）を行った後にレーザ光を照射するとよい。このような処理を行うことにより、単結晶半導体層 112 内部及び表面の結晶欠陥を低減し、単結晶半導体層 112 の表面を平坦化させることができる。

#### 【0049】

まず、単結晶半導体層 112 の表面に対して、エッティング処理を行うことにより、単結晶半導体層 112 の表面を除去する（図示せず）。単結晶半導体層 112 の表面を除去することにより、単結晶半導体層 112 の表面に残存する脆化領域 103 と、分離の際に生じたダメージなどを除去することができる。単結晶半導体層 112 に存在する欠陥の大きさや深さは、イオンを添加するエネルギーの大きさやドーズ量に起因するため、エッティング処理によって単結晶半導体層 112 の表面を除去する膜厚は、エッティング処理前の単結晶半導体層 112 の膜厚とその表面粗さの程度によって適宜設定すればよい。

#### 【0050】

単結晶半導体層 112 の表面に対して行うドライエッティングの方法は、例えば、反応性イオンエッティング (RIE : Reactive Ion Etching) 法、ICP (Inductively Coupled Plasma) エッティング法、ECR (Electron Cyclotron Resonance) エッティング法、平行平板型(容量結合型)エッティング法、マグネットロンプラズマエッティング法、2周波プラズマエッティング法またはヘリコン波プラズマエッティング法等を用いることができる。エッティングガスは、例えば、 $\text{Cl}_2$ 、 $\text{BCl}_3$ 、 $\text{SiCl}_4$  等の塩素系のガス、 $\text{CHF}_3$ 、 $\text{CF}_4$ 、 $\text{C}_4\text{F}_8$ 、 $\text{C}_2\text{F}_6$ 、 $\text{NF}_3$ 、弗化硫黄等のフッ素系のガス、 $\text{HBr}$  等の臭素系のガス、 $\text{He}$  や  $\text{Ar}$  や  $\text{Xe}$  などの不活性ガスを用いることによりエッティングすることが可能である。また、 $\text{O}_2$  ガス、 $\text{H}_2$  ガスを上記ガスと組み合わせてエッティングすることもできる。

#### 【0051】

単結晶半導体層 112 の表面にエッティング処理を行うことにより、単結晶半導体層 112 の表面に残存する脆化領域 103 と、分離の際に生じたダメージなどを除去することができる。また、単結晶半導体層 112 の表面に残存する脆化領域 103 と、分離の際に生じたダメージなどを除去することにより、単結晶半導体層 112 の表面粗さを低減することができる。

10

20

30

40

50

**【 0 0 5 2 】**

本実施の形態では、ドライエッチングを行う場合について説明したが、ウェットエッチングでも行うことができる。ウェットエッチングを行う場合は、エッチング液としては、水酸化テトラメチルアンモニウム (tetramethylammonium hydroxide、略称；TMAH、2.38%の水溶液) 溶液を用いることができる。

**【 0 0 5 3 】**

次に、図2(B)に示すようにエッチング処理が行われた単結晶半導体層112に対して、レーザ光を照射する。単結晶半導体層112の内部には、脆化領域103形成のためのイオン添加工程によって結晶欠陥が形成されている。また、単結晶半導体基板101から単結晶半導体層112を剥離する際の分離がスムーズに行われず、単結晶半導体層112に微細なクラックが生じている場合がある。そこで、単結晶半導体層112に対してレーザ光を照射することにより、単結晶半導体層112を溶融させることができる。単結晶半導体層112を溶融させることにより、内部に形成された結晶欠陥や微小なクラックなどを消滅させることができる。

10

**【 0 0 5 4 】**

レーザ光の照射による単結晶半導体層112の溶融は、部分溶融であることが好ましい。部分溶融状態とは、単結晶半導体層112の上部が溶融して液体となるが、下部は溶融せずに固体のままの状態であることをいう。部分溶融状態とした後に、融液を融点以下の温度にすると、単結晶半導体層112の溶融されていない固相部分(種結晶)と、溶融された液相部分(融液)との界面において、融液側の原子が種結晶に付着することにより結晶が成長していく。このようにして、融液の結晶成長を進行させることで、結晶欠陥の低減とともに表面凹凸を低減させることができる。

20

**【 0 0 5 5 】**

このように、単結晶半導体層112の結晶欠陥の低減、表面凹凸の低減を、レーザ光を用いて行うことにより、支持基板111が直接加熱されないため、支持基板111の温度上昇を抑制することができる。したがって、耐熱性の低い支持基板111を用いた場合であっても、十分に、結晶欠陥の低減、表面凹凸の低減を行うことができる。

**【 0 0 5 6 】**

また、単結晶半導体層112にレーザ光を照射した後に、単結晶半導体層112を用いて形成する素子の特性に合わせて、単結晶半導体層112を薄膜化することが好ましい。支持基板111上に接着された単結晶半導体層112の表面に、薄いゲート絶縁層を段差被覆性良く形成するには、単結晶半導体層112の膜厚は60nm以下とすることが好ましく、具体的には5nm以上60nm以下とすることが好ましい。単結晶半導体層の薄膜化には、ドライエッチング又はウェットエッチングの一方、又は双方を組み合わせたエッチング処理(エッチバック処理)を適用すればよい。例えば、単結晶半導体層がシリコン材料からなる層である場合、ドライエッチングとしてSF<sub>6</sub>とO<sub>2</sub>をプロセスガスに用いて、単結晶半導体層を薄くすることができる。

30

**【 0 0 5 7 】**

次に、レーザ光の照射で回復されなかった単結晶半導体層112の欠陥の消滅、歪みの緩和、ダメージ、ダンギングボンドを修復するために、プラズマ処理を行う(図2(C))。単結晶半導体層112に欠陥や歪み等が残存していると、素子製造時のプロセス、特に熱的なプロセス中に、より大きな欠陥、ひいては素子の特性へ悪影響を及ぼす。そのため、単結晶半導体層112の欠陥や歪み等を修復する必要がある。なお、1000以上の温度で熱処理を行うことで、単結晶半導体層112の欠陥や歪み等を回復させることができるが、耐熱性の低い支持基板に接着された単結晶半導体層112の欠陥や歪み等の回復には、このような高温のプロセスを用いることができない。

40

**【 0 0 5 8 】**

そこで、本発明の一態様では、単結晶半導体層112の欠陥の消滅や歪みの緩和などをを行うために、プラズマ処理を行う(図2(C))。プラズマ処理は、例えば、反応空間に水蒸気(H<sub>2</sub>O蒸気)に代表される水を主成分とするガスを導入し、プラズマを生成して行

50

うことができる。水蒸気をプラズマ化することにより、酸素原子、水素原子、又はH<sub>2</sub>Oの励起分子、さらにOH遊離基などの活性の高い中性の原子が生成される。プラズマ処理に用いるガスは、プラズマ化したときにOH遊離基を生成するものならばよく、水蒸気(H<sub>2</sub>O蒸気)に代表される水を主成分とするガスの他、過酸化水素水(H<sub>2</sub>O<sub>2</sub>)を用いることもできる。

#### 【0059】

エッティングに続けて水蒸気を用いてプラズマ処理を行うことにより、欠陥や歪み、ダメージ、ダングリングボンドにOH遊離基が作用して、OH遊離基で欠陥やダングリングボンド等を修復することができる。

#### 【0060】

10

プラズマの発生方法は、特に限定ではなく、誘導結合型プラズマ( I C P : Inductively Coupled Plasma)方式、容量結合型(平行平板型)プラズマ( CCP : Capacitively Coupled Plasma)方式、電子サイクロトロン共鳴プラズマ( E C R : Electron Cyclotron Resonance)方式、ヘリコン方式などを適用することができる。また、プラズマ処理は、100以上280以下の温度範囲、好ましくは、220以上280以下の温度範囲で行なうことが好ましい。温度が高すぎると単結晶半導体層112のダングリングボンドを終端化したOH基が脱離してしまい、ダングリングボンドの終端化が進まないからである。

#### 【0061】

20

図3に、本実施の形態で使用されるプラズマ処理装置の一例を示す概要構成図を示す。本実施の形態では、プラズマ発生室の下流側に存在するプラズマの雰囲気中に、試料を置く、いわゆるダウンフロー型のICPプラズマ処理装置を用いている。

#### 【0062】

プラズマ処理装置本体を構成する真空容器210の上部には、内部にプラズマ発生室202が形成された放電管203が設けられている。例えば、石英よりなる放電管203の頂部には処理ガス導入管204が設けられている。処理ガス導入管204には、ガス供給手段214が接続されている。ガス供給手段214は、マスフローコントローラ211、ベーパライザ212、シリンドラ213などで構成されている。処理ガスは、処理ガス導入管204からプラズマ発生室202内に導入されるようになっている。

#### 【0063】

30

放電管203の外周部には、プラズマ発生室202内において、プラズマ放電を励起させるための放電コイル205が螺旋状に巻き付けられている。この放電コイル205に電力を供給するため、該放電コイル205には高周波(Radio Frequency)電源206(以下、RF電源と記す)の一端が接続されている。従って、放電コイル205には、RF電源206により100kHz～100MHzの、例えば、13.56MHz程度の高周波の電力が供給される。なお、このRF電源206の他端は接地されてグランドレベルに落とされている。

#### 【0064】

40

真空容器210の下部、つまりプラズマ発生室202の下方にはダウンフロー室207が形成されている。このダウンフロー室207には、試料を保持するためのステージ215が設けられ、プラズマ発生室202からプラズマが導入される。単結晶半導体層を上方に向けて基板保持するステージ215には、この基板を加熱してプラズマ処理を向上させるためのヒータ208が組み込まれている。なお、真空容器210内の圧力を1.0Pa程度の低い圧力に設定するために、ダウンフロー室207の低面壁に開口して排気口209が設けられ、該排気口209は図示しない真空ポンプに接続されている。

#### 【0065】

このような、ダウンフロー型のプラズマ処理装置は、試料とプラズマが発生する領域とは離間しているため、プラズマ処理による試料のプラズマ損傷が抑制されるため好ましい。

#### 【0066】

次に、上記プラズマ処理装置を用いて、基板にプラズマ処理を行う方法の一例について以

10

20

30

40

50

下に説明する。

#### 【0067】

まず、ステージ215の温度をヒータ208によって250度に設定して、基板を加熱した状態にする。チャンバー内の圧力を66.5Paとし、コイル型の電極に1800WのRF(13.56MHz)電力を投入してプラズマを生成し、基板側には電力を投入する。続いて、シリンド213から純水を供給し、ベーパライザー212で気化させて、水蒸気を流量300sccmでプラズマ発生室202に導入する。プラズマ発生室202内では、マイクロ波によって水蒸気がプラズマ化する。そしてプラズマ化した水蒸気が、ガス下流のダウンフロー室207に導入され、ダウンフロー室207のステージ215では、単結晶半導体層112にプラズマ化された水蒸気が供給される。このようなプラズマ化された水蒸気の供給を180秒行う。10

#### 【0068】

エッチングに続けてOH遊離基を含むプラズマに曝すことにより、結晶欠陥を低減することができる。また、600程度の温度で熱処理を行う場合と比べて、結晶欠陥の低減に時間がかからず、SOI基板の作製プロセス全体にかかる時間を削減することができる。

#### 【0069】

また、プラズマ処理を行った後に、500以上700以下の熱処理を行うこともできる。この場合は、プラズマ処理により欠陥や歪み、ダメージを低減させているため、熱処理だけを行ったと比べて、SOI基板の作製プロセス全体にかかる時間を削減することができる。また、プラズマ処理を行う前に熱処理を行うこともできる。この熱処理には、RTA(Rapid Thermal Anneal)装置、抵抗加熱炉、マイクロ波加熱装置を用いることができる。RTA装置は、加熱された気体を用いるガス加熱式のRTA(GRTA: Gas Rapid Thermal Anneal)装置、ランプ加熱式のRTA(LRTA:Lamp Rapid Thermal Anneal)装置を用いることができる。例えば、抵抗加熱炉を用いた場合は、600で4時間加熱するとい20い。

#### 【0070】

以上の工程により、支持基板上に絶縁膜を介して単結晶半導体層が設けられたSOI基板を作製することができる(図2(D))。本実施の形態で示した作製方法を用いることによつて、耐熱性の低い支持基板を用いた場合であつても、十分に平坦性を高め、結晶欠陥を低減させることができる。また、平坦性及び結晶性に優れたSOI基板を歩留まり良く作製することができる。また、このようなSOI基板を用いて、優れた特性の半導体装置を作製することができる。30

#### 【0071】

本実施の形態は、他の実施の形態と自由に組み合わせて行うことができる。

#### 【0072】

(実施の形態2)

本実施の形態では、実施の形態1で示したSOI基板の構成とは異なる構成について説明する。なお、本実施の形態において、実施の形態1と同様の部分には同じ符号を付し、詳しい説明を省略する。40

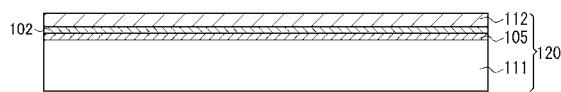

#### 【0073】

図4に、本実施の形態に係るSOI基板の作製方法の一例について示す。まず、図4(A)に示すように、単結晶半導体基板101上に、絶縁膜102が絶縁膜102aと絶縁膜102bの2層構造で形成されている。絶縁膜102を2層構造とする場合には、絶縁膜102に、バリア層を1層含ませることが好ましい。絶縁膜102を2層構造で設ける場合は、上層の絶縁膜をナトリウムなどの不純物をブロッキングするためのバリア層で構成する。上層の絶縁膜は、膜厚5nm以上200nm以下の窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、又は窒化アルミニウム膜で形成することができる。バリア層として機能するこれらの膜は、不純物の拡散を防止するブロッキング効果が高いが、内部応力が高い。よって、単結晶半導体基板101と接する下層の絶縁膜には、上層の絶縁50

膜の絶縁膜の応力を緩和する効果のある膜を選択することが好ましい。このような絶縁膜には、酸化シリコン膜及び酸化窒化シリコン膜、及び単結晶半導体基板101を熱酸化して形成した熱酸化膜などがある。下層の絶縁膜の膜厚は、5nm以上200nm以下とすることができる。

#### 【0074】

絶縁膜102をバリア層として機能させる絶縁膜102aと絶縁膜102bの組み合わせには、例えば、酸化シリコン膜と窒化シリコン膜、酸化窒化シリコン膜と窒化シリコン膜、酸化シリコン膜と窒化酸化シリコン膜、酸化窒化シリコン膜と窒化酸化シリコン膜などがある。

#### 【0075】

10

例えば、下層の絶縁膜102aは、プロセスガスにSiH<sub>4</sub>及びN<sub>2</sub>Oを用いてPECVD法で形成した酸化窒化シリコン膜で形成することができる。また、絶縁膜102aとして、プロセスガスに有機シランガスと酸素を用いて、PECVD法で酸化シリコン膜を形成することもできる。また、単結晶半導体基板101を酸化することで形成された酸化膜を絶縁膜102aとすることもできる。

#### 【0076】

有機シランとは、珪酸エチル(TEOS：化学式Si(OCH<sub>3</sub>)<sub>4</sub>)、テトラメチルシラン(TMS：化学式Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OCH<sub>3</sub>)<sub>3</sub>)、またはトリスジメチルアミノシラン(SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>)などの化合物である。

#### 【0077】

上層の絶縁膜102bは、プロセスガスにSiH<sub>4</sub>、N<sub>2</sub>O、NH<sub>3</sub>又はH<sub>2</sub>を用いてPECVD法で形成した窒化酸化シリコン膜で形成することができる。又は、プロセスガスにSiH<sub>4</sub>、N<sub>2</sub>、NH<sub>3</sub>、又はH<sub>2</sub>を用いてPECVD法で形成した窒化シリコン膜で形成することができる。

#### 【0078】

図4(A)に示すように、酸化窒化シリコン膜でなる絶縁膜102a、窒化酸化シリコン膜でなる絶縁膜102bを形成する場合、単結晶半導体基板101をPECVD装置のチャンバーに搬入し、絶縁膜102aの形成用のプロセスガスとしてSiH<sub>4</sub>及びN<sub>2</sub>Oをチャンバーに供給し、このプロセスガスのプラズマを生成し、窒化酸化シリコン膜を単結晶半導体基板101上に形成する。次に、チャンバーに供給するプロセスガスを絶縁膜102b形成用のプロセスガスに変更する。ここでは、SiH<sub>4</sub>、N<sub>2</sub>O、NH<sub>3</sub>及びN<sub>2</sub>Oを用いる。これらの混合ガスのプラズマを生成して、酸化窒化シリコン膜及び窒化酸化シリコン膜を連続して形成する。また、複数のチャンバーを有するPECVD装置を用いる場合は、酸化窒化シリコン膜と窒化酸化シリコン膜と異なるチャンバーで形成することもできる。もちろん、チャンバーに供給するプロセスガスを変更することで、下層の絶縁膜102aに酸化シリコン膜を形成することもできるし、上層の絶縁膜102bに窒化シリコン膜を形成することもできる。

#### 【0079】

40

上記のように絶縁膜102a及び絶縁膜102bを形成することで、スループット良く単結晶半導体基板101に絶縁膜102を形成することができる。また、大気に触れされることなく絶縁膜102a、絶縁膜102bを形成できるので、絶縁膜102aと絶縁膜102bの界面が大気によって汚染されることを防止することができる。

#### 【0080】

また、絶縁膜102aとして、実施の形態1(図1(A))で示したように、単結晶半導体基板101を酸化処理して形成された酸化膜を用いることもできる。この酸化膜の形成するための熱酸化処理は、ドライ酸化で行うこともできるが、酸化雰囲気中にハロゲン元素を含むガスを添加することが好ましい。ハロゲン元素を含む雰囲気での熱酸化処理方法については、図1(A)において示した方法を用いればよいため、詳しい説明を省略する

10

20

30

40

50

。

### 【0081】

なお、本明細書において、酸化窒化物とは、その組成として、窒素原子よりも酸素原子の数が多い物質とし、また、窒化酸化物とは、その組成として、酸素原子よりも窒素原子の数が多い物質とする。なお、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、ラザフォード後方散乱法 (RBS : Rutherford Backscattering Spectrometry) 及び水素前方散乱法 (HFS : Hydrogen Forward Scattering) を用いて測定した場合に、濃度範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 15 原子%、Si が 25 ~ 35 原子%、水素が 0.1 ~ 10 原子% の範囲で含まれるものという。また、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、RBS 及び HFS を用いて測定した場合に、濃度範囲として酸素が 5 ~ 30 原子%、窒素が 20 ~ 55 原子%、Si が 25 ~ 35 原子%、水素が 10 ~ 30 原子% の範囲で含まれるものという。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を 100 原子%としたとき、窒素、酸素、Si 及び水素の含有比率が上記の範囲内に含まれるものとする。10

### 【0082】

次に、図 4 (B) に示すように、絶縁膜 102 を介して、単結晶半導体基板 101 にイオンを照射することにより、イオンを単結晶半導体基板 101 に導入し、単結晶半導体基板 101 の一方の面から所定の深さの領域に脆化領域 103 を形成する。脆化領域 103 の形成方法については、図 1 (B) において示した方法を用いればよいため、詳しい説明を省略する。20

### 【0083】

次に、図 4 (C) に示すように、脆化領域 103 を形成した後に、絶縁膜 102b 上に絶縁膜 105 を形成する。絶縁膜 105 を形成する際には、単結晶半導体基板 101 の加熱温度は、脆化領域 103 に添加された原子又は分子が析出しない温度とし、例えば、加熱温度は 350 以下が好ましい。言い換えると、この加熱温度は脆化領域 103 からガスが抜けない温度である。なお、絶縁膜 105 は、脆化領域 103 の形成前に形成することもできる。脆化領域 103 の形成前に絶縁膜 105 を形成するときのプロセス温度は、350 以上とすることができます。30

### 【0084】

絶縁膜 105 は、平滑で親水性の接合面を単結晶半導体基板 101 の表面に形成するための層である。絶縁膜 105 の平均粗さ Ra が 0.7 nm 以下、より好ましくは、0.4 nm 以下が好ましい。また、絶縁膜 105 の厚さは 10 nm 以上 200 nm 以下とすることができます。好ましい厚さは 5 nm 以上 500 nm 以下であり、より好ましくは 10 nm 以上 200 nm 以下である。

### 【0085】

絶縁膜 105 は、化学的気相反応により形成されることが好ましい。例えば、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化シリコン膜などを、絶縁膜 105 として形成することができる。絶縁膜 105 として、PECVD 法で酸化シリコン膜を形成する場合には、ソースガスに有機シランガス及び酸素 (O<sub>2</sub>) ガスを用いることが好ましい。ソースガスに有機シランを用いることで、プロセス温度が 350 以下で、平滑な表面を有する酸化シリコン膜を形成することができる。また、熱 CVD 法で、加熱温度が 200 以上 500 以下で形成される低温酸化物 (LTO : Low Temperature Oxide) で形成することができる。LTO の形成には、シリコンソースガスにモノシラン (SiH<sub>4</sub>) 又はジシラン (Si<sub>2</sub>H<sub>6</sub>) などを用い、酸素ソースガスに一酸化二窒素 (N<sub>2</sub>O) などを用いることができる。40

### 【0086】

例えば、ソースガスに TEOS と O<sub>2</sub> を用いて、酸化シリコン膜でなる絶縁膜 105 を形成するための条件例としては、処理室に流量 15 sccm で TEOS を導入し、流量 7550

0 sccmでO<sub>2</sub>を導入する。成膜圧力は100Pa、成膜温度300、RF出力300W、電源周波数13.56MHzが挙げられる。

#### 【0087】

また、単結晶半導体基板101にイオンを照射して脆化領域103を形成した後、絶縁膜102及び絶縁膜105を形成することもできる。この場合、絶縁膜102と絶縁膜105を同じ成膜装置で形成できる場合は、絶縁膜102と絶縁膜105の形成を連続して行うことが好ましい。

#### 【0088】

次に、表面に絶縁膜102及び絶縁膜105が形成され、表面から所定の深さの領域に脆化領域103が形成された単結晶半導体基板101と支持基板111とを、絶縁膜102及び絶縁膜105を介して接着する(図4(E))。次に、熱処理を行い脆化領域103において分離することにより、支持基板111上に絶縁膜105及び絶縁膜102を介して単結晶半導体層112を形成することができる(図4(F))。次に、単結晶半導体層112に対して平坦性を高め、結晶欠陥を低減させる処理を行なった後、OH遊離基を含むプラズマに曝すことによってさらに結晶欠陥を低減させる処理を行い、平坦性及び結晶性の良好な単結晶半導体層112を形成することができる。以上の方法は、実施の形態1(図1(D)乃至図2(C))において示した方法を用いればよいため、詳しい説明を省略する。

#### 【0089】

以上のように、絶縁膜102を2層構造とし、上層の絶縁膜102bをバリア層とすることにより、支持基板111からのナトリウムなどの不純物をブロッキングすることができる。また、絶縁膜102b上に平滑面を有し親水性表面となる絶縁膜105を形成することによって、支持基板111との貼り合わせを良好に行うことができる。

#### 【0090】

図5に、支持基板111上に絶縁膜105及び絶縁膜102を介して単結晶半導体層112を設けた構成を示す。絶縁膜102は、例えば、プロセスガスにSiH<sub>4</sub>及びN<sub>2</sub>Oを用いてPECVD法で形成した酸化窒化シリコン膜を用いることができる。または、プロセスガスに有機シランガスと酸素を用いてPECVD法で酸化シリコン膜を用いることもできる。または、単結晶半導体基板101を、ハロゲン元素を含む酸化性雰囲気で酸化処理を行うことで形成された酸化膜を絶縁膜102とすることができる。絶縁膜105は、バリア層として機能する膜が用いられている。絶縁膜105の膜厚は、5nm以上200nm以下の窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、又は窒化酸化アルミニウム膜で形成されている。

#### 【0091】

次に、図5に示すSOI基板の作製方法について説明する。まず、単結晶半導体基板101上に、絶縁膜102を形成する。次に、絶縁膜102を介して、単結晶半導体基板101にイオンを照射することにより、イオンを単結晶半導体基板101に導入し、単結晶半導体基板の一方の面から所定の深さの領域に脆化領域103を形成する。脆化領域103の形成方法については、図1(B)において示した方法を用いればよいため、詳しい説明を省略する。

#### 【0092】

脆化領域103を形成した後に、絶縁膜102上に絶縁膜105を形成する。絶縁膜105を形成する際には、単結晶半導体基板101の加熱温度は、脆化領域103に添加された原子又は分子が析出しない温度とし、例えば、その加熱温度は350以下が好ましい。言い換えると、この加熱温度は脆化領域103からガスが抜けない温度である。絶縁膜105を350以下で形成することによって、絶縁膜105を、平滑面を有し親水表面とすることができます。また、絶縁膜105をバリア層とすることにより、支持基板111からのナトリウムなどの不純物をブロッキングすることができる。

#### 【0093】

次に、表面に絶縁膜102及び絶縁膜105が形成され、表面から所定の深さの領域に脆

10

20

30

40

50

化領域 103 が形成された単結晶半導体基板 101 と支持基板 111 とを、絶縁膜 102 及び絶縁膜 105 を介して接着する。次に、熱処理を行い脆化領域 103 において分離することにより、支持基板 111 上に絶縁膜 105 及び絶縁膜 102 を介して単結晶半導体層 112 を形成することができる。次に、単結晶半導体層 112 に対して平坦性を高め、結晶欠陥を低減させる処理を行なった後、OH 遊離基を含むプラズマに曝すことによってさらに結晶欠陥を低減させる処理を行い、平坦性及び結晶性の良好な単結晶半導体層 112 を形成することができる。以上 の方法は、実施の形態 1 ( 図 1 ( D ) 乃至図 2 ( C ) ) において示した方法を用いればよいため、詳しい説明を省略する。

#### 【 0094 】

以上のように、図 5 に示す構成にすることによって、絶縁膜 105 がバリア層として機能するため、支持基板 111 から単結晶半導体層 112 へ不純物が拡散し、単結晶半導体層 112 が汚染されることを防止することができる。

#### 【 0095 】

図 6 に、支持基板 111 上に絶縁膜 113 及び絶縁膜 102 を介して単結晶半導体層 112 を設けた構成を示す。絶縁膜 102 は、実施の形態 1 で示したように、単結晶半導体基板 101 の表面に酸化膜を形成したものを用いることができる。また、絶縁膜 113 は、アルミニウム、マグネシウム、ストロンチウム、チタン、タンタル、ジルコニウム、イットリウムから選ばれた一つ又は複数の元素を含む酸化膜又は窒化膜を用いることができる。絶縁膜 113 に、例えば、酸化アルミニウムを主成分とする酸化膜を用いる場合について説明する。酸化アルミニウムを主成分とする酸化膜とは、当該酸化膜に含まれる成分の合計を 100 重量 % とするときに、酸化アルミニウムを 10 重量 % 以上含む酸化膜をいう。他にも、絶縁膜 113 としては、酸化アルミニウムを主成分とし、酸化マグネシウムと酸化ストロンチウムの一方又は両方が含まれる膜を適用することができる。また、窒素を含有する酸化アルミニウムを絶縁膜 113 として用いてもよい。

#### 【 0096 】

次に、図 6 に示す SOI 基板の作製方法について説明する。まず、単結晶半導体基板 101 上に、絶縁膜 102 を形成する。次に、絶縁膜 102 を介して、単結晶半導体基板 101 にイオンを照射することにより、イオンを単結晶半導体基板 101 に導入し、単結晶半導体基板 101 の一方の面から所定の深さの領域に脆化領域 103 を形成する。脆化領域 103 の形成方法については、図 1 ( B ) において示した方法を用いればよいため、詳しい説明を省略する。

#### 【 0097 】

次に、バイアス電圧を印加して支持基板 111 の表面にプラズマ処理による平坦化処理を行う。ここでは、真空状態のチャンバーに不活性ガス ( 例えは、Ar ガス ) 及び / 又は反応性ガス ( 例えは、O<sub>2</sub> ガス、N<sub>2</sub> ガス ) を導入し、被処理面 ( ここでは、支持基板 111 ) にバイアス電圧を印加してプラズマ状態として行う。プラズマ中には電子と Ar の陽イオンが存在し、陰極方向 ( 支持基板 111 側 ) に Ar の陽イオンが加速される。加速された Ar の陽イオンが支持基板 111 表面に衝突することによって、支持基板 111 表面がスパッタエッチングされる。このとき、支持基板 111 表面の凸部から優先的にスパッタエッチングされ、当該支持基板 111 表面の平坦性を向上することができる。反応性ガスを導入する場合、支持基板 111 表面がスパッタエッチングされることにより生じる欠損を、補修することができる。

#### 【 0098 】

バイアス電圧を印加して支持基板 111 の表面にプラズマ処理による平坦化処理を行うことにより、支持基板 111 の表面の平均粗さ ( Ra ) を好ましくは 0.5 nm 以下、より好ましくは 0.3 nm 以下とし、最大高低差 ( P - V ) を好ましくは 6 nm 以下、より好ましくは 3 nm 以下とする。

#### 【 0099 】

具体的な条件としては、処理電力 100 ~ 1000 W、圧力 0.1 ~ 2.0 Pa、ガス流量 5 ~ 150 sccm、バイアス電圧 200 ~ 600 V で行えばよい。

10

20

30

40

50

**【0100】**

また、上述したプラズマ処理を行う際に、チャンバー内をプレコート処理しておくことにより、反応室を構成する金属（鉄（Fe）、ニッケル（Ni）、クロム（Cr）等）が不純物として支持基板111の表面に付着することを防ぐことができる。例えば、反応室内を酸化シリコン膜、シリコン膜、酸化アルミニウム膜、シリコンカーバイド（SiC）膜等の絶縁膜で被覆しておくことにより、平坦化処理に伴う支持基板111の表面汚染を低減することが可能となる。

**【0101】**

このように、平坦化処理を行うことによって、支持基板111の表面の平坦性を向上することができる。仮に支持基板111としてCMP等により研磨された基板を用いる場合であっても、支持基板111上に残留する研磨粒子（CeO<sub>2</sub>等）を除去し、表面を平坦化することができる。その結果、支持基板111上に形成される膜の平坦性を向上させることができる。

10

**【0102】**

なお、支持基板111の平坦化処理を行う前に支持基板111の洗浄を行ってもよい。具体的には、支持基板111を、塩酸過酸化水素水（HPM）、硫酸過酸化水素水（SPM）、アンモニア過酸化水素水（APM）、希フッ酸（DHF）、オゾン水等を用いて超音波洗浄を行う。例えば、支持基板111の表面に塩酸過水を用いて超音波洗浄を行うことが好ましい。このような洗浄処理を行うことによって、ある程度支持基板111表面の平坦化や残存する研磨粒子を除去することができる。

20

**【0103】**

次に、支持基板111上に、絶縁膜113を形成する。絶縁膜113は、スパッタリング法により形成することができる。スパッタリング法に用いるターゲットとしては、例えば、アルミニウム（Al）を含む金属又は酸化アルミニウム等の金属酸化物を用いることができる。なお、ターゲットの材料は、形成したい膜に応じて適宜選択すればよい。

**【0104】**

また、上述した平坦化処理とスパッタリング法による絶縁膜113の形成を大気に曝さずに連続して行なうことが好ましい。連続して処理することによって、スループットの向上を図ることができる。また、プラズマ処理を用いて支持基板111の表面を平坦化した後には、支持基板111表面が活性化しており、有機物等の不純物が付着しやすいが、連続して処理することによって、支持基板111への不純物の付着を低減することができる。

30

**【0105】**

スパッタターゲットとして金属を用いる場合には、反応ガス（例えば、酸素）を導入しながらスパッタすること（反応性スパッタリング法）により、絶縁膜113を形成する。金属としては、アルミニウムの他に、マグネシウム（Mg）、アルミニウムとマグネシウムを含む合金、アルミニウムとストロンチウム（Sr）を含む合金、アルミニウムとマグネシウムとストロンチウムを含む合金を用いることができる。この場合、スパッタリングは直流（DC）電源又は高周波（RF）電源を用いて行なえばよい。

**【0106】**

例えば、ターゲットとしてアルミニウムを用い、ガス流量（アルゴン：0～100 sccm、酸素：5～100 sccm）、成膜圧力0.1～2.0 Pa、成膜電力0.5～4 kW、T-S間距離（ターゲットと基板間距離）が50～185 mmで行なうことができる。なお、絶縁膜113の成膜前に不活性ガス（例えば、アルゴン）を用いてスパッタを行うことや、ダミー基板にあらかじめ成膜することによって、支持基板111上に絶縁膜113を形成する場合に生じるゴミを低減することができる。

40

**【0107】**

ターゲットとして金属酸化物を用いる場合には、高周波（RF）電源を用いてスパッタすること（RFスパッタリング法）により、絶縁膜113を形成する。金属酸化物としては、酸化アルミニウムの他に、酸化マグネシウム、酸化ストロンチウム、アルミニウムとマグネシウムを含有する酸化物、アルミニウムとストロンチウムを含有する酸化物、アルミ

50

ニウムとマグネシウムとストロンチウムを含有する酸化物を用いることができる。

#### 【0108】

例えば、ターゲットとして酸化アルミニウムを用い、ガス流量（アルゴン：0～100 sccm、酸素：5～100 sccm）、成膜圧力0.1～2.0 Pa、成膜電力0.5～4 kW、T-S間距離（ターゲットと基板間距離）が50～185 mmで行うことができる。

#### 【0109】

他にも、バイアススパッタリング法を用いて、絶縁膜113を形成してもよい。バイアススパッタリング法では、ターゲットからの堆積と共に、被処理面（ここでは、支持基板111）にバイアス電圧を印加して当該被処理面にイオンを入射させることにより、被処理面のエッチングと再付着も同時に行われる。エッチングは支持基板111表面の凸から優先的に行われるため、支持基板111表面の平坦化を行いつつ、絶縁膜113の堆積を行うことができる。そのため、バイアススパッタリング法を適用する場合には、絶縁膜113形成前に支持基板111に行う平坦化処理を省略してもよい。10

#### 【0110】

バイアススパッタリング法を用いる場合には、ターゲットとしてアルミニウムを用い、ガス流量（アルゴン：0～100 sccm、酸素：5～100 sccm）、成膜圧力0.1～2.0 Pa、成膜電力0.5～4 kW、T-S間距離（ターゲットと基板間距離）が50～185 mmで行うことができる。20

#### 【0111】

支持基板111上に酸化アルミニウムを主成分とする酸化膜を設けることによって、支持基板111に含まれる可動イオンや水分等の不純物が、当該支持基板111上に形成される単結晶半導体層に拡散することを防ぐことができる。20

#### 【0112】

次に、表面に絶縁膜102が形成され、表面から所定の深さの領域に脆化領域103が形成された単結晶半導体基板101と、支持基板111とを絶縁膜102及び絶縁膜113を介して接着する。次に、熱処理を行い脆化領域103において分離することにより、支持基板111上に絶縁膜113及び絶縁膜102を介して単結晶半導体層112を形成することができる。次に、単結晶半導体層112に対して平坦性を高め、結晶欠陥を低減させる処理を行なった後、OH遊離基を含むプラズマに曝すことによってさらに結晶欠陥を低減させる処理を行い、平坦性及び結晶性の良好な単結晶半導体層112を形成することができる。以上的方法は、実施の形態1（図1（D）乃至図2（C））において示した方法を用いればよいため、詳しい説明を省略する。30

#### 【0113】

以上のように、支持基板111上に酸化アルミニウムを主成分とする酸化膜を設けることによって、支持基板111に含まれる可動イオンや水分等の不純物が、後に当該支持基板111上に形成される単結晶半導体膜に拡散することを防ぐことができる。また、単結晶半導体基板101側の貼り合わせ面にシリコン系の絶縁膜を設け、支持基板111側の貼り合わせ面に酸化アルミニウムを主成分とする酸化膜を用いているため、単結晶半導体基板101と支持基板111の接着は、シリコン系絶縁膜とシリコン系以外の絶縁膜との接着（異種接着）となる。このような材料を用いることによって、単結晶半導体基板101と支持基板111との密着性を向上させることができる。40

#### 【0114】

以上のように、本発明の一態様に係るSOI基板は、様々な態様で作製することができる。

#### 【0115】

本実施の形態は、他の実施の形態と自由に組み合わせて行うことができる。

#### 【0116】

（実施の形態3）

本実施の形態では、上記実施の形態で作製したSOI基板を用いて、薄膜トランジスタを

50

作製する方法について説明する。

**【0117】**

まず、図7及び図8を参照して、nチャネル型薄膜トランジスタ、及びpチャネル型薄膜トランジスタを作製する方法について説明する。複数の薄膜トランジスタを組み合わせることで、各種の半導体装置を形成することができる。なお、実施の形態1及び実施の形態2と同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

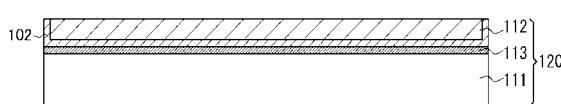

**【0118】**

実施の形態1に従って作製されたSOI基板120を図7(A)に示す。図7(A)に示すSOI基板120は、支持基板111上の絶縁膜102を介して単結晶半導体層112が形成されている。なお、ここでは、図2(C)に示す構成のSOI基板120を適用する例を示すが、本明細書で示すその他の構成のSOI基板120も適用できる。10

**【0119】**

単結晶半導体層112は、単結晶半導体基板101より分離され、平坦化処理が行われている。平坦化処理としては、エッチング処理、レーザ光の照射を組み合わせて行うことにより行うことができる。

**【0120】**

単結晶半導体層112をエッチングして、半導体素子の配置に合わせて島状に分離した単結晶半導体層121、122を形成する(図7(B))。単結晶半導体層121は、nチャネル型の薄膜トランジスタを構成し、単結晶半導体層122は、pチャネル型の薄膜トランジスタを構成する。20

**【0121】**

単結晶半導体層112に対してエッチングを行う前に、薄膜トランジスタのしきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどのp型の不純物元素、又はリン、ヒ素などのn型の不純物元素を単結晶半導体層112に添加することが好ましい。例えば、nチャネル型薄膜トランジスタの形成される領域にp型の不純物元素を添加し、pチャネル型薄膜トランジスタの形成される領域にn型の不純物元素を添加する。

**【0122】**

単結晶半導体層121、122を覆うゲート絶縁膜123を形成する。本実施の形態における単結晶半導体層121、122は平坦性が高いため、単結晶半導体層121、122上に形成されるゲート絶縁膜123が薄膜であっても、被覆性良く覆うことができる。従ってゲート絶縁膜の被覆不良による特性不良を防止することができ、高信頼性の半導体装置を歩留まりよく作製することができる。ゲート絶縁膜123の薄膜化は、薄膜トランジスタを低電圧で高速に動作させる効果がある。30

**【0123】**

ゲート絶縁膜123は、酸化シリコン膜、若しくは酸化シリコン膜と窒化シリコン膜との積層構造で形成すればよい。ゲート絶縁膜123は、プラズマCVD法や減圧CVD法により絶縁膜を堆積することで形成してもよいし、プラズマ処理による固相酸化若しくは固相窒化で形成すると良い。単結晶半導体層121、122をプラズマ処理により酸化又は窒化することにより形成するゲート絶縁膜123は、緻密で絶縁耐圧性が高く、信頼性に優れているためである。40

**【0124】**

また、ゲート絶縁膜123として、二酸化ジルコニウム、酸化ハフニウム、二酸化チタン、五酸化タンタルなどの高誘電率材料を用いても良い。ゲート絶縁膜123に高誘電率材料を用いることにより、ゲートリーコンデンサの電流を低減することができる。

**【0125】**

ゲート絶縁膜123上に導電膜を形成する。導電膜は、スパッタリング法、蒸着法、CVD法等により形成することができる。導電膜は、タンタル、タンゲステン、チタン、モリブデン、アルミニウム、銅、クロム、ネオジムから選ばれた元素、又は前記元素を主成分とする合金材料若しくは化合物材料で形成することができる。また、導電膜は、リン等の不純物元素をドーピングした多結晶シリコン層に代表される半導体層や、AgPdCu合50

金を用いることもできる。導電膜上にマスクを形成し、選択的に導電膜をエッティングすることで、ゲート電極 124、125を形成することができる(図7(C))。

#### 【0126】

単結晶半導体層122を覆うマスク126を形成する。マスク126及びゲート電極124をマスクとして、n型を付与する不純物元素127を添加し、n型不純物領域128a、128bを形成する(図7(D))。本実施の形態では、不純物元素を含むドーピングガスとしてホスフィン(PH<sub>3</sub>)を用いる。ここでは、n型不純物領域128a、128bに、n型を付与する不純物元素が $1 \times 10^{17} \sim 5 \times 10^{18} / \text{cm}^3$ 程度の濃度で含まれるように添加する。本実施の形態では、n型を付与する不純物元素としてリン(P)を用いる。単結晶半導体層121のゲート電極124と重なる領域は、チャネル形成領域129となる。

10

#### 【0127】

次に、マスク126を除去した後、単結晶半導体層121を覆うマスク130を形成する。マスク130及びゲート電極125をマスクとして、p型を付与する不純物元素131を添加し、p型不純物領域132a、132bを形成する(図7(E))。本実施の形態では、不純物元素を含むドーピングガスとしてジボラン(B<sub>2</sub>H<sub>6</sub>)を用いる。本実施の形態では、p型を付与する不純物元素としてボロン(B)を用いる。単結晶半導体層122のゲート電極125と重なる領域は、チャネル形成領域133となる。

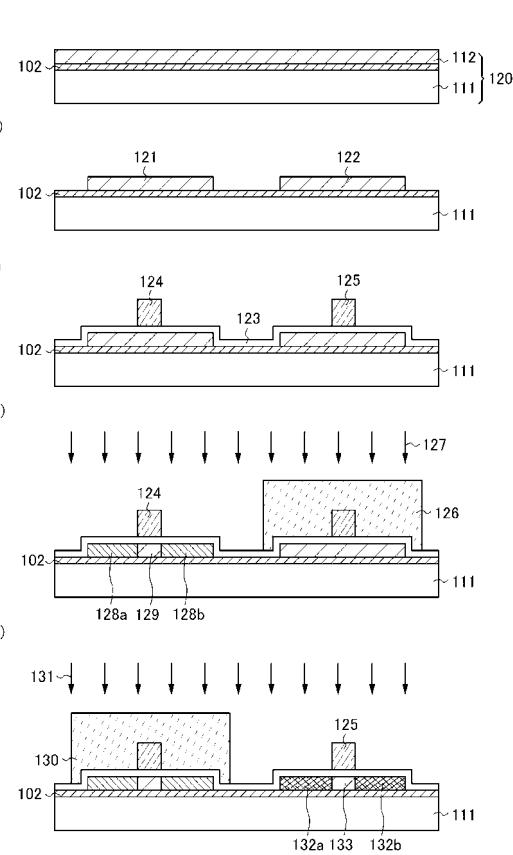

#### 【0128】

次に、マスク130を除去した後、プラズマCVD法等によって、窒化シリコン等の窒化化合物や酸化シリコン等の酸化物からなる単層構造又は積層構造の絶縁膜を形成する。この絶縁膜を垂直方向の異方性エッティングすることで、図8(A)に示すように、ゲート電極124、125の側面に接するサイドウォール絶縁膜134a、134b、135a、135bを形成する。この異方性エッティングにより、絶縁膜123もエッティングされる。

20

#### 【0129】

次に、図8(B)に示すように、単結晶半導体層122をマスク136で覆う。単結晶半導体層121にソース領域又はドレイン領域として機能する高濃度不純物領域を形成するため、イオン注入法又はイオンドーピング法により、単結晶半導体層121に高ドーズ量で不純物元素を添加する。ゲート電極124、及びサイドウォール絶縁膜134a、134bがマスクとなり、n型の高濃度不純物領域138a、138bが形成される。次に、マスク136を除去した後、不純物元素の活性化のための加熱処理を行う。

30

#### 【0130】

活性化の加熱処理の後、図8(C)に示すように、水素を含んだ絶縁膜139を形成する。絶縁膜139を形成した後、350以上450以下の温度による加熱処理を行い、絶縁膜139中に含まれる水素を単結晶半導体層121、122中に拡散させる。絶縁膜139は、プロセス温度が350以下のプラズマCVD法により窒化シリコン膜又は窒化酸化シリコン膜を堆積することで形成することができる。単結晶半導体層121、122に水素を供給することで、単結晶半導体層121、122中及び絶縁膜139との界面での捕獲中心となるような欠陥を効果的に補償することができる。

#### 【0131】

40

次に、層間絶縁膜140を形成する。層間絶縁膜140は、酸化シリコン膜、BPSG(Boron Phosphorus Silicon Glass)膜などの無機材料でなる絶縁膜、又は、ポリイミド、アクリルなどの有機樹脂膜から選ばれた単層構造の膜又は積層構造の膜で形成することができる。次に、層間絶縁膜140にコンタクトホールを形成し、図8(C)に示すように配線141a、141b、142a、142bを形成する。配線141a、141b、142a、142bの形成には、例えば、アルミニウム膜又はアルミニウム合金膜などの低抵抗金属膜をバリアメタル膜で挟んだ3層構造の導電膜で形成することができる。バリアメタル膜は、モリブデン、クロム、チタンなどの金属膜で形成することができる。

#### 【0132】

50

以上の工程により、nチャネル型薄膜トランジスタとpチャネル型薄膜トランジスタを有する半導体装置を作製することができる。SOI基板の作製の過程で、チャネル形成領域を構成する単結晶半導体層の金属元素の濃度を低減させているので、オフ電流が小さく、しきい値電圧の変動が抑制された薄膜トランジスタを作製することができる。

#### 【0133】

図7及び図8を参照して薄膜トランジスタの作製方法を説明したが、薄膜トランジスタの他、容量、抵抗など薄膜トランジスタと共に各種の半導体素子を形成することで、高付加価値の半導体装置を作製することができる。

#### 【0134】

本実施の形態に限定されず、薄膜トランジスタはチャネル形成領域が一つ形成されるシングルゲート構造でも、二つ形成されるダブルゲート構造若しくは三つ形成されるトリプルゲート構造であってもよい。

10

#### 【0135】

このように、本発明の一態様に係るSOI基板を用いて薄膜トランジスタを作製することができる。SOI基板の単結晶半導体層は、結晶欠陥がほとんど無く、ゲート絶縁膜123との界面準位密度が低減された単結晶半導体層であり、その表面が平坦化され、さらにその厚さを50nm以下と薄膜化されている。このことにより、SOI基板に、低い駆動電圧、高い電界効果移動度、小さいサブスレッショルド値など、優れた特性を備えた薄膜トランジスタを形成することができる。さらに、同一基板上に特性のバラツキの少ない、高性能なトランジスタを複数基板上に形成することが可能である。すなわち、本発明の一態様に係るSOI基板を用いることで、しきい値電圧や移動度などトランジスタ特性として重要な特性値の不均一性が抑制され、また、高い電界効果移動度などの高性能化が可能になる。

20

#### 【0136】

したがって、本発明の一態様に係るSOI基板を用いて薄膜トランジスタ等の各種の半導体素子を形成することで、高付加価値の半導体装置を作製することができる。

#### 【0137】

##### (実施の形態4)

実施の形態3を参照して薄膜トランジスタの作製方法を説明したが、薄膜トランジスタの他、容量、抵抗など薄膜トランジスタと共に各種の半導体素子を形成することで、高付加価値の半導体装置を作製することができる。以下、図面を参照しながら半導体装置の具体的な態様を説明する。

30

#### 【0138】

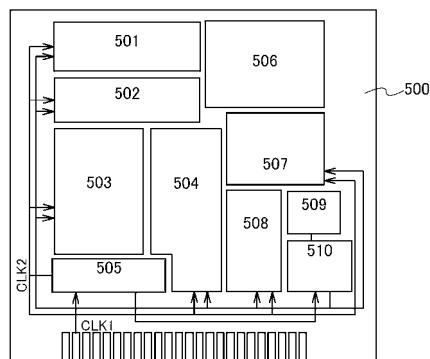

まず、半導体装置の一例として、マイクロプロセッサについて説明する。図9はマイクロプロセッサ500の構成例を示すブロック図である。

#### 【0139】

マイクロプロセッサ500は、演算回路501(Arithmetic logic unit。ALUともいう。)、演算回路制御部502(ALU Controller)、命令解析部503(Instruction Decoder)、割り込み制御部504(Interrupt Controller)、タイミング制御部505(Timing Controller)、レジスタ506(Register)、レジスタ制御部507(Register Controller)、バスインターフェース508(Bus I/F)、読み出し専用メモリ509、およびメモリインターフェース510を有している。

40

#### 【0140】

バスインターフェース508を介してマイクロプロセッサ500に入力された命令は、命令解析部503に入力され、デコードされた後、演算回路制御部502、割り込み制御部504、レジスタ制御部507、タイミング制御部505に入力される。演算回路制御部502、割り込み制御部504、レジスタ制御部507、タイミング制御部505は、デコードされた命令に基づき様々な制御を行う。

50

**【 0 1 4 1 】**

演算回路制御部 502 は、演算回路 501 の動作を制御するための信号を生成する。また、割り込み制御部 504 は、マイクロプロセッサ 500 のプログラム実行中に、外部の入出力装置や周辺回路からの割り込み要求を処理する回路であり、割り込み制御部 504 は、割り込み要求の優先度やマスク状態を判断して、割り込み要求を処理する。レジスタ制御部 507 は、レジスタ 506 のアドレスを生成し、マイクロプロセッサ 500 の状態に応じてレジスタ 506 の読み出しや書き込みを行う。タイミング制御部 505 は、演算回路 501、演算回路制御部 502、命令解析部 503、割り込み制御部 504、およびレジスタ制御部 507 の動作のタイミングを制御する信号を生成する。例えば、タイミング制御部 505 は、基準クロック信号 CLK1 を元に、内部クロック信号 CLK2 を生成する内部クロック生成部を備えている。図 9 に示すように、内部クロック信号 CLK2 は他の回路に入力される。10

**【 0 1 4 2 】**

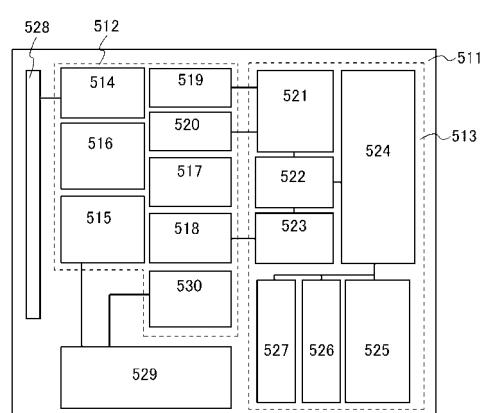

次に、非接触でデータの送受信を行う機能、および演算機能を備えた半導体装置の一例を説明する。図 10 は、このような半導体装置の構成例を示すブロック図である。図 10 に示す半導体装置は、無線通信により外部装置と信号の送受信を行って動作するコンピュータ（以下、「RFCPU」という）と呼ぶことができる。

**【 0 1 4 3 】**

図 10 に示すように、RFCPU 511 は、アナログ回路部 512 とデジタル回路部 513 を有している。アナログ回路部 512 として、共振容量を有する共振回路 514、整流回路 515、定電圧回路 516、リセット回路 517、発振回路 518、復調回路 519 と、変調回路 520 を有している。デジタル回路部 513 は、RF インターフェース 521、制御レジスタ 522、クロックコントローラ 523、CPU インターフェース 524、中央処理ユニット 525、ランダムアクセスメモリ 526、読み出し専用メモリ 527 を有している。20

**【 0 1 4 4 】**

RFCPU 511 の動作の概要は以下の通りである。アンテナ 528 が受信した信号は共振回路 514 により誘導起電力を生じる。誘導起電力は、整流回路 515 を経て容量部 529 に充電される。この容量部 529 はセラミックコンデンサーや電気二重層コンデンサーなどのキャパシタで形成されていることが好ましい。容量部 529 は、RFCPU 511 を構成する基板に集積されている必要はなく、他の部品として RFCPU 511 に組み込むこともできる。30

**【 0 1 4 5 】**

リセット回路 517 は、デジタル回路部 513 をリセットし初期化する信号を生成する。例えば、電源電圧の上昇に遅延して立ち上がる信号をリセット信号として生成する。発振回路 518 は、定電圧回路 516 により生成される制御信号に応じて、クロック信号の周波数とデューティー比を変更する。復調回路 519 は、受信信号を復調する回路であり、変調回路 520 は、送信するデータを変調する回路である。

**【 0 1 4 6 】**

例えば、復調回路 519 はローパスフィルタで形成され、振幅変調（ASK）方式の受信信号を、その振幅の変動をもとに、二値化する。また、送信データを振幅変調（ASK）方式の送信信号の振幅を変動させて送信するため、変調回路 520 は、共振回路 514 の共振点を変化させることで通信信号の振幅を変化させている。40

**【 0 1 4 7 】**

クロックコントローラ 523 は、電源電圧または中央処理ユニット 525 における消費電流に応じてクロック信号の周波数とデューティー比を変更するための制御信号を生成している。電源電圧の監視は電源管理回路 530 が行っている。

**【 0 1 4 8 】**

アンテナ 528 から RFCPU 511 に入力された信号は復調回路 519 で復調された後、RF インターフェース 521 で制御コマンドやデータなどに分解される。制御コマンド50

は制御レジスタ 522 に格納される。制御コマンドには、読み出し専用メモリ 527 に記憶されているデータの読み出し、ランダムアクセスメモリ 526 へのデータの書き込み、中央処理ユニット 525 への演算命令などが含まれている。

#### 【0149】

中央処理ユニット 525 は、CPU インターフェース 524 を介して読み出し専用メモリ 527、ランダムアクセスメモリ 526、制御レジスタ 522 にアクセスする。CPU インターフェース 524 は、中央処理ユニット 525 が要求するアドレスより、読み出し専用メモリ 527、ランダムアクセスメモリ 526、制御レジスタ 522 のいずれかに対するアクセス信号を生成する機能を有している。

#### 【0150】

中央処理ユニット 525 の演算方式は、読み出し専用メモリ 527 に OS (オペレーティングシステム) を記憶させておき、起動とともにプログラムを読み出し実行する方式を採用することができる。また、専用回路で演算回路を構成して、演算処理をハードウェア的に処理する方式を採用することもできる。ハードウェアとソフトウェアを併用する方式では、専用の演算回路で一部の演算処理を行い、プログラムを使って、残りの演算を中央処理ユニット 525 が処理する方式を適用できる。

10

#### 【0151】

このような RFCPU は、結晶欠陥が低減され、結晶方位が一定の単結晶半導体層 112 によって集積回路が形成されているので、処理速度の高速化のみならず低消費電力化を図ることができる。それにより、電力を供給する容量部 529 を小型化しても長時間の動作が保証される。

20

#### 【0152】

##### (実施の形態 5)

本実施の形態では、本発明の一態様の SOI 基板を用いた表示装置について図 11 及び図 12 を参照して説明する。

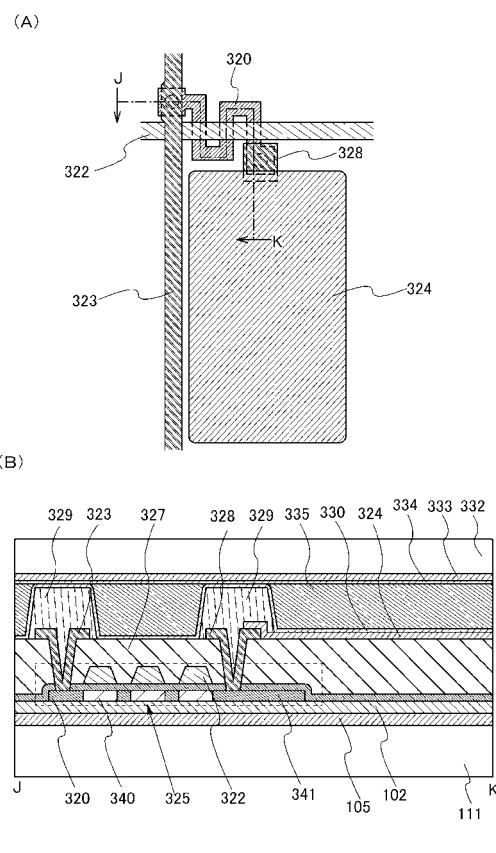

#### 【0153】

図 11 は液晶表示装置を説明するための図面である。図 11 (A) は液晶表示装置の画素の平面図であり、図 11 (B) は、J - K 切断線による図 11 (A) の断面図である。

#### 【0154】

図 11 (A) に示すように、画素は、単結晶半導体層 320、単結晶半導体層 320 と交差している走査線 322、走査線 322 と交差している信号線 323、画素電極 324、画素電極 324 と単結晶半導体層 320 を電気的に接続する電極 328 を有する。単結晶半導体層 320 は、本発明の一態様に係る SOI 基板の有する単結晶半導体層から形成された層であり、第 1 のエッチング処理及び第 2 のエッチング処理の後にレーザ光の照射により、平坦化及び結晶欠陥の低減が図られたものである。単結晶半導体層 320 は、画素の薄膜トランジスタ 325 を構成する。

30

#### 【0155】

SOI 基板には上記実施の形態 1 及び実施の形態 2 で示した SOI 基板が用いられている。図 11 (B) に示すように、支持基板 111 上に、絶縁膜 105 及び絶縁膜 102 を介して単結晶半導体層 320 が積層されている。支持基板 111 としては、ガラス基板を用いることができる。薄膜トランジスタ 325 の単結晶半導体層 320 は、SOI 基板の単結晶半導体層をエッチングにより素子分離して形成された膜である。単結晶半導体層 320 には、チャネル形成領域 340、不純物元素が添加された n 型の高濃度不純物領域 341 が形成されている。薄膜トランジスタ 325 のゲート電極は走査線 322 に含まれ、ソース電極およびドレイン電極の一方は信号線 323 に含まれている。

40

#### 【0156】

層間絶縁膜 327 上には、信号線 323、画素電極 324 および電極 328 が設けられている。層間絶縁膜 327 上には、柱状スペーサ 329 が形成されている。信号線 323、画素電極 324、電極 328 および柱状スペーサ 329 を覆って配向膜 330 が形成されている。対向基板 332 には、対向電極 333、対向電極 333 を覆う配向膜 334 が形

50

成されている。柱状スペーサ 329 は、支持基板 111 と対向基板 332 の隙間を維持するためには形成される。柱状スペーサ 329 によって形成される隙間に液晶層 335 が形成されている。信号線 323 および電極 328 と高濃度不純物領域 341との接続部は、コントラクトホールの形成によって層間絶縁膜 327 に段差が生じるので、この接続部では液晶層 335 の液晶の配向が乱れやすい。そのため、この段差部に柱状スペーサ 329 を形成して、液晶の配向の乱れを防ぐ。

#### 【0157】

本発明の一態様に係る SOI 基板の作製方法により作成された SOI 基板は結晶性が高いため、同一基板上に特性のばらつきの少ない、高性能なトランジスタを複数基板上に形成することが可能である。従って、本発明の一態様に係る SOI 基板を用いて液晶表示装置を作製することで、トランジスタごとの特性のばらつきを少なくすることができます。10

#### 【0158】

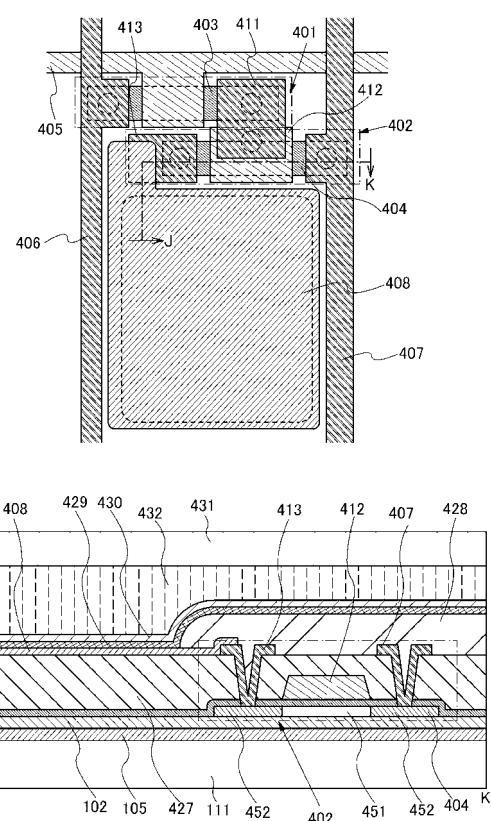

次に、エレクトロルミネンス表示装置（以下、EL 表示装置という。）について図 12 を参照して説明する。図 12 (A) は EL 表示装置の画素の平面図であり、図 12 (B) は、J - K 切断線による図 12 (A) の断面図である。

#### 【0159】

図 12 (A) に示すように、画素は、トランジスタでなる選択用トランジスタ 401、表示制御用トランジスタ 402、走査線 405、信号線 406、および電流供給線 407、画素電極 408 を含む。エレクトロルミネンス材料を含んで形成される層（EL 層）が一対の電極間に挟んだ構造の発光素子が各画素に設けられている。発光素子の一方の電極が画素電極 408 である。また、半導体膜 403 は、選択用トランジスタ 401 のチャネル形成領域、ソース領域およびドレイン領域が形成されている。半導体膜 404 は、表示制御用トランジスタ 402 のチャネル形成領域、ソース領域およびドレイン領域が形成されている。半導体膜 403、404 は、支持基板上に設けられた単結晶半導体層 302 から形成された層である。20

#### 【0160】

選択用トランジスタ 401において、ゲート電極は走査線 405 に含まれ、ソース電極またはドレイン電極の一方は信号線 406 に含まれ、他方は電極 410 として形成されている。表示制御用トランジスタ 402 は、ゲート電極 412 が電極 411 と電気的に接続され、ソース電極またはドレイン電極の一方は、画素電極 408 に電気的に接続される電極 413 として形成され、他方は、電流供給線 407 に含まれている。30

#### 【0161】

表示制御用トランジスタ 402 は p チャネル型の薄膜トランジスタである。図 12 (B) に示すように、半導体膜 404 には、チャネル形成領域 451、および p 型の高濃度不純物領域 452 が形成されている。なお、SOI 基板は、実施の形態 1 及び実施の形態 2 で作製した SOI 基板が用いられている。

#### 【0162】

表示制御用トランジスタ 402 のゲート電極 412 を覆って、層間絶縁膜 427 が形成されている。層間絶縁膜 427 上に、信号線 406、電流供給線 407、電極 411、413 などが形成されている。また、層間絶縁膜 427 上には、電極 413 に電気的に接続されている画素電極 408 が形成されている。画素電極 408 は周辺部が絶縁性の隔壁層 428 で囲まれている。画素電極 408 上には EL 層 429 が形成され、EL 層 429 上には対向電極 430 が形成されている。補強板として対向基板 431 が設けられており、対向基板 431 は樹脂層 432 により支持基板 111 に固定されている。40

#### 【0163】

EL 表示装置の階調の制御は、発光素子の輝度を電流で制御する電流駆動方式と、電圧での輝度を制御する電圧駆動方式とがあるが、電流駆動方式は、画素ごとでトランジスタの特性値の差が大きい場合、採用することは困難であり、そのためには特性のばらつきを補正する補正回路が必要になる。しかし、本発明の一態様に係る SOI 基板の作製方法により作製された SOI 基板は結晶欠陥がほとんどないため、同一基板上に特性のばらつき50

の少ない、高性能なトランジスタを複数基板上に形成することが可能である。従って、本発明の一態様に係るSOI基板を用いてEL表示装置を作製することで、選択用トランジスタ401および表示制御用トランジスタ402は画素ごとに特性のばらつきがなくなるため、電流駆動方式を採用することができる。

#### 【0164】

##### (実施の形態6)

本発明の一態様に係るSOI基板を用いてトランジスタ等の半導体装置を作製し、この半導体装置を用いてさまざまな電子機器を完成することができる。本発明の一態様に係るSOI基板に設けられた単結晶半導体層は結晶欠陥が低減されているため、活性層として用いることで、電気的特性が向上した半導体素子を製造することができる。また、当該単結晶半導体層は結晶欠陥が低減されているため、ゲート絶縁層との界面において、局在準位密度を低減させることができるとなる。さらに、単結晶半導体層が高い平坦性を有するため、単結晶半導体層上に、薄く、且つ高い絶縁耐圧を有するゲート絶縁層を形成することができ、作製される半導体素子の移動度の向上、S値の向上または短チャネル効果抑制を実現することができる。すなわち、本発明の一態様に係るSOI基板を用いることで、電流駆動能力が高く、かつ信頼性の高い半導体素子を作製することができる。その結果、最終製品としての電子機器をスループット良く、良好な品質で作製することができる。この半導体素子を用いて、さまざまな半導体装置を作製することができる。本実施の形態では、図面を用いて具体的な例を説明する。なお、本実施の形態において、上記実施の形態と同様の部分には同じ符号を付し、詳しい説明を省略する。

10

20

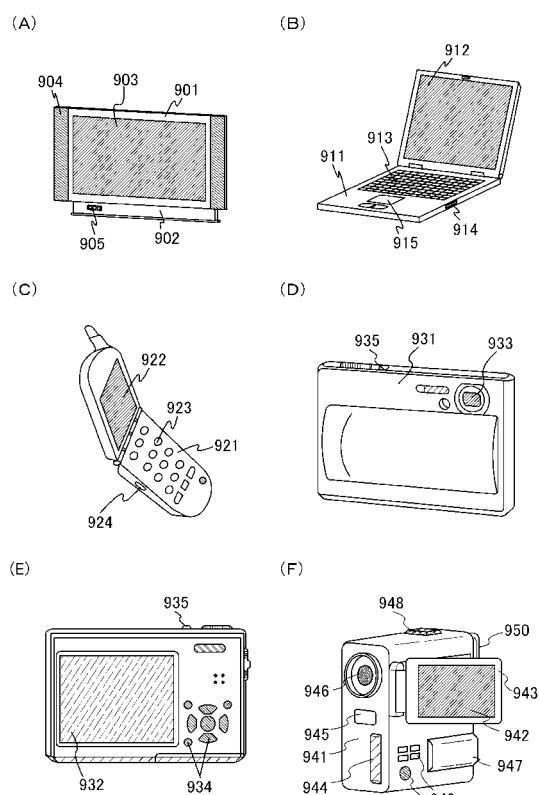

#### 【0165】

図13(A)は表示装置であり、筐体901、支持台902、表示部903、スピーカ部904、ビデオ入力端子905などを含む。この表示装置は、他の実施の形態で示した作製方法により形成したトランジスタを駆動ICや表示部903などに用いることにより作製される。なお、表示装置には液晶表示装置、発光表示装置などがあり、用途別にはコンピュータ用、テレビ受信用、広告表示用などの全ての情報表示用表示装置が含まれる。具体的には、ディスプレイ、ヘッドマウントディスプレイ、反射型プロジェクターなどを挙げることができる。

#### 【0166】

図13(B)はコンピュータであり、筐体911、表示部912、キーボード913、外部接続ポート914、ポインティングデバイス915などを含む。本発明の一態様を用いて作製されたトランジスタは、表示部912の画素部だけではなく、表示用の駆動IC、本体内部のCPU、メモリなどの半導体装置にも適用が可能である。

30

#### 【0167】

また、図13(C)は携帯電話であり、携帯用の情報処理端末の1つの代表例である。この携帯電話は筐体921、表示部922、操作キー923などを含む。本発明の一態様を用いて作製されたトランジスタは表示部922の画素部やセンサ部924だけではなく、表示用の駆動IC、メモリ、音声処理回路などに用いることができる。センサ部924は光センサ素子を有しており、センサ部924で得られる照度に合わせて表示部922の輝度コントロールを行うことや、センサ部924で得られる照度に合わせて操作キー923の照明を抑えることによって、携帯電話の消費電力を抑えることができる。

40

#### 【0168】

上記の携帯電話を初めとして、PDA(Personal Digital Assistant、情報携帯端末)、デジタルカメラ、小型ゲーム機、携帯型の音響再生装置などの電子機器に、本発明の一態様を用いて形成した半導体装置を用いることもできる。例えば、CPU、メモリ、センサなどの機能回路を形成することや、これらの電子機器の画素部や、表示用の駆動ICにも適用することが可能である。

#### 【0169】

また、図13(D)、(E)はデジタルカメラである。なお、図13(E)は、図13(D)の裏側を示す図である。このデジタルカメラは、筐体931、表示部932、レンズ

50

933、操作キー934、シャッターボタン935などを有する。本発明の一態様を用いて作製されたトランジスタは、表示部932の画素部、表示部932を駆動する駆動IC、メモリなどに用いることができる。

#### 【0170】

図13(F)はデジタルビデオカメラである。このデジタルビデオカメラは、本体941、表示部942、筐体943、外部接続ポート944、リモコン受信部945、受像部946、バッテリー947、音声入力部948、操作キー949、接眼部950などを有する。本発明の一態様を用いて作製されたトランジスタは、表示部942の画素部、表示部942を制御する駆動IC、メモリ、デジタル入力処理装置などに用いることができる。

#### 【0171】

この他にも、ナビゲーションシステム、音響再生装置、記録媒体を備えた画像再生装置などに用いることが可能である。これらの表示部の画素部や、表示部を制御する駆動IC、メモリ、デジタル入力処理装置、センサ部などの用途に、本発明の一態様を用いて作製されたトランジスタを用いることができる。

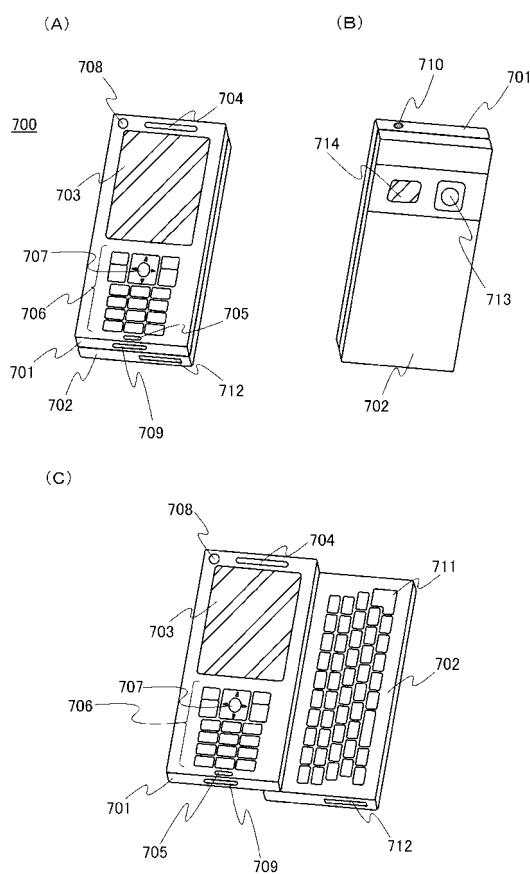

#### 【0172】

また、図14は、本発明の一態様を適用した携帯電話の別の一例であり、図14(A)が正面図、図14(B)が背面図、図14(C)が2つの筐体をスライドさせたときの正面図である。携帯電話700は、携帯電話と携帯情報端末の双方の機能を備えており、コンピュータを内蔵し、音声通話以外にも様々なデータ処理が可能な所謂スマートフォンである。

10

#### 【0173】

携帯電話700は、筐体701及び筐体702で構成されている。筐体701においては、表示部703、スピーカ704、マイクロフォン705、操作キー706、ポインティングデバイス707、カメラ用レンズ708、外部接続端子709及びイヤホン端子710等を備え、筐体702においては、キーボード711、外部メモリスロット712、裏面カメラ713、ライト714等により構成されている。また、アンテナは筐体701に内蔵されている。本発明の一態様を用いて作製された半導体素子は、表示部703の画素部、表示部703を駆動する駆動IC、メモリ、音声処理回路などに用いることができる。また、表示部703に、図11で説明した液晶表示装置又は図12で説明したEL表示装置を適用することで、表示むらが少なく画質の優れた表示部とすることができる。

20

#### 【0174】

また、携帯電話700には、上記の構成に加えて、非接触型ICチップ、小型記録装置等を内蔵していてもよい。

#### 【0175】

重なり合った筐体701と筐体702(図14(A)に示す。)は、スライドさせることができ、スライドさせることで図14(C)のように展開する。表示部703とカメラ用レンズ708を同一の面に備えているため、テレビ電話としての使用が可能である。また、表示部703をファインダーとして用いることで、裏面カメラ713及びライト714で静止画及び動画の撮影が可能である。

30

#### 【0176】

スピーカ704及びマイクロフォン705を用いることで、携帯電話700は、音声記録装置(録音装置)又は音声再生装置として使用することができる。また、操作キー706により、電話の発着信操作、電子メール等の簡単な情報入力操作、表示部に表示する画面のスクロール操作、表示部に表示する情報の選択等を行うカーソルの移動操作等が可能である。

40

#### 【0177】

また、書類の作成、携帯情報端末としての使用等、取り扱う情報が多い場合は、キーボード711を用いると便利である。更に、重なり合った筐体701と筐体702(図14(A))をスライドさせることで、図14(C)のように展開させることができる。携帯情報端末として使用する場合には、キーボード711及びポインティングデバイス707を

50

用いて、円滑な操作でマウスの操作が可能である。外部接続端子 709 は A C アダプタ及び U S B ケーブル等の各種ケーブルと接続可能であり、充電及びパーソナルコンピュータ等とのデータ通信が可能である。また、外部メモリスロット 712 に記録媒体を挿入し、より大量のデータ保存及び移動が可能になる。

【 0178 】

筐体 702 の裏面(図 14(B))には、裏面カメラ 713 及びライト 714 を備え、表示部 703 をファインダーとして静止画及び動画の撮影が可能である。

【 0179 】

また、上記の機能構成に加えて、赤外線通信機能、U S B ポート、テレビワンセグ受信機能、非接触 I C チップ又はイヤホンジャック等を備えたものであってもよい。

10

【 0180 】

以上のように、本発明の一態様により作製された半導体装置の適用範囲は極めて広く、本発明の一態様に係る S O I 基板を材料として、あらゆる分野の電子機器に用いることができる。

【 実施例 1 】

【 0181 】

以下において、本発明の一態様に関し実施例に基づいて更に詳しく説明する。本実施例では、単結晶半導体層を形成し、プラズマ処理を行うことにより単結晶半導体層に与えるプラズマの影響について調べた結果について説明する。プラズマの影響について調べるために、単結晶半導体層に含まれるキャリアのライフタイムを測定した。

20

【 0182 】

ここで、「ライフタイム」とは、半導体中に生成したキャリアが再結合して消滅するまでの平均寿命を示す。例えば、半導体ウエハ(シリコン)に光を照射すると、半導体中に電子及び正孔(キャリア)が生成される。生成された電子と正孔は再結合し、消滅する。このように、キャリアが生成し、再結合して消滅するまでの平均寿命が「ライフタイム」といわれる。なお、「ライフタイム」は、再結合ライフタイム、及びキャリアライフタイムとも呼ばれている。

【 0183 】

光照射などで半導体ウエハに過剰な電子と正孔のキャリアを注入したとき、半導体ウエハ中に格子欠陥や重金属不純物などによるトラップ(捕獲)準位があると、これらのキャリアはトラップを介して再結合するため、ライフタイムは低下する。つまり、ライフタイムが向上することは、キャリア移動度の向上にもつながり、完成するトランジスタの電気的特性(高速動作など)の向上を実現することができる。

30

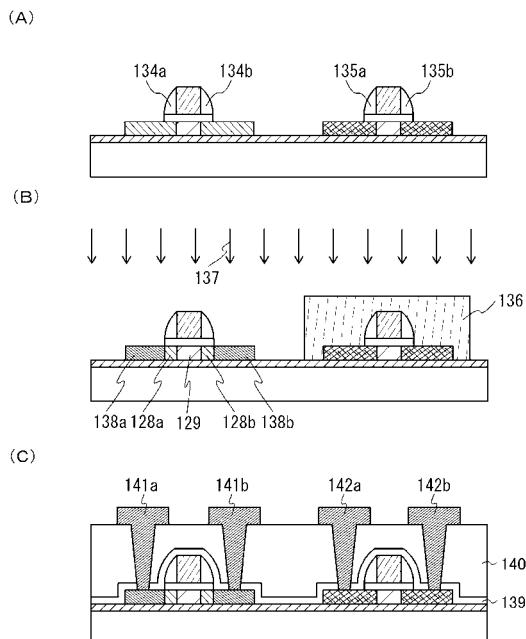

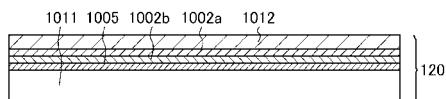

【 0184 】

本実施例で用いた試料である S O I 基板の構成について説明する。図 15 は、本実施例で特性を評価した S O I 基板の構成を示す断面図である。図 15 に示す S O I 基板は、上記実施の形態 1 で説明した図 1 の工程を経て作製したものであり、ガラス基板上に、絶縁膜を介して単結晶シリコン層が接着されている。なお、本実施例では、支持基板としてガラス基板、単結晶半導体基板として単結晶シリコン基板を用いた。以下、S O I 基板の作製方法を簡単に説明する。

40

【 0185 】

まず、単結晶シリコン層 1012 を形成するための単結晶シリコン基板 1001 を準備した。単結晶シリコン基板の一表面上に、酸化処理を行い、単結晶シリコン基板の表面に酸化膜を 100 nm 形成した。酸化処理は、酸化性雰囲気中に塩素元素を含むガスを添加して行った。

【 0186 】

次に、イオンドーピング装置を用いて単結晶シリコン基板にイオンを照射し、該単結晶シリコン基板に脆化領域を形成した。脆化領域を形成する際、原料ガスとしては、100% 水素ガスを用い、水素ガスを励起して生成されたプラズマ中のイオンを質量分離せずに、電圧で加速して、単結晶シリコン基板に照射した。なお、イオンの照射は、酸化窒化シリ

50

コン層 1002a、及び窒化酸化シリコン層 1002b が形成されている面から行った。このときのドーピング条件は、電源出力 100W、加速電圧 40kV、ドーズ量は、 $2 \cdot 2 \times 10^{16}$  ions/cm<sup>2</sup>とした。

#### 【0187】

イオンドーピング装置では、水素ガスを励起することで、H<sup>+</sup>イオン、H<sub>2</sub><sup>+</sup>イオン、H<sub>3</sub><sup>+</sup>イオン、という 3 種類のイオン種が生成される。本実施例では、水素ガスを励起して生成された全てのイオン種を電圧で加速し、単結晶シリコン基板に照射した。このとき水素ガスから生成されたイオン種のうち、80%程度がH<sub>3</sub><sup>+</sup>イオンである。また、分離される単結晶シリコン層 1012 が 100nm 以上 120nm 以下となるように、脆化領域が形成される膜厚方向の深さを制御した。

10

#### 【0188】

絶縁層を形成した単結晶シリコン基板 1001 と、ガラス基板 1011 を純水中で超音波洗浄し、続けてオゾンを含む純水で洗浄した後、絶縁層を間に挟んで、単結晶シリコン基板とガラス基板とを貼り合わせた。すなわち、ガラス基板 1011 の一表面と、単結晶シリコン基板 1001 の脆化領域が形成された側の酸化シリコン層 1005 の一表面とを接合面として密着させ、貼り合わせた。

#### 【0189】

ガラス基板と単結晶シリコン基板を貼り合わせたものに、抵抗加熱式の縦型炉に 600 の加熱処理を行って、単結晶シリコン基板に形成された脆化領域において、単結晶シリコン層 1012 を分離した。絶縁層を間に挟んで単結晶シリコン層 1012 が貼り合わされたガラス基板 1011 が得られた。

20

#### 【0190】

次に、得られた単結晶シリコン層 1012 表面に、第 1 のドライエッチング処理を行い、単結晶シリコン層の表面を 5nm ~ 15nm 程度除去した。第 1 のドライエッチングの条件は、エッチングガスである塩素の流量 100sccm、コイル型の電極に投入する電力 150W、下部電極（バイアス側）に投入する電力 40W、反応圧力 1.0Pa、下部電極の温度を 70 として処理した。

#### 【0191】

次に、ドライエッチングを行った後の単結晶シリコン層にレーザ光を照射した。レーザ光の照射条件は、波長 308nm のビームを発振する XeCl エキシマレーザを用いて、パルス幅 25ns とし、繰り返し周波数 30Hz とした。

30

#### 【0192】

次に、レーザ光が照射された単結晶シリコン層 1012 に、第 2 のドライエッチング処理を行い、単結晶シリコン層を 40 ~ 45nm 程度除去して、単結晶シリコン層の膜厚が 55 ~ 65nm となるようにした。第 2 のドライエッチングの条件は、エッチングガスである塩素の流量 100sccm、コイル型の電極に投入する電力は 150W、下部電極に投入する電力 40W、反応圧力 1.0Pa、下部電極の温度を 40 として処理した。以上により得られた単結晶シリコン層を試料 A とした。

#### 【0193】

次に、試料 A と同様の作製方法で形成した単結晶シリコン層に対して、熱処理を行った単結晶シリコン層を用意した。熱処理は、600、4 時間行った。以上により得られた単結晶シリコン層を試料 B とした。

40

#### 【0194】

次に、試料 A と同様の作製方法で形成した単結晶シリコン層に対して、水蒸気を用いてプラズマ処理を行った単結晶シリコン層を用意した。プラズマ処理の条件は、H<sub>2</sub>O の流量 300sccm、コイル型の電極に投入する電力 1800W、反応圧力 66.5Pa、下部電極の温度を 250 として 180 秒処理した。以上により得られた単結晶シリコン層を試料 C とした。

#### 【0195】

試料 A、試料 B、試料 C の単結晶シリコン層に含まれるキャリアのライフタイムをマイク

50

口波光導電減衰法 (Microwave Photo Conductivity Decay :  $\mu$ -PCD法) により評価した。 $\mu$ -PCD法とは、非接触でライフタイムを評価できる測定法のひとつであり、単結晶シリコン層にマイクロ波及びパルスレーザ光を照射して、単結晶シリコン層に過剰のキャリアが生成されてから当該キャリアが再結合して消滅するまでのライフタイムを測定する方法である。キャリアの生成により、単結晶シリコン層の導電率が増加するため、単結晶シリコン層に照射しているマイクロ波の反射率が過剰のキャリア密度に対して変化する。当該マイクロ波の反射率の減少時間を測定することで、キャリアのライフタイムを測定することができる。

#### 【0196】

本実施例では、マイクロ波を用いた結晶性評価装置（株式会社コベルコ科研製）を用い、試料A、試料B、試料Cに13.56MHzのマイクロ波及び波長が349nmのYLGレーザの3倍波を照射して、マイクロ波の位相差を測定する電圧計でキャリアの発生により変化する反射強度の経時変化を測定した。測定は、単結晶シリコン層の分離後、第1のドライエッチング処理後、レーザ照射後、第2のドライエッチング処理後、熱処理後又はプラズマ処理後の工程毎に行った。測定値のピークが急峻であるため、キャリアの再結合による消滅時間を測定することができない。しかし、反射強度のピーク値が大きいほど相対的にキャリアのライフタイムが長く、結晶性が良いことを示している。そのため、反射強度のピーク値により各試料のキャリアのライフタイムを比較した。なお、本実施例で比較した反射強度のピーク値は規格化されている。反射強度のピーク値は、単結晶シリコン層の膜厚に比例するため、膜厚でピーク値を補正することにより結晶性の情報を抽出することができる。従って、規格化されたピーク値は、反射強度ピーク値を単結晶シリコン層の膜厚(nm)で割ることにより求めることができる。

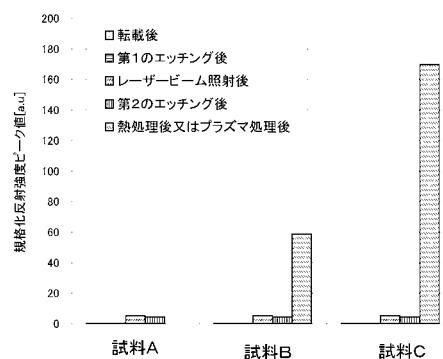

#### 【0197】

表1及び図16に、試料A、試料B、試料Cのライフタイム測定結果を示す。図16において横軸は、試料A、試料B、試料Cであり、縦軸は反射強度ピーク値である。反射強度のピーク値が大きいほど、ライフタイムが長いことを表している。

#### 【0198】

##### 【表1】

|                   | 試料A         |            | 試料B         |            | 試料C         |            |

|-------------------|-------------|------------|-------------|------------|-------------|------------|

|                   | 規格化<br>ピーク値 | 膜厚<br>(nm) | 規格化<br>ピーク値 | 膜厚<br>(nm) | 規格化<br>ピーク値 | 膜厚<br>(nm) |

| 転載後               | 0.265       | 122        | 0.291       | 123        | 0.273       | 122        |

| 第1のエッチング<br>後     | 0.225       | 108        | 0.249       | 108        | 0.228       | 107        |

| レーザ光照射後           | 5.14        | 108        | 5.39        | 108        | 5.27        | 107        |

| 第2のエッチング<br>後     | 4.45        | 62.2       | 4.36        | 63.8       | 4.31        | 61.2       |

| 熱処理後又は<br>プラズマ処理後 | -           | 62.2       | 58.9        | 63.8       | 170         | 61.2       |

#### 【0199】

表1及び図16から、試料C、試料B、試料Aの順に第2のエッチング後の反射強度ピーク値が大きいことがわかった。すなわち、第2のドライエッチングを行った後に水蒸気を用いてプラズマ処理を行った単結晶シリコン層が最もライフタイムが長いことがわかった。したがって、第2のドライエッチングの後、水蒸気を用いてプラズマ処理を行うことにより、単結晶シリコン層のライフタイムを飛躍的に向上させることができたことがわかった。

#### 【0200】

以上の結果から、本発明の一態様を適用することで、耐熱性の低い支持基板を用いた場合であっても、十分に結晶欠陥を低減させることができることが確認できた。また、結晶性

10

20

30

40

50

に優れたS O I基板を歩留まり良く作製することができることが確認できた。

**【実施例2】**

**【0201】**

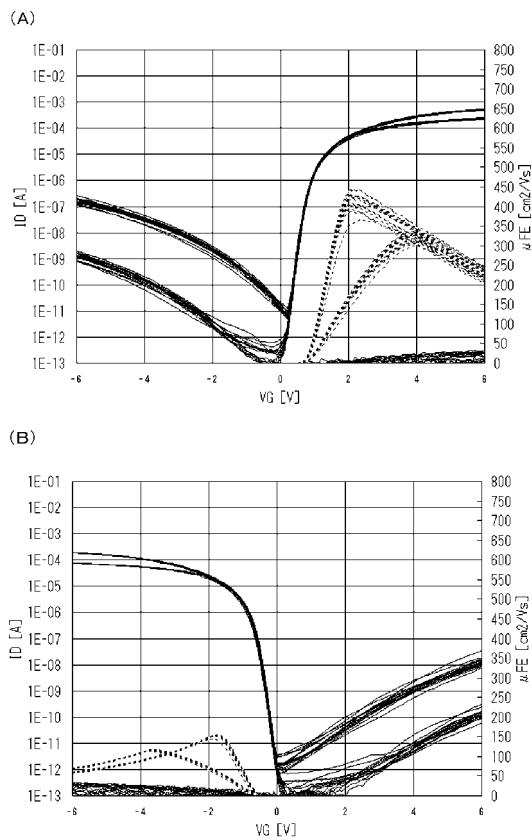

本実施例では、第2のエッチング処理が行われた後に、プラズマ処理が行われた単結晶半導体層を用いて薄膜トランジスタの特性について、図18に示す結果を用いて説明する。以下に、本実施例で用いた薄膜トランジスタについて説明する。

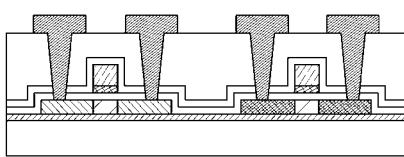

**【0202】**

図17に、本実施例で作製した薄膜トランジスタの構造を示す。本実施例の薄膜トランジスタの構造はシングルゲート構造である。ガラス基板上に、酸化処理により形成された酸化シリコン膜（膜厚100nm）が形成されている。また、シリコン層上にゲート絶縁層（膜厚10nmの酸化シリコン層と10nmの酸化窒化シリコン層の積層）、ゲート絶縁層上にゲート電極層（膜厚30nmの窒化タンタル層と膜厚370nmのタンゲステン層との積層）が形成されている。シリコン層には、ソース領域およびドレイン領域（n型を付与する不純物元素としてリンを含む不純物領域）に接続するソース電極層及びドレイン電極層（膜厚60nmのチタン層、膜厚40nmの窒化チタン層、膜厚300nmのアルミニウム層、膜厚100nmのチタン層の順に積層）が形成されている。また、シリコン層のソース領域およびドレイン領域（p型を付与する不純物元素として硼素を含む不純物領域）に接続するソース電極層及びドレイン電極層（膜厚60nmのチタン層、膜厚40nmの窒化チタン層、膜厚300nmのアルミニウム層、膜厚100nmのチタン層の順に積層）が形成されている。さらに、薄膜トランジスタ上は層間絶縁層（膜厚50nmの酸化シリコン膜、膜厚300nmの窒化酸化シリコン膜、膜厚450nmの酸化シリコン膜の順に積層）が形成されている。本実施例に係る薄膜トランジスタは、チャネル長Lを10μm、チャネル幅Wを8μmとなるように形成した。

**【0203】**

図18に、上記薄膜トランジスタのドレイン電流 - ゲート電圧（ID - VG）特性、電界効果移動度 - ゲート電圧（μFE - VG）特性を測定した結果を示す。図18（A）はnチャネル型薄膜トランジスタの測定結果、図18（B）はpチャネル型薄膜トランジスタの結果である。ここで、ID - VG特性を示すグラフは、横軸は電圧（V）を、縦軸は電流（A）を示している。また、VG - μFE特性を示すグラフは、横軸は電圧（V）を、縦軸は電界効果移動度（cm<sup>2</sup>/Vs）を示している。測定は、ドレイン電圧（VD）は、1Vと3Vとし、ゲート電圧（VG）を-6V乃至6Vまで変動させて行った。なお、図18は、16ポイント測定した実験結果である。

**【0204】**

以上の結果から、本発明の一態様を適用することで、耐熱性の低い支持基板を用いた場合であっても、十分に結晶欠陥を低減させることができることが確認できた。また、結晶性に優れたS O I基板を歩留まり良く作製することができることが確認できた。また、このようなS O I基板を用いて、優れた特性の半導体装置を作製することができることが確認できた。

**【符号の説明】**

**【0205】**

- 101 単結晶半導体基板

- 102 絶縁膜

- 102 a 絶縁膜

- 102 b 絶縁膜

- 103 脆化領域

- 104 単結晶半導体基板

- 105 絶縁膜

- 111 支持基板

- 112 単結晶半導体層

- 113 絶縁膜

10

20

30

40

50

|         |             |    |

|---------|-------------|----|

| 1 2 0   | S O I 基板    |    |

| 1 2 1   | 単結晶半導体層     |    |

| 1 2 2   | 単結晶半導体層     |    |

| 1 2 3   | 絶縁膜         |    |

| 1 2 4   | ゲート電極       |    |

| 1 2 5   | ゲート電極       |    |

| 1 2 6   | マスク         |    |

| 1 2 7   | 不純物元素       |    |

| 1 2 8 a | n型不純物領域     | 10 |

| 1 2 8 b | n型不純物領域     |    |

| 1 2 9   | チャネル形成領域    |    |

| 1 3 0   | マスク         |    |

| 1 3 1   | 不純物元素       |    |

| 1 3 2 a | p型不純物領域     |    |

| 1 3 2 b | p型不純物領域     |    |

| 1 3 3   | チャネル形成領域    |    |

| 1 3 4 a | 絶縁膜         |    |

| 1 3 4 b | 絶縁膜         |    |

| 1 3 5 a | 絶縁膜         |    |

| 1 3 5 b | 絶縁膜         | 20 |

| 1 3 6   | マスク         |    |

| 1 3 7   | 不純物元素       |    |

| 1 3 8 a | n型の高濃度不純物領域 |    |

| 1 3 8 b | n型の高濃度不純物領域 |    |

| 1 3 9   | 絶縁膜         |    |

| 1 4 0   | 層間絶縁膜       |    |

| 1 4 1 a | 配線          |    |

| 1 4 1 b | 配線          |    |

| 1 4 2 a | 配線          |    |

| 1 4 2 b | 配線          | 30 |

| 2 0 2   | プラズマ発生室     |    |

| 2 0 3   | 放電管         |    |

| 2 0 4   | 処理ガス導入管     |    |

| 2 0 5   | 放電コイル       |    |

| 2 0 6   | R F 電源      |    |

| 2 0 7   | ダウンフロー室     |    |

| 2 0 8   | ヒータ         |    |

| 2 0 9   | 排気口         |    |

| 2 1 0   | 真空容器        |    |

| 3 0 2   | 単結晶半導体層     | 40 |

| 3 2 0   | 単結晶半導体層     |    |

| 3 2 2   | 走査線         |    |

| 3 2 3   | 信号線         |    |

| 3 2 4   | 画素電極        |    |

| 3 2 5   | 薄膜トランジスタ    |    |

| 3 2 7   | 層間絶縁膜       |    |

| 3 2 8   | 電極          |    |

| 3 2 9   | 柱状スペーサ      |    |

| 3 3 0   | 配向膜         |    |

| 3 3 2   | 対向基板        | 50 |

|       |              |    |

|-------|--------------|----|

| 3 3 3 | 対向電極         |    |

| 3 3 4 | 配向膜          |    |

| 3 3 5 | 液晶層          |    |

| 3 4 0 | チャネル形成領域     |    |

| 3 4 1 | 高濃度不純物領域     |    |

| 4 0 1 | 選択用トランジスタ    |    |

| 4 0 2 | 表示制御用トランジスタ  |    |

| 4 0 3 | 半導体膜         |    |

| 4 0 4 | 半導体膜         |    |

| 4 0 5 | 走査線          | 10 |

| 4 0 6 | 信号線          |    |

| 4 0 7 | 電流供給線        |    |

| 4 0 8 | 画素電極         |    |

| 4 1 0 | 電極           |    |

| 4 1 1 | 電極           |    |

| 4 1 2 | ゲート電極        |    |

| 4 1 3 | 電極           |    |

| 4 2 7 | 層間絶縁膜        |    |

| 4 2 8 | 隔壁層          |    |

| 4 2 9 | E L 層        | 20 |

| 4 3 0 | 対向電極         |    |

| 4 3 1 | 対向基板         |    |

| 4 3 2 | 樹脂層          |    |

| 4 5 1 | チャネル形成領域     |    |

| 4 5 2 | 高濃度不純物領域     |    |

| 5 0 0 | マイクロプロセッサ    |    |

| 5 0 1 | 演算回路         |    |

| 5 0 2 | 演算回路制御部      |    |

| 5 0 3 | 命令解析部        |    |

| 5 0 4 | 制御部          | 30 |

| 5 0 5 | タイミング制御部     |    |

| 5 0 6 | レジスタ         |    |

| 5 0 7 | レジスタ制御部      |    |

| 5 0 8 | バスインターフェース   |    |

| 5 0 9 | 専用メモリ        |    |

| 5 1 0 | メモリインターフェース  |    |

| 5 1 1 | R F C P U    |    |

| 5 1 2 | アナログ回路部      |    |

| 5 1 3 | デジタル回路部      |    |

| 5 1 4 | 共振回路         | 40 |

| 5 1 5 | 整流回路         |    |

| 5 1 6 | 定電圧回路        |    |

| 5 1 7 | リセット回路       |    |

| 5 1 8 | 発振回路         |    |

| 5 1 9 | 復調回路         |    |

| 5 2 0 | 変調回路         |    |

| 5 2 1 | R F インターフェース |    |

| 5 2 2 | 制御レジスタ       |    |

| 5 2 3 | クロックコントローラ   |    |

| 5 2 4 | インターフェース     | 50 |

|       |             |    |

|-------|-------------|----|

| 5 2 5 | 中央処理ユニット    |    |

| 5 2 6 | ランダムアクセスメモリ |    |

| 5 2 7 | 専用メモリ       |    |

| 5 2 8 | アンテナ        |    |

| 5 2 9 | 容量部         |    |

| 5 3 0 | 電源管理回路      |    |

| 7 0 0 | 携帯電話        |    |

| 7 0 1 | 筐体          |    |

| 7 0 2 | 筐体          |    |

| 7 0 3 | 表示部         | 10 |

| 7 0 4 | スピーカ        |    |

| 7 0 5 | マイクロフォン     |    |

| 7 0 6 | 操作キー        |    |

| 7 0 7 | ポインティングデバイス |    |

| 7 0 8 | カメラ用レンズ     |    |

| 7 0 9 | 外部接続端子      |    |

| 7 1 0 | イヤホン端子      |    |

| 7 1 1 | キー ボード      |    |

| 7 1 2 | 外部メモリスロット   |    |

| 7 1 3 | 裏面カメラ       | 20 |

| 7 1 4 | ライト         |    |

| 9 0 1 | 筐体          |    |

| 9 0 2 | 支持台         |    |

| 9 0 3 | 表示部         |    |

| 9 0 4 | スピーカ部       |    |

| 9 0 5 | ビデオ入力端子     |    |

| 9 1 1 | 筐体          |    |

| 9 1 2 | 表示部         |    |

| 9 1 3 | キー ボード      |    |

| 9 1 4 | 外部接続ポート     | 30 |

| 9 1 5 | ポインティングデバイス |    |

| 9 2 1 | 筐体          |    |

| 9 2 2 | 表示部         |    |

| 9 2 3 | 操作キー        |    |

| 9 2 4 | センサ部        |    |

| 9 3 1 | 筐体          |    |

| 9 3 2 | 表示部         |    |

| 9 3 3 | レンズ         |    |

| 9 3 4 | 操作キー        |    |

| 9 3 5 | シャッター ボタン   | 40 |

| 9 4 1 | 本体          |    |

| 9 4 2 | 表示部         |    |

| 9 4 3 | 筐体          |    |

| 9 4 4 | 外部接続ポート     |    |

| 9 4 5 | リモコン受信部     |    |

| 9 4 6 | 受像部         |    |

| 9 4 7 | パッテリー       |    |

| 9 4 8 | 音声入力部       |    |

| 9 4 9 | 操作キー        |    |

| 9 5 0 | 接眼部         | 50 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

(56)参考文献 特開2005-203596(JP,A)

特開2007-194345(JP,A)

特開2007-201430(JP,A)

特開平11-340444(JP,A)

特開2007-142229(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/02

H01L 21/20

H01L 21/322

H01L 27/12