(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3869849号

(P3869849)

(45) 発行日 平成19年1月17日(2007.1.17)

(24) 登録日 平成18年10月20日(2006.10.20)

(51) Int.C1.

F 1

HO1L 23/12 (2006.01)

HO1L 23/50 (2006.01)HO1L 23/12 501T

HO1L 23/50 R

請求項の数 1 (全 12 頁)

(21) 出願番号 特願2006-72498 (P2006-72498)

(22) 出願日 平成18年3月16日 (2006.3.16)

(62) 分割の表示 特願2001-78791 (P2001-78791)

の分割

原出願日 平成13年3月19日 (2001.3.19)

(65) 公開番号 特開2006-196922 (P2006-196922A)

(43) 公開日 平成18年7月27日 (2006.7.27)

審査請求日 平成18年4月13日 (2006.4.13)

(31) 優先権主張番号 特願2000-124102 (P2000-124102)

(32) 優先日 平成12年4月25日 (2000.4.25)

(33) 優先権主張国 日本国 (JP)

早期審査対象出願

(73) 特許権者 000164461

九州日立マクセル株式会社

福岡県田川郡福智町伊方4680番地

(73) 特許権者 500191761

トレックス・セミコンダクター株式会社

東京都中央区日本橋茅場町一丁目13番1

2号

(72) 発明者 木村 浩

東京都江東区越中島1丁目2-7 トレッ

クス・セミコンダクター株式会社東京支店

内

審査官 坂本 薫昭

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

可撓性平板状の金属基板に、パターニングされた金属層を形成した電着フレームを形成する工程と、前記電着フレームのパターニングされた前記金属層に複数の半導体素子を隣接して搭載する工程と、前記パターニングされた金属層に搭載される各半導体素子間に形成された外部導出用の金属層に、前記隣接する各半導体素子の電極パッドをワイヤで所定間隔を設けて電気的に共通接続するワイヤボンディング工程と、前記電着フレームに搭載されて配線がなされた半導体素子を樹脂封止する樹脂封止工程と、前記金属基板を剥離して樹脂封止体を得る剥離工程と、前記半導体素子が複数封止された樹脂封止体を、パターニングされた金属層の切断マークの間により切断部位が設定され、切断部位を切断することによって個々の半導体装置に切断する切り出し工程とを含む半導体装置の製造方法であって、

前記金属層は、金属基板の一面にレジスト膜をパターンニングして、金属層を形成する金属基板面を露呈させて、薄膜層を電着して形成した後に薄膜金属層が形成されたものであり、

また、半導体素子が搭載される金属層と外部導出用の金属層の形成領域の外周において、前記金属層の切断マーク間に切断部位を設定したことを特徴とする半導体装置の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

**【0001】**

本発明は、半導体装置、その製造方法及び電着フレームに関し、特にリードレス表面実装型の樹脂封止された半導体装置と、その製造方法、及び半導体素子搭載用の電着フレームに関するものである。

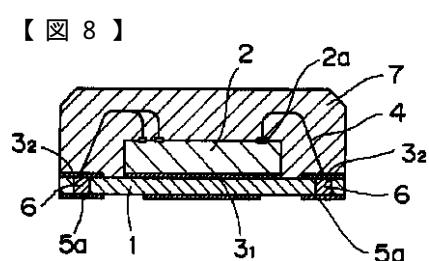

**【背景技術】****【0002】**

図8は、従来の半導体装置を示す断面図であり、この半導体装置は、樹脂封止したリードレス表面実装型の半導体装置である。同図において、ガラスエポキシ基板（又はセラミック基板）1の一面に金属層3<sub>1</sub>、3<sub>2</sub>が形成され、かつ金属層3<sub>2</sub>に対応するガラスエポキシ基板1の裏面に電極金属層5aが形成され、金属層3<sub>2</sub>と電極金属層5aとがスルーホール6で電気的に接続されている。ガラスエポキシ基板1の一面の金属層3<sub>1</sub>には、半導体素子2が接着され、半導体素子2の電極パッド2aと金属層3<sub>2</sub>とがワイヤ4で電気的に接続されている。ワイヤ4で配線がなされた半導体素子2は、エポキシ樹脂7で樹脂封止されている。10

**【発明の開示】****【発明が解決しようとする課題】****【0003】**

従来のリードレス表面実装型の半導体装置では、図8に示したように、ガラスエポキシ基板1に多数のスルーホール6が形成され、ガラスエポキシ基板1上に金属層3<sub>1</sub>が多数形成され、それぞれに半導体素子2が接着されてワイヤ4で電極パッド2aと金属層3<sub>2</sub>との配線がなされている。この半導体装置の製造工程では、一枚のガラスエポキシ基板に数百個単位で半導体素子が搭載されてワイヤボンディングされて、樹脂封止されている。従って、この構造の半導体装置では、スルーホール6の個数が半導体素子2の個数の数倍の数となり、スルーホール形成のための製造工数を無視することができず、この種の半導体装置の製造原価が高騰する要因となっていた。20

**【0004】**

また、従来のリードレス表面実装型の半導体装置では、スルーホールが形成されており、隣接する半導体素子間の隙間にスルーホールを形成するには、半導体素子間の隙間にスルーホールを形成するための領域を用意しなければならないので、実質的に一枚のガラスエポキシ基板に搭載される半導体素子の個数は制限され、製造原価を高騰させる要因となっていた。30

**【0005】**

更に、従来のリードレス表面実装型の半導体装置では、ガラスエポキシ基板上に半導体素子が搭載されて樹脂封止されている。そのため、半導体素子の動作時に発生した熱を発散させることができずガラスエポキシ基板に蓄積され、熱の放熱性が悪いという欠点があった。

**【0006】**

本発明は、上記のような課題に鑑みてなされたものであって、リードレス表面実装型の半導体装置であって、製造原価が安価であって、放熱性が良い半導体装置、その製造方法及び電着フレームを提供することを目的とするものである。40

**【課題を解決するための手段】****【0007】**

本発明は、上記課題を達成したものであり、請求項1の発明は、金属層に接着された半導体素子と、該半導体素子上の電極パッドと外部導出用の金属層とを電気的に接続するワイヤと、該ワイヤで配線を行った該半導体素子を封止する樹脂パッケージとを具備し、該半導体素子が接着されている金属層裏面と前記外部導出用の金属層裏面とが該樹脂パッケージ底面と同一平面であることを特徴とする半導体装置である。

**【0008】**

請求項1の発明によれば、樹脂パッケージ内に封止されている半導体素子が樹脂パッケージから露出する金属膜に搭載され、その外部導出用の金属層の底面も樹脂パッケージ底50

面より露呈したリードレス構造の半導体装置であり、ガラスエポキシ基板やセラミック基板が使用されていないので、半導体装置の高さを低背とすることができますため半導体素子から発生する熱の放熱性がよい利点がある。これら金属層は、薄膜状の金属層であり、リードを用いた半導体装置と比較して、熱伝導性が良好なリードレス型の半導体装置である。また、この半導体装置は、高価な基板を使用する必要がないので、比較的安価な半導体装置とすることができます。しかも、半導体装置裏面の金属層と樹脂パッケージとが同一平面（面一）であり、この半導体装置を回路基板に実装した際の回路基板との密着性が良く、しかも半導体素子から発生する熱が回路基板を介して放散し易い。さらに外部導出用の金属層裏面には、必要に応じて、極めて薄い平坦な電極金属層を成膜してもよい

【0009】

10

また、請求項2の発明は、半導体素子が接着される金属層が該半導体素子底面の面積より広い面積であることを特徴とする請求項1に記載の半導体装置である。

【0010】

請求項2の発明によれば、半導体素子が接着される金属層が半導体素子の底面の面積より広い面積であるので、樹脂パッケージの表面から半導体素子との沿面距離を充分に設けることができ、半導体素子の耐湿特性を高めることができる。

【0011】

また、請求項3の発明は、半導体素子が接着される金属層の膜厚を厚くし、かつ前記金属層の面積が該半導体素子底面の面積より狭いことを特徴とする請求項1に記載の半導体装置である。

20

【0012】

請求項3の発明によれば、半導体素子が接着される金属層の膜厚を厚くすることで、樹脂パッケージの底面から半導体素子までの沿面距離を充分に形成して、半導体装置としての耐湿性を高めることができるとともに、比較的サイズの大きな半導体素子を樹脂封止することができる。さらにまた、金属層の膜厚を厚くすることで、半導体素子を樹脂パッケージ内中央に配置させることができる。従って、半導体装置に熱ストレスが加わったとしても樹脂パッケージにひび割れが発生し難い。

【0013】

また、請求項4の発明は、樹脂パッケージ底面に前記外部導出用の金属層が独立して存在することを特徴とする請求項1, 2又は3に記載の半導体装置である。

30

【0014】

請求項4の発明によれば、外部導出用の金属層の露呈面の形状を独立した不定形な任意の形状とすることができます。無論、金属層を連続するように形成することができる。

【0015】

また、請求項5の発明は、可撓性平板状の金属基板に、パターニングされた金属層を形成した電着フレームを形成する工程と、前記電着フレームがパターニングされた前記金属層に複数の半導体素子を隣接して搭載する工程と、前記パターニングされた金属層に搭載される各半導体素子間に形成された外部導出用の金属層に、前記隣接する各半導体素子の電極パッドをワイヤで所定間隔を設けて電気的に共通接続するワイヤボンディング工程と、前記電着フレームに搭載されて配線がなされた半導体素子を樹脂封止する樹脂封止工程と、前記金属基板を剥離して樹脂封止体を得る剥離工程と、前記半導体素子が複数封止された樹脂封止体を、パターニングされた金属層の切断マークで個々の半導体装置に切断する切り出し工程と、を含むことを特徴とする半導体装置の製造方法である。

40

【0016】

請求項5の発明によれば、ガラスエポキシ基板等の基板を用いることなく、可撓性平板状の金属基板を利用して、半導体装置を製造する製造方法であり、電着フレームの可撓性平板状の金属基板を剥離することによって、多数の半導体素子が樹脂封止された樹脂封止体を形成することができる。金属基板が可撓性を有するので、樹脂封止体から金属基板を剥離する際のストレスが加わり難い。

【0017】

50

また、請求項 6 の発明は、半導体装置を切断する切り出し工程後、前記樹脂封止体の裏面の金属層に外部導出用の金属層を成膜する成膜工程を有することを特徴とする請求項 5 に記載の半導体装置の製造方法である。

#### 【 0 0 1 8 】

請求項 6 の発明によれば、必要に応じて、樹脂封止体の底面から露呈する金属層に電解メッキまたは無電解メッキを利用する半導体装置の製造方法であり、極めて薄い金属薄膜層を形成することで、回路基板のランドとの接着がよい。

#### 【 0 0 1 9 】

また、請求項 7 の発明は、前記樹脂封止体の切り出し工程において、前記外部導出用の金属層の中央部に沿って切断することにより、隣接する前記半導体装置のそれぞれの電極金属層とすることを特徴とする請求項 5 又は 6 に記載の半導体装置の製造方法である。 10

#### 【 0 0 2 0 】

請求項 7 の発明によれば、隣接する半導体装置の外部導出用の金属層を中央から分離することで、それぞれの電極用の金属層とすることができます。従って、隣接する半導体装置を接近させて金属基板に搭載することができるので、半導体素子を金属基板に周密に搭載することができる。

#### 【 0 0 2 1 】

また、請求項 8 の発明は、平板状の金属基板に、半導体素子が搭載される金属層と、該半導体素子の電極パッドと、ワイヤで電気的に接続される外部導出用の金属層とからなるパターンが形成され、前記半導体素子を樹脂封止する際に、前記金属基板を一方の金型とすることを特徴とする電着フレームである。 20

#### 【 0 0 2 2 】

請求項 8 の発明によれば、平板状の金属基板にパターンニングされた金属層が形成され、ワイヤで電気的に接続された半導体素子が搭載されて樹脂封止された後、金属層が樹脂封止体に接着された状態で金属基板から剥離されて金属層を外部電極金属層とし得る電着フレームである。金属基板は、ステンレス鋼板（JIS 記号で SUS）が適している。

#### 【 発明の効果 】

#### 【 0 0 2 3 】

上述のように、本発明の請求項 1 では、リードレス構造の半導体装置であり、外部導出用の金属層が薄膜状の金属層からなり、樹脂パッケージ内に封止されている半導体素子が樹脂パッケージから露出する金属膜に搭載されており、半導体装置の高さを低背とすることができます、半導体素子を搭載する部分や外部導出用の電極がリードを用いていないし、かつガラスエポキシ基板やセラミック基板等の高価な基板を使用する必要がないし、リードや高価な基板を用いていないので、比較的安価な半導体装置とするとともに、半導体素子から発生する熱の放熱性がよい利点がある。 30

#### 【 0 0 2 4 】

また、この半導体装置では、高価な基板を使用する必要がないので、比較的安価な半導体装置とすることができます。しかも、半導体装置裏面の電極金属層と樹脂パッケージとが同一平面（面一）であり、さらに平坦な電極金属層を成膜したものであるので、その膜厚は、極めて薄い膜であり、この半導体装置を回路基板に搭載した際の回路基板との密着性が良く、半導体素子から発生する熱が回路基板を介して放散し易い。しかも、樹脂パッケージ内に封止されている半導体素子が樹脂パッケージから露出する金属膜に搭載された収納されており、半導体装置の高さを低背とすることができますの利点があり、小型の電子機器に容易に実装することができる利点がある。 40

#### 【 0 0 2 5 】

また、請求項 2 の発明によれば、半導体素子が接着される金属層が半導体素子の底面の面積より広い面積であるので、樹脂パッケージの表面から半導体素子との沿面距離を充分に設けることができ、半導体素子の耐湿特性を高めることができる。

#### 【 0 0 2 6 】

また、請求項 3 の発明によれば、半導体素子が接着される金属層の厚さを厚くすること 50

で、この金属層に半導体素子を搭載した際の樹脂パッケージの底面から半導体素子までの沿面距離を充分に保つことができ、耐湿性の向上に寄与する。しかも、半導体素子が接着される金属層の面積は、半導体素子が接着されるに充分な面積を有すればよいので、半導体素子の底面の面積より狭い面積でよく、樹脂パッケージに比較的面積の大きな半導体素子を搭載することができる利点がある。

【0027】

また、請求項4の発明によれば、外部導出用の金属層の平面形状を不定形な任意形状とすることができるので、半導体装置の電極金属層の形状に自由度を与えることができる利点がある。

【0028】

また、請求項5の発明によれば、ガラスエポキシ基板やセラミック基板等を用いることなく、半導体装置を製造する製造工程であり、電着フレームの平板状金属基板を剥離することによって、多数の半導体素子が樹脂封止された樹脂封止体を形成することができ、従来の製造工程と比較して製造工数を簡素化することができる利点がある。

【0029】

また、請求項6の発明によれば、樹脂封止体の底面から露呈する金属層に電解メッキまたは無電解メッキによる成膜工程を利用する半導体装置の製造方法であり、極めて薄い金の金属薄膜層を形成することで、回路基板のランドとの接着がよい利点がある。

【0030】

また、請求項7の発明によれば、隣接する半導体装置の外部導出用の電極となる金属層を中心から分離することで、それぞれの電極用の金属層とすることができます。従って、隣接する半導体装置を接近させて搭載することができるので、半導体素子を金属基板に周密に搭載することができる利点があり、半導体装置を安価に製造することができる利点がある。

【0031】

また、請求項8の発明によれば、平板状の金属基板にパターンニングされた金属層が形成された電着フレームであり、半導体素子が搭載されてワイヤで電気的に接続がなされ、半導体素子が樹脂封止された後、樹脂封止体から金属基板を剥離することで、樹脂封止体の底面に露呈する金属層を外部導出用の金属層とし得る電着フレームであり、互いに独立した金属層を形成することができる、電極金属層の形成に自由度を与えることができる利点がある。

【発明を実施するための最良の形態】

【0032】

以下、本発明に係る半導体装置、その製造方法及び電着フレームの実施の形態について、図面を参照して説明する。なお、本発明は、樹脂封止されたリードレス表面実装型の半導体装置に関し、その製造方法と、その製造工程で利用される電着フレームについて説明する。

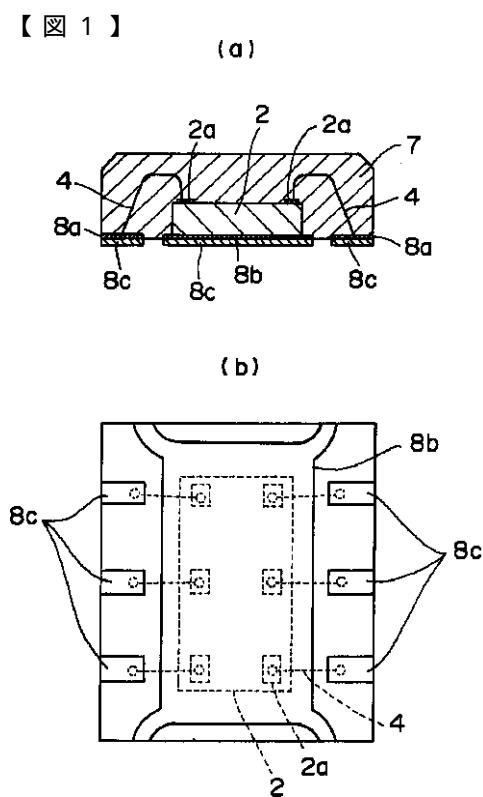

【0033】

図1は、本発明に係るリードレス表面実装型の半導体装置の一実施の形態を示しており、同図(a)はその断面図、同図(b)はその裏面図である。同図において、2は半導体素子であり、半導体素子2には電極パッド2aが形成されている。7は半導体素子2を封止する樹脂パッケージであり、半導体素子2の電極パッド2aと外部導出用の金属層8aとは、ワイヤ4で電気的に接続されている。

【0034】

半導体素子2は金属層8bに接着されて搭載され、金属層8bの面積は半導体素子2の底面の面積より広く、半導体素子2が金属層8bの略中央に接着されている。半導体素子2の底面の面積は、金属層8bの面積より狭いので、半導体素子2と樹脂パッケージ7の底面からの沿面距離が充分に保たれている。

【0035】

金属層8a, 8bの裏面は、樹脂パッケージ7から露呈している。また、金属層8a,

10

20

30

40

50

8 bとの外部露呈面は、樹脂パッケージ7の底面と同一平面(面一)となっており、金属層8 a, 8 bの裏面には、平坦な薄膜状の金属層8 cが形成される。

【0036】

金属層8 a, 8 bは、その露呈面側がニッケル(Ni)又はニッケル・コバルト(Ni・Co)合金を電着したNi薄膜層又はNi・Co薄膜層が形成され、かつNi薄膜層又はNi・Co薄膜層の上に金(Au)又は銀(Ag)の薄膜層が形成される。その厚さは、Ni又はNi・Co合金の薄膜層の厚さが20~35 μmであり、Au薄膜の厚さが約0.05~0.3 μmである。金属層8 cは、Ni又はNi・Co合金のNi薄膜層又はNi・Co薄膜層の厚さが約5 μmであり、Sn薄膜3~15 μm又は、Au薄膜又は銀薄膜の厚さが約0.3 μmである。

10

【0037】

無論、金属層8 aの底面に、金や金の合金等のハンダ乗りの良い金属膜を成膜した後、Ni薄膜層又はNi・Co薄膜層した場合は、金属層8 cを形成する必要はない。

【0038】

なお、本発明の半導体装置は、従来のようにガラスエポキシ基板やセラミック基板に半導体素子等を搭載して樹脂封止したパッケージ構造ではなく、半導体素子が樹脂パッケージに収納されて、金属膜が樹脂パッケージから露呈した形状である。

【0039】

すなわち、この半導体装置は、半導体素子を搭載する基板を必要としないことからその高さが低背となり、プリント基板に半導体装置を実装する際のバランスが良好なものとなる。

20

【0040】

従って、本発明の半導体装置では、プリント基板に実装する際の部品立ち等の不都合が生じ難い利点がある。また、本発明の半導体装置の裏面が平坦であるので、半導体装置の裏面に接着剤を付着させて、半導体装置をプリント基板に接着させて実装することができる。

20

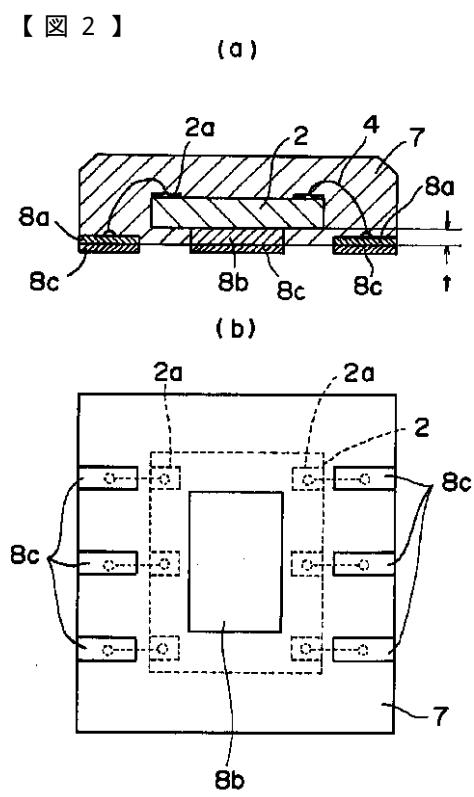

【0041】

次に、本発明に係る半導体装置の他の実施形態について、図2を参照して説明する。図2(a)は、半導体装置の断面図であり、図2(b)は、その底面図である。図2の半導体装置は、金属層8 bの膜厚が図1の半導体装置の金属層8 bの膜厚より厚く、しかも半導体素子2は、その底面の面積が金属層8 bの面積より広い。従って、半導体素子2は、樹脂パッケージ7の底面から約20 μm以上の位置の樹脂パッケージ7内に封止されている。従って、本実施形態の半導体装置樹では、脂パッケージ7の底面から半導体素子2までの沿面距離を充分に設けることができ、しかも比較的大きなサイズの半導体素子2を樹脂封止することができる。また、半導体素子2底部に樹脂が回り込んで、半導体素子2を樹脂封止され、この半導体装置は、充分な沿面距離が形成されて、耐湿性に優れた半導体装置とすることができます。また、小さな樹脂パッケージに大きな半導体素子を樹脂封止することができる。なお、図2の半導体装置の他の形状は、図1の半導体装置と同様であるので、その詳細な説明は省略する。

30

【0042】

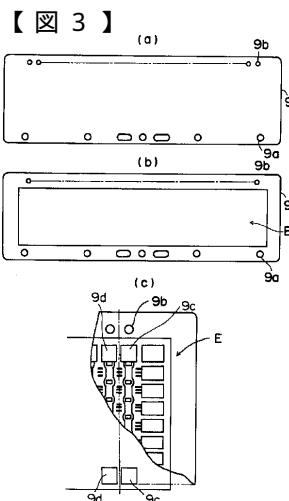

続いて、図1の半導体装置の製造方法の一実施形態について、図3~図6を参照して説明する。本発明の半導体装置の製造方法は、リードレス表面実装型の半導体装置を可撓性平板状の金属基板上に形成し、金属基板を剥離して製造する製造方法である。

40

【0043】

先ず、リードレス表面実装型の半導体装置を製造するにあたり、図3(a)に示した可撓性平板状の金属基板9を用意する。金属基板9は、薄いステンレス鋼板であり、その厚さは、0.1 mmである。金属基板9には、金属基板9の自動搬送用の孔9 a, 9 b等が形成され、金属基板9を自動搬送させるための孔が形成され、かつ金属基板9を金型に固定するための孔が形成されている。

【0044】

50

図3 (b) は、金属基板9に金属層によるパターンが形成され、半導体素子が搭載されるパターンが形成される電着フレームを示している。電着フレームは、金属基板9の片面に搭載された半導体素子を樹脂封止することで、金属基板9の片面に樹脂封止体が形成される。

【0045】

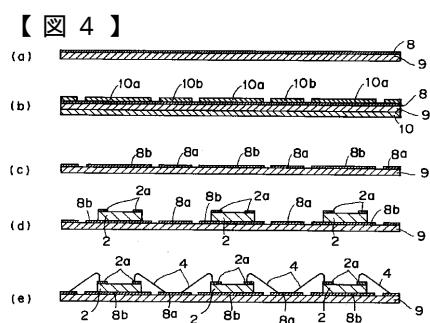

以下、図4, 図5を参照して、半導体装置の製造方法を、第1から第8の工程に大別して説明する。

【0046】

1) 第1の製造工程は、図4 (a) に示すように、ステンレス鋼板等による平板状の金属基板9の片面側全面に金属層8を電着して成膜する電着工程である。先ず、金属基板9の一面には、スピンドルコート法によって光感光性のレジストを塗布して、レジスト膜の全面に露光して硬化させる。続いて、マスクを施した金属基板9を電着槽に浸漬し、金属基板9の他面に金属層8を形成する。金属層8は、Ni又はNi・Co合金を電着したNi又はNi・Co合金薄膜層であり、その後、Ni・Co合金薄膜層上には、金をフラッシュ法等による真空蒸着或いはスパッタリング法等によって成膜される。電着工程は、金属基板9と電着槽内の電極間に通電することによって、金属基板9にNi又はNi・Co合金薄膜層の金属層8が形成される。Ni・Co合金薄膜は、例えば20~35μmの厚さとし、金薄膜層を0.3μmの厚さとする。なお、金属基板9にNi又はNi・Co合金を電着する前に、金を含む合金をフラッシュ法等で真空蒸着することによって、後の電極金属層を形成する成膜工程を省略することができる。

10

20

【0047】

2) 第2の製造工程は、金属層8のエッティング工程である。このエッティング工程では、図4 (b) に示すように、金属基板9の片側にレジスト膜10によるマスクを形成し、金属基板9の金属層8上には、レジスト膜10a, 10bが選択的に形成される。

【0048】

その後、このエッティング工程では、金属層8を選択的にエッティングして除去する。図4 (c) に示したように、金属基板9の片側に金属層8a, 8bが形成された電着フレームが形成する。電着フレームには、図3 (b) に示したように、半導体素子が搭載されて金線をワイヤーボンディングする領域Eが形成される。領域Eは、金属層8a, 8bとがマトリック状に形成されている。図3 (c) には、その詳細なパターンを示した。

30

【0049】

図3 (c) は樹脂封止体裏面の金属基板を剥離した場合におけるワイヤーボンディング領域E裏面のパターンを示す。このパターンには半導体素子が複数封止された樹脂封止体を個々の半導体装置に切断するための切断マーク9d, 9cがマーキングされている。切断時には切断マーク9d, 9cの間に切断部位が設定される。

【0050】

3) 第3の製造工程は、素子搭載工程である。この工程では、図4 (d) に示したように、半導体素子2が、公知の手法によって金属層8bに搭載される。半導体素子2は、図1に示したように、その表面には、電極パッド2aが形成されている。

【0051】

4) 電着フレームに半導体素子2が搭載された後、第4の製造工程のワイヤボンディング工程に進む。第4の製造工程では、図4 (e) に示したように、半導体素子2に金ワイヤ4をワイヤボンディングする工程であり、ワイヤ4は、半導体素子2の電極パッド2aと金属層8aとを超音波ボンディング等によって電気的に接続される。

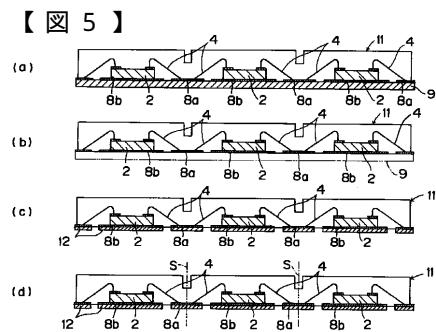

40

【0052】

5) 図4 (e) のワイヤボンディング工程に続いて、図5 (a) に示した第5の製造工程である樹脂モールド工程に進む。樹脂モールド工程は、図5 (a) に示したように、金属基材9に半導体素子2が搭載されて、ワイヤボンディングされた後の電着フレームが、モールド金型(上型)に装着される。モールド金型内には、エポキシ樹脂がモールド金型(上型)に形成されたキャビティ(図示しなし)により圧入される。この樹脂モールドで

50

は、金属基材9が樹脂モールドにおける下型としての機能を果たす。

【0053】

なお、半導体素子2が搭載された金属基材9を並列に配置して、エポキシ樹脂がライナを通してそれぞれの金属基材9と上金型との間に圧入することで、半導体素子が搭載された電着フレームを多数樹脂封止することができる。

【0054】

6) 樹脂モールド工程の後、第6の製造工程に進む。第6の製造工程は、図5(b)に示した金属基材9の剥離工程である。図5(b)に示したように、樹脂封止体11から金属基材9を引き離す。金属基材9は可撓性のある平板状であるので、樹脂封止体11から容易に剥離することができる。樹脂封止体11の底面には、金属層8a, 8bが露出している。金属層8a, 8bの露呈面は、樹脂封止体11の底面と面一である。なお、Ni又はNi・Co合金薄膜層が露呈している場合は、剥離工程に続いて、第7の製造工程であるダイシング工程に進む。

【0055】

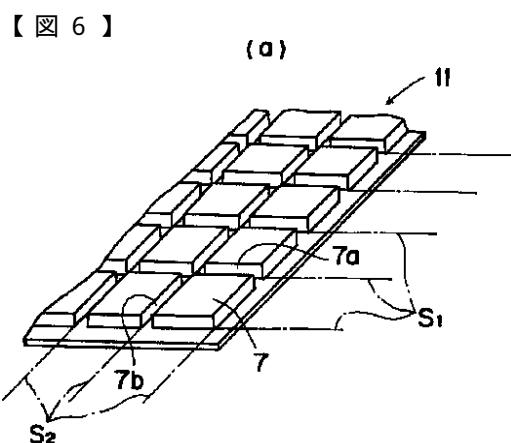

7) 第7の製造工程は、図5(d)に示した樹脂封止体11を切断線Sに沿って切断することで、樹脂封止体を一半導体素子毎に切り出す。樹脂封止体11は、半導体素子2間の金属層8aが中央部から切断されて個々の半導体装置に切り出される。)

【0056】

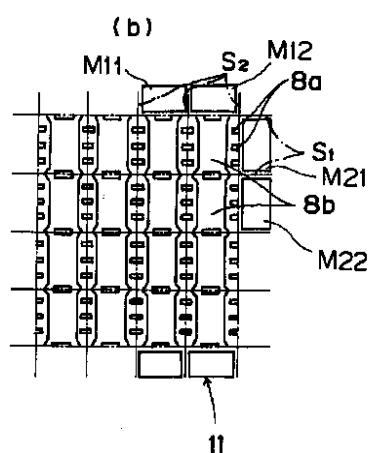

第7の製造工程であるダイシング工程について、図6を参照して説明する。なお、図6(a)は、多数の半導体装置が樹脂封止された樹脂封止体11の一部切欠部斜視図を示しており、同図(b)が樹脂封止体11の裏面を示している。

【0057】

同図において、S<sub>1</sub>, S<sub>2</sub>は、切断線(ダイシングライン)を示しており、それぞれ樹脂封止体11に形成されている溝7a, 7bを、金属基材9の裏面より切断線S<sub>1</sub>, S<sub>2</sub>に沿って切断することにより、各半導体装置に切り分けられる。

【0058】

図6(b)に示した樹脂封止体11の裏面図から明らかのように、電極金属層8aは、切断マークM11とM12との間の切断線S<sub>2</sub>に沿って切り出すことによって、隣接する半導体装置がそれぞれの外部導出用の金属層となる。

【0059】

更に、隣接する半導体装置の隣接間の金属層8bは、切断マークM21とM22との間の切断線S<sub>1</sub>に沿って切り離されている。樹脂封止体11は、ダイシング工程で切断線S<sub>1</sub>, S<sub>2</sub>に沿って、切断することによって、個々の半導体装置に切り出される。

【0060】

ダイシング工程に続いて電極を形成する第8の製造工程に進む。

8) この第8の製造工程は、図1, 2に示すように、切り出された個々の半導体装置の樹脂封止体2の底面の金属層8a, 8bに金薄膜層8cをフラッシュ法または電解メッキあるいは無電解メッキは等によって蒸着する。

【0061】

なお、電着フレームの形成は、上記の実施形態による製造方法に限定されることなく、金属基板の金または金と他の金属とを混合した薄膜層を形成した後、パターニングして、その後、NiまたはNi・Coの薄膜金属層を電着して形成してもよい。

【0062】

金属基板の金または金と他の金属を混合した薄膜層は、金属基板の一方の面にレジスト膜を全面に形成して、他方の面にレジスト膜をパターンニングして、半導体素子の搭載部と外部導出用の金属層とを形成する金属基板面を露呈させて、他はレジスト膜で覆って選択的に金薄膜層に電着して形成する。

【0063】

その後、パターンニングしたレジスト膜を除去して、金薄膜層が選択的に形成された面、全面にNiまたはNi・Coの薄膜金属層を形成し、続いて、NiまたはNi・Co薄

10

20

30

40

50

膜金属層を選択的に除去する。

【0064】

このような製造工程を経て、先の実施形態で説明したように、金属基板9に金属層8aと金属層8bとを形成する。その後の製造工程は、先に説明した製造工程と同様であるので説明を省略する。

【0065】

無論、本発明の半導体装置では、金属基板として、厚さが0.1mmのステンレス鋼板が用いられているが、この厚さに限定するものではない。しかし、半導体が封止された樹脂封止体から金属基板を剥離するのに好ましい。また、従来、金属基板として、銅板を用いて製造した半導体装置では、銅板をエッチングで除去しなければならぬが、ステンレス鋼板を用いることによって、樹脂封止体からステンレス鋼板を容易に剥離することができる。例えば、ステンレス鋼板としては、JIS記号分類によるSUSの何れかが用いられている。

【0066】

また、図2に示した半導体装置を製造する場合は、半導体素子2が搭載される金属層8bの厚さを約20μmとするために、金属層8aを金属基板に形成した後、金属層8bを形成するためのレジストマスクを形成して、金属層8aを成膜する時間より長い時間電着槽に浸漬して電着して形成すればよい。その後の製造工程は、先に説明した通りである。

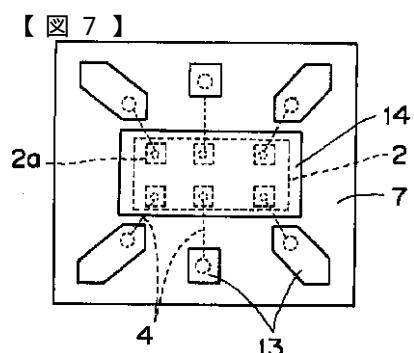

【0067】

なお、図7の半導体装置の裏面図で示したように、半導体装置は、樹脂パッケージ7から露出する金属層13は、その露呈面は平面形状を有し、樹脂パッケージ7に収納された半導体素子2の電極パッド2aと金属層13とがワイヤ4で電気的に接続されている。

【0068】

上記のように、本発明の半導体装置では、樹脂パッケージに半導体素子が封止されて、樹脂パッケージの底面から外部導出用の金属層が露出しており、樹脂パッケージの底面と外部導出用の金属層の底面とが面一であり、この金属層の面に更に、Ni又はNi・Co合金による薄膜層とAu薄膜層を形成して、外部電極とする。この外部電極は、樹脂パッケージの底面から僅かに突出するのみで、この半導体装置を基板に実装した場合、半導体装置の底面を基板に接触させて実装することができる。

【図面の簡単な説明】

【0069】

【図1】図1(a)は本発明の半導体装置の一実施形態の断面図、図1(b)はその裏面図である。

【図2】図2(a)は本発明の半導体装置の他の実施形態の断面図、図2(b)はその裏面図である。

【図3】図3(a)は金属基板の平面図、図3(b)は金属層をパターニングした金属基板の平面図、図3(c)はパターニングした金属層の拡大切欠平面図である。

【図4】図4(a)～図4(e)は本発明の半導体装置の製造方法の一実施形態を示す断面図である。

【図5】図5(a)～図5(d)は図4(e)に続く、半導体装置の製造方法を示す断面図である。

【図6】図6(a)は樹脂封止体の一部切欠斜視図、図6(b)は樹脂封止体の裏面図である。

【図7】図7は本発明に係る半導体装置の他の実施形態を示す裏面図である。

【図8】図8従来の半導体装置の断面図である。

【符号の説明】

【0070】

2 半導体素子

2a 電極パッド

4 ワイヤ

10

20

30

40

50

- 7 樹脂パッケージ

7 a , 7 b 溝

8 , 8 a , 8 b 金属層

8 c 金属層

9 金属基板

10 , 10 a , 10 b レジスト膜

11 樹脂封止体

12 金薄膜層

13 , 14 金属層

S , S<sub>1</sub> , S<sub>2</sub> 切断線

E 半導体素子が搭載される領域

10

【図1】

【図2】

---

フロントページの続き

(56)参考文献 特開平11-274357(JP, A)

特開平11-008260(JP, A)

特開平10-116935(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H01L 23/50