(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4954404号

(P4954404)

(45) 発行日 平成24年6月13日(2012.6.13)

(24) 登録日 平成24年3月23日(2012.3.23)

(51) Int.Cl.

F 1

|      |       |           |      |      |      |

|------|-------|-----------|------|------|------|

| G09G | 3/20  | (2006.01) | G09G | 3/20 | 691E |

| G06T | 1/00  | (2006.01) | G09G | 3/20 | 691B |

| G09F | 9/00  | (2006.01) | G09G | 3/20 | 691D |

| G09F | 9/30  | (2006.01) | G06T | 1/00 | 420G |

| H01L | 27/32 | (2006.01) | G09F | 9/00 | 313  |

請求項の数 4 (全 51 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2001-278744 (P2001-278744)  |

| (22) 出願日     | 平成13年9月13日 (2001.9.13)        |

| (65) 公開番号    | 特開2002-251164 (P2002-251164A) |

| (43) 公開日     | 平成14年9月6日 (2002.9.6)          |

| 審査請求日        | 平成20年5月27日 (2008.5.27)        |

| (31) 優先権主張番号 | 特願2000-280597 (P2000-280597)  |

| (32) 優先日     | 平成12年9月14日 (2000.9.14)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                     |

|-----------|---------------------|

| (73) 特許権者 | 000153878           |

|           | 株式会社半導体エネルギー研究所     |

|           | 神奈川県厚木市長谷398番地      |

| (72) 発明者  | 木村 肇                |

|           | 神奈川県厚木市長谷398番地 株式会社 |

|           | 半導体エネルギー研究所内        |

|           | 審査官 田井 伸幸           |

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の層と第2の層を同一平面に有する第1の基板と、

前記基板と重なるように設けられた画素と、を有し、

前記画素は、発光素子、光電変換素子を第2の基板上に有し、

前記第2の層は柱状であり、前記第1の層は前記第2の層の側面に接しており、

前記第1の層は、光吸収層を有し、

前記第2の層は、光透過層を有し、

前記第1基板と前記第2の基板上の画素間に、前記第2の層と同じ屈折率を有するスペーサが設けられていることを特徴とする表示装置。

10

## 【請求項 2】

第1の層と第2の層を同一平面に有する第1の基板と、

前記基板と重なるように設けられた画素と、を有し、

前記画素は、発光素子、光電変換素子を第2の基板上に有し、

前記第2の層は柱状であり、前記第1の層は前記第2の層の側面に接しており、

前記第1の層は、光吸収層を有し、

前記第2の層は、ガラスファイバであり、

前記第1基板と前記第2の基板上の画素間に、前記第2の層と同じ屈折率を有するスペーサが設けられていることを特徴とする表示装置。

## 【請求項 3】

20

第1の層と第2の層を同一平面に有する第1の基板と、

前記基板と重なるように設けられた画素と、を有し、

前記画素は、発光素子、光電変換素子を第2の基板上に有し、

前記第2の層は柱状であり、前記第1の層は前記第2の層の側面に接しており、

前記第1の層は、光吸收層を有し、

前記第2の層は、コア部及びクラッド部を有し、

前記第1基板と前記第2の基板上の画素間に、前記第2の層と同じ屈折率を有するスペーサが設けられていることを特徴とする表示装置。

**【請求項4】**

請求項1乃至請求項3のいずれか一項において、

10

前記第2の層は円柱状であることを特徴とする表示装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、イメージセンサ機能を有するエリアセンサに関する。より詳細にはE L素子を光源として利用し、マトリクス状に配置されたフォトダイオードと複数の薄膜トランジスタ(TFT)とによって構成されるエリアセンサおよびエリアセンサを備えた表示装置に関する。

**【0002】****【従来の技術】**

20

近年、パソコン等の情報機器が広く普及し、様々な情報を電子情報としてパソコンなどに読み込みたいという要求が高くなっている。そのため、従来の銀塩カメラに代わる手段としてデジタルスチルカメラが注目され、また紙などに印刷されたものを読み取るための手段としてスキャナが大きく注目されている。

**【0003】**

デジタルスチルカメラでは、イメージセンサ部の画素が2次元に配列されたエリアセンサが用いられている。スキャナやコピー機などでは、イメージセンサ部の画素が1次元に配列されたラインセンサが用いられている。

**【0004】**

スキャナは、一般的に、読み取り方式によって、(1)シートフィード型、(2)フラットベッド型、(3)ペン型(ハンディ型)の3つに大まかに分類できる。(1)シートフィード型は、スキャナのイメージセンサ部を固定し、原稿を紙送りで移動させて読み取る方式である。(2)フラットベッド型は、原稿をガラスの上に固定し、ガラスの下でイメージセンサ部を移動させて読み取る方式である。(3)ペン型は、イメージセンサ部を原稿の上で使用者が移動させて読み取る方式である。このように、スキャナでは、ラインセンサが用いられることが多い。

30

**【0005】**

以上の3つのタイプのスキャナでは、用いられる光学系はほぼ決まっている。(2)フラットベッド型のスキャナでは、精密に画像を読み取るため、縮小型光学系を採用する事が多い。なお縮小型光学系で用いるレンズは、焦点距離が長くなってしまう。その結果、被写体とイメージセンサ部の距離が長くなり、装置が大型化してしまう。

40

**【0006】**

(1)シートフィード型や(3)ペン型(ハンディ型)では、装置を小型化する必要がある。そのため、光学系もそれに見合った小型のものが採用される。つまり、密着型光学系が採用されることが多い。密着型光学系は、イメージセンサと被写体の間に、ロッドレンズアレイを配置する。ロッドレンズアレイは、分布屈折率型の棒状のレンズを複数本束ねたものである。また該ロッドレンズアレイは、1対1で結像し、被写体とイメージセンサ部の距離は、縮小型光学系よりも短くなる。

**【0007】**

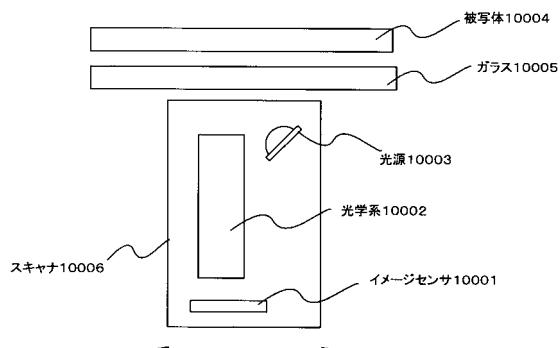

イメージセンサ素子としては、CCD型や単結晶CMOS型のセンサが多く使用されてい

50

る。これらの素子を用いて、密着型光学系を採用したときのスキャナの断面図を図40に示す。C C D型(C M O S型)のイメージセンサ10001の上には、ロッドレンズアレイなどの光学系10002が配置されている。これは、原稿(被写体)上の画像がイメージセンサ10001上に映し出されるようにするために用いられる。像の関係は、等倍系である。光源10003は、被写体10004に光を照射できるような位置に配置されている。用いられる光源としては、L E Dや蛍光灯などが多く用いられる。そして、最上部にガラス10005が配置され、ガラス10005の上に被写体10004が配置される。なお図4に示すスキャナの動作については以下の通りである。まず、光源10003を出た光は、ガラス10005を通って原稿に入射する。そしてその光は被写体10004で反射され、ガラス10005を通って、光学系10002に入射する。光学系10002に入射した光は、次いで、イメージセンサ10001に入射し、そこで光電変換される。そして、電気に変換された信号は、外部に読み出される。そしてイメージセンサ10001で一列分の信号を読み取ったら、スキャナ10006を移動して、再び同様の動作を繰り返す。

10

#### 【0008】

なお図4に示すスキャナは、ラインセンサであるが、該ラインセンサで2次元の被写体を読み取る場合には、センサ、あるいは、被写体のどちらか一方を動かす必要がある。そのため装置が大きくなったり、読み取り速度が遅くなったり、機械的強度が弱くなったりしてしまう。そこで、画素を2次元に配列した密着型のエリアセンサが研究されている。被写体に光を当てるために、基板は光を通す必要がある。そのため基板は、透明なものであることが必要であり、例えば、ガラスのように透明であることが必要になる。エリアセンサでは、画素が2次元に配列されているため、読み取り時に動かす必要がない。このような密着型エリアセンサは、テレビジョン学会技術報告：1993.3.4：p25：アモルファスシリコン2次元イメージセンサとその応用、Jpn.J.Appl.i.Phys.Vol.32(1993) pp458-461：Two-Dimensional Contact-Type Image Sensor Using Amorphous Silicon Photo-Transistorなどに発表されている。

20

#### 【0009】

次いで、イメージセンサ素子を用いて、被写体をカラーで読み取る場合について述べる。カラーの画像を読み込みたい場合は、特別な手法(方式)を用いる必要がある。その手法(方式)としては、大きく分けて、(a)光源切り替え方式、(b)フィルタ切り替え方式、(c)カラーイメージセンサを使う方式の3つがある。(a)光源切り替え方式は、3色の光源(蛍光灯、L E Dなど)を順次点滅し、モノクロイメージセンサで原稿の画像情報を順次読み取り、赤、緑、青の信号出力を得るというものである。(b)フィルタ切り替え方式は、白色光源とモノクロイメージセンサの間に赤、緑、青のカラーフィルタを設けて、該フィルタを切り替えて、順次読み取りを行い、赤、緑、青の信号出力を得るというものである。(c)カラーイメージセンサ方式は3ラインのイメージセンサとカラーフィルタを1パッケージに組み込んだカラーイメージセンサであり、色分解と読み取りを同時に行うというものである。

30

#### 【0010】

次いで、光電変換などをを行うセンサ部について述べる。通常は、センサ部にPN型のフォトダイオードが設けられて、該フォトダイオードを用いて、光を電気に変換する。より詳しくは、被写体の情報を画像信号に変換する。その他には、PIN型のダイオード、アバランシェ型ダイオード、npn埋め込み型ダイオード、ショットキー型ダイオード、フォトトランジスタなどがある。その他には、X線用にフォトコンダクタや、赤外線用のセンサなどもある。これらの光電変換素子については、固体撮像素子の基礎－電子の目のしくみ：安藤隆男、菰淵寛仁著：日本理工出版界に述べられている。

40

#### 【0011】

##### 【発明が解決しようとする課題】

本発明は、イメージセンサ機能を有するエリアセンサに関するもので、より詳細にはE L素子を光源として利用し、マトリクス状に配置されたフォトダイオードと複数の薄膜トランジスタ(T F T)とによって構成されるエリアセンサおよびエリアセンサを備えた表示

50

装置に関するものである。本発明で用いる表示装置（エリアセンサ）は、画像表示機能と画像読み取り機能を一体化したものであり、各画素には、EL発光部（EL発光素子、RGBの合計3個）とイメージセンサ素子（1個）がある。イメージセンサ機能とは、画面に被写体を密着させて、センシングを行い、被写体の情報を読み取る機能である。この場合には、EL素子をイメージセンサ用の照明として用いる。つまり、始めに画素にマトリクス状に設けられたEL素子を発光させ、EL素子から発せられた光を被写体に照射させる。そして、その反射した光がフォトダイオードに照射されることによって、被写体の情報を読み取る仕組みになっている。なおカラーの被写体の場合には、3回センシングを行って画像の情報を読み取る。また本発明で用いる表示装置は、EL発光部を発光させて、画像を表示する表示機能を有しており、表示機能を機能させる場合には、イメージセンサ機能は停止している。

10

## 【0012】

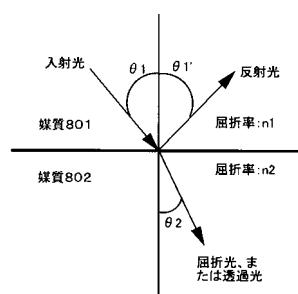

ここで、光の屈折について説明する。光の屈折は、図25に示すように入射光の角度（入射角）とその媒質の屈折率により決まる。さらに、この関係は以下の数1（式（1）、スネルの法則）に従う。屈折率が $n_1$ である媒質801において $\theta_1$ の角度で入射した光（入射光）が、屈折率が $n_2$ である媒質802に出射するとき、以下の数1（式（1））を満たすような角度 $\theta_2$ の光（屈折光）となる。

## 【0013】

## 【数1】

$$n_1 * \sin \theta_1 = n_2 * \sin \theta_2 \cdots (1)$$

20

## 【0014】

屈折光または透過光の角度 $\theta_2$ が90°となるような入射角 $\theta_1$ を臨界角とよぶ。また、媒質802に対する入射角 $\theta_1$ が臨界角よりも大きくなるときに、入射光は全反射する。つまり、光が媒質801に閉じ込められることになる。

## 【0015】

さらに、エネルギーの反射率（R）及び透過率（T）は、以下に示す数2、数3（式（2）、式（3）、フレネルの法則）が成り立つ。

## 【0016】

## 【数2】

$$R = \frac{1}{2} \left\{ \frac{\sin^2(\theta_1 - \theta_2)}{\sin^2(\theta_1 + \theta_2)} + \frac{\tan^2(\theta_1 - \theta_2)}{\tan^2(\theta_1 + \theta_2)} \right\}$$

30

## 【0017】

## 【数3】

$$T = 1 - R$$

## 【0018】

ここで、EL素子とイメージセンサ素子を一画素とし、該画素をマトリクス状に基板上（一例としてここではガラス基板とする）に設けた表示装置（エリアセンサ）における被写体とセンサ部との関係について述べる。

40

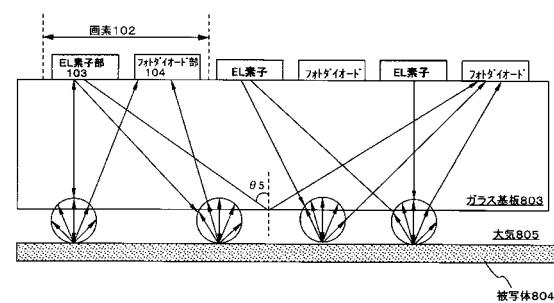

## 【0019】

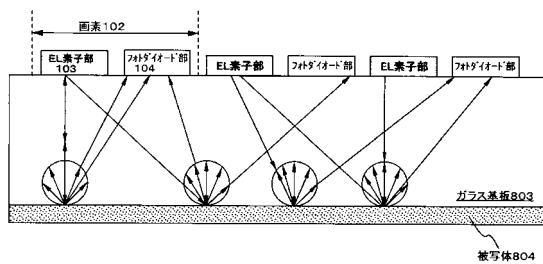

まず、画素102がマトリクス状に設けられたガラス基板803と被写体804とが完全に密着している場合について説明する（図26）。完全に密着している場合は、ガラス基板803と被写体804との間に完全に空気が無い状態のことである。図26において、矢印は光の進行方向を表しており、また画素102、EL素子部103およびフォトダイオード部104は図2に示すものを概略化したものであるので説明は省略する。また画素102は、マトリクス状に設けられているが、図26ではその一部を表している。図2

50

7、図28においても同様である。

**【0020】**

EL素子部103から発せられた光は、被写体804に向けてあらゆる方向に拡散して、被写体804に照射される。画素102は、ガラス基板803上にマトリクス状に設けられており、EL素子部103から発せられる光は被写体804にほぼ均一に照射される。よって、EL素子部103から発せられた光は、被写体804の反射率に応じて反射される。そしてガラス基板803を介して、フォトダイオード部104に照射される光は、すべて被写体804からの反射光となる。

**【0021】**

つまり、被写体804とセンサ部（フォトダイオード部104）が完全に密着している場合（図26）においては、EL素子部103から発せられた光は、被写体804に反射し、その反射光がフォトダイオード部104に照射されることにより、被写体804の情報を読みとるという仕組みになっている。すなわち、EL素子部103から発せられた光は、ガラス基板803を通って、被写体804に照射され、また、フォトダイオード部104に照射される光はすべて被写体804からの反射光であることが分かる。

10

**【0022】**

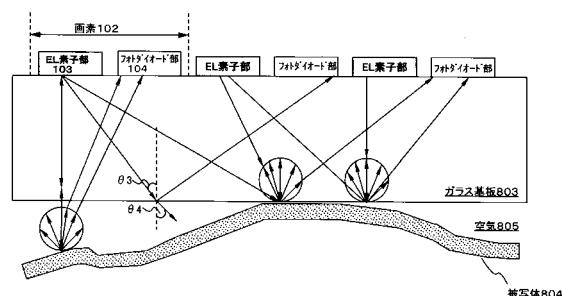

次に、ガラス基板803と被写体804の間の一部に空気805が存在する場合について説明する（図27）。EL素子部103から発せられた光はあらゆる方向に拡散して照射される。このとき、EL素子部103から発せられた光が、ガラス基板803に入射して空気805との界面に到達したとき、屈折して屈折光として被写体804に照射する場合と、反射して反射光としてフォトダイオード部104に照射する場合がある。本明細書中では、EL素子部103から発せられた光が、ガラス基板803と空気805との界面において、全反射してしまう光、すなわちガラス基板803に閉じこめられてしまう光をノイズ光とよぶ。本来ならば、EL素子部103から発せられた光は被写体804に照射され、そして被写体804において反射し、反射光としてフォトダイオード部104に照射されるべきである。しかし、EL素子部103から発せられ、基板803と空気805の界面において全反射した光（ノイズ光）は、被写体804に照射されることなく、そのままフォトダイオード部104に照射されてしまう。このようなノイズ光は被写体804の情報をぼやけて読み取る原因となる。

20

**【0023】**

30

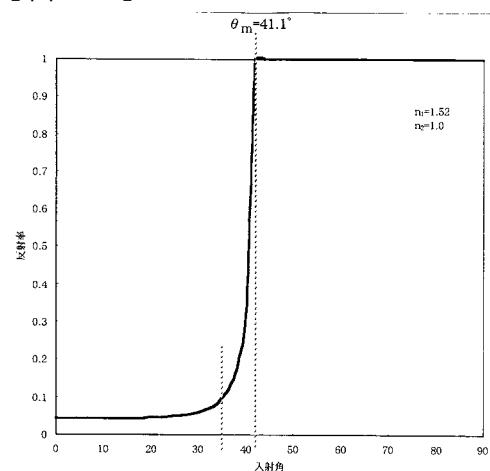

ここで、光の屈折の関係をスネルの法則（数1、式（1））を参考にして考える。ここでは、一例として基板をガラス基板としているので、ガラス基板の屈折率（ $n = 1.52$ ）と、空気の屈折率（ $n = 1.0$ ）を参考にする。また、ノイズ光を発生させないためには、 $\theta_4 = 90^\circ$ であればよいので、これらの値をスネルの法則（数1、式（1））に代入する。そうすると、数4（式（4））のような値が算出される。

**【0024】**

**【数4】**

$$\theta_3 = 41.1 \cdot \dots (4)$$

**【0025】**

すなわち、ガラス基板803と被写体804との間に空気805が存在する場合には、EL素子部103から発せられた光がガラス基板803と空気805との界面に到達したときに、その入射角が $41.1^\circ$ 以上の場合に全反射するということである。また、図39および数4（式（4））を参考にすると入射角が $35^\circ$ 以上 $41.1^\circ$ 以下の場合において反射率が上昇しており、EL素子部103から発せられた光が、ガラス基板803と空気805との界面において、反射する光が急増する。すなわち、入射角が $35^\circ$ 以上 $41.1^\circ$ 以下の場合においては、EL素子部103から発せられた光が、ガラス基板803と空気805との界面において、すべて反射する場合と、屈折する場合とが存在する。また図39より、EL素子部103から発せられた光が、ガラス基板803と空気805との界面において、入射角が $35^\circ$ 以下の場合においては、ほとんど反射せず、屈折して光が外に出ることが分かる。

40

50

**【0026】**

次にガラス基板803と被写体804とが完全に離れている場合について説明する(図28)。この場合は、ガラス基板803と被写体804との間に完全に空気805が存在する場合である。EL素子部103から発せられた光は、被写体807に向けてあらゆる方向に拡散して、被写体804に照射される。そしてEL素子部103から発せられた光は、ガラス基板803と空気805との界面に到達したときに、入射角に応じて、反射光か、屈折光かのどちらかとなる。

**【0027】**

上述のように、図39および数4(式(4))を参考にすると、EL素子部103から発せられた光は、入射角が41.1°以上の場合は全反射し、入射角が35°以上41.1°未満の場合は反射する光と、屈折する光とに分類される。入射角が35°以下の場合はほとんどの光が、屈折光として被写体に照射されるが、図39に示すように、反射する光も少し存在する。もちろん、全反射する光はノイズ光としてフォトダイオード部104に照射されるが、EL素子部103から発せられる光は、あらゆる方向に拡散して照射され、かつ、EL素子部103から発せられる光は、ある角度以上の入射角のみが全反射するため、フォトダイオード部104には均一にノイズ光が照射されることが分かる。

**【0028】**

また、EL素子部103から発せられた光が、ガラス基板803と空気805との界面で屈折光としてガラス基板803の外に出た場合は、被写体804に照射される。そして被写体804の反射率に応じて光が反射され、その反射光がフォトダイオード部104に照射される。すなわちこの場合においては、フォトダイオード部104に照射される光は、被写体804で反射した反射光と、それぞれのフォトダイオード部104に均一に照射されるノイズ光となる。

**【0029】**

上述したように、ガラス基板803と被写体804との間の一部に空気805がある場合(図27)、またガラス基板803と被写体804との間が完全に離れている場合(図28)は、ガラス基板803と空気805との界面において全反射する光がノイズ光として存在する。ノイズ光は被写体804の情報をぼやけてよみとってしまう原因となっている。本発明では、ガラス基板803と被写体804とが完全に密着している場合、ガラス基板803と被写体804との間の一部に空気805が存在する場合、ガラス基板803と被写体804とが完全に離れている場合のいずれにおいても、被写体804の情報が正確によみとれるようにすることを課題とする。また被写体804に凹凸があっても、被写体804の情報を正確に読み取れるようにすることを可能とする。

**【0030】****【課題を解決するための手段】**

本発明では、EL素子部103と被写体804との間に、ガラスファイバプレート、または光ファイバプレートを設け、ノイズ光を光吸收層により吸収されることによって、上記課題を解決する。

**【0031】**

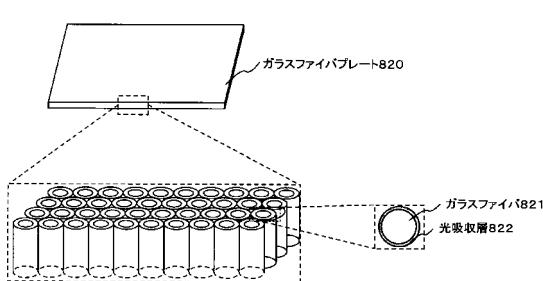

本発明では、それぞれ光吸收層で覆った複数のガラスファイバを軸が平行になるように束ねる。なお本明細書で用いられるガラスファイバとは、細い線状のガラス線、またはガラス棒とよばれるものを使用する。このような複数のガラスファイバを束ね、その軸と垂直方向にプレート状にスライスする。そのスライスしたものを、本明細書中ではガラスファイバプレートとよぶ(図29)。なお図29では、ガラスファイバ821の断面は円状となっているが、本発明ではこれに限らず、断面は橢円状でもよいし、多角形状でもよいが、図30に示すように、軸と平行方向の断面が四角形であることが望ましい。

**【0032】**

また、それぞれ光吸收層で覆った複数のガラスファイバを用いたガラスファイバプレート以外に、複数のガラスファイバを軸が平行になるように束ね、その軸を垂直方向にプレート状にスライスしたものを用いてもよい。この場合には、ガラスファイバとガラスファイ

10

20

30

40

50

バの間に光吸收層を設ける。

**【0033】**

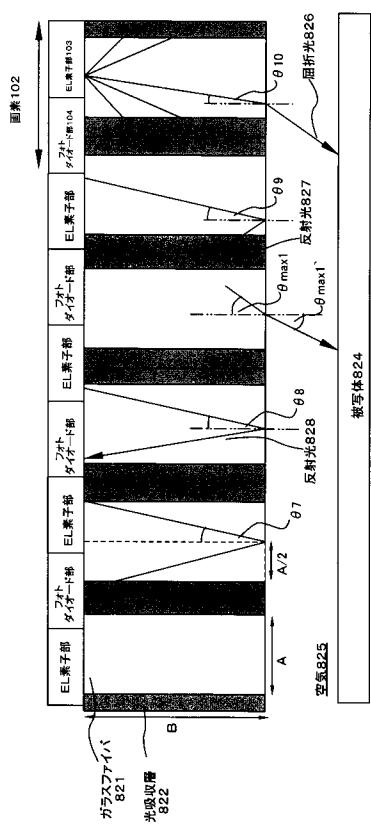

そして本発明では、このようなガラスファイバプレートをセンサ部と被写体の間に設ける。図30は、EL素子部103およびフォトダイオード部104を有する画素102が、マトリクス状に一つの基板上に設けられた一部を示しており、EL素子部103から光吸收層822で覆われた複数のガラスファイバ821に光が照射される様子を表した図である。図30において、画素102、EL素子部103およびフォトダイオード部104は図2に示すものと同じであるので説明は省略する。<sub>7</sub>、<sub>8</sub>および<sub>9</sub>はガラスファイバ821と空気825との界面においての入射角を示しており、<sub>max1</sub>はガラスファイバ821と空気825との界面においての臨界角を示している。また矢印は光の進行方向を示している。

10

**【0034】**

図30から、EL素子部103から発せられた光の進行方向が光吸收層822の場合は、光が吸収されていることが分かる。それ以外の光は、ガラスファイバ821と空気825との界面において、入射角が<sub>10</sub>(ただし<sub>10</sub><<sub>max1</sub>)の場合は、屈折して屈折光826として出射する。ガラスファイバ821と空気825との界面において、入射角が<sub>9</sub>(ただし<sub>9</sub><<sub>max1</sub>)の場合はガラスファイバ821と空気825の界面で全反射し、反射光827として再び光吸收層822に吸収される。もしくは、ガラスファイバ821と空気825との界面において、入射角が<sub>8</sub>(ただし<sub>8</sub><<sub>max1</sub>)場合は、ガラスファイバ821と空気825の界面で全反射し、反射光828としてフォトダイオード部104に照射される。

20

**【0035】**

ここで、EL素子部103から発せられた光が、ガラスファイバ821と空気825の界面において反射され、その反射光828がフォトダイオード部104に照射されないようにしたい。なぜなら、反射光828のような光がフォトダイオード部104に照射されることが、被写体824の情報を正確に読み取ることが出来ない原因であるからである。

**【0036】**

つまり、被写体824がガラスファイバ821に完全に密着している場合、被写体824とガラスファイバ821との間の一部に空気825が存在する場合、被写体824とガラスファイバ821とが完全に離れている場合のいずれの場合にも被写体824の情報を完全に読み取ることができるようにしたい。すなわち、ガラスファイバ821と空気825との界面で全反射し、その反射光がフォトダイオード部104に照射されないようにすればよい。この場合、そのための条件式を、1本のガラスファイバ821の長さ(B)と断面の直径(A)とガラスの屈折率から算出できる。

30

**【0037】**

さらに、EL素子部103から発せられた光が、ガラスファイバ821と空気825の界面で全反射しないようにしたい。また全反射したとしても、その反射光が、光吸收層822に吸収されればよい。以上の状況をふまえると、ガラスファイバ821の断面の直径(A)の半分と、ガラスファイバ821の長さ(B)から以下の式(5)を導き出せる。

40

**【0038】**

**【数5】**

$$\tan \max_1 = A / 2B \cdots (5)$$

**【0039】**

ガラスファイバ821の断面の直径(A)の半分と、ガラスファイバ821の長さ(B)が、式(5)を満たせば、EL素子部103から発せられた光が、ガラスファイバ821と空気825の界面で全反射され、フォトダイオード部104に照射される光はない。よって、一本のガラスファイバ821の断面の直径(A)と長さ(B)との関係式は式(6)のように表すことができる。

**【0040】**

**【数6】**

10

20

30

40

50

$$\max > \tan^{-1}(A / 2B) \dots (6)$$

## 【0041】

上述のように、本発明ではガラスファイバ821の断面の直径(A)と長さ(B)との関係が式(6)を満たすようなガラスファイバ821を用いることが好ましい。このようにすることによって、被写体とセンサ部が完全に密着している場合、被写体とセンサ部の間の一部に空気が存在する場合、被写体とセンサ部が完全に離れている場合のいずれの場合にも被写体の情報をぼやけることなく読み取ることができる。

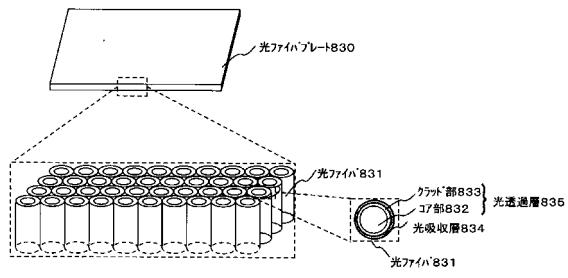

## 【0042】

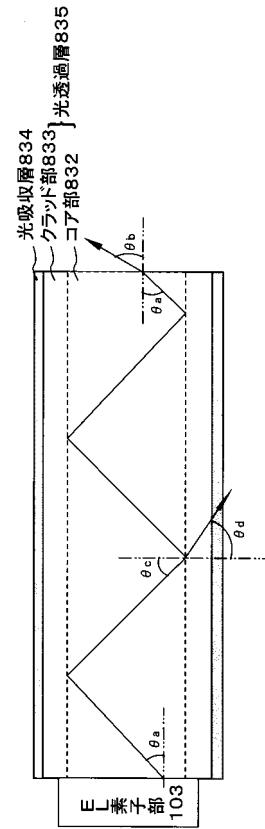

また、ガラスファイバプレート820の代わりに、光ファイバプレート830を被写体とセンサ部の間に設けてもよい。図31にあるように、本明細書中では、複数本の光ファイバ831をそれらの軸が平行になるように束ねて、それぞれの光ファイバ831の軸と垂直方向にプレート状にスライスしたものを光ファイバプレート830とよぶ。1本の光ファイバ831は、光吸收層834と光透過層835とからなっており、光透過層835は光吸收層834に覆われている。光透過層835は、屈折率の高いコア部832と、その周辺を囲むコア部832よりも屈折率の低いクラッド部833からなっている。このような構造をもつ光ファイバプレートは、既に市販されており、浜松ホトニクス社のファイバオプティクプレート(FOP)、旭硝子社のファイバアレイプレート(FAP)、ワイオシステム社の光ファイバプレート等がある。

## 【0043】

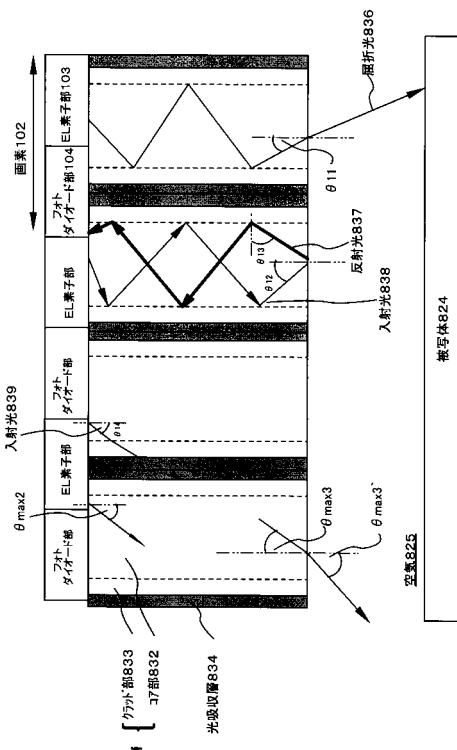

ここで、EL素子部103から発せられた光が、光ファイバ831のコア部832とクラッド部833との境界面を全反射しながら伝搬していくための条件を考えてみる。

## 【0044】

図33を参照する。図33のEL素子部103は、図2に示すものと同じである。またコア部832、クラッド部833、光吸收層834および光透過層835は、図32に示すものと同じであるので、ここでは説明は省略する。そして、コア部832の屈折率を $n_{10}$ 、クラッド部833の屈折率を $n_{11}$ とし、 $\alpha$ 、 $\beta$ 、 $\gamma$ および $\delta$ は角度を示す。

## 【0045】

まず、EL素子部103から発せられた光が、光ファイバ831と空気825との界面で全反射しないための条件を考える。全反射させないためには、 $\beta = 90^\circ$ であればよい。これをスネルの法則(数1、式(1))に代入する。そうすると以下の式(7)が求められる。

## 【0046】

## 【数7】

$$n_{10} * \sin \alpha = 1 \dots (7)$$

## 【0047】

ここで、EL素子部103から発せられた光が、光ファイバ831と空気825との界面で全反射しないためには、左辺よりも右辺の方が大きければよい。よって、数8(式(8))を満たせばよい。

## 【0048】

## 【数8】

$$n_{10} * \sin \alpha < 1 \dots (8)$$

## 【0049】

またEL素子部103から発せられた光が、EL素子部103と光ファイバ831との界面においての入射角がEL素子部103と光ファイバ831との界面においての臨界角よりも大きい場合には、EL素子部103から発せられた光はコア部832とクラッド部833との界面で全反射しない。このような光は、光吸收層834に吸収されなければならない。よって、下記の関係式(9)が求められる。まずはスネルの法則(数1、式(1))に当てはめる。

## 【0050】

## 【数9】

10

20

30

40

50

$$n_{10} * \sin_c = n_{11} * \sin_d \dots (9)$$

【0051】

このとき、 $d = 90$ 、 $c = 90 - a$ となり、これを数7(式(7))、数8(式(8))および数9(式(9))に代入する。そうすると以下の式(10)が求められる。

【0052】

【数10】

$$n_{10} * \sin_c = n_{10} * \sin(90 - a) = n_{11} \dots (10)$$

【0053】

このとき、EL素子部103から発せられた光は、光ファイバのコア部832とクラッド部833の境界面において、反射させずに、コア部832からクラッド部833に入射することにより、光吸収層834に吸収されればよい。よって、右辺よりも左辺の方が大きければよく、以下の数11(式(11))を満たせばよい。

【0054】

【数11】

$$n_{10} * \sin(90 - a) = n_{10} * \cos_a > n_{11} \dots (11)$$

【0055】

ここで、開口数(N.A.)を考えると、開口数(N.A.)は以下の式(12)で表すことができる。

【0056】

【数12】

$$N.A. = (n_{10}^2 - n_{11}^2)^{1/2} \dots (12)$$

【0057】

ここで、本発明のエリアセンサ(表示装置)には、数7(式(7))、数10(式(10))を満たす光ファイバを用いればよいので、数7(式(7))、数10(式(10))を数11(式(11))に代入する。そうすると、以下の数13(式(13))が求められる。

【0058】

【数13】

$$N.A. = (n_{10}^2 - n_{11}^2)^{1/2} < n_{10} * \sin_a < 1 \dots (13)$$

【0059】

上記のように、N.A.(開口数)は1未満であることが望ましい。より最適なN.A.(開口数)を求めたい場合には、 $a$ 、 $b$ 、 $c$ および $d$ に数値を代入して求めるとよい。N.A.(開口数)は、光ファイバ831のコア部832とクラッド部833の屈折率により求めることができる。

【0060】

図32において、EL素子部103から発せられた光が、EL素子部103と光ファイバ831のコア部832との境界面において、臨界角( $\max_2$ )以上の角度で光ファイバ831に入射した場合、すなわち、入射角が $\alpha_1$ (ただし $\alpha_1 > \max_2$ )の場合には、光ファイバ831のコア部832とクラッド部833との境界面において全反射せずに、迷光として複数本の光ファイバ831を横断して伝搬しようとする。しかし本発明で用いる光ファイバ831は、光吸収層834で覆われているために吸収される。ここで、 $\max_2$ とは、EL素子部103から発せられた光が、光ファイバ831のコア部832に入射するときの臨界角を示す。

【0061】

また、EL素子部103から発せられた光が、臨界角( $\max_2$ )以下の角度で光ファイバ831に入射した場合は、コア部832とクラッド部833との境界面における全反射により、光は伝搬していく。伝搬した光が、光ファイバ831と空気825との界面に到達した場合、その界面において臨界角( $\max_3$ )よりも小さい場合は、屈折光836として、被写体824に照射される。ここで、 $\max_3$ とは、EL素子部103から発せられた光が、光ファイバ831を通って、光ファイバ831のコア部832と空気825との界面

10

20

30

40

50

に入射する場合の臨界角を示す。

**【0062】**

EL素子部103から発せられた光が、光ファイバ831のコア部832とクラッド部833の境界面における全反射により、光は伝搬していく。伝搬した光が、光ファイバ831と空気836との界面に到達した場合、その界面において入射角( $\theta_{12}$ )が臨界角( $\theta_{max3}$ )よりも小さい場合がある。すなわち、EL素子部103から発せられた光が、光ファイバ831と空気825との界面においての入射角が $\theta_{12}$ (ただし $\theta_{12} > \theta_{max3}$ )の場合は、光ファイバ831と空気825との界面において全反射する。全反射した光は、反射光837として、コア部832とクラッド部833との境界面の全反射を繰り返すことにより、反射光837は伝搬してフォトダイオード部104に照射される。

10

**【0063】**

光ファイバ831と空気825との界面に到達した光は、入射角により、屈折光836として光ファイバ831の外に出て、被写体824に照射される場合と、反射光837のように再び光ファイバ831内を伝搬してフォトダイオード部104に照射される場合とがある。反射光837のような光が、フォトダイオード部104に照射されることは、被写体の光を正確によみとることが出来ない原因となる。そこで、光ファイバプレートを用いる場合には、入射角を調節する必要があり、また入射角は開口数(N.A.)、すなわちコア部832の屈折率に依存する。

**【0064】**

ガラス基板803と被写体804との間の一部に空気805がある場合、ガラス基板803と被写体804との間が完全に離れている場合は、ガラス基板803と空気805との界面で全反射する光がノイズ光として存在する。ノイズ光は被写体の情報をぼやけてよみとってしまう原因となっている。そこで本発明は被写体とセンサ部との間にガラスファイバプレート、または光ファイバプレートを設けることにより、ノイズ光を光吸收層に吸収する。すなわち、ガラスファイバ、または光ファイバと空気との界面で全反射する光を、光吸收層に吸収する。よって、EL素子から発せられた光が被写体で反射して、その反射光がフォトダイオードに照射されるために、被写体の情報を正確に認識することができる。

20

**【0065】**

すなわち本発明では、ガラス基板803と被写体804とが完全に密着している場合、ガラス基板803と被写体804との間の一部に空気が存在する場合、ガラス基板803と被写体804とが完全に離れている場合の、いずれの場合においても被写体804の情報を正確に読み取ることができるエリアセンサを提供する。また該エリアセンサを備えた表示装置を提供する。

30

**【0066】**

**【発明の実施の形態】**

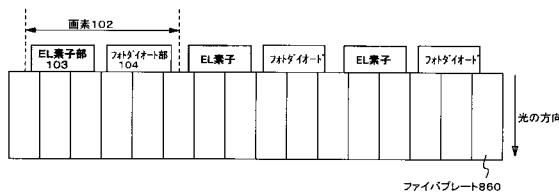

**(実施の形態1)**

本発明のエリアセンサ(表示装置)には、図29にあるようなガラスファイバプレート820、または図31にあるような光ファイバプレート830が被写体とセンサ部との間に設けられる。本実施の形態では、EL素子部103に設けられたEL素子が下面出射するエリアセンサ(表示装置)について、図34を用いて説明する。本明細書中で下面出射するとは、TFTを設けている基板上において、TFTを設けている側とは反対側にEL素子部から発せられた光が照射されることを示す。そしてファイバプレート860の下部に被写体を設けるようにする。なお図34において、画素102、EL素子部103およびフォトダイオード部104は図2と同じであるので、説明は省略する。また本明細書中では、基板上にマトリクス状に設けられている複数の画素をセンサ部とよぶが、図34ではその一部を示す。なお図35~38においても同様である。またファイバプレート860とは、ガラスファイバプレート820もしくは光ファイバプレート830のどちらかを示す。

40

**【0067】**

50

本実施の形態では、E L 素子が下面出射するためにファイバプレート860（ガラスファイバプレート820または光ファイバプレート830）をセンサ部が形成される基板として用いる。

#### 【0068】

ファイバプレート860はセンサ部が形成される基板として用いられ、ファイバプレート860をセンサ部と被写体804との間に設ける。上述したように、E L 素子部103から発せられた光がファイバプレート860を透過し、ファイバプレート860と空気との界面で全反射する光は光吸收層に吸収される。本実施の形態では、被写体とファイバプレート860が完全に密着している場合、また被写体とファイバプレート860との間の一部に空気が存在する場合、また被写体とファイバプレート860とが完全に離れている場合のいずれの場合においても、被写体の情報を正確によみとることができる。すなわち、被写体とファイバプレート860が完全に密着している場合では、フォトダイオード部104に照射される光は被写体からの反射光のみであり、また被写体とファイバプレート860との間の一部に空気が存在する場合、また被写体とファイバプレート860とが完全に離れている場合は、フォトダイオード部104に照射される光は被写体からの反射光とそれぞれのフォトダイオードに均一に照射されるノイズ光となる。すなわち、いずれの場合にも被写体の情報を正確に読み取ることができる。10

#### 【0069】

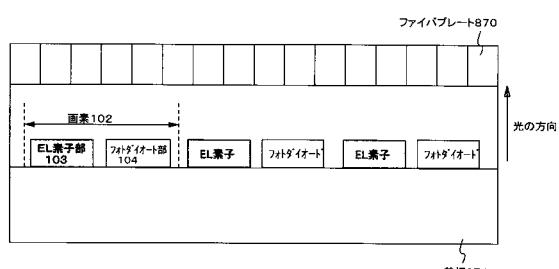

##### （実施の形態2）

本実施の形態では、実施の形態1とは異なる例について、図35を用いて説明する。本発明のエリアセンサ（表示装置）には、図29にあるようなガラスファイバプレート820、または図31にあるような光ファイバプレート830が被写体とセンサ部との間に設けられる。本実施の形態では、E L 素子部103に設けられたE L 素子が上面出射するエリアセンサ（表示装置）について、図35を用いて説明する。本明細書中で上面出射するとは、TFTを設けている基板上において、TFTを設けている側にE L 素子部から発せられた光が照射されることを示す。また被写体を読み取る際には、ファイバプレート870の上部に被写体を設けるようにする。20

#### 【0070】

本実施の形態では、E L 素子部103が上面出射するために、図29にあるようなガラスファイバプレート820、または図31にあるような光ファイバプレート830をセンサ部が形成される基板として用いることは出来ない。そのため本実施の形態で用いる基板871には、可撓性のプラスチックフィルム、ガラス基板、石英基板、プラスチック基板、シリコン基板もしくはセラミックス基板などの基板を用いるとよい。30

#### 【0071】

本実施の形態では、センサ部を形成した基板871上に絶縁膜などの保護膜を必要に応じて形成し、その上にファイバプレート870を設ける。

#### 【0072】

以上のようにして、ファイバプレート860をセンサ部と被写体との間に設ける。上述したように、E L 素子部103から発せられた光が、ファイバプレート860を透過し、ファイバプレート860と空気との界面で全反射する光は光吸收層に吸収される。本実施の形態では、被写体とファイバプレート860が完全に密着している場合、また被写体とファイバプレート860との間の一部に空気が存在する場合、また被写体とファイバプレート860とが完全に離れている場合のいずれの場合においても、被写体の情報を正確によみとることができ。すなわち、被写体とファイバプレート860が完全に密着している場合では、フォトダイオードに照射される光は被写体からの反射光のみであり、また被写体とファイバプレート860との間の一部に空気が存在する場合、また被写体とファイバプレート860とが完全に離れている場合は、フォトダイオードに照射される光は被写体からの反射光とそれぞれのフォトダイオードに均一に照射されるノイズ光となる。よって、いずれの場合にも被写体の情報を正確に読み取ることができる。40

#### 【0073】

50

なお、本実施の形態は実施の形態 1 と自由に組み合わせることが可能である。

**【 0 0 7 4 】**

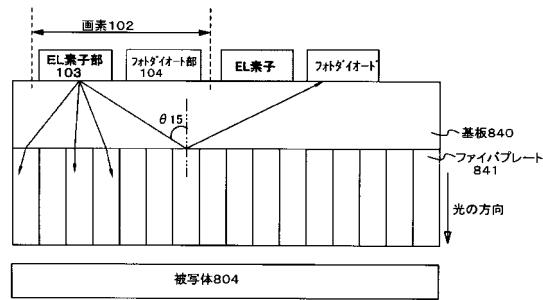

( 実施の形態 3 )

本実施の形態では、可撓性のプラスチックフィルム、ガラス基板、石英基板、プラスチック基板、シリコン基板もしくはセラミックス基板などの基板に、ガラスファイバプレート、または光ファイバプレートを光学のり等により接着したものを用いた表示装置（エリアセンサ）について図 3 6 を用いて説明する。光学のり等で接着する場合には、空気が入らないように注意する。なお用いられる光学のりは、用いる基板とガラスファイバプレートおよび光ファイバプレートとの界面で反射することを避けるために、ガラスファイバの光透過層、光ファイバのコア部および基板と屈折率が同じであることが望ましい。

10

**【 0 0 7 5 】**

本実施の形態では、EL 素子部 103 に設けられた EL 素子が下面出射するエリアセンサ（表示装置）について示す。基板 840 は、可撓性のプラスチックフィルム、ガラス基板、石英基板、プラスチック基板、シリコン基板もしくはセラミックス基板などのうちいずれかが用いられる。ファイバプレート 841 にはガラスファイバプレートもしくは光ファイバプレートのどちらかが用いられる。そして基板 840 とファイバプレート 841 を光学のり等により接着したものを、被写体とセンサ部との間に設ける。

**【 0 0 7 6 】**

EL 素子部 103 が下面出射する場合には、まず基板 840 上にセンサ部を形成し、その後、ファイバプレート 841 を接着してもよい。また、最初に基板 840 とファイバプレート 841 を接着しておき、その上にセンサ部を形成してもよい。このような作製工程は設計者が自由に設計することが出来る。

20

**【 0 0 7 7 】**

EL 素子部 103 から発せられた光は、あらゆる方向に拡散する。基板 840 とファイバプレート 841 の屈折率が異なる場合は、基板 840 とファイバプレート 841 との界面において、入射角によっては反射する光が生じる。このような反射光は、フォトダイオードに照射され、被写体の情報をぼやけて認識してしまう大きな原因となる。よって、基板 840 とファイバプレート 841 の屈折率は同じであることが望ましい。より詳細には、基板 840 とガラスファイバの光透過層、基板 840 と光ファイバのコア部との屈折率は同じあることが望ましい。また上述したように、基板 840 とファイバプレート 840 を接着する光学のりも屈折率は同じであることが望ましい。

30

**【 0 0 7 8 】**

EL 素子部 103 から発せられた光は、あらゆる方向に拡散して照射されるが、基板 840 とファイバプレート 841 との界面で反射する光以外は、EL 素子部 103 から発せられた光は、ファイバプレート 841 に入射される。ファイバプレート 841 とは、ガラスファイバプレートか光ファイバプレートのどちらか一つを示す。なおガラスファイバプレートまたは光ファイバプレートに光が入射した場合については上述してあるので、本実施の形態では説明は省略する。

**【 0 0 7 9 】**

なお被写体 804 とフォトダイオード部 104 の距離は、なるべく短い方が好ましい。そのため、本実施の形態で用いる基板 840 は、ファイバプレート 841 と接着するので、通常用いられる基板 840 よりも薄い方が好ましい。なおファイバプレート 841 の厚さは、ガラス基板の厚さよりも、厚くても構わない。例えばガラス基板を用いるときには、通常用いられるガラス基板（7mm 厚）よりも、比較的うすいガラス基板（5mm 厚）を用いてもよい。また通常用いられるガラス基板（7mm 厚）を研磨して、厚さを薄くして用いてもよい。

40

**【 0 0 8 0 】**

なお、本実施の形態は実施の形態 1 ~ 2 と自由に組み合わせることが可能である。

**【 0 0 8 1 】**

( 実施の形態 4 )

50

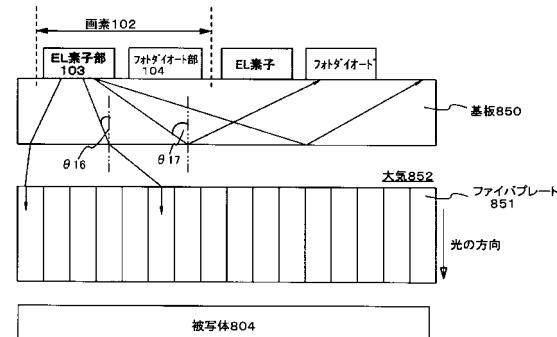

本実施の形態では、基板 850 とファイバプレート 851 の間に吸収材によるスペーサ(図示せず)を設けた例について、図 37 を用いて説明する。なお図 37 には、EL 素子部 103 に設けられた EL 素子が下面出射するエリアセンサ(表示装置)を示す。基板 850 とファイバプレート 851との間にスペーサ等を設ける場合には、基板 850 上に、均一に、且つ、等しい間隔ごとに設ける。ファイバプレート 851 とはガラスファイバプレートもしくは光ファイバプレートのどちらかを示す。また本実施の形態では、基板 850 とファイバプレート 851 の間に吸収材を設けたが、基板の外枠のみに基板 850 とファイバプレート 851 とを固定するスペーサ等を用いてもよい。スペーサが用いられる箇所は設計者が自由に設計することが出来る。基板 850 とファイバプレート 851 との間に用いるスペーサは、EL 素子部 103 から発せられた光が、基板 850 およびファイバプレート 851 との界面で全反射することを防ぐために、基板 850 およびファイバプレート 851 (より詳細には、ガラスファイバの光透過層および光ファイバのコア部を示す) と屈折率が同じであることが望ましい。また基板の外枠に用いるスペーサの屈折率は、特に限定されず、任意のもので構わない。なお図 37 では被写体 804 とファイバプレート 851 とが完全に離れている場合を示す。

#### 【0082】

EL 素子部 103 から発せられる光はあらゆる方向に拡散して照射される。図 37 に示すエリアセンサ(表示装置)においては、基板 850 とファイバプレート 851 との界面に空気 852 が存在するために、入射角の違いに応じて、基板 850 と空気 852 との界面において全反射する光と、屈折して屈折光としてファイバプレート 851 に入射する場合がある。図 37 においては、一例として屈折光及び全反射した光とを示し、基板 850 と空気 852 との界面において、入射角が  $\angle_{16}$  (ただし  $\angle_{16} < \max$ ) の場合は屈折して屈折光として出射しており、入射角が  $\angle_{17}$  (ただし  $\angle_{17} > \max$ ) の場合は、全反射してノイズ光としてフォトダイオードに照射されている。

#### 【0083】

EL 素子部 103 から発せられた光は、被写体 804 に向けてあらゆる方向に拡散して照射される。EL 素子部 103 から発せられた光は、基板 850 と空気 852 との界面に到達した場合、図 36 にあるように、入射角に応じて、反射光か屈折光かのどちらかとなる。

#### 【0084】

ここで、基板 850 をガラス基板とする。ガラス基板には、様々な屈折率のものが存在するが、本実施の形態では一例として、 $n = 1.52$  とする。数 4 (式(4)) および図 39 を参考にすると、EL 素子部 103 から発せられた光は、入射角が  $41.1^\circ$  以上の場合は全反射し、入射角が  $35^\circ$  以上  $41.1^\circ$  未満の場合は反射する光と屈折する光とが存在し、入射角が  $35^\circ$  以下の場合は、多くの場合は屈折光として被写体 804 に照射される。もちろん、全反射する光はノイズ光としてフォトダイオード部 104 に照射されるが、EL 素子部 103 から発せられる光は、あらゆる方向に拡散して照射され、かつ、基板 850 と空気 852 との界面において、図 39 を参照すると、それぞれの入射角の反射率に応じて、EL 素子部 103 から発せられた光は、全反射するため、フォトダイオード部 104 には均一にノイズ光が照射されるということが分かる。

#### 【0085】

また EL 素子部 103 から発せられた光が、基板 850 と空気 852 との界面で屈折光として基板 850 の外に出た場合は、ファイバプレート 851 に照射される。なおファイバプレート 851 とは、ガラスファイバプレートか光ファイバプレートのどちらかを示す。ガラスファイバプレートまたは光ファイバプレートに、光が入射した場合については、上述してあるため本実施の形態では説明は省略する。

#### 【0086】

ファイバプレート 851 を透過した光は、被写体 804 の反射率に応じて光が反射され、その反射光がフォトダイオード部 104 に照射される。すなわち本実施の形態においては、フォトダイオード部に照射される光は、被写体で反射した反射光と、それぞれのフォト

ダイオード部に均一に照射されるノイズ光となる。

**【0087】**

また本実施の形態のように、それぞれのフォトダイオードに均一に照射されるノイズ光の存在があらかじめ分かっている場合には、被写体の情報をより正確に読み取れるように、事前に均一に照射されるノイズ光を測定しておき、その測定した値をもとに被写体の情報を読み取ったときに信号を補正すればよい。このようにすると、ガラス基板803と被写体804とが完全に密着している場合、ガラス基板803と被写体804との間の一部に空気が存在する場合、ガラス基板803と被写体804とが完全に離れている場合の、いずれの場合においても被写体804の情報が正確によりみとれる。

**【0088】**

本実施の形態では、基板850とファイバプレート851とをスペーサ等により接着して用いるため、フォトダイオード部104と被写体804との距離が長くなってしまう。EL素子部103から発せられた光は、被写体804において反射し、その反射光は、被写体804の反射したところの直上のフォトダイオード部104に照射されるべきである。しかし、フォトダイオード部104と被写体804との距離が長い場合には、被写体804からの反射光が、本来照射されるべきではないフォトダイオード部104に光が照射される可能性が高くなる。このような光は、被写体804の情報をぼやけてよみとる原因となる。しかしこの場合には、ファイバプレート851の厚さを薄くする必要はなく、基板850の厚さをなるべく薄くする。また同様に、スペーサの厚さを調節することによって空気852の厚さをなるべく薄くする。

10

20

**【0089】**

なお、本実施の形態は実施の形態1～3と自由に組み合わせることが可能である。

**【0090】**

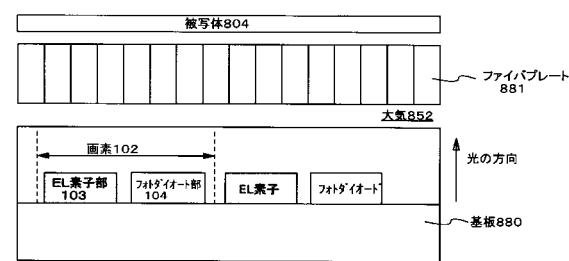

(実施の形態5)

本実施の形態では、基板880とファイバプレート881の間に吸収材によるスペーサ(図示せず)を設けた例について、図38を用いて説明する。なお図38には、EL素子部103に設けられたEL素子が上面出射するエリアセンサ(表示装置)を示す。なお、基板880とファイバプレート881との間にスペーサ等を設ける場合には、基板880上に、均一に等しい間隔ごとに設ける。ファイバプレート881とはガラスファイバプレートもしくは光ファイバプレートのどちらかを示す。また、本実施の形態では、基板の外枠に基板880とファイバプレート881とを固定するスペーサ等を用いてもよい。なお、基板880とファイバプレート881との間に用いるスペーサはEL素子部103から発せられた光が、基板850およびファイバプレート851との界面で全反射することを防ぐために、基板880およびファイバプレート881(ガラスファイバの光透過層および光ファイバのコア部を指す。)と屈折率が同じであることが望ましい。また、基板の外枠に用いるスペーサの屈折率は任意で構わない。なお、図38では被写体804とファイバプレート881とが完全に離れている場合を示す。

30

**【0091】**

本実施の形態では、センサ部を形成した基板880上に絶縁膜などの保護膜を形成し、その上にスペーサ等でファイバプレート881を設ける。本実施の形態では、EL素子部103から発せられる光が上面出射するために、被写体804とセンサ部の間にファイバプレート881を設けるためには、ガラスファイバプレートまたは光ファイバプレートをセンサ部が形成される基板として用いることが出来ない。そのため、本実施の形態で用いる基板880には、可撓性のプラスチックフィルム、ガラス基板、石英基板、プラスチック基板、シリコン基板もしくはセラミックス基板などの基板を用いればよい。

40

**【0092】**

本実施の形態では、センサ部を形成した基板880上に絶縁膜などの保護膜を形成し、その保護膜とファイバプレート881とをスペーサ等により接着して用いるため、フォトダイオード部104と被写体804との距離が長くなってしまう。EL素子部103から発せられた光は、被写体804において反射し、その反射光は、被写体804の反射したと

50

ころの直上のフォトダイオード部 104 に照射されるべきである。しかしフォトダイオード部 104 と被写体 804 との距離が長い場合には、被写体 804 からの反射光が、本来照射されるべきではないフォトダイオード部 104 に光が照射される可能性が高くなる。このような光は、被写体 804 の情報をぼやけてよみとる原因となる。しかし、この場合は、ファイバプレート 881 の厚さを薄くする必要はなく、基板 880 の厚さをなるべく薄くする。また同様に、スペーサの厚さを調節することによって空気 852 の厚さをなるべく薄くする。

#### 【0093】

なお、本実施の形態は実施の形態 1～4 と自由に組み合わせることが可能である。

#### 【0094】

10

#### 【実施例】

以下に、本発明の実施例について説明する。

#### 【0095】

##### (実施例 1)

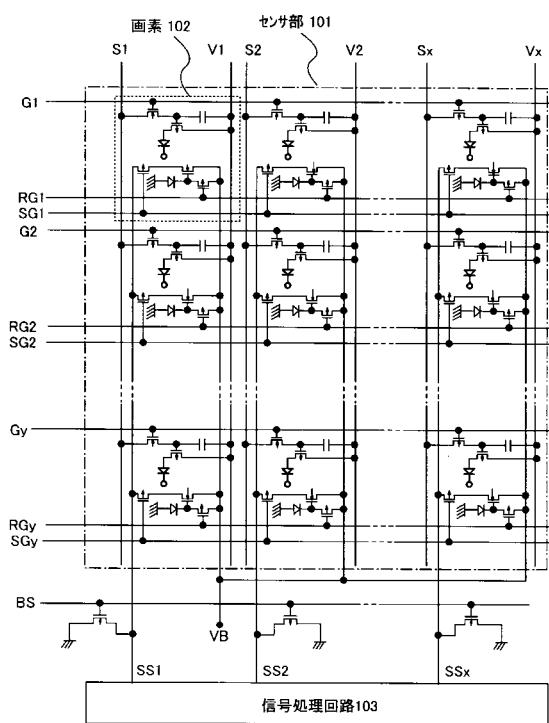

以下に、本発明のエリアセンサ（表示装置）の構成を詳しく説明する。本発明のエリアセンサ（表示装置）は被写体の情報の読み取り、および画像の表示を行うセンサ部と、センサ部の駆動を制御する駆動部とを有している。図 1 に本発明のセンサ部の回路図を示す。

#### 【0096】

センサ部 101 はソース信号線 S1～Sx、電源供給線 V1～Vx、ゲート信号線 G1～Gy、リセット信号線 RG1～RGy、選択信号線 SG1～SGy、センサ用信号出力線 SS1～SSx、センサ用電源線 VB が設けられている。

20

#### 【0097】

センサ部（画素部）101 は複数の画素 102 を有している。画素 102 は、ソース信号線 S1～Sx のいずれか 1 つと、電源供給線 V1～Vx のいずれか 1 つと、ゲート信号線 G1～Gy のいずれか 1 つと、リセット信号線 RG1～RGy のいずれか 1 つと、選択信号線 SG1～SGy のいずれか 1 つと、センサ用信号出力線 SS1～SSx のいずれか 1 つと、センサ用電源線 VB、とを有している。センサ用信号出力線 SS1～SSx は、信号処理回路 103 に接続されている。

#### 【0098】

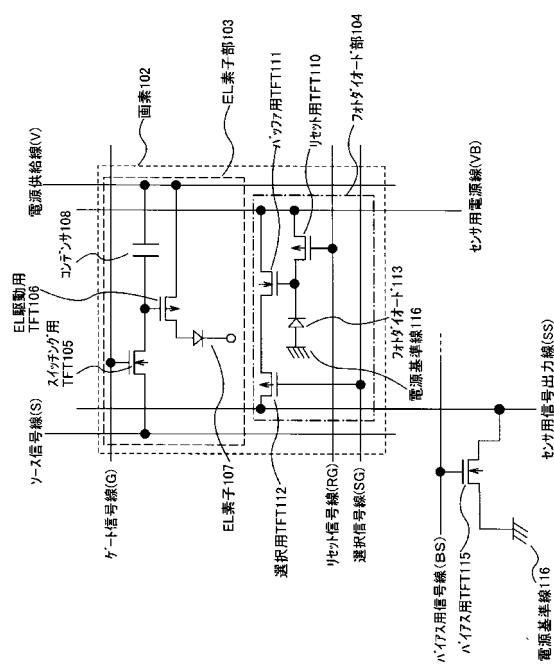

図 2 に画素 102 の詳しい構成を示す。点線で囲まれた領域が画素 102 であり、EL 素子部 103 とフォトダイオード部 104 に分けられる。

30

#### 【0099】

ソース信号線 S は、ソース信号線 S1～Sx のいずれか 1 つを意味する。電源供給線 V は電源供給線 V1～Vx のいずれか 1 つを意味する。ゲート信号線 G はゲート信号線 G1～Gy のいずれか 1 つを意味する。リセット信号線 RG はリセット信号線 RG1～RGy のいずれか 1 つを意味する。選択信号線 SG は、選択信号線 SG1～SGy のいずれか 1 つを意味する。センサ用信号出力線 SS はセンサ用信号出力線 SS1～SSx のいずれか 1 つを意味する。

#### 【0100】

画素 102 はスイッチング用 TFT105、EL 駆動用 TFT106、EL 素子 107 を有している。また図 2 では画素 102 にコンデンサ 108 が設けられているが、コンデンサ 108 を設けなくても良い。

40

#### 【0101】

EL 素子 107 は陽極と陰極と、陽極と陰極との間に設けられた EL 層とからなる。陽極が EL 駆動用 TFT106 のソース領域またはドレイン領域と接続している場合、陽極が画素電極、陰極が対向電極となる。逆に陰極が EL 駆動用 TFT106 のソース領域またはドレイン領域と接続している場合、陽極が対向電極、陰極が画素電極である。

#### 【0102】

スイッチング用 TFT105 のゲート電極はゲート信号線 G に接続されている。そしてスイッチング用 TFT105 のソース領域とドレイン領域は、一方がソース信号線 S に、も

50

う一方が E L 駆動用 T F T 1 0 6 のゲート電極に接続されている。

**【 0 1 0 3 】**

E L 駆動用 T F T 1 0 6 のソース領域とドレイン領域は、一方が電源供給線 V に、もう一方が E L 素子 1 0 7 に接続されている。コンデンサ 1 0 8 は E L 駆動用 T F T 1 0 6 のゲート電極と電源供給線 V とに接続して設けられている。

**【 0 1 0 4 】**

さらに画素 1 0 2 は、リセット用 T F T 1 1 0 、バッファ用 T F T 1 1 1 、選択用 T F T 1 1 2 、フォトダイオード 1 1 3 を有している。

**【 0 1 0 5 】**

リセット用 T F T 1 1 0 のゲート電極はリセット信号線 R G に接続されている。リセット用 T F T 1 1 0 のソース領域はセンサ用電源線 V B に接続されている。またリセット用 T F T 1 1 0 のドレイン領域はフォトダイオード 1 1 3 及びバッファ用 T F T 1 1 1 のゲート電極に接続されている。10

**【 0 1 0 6 】**

フォトダイオード 1 1 3 は p チャネル側端子と、 n チャネル側端子と、 p チャネル側端子と n チャネル側端子の間に設けられた光電変換層とを有している。リセット用 T F T 1 1 0 のドレイン領域は、具体的にはフォトダイオード 1 1 3 の n チャネル側端子または p チャネル側端子に接続されている。

**【 0 1 0 7 】**

バッファ用 T F T 1 1 1 のドレイン領域はセンサ用電源線 V B に接続されている。そしてバッファ用 T F T 1 1 1 のソース領域は選択用 T F T 1 1 2 のソース領域またはドレイン領域に接続されている。20

**【 0 1 0 8 】**

選択用 T F T 1 1 2 のゲート電極は選択信号線 S G に接続されている。そして選択用 T F T 1 1 2 のソース領域とドレイン領域は、一方は上述したとおりバッファ用 T F T 1 1 1 のソース領域に接続されており、もう一方はセンサ用信号出力線 S S に接続されている。センサ用信号出力線 S S はバイアス用 T F T 1 1 5 と接続されている。

**【 0 1 0 9 】**

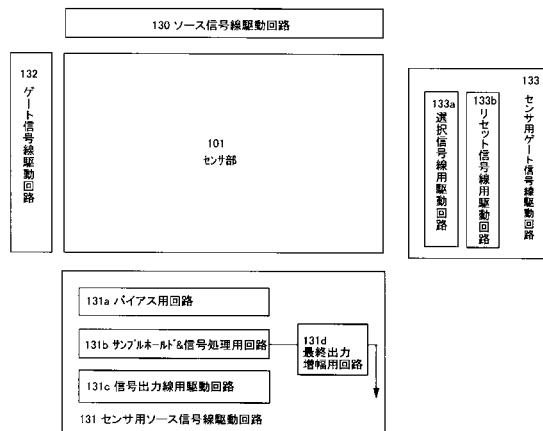

次に本発明のエリアセンサ（表示装置）の駆動方法について、図 3 ~ 図 9 を用いて説明する。30

**【 0 1 1 0 】**

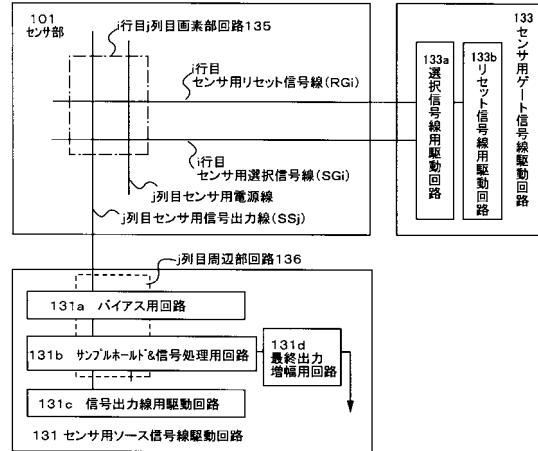

本実施例では、センサ部 1 0 1 の周辺に駆動回路を搭載し、画素を 2 次元に配置したエリアセンサについて説明する。より詳しくは、フォトダイオード 1 1 3 およびリセット用 T F T 1 1 0 、バッファ用 T F T 1 1 1 および選択用 T F T 1 1 2 の駆動方法について説明する。本発明のエリアセンサ（表示装置）の回路図（概略図）を図 3 に示す。まず、画素が 2 次元に配列されたセンサ部 1 0 1 がある。そして、各々の画素のゲート信号線やリセット信号線を駆動するための駆動回路が、センサ部 1 0 1 の周りにそれぞれ配置されている。図 3 ではソース信号線駆動回路 1 3 0 、ゲート信号線用駆動回路 1 3 2 、センサ用ソース信号線駆動回路 1 3 1 、センサ用ゲート信号線駆動回路 1 3 3 がそれぞれ配置されている。40

**【 0 1 1 1 】**

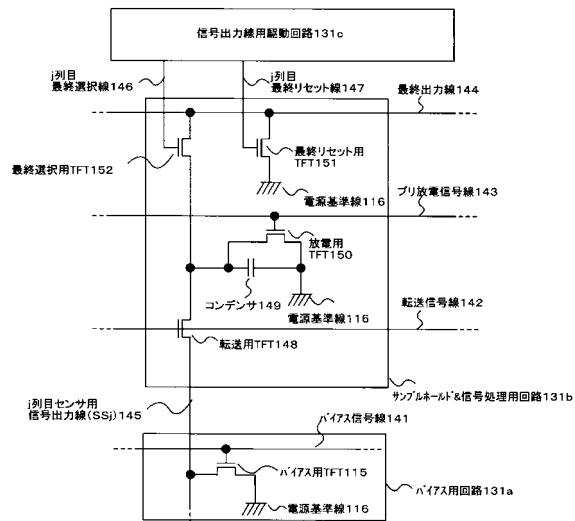

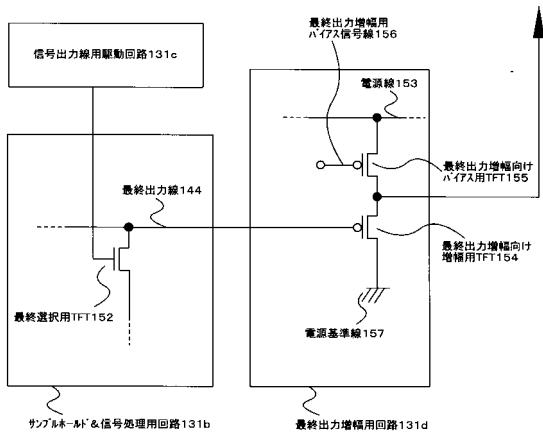

図 4 は、図 3 に示すセンサ部 1 0 1 、センサ用ゲート信号線駆動回路 1 3 3 およびセンサ用ソース信号線駆動回路 1 3 1 を示し、画素 1 0 2 が有するフォトダイオード部 1 0 4 の駆動方法についてより詳しく説明する。センサ用ソース信号線駆動回路 1 3 1 は、バイアス用回路 1 3 1 a 、サンプルホールド & 信号処理用回路 1 3 1 b 、信号出力用駆動回路 1 3 1 c を有している。

**【 0 1 1 2 】**

バイアス用回路 1 3 1 a は、各画素のバッファ用 T F T 1 1 1 と対になって、ソースフォロワ回路を形成する。図 3 において、バイアス用回路 1 3 1 a の下方には、サンプルホールド & 信号処理用回路 1 3 1 b が配置されている。サンプルホールド & 信号処理用回路 1 3 1 c が配置されている。50

31bでは、信号をいったん保存しておいたり、アナログ・デジタル変換を行ったり、雑音を低減したりするための回路である。そしてサンプルホールド&信号処理用回路131bの下方には、信号出力用駆動回路131cが配置されている。信号出力用駆動回路131cは、一時的に保存されていた信号を、順に出力していくための信号を出力している回路である。そして最終出力増幅用回路131dは、サンプルホールド&信号処理用回路131bと信号出力用駆動回路131cとから出力された信号を、外部に信号を出力ために増幅している。つまり信号を増幅しない場合は不必要であるが、現状では配置される場合が多い。

#### 【0113】

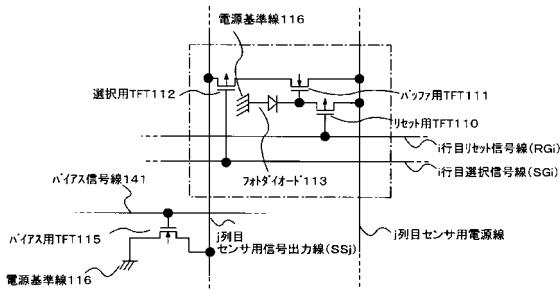

次いで、各部分の回路図を示す。図5にi行目j列目の画素部回路135のフォトダイオード部104の回路図を示す。図5では、Pチャネル型リセット用TFT110、Pチャネル型選択用TFT112、Nチャネル型バッファ用TFT111、光電変換素子（ここでは、最も代表的なフォトダイオード113）から構成されている。また参考のために、Nチャネル型バイアス用TFT115も記述している。

10

#### 【0114】

フォトダイオード113のPチャネル側端子は電源基準線116に、Nチャネル側端子は、バッファ用TFT111のゲート端子に接続されている。リセット用TFT110のゲート端子には、i行目リセット信号線(RGi)が接続され、ソース端子とドレイン端子は、j列目センサ用電源線とバッファ用TFT111のゲート端子に接続されている。選択用TFT112のゲート端子は、i行目選択信号線(SGi)に接続され、ソース端子とドレイン端子は、j列目センサ用信号出力線(SSj)とバッファ用TFT111に接続されている。バッファ用TFT111のソース端子とドレイン端子は、j列目センサ用電源線と選択用TFT112に接続されている。

20

#### 【0115】

図5ではリセット用TFT110として、Pチャネル型TFTを用いているが、Nチャネル型でもよい。しかしNチャネル型の場合には、リセット動作のときに、ゲート・ソース間電圧が大きくとれない。よって、リセット用TFTが飽和領域で動作することになり、フォトダイオード113を十分に充電できない。すなわちリセット用TFT110は、Nチャネル型でも動作するが、Pチャネル型の方が望ましい。

#### 【0116】

30

Pチャネル型選択用TFT112は、j列目センサ用信号出力線(SSj)とバッファ用TFT111の間に配置し、かつ、Pチャネル型を用いるのが望ましい。しかし、従来と同様に、Nチャネル型でも動作するため、Nチャネル型でも構わない。またセンサ用電源線(VB)とバッファ用TFT111の間に配置しても構わない。しかし、正確に信号を出力しにくいため、選択用TFT112は、j列目センサ用電源線(VB)とバッファ用TFT111の間に配置し、かつ、Pチャネル型を用いるのが望ましい。

#### 【0117】

バッファ用TFT111は、図5では、Nチャネル型を用いているが、Pチャネル型を用いることも可能である。しかし、Pチャネル型バッファ用TFTとバイアス用TFTを組み合わせてソースフォロワ回路として動作させるためには、回路の接続方法を変更する必要がある。つまり図5の回路図において、バッファ用TFT141の極性をえるだけでは、動作しないので、適宜周辺回路に応じた極性のTFTを用いるようにするとよい。

40

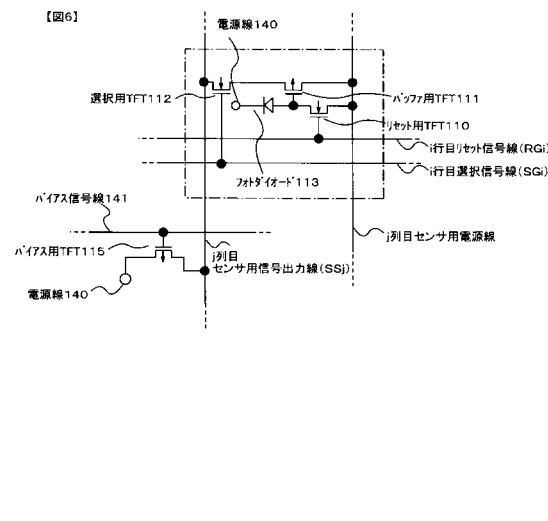

#### 【0118】

そこで、Pチャネル型のバッファ用TFT111を用いた場合の回路構成の一例を図6に示す。図5と異なる点は、バッファ用TFT111とバイアス用TFT115の極性はPチャネル型である点、リセット用TFT110と選択用TFT112の極性がNチャネル型である点、フォトダイオード113の向きが逆になっている点、バイアス用TFT115およびフォトダイオード113のNチャネル側端子が電源線140に接続されている点が挙げられる。

#### 【0119】

50

バッファ用 TFT111 に P チャネル型を用いる場合は、バイアス用 TFT115 も P チャネル型を用いる必要がある。バイアス用 TFT115 は、定電流源として動作させる必要があるからである。図 6 に示すフォトダイオード部 104 は、N チャネル型リセット用 TFT110、N チャネル型選択用 TFT112、P チャネル型バッファ用 TFT111、光電変換素子（ここでは、最も代表的なフォトダイオード 113）から構成されている。

#### 【 0120 】

フォトダイオード 113 は N チャネル側端子と P チャネル側端子を有し、N チャネル側端子は電源線 140 に、P チャネル側端子は P チャネル型バッファ用 TFT111 のゲート端子に接続されている。N チャネル型リセット用 TFT110 のゲート端子には、 $i$  行目リセット信号線（RG $i$ ）が接続され、ソース端子とドレイン端子は、センサ用電源線（VB）と P チャネル型バッファ用 TFT111 のゲート端子に接続されている。N チャネル型選択用 TFT112 のゲート端子は、 $i$  行目選択信号線（SG $i$ ）に接続され、ソース端子とドレイン端子は、 $j$  列目センサ用信号出力線（SS $j$ ）と P チャネル型バッファ用 TFT111 に接続されている。P チャネル型バッファ用 TFT111 のソース端子とドレイン端子は、 $j$  列目センサ用信号出力線（SS $j$ ）と N チャネル型選択用 TFT112 に接続されている。P チャネル型バイアス用 TFT115 のゲート端子は、バイアス信号線 141 に接続され、ソース端子とドレイン端子は、センサ用信号出力線（SS $x$ ）と電源線 140 に接続されている。

#### 【 0121 】

リセット用 TFT110 は、N チャネル型を用いている。しかしリセット用 TFT110 は、P チャネル型でもよいが、リセット動作のとき、ゲート・ソース間電圧が大きくとれない。そのため、リセット用 TFT110 が飽和領域で動作することになり、フォトダイオード 113 を十分に充電できない。つまりリセット用 TFT110 は、P チャネル型でも動作するが、N チャネル型の方が望ましい。

#### 【 0122 】

選択用 TFT112 については、センサ用信号出力線（SS $x$ ）とバッファ用 TFT111 の間に配置し、かつ、N チャネル型を用いるのが望ましい。しかし、P チャネル型でも構わない。また、センサ用電源線（VB）とバッファ用 TFT111 の間に配置しても構わない。ただし、正しく信号を出力しにくいため、選択用 TFT112 は、 $j$  列目センサ用信号出力線（SS $j$ ）とバッファ用 TFT111 の間に配置し、かつ、N チャネル型を用いるのが望ましい。

#### 【 0123 】

このように、図 5 と図 6 を比較すると分かるように、バッファ用 TFT の極性が異なると、最適な TFT の構成、フォトダイオードの向きなども異なる。また図 5 では、選択用 TFT112 とリセット用 TFT110 の両方に、1 本の電源線から電流を供給している。図 6 では、選択用 TFT112 とリセット用 TFT110 の両方に、1 本の電源基準線から電流を供給している。このように、フォトダイオードの向きとバッファ用 TFT の極性をあわせることにより、配線を共有することができる。

#### 【 0124 】

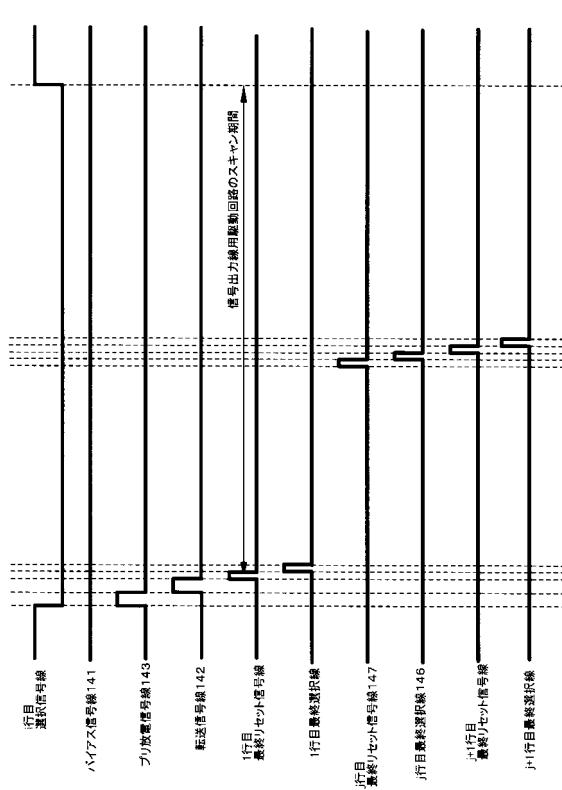

次いで図 7 には、バイアス用回路 131a、サンプルホールド & 信号処理用回路 131b、信号出力線用駆動回路 131c の  $j$  列目周辺部回路 136 の回路図を示す。バイアス用回路 131a には、バイアス用 TFT115 が配置されている。その極性は、各画素のバッファ用 TFT111 の極性と同じである。

#### 【 0125 】

図 7 に示すバイアス用 TFT115 は、N チャネル型 TFT である。バイアス用 TFT115 のゲート端子には、バイアス信号線 141 が接続され、ソース端子とドレイン端子は、 $j$  列目センサ用信号出力線（SS $j$ ）145 と電源基準線 116 に接続されている（バイアス用 TFT115 が P チャネル型の場合は、電源基準線 116 のかわりに、電源線 140 に接続される）。N チャネル型バイアス用 TFT115 は、各画素のバッファ用 TFT

10

20

30

40

50

T 1 1 1 と対になって、ソースフォロワ回路として動作する。

**【 0 1 2 6 】**

転送用 T F T 1 4 8 のゲート端子には、転送信号線 1 4 2 が接続され、ソース端子とドレイン端子は、j 列目センサ用信号出力線 ( S S j ) 1 4 5 とコンデンサ 1 4 9 にそれぞれ接続されている。転送用 T F T 1 4 8 は、j 列目センサ用信号出力線 ( S S j ) 1 4 5 の電位をコンデンサ 1 4 9 に転送する場合に動作する。また、P チャネル型の転送用 T F T 1 4 8 を追加して、N チャネル型転送用 T F T 1 4 8 と並列に接続してもよい。コンデンサ 1 4 9 は、転送用 T F T 1 4 8 と電源基準線 1 1 6 に接続されている。コンデンサ 1 4 9 の役割は、j 列目センサ用信号出力線 ( S S j ) 1 4 5 から出力される信号を一時的に蓄積することである。放電用 T F T 1 5 0 のゲート端子は、プリ放電信号線 1 4 3 に接続され、ソース端子とドレイン端子は、コンデンサ 1 4 9 と電源基準線 1 1 6 にそれぞれ接続されている。放電用 T F T 1 5 0 は、j 列目センサ用信号出力線 ( S S j ) 1 4 5 の電位をコンデンサ 1 4 9 に入力する前に、コンデンサ 1 4 9 に蓄積されている電荷を放電するように動作する。

10

**【 0 1 2 7 】**

なお、アナログ・デジタル信号変換回路や雑音低減回路などを配置することも可能である。

**【 0 1 2 8 】**

そして、コンデンサ 1 4 9 と最終出力線 1 4 4 の間に、最終選択用 T F T 1 5 2 が接続される。最終選択用 T F T 1 5 2 のソース端子とドレイン端子は、コンデンサ 1 4 9 と最終出力線 1 4 4 にそれぞれ接続され、ゲート端子は j 列目最終選択線 1 4 6 に接続される。最終選択線は、センサ部においてマトリクス状に配置されており、1 列目から × 列目まで順にスキャンしていく。そして j 列目最終出力線 1 4 4 が選択され、最終選択用 T F T 1 5 2 が導通状態になると、コンデンサ 1 4 9 の電位と j 列目最終出力線 1 4 4 の電位が等しくなる。その結果、コンデンサ 1 4 9 に蓄積していた信号を最終出力線 1 4 4 に出力することができる。

20

**【 0 1 2 9 】**

ただし、最終出力線 1 4 4 に信号を出力する前に、最終出力線 1 4 4 に電荷が蓄積されていると、その電荷によって最終出力線 1 4 4 に信号を出力したときの電位が影響を受ける。そこで、最終出力線 1 4 4 に信号を出力する前に、最終出力線 1 4 4 の電位を、ある特定の電位値に初期化することが必要である。

30

**【 0 1 3 0 】**

図 7 には、最終出力線 1 4 4 と電源基準線 1 1 6 の間に、最終リセット用 T F T 1 5 1 を配置している図を示している。そして、最終リセット用 T F T 1 5 1 のゲート端子には、j 列目最終リセット線 1 4 7 が接続されている。そして、j 列目最終選択線 1 4 6 を選択する前に、j 列目最終リセット線 1 4 7 を選択し、最終出力線 1 4 4 の電位を電源基準線 1 1 6 の電位に初期化する。その後、j 列目最終選択線 1 4 6 を選択し、最終出力線 1 4 4 に、コンデンサ 1 4 9 に蓄積されていた信号を出力する。

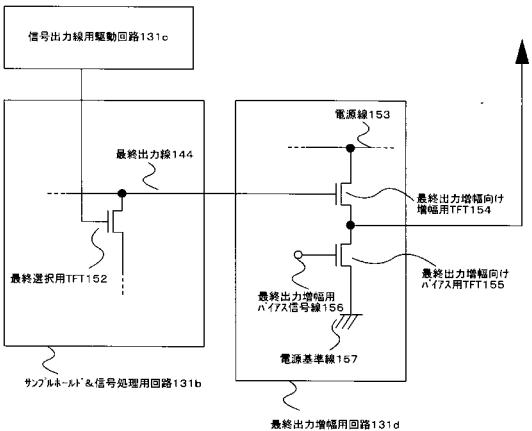

**【 0 1 3 1 】**

最終出力線 1 4 4 に出力される信号は、そのまま外部に取り出しても良い。しかし、信号が微弱であるため、外部に取り出す前に増幅しておく場合が多い。図 8 には、信号を増幅するための回路として、最終出力增幅用回路 1 3 1 d の回路を示す。信号を増幅するための回路としては、演算増幅器などさまざまな種類があるが、本実施例では、最も簡単な回路構成として、ソースフォロワ回路を示す。

40

**【 0 1 3 2 】**

図 8 には、ソースフォロワ回路が N チャネル型の場合の回路図を示す。最終出力增幅用回路 1 3 1 d への入力は、最終出力線 1 4 4 を介して行われる。最終出力線 1 4 4 は、センサ部においてマトリクス状に配置されており、その 1 列目から順に信号が出力される。その信号は、最終出力增幅用回路 1 3 1 d において増幅されて、外部に出力する。最終出力線 1 4 4 は、最終出力增幅向け増幅用 T F T 1 5 4 のゲート端子に接続される。最終出力

50

増幅向け増幅用 TFT154 のドレイン端子は、電源線 153 に接続され、ソース端子は、出力端子となる。最終出力増幅向けバイアス用 TFT155 のゲート端子は、最終出力増幅用バイアス信号線 156 と接続される。また最終出力増幅向けバイアス用 TFT155 のソース端子とドレイン端子は、一方は電源基準線 157 に接続され、もう一方は最終出力増幅向け増幅用 TFT154 のソース端子に接続される。

#### 【0133】

図 9 には、ソースフォロワ回路が P チャネル型の場合の回路図を示す。最終出力線 144 は、最終出力増幅向け増幅用 TFT154 のゲート端子に接続される。最終出力増幅向け増幅用 TFT154 のドレイン端子は、電源基準線 157 に接続され、ソース端子は、出力端子となる。最終出力増幅向けバイアス用 TFT155 のゲート端子は、最終出力増幅用バイアス信号線 156 と接続される。また最終出力増幅向けバイアス用 TFT155 のソース端子とドレイン端子は、一方は電源線 153 に接続され、もう一方は最終出力増幅向け増幅用 TFT154 のソース端子に接続される。なお最終出力増幅用バイアス信号線 156 の電位は、N チャネル型を用いた場合の最終出力増幅用バイアス信号線 156 の電位とは異なる。

10

#### 【0134】

図 8 と図 9 では、ソースフォロワ回路を 1 段のみで構成していた。しかし、複数段で構成しても良い。例えば、2 段で構成する場合は、1 段目の出力端子を 2 段目の入力端子に接続すればよい。また各々の段において、N チャネル型を用いても、P チャネル型を用いても、どちらでも良い。つまりソースフォロワ回路は、設計者が自由に設計することが出来る。

20

#### 【0135】

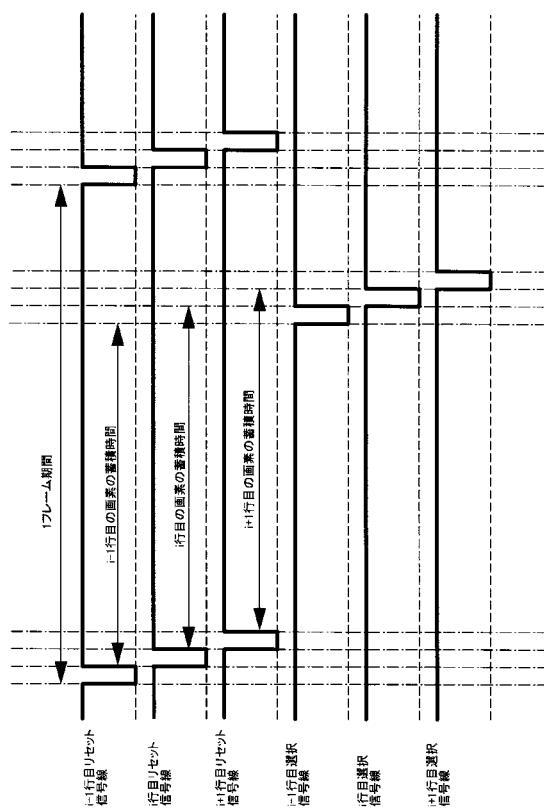

次いで、信号のタイミングチャートについて説明する。始めに、図 4 と図 5 に示す回路における信号のタイミングチャートについて、図 10 を用いて説明する。リセット信号線 RG は、1 行目から y 行目まで順にスキャンしていく。そして、再び同じ行を選択するまでの期間が 1 フレーム期間に相当する。

#### 【0136】

選択信号線 SG も、同様に、1 行目から y 行目まで順にスキャンしていく。ただし、リセット信号線 RG をスキャンし始めるタイミングよりも、選択信号線 SG をスキャンし始めるタイミングの方が遅い。例えば、i 行目の画素 102 に着目すると、i 行目リセット信号線 SRI が選択されて、その後、i 行目選択信号線 SGi が選択される。次いで i 行目ゲート信号線 SSi が選択されると、i 行目の画素 102 から信号が出力される。なお画素 102 がリセットされてから、信号を出力する時までの期間は蓄積時間に相当する。蓄積時間では、フォトダイオードで光によって生成される電荷を蓄積している。各行で、リセットされるタイミングと信号を出力するタイミングは異なっているが、蓄積時間は全ての行の画素 102 で等しくなる。

30

#### 【0137】

次に、図 7 に示す回路図における信号のタイミングチャートを図 11 に示す。繰り返しの動作になるため、本実施例では一例として、i 行目の選択信号線 SGi が選択されたときを説明する。まず、i 行目の選択信号線 SGi が選択された後、プリ放電信号線 171 を選択し、放電用 TFT167 を導通状態にする。その後、転送信号線 170 を選択する。すると、i 行目の画素 102 から、各列の信号が各列のコンデンサ 149 に出力される。

40

#### 【0138】

i 行目に設けられた全ての画素 102 の信号を、各列のコンデンサ 149 に蓄積した後、最終出力線 144 に各列の信号を順に出力していく。転送信号線 142 が非選択されると、信号出力用駆動回路 131c により、1 列目から x 列目までをスキャンしていく。まず 1 列目の最終リセット線を選択し、最終リセット用 TFT151 を導通状態にし、最終出力線 144 を電源基準線 116 の電位に初期化する。その後、1 列目の最終選択線を選択し、最終選択用 TFT152 を導通状態にし、1 列目のコンデンサ 149 の信号を最終出力線 144 に出力する。

50

**【 0 1 3 9 】**

次に、2列目の最終リセット線を選択し、最終リセット用 T F T 1 5 1 を導通状態にし、最終出力線 1 4 4 を電源基準線 1 6 4 の電位に初期化する。その後、2列目の最終選択線を選択し、最終選択用 T F T 1 5 2 を導通状態にし、2列目のコンデンサ 1 4 9 の信号を最終出力線 1 4 4 に出力する。その後は、同様の動作を繰り返していく。

**【 0 1 4 0 】**

j列目の場合も、j列目最終リセット線 1 4 7 を選択し、最終リセット用 T F T 1 5 1 を導通状態にし、最終出力線 1 4 4 を電源基準線 1 1 6 の電位に初期化する。その後、j列目最終選択線 1 4 6 を選択し、最終選択用 T F T 1 5 2 を導通状態にし、j列目のコンデンサ 1 4 9 の信号を最終出力線 1 4 4 に出力する。

10

**【 0 1 4 1 】**

次に、(j + 1)列目の最終リセット線を選択し、最終リセット用 T F T 1 5 1 を導通状態にし、最終出力線 1 4 4 を電源基準線 1 1 6 の電位に初期化する。その後、(j + 1)列目最終選択線 1 4 6 を選択し、最終選択用 T F T 1 5 2 を導通状態にし、(j + 1)列目のコンデンサ 1 4 9 の信号を最終出力線 1 4 4 に出力する。その後は、同様の動作を繰り返し、全ての列の信号を最終出力線 1 4 4 に、順次出力していく。そのあいだ、バイアス信号線 1 4 1 は、一定に保たれている。そして最終出力線 1 4 4 に出力された信号は、最終出力增幅用回路 1 3 1 d で増幅され、外部へ出力されていく。

**【 0 1 4 2 】**

次に、(i + 1)行目ゲート信号線が選択される。すると、i行目ゲート信号線が選択されたのと同様に、動作する。そして、(i + 2)行目のゲート信号線が選択され、同様の動作を繰り返していく。

20

**【 0 1 4 3 】**

なお、光電変換などを行うセンサ部については、通常使用されている P N 型のフォトダイオードの他に、P I N 型のダイオード、アバランシェ型ダイオード、N P N 埋め込み型ダイオード、ショットキー型ダイオード、X 線用のフォトコンダクタ、赤外線用のセンサなどでもよい。また蛍光材やシンチレータにより、X 線を光に変換した後、その光を読み取ってもよい。

**【 0 1 4 4 】**

上述のように、光電変換素子は、ソースフォロワ回路の入力端子に接続されることが多い。しかし、フォトゲート型の光電変換素子を用いる場合には、スイッチを間に挟んでもよい。また、対数変換型の光電変換素子を用いる場合には、光強度の対数値なるように処理した後の信号を入力端子に入力してもよい。

30

**【 0 1 4 5 】**

なお、本実施の形態では、画素が2次元に配置されたエリアセンサについて述べたが、画素が1次元に配置されたラインセンサにも応用することも出来る。

**【 0 1 4 6 】**

なお本実施例は、実施の形態 1 ~ 5 と自由に組み合わせることが可能である。

**【 0 1 4 7 】**

(実施例 2 )

本実施例では、図 2 に示すところの E L 素子 1 0 6 の動作を制御している、スイッチング用 T F T 1 0 5 及び E L 駆動用 T F T 1 0 6 の駆動方法について説明する。なおセンサ部 1 0 1 の構成は実施例 1 で示した構成と同じであるので、図 1 及び図 2 を参照するとよい。

40

**【 0 1 4 8 】**

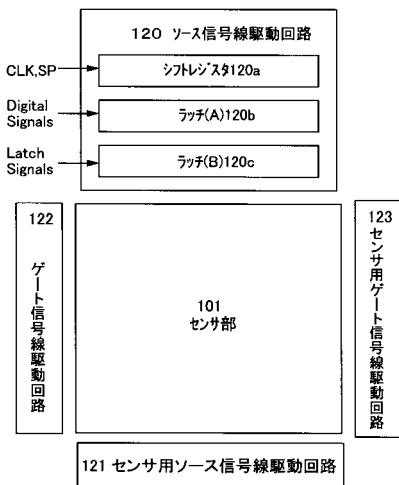

図 1 2 に本実施例のエリアセンサの上面図を示す。1 2 0 はソース信号線駆動回路、1 2 2 はゲート信号線駆動回路であり、共にスイッチング用 T F T 1 0 5 及び E L 駆動用 T F T 1 0 6 の駆動を制御している。また 1 2 1 はセンサ用ソース信号線駆動回路、1 2 3 はセンサ用ゲート信号線駆動回路であり、共にリセット用 T F T 1 1 0 、バッファ用 T F T 1 1 1 及び選択用 T F T 1 1 2 の駆動を制御している。なお本明細書において、ソース信

50

号線駆動回路 120、ゲート信号線駆動回路 122、センサ用ソース信号線駆動回路 121、センサ用ゲート信号線駆動回路 123 を駆動部と呼ぶ。

#### 【0149】

ソース信号線駆動回路 120 は、シフトレジスタ 120a、ラッチ (A) 120b、ラッチ (B) 120c を有している。ソース信号線駆動回路 120 において、シフトレジスタ 120a にクロック信号 (CLK) およびスタートパルス (SP) が入力される。シフトレジスタ 120a は、これらのクロック信号 (CLK) およびスタートパルス (SP) に基づきタイミング信号を順に発生させ、後段の回路へタイミング信号を順次供給する。

#### 【0150】

なおシフトレジスタ 120a からのタイミング信号を、バッファ等 (図示せず) によって緩衝増幅し、後段の回路へ緩衝増幅したタイミング信号を順次供給しても良い。タイミング信号が供給される配線には、多くの回路あるいは素子が接続されているために負荷容量 (寄生容量) が大きい。この負荷容量が大きいために生ずるタイミング信号の立ち上がりまたは立ち下がりの “鈍り” を防ぐために、このバッファが設けられる。

10

#### 【0151】

シフトレジスタ 120a からのタイミング信号は、ラッチ (A) 120b に供給される。ラッチ (A) 120b は、デジタル信号 (digital signals) を処理する複数のステージのラッチを有している。ラッチ (A) 120b は、前記タイミング信号が入力される同時に、デジタル信号を順次書き込み、保持する。

20

#### 【0152】

なお、ラッチ (A) 120b にデジタル信号を取り込む際に、ラッチ (A) 120b が有する複数のステージのラッチに、順にデジタル信号を入力しても良い。しかし本発明はこの構成に限定されない。ラッチ (A) 120b が有する複数のステージのラッチをいくつかのグループに分け、グループごとに並行して同時にデジタル信号を入力する、いわゆる分割駆動を行っても良い。なおこのときのグループの数を分割数と呼ぶ。例えば 4 つのステージごとにラッチをグループに分けた場合、4 分割で分割駆動すると言う。

20

#### 【0153】

ラッチ (A) 120b の全ステージのラッチへのデジタル信号の書き込みが一通り終了するまでの時間を、ライン期間と呼ぶ。すなわち、ラッチ (A) 120b 中で一番左側のステージのラッチにデジタル信号の書き込みが開始される時点から、一番右側のステージのラッチにデジタル信号の書き込みが終了する時点までの時間間隔がライン期間である。実際には、上記ライン期間に水平帰線期間が加えられた期間をライン期間に含むことがある。

30

#### 【0154】

1 ライン期間が終了すると、ラッチ (B) 120c にラッチシグナル (Latch Signal) が供給される。この瞬間、ラッチ (A) 120b に書き込まれ保持されているデジタル信号は、ラッチ (B) 120c に一斉に送出され、ラッチ (B) 120c の全ステージのラッチに書き込まれ、保持される。

#### 【0155】

デジタル信号をラッチ (B) 120c に送出し終えたラッチ (A) 120b は、シフトレジスタ 120a からのタイミング信号に基づき、再びデジタル信号の書き込みを順次行う。

40

#### 【0156】

この 2 順目の 1 ライン期間中には、ラッチ (B) 120b に書き込まれ、保持されているデジタル信号がソース信号線 (S1 ~ Sx) に入力される。

#### 【0157】

一方、ゲート信号線駆動回路 122 は、それぞれシフトレジスタ、バッファ (いずれも図示せず) を有している。また場合によっては、ゲート信号線駆動回路 122 が、シフトレジスタ、バッファの他にレベルシフトを有していても良い。

#### 【0158】

50

ゲート信号線駆動回路 122において、シフトレジスタ（図示せず）からのゲート信号がバッファ（図示せず）に供給され、対応するゲート信号線に供給される。ゲート信号線（G1～Gy）には、それぞれ1ライン分の画素のスイッチング用TFT105のゲート電極が接続されており、1ライン分全ての画素のスイッチング用TFT105を同時にオンの状態にしなくてはならないので、バッファは大きな電流を流すことが可能なものが用いられる。

#### 【0159】

なおソース信号線駆動回路とゲート信号線駆動回路の数、構成及びその動作は、本実施例で示した構成に限定されない。本発明のエリアセンサは、公知のソース信号線駆動回路及びゲート信号線駆動回路を用いることが可能である。

10

#### 【0160】

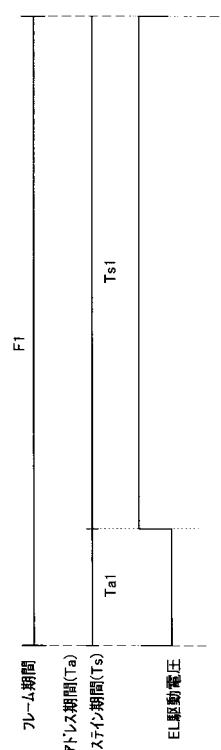

次に、センサ部のスイッチング用TFT105及びEL駆動用TFT106を、デジタル方式で駆動させた場合のタイミングチャートを図13に示す。

#### 【0161】

センサ部101の全ての画素が一通り発光するまでの期間を1フレーム期間（F）と呼ぶ。フレーム期間はアドレス期間Taとサステイン期間Tsとに分けられる。アドレス期間とは、1フレーム期間中、全ての画素にデジタル信号を入力する期間である。サステイン期間（点灯期間とも呼ぶ）とは、アドレス期間において画素に入力されたデジタル信号によって、EL素子を発光又は非発光の状態にし、表示を行う期間を示している。

#### 【0162】

電源供給線（V1～Vx）の電位は所定の電位（電源電位）に保たれている。

20

#### 【0163】

まずアドレス期間Taにおいて、EL素子106の対向電極の電位は、電源電位と同じ高さに保たれている。

#### 【0164】

そしてゲート信号線G1に入力されるゲート信号によって、ゲート信号線G1に接続されている全てのスイッチング用TFT105がオンの状態になる。次に、ソース信号線駆動回路120からソース信号線（S1～Sx）にデジタル信号が入力される。ソース信号線（S1～Sx）に入力されたデジタル信号は、オンの状態のスイッチング用TFT105を介してEL駆動用TFT106のゲート電極に入力される。

30

#### 【0165】

次にゲート信号線G2に入力されるゲート信号によって、ゲート信号線G2に接続されている全てのスイッチング用TFT105がオンの状態になる。次に、ソース信号線駆動回路120からソース信号線（S1～Sx）にデジタル信号が入力される。ソース信号線（S1～Sx）に入力されたデジタル信号は、オンの状態のスイッチング用TFT105を介してEL駆動用TFT106のゲート電極に入力される。

#### 【0166】

上述した動作をゲート信号線Gyまで繰り返し、全ての画素102のEL駆動用TFT106のゲート電極にデジタル信号が入力され、アドレス期間が終了する。

#### 【0167】

40

アドレス期間Taが終了すると同時にサステイン期間となる。サステイン期間において、全てのスイッチング用TFT105は、オフの状態となる。

#### 【0168】

そしてサステイン期間が開始されると同時に、全てのEL素子の対向電極の電位は、電源電位が画素電極に与えられたときにEL素子が発光する程度に、電源電位との間に電位差を有する高さになる。なお本明細書において、画素電極と対向電極の電位差をEL駆動電圧と呼ぶ。また各画素が有するEL駆動用TFT106のゲート電極に入力されたデジタル信号によってEL駆動用TFT106はオンの状態になっている。よって電源電位がEL素子の画素電極に与えられ、全ての画素が有するEL素子は発光する。

#### 【0169】

50

サステイン期間が終了すると同時に、1つのフレーム期間が終了する。本発明では、全てのサンプリング期間 S T 1 ~ S T y において画素が発光する必要があり、よって本実施例の駆動方法の場合、サステイン期間内にセンサフレーム期間 S F が含まれていることが重要である。

#### 【 0 1 7 0 】

なお本実施例では、単色の画像を読み込むエリアセンサの駆動方法について説明したが、カラー画像を読み込む場合も同様である。ただしカラー画像を読み込むエリアセンサの場合、1つのフレーム期間を R G B に対応した3つのサブフレーム期間に分割し、各サブフレーム期間においてアドレス期間とサステイン期間とを設ける。そして R 用のサブフレーム期間のアドレス期間では、R に対応する画素の E L 素子だけ発光するようなデジタル信号を全ての画素に入力し、サステイン期間において R の E L 素子だけ発光を行う。G 用、B 用のサブフレーム期間においても同様に、各サステイン期間において、各色に対応する画素の E L 素子のみが発光を行うようとする。

10

#### 【 0 1 7 1 】

そしてカラー画像を読み込むエリアセンサの場合、R G B に対応した3つのサブフレーム期間の各サステイン期間は、R 用、G 用、B 用センサフレーム期間 ( S F r 、 S F g 、 S F b ) をそれぞれ含んでいることが重要である。

#### 【 0 1 7 2 】

なお本実施例は、実施の形態 1 ~ 5 、及び実施例 1 と自由に組み合わせることが可能である。

20

#### 【 0 1 7 3 】

##### ( 実施例 3 )

本実施例では、センサ部 1 0 1 において画像を表示するときの、スイッチング用 T F T 1 0 5 及び E L 駆動用 T F T 1 0 6 ( E L 素子部 1 0 3 ) の駆動方法について説明する。なおセンサ部 1 0 1 の構成は実施例 1 で示した構成と同じであるので、図 1 及び図 2 を参照すればよい。

#### 【 0 1 7 4 】

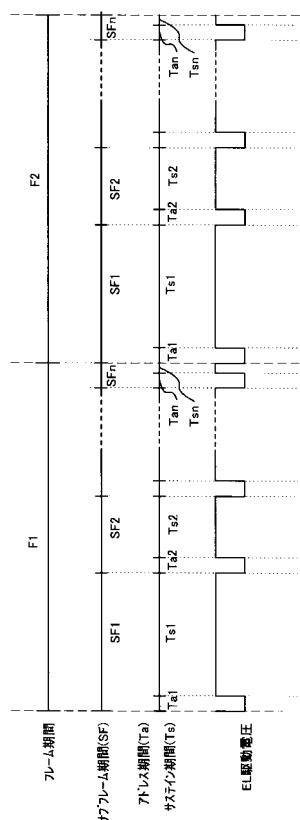

図 1 4 に、本発明のエリアセンサにおいて、デジタル方式でセンサ部 1 0 1 に画像を表示するときのタイミングチャートを示す。

#### 【 0 1 7 5 】

30

まず、1フレーム期間 ( F ) を n 個のサブフレーム期間 ( S F 1 ~ S F n ) に分割する。階調数が多くなるにつれて1フレーム期間におけるサブフレーム期間の数も増える。なおエリアセンサのセンサ部が画像を表示する場合、1フレーム期間 ( F ) とは、センサ部 1 0 1 の全ての画素が1つの画像を表示する期間を指す。

#### 【 0 1 7 6 】

本実施例の場合、フレーム期間は1秒間に 6 0 以上設けることが好ましい。1秒間に表示される画像の数を 6 0 以上にすることで、視覚的にフリッカ等の画像のちらつきを抑えることが可能になる。

#### 【 0 1 7 7 】

サブフレーム期間はアドレス期間 ( T a ) とサステイン期間 ( T s ) とに分けられる。アドレス期間とは、1サブフレーム期間中、全ての画素にデジタルビデオ信号を入力する期間である。なおデジタルビデオ信号とは、画像情報を有するデジタルの信号である。サステイン期間 ( 点灯期間とも呼ぶ ) とは、アドレス期間において画素に入力されたデジタルビデオ信号によって、E L 素子を発光又は非発光の状態にし、表示を行う期間を示している。なおデジタルビデオ信号とは、画像情報を有するデジタル信号を意味する。

40

#### 【 0 1 7 8 】

S F 1 ~ S F n が有するアドレス期間 ( T a ) をそれぞれ T a 1 ~ T a n とする。S F 1 ~ S F n が有するサステイン期間 ( T s ) をそれぞれ T s 1 ~ T s n とする。

#### 【 0 1 7 9 】

電源供給線 ( V 1 ~ V x ) の電位は所定の電位 ( 電源電位 ) に保たれている。

50

**【0180】**

まずアドレス期間 T<sub>a</sub>において、E<sub>L</sub>素子 106 対向電極の電位は、電源電位と同じ高さに保たれている。

**【0181】**

次にゲート信号線 G<sub>1</sub>に入力されるゲート信号によって、ゲート信号線 G<sub>1</sub>に接続されている全てのスイッチング用 TFT105 がオンの状態になる。次に、ソース信号線駆動回路 102 からソース信号線 (S<sub>1</sub> ~ S<sub>x</sub>) にデジタルビデオ信号が入力される。デジタルビデオ信号は「0」または「1」の情報を有しており、「0」と「1」のデジタルビデオ信号は、一方が H<sub>i</sub>、他方が L<sub>o</sub> の電圧を有する信号である。

**【0182】**

そしてソース信号線 (S<sub>1</sub> ~ S<sub>x</sub>) に入力されたデジタルビデオ信号は、オンの状態のスイッチング用 TFT105 を介して、E<sub>L</sub>駆動用 TFT106 のゲート電極に入力される。

**【0183】**

次にゲート信号線 G<sub>1</sub>に接続されている全てのスイッチング用 TFT105 がオフの状態になり、ゲート信号線 G<sub>2</sub>に入力されるゲート信号によって、ゲート信号線 G<sub>2</sub>に接続されている全てのスイッチング用 TFT105 がオンの状態になる。次に、ソース信号線駆動回路 102 からソース信号線 (S<sub>1</sub> ~ S<sub>x</sub>) にデジタルビデオ信号が入力される。ソース信号線 (S<sub>1</sub> ~ S<sub>x</sub>) に入力されたデジタルビデオ信号は、オンの状態のスイッチング用 TFT105 を介して、E<sub>L</sub>駆動用 TFT106 のゲート電極に入力される。

**【0184】**

上述した動作をゲート信号線 G<sub>y</sub>まで繰り返し、全ての画素 102 の E<sub>L</sub>駆動用 TFT106 のゲート電極にデジタルビデオ信号が入力され、アドレス期間が終了する。

**【0185】**

アドレス期間 T<sub>a</sub>が終了すると同時にサステイン期間 T<sub>s</sub>となる。サステイン期間において、全てのスイッチング用 TFT105 はオフの状態になる。サステイン期間において、全ての E<sub>L</sub>素子の対向電極の電位は、電源電位が画素電極に与えられたときに E<sub>L</sub>素子が発光する程度に、電源電位との間に電位差を有する高さになる。

**【0186】**

本実施例では、デジタルビデオ信号が「0」の情報を有していた場合、E<sub>L</sub>駆動用 TFT106 はオフの状態になる。よって E<sub>L</sub>素子の画素電極は対向電極の電位に保たれたままである。その結果、「0」の情報を有するデジタルビデオ信号が入力された画素において、E<sub>L</sub>素子 106 は発光しない。

**【0187】**

逆にデジタルビデオ信号が「1」の情報を有していた場合、E<sub>L</sub>駆動用 TFT106 はオンの状態になる。よって電源電位が E<sub>L</sub>素子 106 の画素電極に与えられる。その結果、「1」の情報を有するデジタルビデオ信号が入力された画素が有する E<sub>L</sub>素子 106 は発光する。

**【0188】**

このように、画素に入力されるデジタルビデオ信号の有する情報によって、E<sub>L</sub>素子が発光または非発光の状態になり、画素は表示を行う。

**【0189】**

サステイン期間が終了すると同時に、1つのサブフレーム期間が終了する。そして次のサブフレーム期間が出現し、再びアドレス期間に入り、全画素にデジタルビデオ信号を入力したら、再びサステイン期間に入る。なお、サブフレーム期間 S<sub>F1</sub> ~ S<sub>Fn</sub> の出現する順序は任意である。

**【0190】**

以下、残りのサブフレーム期間においても同様の動作を繰り返し、表示を行う。n 個のサブフレーム期間が全て終了したら、1つの画像が表示され、1フレーム期間が終了する。1フレーム期間が終了すると次のフレーム期間のサブフレーム期間が出現し、上述した動

10

20

30

40

50

作を繰り返す。

**【0191】**

本発明において、 $n$  個のサブフレーム期間がそれぞれ有するアドレス期間 ( $T_{a1} \sim T_{an}$ ) の長さは全て同じである。また  $n$  個のサステイン期間  $T_{s1}, \dots, T_{sn}$  の長さの比は、 $T_{s1} : T_{s2} : T_{s3} : \dots : T_{s(n-1)} : T_{sn} = 2^0 : 2^{-1} : 2^{-2} : \dots : 2^{-(n-2)} : 2^{-(n-1)}$  で表される。

**【0192】**

各画素の階調は、1フレーム期間においてどのサブフレーム期間を発光させるかによって決まる。例えば、 $n = 8$  のとき、全部のサステイン期間で発光した場合の画素の輝度を 100% とすると、 $T_{s1}$  と  $T_{s2}$  において画素が発光した場合には 75% の輝度が表現でき、 $T_{s3}$  と  $T_{s5}$  と  $T_{s8}$  を選択した場合には 16% の輝度が表現できる。

**【0193】**

なお本実施例は、実施の形態 1 ~ 5、実施例 1、2 と自由に組み合わせることが可能である。

**【0194】**

(実施例 4)

実施例 1 及び 2 では、アドレス期間において対向電極の電位を電源電位と同じ電位に保っていたため、EL 素子は発光しなかった。しかし本発明はこの構成に限定されない。画素電極に電源電位が与えられたときに EL 素子が発光する程度の電位差を、対向電位と電源電位との間に常に設け、アドレス期間においても表示期間と同様に表示を行うようにしても良い。

**【0195】**

ただし EL 素子をエリアセンサの光源として用いる実施例 1 と本実施例を組み合わせる場合、単色の画像を読み込むエリアセンサでは、フレーム期間内にセンサフレーム期間 SF が含まれていることが重要である。またカラー画像を読み込むエリアセンサでは、RGB に対応した 3 つのサブフレーム期間が、それぞれ R 用、G 用、B 用のセンサフレーム期間に含まれていることが重要である。

**【0196】**

またセンサ部に画像を表示する実施例 2 と本実施例を組み合わせる場合、サブフレーム期間全体が実際に表示を行う期間となるので、サブフレーム期間の長さを、 $SF1 : SF2 : SF3 : \dots : SF(n-1) : SFn = 2^0 : 2^{-1} : 2^{-2} : \dots : 2^{-(n-2)} : 2^{-(n-1)}$  となるように設定する。上記構成により、アドレス期間を発光させない駆動方法に比べて、高い輝度の画像が得られる。

**【0197】**

なお本実施例は、実施の形態 1 ~ 5、実施例 1 ~ 3 と自由に組み合わせることが可能である。

**【0198】**

(実施例 5)

本実施例では、図 2 に示す EL 素子 107 の動作を制御している、スイッチング用 TFT 105 及び EL 駆動用 TFT 106 の駆動方法の、実施例 1 とは異なる例について説明する。なおセンサ部の構成は実施例 1 で示した構成と同じであるので、図 1 及び図 2 を参照すればよい。

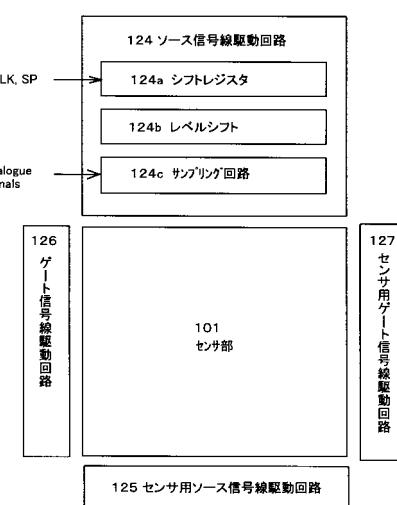

**【0199】**

図 15 に本実施例のエリアセンサの上面図を示す。130 はソース信号線駆動回路、126 はゲート信号線駆動回路であり、共にスイッチング用 TFT 105 及び EL 駆動用 TFT 106 の駆動を制御している。また 125 はセンサ用ソース信号線駆動回路、127 はセンサ用ゲート信号線駆動回路であり、共にリセット用 TFT 110、バッファ用 TFT 111 及び選択用 TFT 112 の駆動を制御している。本実施例ではソース信号線駆動回路とゲート信号線駆動回路とを 1 つずつ設けたが、本発明はこの構成に限定されない。ソース信号線駆動回路を 2 つ設けても良い。また、ゲート信号線駆動回路を 2 つ設けても良

10

20

30

40

50

い。

#### 【0200】

なお本明細書において、ソース信号線駆動回路130、ゲート信号線駆動回路126、センサ用ソース信号線駆動回路125、センサ用ゲート信号線駆動回路127を駆動部と呼ぶ。

#### 【0201】

ソース信号線駆動回路130は、シフトレジスタ130a、レベルシフト130b、サンプリング回路130cを有している。なおレベルシフトは必要に応じて用いればよく、必ずしも用いなくとも良い。また本実施例においてレベルシフトはシフトレジスタ130aとサンプリング回路130cとの間に設ける構成としたが、本発明はこの構成に限定されない。またシフトレジスタ130aの中にレベルシフト130bが組み込まれている構成にしても良い。10

#### 【0202】

クロック信号(CLK)、スタートパルス信号(SP)がシフトレジスタ130aに入力される。シフトレジスタ130aからアナログの信号(アナログ信号)をサンプリングするためのサンプリング信号が出力される。出力されたサンプリング信号はレベルシフト130bに入力され、その電位の振幅が大きくなって出力される。

#### 【0203】

レベルシフト130bから出力されたサンプリング信号は、サンプリング回路130cに入力される。そしてサンプリング回路130cに入力されるアナログ信号がサンプリング信号によってそれぞれサンプリングされ、ソース信号線S1～Sxに入力される。20

#### 【0204】

一方、ゲート信号線駆動回路126は、それぞれシフトレジスタ、バッファ(いずれも図示せず)を有している。また場合によっては、ゲート信号線駆動回路126が、シフトレジスタ、バッファの他にレベルシフトを有していても良い。

#### 【0205】

ゲート信号線駆動回路126において、シフトレジスタ(図示せず)からのゲート信号がバッファ(図示せず)に供給され、対応するゲート信号線に供給される。ゲート信号線G1～Gyには、それぞれ1ライン分の画素のスイッチング用TFT105のゲート電極が接続されており、1ライン分全ての画素のスイッチング用TFT105を同時にオンの状態にしなくてはならないので、バッファは大きな電流を流すことが可能なものが用いられる。30

#### 【0206】

なおソース信号線駆動回路とゲート信号線駆動回路の数、構成及びその動作は、本実施例で示した構成に限定されない。本発明のエリアセンサは、公知のソース信号線駆動回路及びゲート信号線駆動回路を用いることが可能である。

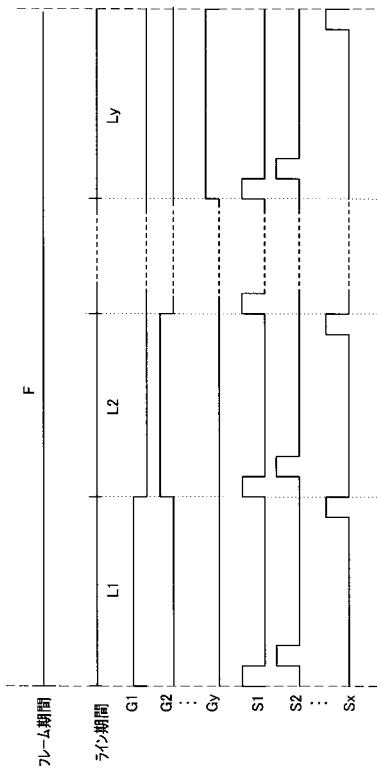

#### 【0207】

次に、センサ部のスイッチング用TFT105及びEL駆動用TFT106を、アナログ方式で駆動させた場合のタイミングチャートを図16に示す。センサ部101の全ての画素が一通り発光するまでの期間を1フレーム期間Fと呼ぶ。1ライン期間Lは、1つのゲート信号線が選択されてから、その後に別のゲート信号線が選択されるまでの期間を意味する。図2に示したエリアセンサの場合、ゲート信号線はy本があるので、1フレーム期間中にy個のライン期間L1～Lyが設けられている。40

#### 【0208】

解像度が高くなるにつれて1フレーム期間中のライン期間の数も増え、駆動回路を高い周波数で駆動しなければならなくなる。

#### 【0209】

まず電源電圧線V1～Vxは一定の電源電位に保たれている。そしてEL素子106の対向電極の電位である対向電位も一定の電位に保たれている。電源電位は、電源電位がEL素子106の画素電極に与えられるとEL素子106が発光する程度に、対向電位との間50

に電位差を有している。

**【0210】**

第1のライン期間 L 1において、ゲート信号線駆動回路 126 からゲート信号線 G 1に入力されるのゲート信号によって、ゲート信号線 G 1に接続された全てのスイッチング用 TFT105 はオンの状態になる。そして、ソース信号線 S 1 ~ S x に順にソース信号線駆動回路 130 からアナログ信号が入力される。ソース信号線 S 1 ~ S x に入力されたアナログ信号は、スイッチング用 TFT105 を介して EL 駆動用 TFT106 のゲート電極に入力される。

**【0211】**

EL 駆動用 TFT106 のチャネル形成領域を流れる電流の大きさは、そのゲート電極に入力される信号の電位の高さ（電圧）によって制御される。よって、EL 素子 106 の画素電極に与えられる電位は、EL 駆動用 TFT106 のゲート電極に入力されたアナログ信号の電位の高さによって決まる。そして EL 素子 105 はアナログ信号の電位に制御されて発光を行う。なお本実施例の場合、全ての画素に入力されるアナログ信号は、同じ高さの電位に保たれている。

10

**【0212】**

ソース信号線 S 1 ~ S x へのアナログ信号の入力が終了すると、第1のライン期間 L 1 が終了する。なお、ソース信号線 S 1 ~ S x へのアナログ信号の入力が終了するまでの期間と水平帰線期間とを合わせて1つのライン期間としても良い。そして次に第2のライン期間 L 2 となり、ゲート信号線 G 1 に接続された全てのスイッチング用 TFT105 はオフの状態になり、ゲート信号線 G 2 に入力されるゲート信号によって、ゲート信号線 G 2 に接続された全てのスイッチング用 TFT105 はオンの状態になる。そして第1のライン期間 L 1 と同様に、ソース信号線 S 1 ~ S x に順にアナログ信号が入力される。

20

**【0213】**

そして上述した動作をゲート信号線 G y まで繰り返し、全てのライン期間 L 1 ~ L y が終了する。全てのライン期間 L 1 ~ L y が終了すると、1フレーム期間が終了する。1フレーム期間が終了することで、全ての画素が有する EL 素子は発光を行う。なお全てのライン期間 L 1 ~ L y と垂直帰線期間とを合わせて1フレーム期間としても良い。

**【0214】**

なお本実施例では、単色の画像を読み込むエリアセンサの駆動方法について説明したが、カラー画像を読み込む場合も同様である。ただしカラー画像を読み込むエリアセンサの場合、1つのフレーム期間を RGB に対応した3つのサブフレーム期間に分割する。そして R 用のサブフレーム期間では、R に対応する画素の EL 素子だけ発光するようなアナログ信号を全ての画素に入力し、R の EL 素子だけ発光を行う。G 用、B 用のサブフレーム期間においても同様に、各色に対応する画素の EL 素子のみが発光を行うようにする。

30

**【0215】**

そしてカラー画像を読み込むエリアセンサの場合、RGB に対応した3つのサブフレーム期間の各サステイン期間は、R 用、G 用、B 用センサフレーム期間 (SFr, SFg, SFb) を含んでいることが重要である。

**【0216】**

40

なお本実施例の駆動方法において、センサ部 101 に画像を表示させる場合は、アナログ信号の代わりに画像情報を有するアナログのビデオ信号（アナログビデオ信号）を入力すると、センサ部 101 に画像を表示することが可能である。

**【0217】**

なお本実施例は、実施の形態 1 ~ 5、実施例 1 ~ 4 と自由に組み合わせることが可能である。

**【0218】**

(実施例 6)

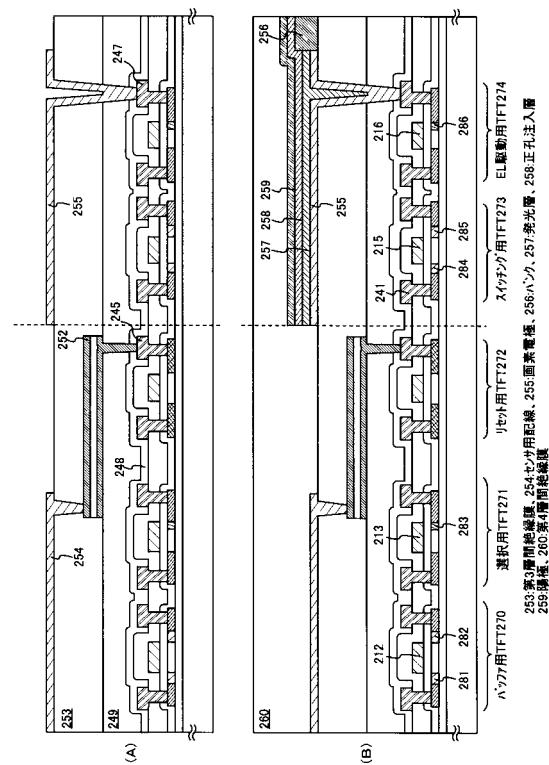

本実施例では、本発明のエリアセンサのセンサ部における断面図について説明する。

**【0219】**

50

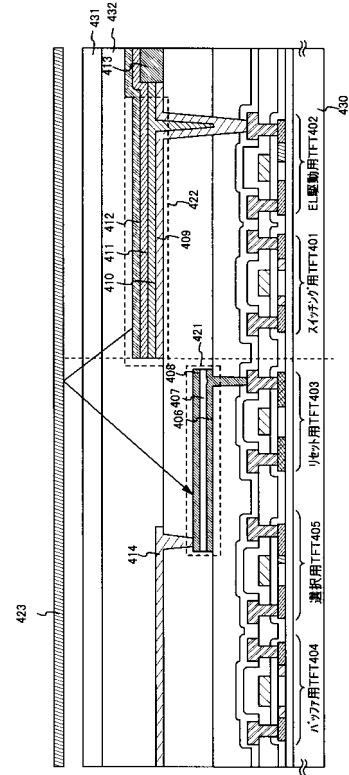

図17に本実施例のエリアセンサの断面図を示す。401はスイッチング用TFT、402はEL駆動用TFT、403はリセット用TFT、404はバッファ用TFT、405は選択用TFTである。

#### 【0220】

また、406はカソード電極、407は光電変換層、408はアノード電極である。カソード電極406と、光電変換層407と、アノード電極408とによって、フォトダイオード421が形成される。414はセンサ用配線であり、アノード電極408と外部の電源とを接続している。

#### 【0221】

また409は画素電極（陰極）、410は発光層、411は正孔注入層、412は対向電極（陽極）である。画素電極（陰極）409と、発光層410と、正孔注入層411と、対向電極（陽極）412とでEL素子422が形成される。なお413はバンクであり、隣り合う画素同士の発光層410を区切っている。

#### 【0222】

432は層間絶縁膜であり、431は光ファイバプレート、またはガラスファイバプレートである。423は被写体であり、EL素子422から発せられた光は、被写体423において反射し、フォトダイオード421に照射される。本実施例では、被写体423を基板430のTFTが形成されている側に設ける。

#### 【0223】

本実施例においては、スイッチング用TFT401、EL駆動用TFT402、バッファ用TFT404、選択用TFT405は全てNチャネル型TFTである。またリセット用TFT403はPチャネル型TFTである。なお本発明はこの構成に限定されない。よってスイッチング用TFT401、EL駆動用TFT402、バッファ用TFT404、選択用TFT405、リセット用TFT403は、Nチャネル型TFTとPチャネル型TFTのどちらでも良い。

#### 【0224】

ただし本実施例のように、EL駆動用TFT402のソース領域またはドレイン領域がEL素子の陰極と電気的に接続されている場合、EL駆動用TFT402はNチャネル型TFTであることが望ましい。また逆に、EL駆動用TFT402のソース領域またはドレイン領域がEL素子の陽極と電気的に接続されている場合、EL駆動用TFT402はPチャネル型TFTであることが望ましい。

#### 【0225】

また、本実施例のように、リセット用TFT403のドレイン領域がフォトダイオード421のカソード電極406とが電気的に接続されている場合、リセット用TFT403はPチャネル型TFT、バッファ用TFT404はNチャネル型TFTであることが望ましい。逆にリセット用TFT403のドレイン領域がフォトダイオード421のアノード電極408と電気的に接続され、センサ用配線414がカソード電極406と接続されている場合、リセット用TFT403はNチャネル型TFT、バッファ用TFT404はPチャネル型TFTであることが望ましい。

#### 【0226】

なお本実施例は、実施の形態1～5、実施例1～実施例5と自由に組み合わせることが可能である。

#### 【0227】

##### (実施例7)

本実施例では、本発明のエリアセンサのセンサ部における断面図の実施例6とは異なる例について説明する。

#### 【0228】

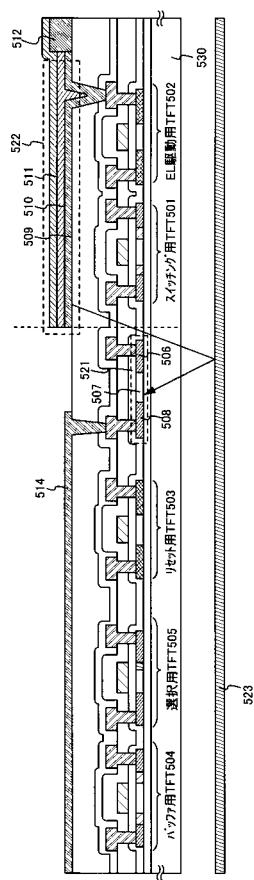

図18に本実施例のエリアセンサの断面図を示す。501はスイッチング用TFT、502はEL駆動用TFT、503はリセット用TFT、504はバッファ用TFT、505は選択用TFTである。

10

20

30

40

50

**【0229】**

また、506はカソード電極、507は光電変換層、508はアノード電極である。カソード電極506と、光電変換層507と、アノード電極508とによって、フォトダイオード521が形成される。514はセンサ用配線であり、アノード電極508と外部の電源とを電気的に接続している。また、フォトダイオード521のカソード電極506とリセット用TFT503のドレイン領域とは電気的に接続されている。

**【0230】**

また509は画素電極（陽極）、510はEL層、511は対向電極（陰極）である。画素電極（陽極）509と、EL層510と、対向電極（陰極）511とでEL素子522が形成される。なお512はバンクであり、隣り合う画素同士のEL層510を区切っている。

10

**【0231】**

523は被写体であり、EL素子522から発せられた光が被写体523上で反射し、フォトダイオード521に照射される。本実施例では、実施例6と異なり、被写体を基板530のTFTが形成されていない側に設ける。

**【0232】**

本実施例では、基板530として、光ファイバプレート、またはガラスファイバプレートを用いることが好ましい。また実施例10にあるように、基板をガラス基板、石英基板、シリコン基板、金属基板（SUS基板）もしくはセラミック基板とし、センサ部を形成してから、光ファイバプレートを基板上に接着することもできる。

20

**【0233】**

本実施例において、スイッチング用TFT501、バッファ用TFT504、選択用TFT505は全てNチャネル型TFTである。またEL駆動用TFT502、リセット用TFT503はPチャネル型TFTである。なお本発明はこの構成に限定されない。よってスイッチング用TFT501、EL駆動用TFT502、バッファ用TFT504、選択用TFT505、リセット用TFT503は、Pチャネル型TFTとPチャネル型TFTのどちらでも良い。

**【0234】**

ただし本実施例のように、EL駆動用TFT502のソース領域またはドレイン領域がEL素子522の陽極509と電気的に接続されている場合、EL駆動用TFT502はPチャネル型TFTであることが望ましい。また逆に、EL駆動用TFT502のソース領域またはドレイン領域がEL素子522の陰極と電気的に接続されている場合、EL駆動用TFT502はNチャネル型TFTであることが望ましい。

30

**【0235】**

また、本実施例のように、リセット用TFT503のドレイン領域がフォトダイオード521のカソード電極506と電気的に接続されている場合、リセット用TFT503はPチャネル型TFT、バッファ用TFT504はNチャネル型TFTであることが望ましい。逆にリセット用TFT503のドレイン領域がフォトダイオード521のアノード電極508と電気的に接続され、センサ用配線514がカソード電極506と電気的に接続されている場合、リセット用TFT503はNチャネル型TFT、バッファ用TFT504はPチャネル型TFTであることが望ましい。

40

**【0236】**

なお本実施例のフォトダイオードは他のTFTと同時に形成することができるので、工程数を抑えることができる。

**【0237】**

なお本実施例は、実施の形態1～5、実施例1～実施例6と自由に組み合わせることが可能である。

**【0238】****(実施例8)**

本実施例では、本発明のエリアセンサのセンサ部における断面図の実施例6、7とは異な

50

る例について説明する。

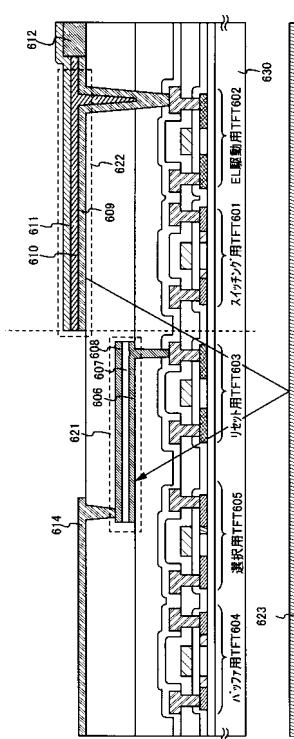

**【0239】**

図19に本実施例のエリアセンサの断面図を示す。601はスイッチング用TFT、602はEL駆動用TFT、603はリセット用TFT、604はバッファ用TFT、605は選択用TFTである。

**【0240】**

また、606はカソード電極、607は光電変換層、608はアノード電極である。カソード電極606と、光電変換層607と、アノード電極608とによって、フォトダイオード621が形成される。614はセンサ用配線であり、アノード電極608と外部の電源とを接続している。また、フォトダイオード621のカソード電極606とリセット用TFT603のドレイン領域とは電気的に接続されている

10

**【0241】**

また609は画素電極（陽極）、610はEL層、611は対向電極（陰極）である。画素電極（陽極）609と、EL層610と、対向電極（陰極）611とでEL素子622が形成される。なお612はバンクであり、隣り合う画素同士のEL層610を区切っている。

**【0242】**

623は被写体であり、EL素子622から発せられた光が被写体623上で反射し、フォトダイオード621に照射される。本実施例では、被写体623を基板630のTFTが形成されていない側に設ける。

20

**【0243】**

本実施例では、基板630として、光ファイバプレート、またはガラスファイバプレートを用いることが好ましい。また実施例10にあるように、基板をガラス基板、石英基板、シリコン基板、金属基板（SUS基板）もしくはセラミックス基板とし、センサ部を形成してから、光ファイバプレートを基板上に接着することもできる。

**【0244】**

本実施例において、スイッチング用TFT601、バッファ用TFT604、選択用TFT605は全てNチャネル型TFTである。またEL駆動用TFT602、リセット用TFT603はPチャネル型TFTである。なお本発明はこの構成に限定されない。よってスイッチング用TFT601、EL駆動用TFT602、バッファ用TFT604、選択用TFT605、リセット用TFT603は、Nチャネル型TFTとPチャネル型TFTのどちらでも良い。

30

**【0245】**

ただし本実施例のように、EL駆動用TFT602のソース領域またはドレイン領域がEL素子の陽極と電気的に接続されている場合、EL駆動用TFT602はPチャネル型TFTであることが望ましい。また逆に、EL駆動用TFT602のソース領域またはドレイン領域がEL素子の陰極と電気的に接続されている場合、EL駆動用TFT602はNチャネル型TFTであることが望ましい。

**【0246】**

また、本実施例のように、リセット用TFT603のドレイン領域がフォトダイオード621のカソード電極606と電気的に接続されている場合、リセット用TFT603はPチャネル型TFT、バッファ用TFT604はNチャネル型TFTであることが望ましい。逆にリセット用TFT603のドレイン領域がフォトダイオード621のアノード電極608と電気的に接続されていて、センサ用配線614がカソード電極606と接続されている場合、リセット用TFT603はNチャネル型TFT、バッファ用TFT604はPチャネル型TFTであることが望ましい。

40

**【0247】**

なお本実施例は、実施の形態1～5、実施例1～実施例7と自由に組み合わせることが可能である。

**【0248】**

10

20

30

40

50

(実施例 9 )

本実施例では、本発明のエリアセンサのセンサ部における断面図の実施例 6 ~ 8 とは異なる例について説明する。

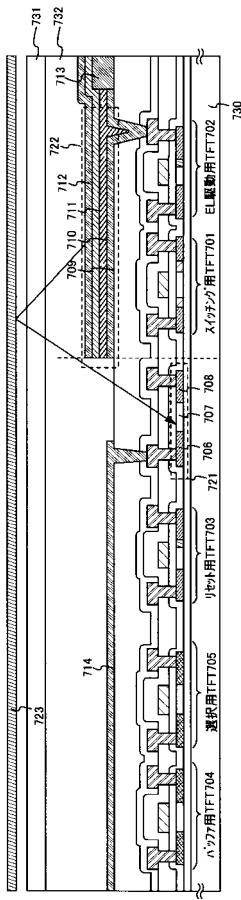

【 0 2 4 9 】

図 19 に本実施例のエリアセンサの断面図を示す。701 はスイッチング用 TFT、702 は EL 駆動用 TFT、703 はリセット用 TFT、704 はバッファ用 TFT、705 は選択用 TFT である。

【 0 2 5 0 】

また、706 はカソード電極、707 は光電変換層、708 はアノード電極である。カソード電極 706 と、光電変換層 707 と、アノード電極 708 とによって、フォトダイオード 721 が形成される。714 はセンサ用配線であり、カソード電極 706 と外部の電源とを接続している。また、フォトダイオード 721 のアノード電極 708 とリセット用 TFT 703 のドレイン領域とは電気的に接続されている

【 0 2 5 1 】

また 709 は画素電極（陰極）、710 は発光層、711 は正孔注入層、712 は対向電極（陽極）である。画素電極（陰極）709 と、発光層 710 と、正孔注入層 711 と、対向電極（陽極）712 とで EL 素子 722 が形成される。なお 713 はバンクであり、隣り合う画素同士の発光層 710 を区切っている。

【 0 2 5 2 】

732 は層間絶縁膜であり、731 は光ファイバプレート、またはガラスファイバプレートである。723 は被写体であり、EL 素子 722 から発せられた光は、被写体 723 上で反射し、フォトダイオード 721 に照射される。本実施例では、被写体 723 を基板 730 の TFT が形成されている側に設ける。

【 0 2 5 3 】

本実施例において、スイッチング用 TFT 701、EL 駆動用 TFT 702、リセット用 TFT 703 は全て N チャネル型 TFT である。またバッファ用 TFT 704、選択用 TFT 705 は P チャネル型 TFT である。なお本発明はこの構成に限定されない。よってスイッチング用 TFT 701、EL 駆動用 TFT 702、バッファ用 TFT 704、選択用 TFT 705、リセット用 TFT 703 は、N チャネル型 TFT と P チャネル型 TFT のどちらでも良い。

【 0 2 5 4 】

ただし本実施例のように、EL 駆動用 TFT 702 のソース領域またはドレイン領域が EL 素子 722 の陰極 709 と電気的に接続されている場合、EL 駆動用 TFT 702 は N チャネル型 TFT であることが望ましい。また逆に、EL 駆動用 TFT 702 のソース領域またはドレイン領域が EL 素子 722 の陽極 712 と電気的に接続されている場合、EL 駆動用 TFT 702 は P チャネル型 TFT であることが望ましい。

【 0 2 5 5 】

また、本実施例のように、リセット用 TFT 703 のドレイン領域がフォトダイオード 721 のアノード電極 708 と電気的に接続されている場合、リセット用 TFT 703 は N チャネル型 TFT、バッファ用 TFT 704 は P チャネル型 TFT であることが望ましい。逆にリセット用 TFT 703 のドレイン領域がフォトダイオード 721 のカソード電極 706 と接続され、センサ用配線 714 がアノード電極 708 と接続されている場合、リセット用 TFT 703 は P チャネル型 TFT、バッファ用 TFT 704 は N チャネル型 TFT であることが望ましい。

【 0 2 5 6 】

なお本実施例のフォトダイオード 721 は他の TFT と同時に形成することができるので、工程数を抑えることができる。

【 0 2 5 7 】

なお本実施例は、実施の形態 1 ~ 5、実施例 1 ~ 実施例 8 と自由に組み合わせることが可能である。

10

20

30

40

50

## 【0258】

(実施例10)

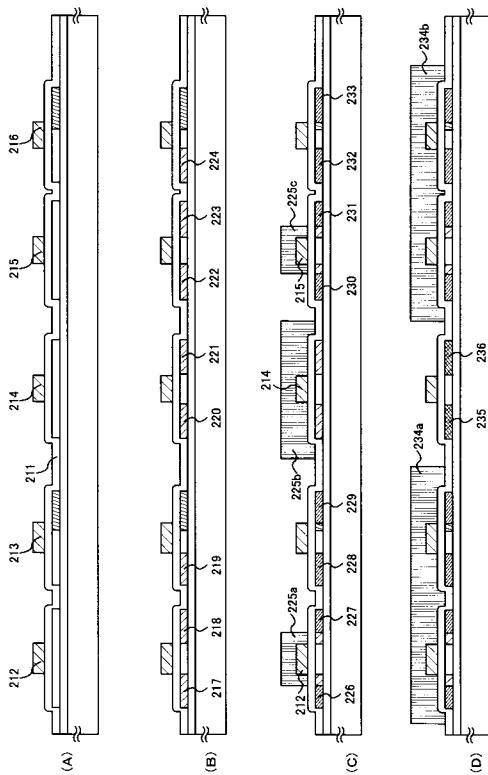

本実施例では、本発明のエリアセンサのセンサ部の作製方法について、図21～図24を用いて説明する。

## 【0259】

まず、図21(A)に示すように、ガラス基板200上に下地膜201を300nmの厚さに形成する。本実施例では下地膜201として窒化酸化珪素膜を積層して用いる。この時、ガラス基板200に接する方の窒素濃度を10～25wt%としておくと良い。また、下地膜201に放熱効果を持たせることは有効であり、 DLC(ダイヤモンドライクカーボン)膜を設けても良い。

10

## 【0260】

次に下地膜201の上に50nmの厚さの非晶質珪素膜(図示せず)を公知の成膜法で形成する。なお、非晶質珪素膜に限定する必要はなく、非晶質構造を含む半導体膜(微結晶半導体膜を含む)であれば良い。さらに非晶質シリコンゲルマニウム膜などの非晶質構造を含む化合物半導体膜でも良い。また、膜厚は20～100nmの厚さであれば良い。

## 【0261】

そして、公知の技術により非晶質珪素膜を結晶化し、結晶質珪素膜(多結晶シリコン膜若しくはポリシリコン膜ともいう)202を形成する。公知の結晶化方法としては、電熱炉を使用した熱結晶化方法、レーザー光を用いたレーザーアニール結晶化法、赤外光を用いたランプアニール結晶化法がある。本実施例では、XeClガスを用いたエキシマレーザー光を用いて結晶化する。

20

## 【0262】

なお、本実施例では線状に加工したパルス発振型のエキシマレーザー光を用いるが、矩形であっても良いし、連続発振型のアルゴンレーザー光や連続発振型のエキシマレーザー光を用いることもできる。

## 【0263】

また、本実施例では結晶質珪素膜をTFTの活性層として用いるが、非晶質珪素膜を用いることも可能である。

## 【0264】

なお、オフ電流を低減する必要のあるスイッチング用TFTの活性層を非晶質珪素膜で形成し、EL駆動用TFTの活性層を結晶質珪素膜で形成することは有効である。非晶質珪素膜はキャリア移動度が低いため電流を流しにくくオフ電流が流れにくい。即ち、電流を流しにくい非晶質珪素膜と電流を流しやすい結晶質珪素膜の両者の利点を生かすことができる。

30

## 【0265】

次に、図21(B)に示すように、結晶質珪素膜202上に酸化珪素膜でなる保護膜203を130nmの厚さに形成する。この厚さは100～200nm(好ましくは130～170nm)の範囲で選べば良い。また、珪素を含む絶縁膜であれば他の膜でも良い。この保護膜203は不純物を添加する際に結晶質珪素膜が直接プラズマに曝されないようにするために、微妙な濃度制御を可能にするために設ける。

40

## 【0266】

そして、その上にレジストマスク204a、204b、204cを形成し、保護膜203を介してn型を付与する不純物元素(以下、n型不純物元素という)を添加する。なお、n型不純物元素としては、代表的には周期表の15族に属する元素、典型的にはリン又は砒素を用いることができる。なお、本実施例ではフォスフィン(PH<sub>3</sub>)を質量分離しないでプラズマ励起したプラズマドーピング法を用い、リンを1×10<sup>18</sup>atoms/cm<sup>3</sup>の濃度で添加する。勿論、質量分離を行いうイオンインプランテーション法を用いても良い。

## 【0267】

この工程により形成されるn型不純物領域(b)205a、205bには、n型不純物元素が2×10<sup>16</sup>～5×10<sup>19</sup>atoms/cm<sup>3</sup>(代表的には5×10<sup>17</sup>～5×10<sup>18</sup>atoms/cm<sup>3</sup>)

50

の濃度で含まれるようにドーズ量を調節する。

**【0268】**

次に、図21(C)に示すように、保護膜203、レジストマスク204a、204b、204cを除去し、添加したn型不純物元素の活性化を行う。活性化手段は公知の技術を用いれば良いが、本実施例ではエキシマレーザー光の照射(レーザーアニール)により活性化する。勿論、パルス発振型でも連続発振型でも良いし、エキシマレーザー光に限定する必要はない。但し、添加された不純物元素の活性化が目的であるので、結晶質珪素膜が溶融しない程度のエネルギーで照射することが好ましい。なお、保護膜203をつけたままレーザー光を照射しても良い。

**【0269】**

なお、このレーザー光による不純物元素の活性化に際して、熱処理(ファーネスアニール)による活性化を併用しても構わない。熱処理による活性化を行う場合は、基板の耐熱性を考慮して450～550程度の熱処理を行えば良い。

**【0270】**

この工程によりn型不純物領域(b)205a、205bの端部、即ち、n型不純物領域(b)205a、205bの周囲に存在するn型不純物元素を添加していない領域との境界部(接合部)が明確になる。このことは、後にTFTが完成した時点において、LDD領域とチャネル形成領域とが非常に良好な接合部を形成しうることを意味する。

**【0271】**

次に、図21(D)に示すように、結晶質珪素膜の不要な部分を除去して、島状の半導体膜(以下、活性層という)206～210を形成する。

**【0272】**

次に、図22(A)に示すように、活性層206～210を覆ってゲート絶縁膜211を形成する。ゲート絶縁膜211としては、10～200nm、好ましくは50～150nmの厚さの珪素を含む絶縁膜を用いれば良い。これは単層構造でも積層構造でも良い。本実施例では110nm厚の窒化酸化珪素膜を用いる。

**【0273】**

次に、200～400nm厚の導電膜を形成し、パターニングしてゲート電極212～216を形成する。なお本実施例では、ゲート電極とゲート電極に電気的に接続された引き回しのための配線(以下、ゲート配線という)とを同一材料で形成している。勿論、ゲート電極と、ゲート配線とを別の材料で形成しても良い。具体的にはゲート電極よりも低抵抗な材料をゲート配線として用いても良い。これは、ゲート電極としては微細加工が可能な材料を用い、ゲート配線には微細加工はできなくとも配線抵抗が小さい材料を用いるためである。このような構造とすることでゲート配線の配線抵抗を非常に小さくすることができるため、面積の大きいセンサ部を形成することができる。即ち、画面の大きさが対角10インチ以上(さらには30インチ以上)のセンサ部を有するエリアセンサを実現する上で、上記の画素構造は極めて有効である。

**【0274】**

また、ゲート電極は単層の導電膜で形成しても良いが、必要に応じて二層、三層といった積層膜とすることが好ましい。ゲート電極212～216の材料としては公知のあらゆる導電膜を用いることができる。

**【0275】**

代表的には、アルミニウム(A1)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、クロム(Cr)、シリコン(Si)から選ばれた元素でなる膜、または前記元素の窒化物膜(代表的には窒化タンタル膜、窒化タングステン膜、窒化チタン膜)、または前記元素を組み合わせた合金膜(代表的にはMo-W合金、Mo-Ta合金)、または前記元素のシリサイド膜(代表的にはタングステンシリサイド膜、チタンシリサイド膜)を用いることができる。勿論、単層で用いても積層して用いても良い。

**【0276】**

10

20

30

40

50

本実施例では、30nm厚の窒化タンゲステン(WN)膜と、370nm厚のタンゲステン(W)膜とでなる積層膜を用いる。これはスパッタ法で形成すれば良い。また、スパッタガスとしてXe、Ne等の不活性ガスを添加すると応力による膜はがれを防止することができる。

#### 【0277】

またこの時、ゲート電極213、216はそれぞれn型不純物領域(b)205a、205bの一部とゲート絶縁膜211を介して重なるように形成する。この重なった部分が後にゲート電極と重なったLDD領域となる。

#### 【0278】

次に、図22(B)に示すように、ゲート電極212～216をマスクとして自己整合的にn型不純物元素(本実施例ではリン)を添加する。こうして形成されるn型不純物領域(c)217～224にはn型不純物領域(b)205a、205bの1/2～1/10(代表的には1/3～1/4)の濃度でリンが添加されるように調節する。具体的には、 $1 \times 10^{16} \sim 5 \times 10^{18}$ atoms/cm<sup>3</sup>(典型的には $3 \times 10^{17} \sim 3 \times 10^{18}$ atoms/cm<sup>3</sup>)の濃度が好ましい。

10

#### 【0279】

次に、図22(C)に示すように、ゲート電極212、214、215を覆う形でレジストマスク225a～225cを形成し、n型不純物元素(本実施例ではリン)を添加して高濃度にリンを含むn型不純物領域(a)226～233を形成する。ここでもフォスフイン(PH<sub>3</sub>)を用いたイオンドープ法で行い、この領域のリンの濃度は $1 \times 10^{20} \sim 1 \times 10^{21}$ atoms/cm<sup>3</sup>(代表的には $2 \times 10^{20} \sim 5 \times 10^{21}$ atoms/cm<sup>3</sup>)となるように調節する。

20

#### 【0280】

この工程によってNチャネル型TFTのソース領域若しくはドレイン領域が形成される。そしてNチャネル型TFTでは、図22(B)の工程で形成したn型不純物領域217、218、222、223の一部を残す。この残された領域がLDD領域となる。

#### 【0281】

次に、図22(D)に示すように、レジストマスク225a～225cを除去し、新たにレジストマスク234a、234bを形成する。そして、p型不純物元素(本実施例ではボロン)を添加し、高濃度にボロンを含むp型不純物領域235、236を形成する。ここではジボラン(B<sub>2</sub>H<sub>6</sub>)を用いたイオンドープ法により $3 \times 10^{20} \sim 3 \times 10^{21}$ atoms/cm<sup>3</sup>(代表的には $5 \times 10^{20} \sim 1 \times 10^{21}$ atoms/cm<sup>3</sup>)濃度となるようにボロンを添加する。

30

#### 【0282】

なお、不純物領域235、236には既に $1 \times 10^{20} \sim 1 \times 10^{21}$ atoms/cm<sup>3</sup>の濃度でリンが添加されているが、ここで添加されるボロンはその少なくとも3倍以上の濃度で添加される。そのため、予め形成されていたn型の不純物領域は完全にp型に反転し、p型の不純物領域として機能する。

#### 【0283】

次に、レジストマスク234a、234bを除去した後、それぞれの濃度で添加されたn型またはp型不純物元素を活性化する。活性化手段としては、ファーネスアニール法、レーザーアニール法、またはランプアニール法で行うことができる。本実施例では電熱炉において窒素雰囲気中、550℃、4時間の熱処理を行う。

40

#### 【0284】

このとき雰囲気中の酸素を極力排除することが重要である。なぜならば酸素が少しでも存在していると露呈したゲート電極の表面が酸化され、抵抗の増加を招くからである。従って、上記活性化工程における処理雰囲気中の酸素濃度は1ppm以下、好ましくは0.1ppm以下とすることが望ましい。

#### 【0285】

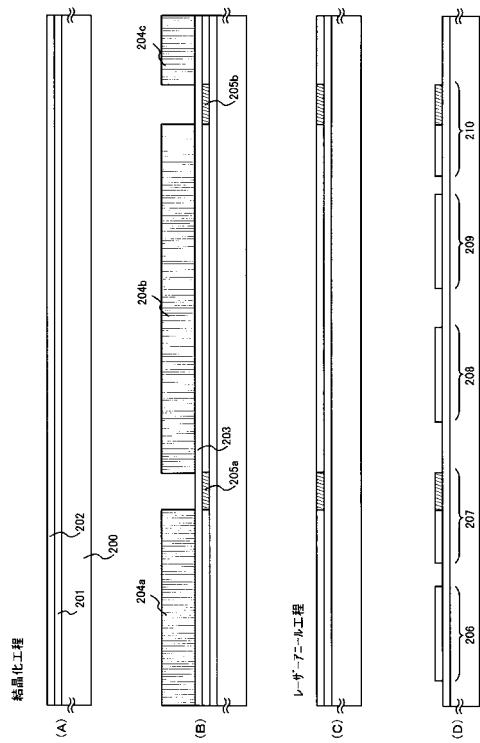

次に、図23(A)に示すように、第1層間絶縁膜237を形成する。第1層間絶縁膜237としては、珪素を含む絶縁膜を単層で用いるか、その中に組み合わせた積層膜を用い

50

れば良い。また、膜厚は 400 nm ~ 1.5 μm とすれば良い。本実施例では、200 nm 厚の窒化酸化珪素膜の上に 800 nm 厚の酸化珪素膜を積層した構造とする。

#### 【0286】

さらに、3~100% の水素を含む雰囲気中で、300~450 度で 1~12 時間の熱処理を行い水素化処理を行う。この工程は熱的に励起された水素により半導体膜の不対結合手を水素終端する工程である。水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる）を行っても良い。

#### 【0287】

なお、水素化処理は第 1 層間絶縁膜 237 を形成する間に入れても良い。即ち、200 nm 厚の窒化酸化珪素膜を形成した後で上記のように水素化処理を行い、その後で残り 800 nm 厚の酸化珪素膜を形成しても構わない。10

#### 【0288】

次に、ゲート絶縁膜 211 及び第 1 層間絶縁膜 237 に対してコンタクトホールを形成し、ソース配線 238~242 と、ドレイン配線 243~247 を形成する。なお、本実施例ではこの電極を、Ti 膜を 100 nm、Ti を含むアルミニウム膜を 300 nm、Ti 膜 150 nm をスパッタ法で連続形成した 3 層構造の積層膜とする。勿論、他の導電膜でも良い。

#### 【0289】

次に、50~500 nm（代表的には 200~300 nm）の厚さで第 1 パッシベーション膜 248 を形成する。本実施例では第 1 パッシベーション膜 248 として 300 nm 厚の窒化酸化珪素膜を用いる。これは窒化珪素膜で代用しても良い。なお、窒化酸化珪素膜の形成に先立って H<sub>2</sub>、NH<sub>3</sub> 等水素を含むガスを用いてプラズマ処理を行うことは有効である。この前処理により励起された水素が第 1 層間絶縁膜 237 に供給され、熱処理を行うことで、第 1 パッシベーション膜 248 の膜質が改善される。それと同時に、第 1 層間絶縁膜 237 に添加された水素が下層側に拡散するため、効果的に活性層を水素化することができる。20

#### 【0290】

次に、図 23 (B) に示すように有機樹脂からなる第 2 層間絶縁膜 249 を形成する。有機樹脂としてはポリイミド、ポリアミド、アクリル、BCB（ベンゾシクロブテン）等を使用することができる。特に、第 2 層間絶縁膜 249 は平坦化の意味合いが強いので、平坦性に優れたアクリルが好ましい。本実施例では TFT によって形成される段差を十分に平坦化しうる膜厚でアクリル膜を形成する。好ましくは 1~5 μm（さらに好ましくは 2~4 μm）とすれば良い。30

#### 【0291】

次に、第 2 層間絶縁膜 249 及び第 1 パッシベーション膜 248 にドレイン配線 245 に達するコンタクトホールを形成し、ドレイン配線 245 に接するようにフォトダイオードのカソード電極 250 を形成する。本実施例では、カソード電極 250 としてスパッタ法によって形成したアルミニウム膜を用いたが、他の金属、例えばチタン、タンタル、タンゲステン、銅を用いることができる。また、チタン、アルミニウム、チタンでなる積層膜を用いてもよい。40

#### 【0292】

次に、水素を含有する非晶質珪素膜を基板全面に成膜した後にパターニングし、光電変換層 251 を形成する。次に、基板全面に透明導電膜を形成する。本実施例では透明導電膜として厚さ 200 nm の ITO をスパッタ法で成膜する。透明導電膜をパターニングし、アノード電極 252 を形成する。（図 23 (C)）

#### 【0293】

次に、図 24 (A) に示すように第 3 層間絶縁膜 253 を形成する。第 3 層間絶縁膜 253 として、ポリイミド、ポリアミド、ポリイミドアミド、アクリル等の樹脂を用いることで、平坦な表面を得ることができる。本実施例では、第 3 層間絶縁膜 253 として厚さ 0.7 μm のポリイミド膜を基板全面に形成した。50

## 【0294】

次に、第3層間絶縁膜253、第2層間絶縁膜249及び第1パッシベーション膜248にドレイン配線247に達するコンタクトホールを形成し、画素電極255を形成する。また第3層間絶縁膜253に、アノード電極252に達するコンタクトホールを形成し、センサ用配線254を形成する。本実施例ではアルミニウム合金膜(1wt%のチタンを含有したアルミニウム膜)を300nmの厚さに形成し、パターニングを行ってセンサ用配線254及び画素電極255を同時に形成する。

## 【0295】

次に、図24(B)に示すように、樹脂材料でなるバンク256を形成する。バンク256は1~2μm厚のアクリル膜またはポリイミド膜をパターニングして形成すれば良い。バンク256はソース配線241上に沿って形成しても良いし、ゲート配線(図示せず)上に沿って形成しても良い。なおバンク256を形成している樹脂材料に顔料等を混ぜ、バンク256を遮蔽膜として用いても良い。

10

## 【0296】

次に、発光層257を形成する。具体的には、発光層257となる有機EL材料をクロロフォルム、ジクロロメタン、キシレン、トルエン、テトラヒドロフラン等の溶媒に溶かして塗布し、その後、熱処理を行うことにより溶媒を揮発させる。こうして有機EL材料でなる被膜(発光層)が形成される。

## 【0297】

なお、本実施例では一画素しか図示されていないが、このとき同時に赤色に発光する発光層、緑色に発光する発光層及び青色に発光する発光層が形成される。本実施例では、赤色に発光する発光層としてシアノポリフェニレンビニレン、緑色に発光する発光層としてポリフェニレンビニレン、青色に発光する発光層としてポリアルキルフェニレンを各々50nmの厚さに形成する。また、溶媒としては1,2-ジクロロメタンを用い、80~150のホットプレートで1~5分の熱処理を行って揮発させる。

20

## 【0298】

次に、正孔注入層258を20nmの厚さに形成する。正孔注入層258は全ての画素に共通で設ければ良いので、スピンドルコート法または印刷法を用いて形成すれば良い。本実施例ではポリチオフェン(PEDOT)を水溶液として塗布し、100~150のホットプレートで1~5分の熱処理を行って水分を揮発させる。この場合、ポリフェニレンビニレンやポリアルキルフェニレンが水に溶けないため、発光層257を溶解させることなく正孔注入層258を形成することが可能である。

30

## 【0299】

なお、正孔注入層258として低分子系有機EL材料を用いることも可能である。その場合は、蒸着法を用いて形成すれば良い。

## 【0300】

本実施例ではEL層を発光層及び正孔注入層でなる2層構造とするが、その他に正孔輸送層、電子注入層、電子輸送層等を設けても構わない。このように組み合わせは既に様々な例が報告されており、そのいずれの構成を用いても構わない。

40

## 【0301】

発光層257及び正孔注入層258を形成したら、対向電極として透明導電膜でなる陽極259を120nmの厚さに形成する。本実施例では、酸化インジウムに10~20wt%の酸化亜鉛を添加した透明導電膜を用いる。成膜方法は、発光層257や正孔注入層258を劣化させないように室温で蒸着法により形成することが好ましい。

## 【0302】

陽極259を形成したら、図24(B)に示すように第4層間絶縁膜260を形成する。第4層間絶縁膜260として、ポリイミド、ポリアミド、ポリイミドアミド、アクリル等の樹脂を用いることで、平坦な表面を得ることができる。本実施例では、第4層間絶縁膜260として厚さ0.7μmのポリイミド膜を基板全面に形成した。

## 【0303】

50

こうして図24(B)に示すような構造の基板が完成する。なお、バンク256を形成した後、第4層間絶縁膜260を形成するまでの工程をマルチチャンバー方式(またはインライン方式)の薄膜形成装置を用いて、空気解放せずに連続的に処理することは有効である。

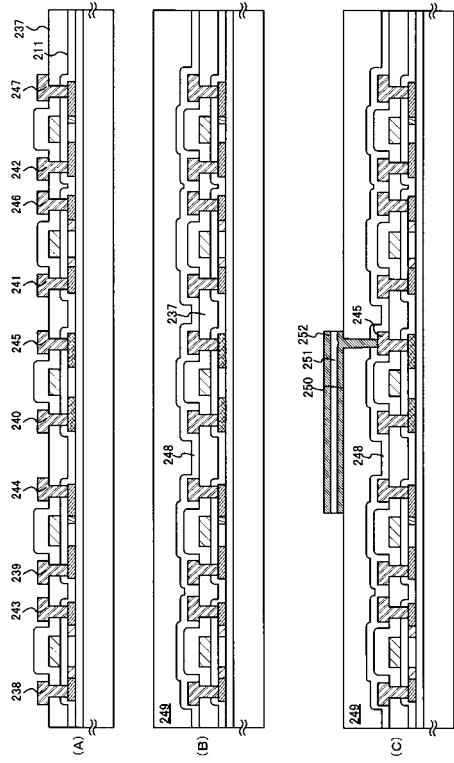

#### 【0304】

270はバッファ用TFT、271は選択用TFT、272はリセット用TFT、273はスイッチング用TFT、274はEL駆動用TFTである。

#### 【0305】

本実施例では、バッファ用TFT270及びスイッチング用TFT273がNチャネル型TFTであり、それぞれソース領域側とドレイン領域側の両方にそれぞれLDD領域281～284を有している。なおこのLDD領域281～284はゲート絶縁膜211を間に介してゲート電極212、215と重なっていない。上記構成により、バッファ用TFT270及びスイッチング用TFT273は、極力ホットキャリア注入を低減させることができる。

10

#### 【0306】

また本実施例では、選択用TFT271及びEL駆動用TFT274がNチャネル型TFTであり、それぞれドレイン領域側にのみそれぞれLDD領域283、286を有している。なおこのLDD領域283、286はゲート絶縁膜211を間に介してゲート電極213、216と重なっている。

20

#### 【0307】

ドレイン領域側のみにLDD領域283、286を形成しているのは、ホットキャリア注入を低減させ、なおかつ動作速度を落とさないための配慮である。また、この選択用TFT271及びEL駆動用TFT274はオフ電流値をあまり気にする必要はなく、それよりも動作速度を重視した方が良い。従って、LDD領域283、286は完全にゲート電極213、216と重ねてしまい、極力抵抗成分を少なくすることが望ましい。即ち、いわゆるオフセットはなくした方がよい。特に、ソース信号線駆動回路又はゲート信号線駆動回路を15V～20Vで駆動させる場合、本実施例のEL駆動用TFT274の上記構成は、ホットキャリア注入を低減させ、なおかつ動作速度を落とさないのに有効である。

#### 【0308】

また本実施例では、リセット用TFT272はPチャネル型TFTであり、LDD領域を有していない。Pチャネル型TFTは、ホットキャリア注入による劣化が殆ど気にならないので、特にLDD領域を設けなくても良い。勿論、Nチャネル型TFTと同様にLDD領域を設け、ホットキャリア対策を講じることも可能である。また、リセット用TFT272がNチャネル型TFTであっても良い。

30

#### 【0309】

なお、実際には図24(B)まで完成したら、さらに外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィルム等)や透光性のシーリング材でパッケージング(封入)することが好ましい。その際、シーリング材の内部を不活性雰囲気にしたり、内部に吸湿性材料(例えば酸化バリウム)を配置したりするとEL素子の信頼性が向上する。

40

#### 【0310】

また、パッケージング等の処理により気密性を高めたら、基板上に形成された素子又は回路から引き回された端子と外部信号端子とを接続するためのコネクター(フレキシブルプリントサーキット:FPC)を取り付けて製品として完成する。このような出荷できる状態にまでした状態を本明細書中ではエリアセンサという。

#### 【0311】

なお、本発明は上述した作製方法に限定されず、公知の方法を用いて作製することが可能である。なお本実施例は、実施の形態1～5、実施例1～実施例9と自由に組み合わせることが可能である。

#### 【0312】

50

(実施例 11 )

本発明を実施して形成されたエリアセンサは、様々な電子機器に用いることができる。その様な本発明の電子機器としては、スキャナ、デジタルスチルカメラ、X線カメラ、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機）、ノート型パーソナルコンピュータ、ゲーム機器、テレビ電話等が上げられる。本実施例では、一例として、携帯型ハンドスキャナーについて図37を用いて説明する。

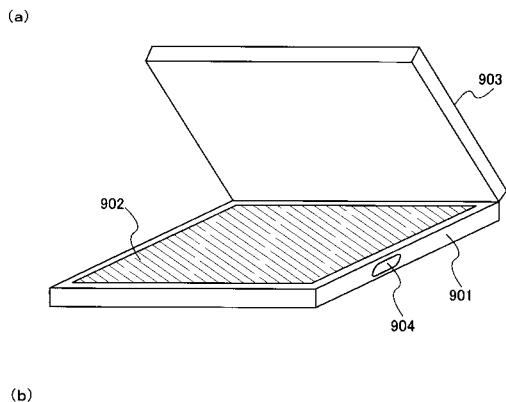

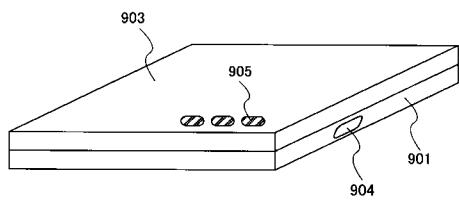

【0313】

図41(a)は携帯型ハンドスキャナーであり、本体901、センサ部902、上部カバー903、外部接続ポート904、操作スイッチ905で構成されている。図41(b)は図41(a)と同じ携帯型ハンドスキャナーの上部カバー903を閉じた図である。

10

【0314】

本発明のエリアセンサは、読み込んだ画像をセンサ部902において表示することが可能であり、新たに電子ディスプレイをエリアセンサに設けなくとも、その場で読み込んだ画像を確認することができる。

【0315】

またエリアセンサ902で読み込んだ画像信号を、外部接続ポート904から携帯型ハンドスキャナーの外部に接続されている電子機器に送り、ソフト上で画像を補正、合成、編集等を行うことも可能である。

【0316】

なお本実施例は、実施の形態1～5、実施例1～実施例10と自由に組み合わせることが可能である。

20

【0317】

(実施例12)

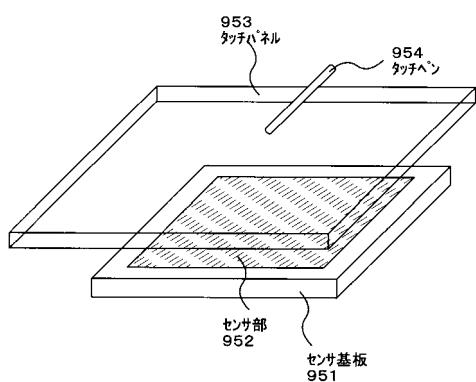

本発明を実施して形成されたエリアセンサは、様々な電子機器に用いることが出来るが、本実施例では、実施例12とは別の携帯型ハンドスキャナーについて図42を用いて説明する。

【0318】

951はセンサ基板、952はセンサ部、953はタッチパネル、954はタッチペンである。タッチパネル953は透光性を有しており、センサ部952から発せられる光及び、センサ部952に入射する光を透過することができ、タッチパネル953を通して被写体上の画像を読み込むことができる。またセンサ部952に画像が表示されている場合にも、タッチパネル953を通して、センサ部952上の画像を見ることが可能である。

30

【0319】

タッチペン954がタッチパネル953に触れると、タッチペン954とタッチパネル953とが接している部分の位置の情報を、電気信号としてエリアセンサに取り込むことができる。本実施例で用いられるタッチパネル953及びタッチペン954は、タッチパネル953が透光性を有していて、なおかつタッチペン954とタッチパネル953とが接している部分の位置の情報を、電気信号としてエリアセンサに取り込むことができるものならば、公知のものを用いることができる。

【0320】

40

上記構成を有する本発明のエリアセンサは、画像を読み込んで、センサ部952に読み込んだ画像を表示し、取り込んだ画像にタッチペン954で書き込みを行うことができる。そして本発明のエリアセンサは、画像の読み込み、画像の表示、画像への書き込みを、全てセンサ部952において行うことができる。よってエリアセンサ自体の大きさを抑え、なおかつ様々な機能をエリアセンサに持たせることができる。

【0321】

なお本実施例は、実施の形態1～5、実施例1～実施例11と自由に組み合わせることが可能である。

【0322】

【発明の効果】

50

本発明は、ファイバプレート（光ファイバプレートまたはガラスファイバプレート）をセンサ部と被写体の間に設けたエリアセンサ及びエリアセンサを備えた表示装置を提供するものである。ファイバプレートを設けることにより、被写体の情報を正確に認識出来ない原因となっていたノイズ光が、ファイバに設けられた光吸収層に吸収される。その結果、ノイズ光がフォトダイオードに入射することを防ぐことが出来るため、凹凸のある被写体を正確に読み取ることができる。

【図面の簡単な説明】

【図 1】センサ部の回路図。

【図 2】画素の回路図。

【図 3】エリアセンサ上面図。

10

【図 4】センサ用駆動回路上面図。

【図 5】フォトダイオード部の回路図。

【図 6】フォトダイオード部の回路図。

【図 7】センサ用ソース駆動回路の回路図。

【図 8】最終出力增幅用回路の回路図。

【図 9】最終出力增幅用回路の回路図。

【図 10】エリアセンサのタイミングチャート。

【図 11】エリアセンサのタイミングチャート。

【図 12】エリアセンサ上面図。

【図 13】画像の読み取りの際のEL素子の発光のタイミングチャート。

20

【図 14】画像の表示の際のEL素子の発光のタイミングチャート。

【図 15】エリアセンサ上面図。

【図 16】画像の読みとりの際のEL素子の発光のタイミングチャート。

【図 17】センサ部の断面図。

【図 18】センサ部の断面図

【図 19】センサ部の断面図

【図 20】センサ部の断面図

【図 21】センサ部の作製工程図。

【図 22】センサ部の作製工程図。

【図 23】センサ部の作製工程図。

30

【図 24】センサ部の作製工程図。

【図 25】スネルの法則の図。

【図 26】画像の読み取りの際の被写体とセンサ部との関係の図。

【図 27】画像の読み取りの際の被写体とセンサ部との関係の図。

【図 28】画像の読み取りの際の被写体とセンサ部との関係の図。

【図 29】ガラスファイバプレートの図。

【図 30】ガラスファイバに光が照射された場合の光の進行方向を示す図。

【図 31】光ファイバプレートの図。

【図 32】光ファイバに光が照射された場合の光の進行方向を示す図。

【図 33】光ファイバに光が照射された場合の光の進行方向を示す図。

40

【図 34】本発明のエリアセンサの実施の形態の一例の図。

【図 35】本発明のエリアセンサの実施の形態の一例の図。

【図 36】本発明のエリアセンサの実施の形態の一例の図。

【図 37】本発明のエリアセンサの実施の形態の一例の図。

【図 38】本発明のエリアセンサの実施の形態の一例の図。

【図 39】入射角と反射率の関係のグラフ。

【図 40】イメージセンサ素子を有するスキヤナの図。

【図 41】本発明の表示装置の一例である携帯ハンドスキヤナーの外観図。

【図 42】本発明の表示装置の一例であるタッチパネル付き表示装置の外観図。

【符号の簡単な説明】

50

- 1 0 1 センサ部

1 0 2 画素

1 0 5 スイッチング用 TFT

1 0 6 EL 駆動用 TFT

1 0 7 EL 素子

1 0 8 コンデンサ

1 1 0 リセット用 TFT

1 1 1 バッファ用 TFT

1 1 2 選択用 TFT

1 1 3 フォトダイオード

10

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

## 【図22】

【図21】

【 図 2 3 】

211.4-耐候膜、212~216.4-ト電極、217~224.n型不純物領域(c)、225a~cシリカスラブ、226~233.m型不純物領域(a)

234abシリカスラブ、235,236.D型不純物領域

200ガラス基板、201下地膜、202絶縁基材、203保護膜、204a～c：不織布マスク、205a、b：不織布接着剤、(b)、206～210活性層

【図24】

【図25】

【図26】

【図27】

【図29】

【 28 】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

(b)

901:本体

902:センサ部

903:上部カバー

904:外部接続ポート

905:操作スイッチ

## フロントページの続き

| (51) Int.CI.   |                | F I              |                |              |                |

|----------------|----------------|------------------|----------------|--------------|----------------|

| <b>G 0 9 G</b> | <b>3/30</b>    | <b>(2006.01)</b> | <b>G 0 9 F</b> | <b>9/00</b>  | <b>3 6 6 Z</b> |

| <b>H 0 1 L</b> | <b>27/14</b>   | <b>(2006.01)</b> | <b>G 0 9 F</b> | <b>9/30</b>  | <b>3 6 5 Z</b> |

| <b>H 0 1 L</b> | <b>31/0232</b> | <b>(2006.01)</b> | <b>G 0 9 G</b> | <b>3/30</b>  | <b>Z</b>       |

| <b>H 0 1 L</b> | <b>27/146</b>  | <b>(2006.01)</b> | <b>H 0 1 L</b> | <b>27/14</b> | <b>D</b>       |

|                |                |                  | <b>H 0 1 L</b> | <b>31/02</b> | <b>C</b>       |

|                |                |                  | <b>H 0 1 L</b> | <b>27/14</b> | <b>C</b>       |

(56)参考文献 特開平07-037688 (JP, A)

特開平11-075115 (JP, A)

特開平05-035207 (JP, A)

特開平05-276312 (JP, A)

特開平10-208022 (JP, A)

特開平10-104442 (JP, A)

特開平10-084105 (JP, A)

特開平06-291935 (JP, A)

特開平09-037194 (JP, A)

特開平05-252344 (JP, A)

特開平11-065763 (JP, A)

特開平06-140672 (JP, A)

特開平10-333605 (JP, A)

(58)調査した分野(Int.CI., DB名)

G09G 3/20

G06T 1/00

G09F 9/00

G09F 9/30

G09G 3/30

H01L 27/14

H01L 27/146

H01L 27/32

H01L 31/0232