(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3732477号

(P3732477)

(45) 発行日 平成18年1月5日(2006.1.5)

(24) 登録日 平成17年10月21日(2005.10.21)

(51) Int.C1.

F 1

|             |              |                  |             |             |                |

|-------------|--------------|------------------|-------------|-------------|----------------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/30</b> | <b>J</b>       |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> | <b>6 1 1 H</b> |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> | <b>6 2 4 B</b> |

|             |              |                  | <b>G09G</b> | <b>3/20</b> | <b>6 4 1 D</b> |

|             |              |                  | <b>G09G</b> | <b>3/20</b> | <b>6 4 2 A</b> |

請求項の数 51 (全 64 頁) 最終頁に続く

(21) 出願番号

特願2002-310562 (P2002-310562)

(22) 出願日

平成14年10月25日 (2002.10.25)

(65) 公開番号

特開2003-223138 (P2003-223138A)

(43) 公開日

平成15年8月8日 (2003.8.8)

審査請求日 平成17年3月8日 (2005.3.8)

(31) 優先権主張番号

特願2001-330050 (P2001-330050)

(32) 優先日

平成13年10月26日 (2001.10.26)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 西島 篤宏

早期審査対象出願

最終頁に続く

(54) 【発明の名称】画素回路、発光装置および電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、第4のトランジスタ及び容量素子が設けられ、

前記第1のトランジスタのゲートは、前記第2のトランジスタのソース又はドレインの一方と前記容量素子の第1の電極とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの一方と前記第4のトランジスタのソース又はドレインの一方とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの他方に電気的に接続され、 10

前記第3のトランジスタのソース又はドレインの他方は、電流供給線に電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記容量素子の第2の電極に電気的に接続され、

前記第2のトランジスタのゲートは、第1のゲート信号線に電気的に接続され、

前記第3のトランジスタのゲートは、第2のゲート信号線に電気的に接続され、

前記第4のトランジスタのゲートは、前記第1のゲート信号線に電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、発光素子の第1の電極又は第2の電極の一方に電気的に接続され、

前記第2のトランジスタは、前記第1のトランジスタのゲートに対する電圧の供給を制御することを特徴とする画素回路。

**【請求項2】**

第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、第4のトランジスタ及び容量素子が設けられ、

前記第1のトランジスタのゲートは、前記第2のトランジスタのソース又はドレインの一方と前記容量素子の第1の電極とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの一方と前記第4のトランジスタのソース又はドレインの一方とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの他方に電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、電流供給線に電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記容量素子の第2の電極に電気的に接続され、

前記第2のトランジスタのゲートは、第1のゲート信号線に電気的に接続され、

前記第3のトランジスタのゲートは、第2のゲート信号線に電気的に接続され、

前記第4のトランジスタのゲートは、第3のゲート信号線に電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、発光素子の第1の電極又は第2の電極の一方電気的に接続され、

前記第2のトランジスタは、前記第1のトランジスタのゲートに対する電圧の供給を制御することを特徴とする画素回路。

**【請求項3】**

第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、第4のトランジスタ、第5のトランジスタ及び容量素子が設けられ、

前記第1のトランジスタのゲートは、前記第2のトランジスタのソース又はドレインの一方と前記容量素子の第1の電極とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの一方と前記第4のトランジスタのソース又はドレインの一方とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの他方に電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、電流供給線に電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記容量素子の第2の電極と前記第5のトランジスタのソース又はドレインの一方とに電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は、ソース信号線に電気的に接続され、

前記第2のトランジスタのゲートは、第1のゲート信号線に電気的に接続され、

前記第3のトランジスタのゲートは、第2のゲート信号線に電気的に接続され、

前記第4のトランジスタのゲートは、前記第1のゲート信号線に電気的に接続され、

前記第5のトランジスタのゲートは、第3のゲート信号線に電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、発光素子の第1の電極又は第2の電極の一方電気的に接続され、

前記第2のトランジスタは、前記第1のトランジスタのゲートに対する電圧の供給を制御することを特徴とする画素回路。

**【請求項4】**

第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、第4のトランジスタ、第5のトランジスタ及び容量素子が設けられ、

10

20

30

40

50

前記第1のトランジスタのゲートは、前記第2のトランジスタのソース又はドレインの一方と前記容量素子の第1の電極とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの一方と前記第4のトランジスタのソース又はドレインの一方とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの他方に電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、電流供給線に電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記容量素子の第2の電極と前記第5のトランジスタのソース又はドレインの一方とに電気的に接続され、 10

前記第5のトランジスタのソース又はドレインの他方は、ソース信号線に電気的に接続され、

前記第2のトランジスタのゲートは、第1のゲート信号線に電気的に接続され、

前記第3のトランジスタのゲートは、第2のゲート信号線に電気的に接続され、

前記第4のトランジスタのゲートは、第3のゲート信号線に電気的に接続され、

前記第5のトランジスタのゲートは、第4のゲート信号線に電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、発光素子の第1の電極又は第2の電極の一方電気的に接続され、

前記第2のトランジスタは、前記第1のトランジスタのゲートに対する電圧の供給を制御することを特徴とする画素回路。 20

#### 【請求項5】

第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、第4のトランジスタ、容量素子及び発光素子が画素に設けられ、

前記第1のトランジスタのゲートは、前記第2のトランジスタのソース又はドレインの一方と前記容量素子の第1の電極とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの一方と前記第4のトランジスタのソース又はドレインの一方とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記発光素子の第1の電極又は第2の電極の一方と、前記第2のトランジスタのソース又はドレインの他方とに電気的に接続され、 30

前記第3のトランジスタのソース又はドレインの他方は、電流供給線に電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記容量素子の第2の電極に電気的に接続され、

前記第2のトランジスタのゲートは、第1のゲート信号線に電気的に接続され、

前記第3のトランジスタのゲートは、第2のゲート信号線に電気的に接続され、

前記第4のトランジスタのゲートは、前記第1のゲート信号線に電気的に接続され、

前記第2のトランジスタは、前記第1のトランジスタのゲートに対する電圧の供給を制御することを特徴とする発光装置。 40

#### 【請求項6】

第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、第4のトランジスタ、容量素子及び発光素子が画素に設けられ、

前記第1のトランジスタのゲートは、前記第2のトランジスタのソース又はドレインの一方と前記容量素子の第1の電極とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの一方と前記第4のトランジスタのソース又はドレインの一方とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記発光素子の第1の電極又 50

は第2の電極の一方と、前記第2のトランジスタのソース又はドレインの他方とに電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、電流供給線に電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記容量素子の第2の電極に電気的に接続され、

前記第2のトランジスタのゲートは、第1のゲート信号線に電気的に接続され、

前記第3のトランジスタのゲートは、第2のゲート信号線に電気的に接続され、

前記第4のトランジスタのゲートは、第3のゲート信号線に電気的に接続され、

前記第2のトランジスタは、前記第1のトランジスタのゲートに対する電圧の供給を制御することを特徴とする発光装置。 10

#### 【請求項7】

第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、第4のトランジスタ、第5のトランジスタ、容量素子及び発光素子が画素に設けられ、

前記第1のトランジスタのゲートは、前記第2のトランジスタのソース又はドレインの一方と前記容量素子の第1の電極とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの一方と前記第4のトランジスタのソース又はドレインの一方とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記発光素子の第1の電極又は第2の電極の一方と、前記第2のトランジスタのソース又はドレインの他方とに電気的に接続され。 20

前記第3のトランジスタのソース又はドレインの他方は、電流供給線に電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記容量素子の第2の電極と前記第5のトランジスタのソース又はドレインの一方とに電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は、ソース信号線に電気的に接続され、

前記第2のトランジスタのゲートは、第1のゲート信号線に電気的に接続され、

前記第3のトランジスタのゲートは、第2のゲート信号線に電気的に接続され、

前記第4のトランジスタのゲートは、前記第1のゲート信号線に電気的に接続され、

前記第5のトランジスタのゲートは、第3のゲート信号線に電気的に接続され、

前記第2のトランジスタは、前記第1のトランジスタのゲートに対する電圧の供給を制御することを特徴とする発光装置。 30

#### 【請求項8】

第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、第4のトランジスタ、第5のトランジスタ、容量素子及び発光素子が画素に設けられ、

前記第1のトランジスタのゲートは、前記第2のトランジスタのソース又はドレインの一方と前記容量素子の第1の電極とに電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの一方と前記第4のトランジスタのソース又はドレインの一方とに電気的に接続され。 40

前記第1のトランジスタのソース又はドレインの他方は、前記発光素子の第1の電極又は第2の電極の一方と、前記第2のトランジスタのソース又はドレインの他方とに電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、電流供給線に電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記容量素子の第2の電極と前記第5のトランジスタのソース又はドレインの一方とに電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は、ソース信号線に電気的に接続 50

され、

前記第2のトランジスタのゲートは、第1のゲート信号線に電気的に接続され、

前記第3のトランジスタのゲートは、第2のゲート信号線に電気的に接続され、

前記第4のトランジスタのゲートは、第3のゲート信号線に電気的に接続され、

前記第5のトランジスタのゲートは、第4のゲート信号線に電気的に接続され、

前記第2のトランジスタは、前記第1のトランジスタのゲートに対する電圧の供給を制御することを特徴とする発光装置。

**【請求項9】**

請求項1乃至請求項4のいずれか一項において、

前記第1のトランジスタの導電型はPチャネル型であることを特徴とする画素回路。 10

**【請求項10】**

請求項1乃至請求項4のいずれか一項において、

前記第1のトランジスタと前記第3のトランジスタの導電型は同じであることを特徴とする画素回路。

**【請求項11】**

請求項1乃至請求項4のいずれか一項において、

前記第2のトランジスタと前記第4のトランジスタの導電型は同じであることを特徴とする画素回路。

**【請求項12】**

請求項1乃至請求項4のいずれか一項において、

前記第1のトランジスタと前記第3のトランジスタの導電型はPチャネル型であることを特徴とする画素回路。 20

**【請求項13】**

請求項1乃至請求項4のいずれか一項において、

前記第2のトランジスタと前記第4のトランジスタの導電型はPチャネル型であることを特徴とする画素回路。

**【請求項14】**

請求項1乃至請求項4のいずれか一項において、

前記第1のトランジスタと前記第3のトランジスタの導電型はNチャネル型であることを特徴とする画素回路。 30

**【請求項15】**

請求項1乃至請求項4のいずれか一項において、

前記第2のトランジスタと前記第4のトランジスタの導電型はNチャネル型であることを特徴とする画素回路。

**【請求項16】**

請求項1乃至請求項4のいずれか一項において、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ及び前記第4のトランジスタの導電型は同じであることを特徴とする画素回路。

**【請求項17】**

請求項3又は請求項4において、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ、前記第4のトランジスタ及び前記第5のトランジスタの導電型は同じであることを特徴とする画素回路。 40

**【請求項18】**

請求項1乃至請求項4のいずれか一項において、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ及び前記第4のトランジスタの導電型はPチャネル型であることを特徴とする画素回路。

**【請求項19】**

請求項3又は請求項4において、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ、前記第4のトランジスタの導電型はPチャネル型であることを特徴とする画素回路。 50

4のトランジスタ及び前記第5のトランジスタの導電型はPチャネル型であることを特徴とする画素回路。

【請求項20】

請求項1乃至請求項4のいずれか一項において、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ及び前記第4のトランジスタは薄膜トランジスタであることを特徴とする画素回路。

【請求項21】

請求項3又は請求項4において、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ、前記第4のトランジスタ及び前記第5のトランジスタは薄膜トランジスタであることを特徴とする画素回路。10

【請求項22】

請求項1乃至請求項4のいずれか一項において、

第2の容量素子を有し、

前記第2の容量素子の第1の電極は、前記第4のトランジスタのソース又はドレインの他方と前記容量素子の第1の電極とに電気的に接続されていることを特徴とする画素回路。20

【請求項23】

請求項1乃至請求項4のいずれか一項において、

第2の容量素子を有し、

前記第2の容量素子の第1の電極は、前記第4のトランジスタのソース又はドレインの他方と前記容量素子の第1の電極とに電気的に接続され、

前記第2の容量素子の第2の電極は、一定の電位に保たれていることを特徴とする画素回路。

【請求項24】

請求項1乃至請求項4のいずれか一項において、

第2の容量素子を有し、

前記第2の容量素子の第1の電極は、前記第4のトランジスタのソース又はドレインの他方と前記容量素子の第1の電極とに電気的に接続され、

前記第2の容量素子の第2の電極は、前記電流供給線に電気的に接続されていることを特徴とする画素回路。30

【請求項25】

請求項3又は請求項4において、

前記ソース信号線にアナログ映像信号が入力されることを特徴とする画素回路。

【請求項26】

請求項3又は請求項4において、

前記ソース信号線にデジタル映像信号が入力されることを特徴とする画素回路。

【請求項27】

請求項5乃至請求項8のいずれか一項において、

前記第1のトランジスタの導電型はPチャネル型であることを特徴とする発光装置。40

【請求項28】

請求項5乃至請求項8のいずれか一項において、

前記第1のトランジスタと前記第3のトランジスタの導電型は同じであることを特徴とする発光装置。

【請求項29】

請求項5乃至請求項8のいずれか一項において、

前記第2のトランジスタと前記第4のトランジスタの導電型は同じであることを特徴とする発光装置。

【請求項30】

請求項5乃至請求項8のいずれか一項において、

50

前記第1のトランジスタと前記第3のトランジスタの導電型はPチャネル型であることを特徴とする発光装置。

**【請求項31】**

請求項5乃至請求項8のいずれか一項において、

前記第2のトランジスタと前記第4のトランジスタの導電型はPチャネル型であることを特徴とする発光装置。

**【請求項32】**

請求項5乃至請求項8のいずれか一項において、

前記第1のトランジスタと前記第3のトランジスタの導電型はNチャネル型であることを特徴とする発光装置。 10

**【請求項33】**

請求項5乃至請求項8のいずれか一項において、

前記第2のトランジスタと前記第4のトランジスタの導電型はNチャネル型であることを特徴とする発光装置。

**【請求項34】**

請求項5乃至請求項8のいずれか一項において、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ及び前記第4のトランジスタの導電型は同じであることを特徴とする発光装置。

**【請求項35】**

請求項7又は請求項8において、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ、前記第4のトランジスタ及び前記第5のトランジスタの導電型は同じであることを特徴とする発光装置。 20

**【請求項36】**

請求項5乃至請求項8のいずれか一項において、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ及び前記第4のトランジスタの導電型はPチャネル型であることを特徴とする発光装置。

**【請求項37】**

請求項7又は請求項8において、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ、前記第4のトランジスタ及び前記第5のトランジスタの導電型はPチャネル型であることを特徴とする発光装置。 30

**【請求項38】**

請求項5乃至請求項8のいずれか一項において、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ及び前記第4のトランジスタは薄膜トランジスタであることを特徴とする発光装置。

**【請求項39】**

請求項7又は請求項8において、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ、前記第4のトランジスタ及び前記第5のトランジスタは薄膜トランジスタであることを特徴とする発光装置。 40

**【請求項40】**

請求項5乃至請求項8のいずれか一項において、

第2の容量素子を有し、

前記第2の容量素子の第1の電極は、前記第4のトランジスタのソース又はドレインの他方と前記容量素子の第1の電極とに電気的に接続されていることを特徴とする発光装置。

。

**【請求項41】**

請求項5乃至請求項8のいずれか一項において、

第2の容量素子を有し、

50

前記第2の容量素子の第1の電極は、前記第4のトランジスタのソース又はドレインの他方と前記容量素子の第1の電極とに電気的に接続され、

前記第2の容量素子の第2の電極は、一定の電位に保たれていることを特徴とする発光装置。

**【請求項42】**

請求項5乃至請求項8のいずれか一項において、

第2の容量素子を有し、

前記第2の容量素子の第1の電極は、前記第4のトランジスタのソース又はドレインの他方と前記容量素子の第1の電極とに電気的に接続され、

前記第2の容量素子の第2の電極は、前記電流供給線に電気的に接続されていることを特徴とする発光装置。 10

**【請求項43】**

請求項7又は請求項8において、

駆動回路を有し、

前記画素と前記駆動回路は、同じ基板上に設けられ、

前記駆動回路は、ゲート信号線駆動回路とソース信号線駆動回路を有することを特徴とする発光装置。

**【請求項44】**

請求項5乃至請求項8のいずれか一項において、

駆動回路を有し、

前記画素と前記駆動回路は、同じ基板上に設けられ、

前記駆動回路は、ゲート信号線駆動回路を有することを特徴とする発光装置。 20

**【請求項45】**

請求項7又は請求項8において、

駆動回路を有し、

前記画素と前記駆動回路は、同じ基板上に設けられ、

前記駆動回路は、ソース信号線駆動回路を有することを特徴とする発光装置。

**【請求項46】**

請求項7又は請求項8において、

駆動回路を有し、

前記画素と前記駆動回路は、同じ基板上に設けられ、

前記駆動回路は、ソース信号線駆動回路を有し、

前記ソース信号線駆動回路は、映像信号を前記ソース信号線に供給するためのスイッチを有することを特徴とする発光装置。 30

**【請求項47】**

請求項7又は請求項8において、

前記ソース信号線にアナログ映像信号が入力されることを特徴とする発光装置。

**【請求項48】**

請求項7又は請求項8において、

前記ソース信号線にデジタル映像信号が入力されることを特徴とする発光装置。 40

**【請求項49】**

請求項5乃至請求項8又は請求項27乃至請求項48のいずれか一項において、

前記発光素子は、EL素子であることを特徴とする発光装置。

**【請求項50】**

請求項1乃至請求項4又は請求項9乃至請求項26のいずれか一項に記載の前記画素回路を用いた電子機器。

**【請求項51】**

請求項5乃至請求項8又は請求項27乃至請求項49のいずれか一項に記載の前記発光装置を用いた電子機器。

**【発明の詳細な説明】**

**【0001】****【発明の属する技术分野】**

本発明は、トランジスタを有する発光装置の構成に関する。本発明は特に、ガラス、プラスチック等の絶縁体上に作製される薄膜トランジスタ(以後、TFTと表記する)を有するアクティブマトリクス型発光装置の構成に関する。また、このような発光装置を表示部に用いた電子機器に関する。

**【0002】****【従来の技术】**

近年、エレクトロルミネッセンス(Electro Luminescence: EL)素子等を始めとした発光素子を用いた表示装置の開発が活発化している。発光素子は、自らが発光するために視認性が高く、液晶表示装置(LCD)等において必要なバックライトを必要としないために薄型化に適しているとともに、視野角にほとんど制限が無い。10

**【0003】**

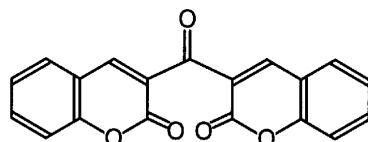

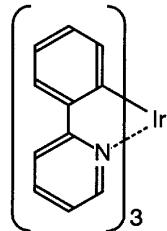

ここで、EL素子とは、電場を加えることで発生するルミネッセンスが得られる発光層を有する素子を指す。この発光層においては、一重項励起状態から基底状態に戻る際の発光(蛍光)と、三重項励起状態から基底状態に戻る際の発光(燐光)とがあるが、本発明の発光装置は、上述したいずれの発光形態であっても良い。

**【0004】**

EL素子は、一对の電極(陽極と陰極)間に発光層が挟まれる形で構成され、通常、積層構造をとっている。代表的には、イーストマン・コダック・カンパニーのTangらが提案した「陽極／正孔輸送層／発光層／電子輸送層／陰極」という積層構造が挙げられる。この構造は非常に発光効率が高く、現在研究が進められているEL素子の多くはこの構造が採用されている。20

**【0005】**

また、これ以外にも、陽極と陰極との間に、「正孔注入層／正孔輸送層／発光層／電子輸送層」または「正孔注入層／正孔輸送層／発光層／電子輸送層／電子注入層」の順に積層する構造がある。本発明の発光装置に用いるEL素子の構造としては、上述の構造のいずれを採用しても良い。また、発光層に対して蛍光性色素等をドーピングしても良い。

**【0006】**

本発明においては、EL素子において、陽極と陰極との間に設けられる全ての層を総称してEL層と呼ぶ。よって、上述の正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層は、全てEL素子に含まれ、陽極、EL層、および陰極で構成される発光素子をEL素子と呼ぶ。30

**【0007】**

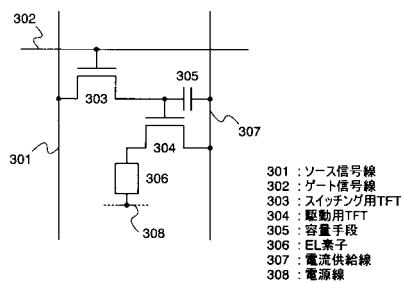

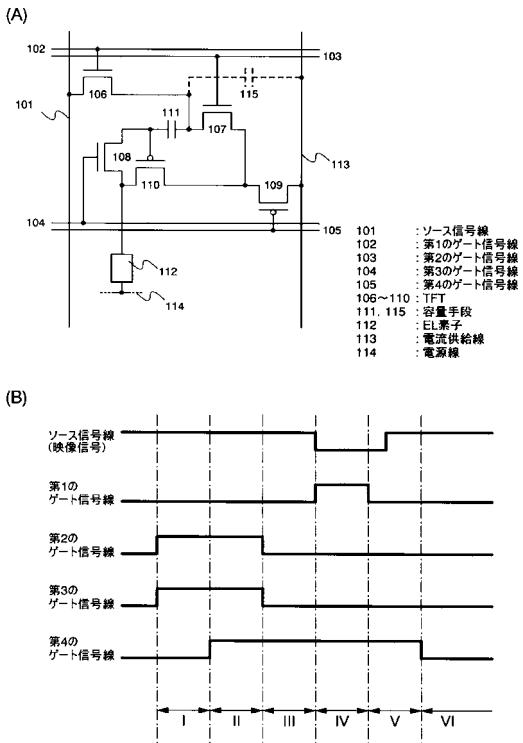

図3に、一般的な発光装置における画素の構成を示す。なお、代表的な発光装置として、EL表示装置を例とする。図3に示した画素は、ソース信号線301、ゲート信号線302、スイッチング用TFT303、駆動用TFT304、容量手段305、EL素子306、電流供給線307、電源308を有している。

**【0008】**

各部の接続関係について説明する。ここで、TFTはゲート、ソース、ドレインの3端子を有するが、ソース、ドレインに関しては、TFTの構造上、明確に区別が出来ない。よって、素子間の接続について説明する際は、ソース、ドレインのうち一方を第1の電極、他方を第2の電極と表記する。TFTのON、OFFについて、各端子の電位等(あるTFTのゲート・ソース間電圧等)について説明が必要な際には、ソース、ドレイン等と表記する。40

**【0009】**

また、本発明において、TFTがONしているとは、TFTのゲート・ソース間電圧がそのしきい値を超えて、ソース、ドレイン間に電流が流れている状態をいい、TFTがOFFしているとは、TFTのゲート・ソース間電圧がそのしきい値を下回り、ソース、ドレイン間に電流が流れていな状態をいう。

10

20

30

40

50

**【0010】**

スイッチング用 TFT303 のゲート電極は、ゲート信号線 302 に接続され、第 1 の電極はソース信号線 301 に接続され、第 2 の電極は駆動用 TFT304 のゲート電極に接続されている。駆動用 TFT304 の第 1 の電極は、電流供給線 307 に接続され、第 2 の電極は EL 素子 306 の第 1 の電極に接続されている。EL 素子 306 の第 2 の電極は、電源 308 に接続されている。容量手段 305 は、駆動用 TFT304 のゲート電極と第 1 の電極との間に接続され、駆動用 TFT304 のゲート・ソース間電圧を保持する。

**【0011】**

ゲート信号線 302 の電位が変化してスイッチング用 TFT303 が ON すると、ソース信号線 301 に入力されている映像信号は、駆動用 TFT304 のゲート電極へと入力される。入力された映像信号の電位に従って、駆動用 TFT304 のゲート・ソース間電圧が決定し、駆動用 TFT304 のソース・ドレイン間を流れる電流(以下、ドレイン電流と表記)が決定する。この電流は EL 素子 306 に供給されて発光する。

10

**【0012】**

ところで、多結晶シリコン(ポリシリコン 以下 P-Si)で形成された TFT は、非晶質シリコン(アモルファスシリコン 以下 A-Si)で形成された TFT よりも電界効果移動度が高く、ON 電流が大きいため、発光装置に用いるトランジスタとしてより適している。

**【0013】**

反面、ポリシリコンで形成された TFT は、結晶粒界における欠陥に起因して、その電気的特性にばらつきが生じやすいといった問題点を有している。

20

**【0014】**

図 3 に示した画素において、画素を構成する TFT のしきい値や ON 電流等の特性が画素ごとにばらつくと、同じ映像信号を入力した場合にも、それに応じて TFT のドレイン電流の大きさが異なってくるため、EL 素子 306 の輝度がばらつく。よってアナログ階調の場合、問題となっていた。

**【0015】**

そこで、TFT のしきい値等が ON 電流に影響しにくい領域を用いて、EL 素子を輝度 100%、0% の 2 つの状態のみで駆動するデジタル階調方式が提案されている。この方式では、白、黒の 2 階調しか表現出来ないため、時間階調方式等と組み合わせて多階調化を実現している。

30

**【0016】**

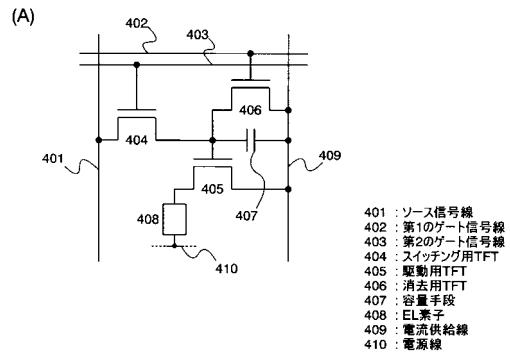

デジタル階調方式と時間階調方式とを組み合わせた方法を用いる場合の発光装置の画素の構成は、図 4(A)(B) に示したようなものがある。スイッチング用 TFT404、駆動用 TFT405 に加え、消去用 TFT406 を用いることによって、発光時間の長さを細かく制御することが可能となっている。

**【0017】**

一方、アナログ階調方式を用いて、TFT のしきい値ばらつきを補正することの出来るものが提案されている(例えば、特許文献 1 参照)。

40

**【0018】****【特許文献 1】**

米国特許第 6229506 号明細書

**【0019】**

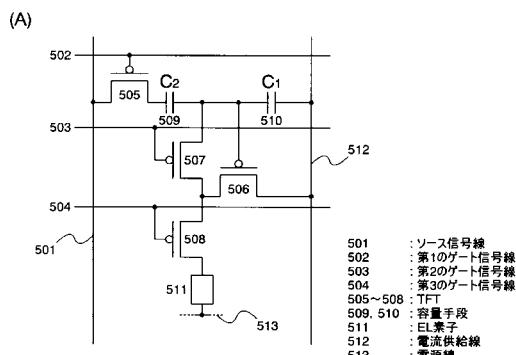

図 5 に示すように、ソース信号線 501、第 1 ~ 第 3 のゲート信号線 502 ~ 504、TFT505 ~ 508、容量手段 509(C<sub>2</sub>)、510(C<sub>1</sub>)、電流供給線 512、EL 素子 511 を有する。

**【0020】**

TFT505 のゲート電極は、第 1 のゲート信号線 502 に接続され、第 1 の電極は、ソース信号線 501 に接続され、第 2 の電極は、容量手段 509 の第 1 の電極に接続されている。容量手段 509 の第 2 の電極は、容量手段 510 の第 1 の電極に接続され、容量手

50

段 510 の第 2 の電極は、電流供給線 512 に接続されている。TFT506 のゲート電極は、容量手段 509 の第 2 の電極および容量手段 510 の第 1 の電極に接続され、第 1 の電極は、電流供給線 512 に接続され、第 2 の電極は、TFT507 の第 1 の電極および TFT508 の第 1 の電極に接続されている。TFT507 のゲート電極は、第 2 のゲート信号線 503 に接続され、第 2 の電極は、容量手段 509 の第 2 の電極および容量手段 510 の第 1 の電極に接続されている。TFT508 のゲート電極は、第 3 のゲート信号線 504 に接続され、第 2 の電極は、EL 素子 511 の第 1 の電極に接続されている。EL 素子 511 の第 2 の電極には、電源 513 によって一定電位が与えられ、電流供給線 512 とは互いに電位差を有する。

【 0 0 2 1 】

10

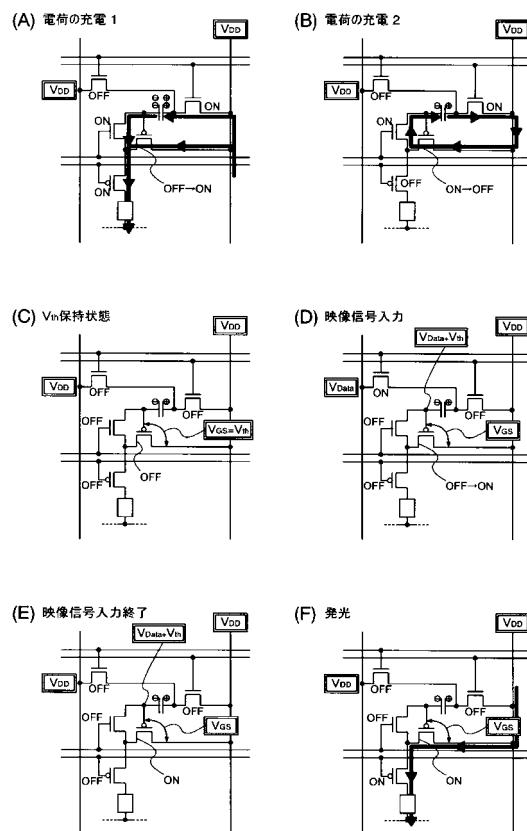

図5(B)および図6(A)～(F)を用いて、動作について説明する。図5(B)は、ソース信号線501、第1～第3のゲート信号線502～504に入力される映像信号およびパルスのタイミングを示しており、図6に示す各動作にあわせて、I～VIIIの区間に分割している。また、図5に示した画素の一例では、4つのTFTを用いて構成され、その極性は全てPチャネル型である。よって、ゲート電極にLレベルが入力されてONし、Hレベルが入力されてOFFするものとする。

【 0 0 2 2 】

まず、第1のゲート信号線502がLレベルとなり、TFT505がONする(区間I)。続いて第2、第3のゲート信号線がLレベルとなり、TFT507、508がONする。ここで、図6(A)に示すように、容量手段509、510が充電され、容量手段510が保持する電圧が、TFT506のしきい値( $V_{th}$ )を上回ったところで、TFT506がONする(区間II)。

【 0 0 2 3 】

続いて、第3のゲート信号線がHレベルとなって、TFT508がOFFする。すると、容量手段509、510に貯まっていた電荷が再び移動し、容量手段510に保持される電圧は、やがて $V_{th}$ に等しくなる。このとき、図6(B)にも示すように、電流供給線512、ソース信号線501の電位はいずれも $V_{DD}$ であるので、容量手段509においても、保持されている電圧は $V_{th}$ に等しくなる。よって、やがてTFT506はOFFする。

[ 0 0 2 4 ]

前述のように、容量手段 509、510 に保持されている電圧が  $V_{th}$  に等しくなったところで、第 2 のゲート信号線 503 が H レベルとなり、TFT507 が OFF する(区間 IV)。この動作により、図 6(C)に示すように、容量手段において  $V_{th}$  が保持される。

【 0 0 2 5 】

このとき、容量手段 5 1 0 ( $C_1$ )に保持されている電荷  $Q_1$ について、式(1)のような関係が成立する。同時に、容量手段 5 0 9 ( $C_2$ )に保持されている電荷  $Q_2$ においては、式(2)のような関係が成立する。

【 0 0 2 6 】

## 【数1】

$$Q_1 = C_1 \times |V_{th}| \quad \dots \dots \dots \quad (1)$$

40

[ 0 0 2 7 ]

【数2】

$$Q_2 = C_2 \times |V_{th}| \quad \dots \dots \dots \quad (2)$$

.....(2)

【 0 0 2 8 】

続いて、図6(D)に示すように、映像信号の入力が行われる(区間V)。ソース信号線50 50

1に映像信号が出力されて、その電位は $V_{DD}$ から映像信号の電位 $V_{Data}$ (ここでは、TF T506がPチャネル型であるので、 $V_{DD} > V_{Data}$ とする。)となる。このときの、TF T506のゲート電極の電位を $V_p$ とし、このノードにおける電荷を $Q$ とすると、容量手段509、510とを含めた電荷保存則により、式(3)、(4)のような関係が成立する。

〔 0 0 2 9 〕

【数3】

$$Q+Q_1=C_1 \times (V_{DD}-V_P) \quad \dots \dots \dots \quad (3)$$

1003

$$Q-Q_2=C_2 \times (V_P - V_{Data}) \quad \dots \dots \dots (4)$$

[ 0 0 3 1 ]

式(1)～(4)より、TFT506のゲート電極の電位 $V_g$ は、式(5)で表される。

【0032】

【数5】

$$V_P = \frac{C_1}{C_1 + C_2} V_{DD} + \frac{C_2}{C_1 + C_2} |V_{Data} - V_{th}| \quad \dots \dots \dots (5)$$

[ 0 0 3 3 ]

よって、TFT506のゲート・ソース間電圧 $V_{GS}$ は、式(6)で表される。

[ 0 0 3 4 ]

【数6】

$$\begin{aligned}

V_{GS} &= V_P - V_{DD} \\

&= \frac{C_2}{C_1 + C_2} (V_{Data} - V_{DD}) - |V_{th}| \\

&= \frac{C_2}{C_1 + C_2} (V_{Data} - V_{DD}) + V_{th} \quad \dots \dots \dots (6)

\end{aligned}$$

〔 0 0 3 5 〕

式(6)右辺には、 $V_{th}$ の項が含まれる。すなわち、ソース信号線より入力される映像信号には、その画素におけるTFT506のしきい値が上乗せされて容量手段510に保持される。

[ 0 0 3 6 ]

映像信号の入力が完了すると、第1のゲート信号線502がHレベルとなって、TFT505がOFFする(区間V1)。その後、ソース信号線は所定の電位に戻る(区間V11)。以上の動作によって、映像信号の画素への書き込み動作が完了する(図6(E))。

[ 0 0 3 7 ]

続いて、第3のゲート信号線がLレベルとなり、TFT508がONし、EL素子に図6(F)に示すように電流が流れることによってEL素子が発光する。このときEL素子に流れる電流の値は、TFT506のゲート・ソース間電圧に従つたものであり、TFT50

6 を流れるドレン電流  $I_{DS}$  は、式(7)で表される。

【 0 0 3 8 】

【数7】

$$I_{DS} = \frac{\beta}{2} (V_{GS} - V_{th})^2$$

$$= \frac{\beta}{2} \left\{ \frac{C_2}{C_1 + C_2} (V_{Data} - V_{DD}) \right\}^2 \quad \dots \dots \dots (7)$$

10

【 0 0 3 9 】

式(7)より、TFT506のドレン電流  $I_{DS}$  には、しきい値  $V_{th}$  の値に依存しないことがわかる。よって、TFT506のしきい値がばらついた場合にも、画素ごとにその値を補正して映像信号に上乗せすることにより、映像信号の電位  $V_{Data}$  に従った電流がEL素子に流れることがわかる。

[ 0 0 4 0 ]

#### 【発明が解決しようとする課題】

しかし、前述の構成の場合、容量手段 509、510 の容量値がばらついた場合には、TFT506 のドレン電流  $I_{DS}$  がばらついてしまうことになる。そこで、本発明においては、容量値のばらつきの影響を受けることのない構成によって、TFT のしきい値ばらつきを補正することの出来る構成の画素を用いた発光装置を提供することを目的とする。

20

[ 0 0 4 1 ]

### 【課題を解決するための手段】

前述の方法によると、TFT506のドレン電流 $I_{DS}$ は、2つの容量手段509、510の容量値に依存していた。つまり、しきい値を保持している状態(図6(C))から、映像信号の書き込み(図6(D))に移るとき、容量手段 $C_1$ 、 $C_2$ においては電荷の移動がある。つまり、 $C_1$ の両電極間の電圧と、 $C_2$ の両電極間の電圧とは、図6(C)～図6(D)において変化する。そのとき、 $C_1$ 、 $C_2$ の容量値にばらつきがあると、 $C_1$ の両電極間の電圧と、 $C_2$ の両電極間の電圧もまたばらつくことになる。本発明においては、容量手段を用いてしきい値を保存した後に、映像信号を入力する過程においては、容量手段において電荷の移動がない。よって、容量手段の両電極間の電圧が変化しない。そのため、映像信号にしきい値をそのまま上乗せすることによって補正を行うことが出来るため、ドレン電流が容量値のばらつきによる影響を受けないようにすることが出来る。

30

[ 0 0 4 2 ]

また、本発明におけるトランジスタとしては、主としてTFTを用いて構成したものを例として挙げているが、単結晶トランジスタ又は有機物を利用したトランジスタでもよい。例えば、単結晶トランジスタとしては、SOI技術を用いて形成されたトランジスタとすることができる。また、薄膜トランジスタとしては、活性層として多結晶半導体を用いたものでも、非晶質半導体を用いたものでもよい。例えば、ポリシリコンを用いたTFTや、アモルファスシリコンを用いたTFTとすることができる。その他、バイポーラトランジスタや、カーボンナノチューブ等により形成されたトランジスタを用いても良い。

40

[ 0 0 4 3 ]

本発明の構成を以下に記す。

[ 0 0 4 4 ]

#### 本発明の発光装置は

発光素子が備えられた画素を有する発光装置であって、

前記画素は

電流供給線と、第1乃至第4のトランジスタと、容量手段とを少なくとも有し、前記第1のトランジスタのゲート電極は、前記第2のトランジスタの第1の電極および、

前記容量手段の第1の電極と電気的に接続され、第1の電極は、前記電流供給線と電気的に接続され、第2の電極は、前記第2のトランジスタの第2の電極および、前記第3のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極には、第1の信号が入力され、

前記第3のトランジスタのゲート電極には、第2の信号が入力され、

前記容量手段の第2の電極は、前記第4のトランジスタの第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極には、第3の信号が入力され、第2の電極は、前記電流供給線と電気的に接続された構成を有することを特徴としている。

【0045】

10

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第4のゲート信号線と、電流供給線と、第1乃至第5のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記電流供給線と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極および、前記第5のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、第2の電極は、前記発光素子の第1の電極と電気的に接続され、

前記第5のトランジスタの第2の電極は、前記電流供給線と電気的に接続されていることを特徴としている。

【0046】

30

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第3のゲート信号線と、電流供給線と、第1乃至第5のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記電流供給線と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極および、前記第5のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第2の電極は、前記発光素子の第1の電極と電気的に接続され、

前記第5のトランジスタの第2の電極は、前記電流供給線と電気的に接続されていることを特徴としている。

【0047】

50

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第4のゲート信号線と、電流供給線と、第1乃至第5のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、

第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記第2のトランジスタの第1の電極および、前記容量手段の第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極および、前記第5のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、

第2の電極は、前記第5のトランジスタの第2の電極および、前記発光素子の第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、

第2の電極は、前記電流供給線と電気的に接続されていることを特徴としている。

【0048】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第3のゲート信号線と、電流供給線と、第1乃至第5のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、

第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記第2のトランジスタの第1の電極および、前記容量手段の第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極および、前記第5のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第5のトランジスタの第2の電極および、前記発光素子の第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、

第2の電極は、前記電流供給線と電気的に接続されていることを特徴としている。

【0049】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第5のゲート信号線と、電流供給線と、第1乃至第6のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、

第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記電流供給線と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極および、前記第5のトランジスタのゲート電極と電気的に接続され、

50

前記第3のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、第2の電極は、前記発光素子の第1の電極と電気的に接続され、

前記第5のトランジスタの第2の電極は、前記電流供給線と電気的に接続され、

前記第6のトランジスタのゲート電極は、前記第5のゲート信号線と電気的に接続され、第1の電極は、前記第3のトランジスタの第1の電極もしくは、前記第3のトランジスタの第2の電極と電気的に接続されていることを特徴としている。

【0050】

10

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第4のゲート信号線と、電流供給線と、第1乃至第6のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記電流供給線と電気的に接続され、

20

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極および、前記第5のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第2の電極は、前記発光素子の第1の電極と電気的に接続され、

前記第5のトランジスタの第2の電極は、前記電流供給線と電気的に接続され、

前記第6のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、第1の電極は、前記第3のトランジスタの第1の電極もしくは、前記第3のトランジスタの第2の電極と電気的に接続されていることを特徴としている。

30

【0051】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第4のゲート信号線と、電流供給線と、第1乃至第6のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

40

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記第5のトランジスタの第1の電極および、前記第6のトランジスタの第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトランジスタのゲート電極と、前記第6のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第2の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、第2の電極は、前記発光素子の第1の電極と電気的に接続され、

50

前記第6のトランジスタの第2の電極は、前記電流供給線と電気的に接続されていることを特徴としている。

【0052】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第3のゲート信号線と、電流供給線と、第1乃至第6のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、

第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第

1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

10

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第5のトランジスタの第1の電極および、前記第6のトランジスタの

第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトランジスタのゲート電極と、前記第6のトランジスタのゲート電極と電気的に接続され、

20

前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの

第2の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、

第2の電極は、前記発光素子の第1の電極と電気的に接続され、

20

前記第6のトランジスタの第2の電極は、前記電流供給線と電気的に接続されていることを特徴としている。

【0053】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第4のゲート信号線と、電流供給線と、第1乃至第6のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、

第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第

1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

30

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第5のトランジスタの第1の電極および、前記第6のトランジスタの

第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトランジスタのゲート電極と、前記第6のトランジスタのゲート電極と電気的に接続され、

40

前記第3のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、

第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの

第2の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、

第2の電極は、前記発光素子の第1の電極と電気的に接続され、

40

前記第6のトランジスタの第2の電極は、前記電流供給線と電気的に接続されていることを特徴としている。

【0054】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第3のゲート信号線と、電流供給線と、第1乃至第6のトランジスタと、容量手段と、発光素子とを有し、

50

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、

第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第

1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第5のトランジスタの第1の電極および、前記第6のトランジスタの

第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトラン

ジスタのゲート電極と、前記第6のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの

第2の電極と電気的に接続され、 10

前記第4のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、

第2の電極は、前記発光素子の第1の電極と電気的に接続され、

前記第6のトランジスタの第2の電極は、前記電流供給線と電気的に接続されていること

を特徴としている。

#### 【0055】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第4のゲート信号線と、電流供給線と、第1乃至第6のトラン

ジスタと、容量手段と、発光素子とを有し、 20

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、

第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第

1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第5のトランジスタの第1の電極および、前記第6のトランジスタの

第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトラン

ジスタのゲート電極と、前記第6のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、

第2の電極は、前記第5のトランジスタの第2の電極および、前記発光素子の第1の電極

と電気的に接続され、 30

前記第4のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、

第1の電極は、前記第6のトランジスタの第2の電極と電気的に接続され、第2の電極は

、前記電流供給線と電気的に接続されていることを特徴としている。

#### 【0056】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第3のゲート信号線と、電流供給線と、第1乃至第6のトラン

ジスタと、容量手段と、発光素子とを有し、 40

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、

第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第

1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第5のトランジスタの第1の電極および、前記第6のトランジスタの

第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトラン

ジスタのゲート電極と、前記第6のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、 50

第2の電極は、前記第5のトランジスタの第2の電極および、前記発光素子の第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第1の電極は、前記第6のトランジスタの第2の電極と電気的に接続され、第2の電極は、前記電流供給線と電気的に接続されていることを特徴としている。

#### 【0057】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第4のゲート信号線と、電流供給線と、第1乃至第6のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトランジスタのゲート電極と、前記第6のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第2の電極は、前記第5のトランジスタの第2の電極および、前記発光素子の第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、第2の電極は、前記第6のトランジスタの第1の電極と電気的に接続され、

前記第6のトランジスタの第2の電極は、前記電流供給線と電気的に接続されていることを特徴としている。

#### 【0058】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第3のゲート信号線と、電流供給線と、第1乃至第6のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトランジスタのゲート電極と、前記第6のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記第5のトランジスタの第2の電極および、前記発光素子の第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第2の電極は、前記第6のトランジスタの第1の電極と電気的に接続され、

前記第6のトランジスタの第2の電極は、前記電流供給線と電気的に接続されていることを特徴としている。

#### 【0059】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

10

20

30

40

50

前記画素は、

ソース信号線と、第1乃至第5のゲート信号線と、電流供給線と、第1乃至第7のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記第5のトランジスタの第1の電極および、前記第6のトランジスタの第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトランジスタのゲート電極と、前記第6のトランジスタのゲート電極と電気的に接続され、10

前記第3のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第2の電極は、前記第5のトランジスタの第2の電極および、前記発光素子の第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、第1の電極は、前記第6のトランジスタの第2の電極と電気的に接続され、第2の電極は、前記電流供給線と電気的に接続され、

前記第7のトランジスタのゲート電極は、前記第5のゲート信号線と電気的に接続され、第1の電極は、前記第3のトランジスタの第1の電極もしくは、前記第3のトランジスタの第2の電極と電気的に接続されていることを特徴としている。20

#### 【0060】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第4のゲート信号線と、電流供給線と、第1乃至第7のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記第5のトランジスタの第1の電極および、前記第6のトランジスタの第1の電極と電気的に接続され、30

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトランジスタのゲート電極と、前記第6のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記第5のトランジスタの第2の電極および、前記発光素子の第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第1の電極は、前記第6のトランジスタの第2の電極と電気的に接続され、第2の電極は、前記電流供給線と電気的に接続され、40

前記第7のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、第1の電極は、前記第3のトランジスタの第1の電極もしくは、前記第3のトランジスタの第2の電極と電気的に接続されていることを特徴としている。

#### 【0061】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第5のゲート信号線と、電流供給線と、第1乃至第7のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、50

第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトランジスタのゲート電極と、前記第6のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、

第2の電極は、前記第5のトランジスタの第2の電極および、前記発光素子の第1の電極と電気的に接続され、

10

前記第4のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、

第2の電極は、前記第6のトランジスタの第1の電極と電気的に接続され、

前記第6のトランジスタの第2の電極は、前記電流供給線と電気的に接続され、

前記第7のトランジスタのゲート電極は、前記第5のゲート信号線と電気的に接続され、

第1の電極は、前記第3のトランジスタの第1の電極もしくは、前記第3のトランジスタの第2の電極と電気的に接続されていることを特徴としている。

#### 【0062】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

20

ソース信号線と、第1乃至第4のゲート信号線と、電流供給線と、第1乃至第7のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、

第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記容量手段の第1の電極および、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第1の電極と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトランジスタのゲート電極と、前記第6のトランジスタのゲート電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

第2の電極は、前記第5のトランジスタの第2の電極および、前記発光素子の第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、

第2の電極は、前記第6のトランジスタの第1の電極と電気的に接続され、

前記第6のトランジスタの第2の電極は、前記電流供給線と電気的に接続され、

前記第7のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、

第1の電極は、前記第3のトランジスタの第1の電極もしくは、前記第3のトランジスタの第2の電極と電気的に接続されていることを特徴としている。

30

#### 【0063】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第5のゲート信号線と、電流供給線と、第1乃至第7のトランジスタと、容量手段と、発光素子とを有し、

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、

第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記第2のトランジスタの第1の電極と、前記容量手段の第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、

40

50

第2の電極は、前記電流供給線と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトランジスタのゲート電極と、前記第6のトランジスタのゲート電極および第2の電極と電気的に接続され、

前記第3のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第4のゲート信号線と電気的に接続され、第2の電極は、前記発光素子の第1の電極と電気的に接続され、

前記第5のトランジスタの第2の電極は、前記電流供給線と電気的に接続され、 10

前記第7のトランジスタは、前記第1のトランジスタの第2の電極と前記第6のトランジスタの第1の電極との間、前記第3のトランジスタの第1の電極と第6のトランジスタの第2の電極との間、もしくは、前記第3のトランジスタの第1の電極と前記第6のトランジスタのゲート電極との間のいずれかに設けられ、そのゲート電極は、前記第5のゲート信号線と電気的に接続されていることを特徴としている。

#### 【0064】

本発明の発光装置は、

発光素子が備えられた画素を有する発光装置であって、

前記画素は、

ソース信号線と、第1乃至第4のゲート信号線と、電流供給線と、第1乃至第7のトランジスタと、容量手段と、発光素子とを有し、 20

前記第1のトランジスタのゲート電極は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気的に接続され、第2の電極は、前記第2のトランジスタの第1の電極と、前記第6のトランジスタの第1の電極と、前記容量手段の第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記電流供給線と電気的に接続され、

前記容量手段の第2の電極は、前記第3のトランジスタの第1の電極と、前記第5のトランジスタのゲート電極と、前記第6のトランジスタのゲート電極および第2の電極と電気的に接続され、 30

前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記第4のトランジスタの第1の電極および、前記第5のトランジスタの第1の電極と電気的に接続され、

前記第4のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第2の電極は、前記発光素子の第1の電極と電気的に接続され、

前記第5のトランジスタの第2の電極は、前記電流供給線と電気的に接続され、

前記第7のトランジスタは、前記第1のトランジスタの第2の電極と前記第6のトランジスタの第1の電極との間、前記第3のトランジスタの第1の電極と第6のトランジスタの第2の電極との間、もしくは、前記第3のトランジスタの第1の電極と前記第6のトランジスタのゲート電極との間のいずれかに設けられ、そのゲート電極は、前記第4のゲート信号線と電気的に接続されていることを特徴としている。 40

#### 【0065】

本発明の発光装置においては、

前記第2のトランジスタと、前記第3のトランジスタとは同一極性であっても良い。

#### 【0066】

本発明の発光装置においては、

前記第5のトランジスタのゲート長を $L_1$ 、チャネル幅を $W_1$ とし、前記第6のトランジスタのゲート長を $L_2$ 、チャネル幅を $W_2$ としたとき、

$$(W_1 / L_1) > (W_2 / L_2)$$

が成立するものを含んでいる。 50

**【0067】**

本発明の発光装置においては、

前記第5のトランジスタのゲート長を $L_1$ 、チャネル幅を $W_1$ とし、前記第6のトランジス

タのゲート長を $L_2$ 、チャネル幅を $W_2$ としたとき、

$(W_1 / L_1) < (W_2 / L_2)$

が成立するものを含んでいる。

**【0068】**

本発明の発光装置は、

前記第6のトランジスタの第2の電極は、前記電流供給線と互いに電位差を有する電源線もしくは、当該画素を制御する前記ゲート信号線を除くいずれか1本のゲート信号線と電気的に接続されていても良い。

10

**【0069】**

本発明の発光装置は、

前記第7のトランジスタの第2の電極は、前記電流供給線と互いに電位差を有する電源線もしくは、当該画素を制御する前記ゲート信号線を除くいずれか1本のゲート信号線と電気的に接続されていても良い。

**【0070】**

本発明の発光装置は、

前記発光素子の第2の電極は、前記電流供給線と互いに電位差を有する電源線と電気的に接続されていても良い。

20

**【0071】**

本発明の発光装置においては、

前記画素は、保持容量手段を有し、

前記保持容量手段の第1の電極は、前記第1のトランジスタの第2の電極と電気的に接続され、第2の電極には一定電位が与えられ、前期ソース信号線より入力される映像信号を保持することを特徴としている。

**【0072】**

本発明の発光装置の駆動方法は、

発光素子が備えられた画素を有する発光装置の駆動方法であって、

前記画素は、ソース信号線と、電流供給線と、発光素子に所望の電流を供給するトランジスタと、発光素子と、容量手段とを少なくとも有し、

30

前記容量手段に電荷を蓄積する第1のステップと、

前記容量手段の両電極間の電圧を、前記トランジスタのしきい値電圧に等しい電圧に収束する第2のステップと、

前記ソース信号線より映像信号を入力する第3のステップと、

前記映像信号の電位に、前記しきい値電圧を加えて、前記トランジスタのゲート電極に印加し、前記トランジスタを介して、電流を前記発光素子に供給し、発光する第4のステップとを有し、

40

少なくとも前記第3のステップにおいて、前記容量手段の両電極間の電圧が一定であり、少なくとも前記第1および第2のステップにおいて、前記第1のトランジスタは非導通状態となることを特徴としている。

**【0073】**

本発明の発光装置の駆動方法は、

発光素子が備えられた画素を有する発光装置の駆動方法であって、

前記画素は、

電流供給線と、第1乃至第3のトランジスタと、容量手段とを少なくとも有し、

前記第1のトランジスタのゲート電極は、前記第2のトランジスタの第1の電極および、前記容量手段の第1の電極と電気的に接続され、第1の電極は、前記電流供給線と電気的に接続され、第2の電極は、前記第2のトランジスタの第2の電極および、前記第3のトランジスタの第1の電極と電気的に接続され、

50

前記第2のトランジスタのゲート電極より、第1の信号が入力され、

前記第3のトランジスタのゲート電極より、第2の信号が入力され、

前記容量手段の第2の電極は、前記第4のトランジスタの第1の電極と電気的に接続され

、かつ前記容量手段の第2の電極より、映像信号が入力され、

前記第4のトランジスタのゲート電極より、第3の信号が入力され、第2の電極は、前記

電流供給線と電気的に接続され、

前記第1乃至第3の信号を入力して前記第2乃至第4のトランジスタを導通することによ

って、前記容量手段に電荷を蓄積する第1のステップと、

前記第3のトランジスタを非導通とし、かつ前記第1、第3の信号を入力して前記第2、

第4のトランジスタを導通することによって、前記容量手段に保持される電圧を、前記第

1のトランジスタのしきい値電圧と等しい値に収束する第2のステップと、

前記第2乃至第4のトランジスタを非導通とし、前記容量手段の第2の電極より、前記映

像信号が入力される第3のステップと、

前記第2、第4のトランジスタを非導通とし、かつ前記第2の信号を入力して前記第3の

トランジスタを導通することによって、前記第1、第3のトランジスタのソース・ドレイ

イン間を電流が流れる第4のステップとを有し、

少なくとも第3のステップにおいて、前記容量手段の両電極間の電圧が一定であることを

特徴としている。

## 【0074】

## 【発明の実施の形態】

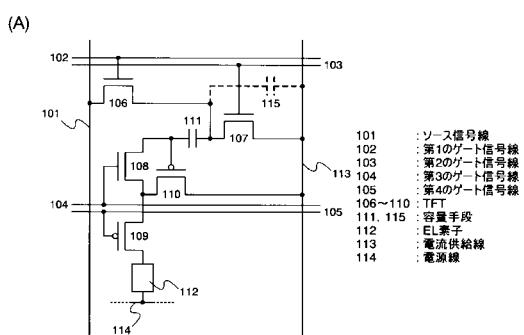

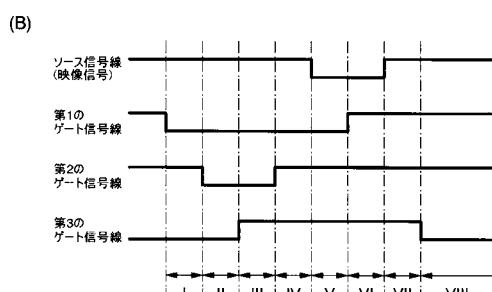

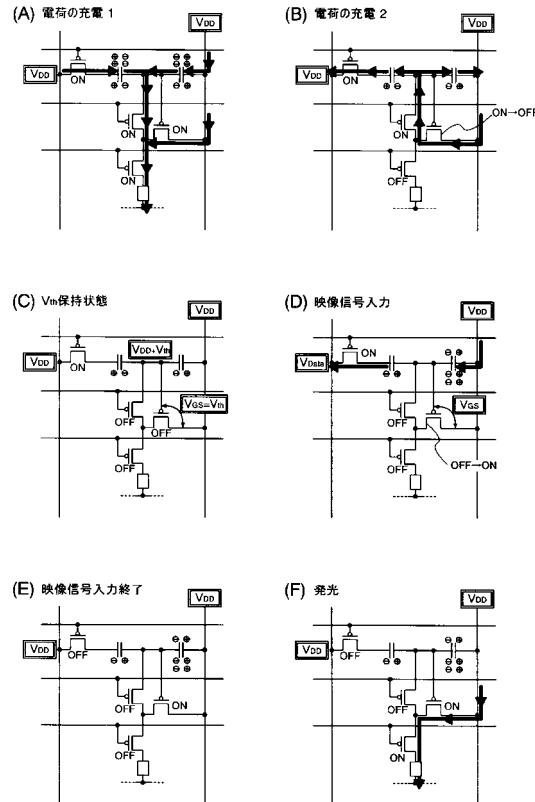

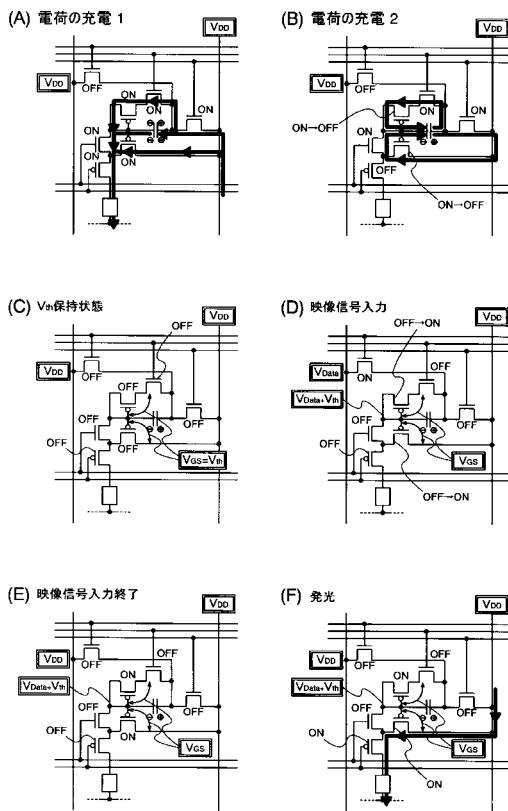

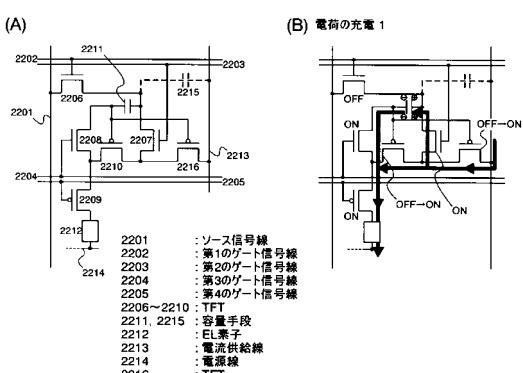

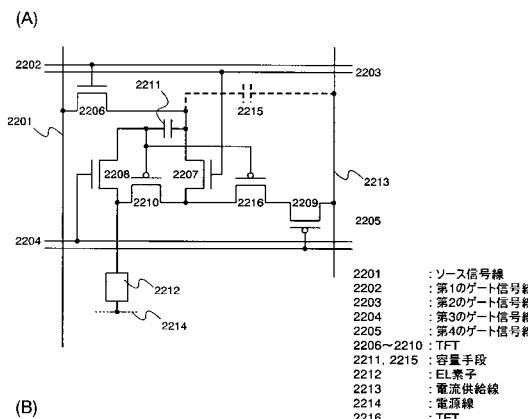

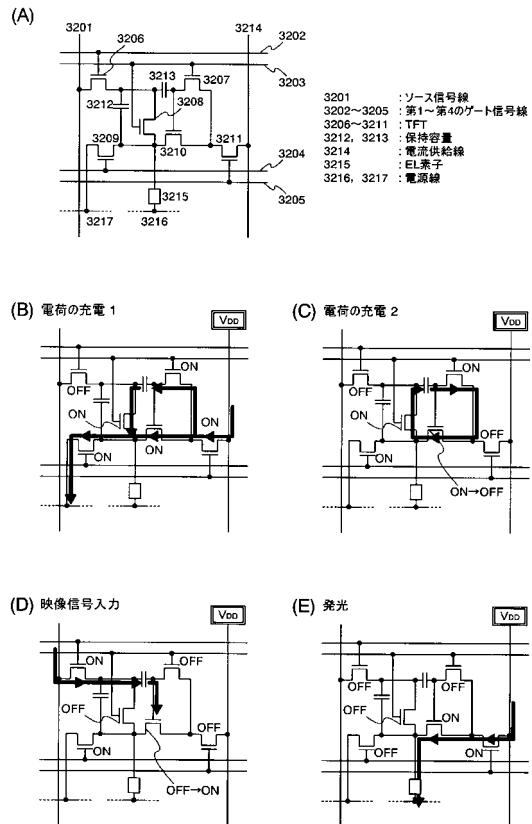

図1(A)に、本発明の一実施形態を示す。ソース信号線101、第1～第4のゲート信

号線102～105、第1～第5のTFT106～110、第1および第2の容量手段1

11、115、EL素子112、電流供給線113、電源線114を有する。

## 【0075】

第1のTFT106のゲート電極は、第1のゲート信号線102に接続され、第1の電

極は、ソース信号線101に接続され、第2の電極は、第2のTFT107の第1の電極

に接続されている。第2のTFT107のゲート電極は、第2のゲート信号線103に接

続され、第2の電極は、電流供給線113に接続されている。第1の容量手段111の第

1の電極は、第2のTFT107の第1の電極に接続され、第2の電極は、第3のTFT

108の第1の電極に接続されている。第3のTFT108のゲート電極は、第3のゲー

ト信号線104に接続され、第2の電極は、第4のTFT109の第1の電極に接続され

ている。第4のTFT109のゲート電極は、第4のゲート信号線105に接続され、第

2の電極は、EL素子112の第1の電極に接続されている。第5のTFT110のゲー

ト電極は、第3のTFT108の第1の電極、および第1の容量手段111の第2の電極

に接続され、第1の電極は、第3のTFT108の第2の電極、および第4のTFT10

9の第1の電極に接続され、第2の電極は、電流供給線113に接続されている。第2の

容量手段115は、第1のTFT106の第2の電極と、電流供給線113との間に配置

され、ソース信号線101より入力される映像信号の電位を保持する。第2の容量手段1

15に関しては、特に設けなくとも動作は可能である。EL素子112の第2の電極には

、電源線114によって一定電位が与えられ、電流供給線113とは互いに電位差を有す

る。

## 【0076】

図1(B)および図2(A)～(F)を用いて、動作について説明する。図1(B)は、ソース信

号線101、第1～第4のゲート信号線102～105に入力される映像信号およびパル

スのタイミングを示しており、図2に示す各動作にあわせて、I～VIの区間に分割して

いる。また、図1(A)に示した構成においては、第1～第3のTFT106～108はNチ

ャネル型、第4のTFT109および第5のTFT110はPチャネル型としている。図

5(A)に示したように、全てPチャネル型のTFTを用いて構成することも可能であるが

、第1のTFT106～第3のTFT108は、ここではNチャネル型としている。Nチ

ャネル型TFTにおいては、ゲート電極にHレベルが入力されてONし、Lレベルが入力

10

20

30

40

50

されてOFFするものとする。Pチャネル型TFTにおいては、ゲート電極にLレベルが入力されてONし、Hレベルが入力されてOFFするものとする。

#### 【0077】

なお、簡単のため、第2の容量手段115は、図2(A)～(F)においては省略する。

#### 【0078】

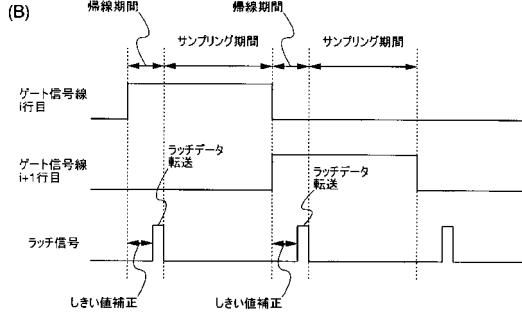

まず、第2、第3のゲート信号線103、104がHレベル、第4のゲート信号線105がLレベルとなり、TFT107～109がONする(区間I)。これにより、図2(A)で示すような電流が生じ、容量手段111が充電される。容量手段111が保持する電圧が、TFT110のしきい値( $V_{th}$ )を上回ったところで、TFT110がONする。

#### 【0079】

その後、第4のゲート信号線105がHレベルとなり、TFT109がOFFする(区間I)。これにより、電流供給線113～EL素子112間の電流パスが閉じるため、電流が停止する。一方、図2に示すように、容量手段111に貯まっていた電荷が再び移動を始める。容量手段111の両電極間の電圧はすなわち、TFT110のゲート・ソース間電圧であるから、この電圧が $V_{th}$ に等しくなったところでTFT110はOFFし、電荷の移動も終了する(図2(B))。

#### 【0080】

その後、第2、第3のゲート信号線103、104がいずれもLレベルとなり、TFT107、108がOFFする。よって、容量手段111には、図2(C)に示すように、TFT110のしきい値電圧が保持される。

#### 【0081】

続いて、第1のゲート信号線102がHレベルとなり、TFT106がONする(区間IV)。ソース信号線101には、映像信号が出力されて、その電位は $V_{DD}$ から映像信号の電位 $V_{Data}$ (ここでは、TFT110がPチャネル型であるので、 $V_{DD} > V_{Data}$ とする。)となる。ここで、容量手段111においては、先程の $V_{th}$ がそのまま保持されているので、TFT110のゲート電極の電位は、ソース信号線101から入力される映像信号電位 $V_{Data}$ に、さらにしきい値 $V_{th}$ を加えた電位となる。よってTFT110がONする(図2(D))。

#### 【0082】

やがて映像信号の書き込みが完了すると、第1のゲート信号線102がLレベルとなり、TFT106がOFFする(区間V)。その後、ソース信号線への映像信号の出力も終了し、その電位は $V_{DD}$ に戻る(図2(E))。

#### 【0083】

続いて、第4のゲート信号線105がLレベルとなり、TFT109がONする(区間VI)。TFT110は既にONしているので、電流供給線113からEL素子112に電流が流れることによってEL素子112が発光する(図2(F))。このとき、EL素子112に流れる電流値は、TFT110のゲート・ソース間電圧に従ったものであり、このときのTFT110のゲート・ソース間電圧は、( $V_{DD} - (V_{Data} + V_{th})$ )である。ここで仮に、TFT110のしきい値 $V_{th}$ が各画素間でばらついたとしても、そのばらつきに応じた電圧が、各画素の容量手段111に保持される。よって、EL素子112の輝度は、しきい値のばらつきに影響されることがない。

#### 【0084】

以上のような動作によって、映像信号の書き込みから発光を行う。本発明においては、容量手段111の容量結合によって、映像信号の電位を、TFT110のしきい値分だけオフセットすることが出来る。よって、前述のように他の素子の特性ばらつき等に影響されることなく、正確にしきい値補正を行うことが可能である。

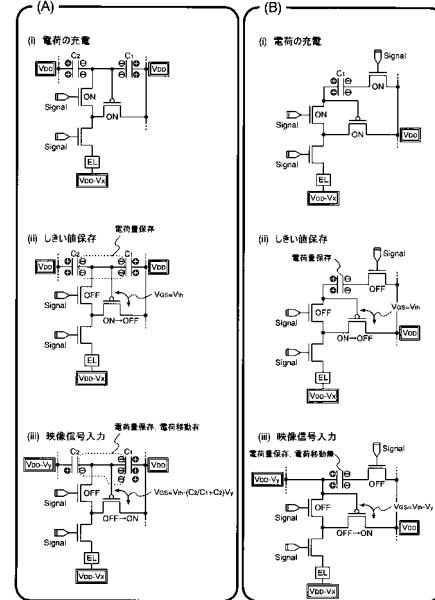

#### 【0085】

図26(A)(B)に、従来例と本発明におけるしきい値補正の動作を簡単に説明する図を示す。図26(A)においては、映像信号入力の際、2つの容量手段C<sub>1</sub>、C<sub>2</sub>において電荷が保存され、かつ電荷の移動が生ずるため、EL素子に電流を供給するTFTのゲート・

10

20

40

50

ソース間電圧  $V_{GS}$  は、図 26(A)の(iii)に示すように、容量値  $C_1$ 、 $C_2$  を項に含む式で表される。よって、容量値  $C_1$ 、 $C_2$  にばらつきが生じた場合、TFT のゲート・ソース間電圧がばらつくことになる。

#### 【0086】

これに対して本発明の場合、容量手段において電荷が保存されるが、映像信号入力の際は、図 26(B)の(iii)に示すように、電荷の移動が生じない。つまり、映像信号の電位にしきい値電圧を上乗せした電位がそのまま TFT のゲート電極に印加されるため、より TFT のゲート・ソース間電圧をばらつきにくくすることが出来る。

#### 【0087】

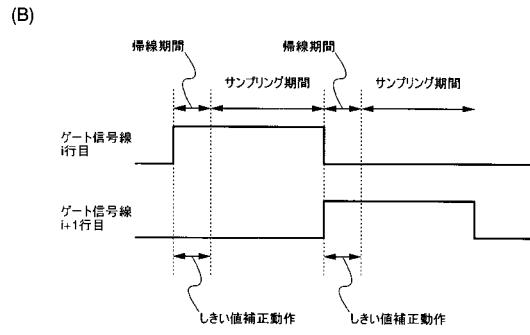

また、画素の選択タイミング、すなわちある画素に映像信号が書き込まれるタイミングは、ソース信号線 101 への信号入力タイミングおよび第 1 のゲート信号線 102 の選択タイミングによる。すなわち、ある画素における初期化や、容量手段への電荷の充電といった動作を、映像信号の書き込みタイミングとは独立して行うことが出来る。これらの動作は複数行が並行して行われていても良いので、異なる行において、第 2 ~ 第 4 のゲート信号線の選択タイミング等は重複しても良い。そのため、図 1(B)において 10 示した期間、つまりしきい値電圧を保存する動作を行う期間を長くとることが出来る。

#### 【0088】

また、図 1(A)において、TFT 109 の配置を変更したものとして、図 20(A)のような構成としても良い。図に付した番号は図 1(A)と同様であり、TFT 109 を、TFT 110 の第 1 の電極と EL 素子 112 の間から、TFT 110 の第 2 の電極および TFT 107 の第 2 の電極と、電流供給線 113 の間に移動したものである。

#### 【0089】

なお、本実施形態において示した構成における TFT の極性はあくまでも一例であり、その極性を限定するものではないことを付記する。

#### 【0090】

図 1 に示した本発明の実施形態においては、1 画素あたり 4 本のゲート信号線を用いて制御しているが、第 2、第 3 のゲート信号線 103、104 によって制御される TFT 107、108 の動作タイミングは、図 1(B)に示すように同時であるので、TFT 107、108 の極性が同じであるならば、これらを同一のゲート信号線によって制御するなどして、ゲート信号線の本数を減らすことも出来る。この場合、開口率を高くすることが出来る。

#### 【0091】

##### 【実施例】

以下に、本発明の実施例について記載する。

#### 【0092】

##### 【実施例 1】

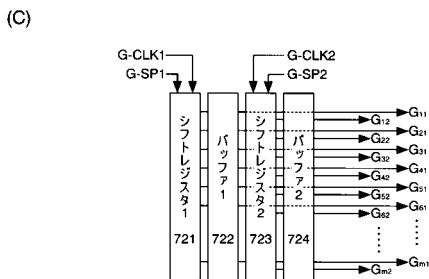

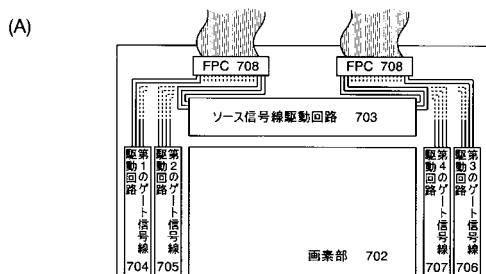

本実施例においては、映像信号にアナログ映像信号を用いて表示を行う発光装置の構成について説明する。図 7(A)に、発光装置の構成例を示す。基板 701 上に、複数の画素がマトリクス状に配置された画素部 702 を有し、画素部周辺には、ソース信号線駆動回路 703 および、第 1 ~ 第 4 のゲート信号線駆動回路 704 ~ 707 を有している。図 7(A)においては、4 組のゲート信号線駆動回路を用い、図 1 に示した画素における第 1 ~ 第 4 のゲート信号線をそれぞれ制御するものである。

#### 【0093】

ソース信号線駆動回路 703、第 1 ~ 第 3 のゲート信号線駆動回路 704 ~ 706 に入力される信号は、フレキシブルプリント基板(Flexible Print Circuit: FPC) 708 を介して外部より供給される。

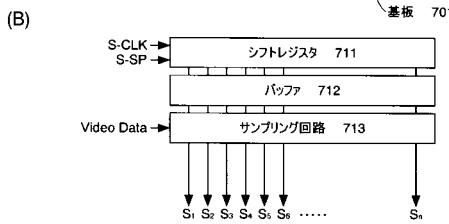

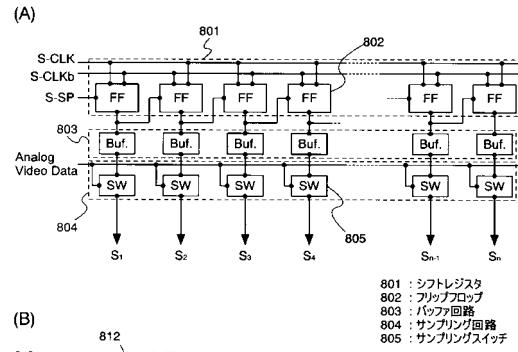

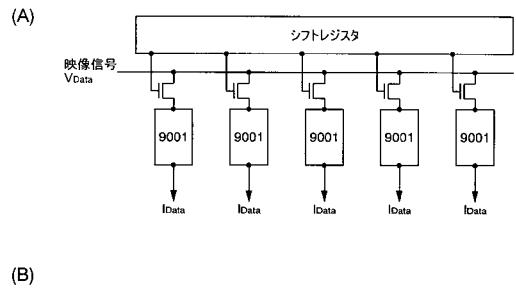

#### 【0094】

図 7(B)に、ソース信号線駆動回路の構成例を示す。これは、映像信号にアナログ映像信号を用いて表示を行うためのソース信号線駆動回路であり、シフトレジスタ 711、バッ

10

20

30

40

50

ファ712、サンプリング回路713を有している。特に図示していないが、必要に応じてレベルシフタ等を追加しても良い。

#### 【0095】

ソース信号線駆動回路の動作について説明する。図8(A)に、より詳細な構成を示したので、そちらを参照する。

#### 【0096】

シフトレジスタ801は、フリップフロップ回路(FF)802等を複数段用いてなり、クロック信号(S-CLK)、クロック反転信号(S-CLKb)、スタートパルス(S-SP)が入力される。これらの信号のタイミングに従って、順次サンプリングパルスが出力される。

10

#### 【0097】

シフトレジスタ801より出力されたサンプリングパルスは、バッファ803等を通じて増幅された後、サンプリング回路へと入力される。サンプリング回路804は、サンプリングスイッチ(SW)805を複数段用いてなり、サンプリングパルスが入力されるタイミングに従って、ある列で映像信号のサンプリングを行う。具体的には、サンプリングスイッチにサンプリングパルスが入力されると、サンプリングスイッチ805がONし、そのときに映像信号が有する電位が、サンプリングスイッチを介して各々のソース信号線へと出力される。

#### 【0098】

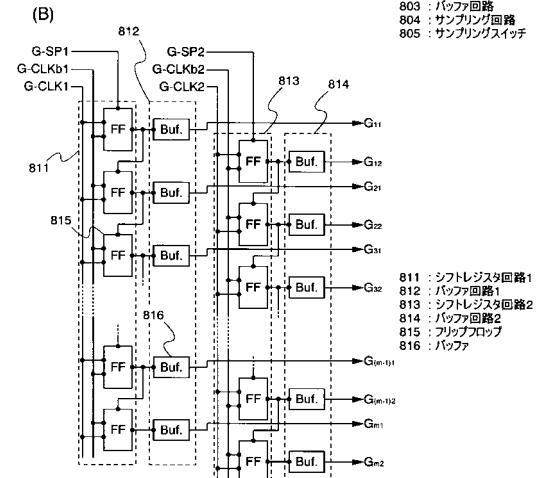

続いて、ゲート信号線駆動回路の動作について説明する。図7(C)に示した、第1、第2のゲート信号線駆動回路704、705、および第3、第4のゲート信号線駆動回路706、707についての詳細な構成を図8(B)に示した。第1のゲート信号線駆動回路は、シフトレジスタ回路811、バッファ812を有し、クロック信号(G-CLK1)、クロック反転信号(G-CLKb1)、スタートパルス(G-SP1)に従って駆動される。第2のゲート信号線駆動回路は、シフトレジスタ回路813、バッファ814を有し、クロック信号(G-CLK2)、クロック反転信号(G-CLKb2)、スタートパルス(G-SP2)に従って駆動される。

20

#### 【0099】

シフトレジスタ～バッファの動作については、ソース信号線駆動回路の場合と同様である。バッファによって増幅された選択パルスは、それぞれのゲート信号線を選択する。第1のゲート信号線駆動回路によって、第1のゲート信号線G<sub>11</sub>、G<sub>21</sub>、…、G<sub>m1</sub>が順次選択され、第2のゲート信号線駆動回路によって、第2のゲート信号線G<sub>12</sub>、G<sub>22</sub>、…、G<sub>m2</sub>が順次選択される。図示していないが、第3のゲート信号線駆動回路についても第1、第2のゲート信号線駆動回路と同様であり、第3のゲート信号線G<sub>13</sub>、G<sub>23</sub>、…、G<sub>m3</sub>が順次選択される。選択された行において、実施形態にて説明した手順により、画素に映像信号が書き込まれて発光する。

30

#### 【0100】

なお、ここではシフトレジスタの一例として、フリップフロップを複数段用いてなるものを図示したが、デコーダ等によって、信号線を選択出来るような構成としても良い。

#### 【0101】

40

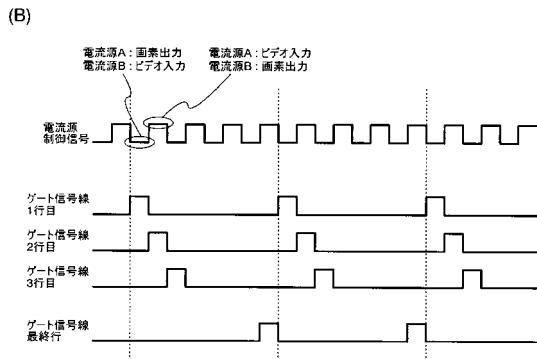

#### [実施例2]

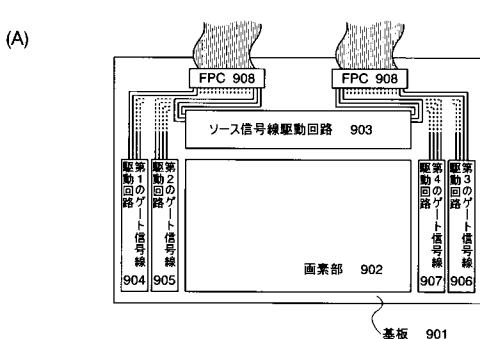

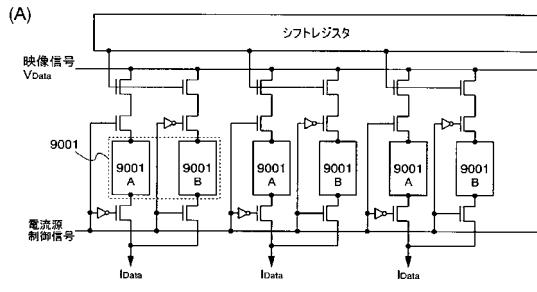

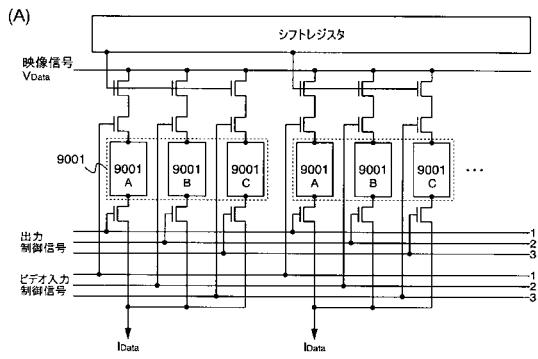

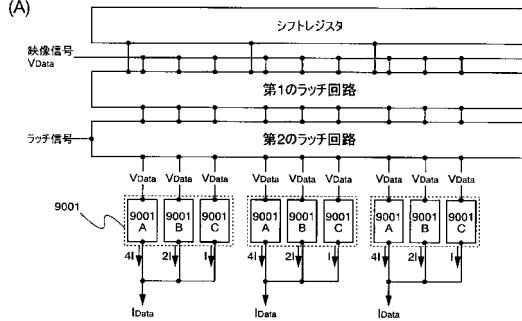

本実施例においては、映像信号にデジタル映像信号を用いて表示を行う発光装置の構成について説明する。図9(A)に、発光装置の構成例を示す。基板901上に、複数の画素がマトリクス状に配置された画素部902を有し、画素部周辺には、ソース信号線駆動回路903および、第1～第4のゲート信号線駆動回路904～907を有している。図9(A)においては、4組のゲート信号線駆動回路を用い、図1に示した画素における第1～第4のゲート信号線をそれぞれ制御するものである。

#### 【0102】

ソース信号線駆動回路903、第1～第4のゲート信号線駆動回路904～907に入力される信号は、フレキシブルプリント基板(Flexible Print Circuit: FPC)908を介

50

して外部より供給される。

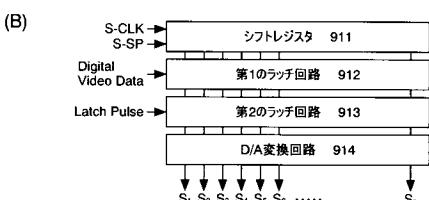

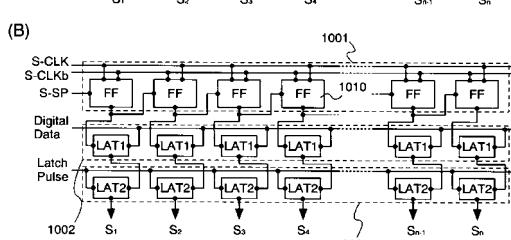

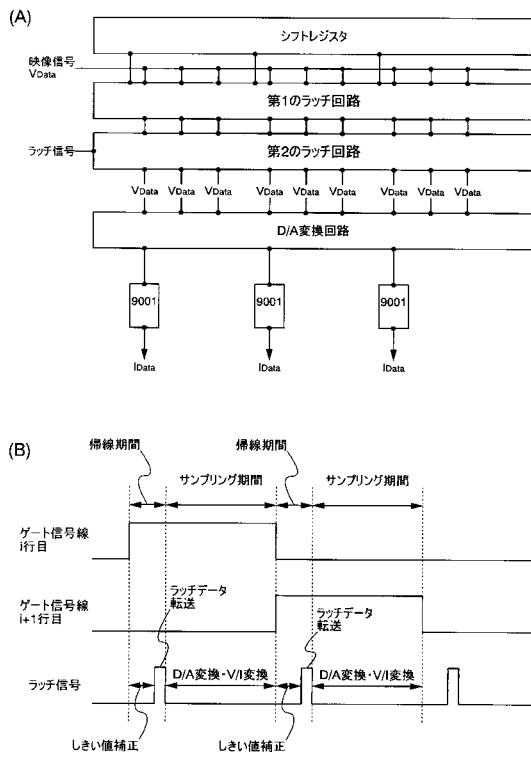

**【0103】**

図9(B)に、ソース信号線駆動回路の構成例を示す。これは、映像信号にデジタル映像信号を用いて表示を行うためのソース信号線駆動回路であり、シフトレジスタ911、第1のラッチ回路912、第2のラッチ回路913、D/A変換回路914を有している。特に図示していないが、必要に応じてレベルシフタ等を追加しても良い。

**【0104】**

第1～第4のゲート信号線駆動回路904～907については、実施例1にて示したものと同様で良いので、ここでは図示および説明を省略する。

**【0105】**

ソース信号線駆動回路の動作について説明する。図10(A)に、より詳細な構成を示したので、そちらを参照する。

**【0106】**

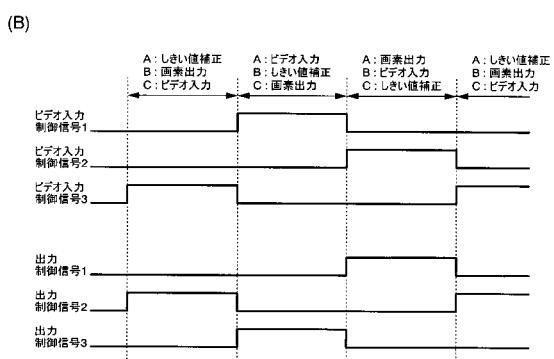

シフトレジスタ1001は、フリップフロップ回路(FF)1010等を複数段用いてなり、クロック信号(S-CLK)、クロック反転信号(S-CLKb)、スタートパルス(S-SP)が入力される。これらの信号のタイミングに従って、順次サンプリングパルスが出力される。

**【0107】**

シフトレジスタ1001より出力されたサンプリングパルスは、第1のラッチ回路1002に入力される。第1のラッチ回路1002には、デジタル映像信号が入力されており、サンプリングパルスが入力されるタイミングに従って、各段でデジタル映像信号を保持していく。ここでは、デジタル映像信号は3ビット入力されており、各ビットの映像信号を、それぞれの第1のラッチ回路において保持する。1つのサンプリングパルスによって、ここでは3つの第1のラッチ回路が並行して動作する。

**【0108】**

第1のラッチ回路1002において、最終段までデジタル映像信号の保持が完了すると、水平帰線期間中に、第2のラッチ回路1003にラッチパルス(Latch Pulse)が入力され、第1のラッチ回路1002に保持されていたデジタル映像信号は、一齊に第2のラッチ回路1003に転送される。その後、第2のラッチ回路1003に保持されたデジタル映像信号は、1行分が同時に、D/A変換回路1004へと入力される。

**【0109】**

第2のラッチ回路1003に保持されたデジタル映像信号がD/A変換回路1004に入力されている間、シフトレジスタ1001においては再びサンプリングパルスが出力される。以後、この動作を繰り返し、1フレーム分の映像信号の処理を行う。

**【0110】**

D/A変換回路1004においては、入力されるデジタル映像信号をデジタル-アナログ変換し、アナログ電圧を有する映像信号としてソース信号線に出力する。

**【0111】**

前記の動作が、1水平期間内に、全段にわたって同時に行われる。よって、全てのソース信号線に映像信号が出力される。

**【0112】**

なお、実施例1においても述べたとおり、シフトレジスタの代わりにデコーダ等を用いて、信号線を選択出来るような構成としても良い。

**【0113】**

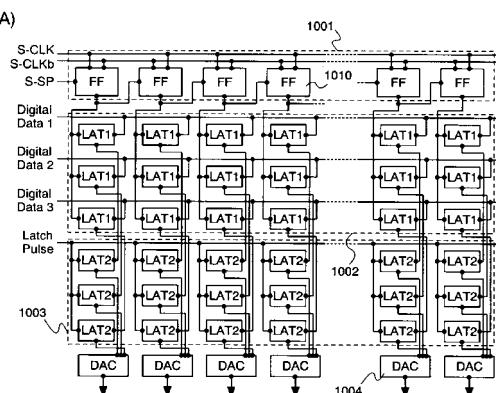

[実施例3]

実施例2においては、デジタル映像信号はD/A変換回路によってデジタル-アナログ変換を受け、画素に書き込まれるが、本発明の発光装置は、時間階調方式によって階調表現を行うことも出来る。この場合には、図10(B)に示すように、D/A変換回路を必要とせず、階調表現は、EL素子の発光時間の長短によって制御されるので、各ビットの映像信号を並列処理する必要がないため、第1および第2のラッチ回路も1ビット分で良い。

10

20

30

40

50

このとき、デジタル映像信号は、各ビットが直列に入力され、順次ラッチ回路に保持され、画素に書き込まれる。

#### 【0114】

また、時間階調方式によって階調表現を行う場合、図1において、第4のTFT109を消去用TFTとして用いることが出来る。この場合、第4のTFT109は、消去期間中を通じてOFFしている必要があり、そのためには、第4のゲート信号線105は、消去用ゲート信号線駆動回路を用いて制御する。通常、ゲート信号線を選択するゲート信号線駆動回路の場合、1水平期間内に1つもしくは複数のパルスを出力するが、消去用ゲート信号線駆動回路の場合、消去期間中は継続して第4のTFT109をOFFさせなければならぬため、独立した駆動回路を用いる。

10

#### 【0115】

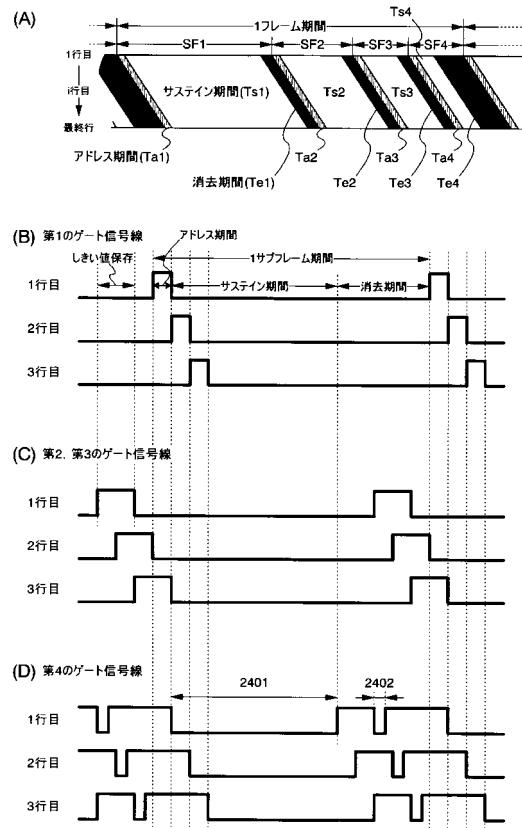

図24に、時間階調方式による一例を示す。図24(A)は、4ビットの階調を得るためにタイミングチャートであり、各ビットのアドレス(書き込み)期間Ta1～Ta4と、サステイン(発光)期間Ts1～Ts4と、消去期間Te1～Te4とを有する。

#### 【0116】

アドレス(書き込み)期間は、1画面分の画素に映像信号を入力する動作に要する期間であるから、各ビットで等しい長さである。これに対し、サステイン(発光)期間は、その長さを $1 : 2 : 4 : \dots : 2^{(n-1)}$ と、2のべき乗の比とし、発光する期間の合計によって、階調を表現する。図24(A)の例では、4ビットであるので、サステイン(発光)期間の長さは、1 : 2 : 4 : 8となっている。

20

#### 【0117】

消去期間については、本来は、サステイン(発光)期間が短い場合に、アドレス(書き込み)期間が重複し、異なるゲート信号線が同時に選択されることのないように設けるものとしている。

#### 【0118】

図24(B)は、図1における第1のゲート信号線に入力されるパルスのタイミングを示したものである。このゲート信号線が1行目～最終行まで選択される期間が、アドレス(書き込み)期間にあたる。

#### 【0119】

図24(C)は、図1における第2、第3のゲート信号線に入力されるパルスのタイミングを示したものである。ここでは、第2、第3のゲート信号線を共通として駆動している。ここでHレベルとなっている期間が、しきい値保存を行う期間であり、各サブフレーム期間において、アドレス期間の前に行う。

30

#### 【0120】

図24(D)は、図1における第4のゲート信号線に入力されるパルスのタイミングを示したものである。2401で示される期間が発光期間である。つまり、消去期間は、第4のゲート信号線にHレベルを入力することによって設けている。2402で示される期間は、しきい値保存動作を行う際、図2(A)に記載のように、この期間にTFT109がONする必要があるためにLレベルが入力される。

#### 【0121】

40

図24においては、しきい値保存は、消去期間中に行うように記載しているが、この期間は発光していても構わない。つまり、上位ビットにおいては必ずしも消去期間を設けず、サステイン(発光)期間中にしきい値保存を行っても良い。

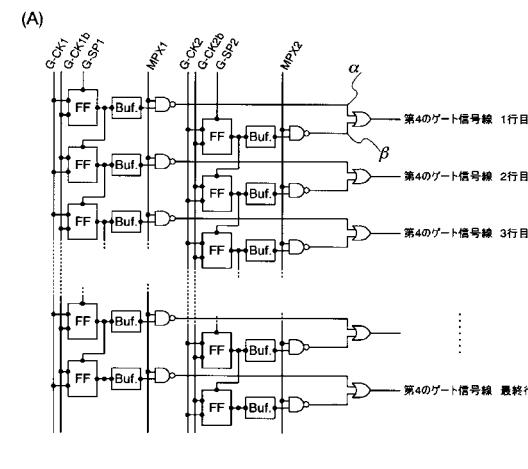

#### 【0122】

図24(B)、(C)のようなパルスは、従来のゲート信号線駆動回路の構成によって容易に作ることが出来るが、図24(D)のようなパルスはやや工夫が必要となる。本実施例では、図25(A)に示すように、ゲート信号線駆動回路を2相構成とし、図25(B)に示すように、 $\text{A}_1, \text{B}_1, \text{A}_2, \text{B}_2$ のノードにそれぞれ現れるパルスをOR回路を用いて組み合わせ、所望のパルスを得ている。

#### 【0123】

50

[実施例 4]

ここまで紹介した発光装置においては、第1～第4のゲート信号線を制御するために、第1～第4のゲート信号線駆動回路をそれぞれ動作させることによって行っていた。このような構成とするメリットとしては、各ゲート信号線の選択タイミングを独立して変更させることが出来るため、様々な駆動方法に対してある程度の対応が可能な点がある。反面、基板内で駆動回路の占有面積が増大するため、表示領域の周辺が大きくなる、すなわち狭額縁化が困難となるデメリットがある。

【0124】

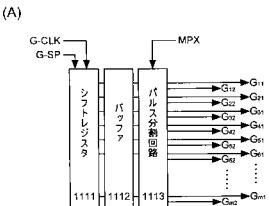

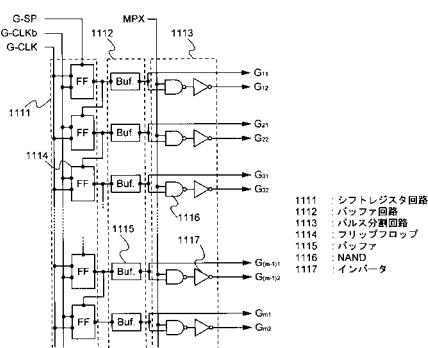

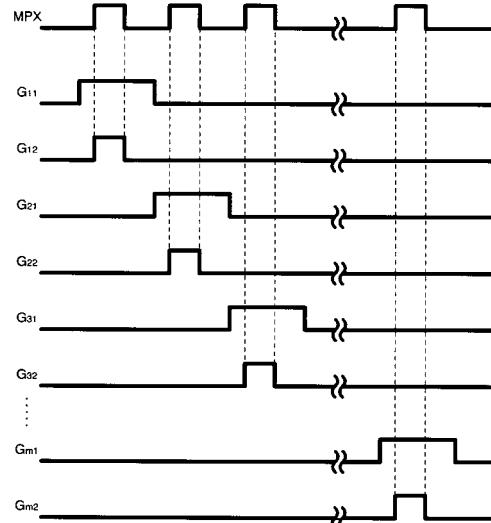

図11(A)は、そのような問題を解決するための一構成例を示している。図11(A)において、シフトレジスタ1111、バッファ1112を有する点は他の実施例にて用いたゲート信号線駆動回路と同様であるが、本実施例においては、バッファの後にパルス分割回路1113を追加した。詳細な構成を図11(B)に示す。

10

【0125】

パルス分割回路1113は、NAND1116、インバータ1117を複数用いてなる。バッファ出力と、外部入力される分割信号(MPX)とのNANDをとることにより、1つのゲート信号線駆動回路によって、異なるパルスで制御される2つのゲート信号線を制御することが出来る。図11の場合、第1のゲート信号線と、第2のゲート信号線とを、1つのゲート信号線駆動回路によって制御する。

【0126】

分割信号(MPX)と、それぞれのゲート信号線の選択タイミングを図12に示した。<sub>11</sub>、

$G_{21}$ 、 $\dots$ 、 $G_{m1}$ は、バッファ出力がそのまま選択パルスとして用いられる。一方、バッファ出力がHレベル、さらに分割信号がHレベルのとき、NAND出力はLレベルとなり、さらにインバータを介してHレベルが出力され、こちらのパルスによって、<sub>12</sub>、 $G_{22}$ 、 $\dots$ 、 $G_{m2}$ が選択される。

20

【0127】

[実施例 5]

本発明において、発光時にEL素子に電流を供給するためのTFT(図1(A)におけるTFT106)は、EL素子の劣化によって輝度がばらつくのを抑えるため、飽和領域で動作させるのが望ましい。このとき、飽和領域における電流が、TFT106のソース・ドレイン間電圧が変化してもほぼ一定となるようにするため、ゲート長Lを大きくしている。<sub>30</sub>。

【0128】

このとき、容量手段においてしきい値を保持する際の動作は、一度容量手段にはTFTのしきい値を上回る電圧を与え、その状態からしきい値電圧に収束させているが、TFTのゲート長Lが大きい場合、ゲート容量等によってこの動作に時間を要する。そこで本実施例においては、このような場合における高速動作を実現する構成について説明する。

【0129】

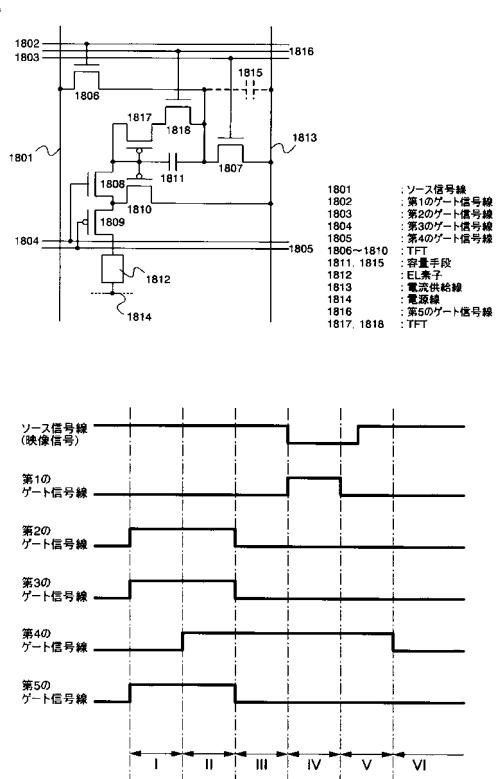

図18(A)に、画素の構成を示す。図1(A)にて示した画素に、TFT1817、1818、およびTFT1818を制御するための第5のゲート信号線1816が追加されている。また、図18(A)に点線で示すように、容量手段1815を、TFT1806の第2の電極と、電流供給線1813との間に設け、映像信号を保持するための容量として用いても良い。

40

【0130】

図18(B)および図19(A)～(F)を用いて、動作について説明する。図18(B)は、ソース信号線1801、第1～第5のゲート信号線1802～1805、1816に入力される映像信号およびパルスのタイミングを示しており、図19に示す各動作にあわせて、I～VIの区間に分割している。本実施例は、容量手段にしきい値電圧を保持するまでの動作を高速にするためのものであるので、映像信号のかきこみ、および発光動作については実施形態にて説明したものと同様である。従ってここでは、容量手段における電荷の充電および保持動作についてのみ説明する。

50

**【0131】**

まず、第2、第3、および第5のゲート信号線1803、1804、1816がHレベル、第4のゲート信号線1805がLレベルとなり、TFT1807、1808、1809、1818がONする(区間I)。これにより、図19(A)で示すような電流が生じ、容量手段1811が充電される。容量手段1811が保持する電圧が、TFT1810、1817のしきい値( $V_{th}$ )を上回ったところで、TFT1810、1817がONする(図19(A))。

**【0132】**

続いて、第4のゲート信号線1805がHレベルとなり、TFT1809がOFFする(区間II)。これにより、電流供給線1813-EL素子1812間の電流バスが閉じるために、電流が停止する。一方、図19(B)に示すように、容量手段1811に貯まっていた電荷が再び移動を始める。容量手段1811の両電極間の電圧はすなわち、TFT1810、1817のゲート・ソース間電圧であるから、この電圧が $V_{th}$ に等しくなったところでTFT1810、1817はOFFし、電荷の移動も終了する。

10

**【0133】**

容量手段1811において、しきい値の保存が完了すると、第2、第5のゲート信号線がLレベル、第3のゲート信号線がHレベルとなり、TFT1807、1808、1818がOFFする(区間III)。

**【0134】**

続いて、第1のゲート信号線1802がHレベルとなり、TFT1806がONする(区間IV)。ソース信号線1801には、映像信号が output されて、その電位は $V_{DD}$ から映像信号の電位 $V_{Data}$ (ここでは、TFT110がPチャネル型であるので、 $V_{DD} > V_{Data}$ とする。)となる。ここで、容量手段1811においては、先程の $V_{th}$ がそのまま保持されているので、TFT1810、1817のゲート電極の電位は、ソース信号線1801から入力される映像信号電位 $V_{Data}$ に、さらにしきい値 $V_{th}$ を加えた電位となる。よってTFT1810、1817がONする(図19(D))。

20

**【0135】**

やがて映像信号の書き込みが完了すると、第1のゲート信号線1802がLレベルとなり、TFT1806がOFFする(区間V)。その後、ソース信号線1801への映像信号の出力も終了し、その電位は $V_{DD}$ に戻る(図19(E))。

30

**【0136】**

続いて、第4のゲート信号線1805がLレベルとなり、TFT1809がONする(区間VI)。TFT1810は既にONしているので、電流供給線1813からEL素子1812に電流が流れることによってEL素子1812が発光する(図19(F))。このとき、EL素子1812に流れる電流値は、TFT1810のゲート・ソース間電圧に従つるものであり、このときのTFT1810のゲート・ソース間電圧は、( $V_{DD} - (V_{Data} + V_{th})$ )である。ここで仮に、TFT1810のしきい値 $V_{th}$ が各画素間でばらついたとしても、そのばらつきに応じた電圧が、各画素の容量手段1811に保持される。よって、EL素子1812の輝度は、しきい値のばらつきに影響されることがない。

**【0137】**

40

ここで、新たに追加したTFT1817は、発光時にEL素子1812に電流を供給するためのTFT1810と、互いのゲート電極が接続されている。図19(A)、(B)に示すように、電荷の移動するバスが実施形態よりも多く、またTFT1817は、EL素子1812に電流を供給する役目を持たないため、ゲート長Lを小さく、チャネル幅Wを大きくとって良い。従って、ゲート容量が小さいために電荷の移動がスムーズに行われ、容量手段に保持されている電圧が $V_{th}$ に収束するまでの時間をより短くすることが出来る。

**【0138】****[実施例6]**

本実施例においては、実施例5とは異なる構成によって、高速なしきい値保存動作を実現

50

する例を示す。

**【0139】**

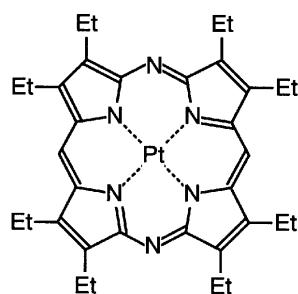

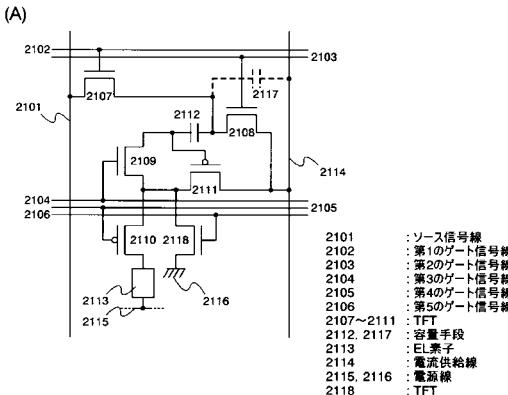

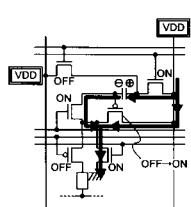

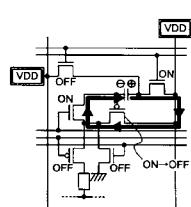

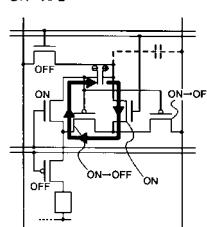

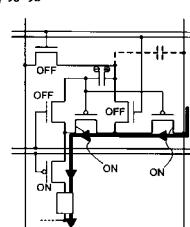

図22(A)に構成を示す。ここで、容量手段2211においてしきい値を保存するTFTは、TFT2210にあたる。EL素子2212が発光する際には、TFT2216、TFT2210、TFT2209を経由して電流が供給される。ここで、TFT2209は、単なるスイッチング素子として機能すればよい。EL素子2212の劣化に対応するため、TFT2216は、飽和領域で動作させ、かつ飽和領域において、ソース・ドレイン間電圧が変化しても、ドレイン電流がほぼ一定となるように、ゲート長Lを大きくする。

**【0140】**

電荷の充電は、図22(B)～(C)に示すような電流経路で行われ、容量手段2211に電荷が充電される。その後、TFT2209がOFFすると、図22(C)に示すように、再び電荷の移動が生じ、容量手段2211に保持されている電圧が、TFT2210およびTFT2216のしきい値に等しくなったところで、TFT2210、2216がOFFする。この動作によって、容量手段2211には、しきい値が保存される。このとき、TFT2210のゲート長Lは小さくしてあるため、図22(C)の動作はより迅速に進行することが出来る。

**【0141】**

その後、実施形態や他の実施例と同様に、映像信号の書き込みを行った後、図22(D)に示すように、TFT2209がONすると、電流供給線-TFT2216-TFT2210-TFT2209を経由して、EL素子2212に電流が供給され、発光する。

**【0142】**

このとき、TFT2210、2216は互いのゲート電極が接続されているため、マルチゲート型TFTとして動作することになる。このとき、TFT2210のゲート長をL<sub>1</sub>、チャネル幅をW<sub>1</sub>とし、TFT2216のゲート長をL<sub>2</sub>、チャネル幅をW<sub>2</sub>とすると、(W<sub>1</sub>/L<sub>1</sub>)>(W<sub>2</sub>/L<sub>2</sub>)となる。つまり、しきい値の保存動作において、図22(C)に示すようなしきい値電圧の保存は、Lが小さくWが大きいTFT2210を用いているため、より大きな電流によって動作を完了出来る。すなわち迅速な動作が出来る。かつ、発光時にはTFT2210、2216をマルチゲート型TFTとして用いており、TFT2216はゲート長Lを大きくしてあるため、TFT2210、2216のソース・ドレイン間電圧が少々変動しても、一定のドレイン電流を流すことが出来る。

**【0143】**

TFT2209の配置箇所に関しては、図22(A)に示したものその他、図23(A)、(B)に示すような例が挙げられる。また、このTFT2209は、デジタル映像信号を用いて時間階調方式による表示を行う際、消去用TFTとして用いることも出来る。

**【0144】**

**[実施例7]**

図1、図18、図20等に示した画素の場合、いずれも容量手段の充電中に、EL素子に電流が流れる。これによって、本来発光すべき期間以外でEL素子が発光してしまう。発光する期間はごく短いため、画質に大きく影響するものではないが、容量手段への電荷の充電中、EL素子自体が負荷となってしまい、これによって充電に時間を要することになる。本実施例においては、容量手段への電荷の充電時にEL素子に電流が流れないようにする構成について説明する。

**【0145】**

図21(A)に、画素の構成例を示す。図1(A)にて示した画素に、TFT2118が追加されている。TFT2118のゲート電極は、第5のゲート信号線2106に接続され、第1の電極は、TFT2109の第1の電極もしくは、TFT2109の第2の電極に接続され、第2の電極は、電源線に接続され、電流供給線2114と互いに電位差を有する。また、図21(A)に点線で示すように、容量手段2117を、第1のTFT2107の第2の電極と、電流供給線2114との間に設け、映像信号を保持するための容量として用いても良い。また、TFT2118の第2の電極は、当該画素を除くいずれかの画素に

10

20

20

30

40

50

おける第1のゲート信号線等に接続しても良い。つまりこの場合、選択されていないゲート信号線がある一定電位にあることを利用し、電源線として代用するわけである。

#### 【0146】

容量手段2112への電荷の充電においては、第2、第3、第5のゲート信号線2103、2104、2106へのパルスの入力によってTFT2108、2109、2118がONし、図21(B)に示すように振舞う。TFT2110がOFFであるため、EL素子2113には電流が流れず、発光しない。この場合にも、新たに追加したTFT2118による電流バスが存在するため、容量手段2112が充電される。その後、第5のゲート信号線2106がLレベルとなってTFT2118がOFFすると、図21(C)に示すように、容量手段2112に貯まっていた電荷の移動が生じ、TFT2111のしきい値を下回る瞬間にTFT2111がOFFし、電荷の移動も終了する。よって容量手段2112には、TFT2111のしきい値が保持される。

10

#### 【0147】

本実施例においては、第1～第5のゲート信号線によって、各TFTを独立して制御しているが、構成はこの限りではない。画素の開口率等を考えた場合、信号線の本数は可能な限り少ないことが望ましく、同期して動作するTFT、例えば図21(A)においてはTFT2108、2109に関しては、その極性を同極性として、1本のゲート信号線を用いて制御しても良い。

#### 【0148】

なお、本実施例と、他の実施例に記載の他の実施例を組み合わせて用いても良い。

20

#### 【0149】

##### [実施例8]

本実施例ではCMOS回路で構成される駆動回路と、スイッチング用TFT及び駆動用TFTを有する画素部とが同一基板上に形成された基板を便宜上アクティブマトリクス基板と呼ぶ。そして本実施例では前記アクティブマトリクス基板の作製工程について図13、図14を用いて説明する。

#### 【0150】

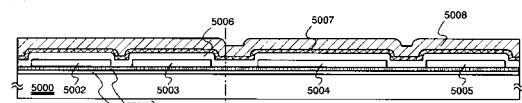

基板5000は、石英基板、シリコン基板、金属基板又はステンレス基板の表面に絶縁膜を形成したものを用いる。また本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板を用いても良い。本実施例ではバリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス等のガラスからなる基板5000を用いた。

30

#### 【0151】

次いで、基板5000上に酸化珪素膜、窒化珪素膜又は酸化窒化珪素膜などの絶縁膜から成る下地膜5001を形成する。本実施例の下地膜5001は2層構造で形成したが、前記絶縁膜の単層構造又は前記絶縁膜を2層以上積層させた構造であっても良い。

#### 【0152】

本実施例では、下地膜5001の1層目として、プラズマCVD法を用いて、SiH<sub>4</sub>、NH<sub>3</sub>、及びN<sub>2</sub>Oを反応ガスとして成膜される窒化酸化珪素膜5001aを10～200nm(好ましくは50～100nm)の厚さに形成する。本実施例では、窒化酸化珪素膜5001aを50nmの厚さに形成した。次いで下地膜5001の2層目として、プラズマCVD法を用いて、SiH<sub>4</sub>及びN<sub>2</sub>Oを反応ガスとして成膜される酸化窒化珪素膜5001bを50～200nm(好ましくは100～150nm)の厚さに形成する。本実施例では、酸化窒化珪素膜5001bを100nmの厚さに形成した。

40

#### 【0153】

続いて、下地膜5001上に半導体層5002～5005を形成する。半導体層5002～5005は公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)により25～80nm(好ましくは30～60nm)の厚さで半導体膜を成膜する。次いで前記半導体膜を公知の結晶化法(レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法等)を用いて結晶化させる。そして、得られた結晶質半導体膜を所望の形状にパターニングして半導体層5002～5005を形成

50

する。なお前記半導体膜としては、非晶質半導体膜、微結晶半導体膜、結晶質半導体膜、又は非晶質珪素ゲルマニウム膜などの非晶質構造を有する化合物半導体膜などを用いても良い。

#### 【0154】

本実施例では、プラズマCVD法を用いて、膜厚55nmの非晶質珪素膜を成膜した。そして、ニッケルを含む溶液を非晶質珪素膜上に保持させ、この非晶質珪素膜に脱水素化(500、1時間)を行った後、熱結晶化(550、4時間)を行って結晶質珪素膜を形成した。その後、フォトリソグラフィ法を用いたパターニング処理によって半導体層5002~5005を形成した。

#### 【0155】

なおレーザ結晶化法で結晶質半導体膜を作製する場合のレーザは、連続発振またはパルス発振の気体レーザ又は固体レーザを用いれば良い。前者の気体レーザとしては、エキシマレーザ、YAGレーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、ガラスレーザ、ルビーレーザ、Ti:Sファイアレーザ等を用いることができる。また後者の固体レーザとしては、Cr、Nd、Er、Ho、Ce、Co、Ti又はTmがドーピングされたYAG、YVO<sub>4</sub>、YLF、YAlO<sub>3</sub>などの結晶を使ったレーザを用いることができる。当該レーザの基本波はドーピングする材料によって異なり、1μm前後の基本波を有するレーザ光が得られる。基本波に対する高調波は、非線形光学素子を用いることで得ることができる。なお非晶質半導体膜の結晶化に際し、大粒径に結晶を得るためにには、連続発振が可能な固体レーザを用い、基本波の第2高調波~第4高調波を適用するのが好ましい。代表的には、Nd:YVO<sub>4</sub>レーザー(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を適用する。

#### 【0156】

また出力10Wの連続発振のYVO<sub>4</sub>レーザから射出されたレーザ光は、非線形光学素子により高調波に変換する。さらに、共振器の中にYVO<sub>4</sub>結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または橢円形状のレーザ光に成形して、被処理体に照射する。このときのエネルギー密度は0.01~100MW/cm<sup>2</sup>程度(好ましくは0.1~10MW/cm<sup>2</sup>)が必要である。そして、10~2000cm/s程度の速度でレーザ光に対して相対的に半導体膜を移動させて照射する。

#### 【0157】

また上記のレーザを用いる場合には、レーザ発振器から放射されたレーザビームを光学系で線状に集光して、半導体膜に照射すると良い。結晶化の条件は適宜設定されるが、エキシマレーザを用いる場合はパルス発振周波数300Hzとし、レーザーエネルギー密度を100~700mJ/cm<sup>2</sup>(代表的には200~300mJ/cm<sup>2</sup>)とすると良い。またYAGレーザを用いる場合には、その第2高調波を用いてパルス発振周波数1~300Hzとし、レーザーエネルギー密度を300~1000mJ/cm<sup>2</sup>(代表的には350~500mJ/cm<sup>2</sup>)とすると良い。そして幅100~1000μm(好ましくは幅400μm)で線状に集光したレーザ光を基板全面に渡って照射し、このときの線状ビームの重ね合わせ率(オーバーラップ率)を50~98%として行っても良い。

#### 【0158】

しかしながら本実施例では、結晶化を助長する金属元素を用いて非晶質珪素膜の結晶化を行ったため、前記金属元素が結晶質珪素膜中に残留している。そのため、前記結晶質珪素膜上に50~100nmの非晶質珪素膜を形成し、加熱処理(RTA法やファーネスアニール炉を用いた熱アニール等)を行って、該非晶質珪素膜中に前記金属元素を拡散させ、前記非晶質珪素膜は加熱処理後にエッチングを行って除去する。その結果、前記結晶質珪素膜中の金属元素の含有量を低減または除去することができる。

#### 【0159】

なお半導体層5002~5005を形成した後、TFTのしきい値を制御するために微量な不純物元素(ボロンまたはリン)のドーピングを行ってもよい。

10

20

20

30

40

50

**【0160】**

次いで、半導体層 5002～5005 を覆うゲート絶縁膜 5006 を形成する。ゲート絶縁膜 5006 はプラズマ CVD 法やスパッタ法を用いて、膜厚を 40～150 nm として珪素を含む絶縁膜で形成する。本実施例では、ゲート絶縁膜 5006 としてプラズマ CVD 法により酸化窒化珪素膜を 115 nm の厚さに形成した。勿論、ゲート絶縁膜 5006 は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

**【0161】**

なおゲート絶縁膜 5006 として酸化珪素膜を用いる場合には、プラズマ CVD 法で TEOS (Tetraethyl Orthosilicate) と O<sub>2</sub> とを混合し、反応圧力 40 Pa、基板温度 300～400 とし、高周波 (13.56 MHz) 電力密度 0.5～0.8 W/cm<sup>2</sup> で放電させて形成しても良い。上記の工程により作製される酸化珪素膜は、その後 400～500 の熱アニールによって、ゲート絶縁膜 5006 として良好な特性を得ることができる。

**【0162】**

次いで、ゲート絶縁膜 5006 上に膜厚 20～100 nm の第 1 の導電膜 5007 と、膜厚 100～400 nm の第 2 の導電膜 5008 とを積層形成する。本実施例では、膜厚 30 nm の TaN 膜からなる第 1 の導電膜 5007 と、膜厚 370 nm の W 膜からなる第 2 の導電膜 5008 を積層形成した。

**【0163】**

本実施例では、第 1 の導電膜 5007 である TaN 膜はスパッタ法で形成し、Ta のターゲットを用いて、窒素を含む雰囲気内でスパッタ法で形成した。また第 2 の導電膜 5008 である W 膜は、W のターゲットを用いたスパッタ法で形成した。その他に 6 フッ化タンゲステン (WF<sub>6</sub>) を用いる熱 CVD 法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W 膜の抵抗率は 20 μ cm 以下にすることが望ましい。W 膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W 膜中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。従って、本実施例では、高純度の W (純度 99.9999%) のターゲットを用いたスパッタ法で、さらに成膜時に気相中からの不純物の混入がないように十分配慮して W 膜を形成することにより、抵抗率 9～20 μ cm を実現することができた。

**【0164】**

なお本実施例では、第 1 の導電膜 5007 を TaN 膜、第 2 の導電膜 5008 を W 膜としたが、第 1 の導電膜 5007 及び第 2 の導電膜 5008 を構成する材料は特に限定されない。第 1 の導電膜 5007 及び第 2 の導電膜 5008 は、Ta、W、Ti、Mo、Al、Cu、Cr、Nd から選択された元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶珪素膜に代表される半導体膜や Ag-Pd-Cu 合金で形成してもよい。

**【0165】**

次いで、フォトリソグラフィ法を用いてレジストからなるマスク 5009 を形成し、電極及び配線を形成するための第 1 のエッチング処理を行う。第 1 のエッチング処理では第 1 及び第 2 のエッチング条件で行う。(図 13(B))

**【0166】**

本実施例では第 1 のエッチング条件として、ICP (Inductively Coupled Plasma : 誘導結合型プラズマ) エッチング法を用い、エッチング用ガスに CF<sub>4</sub> と Cl<sub>2</sub> と O<sub>2</sub> とを用い、それぞれのガス流量比を 25 : 25 : 10 (sccm) とし、1.0 Pa の圧力でコイル型の電極に 500 W の RF (13.56 MHz) 電力を投入してプラズマを生成してエッチングを行った。基板側(試料ステージ)にも 150 W の RF (13.56 MHz) 電力を投入し、実質的に負の自己バイアス電圧を印加した。そしてこの第 1 のエッチング条件により W 膜をエッチングして第 1 の導電層 5007 の端部をテーパー形状とした。

**【0167】**

続いて、レジストからなるマスク 5009 を除去せずに第 2 のエッチング条件に変更し、

10

20

30

40

50

エッティング用ガスに  $\text{C F}_4$  と  $\text{C l}_2$  を用い、それぞれのガス流量比を 30 : 30 (sccm) とし、1.0 Pa の圧力でコイル型の電極に 500 W の RF (13.56 MHz) 電力を投入してプラズマを生成して 15 秒程度のエッティングを行った。基板側(試料ステージ)にも 20 W の RF (13.56 MHz) 電力を投入し、実質的に負の自己バイアス電圧を印加した。第 2 のエッティング条件では第 1 の導電層 5007 及び第 2 の導電層 5008 とも同程度にエッティングを行った。なお、ゲート絶縁膜 5006 上に残渣を残すことなくエッティングするためには、10 ~ 20 % 程度の割合でエッティング時間を増加させると良い。

#### 【0168】

上記の第 1 のエッティング処理では、レジストからなるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第 1 の導電層 5007 及び第 2 の導電層 5008 の端部がテーパー形状となる。こうして、第 1 のエッティング処理により第 1 の導電層 5007 と第 2 の導電層 5008 から成る第 1 の形状の導電層 5010 ~ 5014 を形成した。ゲート絶縁膜 5006においては、第 1 の形状の導電層 5010 ~ 5014 で覆われない領域が 20 ~ 50 nm 程度エッティングされたため、膜厚が薄くなった領域が形成された。10

#### 【0169】

次いで、レジストからなるマスク 5009 を除去せずに第 2 のエッティング処理を行う。(図 13 (C)) 第 2 のエッティング処理では、エッティングガスに  $\text{S F}_6$  と  $\text{C l}_2$  と  $\text{O}_2$  を用い、それぞれのガス流量比を 24 : 12 : 24 (sccm) とし、1.3 Pa の圧力でコイル側の電力に 700 W の RF (13.56 MHz) 電力を投入してプラズマを生成して 25 秒程度のエッティングを行った。基板側(試料ステージ)にも 10 W の RF (13.56 MHz) 電力を投入し、実質的に負の自己バイアス電圧を印加した。こうして、W 膜を選択的にエッティングして、第 2 の形状の導電層 5015 ~ 5019 を形成した。このとき、第 1 の導電層 5015a ~ 5018a は、ほとんどエッティングされない。20

#### 【0170】

そして、レジストからなるマスク 5009 を除去せずに第 1 のドーピング処理を行い、半導体層 5002 ~ 5005 に N 型を付与する不純物元素を低濃度に添加する。第 1 のドーピング処理はイオンドープ法又はイオン注入法で行えば良い。イオンドープ法の条件はドーザ量を  $1 \times 10^{13} \sim 5 \times 10^{14}$  atoms/cm<sup>2</sup> とし、加速電圧を 40 ~ 80 keV として行う。本実施例ではドーザ量を  $5 \cdot 0 \times 10^{13}$  atoms/cm<sup>2</sup> とし、加速電圧を 50 keV として行った。30 N 型を付与する不純物元素としては、15 族に属する元素を用いれば良く、代表的にはリン (P) 又は砒素 (As) を用いられるが、本実施例ではリン (P) を用いた。この場合、第 2 の形状の導電層 5015 ~ 5019 が N 型を付与する不純物元素に対するマスクとなつて、自己整合的に第 1 の不純物領域 (N - 領域) 5020 ~ 5023 を形成した。そして第 1 の不純物領域 5020 ~ 5023 には  $1 \times 10^{18} \sim 1 \times 10^{20}$  atoms/cm<sup>3</sup> の濃度範囲で N 型を付与する不純物元素が添加された。

#### 【0171】

続いてレジストからなるマスク 5009 を除去した後、新たにレジストからなるマスク 5024 を形成して、第 1 のドーピング処理よりも高い加速電圧で第 2 のドーピング処理を行う。イオンドープ法の条件はドーザ量を  $1 \times 10^{13} \sim 3 \times 10^{15}$  atoms/cm<sup>2</sup> とし、加速電圧を 60 ~ 120 keV として行う。本実施例では、ドーザ量を  $3 \cdot 0 \times 10^{15}$  atoms/cm<sup>2</sup> とし、加速電圧を 65 keV として行った。第 2 のドーピング処理は第 2 の導電層 5015b ~ 5018b を不純物元素に対するマスクとして用い、第 1 の導電層 5015a ~ 5018a のテーパー部の下方の半導体層に不純物元素が添加されるようにドーピングを行った。40

#### 【0172】

上記の第 2 のドーピング処理を行った結果、第 1 の導電層と重なる第 3 の不純物領域 (N - 領域、Lov 領域) 5026 には  $1 \times 10^{18} \sim 5 \times 10^{19}$  atoms/cm<sup>3</sup> の濃度範囲で N 型を付与する不純物元素を添加された。また第 2 の不純物領域 (N + 領域) 5025、5028 には  $1 \times 10^{19} \sim 5 \times 10^{21}$  atoms/cm<sup>3</sup> の濃度範囲で N 型を付与50

する不純物元素を添加された。また、第1、第2のドーピング処理を行った後、半導体層5002～5005において、不純物元素が全く添加されない領域又は微量の不純物元素が添加された領域が形成された。本実施例では、不純物元素が全く添加されない領域又は微量の不純物元素が添加された領域をチャネル領域5027、5030とよぶ。また前記第1のドーピング処理により形成された第1の不純物領域( N - 領域 ) 5020～5023のうち、第2のドーピング処理においてレジスト5024で覆われていた領域が存在するが、本実施例では、引き続き第1の不純物領域( N - 領域、 LDD領域 ) 5029とよぶ。

#### 【 0173 】

なお本実施例では、第2のドーピング処理のみにより、第3の不純物領域( N - 領域 ) 5026及び第2の不純物領域( N + 領域 ) 5025、5028を形成したが、これに限定されない。ドーピング処理を行う条件を適宜変えて、複数回のドーピング処理で形成しても良い。

#### 【 0174 】

次いで図14(A)に示すように、レジストからなるマスク5024を除去した後、新たにレジストからなるマスク5031を形成する。その後、第3のドーピング処理を行う。第3のドーピング処理により、Pチャネル型TFTの活性層となる半導体層に、前記第1の導電型とは逆の導電型を付与する不純物元素が添加された第4の不純物領域( P + 領域 ) 5032、5034及び第5の不純物領域( P - 領域 ) 5033、5035を形成する。

#### 【 0175 】

第3のドーピング処理では、第2の導電層5016b、5018bを不純物元素に対するマスクとして用いる。こうして、P型を付与する不純物元素を添加し、自己整合的に第4の不純物領域( P + 領域 ) 5032、5034及び第5の不純物領域( P - 領域 ) 5033、5035を形成する。

#### 【 0176 】

本実施例では、第4の不純物領域5032、5034及び第5の不純物領域5033、5035はジボラン( $B_2H_6$ )を用いたイオンドープ法で形成する。イオンドープ法の条件としては、ドーズ量を $1 \times 10^{16} atoms/cm^2$ とし、加速電圧を80keVとした。

#### 【 0177 】

なお、第3のドーピング処理の際には、Nチャネル型TFTを形成する半導体層はレジストからなるマスク5031によって覆われている。

#### 【 0178 】

ここで、第1及び2のドーピング処理によって、第4の不純物領域( P + 領域 ) 5032、5034及び第5の不純物領域( P - 領域 ) 5033、5035にはそれぞれ異なる濃度でリンが添加されている。しかし、第4の不純物領域( P + 領域 ) 5032、5034及び第5の不純物領域( P - 領域 ) 5033、5035のいずれの領域においても、第3のドーピング処理によって、P型を付与する不純物元素の濃度が $1 \times 10^{19} \sim 5 \times 10^{21} atoms/cm^3$ となるようにドーピング処理される。こうして、第4の不純物領域( P + 領域 ) 5032、5034及び第5の不純物領域( P - 領域 ) 5033、5035は、Pチャネル型TFTのソース領域およびドレイン領域として問題なく機能する。

#### 【 0179 】

なお本実施例では、第3のドーピング処理のみにより、第4の不純物領域( P + 領域 ) 5032、5034及び第5の不純物領域( P - 領域 ) 5033、5035を形成したが、これに限定されない。ドーピング処理を行う条件を適宜変えて、複数回のドーピング処理で形成しても良い。

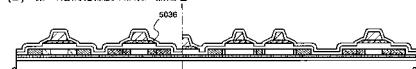

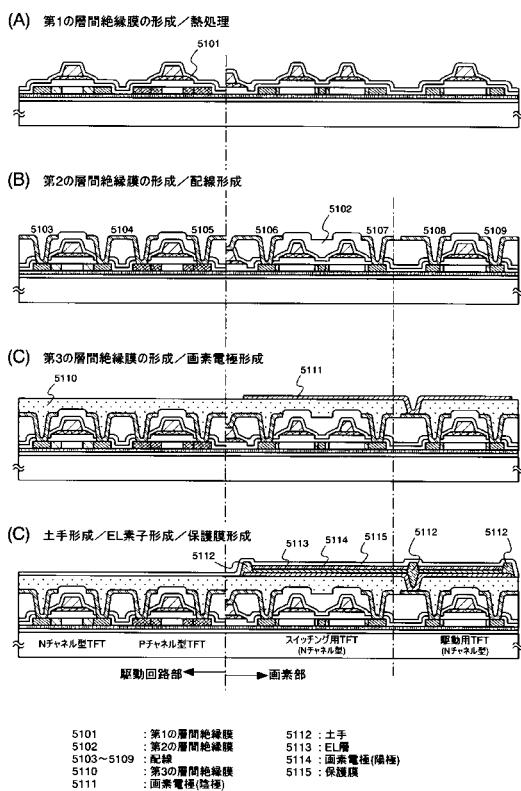

#### 【 0180 】

次いで図14(B)に示すように、レジストからなるマスク5031を除去して第1の層間絶縁膜5036を形成する。この第1の層間絶縁膜5036としては、プラズマCVD法またはスパッタ法を用い、厚さを100～200nmとして珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により膜厚100nmの酸化窒化珪素膜を形成した。勿論

10

20

30

40

50

、第1の層間絶縁膜5036は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

#### 【0181】

次いで、図14(C)に示すように、加熱処理(熱処理)を行って、半導体層の結晶性の回復、半導体層に添加された不純物元素の活性化を行う。この加熱処理はファーネスアニール炉を用いる熱アニール法で行う。熱アニール法としては、酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400～700で行えばよく、本実施例では410、1時間の熱処理で活性化処理を行った。なお、熱アニール法の他に、レーザアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。

#### 【0182】

また、第1の層間絶縁膜5036を形成する前に加熱処理を行っても良い。ただし、第1の導電層5015a～5019a及び、第2の導電層5015b～5019bを構成する材料が熱に弱い場合には、本実施例のように配線等を保護するため第1の層間絶縁膜5036(珪素を主成分とする絶縁膜、例えば窒化珪素膜)を形成した後で熱処理を行うことが好ましい。

#### 【0183】

上記の様に、第1の層間絶縁膜5036(珪素を主成分とする絶縁膜、例えば窒化珪素膜)を形成した後に熱処理することにより、活性化処理と同時に、半導体層の水素化も行うことができる。水素化の工程では、第1の層間絶縁膜5036に含まれる水素により半導体層のダングリングボンドが終端される。

#### 【0184】

なお、活性化処理のための加熱処理とは別に、水素化のための加熱処理を行っても良い。

#### 【0185】

ここで、第1の層間絶縁膜5036の存在に関係なく、半導体層を水素化することもできる。水素化の他の手段として、プラズマにより励起された水素を用いる手段(プラズマ水素化)や、3～100%の水素を含む雰囲気中において、300～450で1～12時間の加熱処理を行う手段でも良い。

#### 【0186】

次いで、第1の層間絶縁膜5036上に、第2の層間絶縁膜5037を形成する。第2の層間絶縁膜5037としては、無機絶縁膜を用いることができる。例えば、CVD法によって形成された窒化珪素膜あるいは窒化酸化珪素膜や、SOG(Spin On Glass)法によって塗布された窒化珪素膜あるいは窒化酸化珪素膜等を用いることができる。また、第2の層間絶縁膜5037として、有機絶縁膜を用いることができる。例えば、ポリイミド、ポリアミド、BCB(ベンゾシクロブテン)、アクリル等の膜を用いることができる。また、アクリル膜と窒化珪素膜あるいは窒化酸化珪素膜の積層構造を用いても良い。

#### 【0187】

本実施例では、膜厚1.6μmのアクリル膜を形成した。第2の層間絶縁膜5037によって、基板上5000に形成されたTFTによる凹凸を緩和し、平坦化することができる。特に、第2の層間絶縁膜5037は平坦化の意味合いが強いので、平坦性に優れた膜が好ましい。

#### 【0188】

次いで、ドライエッティングまたはウエットエッティングを用い、第2の層間絶縁膜5037、第1の層間絶縁膜5036、およびゲート絶縁膜5006をエッティングし、第2の不純物領域5025、5028、第4の不純物領域5032、5034に達するコンタクトホールを形成する。

#### 【0189】

次いで、透明導電膜からなる画素電極5038を形成する。透明導電膜としては、酸化インジウムと酸化スズの化合物(Indium Tin Oxide:ITO)、酸化インジウムと酸化亜鉛の化合物、酸化亜鉛、酸化スズ、酸化インジウム等を用いることができる。また、前記透明導電膜にガリウムを添加したもの用いてもよい。画素電極がEL素子の陽極に相当する

10

20

30

40

50

。

**【 0 1 9 0 】**

本実施例では、ITOを110nm厚さで成膜、その後パターニングし、画素電極5038形成した。

**【 0 1 9 1 】**

次いで、各不純物領域とそれぞれ電気的に接続される配線5039～5045を形成する。なお本実施例では、配線5039～5045は、膜厚100nmのTi膜と、膜厚350nmのAl膜と、膜厚100nmのTi膜との積層膜をスパッタ法で連続形成し、所望の形状にパターニングして形成する。

**【 0 1 9 2 】**

もちろん、三層構造に限らず、単層構造でもよいし、二層構造でもよいし、四層以上の積層構造にしてもよい。また配線の材料としては、AlとTiに限らず、他の導電膜を用いても良い。例えば、TaN膜上にAlやCuを形成し、さらにTi膜を形成した積層膜をパターニングして配線を形成してもよい。

**【 0 1 9 3 】**

こうして、画素部のNチャネル型TFTのソース領域またはドレイン領域の一方は、配線5042によってソース信号線(5019aと5019bの積層)と電気的に接続され、もう一方は、配線5043によって画素部のPチャネル型TFTのゲート電極と電気的に接続される。また、画素部のPチャネル型TFTのソース領域またはドレイン領域の一方は、配線5044によって画素電極5038と電気的に接続されている。ここで、画素電極5038上的一部分と、配線5044的一部分を重ねて形成することによって、配線5044と画素電極5038の電気的接続をとっている。

**【 0 1 9 4 】**

以上の工程により図14(D)に示すように、Nチャネル型TFTとPチャネル型TFTからなるCMOS回路を有する駆動回路部と、スイッチング用TFT、駆動用TFTとを有する画素部を同一基板上に形成することができる。

**【 0 1 9 5 】**

駆動回路部のNチャネル型TFTは、ゲート電極の一部を構成する第1の導電層5015aと重なる低濃度不純物領域5026(Lov領域)、ソース領域またはドレイン領域として機能する高濃度不純物領域5025とを有している。このNチャネル型TFTと配線5040で接続されCMOS回路を形成するPチャネル型TFTは、ゲート電極の一部を構成する第1の導電層5016aと重なる低濃度不純物領域5033(Lov領域)、ソース領域またはドレイン領域として機能する高濃度不純物領域5032とを有している。

**【 0 1 9 6 】**

画素部において、Nチャネル型のスイッチング用TFTは、ゲート電極の外側に形成される低濃度不純物領域5029(Loff領域)、ソース領域またはドレイン領域として機能する高濃度不純物領域5028とを有している。また画素部において、Pチャネル型の駆動用TFTは、ゲート電極の一部を構成する第1の導電層5018aと重なる低濃度不純物領域5035(Lov領域)、ソース領域またはドレイン領域として機能する高濃度不純物領域5034とを有している。

**【 0 1 9 7 】**

次いで、第3の層間絶縁膜5046を形成する。第3の層間絶縁膜としては、無機絶縁膜や有機絶縁膜を用いることができる。無機絶縁膜としては、CVD法によって形成された窒化珪素膜あるいは窒化酸化珪素膜や、SOG(Spin On Glass)法によって塗布された窒化珪素膜あるいは窒化酸化珪素膜等を用いることができる。また、有機絶縁膜としては、アクリル樹脂膜等を用いることができる。

**【 0 1 9 8 】**

第2の層間絶縁膜5037と第3の層間絶縁膜5046の組み合わせの例を以下に挙げる。

10

20

30

40

50

## 【0199】

第2の層間絶縁膜5037として、プラズマCVD法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用い、第3の層間絶縁膜5046としてもプラズマCVD法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用いる組み合わせがある。また、第2の層間絶縁膜5037として、SOG法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用い、第3の層間絶縁膜5046としてもSOG法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用いる組み合わせがある。また、第2の層間絶縁膜5037として、SOG法によって形成した窒化珪素膜あるいは窒化酸化珪素膜とプラズマCVD法によって形成した窒化珪素膜あるいは窒化酸化珪素膜の積層膜を用い、第3の層間絶縁膜5046としてプラズマCVD法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用いる組み合わせがある。また、第2の層間絶縁膜5037として、アクリルを用い、第3の層間絶縁膜5046としてもアクリルを用いる組み合わせがある。また、第2の層間絶縁膜5037として、アクリルとプラズマCVD法によって形成した窒化珪素膜あるいは窒化酸化珪素膜の積層膜を用い、第3の層間絶縁膜5046としてプラズマCVD法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用いる組み合わせがある。また、第2の層間絶縁膜5037として、プラズマCVD法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用い、第3の層間絶縁膜5046としてアクリルを用いる組み合わせがある。

## 【0200】

第3の層間絶縁膜5046の画素電極5038に対応する位置に開口部を形成する。第3の層間絶縁膜は、バンクとして機能する。開口部を形成する際、ウェットエッチング法を用いることで容易にテーパー形状の側壁とすることが出来る。開口部の側壁が十分になだらかでないと段差に起因するEL層の劣化が顕著な問題となってしまうため、注意が必要である。

## 【0201】

第3の層間絶縁膜中に、カーボン粒子や金属粒子を添加し、抵抗率を下げ、静電気の発生を抑制してもよい。この際、抵抗率は、 $1 \times 10^6 \sim 1 \times 10^{12} \Omega$ (好ましくは、 $1 \times 10^8 \sim 1 \times 10^{10} \Omega$ )となるように、カーボン粒子や金属粒子の添加量を調節すればよい。

## 【0202】

次いで、第3の層間絶縁膜5046の開口部において露出している画素電極5038上に、EL層5047を形成する。

## 【0203】

EL層5047としては、公知の有機発光材料や無機発光材料を用いることができる。

## 【0204】

有機発光材料としては、低分子系有機発光材料、高分子系有機発光材料、中分子系有機材料を自由に用いることができる。なお、ここでは、中分子系有機発光材料とは、昇華性を有さず、かつ、分子数が20以下または連鎖する分子の長さが $10 \mu m$ 以下の有機発光材料を示すものとする。

## 【0205】

EL層5047は通常、積層構造である。代表的には、コダック・イーストマン・カンパニーのTangらが提案した「正孔輸送層/発光層/電子輸送層」という積層構造が挙げられる。また他にも、陽極上に正孔注入層/正孔輸送層/発光層/電子輸送層、または正孔注入層/正孔輸送層/発光層/電子輸送層/電子注入層の順に積層する構造でも良い。発光層に対して蛍光性色素等をドーピングしても良い。

## 【0206】

本実施例では蒸着法により低分子系有機発光材料を用いてEL層5047を形成している。具体的には、正孔注入層として $20 nm$ 厚の銅フタロシアニン(CuPc)膜を設け、その上に発光層として $70 nm$ 厚のトリス-8-キノリノラトアルミニウム錯体(A1q<sub>3</sub>)膜を設けた積層構造としている。A1q<sub>3</sub>にキナクリドン、ペリレンもしくはDCM1といった蛍光色素を添加することで発光色を制御することができる。

10

20

30

40

50

## 【0207】

なお、図14(D)では一画素しか図示していないが、複数の色、例えば、R(赤)、G(緑)、B(青)の各色に対応したEL層5047を作り分ける構成とすることができる。

## 【0208】

また、高分子系有機発光材料を用いる例として、正孔注入層として20nmのポリチオフェン(PEDOT)膜をスピニ塗布法により設け、その上に発光層として100nm程度のパラフェニレンビニレン(PPV)膜を設けた積層構造によってEL層5047を構成しても良い。なお、PPVの共役系高分子を用いると、赤色から青色まで発光波長を選択できる。また、電子輸送層や電子注入層として炭化珪素等の無機材料を用いることも可能である。

10

## 【0209】

なお、EL層5047は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等が、明確に区別された積層構造を有するものに限定されない。つまり、EL層5047は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等を構成する材料が、混合した層を有する構造であってもよい。

## 【0210】

例えば、電子輸送層を構成する材料(以下、電子輸送材料と表記する)と、発光層を構成する材料(以下、発光材料と表記する)とによって構成される混合層を、電子輸送層と発光層との間に有する構造のEL層5047であってもよい。

## 【0211】

次に、EL層5047の上には導電膜からなる対向電極5048が設けられる。本実施例の場合、導電膜としてアルミニウムとリチウムとの合金膜を用いる。勿論、公知のMgAg膜(マグネシウムと銀との合金膜)を用いても良い。対向電極5048がEL素子の陰極に相当する。陰極材料としては、周期表の1族もしくは2族に属する元素からなる導電膜もしくはそれらの元素を添加した導電膜を自由に用いることができる。

20

## 【0212】

対向電極5048まで形成された時点でEL素子が完成する。なお、EL素子とは、画素電極(陽極)5038、EL層5047及び対向電極(陰極)5048で形成された素子を指す。

## 【0213】

EL素子を完全に覆うようにしてパッシベーション膜5049を設けることは有効である。パッシベーション膜5049としては、炭素膜、窒化珪素膜もしくは窒化酸化珪素膜を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層で用いることができる。

30

## 【0214】

カバレッジの良い膜をパッシベーション膜5049として用いることが好ましく、炭素膜、特にDLC(ダイヤモンドライクカーボン)膜を用いることは有効である。DLC膜は室温から100℃以下の温度範囲で成膜可能であるため、耐熱性の低いEL層5047の上方にも容易に成膜することができる。また、DLC膜は酸素に対するプロッキング効果が高く、EL層5047の酸化を抑制することが可能である。そのため、EL層5047が酸化するといった問題を防止できる。

40

## 【0215】

なお、第3の層間絶縁膜5046を形成した後、パッシベーション膜5049を形成するまでの工程をマルチチャンバー方式(またはインライン方式)の成膜装置を用いて、大気解放せずに連続的に処理することは有効である。

## 【0216】

なお、実際には図14(D)の状態まで完成したら、さらに外気に曝されないように、気密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィルム等)や透光性のシーリング材でパッケージング(封入)することが好ましい。その際、シーリング材の内部を不活性雰囲気にしたり、内部に吸湿性材料(例えば酸化バリウム)を配置したりするとEL素子の信頼性が向上する。

50

**【0217】**

また、パッケージング等の処理により気密性を高めたら、基板 5000 上に形成された素子又は回路から引き回された端子と外部信号端子とを接続するためのコネクタ(フレキシブルプリントサーキット：FPC)を取り付けて製品として完成する。

**【0218】**

また、本実施例で示す工程に従えば、発光装置の作製に必要なフォトマスクの数を抑えることが出来る。その結果、工程を短縮し、製造コストの低減及び歩留まりの向上に寄与することが出来る。

**【0219】**

[実施例 9] 10

本実施例では、実施例 8 に示した構成とは異なる構成のアクティブマトリクス基板の作製工程について図 15 を用いて説明する。

**【0220】**

なお、図 15(A)までの工程は、実施例 11において、図 13(A)～(D)、図 14(A)に示した工程と同様である。ただし、画素部を構成する駆動用 TFT は、ゲート電極の外側に形成される低濃度不純物領域(L<sub>off</sub>領域)を有する、N チャネル型の TFT である点が異なる。この駆動用 TFT においては、実施例 9 に示したように、レジストによるマスクを用いて、ゲート電極の外側に低濃度不純物領域(L<sub>off</sub>領域)を形成すれば良い。

**【0221】**

図 13 及び図 14 と同じ部分は同じ符号を用いて示し、説明は省略する。 20

**【0222】**

図 15(A)に示すように、第 1 の層間絶縁膜 5101 を形成する。この第 1 の層間絶縁膜 5101 としては、プラズマ CVD 法またはスパッタ法を用い、厚さを 100 ~ 200 nm として珪素を含む絶縁膜で形成する。本実施例では、プラズマ CVD 法により膜厚 100 nm の酸化窒化珪素膜を形成した。勿論、第 1 の層間絶縁膜 5101 は酸化窒化珪素膜に限定されるものではなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

**【0223】**

次いで、図 15(B)に示すように、加熱処理(熱処理)を行って、半導体層の結晶性の回復、半導体層に添加された不純物元素の活性化を行う。この加熱処理はファーネスアニール炉を用いる熱アニール法で行う。熱アニール法としては、酸素濃度が 1 ppm 以下、好ましくは 0.1 ppm 以下の窒素雰囲気中で 400 ~ 700 で行えばよく、本実施例では 410 、 1 時間の熱処理で活性化処理を行った。なお、熱アニール法の他に、レーザアニール法、またはラピッドサーマルアニール法(RTA 法)を適用することができる。 30

**【0224】**

また、第 1 の層間絶縁膜 5101 を形成する前に加熱処理を行っても良い。ただし、第 1 の導電層 5015a ~ 5019a 及び、第 2 の導電層 5015b ~ 5019b が熱に弱い場合には、本実施例のように配線等を保護するため第 1 の層間絶縁膜 5101(珪素を主成分とする絶縁膜、例えば窒化珪素膜)を形成した後で熱処理を行うことが好ましい。

**【0225】**

上記の様に、第 1 の層間絶縁膜 5101(珪素を主成分とする絶縁膜、例えば窒化珪素膜)を形成した後に熱処理することにより、活性化処理と同時に、半導体層の水素化も行うことができる。水素化の工程では、第 1 の層間絶縁膜 5101 に含まれる水素により半導体層のダンギングボンドが終端される。 40

**【0226】**

なお、活性化処理のための加熱処理とは別に、水素化のための加熱処理を行っても良い。

**【0227】**

ここで、第 1 の層間絶縁膜 5101 の存在に関係なく、半導体層を水素化することもできる。水素化の他の手段として、プラズマにより励起された水素を用いる手段(プラズマ水素化)や、3 ~ 100 % の水素を含む雰囲気中において、300 ~ 450 で 1 ~ 12 時間の加熱処理を行う手段でも良い。 50

**【0228】**

以上の工程により、Nチャネル型TFTとPチャネル型TFTからなるCMOS回路を有する駆動回路部と、スイッチング用TFT、駆動用TFTとを有する画素部を同一基板上に形成することができる。

**【0229】**

次いで、第1の層間絶縁膜5101上に、第2の層間絶縁膜5102を形成する。第2の層間絶縁膜5102としては、無機絶縁膜を用いることができる。例えば、CVD法によって形成された窒化珪素膜あるいは窒化酸化珪素膜や、SOG(Spin On Glass)法によって塗布された窒化珪素膜あるいは窒化酸化珪素膜等を用いることができる。また、第2の層間絶縁膜5102として、有機絶縁膜を用いることができる。例えば、ポリイミド、ポリアミド、BCB(ベンゾシクロブテン)、アクリル等の膜を用いることができる。また、アクリル膜と窒化珪素膜あるいは窒化酸化珪素膜の積層構造を用いても良い。10

**【0230】**

次いで、ドライエッチングまたはウェットエッチングを用い、第1の層間絶縁膜5101、第2の層間絶縁膜5102及びゲート絶縁膜5006をエッチングし、駆動回路部及び画素部を構成する各TFTの不純物領域(第3の不純物領域(N+領域)及び第4の不純物領域(P+領域))に達するコンタクトホールを形成する。

**【0231】**

次いで、各不純物領域とそれぞれ電気的に接続される配線5103～5109を形成する。なお本実施例では、配線5103～5109は、膜厚100nmのTi膜と、膜厚350nmのAl膜と、膜厚100nmのTi膜との積層膜をスパッタ法で連続形成し、所望の形状にパターニングして形成する。20

**【0232】**

もちろん、三層構造に限らず、単層構造でもよいし、二層構造でもよいし、四層以上の積層構造にしてもよい。また配線の材料としては、AlとTiに限らず、他の導電膜を用いてもよい。例えば、TaN膜上にAlやCuを形成し、さらにTi膜を形成した積層膜をパターニングして配線を形成してもよい。

**【0233】**

画素部のスイッチング用TFTのソース領域またはドレイン領域の一方は、配線5106によってソース配線(5019aと5019bの積層)と電気的に接続され、もう一方は、配線5107によって画素部の駆動用TFTのゲート電極と電気的に接続される。30

**【0234】**

次いで図15(C)に示すように、第3の層間絶縁膜5110を形成する。第3の層間絶縁膜5110としては、無機絶縁膜や有機絶縁膜を用いることができる。無機絶縁膜としては、CVD法によって形成された窒化珪素膜あるいは窒化酸化珪素膜や、SOG(Spin On Glass)法によって塗布された窒化珪素膜あるいは窒化酸化珪素膜等を用いることができる。また、有機絶縁膜としては、アクリル樹脂膜等を用いることができる。

**【0235】**

第3の層間絶縁膜5110によって、基板上5000に形成されたTFTによる凹凸を緩和し、平坦化することができる。特に、第3の層間絶縁膜5110は平坦化の意味合いが強いので、平坦性に優れた膜が好ましい。40

**【0236】**

次いで、ドライエッチングまたはウェットエッチングを用い、第3の層間絶縁膜5110に、配線5108に達するコンタクトホールを形成する。

**【0237】**

次いで、導電膜をパターニングして画素電極5111を形成する。本実施例の場合、導電膜としてアルミニウムトリチウムとの合金膜を用いる。勿論、公知のMgAg膜(マグネシウムと銀との合金膜)を用いても良い。画素電極5111がEL素子の陰極に相当する。陰極材料としては、周期表の1族もしくは2族に属する元素からなる導電膜もしくはそれらの元素を添加した導電膜を自由に用いることができる。50

## 【0238】

画素電極 5111 は、第3の層間絶縁膜 5110 に形成されたコンタクトホールによって、配線 5108 と電気的な接続がとられる。こうして、画素電極 5111 は、駆動用 TFT のソース領域またはドレイン領域の一方と、電気的に接続される。

## 【0239】

次いで図 15(D)に示すように、各画素間の EL 層を塗り分けるために、土手 5112 を形成する。土手 5112 としては、無機絶縁膜や有機絶縁膜を用いて形成する。無機絶縁膜としては、CVD 法によって形成された窒化珪素膜あるいは窒化酸化珪素膜や、SOG 法によって塗布された窒化珪素膜あるいは窒化酸化珪素膜等を用いることができる。また、有機絶縁膜としては、アクリル樹脂膜等を用いることができる。10

## 【0240】

ここで、土手 5112 を形成する際、ウエットエッチング法を用いることで容易にテープー形状の側壁とすることが出来る。土手 5112 の側壁が十分になだらかでないと段差に起因する EL 層の劣化が顕著な問題となってしまうため、注意が必要である。

## 【0241】

なお、画素電極 5111 と配線 5108 を電気的に接続する際に、第3の層間絶縁膜 5110 に形成したコンタクトホールの部分にも、土手 5112 を形成する。こうして、コンタクトホール部分の凹凸による、画素電極の凹凸を土手 5112 によって埋めることにより、段差に起因する EL 層の劣化を防いでいる。

## 【0242】

第3の層間絶縁膜 5110 と土手 5112 の組み合わせの例を以下に挙げる。20

## 【0243】

第3の層間絶縁膜 5110 として、プラズマ CVD 法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用い、土手 5112 としてもプラズマ CVD 法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用いる組み合わせがある。また、第3の層間絶縁膜 5110 として、SOG 法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用い、土手 5112 としても SOG 法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用いる組み合わせがある。また第3の層間絶縁膜 5110 として、SOG 法によって形成した窒化珪素膜あるいは窒化酸化珪素膜とプラズマ CVD 法によって形成した窒化珪素膜あるいは窒化酸化珪素膜の積層膜を用い、土手 5112 としてプラズマ CVD 法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用いる組み合わせがある。また、第3の層間絶縁膜 5110 として、アクリルを用い、土手 5112 としてもアクリルを用いる組み合わせがある。また、第3の層間絶縁膜 5110 として、アクリルとプラズマ CVD 法によって形成した窒化珪素膜あるいは窒化酸化珪素膜の積層膜を用い、土手 5112 としてプラズマ CVD 法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用いる組み合わせがある。また、第3の層間絶縁膜 5110 として、プラズマ CVD 法によって形成した窒化珪素膜あるいは窒化酸化珪素膜を用い、土手 5112 としてアクリルを用いる組み合わせがある。30

## 【0244】

土手 5112 中に、カーボン粒子や金属粒子を添加し、抵抗率を下げ、静電気の発生を抑制してもよい。この際、抵抗率は、 $1 \times 10^6 \sim 1 \times 10^{12} \Omega$ (好ましくは、 $1 \times 10^8 \sim 1 \times 10^{10} \Omega$ )となるように、カーボン粒子や金属粒子の添加量を調節すればよい。40

## 【0245】

次いで、土手 5112 に囲まれた、露出している画素電極 5111 上に、EL 層 5113 を形成する。

## 【0246】

EL 層 5113 としては、公知の有機発光材料や無機発光材料を用いることができる。

## 【0247】

有機発光材料としては、低分子系有機発光材料、高分子系有機発光材料、中分子系有機材料を自由に用いることができる。なお、ここでは、中分子系有機発光材料とは、昇華性を50

有さず、かつ、分子数が20以下または連鎖する分子の長さが10μm以下の有機発光材料を示すものとする。

【0248】

EL層5113は通常、積層構造である。代表的には、コダック・イーストマン・カンパニーのTangらが提案した「正孔輸送層／発光層／電子輸送層」という積層構造が挙げられる。また他にも、陰極上に電子輸送層／発光層／正孔輸送層／正孔注入層、または電子注入層／電子輸送層／発光層／正孔輸送層／正孔注入層の順に積層する構造でも良い。発光層に対して蛍光性色素等をドーピングしても良い。

【0249】

本実施例では蒸着法により低分子系有機発光材料を用いてEL層5113を形成している。

具体的には、発光層として70nm厚のトリス-8-キノリノラトアルミニウム錯体(A1q<sub>3</sub>)膜を設け、その上に、正孔注入層として20nm厚の銅フタロシアニン(CuPc)膜を設けた積層構造としている。A1q<sub>3</sub>にキナクリドン、ペリレンもしくはDCM1といった蛍光色素を添加することで発光色を制御することができる。

【0250】

なお、図15(D)では一画素しか図示していないが、複数の色、例えば、R(赤)、G(緑)、B(青)の各色に対応したEL層5113を作り分ける構成とすることができる。

【0251】

また、高分子系有機発光材料を用いる例として、正孔注入層として20nmのポリチオフェン(PEDOT)膜をスピニ塗布法により設け、その上に、発光層として100nm程度のパラフェニレンビニレン(PPV)膜を設けた積層構造によってEL層5113を構成しても良い。なお、PPVの共役系高分子を用いると、赤色から青色まで発光波長を選択できる。また、電子輸送層や電子注入層として炭化珪素等の無機材料を用いることも可能である。

【0252】

なお、EL層5113は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等が、明確に区別された積層構造を有するものに限定されない。つまり、EL層5113は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等を構成する材料が、混合した層を有する構造であってもよい。

【0253】

例えば、電子輸送層を構成する材料(以下、電子輸送材料と表記する)と、発光層を構成する材料(以下、発光材料と表記する)とによって構成される混合層を、電子輸送層と発光層との間に有する構造のEL層5113であってもよい。

【0254】

次に、EL層5113の上には、透明導電膜からなる画素電極5114を形成する。透明導電膜としては、酸化インジウムと酸化スズの化合物(ITO)、酸化インジウムと酸化亜鉛の化合物、酸化亜鉛、酸化スズ、酸化インジウム等を用いることができる。また、前記透明導電膜にガリウムを添加したものを用いてもよい。画素電極5114がEL素子の陽極に相当する。

【0255】

画素電極5114まで形成された時点でEL素子が完成する。なお、EL素子とは、画素電極(陰極)5111、EL層5113及び画素電極(陽極)5114で形成されたダイオードを指す。

【0256】

本実施例では、画素電極5114が透明導電膜によって形成されているため、EL素子が発した光は、基板5000とは逆側に向かって放射される。また、第3の層間絶縁膜5110によって、配線5106～5109が形成された層とは別の層に、画素電極5111を形成している。そのため、実施例9に示した構成と比較して、開口率を上げることができる。

【0257】

10

20

30

40

50

E L 素子を完全に覆うようにして保護膜(パッシベーション膜)5115を設けることは有効である。保護膜5115としては、炭素膜、窒化珪素膜もしくは窒化酸化珪素膜を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層で用いることができる。

#### 【0258】

なお本実施例のように、E L 素子が発した光が画素電極5114側から放射される場合、保護膜5115としては、光を透過する膜を用いる必要がある。

#### 【0259】

なお、土手5112を形成した後、保護膜5115を形成するまでの工程をマルチチャンバー方式(またはインライン方式)の成膜装置を用いて、大気開放せずに連続的に処理することは有効である。

10

#### 【0260】

なお、実際には図15(D)の状態まで完成したら、さらに外気に曝されないように、気密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィルム等)等のシーリング材でパッケージング(封入)することが好ましい。その際、シーリング材の内部を不活性雰囲気(例えは酸化バリウム)にしたり、内部に吸湿性材料(例えは酸化バリウム)を配置したりするとE L 素子の信頼性が向上する。

#### 【0261】