(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3906000号

(P3906000)

(45) 発行日 平成19年4月18日(2007.4.18)

(24) 登録日 平成19年1月19日(2007.1.19)

(51) Int.C1.

F 1

G05B 9/02 (2006.01)

B60R 16/02 (2006.01)G05B 9/02

B60R 16/02 650J

E

請求項の数 2 (全 8 頁)

(21) 出願番号

特願平11-250738

(22) 出願日

平成11年9月3日(1999.9.3)

(65) 公開番号

特開2001-75603 (P2001-75603A)

(43) 公開日

平成13年3月23日(2001.3.23)

審査請求日

平成16年6月21日(2004.6.21)

(73) 特許権者 000000929

カヤバ工業株式会社

東京都港区浜松町2丁目4番1号 世界貿易センタービル

(73) 特許権者 000005463

日野自動車株式会社

東京都日野市日野台3丁目1番地1

(74) 代理人 100076163

弁理士 嶋 宣之

(72) 発明者 萩原 慎一

東京都港区浜松町2-4-1 世界貿易センタービルカヤバ工業株式会社内

(72) 発明者 天野 教正

東京都港区浜松町2-4-1 世界貿易センタービルカヤバ工業株式会社内

最終頁に続く

(54) 【発明の名称】フェールセーフ機構

## (57) 【特許請求の範囲】

## 【請求項 1】

車両の電気的なシステムを駆動制御するドライバ回路と、このドライバ回路を制御プログラムに基づいて制御する制御部と、上記ドライバ回路に電流を供給する駆動用電源と、この駆動用電源とドライバ回路との間に接続したメインスイッチ回路と、駆動用電源とメインスイッチ回路との間に接続され、駆動用電源からメインスイッチ回路への電源供給をON, OFF制御するとともに、通常はOFF状態を維持するサブスイッチ回路と、駆動用電源が投入されたとき、一定時間のみサブスイッチ回路をON状態とするタイマー回路と、メインスイッチ回路と制御部との間に接続されたフェール検出回路と、メインスイッチより下流側で上記ドライバ回路と並列に設けられ、ドライバ回路への供給電流によりサブスイッチ回路をON状態とするとともにドライバ回路への供給電流が断たれたときにはサブスイッチ回路をOFF状態とするサブスイッチ制御手段とを備え、上記フェール検出回路が制御部の異常を検出したときには、上記メインスイッチ回路をOFFとし、駆動用電源からドライバ回路への電流供給を断つ構成にし、上記サブスイッチ回路は、互いに並列接続されている第1, 第2スイッチからなり、上記第1スイッチがタイマー回路により制御され、上記第2スイッチがサブスイッチ制御手段により制御されることを特徴とするフェールセーフ機構。

## 【請求項 2】

車両の電気的なシステムを駆動制御するドライバ回路と、このドライバ回路を制御プログラムに基づいて制御する制御部と、上記ドライバ回路に電流を供給する駆動用電源と、

10

20

この駆動用電源とドライバ回路との間に接続したメインスイッチ回路と、駆動用電源とメインスイッチ回路との間に接続され、駆動用電源からメインスイッチ回路への電源供給をON, OFF制御するとともに、通常はOFF状態を維持するサブスイッチ回路と、駆動用電源が投入されたとき、一定時間のみサブスイッチ回路をON状態とするタイマー回路と、メインスイッチ回路と制御部との間に接続されたフェール検出回路と、メインスイッチより下流側で上記ドライバ回路と並列に設けられ、ドライバ回路への供給電流によりサブスイッチ回路をON状態とするとともにドライバ回路への供給電流が断たれたときにはサブスイッチ回路をOFF状態とするサブスイッチ制御手段とを備え、上記フェール検出回路が制御部の異常を検出したときには、上記メインスイッチ回路をOFFとし、駆動用電源からドライバ回路への電流供給を断つ構成とし、上記フェール検出回路が、複数のウォッチャドッグタイマーとAND回路とを備え、それぞれのウォッチャドッグタイマーに、異なる制御プログラムから出力されるフェール検出信号を入力し、上記ウォッチャドッグタイマーの出力信号を、AND回路を介してメインスイッチ回路へ出力することを特徴とするフェールセーフ機構。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この発明は、例えば後輪操舵装置など、車両に搭載した電気的なシステムに故障が発生し、システムが停止した時、走行中に再びシステムが始動することを防止するフェールセーフ機構に関する。 20

##### 【0002】

##### 【従来の技術】

後輪操舵装置のモータの駆動や、油圧系のコントロールバルブを制御する場合において、一般的には故障発生時システムを停止させるが、車両の安全を確保するため、走行中はシステムを復帰させたくない場合がある。こうした場合、CPUに自己診断回路を備えて、上記制御プログラムが正常に動作しているかをチェックしている。そして、上記自己診断回路が、制御プログラムの異常を検出した場合には、フェール信号を出力して、ドライバ回路と駆動用電源との間に設けたスイッチを切るようにしている。このスイッチは、上記CPUからフェール信号が入力されないときには、閉じていて、フェール信号が入力されたときには、切れる仕組みになっている。 30

##### 【0003】

##### 【発明が解決しようとする課題】

上記のように、自己診断回路によってエラーを検出して、一旦、駆動用電源とドライバ回路との間のスイッチを切っても、何らかの要因でフェール信号が出力されなければ、スイッチが入ってドライバ回路に再び電源が供給される。制御プログラムが壊れてしまったのに、フェール信号がとぎれて、制御プログラムがまるで正常に動作しているような信号が出力されることもある。

そのようなことが繰り返された場合には、走行中に、制御が有効になったり、無効になったりして、走行中の車両が不安定な状態になることがある。また、駆動信号のオン・オフが繰り返されることによって、制御機構や、制御対象であるシステムが破損してしまうようなこともある。 40

##### 【0004】

この発明の目的は、システムの故障を検知したとき、ドライバ回路への電力供給を断つて、システムを確実に停止させるとともに、駆動用電源が再投入されない限り、ドライバ回路の電源供給がされないフェールセーフ機構を提供することである。

##### 【0005】

##### 【課題を解決するための手段】

第1の発明は、車両の電気的なシステムを駆動制御するドライバ回路と、このドライバ回路を制御プログラムに基づいて制御する制御部と、上記ドライバ回路に電流を供給する駆動用電源と、この駆動用電源とドライバ回路との間に接続したメインスイッチ回路と、 50

駆動用電源とメインスイッチ回路との間に接続され、駆動用電源からメインスイッチ回路への電源供給をON, OFF制御するとともに、通常はOFF状態を維持するサブスイッチ回路と、駆動用電源が投入されたとき、一定時間のみサブスイッチ回路をON状態とするタイマーハードウェアと、メインスイッチ回路と制御部との間に接続されたフェール検出回路と、メインスイッチより下流側で上記ドライバ回路と並列に設けられ、ドライバ回路への供給電流によりサブスイッチ回路をON状態とするとともにドライバ回路への供給電流が断たれたときにはサブスイッチ回路をOFF状態とするサブスイッチ制御手段とを備え、上記フェール検出回路が制御部の異常を検出したときには、上記メインスイッチ回路をOFFとし、駆動用電源からドライバ回路への電流供給を断つ構成にし、上記サブスイッチ回路は、互いに並列接続されている第1, 第2スイッチからなり、上記第1スイッチがタイマーハードウェアにより制御され、上記第2スイッチがサブスイッチ制御手段により制御される点に特徴を有する。

#### 【0006】

第2の発明は、車両の電気的なシステムを駆動制御するドライバ回路と、このドライバ回路を制御プログラムに基づいて制御する制御部と、上記ドライバ回路に電流を供給する駆動用電源と、この駆動用電源とドライバ回路との間に接続したメインスイッチ回路と、駆動用電源とメインスイッチ回路との間に接続され、駆動用電源からメインスイッチ回路への電源供給をON, OFF制御するとともに、通常はOFF状態を維持するサブスイッチ回路と、駆動用電源が投入されたとき、一定時間のみサブスイッチ回路をON状態とするタイマーハードウェアと、メインスイッチより下流側で上記ドライバ回路と並列に設けられ、ドライバ回路への供給電流によりサブスイッチ回路をON状態とするとともにドライバ回路への供給電流が断たれたときにはサブスイッチ回路をOFF状態とするサブスイッチ制御手段とを備え、上記フェール検出回路が制御部の異常を検出したときには、上記メインスイッチ回路をOFFとし、駆動用電源からドライバ回路への電流供給を断つ構成とし、上記フェール検出回路が、複数のウォッチャップタイマーとAND回路とを備え、それぞれのウォッチャップタイマーに、異なる制御プログラムから出力されるフェール検出信号を入力し、上記ウォッチャップタイマーの出力信号を、AND回路を介してメインスイッチ回路へ出力する点に特徴を有する。

#### 【0007】

**【発明の実施の形態】**

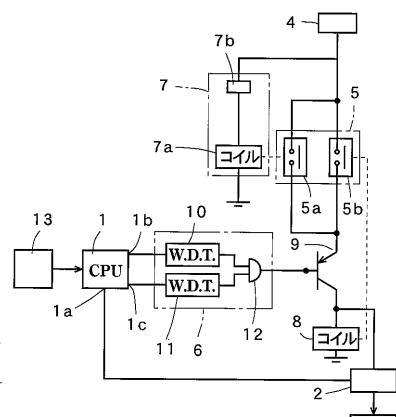

図1に示す実施例は、この発明のフェールセーフ機構を備えた、車両の後輪操舵装置などのシステムを制御する回路である。

制御部であるCPU1のポート1aをドライバ回路2に接続し、このドライバ回路2を介してアクチュエータ3を制御する。このアクチュエータ3は、図示しない後輪操舵装置のバルブユニットである。

また、上記ドライバ回路2には、この発明のメインスイッチ回路であるトランジスタ9を介して駆動用電源4を接続している。

#### 【0008】

上記トランジスタ9と駆動用電源4との間には、サブスイッチ回路5を接続している。このサブスイッチ回路5は、並列に接続した第1, 第2スイッチ5a, 5bとからなる。上記第1スイッチ5aは、上記駆動用電源4に接続したタイマーハードウェア7で制御される。このタイマーハードウェア7はコイル7aとタイマースイッチ7bとからなる。そして、駆動用電源4をONすると、タイマースイッチ7bによって一定時間だけコイル7aに電流が供給され、コイル7aが励磁すると、第1スイッチ5aが閉じるようになっている。

#### 【0009】

また、第2スイッチ5bは、コイル8が励磁されると閉じるスイッチで、このコイル8と第2スイッチ5bとの間にトランジスタ9を接続している。つまり、コイル8がこの発明のサブスイッチ制御手段である。

上記のような回路では、第1スイッチ5aまたは第2スイッチ5bが閉じ、同時にトランジ

10

20

30

40

50

ジスタ 9 に適当なベース電流が供給されたときに回路を閉じ、上記駆動用電源 4 とドライバ回路 2 間が接続される。

#### 【0010】

一方、C P U 1 のポート 1 b、1 c には、フェール検出回路 6 を接続し、このフェール検出回路 6 を上記トランジスタ 9 に接続している。

そして、C P U 1 は、上記ポート 1 b、1 c からフェール検出信号を出力する。すなわち、フェール検出回路 6 は、上記フェール検出信号に基づいて C P U 1 のエラーを検出し、フェール信号をメインスイッチ回路へ入力する回路である。なお、図中、符号 1 3 は、C P U 1 用の電源である。

#### 【0011】

また、フェール検出回路 6 は、上記 C P U 1 のポート 1 b、1 c に接続したウォッヂドッグタイマー 1 0、1 1 と、両ウォッヂドックタイマー 1 0、1 1 の出力をまとめる A N D 回路 1 2 を備えている。上記ウォッヂドックタイマー 1 0、1 1 には、C P U 1 からパルス信号が入力される。このパルス信号は、制御プログラムが正常に動作している間に、連続的に出力される信号である。そして、各ウォッヂドッグタイマー 1 0、1 1 は、上記パルス信号が入力されると、所定の電流値の H 信号を出力し、一定時間パルス信号が入力されなくなると、H 信号より電流値の低い L 信号を出力する。

なお、各ウォッヂドッグタイマー 1 0、1 1 には、異なる制御プログラムから出力されるパルス信号を入力するようにしている。このパルス信号が、この発明のフェール検出信号である。

#### 【0012】

上記ウォッヂドッグタイマー 1 0、1 1 に接続した A N D 回路 1 2 は、ウォッヂドッグタイマー 1 0、1 1 からの出力がどちらも H 信号の場合にだけ、信号を出力し、それ以外のときには信号を出力しない。つまり、両方のウォッヂドッグタイマー 1 0、1 1 にパルス信号を入力する制御プログラムがどちらも正常に作動している場合には、A N D 回路 1 2 からは電流が出力される。この電流が、上記トランジスタ 9 のベース電流となり、トランジスタ 9 に駆動用電源 4 からの電流が流れる。

#### 【0013】

しかし、制御プログラムのどちらか一方に異常が発生した場合には、異常を検出したウォッヂドッグタイマーが L 信号を出力するので、A N D 回路 1 2 からは信号が出力されない。このように信号が出力されることは、ゼロ信号を出力しているのと同じである。つまり、トランジスタ 9 のベース電流が断たれる。

#### 【0014】

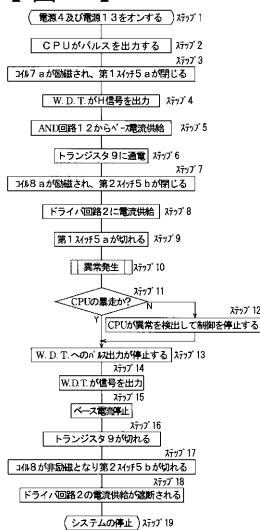

以下に、図 1 の制御回路の動作を図 2 のフローチャートを用いて説明する。なお、このフローチャートは、上記制御回路全体の動きを説明するものであり、C P U 1 の制御プログラムのステップではない。また、図 2 中、「W . D . T .」は、ウォッヂドッグタイマーのことである。

まず、ステップ 1 で駆動用電源 4 および電源 1 3 をオンにする。電源 1 3 がオンされると C P U 1 の制御プログラムが立ち上がり、正常に作動すると、ステップ 2 で、C P U 1 がウォッヂドックタイマー 1 0、1 1 へ、パルス信号を出力する。

一方、駆動用電源 4 がオンされると、ステップ 3 でタイマー回路 7 のコイル 7 a が励磁され、第 1 スイッチ 5 a が閉じる。これにより、駆動用電源 4 とトランジスタ 9 までがつながる。

#### 【0015】

その間に、両ウォッヂドッグタイマー 1 0、1 1 にパルス信号が入力されるので、ステップ 4 で、両ウォッヂドッグタイマー 1 0、1 1 から A N D 回路 1 2 へ H 信号が出力される。したがって、ステップ 5 で、上記 A N D 回路 1 2 がメインスイッチ回路のトランジスタ 9 に対し、ベース電流を供給する。これにより、ステップ 6 で、トランジスタ 9 に電流が流れる。トランジスタ 9 に電流が流れれば、コイル 8 にも電流が供給される。

ステップ 7 で、コイル 8 が励磁され、第 2 スイッチ 5 b が閉じる。これにより、ドライ

10

20

30

40

50

バ回路 2 に電流が供給される（ステップ 8）。つまり、電流は、駆動用電源 4 第 1 スイッチ 5 a トランジスタ 9 コイル 8 およびドライバ回路 2 アクチュエータ 3 と流れ、システムが作動する。このとき、ドライバ回路 2 には、上記 C P U 1 から制御プログラムに基づいた制御信号が入力されている。

#### 【0016】

上記のように、駆動用電源 4 から第 2 スイッチ 5 b およびトランジスタ 9 を介して、ドライバ回路 2 へ電源が供給されるので、所定時間経過したためにタイマー 7 b によって第 1 スイッチ 5 a が切れても（ステップ 9）、電源供給路は確保できる。したがって、上記アクチュエータ 3 に接続した図示しないシステムは作動し続ける。

ステップ 10 で、上記システムのどこかに異常が発生する。この異常が C P U 1 の暴走によるものか、その他の原因によるものかによって、フェールセーフ機構の対応の仕方が異なる。

ステップ 11 で、C P U 1 の暴走が原因の場合には、ステップ 13 へ進み、C P U 1 以外に原因がある場合には、ステップ 12 へ進む。

#### 【0017】

C P U 1 が正常な場合には、C P U 1 がシステム異常を検出することができる。そこで、異常を検出したら、ステップ 12 で C P U 1 が自ら制御を停止し、ステップ 13 で、C P U 1 からウォッチドッグタイマー 10 および 11 へのパルス出力を停止する。ステップ 14 では、ウォッチドッグタイマー 10, 11 が L 信号を出力し、A N D 回路 12 は、信号の出力をやめる。すなわち、ステップ 15 では、トランジスタ 9 のベース電流の供給を停止する。

#### 【0018】

ベース電流がなくなれば、ステップ 16 で、トランジスタ 9 の導通が切れる。ステップ 17 で、コイル 8 が非励磁となり、第 2 スイッチ 5 b が切れる。したがって、ステップ 18 でドライバ回路 2 の電流供給がストップして、システムが停止する（ステップ 19）。

ステップ 11 で、システムの異常が C P U 1 による場合には、ステップ 13 へ進む。C P U 1 は、異常を検出することができないが、制御プログラムが正常に動作していないため、パルス信号がウォッチドッグタイマー 10, 11 へ出力されない（ステップ 13）。

#### 【0019】

以降、上記と同様に、ステップ 14 ~ ステップ 19 でシステムが停止する。

上記のように、この実施例では、異常が発生した場合には、ドライバ回路 2 とこれを駆動する駆動用電源 4 との間を遮断することにより、C P U 1 で制御されるシステムを停止させ、誤動作を確実に防止するようにしている。

#### 【0020】

しかも、フェール検出回路 6 から信号が出力され、トランジスタ 9 のベース電流が供給されなくなることによって、トランジスタ 9 が一旦切れれば、図 2 のステップ 1 に戻って、駆動用電源 4 を手動でオンしない限り、切れたメインスイッチ回路がつながることはない。仮に、C P U 1 の制御プログラムが暴走しているのに、たまたまパルス信号を出力したような場合に、トランジスタ 9 にベース電流が供給されても、駆動用電源 4 とトランジスタ 9 との間が遮断されているので、ドライバ回路 2 に電源が供給されることはない。もちろん、C P U 1 の制御プログラムが復帰しても、勝手にサブスイッチ 5 がつながることはない。

したがって、エラーが発生した場合には、直ちにシステムが停止し、勝手に復帰するようなことはない。

#### 【0021】

また、上記実施例では、フェール検出回路 6 に、2 個のウォッチドッグタイマー 10, 11 を設けて、それぞれ、別の制御プログラムからパルス信号を入力するようにしている。そして、これらウォッチドッグタイマー 10, 11 からの出力信号を A N D 回路 12 に入力している。そのため、2 つの制御プログラムのうちどちらか一方でも、異常な動作をした場合には、トランジスタ 9 のベース電流の供給を止めて、メインスイッチ回路を切る

10

20

30

40

50

ことができる。

ただし、この数は、2個に限らず、1個でも、3個以上でもかまわない。ウォッチドッグタイマーの数を増やして、それぞれに別のプログラムを監視させれば、それだけフェール検出の確度が高くなる。

#### 【0022】

また、フェール検出回路6やメインスイッチ回路、サブスイッチ回路およびサブスイッチ制御手段は、上記実施例の構成に限らない。

要するに、フェール検出回路6は、CPU1から制御プログラムの異常を示す信号を入力されたら、フェール信号を出力し、それによってメインスイッチ回路を切ることができ、このメインスイッチ回路が切れることでサブスイッチ回路が切れて、復帰しなければよい

10

。

#### 【0023】

##### 【発明の効果】

この発明によれば、CPUで駆動制御されるシステムに、異常が発生した場合には、駆動用電源のドライバ回路への供給を断つようにすることによって、システムを停止させるとともに、再度駆動用電源が投入されない限り、ドライバ回路への電流供給がされないので、例えば、車両の走行中にシステムが復帰するといったことが確実に防止される。

特に、第2の発明によれば、複数の制御プログラムの異常を別々に検出し、そのなかで、ひとつでも異常を検出した場合には、システムを停止することができる。したがって、システムの誤動作をより確実に防止できる。

20

##### 【図面の簡単な説明】

##### 【図1】実施例の回路図である。

##### 【図2】実施例のフローチャートである。

##### 【符号の説明】

|     |             |    |

|-----|-------------|----|

| 1   | CPU         |    |

| 2   | ドライバ回路      |    |

| 4   | 駆動用電源       |    |

| 5   | サブスイッチ回路    |    |

| 5 a | 第1スイッチ      |    |

| 5 b | 第2スイッチ      | 30 |

| 6   | フェール検出回路    |    |

| 7   | タイマー回路      |    |

| 8   | コイル         |    |

| 9   | トランジスタ      |    |

| 10  | ウォッチドッグタイマー |    |

| 11  | ウォッチドッグタイマー |    |

| 12  | AND回路       |    |

【図1】

【図2】

---

フロントページの続き

(72)発明者 佐々木 和弘

東京都港区浜松町2-4-1 世界貿易センタービルカヤバ工業株式会社内

審査官 渡邊 豊英

(56)参考文献 特開平07-123504(JP,A)

特開平11-185830(JP,A)

特開平06-267366(JP,A)

(58)調査した分野(Int.Cl., DB名)

G05B 9/02,

B60R 16/02