(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4083581号

(P4083581)

(45) 発行日 平成20年4月30日(2008.4.30)

(24) 登録日 平成20年2月22日(2008.2.22)

(51) Int.Cl.

F 1

|         |       |           |         |       |         |

|---------|-------|-----------|---------|-------|---------|

| G 1 1 C | 19/00 | (2006.01) | G 1 1 C | 19/00 | J       |

| G 1 1 C | 19/28 | (2006.01) | G 1 1 C | 19/00 | G       |

| G 0 2 F | 1/133 | (2006.01) | G 1 1 C | 19/28 | B       |

| G 0 9 G | 3/20  | (2006.01) | G 0 2 F | 1/133 | 5 5 O   |

| G 0 9 G | 3/36  | (2006.01) | G 0 9 G | 3/20  | 6 2 2 E |

請求項の数 43 (全 43 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2002-564334 (P2002-564334)  |

| (86) (22) 出願日 | 平成14年2月7日(2002.2.7)           |

| (65) 公表番号     | 特表2004-524639 (P2004-524639A) |

| (43) 公表日      | 平成16年8月12日(2004.8.12)         |

| (86) 國際出願番号   | PCT/KR2002/000191             |

| (87) 國際公開番号   | W02002/065062                 |

| (87) 國際公開日    | 平成14年8月22日(2002.8.22)         |

| 審査請求日         | 平成16年5月12日(2004.5.12)         |

| (31) 優先権主張番号  | 2001/0007068                  |

| (32) 優先日      | 平成13年2月13日(2001.2.13)         |

| (33) 優先権主張国   | 韓国(KR)                        |

| (31) 優先権主張番号  | 2001/0048649                  |

| (32) 優先日      | 平成13年8月13日(2001.8.13)         |

| (33) 優先権主張国   | 韓国(KR)                        |

|           |                                                                                       |

|-----------|---------------------------------------------------------------------------------------|

| (73) 特許権者 | 503447036<br>サムスン エレクトロニクス カンパニー<br>リミテッド<br>大韓民国キョンギード、スウォンーシ、ヨ<br>ントン、マエタンードン 4 1 6 |

| (74) 代理人  | 110000408<br>特許業務法人高橋・林アンドパートナーズ                                                      |

| (72) 発明者  | ジエオン、ジン<br>大韓民国京畿道安養市東安区葛山洞 大宇<br>アパート 110 棟 306 号                                    |

| (72) 発明者  | キム、ヒュンギエル<br>大韓民国京畿道龍仁市水枝邑 三星來美安<br>5 次アパート 505 棟 206 号                               |

最終頁に続く

(54) 【発明の名称】シフトレジスタ及びこれを用いた液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のステージが接続され、第1ステージには開始信号が入力端子に供給され、各ステージの出力信号を順次に出力するシフトレジスタにおいて、

前記シフトレジスタの奇数番目ステージには第1クロック信号が供給され、偶数番目ステージには前記第1クロック信号と逆相の第2クロック信号が供給され、

前記ステージは、各々、

出力端子に前記第1及び第2クロック信号のうちの対応されるクロック信号を供給するプルアップ部と、

前記出力端子に第1電源電圧を供給するプルダウン部と、

前記プルアップ部の入力ノードに接続され、入力信号の前縁に応答して前記プルアップ部をターンオンさせ、次段ステージのうち一つのステージの出力信号の前縁に応答して前記プルアップ部をターンオフさせるプルアップ駆動部と、

前記プルダウン部の入力ノードに接続され、前記入力信号の前縁に応答して前記プルダウン部をターンオフさせ、前記次段ステージの中一つの出力信号の前縁に応答して前記プルダウン部をターンオンさせるプルダウン駆動部とを具備し、

前記プルダウン駆動部は前記プルダウン部の前記入力ノードに一端が接続され、第2電源電圧に他端が接続され、前記次段ステージの中一つの出力信号がゲートに供給された制御トランジスタを有することを特徴とするシフトレジスタ。

## 【請求項 2】

10

20

前記ステージは、各々、

前記プルダウン部の入力ノードに接続され、前記プルダウン部の入力ノードに前記第2電源電圧を供給して前記プルダウン部の入力ノードがフローティングされることを防止するフローティング防止部

をさらに備えることを特徴とする請求項1に記載のシフトレジスタ。

【請求項3】

複数のステージが接続され、第1ステージには開始信号が入力端子に供給され、各ステージの出力信号を順次に出力するシフトレジスタにおいて、

前記シフトレジスタの奇数番目ステージには第1クロック信号が供給され、偶数番目ステージには前記第1クロック信号と位相が違う第2クロック信号が供給され、

前記ステージは、各々、

出力端子に前記第1及び第2クロック信号のうちの対応されるクロック信号を供給するプルアップ部と、

前記出力端子に第1電源電圧を供給するプルダウン部と、

前記プルアップ部の入力ノードに接続され、入力信号の前縁に応答して前記プルアップ部をターンオンさせ、次段ステージのうち一つのステージの出力信号の前縁に応答して前記プルアップ部をターンオフさせるプルアップ駆動部と、

前記プルダウン部の入力ノードに接続され、前記入力信号の前縁に応答して前記プルダウン部をターンオフさせ、前記次段ステージの中一つの出力信号の前縁に応答して前記プルダウン部をターンオンさせるプルダウン駆動部と

を備えることを特徴とするシフトレジスタであって、

前記ステージは、各々、

前記プルダウン部の入力ノードに接続され、前記プルダウン部の入力ノードに第2電源電圧を供給して前記プルダウン部の入力ノードがフローティングされることを防止するフローティング防止部と、

前記プルダウン部の入力ノードに接続され、前記出力端子の出力信号に応答して前記プルダウン部の入力ノードに前記第1電源電圧を供給して前記プルダウン部がターンオンされることを防止するターンオン防止部

をさらに備えることを特徴とするシフトレジスタ。

【請求項4】

前記ターンオン防止部は、

ドレンが前記プルダウン部の入力ノードに接続され、ゲートが前記出力端子に接続され、ソースが第1電源電圧の供給を受けるN M O Sトランジスタにより構成されていることを特徴とする請求項3に記載のシフトレジスタ。

【請求項5】

複数のステージが接続され、第1ステージには開始信号が入力端子に供給され、各ステージの出力信号を順次に出力するシフトレジスタにおいて、

前記シフトレジスタの奇数番目ステージには第1クロック信号が供給され、偶数番目ステージには前記第1クロック信号と位相が違う第2クロック信号が供給され、

前記ステージは、各々、

出力端子に前記第1及び第2クロック信号のうちの対応されるクロック信号を供給するプルアップ部と、

前記出力端子に第1電源電圧を供給するプルダウン部と、

前記プルアップ部の入力ノードに接続され、入力信号の前縁に応答して前記プルアップ部をターンオンさせ、次段ステージのうち一つのステージの出力信号の前縁に応答して前記プルアップ部をターンオフさせるプルアップ駆動部と、

前記プルダウン部の入力ノードに接続され、前記入力信号の前縁に応答して前記プルダウン部をターンオフさせ、前記次段ステージの中一つの出力信号の前縁に応答して前記プルダウン部をターンオンさせるプルダウン駆動部と

を備えることを特徴とするシフトレジスタであって、

10

20

30

40

50

前記ステージは、各々、

前記プルダウン部の入力ノードに接続され、前記プルダウン部の入力ノードに第2電源電圧を供給して前記プルダウン部の入力ノードがフローティングされることを防止するフローティング防止部を有し、

前記プルアップ駆動部は、

前記プルアップ部の入力ノードと前記出力端子に接続されたキャパシタと、

入力信号にドレイン及びゲートが共通に接続され、前記プルアップ部の入力ノードにソースが接続された第1トランジスタと、

前記プルアップ部の入力ノードにドレインが接続され、前記プルダウン部の入力ノードにゲートが接続され、ソースが前記第1電源電圧の供給を受ける第2トランジスタと、

10

前記プルアップ部の入力ノードにドレインが接続され、次段ステージのうち一つのステージの出力信号がゲートに接続され、ソースが前記第1電源電圧の供給を受ける第3トランジスタと

を備えることを特徴とするシフトレジスタ。

**【請求項6】**

前記プルダウン駆動部は、

第2電源電圧はドレインへ供給され、次段ステージのうち一つのステージの出力信号はゲートに供給され、前記プルダウン部の入力ノードにソースが接続された第4トランジスタと、

前記プルダウン部の入力ノードにドレインが接続され、前記入力信号がゲートに接続され、ソースが前記第1電源電圧の供給を第5トランジスタと

20

を備えることを特徴とする請求項5に記載のシフトレジスタ。

**【請求項7】**

前記フローティング防止部は、

ドレイン及びゲートが共通接続されかつ前記第2電源電圧の供給をうけ、前記プルダウン部の入力ノードにソースが接続された第6トランジスタにより構成され、

前記第6トランジスタは前記第5トランジスタのサイズに比べて相対的に十分に小さいサイズに構成されている

ことを特徴とする請求項6に記載のシフトレジスタ。

30

**【請求項8】**

前記第5トランジスタと第6トランジスタのサイズ比は約20:1程度であることを特徴とする請求項7に記載のシフトレジスタ。

**【請求項9】**

基板上に形成された表示セルアレイ回路、データ駆動回路、ゲート駆動回路を含み、前記表示セルアレイ回路は複数のデータラインと複数のゲートラインを含み、各表示セルアレイ回路は対応するデータ及びゲートライン対に接続された表示装置において、

前記ゲート駆動回路は、請求項1~8のいずれかに記載されたシフトレジスタにより構成されている

ことを特徴とする表示装置。

40

**【請求項10】**

前記ゲート駆動回路に接続される外部接続端子は、第1クロック信号入力端子、第2クロック信号入力端子、開始信号入力端子、第1電源電圧入力端子及び第2電源電圧入力端子の5端子を含むことを特徴とする請求項9に記載の表示装置。

**【請求項11】**

前記表示セルアレイ回路、データ駆動回路、ゲート駆動回路のトランジスタは、a-Si-NMOS TFTにより構成されることを特徴とする請求項9に記載の表示装置。

**【請求項12】**

基板上に形成された表示セルアレイ回路、データ駆動回路、ゲート駆動回路を含み、前記表示セルアレイ回路は複数のデータラインと、複数のゲートラインとを含み、各表示セル

50

アレイ回路は対応するデータライン及びゲートライン対に接続された表示装置において、前記データ駆動回路は複数のデータラインブロック及びシフトレジスタにより構成され、前記データラインブロックはデータ入力端子とデータラインとの間にドレイン及びソースが各々接続され、ゲートがブロック選択端子に共通に接続された複数の駆動トランジスタにより構成され、

前記シフトレジスタは、請求項1～8のいずれかに記載のシフトレジスタであることを特徴とする表示装置。

**【請求項13】**

前記データ駆動回路に接続される外部接続端子は、第1クロック信号入力端子、第2クロック信号入力端子、開始信号入力端子、複数のデータ入力端子を含むことを特徴とする請求項12に記載の表示装置。 10

**【請求項14】**

前記表示セルアレイ回路、データ駆動回路、ゲート駆動回路のトランジスタは、a-Si NMOS TFTにより構成されることを特徴とする請求項12に記載の表示装置。

**【請求項15】**

複数のステージが接続され、第1ステージには開始信号が入力端子に供給され、各ステージの出力信号を順次に出力するシフトレジスタにおいて、

前記シフトレジスタの奇数番目ステージには第1クロック信号が供給され、偶数番目ステージには前記第1クロック信号と位相が違う第2クロック信号が供給され、

前記各ステージは、

出力端子に前記第1及び第2クロック信号のうちの対応されるクロック信号を供給するプルアップ部と、

前記出力端子に前記第1電源電圧を供給するプルダウン部と、

前記プルアップ部の入力ノードに接続され、入力信号の前縁に応答してキャパシタを充電して前記プルアップ部をターンオンさせ、次段ステージのうち一つのステージの出力信号の前縁に応答して前記キャパシタを放電させて前記プルアップ部をターンオフさせるプルアップ駆動部と、

前記プルダウン部の入力ノードに接続され、前記プルアップ部の入力ノードと接続されて前記プルダウン部をターンオフさせ、次段ステージのうち一つのステージの出力信号の前縁に応答して前記プルダウン部をターンオンさせるプルダウン駆動部と

を備えることを特徴とし、

前記プルアップ駆動部は、

前記プルアップ部の入力ノードと前記出力端子に接続されたキャパシタと、

ドレインが第2電源電圧入力端子に接続され、入力信号にゲートが接続され、前記プルアップ部の入力ノードにソースが接続された第1トランジスタと、

前記プルアップ部の入力ノードにドレインが接続され、次段ステージのうち一つのステージの出力信号にゲートが接続され、ソースが第1電源電圧入力端子に接続された第2トランジスタと、

前記プルアップ部の入力ノードにドレインが接続され、前記プルダウン部の入力ノードにゲートが接続され、ソースが第1電源電圧入力端子に接続された第3トランジスタとを備えることを特徴とするシフトレジスタ。 40

**【請求項16】**

前記第1トランジスタと第3トランジスタのサイズ比は約2：1程度であることを特徴とする請求項15に記載のシフトレジスタ。

**【請求項17】**

前記プルダウン駆動部は、

第2電源電圧入力端子にドレインとゲートが共通に接続され、ソースが前記プルダウン部の入力ノードに接続された第4トランジスタと、

前記プルダウン部の入力ノードにドレインが接続され、前記プルアップ部の入力ノードにゲートが接続され、ソースが第1電源電圧入力端子と接続された第5トランジスタと

10

20

30

40

50

を備えることを特徴とする請求項1\_5に記載のシフトレジスタ。

**【請求項 1\_8】**

前記第4トランジスタと第5トランジスタのサイズ比は約16:1程度であることを特徴とする請求項1\_7に記載のシフトレジスタ。

**【請求項 1\_9】**

複数のステージが接続され、第1ステージには開始信号が入力端子に接続され、各ステージの出力信号を順次に出力するシフトレジスタにおいて、

前記シフトレジスタの奇数番目ステージには第1クロック信号が供給され、偶数番目ステージには前記第1クロック信号と位相が違う第2クロック信号が供給され、

前記ステージは、各々、

10

前記第1クロック信号または第2クロック信号がドレインに接続され、第1ノードにゲートが接続され、出力端子にソースが接続されたプルアップトランジスタと、

出力端子にドレインが接続され、第2ノードにゲートが接続され、ソースが第1電源電圧入力端子に接続されたプルダウントランジスタと、

前記第1ノードと前記出力端子間に接続されたキャパシタと、

ドレインが第2電源電圧入力端子に接続され、入力信号にゲートが接続され、ソースが前記第1ノードに接続された第1トランジスタと、

前記第1ノードにドレインが接続され、次段ステージのうち一つのステージの出力信号がゲートに接続され、ソースが第1電源電圧入力端子に接続された第2トランジスタと、

前記第1ノードにドレインが接続され、前記第2ノードにゲートが接続され、ソースが前記第1電源電圧入力端子に接続された第3トランジスタと、

20

前記第2電源電圧入力端子にドレインとゲートが共通に接続され、ソースが前記第2ノードに接続された第4トランジスタと、

前記第2ノードにドレインが接続され、前記第1ノードにゲートが接続され、ソースが前記第1電源電圧入力端子と接続された第5トランジスタと

を備えることを特徴とするシフトレジスタ。

**【請求項 2\_0】**

前記第1トランジスタと第3トランジスタのサイズ比は約2:1程度であることを特徴とする請求項1\_9に記載のシフトレジスタ。

**【請求項 2\_1】**

30

前記第4トランジスタと第5トランジスタのサイズ比は約16:1程度であることを特徴とする請求項1\_9に記載のシフトレジスタ。

**【請求項 2\_2】**

前記トランジスタはa-Si NMOS TFTにより構成されることを特徴とする請求項1\_9に記載のシフトレジスタ。

**【請求項 2\_3】**

複数のステージが接続され、第1ステージには開始信号が入力端子に接続され、各ステージの出力信号を順次に出力するシフトレジスタにおいて、

前記シフトレジスタの奇数番目ステージの第1クロック端子と第2クロック端子には、第1クロック信号と位相が違う第2クロック信号が各々供給され、偶数番目ステージの第1クロック端子と第2クロック端子には前記第2クロック信号と前記第1クロック信号が各々供給され、

40

前記ステージは、各々、

前記開始信号または前段ステージのうち一つのステージの出力信号が入力信号に供給される入力端子と、

対応するゲートラインが接続された出力端子と、

次々段ステージの第2制御端子が接続された第1制御端子と、

第2制御端子と、

対応するクロック信号が入力されるクロック端子と、

出力端子に前記第1及び第2クロック信号のうちの対応されるクロック信号を供給するブ

50

ルアッピング部と、

前記出力端子に第1電源電圧を供給するプルダウン部と、

前記プルアップ部の入力ノードに接続され、入力信号の前縁に応答して前記プルアップ部をターンオンさせ、前記第1制御端子に供給される制御信号の前縁に応答して前記プルアップ部をターンオフさせるプルアップ駆動部と、

前記プルダウン部の入力ノードに接続され、前記プルアップ部の入力ノードと接続されて前記プルダウン部をターンオフさせ、次段ステージの出力信号の前縁に応答して前記プルダウン部をターンオンさせるプルダウン駆動部と

を備えることを特徴とするシフトレジスタ。

**【請求項24】**

10

前記プルアップ駆動部は、

前記プルアップ部の入力ノードと前記出力端子に接続されたキャパシタと、

ドレイン及びゲートが共通接続されて入力信号の供給を受け、前記プルアップ部の入力ノードにソースが接続された第1トランジスタと、

前記プルアップ部の入力ノードにドレインが接続され、次々段ステージの出力信号にゲートが接続され、第1電源電圧入力端子にソースが接続された第2トランジスタと

を備えることを特徴とする請求項23に記載のシフトレジスタ。

**【請求項25】**

前記第1トランジスタは、共通接続されたゲートとドレインを通じて、前段ステージのうち一つのステージから開始信号または入力信号の供給を受けて、ソースを通じて前記キャパシタを充電することを特徴とする請求項24に記載のシフトレジスタ。

20

**【請求項26】**

前記プルアップ駆動部は、次々段ステージの第2制御端子から供給されるプルアップ制御信号を使用して前記プルアップ部の制御信号を放電することを特徴とする請求項24に記載のシフトレジスタ。

**【請求項27】**

基板上に形成された表示セルアレイ回路、データ駆動回路、ゲート駆動回路を含み、前記表示セルアレイ回路は複数のデータラインと複数のゲートラインを含み、各表示セルアレイ回路は対応するデータ及びゲートライン対に接続された表示装置において、

前記ゲート駆動回路は、請求項23～26いずれかに記載のシフトレジスタにより構成され

れている

30

ことを特徴とする表示装置。

**【請求項28】**

複数のステージが接続され、第1ステージには開始信号が入力端子に接続され、各ステージの出力信号を順次に出力するシフトレジスタにおいて、

前記シフトレジスタの奇数番目ステージには第1クロック信号が供給され、偶数番目ステージには前記第1クロック信号と位相が違う第2クロック信号が供給され、

前記ステージは、各々、

出力端子に前記第1及び第2クロック信号のうちの対応されるクロック信号を供給するプルアップ部と、

40

前記出力端子に第1電源電圧を供給するプルダウン部と、

前記プルダウン部の入力ノードに接続され、前記入力信号の前縁に応答して前記プルダウン部をターンオフさせ、次段ステージのうち一つのステージの出力信号の前縁に応答して前記プルダウン部をターンオンさせるプルダウン駆動部と、

一端を通じて、プルアップ部の入力ノードに接続され、他端を通じて出力端子に接続されたキャパシタと、所定の外部入力制御信号に応答して前記キャパシタを強制放電させる放電部を備えて、入力信号の前縁に応答して前記キャパシタの充電を通じて前記プルアップ部をターンオンさせ、次段ステージのうち一つのステージの出力信号の前縁に応答して前記キャパシタの強制放電を通じて前記プルアップ部をターンオフさせるプルアップ駆動部と

50

を備えることを特徴とするシフトレジスタ。

【請求項 2 9】

前記プルアップ駆動部は、

前記プルアップ部の入力ノードと前記出力端子に接続されたキャパシタと、

入力信号にゲートが接続され、第2電源電圧入力端子にドレインが接続され、前記プルアップ部の入力ノードにソースが接続された第1トランジスタと、

前記プルアップ部の入力ノードにドレインが接続され、前記プルダウン部の入力ノードにゲートが接続され、ソースが第1電源電圧入力端子に接続された第2トランジスタと、

前記プルアップ部の入力ノードにドレインが接続され、次段ステージのうち一つのステージの出力信号にゲートが接続され、ソースが第1電源電圧入力端子に接続された第3トランジスタと、

10

前記プルアップ部の入力ノードにドレインが接続され、前記第1電源電圧入力端子にソースが接続され、ゲートが外部入力制御信号の供給を受ける前記キャパシタを強制放電させる第4トランジスタと

を備えることを特徴とする請求項2 8に記載のシフトレジスタ。

【請求項 3 0】

前記プルアップ駆動部は、

前記プルアップ部の入力ノードと前記出力端子に接続されたキャパシタと、

入力信号にゲートが接続され、第2電源電圧入力端子にドレインが接続され、前記プルアップ部の入力ノードにソースが接続された第1トランジスタと、

20

前記プルアップ部の入力ノードにドレインが接続され、前記プルダウン部の入力ノードにゲートが接続され、第1電源電圧入力端子にソースが接続された第2トランジスタと、

前記プルアップ部の入力ノードにドレインが接続され、次段ステージのうち一つのステージの出力信号にゲートが接続され、ソースが外部入力制御信号の供給を受けて前記キャパシタを強制放電させる第3トランジスタと

前記キャパシタを強制放電させる第3トランジスタと

を備えることを特徴とする請求項2 8に記載のシフトレジスタ。

【請求項 3 1】

前記第2トランジスタと第3トランジスタのソースは、共通接続されていることを特徴とする請求項3 0に記載のシフトレジスタ。

【請求項 3 2】

前記外部入力制御信号は、前記第2電源電圧の印加と同時に非アクティブ状態を維持し、前記キャパシタを強制放電させ、第1ステージに印加される開始信号発生前にアクティブ状態であることを特徴とする請求項3 0に記載のシフトレジスタ。

30

【請求項 3 3】

前記外部入力制御信号は、前記第2電源電圧の印加と同時に非アクティブ状態を維持し、前記キャパシタを強制放電させ、第1ステージに印加される開始信号発生前アクティブ状態であることを特徴とする請求項3 1に記載のシフトレジスタ。

【請求項 3 4】

前記外部入力制御信号のレベルは、前記第2電源電圧の印加時、前記第3トランジスタをターンオンさせるレベルであり、第1ステージに開始信号が印加される前に前記第3トランジスタをターンオフさせるレベルであることを特徴とする請求項3 2に記載のシフトレジスタ。

40

【請求項 3 5】

前記ターンオフレベルは第2電源電圧レベルであり、前記ターンオンレベルは第1電源電圧レベルであることを特徴とする請求項3 4に記載のシフトレジスタ。

【請求項 3 6】

基板上に形成された表示セルアレイ回路、データ駆動回路、ゲート駆動回路を含み、前記表示セルアレイ回路は複数のデータラインと複数のゲートラインを含み、各表示セルアレイ回路は対応するデータ及びゲートライン対に接続された表示装置において、

前記ゲート駆動回路は、請求項2 8～3 5いずれかに記載のシフトレジスタで構成されて

50

いる

ことを特徴とする表示装置。

**【請求項 3 7】**

複数のステージが接続され各ステージの出力信号を順次に出力するシフトレジスタにおいて、

前記ステージは、各々

第1クロック信号または前記第1クロック信号と逆相の第2クロック信号が供給されるクロック端子と、

開始信号または前段ステージのうち一つのステージの出力信号が入力信号に供給される入力端子と、

10

第1電源電圧の入力を受ける第1電源電圧と、

対応するゲートラインに接続された出力端子と、

次段ステージのうち一つの出力信号を制御信号で供給を受ける制御端子と、

前記クロック端子と前記出力端子の間に接続されターンオン時に前記第1クロック信号または第2クロック信号のデュティサイクルの間前記対応するゲートラインをプルアップさせるプルアップ部と、

前記出力端子と第1電源電圧入力端子の間に接続され、ターンオン時前記対応するゲートラインをプルダウンさせるプルダウン部と、

前記入力端子、前記制御端子及び前記プルアップ部の入力ノードと接続され、前記入力信号の前縁に応答して前記プルアップ部をターンオンさせて、前記制御信号の前縁に応答して前記プルアップ部をターンオフさせるプルアップ駆動部と、

20

前記プルダウン部の入力ノードに接続され、前記入力信号の前縁に応答して前記プルダウン部をターオフさせ、前記制御信号の前縁に応答して前記プルダウン部をターオンさせるプルダウン駆動部とを具備し、

前記プルダウン駆動部は前記プルダウン部の前記入力ノードに一端が接続され、第2電源電圧に他端が接続され、前記次段ステージの中一つの出力信号がゲートに供給された制御トランジスタを有することを特徴とするシフトレジスタ。

**【請求項 3 8】**

前記ステージは、各々、

前記プルダウン部の入力ノードと第2電源電圧入力端子の間に接続され、前記プルダウン部の入力ノードに第2電源電圧を供給して前記プルダウン部の入力ノードがフローティングされることを防止するフローティング防止部

30

をさらに含むことを特徴とする請求項3\_7記載のシフトレジスタ。

**【請求項 3 9】**

下部基板と上部基板との間に液晶を封入した液晶表示モジュールを有する液晶表示装置において、

前記下部基板上に形成され、複数のデータラインと複数のゲートラインを含み、複数の表示セルアレイ回路各々が対応するデータ及びゲートライン対に接続された表示セルアレイ回路と、

前記基板上に形成され、複数のステージが接続され、第1ステージにはスキャン開始信号が入力端子に接続され、各ステージの出力信号により前記複数のゲートラインを順次に選択する第1シフトレジスタにより構成されたゲート駆動回路と、

40

前記基板上に形成され、データ入力端子とデータラインとの間にドレイン及びソースが各々接続され、ゲートがロック選択端子に共通に接続された複数の駆動トランジスタにより構成された複数のデータラインプロックと、複数のステージが接続され、第1ステージにはロック選択開始信号が入力端子に接続され、各ステージの出力信号により前記複数のデータラインプロックを順次に選択する第2シフトレジスタにより構成されたデータ駆動回路と、

統合制御及びデータ駆動チップが実装され、前記ゲート駆動回路及びデータ駆動回路の各入力端子に制御信号及びデータ信号を供給する可撓性印刷回路基板と、を備え、

50

前記第1及び第2シフトレジスタのうち、少なくとも一つの奇数番目ステージには第1クロック信号が供給され、偶数番目ステージには前記第1クロック信号と逆相の第2クロック信号が供給され、

前記ステージは、各々、

出力端子に前記第1及び第2クロック信号のうちの対応されるクロック信号を供給するプルアップ部と、

前記出力端子に第1電源電圧を供給するプルダウン部と、

前記プルアップ部の入力ノードに接続され、入力信号の前縁に応答して前記プルアップ部をターンオンさせ、次段ステージのうち一つのステージの出力信号の前縁に応答して前記プルアップ部をターンオフさせるプルアップ駆動部と、

10

前記プルダウン部の入力ノードに接続され、前記入力信号の前縁に応答して前記プルダウン部をターンオフさせ、前記次段ステージの中一つの出力信号の前縁に応答して前記プルダウン部をターンオンさせるプルダウン駆動部とを具備し、

前記プルダウン駆動部は前記プルダウン部の前記入力ノードに一端が接続され、第2電源電圧に他端が接続され、前記次段ステージの中一つの出力信号がゲートに供給された制御トランジスタを有することを特徴とする液晶表示装置。

#### 【請求項40】

前記第1シフトレジスタに印加される第1及び第2クロック信号のデュティ期間は、前記第2シフトレジスタに印加される第1及び第2クロック信号のデュティ期間にデータラインブロックの数を乗算した期間より大きいであることを特徴とする請求項39に記載の液晶表示装置。

20

#### 【請求項41】

前記下部基板と可撓性印刷回路基板を接続する外部接続端子は、

ゲート駆動回路に接続される第1クロック信号入力端子、第2クロック信号入力端子、スキャン開始信号入力端子、第1電源電圧入力端子及び第2電源電圧入力端子の5端子と、

データ駆動回路に接続される第1クロック信号入力端子、第2クロック信号入力端子及びブロック選択開始信号入力端子の制御用3端子と複数のデータ入力端子と、を含むことを特徴とする請求項39に記載の液晶表示装置。

#### 【請求項42】

30

下部基板と上部基板との間に液晶を封入した液晶表示モジュールを有する液晶表示装置において、

前記下部基板上に形成され、複数のデータラインと複数のゲートラインを含み、複数の表示セルアレイ回路各々が対応するデータ及びゲートライン対に接続された表示セルアレイ回路と、

前記基板上に形成され、複数のステージが接続され、第1ステージにはスキャン開始信号が入力端子に接続され、各ステージの出力信号により前記複数のゲートラインを順次に選択する第1シフトレジスタにより構成されたゲート駆動回路と、

前記基板上に形成され、データ入力端子とデータラインとの間にドレイン及びソースが各々接続され、ゲートがブロック選択端子に共通に接続された複数の駆動トランジスタにより構成された複数のデータラインブロックと、複数のステージが接続され、第1ステージにはブロック選択開始信号が入力端子に接続され、各ステージの出力信号により前記複数のデータラインブロックを順次に選択する第2シフトレジスタにより構成されたデータ駆動回路と、

40

統合制御及びデータ駆動チップが実装され、前記ゲート駆動回路及びデータ駆動回路の各入力端子に制御信号及びデータ信号を供給する可撓性印刷回路基板と、を備え、

前記第1及び第2シフトレジスタのうち、少なくとも一つの奇数番目ステージには第1クロック信号が供給され、偶数番目ステージには前記第1クロック信号と位相が違う第2クロック信号が供給され、

前記ステージは、各々、

50

出力端子に前記第1及び第2クロック信号のうちの対応されるクロック信号を供給する

プルアップ部と、

前記出力端子に第1電源電圧を供給するプルダウン部と、

前記プルアップ部の入力ノードに接続され、入力信号の前縁に応答して前記プルアップ

部をターンオンさせ、次段ステージのうち一つのステージの出力信号の前縁に応答して前記

プルアップ部をターンオフさせるプルアップ駆動部と、

前記プルダウン部の入力ノードに接続され、前記入力信号の前縁に応答して前記プルダ

ウン部をターンオフさせ、前記次段ステージの中一つの出力信号の前縁に応答して前記プ

ルダウン部をターンオンさせるプルダウン駆動部と、を備え、

前記ステージは、各々、

10

前記プルダウン部の入力ノードに接続され、前記プルダウン部の入力ノードに第2電源

電圧を供給して前記プルダウン部の入力ノードがフローティングされることを防止するフ

ロー・ティング防止部と、

前記プルダウン部の入力ノードに接続され、前記出力端子の出力信号に応答して前記プ

ルダウン部の入力ノードに前記第1電源電圧を供給して前記プルダウン部がターンオンさ

れることを防止するターンオン防止部と、

をさらに備えることを特徴とする液晶表示装置。

【請求項43】

下部基板と上部基板との間に液晶を封入した液晶表示モジュールを有する液晶表示装置

において、

20

前記下部基板上に形成され、複数のデータラインと複数のゲートラインを含み、複数の

表示セルアレイ回路各々が対応するデータ及びゲートライン対に接続された表示セルアレ

イ回路と、

前記基板上に形成され、複数のステージが接続され、第1ステージにはスキャン開始信

号が入力端子に接続され、各ステージの出力信号により前記複数のゲートラインを順次に

選択する第1シフトレジスタにより構成されたゲート駆動回路と、

前記基板上に形成され、データ入力端子とデータラインとの間にドレイン及びソースが

各々接続され、ゲートがロック選択端子に共通に接続された複数の駆動トランジスタに

より構成された複数のデータラインブロックと、複数のステージが接続され、第1ステー

ジにはロック選択開始信号が入力端子に接続され、各ステージの出力信号により前記複

数のデータラインブロックを順次に選択する第2シフトレジスタにより構成されたデータ

駆動回路と、

30

統合制御及びデータ駆動チップが実装され、前記ゲート駆動回路及びデータ駆動回路の

各入力端子に制御信号及びデータ信号を供給する可撓性印刷回路基板とを備え、

前記第1及び第2シフトレジスタのうち、少なくとも一つの奇数番目ステージには第1

クロック信号が供給され、偶数番目ステージには前記第1クロック信号と位相が違う第2

クロック信号が供給され、

前記ステージは、各々、

出力端子に前記第1及び第2クロック信号のうちの対応されるクロック信号を供給する

プルアップ部と、

40

前記出力端子に第1電源電圧を供給するプルダウン部と、

前記プルアップ部の入力ノードに接続され、入力信号の前縁に応答して前記プルアップ

部をターンオンさせ、次段ステージのうち一つのステージの出力信号の前縁に応答して前記

プルアップ部をターンオフさせるプルアップ駆動部と、

前記プルダウン部の入力ノードに接続され、前記入力信号の前縁に応答して前記プルダ

ウン部をターンオフさせ、前記次段ステージの中一つの出力信号の前縁に応答して前記プ

ルダウン部をターンオンさせるプルダウン駆動部と、を備え、

前記ステージは、各々、

前記プルダウン部の入力ノードに接続され、前記プルダウン部の入力ノードに第2電源

電圧を供給して前記プルダウン部の入力ノードがフローティングされることを防止するフ

ロー・ティング防止部と、

50

ローティング防止部を有し、

前記プルアップ駆動部は、

前記プルアップ部の入力ノードと前記出力端子に接続されたキャパシタと、

入力信号にドレイン及びゲートが共通に接続され、前記プルアップ部の入力ノードにソースが接続された第1トランジスタと、

前記プルアップ部の入力ノードにドレインが接続され、前記プルダウン部の入力ノードにゲートが接続され、ソースが前記第1電源電圧の供給を受ける第2トランジスタと、

前記プルアップ部の入力ノードにドレインが接続され、次段ステージのうち一つのステージの出力信号がゲートに接続され、ソースが前記第1電源電圧の供給を受ける第3トランジスタと、を備えることを特徴とする液晶表示装置。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置のシフトレジスタ及びこれを利用した液晶表示装置に関するものであり、より詳細には、AM TFT - LCD (Active Matrix Thin Film Transistor Liquid Crystal Display : アクティブマトリックス薄膜トランジスタ液晶表示装置) のゲートライン駆動回路においてゲートラインをスキャンするためのスキャン信号を発生するためのシフトレジスタ、及びデータラインブロック駆動回路においてデータラインのブロックを選択するためのシフトレジスタに関するものである。 20

【背景技術】

【0002】

最近、情報処理機器は、多様な形態、多様な機能、より高速の情報処理速度を有するように急速に発展している。このような情報処理装置で処理される情報は、電気信号の形態を有する。使用者が情報処理装置で処理された情報を目で確認するためには、インターフェース機能を有するディスプレイ装置を必要とする。

また、最近、CRT方式のディスプレイ装置に比べて、軽量、小型でありながら、フルカラー、高解像度化などの特徴を有する液晶表示装置の開発が進んでいる。

【0003】

液晶表示装置は、液晶の特定の分子配列に電圧を印加して異なる分子配列へ変換させ、このような分子配列により発光する液晶セルの複屈折性、旋光性、2色性及び光散乱特性などの光学的性質の変化を視覚変化へ変換することで、液晶セルによる光の変調を利用したディスプレイである。 30

【0004】

液晶表示装置は、大別すると、TN (Twisted Nematic) 方式とSTN (Super-Twisted Nematic) 方式に分かれ、駆動方式の差異で分けると、スイッチング素子及びTN液晶を利用したアクティブマトリックス (Active matrix) 表示方式と、STN液晶を利用したパッシブマトリックス (Passive matrix) 表示方式がある。

【0005】

この二つ方式の大きな差異は、アクティブマトリックス表示方式がTFT (薄膜トランジスタ) をスイッチとして利用して、液晶表示装置を駆動するTFT-LCDに使用される表示方式であるに対し、パッシブマトリックス表示方式がトランジスタを使用しないので、該トランジスタと関連した複雑な回路を必要としない表示方式であるという点である。

【0006】

TFT-LCDは、a-Si TFT LCDとpoly-Si TFT LCDに区分される。poly-Si TFT LCDは、消費電力が小さく、価格が高くないが、a-Si TFT LCDに比べて、TFT製造工程が複雑であるという短所がある。したがって、poly-Si TFT LCDは、IMT-2000フォンのディスプレイ 50

のような小型ディスプレイ装置に主に適用される。

a - Si TFT LCD は、大面積化が容易であって生産性が高く、主にノートブックPC、LCDモニタ、HDTVなどの大画面ディスプレイ装置に主に適用される。

#### 【0007】

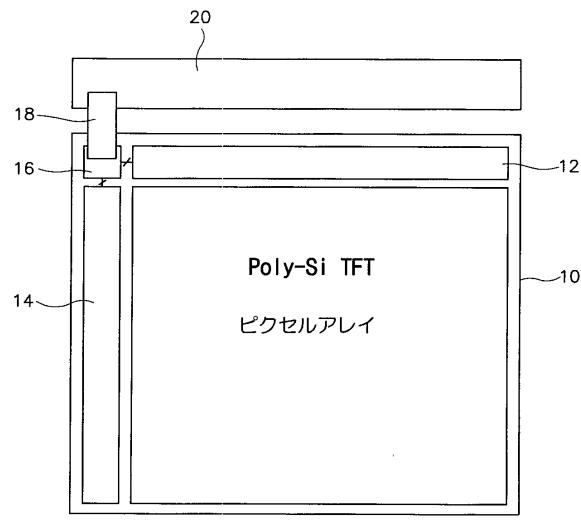

図1に示すように、poly-Si TFT LCD は、ピクセルアレイが形成されたガラス基板10上にデータ駆動回路12及びゲート駆動回路14を形成し、端子部16と集積プリント回路基板20をフィルムケーブル18により接続する。このような構造は、製造原価を節減し、駆動回路の一体化により電力損失を最少化することができる。

#### 【0008】

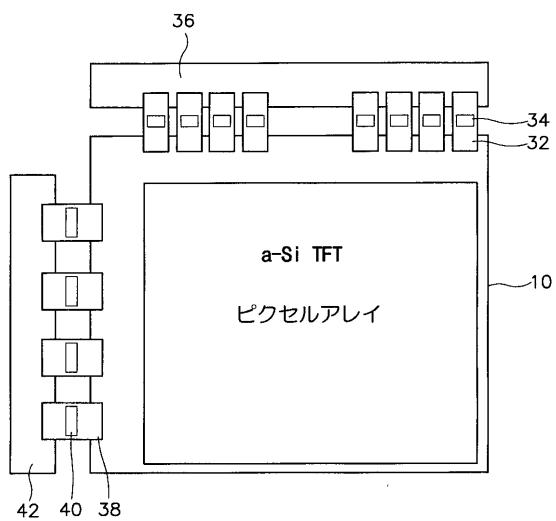

一方、図2に示すように、a - Si TFT LCD は、可撓性プリント回路基板上にCOF (CHIP ON FILM) 方式にデータ駆動チップ34を形成し、可撓性プリント回路基板を通じてデータプリント回路基板36とピクセルアレイのデータライン端子部を接続する。また、可撓性プリント回路基板上には、前述したCOF方式によりゲート駆動チップ40を形成し、可撓性プリント回路基板を通じて、ゲートプリント回路基板42とピクセルアレイのゲートライン端子部を接続する。

#### 【0009】

また、最近、ゲート電源供給部をデータプリント回路基板に実装する集積プリント回路基板技術を利用して、ゲートプリント回路基板を不要にする技術が紹介されている。以下の特許文献1は、ゲート印刷回路基板を除去した統合印刷回路基板を利用したLCDモジュールを開示する。

#### 【0010】

しかし、統合印刷回路基板を利用してても、ゲート駆動回路が形成された可撓性プリント回路基板は、そのままに使用する。したがって、複数の可撓性プリント回路基板をガラス基板に組立てる工程を実施するために、a - Si TFT LCD は、poly-Si TFT LCD に比べて、OLB (OUTER LEAD BONDING) 工程が複雑であるので、製造原価が高くなる。

#### 【0011】

上記した観点から、最近では、a - Si TFT LCDにおいても、poly-Si TFT LCD のように、ガラス基板上にデータ駆動回路及びゲート駆動回路をピクセルアレイと同時に形成することにより、組立工程の数を減少させるための技術開発が行われようとしている。

#### 【0012】

以下の特許文献2は、ガラス基板上に形成されたa - Si TFT ゲート駆動回路に関する技術を開示している。

特許文献2におけるゲート駆動回路のシフトレジスタは、3個のクロック信号を使用する。シフトレジスタの各ステージは、3個のクロック信号のうち、2個のクロック信号を使用し、前段ステージの出力信号が入力されるとイネーブルされ、次段(第2)ステージの出力をフィードバック入力することによりディセーブル状態を維持する。

#### 【0013】

特許文献2における各ステージは、ディセーブル状態を維持するために、プルダウントランジスタのゲートに印加される電圧をキャパシタチャージ方式で提供している。したがって、プルダウントランジスタのストレスによってプルダウントランジスタのゲートレスショルド電圧の上昇がキャパシタのチャージ電圧より高くなる場合には、ディセーブル状態でプルダウントランジスタがターンオフされる誤動作が生じる恐れがある。

特許文献2においては、このようなスレッショルド電圧上昇による誤動作を防止するために、a - Si TFT のスレッショルド電圧の上昇に比例してVDD電源電圧を上昇させる電源供給回路を用いている。

【特許文献1】韓国特公開第2000-66493号

【特許文献2】米国特許第5,517,542号

【発明の開示】

10

20

30

40

50

**【発明が解決しようとする課題】****【0014】**

本発明の目的は、プルダウン部の入力ノードを常に電源電圧と結合された状態に維持することにより、長時間使用の経年変化によって a - S i T F T のスレッショルド電圧が変動したとしても、常に安定した動作が可能であるシフトレジスタを提供することにある。

本発明の他の目的は、二つのクロック信号を使用することにより、外部回路と接続するための液晶パネル上の外部接続端子の数を最少化することができる液晶表示装置を提供することにある。

**【0015】**

10

本発明の他の目的は、基板上にデータ駆動回路を集積した a - S i 液晶表示装置を提供することにある。

本発明の別の目的は、液晶表示装置のゲートラインの駆動方法を提供することである。

本発明のさらに別の目的は、液晶表示装置のデータラインブロック駆動方法を提供することにある。

**【課題を解決するための手段】****【0016】**

上述した目的を達成するための本発明によるシフトレジスタは、複数のステージが縦属接続され、第1ステージには開始信号が入力端子に結合され、各ステージの出力信号を順次に出力するシフトレジスタにおいて、前記シフトレジスタの奇数番目ステージには第1クロック信号が提供され、偶数番目ステージには前記第1クロック信号と位相が反転された第2クロック信号が提供される。

20

**【0017】**

各ステージは、出力端子に前記第1及び第2クロック信号のうちの対応されるクロック信号を提供するプルアップ部と、前記出力端子に前記第1電源電圧を提供するプルダウン部と、前記プルアップ部の入力ノードに接続され、入力信号の先端に応答して前記プルアップ部をターンオンさせ、次段ステージの出力信号の先端に応答して前記プルアップ部をターンオフさせるプルアップ駆動部と、前記プルダウン部の入力ノードに接続され、前記入力信号の先端に応答して前記プルダウン部をターンオフさせ、次段ステージの出力信号の先端に応答して前記プルダウン部をターンオンさせるプルダウン駆動部と、プルダウン部の入力ノードに接続され、前記プルダウン部の入力ノードに常に第2電源電圧を接続して前記プルダウン部の入力ノードがフローティングされることを防止する手段をさらに備える。

30

**【0018】**

ここで、第1電源電圧はターンオフ電圧 (V<sub>OFF</sub>、V<sub>SS</sub>) であり、第2電源電圧はターンオン電圧 (V<sub>ON</sub>、V<sub>DD</sub>) である。

本発明で、各ステージは、プルダウン部の入力ノードに接続され、出力端子の出力信号に応答して前記プルダウン部の入力ノードに第1電源電圧を接続して前記プルダウン部がターンオンされることを防止する手段をさらに備えることが望ましい。

本発明で、ターンオン防止手段は、ドレインが前記プルダウン部の入力ノードに接続され、ゲートが前記出力端子に接続され、ソースが第1電源電圧に接続されたN M O Sトランジスタにより構成する。

40

**【0019】**

また、プルアップ駆動部は、プルアップ部の入力ノードと前記出力端子に接続されたキヤバシタと、入力信号にドレイン及びゲートが共通に結合され、前記プルアップ部の入力ノードにソースが接続された第1トランジスタと、プルアップ部の入力ノードにドレインが接続され、前記プルダウン部の入力ノードにゲートが接続され、ソースが第1電源電圧に接続された第2トランジスタと、プルアップ部の入力ノードにドレインが接続され、次段ステージの出力信号がゲートに結合され、ソースが第1電源電圧に接続された第3トランジスタにより構成する。

50

## 【0020】

プルダウン駆動部は、第2電源電圧にドレインが結合され、次段ステージの出力信号がゲートに結合され、前記プルダウン部の入力ノードにソースが結合された第4トランジスタと、前記プルダウン部の入力ノードにドレインが接続され、前記入力信号がゲートに結合され、ソースが第1電源電圧に接続された第5トランジスタにより構成する。

## 【0021】

フローティング防止部は、第2電源電圧にドレイン及びゲートが接続され、前記プルダウン部の入力ノードにソースが接続された第6トランジスタにより構成され、第6トランジスタは前記第5トランジスタのサイズに比べて相対的に十分に小さいサイズにより構成する。ここで、第5トランジスタと第6トランジスタのサイズ比は約20:1程度であることが望ましい。10

## 【0022】

このように構成することにより、シフトレジスタに接続される外部接続端子は、第1クロック信号入力端子、第2クロック信号入力端子、開始信号入力端子、第1電源電圧入力端子及び第2電源電圧入力端子の5端子により構成することができる。

また、本発明で第5トランジスタと第7トランジスタのサイズ比は約2:1程度であることが望ましい。

## 【0023】

上述した他の目的を達成するための本発明によるシフトレジスタは、複数のステージが縦属接続され、第1ステージには開始信号が入力端子に結合され、各ステージの出力信号を順次に出力するシフトレジスタにおいて、前記シフトレジスタの奇数番目ステージの第1クロック端子と第2クロック端子には、第1クロック信号と位相が反転する第2クロック信号が各々提供され、偶数番目ステージの第1クロック端子と第2クロック端子には前記第1クロック信号と第2クロック信号が各々提供され、前記各ステージは、前段ステージの出力端子が接続された入力端子と、対応するゲートラインが接続された出力端子と、次々段ステージの第2制御端子が接続された第1制御端子と、第2制御端子と、対応するクロック信号が入力されるクロック端子と、出力端子に前記第1及び第2クロック信号のうちの対応されるクロック信号を提供するプルアップ部と、前記出力端子に前記第1電源電圧を提供するプルダウン部と、前記プルアップ部の入力ノードに接続され、入力信号の前縁に応答して前記プルアップ部をターンオンさせ、前記第1制御端子に供給される制御信号の前縁に応答して前記プルアップ部をターンオフさせるプルアップ駆動部と、前記プルダウン部の入力ノードに接続され、前記プルアップ部の入力ノードと接続されて前記プルダウン部をターンオフさせ、次段ステージの出力信号の前縁に応答して前記プルダウン部をターンオンさせるプルダウン駆動部とを備える。20

## 【0024】

ここで、プルアップ駆動部は、プルアップ部の入力ノードと前記出力端子に接続されたキャパシタと、ドレイン及びゲートが共通結合されて入力信号に接続され、前記プルアップ部の入力ノードにソースが接続された第1トランジスタと、プルアップ部の入力ノードにドレインが接続され、次段ステージの出力信号にゲートが接続され、第1電源電圧にソースが接続された第2トランジスタとを備えることが望ましく、第1トランジスタは共通接続されたゲートとドレインを通じて、前段ステージから開始信号または入力信号の提供を受けて、ソースを通じて前記キャパシタを充電させることを特徴とする。30

## 【0025】

プルアップ駆動部は次々段ステージの第2制御端子から提供されるプルアップ制御信号を使用して前記プルアップ部の制御信号を放電させることを特徴とする。

また、プルダウン駆動部は、第1電源電圧にドレインが接続され、次段ステージの出力信号にゲートが接続され、前記プルダウン部の入力ノードにソースが接続された第3トランジスタと、ドレイン及びゲートが共通結合されて第2クロック信号に接続され、前記プルダウン部の入力ノードにソースが接続された第4トランジスタとを含むことを特徴とする。40

## 【0026】

本発明はまた、複数のステージが縦属接続され、第1ステージには開始信号が入力端子に結合され、各ステージの出力信号を順次に出力するシフトレジスタを提供するが、該シフトレジスタの奇数番目ステージには第1クロック信号が提供され、偶数番目ステージには前記第1クロック信号と位相が反転された第2クロック信号が提供され、ステージはそれぞれ、出力端子に前記第1及び第2クロック信号のうちの対応されるクロック信号を提供するプルアップ部と、出力端子に前記第1電源電圧を提供するプルダウン部と、プルダウン部の入力ノードに接続され、前記入力信号の先端に応答して前記プルダウン部をターンオフさせ、次段ステージの出力信号の先端に応答して前記プルダウン部をターンオンさせるプルダウン駆動部と、一端を通じてプルアップ部の入力ノードに接続され、他端を通じて出力端子に接続されたキャパシタと、所定の外部入力制御信号に沿って前記キャパシタを強制放電させる放電手段を備えて、入力信号の先端に応答して前記キャパシタの充電を通じて前記プルアップ部をターンオンさせ、次段ステージの出力信号の先端に応答して前記キャパシタの強制放電を通じて前記プルアップ部をターンオフさせるプルアップ駆動部とを備える。10

## 【0027】

ここで、前記プルアップ駆動部は、前記プルアップ部の入力ノードと前記出力端子に接続されたキャパシタと、入力信号にゲートが接続され、第2電源電圧にドレインが接続され、前記プルアップ部の入力ノードにソースが接続された第1トランジスタと、前記プルアップ部の入力ノードにドレインが接続され、ソースが第1電源電圧に接続された第2トランジスタと、前記プルアップ部の入力ノードにドレインが接続され、次段ステージの出力信号にゲートが結合され、ソースが第1電源電圧に接続された第3トランジスタと、前記プルアップ部の入力ノードにドレインが接続され、前記第1電源電圧にソースが接続され、ゲートが外部入力制御信号の提供を受ける前記キャパシタを強制放電させる第4トランジスタとを備える。20

## 【0028】

外部入力制御信号のレベルは、電源印加時、前記トランジスタをターンオンさせるレベルであり、第1ステージに開始信号が印加される前に前記トランジスタをターンオフさせるレベルであることを特徴とし、外部入力制御信号は、第1ステージに開始信号が印加され、最終段ステージの出力が発生する間に、前記トランジスタをターンオフさせるレベルであり、最終段ステージの出力が発生した後、前記トランジスタをターンオンさせるレベルになり、最終段ステージ内の前記キャパシタを放電することを特徴とする。30

## 【0029】

また、プルアップ駆動部は、プルアップ部の入力ノードと前記出力端子に接続されたキャパシタと、入力信号にゲートが接続され、第2電源電圧にドレインが接続され、前記プルアップ部の入力ノードにソースが接続された第1トランジスタと、プルアップ部の入力ノードにドレインが接続され、前記プルダウン部の入力ノードにゲートが接続され、第1電源電圧にソースが接続された第2トランジスタと、プルアップ部の入力ノードにドレインが接続され、次段ステージの出力信号にゲートが接続され、ソースが外部入力制御信号の提供を受けて前記キャパシタを強制放電させる第3トランジスタとを備えることが望ましく、第2トランジスタと第3トランジスタのソースは共通接続されることを特徴とし、外部入力制御信号は電源印加と同時にロー状態を維持し、前記キャパシタを強制放電させ、第1ステージに印加される開始信号発生前にハイ状態であることを特徴とする。40

## 【0030】

また、外部入力制御信号のレベルは、電源印加時、前記第3トランジスタをターンオンさせるレベルであり、第1ステージに開始信号が印加される前に前記第3トランジスタをターンオフさせるレベルであることを特徴とし、ターンオンレベルは、第2電源電圧レベルであり、前記ターンオンレベルは、第1電源電圧レベルであることを特徴とする。

## 【0031】

また、第2電源電圧は、前記第3トランジスタのゲート端子に第1電源電圧が印加され50

る場合にも前記第3トランジスタをターンオンさせるスレッショルド電圧以上であり、前記第1電源電圧より低いことが望ましく、外部入力制御信号は、第1ステージに開始信号が印加され、最終段ステージの出力が発生するの間に、前記トランジスタをターンオフさせるレベルであり、最終段ステージの出力が発生した後、前記トランジスタをターンオンさせるレベルになって最終段ステージ内のキャパシタを放電させることを特徴とする。

#### 【0032】

また、上述した目的を達成するための本発明による液晶表示装置は、透明基板上に形成された表示セルアレイ回路、データ駆動回路、ゲート駆動回路を含む。

表示セルアレイ回路は複数のデータラインと複数のゲートラインを含み、各表示セルアレイ回路は対応するデータ及びゲートライン対に接続される。

ゲート駆動回路は複数のステージが縦属接続され、第1ステージにはスキャン開始信号が入力端子に結合され、各ステージの出力信号により前記複数のゲートラインを順次に選択する第1シフトレジスタにより構成される。

#### 【0033】

データ駆動回路は、データ入力端子とデータラインとの間にドレイン及びソースが各々接続され、ゲートがブロック選択端子に共通に接続された複数の駆動トランジスタにより構成された複数のデータラインブロックと、複数のステージが縦属接続され、第1ステージにはデータラインブロック開始信号が入力端子に結合され、各ステージの出力信号により、複数のデータラインブロックを順次に選択する第2シフトレジスタにより構成される。

#### 【0034】

液晶表示装置は、可撓性印刷回路基板をさらに含み、可撓性印刷回路基板は統合制御及びデータ駆動チップが設けられ、ゲート駆動回路及びデータ駆動回路の各入力端子に制御信号及びデータ信号を提供する。

前記第1及び第2シフトレジスタは上述した第1目的のシフトレジスタを用いる。

前記第1シフトレジスタに印加される第1及び第2クロック信号のデュティ期間は、第2シフトレジスタに印加される第1及び第2クロック信号のデュティ期間にデータラインブロックの数を乗算した期間より大きい。

#### 【0035】

透明基板と可撓性印刷回路基板を接続する外部接続端子は、ゲート駆動回路に接続される第1クロック信号入力端子、第2クロック信号入力端子、スキャン開始信号入力端子、第1電源電圧入力端子及び第2電源電圧入力端子の5端子と、データ駆動回路に接続される第1クロック信号入力端子、第2クロック信号入力端子、及びデータラインブロック選択信号入力端子の制御用の3端子と複数のデータ信号入力端子とを含む。

#### 【0036】

また、上述した他の目的を達成するための本発明による液晶表示装置において、各ステージの対応するゲートライン駆動方法は、入力信号にキャパシタを充電させてクロック信号の1デュティ期間の間に出力端子に接続されたゲートラインをプルアップさせる段階と、出力端子の出力信号によりプルアップ状態を維持させる段階と、出力信号の後縁に応答してゲートラインのプルダウンを始めて、前記キャパシタの放電を始める段階と、次段ステージの出力信号に応答してゲートラインを完全プルダウンさせる段階と、プルダウン部の入力ノードに常に提供される第2電源電圧によりプルダウン状態を維持する段階とを備えることを特徴とする。

#### 【0037】

また、本発明のゲートライン駆動方法は、スキャン開始信号に応答して、複数のゲートラインを複数のステージを有するシフトレジスタに順次に駆動し、各ゲートラインの駆動は、奇数番目ゲートラインはシフトレジスタの奇数番目ステージにより第1クロック信号を順次にサンプリングし、サンプリングされた第1クロック信号の1デュティ期間の間に駆動し、偶数番目ゲートラインはシフトレジスタの偶数番目ステージにより1クロック信号と位相が反転された第2クロック信号をサンプリングし、サンプリングされた第2クロ

10

20

30

40

50

ック信号の1デュティ期間の間に駆動し、各ステージのサンプリングは前段ステージの出力信号に応答して開始し、次段ステージの出力信号に応答して終了することを特徴とする。

#### 【0038】

また、上述した他の目的を達成するための本発明による液晶表示装置のデータラインブロック駆動方法は、入力信号によりキャパシタを充電させてクロック信号の1デュティ期間の間に出力端子に接続されたデータラインブロックをイネーブルさせる段階と、出力端子の出力信号によりイネーブル状態を維持する段階と、出力信号の後縁に応答してデータラインブロックのディセーブルを開始して、前記キャパシタの放電を始める段階と、次段ステージの出力信号に応答してデータラインブロックを完全ディセーブルさせる段階と、プルダウン部の入力ノードに常に提供される第2電源電圧によりディセーブル状態を維持する段階とを備えることを特徴とする。 10

#### 【0039】

また、本発明のデータラインブロック駆動方法は、データラインブロックスキャン開始信号に応答して複数のデータラインを複数のステージを有するシフトレジスタに順次に駆動し、各データラインブロックの駆動は、奇数番目データラインブロックはシフトレジスタの奇数番目ステージにより第1クロック信号を順次にサンプリングし、サンプリングされた第1クロック信号の1デュティ期間の間に駆動し、偶数番目ゲートラインブロックはシフトレジスタの偶数番目ステージにより1クロック信号と位相が反転された第2クロック信号をサンプリングし、サンプリングされた第2クロック信号の1デュティ期間の間に駆動し、各ステージのサンプリングは前段ステージの出力信号に応答して開始し、次段ステージの出力信号に応答して終了することを特徴とする。 20

#### 【発明の効果】

#### 【0040】

本発明によると、液晶パネルのガラス基板に集積されるシフトレジスタに2個のクロック信号を使用することにより、外部接続端子の数を減少させることができ、プルダウントランジスタのゲートがディセーブル状態でフローティングされることを防止するために、持続的に第2電源電圧を供給することにより、a-Si NMOS TFTの経年変化によるスレッショルド電圧の変化に無関係に常に安定された回路動作が可能である。

また、2"パネルのように小型a-Si TFTパネルでデータ駆動方式をシフトレジスタを利用したブロック駆動方式を使用することにより、データ駆動チップとパネルとの間の接続チャンネル数を大幅的に減少させることができる。 30

#### 【発明を実施するための最良の形態】

#### 【0041】

以下、図面を参照して本発明の望ましい一実施形態をより詳細に説明する。

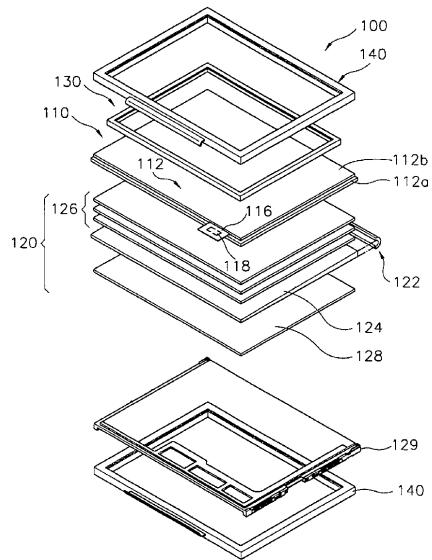

図3は、本発明によるa-Si TFT液晶表示装置の分解斜視図を示す。図3に示すように、液晶表示装置100は、液晶表示パネルアセンブリ110、バックライトアセンブリ120、シャーシ130及びカバー140を含む。

#### 【0042】

液晶表示パネルアセンブリ110は、液晶表示パネル112、可撓性プリント回路基板116、集積化された制御及びデータ駆動チップ118を含む。液晶表示パネル112は、TFT基板112aとカラーフィルタ基板112bを含む。TFT基板112aには、a-Si TFT工程により表示セルアレイ回路、データ駆動回路、ゲート駆動回路及び外部接続端子が形成される。カラーフィルタ基板112bには、カラーフィルタ及び透明共通電極が形成される。TFT基板112aとカラーフィルタ基板112bは、互いに対向され、これら間に液晶が注入された後に封入される。 40

#### 【0043】

可撓性プリント回路基板116に設けられた制御及びデータ駆動チップ118とTFT基板112aの表示セルアレイに形成されたTFTは、可撓性プリント回路基板116により電気的に接続される。可撓性プリント回路基板116は、データ信号、データタイミ 50

ング信号、ゲートタイミング信号、及びゲート駆動電圧を、TFT基板112aのデータ駆動回路及びゲート駆動回路に提供する。バックライトアセンブリ120は、ランプアセンブリ122、導光板124、光学シート126、反射板128、及びモールドフレーム129を含んでいる。

#### 【0044】

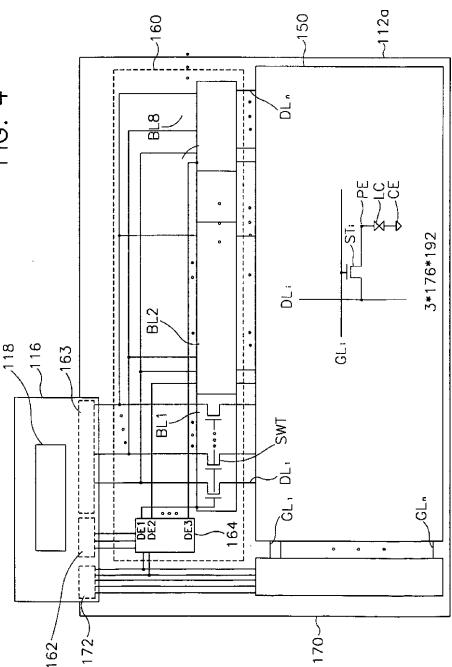

図4に示すように、本発明においては、TFT基板112a上に、表示セルアレイ150、データ駆動回路160、ゲート駆動回路170、データ駆動回路外部接続端子162、163、ゲート駆動回路外部接続端子169が、TFT工程時に共に形成される。

#### 【0045】

表示セルアレイ150は、列方向に延びたm個のデータライン(DL1～DLm)と行方向に延びたn個のゲートライン(GL1～GLn)を含む。

10

本発明の実施形態では、2インチ液晶表示パネルであり、176個のデータラインおよび192個のゲートラインを有し、 $525 (= 176 \times 3) \times 192$ の解像度を有する。

#### 【0046】

データラインとゲートラインの各交差点には、スイッチングトランジスタ(ST)が形成される。スイッチングトランジスタ(STi)のドレインはデータライン(DLi)に接続され、ゲートはゲートライン(GLi)に接続される。スイッチングトランジスタ(STi)のソースは透明画素電極(PE)に接続される。透明画素電極(PE)とカラーフィルタ基板112bに形成された透明共通電極(CE)の間に、液晶(LC)が位置することになる。

20

これにより、透明画素電極(PE)と透明共通電極(CE)間に印加された電圧により、液晶配列が制御されて通過される光量を制御して、各ピクセルのグレイ表示をすることになる。

#### 【0047】

データ駆動回路160は、シフトレジスタ164と528個のスイッチングトランジスタ(SWT)を含む。528個のスイッチングトランジスタ(SWT)は、66個ずつ8個のデータラインブロック(BL1～BL8)を形成する。

各データラインブロック(BLi)は、66個のデータ入力端子により構成された外部接続端子163に66個の入力端子が共通に接続され、対応する66個のデータラインに66個の出力端子が接続される。また、シフトレジスタ164の8個の出力端子のうちの対応する一つの出力端子にブロック選択端子が接続される。

30

#### 【0048】

528個のスイッチングトランジスタ(SWT)の各々は、対応するデータラインにソースが接続され、66個のデータ入力端子の対応する入力端子にドレインが接続され、ブロック選択端子にゲートが接続されたa-Si TFT MOSトランジスタにより構成される。

したがって、528個のデータラインは、66個ずつ8個のブロックに分割され、シフトレジスタ164の8個のブロック選択信号により、順次に各ブロックが選択される。

シフトレジスタ164は、3端子の外部接続端子162を通じて、第1クロック(CKH)、第2クロック(CKHB)、ブロック選択開始信号(STH)が提供される。シフトレジスタ164の出力端子は各々、対応するデータラインブロックのブロック選択端子に接続される。

40

#### 【0049】

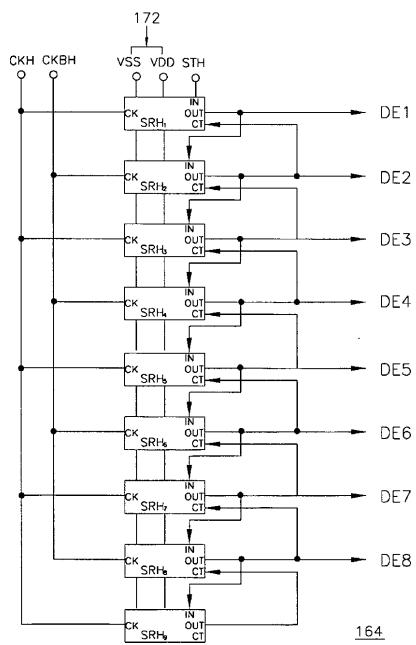

図5に示すように、本発明によるシフトレジスタ164は、9個のステージ(SRH1～SRH9)が従属接続される。即ち、各ステージの出力端子(OUT)が次段ステージの入力端子(IN)に接続される。ステージは、データラインブロックに対応する8個のステージ(SRH1～SRH8)と一つのダミーステージ(SRH9)により構成される。各ステージは、入力端子(IN)、出力端子(OUT)、制御端子(CT)、クロック入力端子(CK)、第1電源電圧端子(VSS)、第2電源電圧端子(VDD)を有する。8個のステージ(SRH1～SRH8)は、各データラインブロック(BL1～BL8)

50

) のブロック選択端子にブロック選択開始信号 ( D E 1 ~ D E 8 ) を各々提供する。ブロック選択開始信号は、各ラインブロックのイネーブル信号である。

#### 【 0 0 5 0 】

奇数番目ステージ ( S R H 1 、 S R H 3 、 S R H 5 、 S R H 7 、 S R H 9 ) には、第 1 クロック ( C K H ) が提供され、偶数番目ステージ ( S R C 2 、 S R C 4 、 S R C 6 、 S R C 8 ) には、第 2 クロック ( C K H B ) が提供される。第 1 クロック ( C K H ) と第 2 クロック ( C K H B ) は相補的な位相を有する。第 1 クロック ( C K H ) 及び第 2 クロック ( C K H B ) のデューティサイクルは、例えば 1 / 6 6 m s 以下である。

#### 【 0 0 5 1 】

各ステージの制御端子 ( C T ) には、次段ステージの出力信号が制御信号として入力される。これにより、制御端子 ( C T ) に入力される制御信号は、自身の出力信号のデューティサイクル遅延された信号になる。10

したがって、各ステージの出力信号 ( ゲートライン駆動信号 ) が順次にアクティブ ( 即ち、ハイ状態 ) となるので、各出力信号のアクティブ区間に對応するデータラインブロックが選択され、イネーブルされることになる。

ダミーステージ ( S R H 9 ) は、その前段のステージ ( S R H 8 ) の制御端子 ( C T ) に制御信号を提供するためのものである。

#### 【 0 0 5 2 】

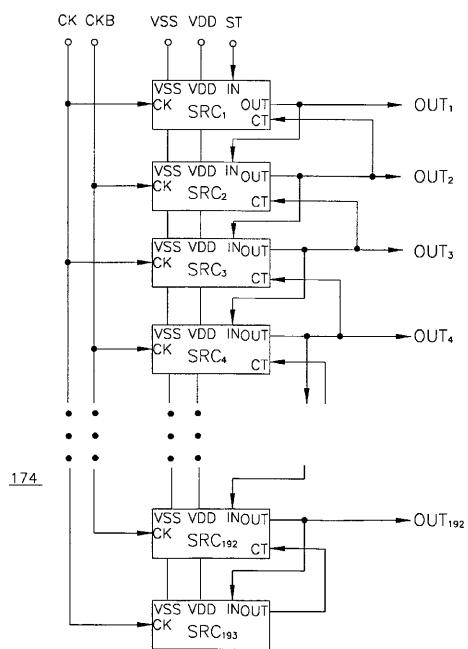

図 6 は、前述した図 4 のゲート駆動回路に利用されるシフトレジスタを説明するためのブロック図である。20

図 6 に示すように、図 4 のゲート駆動回路 1 7 0 は、一つのシフトレジスタにより構成され、該シフトレジスタは、複数のステージ ( S R C 1 ~ S R C 4 ) が縦属接続される。すなわち、各ステージの出力端子 ( O U T ) が次段ステージの入力端子 ( I N ) に接続される。複数のステージは、ゲートラインに対応する 1 9 2 個のステージ ( S R C 1 ~ S R C 1 9 2 ) と一つのダミーステージ ( S R C 1 9 3 ) を含んでいる。各ステージは、入力端子 ( I N ) 、出力端子 ( O U T ) 、制御端子 ( C T ) 、クロック入力端子 ( C K ) 、第 1 電源電圧端子 ( V S S ) 、第 2 電源電圧端子 ( V D D ) を有する。

#### 【 0 0 5 3 】

第 1 ステージ ( S R C 1 ) の入力端子 ( I N ) には、図 7 に図示した開始信号 ( S T ) が入力される。開始信号 ( S T ) は、垂直同期信号に同期されたパルス信号である。30

各ステージの出力信号 ( G O U T 1 ~ G O U T 1 9 2 ) は、対応する各ゲートラインに接続される。奇数番目ステージ ( S R C 1 、 S R C 3 、 . . . ) には、第 1 クロック信号 ( C K ) が提供され、偶数番目ステージ ( S R C 2 、 S R C 4 、 . . . ) には、第 2 クロック信号 ( C K B ) が提供される。ここで、第 1 クロック信号 ( C K ) と第 2 クロック信号 ( C K B ) は相補的な位相 ( 反対位相 ) を有する。また、第 1 クロック信号 ( C K ) と第 2 クロック信号 ( C K B ) のデューティサイクルは、例えば、 1 6 . 6 / 1 9 2 m s である。

したがって、データ駆動回路のシフトレジスタ 1 6 4 のクロック信号のデューティサイクルに比べて、ゲート駆動回路のシフトレジスタのクロック信号のデューティサイクルが約 8 倍以上になる。40

#### 【 0 0 5 4 】

各ステージ ( S R C 1 、 S R C 2 、 S R C 3 、 . . . ) の各制御端子 ( C T ) には、次段ステージ ( S R C 2 、 S R C 3 、 S R C 4 、 . . . ) の出力端子 ( G O U T 2 、 G O U T 3 、 G O U T 4 ) の制御信号が入力される。即ち、制御端子 ( C T ) に入力される制御信号は、自身の出力信号のデューティサイクル遅延された信号になる。

従って、各ステージの出力信号が順次にアクティブ ( ハイ状態 ) となるので、各出力信号のアクティブ区間に對応する水平ラインが選択されることになる。

#### 【 実施形態 1 】

#### 【 0 0 5 5 】

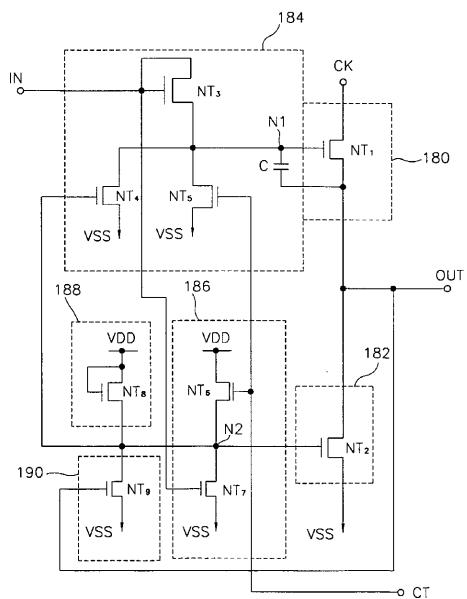

図 7 は、本発明の第 1 実施形態によるシフトレジスタの各ステージの具体回路図として50

、特に、上述した図4のデータ駆動回路及び図5のゲート駆動回路のシフトレジスタの各ステージの具体的な回路構成を示す断面図である。

図7に示すように、本発明の第1実施形態によるシフトレジスタ164、170の各ステージは、プルアップ部180、プルダウン部182、プルアップ駆動部184、プルダウン駆動部186、フローティング防止手段188、ターンオン防止手段190とを含む。

#### 【0056】

プルアップ部180は、クロック信号入力端子(CK)にドレインが接続され、第1ノード(N1)にゲートが接続され、出力端子(OUT)にソースが接続されたプルアップNMOSトランジスタ(NT1)により構成される。

プルダウン部182は出力端子(OUT)にドレインが接続され、第2ノード(N2)にゲートが接続され、ソースが第1電源電圧端子(VSS)に接続されたプルダウンNMOSトランジスタ(NT2)により構成される。

#### 【0057】

プルアップ駆動部184は、キャパシタ(C)、NMOSトランジスタ(NT3～NT5)により構成される。キャパシタ(C)は、第1ノード(N1)と出力端子(OUT)間に接続される。トランジスタ(NT3)は、入力端子(IN)にドレイン及びゲートが共通に結合され、第1ノード(N1)にソースが接続される。トランジスタ(NT4)は第1ノード(N1)にドレインが接続され、第2ノード(N2)にゲートが接続され、ソースが第1電源電圧(VSS)に接続される。トランジスタ(NT5)は第1ノード(N1)にドレインが接続され、制御端子(CT)にゲートが接続され、ソースが第1電源電圧(VSS)に接続される。

#### 【0058】

プルダウン駆動部186は、二つのトランジスタ(NT6、NT7)により構成される。トランジスタ(NT6)は、第2電源電圧(VDD)にドレインが結合され、制御端子(CT)にゲートが接続され、第2ノード(N2)にソースが接続される。トランジスタ(NT7)は第2ノード(N2)にドレインが接続され、入力端子(IN)にゲートが接続され、ソースが第1電源電圧(VSS)に接続される。

#### 【0059】

フローティング防止手段188は第2電源電圧(VDD)にドレイン及びゲートが共通接続され、第2ノード(N2)にソースが接続されたトランジスタ(NT8)により構成される。トランジスタ(NT8)はトランジスタ(NT7)のサイズに比べて相対的に十分に小さいサイズ、例えば、1：20程度のサイズ比により構成される。

#### 【0060】

ターンオン防止手段190は第2ノード(N2)にドレインが接続され、出力端子(OUT)にゲートが接続され、第1電源電圧(VSS)にソースが接続されたトランジスタ(NT9)により構成される。トランジスタ(NT9)のサイズはトランジスタ(NT7)のサイズに比べて約1：2の比を有する。

#### 【0061】

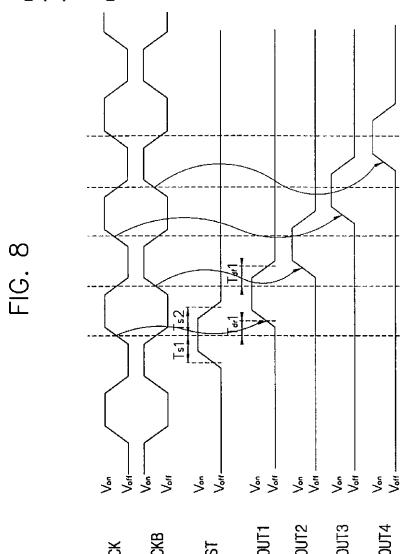

図8に示したように、第1及び第2クロック信号(CK、CKB)とスキャン開始信号(ST)がシフトレジスタ170に供給されると、第1ステージ(SRC1)では、スキャン開始信号(ST)の先端に応答して第1クロック信号(CK)のハイレベル区間を所定時間(Tdr1)遅延させて出力端子に出力信号(OUT1)に発生する。

#### 【0062】

スキャン開始信号(ST)のアクティブ区間は第1クロック信号(CK)のハイレベル区間に比べて約1/4周期先立つ位相を有する。スキャン開始信号(ST)のアクティブ区間はパルス先端、即ち、上昇エッジからのセットアップタイム(Ts1)のパルス後端、即ち、下降エッジまでのホールドタイム(Ts2)に分割される。

従って、出力信号(OUT1)の先端は、ホールドタイム(Ts2)の開始時点から所定時間約2～4μs遅延された先端、即ち、上昇エッジを有する。即ち、第1クロック信

10

20

30

40

50

号(CK)のアクティブ区間、ハイレベル区間がTd r 1時間ほど遅延されて出力端子(OUT)に出力される。

#### 【0063】

このような遅延特性は、プルアップ駆動部184のキャパシタ(C)が開始信号(ST)の先端でトランジスタ(NT4)がターンオフされた状態からトランジスタ(NT3)を通じて充電され始め、キャパシタの充電電圧がプルアップトランジスタ(NT1)のゲートソース間スレッショルド電圧以上に充電された以後に、プルアップトランジスタ(NT1)がターンオンされ、第1クロック信号(CK)のハイレベル区間が出力端子に出力され始めるからである。

#### 【0064】

出力端子(OUT)にクロック信号のハイレベルが現れ始めると、この出力電圧がキャパシタ(C)にブートストラップされ、プルアップトランジスタ(NT1)のゲート電圧がターンオン電圧(VDD)以上に上昇される。従って、NMOSトランジスタであるプルアップトランジスタ(NT1)が完全導通状態を維持することになる。

#### 【0065】

一方、プルダウン駆動部186は、トランジスタ(NT6)がターンオフされた状態で、開始信号(ST)の先端でトランジスタ(NT7)がターンオンされるので、第2ノード(N2)の電位が第1電源電圧(VSS)にダウンされる。ここで、フローティング防止手段188のトランジスタ(NT8)はターンオン状態を維持するが、ターンオンされたトランジスタ(NT7)のサイズがトランジスタ(NT8)のサイズより約20倍程度大きいために、第2ノード(N2)は第2電源電圧(VDD)状態から第1電源電圧(VSS)にダウンされる。これにより、プルダウントランジスタ(NT2)はターンオン状態からターンオフ状態に遷移される。

10

#### 【0066】

出力端子(OUT)にターンオン電圧(VON = VDD)が現れると、ターンオン防止手段190のトランジスタ(NT9)がターンオンされ、第2ノード(N2)を第1電源電圧(VSS)に駆動する能力が約50%程度さらに増加される。したがって、出力信号の上昇遷移時にプルダウントランジスタのドレインソース間寄生キャパシタにより第2ノード(N2)の電圧が上昇されることを防止することができる。従って、出力信号の上昇遷移時、プルダウントランジスタがターンオンされる誤動作を確実に防止することができる。

20

#### 【0067】

出力端子(OUT)の出力信号(OUT1)は、第1クロック信号(CK)のデュティ周期遅延されて出力される。

出力端子(OUT)の出力信号の電圧がターンオフ電圧(VOFF = VSS)状態に低下されると、トランジスタ(NT9)がターンオフされる。これにより、トランジスタ(NT8)を通じて第2ノード(N2)に第2電源電圧(VDD)が供給される状態であるので、第2ノード(N2)の電位は第1電源電圧(VSS)から第2電源電圧(VDD)に上昇され始める。第2ノード(N2)の電位が上昇され始めると、トランジスタ(NT4)がターンオンされ、これにより、キャパシタの充電電圧はトランジスタ(NT4)を通じて放電される。したがって、プルアップトランジスタ(NT1)もターンオフされ始める。

30

#### 【0068】

続いて、制御端子(CT)に提供される次段ステージの出力信号がターンオン電圧に上昇するので、これによりトランジスタ(NT5、NT6)がターンオンされる。よって、第2ノード(N2)の電位はトランジスタ(NT6、NT8)により提供される第2電源電圧(VDD)に高速で上昇され、第1ノード(N1)の電位はトランジスタ(NT4、NT5)を通じて高速で第1電源電圧(VSS)にダウンされる。

これにより、プルアップトランジスタ(NT1)はターンオフされ、プルダウントランジスタ(NT2)はターンオンされて、出力端子(OUT)はターンオン電圧(VON)

40

50

で第2電源電圧( VDD )のターンオフ電圧( VOFF )にダウンされる。

#### 【0069】

制御端子( CT )に印加される次段ステージの出力信号がローレベルに下降され、トランジスタ( NT6 )がターンオフされても、第2ノード( N2 )はトランジスタ( NT8 )を通じて第2電源電圧( VDD )にバイアスされた状態を維持することになり、第1ノード( N1 )は、ターンオン状態を維持するトランジスタ( NT4 )を介して第1電源電圧( VSS )にバイアスされた状態を維持する。したがって、長時間使用によりトランジスタ( NT2 、 NT4 )のスレッショルド電圧が上昇されても、第2ノード( N2 )の電位が第2電源電圧( VDD )に維持されるので、プルダウントランジスタ( NT2 )がターンオフされる誤動作の懼れなしに、安定された動作が確保される。

10

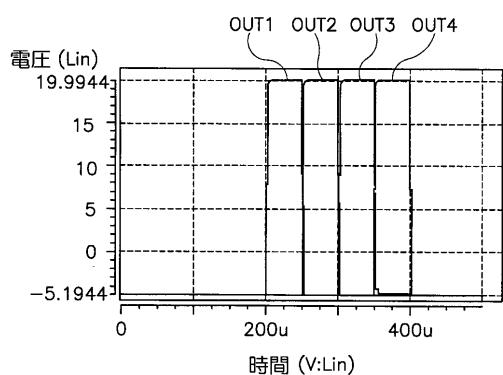

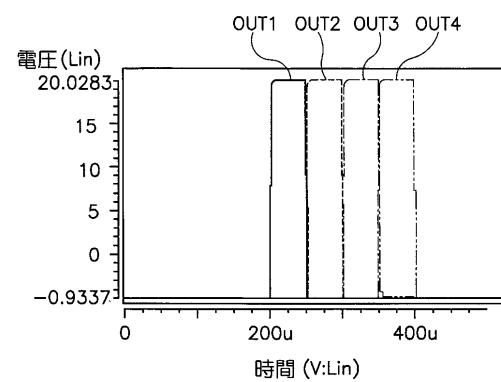

上述した動作と同一である動作により、各ステージ( SRC1 ~ SRC4 )が動作して、出力信号( OUT1 ~ OUT4 )が図9に示したように順次に安定して発生する。

#### 【0070】

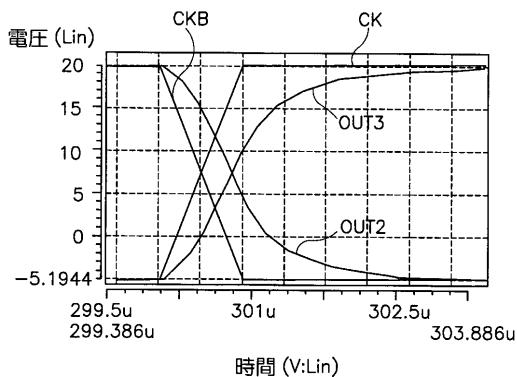

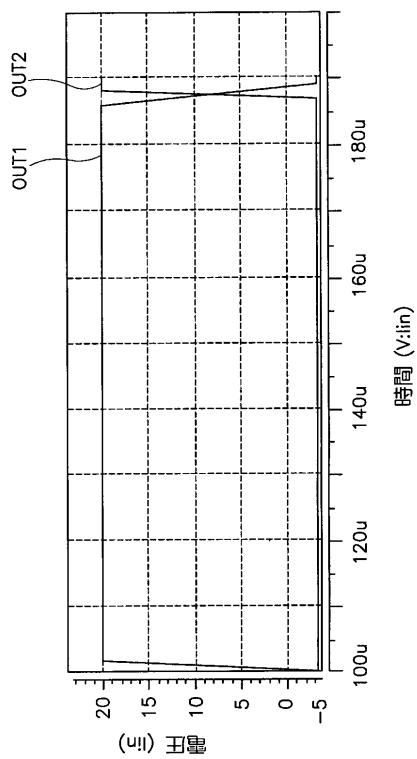

上述した本発明のシフトレジスタに2インチパネルのゲートラインロード30pFを接続し、シミュレーションした結果、図10に示すような、第1及び第2クロック信号( CK 、 CKB )に対する出力信号の遅延特性を示した。図10から、出力信号の上昇時間( Tr )及び下降時間( Tf )は約1.5μsであり、クロック信号から遅延上昇時間( Tdr )及び遅延下降時間( Tdf )は約0.3μsであることが分かる。

#### 【0071】

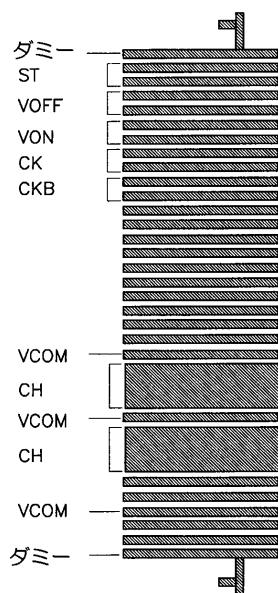

図11は、本発明による液晶パネル上に集積されたゲート駆動回路のシフトレジスタに提供される外部接続端子部のレイアウトを示す。このレイアウトにおいて、右側は TFT 側であり、左側はフィルムケーブル側である。図面に示したように、本発明では、シフトレジスタのために5個の外部接続端子、スキャン開始信号入力端子( ST )、第1クロック信号入力端子( CK )、第2クロック信号入力端子( CKB )、第1電源電圧端子( VOFF 又は VSS )、第2電源電圧端子( VON 又は VDD )のみを必要とする。従って、ガラス基板上に端子部172の空間占有率を減少させることができる。

20

#### 【0072】

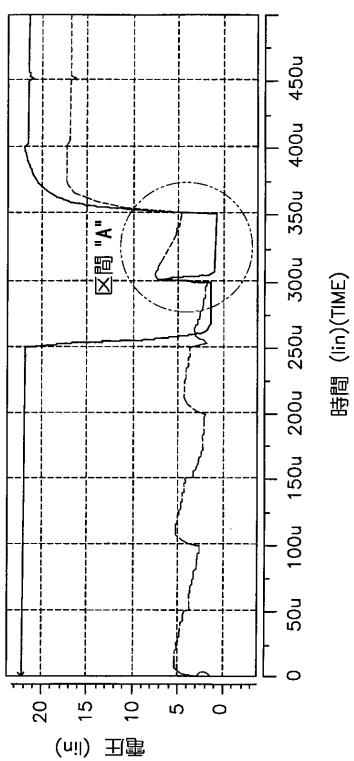

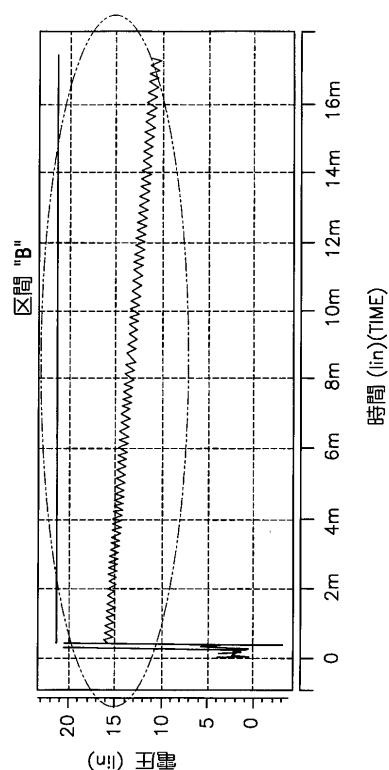

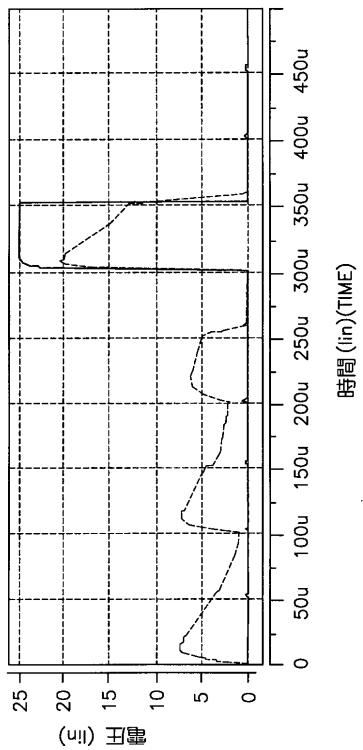

図12～図14は、従来のキャパシタを利用したプルダウン制御技術を用いたシフトレジスタの出力特性と本発明のシフトレジスタの出力特性を比較した波形図である。

図12は、第2ノード( N2 )の電圧波形を比較したものであり、区間Aにおいて、本発明( 実線 )の波形が従来技術( 鎮線 )の波形に比べてより安定されたローレベル状態を維持することが分かる。

30

#### 【0073】

図13は、時間による第2ノード( N2 )のハイレベルの状態変化を比較したものである。実線の本発明に比べて、鎮線の従来技術は、時間経過によりレベルが徐々にダウンされる現象を示すことが分かり、一方、本発明においては、VDD電源電圧がフローティング防止手段を通じて常に提供された状態を維持することにより、プルダウン維持期間の間、常に一定なレベル状態を維持することができる。

#### 【0074】

図14は、出力端子の出力信号の波形を比較したものである。鎮線の従来技術の出力信号の波形に比べて、実線の本発明の出力信号の波形がアクティブ状態( ハイレベル )により確実であるハイレベル状態を維持し、ノンアクティブ状態( ローレベル )でも変動なしに安定されるように、ローレベルにバイアスされることが分かる。

40

#### 【実施形態2】

#### 【0075】

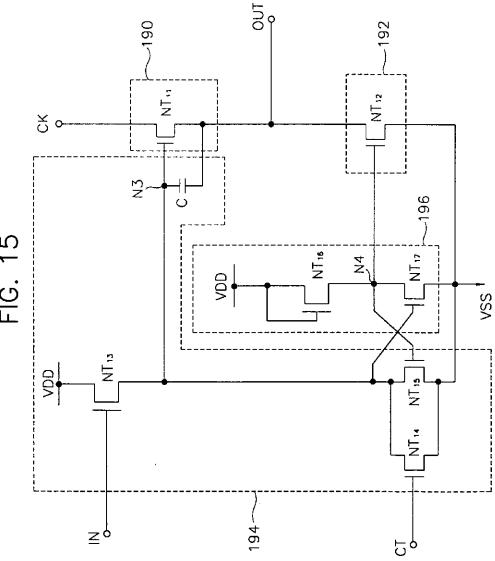

図15は、本発明の第2実施形態によるシフトレジスタの各ステージの具体的回路図として、特に、上述した図4のデータ駆動回路及びゲート駆動回路のシフトレジスタの各ステージの具体的な回路構成を示す図である。

図15に示すように、シフトレジスタ164、170の各ステージは、プルアップ部190、プルダウン部192、プルアップ駆動部194、プルダウン駆動部196とを含む

50

。

### 【0076】

プルアップ部190は、クロック信号入力端子(CK)にドレインが接続され、第3ノード(N3)にゲートが接続され、出力端子(OUT)にソースが接続されたプルアップNMOSトランジスタ(NT11)により構成される。

プルダウン部192は、出力端子(OUT)にドレインが接続され、第4ノード(N4)にゲートが接続され、ソースが第1電源電圧端子(VSS)に接続されたプルダウンNMOSトランジスタ(NT12)により構成される。

### 【0077】

プルアップ駆動部194は、キャパシタ(C)、NMOSトランジスタ(NT13～NT15)により構成される。キャパシタ(C)は、第3ノード(N3)と出力端子(OUT)間に接続される。トランジスタ(NT13)は、第2電源電圧(VDD)にドレインが接続され、入力端子(IN)にゲートが接続され、第3ノード(N3)にソースが接続される。トランジスタ(NT14)は、第3ノード(N3)にドレインが接続され、制御端子(CT)にゲートが接続され、ソースが第1電源電圧(VSS)に接続される。トランジスタ(NT15)は、第3ノード(N3)にドレインが接続され、第4ノード(N4)にゲートが接続され、ソースが第1電源電圧(VSS)に接続される。ここで、トランジスタ(NT13)のサイズは、トランジスタ(NT15)のサイズより約2倍程度大きく形成される。

### 【0078】

プルダウン駆動部196は、二つのトランジスタ(NT16、NT17)により構成される。トランジスタ(NT16)は、第2電源電圧(VDD)にドレインとゲートが共通に結合され、第4ノード(N4)にソースが接続される。トランジスタ(NT17)は、第4ノード(N4)にドレインが接続され、第3ノード(N3)にゲートが接続され、ソースが第1電源電圧(VSS)に結合される。ここで、トランジスタ(NT16)のサイズは、トランジスタ(NT17)のサイズより約16倍程度大きく形成される。

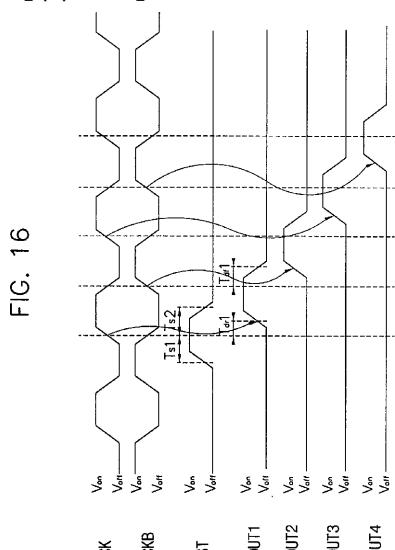

### 【0079】

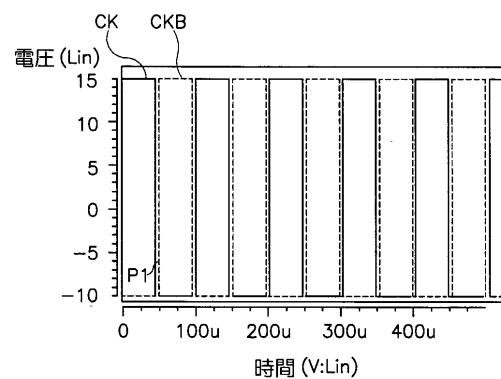

図16に図示したように、第1及び第2クロック信号(CK、CKB)とスキャン開始信号(ST)がシフトレジスタ170に供給されると、第1ステージ(SRC1)では、スキャン開始信号(ST)の先端(前縁)に応答して第1クロック信号(CK)のハイレベル区間を所定時間(Tdr1)遅延させて出力端子に出力信号(OUT1)に発生する。

### 【0080】

スキャン開始信号(ST)のアクティブ区間は、第1クロック信号(CK)のハイレベル区間に比べて約1/4周期先立つ位相を有する。スキャン開始信号(ST)のアクティブ区間は、パルス先端、即ち、上昇エッジからのセットアップタイム(Ts1)のパルス後端(後縁)、即ち、下降エッジまでのホールドタイム(Ts2)に分割される。

従って、出力信号(OUT1)の先端は、ホールドタイム(Ts2)の開始時点から所定時間である約2～4μs遅延された先端、即ち、上昇エッジとなる。即ち、第1クロック信号(CK)のアクティブ区間、ハイレベル区間が、Tdr1時間ほど遅延されて出力端子(OUT)に現れる。

### 【0081】

このような遅延特性は、プルアップ駆動部194のキャパシタ(C)が開始信号(ST)の先端でトランジスタ(NT13)を通じて充電され始め、キャパシタの充電電圧がプルアップトランジスタ(NT11)のゲートソース間スレッショルド電圧以上に充電された後に、プルアップトランジスタ(NT11)がターンオンされ、第1クロック信号(CK)のハイレベル区間が出力端子に現れ始めるからである。

### 【0082】

出力端子(OUT)にクロック信号のハイレベル区間が現れ始めると、この出力電圧がキャパシタ(C)にブーストストラップされ、プルアップトランジスタ(NT11)のゲー

10

20

30

40

50

ト電圧がターンオン電圧（VDD）以上に上昇される。従って、N MOSトランジスタであるプルアップトランジスタ（NT11）が完全（FULL）導通状態を維持することになる。ここで、トランジスタ（NT13）のサイズはトランジスタ（NT15）のサイズより約2倍程度大きいために、開始信号（ST）によりトランジスタ（NT15）がターンオンされても、トランジスタ（NT11）をターンオン状態に遷移させる。

#### 【0083】

一方、プルダウン駆動部196は、トランジスタ（NT17）がターンオフされて第4ノード（N4）が第2電源電圧（VDD）に上昇され、トランジスタ（NT12）をターンオンさせる。従って、出力端子（OUT）の出力信号の電圧が第1電源電圧（VSS）状態にある。ここで、開始信号（ST）によりトランジスタ（NT17）がターンオンされるので、第4ノード（N4）の電位が第1電源電圧（VSS）にダウンされる。以後、トランジスタ（NT16）がターンオンされても、トランジスタ（NT17）のサイズがトランジスタ（NT16）のサイズより約16倍程度大きいために、第4ノード（N4）は第1電源電圧（VSS）のレベルに維持される。従って、プルダウントランジスタ（NT12）はターンオン状態でターンオフ状態に遷移される。

#### 【0084】

出力端子（OUT）の出力信号（OUT1）は、第1クロック信号（CK）のデュティ期間程度、遅延されて現れる。

出力端子（OUT）の出力信号の電圧がターンオフ電圧（VOFF = VSS）状態に落ちると、トランジスタ（NT17）がターンオフされる。これにより、トランジスタ（NT16）を通じて第4ノード（N4）に第2電源電圧（VDD）が供給される状態であるので、第4ノード（N4）の電位は、第1電源電圧（VSS）から第2電源電圧（VDD）に上昇され始める。第4ノード（N4）の電位が上昇され始めると、トランジスタ（NT15）がターンオンされ、これにより、キャパシタの充電電圧はトランジスタ（NT15）を通じて放電される。従って、プルアップトランジスタ（NT11）もターンオフされる。

#### 【0085】

続いて、制御端子（CT）に提供される次段ステージの出力信号がターンオン電圧に上昇するので、これによりトランジスタ（NT14）がターンオンされる。ここで、トランジスタ（NT14）のサイズはトランジスタ（NT15）より約2倍程度大きいために、第3ノード（N3）の電位は、トランジスタ（NT15）のみターンオンされた場合より、さらに速く第1電源電圧（VSS）にダウンされる。

したがって、プルアップトランジスタ（NT11）はターンオフされ、一方プルダウントランジスタ（NT12）はターンオンされて、出力端子（OUT）はターンオン電圧（VON）で第2電源電圧（VDD）のターンオフ電圧（VOFF）にダウンされる。

#### 【0086】

制御端子（CT）に印加される次段ステージの出力信号がローレベルに下降され、トランジスタ（NT14）がターンオフされても、第4ノード（N4）はトランジスタ（NT16）を通じて第2電源電圧（VDD）にバイアスされた状態を維持することにより、第3ノード（N3）は、ターンオン状態を維持するトランジスタ（NT15）により第1電源電圧（VSS）にバイアスされた状態を維持する。第4ノード（N4）の電位が第2電源電圧（VDD）に維持されるので、プルダウントランジスタ（NT2）がターンオフされる誤動作の恐れなしに、安定された動作が確保される。

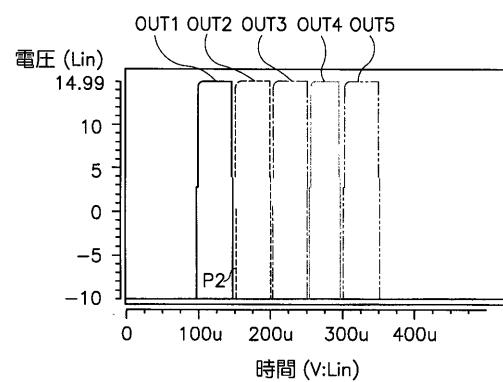

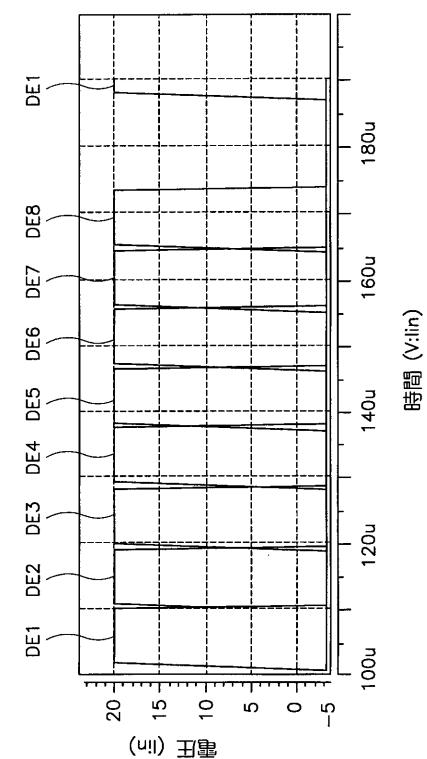

上述した動作により、各ステージが動作して出力信号（OUT11～OUT14）が図17に図示したように順次に安定されるように発生する。

#### 【0087】

上述したように、本発明による第2実施形態は、トランジスタ（NT15）及びトランジスタ（NT17）をラッチ形態に配置することにより、第3ノード（N3）及び第4ノード（N4）に安定された状態を維持することができる。また、二つのトランジスタを除去するだけでなく、トランジスタのサイズも減少させることにより、パネル内でシフトレ

10

20

30

40

50

ジスタが占める面積を10%程度減少させることができる。

また、本発明による第2実施形態は、本発明による第1実施形態に比べて、スキャン開始信号(ST)のパルス幅に関係なしに、安定された動作が可能である。

#### 【0088】

即ち、本発明による第1実施形態は、スキャン開始信号(ST)のパルス幅がクロック信号のパルス幅より狭い場合には、クロック信号が入る前にキャパシタが放電を開始する。この理由により、プルダウントランジスタがターンオンされるので、出力が発生されない。よって、出力信号が次端にシフトされないので、動作不能状態になる恐れがある。

一方、本発明による第2実施形態は、スキャン開始信号(ST)をラッチするために、スキャン開始信号(ST)のパルス幅の広狭に関係なしに、安定された動作が可能である

10

。

#### 【0089】

図18は、本発明の他の実施形態による第1及び第2クロック信号波形図であり、図19は各ステージの出力波形図である。

シフトレジスタ164、170のそれぞれのステージには、図18及び図19に示すような第1及び第2クロック信号(CK、CKB)が提供される。具体的には、奇数番目ステージには第1クロック信号(CK)が提供され、偶数番目ステージには第2クロック信号(CKB)が提供される。ここで、第1及び第2クロック信号(CK、CKB)は、互いに反転された位相を有する。ステージそれぞれに第1及び第2クロック信号(CK、CKB)が提供されると、第1及び第2クロック信号(CK、CKB)のハイレベル区間がそれぞれのステージの出力端子(OUT)の出力信号に発生する。

20

#### 【0090】

ここで、それぞれのステージに提供される第1クロック信号(CK)で発生されるハイレベル区間と、第2クロック信号(CKB)のハイレベル区間の間に一定の位相差(P1)を設ける。即ち、奇数番目ステージに第1クロック信号(CK)のハイレベル区間が提供された後、一定時間後、偶数番目ステージに第2クロック信号(CKB)のハイレベル区間が提供される。

#### 【0091】

従って、図19に示すように、各ステージで出力される出力信号(OUT1、OUT2、OUT3、OUT4、OUT5)のハイ区間の間に一定の位相差(P2)が発生する。即ち、第1クロック信号(CK)が提供される奇数番目ステージの出力信号(OUT1、OUT3、OUT5)のハイレベル区間が発生された後、一定時間後に第2クロック信号(CKB)が提供される偶数番目ステージの出力信号(OUT2、OUT4)のハイレベル区間が発生される。従って、各ステージの出力信号の下降遷移と次段ステージの出力信号の上昇遷移のオーバーラップ現象を防止することができる。

30

#### 【実施形態3】

#### 【0092】

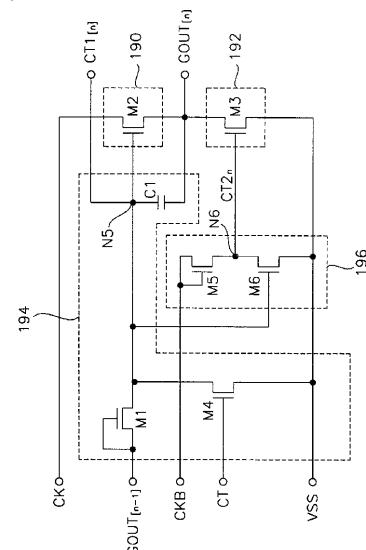

図20は、本発明の第3実施形態によるシフトレジスタの各ステージの具体回路図を示し、図21は、上述した図20によるシフトレジスタの駆動波形を説明するための図面である。

40

図20に示すように、本発明の第3実施形態によるシフトレジスタ170の各ステージは、プルアップ部190、プルダウン部192、プルアップ駆動部194及びプルダウン駆動部196とを含む。

#### 【0093】

プルアップ部190は、クロック信号入力端子(CK)にドレインが接続され、第5ノード(N5)にゲートが接続され、出力端子(OUT)にソースが接続されたプルアップNMOSトランジスタ(M2)により構成される。

プルダウン部192は、出力端子(OUT)にドレインが接続され、第6ノード(N6)にゲートが接続され、ソースが第1電源電圧端子(VSS)に接続されたプルダウンNMOSトランジスタ(M3)により構成される。

50

## 【0094】

プルアップ駆動部194は、キャパシタ(C)、NMOSトランジスタ(M1、M4)により構成される。キャパシタ(C)は、第5ノード(N5)と出力端子(GOUT)間に接続される。トランジスタ(M1)は、共通接続されたドレインとゲートが入力信号に接続され、ソースは第5ノード(N5)を経てプルアップ部190の入力ノードに接続されるが、第1ステージである場合には、共通接続されたドレインとゲートは入力信号に接続されるが、第2番目以降のステージである場合には、共通接続されたドレインとゲートは前段ステージの出力端子に接続されて、前端キャリ信号の提供を受ける。トランジスタM4はドレインがプルアップ部の入力ノードに接続され、ゲートが次段ステージの出力信号に接続され、ソースが第1電源電圧(VSS)に接続される。

10

## 【0095】

プルダウン駆動部196は、二つのトランジスタ(M5、M6)により構成されてインバータ動作を実施する。トランジスタ(M5)は、第2電源電圧(VDD)にドレインとゲートが共通に結合され、第6ノード(N6)にソースが接続される。トランジスタ(M6)は第6ノード(N6)にドレインが接続され、第5ノード(N5)にゲートが接続され、ソースが第1電源電圧(VSS)に接続される。ここで、トランジスタ(M5)のサイズは、トランジスタ(M6)のサイズより約16倍程度大きく形成される。

## 【0096】

動作時、前段ステージの出力信号(GOUT[n-1])(または、STV)によりキャパシタC1が充電されると、トランジスタM2のV<sub>GS</sub>バイアスがかかって、ターンオン可能状態になり、トランジスタM2のドレインのCKがハイになると、この電圧がGOUT[n]ノードに現れる。このとき、GOUT[n]ノードを基準電位にするキャパシタC1によりCT1[n]ノードの電位がレベルシフトされて、CKがハイレベルである間にトランジスタM2がターンオン状態を維持する。

20

## 【0097】

トランジスタ(M2)のターンオン状態で、次段ステージのCT1[n+2]信号をCT信号に印加すると、トランジスタ(M4)がターンオンされて第5ノード(N5)が第1電源電圧(VSS)レベルに放電される。このとき、トランジスタ(M2)がターンオン状態である時には、トランジスタ(M3)が必ずターンオフされなければならない。万一、トランジスタ(M3)が十分にターンオフされなければならず、トランジスタ(M2)からトランジスタ(M3)の経路に漏洩電流が発生して消費電力が増加される問題があるからである。

30

このために、トランジスタ(M5)とトランジスタ(M6)は、トランジスタ(M2)のゲート電圧である第5ノード(N5)の電圧を反転することにより、トランジスタ(M2)とトランジスタ(M3)が同時にターンオンされることを防止することになる。

## 【0098】

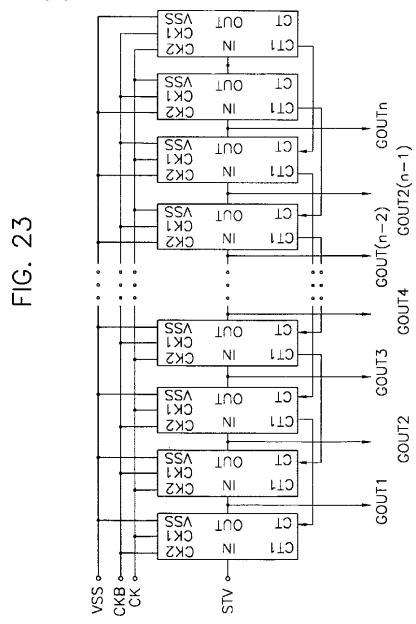

図22は、本発明の第2実施形態によるシフトレジスタを利用したa-TFTLCDゲート駆動回路を説明するための図面であり、図23は、本発明の第3実施形態によるシフトレジスタを利用したa-TFTLCDゲート駆動回路を説明するための図面である。

40

図22に示すように、上述した図15に示したステージをゲートライン数以上に従属接続してゲート駆動回路の動作を実行する。しかし、外部入力に全体で5個の転送配線(VDD、VSS、CKV、CKVB、STV)が必要であり、ステージ毎に7個のトランジスタが必要である。このように回路配線とトランジスタの数が多ければ、a-TFTLCD基板で設計することができる空間の制約が発生する。

## 【0099】

また、トランジスタ(NT12)をターンオフすることができるレベルを作くるためのトランジスタ(NT16)及びトランジスタ(NT17)からなるインバータ回路196で2つトランジスタ(NT16、NT17)が同時にターンオンされる条件が動作中に発生することになり、消費電力上問題が発生し、プルダウン部(NT12)に印加されるタ

50

ーンオフ電圧にVSSが印加されることが困難であるために、プルアップ部(NT11)とプルダウン部(NT12)の経路に漏洩電流の問題がある。

#### 【0100】

また、第4ノード(N4)が初期ハイ状態であるので、トランジスタ(NT15)がターンオンされた状態でキャパシタへの充電が困難になる回路的限界にトランジスタ(NT13、NT15、NT16、NT17)のサイズが精密に調整されなければ、トランジスタ(NT15)のターンオンによって、“IN”信号がキャパシタに充電されないという動作不能状態になる可能性があるという問題点がある。

しかし、本発明の第3実施形態で開示するシフトレジスタによると、少ない数のトランジスタと減少された転送配線をa-TFT LCD基板に適用することができるので、その設計が容易であり、駆動上問題点を解決するa-TFTゲート駆動回路を提供することができる。10

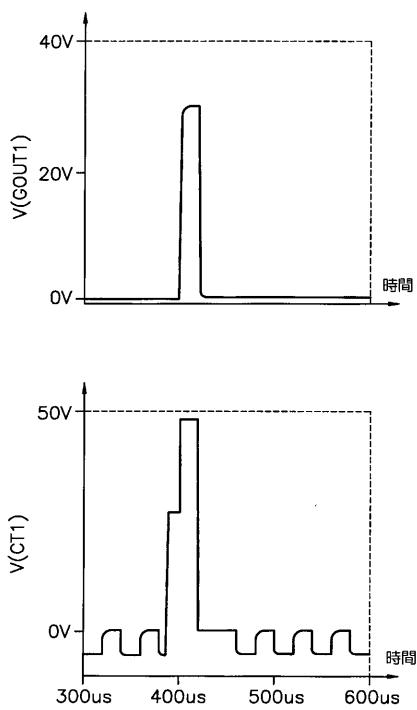

#### 【0101】

図23に示すように、第2電源電圧(VDD)の供給を必要とせず、次々段ステージ(2段先のステージ)のCT1信号を制御端子(CT)の入力に使用する。

このように、次々段ステージ( $n+2$ )のCT1信号を制御端子(CT)の入力に使用する特徴は、トランジスタM2のドレインとゲート間の寄生結合容量により発生されるCT1のノードの電位変動による誤動作を防止してくれる。即ち、次段ステージのGOUT出力を制御端子(CT)の入力に使用した時に発生したCT1ノードの電位変動による誤動作を制御するために必要とした別途の放電トランジスタ(NT15)を不要とするものである。20

#### 【0102】

例えば、次段ステージのGOUT出力を制御端子(CT)の入力に使用したとき、CKが上昇時にCT1ノードが付随して上昇して、CT1ノード電圧がVSS + Vth(トランジスタ(M2)のスレッショルド電圧)以上となる場合、トランジスタM2がターンオンされる誤動作が生じるとともにトランジスタM3に多い電流が流れるという問題が発生する。

#### 【0103】

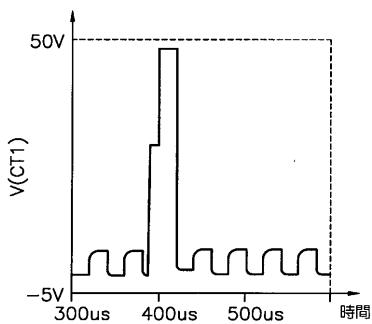

図24A、図24Bは、本発明の第2実施形態による次段ステージのGOUT出力をCT入力に使用した時のゲート出力波形と、本発明の第3実施形態による次々段ステージのCT1信号を使用した時のゲート出力波形を各々シミュレーションした結果である。30

図24Aに示すように、本発明の第2実施形態のように次段ステージのGout[ $n+1$ ]をトランジスタM4をターンオンするに使用したとすると、CKがロー状態である時にCT1がVSSにクランプされた後にCKが上昇する時、CT1のカップリング電圧がVSS + Vth以上になって、トランジスタM2がターンオンされる誤動作が発生され、このために別途の放電用トランジスタが必要であった。

#### 【0104】

しかし、図24Bの場合には、CT1がCKにカップリングされ、CKがハイ状態である時、放電用トランジスタM4がCT1をVSSにクランピングさせることができ、したがって、以後CKが降下しても、CT1のカップリング電圧がVSS以下になるようにして、トランジスタM2がターンオンされる状況を除去することができる。40

#### 【0105】

上述したシミュレーション結果で分かるように、本発明の第3実施形態において、CT1電圧がCKにカップリングされても、VSS以下に維持することができてトランジスタM2の誤動作を防止することができる。

従って、本発明の第3実施形態によると、上述した図15で開示した別途の放電用トランジスタ(NT15)を除去することができるので、トランジスタ(NT15)による回路的誤動作防止は勿論、シフトレジスタを構成するトランジスタの数を6個に単純化することができる。

#### 【0106】

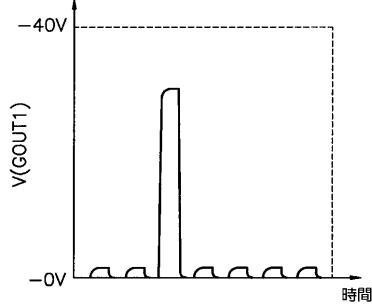

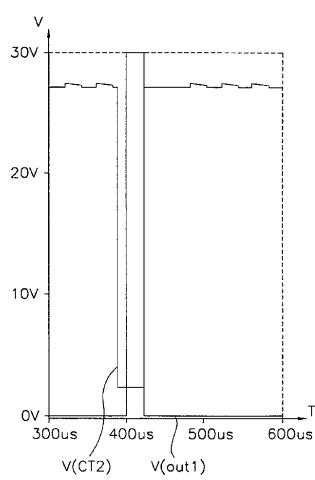

図25A、図25Bは、本発明の第2実施形態と第3実施形態によるゲートドライバから出力されるゲート信号の出力波形を各々説明するための波形図であり、特に、トランジスタM3をターンオフさせるためのCT2波形のシミュレーション結果を説明するための波形図である。

#### 【0107】

図25Aに示した本発明の第2実施形態によると、CT2レベルがVSS以上になって、トランジスタM3とトランジスタM2が同時にターンオンされる状況が発生されて過電流発生になる可能性がある。

しかし、図25Bに示した本発明の第3実施形態によると、トランジスタM2がターンオンされる時、ロー状態になるCKB信号を第2電源電圧(VDD)代わりに使用してトランジスタM2がターンオンされてOUT1信号が発生された時、CT2が必ず第1電源電圧(VSS)レベルになるので、トランジスタM3をターンオフさせて過電流の発生を除去することができた。10

#### 【0108】

このように、本発明の第3実施形態のシミュレーション結果から分かるように、既存のa-TFTゲート駆動回路で問題になった誤動作や過電流発生状況を除去して、本発明の第2実施形態に比べて安定性と優れている特性を確保することができる。

また、シフトレジスタ構成に必要としたトランジスタ1個と別途の第2電源電圧(VDD)のための配線を不要として、集積度を高くすることができるa-TFTゲート駆動回路を提供することができる。20

#### 【0109】

以上で説明したように、本発明の第3実施形態による図20と本発明の第2実施形態による図15を比較すると、トランジスタの数を7個から6個に減少させることができ、また、外部入力端子数を5個から4個に減少させながら、回路動作の安定性を確保しつつ高集積化を実現することができる。

#### 【0110】

一方、前述した図15に示すように各々ステージが作られ、各々のステージは前述した図22のようにゲートライン数以上に直列接続してゲートドライバICの動作と同一である動作を実現する。

しかし、図22のような回路で駆動する時には次のような問題が発生される。30

#### 【0111】

第一は信頼性に関する問題であり、初期モジュール駆動時に液晶パネル上に配線されるVSS、CKVまたはCKVBに過電流が流れて断線したり、電源回路に過負荷がかかってシステムダウンが発生する現象である。

これに対する原因を分析した結果、ステージに必ず必要であるN3ノードのキャパシタCが原因であることが分かった。これは、複数のステージで静電気により所望でない電荷がキャパシタに充電されたり、初期外部電源印加時に不安定な電源及び信号状態でキャパシタに電荷が充電され、CKVとCKVBが回路に印加される場合、複数のステージが同時に動作する場合に発生することになる。40

#### 【0112】

即ち、キャパシタに電荷が充電されている場合、各ステージのNT11はGOUTにかかるロードキャパシタに充電を行い、直にCKVまたはCKVB信号の位相遷移になる時、トランジスタNT12により放電が行われるが、複数のラインのステージが同時にこのような動作が実行される場合、VSS、CKVまたはCKVB配線に過電流が流れることになる。

#### 【0113】

一つのトランジスタの駆動電流が0.1mAとする時、XGA解像度(1024×3×3768)の場合、768個のゲートラインが存在するので、第1電源電圧(VSS)には最大38.4mA(=0.1mA×768/2)が流れることになる。

このような過電流状況は、シフト動作が完了される1フレーム時間、例えば、60Hz50

である 16.7 msec 間発生し、この時間の間に抵抗を有する VSS 配線での発熱により配線自体が溶けて切れる現象が発生される。

このような状況は、ステージに提供される電源が安定な場合であり、配線抵抗が大きくて電圧強化が発生される場合や十分でない電圧状態でトランジスタが正常動作をしない場合には、誤動作時間が 16.7 msec 以上になって、駆動不能状態になる恐れがある。

#### 【0114】

第二の問題として、駆動時に最終段ステージのキャパシタを放電することができなくて、最終段のゲートライン出力電圧が低く、または発生されないなどの不良動作を誘発する問題がある。勿論、これを解決するために、最終段ステージに追加してステージ（すなわちダミーステージ）を装着することができるが、これも追加されるステージのキャパシタを放電させることができないので、前段ステージのキャパシタを CK または CKB により周期的に充電を妨害することになって、問題が発生するものである。10

#### 【0115】

本発明の第 4 及び第 5 実施形態では、このような二つ問題を解決して信頼性側面で優れて、機能性側面で良好である a-TFT LCD ゲート駆動回路を提供する。

#### 【実施形態 4】

#### 【0116】

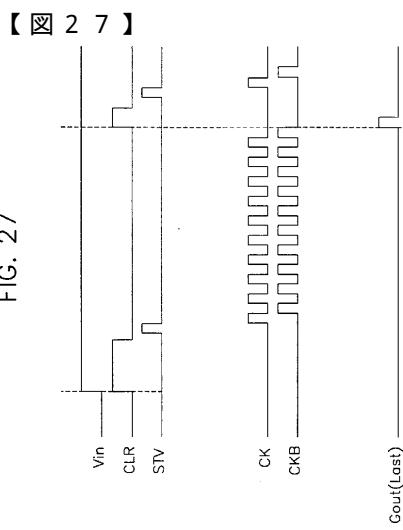

図 26 は、本発明の第 4 実施形態によるシフトレジスタの各ステージの具体回路図であり、図 27 は上述した図 26 を駆動するための波形図である。特に、図 26 に示すように、初期駆動時にキャパシタに充電された電荷を放電する放電専用トランジスタを各ステージに装着する。20

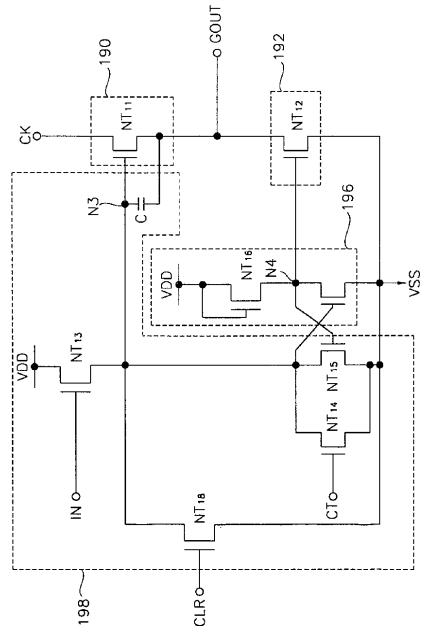

図 26 に示すように、本発明の第 4 実施形態によるシフトレジスタ 170 の各ステージは、プルアップ部 190、プルダウン部 192、プルアップ駆動部 198、プルダウン駆動部 196 を含む。上述した図 15 と比較する時、プルアップ部 190、プルダウン部 192 及びプルダウン駆動部 196 は同一であるので、その説明は省略する。

#### 【0117】

プルアップ駆動部 198 は、キャパシタ (C) 及び NMOS トランジスタ (NT13、NT14、NT15、NT18) により構成される。より詳細には、キャパシタ (C) は第 3 ノード (N3) と出力端子 (OUT) 間に接続される。トランジスタ (NT13) は第 2 電源電圧 (VDD) にドレインが接続され、入力端子 (IN) にゲートが接続され、第 3 ノード (N3) にソースが接続される。トランジスタ (NT4) は第 3 ノード (N3) にドレインが接続され、制御端子 (CT) にゲートが接続され、ソースが第 1 電源電圧 (VSS) に接続される。トランジスタ (NT15) は第 3 ノード (N3) にドレインが接続され、第 4 ノード (N4) にゲートが接続され、ソースが第 1 電源電圧 (VSS) に接続される。ここで、トランジスタ (NT13) のサイズは、トランジスタ (NT15) のサイズより約 2 倍程度大きく形成される。トランジスタ (NT18) は第 1 電源電圧 (VSS) にソースが接続され、外部入力制御信号 (またはクリア信号) (CLR) にゲートが接続され、ドレンを利用してプルアップ部 190 の第 3 ノード (N3) と並列接続されたキャパシタの充電電荷を強制放電する。30

#### 【0118】

ここで、外部入力制御信号 (CLR) は、キャパシタ (C) を第 1 電源電圧 (VSS) に放電させる信号として、最初電源オン時にキャパシタを放電させることができるよう、所定の時間の間に第 2 電源電圧 (VDD) 状態を維持するが、画面がディスプレイされる期間中ではトランジスタがターンオフ状態を維持することができるスレッシュホールド電圧以下、例えば、第 1 電源電圧 (VSS) 状態である信号である。40

#### 【0119】

図 27 に示すように、外部入力制御信号 (CLR) は電源印加 (Vin) と同時にハイ状態を維持してステージのキャパシタに充電された電荷を放電させ、以後、垂直開始信号 (STV) を発生する。

また、CK 及び CKB 信号に過ロードがかかる 것을防止するために外部入力制御信号50

( C L R ) がハイである場合には、二つ信号がロー状態である。

また、正常動作中、最終段のゲートパルス ( G o u t ( L a s t ) ) 発生後、ハイ状態になって最終段ステージのキャパシタを放電させる。

#### 【 0 1 2 0 】

以上で説明した本発明の第4実施形態によると、プルアップ駆動部に備えられるキャパシタの充電電荷を放電させる手段を別途に提供することにより、初期起動時にキャパシタに充電されている電荷による誤動作や液晶パネル、特に、a-TFT液晶パネルの配線が損傷される問題を解決することができるので、信頼性高いTFT-LCDモジュールを提供することができる。

また、最終段のゲートラインの駆動信号のエラーを解決することにより、画面下端縁に生じるライン損傷を防止して、機能的に安定であるa-TFTトランジスタからなるゲート駆動回路を内蔵したTFT-LCDモジュールを提供することができる。 10

#### 【 実施形態 5 】

#### 【 0 1 2 1 】

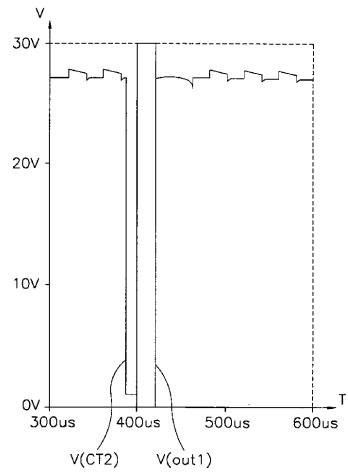

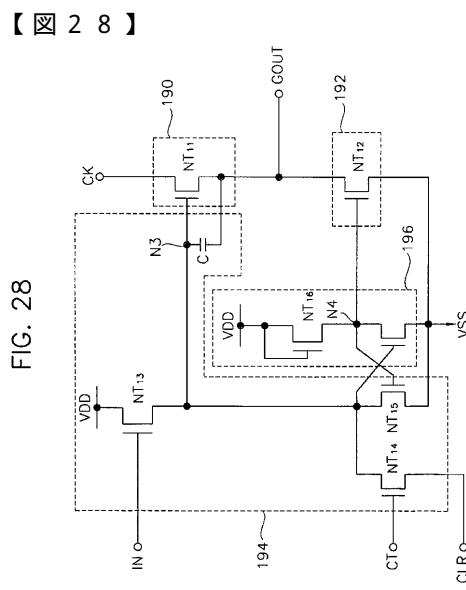

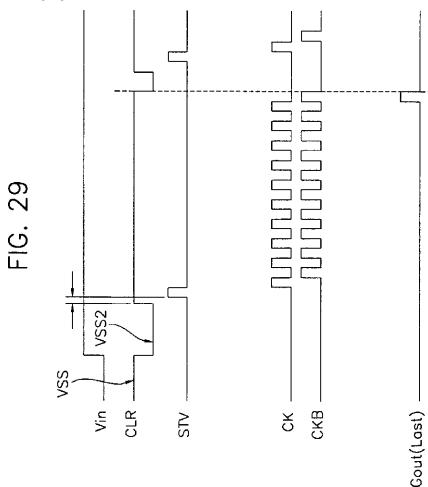

図28は、本発明の第5実施形態によるシフトレジスタの各ステージの具体回路図であり、図29は、図28を駆動するための波形図である。特に、放電専用トランジスタを追加することなくステージのキャパシタに充電された電荷を放電させることができるようにした回路図である。

図28に示すように、本発明の第5実施形態によるシフトレジスタ170の各ステージは、プルアップ部190、プルダウン部192、プルアップ駆動部194、プルダウン駆動部196を含み、上述した図15でキャパシタの放電動作を実施するプルアップ駆動部194のトランジスタ(NT14)のソースに外部入力制御信号(CLR)を印加する。勿論、図示していないが、トランジスタ(NT15)のソースに外部入力制御信号(CLR)を印加することもでき、トランジスタ(NT14)とトランジスタ(NT15)の共通接続されたソースに外部入力制御信号(CLR)を印加することもできる。 20

#### 【 0 1 2 2 】

図示したように、トランジスタ(NT14)のゲートには常に、VSS電圧以上かかる利用することとして、 $V_{g s} > V_{t h}$  (ここで、 $V_{t h}$ はトランジスタ(NT14)のスレッショルド電圧)を作るためにソースに、 $V_{S S 2} > (V_{S S} - V_{t h})$  であるVSS2電圧を印加して、トランジスタ(NT14)をターンオンさせることにより、キャパシタの充電電圧を強制的にVSS2電圧レベルに引き下げる放電動作を実行する。 30

#### 【 0 1 2 3 】

このために、外部入力制御信号(CLR)は、電源印加(Vin)と同時にロー状態(VSS2)を維持してステージのキャパシタに充電されている電荷を放電させ、その後、STV信号の発生前にハイ状態(VSS)になる。

また、CKV及びCKVB信号に過ロードがかかるのを防止するために、外部入力制御信号(CLR)がロー状態(VSS2)である場合には、二つ信号がロー状態である。

また、正常動作中、最終段のゲートパルス(Gout(Last))発生後、外部入力制御信号CLRがロー状態(VSS2)になって、最終段ステージのキャパシタを放電させる。 40

#### 【 0 1 2 4 】

以上で説明した本発明の第5実施形態によると、キャパシタの充電電荷を放電するために、プルアップ駆動部のトランジスタのソースに外部入力制御信号(CLR)を提供することにより、初期起動時にキャパシタに充電されている電荷による誤動作や液晶パネルの配線が損傷される問題を解決することができるので、信頼性高いTFT-LCDモジュールを提供することができる。

また、最後ゲートラインの駆動信号におけるエラーを解決することにより、画面下端縁に生じるライン損傷を防止して、機能的に安定であるa-TFTトランジスタからなるゲート駆動回路を内蔵したTFT-LCDモジュールを提供することができる。

#### 【 0 1 2 5 】

50

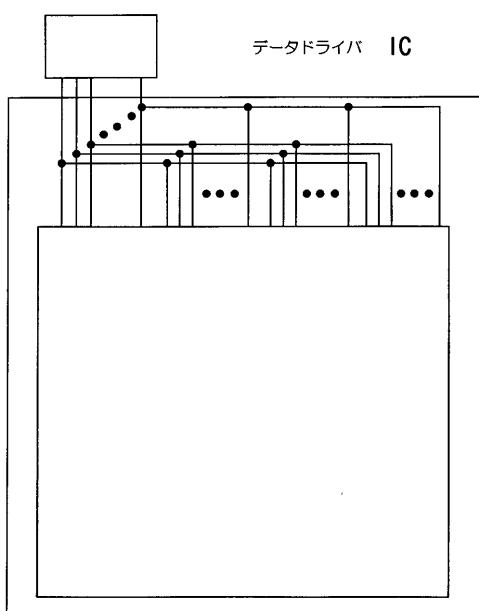

一方、本発明のデータ駆動回路 160 は、全チャンネル同時駆動方式（図 30 参照）を採択せずに、ブロック駆動方式（図 31 参照）を採択する。

a - S i T F T によりデータ駆動チップの複雑なアナログ機能を具現することが、現在の技術としては容易でない。しかし、スイッチングトランジスタを利用してブロック駆動をする場合には、データ駆動チップから液晶表示パネルに提供されるビデオチャネル数を大幅に減少させることができる。ブロック駆動の場合、ピクセル充電時間が減少するが、液晶表示パネルのサイズが 2 インチである小型パネルの場合にはノートブックやデスクトップ液晶モニタに比べて十分なラインタイムを有することができるので、ブロック駆動が可能である。

解像度によるピクセル充電時間は次の表 1 のとおりである。

10

【表 1】

| 解像度  | 2" (176*192) | X G A (1024*768) | S X G A (1280*1024) | U X G A (1600*1200) |

|------|--------------|------------------|---------------------|---------------------|

| 充電時間 | 8 6 $\mu$ s  | 2 0 $\mu$ s      | 1 5 $\mu$ s         | 1 3 $\mu$ s         |

## 【0126】

U X G A 級パネルでは、パネルサイズの大きさによるロードと遅延時間を考慮する場合、可能である充電時間は 7 ~ 8  $\mu$ s 程度である。従って、同一電流駆動能力のデータ駆動チップを考慮する場合、2" パネルは U X G A 級パネルに比べて約 10 倍以上の充電時間 20 を有する。従って、データラインを 10 ブロックに分割してブロック駆動をしても、U X G A 級パネルと同一である充電特性を有することができる。

## 【0127】

従って、本発明では、2" パネルでデータラインを 8 ブロックに分割してブロックを駆動する。よって、528 ビデオチャネルを 8 ブロックに分割すると、各ブロック当たり 66 チャネルが割当てられ、これにより、528 個の全チャンネル同時駆動方式（図 30 参照）に比べてデータ駆動チップとパネル間の接続チャネル数を 528 チャネルから 66 チャネルに減少させることができる。

## 【0128】

本発明では、このようなデータラインの駆動をブロック駆動方式に採択し、各ブロックをシフトレジスタに順次に選択するデータライン駆動回路をパネル上に集積させることにより、データ駆動チップとパネルの接続端子数を 1 / 8 に大幅減少させることができる。

30

従って、本発明の実施形態では、全体で外部接続端子は 66 チャネル端子、データ制御用 3 端子、ゲート制御用 5 端子、共通電圧（V C O M ）用 1 端子を必要とするので、75 個の外部接続端子のみが必要である。

このように、外部接続端子数を大幅減少させることができるので、パネルの外郭サイズを減少させることができるために、原価節減及び生産性が向上され、パネル実装の薄形化により商品性が向上される。

## 【0129】

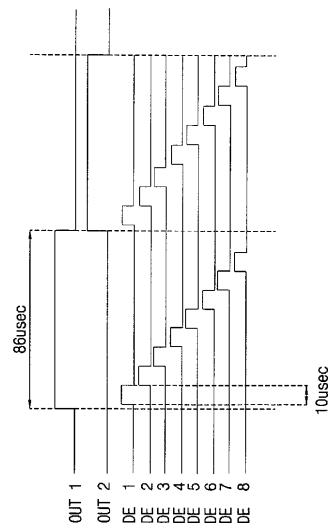

図 32 に示すように、ブロック駆動方式は、ゲートラインアクティブ区間で 8 個のブロックを順次にイネーブルさせるために、ブロック選択信号（D E 1 ~ D E 8 ）がシフトレジスタ 164 を通じて発生される。

40

本発明では、176 \* 192 の解像度を有する 2" パネルでゲートラインアクティブ期間は 8 6  $\mu$ s であり、各ブロック選択信号のアクティブ期間は 10  $\mu$ s に設計する。従って、ブロック駆動時にも十分であるピクセル充電特性を維持することができる。

## 【0130】

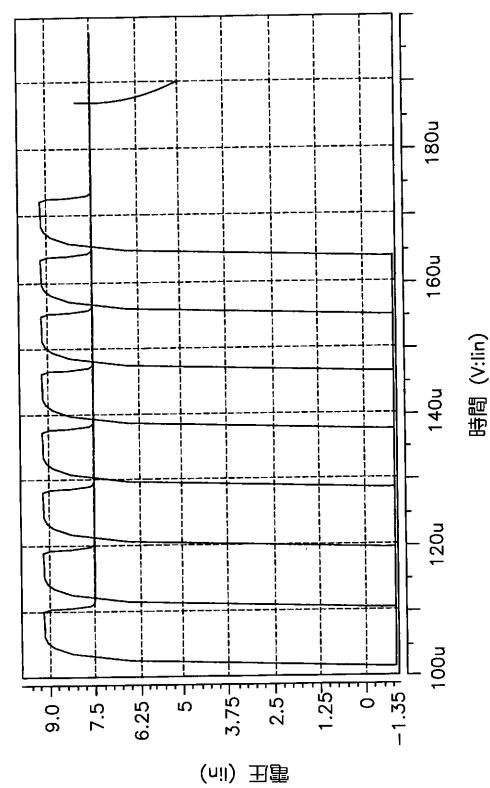

図 33 ~ 図 35 は、スイッチングトランジスタ（S W T ）を幅 4 , 000  $\mu$ m、長さ 5  $\mu$ s の a - S i T F T に設計し、20 V の電圧を印加した時、ゲートライン駆動信号、データラインブロック選択信号及びピクセル充電特性シミュレーション結果を各々示す。ここで、ゲートライン駆動信号（O U T i ）のアクティブ期間は 8 6  $\mu$ s であり、データ 50

ラインプロック選択信号( D E i )のアクティブ期間は  $10 \mu s$  である。

図 35 に示すように、上述したプロック駆動時にシミュレーションした結果、99%以上のピクセル充電率が得られている。

### 【 0 1 3 1 】

以上の実施形態では、データ駆動回路及びゲート駆動回路の両方に本発明のシフトレジスタを利用した例を示したが、データ駆動回路またはゲート駆動回路いずれか一方のみに本発明のシフトレジスタを利用することができることは、当業者には明らかであろう。

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離れることなく、本発明を修正または変更できるであろう。

10

### 【 図面の簡単な説明 】

#### 【 0 1 3 2 】

【図 1】 poly - TFT LCD の TFT 基板の構成を示す概略図である。

【図 2】従来の a - Si TFT LCD の TFT 基板の構成を示す概略図である。

【図 3】本発明による a - Si TFT LCD の液晶表示装置の分解斜視図である。

【図 4】本発明による望ましい一実施形態の a - Si TFT LCD の TFT 基板の構成を示す図面である。

【図 5】図 4 のデータ駆動回路のシフトレジスタのプロック図である。

【図 6】図 4 のゲート駆動回路のシフトレジスタのプロック図である。

【図 7】本発明の第 1 実施形態によるシフトレジスタの各ステージの具体回路図である。

20

【図 8】図 7 の各部のタイミング図である。

【図 9】図 7 の各ステージのシミュレーション出力波形図である。

【図 10】図 7 の出力信号のクロック信号に対する遅延特性シミュレーション波形図である。

【図 11】本発明によるゲート駆動回路の外部接続端子部レイアウト図である。

【図 12】本発明のゲート駆動回路のシフトレジスタと従来技術の比較波形図である。

【図 13】本発明のゲート駆動回路のシフトレジスタと従来技術の比較波形図である。

【図 14】本発明のゲート駆動回路のシフトレジスタと従来技術の比較波形図である。

【図 15】本発明の第 2 実施形態によるシフトレジスタの各ステージの具体回路図である。

30

【図 16】図 15 の各部のタイミング図である。

【図 17】図 15 の各ステージのシミュレーション出力波形図である。

【図 18】本発明の他の実施形態による第 1 及び第 2 クロック信号のシミュレーション波形図である。

【図 19】各ステージのシミュレーション出力波形図である。

【図 20】本発明の第 3 実施形態によるシフトレジスタの各ステージの具体回路図である。

。

【図 21】図 20 によるシフトレジスタの駆動波形を説明するための図面である。

【図 22】本発明の第 2 実施形態によるシフトレジスタを利用した a - TFT LCD ゲート駆動回路を説明するための図面である。

40

【図 23】本発明の第 3 実施形態によるシフトレジスタを利用した a - TFT LCD ゲート駆動回路を説明するための図面である。

【図 24 A】次段ステージの G O U T 出力を C T 入力に使用したときのゲート出力波形と次々段ステージの C T 1 信号を使用した時のゲート出力波形を各々シミュレーションした結果を示す図面である。

【図 24 B】次段ステージの G O U T 出力を C T 入力に使用したときのゲート出力波形と次々段ステージの C T 1 信号を使用した時のゲート出力波形を各々シミュレーションした結果を示す図面である。

【図 25 A】本発明の第 2 実施形態と第 3 実施形態によるゲートドライバから出力されるゲート信号の出力波形を各々説明するための波形図である。

50

【図25B】本発明の第2実施形態と第3実施形態によるゲートドライバから出力されるゲート信号の出力波形を各々説明するための波形図である。

【図26】本発明の第4実施形態によるシフトレジスタの各ステージの具体回路図である。

【図27】図26の駆動波形図である。

【図28】本発明の第5実施形態によるシフトレジスタの各ステージの具体回路図である。

【図29】図28の駆動波形図である。

【図30】全チャネル同時駆動方式のパネルを説明するための図面である。

【図31】本発明によるロック駆動方式のパネルを示す図面である。

10

【図32】本発明によるロック駆動方式の各部のタイミングを示す図面である。

【図33】スイッチングトランジスタ(SWT)を幅4,000μm、長さ5μsのa-Si TFTに設計し、20Vの電圧を印加した時、ゲートライン駆動信号、データラインブロック選択信号及びピクセル充電特性のシミュレーション結果を各々示す図面である。

【図34】スイッチングトランジスタ(SWT)を幅4,000μm、長さ5μsのa-Si TFTに設計し、20Vの電圧を印加した時、ゲートライン駆動信号、データラインブロック選択信号及びピクセル充電特性のシミュレーション結果を各々示す図面である。

【図35】スイッチングトランジスタ(SWT)を幅4,000μm、長さ5μsのa-Si TFTに設計し、20Vの電圧を印加した時、ゲートライン駆動信号、データラインブロック選択信号及びピクセル充電特性のシミュレーション結果を各々示す図面である。

#### 【符号の説明】

##### 【0133】

|     |              |

|-----|--------------|

| 100 | 液晶表示装置       |

| 110 | 液晶表示パネルアセンブリ |

| 120 | バックライトアセンブリ  |

| 130 | シャーシ         |

| 140 | カバー          |

| 180 | プルアップ部       |

| 182 | プルダウン部       |

| 184 | プルダウン駆動部     |

| 186 | プルダウン駆動部     |

| 188 | フローティング防止手段  |

| 190 | ターンオン防止手段    |

20

30

【図1】

(従来例)

【図2】

(従来例)

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

【図 9】

【図 11】

【図 10】

【図 12】

【図 13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図 19】

【図 20】

【図 2 3】

【図 2 4 A】

【図 2 4 B】

【図 2 5 A】

FIG. 25A

【図 25B】

FIG. 25B

【図 26】

【図 29】

【図 30】

【図 31】

【図 32】

【図 3 3】

【図 3 4】

【図 3 5】

---

フロントページの続き

(51)Int.Cl.

|         | F I          |

|---------|--------------|

| G 0 9 G | 3/20 6 2 3 H |

| G 0 9 G | 3/20 6 2 3 V |

| G 0 9 G | 3/20 6 7 0 E |

| G 0 9 G | 3/20 6 7 0 J |

| G 0 9 G | 3/36         |

(31)優先権主張番号 2002/0003398

(32)優先日 平成14年1月21日(2002.1.21)

(33)優先権主張国 韓国(KR)

(72)発明者 モン , セウン - ホワン

大韓民国ソウル市瑞草区蠶院洞70番地 新盤浦4次アパート210棟404号

審査官 堀江 義隆

(56)参考文献 特開2001-052494 (JP, A)

特開2002-258819 (JP, A)

特開昭58-182196 (JP, A)

特開平06-202588 (JP, A)

特表平11-502355 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 19/00

G11C 19/28

G02F 1/133

G09G 3/20

G09G 3/36