(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-235118

(P2007-235118A)

(43) 公開日 平成19年9月13日(2007.9.13)

| (51) Int.C1.          | F 1         | テーマコード (参考) |

|-----------------------|-------------|-------------|

| HO1L 21/20 (2006.01)  | HO1L 21/20  | 5F11O       |

| HO1L 21/268 (2006.01) | HO1L 21/268 | J 5F152     |

| HO1L 29/786 (2006.01) | HO1L 21/268 | F           |

| HO1L 21/336 (2006.01) | HO1L 29/78  | 627G        |

審査請求 未請求 請求項の数 18 O L (全 49 頁)

|              |                            |          |                     |

|--------------|----------------------------|----------|---------------------|

| (21) 出願番号    | 特願2007-22864 (P2007-22864) | (71) 出願人 | 000153878           |

| (22) 出願日     | 平成19年2月1日 (2007.2.1)       |          | 株式会社半導体エネルギー研究所     |

| (31) 優先権主張番号 | 特願2006-25276 (P2006-25276) |          | 神奈川県厚木市長谷398番地      |

| (32) 優先日     | 平成18年2月2日 (2006.2.2)       | (74) 代理人 | 100110858           |

| (33) 優先権主張国  | 日本国 (JP)                   |          | 弁理士 柳瀬 瞳            |

|              |                            | (74) 代理人 | 100100413           |

|              |                            |          | 弁理士 渡部 温            |

|              |                            | (72) 発明者 | 田中 幸一郎              |

|              |                            |          | 神奈川県厚木市長谷398番地 株式会社 |

|              |                            |          | 半導体エネルギー研究所内        |

最終頁に続く

(54) 【発明の名称】半導体膜の結晶化方法、半導体装置の製造方法、及びレーザ照射装置

## (57) 【要約】

【課題】半導体膜の品質に面内ばらつきが生じることを抑制できる半導体膜の結晶化方法を提供する。

【解決手段】半導体膜の結晶化方法は、基板510上に形成された半導体膜506に、第1のレーザ光503を基板510の底面510aに対して傾斜した状態で照射しつつ、第1のレーザ光503とは異なる発振器から発振された第2のレーザ光504を、基板510の底面510aに対して第1のレーザ光503とは反対の方向に傾斜した状態で照射することにより、半導体膜506の一部を溶融させ、かつ第1及び第2のレーザ光503、504の照射位置を、該第1又は第2のレーザ光503、504が傾斜している方向に略沿って走査して、半導体膜506の溶融している部分を移動させることにより、半導体膜506を結晶化するものである。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

基板上に形成された半導体膜に、第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第1のレーザ光とは異なる発振器から発振された第2のレーザ光を、前記第1のレーザ光とは反対の方向に傾斜した状態で前記基板の底面に対して照射することにより、前記半導体膜の一部を溶融させ、

かつ前記第1のレーザ光及び前記第2のレーザ光の照射位置を、該第1のレーザ光又は該第2のレーザ光が傾斜している方向に略沿って走査して、前記半導体膜の溶融している部分を移動させることにより、前記半導体膜を結晶化する半導体膜の結晶化方法。

**【請求項 2】**

前記第1のレーザ光及び前記第2のレーザ光は、発振周波数が10MHz以上のパルスレーザ、又はCWレーザから発振されたレーザ光である請求項1に記載の半導体膜の結晶化方法。

**【請求項 3】**

基板上に形成された半導体膜に、第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第1のレーザ光とは異なる長さの光路を経由した第2のレーザ光を、前記第1のレーザ光とは反対の方向に傾斜した状態で前記基板の底面に対して照射することにより、前記半導体膜の一部を溶融させ、

かつ前記第1のレーザ光及び前記第2のレーザ光の照射位置を、該第1のレーザ光又は該第2のレーザ光が傾斜している方向に沿って走査し、前記半導体膜の溶融している部分を移動させることにより、前記半導体膜を結晶化する半導体膜の結晶化方法。

**【請求項 4】**

前記第1のレーザ光及び前記第2のレーザ光は、同一の発振器から発振されたレーザ光をビームスプリッタで分岐することにより形成されている請求項3に記載の半導体膜の結晶化方法。

**【請求項 5】**

前記第1のレーザ光及び前記第2のレーザ光は、発振周波数が10MHz以上のパルスレーザから発振されたレーザ光である請求項3又は請求項4に記載の半導体膜の結晶化方法。

**【請求項 6】**

基板上に形成された半導体膜に、第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、第2のレーザ光を、前記第1のレーザ光とは反対の方向に傾斜した状態で前記基板の底面に対して照射することにより、前記半導体膜の一部を溶融させ、

かつ前記第1のレーザ光及び前記第2のレーザ光の照射位置を、該第1のレーザ光又は該第2のレーザ光が傾斜している方向に沿って走査し、前記半導体膜の溶融している部分を移動させることにより、前記半導体膜を結晶化する半導体膜の結晶化方法。

**【請求項 7】**

前記第1のレーザ光及び前記第2のレーザ光は、ビームスポットの強度が互いに略同一である請求項1乃至請求項6のいずれか一項に記載の半導体膜の結晶化方法。

**【請求項 8】**

前記第1のレーザ光及び前記第2のレーザ光は、前記半導体膜で交差する請求項1乃至請求項7のいずれか一項に記載の半導体膜の結晶化方法。

**【請求項 9】**

前記第1のレーザ光及び前記第2のレーザ光のビームスポットは細長い形状であり、走査方向に対して略直角方向に延伸している請求項1乃至請求項8のいずれか一項に記載の半導体膜の結晶化方法。

**【請求項 10】**

前記第1のレーザ光の傾斜角及び前記第2のレーザ光の傾斜角は、絶対値が互いに同一である請求項1乃至請求項9のいずれか一項に記載の半導体膜の結晶化方法。

**【請求項 11】**

10

20

30

40

50

基板上に半導体膜を形成し、

前記半導体膜に、第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第1のレーザ光とは異なる発振器から発振された第2のレーザ光を、前記第1のレーザ光とは反対の方向に傾斜した状態で前記基板の底面に対して照射することにより、前記半導体膜の一部を溶融させ、かつ前記第1のレーザ光及び前記第2のレーザ光の照射位置を、該第1のレーザ光又は該第2のレーザ光が傾斜している方向に沿って走査して、前記半導体膜の溶融している部分を移動させることにより、前記半導体膜を結晶化し、前記半導体膜を選択的に除去することにより島状半導体膜を形成することを特徴とする半導体装置の製造方法。

【請求項12】

基板上に半導体膜を形成し、

前記半導体膜に、第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第1のレーザ光とは異なる長さの光路を経由した第2のレーザ光を、前記第1のレーザ光とは反対の方向に傾斜した状態で前記基板の底面に対して照射することにより、前記半導体膜の一部を溶融させ、かつ前記第1のレーザ光及び前記第2のレーザ光の照射位置を、該第1のレーザ光又は該第2のレーザ光が傾斜している方向に沿って走査して、前記半導体膜の溶融している部分を移動させることにより、前記半導体膜を結晶化し、前記半導体膜を選択的に除去することにより島状半導体膜を形成することを特徴とする半導体装置の製造方法。

【請求項13】

基板上に半導体膜を形成し、

前記半導体膜に、第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、第2のレーザ光を、前記第1のレーザ光とは反対の方向に傾斜した状態で前記基板の底面に対して照射することにより、前記半導体膜の一部を溶融させ、かつ前記第1のレーザ光及び前記第2のレーザ光の照射位置を、該第1のレーザ光又は該第2のレーザ光が傾斜している方向に沿って走査して、前記半導体膜の溶融している部分を移動させることにより、前記半導体膜を結晶化し、

前記半導体膜を選択的に除去することにより島状半導体膜を形成することを特徴とする半導体装置の製造方法。

【請求項14】

前記島状半導体膜には、薄膜トランジスタのソース、チャネル領域及びドレインが形成される請求項11乃至請求項13のいずれか一項に記載の半導体装置の製造方法。

【請求項15】

第1のレーザ光を発振する第1の発振器と、

第2のレーザ光を発振する第2の発振器と、

基板に形成された半導体膜に、前記第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第2のレーザ光を、前記第1のレーザ光とは反対の方向に傾斜した状態で前記基板の底面に対して前記半導体膜に照射する光学系と、

前記基板と前記光学系の相対位置を、該第1のレーザ光及び該第2のレーザ光が傾斜している方向に沿って移動させる移動手段と、

を具備するレーザ照射装置。

【請求項16】

レーザ光を発振する発振器と、

前記レーザ光を第1のレーザ光及び第2のレーザ光に分岐するビームスプリッタと、

基板に形成された半導体膜に、前記第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第2のレーザ光を、前記第1のレーザ光とは異なる長さの光路を経由した後に、前記第1のレーザ光とは反対の方向に傾斜した状態で前記基板の底面に対して前記半導体膜に照射する光学系と、

前記基板と前記光学系の相対位置を、該第1のレーザ光及び該第2のレーザ光が傾斜している方向に沿って移動させる移動手段と、

10

20

30

40

50

を具備するレーザ照射装置。

【請求項 17】

レーザ光を発振する発振器と、

前記レーザ光を第1のレーザ光及び第2のレーザ光に分岐するビームスプリッタと、

基板に形成された半導体膜に、前記第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第2のレーザ光を、前記第1のレーザ光とは反対の方向に傾斜した状態で前記基板の底面に対して前記半導体膜に照射する光学系と、

前記基板と前記光学系の相対位置を、該第1のレーザ光及び該第2のレーザ光が傾斜している方向に沿って移動させる移動手段と、

を具備するレーザ照射装置。

10

【請求項 18】

前記光学系は、シリンドリカルレンズを具備し、

前記第1のレーザ光及び第2のレーザ光は、前記シリンドリカルレンズに距離を隔てて進入し、該シリンドリカルレンズを透過した後に前記半導体膜に照射する請求項15乃至請求項17のいずれか一項に記載のレーザ照射装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体膜の結晶化方法、半導体装置の製造方法、及びレーザ照射装置に関する特

に本発明は、結晶化を行った半導体膜の品質に面内ばらつきが生じることを抑制できる半導体膜の結晶化方法、半導体装置の製造方法、及びレーザ照射装置に関する。

20

【背景技術】

【0002】

近年、ガラス基板上に形成された半導体膜（例えば非晶質半導体膜）にレーザ光を照射し、半導体膜を結晶化させるレーザ結晶化法が広く研究されている。

【0003】

半導体膜を結晶化させるのは、半導体膜を結晶化させることによりキャリアの移動度が高くなるためである。結晶化させた半導体膜は、例えば薄膜トランジスタ（以下TFTと記載）に利用されている。例えばガラス基板上に形成した半導体膜を結晶化した場合、この半導体膜を用いて画素用のTFT及び駆動回路用のTFTを形成することにより、アクティブマトリクス型の表示装置（例えば液晶表示装置や有機EL表示装置）を作製することができる。

30

【0004】

半導体膜を結晶化させる方法には、レーザ結晶化法以外に、ファーネスアニール炉を用いた熱アニール法や、瞬間熱アニール法（RTA法）がある。しかし、これらの方法は600以上

の高温処理が必要である。このため、基板として、高温処理に耐えることができる石英基板を用いる必要があり、製造コストが上昇する。これに対し、レーザ結晶化法は半導体膜にのみ熱を吸収させることができるために、基板の温度をそれほど上昇させずに半導体膜を結晶化させることができる。このため、基板としてガラスやプラスチック等の耐熱性が低い材料を使用することができる。これにより、安価で大面積に容易に加工できるガラス基板を用いることができ、アクティブマトリクス型の表示装置の生産効率が著しく向上する。

40

【0005】

レーザ結晶化法として、パルスレーザであるエキシマレーザを用いた方法が従来からある。エキシマレーザは、波長が紫外域に属しているためシリコンに効率よく吸収され、シリコンに選択的に熱を与えることができる。エキシマレーザを用いる場合、例えばレーザ発振器（レーザ、発振器とも呼ぶ）から射出される矩形状のレーザ光（例えば10mm×30mm）を、光学系によって線状の断面（例えば数百μm×300mm）を持つレーザ光に加工する。そして、線状に加工されたレーザ光（以下、線状のビームスポットと称する）を半導体膜に対して相対的に走査させながら照射することにより、半導体膜の全体を順

50

次結晶化させる。線状のビームスポットの走査する方向を線状のビームスポットに対して垂直な方向にすることで、結晶化効率が高くなる。

#### 【0006】

これに対し、最近は、C W レーザや発振周波数（繰り返し周波数）が 10 M H z 以上のパルスレーザ（以下、モードロックレーザと記載）を線状のビームスポットに加工して半導体膜に対して相対的に走査させながら照射することにより、エキシマレーザを用いて結晶化された半導体膜と比較して結晶の粒径が非常に大きい半導体膜を製造する技術が開発された。この半導体膜が有する大粒径結晶を T F T のチャネル領域に使用すると、チャネル方向には結晶粒界がほとんど存在しなくなるため、キャリア（電子又は正孔）に対するエネルギー障壁が低くなる。この結果、移動度が数百  $c m^2 / V s$  の T F T の作製が可能になる（例えば特許文献 1 参照）。 10

【特許文献 1】特開 2003-332236 号公報（第 4 段落）

#### 【0007】

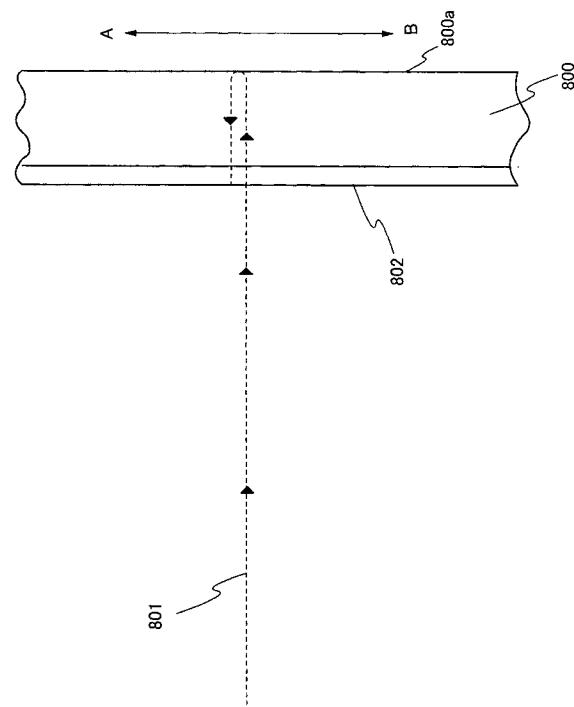

図 37 は、連続発振レーザ又はモードロックレーザから発振されたレーザ光 801（以下レーザ光 801 と記載）を用いて基板 800 上に形成された半導体膜 802 を結晶化する方法の第 1 の従来例を説明する為の図である。本例では、レーザ光 801 は基板 800 に対して垂直な方向から照射されており、かつ基板 800 に対して図中 A - B 方向に相対的に走査されている。レーザ光 801 の一部は半導体膜 802 を透過して基板 800 の下面 800a で反射し、入射してきたレーザ光 801 と半導体膜 802 で干渉する。基板 800 の厚さは場所によってばらついているため、レーザ光 801 の入射光と反射光が場所によって強めあったり弱めあったりする。この結果、結晶化された半導体膜 802 の特性に面内ばらつきが生じる。 20

#### 【0008】

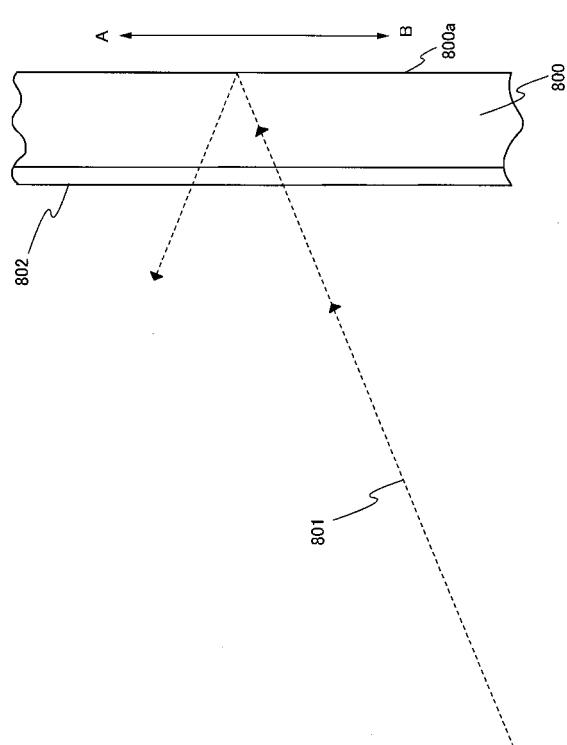

図 38 は、レーザ光 801 を用いて半導体膜 802 を結晶化する方法の第 2 の従来例を説明する為の図である。本例では、レーザ光 801 は基板 800 に対して斜めに照射されている。レーザ光 801 の傾斜方向はレーザ光 801 の走査方向 A - B に沿う方向である。

#### 【0009】

本例では、レーザ光 801 の入射光と反射光が干渉しないが、レーザ光 801 の走査方向によって結晶化条件が異なってしまう。すなわち図中 B から A 方向にレーザ光 801 が相対的に走査される場合、半導体膜 802 には反射光が照射された後に入射光が照射される。これに対し、図中 A から B 方向にレーザ光 801 が相対的に走査される場合、半導体膜 802 には入射光が照射された後に反射光が照射される。レーザ光 801 の入射光と反射光は強度が異なるため、半導体膜 802 には異なる条件で結晶化された 2 つの領域が存在することになる。これら 2 つの領域は互いに異なる特性を持つ。 30

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0010】

上記したように、連続発振レーザ又はモードロックレーザを用いた従来の半導体膜の結晶化方法では、結晶化された半導体膜の特性に面内ばらつきが生じる。

本発明は上記のような事情を考慮してなされたものであり、その目的は、結晶化を行った半導体膜の品質に面内ばらつきが生じることを抑制できる半導体膜の結晶化方法、半導体装置の製造方法、及びレーザ照射装置を提供することにある。 40

#### 【課題を解決するための手段】

#### 【0011】

上記課題を解決するため、本発明に係る半導体膜の結晶化方法は、基板上に形成された半導体膜に、第 1 のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第 1 のレーザ光とは異なる発振器から発振された第 2 のレーザ光を、前記基板の底面に対して前記第 1 のレーザ光とは反対の方向に傾斜した状態で照射することにより、前記半導体膜の一部を溶融させ、かつ前記第 1 及び第 2 のレーザ光の照射位置を、該第 1 又は第 2 のレーザ光が傾斜している方向に略沿って走査して、前記半導体膜の溶融している部分を移 50

動させることにより、前記半導体膜を結晶化するものである。

【0012】

この半導体膜の結晶化方法によれば、前記半導体膜には前記第1のレーザ光及び前記第2のレーザ光が傾斜して照射される。前記第2のレーザ光の傾斜方向は前記第1のレーザ光の傾斜方向とは反対であり、かつ照射位置の移動方向に沿う方向である。このため、前記第1及び第2のレーザ光の照射位置が往復移動する場合、往路及び復路のいずれにおいても、反射光、入射光、及び反射光の順で照射される。従って、前記半導体膜の結晶化条件は、往路及び復路のいずれにおいても略同一になる。

【0013】

また、前記第1のレーザ光及び前記第2のレーザ光は、それぞれ前記基板の底面に対して傾斜しているため、反射光は入射光と重ならず、相互に干渉しない。このため、反射光と入射光が干渉することにより前記半導体膜の結晶化条件にはらつきが生じることを防止できる。

10

【0014】

また前記第1及び第2のレーザ光は異なる発振器から発振されているため、互いに干渉することが抑制される。

【0015】

従って、結晶化された半導体膜の特性に面内はらつきが生じることを抑制できる。なお、前記第1及び第2のレーザ光は、発振周波数が10MHz以上のパルスレーザ、又はCWレーザから発振されたレーザ光であるのが好ましい。

20

【0016】

本発明に係る他の半導体膜の結晶化方法は、基板上に形成された半導体膜に、第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第1のレーザ光とは異なる長さの光路を経由した第2のレーザ光を、前記基板の底面に対して前記第1のレーザ光とは反対の方向に傾斜した状態で照射することにより、前記半導体膜の一部を溶融させ、かつ前記第1及び第2のレーザ光の照射位置を、該第1又は第2のレーザ光が傾斜している方向に沿って走査し、前記半導体膜の溶融している部分を移動させることにより、前記半導体膜を結晶化するものである。

【0017】

この半導体膜の結晶化方法によれば、前記第1及び第2のレーザ光の照射位置が往復移動する場合、往路及び復路のいずれにおいても、反射光、入射光、及び反射光の順で照射される。従って、前記半導体膜の結晶化条件は、往路及び復路のいずれにおいても略同一になる。また、前記第1のレーザ光及び前記第2のレーザ光の反射光は入射光と重ならず、相互に干渉しない。このため、反射光と入射光が干渉することにより前記半導体膜の結晶化条件にはらつきが生じることを防止できる。

30

【0018】

また前記第1及び第2のレーザ光は光路の長さが異なるため、互いに干渉することが抑制される。

【0019】

従って、結晶化された半導体膜の特性に面内はらつきが生じることを抑制できる。なお、前記第1のレーザ光及び前記第2のレーザ光は、同一の発振器から発振されたレーザ光をビームスプリッタで分岐することにより形成されているのが好ましい。また、前記第1及び第2のレーザ光は、発振周波数が10MHz以上のパルスレーザから発振されたレーザ光であるのが好ましい。

40

【0020】

本発明に係る他の半導体膜の結晶化方法は、基板上に形成された半導体膜に、第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、第2のレーザ光を、前記基板の底面に対して前記第1のレーザ光とは反対の方向に傾斜した状態で照射することにより、前記半導体膜の一部を溶融させ、かつ前記第1及び第2のレーザ光の照射位置を、該第1又は第2のレーザ光が傾斜している方向に沿って走査し、前記半導体膜の溶融している

50

部分を移動させることにより、前記半導体膜を結晶化するものである。

【0021】

この半導体膜の結晶化方法によれば、前記第1及び第2のレーザ光の照射位置が往復移動する場合、往路及び復路のいずれにおいても、反射光、入射光、及び反射光の順で照射される。従って、前記半導体膜の結晶化条件は、往路及び復路のいずれにおいても略同一になる。また、前記第1のレーザ光及び前記第2のレーザ光の反射光は入射光と重ならず、相互に干渉しない。このため、反射光と入射光が干渉することにより前記半導体膜の結晶化条件にばらつきが生じることを防止できる。従って、結晶化された半導体膜の特性に面内ばらつきが生じることを抑制できる。

【0022】

上記した半導体膜の結晶化方法それにおいて、前記第1及び第2のレーザ光は、ビームスポットの強度が互いに略同一であるのが好ましく、また、前記半導体膜で交差するのが好ましい。また、前記第1及び第2のレーザ光のビームスポットは細長い形状であり、走査方向に対して略直角方向に延伸しているのが好ましい。このとき、第1のレーザ光は、第1のレーザ光の長軸を含み、かつ半導体膜に垂直な面に対して第1の角度をもって半導体膜に入射し、第2のレーザ光はその面に対して第1のレーザ光とは反対方向から第2の角度をもって半導体膜に入射する。さらに、前記第1のレーザ光の傾斜角及び前記第2のレーザ光の傾斜角は、絶対値が互いに同一であるのが好ましい。

【0023】

本発明に係る半導体装置の製造方法は、基板上に半導体膜を形成する工程と、前記半導体膜に、第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第1のレーザ光とは異なる発振器から発振された第2のレーザ光を、前記基板の底面に対して前記第1のレーザ光とは反対の方向に傾斜した状態で照射することにより、前記半導体膜の一部を溶融させ、かつ前記第1及び第2のレーザ光の照射位置を、該第1又は第2のレーザ光が傾斜している方向に沿って走査して、前記半導体膜の溶融している部分を移動させることにより、前記半導体膜を結晶化する工程と、前記半導体膜を選択的に除去することにより島状半導体膜を形成する工程とを具備する。

【0024】

この半導体装置の製造方法によれば、結晶化された前記半導体膜の面内ばらつきが抑制されるため、前記島状半導体膜の品質にばらつきが生じることが抑制される。

【0025】

本発明に係る他の半導体装置の製造方法は、基板上に半導体膜を形成する工程と、前記半導体膜に、第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第1のレーザ光とは異なる長さの光路を経由した第2のレーザ光を、前記基板の底面に対して前記第1のレーザ光とは反対の方向に傾斜した状態で照射することにより、前記半導体膜の一部を溶融させ、かつ前記第1及び第2のレーザ光の照射位置を、該第1又は第2のレーザ光が傾斜している方向に沿って走査して、前記半導体膜の溶融している部分を移動させることにより、前記半導体膜を結晶化する工程と、前記半導体膜を選択的に除去することにより島状半導体膜を形成する工程とを具備する。

【0026】

本発明に係る他の半導体装置の製造方法は、基板上に半導体膜を形成する工程と、前記半導体膜に、第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、第2のレーザ光を、前記基板の底面に対して前記第1のレーザ光とは反対の方向に傾斜した状態で照射することにより、前記半導体膜の一部を溶融させ、かつ前記第1及び第2のレーザ光の照射位置を、該第1又は第2のレーザ光が傾斜している方向に沿って走査して、前記半導体膜の溶融している部分を移動させることにより、前記半導体膜を結晶化する工程と、前記半導体膜を選択的に除去することにより島状半導体膜を形成する工程とを具備する。

【0027】

前記島状半導体膜には、例えば薄膜トランジスタのソース、チャネル領域及びドレインが

10

20

30

40

50

形成される。

【0028】

本発明に係るレーザ照射装置は、第1のレーザ光を発振する第1の発振器と、第2のレーザ光を発振する第2の発振器と、基板に形成された半導体膜に、前記第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第2のレーザ光を、前記基板の底面に対して前記第1のレーザ光とは反対の方向に傾斜した状態で前記半導体膜に照射する光学系と、前記基板と前記光学系の相対位置を、該第1及び第2のレーザ光が傾斜している方向に沿って移動させる移動手段とを具備する。

【0029】

本発明に係る他のレーザ照射装置は、レーザ光を発振する発振器と、前記レーザ光を第1のレーザ光及び第2のレーザ光に分岐するビームスプリッタと、基板に形成された半導体膜に、前記第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第2のレーザ光を、前記第1のレーザ光とは異なる長さの光路を経由した後に、前記基板の底面に対して前記第1のレーザ光とは反対の方向に傾斜した状態で前記半導体膜に照射する光学系と、前記基板と前記光学系の相対位置を、該第1及び第2のレーザ光が傾斜している方向に沿って移動させる移動手段とを具備する。

【0030】

本発明に係る他のレーザ照射装置は、レーザ光を発振する発振器と、前記レーザ光を第1のレーザ光及び第2のレーザ光に分岐するビームスプリッタと、基板に形成された半導体膜に、前記第1のレーザ光を前記基板の底面に対して傾斜した状態で照射しつつ、前記第2のレーザ光を、前記基板の底面に対して前記第1のレーザ光とは反対の方向に傾斜した状態で前記半導体膜に照射する光学系と、前記基板と前記光学系の相対位置を、該第1及び第2のレーザ光が傾斜している方向に沿って移動させる移動手段とを具備する。

【0031】

上記したレーザ照射装置それぞれにおいて、前記光学系は、シリンドリカルレンズを具備し、前記第1及び第2のレーザ光は、前記シリンドリカルレンズに距離を隔てて進入し、該シリンドリカルレンズを透過した後に前記半導体膜に照射するようにしても良い。

【発明の効果】

【0032】

上記したように本発明によれば、結晶化された半導体膜の特性に面内ばらつきが生じることを抑制できる。また、この半導体膜を用いて形成された島状半導体層の品質にばらつきが生じることを抑制できる。

【発明を実施するための最良の形態】

【0033】

(第1の実施形態)

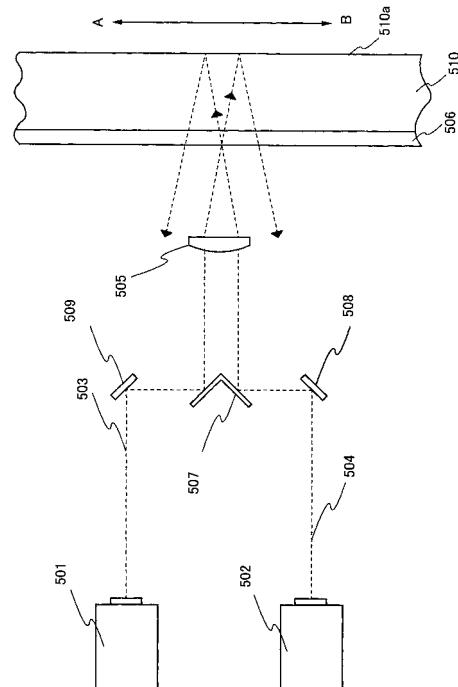

図1は、本発明の第1の実施形態に係る半導体膜の結晶化方法を説明する為の図である。本実施形態は、レーザ照射装置を用いて半導体膜506を溶融結晶化する方法である。半導体膜506は基板510上に形成されている。レーザ照射装置は、基板510を図中A-B方向に往復移動させることにより、半導体膜506に対するレーザ光の照射位置を移動させる。

【0034】

半導体膜506は、例えばアモルファス状又は微結晶状の半導体膜(例えばアモルファスシリコン膜又はポリシリコン膜)である。基板510は、例えばガラス基板、石英基板、アルミナなど絶縁物で形成される基板、後工程の処理温度に耐え得る耐熱性を有するプラスチック基板、シリコン基板、または金属板である。また、基板510は、ステンレスなどの金属基板または半導体基板などの表面に、酸化珪素や窒化珪素などの絶縁膜を形成した基板であっても良い。なお、基板510にプラスチック基板を用いる場合、P C(ポリカーボネート)、P E S(ポリエーテルサルファン)、P E T(ポリエチレンテレフタレート)もしくはP E N(ポリエチレンナフタレート)等、プラスチックの中でもガラス転移点が比較的高いものを用いることが好ましい。なお、半導体膜506と基板510の間

10

20

20

30

40

50

に下地となる絶縁膜があつても良い。

【0035】

半導体膜506には、第1の発振器501が発振した第1のレーザ光503、及び第2の発振器502が発振した第2のレーザ光504それぞれが、線状のビームスポットに加工された後に照射される。第1の発振器501及び第2の発振器502は同一の構造を有しており、第1の発振器501及び第2の発振器502は出力が互いに同一である。

【0036】

ここでいう「線状」は、厳密な意味で「線」を意味しているのではなく、アスペクト比の大きい長方形若しくは長楕円形を意味している。例えばアスペクト比が2以上(好ましくは10以上1000以下)のものを「線状」と呼ぶが、「線状」が矩形状に含まれることに変わりはない。線状のビームスポットは、例えば短軸が5μm以上15μmであり、長軸が500μm以上1000μm以下である。

10

【0037】

第1の発振器501及び第2の発振器502は、CWレーザ又は発振周波数(繰り返し周波数)が10MHz以上のパルスレーザ(例えばモードロックレーザ、以下、モードロックレーザと記載)である。第1の発振器501及び第2の発振器502がパルスレーザの場合、パルスレーザの発振周波数は、半導体膜506がパルス照射によって溶融した後、溶融部が固化する前に次のパルスが入射するように下限値が設定される。このようにすることにより、レーザ光が照射されている領域は溶融状態を維持できる。

20

【0038】

連続発振レーザの例としては、Arレーザ、Krレーザ、及びCO<sub>2</sub>レーザ等のガスレーザ、YAGレーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、GdVO<sub>4</sub>レーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、及びY<sub>2</sub>O<sub>3</sub>レーザ等の固体レーザ、ヘリウムカドミウムレーザ等の金属蒸気レーザがある。固体レーザの中には、レーザ結晶が多結晶であるセラミックレーザがあり、例えばY<sub>2</sub>O<sub>3</sub>レーザ又はYAGレーザが本発明に適用できる。モードロックレーザの例としては、YVO<sub>4</sub>レーザ、チタンサファイアレーザ、YAGレーザがある。また、Diskレーザを用いても良い。Diskレーザを用いる場合、レーザ媒質の形状がディスク形状であるため、冷却効率が良いという特徴、すなわちエネルギー効率及びレーザ品質が高いという特徴がある。

30

【0039】

また、第1のレーザ光503及び第2のレーザ光504は、TEM<sub>00</sub>で第1の発振器501及び第2の発振器502から発振されるのが良い。この場合、半導体膜506の被照射面において、線状のビームスポットのエネルギー均一性を向上させることができる。ただし、他のモード(例えば第2高調波)で発振されるレーザ光を第1のレーザ光503及び第2のレーザ光504として用いても良い。

30

【0040】

第1のレーザ光503は第1の発振器501から発振された後、ミラー509及びV字型のミラー507それぞれに反射され、その後シリンドリカルレンズ505に入射する。第2のレーザ光504は第2の発振器502から発振された後、ミラー508及びミラー507それぞれに反射され、その後シリンドリカルレンズ505に入射する。ミラー507によって光路が変更された後、第1のレーザ光503及び第2のレーザ光504は互いに平行であるが、相互間の距離は、シリンドリカルレンズ505に入射できる距離が維持されている。

40

【0041】

第1のレーザ光503及び第2のレーザ光504は、シリンドリカルレンズ505によって線状のビームスポットに加工され、基板510の底面に対して傾斜した状態で照射される。このとき、第1のレーザ光503及び第2のレーザ光504は、半導体膜506で交差するように照射されるのが好ましいが、後述する半導体膜506の結晶化工程において半導体膜506のうち同一の部分を溶融するのであれば、相互に離間した状態で半導体膜506に照射されても良い。

50

## 【0042】

第1のレーザ光503及び第2のレーザ光504の傾斜方向は、基板510の移動方向に沿う方向(図中A-B方向に沿う方向)であるが、第2のレーザ光504の傾斜方向は第1のレーザ光503の傾斜方向とは反対である。基板510の底面に対する第1のレーザ光503及び第2のレーザ光504それぞれの傾斜角度は、互いに絶対値が同一であるのが好ましい。また、第1のレーザ光503及び第2のレーザ光504は、ビームスポットの強度は互いに略同一であるのが好ましい。

## 【0043】

なお、第1のレーザ光503及び第2のレーザ光504は、発振器から半導体膜506に入射するまでの光路の長さは略同一であるが、互いに異なる発振器から発振されるため、半導体膜506で交差するときの位相が互いに異なる。従って、半導体膜506で交差するときに第1のレーザ光503及び第2のレーザ光504が互いに干渉することが抑制される。

## 【0044】

半導体膜506に照射された第1のレーザ光503及び第2のレーザ光504は、半導体膜506に吸収されるが、一部は吸収されずに基板510に入射し、その後その一部が基板510の底面510aで反射する。第1のレーザ光503及び第2のレーザ光504は、それぞれ基板510の底面510aに対して傾斜しているため、反射光は入射光と重ならず、相互に干渉しない。

## 【0045】

半導体膜506を結晶化する時、レーザ照射装置は、基板510を載置しているステージ(図示せず)を図中A-B方向すなわち第1のレーザ光503及び第2のレーザ光504が傾斜している方向に沿って移動させる。半導体膜506は、第1のレーザ光503及び第2のレーザ光504が照射されている部分が溶融するが、この溶融している部分は、基板510が図中A-B方向に移動するにつれて途切れることなく連続的に移動する。これにより、固液界面が連続的に移動して半導体膜506が結晶化する。その結晶粒は第1のレーザ光503及び第2のレーザ光504の走査方向すなわち図中A-B方向に長くなる。

## 【0046】

半導体膜506の全面を結晶化するためには、レーザ照射装置は、基板510を図中AからBに向けて移動させた後、図中A-B方向に直交する方向に移動し、さらに図中BからAに向けて移動させる、という動きを繰り返し行う必要がある。本実施形態において、第2のレーザ光504の傾斜方向は第1のレーザ光503の傾斜方向とは反対であり、かつ基板510の移動方向に沿う方向(図中A-B方向に沿う方向)である。このため、半導体膜506は、図中AからBに向けて移動する場合、及び図中BからAに向けて移動する場合のいずれの場合においても、反射光、入射光、及び反射光の順で照射される。従って、半導体膜506の結晶化条件は、基板510の移動方向によらず略同一になる。特に第1のレーザ光503と第2のレーザ光504の傾斜角の絶対値が同一である場合、半導体膜506の結晶化条件は更に均一になる。

## 【0047】

また、上記したように、第1のレーザ光503及び第2のレーザ光504は、それぞれ基板510の底面に対して傾斜しているため、反射光は入射光と重ならず、相互に干渉しない。このため、反射光と入射光が干渉することにより半導体膜506の結晶化条件にばらつきが生じることを防止できる。

## 【0048】

従って、本実施形態によれば、結晶化された半導体膜の特性に面内ばらつきが生じることを抑制できる。

## 【0049】

なお、本実施形態において、さらに偶数個(例えば2つ)のレーザ発振源を追加することにより、半導体膜506に照射するレーザ光を追加しても良い。この場合、追加されたレ

10

20

30

40

50

レーザ光は、第1のレーザ光503及び第2のレーザ光504と同一の方向に傾斜するが、一部（例えば一つ）は第1のレーザ光503と同一方向から照射され、他（例えば残りの一つ）は第2のレーザ光504と同一方向からされる。追加されたレーザ発振源が2つの場合、追加されたレーザ光の傾斜角は互いに同一であるのが好ましい。

#### 【0050】

##### （第2の実施形態）

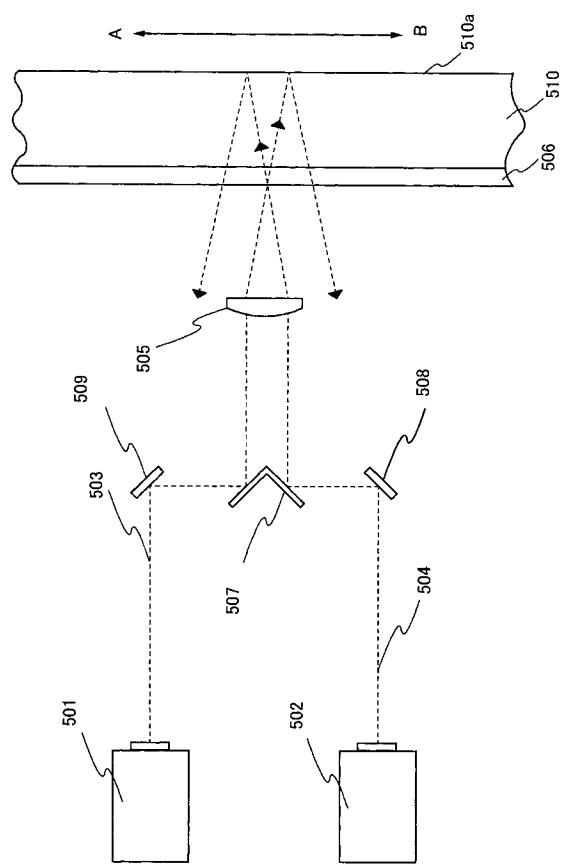

図2は、本発明の第2の実施形態に係る半導体膜の結晶化方法を説明する為の図である。本実施形態は、レーザ照射装置の発振器が一つであり、この発振器（例えば、モードロックレーザ）520から発振されたレーザ光520aをビームスプリッタ521で2つに分けることにより、第1のレーザ光503及び第2のレーザ光504を生成する点、及び第1のレーザ光503及び第2のレーザ光504がシリンドリカルレンズ505に入射するまでの光学系を除いて、第1の実施形態と同様である。発振器520の具体的な例は、第1の実施形態に示したモードロックレーザの例と同様である。以下、第1の実施形態と同様の構成については同一の符号を付し、説明を省略する。

#### 【0051】

第1のレーザ光503及び第2のレーザ光504は、シリンドリカルレンズ505に入射するまでの光路の距離が、互いに異なる。具体的には、第1のレーザ光503は、ビームスプリッタ521から直接シリンドリカルレンズ505に入射し、第2のレーザ光504は、ビームスプリッタ521からミラー522、523、524それぞれによって反射された後、シリンドリカルレンズ505に入射する。第1のレーザ光503と第2のレーザ光504の光路の差は、例えば1cm以上30m以下である。

#### 【0052】

このため、第1のレーザ光503及び第2のレーザ光504は、シリンドリカルレンズ505に入射するときのパルスのタイミングが互いにずれている。従って、第1のレーザ光503及び第2のレーザ光504が半導体膜506で交差するときに互いに干渉することが抑制される。

#### 【0053】

また、第1の実施形態と同様に、半導体膜506は、図中AからBに向けて移動する場合、及び図中BからAに向けて移動する場合のいずれの場合においても、反射光、入射光、及び反射光の順で照射される。従って、半導体膜506の結晶化条件は、基板510の移動方向によらず同一になる。

#### 【0054】

また、第1の実施形態と同様に、第1のレーザ光503及び第2のレーザ光504は、それぞれ基板510の底面に対して傾斜しているため、反射光は入射光と重ならず、相互に干渉しない。このため、反射光と入射光が干渉することにより半導体膜506の結晶化条件にはらつきが生じることを防止できる。

#### 【0055】

従って、本実施形態によっても、結晶化された半導体膜の特性に面内はらつきが生じることを抑制できる。なお、本実施形態において、発振器520から発振されるレーザ光はCWレーザから発振されたレーザ光であっても良いが、光路差をコヒレント長以上にする必要がある。CWレーザの具体例は第1の実施形態と同様である。

#### 【0056】

なお、第1及び第2の実施形態それぞれにおいて、光学系を図中A-B方向すなわち第1のレーザ光503又は第2のレーザ光504が傾斜している方向に移動させることにより、半導体膜506に対する第1及び第2のレーザ光503、504の照射位置を移動させても良い。

#### 【0057】

また、半導体膜506のうち高い結晶性を要求されない部分については、第1及び第2のレーザ光503、504を照射しなくても良い。又は、第1及び第2のレーザ光503、504の走査速度を増加させるなど、高い結晶性が得られないような条件でレーザ照射を

10

20

30

40

50

行っても良い。

【実施例 1】

【0058】

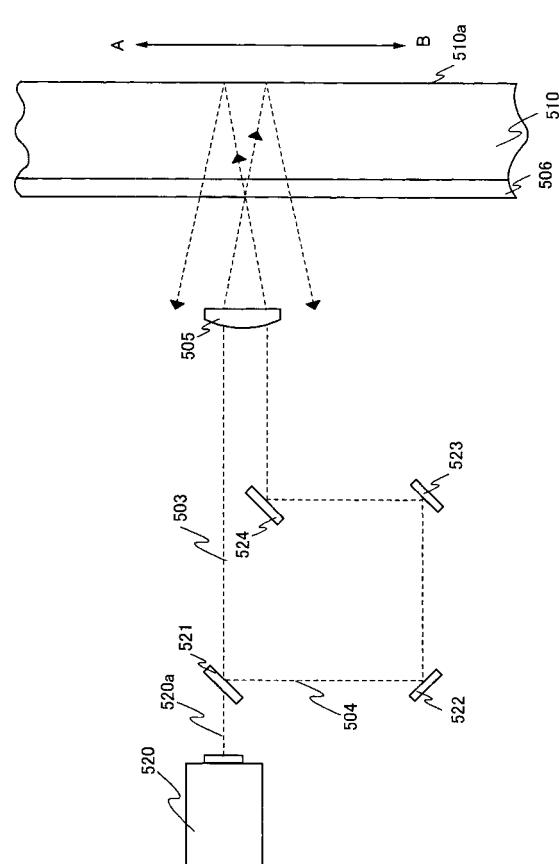

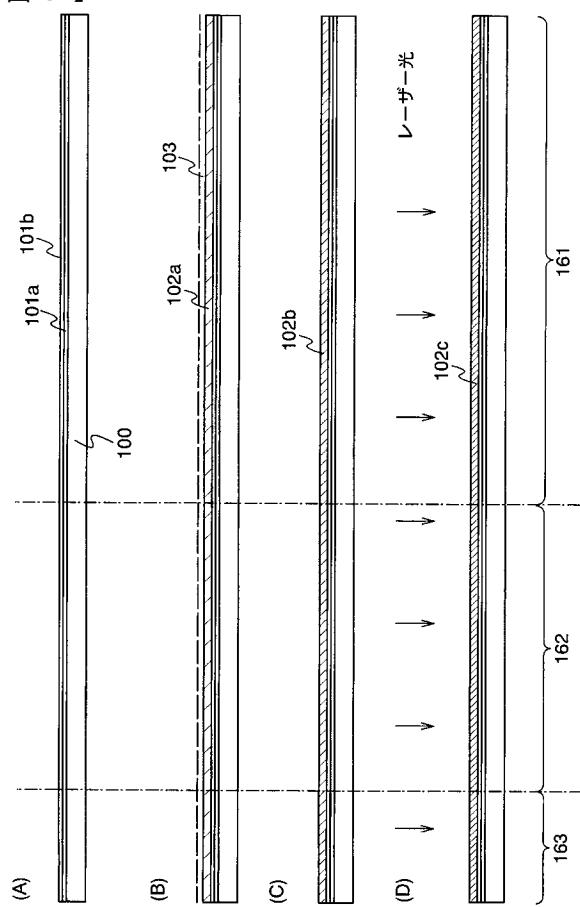

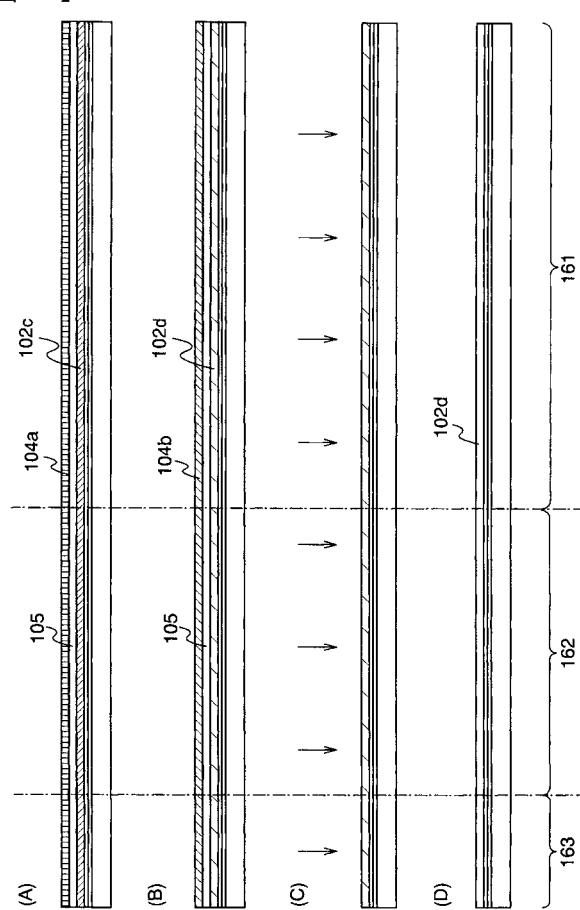

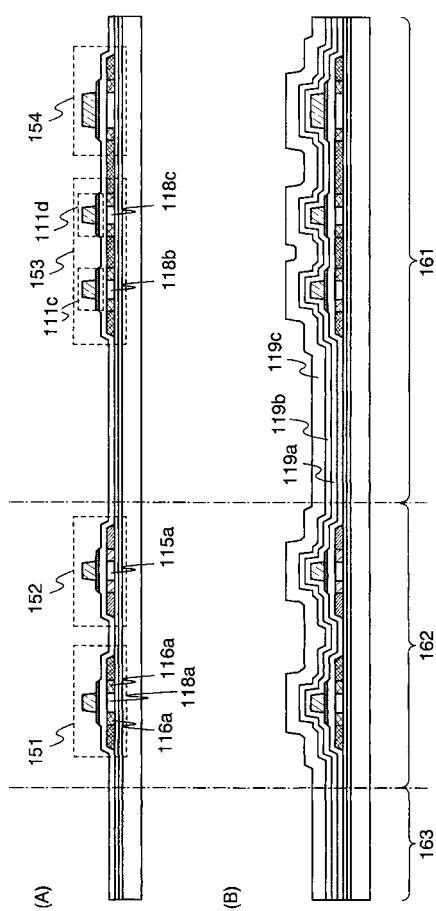

実施例 1 に係る半導体装置及びその半導体装置を用いた発光装置の作製方法の一態様について図 3 ~ 図 13 を用いて説明する。

【0059】

先ず、基板 100 の上に絶縁層 101a を形成した後、さらに絶縁層 101a 上に積層するように絶縁層 101b を形成する。絶縁層 101a は、基板 100 からの不純物の拡散を阻止できるように形成されていることが好ましく、例えば、窒化珪素、または酸素を含む窒化珪素等も用いて形成された層であることが好ましい。また、絶縁層 101b は、後の工程で形成する半導体層との間に生じる応力差が小さくなるような層であることが好ましく、例えば酸化珪素、または微量の窒素を含む酸化珪素等によって形成された層であることが好ましい。ここで、絶縁層 101a、101b の形成方法について特に限定はなく、プラズマ CVD 法、減圧 CVD 法、スパッタリング法、PVD 法等を用いて形成すれば良い。また、基板 100 について特に限定はなく、ガラス、石英等の絶縁体から成る基板の他、シリコン、ステンレス等から成る基板上に絶縁層を設けたもの等を用いても良いし、この他、ポリエチレンテレフタレート (PET)、ポリエチレンナフタレート (PEN) 等のプラスチック等からなり可撓性を有する基板を用いても良い。なお、石英からなる基板のように不純物の含有量が非常に少ない基板を用いる場合は、絶縁層 101a、101b は必ずしも形成しなくても良い (図 3 (A))。

10

20

30

40

50

【0060】

次いで、絶縁層 101b 上に TFT (薄膜トランジスタ) の活性層として用いられる半導体層 (半導体層 106a ~ 106c (図 5 (A) 参照。)) を形成する。トランジスタ活性層として用いられる半導体層は結晶質半導体で形成されることが好ましい。結晶質半導体の作製方法について以下に説明する。

【0061】

先ず、絶縁層 101b の上に珪素、シリコンゲルマニウム等の半導体を含む非晶質半導体層 102a を形成する。非晶質半導体層 102a の厚さは 40 ~ 80 nm とすることが好ましい。なお、絶縁層 101a、101b を形成した成膜装置と同じ成膜装置を用いて絶縁層 101a、101b と非晶質半導体層 102a とを連続的に、つまり絶縁層 101a、101b の形成後大気に曝すことなく非晶質半導体層 102a を連続的に形成してもよい。このようにすることにより、大気中に含まれる不純物が絶縁層 101b に付着することを防ぐことができる。

【0062】

次いで、非晶質半導体層 102a の表面に結晶化を助長する金属元素 103 を添加する。結晶化を助長する金属元素としては、鉄 (Fe)、ニッケル (Ni)、コバルト (Co)、ルテニウム (Ru)、ロジウム (Rh)、パラジウム (Pd)、オスニウム (Os)、イリジウム (Ir)、白金 (Pt)、銅 (Cu)、金 (Au) 等の元素を用いることができる。これらの金属元素のうち 1 つ又は複数の元素を用いて、スパッタ法、PVD 法、減圧 CVD 法、プラズマ CVD 法、蒸着法等により前記金属元素又は前記金属元素の珪化物の薄膜を形成する方法、又は前記金属元素を含む溶液を塗布する方法等を用いて非晶質半導体膜 102 に金属元素を添加すれば良い。また、非晶質半導体膜 102 上にマスクを形成して、選択的に金属元素を添加しても良い。

【0063】

また、金属元素 103 を添加する際には、非晶質半導体層 102a 上に薄い酸化膜を形成しておくのが好ましい。例えば、非晶質半導体膜 102a の表面に 1 ~ 10 nm の薄い酸化膜を形成した後、結晶化を助長する金属元素 103 を酸化膜上に保持させれば良い。酸化膜の形成方法について特に限定はなく、オゾン水または過酸化水素水などの酸化性を有する溶液で非晶質半導体層 102a の表面を処理することによって形成しても良いし、または酸素雰囲気中における紫外線の照射によってオゾンを発生させる方法等を用いて形成

しても良い。また、結晶化を助長する金属元素を保持させる方法について特に限定はなく、結晶化を助長する金属元素を含む溶液を用いて酸化膜の表面を処理することによって金属元素を酸化膜に付着させて保持させても良いし、または、スパッタリング法等を用いて酸化膜上に結晶化を助長する金属元素を含む層若しくはクラスタを形成することによって保持させても良い。なお、結晶化を助長する金属元素を含む溶液としては、例えばニッケル酢酸塩溶液等の金属塩溶液が挙げられる(図3(B))。

#### 【0064】

次いで、ラピッドサーマルアニール(RTA)法、またはファーネスアニール炉等を用いた熱処理によって非晶質半導体層102aを結晶化し、非結晶成分と結晶成分とを含む結晶質半導体層102bを形成する(図3(C))。RTA法は、光照射によって加熱するランプ方式のRTA法であっても良いし、または高温のガスによって加熱するガス方式のRTA法であっても良い。熱処理は、窒素ガス、または希ガス等の反応性の低いガスで充填された雰囲気下で行うことが好ましい。また、RTA法を用いる場合、熱処理温度は600~800になるようにすることが好ましく、熱処理時間は、3~9分であることが好ましい。ファーネスアニール炉によって熱処理する場合、熱処理温度は500~600、熱処理時間は3~6時間であることが好ましい。なお、非晶質半導体層102aに水素が多く含まれている場合は、350~500の熱処理によって非晶質半導体層102aから水素を放出させ $1 \times 10^{20}$ atoms/cm<sup>3</sup>以下の水素濃度となるようにした後、結晶化の為の熱処理を行うことが好ましい。

#### 【0065】

次いで、大気中において結晶質半導体層102bを、第1の実施形態又は第2の実施形態で説明した方法を用いて再び結晶化し、結晶質半導体層102cを形成する(図3(D))。具体的には、第1のレーザ光及び第2のレーザ光それぞれを傾斜させて結晶質半導体層102bに照射して交差させ、かつ結晶質半導体層102bが形成された基板100に對して相対的に第1及び第2のレーザ光が移動するように、基板100を走査させる。これにより、結晶質半導体層102cの結晶粒は、走査方向に沿って連続的に成長した状態になる。また、結晶質半導体層102cの面内ばらつきが抑制される。なお、後述するTFTのチャネル方向は、結晶粒が連続して成長した方向と略同一方向になる。

#### 【0066】

次いで、結晶質半導体層102cの上に珪素、シリコンゲルマニウム等の半導体、及びアルゴン(Ar)等の希ガスを含む非晶質半導体層104aを形成した後、熱処理をする(図4(A))。ここで、結晶質半導体層102cと非晶質半導体層104aとの間には1~10nmの薄い酸化膜105が設けられていることが好ましい。この酸化膜105は、先のレーザ光照射による結晶質半導体層102cの形成に伴って形成された酸化膜であっても良いし、または、レーザ光の照射後に結晶質半導体層102cの表面をオゾン水等を用いて処理することによって形成された酸化膜であっても良い。また、非晶質半導体層104aの形成方法について特に限定はなく、プラズマCVD法、減圧CVD法、スパッタリング法、PVD法等を用いて形成すれば良い。また、非晶質半導体層104aの厚さは20~40nmであることが好ましい。また、熱処理にRTA法を用いる場合、熱処理温度は600~800になるようにすることが好ましく、熱処理時間は、3~9分であることが好ましい。ファーネスアニール炉によって熱処理する場合、熱処理温度は500~600、熱処理時間は3~6時間であることが好ましい。

#### 【0067】

熱処理することによって、結晶質半導体層102cに含まれていた結晶化を助長する金属元素は結晶質半導体層102cから非晶質半導体層104aへゲッタリングされる(ゲッタリング後の結晶質半導体層102cを結晶質半導体層102dと称する)。なお、結晶化を助長する金属元素が非晶質半導体層104aへゲッタリングされるのに伴い、非晶質半導体層104aは結晶成分を含む半導体層104bとなる(図4(B))。

#### 【0068】

ゲッタリング後、半導体層104bを選択的にエッチングして除去する。半導体層104

10

20

30

40

50

b のエッティング方法について特に限定はないが、テトラメチルアンモニウムハイドロオキサイド (TMAH) 若しくはコリン等の溶液等の溶液を用いることによって特に酸化膜 105 に対して高選択比でエッティングできる。このように酸化膜 105 は半導体層 104b のエッティングと共に結晶質半導体層 102d がエッティングされてしまうことを防ぐ為のストッパーとして機能する。なお、半導体層 104b の表面に自然酸化膜等の酸化膜が形成されている場合は、予め、フッ酸を含む溶液等を用いて該酸化膜を除去してから半導体層 104b をエッティングすることが好ましい。半導体層 104b を除去した後、フッ酸を含む溶液等を用いて酸化膜 105 を除去する (図 4 (C))。

#### 【0069】

以上のような工程を得ることによって表面の平均粗さが非常に小さい結晶質半導体層 102d を得ることができる (図 4 (D))。なお、結晶化を助長する元素を添加せずに半導体層の結晶化を行っても良い。この場合、結晶質半導体層に金属元素が含まれていないため、ゲッタリングに係る各工程を行う必要はない。

#### 【0070】

なお、熱処理によって結晶質半導体層 102b を形成する処理を省略して、第 1 の実施形態又は第 2 の実施形態で説明した方法を用いて非晶質半導体層 102a を結晶化することにより、結晶質半導体層 102c を形成しても良い。また、金属元素 103 を添加する工程及び金属元素 103 をゲッタリングする工程を省略しても良い。

#### 【0071】

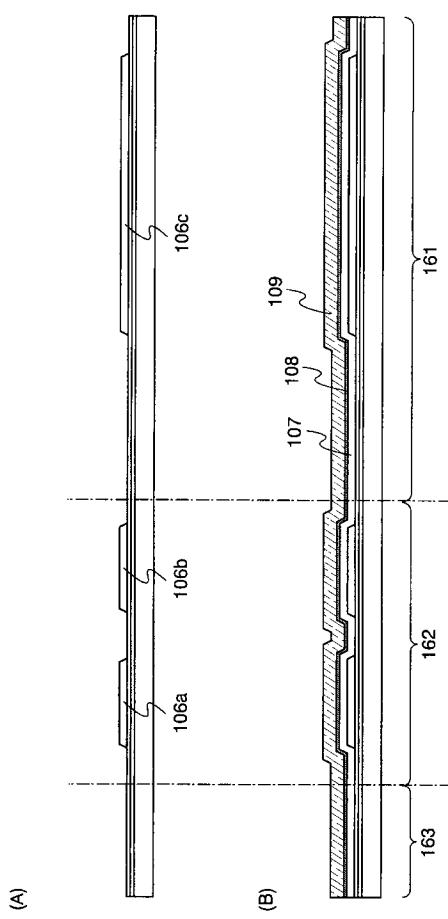

次いで、結晶質半導体層 102d を所望の形状に加工し、島状の半導体層 106a ~ 106c を得る (図 5 (A))。結晶質半導体層 102d の加工方法について特に限定はなく、例えば、結晶質半導体層 102d の上にレジストマスクを形成した後不要な部分をエッティングによって除去する方法を用いることができる。なお、レジストマスクの形成方法についても特に限定はなく、フォトリソグラフィ法の他、インクジェット法のように液滴を吐出するタイミングと位置を制御しながら描画して所望の形状のマスクを形成する方法を用いても良い。また、エッティング方法についても特に限定はなく、ドライエッティング法またはウェットエッティング法の何れを用いて行っても良い。

#### 【0072】

なお、半導体層 106a ~ 106c には、TFT の閾値電圧を調節する為の不純物が添加されても良い。添加される不純物について特に限定はなく、燐あるいはヒ素等の n 型の導電性を付与する不純物であっても良いし、またはボロン等の p 型の導電性を付与する不純物であっても良い。また、閾値電圧を調整する為の不純物が添加されるタイミングについても特に限定はなく、結晶質半導体層 102d を形成した後であって、半導体層 106a ~ 106c を形成する前であっても良いし、または、半導体層 106a ~ 106c の形成後、次工程で形成されるゲート絶縁層 107 の形成前であっても良い。また、本工程において不純物は、半導体層 106a ~ 106c (あるいは結晶質半導体層 102d) の全体に添加しても良いし、またはレジスト等を用いて一部をマスクし、部分的に添加されるようにしても良い。

#### 【0073】

次いで、半導体層 106a ~ 106c を覆うようにゲート絶縁層 107 を形成する (図 5 (B))。ゲート絶縁層 107 の形成方法について特に限定はなく、プラズマ CVD 法、減圧 CVD 法、スパッタリング法、PVD 法等の成膜方法を用いて形成すれば良い。この他、半導体層 106a ~ 106c の表面を酸化させてゲート絶縁層 107 を形成しても良い。また、ゲート絶縁層 107 は酸化珪素または窒化珪素、又は窒素を含む酸化珪素、または酸素を含む窒化珪素等を用いて形成すれば良い。また、ゲート絶縁層 107 は单層で成る層、または異なる物質から成る層が積層した多層で成る層のいずれであっても構わない。

#### 【0074】

次いで、ゲート絶縁層 107 の上にゲート電極 111a ~ 111d、及び容量電極 111e を形成する (図 6 (B) 参照)。ゲート電極の構成及び形成方法について特に限定はな

10

20

30

40

50

いが、本形態では、第1の導電層と、第1の導電層と第2の導電層とが積層してなるゲート電極111a～111d、及び容量電極111eの形成方法について、図5(B)～図6(B)を用いて以下に説明する。

【0075】

先ず、ゲート絶縁層107の上に第1の導電層108を形成し、さらに第1の導電層108の上に第2の導電層109を形成する(図5(B))。第1の導電層108と第2の導電層109とは、それぞれ異なる導電物を用いて形成されていることが好ましい。第1の導電層108は、ゲート絶縁層107との密着性が良い導電物を用いて形成されることが好ましく、例えば窒化チタン、窒化タンタル、チタン、タンタル等を用いて形成されていることが好ましい。また、第2の導電層109は、抵抗率の低い導電物を用いて形成されていることが好ましく、例えば、タンゲステン(W)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、またはこれらの金属を主成分として含む合金、或いは金属化合物等を用いて形成されていることが好ましい。合金としては、アルミニウムと珪素との合金、アルミニウムとネオジウムとの合金等が挙げられる。また金属化合物としては窒化タンゲステン等が挙げられる。第1の導電層108と第2の導電層109の形成方法について特に限定はなく、スパッタリング法、蒸着法等、いずれの方法を用いても良い。

【0076】

次いで、マスク135a、マスク135b、マスク135c、マスク135d、及びマスク135eを第2の導電層109上に形成する。そして、第1の導電層108と第2の導電層109とをエッチングして、第1の導電層108a、第1の導電層108b、第1の導電層108c、第1の導電層108d、第1の導電層108e、第2の導電層109a、第2の導電層109b、第2の導電層109c、第2の導電層109d、第2の導電層109eをそれぞれ導電層の側壁がそれぞれの導電層の水平面に対し傾斜を有するような形状となるように形成する(図6(A))。

【0077】

次いで、マスク135a～135eを設けたまま、第2の導電層109a～109eを選択的にエッチングし、第2の導電層110a、第2の導電層110b、第2の導電層110c、第2の導電層110d、第2の導電層110eを形成する(図6(B))。この時、第2の導電層110a～110eそれぞれの導電層の側壁がそれぞれの導電層の水平面に対し垂直になるように異方性の高い条件でエッチングし加工することが好ましい。これによって、第2の導電層109a～109eの側壁の傾斜部が除去される。このようにして第1の導電層108a～108eのそれぞれの上に第1の導電層108a～108eのそれよりも幅が短い第2の導電層110a～110eを設けることにより、第1の導電層108a～108eと第2の導電層110a～110eとがそれぞれ組み合わせられてなるゲート電極111a～111d、及び容量電極111eを形成することができる。

【0078】

なお、マスク135a～135eは、それぞれ、所望の形状に形成した後、さらにアッシングすることによって細らせて形成されたマスクであっても良い。このようなマスクを用いることによって、より微細な形状の電極を形成でき、その結果、チャネル長の短いTFTを得ることができる。そして、チャネル長が短いTFTを作製することによってより高速で動作する回路を得られるようになる。

【0079】

次に、ゲート電極111a～111d、及び容量電極111eをマスクとして、n型の導電性を付与する不純物元素を添加し、第1のn型不純物領域112a、第1のn型不純物領域112b、第1のn型不純物領域112cを設ける。n型を付与できる不純物元素について特に限定はなく、燐、ヒ素などを用いることができる。第1のn型不純物領域112a～112cを設けた後、マスク135a～135eを除去する(図6(C))。

【0080】

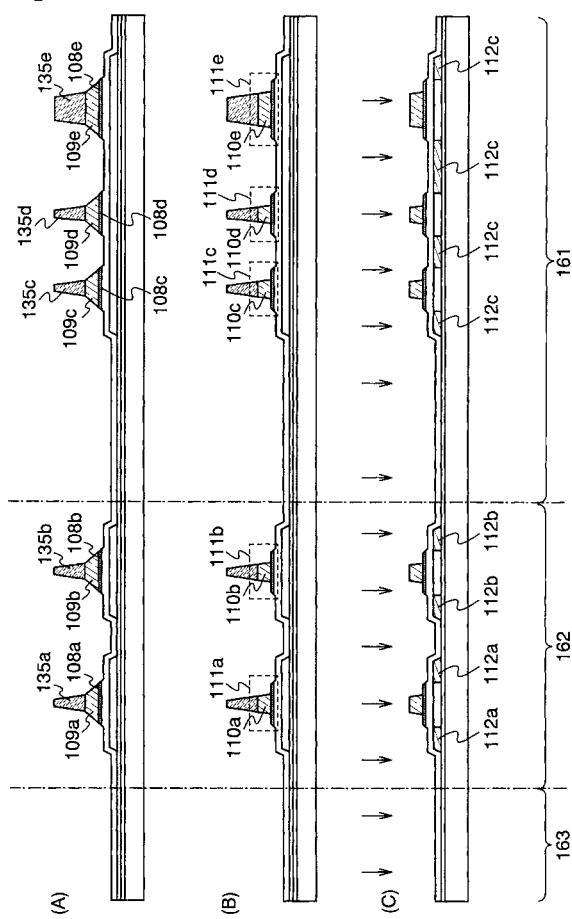

マスク135a～135eを除去した後、半導体層106aを覆うマスク136a、半導体層106cを覆うマスク136bを形成する。マスク136aおよびマスク136b並

10

20

30

40

50

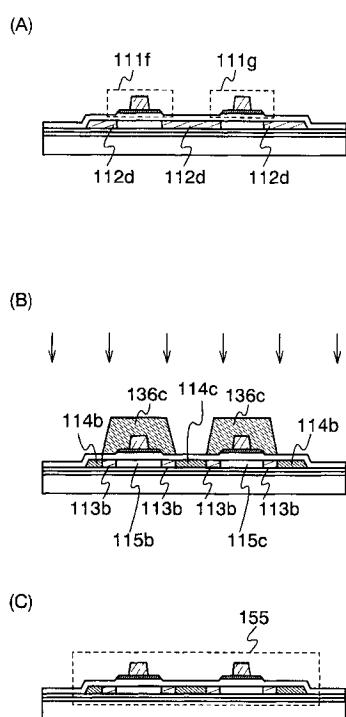

びに第1の導電層108b、第2の導電層110bをマスクとしてn型の導電性を付与する不純物元素を半導体層106bへさらに添加し、第1の導電層108bと重なる領域に第2のn型不純物領域113aを、第1の導電層108b及び第2の導電層110bのいずれとも重なっていない領域に第3のn型不純物領域114aを設ける(図7(A))。このようにして設けられた第3のn型不純物領域114aはTFTのソース若しくはドレイン、またはTFTと容量とを接続する機能を有する。また、ゲート電極111bと重なり、ソース若しくはドレインとして機能する第3のn型不純物領域114aとチャネル形成領域115aとの間に、第3のn型不純物領域114aと同じ導電型であると共に第3のn型不純物領域114aよりも低い濃度を有する第2のn型不純物領域113aを設けることによって、ホットキャリア劣化に対する耐性に優れたnチャネル型TFT152を得ることができる。なお、第2のn型不純物領域113aに挟まれた領域はチャネル形成領域115aとして機能する。

#### 【0081】

なお、図13の各図に示すように、第1のn型不純物領域112dのうちゲート電極とオーバーラップしていない領域の一部をマスク136cで覆っても良い。このようにすると、ゲート電極111f、111gと重なっていてソース若しくはドレインとして機能する第3のn型不純物領域114b、114cと、チャネル形成領域115b、115cとの間に、第3のn型不純物領域114b、114cと同じ導電型であり第3のn型不純物領域114b、114cよりも低い濃度を有する第2のn型不純物領域113bを設けることができる。これによってオフリーケ電流を低減することができるnチャネル型TFT155を得ることができる。なお、TFT155のゲート電極111fとゲート電極111gは同じタイミングで同じ電圧が印加されるように相互に電気的に接続している。すなわちTFT155は二つのチャネル形成領域115b、115cを有するダブルゲート型のTFTである。

#### 【0082】

次いで、図7(B)に示すように、マスク136a、136bを除去した後、半導体層106bを覆うマスク137を形成する。次いで、マスク137、及び第2の導電層110a、110c~110eをマスクとしてp型の導電性を付与する不純物元素を半導体層106a、106cへ添加し、第1の導電層108a、108c~108eのそれと重なる領域に第1のp型不純物領域116a、116bを設けると共に、第1の導電層108a、108c~108eと重なっていない領域に第2のp型不純物領域117a、117b、117cを設ける。このようにして設けられた第2のp型不純物領域117a、117b、117cはTFTのソース若しくはドレインとなるか、またはTFTと容量とを接続する機能を有する。

#### 【0083】

このようにしてpチャネル型TFT151、153及び容量154を得ることができる(図8(A)参照)。なお、TFT151のうち第1のp型不純物領域116aに挟まれた領域はチャネル形成領域118aとして機能する。また、TFT153においてゲート電極111cとゲート電極111dとは同じタイミングで同じ電圧が印加されるように電気的に接続しており、TFT153は二つのチャネル形成領域118b、118cを有するダブルゲート型のTFTである。なお、p型の導電性を付与する不純物元素の添加工程では、先に形成されていた第1のn型不純物領域112a、112cに含まれる不純物元素よりも高濃度のp型の導電性を付与する為、n型の導電性は打ち消される。

#### 【0084】

次いで、マスク137を除去する。以上のようにして、画素部161で用いられるTFT153、容量154、及び駆動回路部162で用いられるTFT151、152を含む半導体装置を作製することができる(図8(A))。半導体装置には、画素部161、駆動回路部162の他、外部から信号を入力する為の端子部163が後述の工程を経ることによって設けられる。なお、TFTの構造について特に限定はなく、例えば、二つのゲート電極の間に半導体層が挟まれた構造を有するマルチゲート型のTFTであっても良いし、

ソースまたはドレインとして機能する不純物領域とチャネル形成領域とが隣接した（これらの間にソースまたはドレインとして機能する不純物領域よりも低濃度の領域を含まない）シングルドレイン型のTFT等であっても良い。

【0085】

TFT151、152のチャネル形成領域118a、115a及びTFT153のチャネル形成領域118b、118cそれぞれのチャネル方向は、結晶質半導体層の結晶粒が成長する方向と略同一方向である。このため、チャネル形成領域115a、118a、118b、118cそれぞれにおいて結晶粒界がほとんど含まれなくなり、電子や正孔などのキャリアに対するエネルギー障壁が低くなる。その結果、TFT151、152、153の移動度が、例えば数百  $\text{cm}^2/\text{Vs}$  になる。また、結晶質半導体層の面内ばらつきが抑制されるため、TFTの特性にばらつきが生じることを抑制できる。

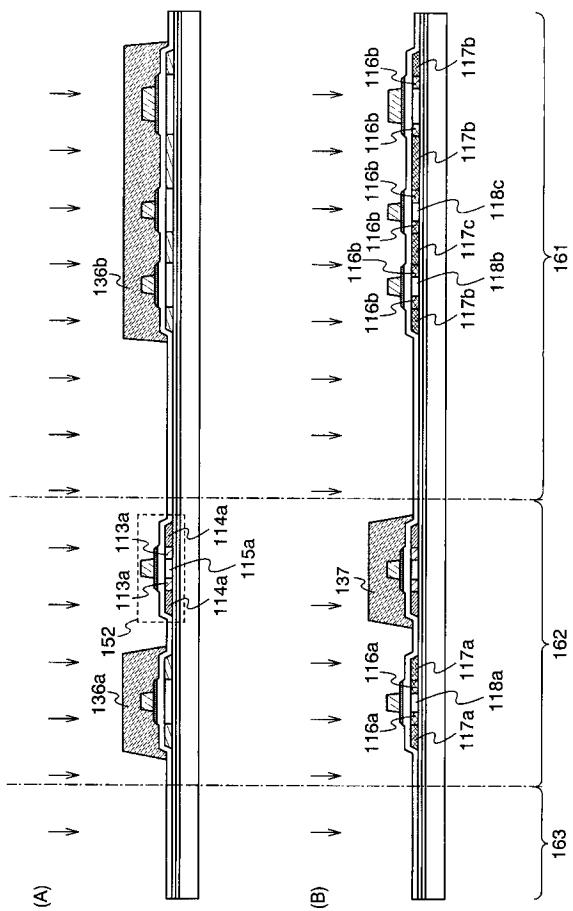

【0086】

次いで、TFT151、152、153、及び容量154を覆うように、第1の層間絶縁層119a、119b、119cを順に形成する（図8（B））。第1の層間絶縁層119aは、酸化珪素、窒化珪素等の絶縁物を用いて形成することができる。ここで、酸化珪素、窒化珪素には、それぞれ、窒素、酸素が含まれていても良い。また、酸化珪素及び窒化珪素等の無機絶縁物の他、アクリルやポリイミド等の有機絶縁物、及びシロキサン系材料を出発材料として形成されたSi-O-Si結合を含む絶縁膜（以下、シロキサン系絶縁膜と記載する）等から選ばれる一または二以上の化合物を用いて形成しても良い。なお、シロキサンとは、シリコン（Si）と酸素（O）との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基（例えばアルキル基、芳香族炭化水素）が用いられる。置換基として、フルオロ基を用いても良い。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いても良い。以下、同様である。

【0087】

また、第1の層間絶縁層119a、119b、119cの形成方法についても特に限定はなく、プラズマCVD法、減圧CVD法、スパッタリング法、PVD法等の成膜方法を用いて形成すれば良い。さらに、本形態では第1の層間絶縁層は119a、119b、119cの三層が積層した多層となっているが、第1の層間絶縁層の積層数についても特に限定はなく、単層であっても良いし、二層以上の多層であっても良い。

【0088】

なお、第1の層間絶縁層119a、119b、119cのなかで少なくとも一層は、水素を含む絶縁層であることが好ましい。水素を含む絶縁層としては、例えば、SiH<sub>4</sub>ガス、NH<sub>3</sub>ガス、N<sub>2</sub>Oガス及びH<sub>2</sub>ガスを原料ガスとしプラズマCVD法を用いて形成された窒化珪素からなる層が挙げられる。このようにして形成された窒化珪素には水素の他、酸素も含まれる。第1の層間絶縁層119a、119b、119cの少なくとも一層に水素を含む絶縁層とすることによって、絶縁層に含まれた水素を利用して半導体層106a～106cに含まれるダングリングボンドを終端化させる為の水素化をすることができる。従って、例えば炉内に水素ガスを充填した雰囲気で水素化処理を行う必要がなく、簡便に水素化を行うことができる。また、水素を含む窒化珪素を第1の層間絶縁層に用いる場合、当該水素を含む窒化珪素で形成された層とTFTとの間に酸化珪素、若しくは窒素を含む酸化珪素で形成された層を設けることが好ましい。本形態のように、第1の層間絶縁層が119a、119b、119cの三層で構成される場合は、第1の層間絶縁層119aを酸化珪素、若しくは窒素を含む酸化珪素で形成し、第1の層間絶縁層119bを水素を含む窒化珪素（さらに酸素が含まれていても良い）で形成し、第1の層間絶縁層119cを酸化珪素、若しくは窒素を含む酸化珪素で形成することが好ましい。第1の層間絶縁層119a～119cは、例えば発光素子からの発光が第1の層間絶縁層119a～119cを介して外部に取り出される場合には、発光が通る光路の長さを調節する為の光路長調整手段として用いることができる。

【0089】

また、第1の層間絶縁層119a、119b、119cのいずれかの形成前若しくは形成

10

20

30

40

50

後において、先に添加したn型若しくはp型の導電性を付与する為の不純物元素を活性化する為の処理をすることが好ましい。活性化の為の処理方法について特に限定はなく、ファーネスアーニール炉、RTA、またはレーザ光照射等を用いて行えば良い。

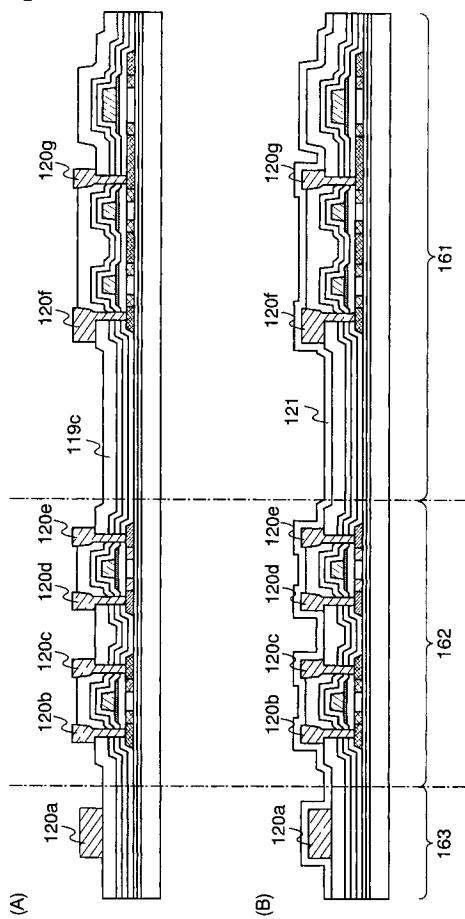

【0090】

次いで、第1の層間絶縁層119a、119b、119cに、半導体層106a～106cへ至る開口部を形成する。さらに、該開口部及び第1の層間絶縁層119cを覆う導電層を形成した後、これを所望の形状に加工し、画素部161に配線120f、120gを、駆動回路部162に配線120b～120eを、端子部163に配線120aを、それぞれ形成する(図9(A))。

【0091】

開口部の形成方法について特に限定はなく、レジスト等により形成されたマスクを第1の層間絶縁層119c上に設けた後、第1の層間絶縁層119a、119b、119cをエッチングすることによって形成すれば良い。ここで、エッチング方法について特に限定はなく、ウェットエッチング法若しくはドライエッチング法の何れの方法を用いても良い。

【0092】

また、導電層は、単層であっても多層であっても良いが、少なくとも一層はアルミニウム、銅等の導電性の高い金属、またはアルミニウムとネオジウム等の合金を用いて形成された層であることが好ましい。ここでアルミニウムには珪素等が含まれていても良い。また、多層とする場合には、導電性の高い金属を含む層を挟むように、窒化チタン、窒化タンタル等の金属窒化物を用いて形成された層を設けることが好ましい。なお、配線120a～120gには、異なる層に設けられた配線若しくは電極を電気的に接続する為の接続部として機能する導電層も含まれる。

【0093】

次いで、配線120a～120gを覆うように第2の層間絶縁層121を形成する(図9(B))。第2の層間絶縁層121は、酸化珪素、窒化珪素等の絶縁物を用いて形成することができる。ここで、酸化珪素、窒化珪素には、それぞれ、窒素、酸素が含まれていても良い。また、酸化珪素及び窒化珪素等の無機絶縁物の他、アクリルやポリイミド等の有機絶縁物、及びシリコサン等から選ばれる一または二以上の化合物を用いて形成しても良い。また、第2の層間絶縁層121の形成方法についても特に限定はなく、プラズマCVD法、減圧CVD法、スパッタリング法、PVD法等の成膜方法を用いて形成すれば良い。さらに、本実施例では第2の層間絶縁層121は単層となっているが、これに限らず二層以上の多層であっても良い。

【0094】

次いで、第2の層間絶縁層121を通って配線120fに至る開口部を設け、かつ配線120aを露出させるために、第2の層間絶縁層121を選択的にエッチングする。エッチングは、第2の層間絶縁層121上にレジスト等により形成されたマスクを設けた後、ウェットエッチング法またはドライエッチング法等によって行えば良い。

【0095】

次いで、第2の層間絶縁層121上に発光素子の電極122を形成する(図10(A))。発光素子の電極122を形成に用いられる材料について特に限定はなく、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛等の酸化物半導体、またはアルミニウム、金、白金等の導電体を用いて形成すれば良い。発光素子の電極122の形成方法についても特に限定はなく、例えば、第2の層間絶縁層121上に前記した酸化物半導体若しくは導電体を用いて形成された層の上にレジスト等により形成されたマスクを設けた後、酸化物半導体若しくは導電体を用いて形成された層をエッチングし、所望の形状に加工すれば良い。

【0096】

次いで、発光素子の電極122の端部を覆う絶縁層123を形成する(図10(B))。絶縁層123は、酸化珪素、窒化珪素等の無機絶縁物、アクリル、ポリイミド、レジスト等の有機絶縁物、またはシリコサン等を用いて形成することができるが、なかでも感光性

10

20

30

40

50

アクリル、感光性ポリイミド、レジスト等の感光性樹脂を用いて形成することが好ましい。感光性樹脂を用いてフォトリソグラフィにより所望の形状となるように形成することによって、丸みを帯びた形状のエッジを有する絶縁層123とすることができる、その結果、発光素子の劣化を低減させることができる。なお、配線120a上には絶縁層123は形成されていないため、配線120aは露出したままである。

【0097】

次いで、発光素子の電極122及び絶縁層123の上に発光層124を形成する(図11(A))。発光層124は、有機物若しくは無機物のいずれか一方を用いて形成されても良いし、または有機物と無機物の両方を用いて形成されても良い。また、発光層124は、単層であっても良いし、または、所望の波長の発光を呈する物質(発光物質)を含む層の他に正孔輸送層、電子輸送層、正孔注入層、電子注入層等を有する多層であっても良い。また、多層とする場合、発光素子の電極122上に、PEDOT等の導電性の高い有機物を用いて形成された層、正孔輸送性の高い物質とその物質に対し電子受容性を示す物質とを混合して形成された層、または電子輸送性の高い物質とその物質に対し電子供与性を示す物質とを混合して形成された層のいずれかを設けた後、発光物質を含む層、正孔輸送層、電子輸送層等の他の層を形成することが好ましい。PEDOT(ポリエチレンジオキシチオフェン)等の導電性の高い有機物を用いて形成された層、正孔輸送性の高い物質とその物質に対し電子受容性を示す物質とを混合して形成された層、及び電子輸送性の高い物質とその物質に対し電子供与性を示す物質とを混合して形成された層は、これらの層の厚さを厚くしても発光素子の駆動電圧の増加を招き難い為、これらの層の厚さを厚くすることで、発光素子の電極122の表面に形成された凹凸を緩和し、発光素子の電極間の短絡等を防ぐことができる。なお、発光物質は蛍光を発光するものでも良いし燐光を発光するものであっても良い。

【0098】

なお、発光層124は、発光色の異なる発光素子毎に作り分けても良いし、または同じ発光色を呈する一つの層として連なった状態で形成されても良い。同じ発光色を呈する場合、カラーフィルタ等と組み合わせ、発光装置の外部に取り出される発光は画素毎に異なった色となるようにしても良い。

【0099】

次いで、発光層124の上に発光素子の電極125を形成する(図11(A))。発光素子の電極125の形成に用いられる材料について特に限定はなく、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛等の酸化物半導体、またはアルミニウム、金、白金等の導電体を用いて形成すれば良い。なお、発光素子の電極122若しくは発光素子の電極125の少なくとも一方は発光層124からの発光を透過できるように、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛等の透明導電材料で形成されていることが好ましい。

【0100】

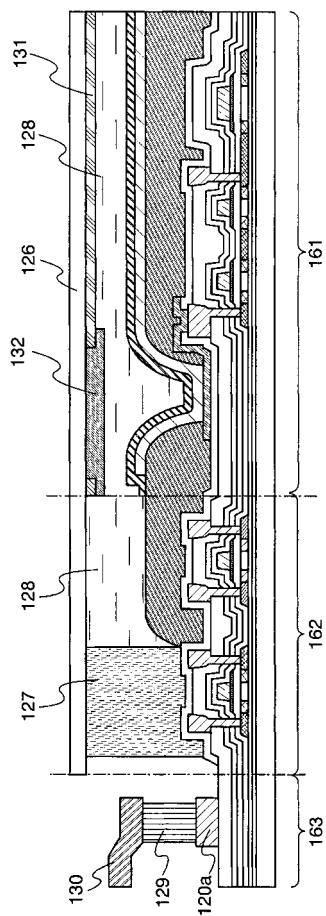

次いで、基板100と基板126とを、先に形成したTFT及び発光素子が封じ込められるように、シール材127を用いて貼り合わせる。なお、基板126には、図12に示すように、遮光層131とカラーフィルタ132が設けられていても良い。さらに基板100と基板126とで封止された内部128は、窒素、またはアルゴン等の不活性ガスで充填されていても良いし、樹脂材料等によって充填されていても良い。充填される樹脂材料には、乾燥剤が含まれていても良い。

【0101】

次いで、導電性接着剤129等を用いて配線120aにFPC(フレキシブルプリントサーキット)130を接続する(図11(B)、図12)。

【0102】

以上のようにして、発光装置を作製することができる。上記したように、発光装置が有するTFTのチャネル方向は、結晶質半導体層102cの結晶粒が成長する方向と略同一方向である。このため、TFTの移動度が高くなる。また、結晶質半導体層102cの面内

10

20

20

30

40

50

ばらつきが抑制できるため、TFTの特性にはばらつきが生じることを抑制できる。

【0103】

従って、発光装置の応答特性は良くなり、かつ発光品質に面内ばらつきが生じることを抑制できる。なお、本形態では、発光装置の作製方法について説明したが、発光素子の電極122以降の工程及び回路構成を適宜変更することによって液晶装置等も作製することができる。

【実施例2】

【0104】

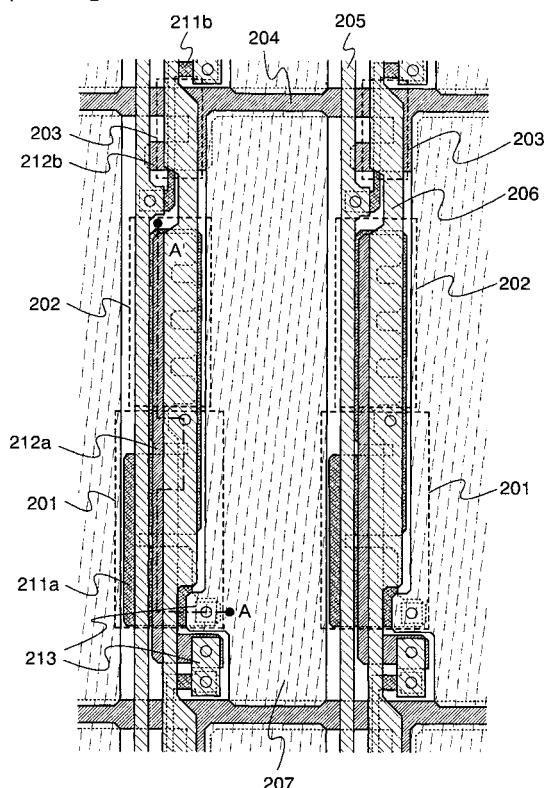

実施例1で説明した作製方法によって作製される発光装置の画素部の一態様について図14の上面図を用いて説明する。

10

【0105】

図14において、破線A-A'で表される部分の断面は、図10(B)における画素部161の断面図に相当する。なお、図14では、発光素子の電極122の端部を覆う絶縁層123は図示していないが、実際には設けられている。図14に示すように、半導体層211aと、ゲート電極及び容量電極として機能する領域を含む第1の導電層212aとが重なり、図10のTFT153に相当するTFT201、及び容量154に相当する容量202とがそれぞれ設けられている。

【0106】

第1の導電層212aは、第2の導電層213を介して発光素子の電極207(図10の発光素子の電極122に相当)と接続している。また、ゲート線204が第1の導電層212aと同じ層で形成されている。さらに、ゲート線204と交差するようにソース線205と電流供給線206とが設けられている。ソース線205は、半導体層211b及び第3の導電層212bそれぞれを含むTFT203のソースに接続している。なお、第3の導電層212bはゲート線204及び第1の導電層212aと同じ層で設けられていると共に、ゲート線204と接続している。

20

【0107】

また、ゲート線204の一部はTFT203のゲート電極として機能するように設けられている。電流供給線206は、TFT201がオンになったときに発光素子へ電流が供給されるように半導体層211aと接続している。なお、本形態における接続には、例えば半導体層211bと第1の導電層212aとの接続のように間に別の導電層(本形態の場合は第4の導電層214)を介して電気的に接続する場合も含まれる。また、本形態では、第1の導電層212aのうち容量202の電極として機能部分は凸凹した鋸歯状の形状になっている。このような形状とすることで、容量202へ電荷を蓄積し易くなる。

30

【0108】

TFT201、203、容量202、ゲート線204、ソース線205、電流供給線206のそれぞれの接続関係を図15の回路図で示した。なお、図14の発光素子の電極207は、発光素子208に含まれている。発光素子208はダイオード型の素子であり、本形態のように発光素子208と直列に接続したTFT201がpチャネル型TFTである場合は発光素子の電極207は陽極として機能する。これとは反対にTFT201がnチャネル型TFTである場合は発光素子208の電極207は陰極として機能する。

40

【0109】

本発明の発光装置の画素部には、図15で表されるような回路によって駆動する複数の発光素子がマトリクス状に配列されている。なお、発光素子を駆動させる為の回路については、図15に示したものには限定されるわけではなく、例えば入力された信号を強制的に消去する為の消去線及び消去動作に用いられる消去用のTFTを設けた構成の回路等であっても良い。

【実施例3】

【0110】

実施例1又は2に示した構成を表示装置として利用した電子機器について、図16を参照しつつ説明する。

50

## 【0111】

図16(A)に示すテレビジョンは、本体8001、表示部8002等を含んでいる。表示部8002には、実施例1又は2に示した表示装置を有している。この表示装置は、画素を駆動するTFTの特性のばらつきが抑制されている。このため、表示のばらつきを抑制したテレビジョンを提供することができる。

## 【0112】

図16(B)に示す情報端末機器は、本体8101、表示部8102等を含んでいる。表示部8102は、実施例1又は2に示した表示装置を有している。この表示装置は、画素を駆動するTFTの特性のばらつきが抑制されている。このため、表示のばらつきを抑制した情報端末機器を提供することができる。

10

## 【0113】

図16(C)に示すビデオカメラは、本体8201、表示部8202等を含んでいる。表示部8202は、実施例1又は2に示した表示装置を有している。この表示装置は、画素を駆動するTFTの特性のばらつきが抑制されている。このため、表示のばらつきを抑制したビデオカメラを提供することができる。

## 【0114】

図16(D)に示す電話機は、本体8301、表示部8302等を含んでいる。表示部8302は、実施例1又は2に示した表示装置を有している。この表示装置は、画素を駆動するTFTの特性のばらつきが抑制されている。このため、表示のばらつきを抑制した電話機を提供することができる。

20

## 【0115】

図16(E)に示す携帯型のテレビジョンは、本体8401、表示部8402等を含んでいる。表示部8402は、実施例1又は2に示した表示装置を有している。この表示装置は、画素を駆動するTFTの特性のばらつきが抑制されている。このため、表示のばらつきを抑制した携帯型のテレビジョンを提供することができる。またテレビジョンとしては、携帯電話機などの携帯端末に搭載する小型のものから、持ち運びをすることができる中型のもの、また、大型のもの(例えば40インチ以上)まで、幅広いものに、本発明の発光装置を適用することができる。

## 【0116】

なお、実施例3に係る電子機器は、図16(A)～(E)に限定されず、表示部等にTFTを有する表示装置を含む様々な電子機器が含まれる。

30

## 【実施例4】

## 【0117】

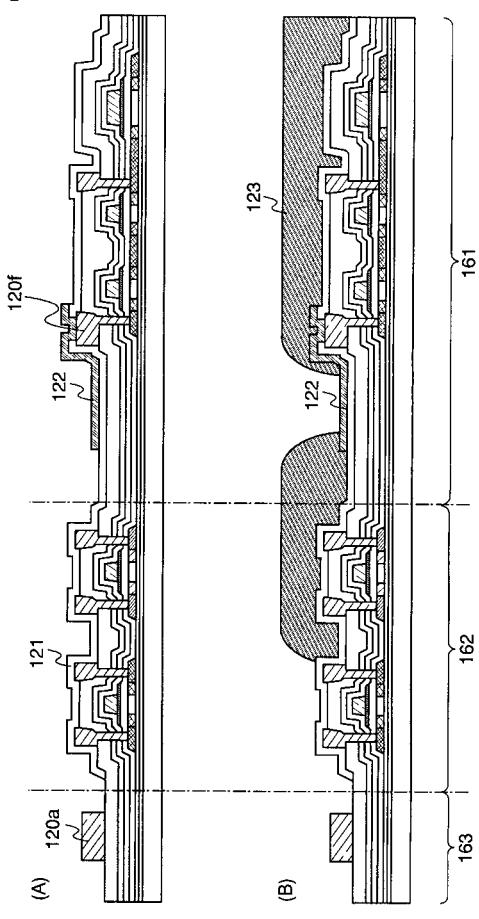

実施例4に係る半導体装置の作製方法について、図17～図21の断面図と、図22の上面図を参照して説明する。

## 【0118】

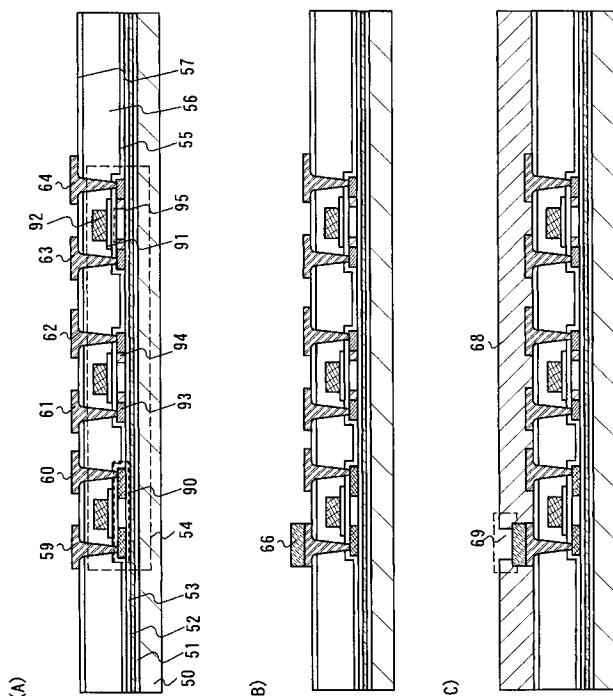

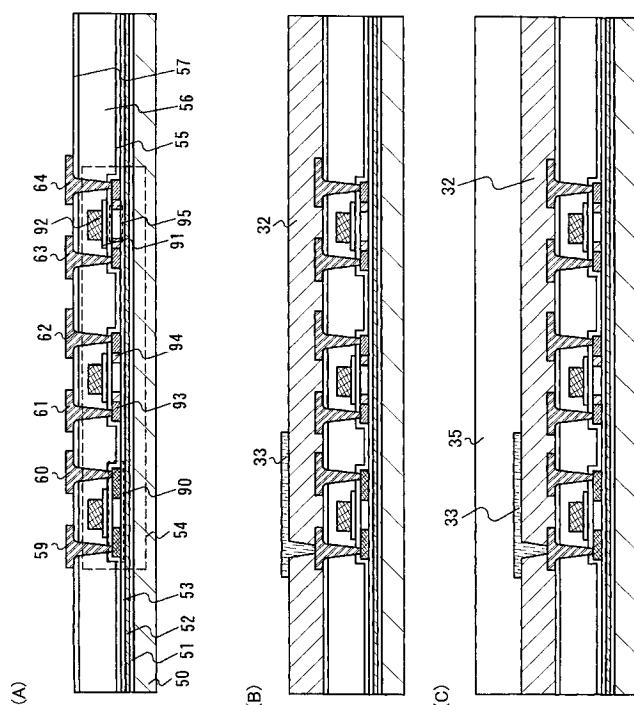

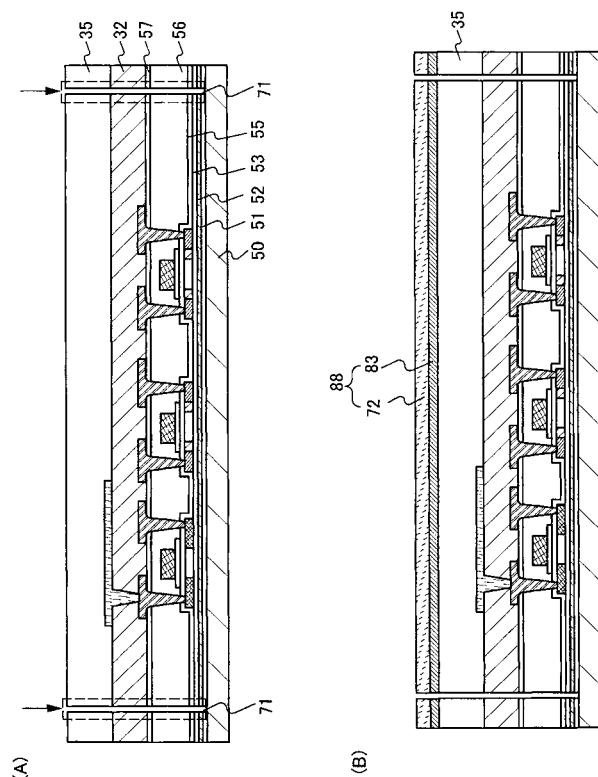

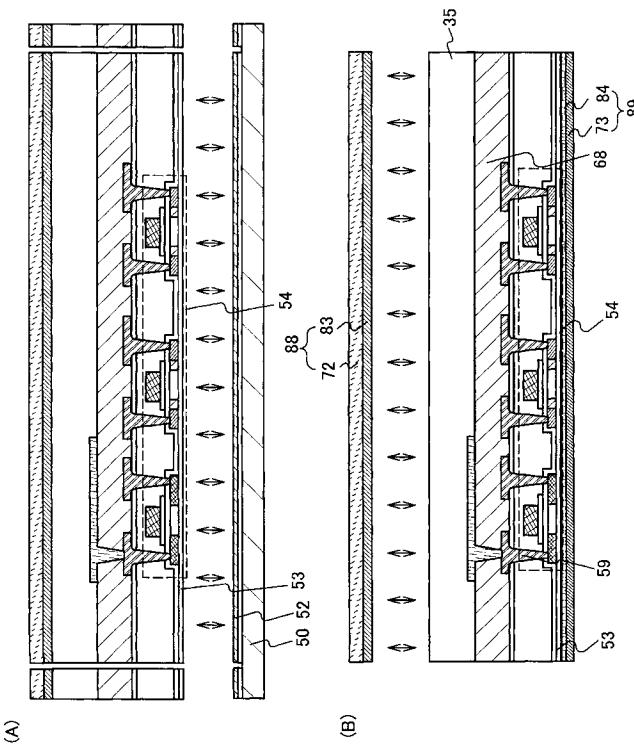

先ず、基板50の一方の面上に、絶縁層51を形成する(図17(A)参照)。次に、絶縁層51上に剥離層52を形成する。続いて、剥離層52上に絶縁層53を形成する。

## 【0119】

基板50は、絶縁表面を有する基板であり、例えば、ガラス基板、プラスチック基板、石英基板等である。好適には、基板50として、ガラス基板又はプラスチック基板を用いることが良い。ガラス基板とプラスチック基板は、1辺が1メートル以上のものを作製することが容易であり、また、四角形状等の所望の形状のものを作製することが容易である。そうすると、例えば、四角形状で、1辺が1メートル以上のガラス基板やプラスチック基板を用いると、生産性を大幅に向上させることができる。このような利点は、円形で、最大で直径が30センチ程度のシリコン基板を用いる場合と比較すると、大きな優位点である。

40

## 【0120】

絶縁層51、53は、気相成長法(CVD法)やスパッタリング法等により、珪素の酸化物、珪素の窒化物、窒素を含む珪素の酸化物、酸素を含む珪素の窒化物などで形成する。

50

絶縁層 5 1 は、基板 5 0 からの不純物元素が上層に侵入してしまうことを防止する役目を担う。但し、絶縁層 5 1 は、必要がなければ、形成しなくても良い。

【 0 1 2 1 】

剥離層 5 2 は、スパッタリング法等により、タンゲステン (W)、モリブデン (Mo)、チタン (Ti)、タンタル (Ta)、ニオブ (Nb)、ニッケル (Ni)、コバルト (Co)、ジルコニウム (Zr)、亜鉛 (Zn)、ルテニウム (Ru)、ロジウム (Rh)、パラジウム (Pd)、オスミウム (Os)、イリジウム (Ir)、珪素 (Si) 等から選択された元素または前記元素を主成分とする合金材料若しくは化合物材料を含む層を、単層又は積層して形成する。なお、珪素を含む層は、非晶質、微結晶、多結晶のいずれでも良い。

10

【 0 1 2 2 】

剥離層 5 2 が単層構造の場合、好ましくは、タンゲステン、モリブデン、タンゲステンとモリブデンの混合物、タンゲステンの酸化物、タンゲステンの酸化窒化物、タンゲステンの窒化酸化物、モリブデンの酸化物、モリブデンの酸化窒化物、モリブデンの窒化酸化物、タンゲステンとモリブデンの混合物の酸化物、タンゲステンとモリブデンの混合物の酸化窒化物、タンゲステンとモリブデンの混合物の窒化酸化物のいずれかを含む層を形成する。

【 0 1 2 3 】

剥離層 5 2 が積層構造の場合、好ましくは、1層目として、タンゲステン、モリブデン、タンゲステンとモリブデンの混合物のいずれかを含む層を形成し、2層目として、タンゲステンの酸化物、モリブデンの酸化物、タンゲステンとモリブデンの混合物の酸化物、タンゲステンの酸化窒化物、モリブデンの酸化窒化物、タンゲステンとモリブデンの混合物の酸化窒化物のいずれかを含む層を形成する。この場合、2層目は、1層目の表面を酸素プラズマ処理又は窒素酸素プラズマ処理することにより形成することができる。

20

【 0 1 2 4 】

剥離層 5 2 として、タンゲステンとタンゲステンの酸化物の積層構造を形成する場合、先ず、剥離層 5 2 としてタンゲステンを含む層を形成し、その上層の絶縁層 5 3 として、珪素の酸化物を含む層を形成することにより、タンゲステンを含む層と珪素の酸化物を含む層との間に、タンゲステンの酸化物を含む層が形成されることを活用しても良い。タンゲステンの窒化物、タンゲステンの酸化窒化物、タンゲステンの窒化酸化物を含む層等を形成する場合も同様であり、タンゲステンを含む層を形成後、その上層に珪素の窒化物を含む層、酸素を含む窒化珪素層、窒素を含む酸化珪素層を形成すると良い。

30

【 0 1 2 5 】

次に、絶縁層 5 3 上に複数の TFT 5 4 を形成する。複数の TFT 5 4 の各々は、島状の半導体層 9 0、ゲート絶縁層（単に絶縁層ともいう）5 5、第 1 の導電層 9 1、ゲート（ゲート電極ともいう）である第 2 の導電層 9 2 を有する。半導体層 9 0 は、ソース又はドレインとして機能する不純物領域 9 3、9 4、チャネル形成領域 9 5 を有する。不純物領域 9 3、9 4 には、N 型を付与する不純物元素（例えばリン (P)、砒素 (As)）、又は P 型を付与する不純物元素（例えばボロン (B)）が添加されている。不純物領域 9 4 は、LDD (Lightly Doped Drain) 領域である。

40

【 0 1 2 6 】

島状の半導体層 9 0 は、例えば第 1 の実施例における島状の半導体層 106a ~ 106c と同様の方法により形成される。このため、半導体層 9 0 はチャネル方向に結晶粒が長くなり、チャネル形成領域 9 5 に結晶粒界がほとんど含まれなくなり、電子や正孔などのキャリアに対するエネルギー障壁が低くなる。その結果、TFT 5 4 の移動度が、例えば数百  $\text{cm}^2 / \text{Vs}$  になる。また、半導体層 9 0 のばらつきが抑制されたため、TFT 5 4 の特性にばらつきが生じることを抑制できる。

【 0 1 2 7 】

複数の TFT 5 4 の各々は、半導体層 9 0 上にゲート絶縁層 5 5 が設けられ、ゲート絶縁層 5 5 上に第 1 の導電層 9 1 が設けられ、第 1 の導電層 9 1 上に第 2 の導電層 9 2 が設け

50

られたトップゲート型、第2の導電層92上にゲート絶縁層55が設けられ、ゲート絶縁層55上に半導体層90が設けられたボトムゲート型のどちらのタイプでも良い。また、複数のTFT54から選択された1つ又は複数のTFTは、ゲート電極が2つ以上、チャネル形成領域が2つ以上あるマルチゲート型のTFTでも良い。

【0128】

また、基板50上に複数のTFT54のみを形成しているが、本発明はこの構成に制約されない。基板50上に設ける素子は、半導体装置の用途によって適宜調整される。例えば、非接触でデータの送信と受信を行う機能を有する場合、基板50上に複数のTFTのみ、又は基板50上に複数のTFTとアンテナとして機能する導電層を形成すると良い。また、データを記憶する機能を有する場合、基板50上に複数のTFTと記憶素子（例えば、トランジスタ、メモリトランジスタ等）を形成すると良い。また、回路を制御する機能や信号を生成する機能等を有する場合（例えば、CPU、信号生成回路等）、基板50上にTFTを形成すると良い。また、上記以外にも、必要に応じて、抵抗素子や容量素子などの他の素子を形成すると良い。

【0129】

次に、複数のTFT54上に、絶縁層56、57を形成する。絶縁層56、57は、気相成長法、スパッタリング法、SOG（スピンドルオングラス）法、液滴吐出法（例えば、インクジェット法）等を用いて、珪素の酸化物、珪素の窒化物、ポリイミド、アクリル、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む絶縁膜（以下、シロキサン系絶縁膜と記載する）、オキサゾール樹脂等を用いて形成する。なお、オキサゾール樹脂は、例えば、感光性ポリベンゾオキサゾール等である。オキサゾール樹脂は、ポリイミド等の比誘電率（3.2～3.4程度）と比較すると、比誘電率が低いため（2.9程度）、寄生容量の発生を抑制し、高速動作を行うことができる。

【0130】

また上記の構成では、複数のTFT54上に2層の絶縁層（絶縁層56、57）を形成しているが、本発明はこの構成に制約されない。複数のTFT54上に設けられる絶縁層の数は制約されない。

【0131】

次に、ゲート絶縁層55及び絶縁層56、57に開口部を形成して、複数のTFT54の各々のソース（ソース領域、ソース電極ともいう）又はドレイン（ドレイン領域、ドレイン電極ともいう）に接続された導電層59～64を形成する（図17（A）参照）。導電層59～64は、同じ層に設けられている。また、導電層59～64はソース配線又はドレイン配線である。外部から供給される信号は、導電層59～64を介して、複数のTFT54に供給される。

【0132】

導電層59～64は、スパッタリング法等により、チタン、タンゲステン、クロム、アルミニウム、タンタル、ニッケル、ジルコニウム、ハフニウム、バナジウム、イリジウム、ニオブ、鉛、白金、モリブデン、コバルト又はロジウム等から選択された元素、又はこれらの元素を主成分とする合金材料、又はこれらの元素を主成分とする酸化物や窒化物などの化合物材料で、単層又は積層で形成する。導電層59～64の積層構造の例を挙げると、例えば、チタン、アルミニウム、チタンの3層構造、チタン、窒化チタン、アルミニウム、チタン、窒化チタンの5層構造、チタン、窒化チタン、シリコンが添加されたアルミニウム、チタン、窒化チタンの5層構造等がある。

【0133】

次に、導電層59上に、導電層66を形成する（図17（B）参照）。導電層66は、スクリーン印刷法、液滴吐出法等を用いて、金、銀又は銅を含む層を形成する。好ましくは、スクリーン印刷法を用いて、銀の微粒子を含むペースト（銀の微粒子と樹脂が混合した材料）で形成すると良い。スクリーン印刷法は、作製時間を短縮することができ、装置が安価であるからである。また、銀を使用するのは抵抗値が低いからである。

【0134】

10

20

30

40

50

次に、導電層 6 6 及び導電層 5 9 の一方もしくは双方を溶融させることのできるレーザ光を照射する。レーザ光を照射する前は、導電層 6 6 と導電層 5 9 とは部分的に接していたが、レーザ光の照射により、導電層 6 6 と導電層 5 9 の接する部分を増大させることができる。そのため、導電層 6 6 と導電層 5 9 の電気的な接続をより確実なものとして、信頼性を向上させることができる。ここで使用することができるレーザには、媒質により分類すると、気体レーザ、液体レーザ、固体レーザがあり、発振の特徴により分類すると、自由電子レーザ、半導体レーザ、X線レーザがあるが、本発明では、いずれのレーザを用いても良い。但し、好ましくは気体レーザ又は固体レーザを用いるとよく、さらに好ましくは固体レーザを用いると良い。また、連続発振型のレーザ、パルス発振型のレーザのどちらを用いても良い。

10

## 【0135】

次に、絶縁層 5 7 と導電層 5 9 ~ 6 4 上に、絶縁層 6 8 を選択的に形成する（図 17 (C)）。絶縁層 6 8 には、開口部 6 9 が設けられている。導電層 6 6 は、開口部 6 9 を介して露出している。

## 【0136】

なお、開口部 6 9 は、導電層 6 6 の全ての表面が露出されるような形状ではなく、導電層 6 6 の一部の表面が露出されるような形状とすると良い。具体的には、開口部 6 9 は、導電層 6 6 の中心部が露出されるような形状とすると良い。これは、後の工程において、正確に転置を行うためである。仮に、導電層 6 6 の一表面の全てが露出されるように開口部 6 9 を形成すると、導電層 6 6 と絶縁層 6 8 の両方が設けられていない領域が生じてしまう場合がある。後に行う転置の工程では、絶縁層 6 8 と基板 8 8 とを接着させて行うため、導電層 6 6 と絶縁層 6 8 のいずれも設けられていない領域があると、正確に転置を行うことができない場合がある。しかしながら、上記の工程では、絶縁層 6 8 は、導電層 6 6 の中心部が露出されるように、選択的に設けられている。そうすると、導電層 6 6 と絶縁層 6 8 のいずれも設けられていない領域がないため、正確に転置を行うことができる。

20

## 【0137】

絶縁層 6 8 は、エポキシ樹脂、アクリル樹脂及びポリイミド樹脂等の絶縁性の樹脂により、5 ~ 200  $\mu\text{m}$ 、好適には15 ~ 35  $\mu\text{m}$ の厚さで形成する。また、絶縁層 6 8 は、スクリーン印刷法、液滴吐出法等を用いて、均一に形成する。好ましくは、スクリーン印刷法を用いると良い。スクリーン印刷法は、作製時間を短縮することができ、装置が安価であるからである。次に、必要に応じて、加熱処理を行う。

30

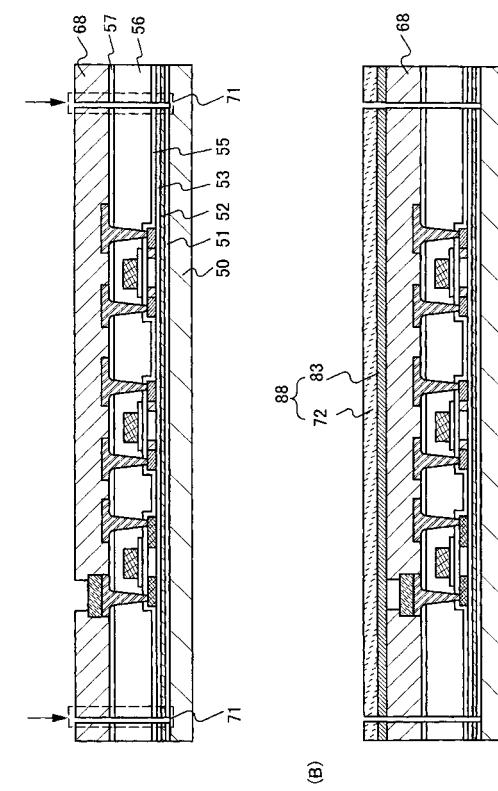

## 【0138】

次に、少なくとも、剥離層 5 2 の一部が露出するような開口部 7 1 を形成する（図 18 (A) 参照）。この工程は、処理時間が短い点から、レーザ光の照射により行うと良い。レーザ光は、基板 5 0 、絶縁層 5 1 、剥離層 5 2 、絶縁層 5 3 、ゲート絶縁層 5 5 、絶縁層 5 6 、5 7 、6 8 に対して照射される。また、レーザ光は、絶縁層 6 8 の表面から照射される。開口部 7 1 は、少なくとも、剥離層 5 2 の一部が露出するように形成される。そのため、少なくとも、ゲート絶縁層 5 5 、絶縁層 5 6 、5 7 、6 8 には、開口部 7 1 が設けられる。図示する構成では、レーザ光が、絶縁層 5 1 にまで達し、絶縁層 5 1 、5 3 、ゲート絶縁層 5 5 、絶縁層 5 6 、5 7 、6 8 が分断された場合を示す。なお、レーザ光は、基板 5 0 まで達しても良い。

40

## 【0139】

上記のレーザ光を照射する工程では、アブレーション加工が用いられる。アブレーション加工とは、レーザ光を照射した部分、つまり、レーザ光を吸収した部分の分子結合が切斷されて、光分解し、気化する現象を用いた加工である。つまり、レーザ光を照射して、絶縁層 5 1 、剥離層 5 2 、絶縁層 5 3 、ゲート絶縁層 5 5 、絶縁層 5 6 、5 7 、6 8 のある部分の分子結合を切斷し、光分解し、気化させることにより、開口部 7 1 を形成している。

## 【0140】

また、レーザは、紫外領域である 150 ~ 380 nm の波長の固体レーザを用いると良い

50

。好ましくは、150～380nmの波長のNd:YVO<sub>4</sub>レーザを用いると良い。その理由は、150～380nmの波長のNd:YVO<sub>4</sub>レーザは、他の高波長側のレーザに比べ、基板に光が吸収されやすく、アブレーション加工が可能であるからである。また、加工部の周辺に影響を与えることなく、加工性が良いからである。

#### 【0141】

次に、絶縁層68上に、基板88を設ける(図18(B)参照)。基板88は、絶縁層72と接着層83が積層された基板であり、熱剥離型の基板である。接着層83は、加熱処理により接着力が低下する層であり、例えば、熱可塑性接着剤の加熱時の軟化を用いる材料からなる層、加熱により膨張するマイクロカプセルや発泡剤を混入した材料からなる層、熱硬化性樹脂に熱溶融性や熱分解性を付与した材料からなる層、水の侵入による界面強度劣化やそれに伴う吸水性樹脂の膨張を用いた層である。

#### 【0142】

次に、基板88を用いて、基板50から、複数のTFT54を含む積層体を分離する(図19(A)参照)。基板50から、複数のTFT54を含む積層体の分離は、剥離層52の内部又は剥離層52と絶縁層53を境界として行われる。図示する構成では、分離は、剥離層52と絶縁層53の間を境界として行われた場合を示す。このように、基板88を用いることにより、分離の工程を容易にかつ短時間で行うことができる。なお基板50から上記した積層体を分離する方法は、(A)応力を加えることにより物理的に分離する方法、(B)剥離層52をエッティング材により除去する方法、(C)剥離層52をエッティング材により部分的に除去し、その後物理的に剥離する方法のいずれを用いても良い。

#### 【0143】

次に、加熱処理を行って、絶縁層53の表面に基板89を設けると共に、基板88から複数のTFT54を含む積層体を分離する(図19(B)参照)。基板89は、絶縁層73と接着層84が積層された基板である。接着層84は、加熱処理により接着力が増す層であり、熱可塑性の樹脂を含む層に相当する。熱可塑性の樹脂とは、例えば、ポリエチレン、ポリスチレン、ポリプロピレン、ポリ塩化ビニル等に相当する。

#### 【0144】

上述したように、基板88の表面に位置する接着層83は加熱処理により接着力が低下するため、加熱処理により、基板88と絶縁層68の間の接着力が低下し、基板88から複数のTFT54を含む積層体が分離される。同時に、加熱処理により、基板89の表面に位置する接着層84(熱可塑性の樹脂)が硬化し、絶縁層53と基板89の一表面との接着力が増す。このように、性質が異なる接着層が設けられた2枚の基板88、89を用いることにより、基板88から積層体を分離する工程と、積層体を基板89上に設ける工程とを同時に行うことができる。従って、作製時間を短縮することができる。

#### 【0145】

次に必要に応じて、再度、導電層66にレーザ光を照射する。これは、上記の分離の工程の影響により、導電層59と導電層66との電気的な接続に不良が生じる可能性があり、そのような不良を改善するためである。従って、必要がなければ、レーザ光を照射する工程を行わなくても良い。

#### 【0146】

次に、導電層66に接するように、端子12を形成する(図20(A)参照)。端子12は、スクリーン印刷法、液滴吐出法等を用いて、金、銀又は銅を含む層で形成する。好ましくは、スクリーン印刷法を用いて、銀の微粒子を含むペースト(銀の微粒子と樹脂が混合した材料)で形成する。スクリーン印刷法は、作製時間を短縮することができ、装置が安価であるからであり、銀は抵抗値が低いからである。次に、必要に応じて加熱処理を行う。

#### 【0147】

次に、基板89、絶縁層53、ゲート絶縁層55、絶縁層56、57、68に、レーザ光を照射して、開口部76を形成する(図20(B)参照)。なお、開口部76を形成する工程を省略しても良い。

10

20

30

40

50

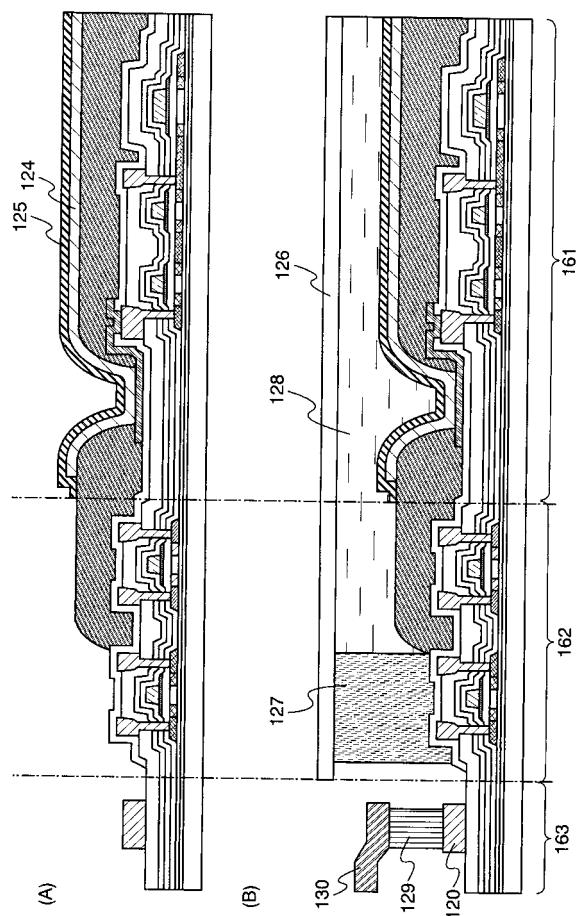

## 【0148】

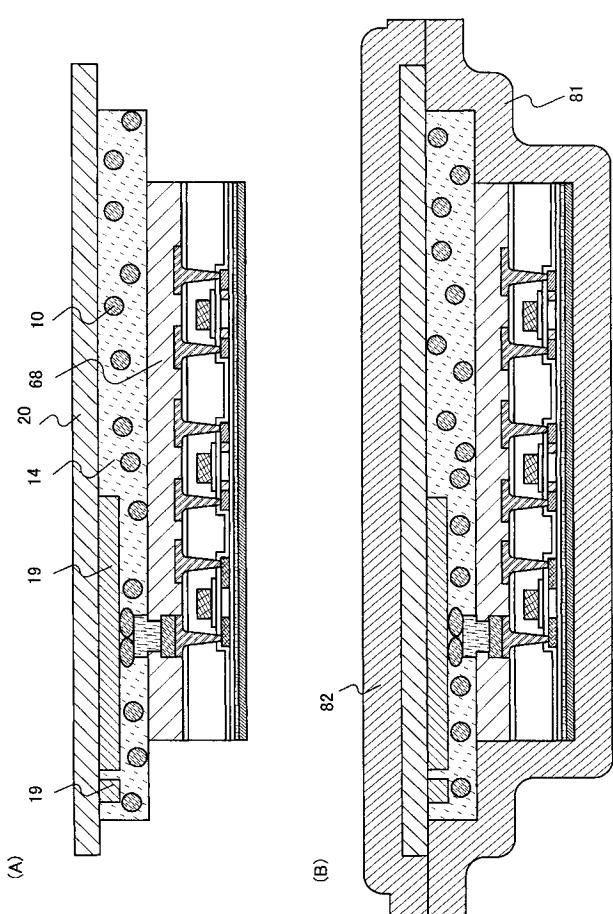

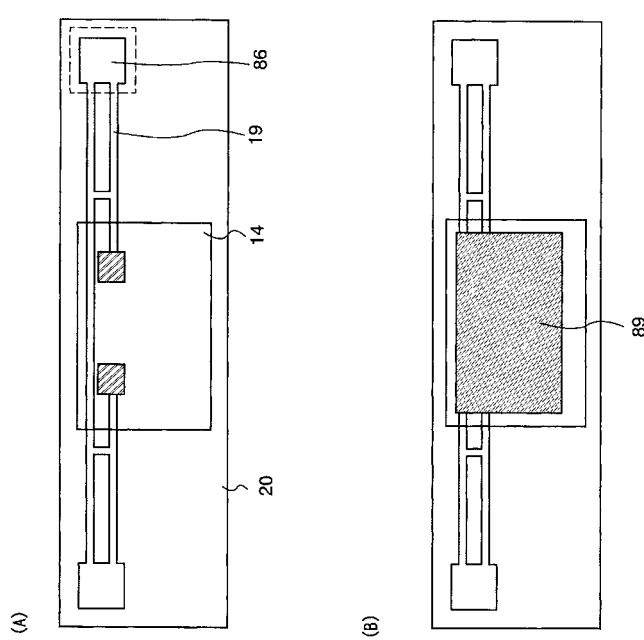

次に、アンテナとして機能する導電層19が設けられた基板20を準備する(図21(A))。なお、アンテナとして機能する導電層は、容量素子86を有している(図22(A)、(B)参照)。アンテナとして機能する導電層19、容量素子86の各々は、スクリーン印刷法、液滴吐出法等を用いて形成される。図21(A)には、アンテナとして機能する導電層19を図示する。樹脂層14は、接着剤中に導電性粒子10が設けられた材料であり、ACP(Anisotropic Conductive Paste)とも呼ばれる。樹脂層14は、スクリーン印刷法、液滴吐出法等を用いて、均一に形成する。

## 【0149】

次に、樹脂層14を用いて、基板89と基板20とを貼り合わせる(図21(A)、図22(B)参照)。次に、必要があれば、絶縁層68と樹脂層14とを接着する。この際、フリップチップボンダー、ダイボンダー、ACF(Anisotropic Conductive Film)貼り付け機、圧着機等により、加圧処理と加熱処理の一方又は両方を行う。

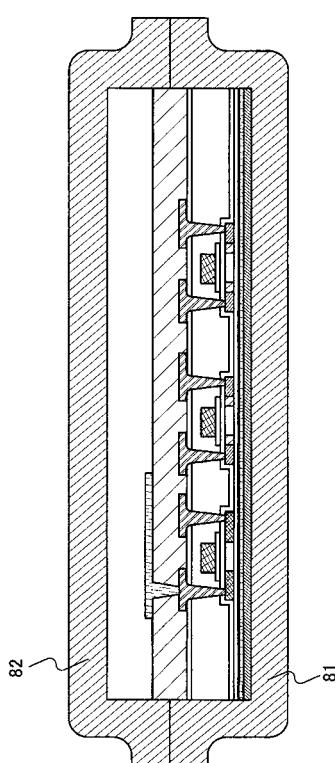

## 【0150】

なお、複数のTFT54を含む積層体の表面に、さらに基板を設けても良い(図21(B)参照)。具体的には、基板89と基板20の一方又は両方の表面に、新たに基板を設けても良い。図示する構成では、基板89の表面に基板81を設け、基板20の表面に基板82を設けている。基板81、82を設けることにより、さらに強度を向上させることができる。基板81、82による複数のTFT54を含む積層体の封止は、基板81、82の各々の表面の層、又は基板81、82の各々の表面の接着層を加熱処理によって溶かすことにより行われる。また必要に応じて加圧処理も行われる。

## 【0151】

なお、基板50から複数のTFT54を含む積層体を分離する方法を示したが(図19(A)参照)、本発明はこの形態に制約されない。例えば以下に示すように、導電層59～64を形成した後(図17(A)参照。)に、基板50を薄型化しても良い。

## 【0152】

基板50を薄型化するためには、基板50の複数のTFT54が形成されていない面を、研削装置(例えば研削盤)を用いて研削する。好適には、基板50の厚さが100μm以下になるまで研削する。次に、研削した基板50の複数のTFT54が形成されていない面を、研磨装置(例えば、研磨パッド、研磨砥粒(例えば酸化セリウム等))を用いて研磨する。好適には、基板50の厚さが50μm以下、好ましくは20μm以下、より好ましくは5μm以下になるまで研磨する。なお、基板50を薄型化するためには、基板50の研削と研磨の一方又は両方を行うと良い。また、研削工程と研磨工程を行う前に、必要に応じて、導電層59～64上に保護を目的とした層を設けると良い。また、研削工程と研磨工程の後は、必要に応じて、ゴミを除去するための洗浄工程、乾燥工程の一方又は両方を行うと良い。

## 【0153】

薄型化した基板50の厚さは、研削工程と研磨工程に必要な時間、後に行う切断工程に必要な時間、半導体装置の用途、半導体装置の用途に必要な強度などを考慮して、適宜決めるといい。例えば、研削工程と研磨工程の時間を短縮して生産性を向上させる場合は、研磨後の基板50の厚さは50μm程度にすると良い。また、後に行う切断工程に必要な時間を短縮して生産性を向上させる場合、研磨後の基板50の厚さは、20μm以下、より好適には5μm以下とするといい。また、半導体装置を薄い物品に貼り付けたり、埋め込んだりする場合、研磨後の基板50の厚さは20μm以下、より好適には5μm以下とするといい。また、薄型化した基板50の厚さの下限は特に制約されない。基板50が除去されるまで(基板50の厚さが0μmになるまで)、薄型化しても良い。

## 【0154】

次に、導電層59に接するように、導電層66を形成する(図17(B)参照)。次に、導電層66にレーザ光を照射する(図17(B)参照)。次に、絶縁層68を選択的に形

成する（図17（C）参照）。次に、レーザ光を照射して、開口部71を形成する（図18（A）参照）。図示する構成では、開口部71の形成の際に、基板50を切断していないが、基板50を薄型化した場合は、基板50も切断すると良い。そして、基板50から、複数のTFT54を含む積層体を分離する工程を省略すると良い。その後の工程は、上述の工程と同様である。基板50から複数のTFT54を含む積層体を分離せずに、薄型化した基板50を残存させておくと、有害な気体の侵入、水の侵入、不純物元素の侵入を抑制することができる。従って、劣化や破壊を抑制し、信頼性を向上させることができる。また、バリア性を向上させることができる。

#### 【実施例5】

##### 【0155】

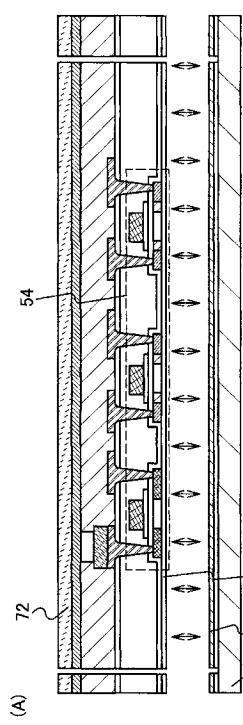

実施例5に係る半導体装置の作製方法について、図23～図26を参照して説明する。本実施例において、TFTを形成し、絶縁層57を形成する工程までは実施例4と同様な工程であるため、説明を省略している。また、以下の説明において、実施例4と同様の構成については同一の符号を付して説明を省略する。

##### 【0156】

絶縁層57を形成した後、ゲート絶縁層55、絶縁層56～57に開口部を形成して、複数のTFT54の各々のソース（ソース領域、ソース電極ともいう）又はドレイン（ドレイン領域、ドレイン電極ともいう）に接続された導電層59～64とを形成する（図23（A）参照）。導電層59～64は、同じ層に設けられている。また、導電層59～64はソース配線又はドレイン配線である。外部から供給される信号は、導電層59～64を介して、複数のTFT54に供給される。

##### 【0157】

次に、図23（B）に示すように、導電層59～64を覆うように、単層又は積層で絶縁層32を形成する。続いて、導電層59～64を覆う絶縁層32に、導電層59上に位置するコンタクトホールを形成し、さらに導電層33を形成する。導電層33はコンタクトホールを介して導電層59に接続し、かつアンテナとして機能する。なお、導電層33はスクリーン印刷法、液滴吐出法等を用いて形成する。

##### 【0158】

次に、導電層59、導電層33の一方もしくは双方を溶融させることのできるレーザ光を照射する。レーザ光を照射する前は、導電層59と導電層33とは部分的に接していたが、レーザ光の照射により、導電層59と導電層33の接する部分を増大させることができる。そのため、導電層59と導電層33の電気的な接続をより確実なものとして、信頼性を向上させることができる。ここで使用することができるレーザは、媒質により分類すると、気体レーザ、液体レーザ、固体レーザがあり、発振の特徴により分類すると、自由電子レーザ、半導体レーザ、X線レーザがあるが、本発明では、いずれのレーザを用いても良い。但し、好ましくは気体レーザ又は固体レーザを用いるとよく、さらに好ましくは固体レーザを用いると良い。また本発明には、連続発振型のレーザ、パルス発振型のレーザのどちらを用いても良い。

##### 【0159】

この後、絶縁層32、アンテナとして機能する導電層33上に、 DLC（ダイヤモンドライカーボン）等の炭素を含む層、窒化珪素を含む層、窒化酸化珪素を含む層等の保護層を形成しても良い。

##### 【0160】

次に、図23（C）に示すように絶縁層32、アンテナとして機能する導電層33上に、絶縁層35をスクリーン印刷法等で形成する。絶縁層35は、後の剥離工程での保護層として設けるため、平坦化層であることが好ましい。

##### 【0161】

次に、少なくとも、剥離層52の一部が露出するような開口部71を形成する（図24（A）参照）。この工程は、処理時間が短い点から、レーザ光の照射により行うと良い。レーザ光は、基板50、絶縁層51、剥離層52、絶縁層53、ゲート絶縁層55、絶縁層

10

20

30

40

50

56、57、32、35に対して照射される。また、レーザ光は、絶縁層35の表面から照射される。開口部71は、少なくとも、剥離層52の一部が露出するよう形成される。そのため、少なくとも、絶縁層53、ゲート絶縁層55、絶縁層56、57、32、35には、開口部71が設けられる。図示する構成では、レーザ光が、絶縁層51にまで達し、絶縁層51、53、ゲート絶縁層55、絶縁層56、57、32、35が分断された場合を示す。なお、レーザ光は、基板50まで達しても良い。

#### 【0162】

また、レーザは、紫外領域である150～380nmの波長の固体レーザを用いると良い。好ましくは、150～380nmの波長のNd:YVO<sub>4</sub>レーザを用いると良い。その理由は、150～380nmの波長のNd:YVO<sub>4</sub>レーザは、他の高波長側のレーザに比べ、基板に光が吸収されやすく、アブレーション加工が可能であるからである。また、加工部の周辺に影響を与えることなく、加工性が良いからである。

#### 【0163】

次に、絶縁層35上に、基板88を設ける(図24(B)参照)。基板88は、絶縁層72と接着層83が積層された基板である。

#### 【0164】

次に、基板88を用いて、基板50から、複数のTFT54を含む積層体を分離する(図25(A)参照)。基板50から、複数のTFT54を含む積層体の分離は、剥離層52の内部又は剥離層52と絶縁層53を境界として行われる。図示する構成では、分離は剥離層52と絶縁層53の間を境界として行われた場合を示す。このように、基板88を用いることにより、分離の工程を容易にかつ短時間で行うことができる。

#### 【0165】

次に、加熱処理を行って、絶縁層53の表面に基板89を設けると共に、基板88から複数のTFT54を含む積層体を分離する(図25(B)参照)。基板89は、絶縁層73と接着層84が積層された基板である。

#### 【0166】

上述したように、基板88の表面に位置する接着層83は加熱処理により接着力が低下するため、加熱処理により、基板88と絶縁層35の間の接着力が低下し、基板88から複数のTFT54を含む積層体が分離される。同時に、加熱処理により、基板89の表面に位置する接着層84(熱可塑性の樹脂)が硬化し、絶縁層53と基板89の一表面との接着力が増す。このように、性質が異なる接着層が設けられた2枚の基板88、89を用いることにより、基板88から積層体を分離する工程と、積層体を基板89上に設ける工程とを同時に行うことができる。従って、作製時間を短縮することができる。

#### 【0167】

なお、複数のTFT54を含む積層体の表面に、さらに基板を設けても良い(図26参照)。具体的には、絶縁層35と基板89の一方又は両方の表面に、新たに、基板を設けても良い。図示する構成では、基板89の表面に基板81を設け、絶縁層35の表面に基板82を設けている。基板81、82を設けることにより、さらに強度を向上させることができる。基板81、82による複数のTFT54を含む積層体の封止は、基板81、82の各々の表面の層、又は基板81、82の各々の表面の接着層を加熱処理によって溶かすことにより行われる。また必要に応じて、加圧処理も行われる。

#### 【0168】

なお、基板50から複数のTFT54を含む積層体を分離する方法を示したが、本発明はこの形態に制約されず、基板50を薄型化しても良い。工程については、実施例4と同様な工程を用いて行われるため、ここでは説明を省略する。

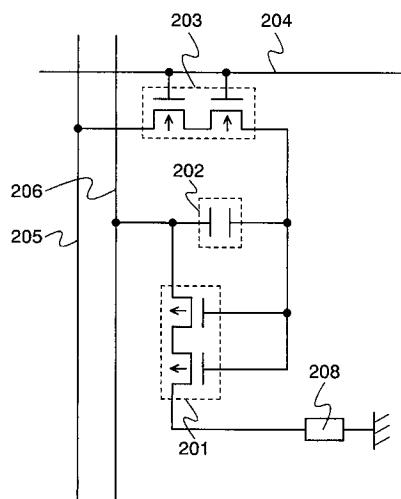

#### 【実施例6】

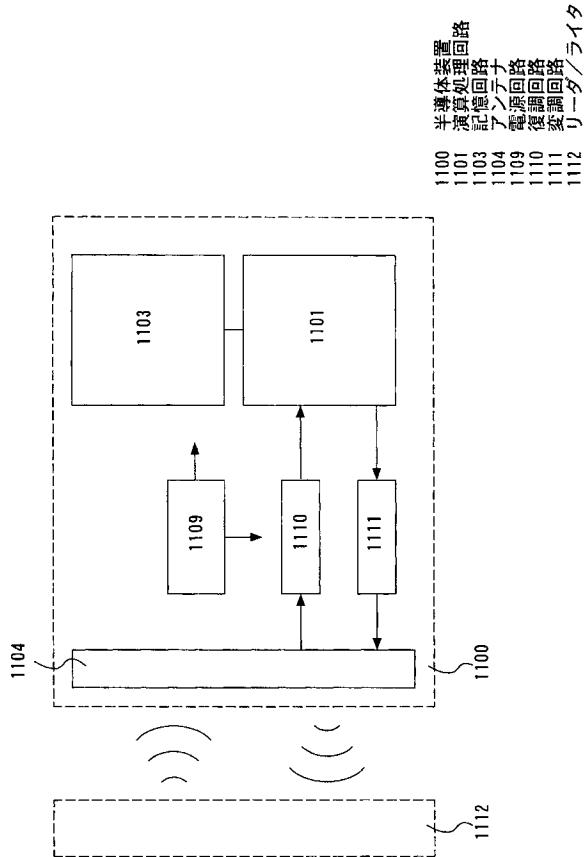

#### 【0169】

実施例6に係る半導体装置の構成について、図27を参照して説明する。本発明の半導体装置1100は、演算処理回路1101、記憶回路1103、アンテナ1104、電源回路1109、復調回路1110、変調回路1111を有する。半導体装置1100は、ア

10

20

30

40

50

ンテナ 1104 と電源回路 1109 を必須の構成要素としており、他の要素は、半導体装置 1100 の用途に従って、適宜設けられる。アンテナ 1104 としては、例えば実施例 4 又は実施例 5 に示された構成を利用することができる。

#### 【0170】

演算処理回路 1101 は、復調回路 1110 から入力される信号に基づき、命令の解析、記憶回路 1103 の制御、外部に送信するデータの変調回路 1111 への出力などを行う。

#### 【0171】

記憶回路 1103 は、記憶素子を含む回路と、データの書き込みやデータの読み出しを制御する制御回路を有する。記憶回路 1103 には、少なくとも、半導体装置自体の識別番号が記憶されている。識別番号は、他の半導体装置と区別するために用いられる。また、記憶回路 1103 は、有機メモリ、DRAM (Dynamic Random Access Memory)、SRAM (Static Random Access Memory)、FeRAM (Ferroelectric Random Access Memory)、マスクROM (Read Only Memory)、PROM (Programmable Read Only Memory)、EPROM (Electrically Programmable Read Only Memory)、EEPROM (Electrically Erasable Programmable Read Only Memory) 及びフラッシュメモリから選択された一種又は複数種を有する。有機メモリは、一対の導電層間に有機化合物を含む層が挟まれた構造を有する。有機メモリは、構造が単純であるため、作製工程を簡略化することができ、費用を削減することができる。また、構造が単純であるために、積層体の面積を小型化することが容易であり、大容量化を容易に実現することができる。また、不揮発性であり、電池を内蔵する必要がないという長所がある。従って、記憶回路 1103 として、有機メモリを用いることが好ましい。

#### 【0172】

アンテナ 1104 は、リーダ / ライタ 1112 から供給された搬送波を、交流の電気信号に変換する。また、変調回路 1111 により、負荷変調が加えられる。電源回路 1109 は、アンテナ 1104 が変換した交流の電気信号を用いて電源電圧を生成し、各回路に電源電圧を供給する。

#### 【0173】

復調回路 1110 は、アンテナ 1104 が変換した交流の電気信号を復調し、復調した信号を、演算処理回路 1101 に供給する。変調回路 1111 は、演算処理回路 1101 から供給される信号に基づき、アンテナ 1104 に負荷変調を加える。

#### 【0174】

リーダ / ライタ 1112 は、アンテナ 1104 に加えられた負荷変調を、搬送波として受信する。また、リーダ / ライタ 1112 は、搬送波を半導体装置 1100 に送信する。なお、搬送波とは、リーダ / ライタ 1112 が発する電磁波である。

#### 【0175】

なお、本実施例の構成は他の実施例の構成と組み合わせて用いることが可能である。

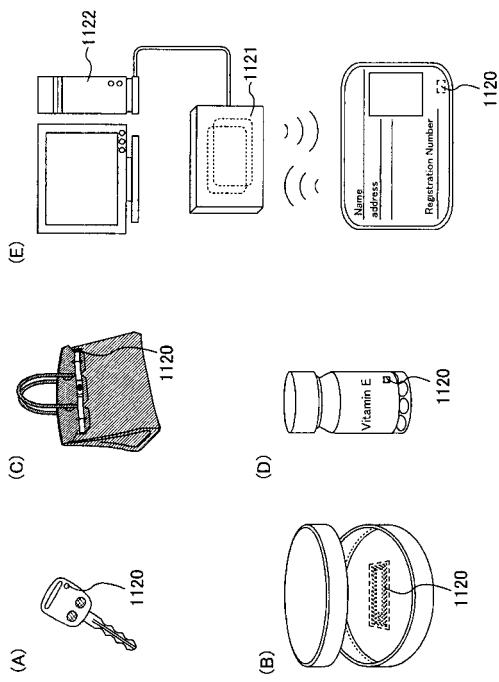

#### 【実施例 7】

#### 【0176】

実施例 7 に係る半導体装置は、実施例 6 と同様の構成を有しており、非接触でデータの送信と受信ができるという機能を有している。この機能を活用することにより、様々な物品、様々なシステムに組み込むことができる。物品とは、例えば、鍵 (図 28 (A) 参照)、紙幣、硬貨、有価証券類、無記名債券類、証書類 (運転免許証や住民票等)、書籍類、容器類 (シャーレ等、図 28 (B) 参照)、装身具 (鞄や眼鏡等、図 28 (C) 参照)、包装用容器類 (包装紙やボトル等、図 28 (D) 参照)、記録媒体 (ディスクやビデオテープ等)、乗物類 (自転車等)、食品類、衣類、生活用品類、電子機器 (液晶表示装置、EL 表示装置、テレビジョン装置、携帯端末等) 等である。本発明の半導体装置 1120

10

20

30

40

50

は、上記のような様々な形状の物品の表面に貼り付けたり、埋め込んだりして、固定される。

【0177】

また、システムとは、物流・在庫管理システム、認証システム、流通システム、生産履歴システム、書籍管理システム等であり、実施例6と同様の構成の半導体装置1120を用いることにより、システムの高機能化、多機能化、高付加価値化を図ることができる。例えば、半導体装置1120を身分証明証の内部に設けておき、かつ、建物の入り口などに、リーダ／ライタ1121を設けておく(図28(E)参照)。リーダ／ライタ1121は、各人が所有する身分証明証内の認証番号を読み取り、その読み取った認証番号に関する情報を、コンピュータ1122に供給する。コンピュータ1122では、リーダ／ライタ1121から供給された情報に基づき、入室又は退室を許可するか否かを判断する。このように、本発明の半導体装置を用いることにより、利便性を向上させた入退室管理システムを提供することができる。

【実施例8】

【0178】

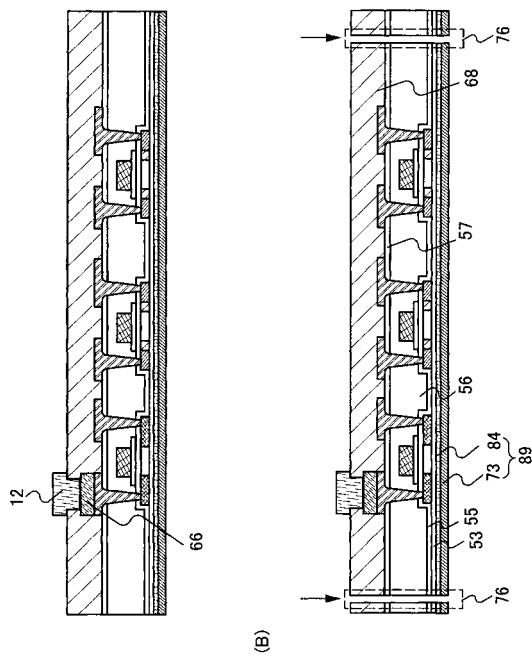

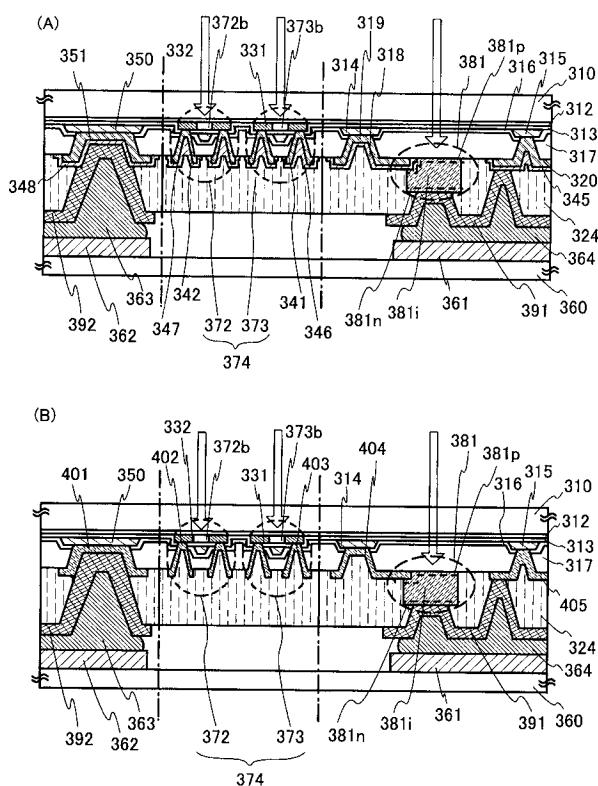

実施例8に係る半導体装置を、図29(A)～図29(B)、図30(A)～図30(D)、図31(A)～図31(C)及び図32(A)～図32(C)を用いて説明する。本実施例に係る半導体装置は光電変換素子を有しており、光センサ(例えば可視光センサ)として用いられる。

【0179】

図29(A)において、310は基板、312は下地絶縁膜、313はゲート絶縁膜である。光電変換素子が受光する光は基板310、下地絶縁膜312、およびゲート絶縁膜313を通過するため、これらの材料は全て透光性の高い材料を用いることが望ましい。

【0180】

光電変換素子は、配線319と、保護電極318と、光電変換層381、及び端子電極391を有する。光電変換層381は、p型半導体層381p、n型半導体層381n、及びp型半導体層381pとn型半導体層381nの間に挟まれた真性(i型)半導体層381iを有する。

【0181】

p型半導体層381pは、13属の不純物元素、例えばホウ素(B)を含んだセミアモルファスシリコン膜をプラズマCVD法にて成膜して形成すれば良い。

【0182】

なおセミアモルファス半導体膜とは、非晶質半導体と結晶構造を有する半導体(単結晶、多結晶を含む)の中間的な構造の半導体を含む膜である。このセミアモルファス半導体膜は、自由エネルギー的に安定な第3の状態を有する半導体膜であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を0.5～20nmとして非単結晶半導体膜中に分散させて存在させることが可能である。セミアモルファス半導体膜は、そのラマンスペクトルが520cm<sup>-1</sup>よりも低波数側にシフトしており、またX線回折ではSi結晶格子に由来するとされる(111)、(220)の回折ピークが観測される。また、未結合手(ダングリングボンド)を終端化するため水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。本明細書では便宜上、このような半導体膜をセミアモルファス半導体(SAS)膜と呼ぶ。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なセミアモルファス半導体膜が得られる。なお微結晶半導体膜(マイクロクリスタル半導体膜)もセミアモルファス半導体膜に含まれる。

【0183】

またセミアモルファス半導体膜は珪化物を含む気体をグロー放電分解することにより得ることができる。代表的な珪化物を含む気体としては、SiH<sub>4</sub>であり、その他にもSi<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>などを用いることができる。また水素や、水素にヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または

10

20

30

40

50

複数種の希ガス元素を加えたガスで、この珪化物を含む気体を希釈して用いることで、S A S 膜の形成を容易なものとすることができます。希釈率は2倍～1000倍の範囲で珪化物を含む気体を希釈することができます。またさらに、珪化物を含む気体中に、C H<sub>4</sub>、C<sub>2</sub> H<sub>6</sub>などの炭化物気体、Ge H<sub>4</sub>、Ge F<sub>4</sub>などのゲルマニウム化気体、F<sub>2</sub>などを混入させて、エネルギー bandwidth 幅を1.5～2.4 eV、若しくは0.9～1.1 eVに調節しても良い。

#### 【0184】

p型半導体層381pを形成したら、さらに導電型を付与する不純物を含まない半導体層(真性半導体層又はi型半導体層と呼ぶ)381i及びn型半導体層381nを順に形成する。これによりp型半導体層381p、i型半導体層381i及びn型半導体層381nを有する光電変換層381が形成される。

#### 【0185】

なお本明細書においては、i型半導体層とは、半導体層に含まれるp型もしくはn型を付与する不純物が $1 \times 10^{20} \text{ cm}^{-3}$ 以下の濃度であり、酸素及び窒素が $5 \times 10^{19} \text{ cm}^{-3}$ 以下の濃度であり、暗伝導度に対して光伝導度が1000倍以上である半導体層を指す。またi型半導体層には、ホウ素(B)が10～1000 ppm添加されていても良い。

#### 【0186】

i型半導体層381iとしては、例えばプラズマCVD法でセミアモルファスシリコン膜を形成すれば良い。またn型半導体層381nとしては、15属の不純物元素、例えばリン(P)を含むセミアモルファスシリコン膜を形成しても良いし、セミアモルファスシリコン膜を形成後、15属の不純物元素を導入しても良い。

#### 【0187】

またp型半導体層381p、真性半導体層381i、n型半導体層381nとして、セミアモルファス半導体膜だけではなく、アモルファス半導体膜を用いても良い。

#### 【0188】

また、TFT372、373のチャネル形成領域372b、373b並びにソース及びドレインとなる不純物領域は、島状半導体層332、331に形成されている。島状半導体層332、331は、例えば第1の実施例における島状の半導体層106a～106cと同様の方法により形成される。このため、島状半導体層332、331はチャネル方向に結晶粒が長くなり、チャネル形成領域372b、373bに結晶粒界がほとんど含まれなくなり、電子や正孔などのキャリアに対するエネルギー障壁が低くなる。その結果、TFT372、373の移動度が、例えば数百 cm<sup>2</sup> / V sになる。また、島状半導体層332、331のばらつきが抑制されるため、TFT372、373の特性にばらつきが生じることを抑制できる。

#### 【0189】

また、配線319、接続電極320、端子電極351、TFT373のソース電極又はドレイン電極341、並びにTFT372のソース電極又はドレイン電極342は、高融点金属膜と低抵抗金属膜(アルミニウム合金または純アルミニウムなど)との積層構造となっている。ここでは、配線319は、チタン膜(Ti膜)とアルミニウム膜(Al膜)とTi膜とを順に積み重ねた三層構造とする。

#### 【0190】

さらに配線319、接続電極320、端子電極351、TFT373のソース電極又はドレイン電極341、並びにTFT372のソース電極又はドレイン電極342を覆うように、それぞれ保護電極318、345、348、346及び347が形成されている。

#### 【0191】

光電変換層381をエッティングする際に、配線319は保護電極318によって保護される。保護電極318の材料は、光電変換層381をエッティングするガス(またはエッチャント)に対して光電変換層よりもエッティング速度の小さい導電材料であることが好ましい。加えて、保護電極318の材料は、光電変換層381と反応して合金とならない導電材

10

20

30

40

50

料であることが好ましい。なおその他の保護電極 345、348、346 及び 347 も保護電極 318 と同様の材料及び作製工程により形成される。

【0192】

また、配線 319、接続電極 320、端子電極 351 上に保護電極 318、345、348、346 及び 347 を設けない構造にしても良い。このような構造の光センサを図 29 (B) に示す。図 29 (B) において、配線 404、接続電極 405、端子電極 401、TFT 372 のソース電極又はドレイン電極 402、及び TFT 373 のソース電極又はドレイン電極 403 は単層の導電膜により形成されており、このような導電膜として、チタン膜 (Ti 膜) が好ましい。またチタン膜に変えて、タンゲステン (W)、タンタル (Ta)、モリブデン (Mo)、ネオジウム (Nd)、コバルト (Co)、ジルコニウム (Zr)、亜鉛 (Zn)、ルテニウム (Ru)、ロジウム (Rh)、パラジウム (Pd)、オスミウム (Os)、イリジウム (Ir)、白金 (Pt) から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物、例えば、窒化チタン、窒化タンゲステン、窒化タンタル、窒化モリブデンからなる単層膜を用いることができる。配線 404、接続電極 405、端子電極 401、TFT 372 のソース電極又はドレイン電極 402、及び TFT 373 のソース電極又はドレイン電極 403 を単層膜とすることにより、作製工程において成膜回数を減少させることが可能となる。

【0193】

また図 29 (A) 及び図 29 (B) においては、n チャネル型 TFT 372 及び 373 は 1 つのチャネル形成領域を含む構造 (本明細書では「シングルゲート構造」という) のトップゲート型 TFT の例を示しているが、チャネル形成領域が複数ある構造にしてオン電流値のバラツキを低減させても良い。また、オフ電流値を低減するため、n チャネル型 TFT 372 及び 373 に低濃度ドレイン (Lightly Doped Drain (LDD)) 領域を設けても良い。LDD 領域とは、チャネル形成領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との間に低濃度に不純物元素を添加した領域のことであり、LDD 領域を設けると、ドレイン領域近傍の電界を緩和してホットキャリア注入による劣化を防ぐという効果がある。また、ホットキャリアによるオン電流値の劣化を防ぐため、n チャネル型 TFT 372 及び 373 を、ゲート絶縁膜を介して LDD 領域をゲート電極と重ねて配置させた構造 (本明細書では「GOLD (Gate-drawn Overlapped LDD) 構造」と呼ぶ) としても良い。

【0194】

GOLD 構造を用いた場合、LDD 領域をゲート電極と重ねて形成しなかった場合よりも、さらにドレイン領域近傍の電界を緩和してホットキャリア注入による劣化を防ぐ効果がある。このような GOLD 構造とすることで、ドレイン領域近傍の電界強度が緩和されてホットキャリア注入を防ぐことができ、劣化現象の防止に有効である。

【0195】

またカレントミラー回路 374 を構成する TFT 372 及び 373 は、トップゲート型 TFT だけでなく、ボトムゲート型 TFT、例えば逆スタガ型 TFT でも良い。この場合、受光する光を妨げないよう、ゲート電極が光透過性を持つことが望ましい。

【0196】

また、配線 314 は配線 319 (図 29 (B) においては配線 404) に接続する配線であり、増幅回路の TFT 373 のチャネル形成領域 373b 上方にも延在してゲート電極にもなっている。

【0197】

また、配線 315 は n 型半導体層 381n に接続する配線であり、TFT 372 のドレイン配線 (ドレイン電極とも呼ぶ) またはソース配線 (ソース電極とも呼ぶ) と接続している。また、316 及び 317 は絶縁膜、320 は接続電極である。受光する光は絶縁膜 316 及び 317 を通過するため、これらの材料は全て透光性の高い材料を用いることが望ましい。なお、絶縁膜 317 は、CVD 法により形成される酸化珪素膜 (SiO<sub>x</sub>) 膜を

10

20

30

40

50

用いることが好ましい。絶縁膜317をCVD法で形成する酸化珪素膜とすると固着強度が向上する。

【0198】

また、端子電極350は、配線314及び315と同一工程で形成され、端子電極351は配線319及び接続電極320と同一工程で形成されている。

【0199】

また、端子電極391はn型半導体層381nに接続されており、半田364で基板360の電極361に実装されている。また、端子電極392は端子電極391と同一工程で形成され、半田363で基板360の電極362に実装されている(図29(A)参照)。

10

【0200】

図29(A)及び図29(B)において、光は図中の矢印に示すとおり、基板310側から光電変換層381及びTFT372及び373の島状半導体層332、331に入射する。これにより光電流が発生し、光を検知することが可能となる。

【0201】

ただし図示はしていないが、光は矢印の方向からではなく、反対側すなわち基板360側からも入射する。入射した光は封止層324を通り、遮光する電極や配線を回り込んで光電変換層381及びTFT372及び373の島状半導体層332、331に入り込むので、これにより光電流を発生させることも可能である。

【0202】

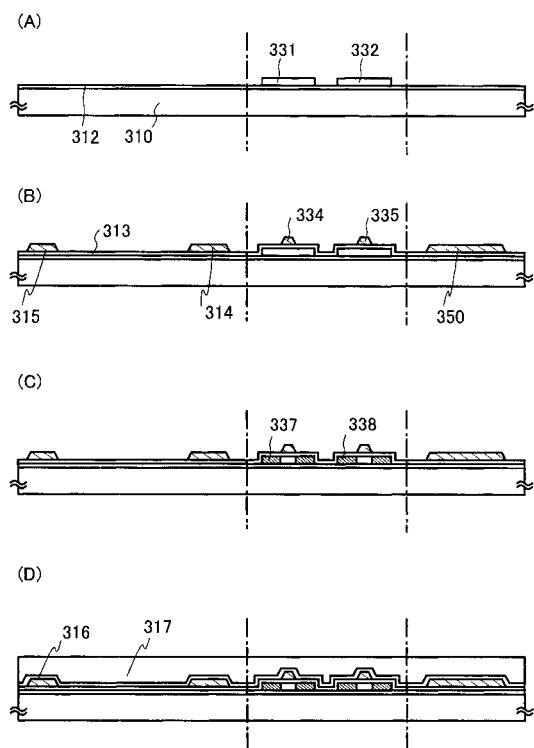

続いて、図29に示した半導体装置の作製方法について説明する。まず、以下のようにして、基板(第1の基板310)上に半導体素子を形成する。ここでは基板310として、ガラス基板の一つであるAN100(商品名)を用いる。

20

【0203】

まず、プラズマCVD法で下地絶縁膜312となる窒素を含む酸化珪素膜(膜厚100nm)を形成し、さらに大気にふれることなく、半導体膜例えば水素を含む非晶質珪素膜(膜厚66nm)を積層形成する。また、下地絶縁膜312は酸化珪素膜、窒化珪素膜、窒素を含む酸化珪素膜を用いた積層構造にしても良い。例えば、下地絶縁膜312として、酸素を含む窒化珪素膜を50nm、さらに窒素を含む酸化珪素膜を100nm積層した膜を形成しても良い。なお、窒素を含む酸化珪素膜や窒化珪素膜は、ガラス基板からのアルカリ金属などの不純物拡散を防止するブロッキング層として機能する。

30

【0204】

次いで、上記非晶質珪素膜をレーザ装置を用いて結晶化させて、結晶構造を有する半導体膜、例えば多結晶珪素膜を形成する。この工程には第1又は第2の実施の形態と同様な方法を用いることができるため、ここでは詳細な説明は省略する。

【0205】

次いで、得られた結晶構造を有する半導体膜(例えば結晶性珪素膜)の表面にオゾン水で薄い酸化膜を形成した後、第1のフォトマスクを用いてレジストからなるマスクを形成し、所望の形状にエッチング処理して島状に分離された半導体膜(本明細書では「島状半導体層」という)331及び332を形成する(図30(A)参照)。島状半導体層331・332にはTFT373、372が形成される。島状半導体層331及び332を形成した後、レジストからなるマスクを除去する。

40

【0206】

上記したように、結晶構造を有する半導体膜は第1又は第2の実施の形態と同様な方法によって形成される。このため、島状半導体層331、332はチャネル方向に結晶粒が長くなり、TFT373、372のチャネル形成領域373b、372bに結晶粒界がほとんど含まれなくなり、電子や正孔などのキャリアに対するエネルギー障壁が低くなる。その結果、TFT373、372の移動度が、例えば数百cm<sup>2</sup>/Vsになる。また、島状半導体層331、332のばらつきが抑制されるため、TFT373、372の特性にばらつきが生じることを抑制できる。

50

## 【0207】

次いで、必要があればTFTのしきい値を制御するために微量な不純物元素（ホウ素またはリン）のドーピングを行う。ここでは、ジボラン（B<sub>2</sub>H<sub>6</sub>）を質量分離しないでプラズマ励起したイオンドープ法を用いる。

## 【0208】

次いで、フッ酸を含むエッチャントで酸化膜を除去すると同時に島状半導体層331及び332の表面を洗浄した後、ゲート絶縁膜313となる珪素を主成分とする絶縁膜を形成する。ここでは、プラズマCVD法により115nmの厚さで窒素を含む酸化珪素膜（例えば組成比Si=32%、O=59%、N=7%、H=2%）で形成する。

## 【0209】

次いで、ゲート絶縁膜313上に金属膜を形成した後、第2のフォトマスクを用いてパターニングを行い、ゲート電極334及び335、配線314及び315、端子電極350を形成する（図30（B）参照）。この金属膜として、例えば窒化タンタル（TaN）及びタンクスチン（W）をそれぞれ30nm、370nm積層した膜を用いる。

## 【0210】

また、ゲート電極334及び335、配線314及び315、端子電極350として、上記以外にもチタン（Ti）、タンクスチン（W）、タンタル（Ta）、モリブデン（Mo）、ネオジウム（Nd）、コバルト（Co）、ジルコニウム（Zr）、亜鉛（Zn）、ルテニウム（Ru）、ロジウム（Rh）、パラジウム（Pd）、オスミウム（Os）、イリジウム（Ir）、白金（Pt）、アルミニウム（Al）、金（Au）、銀（Ag）、銅（Cu）から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物、例えば、窒化チタン、窒化タンクスチン、窒化タンタル、窒化モリブデンからなる単層膜を用いることができる。

## 【0211】

次いで、島状半導体層331及び332への一導電型を付与する不純物の導入を行って、TFT373のソース領域またはドレイン領域337、並びにTFT372のソース領域またはドレイン領域338の形成を行う（図30（C）参照）。本実施例ではnチャネル型TFTを形成するので、n型の不純物、例えばリン（P）、砒素（As）を島状半導体層331及び332に導入する。

## 【0212】

次いで、CVD法により酸化珪素膜を含む第1の層間絶縁膜（図示しない）を50nm形成した後、それぞれの島状半導体層に添加された不純物元素を活性化処理する工程を行う。この活性化工程は、ランプ光源を用いたラピッドサーマルアニール法（RTA法）、或いはYAGレーザまたはエキシマレーザを裏面から照射する方法、或いは炉を用いた熱処理、或いはこれらの方のうち、いずれかと組み合わせた方法によって行う。

## 【0213】

次いで、水素及び酸素を含む窒化珪素膜を含む第2の層間絶縁膜316を、例えば10nmの膜厚で形成する。

## 【0214】

次いで、第2の層間絶縁膜316上に絶縁物材料から成る第3の層間絶縁膜317を形成する（図30（D）参照）。第3の層間絶縁膜317はCVD法で得られる絶縁膜を用いることができる。本実施例においては密着性を向上させるため、第3の層間絶縁膜317として、900nmの膜厚で形成した窒素を含む酸化珪素膜を形成する。

## 【0215】

次に、熱処理（300～550℃で1～12時間の熱処理、例えば窒素雰囲気中410℃で1時間）を行い、島状半導体層を水素化する。この工程は第2の層間絶縁膜316に含まれる水素により島状半導体層のダングリングボンドを終端させるために行うものである。ゲート絶縁膜313の存在に関係なく島状半導体層を水素化することができる。

## 【0216】

また第3の層間絶縁膜317として、シロキサンを用いた絶縁膜、及びそれらの積層構造

10

20

30

40

50

を用いることも可能である。

【0217】

第3の層間絶縁膜317としてシロキサンを用いた絶縁膜、及びそれらの積層構造を用いた場合は、第2の層間絶縁膜316を形成後、島状半導体層を水素化するための熱処理を行い、次に第3の層間絶縁膜317を形成することもできる。

【0218】

次いで、第3のフォトマスクを用いてレジストからなるマスクを形成し、第1の層間絶縁膜、第2の層間絶縁膜316及び第3の層間絶縁膜317またはゲート絶縁膜313を選択的にエッチングしてコンタクトホールを形成する。そして、レジストからなるマスクを除去する。

10

【0219】

なお、第3の層間絶縁膜317は必要に応じて形成すればよく、第3の層間絶縁膜317を形成しない場合は、第2の層間絶縁膜316を形成後に第1の層間絶縁膜、第2の層間絶縁膜316及びゲート絶縁膜313を選択的にエッチングしてコンタクトホールを形成する。

【0220】

次いで、スパッタ法で金属積層膜を成膜した後、第4のフォトマスクを用いてレジストからなるマスクを形成し、選択的に金属膜をエッチングして、配線319、接続電極320、端子電極351、TFT372のソース電極またはドレイン電極341、TFT373のソース電極またはドレイン電極342を形成する。そして、レジストからなるマスクを除去する。なお、本実施例の金属膜は、膜厚100nmのTi膜と、膜厚350nmのSiを微量に含むAl膜と、膜厚100nmのTi膜との3層を積層したものとする。

20

【0221】

また図29(B)で示すように、配線404、接続電極405、端子電極401、TFT372のソース電極又はドレイン電極402、並びにTFT373のソース電極又はドレイン電極403を単層の導電膜により形成する場合は、耐熱性及び導電率等の点からチタン膜(Ti膜)を用いるのが好ましい。またチタン膜に変えて、タンゲステン(W)、タンタル(Ta)、モリブデン(Mo)、ネオジウム(Nd)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、白金(Pt)から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物、例えば、窒化チタン、窒化タンゲステン、窒化タンタル、窒化モリブデンからなる単層膜を用いることができる。配線404、接続電極405、端子電極401、TFT372のソース電極又はドレイン電極402、並びにTFT373のソース電極又はドレイン電極403を単層膜にすることにより、作製工程において成膜回数を減少させることができる。

30

【0222】

以上の工程で、多結晶珪素膜を用いたトップゲート型TFT372及び373を作製することができる。

40

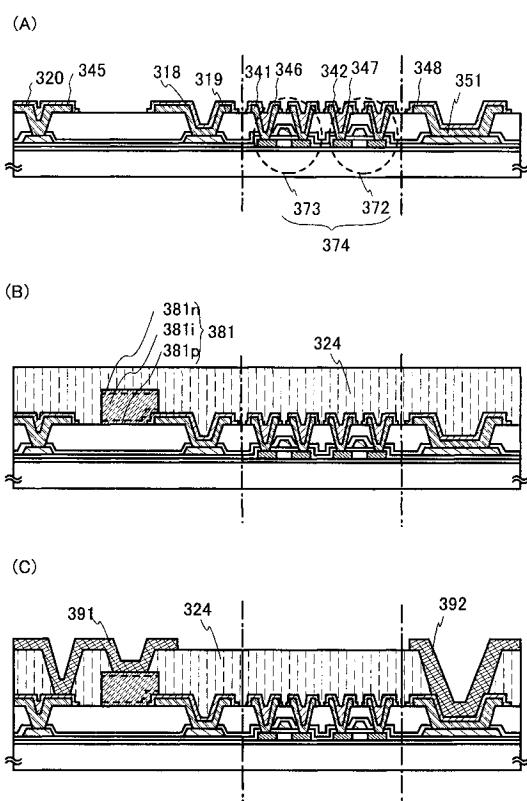

【0223】

次いで、後に形成される光電変換層(代表的にはアモルファスシリコン)と反応して合金になりにくい導電性の金属膜(チタン(Ti)またはモリブデン(Mo)など)を成膜した後、第5のフォトマスクを用いてレジストからなるマスクを形成し、選択的に導電性の金属膜をエッチングして配線319を覆う保護電極318を形成する(図31(A)参照)。ここではスパッタ法で得られる膜厚200nmのTi膜を用いる。なお、同様に接続電極320、端子電極351、TFTのソース電極またはドレイン電極も導電性の金属膜345、348、346、347で覆われる。従って、導電性の金属膜は、これらの電極における2層目のAl膜が露呈されている側面も覆い、導電性の金属膜は光電変換層へのアルミニウム原子の拡散も防止できる。

【0224】

50

ただし、配線 319、接続電極 320、端子電極 351、TFT372 のソース電極またはドレイン電極 341、並びに TFT373 のソース電極またはドレイン電極 342 を、単層の導電膜で形成する場合、すなわち図 29 (B) で示すように、これらの電極又は配線に代えて、配線 404、接続電極 405、端子電極 401、及び TFT372 のソース電極又はドレイン電極 402、並びに TFT373 のソース電極又はドレイン電極 403 を形成する場合は、保護電極 318、345、348、346、347 は形成しなくてても良い。

#### 【0225】

次に第 3 の層間絶縁膜 317 上に、p 型半導体層 381p、i 型半導体層 381i 及び n 型半導体層 381n を含む光電変換層 381 を形成する。

10

#### 【0226】

p 型半導体層 381p は、13 属の不純物元素、例えばホウ素 (B) を含んだセミアモルファスシリコン膜をプラズマ CVD 法にて成膜して形成すれば良い。

#### 【0227】

また配線 319 及び保護電極 318 は光電変換層 381 の最下層、本実施例では p 型半導体層 381p と接している。

#### 【0228】

p 型半導体層 381p を形成したら、さらに i 型半導体層 381i 及び n 型半導体層 381n を順に形成する。これにより p 型半導体層 381p、i 型半導体層 381i 及び n 型半導体層 381n を有する光電変換層 381 が形成される。

20

#### 【0229】

i 型半導体層 381i としては、例えばプラズマ CVD 法でセミアモルファスシリコン膜を形成すれば良い。また n 型半導体層 381n としては、15 属の不純物元素、例えばリン (P) を含むセミアモルファスシリコン膜を形成しても良いし、セミアモルファスシリコン膜を形成後、15 属の不純物元素を導入しても良い。

#### 【0230】

また p 型半導体層 381p、真性半導体層 381i、n 型半導体層 381n として、セミアモルファス半導体膜だけではなく、アモルファス半導体膜を用いても良い。

#### 【0231】

次いで、全面に絶縁物材料 ( 例えば珪素を含む無機絶縁膜 ) からなる封止層 324 を厚さ 1 μm ~ 30 μm で形成して図 31 (B) の状態を得る。ここでは絶縁物材料膜として CVD 法により、膜厚 1 μm の窒素を含む酸化珪素膜を形成する。CVD 法による絶縁膜を用いることによって密着性の向上を図っている。

30

#### 【0232】

次いで、封止層 324 をエッチングして開口部を設けた後、スパッタ法により端子電極 391 及び 392 を形成する。端子電極 391 及び 392 は、チタン膜 (Ti 膜) (100 nm) と、ニッケル膜 (Ni 膜) (300 nm) と、金膜 (Au 膜) (50 nm) との積層膜とする。こうして得られる端子電極 391 及び端子電極 392 の固着強度は 5 N を超え、端子電極として十分な固着強度を有している。

#### 【0233】

以上の工程で、半田接続が可能な端子電極 391 及び端子電極 392 が形成され、図 31 (C) に示す構造が得られる。

40

#### 【0234】

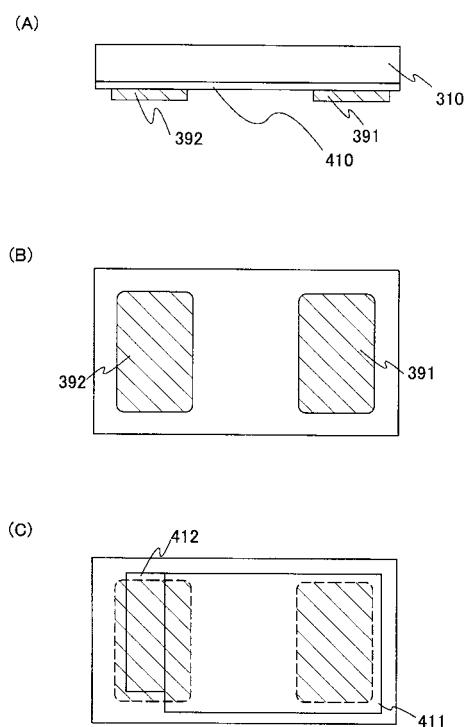

次いで、個々に切断して複数の光センサチップを切り出す。1 枚の大面積基板 ( 例えば 600 cm × 720 cm ) からは大量の光センサチップ ( 例えば 2 mm × 1.5 mm ) を製造することが可能である。

#### 【0235】

切り出した 1 つの光センサチップ ( 例えば 2 mm × 1.5 mm ) の断面図を図 32 (A) に示し、その下面図を図 32 (B)、上面図を図 32 (C) に示す。図 32 (A) ~ 図 32 (C) において、図 29 (A) ~ 図 29 (C)、図 30 (A) ~ 図 30 (C)、図 31

50

(A)～図31(C)と同一である箇所には同じ符号を用いている。なお、図32(A)において、基板310と、素子形成領域410と、端子電極391及び端子電極392とを含む総膜厚は、例えば0.8±0.05mmである。

【0236】

また、光センサチップの総膜厚を薄くするために、基板310をCMP処理等によって削って薄くした後、ダイサーで個々に切断して複数の光センサチップを切り出しても良い。

【0237】

また、図32(B)において、端子電極391及び392の一つの電極サイズは、例えば0.6mm×1.1mmであり、電極間隔は例えば0.4mmである。また、図32(C)において受光部411の面積は、例えば1.57mm<sup>2</sup>である。また、增幅回路部412には、約100個のTFTが設けられている。

【0238】

最後に、得られた光センサチップを基板360の実装面に実装する。なお、端子電極391と電極361、並びに端子電極392と電極362との接続には、それぞれ半田364及び363を用い、予め基板360の電極361及び362上にスクリーン印刷法などによって形成しておき、半田と端子電極を当接した状態にしてから半田リフロー処理を行って実装する。半田リフロー処理は、例えば不活性ガス雰囲気中、255～265程度の温度で約10秒行う。また、半田の他に金属(金、銀等)で形成されるバンプ、又は導電性樹脂で形成されるバンプ等を用いることができる。また、環境問題を考慮して鉛フリーはんだを用いて実装しても良い。

【0239】

なお本実施例は、他の実施例のいかなる記載と組み合わせることも可能である。

【実施例9】

【0240】

本実施例では、実施例8によって得られた半導体装置を様々な電子機器に組み込んだ例について説明する。本発明が適用される電子機器として、コンピュータ、ディスプレイ、携帯電話、テレビなどが挙げられる。それらの電子機器の具体例を図33、図34(A)～図34(B)、図35(A)～図35(B)及び図36に示す。

【0241】

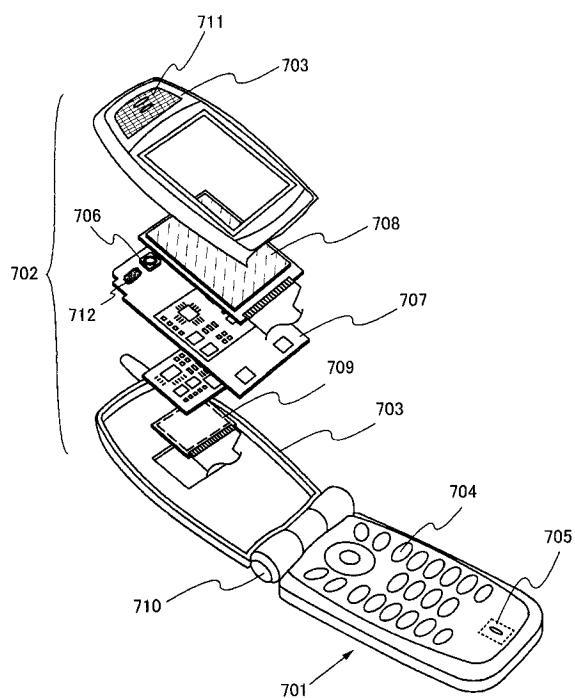

図33は携帯電話であり、本体(A)701、本体(B)702、筐体703、操作キー704、音声入力部705、音声出力部706、回路基板707、表示パネル(A)708、表示パネル(B)709、蝶番710、透光性材料部711、光センサ712を有している。実施例8に示した半導体装置は光センサ712に適用することができる。このため、光センサ712に特性のばらつきが生じることを抑制できる。

【0242】

光センサ712は透光性材料部711を透過した光を検知し、検知した外部光の照度に合わせて表示パネル(A)708及び表示パネル(B)709の輝度コントロールを行い、また光センサ712で得られる照度に合わせて操作キー704の照明制御を行う。これにより携帯電話の消費電流を抑えることができる。

【0243】

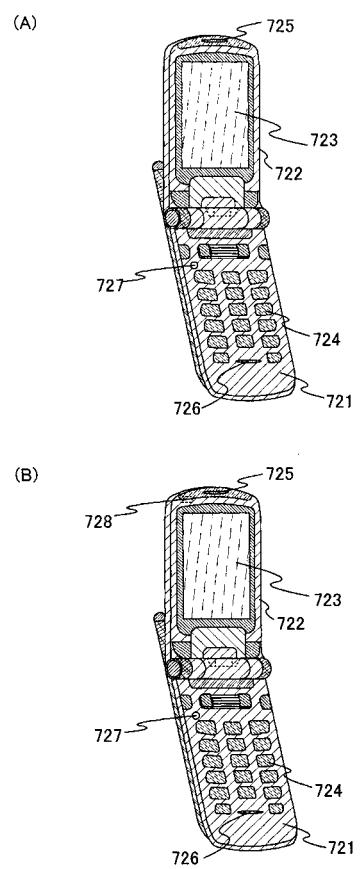

図34(A)及び図34(B)に携帯電話の別の例を示す。図34(A)及び図34(B)において、721は本体、722は筐体、723は表示パネル、724は操作キー、725は音声出力部、726は音声入力部、727及び728は光センサ部であり、実施例8に示した半導体装置を適用することができる。このため、光センサ部727、728に特性のばらつきが生じることを抑制できる。

【0244】

図34(A)に示す携帯電話では、本体721に設けられた光センサ部728により外部の光を検知することにより表示パネル723及び操作キー724の輝度を制御することが可能である。

【0245】

10

20

30

40

50

また図34(B)に示す携帯電話では、図34(A)の構成に加えて、本体721の内部に光センサ部728を設けている。光センサ部728により、表示パネル723に設けられているバックライトの輝度を検出することも可能となる。

【0246】

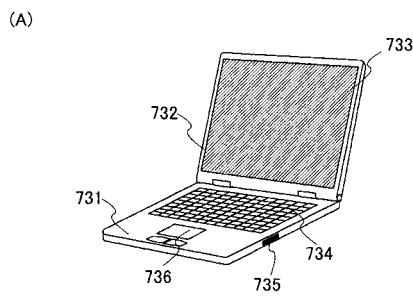

図35(A)はコンピュータであり、本体731、筐体732、表示部733、キーボード734、外部接続ポート735、ポインティングマウス736等を含む。

【0247】

また図35(B)は表示装置でありテレビ受像器などがこれに当たる。本表示装置は、筐体741、支持台742、表示部743などによって構成されている。

【0248】

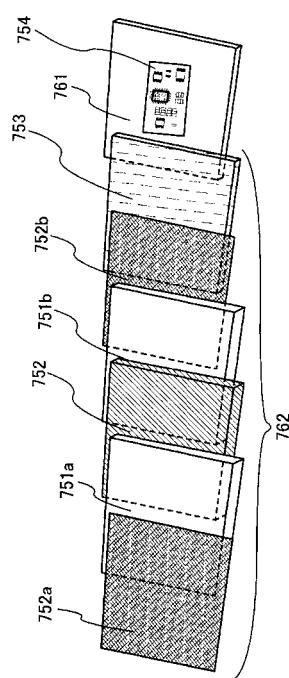

図35(A)のコンピュータに設けられる表示部733、及び図35(B)に示す表示装置の表示部743として、液晶パネルを用いた場合の詳しい構成を図36に示す。

【0249】

図36に示す液晶パネル762は、筐体761に内蔵されており、基板751a及び751b、基板751a及び751bに挟まれた液晶層752、偏光フィルタ752a及び752b、及びバックライト753等を有している。また筐体761には光センサ部754が形成されている。光センサ部754には実施例8に示した半導体装置を適用することができる。このため、光センサ部754に特性のばらつきが生じることを抑制できる。

【0250】

光センサ部754は、バックライト753からの光量を感知し、その情報がフィードバックされて液晶パネル762の輝度が調節される。

【0251】

尚、本発明は上述した実施形態及び実施例に限定されるものではなく、本発明の主旨を逸脱しない範囲内で種々変更して実施することが可能である。

【図面の簡単な説明】

【0252】

【図1】第1の実施形態に係る半導体膜の結晶化方法を説明する為の図。

【図2】第2の実施形態に係る半導体膜の結晶化方法を説明する為の図。

【図3】実施例1に係る半導体装置及び発光装置の作製方法を説明する為の図。

【図4】実施例1に係る半導体装置及び発光装置の作製方法を説明する為の図。

【図5】実施例1に係る半導体装置及び発光装置の作製方法を説明する為の図。

【図6】実施例1に係る半導体装置及び発光装置の作製方法を説明する為の図。

【図7】実施例1に係る半導体装置及び発光装置の作製方法を説明する為の図。

【図8】実施例1に係る半導体装置及び発光装置の作製方法を説明する為の図。

【図9】実施例1に係る半導体装置及び発光装置の作製方法を説明する為の図。

【図10】実施例1に係る半導体装置及び発光装置の作製方法を説明する為の図。

【図11】実施例1に係る半導体装置及び発光装置の作製方法を説明する為の図。

【図12】実施例1に係る半導体装置及び発光装置の作製方法を説明する為の図。

【図13】実施例1に係る半導体装置及び発光装置の作製方法を説明する為の図。

【図14】実施例2に係る発光装置の画素部を示す上面図。

【図15】図14の回路図。

【図16】実施例3に係る電子機器を示す斜視図。

【図17】実施例4に係る半導体装置の作製方法を説明する為の図。

【図18】実施例4に係る半導体装置の作製方法を説明する為の図。

【図19】実施例4に係る半導体装置の作製方法を説明する為の図。

【図20】実施例4に係る半導体装置の作製方法を説明する為の図。

【図21】実施例4に係る半導体装置の作製方法を説明する為の図。

【図22】実施例4に係る半導体装置の作製方法を説明する為の図。

【図23】実施例5に係る半導体装置の作製方法を説明する為の図。

【図24】実施例5に係る半導体装置の作製方法を説明する為の図。

10

20

30

40

50

- 【図 2 5】実施例 5 に係る半導体装置の作製方法を説明する為の図。

- 【図 2 6】実施例 5 に係る半導体装置の作製方法を説明する為の図。

- 【図 2 7】実施例 6 に係る半導体装置を説明する為の図。

- 【図 2 8】実施例 7 に係る半導体装置を説明する為の図。

- 【図 2 9】実施例 8 に係る半導体装置を説明する為の図。

- 【図 3 0】実施例 8 に係る半導体装置の作製方法を説明する為の図。

- 【図 3 1】実施例 8 に係る半導体装置の作製方法を説明する為の図。

- 【図 3 2】実施例 8 に係る半導体装置を説明する為の図。

- 【図 3 3】実施例 9 に係る電子機器を説明する為の図。

- 【図 3 4】実施例 9 に係る電子機器を説明する為の図。

- 【図 3 5】実施例 9 に係る電子機器を説明する為の図。

- 【図 3 6】実施例 9 に係る電子機器が有する液晶パネルを説明する為の図。

- 【図 3 7】第 1 の従来例に係る半導体膜の結晶化方法を示す図。

- 【図 3 8】第 2 の従来例に係る半導体膜の結晶化方法を示す図。

10

### 【符号の説明】

【 0 2 5 3 】

501、502…発振器、503…第1のレーザ光、504…第2のレーザ光、505…シリンドリカルレンズ、506…半導体膜、507、508、509、522、523、524…ミラー、510…基板、510a…底面、521…ビームスプリッタ

### 【圖 1】

〔 図 2 〕

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図3 1】

【図3 2】

【図3 3】

【図3 4】

【図35】

【図36】

【図37】

【図38】

## フロントページの続き

F ターム(参考) 5F110 AA01 AA28 AA30 BB02 BB04 BB09 CC02 CC07 DD01 DD02

DD03 DD05 DD12 DD13 DD14 DD15 DD17 DD25 EE01 EE02

EE03 EE04 EE06 EE14 EE22 EE23 EE28 EE43 EE44 FF02

FF03 FF04 FF09 FF27 FF28 FF29 FF30 FF32 GG01 GG02

GG13 GG25 GG32 GG42 GG43 GG45 GG47 GG51 GG53 HJ01

HJ23 HL01 HL02 HL03 HL04 HL06 HL12 HL22 HL23 HL24

HL27 HM13 HM15 NN03 NN04 NN22 NN23 NN24 NN27 NN33

NN34 NN35 NN36 NN71 NN72 NN73 NN78 PP01 PP02 PP03

PP05 PP06 PP07 PP13 PP24 PP29 PP34 PP35 QQ09 QQ16

QQ23 QQ28

5F152 AA03 AA08 AA10 BB02 CC02 CC03 CC04 CC05 CC06 CC07

CC08 CC09 CD13 CD14 CD15 CE04 CE05 CE06 CE13 CE14

CE15 CE16 CE24 CE45 CF13 CF18 DD05 DD07 EE01 EE02

EE03 EE06 EE16 FF02 FF03 FF04 FF05 FF06 FF07 FF08

FF11 FF21 FF22 FF26 FF28 FF30 FF31 FF32 FF47 FG01

FG04 FG12 FG13 FG18 FG23 FH02 FH03 FH08 LP01 LP08

LP09 MM04 NN14 NN16 NN20 NQ03 NQ12