#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

### (43) International Publication Date 22 December 2011 (22.12.2011)

# (10) International Publication Number WO 2011/160011 A1

(51) International Patent Classification:

**H01L 21/28** (2006.01) **H01L 27/115** (2006.01) **H01L 21/8247** (2006.01) **H01L 21/764** (2006.01)

(21) International Application Number:

PCT/US2011/040874

(22) International Filing Date:

17 June 2011 (17.06.2011)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/356,600 19 June 2010 (19.06.2010) US 13/162,550 16 June 2011 (16.06.2011) US

- (71) Applicant (for all designated States except US): SAN-DISK TECHNOLOGIES, INC. [US/US]; Two Legacy Town Center, 6900 North Dallas Parkway, Plano, TX 75024 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): PURAYATH, Vinod, Robert [IN/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). MATAMIS, George [US/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). CHIEN, Henry [US/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). KAI, James [US/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US). ZHANG, Yuan

[CN/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US).

- (74) Agent: CROMER, David, E.; Vierra Magen Marcus & DeNiro, LLP, 575 Market Street, Suite 2500, San Francisco, CA 94105 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

[Continued on next page]

(54) Title: ISOLATION BETWEEN NONVOLATILE MEMORY CELLS BY MEANS OF LOW- DIELECTRIC- CONSTANT DIELECTRICS AND AIR GAPS AND CORRESPONDING MANUFACTURING METHOD

FIG. 7G

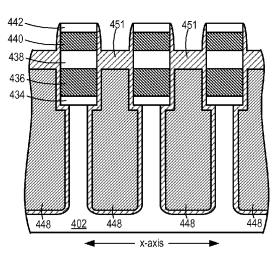

(57) Abstract: High - density semiconductor memory is provided with enhancements to gate coupling and electrical isolation between discrete devices in non-volatile memory. The intermediate dielectric (438) between control gates (442) and charge storage regions (436) is varied in the row direction, with different dielectric constants for the varied materials to provide adequate inter-gate coupling while protecting from fringing fields and parasitic capacitances. Dielectric caps (451,453) are provided between memory cells and have a dielectric constant smaller than the one of the intermediate dielectric (438). Electrical isolation is further provided, at least in part, by air gaps that are formed in the column (bit line) direction and/or air gaps that are formed in the row (word line) direction.

#### Published:

— with international search report (Art. 21(3))

ISOLATION BETWEEN NONVOLATILE MEMORY CELLS BY MEANS OF LOW-DIELECTRIC-CONSTANT DIELECTRICS AND AIR GAPS AND CORRESPONDING MANUFACTURING METHOD

#### PRIORITY CLAIM

**[0001]** The present application claims priority from U.S. Provisional Patent Application No. 61/356,600 (Attorney Docket No. SAND-01475USO), entitled "Flat Non-Volatile Memory Cells with Air Gap Isolation," by Purayath, et al., filed June 19, 2010, incorporated by reference herein in its entirety.

#### BACKGROUND OF THE INVENTION

#### Field of the Disclosure

[0002] Embodiments of the present disclosure are directed to high density semiconductor devices, such as non-volatile storage, and methods of forming the same.

#### Description of the Related Art

[0003] In most integrated circuit applications, the substrate area allocated to implement the various integrated circuit functions continues to decrease. Semiconductor memory devices, for example, and their fabrication processes are continuously evolving to meet demands for increases in the amount of data that can be stored in a given area of the silicon substrate. These demands seek to increase the storage capacity of a given size of memory card or other type of package and/or decrease their size.

[0004] Electrical Erasable Programmable Read Only Memory (EEPROM), including flash EEPROM, and Electronically Programmable Read Only Memory (EPROM) are among the most popular non-volatile semiconductor memories. One popular flash EEPROM architecture utilizes a NAND array having a large number of strings of memory cells connected through one or more select transistors between individual bit lines and common source lines.

2

Figure 1 is a top view showing a single NAND string and Figure 2 is an equivalent circuit thereof. The NAND string depicted in Figures 1 and 2 includes four transistors 100, 102, 104 and 106 in series between a first select gate 120 and a second select gate 122. Select gate 120 connects the NAND string to a bit line via bit line contact 126. Select gate 122 connects the NAND string to a common source line via source line contact 128. Each of the transistors 100, 102, 104 and 106 is an individual storage element and includes a control gate and a floating gate. For example, transistor 100 includes control gate 100CG and floating gate 102FG, transistor 102 includes control gate 102CG and floating gate 102FG, transistor 104 includes control gate 104CG and floating gate 104FG, and transistor 106 includes control gate 106CG and floating gate 106FG. Control gate 100CG is connected to word line WL3, control gate 102CG is connected to word line WL2, control gate 104CG is connected to word line WL1, and control gate 106CG is connected to word line WL0.

[0005] Note that although Figures 1 and 2 show four memory cells in the NAND string, the use of four transistors is only provided as an example. A NAND string can have less than four memory cells or more than four memory cells. For example, some NAND strings will include eight memory cells, 16 memory cells, 32 memory cells, or more.

[0006] The charge storage elements of current flash EEPROM arrays are most commonly electrically conductive floating gates, typically formed from a doped polysilicon material. Another type of memory cell useful in flash EEPROM systems utilizes a non-conductive dielectric material in place of a conductive floating gate to form a charge storage element capable of storing charge in a non-volatile manner. Such a cell is described in an article by Chan et al., "A True Single-Transistor Oxide-Nitride-Oxide EEPROM Device," IEEE Electron Device Letters, Vol. EDL-8, No. 3, March 1987, pp. 93-95. A triple layer dielectric formed of silicon oxide, silicon nitride and silicon oxide

3

("ONO") is sandwiched between a conductive control gate and a surface of a semi-conductive substrate above the memory cell channel. The cell is programmed by injecting electrons from the cell channel into the nitride, where they are trapped and stored in a limited region. This stored charge then changes the threshold voltage of a portion of the channel of the cell in a manner that is detectable. The cell is erased by injecting hot holes into the nitride. See also Nozaki et al., "A 1-Mb EEPROM with MONOS Memory Cell for Semiconductor Disk Application," EEE Journal of Solid-State Circuits, Vol. 26, No. 4, April 1991, pp. 497-501, which describes a similar cell in a split-gate configuration where a doped polysilicon gate extends over a portion of the memory cell channel to form a separate select transistor.

[0007] Memory cells of typical non-volatile flash arrays are divided into discrete blocks of cells that are erased together. That is, the block contains the minimum number of cells that are separately erasable together as an erase unit, although more than one block may be erased in a single erase operation. Additionally, more recent memories may provide erasing in smaller units than blocks. Each block typically stores one or more pages of data, where a page includes the minimum number of cells that are simultaneously subjected to a data programming and read operation as the basic unit of programming and reading, although more than one page may be programmed or read in a single operation. Each page typically stores one or more sectors of data, the size of the sector being defined by the host system. An example is a sector of 512 bytes of user data, following a standard established with magnetic disk drives, plus some number of bytes of overhead information about the user data and/or the block in which it is stored.

[0008] As demands for higher densities in integrated circuit applications have increased, fabrication processes have evolved to reduce the minimum feature sizes of circuit elements such as the gate and channel regions of transistors. As the feature sizes have decreased, modifications to the traditional

WO 2011/160011

PCT/US2011/040874

4

NAND memory array have been made to, among other things, decrease parasitic capacitances associated with small feature sizes.

#### BRIEF DESCRIPTION OF THE DRAWINGS

- [0009] Figure 1 is a top view of a NAND string.

- [0010] Figure 2 is an equivalent circuit diagram of the NAND string depicted in Figure 1.

- [0011] Figure 3 is a plan view of a portion of a NAND flash memory array.

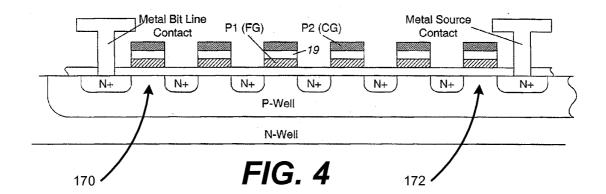

- **[0012]** Figure 4 is an orthogonal cross-sectional view taken along line A--A of the portion of the flash memory array depicted in Figure 3.

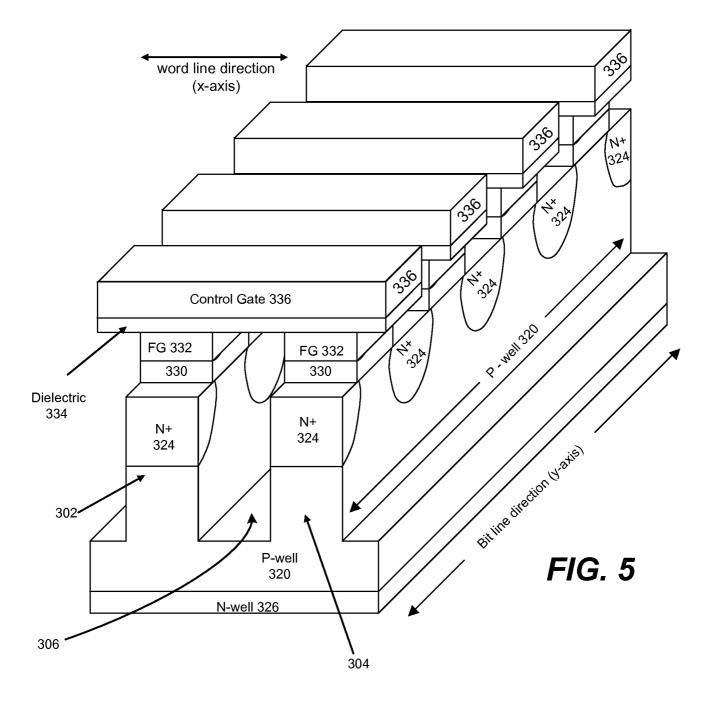

- [0013] Figure 5 is a three-dimensional drawing of a pair of four word line long portions of two NAND strings.

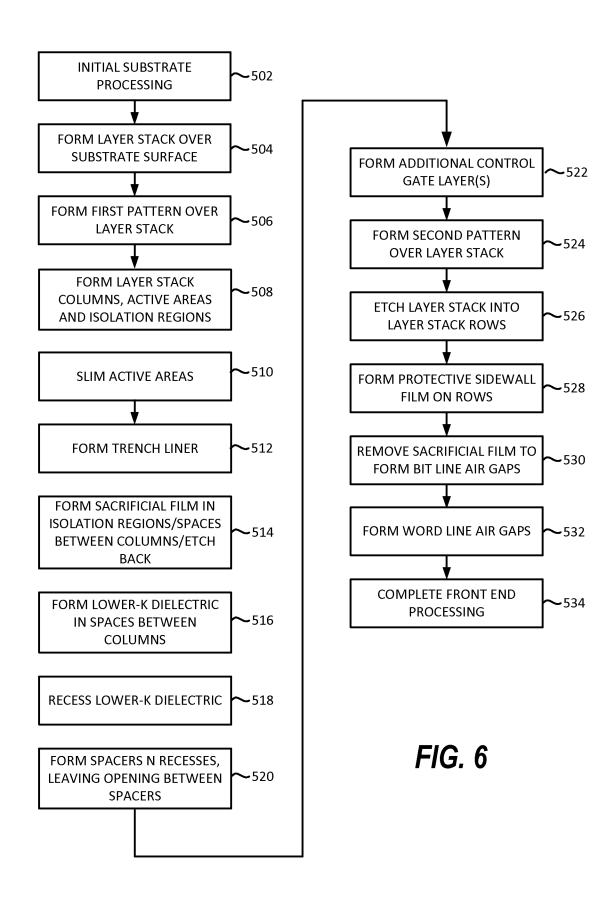

- [0014] Figure 6 is a flowchart describing a method of forming a non-volatile memory array in accordance with one embodiment.

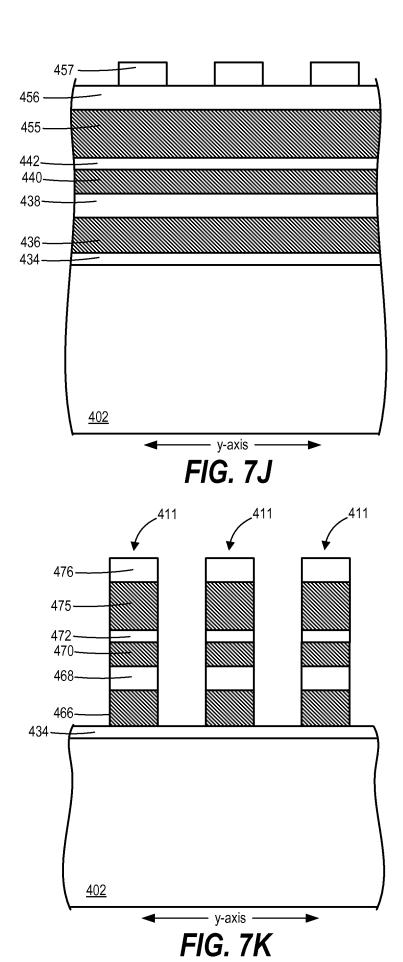

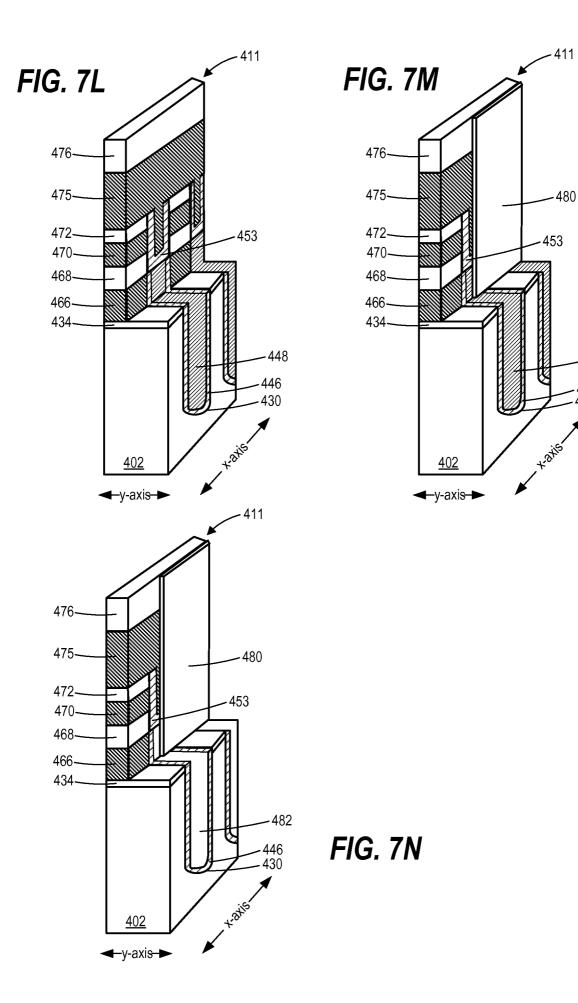

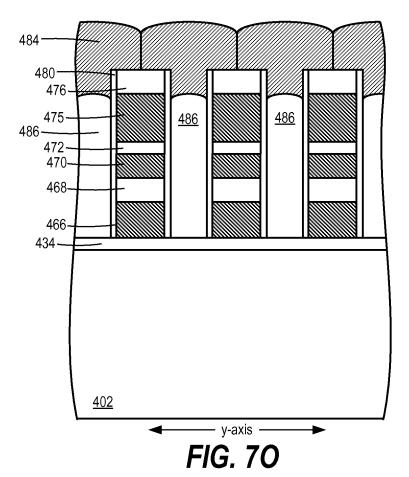

- **[0015]** Figures 7A-7O are cross-sectional and perspective views of a portion of a non-volatile memory array depicting a fabrication process according to the method of Figure 6 in one embodiment.

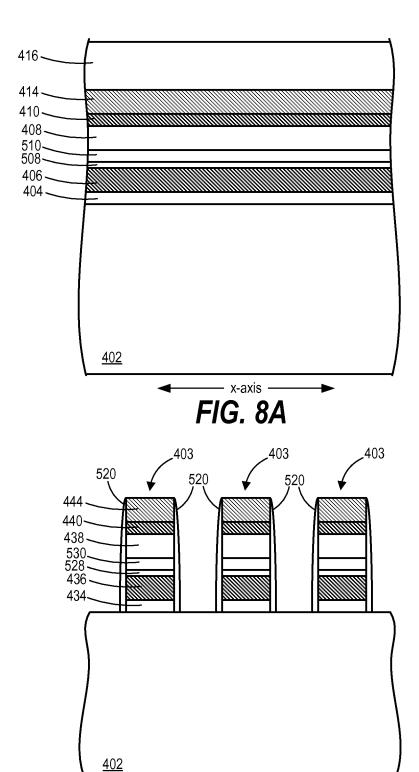

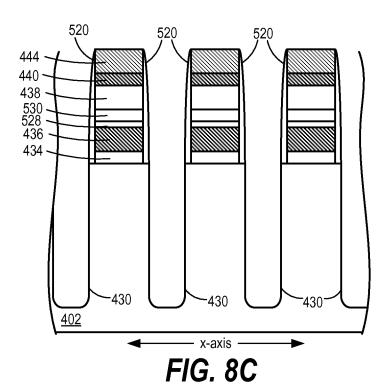

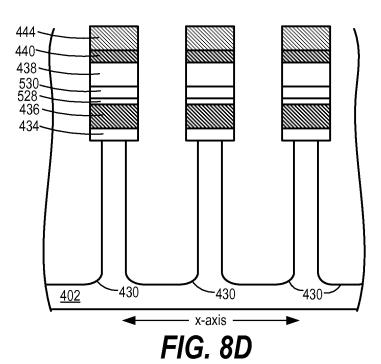

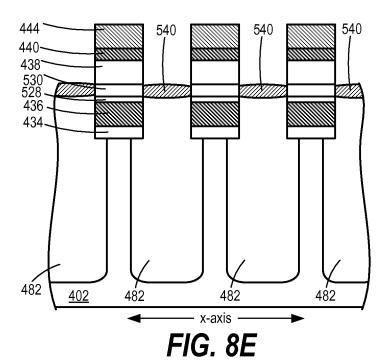

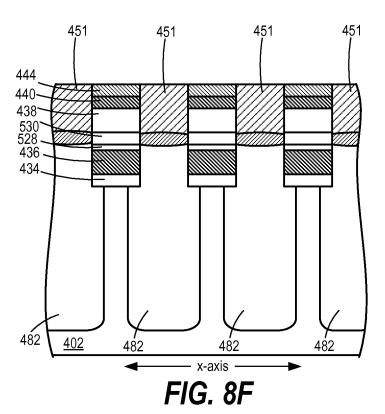

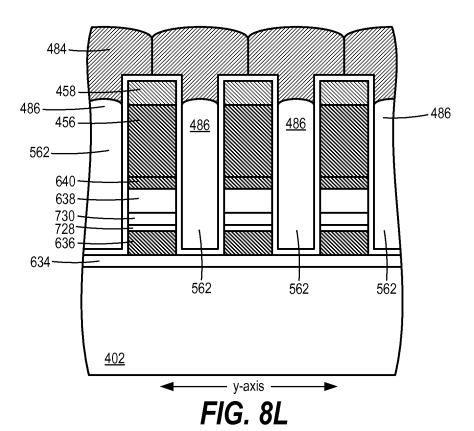

- [0016] Figures 8A-8L are cross-views of a portion of a non-volatile memory array depicting a fabrication process in accordance with one embodiment.

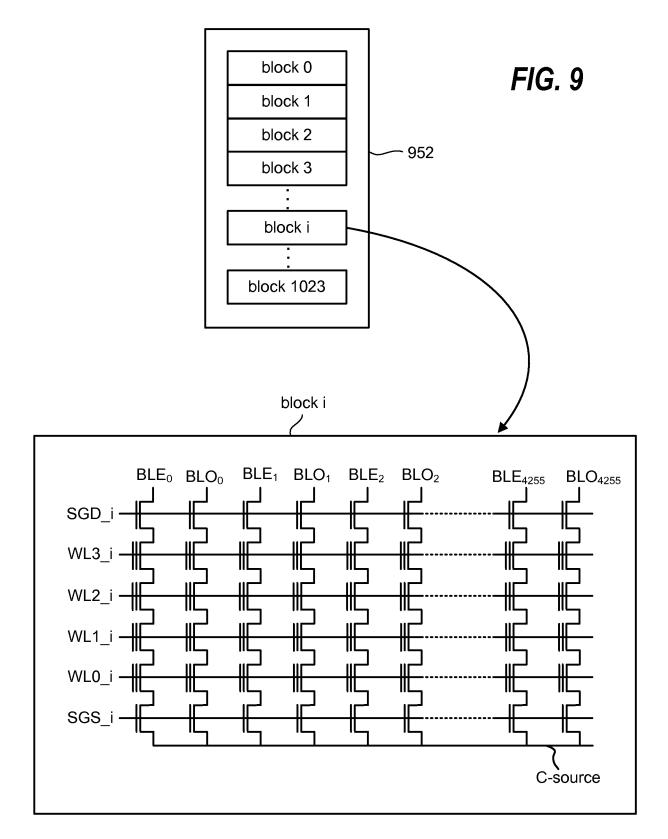

- **[0017]** Figure 9 depicts an example of the organization of a memory array in accordance with one embodiment.

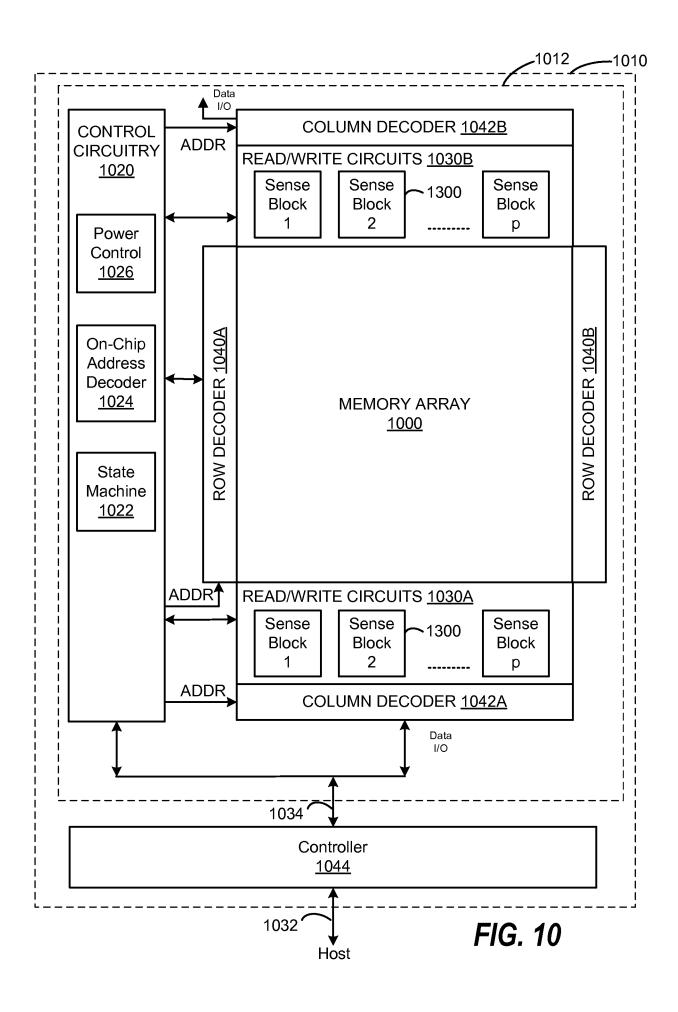

- **[0018]** Figure 10 is a block diagram depicting an example of a memory system that can be fabricated or used to implement embodiments of the disclosed technology.

5

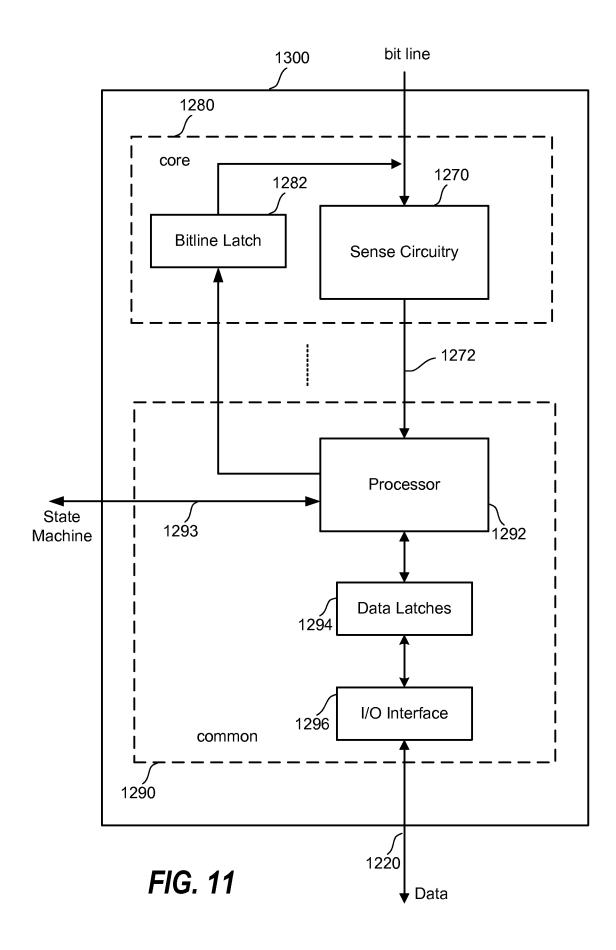

[0019] Figure 11 is a block diagram depicting one embodiment of a sense block.

#### **DETAILED DESCRIPTION**

[0020] Embodiments of the present disclosure are directed to high-density semiconductor memory, and more particularly to electrical isolation between discrete devices in non-volatile memory. The intermediate dielectric between control gates and charge storage regions is varied in the row direction, with different dielectric constants for the varied materials to provide adequate intergate coupling while protecting from fringing fields and parasitic capacitances. Electrical isolation is further provided, at least in part, by air gaps that are formed in the column (bit line) direction and/or air gaps that are formed in the row (word line) direction. Non-volatile memory arrays and related methods of fabrication are provided.

In one embodiment, a flat memory cell structure is provided, having [0021] an intermediate dielectric region between an individual charge storage region and its overlying control gate. The intermediate dielectric region is etched in both the column and row directions, forming a discrete region for each storage element. A first control gate layer (optional) is formed with an intermediate dielectric layer, charge storage layer, and tunnel dielectric layer, which are etched to form layer stack columns (in the column direction). Isolation regions are etched in the substrate between active areas underlying the columns. Cap strips are formed between the layer stack columns, extending in the row and column directions over the corresponding isolation region. Sacrificial materials may be formed in the isolation region or a bridge strip formed along a portion of the charge storage material prior to forming the cap strips. The intermediate dielectric region overlying the charge storage regions has a high dielectric constant. The cap strips, which are formed adjacent to the intermediate dielectric regions and overlie the isolation regions, have a lower dielectric

6

constant to provide less coupling at these regions. The cap strips can be recessed in one embodiment. A second control gate layer is then formed, which can extend into the recesses. The layer stack is then etched to form second control gate strips that are continuous in the row direction and that contact a row of control gate regions formed from the first control gate layer if provided. Etching also forms the intermediate dielectric regions and individual charge storage regions.

[0022] In one embodiment, air gaps are formed in the column direction, referred to as bit line air gaps, to provide electrical isolation between devices adjacent in the row direction. For example, adjacent columns of non-volatile storage elements, such as adjacent strings in a NAND type non-volatile memory, can be isolated using air gaps that are formed in the substrate between active areas underlying the adjacent columns. Although principally described with respect to NAND type non-volatile memory, it will be understood that the various air gaps described herein can be utilized in other arrays utilizing column and/or row arrangements for storage elements. The dimensions of the bit line air gaps may vary according to the specifications for individual implementations. The bit line air gaps are formed at least partially in the isolation regions and extend above the substrate surface to caps or bridges overlying the isolation regions.

[0023] The air gaps formed in the row direction, referred to as word line air gaps, can provide electrical isolation between devices adjacent in the column direction. For example, adjacent rows of non-volatile storage elements such as the non-volatile storage elements associated with adjacent word lines in a NAND type non-volatile memory can be isolated using air gaps that are formed above the substrate between adjacent rows of storage elements. The dimensions of the word line air gaps may vary according to the specifications for individual implementations. In one embodiment, the bit line air gaps are formed entirely above the substrate surface. These air gaps may extend above the surface of the

7

substrate to at least partially occupy the area between adjacent rows of storage elements.

A portion of a NAND memory array as can be fabricated in [0024] accordance with an embodiment of the present disclosure is shown in plan view in Figure 3. BL0-BL4 represent bit line connections to global vertical metal bit lines (not shown). Four floating gate memory cells are shown in each string by way of example. Typically, the individual strings include 16, 32 or more memory cells, forming a column of memory cells. Control gate (word) lines labeled WL0-WL3 extend across multiple strings over rows of floating gates, often in polysilicon. Figure 4 is a cross-sectional view taken along line A--A of Figure 3, depicting polysilicon layer P2 from which the control gate lines are formed. The control gate lines are typically formed over the floating gates as a self-aligned stack, and are capacitively coupled to the floating gates through an intermediate dielectric layer 162. The top and bottom of the string connect to a bit line and a common source line through select transistors (gates) 170 and 172, respectively. Gate 170 is controlled by selection line DSL and gate 172 is controlled by selection line SSL. The floating gate material (P1) can be shorted to the control gate for the select transistors to be used as the active gate. Capacitive coupling between the floating gate and the control gate allows the voltage of the floating gate to be raised by increasing the voltage on the control gate. An individual cell within a column is read and verified during programming by causing the remaining cells in the string to be turned on hard by placing a relatively high voltage on their respective word lines and by placing a relatively lower voltage on the one selected word line so that the current flowing through each string is primarily dependent only upon the level of charge stored in the addressed cell below the selected word line. That current typically is sensed for a large number of strings in parallel, in order to read charge level states along a row of floating gates in parallel. Examples of NAND

8

memory cell array architectures and their operation as part of a memory system are found in U.S. Pat. Nos. 5,570,315, 5,774,397 and 6,046,935.

Figure 5 is a three-dimensional block diagram of two exemplary [0025] NAND strings 302 and 304 that may be fabricated as part of a larger flash memory array. Figure 5 depicts four memory cells on strings 302 and 304 as an example. Figure 5 depicts N-well 326 below P-well 320. The bit line or ydirection runs along the NAND strings, and the word line or x-direction runs perpendicular to the NAND string or the bit line direction. The word line direction may also be referred to as the row direction and the bit line direction referred to as the column direction. The P-type substrate below N-well 326 is not shown in Figure 5. In one embodiment, the control gates form the word lines. A continuous layer of conductive layer 336 can be formed which is consistent across a row in order to provide a common word line or control gate for each device on that word line. In such a case, this layer can be considered to form a control gate for each memory cell at the point where the layer overlaps a corresponding floating gate layer 332. In other embodiments, individual control gates can be formed and then interconnected by a separately formed word line.

[0026] When fabricating a NAND-type non-volatile memory system, including NAND strings as depicted in Figure 5, electrical isolation is provided in the word line direction between adjacent strings. In the embodiment depicted in Figure 5, NAND string 302 is separated from NAND string 304 by isolation area 306. Typically, an insulating material or dielectric is formed between adjacent NAND strings in this isolation area.

[0027] Although not shown, many non-volatile memory systems utilize control gates or word lines that wrap around the floating gate in the row direction. That is, in the word line direction, the control gate overlies a row of floating gate regions, and further extends downward between adjacent ones of the floating gate regions. The control gate layer may extend below an upper

9

surface level of the floating gate regions in between floating gates adjacent in the row direction. The intermediate dielectric layer will likewise wrap around the floating gates and not completely fill the space between adjacent floating gates so that the control gate material may occupy a portion of that space. Such a structure provides improved coupling between the control gates and floating gates by increasing the surface area for coupling. There will exist coupling between the upper surface of the floating and lower surface of the overlying control gate and also coupling between the control gate and the sidewalls of the floating gates.

[0028] As devices continue to be scaled, reaching 2x and 1x nm feature sizes for example, there exists little space between floating gates adjacent in the row direction. Techniques for efficient utilization of this space to achieve control gate wrap around with small features sizes are provided. A flat non-volatile memory cell-type structure is further introduced to address issues with space limitations between floating gates. The floating gate and intermediate dielectric layers can be modified to get an equally robust performance as with traditional devices.

[0029] In accordance with an embodiment of the present disclosure, a flat type of memory cell structure is provided having one or more intermediate dielectric layers and/or one or more control gate layers that do not wrap around the charge storage regions. In one embodiment, the intermediate dielectric material is cut or discontinuous in the row direction. The intermediate dielectric material is a high-K material in one example. Between the cut portions of the intermediate dielectric layer above the isolation regions, a second dielectric material is formed. This material has a lower K value than the high-K intermediate dielectric material formed directly over the floating gate. This can reduce parasitic interference and leakage between the control and floating gate. The high-K intermediate dielectric layer still provides enhanced coupling. In one example, the second dielectric material is recessed, allowing

**10**

the metal control gate layer to extend below the upper surface of the intermediate dielectric layer. This achieves a flat type cell device, while also providing a partial wrap-around for the control gate. Metal control gates may be provided to improve coupling between the control gates and floating gates where the control gate does not wrap around the floating gate.

[0030] In accordance with one embodiment, air gaps are introduced in the column (bit line) and/or row (word line) direction to form isolation between closely spaced components in the memory structure. Air gaps can decrease parasitic interferences between neighboring floating gates, neighboring control gates and/or between neighboring floating and control gates. Air gaps can include various material compositions and need not correspond to atmospheric air. For example, concentrations of elemental gases may vary in the air gap regions. An air gap is simply a void where no solid material is formed in the semiconductor structure.

[0031] Figure 6 is a flowchart describing a method of fabricating non-volatile storage with air gap isolation in accordance with one embodiment. Figures 7A-7O are orthogonal cross-sectional views of one example of a non-volatile memory array that can be fabricated according to the method in Figure 6. The described embodiment is exemplary only and its precise form should not be taken as limiting the disclosure. The exact materials, dimensions and order of processing may vary according to the requirements of a given implementation. It is noted that the dimensions of the various features are not necessarily drawn to scale.

**[0032]** At step 502, initial processing is performed to prepare a substrate for memory fabrication. One or more wells (e.g., a triple well) are typically formed in the substrate prior to forming a layer stack over the substrate surface. For example, a p-type substrate may be used. Within the p-type substrate, an n-type well may be created and within the n-type well a p-type well may be created.

11

Various units of a memory array may be formed within individual p-type wells. The well(s) can be implanted and annealed to dope the substrate. A zero layer formation step may also precede well formation.

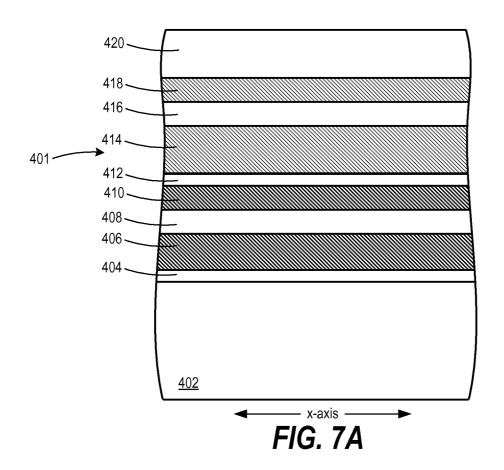

[0033] At step 504, an initial layer stack is formed over the substrate surface. Figure 7A is a cross-sectional view along the x-axis in the row or word line direction of a memory array 400 showing a layer stack 401 formed over the surface of a substrate 402. In this example, layer stack 401 includes a tunnel dielectric layer (TDL) 404, a charge storage layer (CSL) 406, an intermediate dielectric layer (IDL) 408, a first control gate layer 410, a second control gate layer 412, a sacrificial layer (SL) 414 and hard masking layer(s) (HML) 416, 418 and 420. It is noted that a layer may be said to be over another layer when one or more layers are between the two layers as well as when the two layers are in direct contact.

[0034] The tunnel dielectric layer 404 is a thin layer of oxide (e.g., SiO<sub>2</sub>) grown in one embodiment, although different materials and processes can be used. Chemical vapor deposition (CVD) processes, metal organic CVD processes, physical vapor deposition (PVD) processes, atomic layer deposition (ALD) processes, thermal oxidation or other suitable techniques can be used. In one example, the tunnel oxide layer is formed to a thickness of about 8 nanometers (nm). Although not shown, one or more high voltage gate dielectric regions may be formed at a peripheral circuitry region before or after forming the tunnel dielectric layer. The high voltage gate dielectric regions may be formed with a larger thickness (e.g., 30-40nm) than the tunnel dielectric layer.

[0035] The charge storage layer is a polysilicon floating gate layer in one embodiment. The vertical dimension (with respect to the substrate surface) or thickness of the charge storage layer can vary by embodiment. In one example, the charge storage layer has a vertical dimension of 30nm.

12

[0036] Dielectric charge storage materials, metal and non-metal nanostructures (e.g., carbon) can also be used for the layer of charge storage material. In one embodiment, the charge storage layer is a metal layer forming a charge-trap type floating gate layer. A thin metal charge-trap type floating gate can reduce concerns with ballistic charge programming issues that may arise with conventional polysilicon floating gates. In one embodiment, a metal floating gate layer is formed to a thickness of between 10nm and 20nm. In another embodiment, metal thicknesses greater than 20nm or less than 10nm are used. In one embodiment, the metal floating gate layer is a high work function metal. In one example, the metal is ruthenium. Other metals such as titanium, tungsten, tantalum, nickel, cobalt, etc., and their alloys (e.g., TiN, WN, TaN, NiSi, CoSi, WSix) can be used.

[0037] The intermediate dielectric layer 408 is a high-K dielectric material in one embodiment, which can provide enhanced control gate to floating gate coupling, while reducing charge transfer through the intermediate dielectric layer. In one embodiment, layer 408 has a dielectric constant greater than 3.9. It is not required that layer 408 have a high dielectric constant, although a high-K material will provide enhanced coupling which may be beneficial when the intermediate dielectric and control gate materials do not wrap around the charge storage regions as hereinafter described. The intermediate dielectric layer may contain a triple layer of oxide, nitride and oxide (ONO) sandwiched between high-K dielectric materials in one embodiment. High-k dielectric materials include, but are not limited to, hafnium oxides, aluminum oxides, zirconium oxides, and lanthanum oxides or laminate films or combination(s) of similar films.

**[0038]** The first control gate layer 410 and the second control gate layer 412 may include metals, polysilicon, silicides, barrier metals and combinations of these materials. In one embodiment, the first control gate layer is formed from polysilicon and the second control gate layer is formed from a barrier metal. By

13

way of example, the first and second control gate layers can include, respectively, (from layers to upper layers as move away from substrate surface): a barrier metal and metal; a barrier metal and polysilicon; a barrier metal and silicide (e.g., fully-silicided polysilicon (FUSI)); polysilicon and metal; or polysilicon and a barrier metal. Barrier metals may include, but are not limited to, titanium (Ti), titanium nitride (TiN), tungsten nitride (WN) and tantalum nitride (TaN) or a combination with related alloys that have a suitable electron work function. Metals may include, but are not limited to, tungsten (W), tungsten silicide (WSix) or other similar low resistivity metals. Silicides may include, but are not limited to, NiSi, CoSi. In one example, the control gate layer includes polysilicon that is subjected to silicidation after being etched into control gates so as to form a partially or fully-silicided (FUSI) control gate structures. The control gate layer may be formed by chemical vapor deposition (CVD), atomic layer deposition (ALD), plating, or other techniques.

[0039] In another embodiment, the initial layer stack does not include any control gate layers. One or more control gate layers can be provided after etching to form layer stack columns as described below.

**[0040]** The sacrificial layer 414 is a layer of nitride in one embodiment although other materials such as oxides can be used. In one example hard mask layer 416 is an oxide, hard mask layer 418 is polysilicon or nitride, and hard mask layer 420 is oxide. Other materials and combinations of those described may be used in other implementations.

[0041] The layer stack is patterned at step 506. The first pattern applied at step 506 corresponds to intended columns of the memory array and may be repetitive in the row or direction of the x-axis. The pattern also corresponds to intended active areas of the substrate which will be separated by isolation regions. In one embodiment, conventional photolithography using photoresist is used to pattern the hard mask layer 412 into strips elongated in the direction

14

of the y-axis with spaces between strips adjacent in the direction of the x-axis. The hard mask layer may be patterned into a first sub-pattern at the memory array area and one or more different sub-patterns at the peripheral circuitry areas to define active areas in the substrate with different dimensions in the direction of the x-axis. Spacer-assisted patterning, nano-imprint patterning, and other patterning techniques can also be used to form strips of the hard mask layer at reduced features sizes. The pattern, repetitive in the second or row direction, may define a first direction of etching to form columns of the targeted memory array.

[0042] After forming the pattern, the layer stack and substrate are etched at step 508 using the pattern formed at step 506. The layer stack is etched into layer stack columns and the substrate is etched into active areas which underlie the columns and isolation regions which separate the active areas. The term layer stack is used to refer to the layers formed over the substrate throughout processing. Thus, layer stack 401 may refer to the collection of layer stack columns that result from etching the initial layer stack.

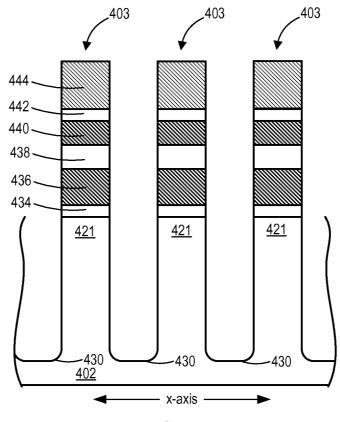

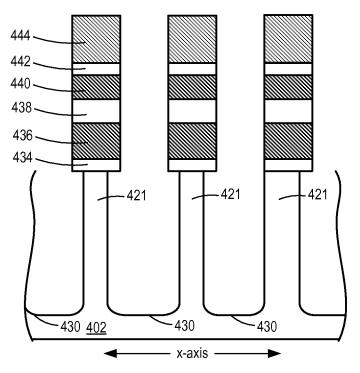

[0043] Figure 7B depicts the memory array after etching in one example. Etching forms layer stack columns 403 that are elongated in the direction of the y-axis with spaces therebetween in the direction of the x-axis. Each layer stack column 403 includes a tunnel dielectric strip (TDS) 434, a charge storage strip (CSS) 436, an intermediate dielectric strip (IDS) 438, a first control gate strip 440, a second control gate strip 442 and a sacrificial strip (SS) 444. The hard mask strips are removed after etching. Etching continues into substrate 402 to form isolation regions 430 which are separated by active areas 421. In one example, the depth of the isolation regions in the substrate is 200nm Various depths can be used, for example, ranging from 180-220nm in one embodiment. In one embodiment, reactive ion etching is used with various combinational etch chemistries to etch the different layers. Any suitable etch process(es) can be used.

15

[0044] At step 510, the active areas underlying the layer stack columns are slimmed, in effect increasing the row dimension of the isolation regions. Figure 7C depicts the results of step 510 in one example. Horizontal etching of the silicon substrate in the trenches will recess the active areas laterally. A dry or wet etch process, selective to silicon may be used. In another embodiment, oxidation may be used to consume a portion of the substrate to widen the isolation regions.

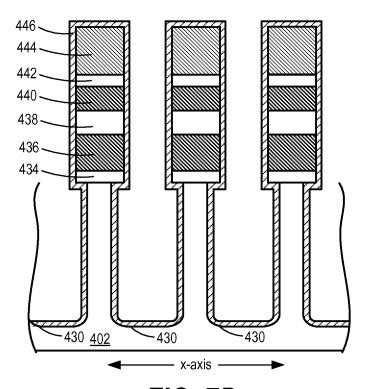

[0045] At step 512, a dielectric liner is formed along the exposed surfaces of the isolation regions in the substrate and along the exposed surfaces of the layer stack columns. Figure 7D depicts the results of step 512 in one embodiment. A thin dielectric liner 446 coats the vertical sidewalls of the layer stack columns as well as the vertical sidewalls and lower surface of the isolation regions. In one embodiment, the liner is a high-temperature oxide (HTO) formed using a deposition process. Different thicknesses of the liner may be used. In one example, the liner has a thickness of 4nm or less. In other examples, larger thicknesses may be used.

[0046] At step 514, the isolation regions and spaces between adjacent layer stack columns are filled with a sacrificial dielectric material. In one example, the dielectric liner is formed from a first dielectric material and a second, different dielectric material is used for the sacrificial material to fill the isolation regions. The second material may be formed with an etch selectivity that permits etching the second dielectric material without etching the first dielectric material. The sacrificial material is also etched back at step 514 so that its upper surface is below that of the upper surface of the layer stack columns. The amount of etch back may vary by embodiment. Timed etch processes may be used.

[0047] Figure 7E depicts the memory array after forming and etching back a sacrificial dielectric material in one embodiment. The sacrificial film is formed

16

in the remaining portions of the isolation regions and also the spaces between layer stack columns. In one embodiment, the sacrificial material 448 is a spin on dielectric (SOD) having a high etch selectivity with respect to the liner 446. In one example, the sacrificial film is a borosilicate glass (BSG) or other type of oxide. In another example, a spin-on-carbon can be used. Other materials can also be used such as polysilicon, silicon nitride (SiN) or an undensified polysilazane (PSZ) such as a PSZ-based inorganic spin-on-glass (SOG) material. The sacrificial film can be chosen for a high etch selectivity with respect to the liner so that it etches at a faster rate than the liner. A high etch selectivity of material 448 to material 446 can be achieved by skipping anneals. By not annealing sacrificial material 448, or by not annealing sacrificial material 448 to the same degree as liner 446, a high etch selectivity between layer 448 and liner 446 may be obtained.

[0048] The etch back of material 448 causes a tapered shape to portions of liner 446 lining the sidewalls of the layer stack strips. Material 448 is etched back so that its upper surface is at the level of the lower surface of the intermediate dielectric strips 438 in this example. In another embodiment, material 448 is etched back to the level of the upper surface of the intermediate dielectric strips 438. Material 448 may be etched back more or less than to these levels. Etching material 448 to the level of the lower surface of the intermediate dielectric layer facilitates the placement of an additional coupling dielectric layer at about the same level as the intermediate dielectric layer.

[0049] At step 516, the spaces between layer stack columns that result from the etch back at step 514 are filled with a second coupling dielectric layer having a lower dielectric constant than that of the intermediate dielectric layer (first coupling dielectric layer). As will be described hereinafter, this second coupling dielectric layer will overlie the isolation regions and air gaps in the final device, providing some of the separation from the control gate to the charge storage region. With a high-k intermediate dielectric layer overlying the

**17**

charge storage region, this lower-k coupling dielectric layer overlying the isolation regions and air gaps can avoid parasitic capacitances that may result at the sharp edges where these materials meet.

**[0050]** Figure 7F depicts the results of step 516 in one embodiment. A second coupling dielectric layer is formed in the spaces shown in Figure 7E that remain between layer stack columns. Layer 450 fills the spaces and has been etched back or planarized (e.g., CMP) to create a flat surface with interleaving strips of the sacrificial layer. In one embodiment, the second dielectric coupling layer is a layer of high temperature oxide, similar to or the same as the liner 446. Other materials having a lower dielectric constant than the intermediate dielectric strips 438 can be used.

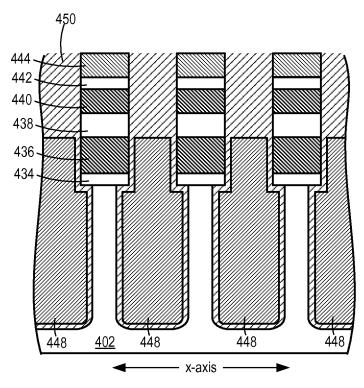

[0051] At step 518, the second dielectric coupling layer is recessed below the upper surface of the previously formed control gate strips. Figure 7G depicts the results of step 518 in one embodiment. Material 450 is etched back to form cap strips 451 having an upper surface at or near to the level of the upper surface of the intermediate dielectric strips 438. Material 450 may be etched back by different amounts. The amount of etch back affects the distance a later formed control gate material will extend vertically toward the substrate surface. The amount of etch back may be chosen for a desired amount of coupling while avoiding unnecessary fringing fields that may degrade performance. In one embodiment, the cap strips 451 have an upper surface that is below the upper surface of control gate strips 442, but above the upper surface of the intermediate dielectric strips 438.

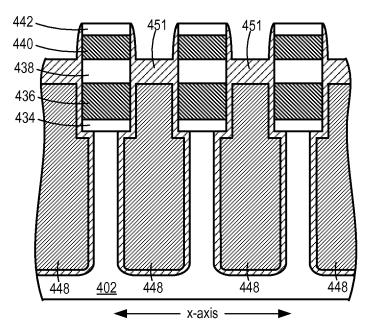

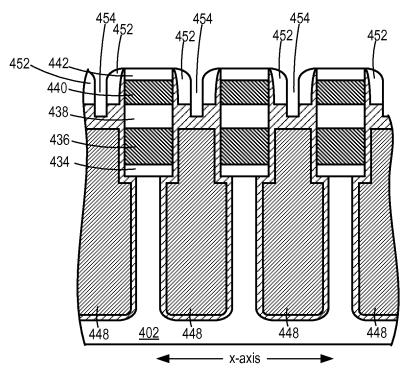

[0052] As shown in Figure 7G, the distance between the upper surface of the strips 451 and charge storage regions 436 is small at the corners where strips 451 meet liner 456. Accordingly, one embodiment includes forming spacers at step 520. Figure 7H depicts the results of step 520 in one embodiment. Spacers 452 are formed along the exposed surfaces of the liner material 446 coating the

18

sidewalls of control gate strips 442 and 440. If the liner material 446 has been removed from these sidewalls, spacers 452 can be formed directly on any exposed sidewalls of the control gate strips. Spacers 452 can be formed by depositing (e.g., ALD) an oxide and etching it back in one embodiment so that spaces 454 remain between adjacent spacers, lining the opposing sidewalls of adjacent layer stack columns. In one embodiment, the material of spacers 452 has a lower dielectric constant, similar to the second coupling dielectric material formed at step 516. In another embodiment, the spacers are a high-K dielectric. As shown in Figure 7G, an overetch is used when etching back the material to form spacers 452 to form vertical recesses or indentions in the cap strips.

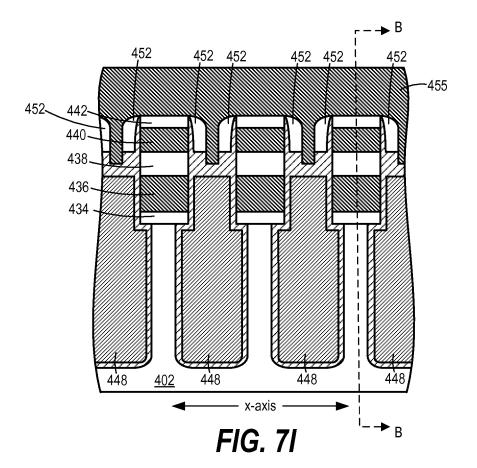

[0053] After forming the spacers, a third control gate layer 455 is formed at step 522. In one embodiment, the control gate layer formed at step 522 is the first control gate layer that is applied. Figure 7I depicts the results of step 522 in one embodiment. The third control gate layer 455 contacts the second control gate strips 442, forming a vertically continuous control gate structure with strips 442 and 440 over each charge storage region. This third control gate layer may remain continuous in the row direction to from word lines. The third control gate layer fill spaces 454 so that the control gate extends vertically toward the substrate surface. In this example, the spaces 454 extend some distance below the upper surface of strips 451 due to the notch formed at step 520. Thus, the control gate layer extends vertically to below the upper surface of the intermediate dielectric strips 438. In other embodiments, the control gate layer may extend further toward the substrate surface or further away from the substrate surface. The amount of vertical control gate extension will influence both the amount of coupling and the potential for parasitic capacitances and fringing fields so that the distance may vary by implementation. In one embodiment, the third control gate layer is polysilicon. In another embodiment, the third control gate layer is a metal as described above.

19

[0054] At step 524, a second pattern is applied over the layer stack. The second pattern is formed for etching orthogonal to the direction of etching using the first pattern. The second pattern may include strips of hard mask material and/or photoresist, or other suitable mask, that are elongated in the row direction along the x-axis with a spacing between strips in the column direction along the y-axis. The pattern may define the gate length for the charge storage region of each memory cell and column dimension for each control gate structure.

[0055] Figure 7J is a cross-sectional view taken along line B--B of Figure 7I, depicting the device in cross-section in the direction of the y-axis or bit line direction. Figure 7J depicts the results of step 524 after forming the second pattern. Over the control gate layer is formed one or more hard mask layers 456. Strips 457 of photoresist or another patterning agent are applied.

[0056] At step 526, the layer stack is etched into layer stack rows. In one embodiment, etching the layer stack includes etching strips 434 of the tunnel dielectric material. In another embodiment, the tunnel dielectric is not etched. Reactive ion or another suitable etch process may be used. One or more etch chemistries may be applied to etch through the various layers of the stack.

[0057] Figures 7K and 7L depict the results of step 526 in one embodiment. Figure 7L is a perspective view of the device depicting the point in processing shown in the cross-sectional view of Figure 7K. Etching continues until reaching the tunnel dielectric layer in this example. In other examples, etching may continue until reaching the substrate surface. In another example, some portion of the tunnel dielectric layer is etched without completely etching through the layer. Etching forms layer stack rows 411. The hard mask material is etched into hard mask strips (HMS) 476, the third control gate layer is etched into third control gate strips 475, the intermediate dielectric strips 442 are etched into intermediate dielectric regions 472, the second control gate strips

20

440 are etched into second control gate regions 470, the first control gate strips 438 are etched into first control gate regions 468 and the charge storage strips 436 are etched into charge storage regions 466. Etching through the cap strips will also form individual cap regions or caps 453. A plurality of these caps 453 will extend over each isolation region where the rows are formed. After etching the layer stack into rows an implant process can be performed to create n+source/drain regions. In one embodiment, the n+ source/drain regions are created by implanting n-type dopants such as arsenic or phosphorus into the p-well.

[0058] At step 528, a protective sidewall film is formed along the vertical sidewalls of the layer stack rows. Different films may be used in different implementations. In one example, an oxide can be deposited and etched back to form sidewall films along the sidewalls of the individual layer stack rows. Traditional spacer formation processes may be used. Figure 7M depicts a protective sidewall spacer 480 that is formed along the sidewall (extending in the word line direction) of one of the layer stack rows 411. The sidewall spacer 480 is depicted as only partially extending along the sidewall in the x-axis direction for clarity. The spacer will actually extend fully along the length of each layer stack row. Each layer stack row will include two sidewall spacers 480, with one on each vertical sidewall.

[0059] The sidewall spacers 480 will protect each layer stack row during subsequent processing steps. In one embodiment, the spacer material is chosen for its etch selectivity with respect to the sacrificial film 448. In this manner, the sacrificial film can later be removed in processes where the layer stack sidewalls are not exposed to the various etch chemistries. This will protect the sidewalls of the control gate layer and charge storage layer as well as the various dielectric layers.

21

**[0060]** Figure 7M illustrates that etching back the sidewall spacer material exposes the sacrificial material 448 in trenches 430. A portion of an upper surface of the sacrificial material 448 corresponding to the spaces between adjacent layer stack rows is exposed. This allows subsequent processing to remove the sacrificial material in order to form an air gap in the bit line direction.

**[0061]** At step 530, the sacrificial material is removed from the isolation regions 430 and from between the layer stack columns 403. A wet etch process is used in one embodiment, although other suitable etch processes (e.g., dry) can be used. As earlier described, the etch process is selective for the sacrificial film so that it can be removed without removing the liner 446 in the isolation regions and the sidewalls spacers 480 on the layer stack rows.

[0062] Figure 7N depicts the array after removing sacrificial material 448 from isolation regions 430 and the areas between layer stack columns. Etching removes the film from the isolation regions, beginning with the material exposed by etching back spacers 480. Etching will also remove the sacrificial material in the isolation regions that underlies the layer stack rows. Etching will begin attacking the sacrificial material from the side under the rows after etching proceeds vertically down into the isolation regions. Etching will further continue behind the sidewall spacers 480 to remove portions of the sacrificial material that extend above the isolation regions and substrate surface. Etching removes the material between charge storage regions 466 and intermediate dielectric regions 468 that are adjacent in the word line or row direction. Some of the sacrificial material may not be removed. Thus, removing the sacrificial material does not necessarily have to include removing all of the material.

**[0063]** Removing the sacrificial material forms bit line air gaps 482. The air gaps are elongated in the column direction in the isolation regions 430. The air gaps extend from below the surface of the substrate to the level of the upper

22

surface of the intermediate dielectric regions. The caps 453 define an upper endpoint for portions of the air gap underlying the layer stack rows. Word line air gaps, as described hereinafter, may be formed with a capping layer that can serve as an upper endpoint of the portion of the bit line air gap not underlying a layer stack row. As earlier described, the air gaps may have different vertical dimensions in different embodiments. The air gaps may not extend as deep within isolation regions and may not extend as far above the substrate surface. Further, the air gaps may be formed exclusively within the isolation regions or exclusively between adjacent layer stack columns in other examples.

**[0064]** At step 532 word line air gaps are formed at least partially in the spaces between the layer stack rows. The word line air gaps extend in the x-axis or row direction between adjacent layer stack rows to provide electrical isolation or shielding between elements of adjacent layer stack rows. The vertical dimension and column dimension (along y-axis) of the air gaps can vary to meet the particular requirements of a given implementation.

[0065] Figure 70 depicts the results of step 520 in an example where a capping layer 484 is formed over the layer stack rows using a non-conformal deposition process. By using a non-conformal deposition process, material 484 will be deposited unequally at the upper portion of the layer stack rows. Material 484 quickly accumulates, meeting at a location over the space between rows to form word line air gaps 486. Material 484 extends vertically toward the substrate surface along spacers 480. In this example, material 484 extends along spacers 480 to a level between the upper surface and lower surface of the third control gate strips 475. Because material 484 accumulates faster along spacers 480, the upper endpoint of air gap 486 extends to about the level of the upper surface of the third control gate strips 475. This distance for the air gap, extending above the control gate layers, may decrease or eliminates any fringing fields.

23

[0066] In one embodiment, layer 484 is an oxide but other materials such as nitrides may used in other implementations. Although not shown, some portion of dielectric 484 may enter the space between charge storage regions. This portion of the dielectric may raise the lower endpoint of the air gap in the spaces between rows, but by only a small amount. However, a very nonconformal oxide will quickly grow together to seal off the spaces as shown without a substantial decrease in the vertical dimension of the air gap. Although referred to as "air" gaps, the elemental composition of the air can include many different materials. Thus, the term "air" should not be construed as having any particular elemental composition. The air gaps are voids, where no solid material is formed. Any number and type of gases may be in the gaps 486. Although not shown, a polishing step can be applied to form individual caps from layer 484. The capping layer 484 can be polished to form plugs sealing the word line air gaps 486. A planar surface can be created for further processing steps.

[0067] At step 534, front end processing is completed. In one example, step 534 may include interconnecting the floating gate and control gate regions of select and peripheral circuitry transistors. Peripheral gate connections can be formed using vias or contact holes, etc. to form contacts to individual gate regions or to connect multiple transistors to a common control line. The select gate transistors can have their floating gate regions shorted to the control gate regions to form a single gate structure. Array connections can also be patterned and formed. After forming contacts, etc., further backend processing to form metal layers, etc. to complete the device according to known techniques can be performed. Various backend processes can be performed to finalize fabrication of the array. For example, a passivation dielectric layer can be deposited, followed by forming metal conductive lines and vias to connect the lines with source and drain regions at the end of the memory cell strings, etc.

24

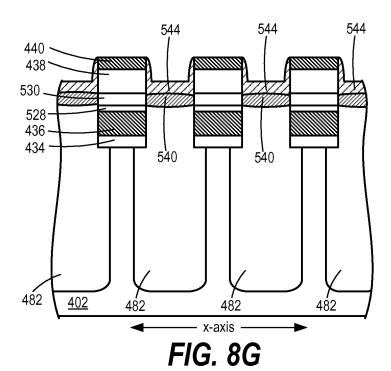

[8900] Figures 8A-8L are orthogonal cross-sectional views depicting a variation to the fabrication process in Figures 6 and 7A-7O for forming a flatcell type memory structure in one embodiment. A layer stack 401 is again formed as shown in Figure 8A. In this embodiment, the layer stack includes the tunnel dielectric layer 404, and three charge storage layers 406, 508 and 510. In this example, layer 406 is polysilicon, layer 508 is a barrier metal and layer 510 is a metal. Various materials as described above can be used for the metal layer 510 and barrier metal layer 508, such as Ta and TaN, respectively. In another embodiment, a single metal or barrier metal layer can be used in place of the two metal layers 510 and 508. In one embodiment, an anneal can be performed to cause the silicon in layer 406 to react with the metal (e.g., Ta) in layer 508 to form a metal silicide. This creates a very good ohmic contact between polysilicon and the above lying metal. This will enable the three layers to function well as a single charge storage region. The high-dielectric constant intermediate dielectric layer 408 is formed, followed by the first control gate layer 410, sacrificial layer 414 and hard mask layer 416. In this embodiment, the first control gate layer 410 may be polysilicon and the second control gate layer 412 omitted as shown. Other combinations could be used, for example, including a polysilicon first control gate layer and a barrier metal second control gate layer as earlier described.

[0069] The initial layer stack is patterned and etched as shown in Figure 8B. Etching proceeds to the substrate but does not include etching the substrate in the initial layer stack as with the embodiment in Figure 8B. The layer stack columns 403 include tunnel dielectric strips 434, first charge storage strips 436, second charge storage strips 528, third charge storage strips 530, intermediate dielectric strips 438, first control gate strips 440 and sacrificial strips 444. Sidewall spacers 520 are formed along the vertical sidewalls of each layer stack row as shown. The sidewalls spacers are formed by depositing and etching back a TEOS layer in one embodiment but other dielectric materials may be

25

used. After forming the sidewall spacers 520, the isolation regions 430 are etched as shown in Figure 8C, and their row dimension in the x-axis direction is increased as shown in Figure 8D.

[0070] Figure 8E depicts the formation of bridge strips 540 that are selectively grown on the third charge storage strips 530. Selective growth processes can be used to selectively grow an oxide or other dielectric capping material along the vertical sidewalls of the third charge storage strips. Although the bridge material is shown as exclusively growing on the polysilicon third charge strips to form bridge strips 540, some amount of material may grown at other locations. Thus, the term selective does not exclude the growth or formation of the material at other locations. However, selective growth does refer to a faster growth rate or accumulation at one location or region than another. In one embodiment, the bridge strips may be grown on all charge storage layers or a single charge storage layer if a single layer is provided. Additionally, the bridge strips may only be grown on a polysilicon charge storage material in one embodiment. The polysilicon may be the lowest charge storage layer as with strips 436 or may be the highest charge storage layer as with strips 530.

[0071] As shown, the bridge material, shown here as strips 540, is grown on the sidewalls of the third charge storage strips and meets to form a continuous cap in the x-axis direction. The bridge strips 540 overlie air in the isolation regions, defining bit line air gaps 482 as earlier described. In this embodiment, the bridge strips will define a portion of the upper endpoint for the bit line air gaps, rather than the capping strips formed of the second coupling dielectric. The bridge layer may also form on the sidewalls and lower surface of the isolation regions, the sidewalls of the tunnel dielectric strips 434 and sacrificial strips 444 or along portions of these surfaces. Nevertheless, the selective growth on the polysilicon material allows the bridge layer to form more quickly on the sidewalls of the charge storage strips. Thus, although the bridge layer

26

may also grow in the isolation regions, it accumulates faster along the sidewalls of the charge storage material. Accordingly, the bridge layer meets over isolation regions 430, sealing or providing an upper cap over them (at least temporarily) so that an air gap 482 is formed in the isolation regions. In another embodiment, the bridge material can be selectively grown upon all portions of the layer stack columns above the third charge storage strips. A polishing or etch back process could be performed to create a planar layer stack surface in such an example. In either case, the bridge layer will accumulate faster along the layer stack columns so that before the regions are completely filled, the bridge layer meets to provide an upper surface for the isolation regions and air gaps. The oxide will "pinch off" or form a solid bridge or dielectric cap at the upper portion of the trench.

In one embodiment, the bridge layer is an oxide formed using a [0072] high-density plasma chemical vapor deposition process (HDP-CVD). During deposition, a TEOS and ozone (O<sub>3</sub>) mixture may applied at a first ratio to form a nucleation layer on the modified surface(s). The nucleation layer may form on untreated surfaces as well, but not as quickly such that a greater quantity accumulates as on the modified surfaces. After forming the nucleation layer, the ratio of TEOS to O<sub>3</sub> may be modified to promote selective growth of the oxide on the modified surfaces of the charge storage strips. For example, the amount of ozone may be increased. Other deposition techniques that will deposit oxide faster on a polysilicon charge storage layer than on a single crystal silicon substrate can be used. In one embodiment, the third charge storage strips 530 are polysilicon and are subjected to surface modification after forming the third charge storage layer or after being etched into strips (e.g., where the first control gate layer is metal) to promote the selective growth of an HDP oxide, although this is not required. Ion implanation or other techniques may be used to introduce dopants (e.g., n-type impurities). In another

27

embodiment, a catalyst layer may be applied over the column sidewalls or any portion thereof to selectively grow the cap strips 540.

[0073] After forming bridge strips 540, the remaining spaces between layer stack columns are filled with a dielectric fill material, such as an oxide, which can be polished or etched back to form a planar upper surface of the layer stack and cap strips 451 of the fill material as shown in Figure 8F. These cap strips, like cap strips 451 in Figures 7A-7O, are formed using a lower dielectric constant material, such as HTO, than the dielectric constant of the intermediate dielectric material.

[0074] Using the sacrificial strips 444 as a mask, an etch back is then performed to recess the fill material as shown in 8G. Recessing the fill material 544 creates spacers along a portion of the intermediate dielectric strips 438 and the first control gate strips 440 as shown. This etch back is similar to the etch back of material 450 to form strips 451 in Figure 7G to permit a later formed control gate layer to extend vertically toward the substrate surface at a level lower than that of the previously formed first control gate strips 440. In this example, the etch back recesses an upper surface of each cap strip 451 to a level below the level of the upper surface of the intermediate dielectric strips 438.

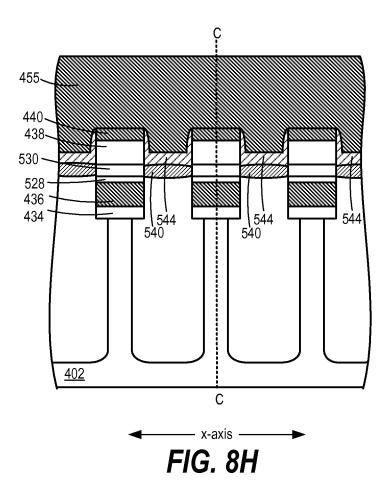

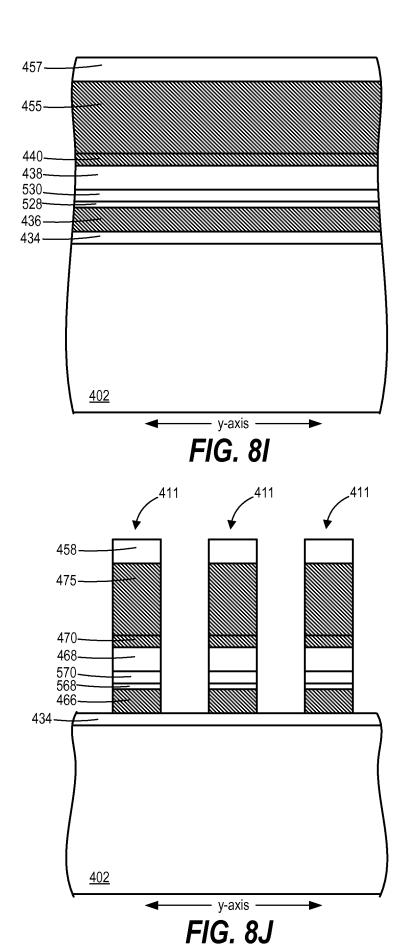

[0075] After etching back the fill strips 544, a second control gate layer 455 is formed as shown in Figure 8H. In this example, additional spacers 452 as formed in Figure 7H are not formed. However, these spacers may be added as earlier described. The second control gate layer 455 is a metal in one embodiment. A barrier metal layer may also be used or polysilicon.

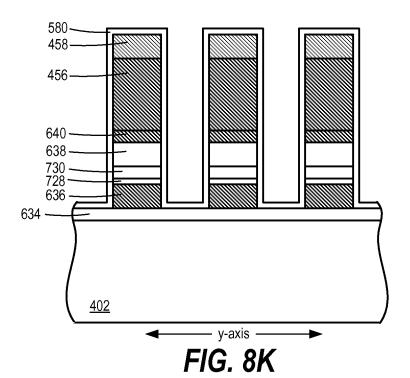

**[0076]** Figure 8I is a cross-sectional view along line C--C of Figure 8H after forming a hard mask layer 457 over (e.g., SiN) the layer stack. The layer stack is then patterned and etched into layer stack rows 411 as shown in Figure 8J. Each row includes a hard mask strip 458, a second control gate strip 475, a first control gate region 470, an intermediate dielectric region 468, a third charge

28

storage region 570, a second charge storage region 568 and a first charge storage region 466. A liner 580 is then formed along the vertical sidewalls of the layer stack rows as shown in Figure 8K. The liner is an oxide, formed using an ALD process in one example. The liner overlies the upper surface of each layer stack row and the exposed upper surface of the tunnel dielectric strips between layer stack rows. Figure 8L depicts the device after depositing a capping layer 484 to define word line air gaps 486 as earlier described.

that can be fabricated using one or more embodiments of the disclosed technology. As one example, a NAND flash EEPROM is described that is partitioned into 1,024 blocks. The data stored in each block can be simultaneously erased. In one embodiment, the block is the minimum unit of cells that are simultaneously erased. In each block, in this example, there are 8,512 columns that are divided into even columns and odd columns. The bit lines are also divided into even bit lines (BLE) and odd bit lines (BLO). Figure 9 shows four memory cells connected in series to form a NAND string. Although four cells are shown to be included in each NAND string, more or less than four can be used (e.g., 16, 32, or another number). One terminal of the NAND string is connected to a corresponding bit line via a first select transistor (also referred to as a select gate) SGD, and another terminal is connected to c-source via a second select transistor SGS.

[0078] During read and programming operations for memory cells of one embodiment, 4,256 memory cells are simultaneously selected. The memory cells selected have the same word line (e.g. WL2-i), and the same kind of bit line (e.g. even bit lines). Therefore, 532 bytes of data can be read or programmed simultaneously. These 532 bytes of data that are simultaneously read or programmed form a logical page. Therefore, in this example, one block can store at least eight pages. When each memory cell stores two bits of data (e.g. a multi-level cell), one block stores 16 pages. In another embodiment, a

29

memory array is formed that utilizes an all bit-line architecture such that each bit line within a block is simultaneously selected, including those adjacent in the x-direction.

[0079] In other embodiments, the bit lines are not divided into odd and even bit lines. Such architectures are commonly referred to as all bit line architectures. In an all bit line architecture, all the bit lines of a block are simultaneously selected during read and program operations. Memory cells along a common word line and connected to any bit line are programmed at the same time. In other embodiments, the bit lines or block can be broken up into other groupings (e.g., left and right, more than two groupings, etc.).

[0800]Figure 10 illustrates a non-volatile storage device 1010 that may include one or more memory die or chips 1012. Memory die 1012 includes an array (two-dimensional or three dimensional) of memory cells 1000, control circuitry 1020, and read/write circuits 1030A and 1030B. In one embodiment, access to the memory array 1000 by the various peripheral circuits is implemented in a symmetric fashion, on opposite sides of the array, so that the densities of access lines and circuitry on each side are reduced by half. The read/write circuits 1030A and 1030B include multiple sense blocks 1300 which allow a page of memory cells to be read or programmed in parallel. The memory array 1000 is addressable by word lines via row decoders 1040A and 1040B and by bit lines via column decoders 1042A and 1042B. In a typical embodiment, a controller 1044 is included in the same memory device 1010 (e.g., a removable storage card or package) as the one or more memory die 1012. Commands and data are transferred between the host and controller 1044 via lines 1032 and between the controller and the one or more memory die 1012 via lines 1034. One implementation can include multiple chips 1012.

[0081] Control circuitry 1020 cooperates with the read/write circuits 1030A and 1030B to perform memory operations on the memory array 1000. The

30

control circuitry 1020 includes a state machine 1022, an on-chip address decoder 1024 and a power control module 1026. The state machine 1022 provides chip-level control of memory operations. The on-chip address decoder 1024 provides an address interface to convert between the address that is used by the host or a memory controller to the hardware address used by the decoders 1040A, 1040B, 1042A, and 1042B. The power control module 1026 controls the power and voltages supplied to the word lines and bit lines during memory operations. In one embodiment, power control module 1026 includes one or more charge pumps that can create voltages larger than the supply voltage.

[0082] In one embodiment, one or any combination of control circuitry 1020, power control circuit 1026, decoder circuit 1024, state machine circuit 1022, decoder circuit 1042A, decoder circuit 1042B, decoder circuit 1040A, decoder circuit 1040B, read/write circuits 1030A, read/write circuits 1030B, and/or controller 1044 can be referred to as one or more managing circuits.

[0083] Figure 11 is a block diagram of an individual sense block 1300 partitioned into a core portion, referred to as a sense module 1280, and a common portion 1290. In one embodiment, there will be a separate sense module 1280 for each bit line and one common portion 1290 for a set of multiple sense modules 1280. In one example, a sense block will include one common portion 1290 and eight sense modules 1280. Each of the sense modules in a group will communicate with the associated common portion via a data bus 1272. For further details, refer to U.S. Patent Application Publication 2006/0140007, which is incorporated herein by reference in its entirety.

[0084] Sense module 1280 comprises sense circuitry 1270 that determines whether a conduction current in a connected bit line is above or below a predetermined threshold level. In some embodiments, sense module 1280 includes a circuit commonly referred to as a sense amplifier. Sense module 1280 also includes a bit line latch 1282 that is used to set a voltage condition on

31

the connected bit line. For example, a predetermined state latched in bit line latch 1282 will result in the connected bit line being pulled to a state designating program inhibit (e.g., Vdd).

[0085] Common portion 1290 comprises a processor 1292, a set of data latches 1294 and an I/O Interface 1296 coupled between the set of data latches 1294 and data bus 1220. Processor 1292 performs computations. For example, one of its functions is to determine the data stored in the sensed memory cell and store the determined data in the set of data latches. The set of data latches 1294 is used to store data bits determined by processor 1292 during a read operation. It is also used to store data bits imported from the data bus 1220 during a program operation. The imported data bits represent write data meant to be programmed into the memory. I/O interface 1296 provides an interface between data latches 1294 and the data bus 1220.

[0086] During read or sensing, the operation of the system is under the control of state machine 1022 that controls the supply of different control gate voltages to the addressed cell. As it steps through the various predefined control gate voltages corresponding to the various memory states supported by the memory, the sense module 1280 may trip at one of these voltages and an output will be provided from sense module 1280 to processor 1292 via bus 1272. At that point, processor 1292 determines the resultant memory state by consideration of the tripping event(s) of the sense module and the information about the applied control gate voltage from the state machine via input lines 1293. It then computes a binary encoding for the memory state and stores the resultant data bits into data latches 1294. In another embodiment of the core portion, bit line latch 1282 serves double duty, both as a latch for latching the output of the sense module 1280 and also as a bit line latch as described above.

32

[0087] It is anticipated that some implementations will include multiple processors 1292. In one embodiment, each processor 1292 will include an output line (not depicted in Figure 12) such that each of the output lines is wired-OR'd together. In some embodiments, the output lines are inverted prior to being connected to the wired-OR line. This configuration enables a quick determination during the program verification process of when the programming process has completed because the state machine receiving the wired-OR line can determine when all bits being programmed have reached the desired level. For example, when each bit has reached its desired level, a logic zero for that bit will be sent to the wired-OR line (or a data one is inverted). When all bits output a data 0 (or a data one inverted), then the state machine knows to terminate the programming process. In embodiments where each processor communicates with eight sense modules, the state machine may (in some embodiments) need to read the wired-OR line eight times, or logic is added to processor 1292 to accumulate the results of the associated bit lines such that the state machine need only read the wired-OR line one time.

[0088] During program or verify, the data to be programmed is stored in the set of data latches 1294 from the data bus 1220. The program operation, under the control of the state machine, comprises a series of programming voltage pulses (with increasing magnitudes) applied to the control gates of the addressed memory cells. Each programming pulse is followed by a verify process to determine if the memory cell has been programmed to the desired state. Processor 1292 monitors the verified memory state relative to the desired memory state. When the two are in agreement, processor 1292 sets the bit line latch 1282 so as to cause the bit line to be pulled to a state designating program inhibit. This inhibits the cell coupled to the bit line from further programming even if it is subjected to programming pulses on its control gate. In other embodiments the processor initially loads the bit line latch 1282 and the sense circuitry sets it to an inhibit value during the verify process.

33

[0089] Data latch stack 1294 contains a stack of data latches corresponding to the sense module. In one embodiment, there are 3-5 (or another number) data latches per sense module 1280. In one embodiment, the latches are each one bit. In some implementations (but not required), the data latches are implemented as a shift register so that the parallel data stored therein is converted to serial data for data bus 1220, and vice versa. In one preferred embodiment, all the data latches corresponding to the read/write block of m memory cells can be linked together to form a block shift register so that a block of data can be input or output by serial transfer. In particular, the bank of read/write modules is adapted so that each of its set of data latches will shift data in to or out of the data bus in sequence as if they are part of a shift register for the entire read/write block.

[0090] Additional information about the read operations and sense amplifiers can be found in (1) United States Patent 7,196,931, "Non-Volatile Memory And Method With Reduced Source Line Bias Errors,"; (2) United States Patent 7,023,736, "Non-Volatile Memory And Method with Improved Sensing,"; (3) U.S. Patent Application Pub. No. 2005/0169082; (4) U.S. Patent 7,196,928, "Compensating for Coupling During Read Operations of Non-Volatile Memory," and (5) United States Patent Application Pub. No. 2006/0158947, "Reference Sense Amplifier For Non-Volatile Memory," published on July 20, 2006. All five of the immediately above-listed patent documents are incorporated herein by reference in their entirety.

[0091] Various features and techniques have been presented with respect to the NAND flash memory architecture. It will be appreciated from the provided disclosure that implementations of the disclosed technology are not so limited. By way of non-limiting example, embodiments in accordance with the present disclosure can provide and be used in the fabrication of a wide range of semiconductor devices, including but not limited to logic arrays, volatile

34

memory arrays including SRAM and DRAM, and non-volatile memory arrays including both the NOR and NAND architecture.

[0092] In one embodiment, a non-volatile memory is provided that includes a first column of non-volatile storage elements including a first set of charge storage regions arranged in a column direction and separated from a surface of a substrate by a tunnel dielectric. The first set of charge storage regions are separated from a first set of optional control gate regions by a first set of intermediate dielectric regions overlying the first set of charge storage regions. The memory includes a second column of non-volatile storage elements adjacent to the first column of non-volatile storage elements in a row direction. The second column includes a second set of charge storage regions that are separated from the surface of the substrate by a tunnel dielectric and that are separated from an optional second set of control gate regions by a second set of intermediate dielectric regions overlying the first set of charge storage regions. The memory includes an isolation region in the substrate between an active area underlying the first column of non-volatile storage elements and an active area underlying the second column of non-volatile storage elements and a set of dielectric caps formed over the isolation region between the first column of nonvolatile storage elements and the second column of non-volatile storage elements. Each cap extends in the row direction between corresponding intermediate dielectric regions of the first column and the second column that are adjacent in the row direction and have a lower dielectric constant than a dielectric constant of the intermediate dielectric regions.

[0093] In one embodiment, a method of fabricating non-volatile storage using a substrate is provided that includes forming a first layer stack column and a second layer stack column where each layer stack column includes a tunnel dielectric strip, a charge storage strip, and an intermediate dielectric strip. The first layer stack column overlies a first active area of the substrate and the second layer stack column overlies a second active of the substrate. The

35

method further includes forming an isolation region in the substrate between the first active area and the second active area after forming the first layer stack column and the second layer stack column, forming a dielectric strip over the isolation region that extends between the intermediate dielectric strip in the first layer stack column and the intermediate dielectric strip in the second layer stack column. The dielectric cap strip has a lower dielectric constant than a dielectric constant of the intermediate dielectric strips. The method further includes forming a control gate layer after forming the dielectric strip over the isolation region.

**[0094]** In one embodiment, a method of fabricating non-volatile storage is provided that includes forming a first layer stack column and a second layer stack column that each includes a tunnel dielectric strip, a charge storage strip, an intermediate dielectric strip, and a first control gate strip. The first layer stack column overlies a first active area of the substrate and the second layer stack column overlies a second active of the substrate. An isolation is formed in the substrate between the first active area and the second active area and a sacrificial material is formed at least partially in the isolation region and at least partially occupying a space between the first layer stack column and the second layer stack column. The method includes forming a dielectric cap strip over the sacrificial material that extends between the intermediate dielectric strip in the first layer stack column and the intermediate dielectric strip in the second layer stack column. The dielectric cap strip has a lower dielectric constant than a dielectric constant of the intermediate dielectric strips.

[0095] In one embodiment, a method of fabricating non-volatile storage is provided that includes forming a first layer stack column and a second layer stack column that each include a tunnel dielectric strip, a charge storage strip, an intermediate dielectric strip, and a first control gate strip. The first layer stack column overlies a first active area of the substrate and the second layer stack column overlies a second active of the substrate. An isolation region is

36

formed in the substrate between the first active area and the second active area. The method includes selectively growing a cap between the first layer stack column and the second layer stack column that extends vertically along at least a portion of the charge storage strip of the first column and the charge storage strip of the second column. The method includes forming a dielectric strip over the cap between the first layer stack column and the second layer stack column that extends vertically along at least a portion of the intermediate dielectric strip of the first layer stack column and the intermediate dielectric strip of the second layer stack column. The method includes forming a bit line air gap in the isolation region having an upper endpoint defined at least partially by the cap.

[0096] The foregoing detailed description has been presented for purposes of illustration and description. It is not intended to be exhaustive or to limit the subject matter claimed herein to the precise form(s) disclosed. Many modifications and variations are possible in light of the above teachings. The described embodiments were chosen in order to best explain the principles of the disclosed technology and its practical application to thereby enable others skilled in the art to best utilize the technology in various embodiments and with various modifications as are suited to the particular use contemplated. It is intended that the scope of the invention be defined by the claims appended hereto.

**37**

### **CLAIMS**

What is claimed is:

1. A non-volatile memory, comprising:

a first column of non-volatile storage elements including a first set of charge storage regions arranged in a column direction and separated from a surface of a substrate by a tunnel dielectric and a first set of intermediate dielectric regions overlying the first set of charge storage regions;

a second column of non-volatile storage elements adjacent to the first column of non-volatile storage elements in a row direction, the second column including a second set of charge storage regions separated from the surface of the substrate by a tunnel dielectric and a second set of intermediate dielectric regions overlying the second set of charge storage regions;

an isolation region in the substrate between an active area underlying the first column of non-volatile storage elements and an active area underlying the second column of non-volatile storage elements; and