(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6534602号

(P6534602)

(45) 発行日 令和1年6月26日(2019.6.26)

(24) 登録日 令和1年6月7日(2019.6.7)

(51) Int.Cl.

H05K 1/02 (2006.01)

H05K 3/00 (2006.01)

F 1

H05K 1/02

H05K 3/00R

P

請求項の数 10 (全 23 頁)

(21) 出願番号 特願2015-224688 (P2015-224688)

(22) 出願日 平成27年11月17日 (2015.11.17)

(65) 公開番号 特開2017-92411 (P2017-92411A)

(43) 公開日 平成29年5月25日 (2017.5.25)

審査請求日 平成30年9月6日 (2018.9.6)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100105957

弁理士 恩田 誠

(74) 代理人 100068755

弁理士 恩田 博宣

(72) 発明者 北城 奈津子

長野県長野市小島田町80番地 新光電氣

工業 株式会社 内

(72) 発明者 雪入 裕司

長野県長野市小島田町80番地 新光電氣

工業 株式会社 内

最終頁に続く

(54) 【発明の名称】配線基板、半導体装置及び配線基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

最外層の絶縁層と、

前記絶縁層を厚さ方向に貫通し、文字及び記号を含む特定の形状に形作られた第1貫通孔と、

前記第1貫通孔内に形成された第1ビア配線と、

前記第1ビア配線と同一の材料からなり、前記第1ビア配線と接続され、前記絶縁層の上面に形成された導電パターンと、

前記導電パターンの上面よりも前記第1貫通孔の底面側に凹むように前記第1ビア配線の上面に形成された凹部と、

前記凹部を充填し、前記導電パターン及び前記第1ビア配線を被覆するように前記絶縁層の上面に形成された保護絶縁層と、を有し、

前記第1ビア配線と前記導電パターンと前記凹部と前記保護絶縁層とは、前記特定の形状として識別可能に構成された識別マークを構成し、

前記凹部の内側面は曲面であり、

前記第1ビア配線上に形成された前記保護絶縁層は、前記導電パターン上に形成された前記保護絶縁層よりも厚く形成されていることを特徴とする配線基板。

## 【請求項 2】

前記凹部の底面は、前記絶縁層の上面よりも前記第1貫通孔の底面側の位置に形成されていることを特徴とする請求項1に記載の配線基板。

**【請求項 3】**

前記導電パターンは、前記識別マークが形成された領域全体に形成されていることを特徴とする請求項 1 又は 2 に記載の配線基板。

**【請求項 4】**

前記第 1 貫通孔は、前記絶縁層の上面側から前記第 1 貫通孔の底面に向かうに連れて開口幅が小さくなるテーパ状に形成されていることを特徴とする請求項 1 ~ 3 のいずれか一項に記載の配線基板。

**【請求項 5】**

前記保護絶縁層は、ソルダレジスト層であることを特徴とする請求項 1 ~ 4 のいずれか一項に記載の配線基板。

10

**【請求項 6】**

前記特定の形状は、7 セグメント式文字であることを特徴とする請求項 1 ~ 5 のいずれか一項に記載の配線基板。

**【請求項 7】**

前記絶縁層の下層に形成された第 1 配線パターン及び第 2 配線パターンと、

前記絶縁層を厚さ方向に貫通して前記第 1 配線パターンの上面の一部を露出する前記第 1 貫通孔と、

前記絶縁層を厚さ方向に貫通して前記第 2 配線パターンの上面の一部を露出する第 2 貫通孔と、

前記第 2 貫通孔を充填する第 2 ピア配線と、

20

前記第 2 ピア配線を介して前記第 2 配線パターンと電気的に接続され、前記絶縁層の上面に形成された配線層と、を有し、

前記保護絶縁層は、前記配線層の少なくとも一部を接続パッドとして露出させるための開口部を有し、

前記第 1 貫通孔は、前記第 2 貫通孔よりも体積が大きくなるように形成されていることを特徴とする請求項 1 ~ 6 のいずれか一項に記載の配線基板。

**【請求項 8】**

請求項 7 に記載の配線基板と、

前記接続パッドと電気的に接続され、前記配線基板に実装された半導体チップと、

を有することを特徴とする半導体装置。

30

**【請求項 9】**

最外層の絶縁層を形成する工程と、

前記最外層の絶縁層を厚さ方向に貫通し、平面形状が文字及び記号を含む特定の形状に形作られた第 1 貫通孔を形成する工程と、

前記第 1 貫通孔に対応する平面形状の凹部が上面に形成された第 1 ピア配線を前記第 1 貫通孔内に形成するとともに、前記第 1 ピア配線と同一の材料からなり、前記第 1 ピア配線と接続される導電パターンを前記絶縁層の上面に形成する工程と、

前記凹部を充填し、前記導電パターン及び前記第 1 ピア配線を被覆する保護絶縁層を前記絶縁層の上面に形成し、前記第 1 ピア配線と前記導電パターンと前記凹部と前記保護絶縁層とから構成され、前記特定の形状として識別可能に構成された識別マークを形成する工程と、を有し、

40

前記凹部は、前記導電パターンの上面よりも前記第 1 貫通孔の底面側に凹むように形成され、

前記凹部の内側面は、曲面に形成され、

前記第 1 ピア配線上に形成された前記保護絶縁層は、前記導電パターン上に形成された前記保護絶縁層よりも厚く形成されることを特徴とする配線基板の製造方法。

**【請求項 10】**

第 1 配線パターン及び第 2 配線パターンを被覆する最外層の絶縁層を形成する工程と、

前記絶縁層を厚さ方向に貫通して前記第 1 配線パターンの上面の一部を露出し、平面形状が文字及び記号を含む特定の形状に形作られた第 1 貫通孔を形成するとともに、前記絕

50

縁層を厚さ方向に貫通して前記第2配線パターンの上面の一部を露出する第2貫通孔を形成する工程と、

前記第1貫通孔に対応する平面形状の凹部が上面に形成された第1ビア配線を前記第1貫通孔内に形成し、前記第1ビア配線と同一の材料からなり、前記第1ビア配線と接続される導電パターンを前記絶縁層の上面に形成するとともに、前記第2貫通孔を充填する第2ビア配線を形成し、前記第2ビア配線を介して前記第2配線パターンと電気的に接続される配線層を前記絶縁層の上面に形成する工程と、

前記配線層の少なくとも一部を接続パッドとして露出させる開口部を有し、前記凹部を充填するとともに、前記導電パターン及び前記第1ビア配線を被覆する保護絶縁層を前記絶縁層の上面に形成し、前記第1ビア配線と前記導電パターンと前記凹部と前記保護絶縁層とから構成され、前記特定の形状として識別可能に構成された識別マークを形成する工程と、を有し、

前記第1貫通孔と前記第2貫通孔とは、レーザ加工法により形成され、

前記第1貫通孔は、前記第2貫通孔よりも体積が大きくなるように形成され、

前記凹部は、前記絶縁層の上面よりも前記第1貫通孔の底面側に凹むように形成され、前記凹部の内側面は、曲面に形成され、

前記第1ビア配線上に形成された前記保護絶縁層は、前記導電パターン上に形成された前記保護絶縁層よりも厚く形成されることを特徴とする配線基板の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

本発明は、配線基板、半導体装置及び配線基板の製造方法に関するものである。

##### 【背景技術】

##### 【0002】

近年では、半導体チップ搭載用等に用いられる配線基板は、小型化、高密度化が進み、複数の単位配線基板（単位基板）が設けられた大判の配線基板の形態で取り扱われている（例えば、特許文献1，2参照）。

##### 【0003】

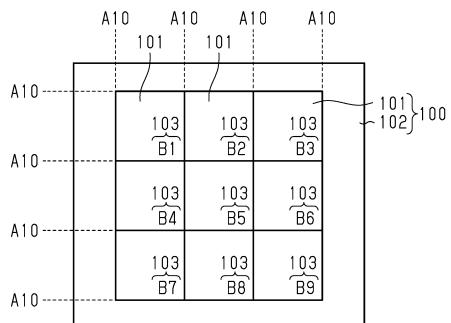

図16に示すように、大判の配線基板100は、複数（ここでは、9個）の単位配線基板101と、それら複数の単位配線基板101を囲む外枠102とを有している。配線基板100は、切断位置A10において切断されることにより個片化され、個々の単位配線基板101となる。

##### 【0004】

複数の単位配線基板101には、平面視したときに特定の文字や記号として識別される識別マーク103が形成されている。図16に示した複数の単位配線基板101には、平面視したときに「B1」～「B9」として識別される識別マーク103が形成されている。この識別マーク103は、単位配線基板101の位置情報やロット情報などを示している。以下に、識別マーク103の形成方法の一例について説明する。

##### 【0005】

最上層の絶縁層に貫通孔を形成した後、その貫通孔の内面にめっき層を形成し、それら貫通孔及びめっき層によって識別マーク103を形成する。このとき、貫通孔は、平面視したときに特定の形状（例えば、「B1」）として識別可能なように形作られて形成される。

##### 【先行技術文献】

##### 【特許文献】

##### 【0006】

【特許文献1】特開2009-194321号公報

【特許文献2】特開2005-252155号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

10

20

30

40

50

**【0007】**

ところで、上述した配線基板100（単位配線基板101）では、識別マーク103の視認性の向上が望まれており、この点においてなお改善の余地があった。

**【課題を解決するための手段】****【0008】**

本発明の一観点によれば、最外層の絶縁層と、前記絶縁層を厚さ方向に貫通し、文字及び記号を含む特定の形状に形作られた第1貫通孔と、前記第1貫通孔内に形成された第1ビア配線と、前記第1ビア配線と同一の材料からなり、前記第1ビア配線と接続され、前記絶縁層の上面に形成された導電パターンと、前記導電パターンの上面よりも前記第1貫通孔の底面側に凹むように前記第1ビア配線の上面に形成された凹部と、前記凹部を充填し、前記導電パターン及び前記第1ビア配線を被覆するように前記絶縁層の上面に形成された保護絶縁層と、を有し、前記第1ビア配線と前記導電パターンと前記凹部と前記保護絶縁層とは、前記特定の形状として識別可能に構成された識別マークを構成し、前記凹部の内側面は曲面であり、前記第1ビア配線上に形成された前記保護絶縁層は、前記導電パターン上に形成された前記保護絶縁層よりも厚く形成されている。10

**【発明の効果】****【0009】**

本発明の一観点によれば、識別マークの視認性を向上させることができるという効果を奏する。

**【図面の簡単な説明】****【0010】**

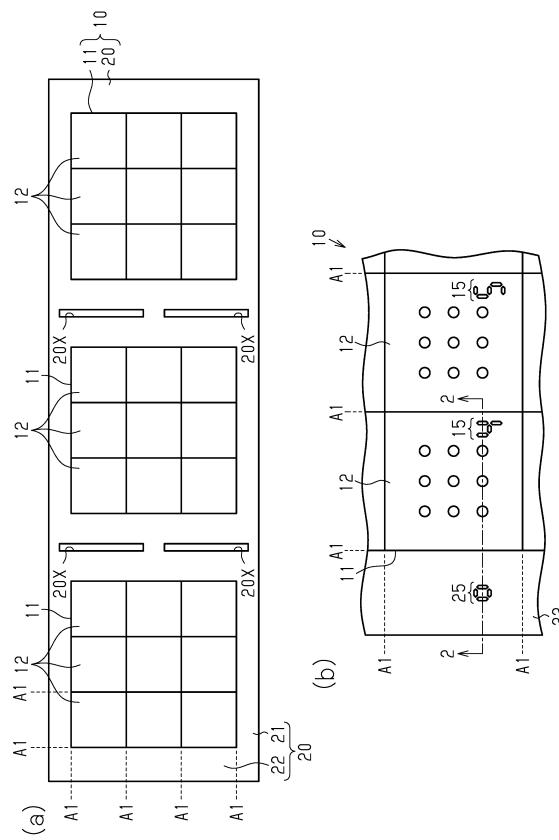

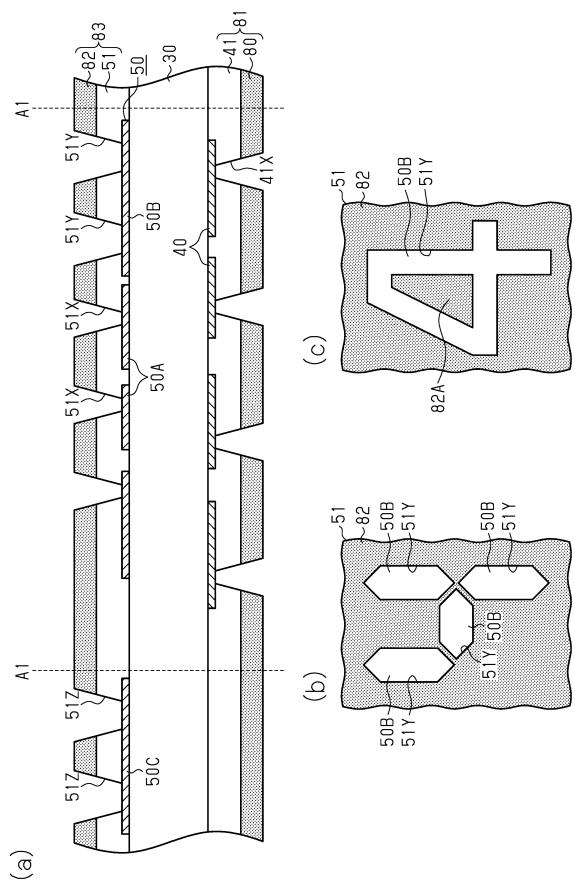

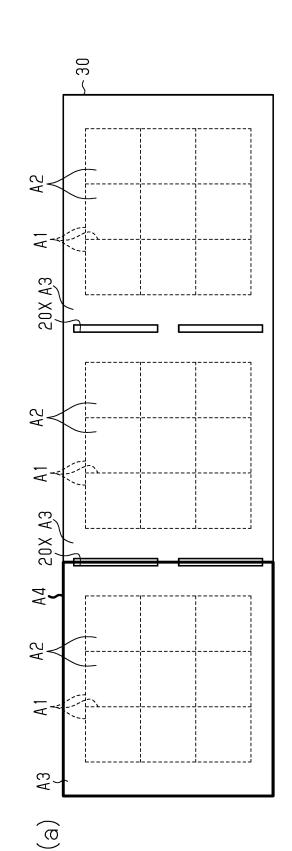

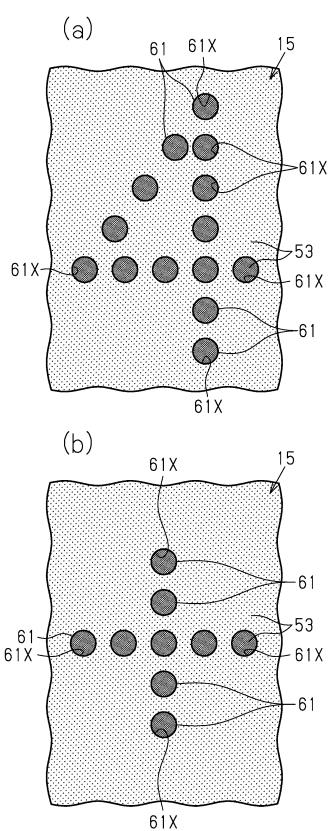

【図1】(a)は、一実施形態の配線基板を示す概略平面図、(b)は、(a)に示した配線基板の一部を拡大した拡大平面図。

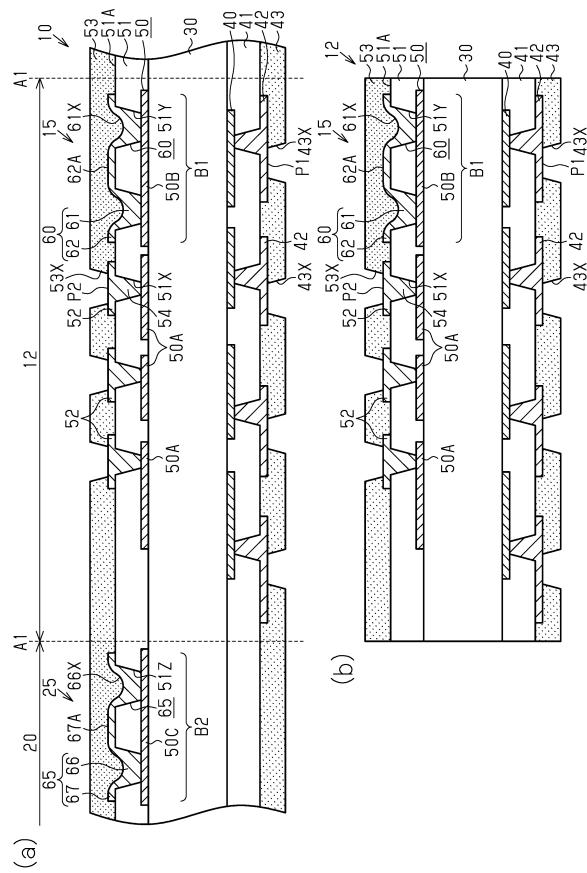

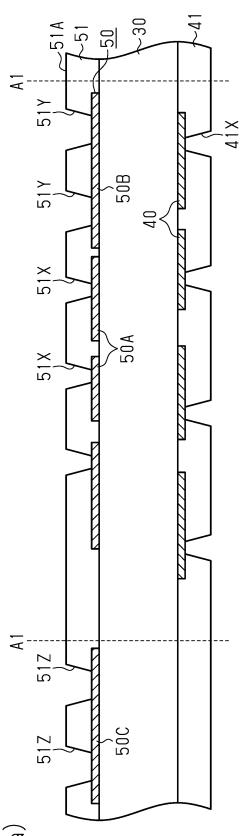

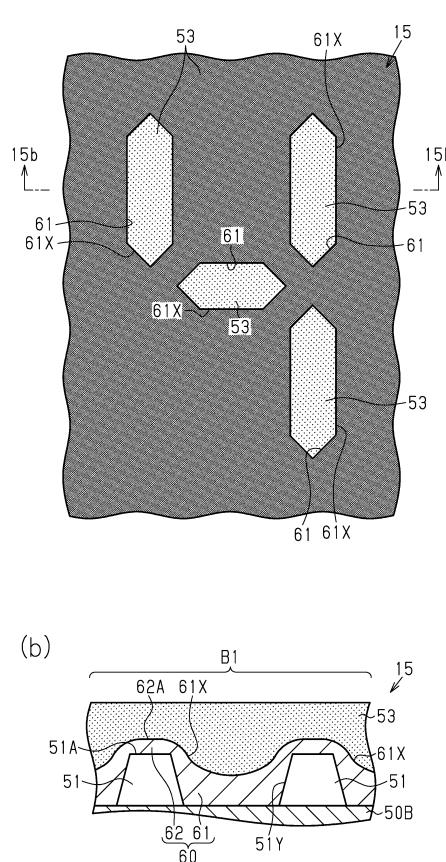

【図2】(a)は、一実施形態の配線基板を示す概略断面図(図1(b)における2-2断面図)、(b)は、一実施形態の配線基板を示す概略断面図。

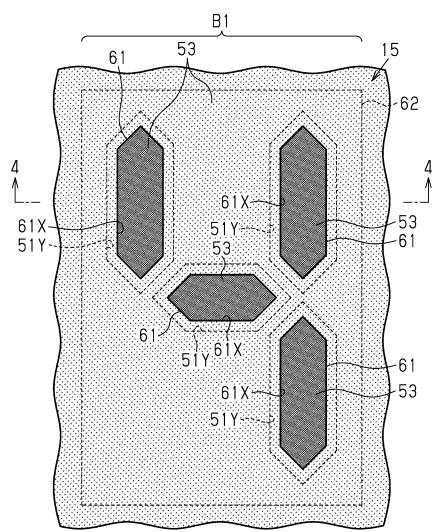

【図3】一実施形態の識別マークを示す概略平面図。

【図4】一実施形態の識別マークを示す概略断面図。

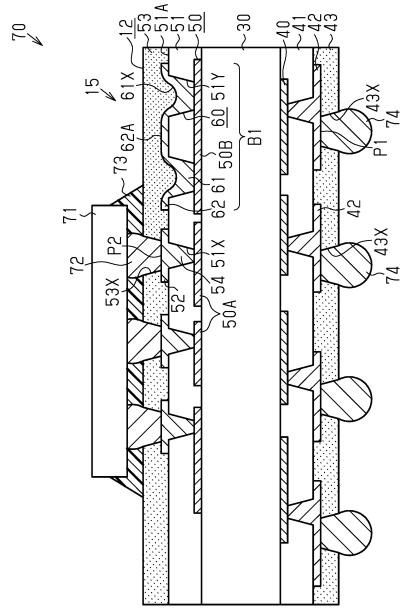

【図5】一実施形態の半導体装置を示す概略断面図。

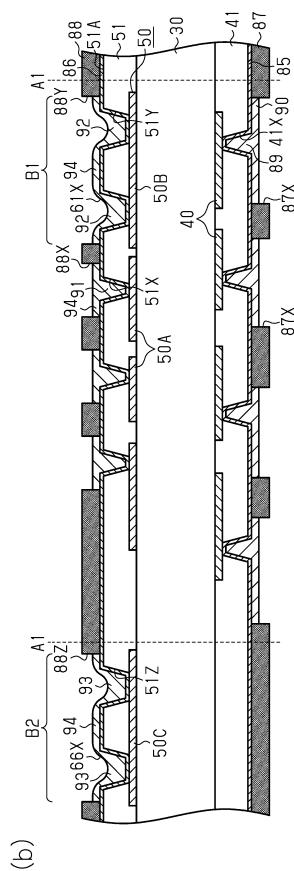

【図6】(a)は、一実施形態の識別マークの作用を示す説明図、(b)は、従来の識別マークの問題点を示す説明図。30

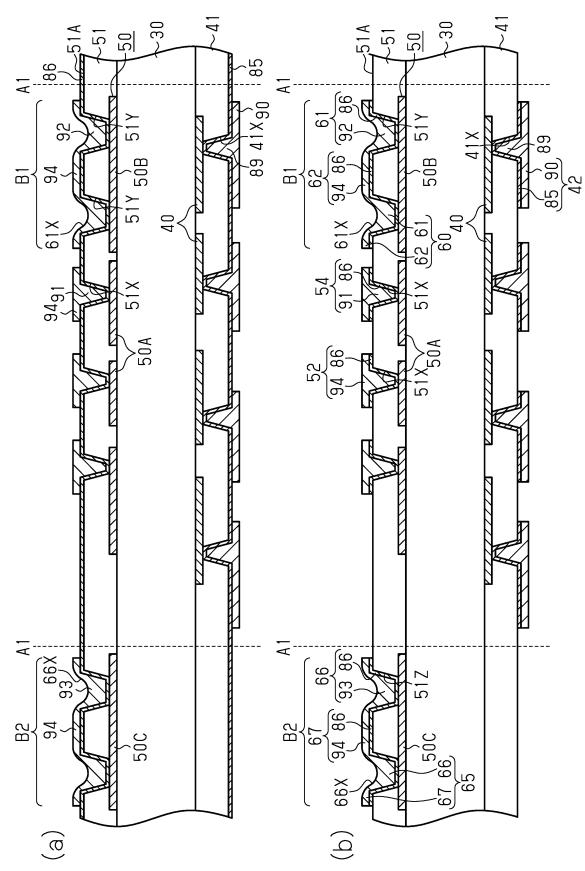

【図7】(a), (b)は、一実施形態の配線基板の製造方法を示す概略断面図。

【図8】(a)は、一実施形態の配線基板の製造方法を示す概略断面図、(b)は、一実施形態の配線基板の製造方法を示す概略平面図、(c)は、参考例の配線基板の製造方法を示す概略平面図。

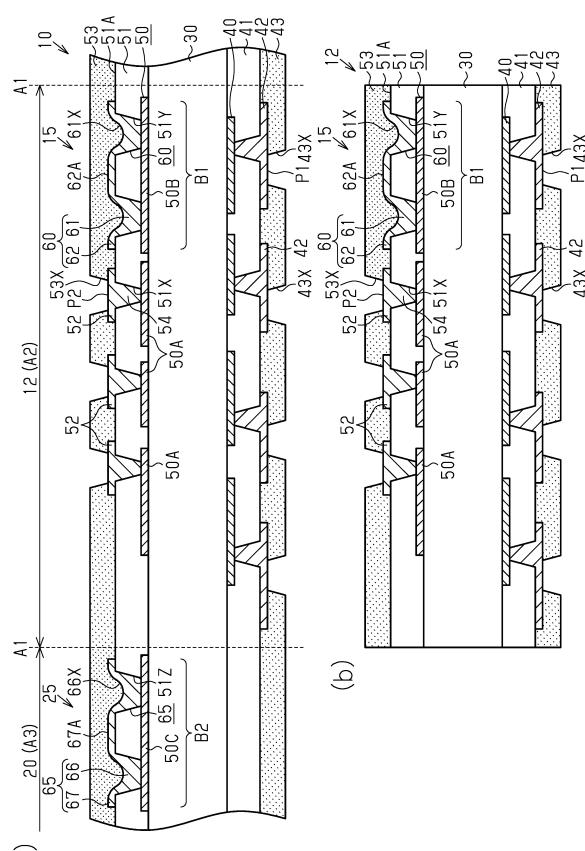

【図9】(a), (b)は、一実施形態の配線基板の製造方法を示す概略断面図。

【図10】(a), (b)は、一実施形態の配線基板の製造方法を示す概略断面図。

【図11】(a), (b)は、一実施形態の配線基板の製造方法を示す概略断面図。

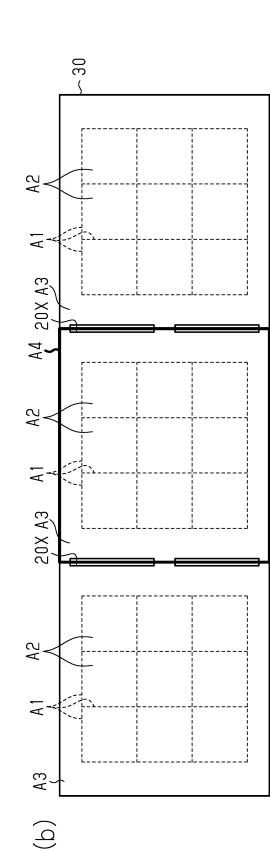

【図12】(a), (b)は、一実施形態の配線基板の製造方法を示す概略平面図。

【図13】(a), (b)は、一実施形態の配線基板の製造方法を示す概略断面図。

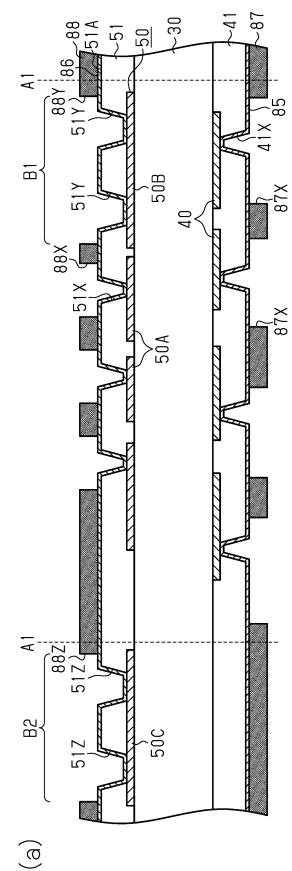

【図14】(a), (b)は、変形例の識別マークを示す概略平面図。40

【図15】(a)は、変形例の識別マークを示す概略平面図、(b)は、変形例の識別マークを示す概略断面図(図15(a)における15b-15b断面図)。

【図16】従来の配線基板を示す概略平面図。

**【発明を実施するための形態】****【0011】**

以下、一実施形態について添付図面を参照して説明する。

なお、添付図面は、特徴を分かりやすくするために便宜上特徴となる部分を拡大して示している場合があり、各構成要素の寸法比率などが実際と同じであるとは限らない。また、断面図では、各部材の断面構造を分かりやすくするために、一部の部材のハッチングを梨地模様に代えて示し、一部の部材のハッチングを省略している。50

**【0012】**

まず、図1～図4に従って、配線基板10の構造について説明する。

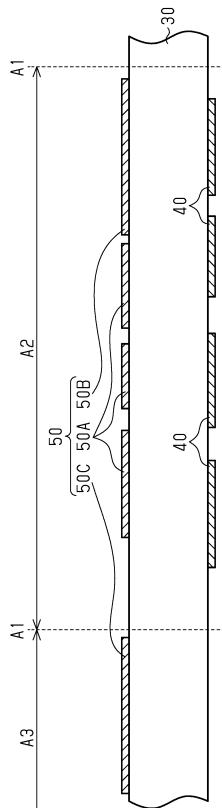

図1(a)に示すように、配線基板10は、例えば、シート状の配線基板である。配線基板10は、例えば、平面視略矩形状に形成されている。配線基板10は、複数(ここでは、3つ)のブロック11と、複数のブロック11を囲むように形成された外枠20とを有している。複数のブロック11は互いに分離して画定されている。各ブロック11には、単位配線基板(配線基板)12がマトリクス状(ここでは、3×3)に複数個連設して設けられている。配線基板10は、切断位置A1において切断されることにより個片化され、個々の単位配線基板12となる。なお、外枠20は、個片化の際に廃棄される部分である。

10

**【0013】**

ここで、本明細書において、「平面視」とは、対象物を図2等の鉛直方向(図2の上下方向)から視ることを言い、「平面形状」とは、対象物を図2等の鉛直方向から視た形状のことを言う。

**【0014】**

図1(b)に示すように、各配線基板12には、平面視したときに文字及び記号を含む特定の形状として識別される識別マーク15が形成されている。図示の例では、ブロック11の中央左側の配線基板12には、「4」として識別される識別マーク15が形成され、その右隣の配線基板12には、「5」として識別される識別マーク15が形成されている。なお、図1(b)において図示されていない配線基板12にも同様の識別マーク15が形成されている。この識別マーク15は、例えば、個片化後の配線基板12に何らかの不具合が生じた場合などに利用される。例えば、不具合が生じた配線基板12が、配線基板10のどの位置に配置されていたかを特定することができるため、その不具合が配線基板10における特定の場所に依存して生じたものか、あるいは製造工程中の特定のプロセスに関連して生じたものか等を解析することができる。このような識別マーク15としては、例えば、識別番号、座標情報、ロット番号、シリアル番号、図面番号、製品名称や認識マーク(アライメントマーク)などが挙げられる。

20

**【0015】**

図1(a)に示すように、外枠20は、長手方向(図中の左右方向)に延在される一対のレール部21と、幅方向(図中の上下方向)に延在される一対のレール部22とを有している。隣接するブロック11間に形成されたレール部22には、幅方向に沿って延びる複数(ここでは、2個)のスリット20Xが形成されている。スリット20Xは、例えば、レール部22(配線基板10)の表面と裏面との間に貫通形成されている。

30

**【0016】**

図1(b)に示すように、レール部22には、平面視したときに文字及び記号を含む特定の形状として識別される識別マーク25が形成されている。図示の例では、ブロック11の左側に形成されたレール部22に、「」として識別される識別マーク25が形成されている。なお、図1(b)では、レール部22に1つの識別マーク25のみを図示したが、実際にはレール部22には多数及び多種類の識別マーク25が形成されている。また、図1(b)では図示を省略しているが、レール部21(図1(a)参照)にも多数及び多種類の識別マーク25が形成されている。このような識別マーク25としては、例えば、識別マーク15と同様に、ブロック11の識別番号、座標情報、ロット番号、シリアル番号、図面番号、製品名称や認識マークなどが挙げられる。

40

**【0017】**

図2(a)に示すように、配線基板10は、基板本体30を有している。基板本体30としては、例えば、コア基板、コア基板を有するコア付きビルドアップ基板、コア基板を有していないコアレス基板を用いることができる。

**【0018】**

基板本体30の下面には、配線層40と、絶縁層41と、配線層42と、ソルダレジスト層(保護絶縁層)43とが順に積層されている。また、基板本体30の上面には、配線

50

層 50 と、絶縁層 51 と、配線層 52 と、ソルダレジスト層（保護絶縁層）53 とが順に積層されている。

#### 【 0019 】

ここで、配線層 40, 42, 50, 52 の材料としては、例えば、銅 (Cu) や銅合金を用いることができる。絶縁層 41, 51 の材料としては、例えば、エポキシ系樹脂やポリイミド系樹脂などの絶縁性樹脂、又はこれら樹脂にシリカ (SiO<sub>2</sub>) やアルミナ (Al<sub>2</sub>O<sub>3</sub>) 等のフィラーを混入した樹脂材を用いることができる。

#### 【 0020 】

配線層 40 は、基板本体 30 内の配線層や貫通電極を介して、配線層 50 と電気的に接続されている。絶縁層 41 は、配線層 40 を被覆するように、基板本体 30 の下面に形成されている。配線層 42 は、絶縁層 41 の下面に形成されている。配線層 42 は、絶縁層 41 を厚さ方向に貫通するビア配線を介して、配線層 40 と電気的に接続されている。

#### 【 0021 】

ソルダレジスト層 43 は、最下層の配線層 42 の一部を被覆するように、最下層の絶縁層 41 の下面に積層されている。ソルダレジスト層 43 には、配線層 42 の一部を外部接続用パッド P1 として露出させるための開口部 43X が形成されている。この外部接続用パッド P1 には、配線基板 12 をマザーボード等の実装基板に実装する際に使用される外部接続端子 74 (図 5 参照) が接続されるようになっている。すなわち、外部接続用パッド P1 が形成されている側 (下側) の面が外部接続端子面となる。

#### 【 0022 】

なお、必要に応じて、開口部 43X から露出する配線層 42 上に表面処理層を形成するようにしてもよい。表面処理層の例としては、金 (Au) 層、ニッケル (Ni) 層 / Au 層 (Ni 層と Au 層をこの順番で積層した金属層)、Ni 层 / パラジウム (Pd) 层 / Au 層 (Ni 層と Pd 層と Au 層をこの順番で積層した金属層) などを挙げることができる。これら Au 層、Ni 層、Pd 層としては、例えば、無電解めっき法により形成された金属層 (無電解めっき金属層) を用いることができる。また、Au 層は Au 又は Au 合金からなる金属層、Ni 層は Ni 又は Ni 合金からなる金属層、Pd 層は Pd 又は Pd 合金からなる金属層である。また、外部接続用パッド P1 の表面に、OSP (Organic Solderability Preservative) 処理などの酸化防止処理を施して表面処理層を形成するようにしてもよい。例えば、OSP 处理を施した場合には、外部接続用パッド P1 の表面に、アゾール化合物やイミダゾール化合物等の有機被膜による表面処理層が形成される。なお、開口部 43X から露出する配線層 42 (又は、配線層 42 上に表面処理層が形成されている場合には、その表面処理層) 自体を、外部接続端子としてもよい。

#### 【 0023 】

なお、ソルダレジスト層 43 の材料としては、例えば、フェノール系樹脂やポリイミド系樹脂などを主成分とする感光性の絶縁性樹脂を用いることができる。ソルダレジスト層 43 は、例えば、シリカやアルミナ等のフィラーを含有していてもよい。

#### 【 0024 】

一方、配線層 50 は、基板本体 30 の上面に形成されている。配線層 50 は、各配線基板 12 に実装される半導体チップ 71 (図 5 参照) と電気的に接続される配線パターン 50A と、識別マーク 15 が形成された領域 B1 に設けられた配線パターン 50B と、識別マーク 25 が形成された領域 B2 に設けられた配線パターン 50C とを有している。

#### 【 0025 】

絶縁層 51 は、配線層 50 (配線パターン 50A, 50B, 50C) を被覆するように、基板本体 30 の上面に形成されている。各配線基板 12 に位置する絶縁層 51 には、上面 51A から当該絶縁層 51 を厚さ方向に貫通して配線パターン 50A の上面の一部を露出する貫通孔 51X が形成されている。貫通孔 51X は、図 2 (a) において上側 (絶縁層 51 の上面 51A 側) から下側 (基板本体 30 側) に向かうに連れて径が小さくなるテーパ状に形成されている。例えば、貫通孔 51X は、上側の開口部の開口径が下側の開口部の開口径よりも大径となる略逆円錐台形状に形成されている。なお、配線パターン 50

10

20

30

40

50

A, 50B, 50Cの上面から絶縁層51の上面51Aまでの厚さは、例えば、10~50μm程度とすることができます。

#### 【0026】

各貫通孔51X内には、配線パターン50Aと配線層52とを電気的に接続するビア配線54が形成されている。ビア配線54は、例えば、貫通孔51X内に充填されている。配線層52は、絶縁層51の上面51Aに形成されている。配線層52は、例えば、ビア配線54と一緒に形成されている。なお、ビア配線54の材料としては、例えば、銅や銅合金を用いることができる。

#### 【0027】

ソルダレジスト層53は、最上層の配線層52の一部を被覆するように、最上層の絶縁層51の上面51Aに積層されている。ソルダレジスト層53には、配線層52の一部を接続パッドP2として露出させるための開口部53Xが形成されている。この接続パッドP2には、半導体チップ71(図5参照)のバンプ72がフリップチップ接合される。すなわち、接続パッドP2が形成されている上側の面がチップ搭載面になっている。なお、必要に応じて、開口部53Xから露出する配線層52上に表面処理層を形成するようにしてもよい。表面処理層の例としては、Au層、Ni層/Au層、Ni層/Pd層/Au層やOSP処理等による有機被膜などを挙げることができる。

10

#### 【0028】

ここで、ソルダレジスト層53の材料としては、例えば、半透明な材料を用いることができる。例えば、ソルダレジスト層53の材料としては、半透明な青緑色の材料を用いることができる。このようなソルダレジスト層53の材料としては、例えば、エポキシ系樹脂やアクリル系樹脂などの絶縁性樹脂に、所定の青緑色系顔料を含有した樹脂材を用いることができる。また、ソルダレジスト層53は、例えば、シリカやアルミナ等のフィラーを含有していてもよい。但し、絶縁性樹脂自体の外観色調により、識別マーク15のコントラストが強く、視認性に問題が無ければ、必ずしもソルダレジスト層53の材料として半透明な材料を用いなくてもよい。

20

#### 【0029】

配線基板10のチップ搭載面側には、識別マーク15と識別マーク25とが形成されている。以下に、識別マーク15, 25の構造について詳述する。

まず、識別マーク15及びその周辺の構造について詳述する。

30

#### 【0030】

図3に示すように、識別マーク15の平面形状は、特定の文字・記号(図示の例では、「4」)として識別可能のように形成されている。本例の識別マーク15は、7セグメント式文字の「4」として識別可能のように形成されている。すなわち、本例の識別マーク15は、7つの線分(セグメント)で1桁の数字を表わす7セグメント式表示によって表現された「4」として識別可能のように形成されている。

#### 【0031】

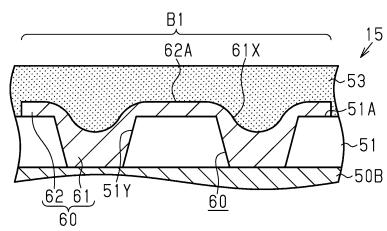

図2(a)に示すように、識別マーク15が形成された領域B1には、例えば、基板本体30の上面に配線パターン50Bがべた状に形成されている。配線パターン50Bは、領域B1全体に広がるようにべた状に形成されている。配線パターン50Bは、例えば、識別マーク15と平面視で重なる位置に、識別マーク15全体の平面形状よりも大きく形成されている。

40

#### 【0032】

領域B1に位置する絶縁層51には、上面51Aから当該絶縁層51を厚さ方向に貫通して配線パターン50Bの上面の一部を露出する貫通孔51Yが複数個形成されている。各貫通孔51Yは、図2(a)において上側(絶縁層51の上面51A側)から下側(貫通孔51Yの底面側)に向かうに連れて開口幅が小さくなるテーパ状に形成されている。各貫通孔51Yは、貫通孔51Xよりも体積が大きくなるように形成されている。例えば、各貫通孔51Yの平面形状は、貫通孔51Xの平面形状よりも大きく形成されている。

#### 【0033】

50

図3に示すように、複数の貫通孔51Yは、識別マーク15として識別される特定の文字・記号（ここでは、7セグメント式数字の「4」）を形作るように形成されている。詳述すると、図3に示した領域B1には、7セグメント式表示における各セグメント（線分）に対応する平面形状（ここでは、平面視略矩形状）に形成された貫通孔51Yが4つ形成されている。そして、4つの貫通孔51Yは、平面視したときの全体像が7セグメント式数字の「4」を形作るように形成されている。これら複数の貫通孔51Yは、互いに離間して形成されている。なお、各貫通孔51Yの幅は、例えば、50～200μm程度とすることができます。

#### 【0034】

図4に示すように、領域B1には、各貫通孔51Y内に形成されたピア配線61と、ピア配線61と接続され、絶縁層51の上面51Aに形成された導電パターン62とを有する導電層60が形成されている。10

#### 【0035】

各ピア配線61は、貫通孔51Yの一部を埋めるように形成されている。具体的には、各ピア配線61は、貫通孔51Yの内面を被覆し、貫通孔51Yの底部を埋めるように形成されている。この各ピア配線61の上面には、導電パターン62の上面62Aよりも配線パターン50B側（貫通孔51Yの底面側）に凹む凹部61Xが形成されている。本例の凹部61Xは、例えば、絶縁層51の上面51Aよりも配線パターン50B側に凹むように形成されている。すなわち、凹部61Xの底面は、絶縁層51の上面51Aよりも配線パターン50B側（貫通孔51Yの底面側）の位置（ここでは、下方）に形成されている。また、凹部61Xの内側面は曲面に形成されている。例えば、本例の凹部61Xは、断面視略半円状に形成されている。すなわち、本例の凹部61Xは、その内側面及び底面が曲面に形成されている。また、凹部61Xの内側面は、導電パターン62の上面62Aと連続して形成されている。20

#### 【0036】

図3に示すように、複数の凹部61Xは、識別マーク15として識別される特定の文字・記号（ここでは、7セグメント式数字の「4」）を形作るように形成されている。詳述すると、各凹部61Xの平面形状は、貫通孔51Yの平面形状に対応する形状に形成されている。具体的には、各凹部61Xの平面形状は、貫通孔51Yの平面形状よりも一回り小さい形状（ここでは、略矩形状）に形成されている。すなわち、各凹部61Xは、7セグメント表示における各セグメントに対応する平面形状に形成されている。そして、図3に示した4つの凹部61Xは、平面視したときの全体像が7セグメント式数字の「4」を形作るように形成されている。これら複数の凹部61Xは、互いに離間して形成されている。なお、各凹部61Xの幅は、例えば、40～190μm程度とすることができます。30

#### 【0037】

図4に示すように、導電パターン62は、例えば、ピア配線61を介して配線パターン50Bと電気的に接続されている。導電パターン62は、隣接するピア配線61を互いに接続するように形成されている。導電パターン62は、例えば、領域B1全体に広がるよう絶縁層51の上面51Aの上に形成されている。導電パターン62は、例えば、ピア配線61と一緒に形成されている。なお、ピア配線61と導電パターン62とは、同一の材料からなる。ピア配線61及び導電パターン62の材料としては、例えば、銅や銅合金を用いることができる。40

#### 【0038】

領域B1に位置するソルダレジスト層53は、凹部61Xを充填し、ピア配線61及び導電パターン62の表面（上面及び側面）全面を被覆するように形成されている。ソルダレジスト層53の上面は平坦に形成されている。そして、ピア配線61上に形成されたソルダレジスト層53は、導電パターン62上に形成されたソルダレジスト層53よりも厚く形成されている。すなわち、ピア配線61上に形成されたソルダレジスト層53は、導電パターン62上に形成されたソルダレジスト層53よりも、凹部61Xに充填された分だけ厚く形成されている。この厚さの違いにより、図3に示すように、凹部61Xに充填50

された部分のソルダレジスト層 5 3 と、それ以外の部分のソルダレジスト層 5 3 との濃淡（コントラスト）が強くなる。具体的には、図 4 における上側（つまり、導電層 6 0 の上部方向）から識別マーク 1 5 を見たときに、凹部 6 1 X と平面視で重なる部分のソルダレジスト層 5 3 と、導電パターン 6 2 と平面視で重なる部分のソルダレジスト層 5 3 とのコントラストが強くなる。このため、領域 B 1 では、複数の凹部 6 1 X によって形作られた形状（ここでは、7 セグメント式数字の「4」）、つまり識別マーク 1 5 として識別される形状が視認し易くなる。

#### 【0039】

このように、識別マーク 1 5 は、貫通孔 5 1 Y 内に形成されたビア配線 6 1 と、導電パターン 6 2 と、ビア配線 6 1 の上面に形成された凹部 6 1 X と、凹部 6 1 X を充填し、ビア配線 6 1 及び導電パターン 6 2 を被覆するソルダレジスト層 5 3 とによって構成されている。

#### 【0040】

次に、識別マーク 2 5 の構造について説明する。なお、識別マーク 2 5 の断面構造は、識別マーク 1 5 の断面構造と同様であるため、ここでは詳細な説明を省略する。

図 1 ( b ) に示すように、識別マーク 2 5 の平面形状は、特定の文字・記号（図示の例では、「4」）として識別可能なように形成されている。本例の識別マーク 2 5 は、7 セグメント式表示における 4 つのセグメントによって表現された「4」として識別可能なように形成されている。

#### 【0041】

図 2 ( a ) に示すように、識別マーク 2 5 が形成された領域 B 2 では、絶縁層 5 1 の上面 5 1 A に、当該絶縁層 5 1 を厚さ方向に貫通して配線パターン 5 0 C の上面を露出する複数の貫通孔 5 1 Z が形成されている。複数の貫通孔 5 1 Z は、複数の貫通孔 5 1 Y と同様に、「4」という記号を形作るように形成されている。また、各貫通孔 5 1 Z は、各貫通孔 5 1 X よりも体積が大きくなるように形成されている。

#### 【0042】

領域 B 2 には、各貫通孔 5 1 Z 内に形成されたビア配線 6 6 と、ビア配線 6 6 と接続され、絶縁層 5 1 の上面 5 1 A に形成された導電パターン 6 7 とを有する導電層 6 5 が形成されている。各ビア配線 6 6 の上面には、凹部 6 1 X と同様に、導電パターン 6 7 の上面 6 7 A 及び絶縁層 5 1 の上面 5 1 A よりも配線パターン 5 0 C 側に凹む凹部 6 6 X が形成されている。すなわち、各凹部 6 6 X は、各貫通孔 5 1 Z よりも一回り小さい平面形状に形成され、「4」という記号を形作るように形成されている。ソルダレジスト層 5 3 は、凹部 6 6 X を充填し、ビア配線 6 6 及び導電パターン 6 7 の表面（側面及び上面）全面を被覆するように形成されている。そして、本例の識別マーク 2 5 は、貫通孔 5 1 Z に形成されたビア配線 6 6 と、導電パターン 6 7 と、ビア配線 6 6 の上面に形成された凹部 6 6 X と、凹部 6 6 X を充填し、ビア配線 6 6 及び導電パターン 6 7 を被覆するソルダレジスト層 5 3 とによって構成されている。

#### 【0043】

図 2 ( b ) には、図 2 ( a ) に示した切断位置 A 1 で基板本体 3 0 、絶縁層 4 1 , 5 1 及びソルダレジスト層 4 3 , 5 3 が切断されて個片化された後の配線基板 1 2 が示されている。なお、各配線基板 1 2 には、切断後にも識別マーク 1 5 が残っている。

#### 【0044】

次に、図 5 に従って、配線基板 1 2 を有する半導体装置 7 0 の構造を説明する。

半導体装置 7 0 は、配線基板 1 2 と、その配線基板 1 2 に実装された半導体チップ 7 1 と、アンダーフィル樹脂 7 3 と、外部接続端子 7 4 とを有している。

#### 【0045】

半導体チップ 7 1 は、例えば、配線基板 1 2 にフリップチップ実装されている。すなわち、半導体チップ 7 1 の回路形成面（ここでは、下面）に配設されたバンプ 7 2 を配線基板 1 2 の接続パッド P 2 に接合することにより、半導体チップ 7 1 は、バンプ 7 2 を介して、配線基板 1 2 の配線層 5 2 と電気的に接続されている。

10

20

30

40

50

**【 0 0 4 6 】**

半導体チップ71としては、例えば、C P U (Central Processing Unit)チップやG P U (Graphics Processing Unit)チップなどのロジックチップを用いることができる。また、半導体チップ71としては、例えば、D R A M (Dynamic Random Access Memory)チップ、S R A M (Static Random Access Memory)チップやフラッシュメモリチップなどのメモリチップを用いることもできる。なお、配線基板12に複数の半導体チップ71を搭載する場合には、ロジックチップとメモリチップとを組み合わせて配線基板12に搭載するようにしてもよい。

**【 0 0 4 7 】**

バンプ72としては、例えば、金バンプやはんだバンプを用いることができる。はんだバンプの材料としては、例えば、鉛を含む合金、S nとA uの合金、S nとC uの合金、S nとA gの合金、S nとA gとC uの合金等を用いることができる。10

**【 0 0 4 8 】**

アンダーフィル樹脂73は、配線基板12と半導体チップ71との隙間を充填するように設けられている。アンダーフィル樹脂73の材料としては、例えば、エポキシ系樹脂などの絶縁性樹脂を用いることができる。

**【 0 0 4 9 】**

外部接続端子74は、配線基板12の外部接続用パッドP1上に形成されている。この外部接続端子74は、例えば、図示しないマザーボード等の実装基板に設けられたパッドと電気的に接続される接続端子である。外部接続端子74としては、例えば、はんだボールやリードピンを用いることができる。本実施形態では、外部接続端子74として、はんだボールを用いている。20

**【 0 0 5 0 】**

次に、図6に従って、配線基板10の作用について説明する。

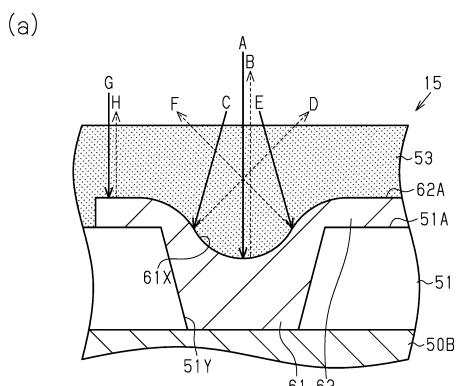

まず、図6(b)に従って、従来の配線基板に形成された識別マーク15Aについて説明する。識別マーク15Aは、配線パターン110を被覆する絶縁層111に形成された貫通孔111Xと、貫通孔111Xの内面及び絶縁層111の上面を連続的に被覆するめっき層112とから構成されている。貫通孔111Xは、図6(b)において上側から下側に向かうに連れて径が小さくなるテーパ状に形成されている。このため、貫通孔111Xの内側面を被覆するめっき層112は、配線パターン110の上面に対して直線状に傾斜して形成されている。すなわち、貫通孔111Xの内側面を被覆するめっき層112の表面は平面に形成されている。このような識別マーク15Aでは、配線パターン110の上面に対して垂直に入射する入射光Aは、貫通孔111Xの底部に形成されためっき層112で反射し、反射光Bのように上方に反射する。一方、入射光C, Eのように配線パターン110の上面に対して斜めに入射する光は、貫通孔111Xの内側面に形成されためっき層112で反射する。このとき、上述したように、貫通孔111Xの内側面を被覆するめっき層112の表面が平面に形成されている。このため、貫通孔111Xの内側面を被覆するめっき層112の表面では拡散反射(乱反射)が起こりにくい。この結果、識別マーク15Aでは、絶縁層111の上面に形成されためっき層112に入射された入射光Gの反射光Hと、貫通孔111X内に形成されためっき層112から上方に反射された反射光との強度の差が小さくなる。このため、貫通孔111X内に形成されためっき層112と、絶縁層111の上面に形成されためっき層112とのコントラストが弱くなり、識別マーク15Aの視認性が低くなる。30

**【 0 0 5 1 】**

また、図6(b)に示すようなめっき層112の形状の場合には、そのめっき層112上にソルダレジスト層113(一点鎖線)を形成すると、そのソルダレジスト層113が貫通孔111X内に垂れ下がってしまう。すると、ソルダレジスト層113の上面の平坦性が損なわれるため、識別マーク15Aの視認性が低くなる。40

**【 0 0 5 2 】**

これに対し、本実施形態では、図6(a)に示すように、貫通孔51Yに形成されたビ

50

ア配線 6 1 と、導電パターン 6 2 と、ビア配線 6 1 の上面に形成された凹部 6 1 X と、凹部 6 1 X を充填し、ビア配線 6 1 及び導電パターン 6 2 を被覆するソルダレジスト層 5 3 とによって識別マーク 1 5 を構成した。また、凹部 6 1 X の内側面を曲面に形成した。この曲面である凹部 6 1 X の内側面は、配線パターン 5 0 B の上面に対して斜めに入射する入射光 C , E を受け、それら入射光 C , E を反射光 D , F のように上方に拡散反射（乱反射）する。これにより、導電パターン 6 2 から上方に反射された反射光 H と、ビア配線 6 1 から上方に反射された反射光との強度の差が、従来の識別マーク 1 5 A よりも大きくなる。このため、導電パターン 6 2 の上面 6 2 A とビア配線 6 1 の上面とのコントラストが強くなり、識別マーク 1 5 （つまり、凹部 6 1 X によって形作られた形状）の視認性を向上させることができる。

10

#### 【 0 0 5 3 】

また、識別マーク 1 5 では、ビア配線 6 1 上に形成されたソルダレジスト層 5 3 を、導電パターン 6 2 上に形成されたソルダレジスト層 5 3 よりも厚く形成した。これにより、ビア配線 6 1 上に位置するソルダレジスト層 5 3 と、導電パターン 6 2 上に位置するソルダレジスト層 5 3 とのコントラストが強くなる。この結果、識別マーク 1 5 の視認性をより向上させることができる。

#### 【 0 0 5 4 】

さらに、識別マーク 1 5 では、貫通孔 5 1 Y 内にその底部を埋めるビア配線 6 1 を形成し、凹部 6 1 X の底面を底上げした。このため、ソルダレジスト層 5 3 が凹部 6 1 X 内に垂れ下がっても、そのソルダレジスト層 5 3 によって凹部 6 1 X が充填される。これにより、従来の識別マーク 1 5 A に比べて、ソルダレジスト層 5 3 の上面の平坦性を向上させることができる。この結果、識別マーク 1 5 の視認性をより向上させることができる。なお、識別マーク 2 5 についても、識別マーク 1 5 と同様のことが言える。

20

#### 【 0 0 5 5 】

次に、配線基板 1 0 の製造方法について説明する。なお、説明の便宜上、最終的に配線基板 1 0 の各構成要素となる部分には、最終的な構成要素の符号を付して説明する。

まず、図 7 ( a ) に示す工程では、基板本体 3 0 を準備する。基板本体 3 0 は、配線基板 1 2 ( 図 2 ( a ) 参照 ) が形成される基板形成領域 A 2 を複数有するとともに、それら基板形成領域 A 2 の外側に形成され、外枠 2 0 ( 図 2 ( a ) 参照 ) が形成される外枠形成領域 A 3 を有している。続いて、基板本体 3 0 の上面に、配線パターン 5 0 A , 5 0 B , 5 0 C を有する配線層 5 0 を形成し、基板本体 3 0 の下面に配線層 4 0 を形成する。配線層 4 0 , 5 0 は、例えば、セミアディティブ法やサブトラクティブ法などの各種の配線形成方法を用いて形成することができる。

30

#### 【 0 0 5 6 】

次に、図 7 ( b ) に示す工程では、キャリア層 8 0 の上面に離型剤（剥離層）を介してシート状の絶縁層 4 1 が積層された構造体 8 1 と、キャリア層 8 2 の下面に離型剤（剥離層）を介してシート状の絶縁層 5 1 が接着された構造体 8 3 を準備する。絶縁層 4 1 , 5 1 は、B - ステージ状態（半硬化状態）のものが使用される。キャリア層 8 0 , 8 2 はそれぞれ、絶縁層 4 1 , 5 1 の取り扱いを容易にするための支持材として設けられている。キャリア層 8 0 , 8 2 としては、例えば、P E T ( ポリエチレンテレフタレート ) フィルム、P I ( ポリイミド ) フィルム、P E N ( ポリエチレンナフタレート ) フィルムを用いることができる。離型剤としては、例えば、シリコーン系離型剤、フッ素系離型剤やアルキッド樹脂系離型剤を用いることができる。

40

#### 【 0 0 5 7 】

続いて、基板本体 3 0 の下面側に、絶縁層 4 1 を上側に向けた状態で構造体 8 1 を配置し、基板本体 3 0 の上面側に、絶縁層 5 1 を下側に向けた状態で構造体 8 3 を配置する。次いで、構造体 8 1 , 8 3 を両面側から真空雰囲気で 1 1 0 ~ 1 3 0 度程度の温度で加熱・加圧する。これにより、絶縁層 4 1 中に配線層 4 0 が圧入され、絶縁層 5 1 中に配線層 5 0 ( 配線パターン 5 0 A , 5 0 B , 5 0 C ) が圧入される。その後、1 7 0 ~ 1 9 0 度程度の温度でキュア（熱硬化処理）を実施して絶縁層 4 1 , 5 1 を硬化させる。本工程に

50

より、基板本体30の下面に、絶縁層41とキャリア層80とが順に積層された構造体81が積層され、基板本体30の上面に、絶縁層51とキャリア層82とが順に積層された構造体83が積層される。

#### 【0058】

なお、本工程では、キャリア層80, 82を省略するようにしてもよい。この場合に、絶縁層41, 51として液状又はペースト状の絶縁性樹脂を用いる場合には、基板本体30の上面及び下面に液状又はペースト状の絶縁性樹脂をスピンドルコート法などにより塗布し、その塗布した絶縁性樹脂を130～190程度の温度で熱処理して硬化させることにより絶縁層41, 51を形成することもできる。

#### 【0059】

次に、図8(a)に示す工程では、絶縁層41に貫通孔41Xを形成し、絶縁層51に貫通孔51X, 51Y, 51Zを形成する。貫通孔41X, 51X, 51Y, 51Zは、例えば、CO<sub>2</sub>レーザやYAGレーザ等によるレーザ加工法によって形成することができる。本例では、キャリア層80, 82を絶縁層41, 51上に積層した状態で、レーザ加工法によって貫通孔41X, 51X, 51Y, 51Zが形成される。本例の貫通孔41Xは、キャリア層80及び絶縁層41を厚さ方向に貫通し、配線層40の下面の一部を露出するように形成される。本例の貫通孔51X, 51Y, 51Zは、キャリア層82及び絶縁層51を厚さ方向に貫通し、配線パターン50A, 50B, 50Cの上面の一部をそれぞれ露出するように形成される。

#### 【0060】

このとき、貫通孔51Y, 51Zは、貫通孔51Xよりも体積が大きくなるように形成される。具体的には、貫通孔51Y, 51Zは、平面視したときに文字及び記号を含む特定の形状を作るように形成される。例えば、図8(b)に示すように、複数の貫通孔51Yは、平面視したときの全体像が特定の形状、ここでは7セグメント式数字の「4」を作るように形成される。すなわち、図示の例では、7セグメント式数字の「4」を表現する4つのセグメントに対応する配置で4つの貫通孔51Yが形成され、各貫通孔51Yの平面形状が各セグメントに対応する形状に形成される。各貫通孔51Yの底部には、配線パターン50Bの上面が露出される。同様に、貫通孔51Zは、平面視したときの全体像が特定の形状(例えば、「」)を作るように形成される。

#### 【0061】

なお、図8(a)に示した貫通孔41X, 51X, 51Y, 51Zは、キャリア層80, 82を除去した後に形成してもよい。また、絶縁層41, 51が感光性樹脂を用いて形成されている場合には、例えば、フォトリソグラフィ法により所要の貫通孔41X, 51X, 51Y, 51Zを形成するようにしてもよい。

#### 【0062】

続いて、キャリア層80, 82を除去する。例えば、キャリア層80を絶縁層41から機械的に剥離し、キャリア層82を絶縁層51から機械的に剥離する。このとき、例えば図8(c)に示すように、貫通孔51Yを、アラビア数字の「4」を作るように形成した場合には、キャリア層82に、貫通孔51Yによって囲まれて他の部分と分離された分離部82Aが形成される。この分離部82Aが形成された状態で、キャリア層82を機械的に剥離すると、分離部82A(つまり、キャリア層82の一部)が絶縁層51上に残ってしまう。これに対し、図8(b)に示すように、貫通孔51Yを、7セグメント式数字の「4」を作るように形成した場合には、複数の貫通孔51Yが互いに離間して形成されるため、分離部82Aが形成されない。このため、本例では、キャリア層82を機械的に剥離すると、キャリア層82全体を剥離することができる。すなわち、本例では、キャリア層82の一部が絶縁層51上に残るという問題の発生を抑制することができる。

#### 【0063】

図9(a)に示すように、キャリア層80, 82(図8(a)参照)を剥離すると、絶縁層41の下面が外部に露出され、絶縁層51の上面51Aが外部に露出される。なお、図7(b)及び図8に示した工程において、キャリア層80, 82を省略した場合には、

10

20

30

40

50

当然、本工程を省略することができる。

#### 【0064】

次いで、貫通孔 41X, 51X, 51Y, 51Z をレーザ加工法によって形成した場合には、デスマニア処理を行う。これにより、貫通孔 41X の底部に露出する配線層 40 の下面及び貫通孔 51X, 51Y, 51Z の底部に露出する配線層 50 の上面に付着した樹脂スミア（樹脂残渣）を除去する。

#### 【0065】

続いて、図 9 (b) に示す工程では、絶縁層 41 の下面全面と、貫通孔 41X の内側面全面と、貫通孔 41X の底部に露出する配線層 40 の下面全面とを連続的に被覆するシード層 85 を形成する。また、絶縁層 51 の上面 51A 全面と、貫通孔 51X, 51Y, 51Z の内側面全面と、貫通孔 51X, 51Y, 51Z の底部に露出する配線層 50 の上面全面とを連続的に被覆するシード層 86 を形成する。これらシード層 85, 86 は、例えば、スパッタ法や無電解めっき法を用いて形成することができる。なお、シード層 85, 86 の材料としては、例えば、銅や銅合金を用いることができる。また、シード層 85, 86 としては、例えば、複数の金属膜を積層した構造を有するシード層を用いることもできる。このようなシード層 85, 86 としては、例えば、窒化チタン、窒化タンタル (TaN)、タンタル (Ta)、クロム (Cr) 等からなる金属膜と、銅や銅合金からなる金属膜とを順に積層した構造を有するシード層を用いることができる。ここで、窒化チタンや窒化タンタルは、銅よりも耐腐食性の高い金属であって、銅よりも絶縁層 41, 51 との密着性が高い金属である。

10

20

#### 【0066】

次いで、図 10 (a) に示す工程では、シード層 85 上に、所定の箇所に開口パターン 87X を有するレジスト層 87 を形成する。また、シード層 86 上に、所定の箇所に開口パターン 88X, 88Y, 88Z を有するレジスト層 88 を形成する。開口パターン 87X は、配線層 42 (図 2 (a) 参照) の形成領域に対応する部分のシード層 85 を露出するように形成される。開口パターン 88X は、配線層 52 (図 2 (a) 参照) の形成領域に対応する部分のシード層 86 を露出するように形成される。開口パターン 88Y は、識別マーク 15 (図 2 (a) 参照) が形成される領域 B1 におけるシード層 86 の表面全面を露出するように形成される。開口パターン 88Z は、識別マーク 25 (図 2 (a) 参照) が形成される領域 B2 におけるシード層 86 の表面全面を露出するように形成される。レジスト層 87, 88 の材料としては、例えば、次工程のめっき処理に対して耐めっき性がある材料を用いることができる。例えば、レジスト層 87, 88 の材料としては、感光性のドライフィルムレジスト又は液状のフォトレジスト (例えば、ノボラック系樹脂やアクリル系樹脂等のドライフィルムレジストや液状レジスト) 等を用いることができる。例えば、感光性のドライフィルムレジストを用いる場合には、シード層 85 の下面及びシード層 86 の上面にドライフィルムを熱圧着によりラミネートし、そのドライフィルムをフォトリソグラフィ法によりパターニングしてレジスト層 87, 88 を形成する。なお、液状のフォトレジストを用いる場合にも、同様の工程を経て、レジスト層 87, 88 を形成することができる。

30

40

#### 【0067】

次に、図 10 (b) に示す工程では、レジスト層 87 をめっきマスクとして、シード層 85 の下面に、そのシード層 85 をめっき給電層に利用する電解めっき法を施す。例えば、レジスト層 87 の開口パターン 87X から露出されたシード層 85 の下面に電解めっき法 (ここでは、電解銅めっき法) を施す。これにより、シード層 85 よりも内側の貫通孔 41X を充填する金属層 89 (電解めっき金属層) が形成され、その金属層 89 の下面及びシード層 85 の下面に金属層 90 (電解めっき金属層) が形成される。

#### 【0068】

また、図 10 (b) に示す工程では、レジスト層 88 をめっきマスクとして、シード層 86 の上面に、そのシード層 86 をめっき給電層に利用する電解めっき法を施す。例えば

50

、レジスト層 8 8 の開口パターン 8 8 X , 8 8 Y , 8 8 Z から露出されたシード層 8 6 の上面に電解めっき法（ここでは、電解銅めっき法）を施す。これにより、シード層 8 6 よりも内側の貫通孔 5 1 X を充填する金属層 9 1 が形成され、シード層 8 6 よりも内側の貫通孔 5 1 Y 内に金属層 9 2 が形成され、シード層 8 6 よりも内側の貫通孔 5 1 Z 内に金属層 9 3 が形成される。さらに、金属層 9 1（電解めっき金属層）の上面及びシード層 8 6 の上面に金属層 9 4（電解めっき金属層）が形成される。

#### 【 0 0 6 9 】

このとき、領域 B 1 , B 2 にそれぞれ形成された貫通孔 5 1 Y , 5 1 Z は、貫通孔 5 1 X よりも体積が大きくなるように形成されている。このため、各貫通孔 5 1 X には金属層 9 1 が充填される一方で、各貫通孔 5 1 Y , 5 1 Z にはめっき膜（金属層 9 2 , 9 3 ）が充填されず、金属層 9 2 , 9 3 の上面に凹部 6 1 X , 6 6 X がそれぞれ形成される。これら凹部 6 1 X , 6 6 X の内面は曲面に形成される。換言すると、本工程において内面が曲面となる凹部 6 1 X , 6 6 X が形成されるように、各貫通孔 5 1 Y , 5 1 Z の体積が設定されている。

10

#### 【 0 0 7 0 】

このとき、各凹部 6 1 X の平面形状は、貫通孔 5 1 Y の平面形状に対応して形成される。具体的には、各凹部 6 1 X の平面形状は、例えば、対応する貫通孔 5 1 Y の平面形状よりも一回り小さく形成される。このため、複数の凹部 6 1 X は、複数の貫通孔 5 1 Y と同様に、平面視したときの全体像が特定の形状（例えば、7 セグメント式数字の「4」）を作成するように形成される。同様に、凹部 6 6 X の平面形状は、例えば、対応する貫通孔 5 1 Z の平面形状よりも一回り小さく形成される。このため、複数の凹部 6 6 X は、複数の貫通孔 5 1 Z と同様に、平面視したときの全体像が特定の形状（例えば、「」）を作成するように形成される。

20

#### 【 0 0 7 1 】

続いて、図 11 ( a ) に示す工程では、図 10 ( b ) に示したレジスト層 8 7 , 8 8 を、例えば、アルカリ性の剥離液により除去する。次いで、図 11 ( b ) に示す工程では、金属層 8 9 , 9 0 をエッティングマスクとして、不要なシード層 8 5 をエッティングにより除去する。これにより、絶縁層 4 1 の下面に形成されたシード層 8 5 と金属層 9 0 とから構成される配線層 4 2 が形成される。また、金属層 9 1 ~ 9 4 をエッティングマスクとして、不要なシード層 8 6 をエッティングにより除去する。これにより、貫通孔 5 1 X 内に形成されたシード層 8 6 と金属層 9 1 とから構成されるビア配線 5 4 と、絶縁層 5 1 上に形成されたシード層 8 6 と金属層 9 4 とから構成される配線層 5 2 とが形成される。また、貫通孔 5 1 Y に形成されたシード層 8 6 と金属層 9 2 とから構成されるビア配線 6 1 と、領域 B 1 における絶縁層 5 1 上に形成されたシード層 8 6 と金属層 9 4 とから構成される導電パターン 6 2 とが形成される。さらに、貫通孔 5 1 Z に形成されたシード層 8 6 と金属層 9 3 とから構成されるビア配線 6 6 と、領域 B 2 における絶縁層 5 1 上に形成されたシード層 8 6 と金属層 9 4 とから構成される導電パターン 6 7 とが形成される。

30

#### 【 0 0 7 2 】

ここで、以上説明した製造工程のうちレジスト層 8 7 , 8 8（図 10 ( a ) 参照）のパターニング（露光）工程においては、例えば、大判の基板本体 3 0 を複数の領域に分割して露光するステップアンドリピート方式の露光方法（ステップパを用いた露光方法）が用いられる。この露光方法では、図 12 ( a ) 及び図 12 ( b ) に示すように、基板本体 3 0 を複数（ここでは、3 つ）の領域、つまり図 12 ( a ) に太線枠で示した領域 A 4 と、図 12 ( b ) に太線枠で示した領域 A 4 と、残りの領域 A 4 との3つの領域 A 4 に分割する。そして、その分割した3つの領域 A 4 の1つ1つの領域を順次露光していく。すなわち、まず、図 12 ( a ) に太線枠で示した領域 A 4 を露光し、次に、図 12 ( b ) に太線枠で示した領域 A 4 を露光した後に、残りの領域 A 4 を露光する。このとき、3つの領域 A 4 に対して共通の露光マスクを使用して露光が行われるため、各領域 A 4 においてレジスト層 8 7 , 8 8（図 10 ( a ) 参照）が同じようにパターニングされる。換言すると、ステップパを用いた露光方法では、3つの領域 A 4 に対して、同一の開口パターン 8 7 X , 8

40

8 X , 8 8 Y , 8 8 Z ( 図 1 0 ( a ) 参照 ) しか形成できず、同一パターンの配線層 4 2 , 5 2 ( 図 1 1 ( b ) 参照 ) しか形成することができない。このため、ステッパを用いた露光方法を用いて識別マークを形成する場合には、基板形成領域 A 2 每に異なる形状の識別マークを形成することは困難であり、各領域 A 4 内の外枠形成領域 A 3 每に異なる形状の識別マークを形成することは困難である。なお、基板形成領域 A 2 每に異なる露光マスクを使用することにより、基板形成領域 A 2 每に異なる形状の識別マークを形成することができる。しかし、この場合には、基板形成領域 A 2 每に露光を行う必要があり、さらに露光のたびに露光マスクを交換する必要があるため、配線基板 1 0 の製造コストが大幅に増大するという問題がある。

## 【 0 0 7 3 】

10

これに対し、本実施形態では、図 8 ~ 図 1 1 に示したように、レジスト層 8 8 のパターニングとは別に、貫通孔 5 1 X を形成する工程と同一の工程において、貫通孔 5 1 Y , 5 1 Z を形成するようにした。また、本実施形態では、ビア配線 5 4 及び配線層 5 2 を形成する工程と同一の工程において、ビア配線 6 1 , 6 6 及び導電パターン 6 2 , 6 7 を形成するようにした。さらに、本実施形態では、貫通孔 5 1 Y , 5 1 Z をレーザ加工法により形成するようにした。このため、基板形成領域 A 2 每に異なる平面形状となる複数の貫通孔 5 1 Y 及びビア配線 6 1 を容易に形成することができ、各領域 A 4 の外枠形成領域 A 3 每に異なる平面形状となる複数の貫通孔 5 1 Z 及びビア配線 6 6 を容易に形成することができる。さらに、本実施形態では、貫通孔 5 1 X の体積と貫通孔 5 1 Y , 5 1 Z の体積とを調整することにより、ビア配線 5 4 の形成と同時に、上面に凹部 6 1 X , 6 6 X を有するビア配線 6 1 , 6 6 を形成することができる。また、本実施形態では、導電パターン 6 2 を領域 B 1 全体に広がるように形成し、導電パターン 6 7 を領域 B 2 全体に広がるように形成するようにした。このため、導電パターン 6 2 , 6 7 の形状に対応する開口パターン 8 8 Y , 8 8 Z の形状を、基板形成領域 A 2 每及び外枠形成領域 A 3 每に変更する必要がなく、共通の形状に設定することができる。

20

## 【 0 0 7 4 】

なお、貫通孔 5 1 Y , 5 1 Z を形成するために製造時間 ( レーザ加工時間 ) が増加するが、貫通孔 5 1 X を形成する工程と同一の工程において対応できるため、配線基板 1 0 の製造時間の増大を好適に抑制することができる。すなわち、基板形成領域 A 2 每に異なる露光マスクを使用し、各領域 A 4 の外枠形成領域 A 3 每に異なる露光マスクを使用する場合に比べて、配線基板 1 0 の製造時間の増加を好適に抑制することができる。このため、識別マーク 1 5 , 2 5 の形成に伴って配線基板 1 0 の製造コストが増大することを好適に抑制することができる。

30

## 【 0 0 7 5 】

40

次に、図 1 3 ( a ) に示す工程では、絶縁層 4 1 の下面に、配線層 4 2 の所要箇所に画定される外部接続用パッド P 1 を露出させるための開口部 4 3 X を有するソルダレジスト層 4 3 を形成する。また、絶縁層 5 1 の上面 5 1 A に、配線層 5 2 の所要箇所に画定される接続パッド P 2 を露出させるための開口部 5 3 X を有するソルダレジスト層 5 3 を形成する。ソルダレジスト層 5 3 は、ビア配線 6 1 , 6 6 の凹部 6 1 X , 6 6 X を充填し、導電パターン 6 2 , 6 7 の表面全面を被覆するように形成される。このとき、凹部 6 1 X , 6 6 X と平面視で重なる部分のソルダレジスト層 5 3 は、それ以外の部分のソルダレジスト層 5 3 よりも厚く形成される。本工程により、ビア配線 6 1 と導電パターン 6 2 と凹部 6 1 X とソルダレジスト層 5 3 とによって構成される識別マーク 1 5 と、ビア配線 6 6 と導電パターン 6 7 と凹部 6 6 X とソルダレジスト層 5 3 とによって構成される識別マーク 2 5 とが形成される。

## 【 0 0 7 6 】

以上の製造工程により、本実施形態の配線基板 1 0 が製造される。すなわち、各基板形成領域 A 2 に配線基板 1 2 が製造され、外枠形成領域 A 3 に外枠 2 0 が製造される。

次に、図 1 3 ( a ) に示した構造体を切断位置 A 1 に沿ってダイシングブレード等によつて切断する。これにより、図 1 3 ( b ) に示すように、配線基板 1 2 が個片化され、複

50

数の配線基板 12 が製造される。なお、本工程において、外枠 20（図 13(a) 参照）は廃棄される。

#### 【0077】

以上説明した本実施形態によれば、以下の効果を奏することができる。

(1) 貫通孔 51Y に形成されたビア配線 61 と、導電パターン 62 と、ビア配線 61 の上面に形成された凹部 61X と、凹部 61X を充填し、ビア配線 61 及び導電パターン 62 を被覆するソルダレジスト層 53 とによって識別マーク 15 を構成した。また、凹部 61X の内側面を曲面に形成した。これにより、導電パターン 62 の上面 62A とビア配線 61 の上面とのコントラストが強くなる。このため、ビア配線 61 の上面に形成された凹部 61X によって形作られた識別マーク 15 の視認性を向上させることができる。 10

#### 【0078】

(2) ビア配線 61 上に形成されたソルダレジスト層 53 を、導電パターン 62 上に形成されたソルダレジスト層 53 よりも厚く形成した。これにより、ビア配線 61 上に位置するソルダレジスト層 53 と、導電パターン 62 上に位置するソルダレジスト層 53 とのコントラストが強くなる。この結果、識別マーク 15 の視認性をより向上させることができる。

#### 【0079】

(3) レジスト層 88 のパターニング（配線層 52 の形成）とは別に、絶縁層 51 に貫通孔 51Y, 51Z を形成し、それら貫通孔 51Y, 51Z 内に凹部 61X, 66X を有するビア配線 61, 66 をそれぞれ形成するようにした。また、貫通孔 51Y, 51Z をレーザ加工法により形成するようにした。これにより、基板形成領域 A2 毎に異なる形状の識別マーク 15 を容易に形成することができ、各領域 A4 の外枠形成領域 A3 毎に異なる形状の識別マーク 25 を容易に形成することができる。換言すると、識別マーク 15, 25 の設置位置及び形状を自由に選択することができるため、各单位配線基板 12 に形成される識別マーク 15 の設計自由度を向上させることができ、外枠 20 に形成される識別マーク 25 の設計自由度を向上させることができる。 20

#### 【0080】

(4) 導電パターン 62 を領域 B1 全体に広がるように形成し、導電パターン 67 を領域 B2 全体に広がるように形成するようにした。これにより、導電パターン 62, 67 の形状に対応してレジスト層 88 の開口パターン 88Y, 88Z の形状を、各基板形成領域 A2 毎及び各外枠形成領域 A3 毎に変更する必要がなく、共通の形状に設定することができる。このため、ステッパーを用いた露光方法によって、各基板形成領域 A2 における導電パターン 62 と各外枠形成領域 A3 における導電パターン 67 とを形成することができる。 30

#### 【0081】

(5) 貫通孔 51X を形成する工程と同一の工程において、レーザ加工法により、貫通孔 51Y, 51Z を形成するようにした。これにより、配線基板 10 の製造時間の増大を抑制することができ、配線基板 10 の製造コストが増大することを好適に抑制することができる。

#### 【0082】

(6) さらに、貫通孔 51X の体積より貫通孔 51Y, 51Z の体積の方が大きくなるように貫通孔 51X, 51Y, 51Z を形成することにより、ビア配線 54 の形成とともに、上面に凹部 61X, 66X を有するビア配線 61, 66 を形成するようにした。これにより、識別マーク 15, 25 の形成に伴って配線基板 10 の製造時間が増加することを好適に抑制できるため、配線基板 10 の製造コストが増大することを好適に抑制できる。 40

#### 【0083】

##### （他の実施形態）

なお、上記実施形態は、これを適宜変更した以下の態様にて実施することもできる。

- ・上記実施形態では、凹部 61X, 66X を断面視略半円状に形成した。すなわち、凹部 61X, 66X の内側面及び底面を曲面に形成した。これに限らず、例えば、凹部 61

X , 6 6 X の底面を平坦面に形成するようにしてもよい。すなわち、凹部 6 1 X , 6 6 X の内側面が曲面であれば、凹部 6 1 X , 6 6 X の底面の形状は特に限定されない。

#### 【 0 0 8 4 】

・上記実施形態の配線基板 1 0において、凹部 6 1 X , 6 6 X を充填し、絶縁層 5 1 上に形成されるのは、ソルダレジスト層 5 3 に限定されず、ソルダレジスト層以外の保護絶縁層（絶縁層）であってもよい。

#### 【 0 0 8 5 】

- ・上記実施形態の配線パターン 5 0 B を省略してもよい。

- ・上記実施形態の配線パターン 5 0 C を省略してもよい。

- ・上記実施形態では、7セグメント式数字として識別される識別マーク 1 5 に具体化した。これに限らず、7セグメント式数字以外の文字・記号として識別される識別マーク 1 5 に具体化してもよい。例えば、図 1 4 ( a ) 及び図 1 4 ( b ) に示すように、複数の凹部 6 1 X の配置によって形作られる文字・記号（図 1 4 ( a ) では、アラビア数字の「4」、図 1 4 ( b ) では「+」）として識別される識別マーク 1 5 に具体化してもよい。すなわち、図 1 4 ( a ) 及び図 1 4 ( b ) に示した複数の凹部 6 1 X は、平面視したときの全体像が特定の形状として識別可能となるように、その特定の形状を形作るように配置されている。なお、識別マーク 2 5 についても識別マーク 1 5 と同様に変更可能である。

#### 【 0 0 8 6 】

・上記実施形態では、複数の凹部 6 1 X , 6 6 X によって特定の形状（例えば、7セグメント式表示の「4」や「+」）自体を形作るように、複数の凹部 6 1 X , 6 6 X を形成するようにした。

#### 【 0 0 8 7 】

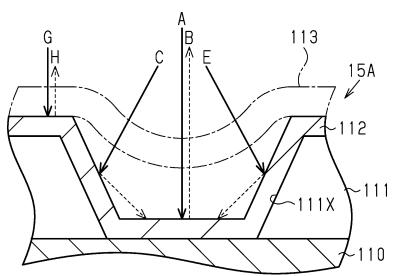

これに限らず、例えば図 1 5 ( a ) に示すように、特定の形状（ここでは、7セグメント式数字の「4」）の外形を囲むように凹部 6 1 X を形成するようにしてもよい。この場合には、凹部 6 1 X により縁取られた部分の平面形状が特定の形状（ここでは、7セグメント式数字の「4」）として識別される。すなわち、図 1 5 ( b ) に示すように、凹部 6 1 X により縁取られた導電パターン 6 2 の平面形状が特定の形状として形作られる。このため、導電パターン 6 2 の上面 6 2 A に形成されたソルダレジスト層 5 3 （つまり、ビア配線 6 1 上に形成されたソルダレジスト層 5 3 よりも薄いソルダレジスト層 5 3 ）の平面形状が特定の形状として識別される。なお、識別マーク 2 5 についても識別マーク 1 5 と同様に変更可能である。

#### 【 0 0 8 8 】

・上記実施形態の配線基板 1 0において、貫通孔 5 1 Y , 5 1 Z 及び凹部 6 1 X , 6 6 X 等によって形作られた識別マーク 1 5 , 2 5 と併せて、ステッパを用いた露光方法によって形成される識別マークを形成するようにしてもよい。

#### 【 0 0 8 9 】

・上記実施形態では、識別マーク 1 5 , 2 5 をチップ搭載面側（接続パッド P 2 側）に形成するようにした。これに限らず、例えば、識別マーク 1 5 , 2 5 を外部接続端子面側（外部接続用パッド P 1 側）に形成するようにしてもよい。

#### 【 0 0 9 0 】

- ・上記実施形態の識別マーク 2 5 を省略してもよい。

- ・上記実施形態の配線基板 1 2 における配線層 4 0 , 5 0 , 4 2 , 5 2 及び絶縁層 4 1 , 5 1 の層数や配線の取り回しなどは様々に変形・変更することが可能である。

#### 【 0 0 9 1 】

・上記実施形態では、配線基板 1 2 に半導体チップ 7 1 を実装する場合について説明したが、被実装体としては半導体チップ 7 1 に限定されない。例えば、配線基板 1 2 の上に別の配線基板を積み重ねる構造を有するパッケージ（パッケージ・オン・パッケージ）にも、本発明を適用することができる。

#### 【 0 0 9 2 】

- ・上記実施形態における配線基板 1 2 に実装される半導体チップの数や、その半導体チ

10

20

30

40

50

ツップの実装の形態（例えば、フリップチップ実装、ワイヤボンディング実装、又はこれらの組み合わせ）などは様々に変形・変更することが可能である。

#### 【0093】

・上記実施形態では、3つのブロック11を有する配線基板10に具体化したが、ブロック11の数は特に限定されない。例えば、1つ又は2つのブロック11を有する配線基板10に具体化してもよいし、4つ以上のブロック11を有する配線基板10に具体化してもよい。

#### 【0094】

・上記実施形態では、単位配線基板12がマトリクス状に複数個連設されたブロック11を有する配線基板10に具体化したが、例えば、単位配線基板12が帯状に複数個連設されたブロック11を有する配線基板10に具体化してもよい。すなわち、単位配線基板12がN×M個（Nは2以上の整数、Mは1以上の整数）連設されたブロック11を有する配線基板であれば、その単位配線基板12の配列は特に限定されない。10

#### 【符号の説明】

##### 【0095】

10 配線基板

11 ブロック

12 配線基板

15, 25 識別マーク

20 20 外枠

50 配線層

50A 配線パターン（第2配線パターン）

50B, 50C 配線パターン（第1配線パターン）

51 絶縁層

51X 貫通孔（第2貫通孔）

51Y, 51Z 貫通孔（第1貫通孔）

52 配線層

53 ソルダレジスト層（保護絶縁層）

53X 開口部

54 ビア配線（第2ビア配線）

61, 66 ビア配線（第1ビア配線）

61X, 66X 凹部

62, 67 導電パターン

70 半導体装置

71 半導体チップ

P2 接続パッド

10

20

30

【図1】

【図2】

【図3】

【図5】

【図4】

【 図 6 】

(b)

【 図 7 】

(b)

【 四 8 】

【図9】

8

【図10】

【 図 1 1 】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(72)発明者 田中 泉

長野県長野市小島田町80番地 新光電気工業 株式会社 内

審査官 黒田 久美子

(56)参考文献 特開2009-194321(JP,A)

特開平4-174586(JP,A)

特開2008-270769(JP,A)

特開2013-080836(JP,A)

(58)調査した分野(Int.Cl., DB名)

H05K 1/02

H05K 3/00