(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 696 30 958 T2 2004.10.28

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 0 840 930 B1

(51) Int Cl.<sup>7</sup>: G11C 16/04

(21) Deutsches Aktenzeichen: 696 30 958.0

(86) PCT-Aktenzeichen: PCT/US96/09889

(96) Europäisches Aktenzeichen: 96 921 471.7

(87) PCT-Veröffentlichungs-Nr.: WO 97/005624

(86) PCT-Anmeldetag: 14.06.1996

(87) Veröffentlichungstag

der PCT-Anmeldung: 13.02.1997

(97) Erstveröffentlichung durch das EPA: 13.05.1998

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 03.12.2003

(47) Veröffentlichungstag im Patentblatt: 28.10.2004

(30) Unionspriorität:

506828 25.07.1995 US

(84) Benannte Vertragsstaaten:

AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LI, LU, MC, NL, PT, SE

(73) Patentinhaber:

Advantage Logic Inc., Cupertino, Calif., US

(72) Erfinder:

PANI, M., Peter, Mountain View, US; TING, S., Benjamin, Saratoga, US; MA, Benny, Saratoga, US

(74) Vertreter:

Zenz, Helber, Hosbach & Partner GbR, 45128

Essen

(54) Bezeichnung: PROGRAMMIERBARER NICHTFLÜCHTIGER ZWEIWEGSCHALTER FÜR PROGRAMMIERBARE LOGIK

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****HINTERGRUND DER ERFINDUNG****1. Gebiet der Erfindung**

**[0001]** Diese Erfindung bezieht sich auf Schalter zum Programmieren programmierbarer Logikbauelemente. Insbesondere bezieht die vorliegende Erfindung sich auf die Verwendung nichtflüchtiger Speicherbauelemente, wie beispielsweise Speicher- und Schalterelemente zum Bereitstellen programmierbarer bidirektionaler Verbindungen.

**2. Technischer Hintergrund**

**[0002]** Programmierbare Logikschaltungen, wie z. B. anwenderprogrammierbare Gate-Arrays (FPGA), benötigen viele programmgesteuerte Schaltelemente, um zwei oder mehr Leiter miteinander zu verbinden, um die im Design spezifizierten richtigen Logikfunktionen zu bilden. Bei einem einmal-programmierbaren Bauelement, wie z. B. Anti-Fuse-FPGAs, wird die Verbindung von zwei oder mehr Leitern durch elektrisches Tempern eines Verbindungspunkts (Anti-Fuse) mit hoher Spannung und Strom erreicht, so daß der Widerstand von sehr hoch auf sehr niedrig gesenkt wird, wodurch ermöglicht wird, daß Signale durch die Anti-Fuse-Elemente von dem einen Leiter auf den anderen geleitet werden. Bei erneut programmierbaren FPGAs werden zwei Leiter üblicherweise durch die Verwendung von SRAM-gesteuerten Durchlaßgattern als Schalter verbunden. Der SRAM kann durch Standardspeicherprogrammertechnik so programmiert werden, daß das Ausgangssignal des SRAM-Bits das zugehörige Durchlaßgatter „ein“- oder „aus“-schalten kann, wodurch ermöglicht wird, daß die zwei gewünschten Leiter durch das Durchlaßgatter verbunden werden. Jedes Mal, wenn das Bauelement ausgeschaltet wird, müßten die Zustände der Bits jedoch aus einer Quelle, wie z. B. einem nicht-flüchtigen EEPROM o. dgl., neu geladen werden, um die Bits wieder zu programmieren.

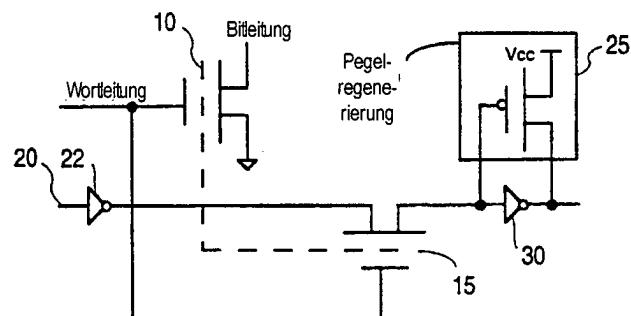

**[0003]** Es ist klar, daß bestimmte deutliche Vorteile erreicht werden können, falls nicht-flüchtige Speicherelemente so verwendet werden, daß sie als Schalter funktionieren, die das programmierbare Logikbauelement programmieren. Solche bekannten Elemente sind jedoch unidirektional und führen zu Datenhalte-Problemen. **Fig. 1A** veranschaulicht ein bekanntes Beispiel eines nicht-flüchtigen Speicherschalters mit einem unidirektionalen Signalweg. Die zwei nicht-flüchtigen n-Kanal-Transistoren teilen gemeinsame Gates, einschließlich des Kondensators der schwimmenden Ladung des Elements. Der erste Transistor **10** wird als ein Speicherelement und der zweite Transistor **15** als ein unidirektionales Durchlaßgatter verwendet. Wenn der Schalter eingeschaltet wird, geht ein von Punkt **20** herrührendes Signal

durch den Invertierer **22** und den zweiten Transistor **15** zur Pegelregenerierungsschaltung **25**, die den Signalpegel wiederherstellt, der durch das Durchlaßgatter geschwächt wurde. Das regenerierte Signal wird durch einen zweiten Treiber-Invertierer **30** weiter angehoben (boosted).

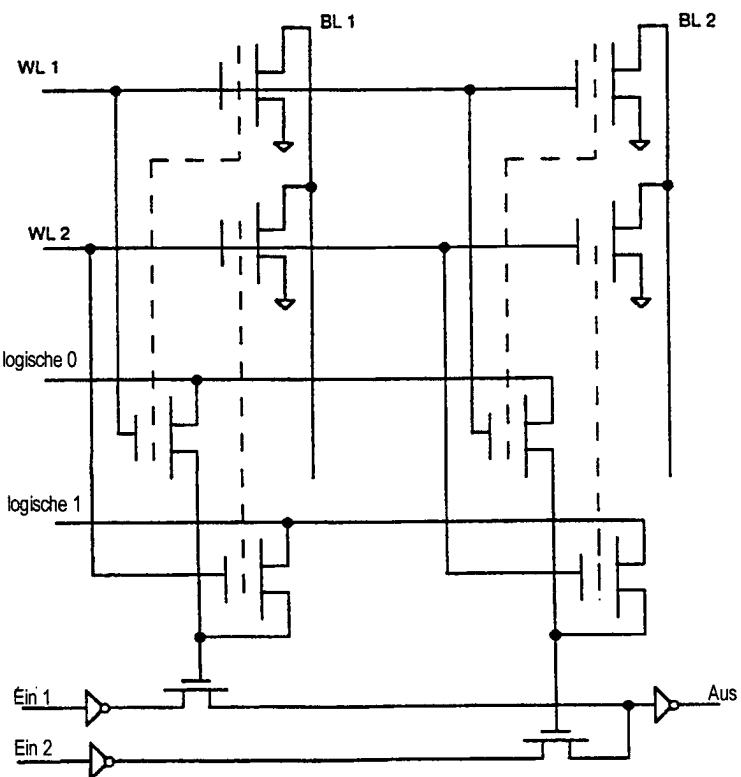

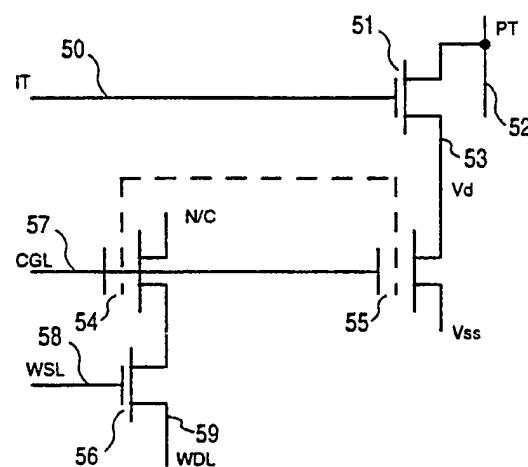

**[0004]** **Fig. 1B** zeigt ein weiteres bekanntes Beispiel eines Arrays von Elementen, in dem die logische 0 und die logische 1 eines unidirektionalen Schalters separat gesteuert werden, um zu bewirken, daß ein unidirektionaler Signalweg einen Produktausdruck der Eingänge selektiv produziert. **Fig. 1C** veranschaulicht ein bekanntes Beispiel, bei dem ein nicht-flüchtiger Speicher verwendet wird, um eine programmierbare NOR-Funktion zu bilden. Ein nicht-programmierbares n-Eingänge-NOR-Gatter kann dadurch gebildet werden, daß n-parallele Stufen des n-Kanal-Transistors **51** mit verschiedenen Eingangsanschlüssen (IT) **50** als Eingängen und gemeinsamen Produktanschlüssen (PT) **52** als Ausgang mit Vds (**53**) auf Masse gelegt vorgesehen sind. Für den programmierbaren Fall zeigt **Fig. 1C** unter Verwendung der Transistoren **54**, **55** und **56** und durch Einstellen der Zustände der gemeinsamen Gate-Leitung (CGL) **57**, der Wortauswahlleitung (WSL) **58** und der WDL **59**, daß der Knoten Vd **53** so programmiert werden kann, daß er entweder auf Masse gelegt oder schwimmend ist. Falls Vd **53** schwimmend ist, wird IT **50** abgetrennt, so daß er kein Eingang für die NOR-Struktur ist. Wenn Vd **53** auf Masse gelegt ist, ist IT **50** einer der NOR-Eingänge. Wenn n-parallele Strukturen der Bauelemente der **Fig. 1C** mit gemeinsamen PTs (**52**) und individuell gesteuerten Vds (**53**) so konzipiert sind, daß sie entweder auf Masse gelegt oder schwimmend sind, kann eine m-Eingänge-NOR-Funktion programmiert werden, in der m kleiner oder gleich n ist. Die Eingangssignale gehen zu den ITs (**50**), und die NOR-Funktion wirkt auf die Transistoren **51**, bei denen die zugehörigen Vds (**53**) auf Masse gelegt sind. Der sich ergebende Ausgang der m-Eingänge-NOR ist der gemeinsame Produktausdruck **52**.

**[0005]** Wie es aus den obigen Beispielen zu erkennen ist, werden die beschriebenen bekannten Bauelemente verwendet, um programmierbare n-Eingänge- sowie Ein-Ausgang-Logikfunktionen mit unidirektionalem Signalfluß zu bilden. Es gibt jedoch weitere Probleme mit den bekannten Bauelementen. Diese Probleme werden unter Bezugnahme auf **Fig. 2-5** erläutert.

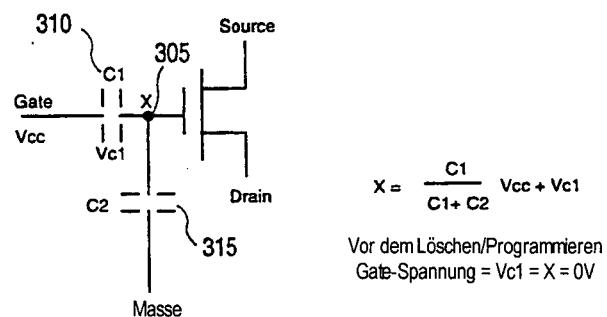

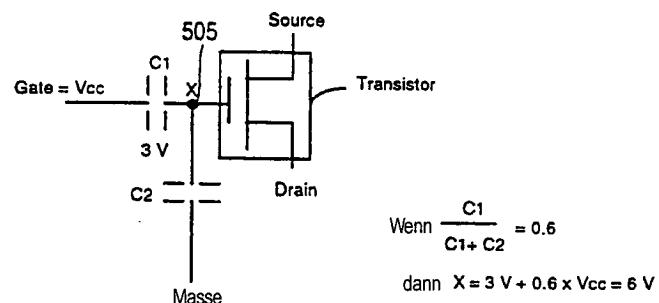

**[0006]** **Fig. 2** zeigt einen allgemein bekannten nicht-flüchtigen n-Kanal-Transistor in symbolischer Form. **Fig. 3** veranschaulicht denselben nicht-flüchtigen n-Kanal-Transistor in einer vereinfachten Kondensator-Modell-Form, die ein Modell mit einem Kondensator der schwimmenden Ladung sowie einem Substratkondensator darstellt. Es ist allgemein be-

kannt, daß die Spannung bei dem (als ein X dargestellten) Knoten **305** der Quotient der Kapazität des Kondensators der schwimmenden Ladung **310** geteilt durch die Summe der Kapazitäten des Kondensators der schwimmenden Ladung **310** und der Kapazität des Substratkondensators **315** (Kopplungsverhältnis) multipliziert mit der Gate-Spannung ist. Vor der Programmierung sind alle Spannungen Null.

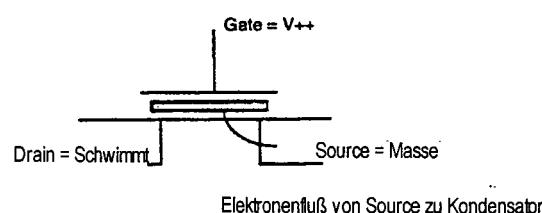

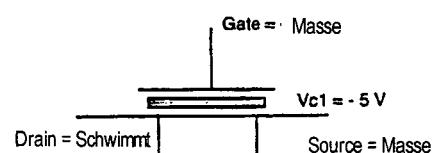

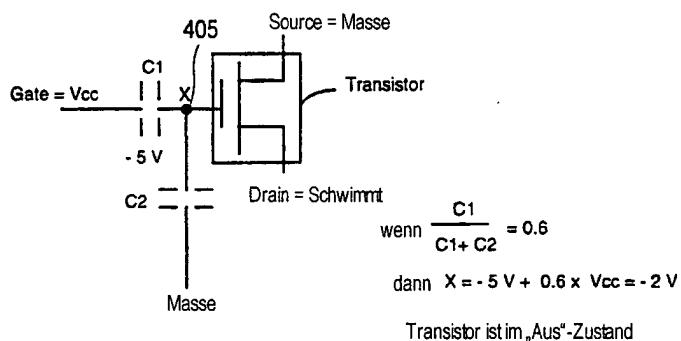

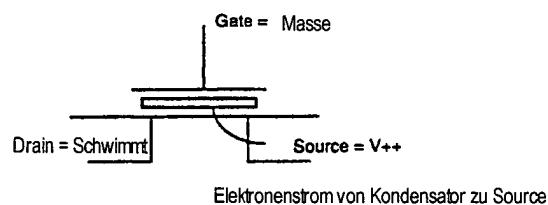

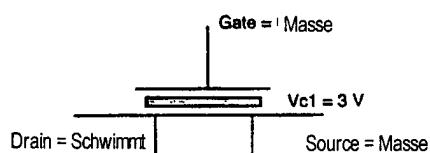

**[0007]** Während des Lösch-Modus ist das Gate, wie in **Fig. 4A** gezeigt, an die V++-Programmierspannung (Vpp) gelegt, damit Elektronen von dem Source-Anschluß zu dem Floating-Gate-Kondensator fließen können, was zu einer negativen Spannung auf dem Floating-Gate-Kondensator C1 führt. Wenn die Löschoperation beendet ist, werden die Source- und Gate-Anschlüsse auf Masse gelegt, so wie es in **Fig. 4B** gezeigt ist, und der geladene Floating-Gate-Kondensator C1 liegt bei -5 V. Im tatsächlichen Schaltungsbetrieb wird das Gate an Vcc gelegt, die 5 V beträgt (oder 3,3 V bei Niederspannungsbetrieb). In dem in **Fig. 4C** gezeigten Fall mit 5 V beträgt die Knotenspannung **405** - 2 V, was anzeigt, daß der Transistor sich im „Aus“-Zustand befindet, d. h. der Transistor ist nicht-leitend.

**[0008]** Eine Einzeltransistor-Struktur wie die oben beschriebene kann sowohl als ein nicht-flüchtiges Speicherelement als auch als ein Schalter verwendet werden, der zwei Leitungen verbindet oder trennt, was viel Platz auf dem Bauelementenchip spart. Das Mischen von Programmierleitungen und der Verdrahtungsleitungen bei den Source- und Drain-Knoten des Transistors führt jedoch zu Problemen, wenn ein Einzeltransistor für zwei Funktionen verwendet wird. Darüber hinaus stellt die Datenbewahrung ein Problem dar, wenn eine Einzeltransistor-Struktur verwendet wird.

**[0009]** Es gibt Lesestörungsprobleme, wenn das Durchlaßgatter leitend ist, um zwei Verbinder zu koppeln, was zu Datenhalte-Problemen führt. Ein nicht-flüchtiges Bauelement mit gespeicherter Ladung auf einem Floating-Gate hat möglicherweise einen Ladungsverlust über einen langen Zeitraum auf Grund von unerwünschtem Tunneln (Ladungsinjektion) durch das Tunneldielektrikum, das aus einem dünnen Oxid (typischerweise unter 100 Angström) besteht. Ein solches unerwünschtes Tunneln ist eine der Hauptursachen für den Verlust von Daten. Das Oxid ist dünn, um die Programmierung des Bauelements zu ermöglichen. Wenn das Bauelement nur als Speicher verwendet wird, stellt das Datenverlustpotential kein Problem dar, da die Datenlese-Operationen von kurzer Dauer sind. Die meisten Hersteller geben für normal verwendete Bauelemente typischerweise einen Mindestdatenbewahrungszeitraum von zehn Jahren an.

**[0010]** Das unerwünschte Tunneln kann jedoch

während der Leseoperation der Speicherzelle passieren, wenn das Bauelement sich im leitenden Modus befindet. Wegen des Spannungsunterschieds zwischen der Quelle bzw. Source und dem Gate wird ein Feld quer über das Dielektrikum eingeführt. Für die Speicherzelle ist diese Leseperiode sehr kurz und die Störung daher minimal. Bei Anwendungen, bei denen das Bauelement verwendet wird, um zwei Leiter zu verbinden, die Signale von/zu der Quelle zu/von dem Drain des Bauelements leiten, kann die Störung und somit das Tunneln quer über das Dielektrikum bedeutend sein, was in kurzer Zeit zu einem Fehler in dem Bauelement führen kann.

**[0011]** Weitere Beispiele bekannter Anordnungen sind in US-A-4573144 (Countryman), EP-A-0582319 (Advanced Micro Devices, Inc.) und EP-A-0085550 (Seeq Technology, Inc.) zu finden.

#### ZUSAMMENFASENDE DARSTELLUNG DER ERFINDUNG

**[0012]** Die vorliegende Erfindung stellt einen nicht-flüchtigen Schalter, der im Anspruch 1 spezifiziert wird, sowie ein Verfahren zum Betreiben dieses Schalters, das im Anspruch 11 spezifiziert wird, zur Verfügung. Der nicht-flüchtige Schalter ersetzt die frühere Verwendung eines SRAM-Bits und eines zugehörigen Durchlaßgatters, was den Siliziumbereich und somit die Kosten reduziert.

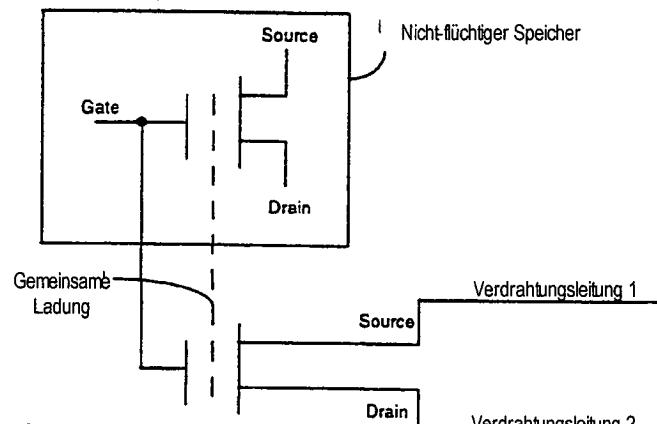

**[0013]** Bei einer Ausführungsform verwendet der bidirektionale Durchlaßgatter-Schalter eine Technologie wie beispielsweise einen elektrisch löschen- und programmierbaren Nur-Lese-Speicher (EEPROM) oder einen Flash-Speicher. Der Schalter enthält zwei EEPROM- oder Flash-Speicherbauelemente, wobei die Floating-Gates der Bauelemente gemeinsam benutzt werden. Der erste n-Kanal-Durchlaßgatter-Transistor wird zum Programmieren und Speichern des Zustands des Schalters verwendet. Das Oxid des ersten Transistors ist ein dünnes Oxid, um ein leichtes Programmieren zu ermöglichen. Der zweite n-Kanal-Durchlaßgatter-Transistor funktioniert als bidirektionaler Schalter, wobei die Source- und Drain-Anschlüsse mit den selektiv zu verbindenden Verdrahtungsleitungen (routing lines) gekoppelt werden. Das zweite Transistor-Oxid ist ein dickes Oxid, um den Leckstrom auf Grund von Tunneln zu minimieren. Die Programmierleitungen und die Verdrahtungsleitungen sind somit getrennt, was das Programmierverfahren vereinfacht und den Leckstrom minimiert.

#### KURZBESCHREIBUNG DER ZEICHNUNGEN

**[0014]** **Fig. 1A** veranschaulicht ein bekanntes Beispiel eines nicht-flüchtigen Speicherschalters mit einem unidirektionalen Signalweg. **Fig. 1B** zeigt ein weiteres bekanntes Beispiel, bei dem die logische 0

und die logische 1 separat gesteuert werden, um einen unidirektionalen Signalweg zu erwirken. **Fig. 1C** zeigt ein bekanntes Beispiel mit einer Vier-Transistor-Struktur.

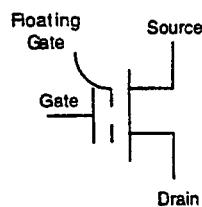

**[0015]** **Fig. 2** zeigt einen allgemein bekannten nicht-flüchtigen n-Kanal-Transistor in symbolischer Form.

**[0016]** **Fig. 3** zeigt den nicht-flüchtigen n-Kanal-Transistor der **Fig. 2** mittels einer Modelldarstellung mit einem Kondensator der schwimmenden Ladung und einem Substratkondensator.

**[0017]** **Fig. 4A** veranschaulicht ein Bauelement während des Löschmodus. **Fig. 4B** veranschaulicht ein Bauelement nach dem Löschen. **Fig. 4C** zeigt ein Bauelement gemäß dem Kondensatormodell, wenn das Bauelement sich im „Aus“-Zustand befindet.

**[0018]** **Fig. 5A** veranschaulicht ein Bauelement während des Programmier-Modus. **Fig. 5B** veranschaulicht das Bauelement nach dem Programmieren. **Fig. 5C** veranschaulicht ein Bauelement gemäß dem Kondensatormodell, wenn das Bauelement sich im „Ein“-Zustand befindet.

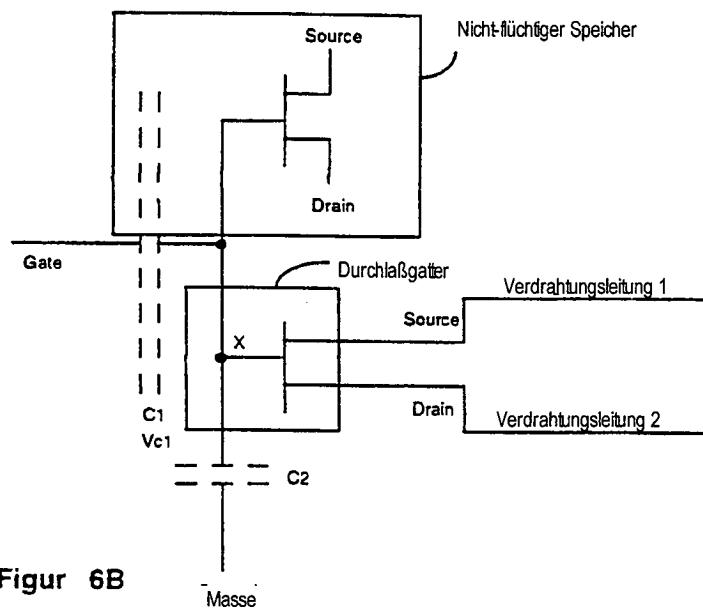

**[0019]** **Fig. 6A** und **6B** veranschaulichen Ausführungsformen des nicht-flüchtigen bidirektionalen Schalters der vorliegenden Erfindung.

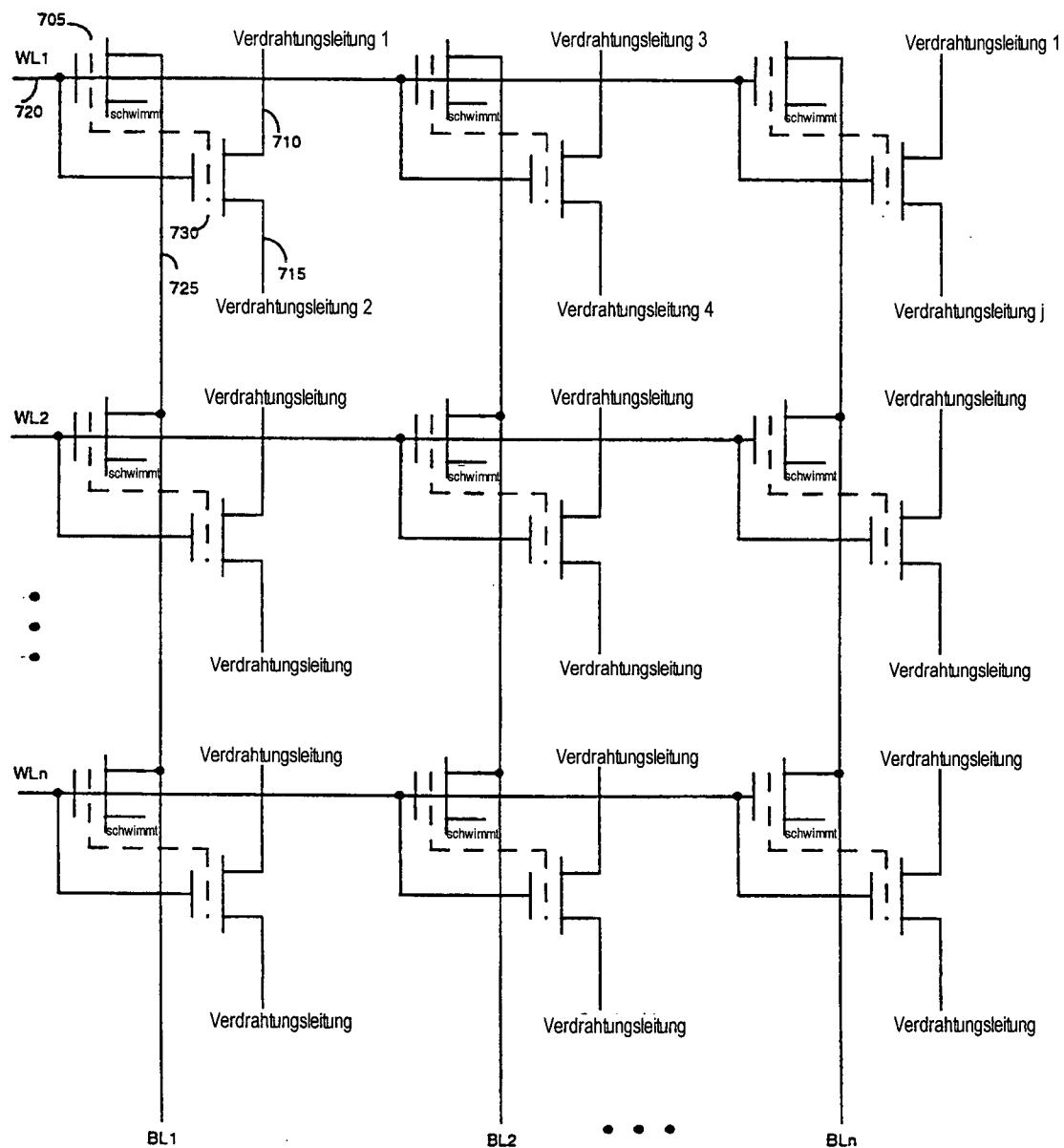

**[0020]** **Fig. 7** veranschaulicht ein Array nicht-flüchtiger bidirektionaler Schalter gemäß den Lehren der vorliegenden Erfindung.

**[0021]** **Fig. 8** ist eine Tabelle, in der Beispieldaten aufgeführt sind, die an die Bit- und Wortleitungen eines Arrays von Schaltern angelegt werden, um den identifizierten Schalter ein und aus zu programmieren.

#### DETAILLIERTE BESCHREIBUNG DES BEVOR-ZUGTEN AUSFÜHRUNGSBEISPIELS

**[0022]** Zu Erläuterungszwecken werden in der nachfolgenden Beschreibung zahlreiche Einzelheiten erwähnt, damit die vorliegende Erfindung ganz verstanden wird. Für einen Fachmann ist es jedoch klar, daß diese speziellen Einzelheiten nicht erforderlich sind, um die vorliegende Erfindung auszuführen. An anderen Stellen werden bekannte elektrische Strukturen und Schaltungen in Blockdarstellungsform gezeigt, um die vorliegende Erfindung nicht unnötig zu verdecken.

**[0023]** Wie es nachstehend klar wird, hat der nicht-flüchtige Schalter der vorliegenden Erfindung einige klare Vorteile, einschließlich einer Verbesserung der Schalterdichte von 40% oder mehr gegenüber bekannten SRAMs mit derselben verfahrenstechnischen

nologischen Eigenschaftsgröße sowie Eliminierung eines Begleit-EPROM- oder -EEPROM-Bauelements für die Konfigurationsladung. Der nicht-flüchtige Schalter der vorliegenden Erfindung hat ferner Vorteile gegenüber bekannten nichtflüchtigen Speicherbauelementen, einschließlich verbesserter Datenbewahrung und bidirektionaler Verbindungen, ohne den Bedarf einer Spannungsregenerierungsschaltung. Der beschriebene nicht-flüchtige, bidirektionale Schalter der vorliegenden Erfindung verwendet n-Kanal-Transistoren; es ist jedoch zu erwarten, daß weitere Konfigurationen nicht-flüchtiger Transistoren verwendet werden können.

**[0024]** **Fig. 6A** und **6B** veranschaulichen eine Ausführungsform des nicht-flüchtigen bidirektionalen Durchlaßgatter-Schalters unter Verwendung einer Technologie wie z. B. dem elektrisch löschen- und programmierbaren Nur-Lese-Speicher (EEPROM), einschließlich eines Flash-Speichers.

**[0025]** Der Schalter enthält zwei Transistoren, wobei die Floating-Gates der beiden Transistoren gemeinsam benutzt werden. Der erste n-Kanal-Durchlaßgatter-Transistor wird zum Programmieren des Schalters verwendet und hat typischerweise ein dünnes Oxid von 50–100 Angström. Das dünne Oxid ermöglicht, daß eine ausreichende Ladung für eine lange Aufbewahrung von Daten auf das Floating-Gate gebracht wird. Darüber hinaus ermöglicht das dünne Oxid eine Programmierung bei typischen oder niedrigeren EEPROM-Programmierspannungen. Der zweite n-Kanal-Durchlaßgatter-Transistor funktioniert als ein bidirektionaler Schalter, der zwei Leiter, wie z. B. Verdrahtungsleitungen, in einer Matrix verbindet. Um den Leckstrom zu minimieren und die Datenbewahrung zu verbessern, besteht der zweite Transistor üblicherweise aus einem dicken Oxid (ca. 100–500 Angström).

**[0026]** Der bidirektionale nicht-flüchtige Schalter führt zu einer Konfiguration, in der die Programmierleitungen und die Verdrahtungsleitungen getrennt sind. Die Programmierleitungen werden zum Ausführen eines geradeaus gerichteten Programmierprozesses eines Abschnittes des Bauelements verwendet, das als ein herkömmlicher nicht-flüchtiger Schalter wirkt, z. B. ein Speicherbit. Ein zweiter Abschnitt des Bauelements enthält ein Durchlaßgatter-Bauelement aus dickem Oxid, das als bidirektionaler Durchlaßgatter-Schalter funktioniert, der mindestens zwei Signalleitungen verbindet und von dem Speicherbit gesteuert wird. Das sich ergebende Speicher-Durchlaßgatter-Bauelement ist viel kleiner als das vergleichbare SRAM-Durchlaßgatter-Bauelement. Neben der Chipgrößenverringerung eliminiert diese Ausführungsform ferner den Bedarf an einem Begleit-EPROM/EEPROM-Speicherbauelement zum Laden der Programmkonfiguration, was zu weiteren Einsparungen bezüglich des Platinenplatzes und der

Komponentenkosten führt.

**[0027]** Gemäß der in **Fig. 6B** veranschaulichten Ausführungsform wird das Programmierfenster auf [−5 V, 3 V] eingestellt, wobei die Kondensatorspannung bei C1 im Lösch-Modus auf −5 V aufgeladen wird und die Kondensatorspannung bei C1 im Programmier-Modus auf 3 V aufgeladen wird. Da die Spannung bei X 6 V beträgt, wenn das n-Kanal-Durchlaßgatter „ein“ ist, wird das Durchlaßgatter im wesentlichen über die Versorgungsspannung von 5 V „aufgeladen“, wodurch der Durchlaßwiderstand reduziert und die Schaltgeschwindigkeit verbessert wird. Da separate Transistoren mit gemeinsam benutzter Ladung und gemeinsam benutzten Gates verwendet werden, stellt die Datenbewahrung auf dem dünnen Oxid-Gate kein Problem dar, weil das „Lesen“ bei dem dicken Oxid-Gate stattfindet. Das Leckstromproblem ist wesentlich geringer bei dem dicken Gate wegen der Oxiddicke, was sowohl die Zuverlässigkeit als auch die Lebensdauer des programmierbaren Schalters erhöht.

**[0028]** Wie es oben angemerkt wurde, kann der oben beschriebene bidirektionale Schalter in einem programmierbaren Logikbauelement, wie z. B. einem anwenderprogrammierbaren Gate-Array (FPGA), verwendet werden. Die bidirektionalen Schalter werden zum selektiven Verbinden von Verdrahtungsleitungen in der FPGA-Struktur verwendet, um mehrere Logik- und kombinatorische Elemente miteinander zu verbinden, was zu einem Bauelement führt, das die programmierte Funktion ausführt.

**[0029]** **Fig. 7** veranschaulicht ein Array der oben beschriebenen nicht-flüchtigen bidirektionalen Schalter, das die im Stand der Technik verwendeten früheren SRAM-/Durchlaßgatter-Strukturen ersetzen soll. Jeder Schalter wird mit zwei Verdrahtungsleitungen gekoppelt, Schalter **730** wird beispielsweise mit den Verdrahtungsleitungen **710** und **715** gekoppelt. Um den Schalter derart zu programmieren, daß er mit den Verdrahtungsleitungen **710** und **715** verbunden ist, wird die entsprechende Wortleitung **720** auf Masse gelegt und die entsprechende Bitleitung **725** auf die Programmierspannung Vpp (z. B. 12 V) eingestellt. Die übrigen Wortleitungen werden auf einen Spannungspegel eingestellt, der ausreichend hoch ist, um ein versehentliches Programmieren der übrigen Bauelemente zu verhindern, z. B. auf Vcc (**5V**). Die übrigen Bitleitungen werden auf Masse gelegt. Nach der Programmierung werden alle Wortleitungen auf Vcc eingestellt (z. B. 5 V oder 3,3 V im Falle eines Niederspannungsbaulements), und alle Bitleitungen befinden sich in einem „Beliebig“-Zustand, der je nach den tatsächlichen Prozeßeigenschaften Vcc oder schwimmend sein kann. Der Transistor **705**, der das Speicherbit ist, wird folglich in den „Ein“-Zustand („1“) programmiert, was dazu führt, daß der programmierbare Schalter **730** (der ein dickes Gate-Oxid hat)

sich im leitenden Modus befindet und daher als eine Verbindung zwischen den Verdrahtungsleitungen **710** und **715** funktioniert, ohne daß es Datenhalte-Probleme wegen Leckstroms gibt.

**[0030]** Alle Bits in dem Array werden zu Beginn in einen „Aus“-Zustand durch eine Löschoperation programmiert, die dadurch ausgeführt wird, daß eine ausgewählte Wortleitung auf die Programmier-Vpp eingestellt wird, alle Bitleitungen auf Masse gelegt werden und die übrigen nicht ausgewählten Wortleitungen aus Masse gelegt werden. Dieser Schritt wird für jede Wortleitung wiederholt, bis alle Bits „gelöscht“ sind. Wenn das Array in einen Aus-Zustand initialisiert wird, werden ausgewählte Schalter programmiert, um durch das oben beschriebene Ein-Zustand-Programmier-Verfahren die gewünschte Zusammenschaltung bereitzustellen.

**[0031]** **Fig. 8** zeigt die Programmierfolge des Arrays nichtflüchtiger Schalter. Die in **Fig. 8** aufgeführten Werte werden vorzugsweise verwendet, indem alle Bits zuerst durch Nullstellung durch einen „Massenlösch“-Schritt „aus“ sind. Dieser Schritt kann mit einem geschriebenen „0“-Zustand verglichen werden, und das selektive Programmieren der Schalter kann mit dem „Ein“-Zustand verglichen werden, der dem Schreiben einer „1“ in die gewünschten Speicherbits ähnelt. Wenn alle programmierbaren Schalter durch das Programmieren der zugehörigen Speicherbits in den gewünschten „Ein“- oder „Aus“-Zustand gesetzt worden sind, sind die Programmierleitungen (wort- und Bitleitungen) nicht ausgewählt. Die Wortleitungen werden an Vcc gelegt und die Bitleitungen in einen „Beliebig“-Zustand gesetzt, der je nach den Eigenschaften der Prozeßtechnologie Vcc oder schwimmend sein kann.

**[0032]** Die Erfindung ist anhand der bevorzugten Ausführungsform beschrieben worden. Es ist klar, daß ein Fachmann anhand der obigen Beschreibung zahlreiche Alternativen, Modifikationen, Variationen und Verwendungen erkennen wird.

## Patentansprüche

1. Ein in einer anwenderprogrammierbaren integrierten Schaltung verwendeter nicht-flüchtiger bidirektionaler Schalter, aufweisend: ein erstes nicht-flüchtiges Transistorlement, das einen ersten Abschnitt eines Floating-Gate, der zum Teil durch ein erstes Oxid umgeben ist, einen ersten Gate-Anschluß, einen ersten Source/Drain-Anschluß und einen ersten Drain/Source-Anschluß aufweist, wobei das erste Oxid eine Dicke aufweist, die dünn genug ist, um zu ermöglichen, daß eine ausreichende Ladung für eine lange Bewahrung von Daten auf das Floating-Gate gebracht wird, indem Programmierspannungen an den ersten Gate-Anschluß und an den ersten Source/Drain-Anschluß angelegt wer-

den; ein zweites nicht-flüchtiges Transistorelement, das einen zweiten Abschnitt des Floating-Gates, der zum Teil durch ein zweites Oxid umgeben ist, einen zweiten Gate-Anschluß, einen zweiten Source/Drain-Anschluß und einen zweiten Drain/Source-Anschluß aufweist, wobei der zweite Source/Drain-Anschluß und der zweite Drain/Source-Anschluß mit einem ersten Leiter bzw. einem zweiten Leiter gekoppelt sind und wobei das zweite Oxid dazu dient, einen unerwünschten Leckstrom zu verhindern, wenn das Floating-Gate in einen "Ein"-Zustand programmiert ist, der den ersten Leiter und den zweiten Leiter miteinander verbindet, und der zweite Abschnitt des Floating-Gate auf eine höhere Spannung aufgeladen ist als die Versorgungsspannung der integrierten Schaltung; und wobei der erste Abschnitt des Floating-Gate des ersten nicht-flüchtigen Transistorelements und der zweite Abschnitt des Floating-Gate des zweiten nicht-flüchtigen Transistorelements miteinander verbunden sind.

2. Der nicht-flüchtige bidirektionale Schalter nach Anspruch 1, wobei das erste Oxid eine Dicke im Bereich von 50–110 Angström aufweist.

3. Der nicht-flüchtige bidirektionale Schalter nach Anspruch 1, wobei das zweite Oxid eine Dicke im Bereich von 100–500 Angström aufweist.

4. Der nicht-flüchtige bidirektionale Schalter nach Anspruch 1, wobei der erste Gate-Anschluß und der zweite Gate-Anschluß miteinander gekoppelt sind.

5. Der nicht-flüchtige bidirektionale Schalter nach Anspruch 1, wobei das Floating-Gate gelöscht wird, indem eine Programmierspannung  $V_{pp}$  an den ersten Gate-Anschluß angelegt und der erste Source/Drain-Anschluß auf Masse gelegt wird.

6. Der nicht-flüchtige bidirektionale Schalter nach Anspruch 5, wobei das Floating-Gate programmiert wird, indem der erste Gate-Anschluß auf Masse gelegt und der erste Source/Drain-Anschluß auf die Programmierspannung eingestellt wird.

7. Der nicht-flüchtige bidirektionale Schalter nach Anspruch 1, ferner umfassend:

ein Array nicht-flüchtiger bidirekionaler Schalter, die in Zeilen und Spalten angeordnet sind, wobei jeder Schalter programmierbar mit einem Paar von Verdrahtungsleitungen gekoppelt ist;

einen ersten Satz von Steuerleitungen, wobei jede Steuerleitung mit jedem ersten Gate-Anschluß und zweiten Gate-Anschluß jedes Schalters in einer Zeile gekoppelt ist;

einen zweiten Satz von Steuerleitungen, wobei jede Steuerleitung mit jedem ersten Source/Drain-Anschluß jedes Schalters in einer Spalte gekoppelt ist.

8. Das Array nach Anspruch 7, wobei die ersten und zweiten Gate-Anschlüsse miteinander gekoppelt sind.

9. Das Array nach Anspruch 7, wobei das Floating-Gate jedes Schalters einer ausgewählten Zeile gelöscht wird, indem eine Programmierspannung  $V_{pp}$  mit einer ersten ausgewählten Steuerleitung des ersten Satzes von Steuerleitungen, die mit der ausgewählten Zeile gekoppelt ist, angelegt und der zweite Satz von Steuerleitungen mit Masse gekoppelt wird und die ersten Steuerleitungen mit Ausnahme der ausgewählten Steuerleitung des Satzes von Steuerleitungen mit Masse gekoppelt werden.

10. Das Array nach Anspruch 7, wobei das Floating-Gate eines ausgewählten Schalters programmiert wird, indem eine ausgewählte erste Steuerleitung des ersten Satzes von Steuerleitungen, die mit einem Anschluß des ausgewählten Schalters gekoppelt ist, mit Masse gekoppelt wird, eine ausgewählte zweite Steuerleitung des zweiten Satzes von Steuerleitungen, die mit einem Anschluß des ausgewählten Schalters gekoppelt ist, mit der Programmierspannung gekoppelt wird, Steuerleitungen des ersten Satzes von Steuerleitungen mit Ausnahme der ausgewählten ersten Steuerleitung mit einem Spannungspegel gekoppelt werden, der ausreichend hoch ist, um ein versehentliches Programmieren nicht ausgewählter Bauelemente zu verhindern, und Steuerleitungen des zweiten Satzes von Steuerleitungen mit Ausnahme der ausgewählten zweiten Steuerleitung mit Masse gekoppelt werden.

11. Ein Verfahren zum Betreiben eines nicht-flüchtigen bidirekionalen Schalters in einer anwenderprogrammierbaren integrierten Schaltung, umfassend die Schritte:

Bereitstellen eines ersten nicht-flüchtigen Transistorelements mit einem ersten Abschnitt eines Floating-Gate, der zum Teil durch ein erstes Oxid umgeben ist, und einem ersten Gate-Anschluß, einem ersten Source/Drain-Anschluß und einem ersten Drain/Source-Anschluß, wobei das erste Oxid dazu dient, das Aufbringen einer ausreichenden Ladung auf das Floating-Gate für ein langes Halten von Daten zu ermöglichen, indem Programmierspannungen an den ersten Gate-Anschluß und den ersten Source/Drain-Anschluß angelegt werden, und eines zweiten nicht-flüchtigen Transistorelements mit einem zweiten Abschnitt des Floating-Gate, der zum Teil durch ein zweites Oxid umgeben ist, und einem zweiten Gate-Anschluß, einem zweiten Source/Drain-Anschluß und einem zweiten Drain/Source-Anschluß, wobei der zweite Source/Drain-Anschluß und der zweite Drain/Source-Anschluß mit einem ersten bzw. einem zweiten Leiter gekoppelt sind, wobei das zweite Oxid dazu dient, einen unerwünschten Leckstrom zu verhindern, wenn das Floating-Gate in einen "Ein"-Zustand programmiert ist, der den ersten Leiter

und den zweiten Leiter miteinander verbindet, der den ersten Gate-Anschluß und den zweiten Gate-Anschluß miteinander koppelt, und der zweite Abschnitt des Floating-Gate auf eine höhere Spannung als die Versorgungsspannung der integrierten Schaltung aufgeladen wird, wobei die Floating-Gates des ersten nicht-flüchtigen Transistorelements und des zweiten nichtflüchtigen Transistorelements miteinander verbunden sind;

Anlegen einer Programmierspannung VPP an den ersten Gate-Anschluß und Verbinden des ersten Source/Drain-Anschluß mit Masse, wenn das Floating-Gate gelöscht werden soll; und

Verbinden des ersten Gate-Anschluß mit Masse und Setzen des ersten Source/Drain-Anschluß auf die Programmierspannung, wenn das Floating-Gate programmiert werden soll.

Es folgen 7 Blatt Zeichnungen

## Anhängende Zeichnungen

Figur 1A

Figur 1B

Figure 1C

Figur 2

Figur 3

Figur 4A

Figur 4B

Figur 4C

Figur 5A

Figur 5B

Figur 5C

Transistor ist im „Ein“-Zustand

Figur 6A

Figur 6B

Figur 7

**Figur 8**

|                                                                                                                                                                                      | Wortleitung (WL)                     | Bitleitung (BL)                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------|

| Lösch-Modus („0“-Zustand)<br>Zeilenbreites Löschen<br><br>Ausgewählte Zeile(n)<br>Unausgewählte Zeile(n)                                                                             | V <sub>pp</sub><br>Masse †           | Masse<br>Masse                     |

| Programmier-Modus („1“-Zustand)<br>Bitleites Programmieren<br><br>Ausgewählte Wortleitung<br>Ausgewählte Bitleitung<br>Unausgewählte Wortleitung(en)<br>Unausgewählte Bitleitung(en) | Masse<br>—<br>V <sub>cc</sub> *<br>— | —<br>V <sub>pp</sub><br>—<br>Masse |

| Betrieb<br><br>Unausgewählte Leitungen                                                                                                                                               | V <sub>cc</sub>                      | ..                                 |

\*: Hebe den Spannungspegel hoch genug an, um ein versehentliches Programmieren anderer Einrichtungen in dem Array zu vermeiden.

\*\*: Nicht von Bedeutung, kann V<sub>cc</sub> oder schwimmend sein.