(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5076216号

(P5076216)

(45) 発行日 平成24年11月21日(2012.11.21)

(24) 登録日 平成24年9月7日(2012.9.7)

(51) Int.Cl.

G05B 19/05 (2006.01)

F 1

G 05 B 19/05

L

請求項の数 1 (全 8 頁)

(21) 出願番号 特願2007-316670 (P2007-316670)

(22) 出願日 平成19年12月7日 (2007.12.7)

(65) 公開番号 特開2009-140286 (P2009-140286A)

(43) 公開日 平成21年6月25日 (2009.6.25)

審査請求日 平成22年12月6日 (2010.12.6)

(73) 特許権者 000167288

光洋電子工業株式会社

東京都小平市天神町1丁目171番地

(74) 代理人 100086737

弁理士 岡田 和秀

(72) 発明者 伊東 太志

東京都小平市天神町1丁目171番地 光

洋電子工業株式会社内

審査官 佐藤 彰洋

最終頁に続く

(54) 【発明の名称】プログラマブルコントローラ

## (57) 【特許請求の範囲】

## 【請求項 1】

データをバイナリ式のフォーマット(内部フォーマット)で処理するCPUと、このCPUが実行するシーケンスプログラムを格納するプログラムメモリと、CPUがシーケンスプログラムの実行に際して扱うデータ等の格納に用いる内部メモリとを備えたプログラマブルコントローラであって、

上記プログラムメモリには、外部デバイスとの間で外部フォーマットのデータを送受するデータ送受ソフトウェアと、データのフォーマットを外部フォーマットから内部フォーマットに変換して上記内部メモリに格納し、上記内部メモリに格納したデータを読み出し、その読み出したデータを内部フォーマットから外部フォーマットに変換するデータフォーマット変換ソフトウェアと、上記シーケンスプログラムに基づく命令の実行により、上記データをバイナリ式で格納、読み出し処理するデータ処理ソフトウェアとが記憶されており、上記CPUは、

上記データ送受ソフトウェアに従い、外部デバイスから送信されてくるデータを受信し、

上記データフォーマット変換ソフトウェアと上記データ処理ソフトウェアに従い、受信したデータのフォーマットを外部フォーマットから内部フォーマットに変換すると共に、変換したデータを上記内部メモリに格納し、

上記データ処理ソフトウェアに従い、上記シーケンスプログラムに基づく命令の実行により、データをバイナリ式で格納、読み出し処理し、

上記データフォーマット変換ソフトウェアと上記データ処理ソフトウェアに従い、上記内部メモリからデータを読出すと共に、読出したデータのデータフォーマットを内部フォーマットから外部フォーマットに変換し、

上記データ送受ソフトウェアに従い、データを外部フォーマットで送信する、

ことを特徴とするプログラマブルコントローラ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えば内部で扱うデータ形式（フォーマット）がバイナリ式であるプログラマブルコントローラ（以下、PLCと称する）が、外部デバイスとの間で、上記フォーマットとは相違するフォーマットでデータを送受処理する方式に関するものである。 10

【背景技術】

【0002】

PLCと外部デバイスとで制御システムを構築した場合、PLCは、CPUと、システム制御プログラム（ファームウェア）や、ラダープログラム等のプログラムメモリや、入出力メモリ、内部リレーメモリ、データメモリ、等の内部メモリが、内部バスで相互接続され、CPUは、ラダープログラムをシステム制御プログラムに従い実行することで、外部デバイスである入出力機器を介して、被制御機器を制御する。この制御に際して、CPUは、内部メモリに格納されている各種データを参照しながらラダープログラムを実行する。このようなPLCでは、外部デバイスと通信線で接続して通信する場合、外部デバイスの通信仕様に合う通信プロトコルが必要である。このための通信プロトコルを内部で作成するようにしたPLCも提供されている（特許文献1参照）。 20

【0003】

ところで、PLCは、内部でデータを処理する場合、CPUが実行しやすいバイナリ式と、アプリケーションに依存し浮動小数点式と、の2種類でデータを処理することが一般的となっている。そして、外部デバイスとの通信プロトコルで扱うデータ形式には、例えば8ビットヘキサデシマル（Hex）、符号付き16ビットバイナリ、符号無し16ビットバイナリ、16ビットHex、16ビットBCD等、きわめて多様である。そのため、従来では、PLC内部に、外部デバイスとのデータ通信で扱う多様なフォーマットに合わせてフォーマットをバイナリ式に変換して対応している。 30

【0004】

しかしながら、上記データフォーマット変換は、PLC内のCPUに対してソフトウェア処理負荷が大きくなり、また、CPUが対応すべきプログラムサイズも増加するため、データのフォーマット変換にかかる時間が増加し、内部でのデータ処理速度が減少する（特許文献2参照。）。なお、データのフォーマット変換については、以下の特許文献も参照することができる。 40

【特許文献1】特開2002-189505号公報

【特許文献2】特開2005-235213号公報

【特許文献3】特開2005-092533号公報

【特許文献4】特開2003-208382号公報

【特許文献5】特開2004-318420号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明は、外部デバイスとの通信で扱うデータの多様なフォーマットに対応することができる一方で、PLC等の制御機器内部のCPUに対するソフトウェア処理負荷を軽減可能として内部でのデータ処理速度を向上できるようにしたものである。

【課題を解決するための手段】

【0006】

本発明によるプログラマブルコントローラは、データをバイナリ式のフォーマット（内 50

部フォーマット)で処理するCPUと、このCPUが実行するシーケンスプログラムを格納するプログラムメモリと、CPUがシーケンスプログラムの実行に際して扱うデータ等の格納に用いる内部メモリとを備えたプログラマブルコントローラであって、上記プログラムメモリには、外部デバイスとの間で外部フォーマットのデータを送受するデータ送受ソフトウェアと、データのフォーマットを外部フォーマットから内部フォーマットに変換して上記内部メモリに格納し、上記内部メモリに格納したデータを読み出し、その読み出したデータを内部フォーマットから外部フォーマットに変換するデータフォーマット変換ソフトウェアと、上記シーケンスプログラムに基づく命令の実行により、上記データをバイナリ式で格納、読み出し処理するデータ処理ソフトウェアとが記憶されており、上記CPUは、上記データ送受ソフトウェアに従い、外部デバイスから送信されてくるデータを受信し、上記データフォーマット変換ソフトウェアと上記データ処理ソフトウェアに従い、受信したデータのフォーマットを外部フォーマットから内部フォーマットに変換すると共に、変換したデータを上記内部メモリに格納し、上記データ処理ソフトウェアに従い、上記シーケンスプログラムに基づく命令の実行により、データをバイナリ式で格納、読み出し処理し、上記データフォーマット変換ソフトウェアと上記データ処理ソフトウェアに従い、上記内部メモリからデータを読み出すと共に、読み出したデータのデータフォーマットを内部フォーマットから外部フォーマットに変換し、上記データ送受ソフトウェアに従い、データを外部フォーマットで送信することを特徴とするものである。

#### 【0007】

本発明では、外部デバイスとの通信プロトコルで扱うデータ形式として、例えば8ビットヘキサデシマル(Hex)、符号付き16ビットバイナリ、符号無し16ビットバイナリ、16ビットHex、16ビットBCD等、きわめて多様であっても、PLCのCPUは、当該CPUが実行しやすいバイナリ式でデータを処理することができる所以、CPUはデータフォーマット変換を外部デバイスとのデータ送受時のみ、そのデータ送受ソフトウェアを実行するだけで済むからソフトウェア処理負荷が小さく済むと共に、内部ではデータを高速で処理することができ、高速なPLCを得ることができる。

#### 【発明の効果】

#### 【0008】

本発明によれば、外部デバイスとの通信データのフォーマットが多様であっても、内部CPUではバイナリ式でデータを扱うことが可能であるので、データフォーマット変換を要していたソフトウェア処理の負荷が軽減されCPUのデータ処理速度が向上し、結果として、高速なPLCを提供することができるようになる。

#### 【発明を実施するための最良の形態】

#### 【0009】

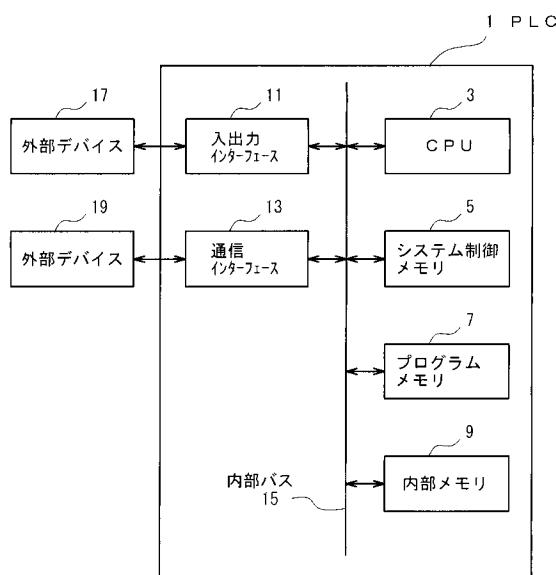

以下、添付した図面を参照して、本発明の実施の形態に係るPLCにおけるデータ送受処理方式を説明する。図1はPLC1の内部ブロック構成を示す。

#### 【0010】

図1を参照して、PLC1は、データを符号付き32ビットバイナリ式のフォーマット(内部フォーマット)と、32ビット浮動小数点でのフォーマットで処理してラダープログラムを実行するCPU3、システム制御プログラム(ファームウェア)を格納するROM等からなるシステム制御メモリ5、ラダープログラムやアプリケーションプログラム等を格納するRAM等からなるプログラムメモリ7、制御に使用する変数等のデータを記憶する内部メモリ9、入出力インターフェース11、通信インターフェース13を有し、これらは内部バス15で相互に接続されている。

#### 【0011】

入出力インターフェース11にはセンサやアクチュエータ等の各種入出力機器、機械や装置等の各種の被制御機器等の外部デバイス17が接続される。通信インターフェース13には、MODBUSで通信する外部デバイス19が接続される。

#### 【0012】

PLC1の内部メモリ9は、各種RAMから、例えば、入出力メモリ、内部リレーメモ

10

20

30

40

50

リ、データメモリ等を構成している。

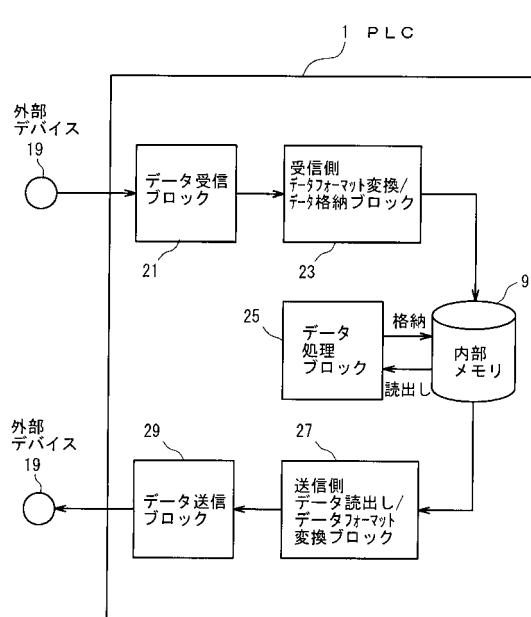

【0013】

図2は、外部デバイス19との間でMODBUSプロトコルでデータの送受を行う場合において、そのデータを内部メモリ9に格納したり読出したりするためのPLC1の内部機能ブロック構成を示す。

【0014】

この内部機能ブロックを構成するソフトウェア（アプリケーションプログラム）は、プログラムメモリ7にインストールされている。

【0015】

プログラムメモリ7にインストールされているソフトウェアは、外部デバイス19との間で外部フォーマットのデータを送受するデータ送受ソフトウェア、データのフォーマットを外部フォーマットから内部フォーマットに変換して内部メモリ9に格納し、内部メモリ9に格納したデータを読み出し、その読み出したデータを内部フォーマットから外部フォーマットに変換するデータフォーマット変換ソフトウェア、上記シーケンスプログラムに基づく命令の実行により、上記データを上記バイナリ式で格納、読み出し処理するデータ処理ソフトウェア、等である。

【0016】

図2に示す機能ブロックにおいて、21は、外部デバイス19からMODBUSで送信されてくるデータを受信するデータ受信ブロックである（データ送受ソフトウェアに対応する）。

【0017】

23は、データ受信ブロック21で受信したデータのフォーマットを外部フォーマットから内部フォーマットに変換すると共に、変換したデータを内部メモリ9に格納するデータフォーマット変換/データ格納ブロックである（データフォーマット変換ソフトウェア、データ処理ソフトウェアに対応する）。

【0018】

25は、シーケンスプログラムに基づく命令の実行により、データをバイナリ式で格納、読み出し処理するデータ処理ブロックである（データ処理ソフトウェアに対応する）、

27は、内部メモリ9からデータを読み出すと共に、読み出したデータのデータフォーマットを内部フォーマットから外部フォーマットに変換するデータ読み出し/データフォーマット変換ブロックである（データフォーマット変換ソフトウェア、データ処理ソフトウェアに対応する）。

【0019】

29は、データを外部フォーマットで送信するデータ送信ブロックである（データ送受ソフトウェアに対応する）。

【0020】

そして、CPU3は、上記プログラムメモリ7にダウンロードされたソフトウェアに従い、データ受信ブロック21、データフォーマット変換/データ格納ブロック23、データ処理ブロック25、データ読み出し/データフォーマット変換ブロック27、データ送信ブロック29の実行機能を有して、MODBUSデータの送受処理を実行する。

【0021】

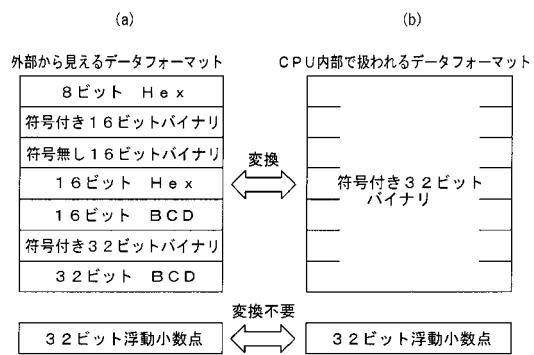

図3を参照して、外部デバイス19からPLC1を見た場合のデータフォーマットは、図3(a)の表に示すように、8ビットヘキサデシマル(Hex)、符号付き16ビットバイナリ、符号無し16ビットバイナリ、16ビットHex、16ビットBCD、符号付き32ビットバイナリ、32ビットBCD、ならびに32ビット浮動小数点である。一方、PLC1のCPU3内部で扱うデータは、図3(b)の表に示すように、符号付き32ビットバイナリと32ビット浮動小数点である。そして、図2で示すように、PLC1のデータ受信ブロック21は、外部デバイス19から図3(a)の表に示すフォーマットのデータを受信する。また、データ送信ブロック29は、外部デバイス19に図3(a)の表に示すフォーマットのデータを送信する。この場合、データ受信ブロック21とデータ

10

20

30

40

50

送信ブロック 29 では、通信設定条件として、センサやアクチュエータ等の各種入出力機器、機械や装置等の各種の被制御機器等の当該 PLC 1 をサポートする外部デバイス 17 との通信のための内部通信プロトコル (IMM プロトコル) と、外部デバイス 19 との MODBUS による通信プロトコルとにより、データ受信、データ送信することが可能になつている。

【0022】

受信側データフォーマット変換 / データ格納ブロック 23 では、受信データを図 3 (a) の表に示すデータフォーマットから図 3 (b) の表に示すデータフォーマットに変換する。この場合、浮動小数点は変換不要である。また、外部デバイス 17 の場合は、PLC 1 と同様に、符号付き 32 ビットバイナリであれば、変換不要である。

10

【0023】

そして、受信側データフォーマット変換 / データ格納ブロック 23 は、符号付き 32 ビットバイナリに変換したデータを内部メモリ 9 に格納する。データ処理ブロック 25 では、シーケンスプログラムであるラダープログラムの命令実行に伴い扱うデータを処理したり各種演算をして内部メモリ 9 にデータを格納したり読出したりする。

【0024】

送信側データ読み出し / データフォーマット変換ブロック 27 では、内部メモリ 9 からデータを読み出すと共に、その読み出したデータを外部デバイス 19 との間での通信プロトコルに対応したデータフォーマットに変換する。例えば、外部デバイス 19 が 8 ビット Hex であれば、内部メモリ 9 に格納している符号付き 32 ビットバイナリ式のデータを 8 ビット Hex に変換する。

20

【0025】

こうしてフォーマットを変換されたデータは、データ送信ブロック 29 から外部デバイス 19 に送信される。

【0026】

以上説明したように本実施の形態では、外部デバイス 19 との通信プロトコルで扱うデータフォーマットが多様であっても、PLC 1 の CPU 3 は、当該 CPU 3 が実行しやすいバイナリ式でデータを処理することができるので、CPU 3 はデータ送受処理に必要なソフトウェア処理負荷が小さく済むようになり、内部でデータを高速で処理することができ、高速な PLC を得ることができる。

30

【図面の簡単な説明】

【0027】

【図 1】図 1 は本発明の実施の形態に係る PLC の概略構成を示す図である。

【図 2】図 2 は図 1 の PLC の機能ブロック構成を示す図である。

【図 3】図 3 (a) は外部デバイスから見たデータフォーマットを示す表図、図 3 (b) は PLC の CPU 内部で扱うデータフォーマットを示す表図である。

【符号の説明】

【0028】

1 PLC (プログラマブルコントローラ)

40

3 CPU

5 システム制御メモリ

7 プログラムメモリ

9 内部メモリ

11 入出力インターフェース

13 通信インターフェース

17, 19 外部デバイス

21 データ受信ブロック

23 受信側データフォーマット変換 / データ格納ブロック

25 データ処理ブロック

27 送信側データ読み出し / データフォーマット変換ブロック

50

## 29 データ送信ブロック

【図1】

【図2】

【図3】

---

フロントページの続き

(56)参考文献 特開2002-189505(JP,A)

特開昭63-098054(JP,A)

特開2001-255909(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 05 B 19 / 05