**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) . Int. Cl.<sup>7</sup>

H01L 27/088

(11) 공개번호 10-2005-0086701

(43) 공개일자 2005년08월30일

|             |                            |

|-------------|----------------------------|

| (21) 출원번호   | 10-2005-7008870            |

| (22) 출원일자   | 2005년05월17일                |

| 번역문 제출일자    | 2005년05월17일                |

| (86) 국제출원번호 | PCT/US2003/032782          |

| 국제출원일자      | 2003년10월14일                |

|             | (87) 국제공개번호 WO 2004/049445 |

|             | 국제공개일자 2004년06월10일         |

(30) 우선권주장 10/301,617 2002년11월22일 미국(US)

(71) 출원인 어드밴스드 마이크로 디바이시즈, 인코포레이티드

미국 캘리포니아 94088-3453 서니베일 원 에이 엠디 플레이스 메일 스텝68

(72) 발명자 크리보카프 조란

미국 캘리포니아 95050 산타 클라라 데 베로나 플레이스 2321

안 주디 질린

미국 캘리포니아 95129 산 호세 레인트리 코트 905

린 링-렌

미국 캘리포니아 95014 쿠퍼티노 산타 테레사 드라이브 10970

왕 하이홍

미국 캘리포니아 94555 프레몬트 도나휴 테라스 34170

(74) 대리인 박장원

**심사청구 : 없음**

**(54) 2개의 트랜지스터로 구성된 NOR 디바이스**

**요약**

본 발명은 종래 4개의 트랜지스터로 구성된 NOR 게이트 대신에 2개의 비대칭 FinFET 형 트랜지스터(801, 802)로 구성된 NOR 게이트를 제시한다. 4개에서 2개로의 트랜지스터 수를 감소시킴으로써 집적 반도체 회로를 크게 개선시킬 수 있다.

**대표도**

도 8

**명세서**

**기술분야**

본 발명은 일반적으로 반도체 제조 및 반도체 디바이스에 관한 것으로, 더욱 상세히는 더블 게이트(double gate) 모스 전계 효과 트랜지스터(MOSFET: metal-oxdie semiconductor field-effect transistor)에 관한 것이다.

## 배경기술

MOSFET와 같은 트랜지스터들은 대다수의 반도체 디바이스들에서 핵심 구성 요소이다. 고성능 프로세스와 같은 일부 반도체 디바이스들은 수백만 개의 트랜지스터들을 포함할 수 있다. 일반적으로 반도체 제조 분야에서는 트랜지스터의 크기를 감소시켜, 밀도를 증가시키는 것이 중요사항이여 왔다.

일반적으로 MOSFET은 50nm 스케일(scale) 이하로 가공 공정 하는데 어려움을 가지고 있었다. 50nm 이하의 MOSFET을 개발하기 위해서, 더블-케이트 MOSFET이 제안되어 왔다. 많은 점에서, 상기 더블-케이트 MOSFET은 종래의 벌크 실리콘(bulk silicon) MOSFET들 보다 나은 특성을 제공한다. 이는 종래의 MOSFET에서는 채널의 한 측에서만 게이트 전극을 갖는 데 반해, 상기 더블-케이트 MOSFET는 채널의 양측 상에 게이트 전극(electrode)을 가지기 때문에 개선될 수 있는 것이다. 2개의 게이트가 존재할 때, 드레인(drain)에 의해 발생된 전기장(electric field)은 채널의 소스(source) 종단으로부터 보다 잘 스크린(screen) 된다. 또한, 2개의 게이트들은 싱글 게이트보다 대략 2배의 전류를 제어할 수 있고, 이에 따라 강력한 스위칭 시그널을 만든다.

반도체 디바이스 상의 트랜지스터들은 종종 고 레벨 논리 게이트를 구현하는 그룹들 내에 연결된다. 논리 게이트로 종종 사용되는 것 중 하나는 NOR 게이트이다. 종래에는 4개의 더블-케이트 MOSFET처럼 4개의 트랜지스터가 NOR 게이트를 형성하기 위해서 사용되었다.

반도체 디바이스의 전체 효율성을 증가시키기 위해서는, NOR 게이트와 같은 논리 게이트를 보다 효율적으로 구현하는 것이 바람직하다.

## 발명의 상세한 설명

본 발명에 따른 구현은 단지 2개의 트랜지스터만으로 구현되는 NOR 게이트를 포함한다.

본 발명의 일 양상은 집적 반도체 디바이스에 관한 것이다. 상기 디바이스는 다수의 비대칭 FinFET들을 포함하며, 여기서 상기 FinFET들 중 적어도 하나는 논리 NOR 게이트를 정의하는 FinFET들의 쌍으로 배열된다.

본 발명의 제 2 양상은 제 1 더블-케이트 트랜지스터와 제 2 더블-케이트 트랜지스터로 구성된 논리 NOR 게이트에 관한 것이다. 상기 제 1 및 제 2 트랜지스터에 연결된 출력 신호는 제 1 및 제 2 트랜지스터에 연결된 2개의 입력 신호의 논리 NOR 동작을 반영한다.

## 도면의 간단한 설명

하기는 첨부된 도면에 관한 참조가 기술되어 있으며, 동일 부호를 갖는 구성 요소들은 동일한 구성 요소들을 나타내는 것이다.

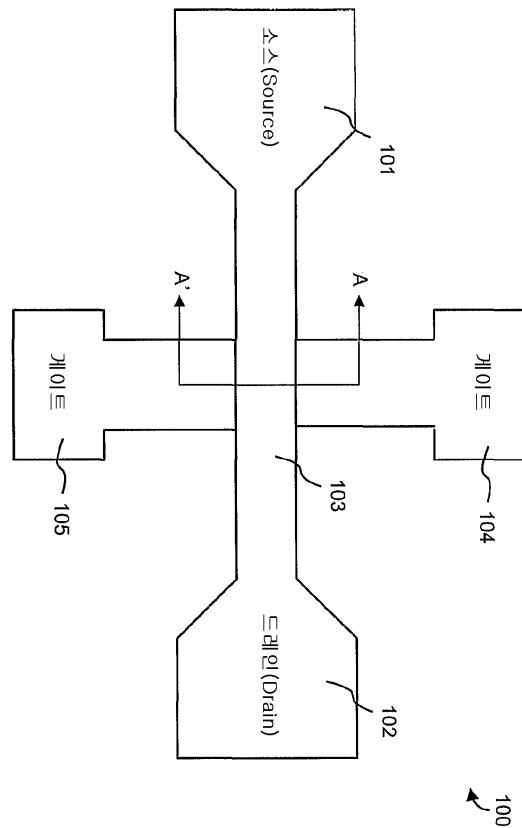

도 1은 본 발명의 원리를 따르는 FinFET의 평면도를 도시하는 개요도이다.

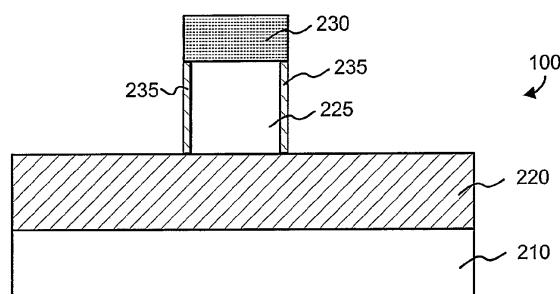

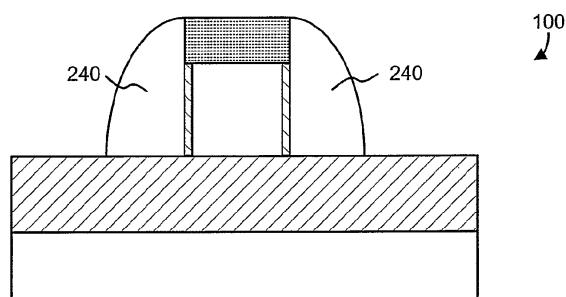

도 2- 7은 비대칭 FinFET를 형성하는 방법을 도시하는 도 1 내의 라인 A-A'따라 도시한 개요도이다.

도 8은 본 발명에 따른 방법으로 구성된 NOR 게이트의 평면도를 도시하는 개요 도이다.

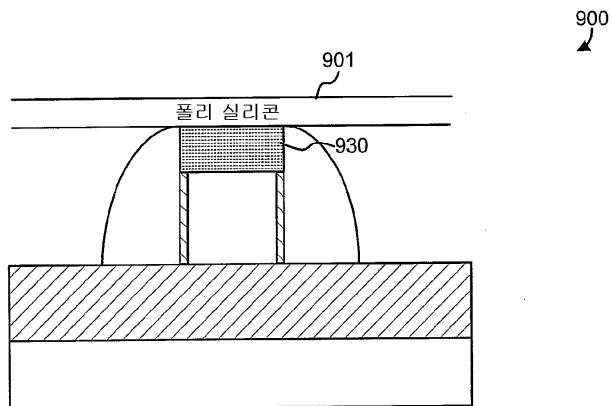

도 9는 FinFET의 2 개의 게이트 부분에 대한 폴리실리콘의 증착을 도시하는 도이다.

## 실시예

본 발명에 대한 하기의 설명은 첨부된 도를 참조하여 기술된다. 동일 부호는 동일 또는 유사한 구성요소를 구별하기 위하여 다른 도에서 사용될 수도 있다. 또한, 본 발명은 하기의 설명에 의해 제한되는 것은 아니며, 본 발명의 범위는 청구 범위와 이와 균등한 균등물에 의해 한정된다.

2 개의 트랜지스터들이 NOR 게이트를 구현하기 위해서 서로 연결되어 있다. 상기 트랜지스터들 중 각각은 독립적으로 어드레스 지정이 가능한 2 개의 게이트들을 갖는 비대칭 FinFET일 수 있다.

## 비대칭 FinFET

전도 채널이 자기 정렬(self-aligned) 더블-게이트에 의해 제어되는 수직 Si "핀" 내에 형성되는 더블-게이트 MOSFET를 이하 비대칭 FinFET라 하며, 상기 FinFET들은 산업에 알려져 있는 것이다. 종래의 FinFET들이 일반적으로 "더블-게이트" MOSFET으로 기술되나, 2개의 게이트들은 전기적으로 연결되어 논리적으로 주소지정 가능한 싱글 게이트를 형성한다.

도 1은 본 발명의 원리를 따르는 FinFET(100)의 평면도이다. FinFET(100)는 소스 영역(101), 드레인(drain) 영역(102), 그리고 채널 영역(103)을 포함한다. 상기 채널 영역(103)은 하기에 도 2에 대한 참조로 기술된 트랜지스터의 핀을 포함한다. 게이트의 양 측면이 전기적으로 함께 연결되어 있는 종래의 FinFET들과는 다르게, 본 발명의 FinFET(100)은 부가적으로 주소지정 가능한 2개의 게이트-게이트(104) 및 게이트(105)-를 포함할 수 있다. 상기 게이트들은 추가로 비대칭으로 불순물이 도핑(doping)된다. 예를 들면, 하기에 더욱 상세히 기재될 바처럼, 게이트(104)는 n형 도우편트(dopant)(예컨대,  $As^+$  또는  $P^+$ )가 주입되고, 그리고 게이트(105)는 p형 도우편트(예컨대, B 또는  $BF_2$ )가 주입된다.

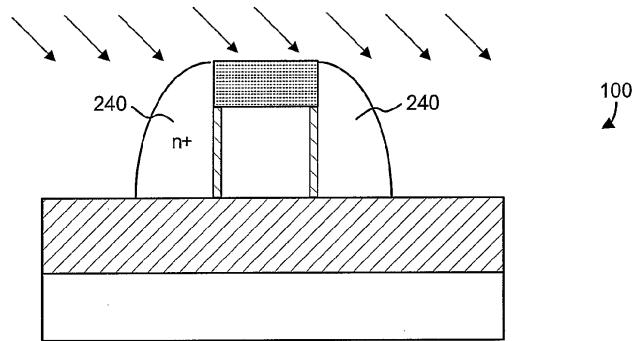

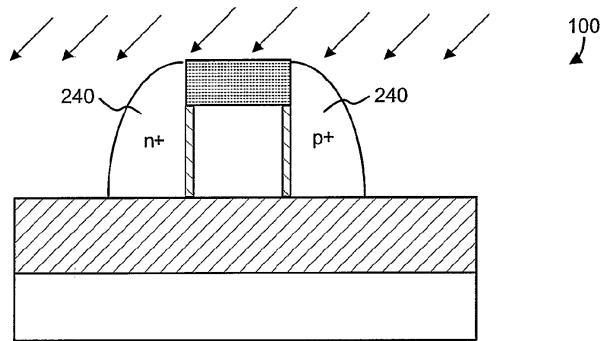

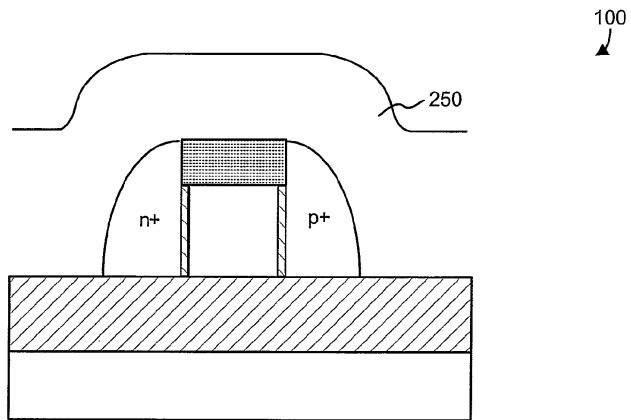

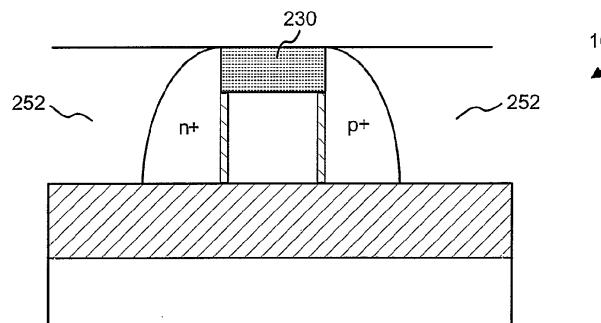

도 2-7은 도 1 내의 선 A-A'을 따라 그려진 횡단면이다. 도 2-8 각각은 FinFET(100)의 제조 공정 단계를 도시한다.

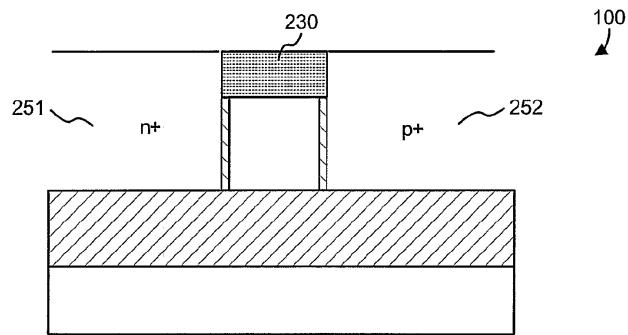

도 2를 참조하면, FinFET(100)는 실리콘 기판(210) 그리고 상기 실리콘 기판에 증착된 매몰 산화막(BOX: Buried Oxide) 층(210)을 포함하는 SOI(silicon on insulator)일 수 있다. 기판(210) 및 층(230)은 대안적으로, 게르마늄, 금속, 또는 실리콘-게르마늄(silicon-germanium)과 같은 합금일 수 있다. 매몰 산화막 층(220)은 종래의 방식대로 실리콘 기판(210)상에 형성될 수 있다. 예를 들면, 매몰 산화막 층(210)은 두께가 대략 200 nm에서 400nm 정도일 수 있다.

실리콘층은 BOX 층(220)상에 증착될 수 있고, 그리고 소스, 드레인, 및 핀(225)(소스 및 드레인은 도 2에 도시되어 있지 않음) 생성하기 위해 식각된다. 대안적으로, 소스/드레인 영역(101 및 102)은 실리콘을 증착하고, 그리고 상기 핀(225)가 형성된 후에 상기 실리콘을 식각함으로써 형성될 수 있다. 예를 들면, 일 실시예에서 핀(225)은 폭이 대략 5nm에서 25nm 정도가 될 수 있다. 핀(225)을 식각하기 전에  $Si_3N_4$  층(230)이 핀(225) 상의 화학 기상 증착(CVD: chemical vapor deposition)을 통하여 증착될 수 있다. 층(230)은 대안적으로  $SiO_2$  층일 수도 있다. 예를 들면, 층(230)은 가공 공정 동안 핀(225)을 보호하고, 대략 20-50nm 범위 두께로 증착될 수 있다.

핀(225)의 실리콘 표면을 산화시킴으로써, 게이트 유전체 층(dielectric layer)은 핀(225)의 측면에서 성장될 수 있다. 게이트 유전체 층(235)은 폭이 0.8nm에서 2nm정도로 얇을 수 있다.

도 3을 참조하면, 다음으로 폴리실리콘 스페이서(spacer)(240)가 종래의 증착 및 식각 기법을 사용하여 핀(225) 주위에 (그리고 게이트 유전체 층(235) 및 층(230) 주위에) 형성될 수 있다.

다음으로, 폴리실리콘 스페이서(240)에는 일명 주입(implant) 공정(도 4)을 사용하여 n형 도우편트가 주입된다. 예를 들면, 상기 도우편트는  $As^+$  또는  $P^+$  일 수 있고, 그리고 15에서 45도 사이의 기울기 각도에서 ( $P^+$ 에 대해서는) 3-6keV 또는 ( $As^+$ 에 대해서는) 12-15KeV 이온빔을 사용하여 주입될 수 있다. 게이트 유전체 층(235) 및 층(230)을 포함하는 핀 구조(225)가 존재하기 때문에, n형 도우편트는 폴리실리콘 스페이서(240)의 일 측면 진입으로부터 크게 가로막히게(예컨대, 도 5의 우측에 도시된 것처럼) 된다. 따라서, 2개의 폴리실리콘 스페이서들(240)은 n형 및 p형 도우편트로 비대칭으로 도핑(doping) 될 수 있다. 당업자는 도 4 및 5에 기술된 단계의 순서를 쉽게 변경할 수 있다는 것은 명백하다.

도 6을 참조하면, 도핑 되지 않은 폴리실리콘 층(250)이 이어서 FinFET(100)에 증착될 수 있다. 폴리실리콘 층(250)은 FinFET(100)의 게이트들을 형성할 것이다. 예를 들면, 층(250)은 대략 100nm의 깊이로 CVD를 통하여 증착될 수 있다.

상기 폴리실리콘 층(250)을 증착한 후에, FinFET(100)은 평탄화되어서 층(250)이 도 7A에 도시된 바와 같이 층(230)의 상부 표면과 실질적으로 평행하게 된다. 이는 층(251) 및 층(252)와 같은 전기적으로 연결되지 않은 2개의 폴리실리콘 층들을 산출한다. 이어서 FinFET(100)은 도 7B에 도시된 바와 같이, 충분히 규소화합된 폴리실리콘 층(251 및 252)을 생성하기 위해서 어닐링(annealing)된다. 층들(251 및 252)은 게이트 패드들(104 및 105)에 연결될 수 있고, 그리고 독립적으로 제어될 수 있다.

도 7B에 도시된 바와 같이 비대칭 FinFET들을 생성하기 위한 다른 공정들이 대안적으로 사용될 수도 있다. 예를 들면, 도 4 및 5에 관하여 기술된 경사 주입 공정은 폴리실리콘 게이트 재료가 증착되고 평탄화된 후에 수행될 수 있다. 각각의 경우에서, 구조의 결과는 도 7B에 도시된 바와 같이 개별적으로 제어가능한 2개의 게이트들을 포함한다.

### NOR 게이트

NOR 게이트는 집적회로에서 빈번하게 사용되는 논리 게이트이다. NOR 게이트는 2 이상의 입력 신호에 기초하여 값을 출력한다. 일반적으로, NOR 게이트는 4개의 트랜지스터를 사용하여 구성된다.

2개의 입력 NOR 게이트에 대한 로직은 하기의 테이블 1에 나타난다.

| 테이블 1 |      |    |

|-------|------|----|

| 입력 A  | 입력 B | 출력 |

| 0     | 0    | 1  |

| 0     | 1    | 0  |

| 1     | 0    | 0  |

| 1     | 1    | 0  |

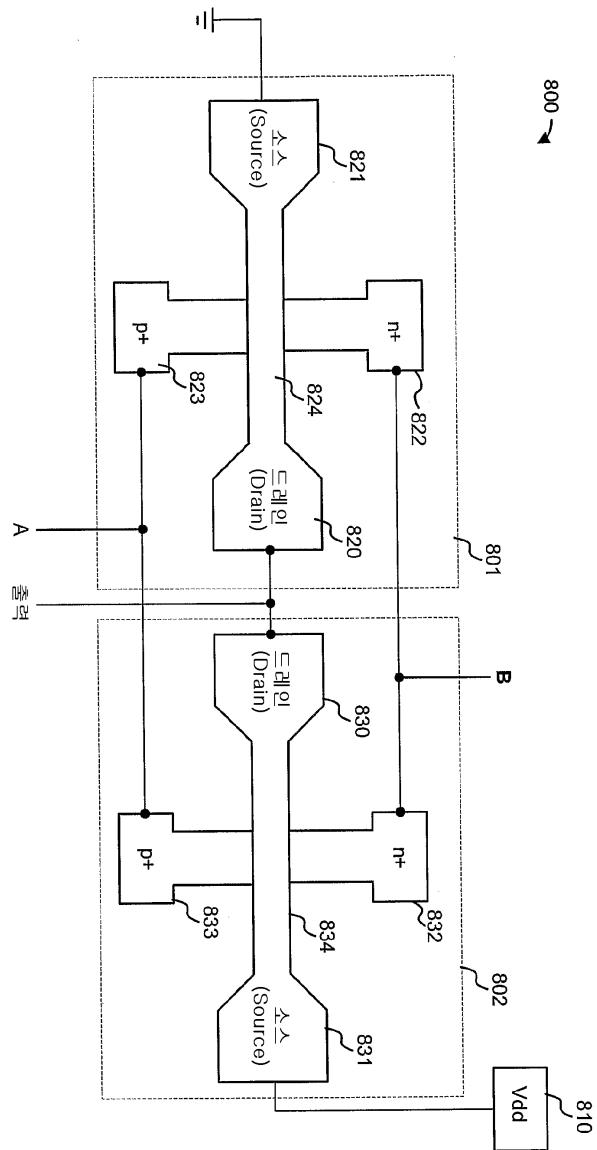

본 발명의 양상에 따라서, NOR 게이트는 2개의 비대칭 FinFET들을 사용하여 FinFET(100)처럼 구성된다. 도 8은 본 발명에 따른 방식으로 구성된 NOR 게이트(800)의 평면도이다. NOR 게이트(800)는 집적 반도체 디바이스 내에 위치될 수 있다.

NOR 게이트(800)는 2개의 FinFET들-FinFET(801 및 802)-을 포함한다. FinFET(801 및 802)들 중 각각은 FinFET(100)와 유사하다. 특히, FinFET(801)은 FinFET(100)과 유사하게 드레인 영역(820), 소스 영역(821), 제 1 게이트(822), 제 2 게이트(823), 그리고 채널 영역(834)을 포함한다. 제 1 게이트들(822 및 832)은 n형 불순물로 도핑 되지만, 제 2 게이트들(823 및 833)은 p형 불순물로 도핑된다.

도 8에서 도시된 바와 같이, 게이트들(822 및 833)은 전기적으로 연결될 수 있고; 게이트들(823 및 833)은 전기적으로 연결될 수 있고; 그리고, 소스(821)는 전기적으로 드레인(830)에 연결될 수 있다. 드레인(820)은 접지에 연결될 수 있고, 그리고 소스(831)는 전원(810)에 연결될 수 있다.

동작에서, NOR 게이트(800)에 대한 입력 신호 라인들(도 8의 입력 "A" 및 "B")은 전기적으로 연결된 게이트들의 제 1 및 제 2 쌍에 인가된다. 따라서, 입력 시그널 라인 A는 게이트들(823 및 833)에 연결될 수 있는 반면에, 입력 신호 라인(B)은 게이트들(822 및 832)에 연결될 수 있다. NOR 게이트(800)의 출력 신호는 소스(821)와 드레인(831) 사이에서 나온다. 상기 출력의 값은 테이블 1에 도시된 논리에 따라 입력 A 및 B에 의존한다.

### 추가적 개시

특정한 상황에서는, 싱글로 연결된 더블-게이트를 갖는 종래의 FinFET들과 독립적으로 주소지정이 가능한 2개의 게이트들을 갖는 비대칭 FinFET 모두를 포함하는 집적 회로를 생성하는 것이 바람직 할 수 있다. 이러한 상황에서는, 상기 FinFET들 모두는 도 2-7을 참조로 상술한 바처럼, 초기에 생성될 수 있다. 다음으로, 부가 선택적 에pitaxial 성장(additional selective epitaxial growth) 단계가 조래의 FinFET들이 될 FinFET들의 그것에 인가될 수 있다.

도 9는 FinFET(900)의 2개 게이트 부분에 대한 폴리실리콘의 증착을 도시한다. 폴리실리콘 층(901)은 싱글 연결 게이트 구조를 갖도록 설계된 집적 회로 내의 FinFET들의 그것 상에 선택적으로 형성될 수 있다. 예를 들면, 폴리실리콘 층(901)은 선택적 에피테셜(epitaxial) 성장에 의해 100nm 깊이로 형성될 수 있다.

다른 상황에서는, FinFET에 대한 쇼트키(Schottky) 형 소스/드레인 형성물을 형성하는 것이 바람직하다. 이는 편 상에 질화물층이 식각-멈춤처럼 사용되는 물결 무늬 접근법(damascene approach)을 사용하여 수행될 수 있다. 도 9를 참조하면, 폴리실리콘 층(901)이 질화물 층(930)에 대한 트렌치(trench)를 식각하기 위해 식각-멈춤처럼 사용될 수 있다. 실리콘을 제거한 후에, 트렌치는 소스/드레인 영역 상에 남게 된다. 다음으로, 금속은 증착되고, 멈춤 층과 같은 질화물 층(930)을 사용하여 폴리싱(polishing)된다. 상기 금속은 실리콘 채널을 갖는 쇼트키 접합을 형성 한다.

## 결론

종래 4개의 트랜지스터 대신에 2개의 FinFET 형 트랜지스터로 구현될 수 있는 NOR 게이트가 상술 되었다. 결국, 여기서의 NOR 게이트는 종래의 트랜지스터 수의 반을 사용하고, 그로 인해 게이트의 밀도 및 집적 실리콘 디바이스의 전반적인 기능에서 큰 개선을 가져온다.

전술된 설명에서, 본 발명의 이해를 돋고자 많은 특정한 세부사항들이 특정 재료, 구조, 화학물질, 공정, 등등과 같은 것들을 통하여 설명되었다. 그러나 본 발명은 여기에 설명된 특정한 세부사항들에 국한되지 않고 구현될 수 있다. 예를 들면, 저압 화학 기상 증착(LPCVD:low pressure chemical vapor deposition) 및 개선된 화학 기상 증착(ECVD:enhanced chemical vapor deposition) 공정을 포함하는, 다양한 형태의 화학 기상 증착(CVD:chemical vapor deposition)처럼 금속화 기법을 들 수 있다.

본 발명은 반도체 디바이스의 제조에 적용될 수 있는데, 특히는 100nm 혹은 100nm 이하의 설계 피처(feature)를 갖는 반도체 디바이스들에 적용될 수 있고, 이로 인해 트랜지스터 수, 회로 속도, 그리고 신뢰도를 향상시킬 수 있게 되었다. 본 발명은 반도체 디바이스의 다양한 형태들 중 어떠한 형태에나 적용될 수 있으나, 본 발명의 모호성을 회피하기 위해서 이에 대한 세부적인 내용은 기술되지 않았다. 본 발명을 구현하는데 있어서, 종래의 포토리토그래픽(photolithographic) 및 식각 기술이 사용되나, 이에 대한 세부적인 내용이 상기 상세한 설명에는 기술되지 않았다.

본 발명의 바람직한 실시예들 및 본 발명의 다재다능성의 소수 예들만이 상세한 설명에 기술되었다. 본 발명은 다양한 다른 조합으로 사용될 수도 있으며, 그리고 상술 된 발명 개념의 범위 내에서 수정이 가능하다.

## (57) 청구의 범위

### 청구항 1.

독립적으로 제어가능한 제 1 및 제 2 게이트 영역(811, 823), 소스 영역(821), 그리고 드레인 영역(820)을 포함하는 제 1 FinFET(801)와;

독립적으로 제어 가능핚 제 1 및 제 2 게이트 영역들(832, 833), 소스 영역(831), 그리고 드레인 영역(830)을 포함하는 제 2 FinFET(802)와;

상기 제 1 FinFET(801)의 제 1 게이트 영역(822) 및 상기 제 2 FinFET(802)의 제 1 게이트 영역(832)에 연결된 NOR 게이트의 제 1 입력 라인과;

상기 제 1 FinFET(801)의 제 2 게이트 영역(823) 및 상기 제 2 FinFET(802)의 제 1 게이트 영역(833)에 연결된 NOR 게이트의 제 2 입력 라인과; 그리고,

상기 제 1 FinFET(801)의 소스(820) 및 상기 제 2 FinFET(802)의 드레인(830)에 연결된 NOR 게이트의 출력 라인을 포함하는 NOR 게이트.

### 청구항 2.

제 1 항에 있어서,

상기 제 1 및 제 2 FinFET들의 제 1 게이트 영역들은 n형 불순물로 도핑(doping)되는 것을 특징으로 하는 NOR 게이트.

### 청구항 3.

제 2 항에 있어서,

상기 제 1 및 제 2 FinFET들의 제 2 게이트 영역들은 p형 불순물로 도핑되는 것을 특징으로 하는 NOR 게이트.

### 청구항 4.

제 1 항에 있어서,

상기 제 1 및 제 2 FinFET들은 상기 NOR 게이트 내에 포함되어 있는 오직 트랜지스터들만으로 이루어진 것을 특징으로 하는 NOR 게이트.

### 청구항 5.

다수의 FinFET들(801 및 802)를 포함하는 집적 반도체 디바이스로서, 여기서 상기 디바이스는:

다수의 FinFET들 중 적어도 일부는 논리 NOR 게이트들을 정의하는 FinFET들 의 쌍으로 배열되는 것을 특징으로 하는 다수의 FinFET들(801 및 802)를 포함하는 집적 반도체 디바이스.

### 청구항 6.

제 5항에 있어서, 상기 FinFET들의 쌍들은

독립적으로 제어가능한 제 1 및 제 2 게이트 영역(811, 823), 소스 영역(821), 그리고 드레인 영역(820)을 포함하는 제 1 FinFET(801)와;

독립적으로 제어 가능핚 제 1 및 제 2 게이트 영역들(832, 833), 소스 영역(831), 그리고 드레인 영역(830)을 포함하는 제 2 FinFET(802)와;

상기 제 1 FinFET(801)의 제 1 게이트 영역(822) 및 상기 제 2 FinFET(802)의 제 1 게이트 영역(832)에 연결된 NOR 게이트의 제 1 입력 라인과;

상기 제 1 FinFET(801)의 제 2 게이트 영역(823) 및 상기 제 2 FinFET(802)의 제 1 게이트 영역(833)에 연결된 NOR 게이트의 제 2 입력 라인과; 그리고,

상기 제 1 FinFET(801)의 소스(820) 및 상기 제 2 FinFET(802)의 드레인(830)에 연결된 NOR 게이트의 출력 라인을 포함하는 것을 특징으로 하는 다수의 FinFET들(801 및 802)를 포함하는 집적 반도체 디바이스.

### 청구항 7.

제 1 더블-게이트(double-gate) 트랜지스터(801); 그리고

제 2 더블-케이트 트랜지스터(802)를 포함하는 논리 NOR 회로로서, 여기서 제 1 및 제 2 트랜지스터에 연결된 출력 신호는 상기 제 1 및 제 2 트랜지스터에 인가된 2 개의 입력 신호들의 논리 NOR 동작을 반영하는 것을 특징으로 하는 논리 NOR 회로.

### 청구항 8.

제 7항에 있어서,

상기 제 1 및 제 2 더블-케이트 트랜지스터들은 FinFET들인 것을 특징으로 하는 논리 NOR 회로.

### 청구항 9.

제 7항에 있어서,

상기 제 1 및 제 2 더블-케이트 트랜지스터들 각각은:

제 1 게이트 영역(822 또는 832)와;

제 1 게이트 영역과 독립적으로 제어 가능하도록 구성된 제 2 게이트 영역(823 또는 832)와;

소스 영역(821 또는 831)과; 그리고,

드레인 영역(820 또는 830)을 포함하는 것을 특징으로 하는 논리 NOR 회로.

### 청구항 10.

제 9항에 있어서,

상기 제 1 게이트 영역은 n형 불순물로 도핑되는 것을 특징으로 하는 논리 NOR 회로.

**도면**

도면1

도면2

도면3

도면4

도면5

도면6

도면7A

도면7B

도면8

도면9