(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2015년12월31일

(11) 등록번호 10-1581969

(24) 등록일자 2015년12월24일

(51) 국제특허분류(Int. Cl.)

*H01L 23/60* (2006.01) *G05F 1/00* (2006.01)

*H01L 23/62* (2006.01)

(21) 출원번호 10-2010-7015023

(22) 출원일자(국제) 2008년12월10일

심사청구일자 2013년12월10일

(85) 번역문제출일자 2010년07월07일

(65) 공개번호 10-2010-0098680

(43) 공개일자 2010년09월08일

(86) 국제출원번호 PCT/US2008/086180

(87) 국제공개번호 WO 2009/088622

국제공개일자 2009년07월16일

(30) 우선권주장

11/971,591 2008년01월09일 미국(US)

(56) 선행기술조사문헌

US20060262469 A1\*

US7301741 B2\*

US20070025034 A1\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

프리스케일 세미컨덕터, 잉크.

미합중국 텍사스 (우편번호 78735) 오스틴 월리암

캐든 드라이브 웨스트 6501

(72) 발명자

카진스키, 마이클 지.

미국 78726 텍사스주 오스틴 브리스타 웨이 11209

매튜, 레오

미국 78717 텍사스주 오스틴 가리슨 씨클 15844

밀러, 제임스 더블유.

미국 78705 텍사스주 오스틴 웨스트 33번 스트리

트 209

(74) 대리인

양영준, 백만기

전체 청구항 수 : 총 18 항

심사관 : 정구원

(54) 발명의 명칭 M I G F E T 을 구비한 E S D 보호된 회로 및 E S D 보호된 회로에서의 방법

**(57) 요약**

정전기 방전(ESD) 보호된 회로(30)는 전원 전압 레일(VDD, VSS)에 연결되어 있으며, 다수의 독립 게이트 전계 효과 트랜지스터(MIGFET)(32, 34, 36, 38), 프리-드라이버(pre-driver)(60, 62) 및 핫 게이트 바이어스 회로(hot gate bias circuit)(40, 42)를 포함한다. MIGFET는 출력 패드(44, 46)와 전원 전압 레일 사이에 연결된 소스/드레인 경로, 제1 게이트 단자 및 제2 게이트 단자를 가진다. 프리-드라이버 회로는 출력을 갖는다. 핫 게이트 바이어스 회로는 MIGFET(34)의 제1 게이트 단자(68)에 연결되어 있으며, 프리-드라이버 회로(60)의 출력은 MIGFET의 제2 게이트 단자(64)에 연결되어 있다. 핫 게이트 바이어스 회로(40)는 ESD 사건 동안 MIGFET의 제1 게이트 단자에 바이어스 전압을 인가하도록 구성되며 이는 ESD 사건을 더 잘 견딜 수 있도록 MIGFET의 과괴 전압(breakdown voltage)을 증가시킨다.

## 대표도

## 명세서

### 청구범위

#### 청구항 1

전원 전압 레일(power supply voltage rail)에 연결된 정전기 방전(ESD; electrostatic discharge) 보호된 회로로서,

출력 패드와 상기 전원 전압 레일 사이에 연결된 소스/드레인 경로를 갖는 다수의 독립 게이트 전계 효과 트랜지스터(MIGFET; multiple independent gate field effect transistor) - 상기 MIGFET는 제1 게이트 단자와 제2 게이트 단자를 가짐 -;

출력을 갖는 프리-드라이버 회로(pre-driver circuit); 및

상기 MIGFET의 제1 게이트 단자에 연결된 핫 게이트 바이어스 회로(hot gate bias circuit) - 상기 프리-드라이버 회로의 출력은 상기 MIGFET의 제2 게이트 단자에 연결되고, 상기 핫 게이트 바이어스 회로는, ESD 사건 동안에 상기 MIGFET의 제1 게이트 단자에 바이어스 전압을 인가하도록 구성됨 -

를 포함하고,

상기 MIGFET는 상기 프리-드라이버의 출력에 응답하여 상기 출력 패드 상에서 신호를 제공하는, ESD 보호된 회로.

#### 청구항 2

제1항에 있어서,

상기 핫 게이트 바이어스 회로는 또한 상기 정전기 방전 사건을 검출하도록 구성되는, ESD 보호된 회로.

#### 청구항 3

제1항에 있어서,

상기 핫 게이트 바이어스 회로는, 상기 출력 패드에서의 전압과 동일한 바이어스 전압을 만들기 위해서 바이어스 전압을 인가하도록 구성되는, ESD 보호된 회로.

#### 청구항 4

제1항에 있어서,

상기 핫 게이트 바이어스 회로는 상기 MIGFET와 연관된 파괴 전압(breakdown voltage)을 올리기 위해서 바이어스 전압을 인가하도록 구성되는, ESD 보호된 회로.

#### 청구항 5

제1항에 있어서,

정전기 방전 사건을 검출하도록 구성된 정전기 방전(ESD) 검출 회로를 더 포함하며, 상기 ESD 검출 회로는 상기 핫 게이트 바이어스 회로에 연결되는, ESD 보호된 회로.

#### 청구항 6

제5항에 있어서,

상기 ESD 검출 회로는, 상기 정전기 방전 사건의 검출에 응답하여 상기 핫 게이트 바이어스 회로에 트리거 신호를 제공하도록 구성되고, 상기 핫 게이트 바이어스 회로는, 상기 트리거 신호에 응답하여 상기 MIGFET의 제1 게이트 단자에 상기 바이어스 전압을 인가하는, ESD 보호된 회로.

#### 청구항 7

제1 전원 전압 레일과 제2 전원 전압 레일에 연결된 정전기 방전(ESD) 보호된 회로로서,

출력 패드와 상기 제1 전원 전압 레일 사이에 연결된 소스/드레인 경로를 갖는 제1 다수의 독립 게이트 전계 효과 트랜지스터(MIGFET) - 상기 제1 MIGFET는 제1 게이트 단자와 제2 게이트 단자를 가짐 - ;

상기 출력 패드와 상기 제2 전원 공급 전력 레일 사이에 연결된 소스/드레인 경로를 갖는 제2 MIGFET - 상기 제2 MIGFET는 제1 게이트 단자와 제2 게이트 단자를 가짐 - ;

출력을 갖는 프리-드라이버 회로; 및

상기 제1 MIGFET의 제1 게이트 단자와 상기 제2 MIGFET의 제1 게이트 단자에 연결되는 게이트 바이어스 회로 -

상기 프리-드라이버 회로는 상기 제1 MIGFET의 제2 게이트 단자와 상기 제2 MIGFET의 제2 게이트 단자에 연결되고, 상기 게이트 바이어스 회로는, ESD 사건 동안 상기 제1 MIGFET의 제1 게이트 단자에 제1 바이어스 전압을 인가하고 상기 제2 MIGFET의 제1 게이트 단자에 제2 바이어스 전압을 인가하도록 구성됨 -

를 포함하고,

상기 제1 MIGFET는 프리-드라이버의 출력에 응답하여 상기 출력 패드 상에서 신호를 제공하는, ESD 보호된 회로.

#### 청구항 8

제7항에 있어서,

상기 게이트 바이어스 회로는 또한 상기 ESD 사건을 검출하도록 구성되는, ESD 보호된 회로.

#### 청구항 9

제7항에 있어서,

상기 게이트 바이어스 회로는, 상기 출력 패드에서의 전압과 동일한 제1 바이어스 전압을 만들기 위해 제1 바이어스 전압을 인가하도록 구성되는, ESD 보호된 회로.

#### 청구항 10

제7항에 있어서,

상기 게이트 바이어스 회로는, 상기 제1 MIGFET와 연관된 파괴 전압을 올리기 위해서 제1 바이어스 전압을 인가하고 상기 제2 MIGFET와 연관된 파괴 전압을 올리기 위해서 제2 바이어스 전압을 인가하도록 구성되는, ESD 보호된 회로.

#### 청구항 11

제7항에 있어서,

정전기 방전 사건을 검출하도록 구성된 ESD 검출 회로를 더 포함하며, 상기 ESD 검출 회로는 상기 게이트 바이어스 회로에 연결되는, ESD 보호된 회로.

#### 청구항 12

제11항에 있어서,

상기 ESD 검출 회로는, 상기 정전기 방전 사건의 검출에 응답하여 상기 게이트 바이어스 회로에 트리거 신호를 제공하도록 구성되고, 상기 게이트 바이어스 회로는, 상기 트리거 신호에 응답하여 상기 제1 MIGFET의 제1 게이트 단자에 상기 제1 바이어스 전압을 인가하며 상기 제2 MIGFET의 제1 게이트 단자에 상기 제2 바이어스 전압을 인가하는, ESD 보호된 회로.

#### 청구항 13

제7항에 있어서,

정상 동작 동안, 상기 게이트 바이어스 회로는, 상기 제1 전원 전압 레일과 동일한 제1 바이어스 전압을 만들기 위하여 상기 제1 MIGFET의 제1 게이트 단자에 제1 바이어스 전압을 인가하도록 구성되는, ESD 보호된 회로.

**청구항 14**

제7항에 있어서,

상기 제1 MIGFET는 n-형 트랜지스터이고, 상기 제2 MIGFET는 p-형 트랜지스터인, ESD 보호된 회로.

**청구항 15**

제1 전원 전압 레일과 제2 전원 전압 레일 사이에 연결된 정전기 방전(ESD) 보호된 회로에서의 방법으로서 - 상기 ESD 보호된 회로는, 출력 패드와 상기 제2 전원 전압 레일 사이에 연결된 소스/드레인 경로를 갖는 다수의 독립 게이트 전계 효과 트랜지스터(MIGFET)를 포함하고, 상기 MIGFET는 제1 게이트 단자와 제2 게이트 단자를 가짐 - ,

상기 MIGFET의 게이트가 입력 신호를 수신하는 것에 응답하여 상기 MIGFET의 소스/드레인 경로를 통해 상기 출력 패드 상에서 출력 신호를 제공하는 단계;

정상 동작 동안 상기 제2 전원 전압 레일과 동일한 제1 바이어스 전압을 만들기 위하여 상기 MIGFET의 제1 게이트 단자에 제1 바이어스 전압을 인가하는 단계; 및

ESD 사건 동안 상기 출력 패드에서의 전압과 동일한 제2 바이어스 전압을 만들기 위하여 상기 MIGFET의 제1 게이트 단자에 제2 바이어스 전압을 인가하는 단계

를 포함하는, ESD 보호된 회로에서의 방법.

**청구항 16**

제15항에 있어서,

상기 인가하는 단계들은, 상기 제1 바이어스 전압 및 제2 바이어스 전압을 인가하기 위해 바이어스 회로를 사용하는 것을 또한 특징으로 하며, 상기 ESD 사건을 검출하기 위해 상기 바이어스 회로를 사용하는 단계를 더 포함하는, ESD 보호된 회로에서의 방법.

**청구항 17**

제15항에 있어서,

상기 MIGFET와 연관된 파괴 전압을 올리기 위하여 상기 제2 바이어스 전압을 선택하는 단계를 더 포함하는, ESD 보호된 회로에서의 방법.

**청구항 18**

제15항에 있어서,

상기 정전기 방전 사건의 검출에 응답하여 핫 게이트 바이어스 회로에 트리거 신호를 제공하는 단계를 더 포함하며, 상기 핫 게이트 바이어스 회로는, 상기 트리거 신호에 응답하여 상기 MIGFET의 제1 게이트 단자에 상기 제2 바이어스 전압을 인가하는, ESD 보호된 회로에서의 방법.

**청구항 19**

삭제

**청구항 20**

삭제

**발명의 설명****기술 분야**

본 개시는 일반적으로, 통상 FinFET의 형태로 구현되는 다수의 독립 게이트 전계 효과 트랜지스터들(multiple independent gate field effect transistors; MIGFETs)에 관한 것으로, 보다 구체적으로는 MIGFET들에 대한 정전기 방전(electrostatic discharge; ESD) 보호에 관한 것이다.

## 배경 기술

[0002]

FinFET들과 같은 횡형 트랜지스터들(lateral transistors)을 만드는데 있어서, 핀들(fins)을 사용하면 주어진 표면적 하에서 회로의 성능을 향상시킬 가능성이 높아진다. 주어진 면적에서 더 많은 포텐셜 전류 드라이브(potential current drive)가 있도록, 채널 폭(channel width)은 수직의 깊이(vertical dimension)으로 측정된다. 그러나, 핀들(fins)의 사용이 ESD에 관련된 문제점들을 없애지는 않으며, 이에 따라 ESD 보호에 대한 필요성을 남아 있다.

[0003]

그러므로 FinFET들을 위한 효과적인 ESD 보호를 제공할 필요성이 있다.

## 발명의 내용

### 도면의 간단한 설명

[0004]

본 발명은 예를 통해 예시되며 첨부한 도면들에 의해 한정되는 것은 아니며, 첨부한 도면들에서 동일한 참조번호는 유사한 구성요소들을 가리킨다. 도면들에 있는 구성요소들은 간략하고 명료하게 그려졌고, 반드시 일정한 비율로 그려진 것은 아니다.

도 1은 블럭도와 단면도의 조합으로 나타낸 ESD 보호된 회로이다.

도 2는 도 1의 ESD 보호된 회로의 구현을 나타낸 회로도이다.

도 3은 도 1의 OR 게이트 및 핫 게이트(hot gate) 바이어스 회로들을 예시적으로 구현한 것을 나타낸 회로도이다.

### 발명을 실시하기 위한 구체적인 내용

[0005]

하나의 관점에서, ESD 보호된 회로는, 동일한 채널을 제어하는 제1 게이트와 제2 게이트를 가지는 입력 및/또는 출력 패드(I/O pad)에 연결된 다수의 독립 게이트 전계 효과 트랜지스터(MIGFET)(이는 출력 드라이버일 수 있음)를 포함한다. 프리-드라이버 회로(pre-driver circuit)는 제1 게이트에 연결되어 있고 핫 게이트 바이어스 회로는 제2 게이트에 연결되어 있다. 외부의 ESD 사건이 발생할 때, 핫 게이트 바이어스 회로는, 순상없이 더 높은 드레인 대 소스 전압(drain to source voltage)을 견딜 수 있는 레짐(regime)으로 MIGFET가 바이어스 되도록 제2 게이트에 신호를 인가한다. 그 결과, I/O 패드에 연결된 MIGFET을 위한 보호가 강화된다. 이는 다음의 설명과 도면들을 참조하면 더 잘 이해된다.

[0006]

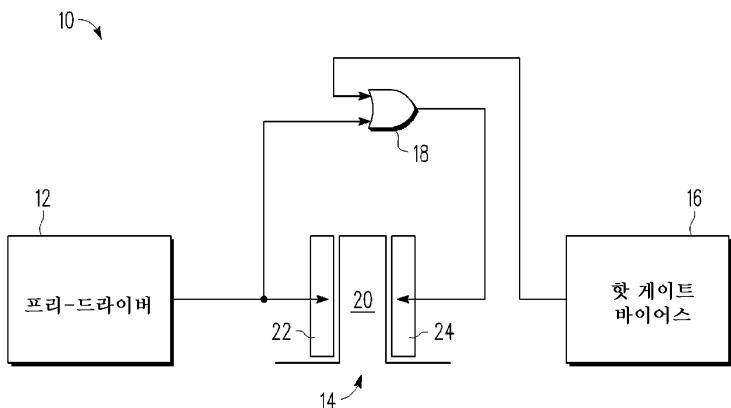

도 1에, ESD 보호된 회로(10)가 프리-드라이버 회로(12), N 채널 MIGFET(14), 핫 게이트 바이어스 회로(16), 및 OR 게이트(18)를 포함하고 있는 것이 도시되어 있다. MIGFET(14)는, 소스와 드레인 사이에서 채널로서 기능하는 핀(fin)(20), 핀(20)의 제1 측면을 따라 있는 컨트롤 게이트(control gate)(22), 및 핀(20)의 제2 측면을 따라 있는 컨트롤 게이트(24)를 포함한다. 컨트롤 게이트(22 또는 24)는 MIGFET(14)가 전도성이 되도록 할 수 있다. 프리-드라이버 회로(12)는 컨트롤 게이트(22)와 OR 게이트(18)의 제1 입력에 신호를 제공한다. 핫 게이트 바이어스 회로(16)는 OR 게이트(18)의 제2 입력에 연결된 출력을 갖는다. OR 게이트(18)는 컨트롤 게이트(24)에 연결된 출력을 갖는다. ESD 사건이 일어날 때, 다른 패드에 비해 MIGFET(14)의 드레인에 연결된 출력 패드에 상대적으로 높은 전압이 발생하는 상황에서, 핫 게이트 바이어스 회로(16)는, OR 게이트(18)가 컨트롤 게이트(24)에 로직 하이(logic high)를 제공하는 것을 보장하도록 로직 하이의 출력을 제공하며, 이로써 ESD 사건 동안, MIGFET(14)의 드레인과 소스 사이에 인가되는 전압과 동일하거나 그 근처의 전압에서 게이트 대 소스 바이어스를 가지고 MIGFET(14)가 전도성이 되는 것을 보장하게 된다. N 채널 트랜지스터의 게이트와 드레인의 동일한 전압을 가진다면, 게이트 전압이 드레인 전압보다 상당히 (예를 들면 2볼트) 아래에 있는 경우보다, 드레인 대 소스 파괴 전압(drain to source breakdown voltage)이 더 높은 상황에 채널이 놓여지는 것을 발견하였다. 정상 동작시, ESD 사건이 발생하지 않을 때에, 프리-드라이버 회로(12)는, 컨트롤 게이트(22)에 연결되고 OR 게이트(18)를 통해 컨트롤 게이트(24)에 연결되는 신호를 제공한다. MIGFET(14)가 P채널 트랜지스터인 경우에, 게이트(18)는 NOR 게이트가 될 것이며, 이에 따라 핫 게이트 바이어스 회로(16)가, 출력 패드에서의 전압이 다른 패드에서의 높은 전압에 비하여 상대적으로 낮은 ESD 사건을 견딜 수 있는 것에 응답하여 컨트롤 게이트(24)에 로직 로우(logic low)가 인가될 것이다. 정상 동작시, OR 게이트(18)에 의하여 야기되는 약간의 딜레이가, 스위칭 노이즈(또는  $di/dt$  노이즈라 불림)가 문제로 되는 경우 등의 어떤 상황들에서는 장점이 될 수 있다. 약간의 딜레이에는 OR 게이트(18)의 두 입력에 스태거드 전도(staggered conduction)를 일으켜서  $di/dt$ 를 감소시킨다. 대안으로서 OR 게이트(18)는 사용되지 않을 수도 있다. 그러한 경우에, 프리-드라이버

회로(12)는 단지 컨트롤 게이트(22)에 연결될 것이고, 핫 게이트 바이어스(16)는 OR 게이트(18)를 통하여 컨트롤 게이트(24)에 연결되지 않고 컨트롤 게이트(24)에 직접 연결될 것이다. MIGFET가 P채널인 경우에, 핫 게이트 바이어스 회로(16)는 로직 로우 출력을 컨트롤 게이트(24)에 직접 제공할 것이다. 이에 따라 핫 게이트 바이어스 회로(16)는, MIGFET(14)가 ESD 사건 동안 최대 또는 거의 최대의 파괴 전압을 나타내도록, 전압을 컨트롤 게이트(24)에 연결한다. 이러한 방식으로 출력 드라이버 MIGFET는 손상으로부터 더욱 잘 보호된다.

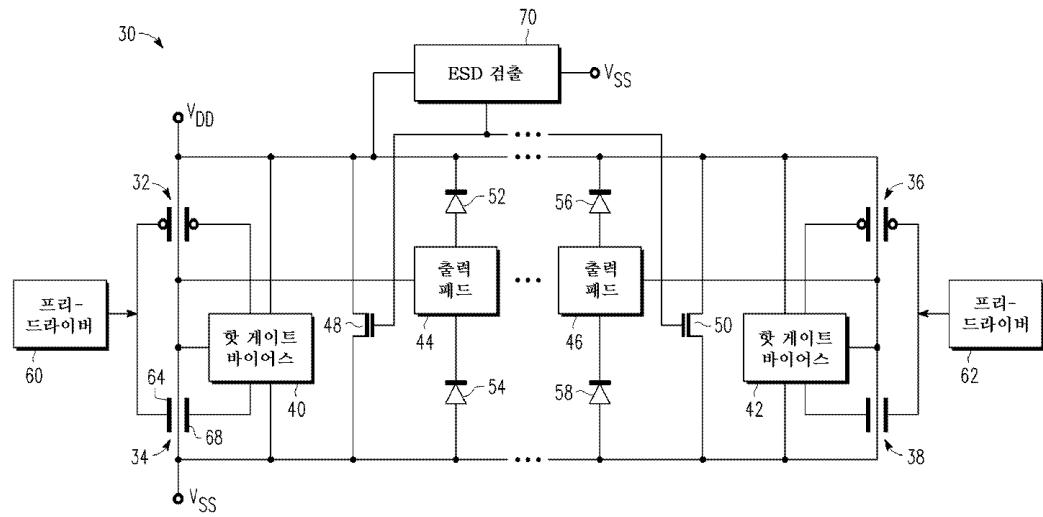

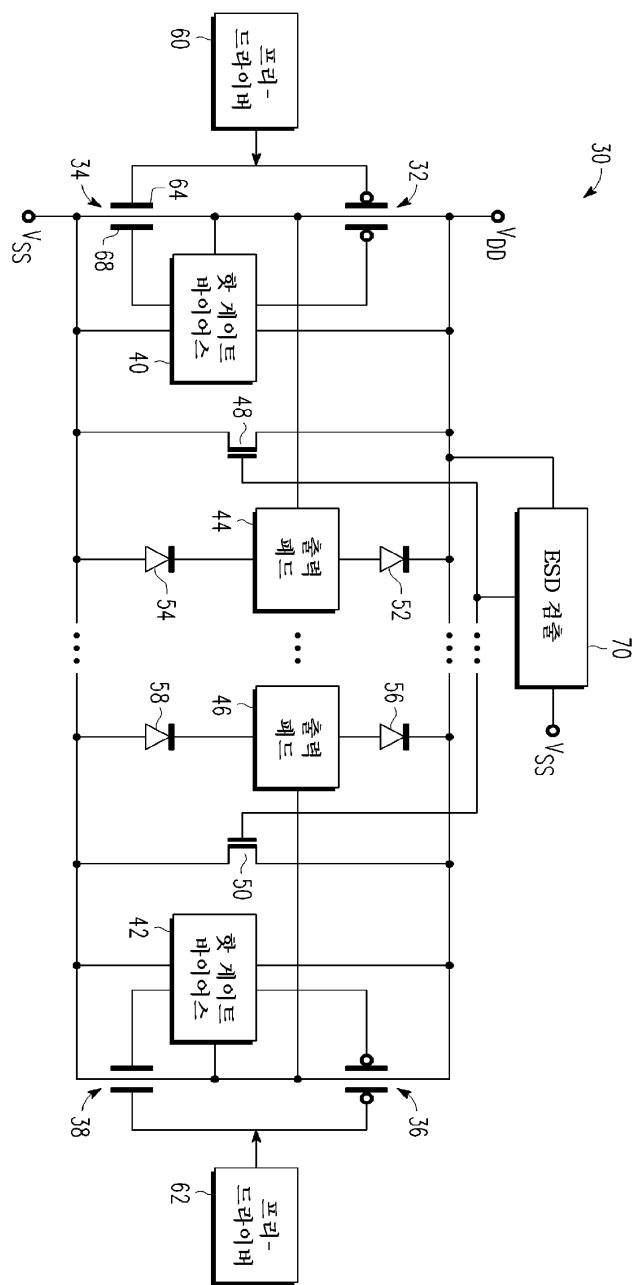

[0007] 도 2에, ESD 보호된 회로(30)가 P채널 MIGFET(32), N채널 MIGFET(34), P채널 MIGFET(36), N채널 MIGFET(38), 핫 게이트 바이어스 회로(40), 핫 게이트 바이어스 회로(42), 출력 패드(44), 출력 패드(46), N채널 트랜지스터(48), N채널 트랜지스터(50), 다이오드(52), 다이오드(54), 다이오드(56), 다이오드(58), ESD 검출 회로(70), 프리-드라이버 회로(60) 및 프리-드라이버 회로(62)를 포함하고 있는 것으로 도시되어 있다. 도시된 구성에서는, 단일의 프리-드라이버 회로(60)가 N-채널 MIGFET(34)와 P-채널 MIGFET(32) 양쪽 모두의 게이트들을 제어한다. 대안적으로, 두 개의 개별적인 프리-드라이버 회로들이 N-채널 MIGFET(34)와 P-채널 MIGFET(32)를 위하여 사용될 수 있다. MIGFET(34)는 또한 제1 컨트롤 게이트(64)와 제2 컨트롤 게이트(68)를 갖는 것으로 도시되어 있다. MIGFET들(32, 36 및 38)도 마찬가지로 하나의 채널과, 각각 독립적으로 이 채널을 제어하는 두 개의 컨트롤 게이트들을 가지고 있다. MIGFET(32)는 양의 전력 공급 단자 VDD에 연결된 소스, 출력 패드(44)에 연결된 드레인, 프리-드라이버 회로(60)의 출력에 연결된 제1 컨트롤 게이트, 및 핫 게이트 바이어스 회로(40)의 제2 출력에 연결된 제2 컨트롤 게이트를 가지고 있다. 핫 게이트 바이어스 회로(40)는 또한 VDD, VSS, 및 MIGFET들(32, 34)의 드레인들에 연결되어 있다. 핫 게이트 바이어스 회로(40)는, 출력 패드(44)가 출력 패드(46) 등의 다른 패드에 비하여 높은 전압을 받는, ESD 사건의 검출에 응답하여 MIGFET(34)의 드레인에 컨트롤 게이트(68)를 연결한다. 핫 게이트 바이어스 회로(40)는, 출력 패드(46) 등의 다른 출력 패드가 출력 패드(44)에 비하여 높은 전압을 받는, ESD 사건의 검출에 응답하여 MIGFET(32)의 드레인에 MIGFET(32)의 제2 컨트롤 게이트를 연결한다. 통상의 전원이 인가되는 동작 동안에는, 핫 게이트 바이어스 회로(40)는 MIGFET(34)에 로직 로우를 제공하며, MIGFET(32)에 로직 하이를 제공한다. 트랜지스터(48)는 VDD에 연결된 드레인, VSS에 연결된 소스, 및 ESD 검출 회로(70)의 출력에 연결된 게이트를 가진다. 트랜지스터(50)는 VDD에 연결된 드레인, VSS에 연결된 소스, 및 ESD 검출 회로(70)의 출력에 연결된 게이트를 가진다. 다이오드(52)는 출력 패드(44)와 VDD 사이에 애노드와 캐소드가 연결된다. 다이오드(54)는 VSS와 출력 패드(44) 사이에 애노드와 캐소드가 연결된다. 다이오드(56)는 출력 패드(46)와 VDD 사이에 애노드와 캐소드가 연결된다. 다이오드(58)는 VSS와 출력 패드(46) 사이에 애노드와 캐소드가 연결된다. MIGFET(36)는 양의 전력 공급 단자 VDD에 연결된 소스, 출력 패드(46)에 연결된 드레인, 프리-드라이버 회로(62)의 출력에 연결된 제1 컨트롤 게이트, 및 핫 게이트 바이어스 회로(42)의 제1 출력에 연결된 제2 컨트롤 게이트를 갖는다. MIGFET(38)는 음의 전력 공급 단자 VSS에 연결된 소스, 출력 패드(46)에 연결된 드레인, 프리-드라이버 회로(62)의 출력에 연결된 제1 컨트롤 게이트, 및 핫 게이트 바이어스 회로(42)의 제2 출력에 연결된 제2 컨트롤 게이트를 가진다. 또한 핫 게이트 바이어스 회로(42)는 VDD, VSS, 및 MIGFET들(36 및 38)의 드레인들에 연결된다. 핫 게이트 바이어스 회로(40)가 출력 패드(44) 및 MIGFET들(32, 34)과 관련하여 동작하는 것과 동일한 방식으로 핫 게이트 바이어스 회로는 출력 패드(46)와 MIGFET들(36, 38)과 관련하여 작동한다. 통상의 전원이 인가되는 동작 동안에는, 핫 게이트 바이어스 회로(42)는 MIGFET(38)에 로직 로우를 제공하고, MIGFET(36)에 로직 하이를 제공한다. 단지 출력 패드들(44 및 46) 및 그들과 연관된 회로만이 도시되어 있지만, 생략 부호(….)로 나타낸 바와 같이, 전형적인 집적회로에는 추가적인 출력 패드들 및 관련된 회로가 존재할 것이다.

[0008] 출력 패드(46)에 비하여 출력 패드(44)에 높은 전압이 발생하는 ESD 사건의 경우에는, 다이오드(52)는 그 전압을 VDD에 연결하여, ESD 검출 회로(70)와 핫 게이트 바이어스 회로들(40 및 42)이 ESD 사건을 검출하게 된다. ESD 검출 회로(70)는 트랜지스터들(48 및 50)이 전도성이 되도록 야기시키는 로직 하이 신호들을 발생시킴으로써 응답한다. 핫 게이트 바이어스 회로(40)는 MIGFET(34)의 드레인에 컨트롤 게이트(68)를 연결함으로써 응답한다. ESD 사건의 낮은 전압 쪽에 연결된 핫 게이트 바이어스 회로(42)는, MIGFET(36)의 드레인에 MIGFET(36)의 제2 컨트롤 게이트를 연결함으로써 응답한다. 이에 따라 전류는, 출력 패드(44)로부터 다이오드(52)를 통하여 VDD로, VDD로부터 트랜지스터들(48 및 50)을 통하여 VSS로, VSS로부터 다이오드(58)를 통하여 출력 패드(46)로 흐른다. 이러한 전류 흐름이 ESD 사건을 완화하는 반면에, 컨트롤 게이트(68)가 MIGFET(34)의 드레인에 연결되게 함으로써 MIGFET(34)는 높은 드레인 대 소스 파괴 레짐(hight drain to source breakdown regime)에 있게 되며, 또한 트랜지스터(36)의 제2 컨트롤 게이트가 MIGFET(36)의 드레인에 연결됨으로써 MIGFET(36)가 높은 드레인 대 소스 파괴 레짐에 있게 된다. 출력 패드(44)로부터 MIGFET(34)를 통하여 VSS에 이르는 전류 흐름

및 VDD로부터 MIGFET(36)를 통하여 출력 패드(46)에 이르는 전류 흐름에 의하여 ESD 사건은 또한 부분적으로 완화된다.

[0009] 통상 P채널 트랜지스터들은 N채널 트랜지스터들보다 더 높은 드레인 대 소스 파괴 전압을 가지므로, 핫 게이트 바이어스 회로(40 및 42)가 MIGFET들(32 및 36)의 제2 컨트롤 게이트들과 그들에 대응하는 드레인들 사이에 연결을 제공하는 것이 필요하지 않을 수도 있다. 이에 따라, 예를 들면, 출력 패드(46)에 비하여 출력 패드(44)에 높은 전압이 있게 되는 ESD 사건의 경우, 핫 게이트 바이어스 회로(42)가 MIGFET(36)의 드레인에 MIGFET(36)의 제2 컨트롤 게이트를 연결하는 것이 필요하지 않을 수도 있다. 핫 게이트 바이어스 회로들(40 및 42)은 단지 대응하는 N-채널 MIGFET들(34 및 38)에 출력을 제공하기만 하면 될 수 있다. 다른 대체 구성에서, 별개의 핫 게이트 바이어스 회로들이 각각의 N-채널 풀 다운(pull-down) MIGFET를 위해 제공될 수 있고, 별개의 핫 게이트 바이어스 회로들이 각각의 P-채널 풀 업(pull-up) MIGFET를 위해 제공될 수 있다. 또 다른 대체 구성에서, 핫 게이트 바이어스 회로는, 도 1에 도시된 구성과 유사하게, OR 게이트를 통하여 출력 드라이버 MIGFET에 연결될 수도 있다. 이 구성의 이점은 프리-드라이버 회로가 MIGFET의 컨트롤 게이트들 양쪽 모두에 연결되도록 허용한다는 것이다. 또한 대체 구성으로서, ESD 검출 회로(70)는 ESD 사건 검출에 응답하여 핫 게이트 바이어스 회로들(40 및 42)에 트리거 신호를 제공하도록 구성될 수도 있다. 그러한 경우에 핫 게이트 바이어스 회로들(40 및 42)은 트리거 신호에 응답하여 각자의 MIGFET의 게이트 단자에 바이어스 전압을 인가한다.

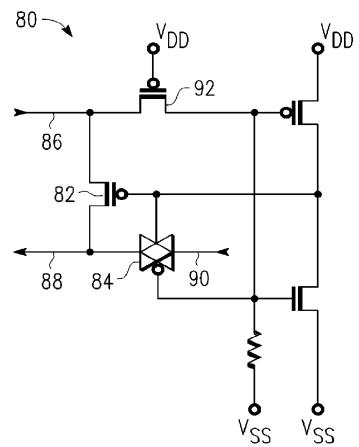

[0010] 도 3에는 도 1의 OR 게이트(18) 기능과 핫 게이트 바이어스(16)를 결합한 예시적인 구현인 회로(80)가 도시되어 있다. 도 3에서 P-채널 트랜지스터(82)는 ESD 사건 동안 MIGFET(14)의 드레인에 컨트롤 게이트(24)를 연결한다. 입력 핀(86)은 MIGFET(14)의 드레인에 연결되고 출력 핀(88)은 MIGFET(14)의 게이트에 연결된다. 전송 게이트(84)는, 정상 작동 동안 출력 핀(88)에서의 컨트롤 게이트(24)에 입력 핀(90)에서의 프리-드라이버 회로(12)의 출력을 연결한다. 주목할 것은, 도 3의 회로에서, MIGFET(14)의 드레인이 P-채널 MOSFET(92)의 임계전압보다 더 크게 VDD를 초과할 때마다 ESD 사건이 감지된다는 점이다. 모든 통상의 전력 공급 동작 동안(여기서는 MIGFET(14)의 드레인이 항상 VDD이거나 VDD 아래에 있다고 가정됨), 오직 프리-드라이버 회로(12)의 출력만이 MIGFET(14)의 게이트에 연결된다.

[0011] 지금쯤은 다수의 독립 게이트 전계 효과 트랜지스터(MIGFET), 출력을 갖는 프리-드라이버 회로, 및 핫 게이트 바이어스 회로를 포함하는 전원 전압 레일(power supply voltage rail)에 연결된 정전기 방전(ESD) 보호된 회로가 제공되었음을 알 수 있을 것이다. MIGFET는 출력 패드와 전원 전압 레일 사이에 연결된 소스/드레인 경로를 가지며, MIGFET는 제1 게이트 단자와 제2 게이트 단자를 갖는다. 핫 게이트 바이어스 회로는 MIGFET의 제1 게이트 단자에 연결되어 있고, 프리-드라이버 회로의 출력은 MIGFET의 제2 게이트 단자에 연결되어 있다. 핫 게이트 바이어스 회로는, ESD 사건 동안 MIGFET의 제1 게이트 단자에 바이어스 전압을 인가하도록 구성된다. 핫 게이트 바이어스 회로는 또한 정전기 방전 사건을 검출하도록 구성될 수 있다. 핫 게이트 바이어스 회로는, 출력 패드에서의 전압과 실질적으로 동일한 바이어스 전압을 만들기 위해서 충분한 크기의 바이어스 전압을 인가하도록 구성될 수 있다. 핫 게이트 바이어스 회로는, MIGFET와 관련된 파괴 전압을 올리기 위하여 충분한 크기의 바이어스 전압을 인가하도록 구성될 수도 있다. 또한, 보호된 회로는 정전기 방전 사건을 검출하도록 구성된 정전기 방전(ESD) 검출 회로를 포함할 수 있으며, 이 경우 ESD 검출 회로는 핫 게이트 바이어스 회로에 연결된다. ESD 검출 회로는, 정전기 방전 사건의 검출에 응답하여 핫 게이트 바이어스 회로에 트리거 신호를 제공하도록 구성될 수 있으며, 이에 따라, 핫 게이트 바이어스 회로는 트리거 신호에 응답하여 MIGFET의 제1 게이트 단자에 바이어스 전압을 인가하게 된다. 프리-드라이버 회로와 핫 게이트 바이어스 회로는 로직 게이트를 경유하여 MIGFET의 제1 게이트 단자에 연결될 수 있다.

[0012] 또한 제1 전원 전압 레일과 제2 전원 전압 레일에 연결된 정전기 방전(ESD) 보호된 회로가 기술되어 있다. ESD 회로는, 출력 패드와 제1 전원 전압 레일 사이에 연결된 소스/드레인 경로를 갖는 제1 다수의 독립 게이트 전계 효과 트랜지스터(MIGFET)를 포함하며, 여기서 제1 MIGFET는 제1 게이트 단자와 제2 게이트 단자를 갖는다. ESD 회로는 출력 패드와 제2 전원 전압 레일 사이에 연결된 소스/드레인 경로를 가지는 제2 MIGFET를 포함하며, 여기서, 제2 MIGFET는 제1 게이트 단자와 제2 게이트 단자를 갖는다. ESD 회로는 출력을 갖는 프리-드라이버 회로를 포함한다. ESD 회로는 제1 MIGFET의 제1 게이트 단자에 연결된 핫 게이트 바이어스 회로, 제2 MIGFET의 제1 게이트 단자, 제1 MIGFET의 제2 게이트 단자에 연결된 프리-드라이버 회로, 및 제2 MIGFET의 제2 게이트 단자를 포함하며, 이 경우 핫 게이트 바이어스 회로는, ESD 사건 동안 제1 MIGFET의 제1 게이트 단자에 제1 바이어스 전압을 인가하고 제2 MIGFET의 제1 게이트 단자에 제2 바이어스 전압을 인가하도록 구성된다. 핫 게이트 바이어스 회로는, 출력 패드에서의 전압과 실질적으로 동일한 제1 바이어스 전압을 만들기 위하여 충분한 크기의 제1 바이어스 전압을 인가하도록 구성될 수 있다. 또한, 핫 게이트 바이어스 회로는 ESD 사건을 검출하도록

구성될 수 있다. 핫 게이트 바이어스 회로는, 제1 MIGFET와 관련된 파괴 전압을 높이기에 충분한 크기의 제1 바이어스 전압을 인가하고, 제2 MIGFET와 관련된 파괴 전압을 높이기에 충분한 크기의 제2 바이어스 전압을 인가하도록 구성될 수 있다. 또한, ESD 보호된 회로는 정전기 방전 사건을 검출하도록 구성된 ESD 검출 회로를 포함할 수 있으며, 이 경우, ESD 검출 회로는 핫 게이트 바이어스 회로에 연결되어 있다. ESD 검출 회로는, 정전기 방전 사건의 검출에 응답하여 핫 게이트 바이어스 회로에 트리거 신호를 제공하도록 구성될 수 있으며, 이에 따라 핫 게이트 바이어스 회로는 트리거 신호에 응답하여 제1 MIGFET의 제1 게이트 단자에 제1 바이어스 전압을 인가하고 제2 MIGFET의 제1 게이트 단자에 제2 바이어스 전압을 인가하게 된다. 정상 동작 동안, 핫 게이트 바이어스 회로는, 제1 전원 전압 레일과 실질적으로 동일한 제1 바이어스 전압을 만들기 위하여 제1 MIGFET의 제1 게이트 단자에 충분한 크기의 제1 바이어스 전압을 인가하도록 구성될 수 있다. 제1 MIGFET는 N 채널 트랜지스터일 수 있고 제2 MIGFET는 P 채널 트랜지스터일 수 있다.

[0013] 또한, 정전기 방전(ESD) 보호된 회로에 있어서의 한 방법이 기술되어 있는데, ESD 보호된 회로는 제1 전원 전압 레일과 제2 전원 전압 레일 사이에 연결되어 있으며 출력 패드와 제2 전원 전압 레일 사이에 연결된 소스/드레인 경로를 갖는 다수의 독립 게이트 전계 효과 트랜지스터(MIGFET)를 포함한다. MIGFET는 제1 게이트 단자와 제2 게이트 단자를 가진다. 본 방법은, 정상 동작 동안 제2 전원 전압 레일과 실질적으로 동일한 제1 바이어스 전압을 만들기 위하여 MIGFET의 제1 게이트 단자에 충분한 크기의 제1 바이어스 전압을 인가하는 단계를 포함한다. 또한, 본 방법은, ESD 사건 동안에 출력 패드에서의 전압과 실질적으로 동일한 제2 바이어스 전압을 만들기 위하여 MIGFET의 제1 게이트 단자에 충분한 크기의 제2 바이어스 전압을 인가하는 단계를 포함한다. 상기 인가하는 단계들은 또한, 제1 및 제2 바이어스 전압들을 인가하기 위하여 바이어스 회로를 사용하는 것을 특징으로 할 수 있으며, 본 방법은 ESD 사건을 검출하기 위해 상기 바이어스 회로를 사용하는 단계를 더 포함할 수 있다. 본 방법은 MIGFET와 관련된 파괴 전압을 높이기 위하여 제2 바이어스 전압을 선택하는 단계를 더 포함할 수 있다. 본 방법은 정전기 방전 사건의 검출에 응답하여 핫 게이트 바이어스 회로에 트리거 신호를 제공하는 단계를 더 포함할 수 있으며, 이에 따라 핫 게이트 바이어스 회로는 트리거 신호에 응답하여 MIGFET의 제1 게이트 단자에 제2 바이어스 전압을 인가하게 된다.

[0014] 본 발명을 구현하는 장치들은 대부분 본 기술 분야에 통상의 지식을 가진 자에게 알려진 전자 부품들과 회로들로 구성되어 있기 때문에, 본 발명의 근원적인 개념들의 이해와 인식을 위하여 그리고 본 발명의 개시를 불명료하게 하거나 흐트러지게 하지 않기 위하여 위에서 예시된 바와 같이 필요한 것으로 간주되는 것보다, 더 큰 범위의 회로의 세부적인 것은 설명되지 않을 것이다.

[0015] 비록 본 발명은 특정한 전도성 타입들 또는 전위(potentials)들의 극성과 관련하여 기술되었지만, 본 기술 분야에 통상의 지식을 가진 자라면 전도성 타입들과 전위들의 극성들이 뒤바뀌어질 수도 있다는 것을 알 것이다.

[0016] 또한 상세한 설명과 청구항들에 있는 앞(front), 뒤(back), 상부(top), 하부(bottom), 위쪽(over), 아래쪽(under), 기타 등등의 용어들이, 만약 있다면, 설명의 목적들을 위해서 사용되었고 반드시 영구적인 상대적인 위치들을 기술하는 것은 아니다. 그와 같이 사용된 용어들은 적당한 상황들에서 호환성이 있으며, 이에 따라 본원에서 기술된 발명의 실시예들은, 예를 들면, 본원에서 예시되거나 혹은 기술된 실시예들과는 다른 방향들(other orientations)에서 작동을 할 수 있음을 알 것이다.

[0017] 비록 본원에서는 본 발명에 대해 특정한 실시예들과 관련하여 기술하였지만, 이하의 청구항들에 제시되는 바와 같은 본 발명의 범위를 벗어남이 없이 다양한 변경들과 변화들이 만들어질 수 있다. 예를 들면, 트랜지스터들(48 및 50)은 N 채널 트랜지스터들로 기술되었으나 일부 다른 클램핑 작용(clamping operation)이 사용될 수도 있다. 또한 다이오드들(52, 54, 56, 58)은 다이오드가 연결된 트랜지스터들일 수도 있고 효과적일 수도 있다. 따라서 본 명세서와 도면들은 한정적인 의미가 아니라 예시적인 것으로 간주되어져야 할 것이며, 모든 그러한 변경들은 본 발명의 범위 내에 포함되도록 의도되는 것이다. 임의의 이익들, 이점들, 또는 본원에서 특정한 실시예들과 관련하여 기술된 문제점들에 대한 해결책들은 임의의 또는 모든 청구항들의 중대하거나 필수적이거나 본질적인 특징 또는 요소로서 해석되도록 의도된 것은 아니다.

[0018] 본원에서 사용된 "연결된(coupled)"이라는 용어는 직접적인 연결(direct coupling)이나 기계적인 연결(mechanical coupling)로 제한되도록 의도된 것은 아니다.

[0019] 또한, 본원에서 사용된 "하나의(a 혹은 an)"란 용어들은 하나 혹은 하나 이상으로서 정의된다. 또한, 십지어 동일한 청구항이 시작 문구들인 "하나 이상" 혹은 "적어도 하나" 그리고 "a"나 "an"과 같은 부정관사를 포함할 때에도, 청구항들에 있는 "적어도 하나" 및 "하나 이상"과 같은 시작 문구들의 사용은, 부정 관사 "a" 혹은 "an"에 의한 다른 청구항 요소의 도입이, 그러한 도입된 청구항의 요소를 포함하는 임의의 특정한 청구항을 오

직 하나의 그러한 요소를 포함하는 발명들로 제한한다는 것을 암시하는 것으로 해석되어서는 안 된다. 이와 동일한 내용이 정관사의 사용에도 적용된다.

[0020]

달리 진술되지 않는 한, "제1" 및 "제2"와 같은 용어들은 그러한 용어들이 기술하는 요소들을 구별하는데에 임의적으로 사용된다. 그러므로, 이러한 용어들은 반드시 그러한 요소들의 일시적 또는 다른 우선순위화를 나타내도록 의도되는 것은 아니다.

## 도면

### 도면1

도면2

도면3