OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

⑪ Número de publicación: **2 875 037**

⑮ Int. Cl.:

**H01L 27/02** (2006.01)

**H01L 27/11** (2006.01)

⑫

TRADUCCIÓN DE PATENTE EUROPEA

T3

⑥ Fecha de presentación y número de la solicitud internacional: **20.04.2015 PCT/US2015/026588**

⑦ Fecha y número de publicación internacional: **26.11.2015 WO15179050**

⑨ Fecha de presentación y número de la solicitud europea: **20.04.2015 E 15719395 (4)**

⑩ Fecha y número de publicación de la concesión europea: **26.05.2021 EP 3146564**

---

④ Título: **Matriz de memoria estática de acceso aleatorio de alta densidad con patrones metálicos avanzados**

⑩ Prioridad:

**19.05.2014 US 201414281710**

④ Fecha de publicación y mención en BOPI de la traducción de la patente:

**08.11.2021**

⑦ Titular/es:

**QUALCOMM INCORPORATED (100.0%)

5775 Morehouse Drive

San Diego, CA 92121-1714, US**

⑦ Inventor/es:

**MOJUMDER, NILADRI;

SONG, STANLEY SEUNGCHUL;

WANG, ZHONGZE y

YEAP, CHOH FEI**

⑦ Agente/Representante:

**ISERN JARA, Jorge**

**ES 2 875 037 T3**

---

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín Europeo de Patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre Concesión de Patentes Europeas).

## DESCRIPCIÓN

Matriz de memoria estática de acceso aleatorio de alta densidad con patrones metálicos avanzados

5 Campo de la divulgación

Esta divulgación se refiere, en general, a la electrónica, y más específico, pero no exclusivamente, a los procedimientos dirigidos hacia una matriz de memoria estática de acceso aleatorio de alta densidad que tiene un patrón metálico avanzado.

10 Antecedentes

La Memoria de Acceso Aleatorio (RAM) es un componente omnipresente de las arquitecturas digitales modernas. La RAM puede ser un dispositivo independiente o puede integrarse en un dispositivo que utiliza la RAM, como un microprocesador, un microcontrolador, un circuito integrado específico de aplicación (ASIC), sistema en chip (SoC) y otros dispositivos similares. La RAM puede ser volátil o no volátil. La RAM volátil pierde su información almacenada cuando se corta la energía. La RAM no volátil puede mantener el contenido de la memoria incluso cuando se corta la energía. Un tipo de RAM volátil es la Memoria Estática de Acceso Aleatorio (SRAM), que normalmente utiliza un circuito de enclavamiento biestable como célula de bits de memoria.

20 Las fuerzas del mercado moderno afectan el diseño y la producción de SRAM y, por lo tanto, existe una demanda para reducir el tamaño físico de los nuevos diseños de SRAM. Para continuar duplicando la densidad de los circuitos SRAM (según la ley de Moore) en un tamaño de característica de 14 nm y por debajo de este mediante la tecnología CMOS, el diseño de SRAM debe optimizarse para permitir una mayor densidad, mayor rendimiento y menores costos de producción. Los investigadores se enfrentan a la búsqueda de una optimización de diseño de SRAM rentable tanto a nivel de célula de bits como de matriz de memoria.

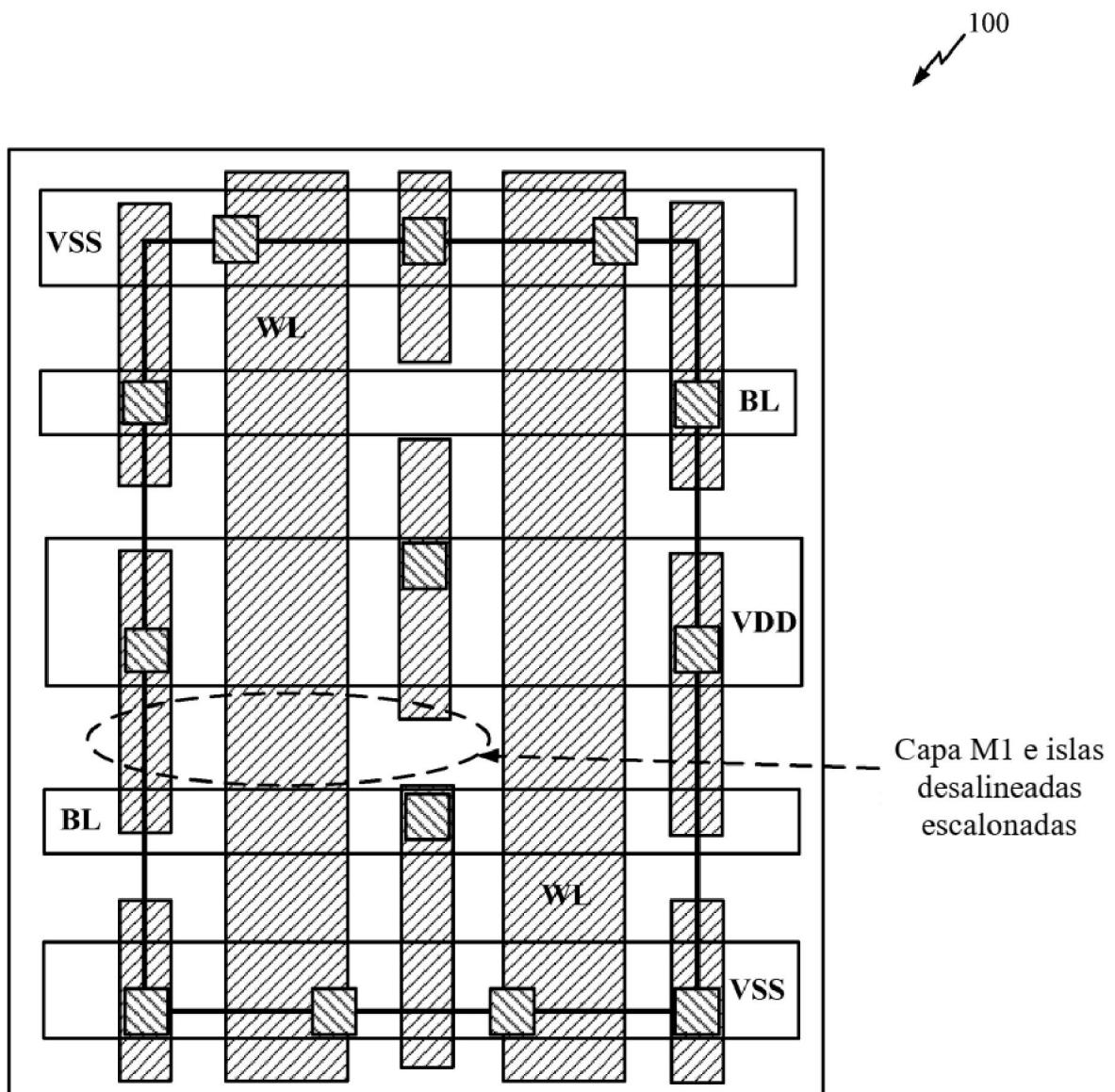

30 Los diseños convencionales de SRAM de seis transistores (6T), como muestra la Figura 1 el diseño de SRAM 6T 100 que tiene una línea de palabras (WL) en una primera capa de metal y una línea de bits (BL) en una segunda capa de metal, tiene islas metálicas escalonadas y desalineadas. Cuando el tamaño de la característica del circuito es de 22 nm, las estructuras representadas en la Figura 1 deben fabricarse por separado e individualmente mediante el uso de una técnica de fabricación conocida como litografía-grabado-litografía-grabado (también conocida como LELE). Sin embargo, para reducir el tamaño de la característica a menos de 22 nm, se requiere un patrón triple (es decir, LELELE) con un mayor recuento de máscaras para fabricar por separado e individualmente las islas metálicas escalonadas y desalineadas. El mayor número de máscaras aumenta los costos de fabricación, reduce la velocidad de fabricación, aumenta el número de máscaras y disminuye el rendimiento de fabricación.

35 En consecuencia, existen necesidades de la industria desde hace mucho tiempo de procedimientos y aparatos que mejoren los procedimientos y aparatos convencionales, que incluyen los procedimientos y aparatos mejorados proporcionados por la presente memoria.

40 El documento US 2014/077380 A1 describe un enfoque para proporcionar células de bits SRAM con estructuras de capa metálica de doble patrón.

45 El documento US 2009/189227 A1 describe una célula de bit SRAM y un procedimiento de producción asociado de la célula de bit SRAM.

Sumario

50 De acuerdo con la invención, se proporcionan un procedimiento para fabricar una memoria estática de acceso aleatorio, y un medio legible por ordenador no transitorio que comprende instrucciones ejecutables del dispositivo litográfico almacenadas en el mismo configuradas para hacer que un dispositivo litográfico ejecute un procedimiento, como se establece en las reivindicaciones.

55 Este sumario proporciona una comprensión básica de algunos aspectos de las presentes enseñanzas. Este sumario no es exhaustivo en detalle y no pretende identificar todas las características críticas, ni pretende limitar el ámbito de las reivindicaciones.

60 Se divulan procedimientos y aparatos ilustrativos para fabricar una memoria de acceso aleatorio estática (SRAM). Un procedimiento ilustrativo incluye formar, mediante el uso de una técnica de modelado doble autoalineante, una pluralidad de primeras líneas metálicas sustancialmente paralelas orientadas en una primera dirección en una primera capa. El procedimiento también incluye grabar las primeras líneas metálicas sustancialmente paralelas, mediante el uso de una máscara de corte, en una segunda dirección sustancialmente perpendicular a la primera dirección, para separar las primeras líneas metálicas sustancialmente paralelas en una pluralidad de islas que tienen los primeros lados respectivos que están sustancialmente alineados en la primera dirección y los segundos lados respectivos que están sustancialmente alineados en la segunda dirección. Una isla en la pluralidad de las islas

5 puede configurarse como uno de una línea de bits, un conductor de potencia positivo y un conductor de potencia negativo. El procedimiento también incluye formar, en una segunda capa, una pluralidad de segundas líneas metálicas orientadas en la primera dirección, así como formar un transistor de paso de silicio-germanio de óxido metálico-silicio tipo p (PMOS) que incluye una compuerta acoplada a una segunda línea metálica en la pluralidad de

10 segundas líneas metálicas y un drenaje acoplado a una isla en la pluralidad de islas. Una segunda línea metálica en la pluralidad de segundas líneas metálicas puede configurarse como una línea de palabras. La SRAM se puede integrar en al menos uno de un dispositivo móvil, un decodificador, un reproductor de música, un reproductor de video, una unidad de entretenimiento, un dispositivo de navegación, un dispositivo de comunicaciones, un asistente digital personal, una unidad de datos de ubicación fija y un ordenador.

15 10 En un ejemplo adicional, se proporciona un medio legible por ordenador no transitorio, que comprende instrucciones ejecutables del dispositivo litográfico almacenadas en el mismo configuradas para hacer que un dispositivo litográfico ejecute al menos una parte del procedimiento mencionado anteriormente.

15 15 En otro ejemplo, se proporciona un aparato. El aparato incluye una SRAM que incluye una pluralidad de islas metálicas formadas sobre un sustrato y que tienen unos primeros lados respectivos que están sustancialmente alineados en una primera dirección y unos segundos lados respectivos que están sustancialmente alineados en una segunda dirección excepto por cada tercera isla. La SRAM también incluye una pluralidad de líneas metálicas en una segunda capa y orientadas en la primera dirección, así como un transistor de paso PMOS de silicio-germanio que incluye una puerta acoplada a una línea metálica en la pluralidad de segundas líneas metálicas y un drenaje acoplado a una isla en la pluralidad de islas metálicas. Al menos una parte del aparato se puede integrar en un molde semiconductor. El aparato puede incluir al menos uno de una estación base y un dispositivo móvil, con el que se integra la SRAM. El aparato también puede incluir al menos uno de un dispositivo móvil, una estación base, un terminal, un decodificador, un reproductor de música, un reproductor de video, una unidad de entretenimiento, un dispositivo de navegación, un dispositivo de comunicaciones, un asistente digital personal, una unidad de datos de ubicación fija y un ordenador, de los cuales la SRAM es una parte constituyente.

30 20 También se divulga un procedimiento ilustrativo para fabricar una SRAM. El procedimiento incluye una etapa para formar, mediante el uso de una técnica de patrón doble autoalineante, una pluralidad de primeras líneas metálicas sustancialmente paralelas orientadas en una primera dirección en una primera capa, así como una etapa para grabar las primeras líneas metálicas sustancialmente paralelas, mediante el uso de una máscara de corte, en una segunda dirección sustancialmente perpendicular a la primera dirección, para separar las primeras líneas metálicas sustancialmente paralelas en una pluralidad de islas que tienen los primeros lados respectivos que están sustancialmente alineados en la primera dirección y los segundos lados respectivos que están sustancialmente alineados en la segunda dirección. Una isla en la pluralidad de las islas puede configurarse como uno de una línea de bits, un conductor de potencia positivo y un conductor de potencia negativo. El procedimiento también incluye una etapa para formar, en una segunda capa, una pluralidad de segundas líneas metálicas orientadas en la primera dirección, así como una etapa para formar un transistor de paso PMOS de silicio-germanio que incluye una puerta acoplada a una segunda línea metálica en la pluralidad de segundas líneas metálicas y un drenaje acoplado a una isla en la pluralidad de islas. Una segunda línea metálica en la pluralidad de segundas líneas metálicas puede configurarse como una línea de palabras. El procedimiento también puede incluir una etapa para integrar la SRAM en al menos uno de un dispositivo móvil, un decodificador, un reproductor de música, un reproductor de video, una unidad de entretenimiento, un dispositivo de navegación, un dispositivo de comunicaciones, un asistente digital personal, una unidad de datos de ubicación fija y un ordenador.

35 40 45 También se divulga un procedimiento para leer una célula de bits de memoria de sólo lectura estática de seis transistores. El procedimiento incluye la descarga previa de una línea de bits y mantener una línea de palabras en un nivel lógico bajo para encender un transistor de paso PMOS de silicio-germanio de alta movilidad de canal, provocando así que una corriente de lectura fluya desde la línea de bits, a través del transistor de paso y un transistor de subida PMOS (en un circuito de enclavamiento biestable de cuatro transistores) a una fuente de alimentación.

50 55 60 Lo anterior describe ampliamente algunas de las características y ventajas técnicas de las presentes enseñanzas a fin de que la descripción detallada y los dibujos puedan entenderse mejor. Las características y ventajas adicionales también se describen en la descripción detallada. La concepción y las realizaciones divulgadas se pueden utilizar fácilmente como base para modificar o diseñar otras estructuras para llevar a cabo los mismos propósitos de las presentes enseñanzas. Tales construcciones equivalentes no se apartan de la tecnología de las enseñanzas como se establece en las reivindicaciones. Las características inventivas que son distintivas de las enseñanzas, junto con otros objetos y ventajas, se entienden mejor a partir de la descripción detallada y las figuras adjuntas. Cada una de las figuras se proporciona únicamente con fines ilustrativos y descriptivos, y no limitan las presentes enseñanzas.

Breve descripción de los dibujos

65 Los dibujos adjuntos se presentan para describir ejemplos de las presentes enseñanzas y no son limitantes.

La Figura 1 representa un diseño ilustrativo de memoria de acceso aleatorio estática convencional de seis transistores.

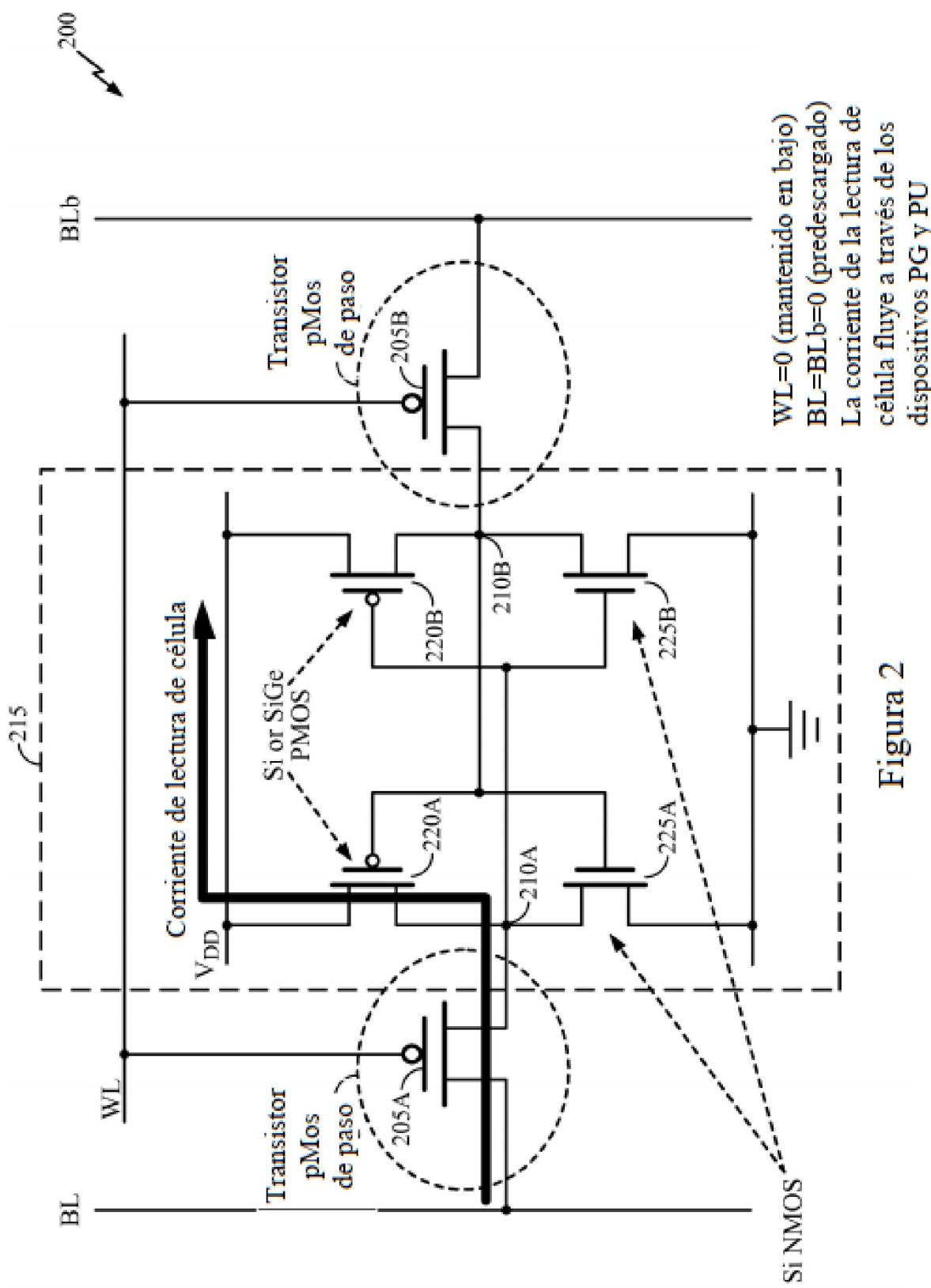

La Figura 2 representa un esquema de una célula de bits de alto rendimiento ilustrativa.

La Figura 3 representa un procedimiento ilustrativo para fabricar una célula de bits de memoria de acceso aleatorio estática de alta densidad que tiene un patrón metálico avanzado.

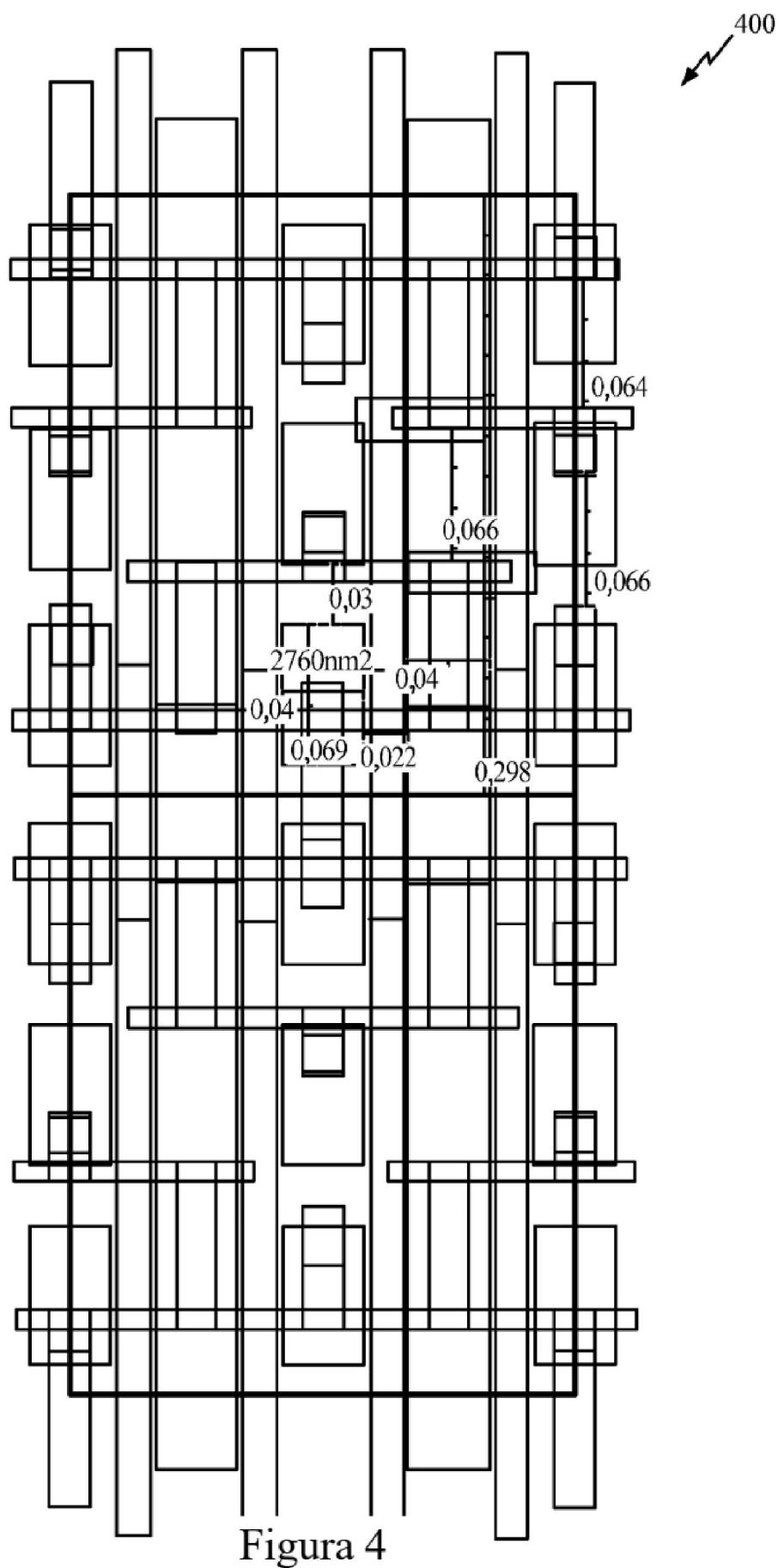

La Figura 4 representa un detalle ilustrativo sobre la fabricación de la línea de palabras de una capa de metal.

La Figura 5 también representa un procedimiento ilustrativo para fabricar una célula de bits de memoria de acceso aleatorio estática de alta densidad que tiene un patrón metálico avanzado.

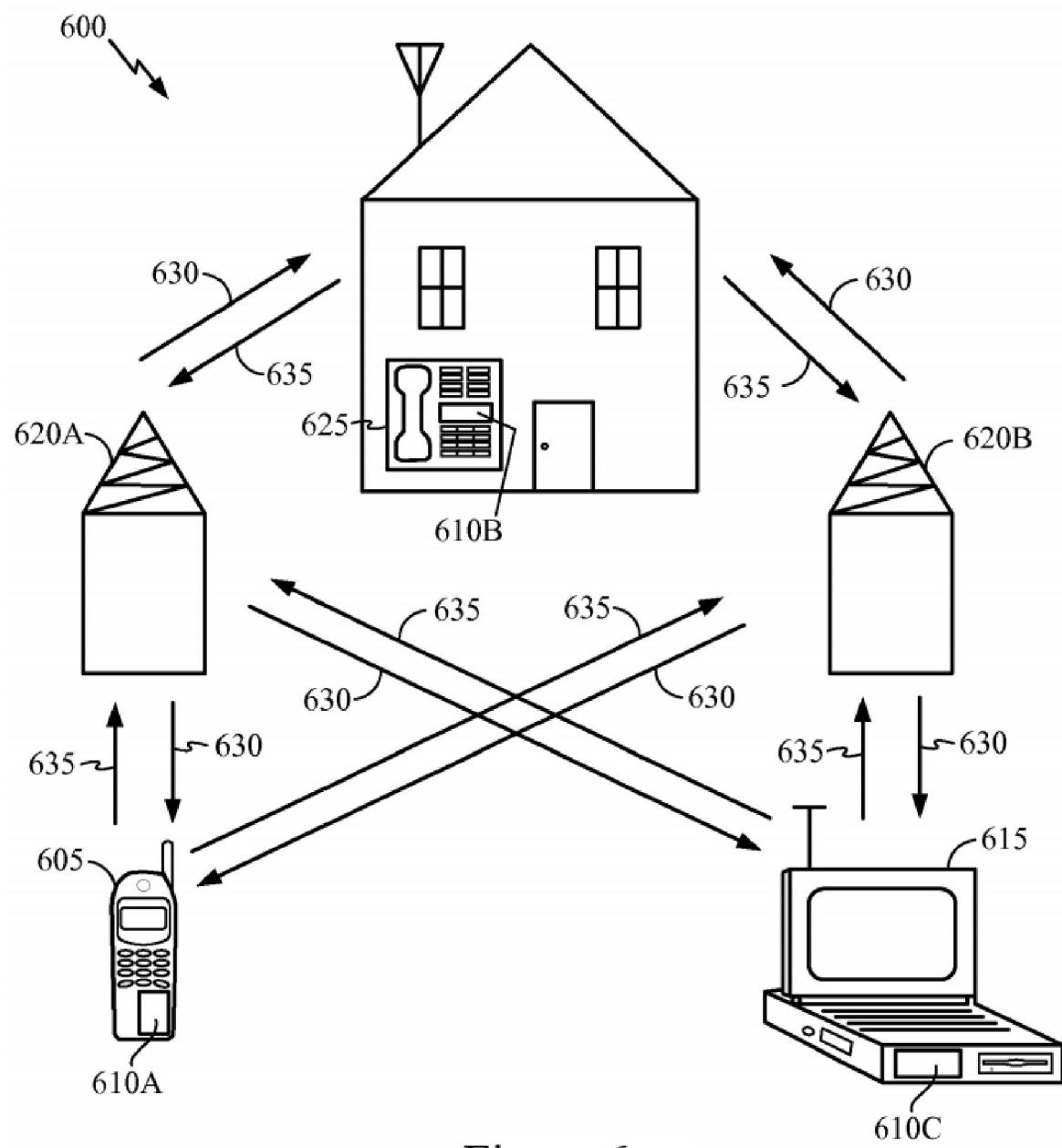

La Figura 6 representa un de sistema de comunicación ilustrativo.

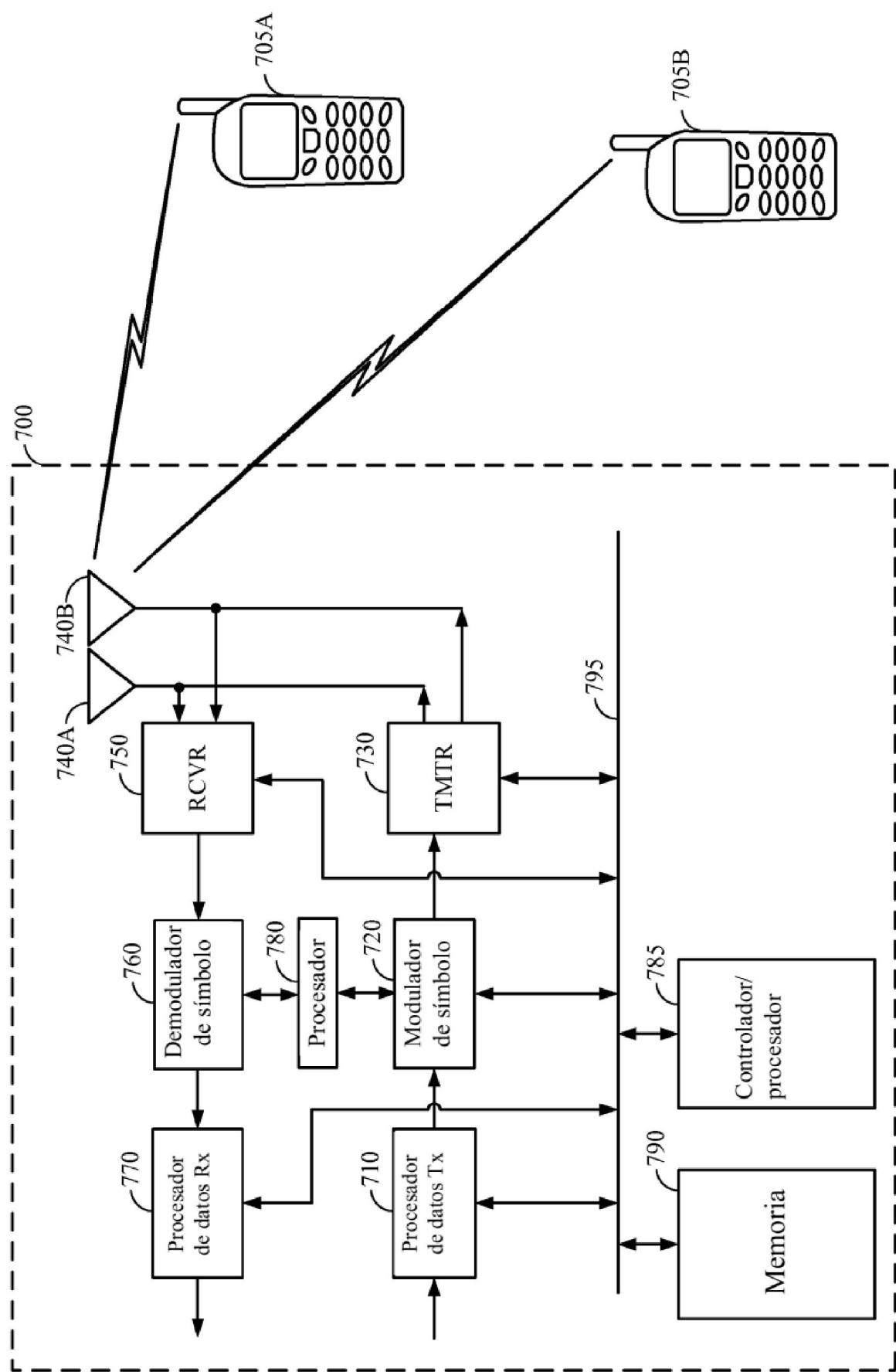

La Figura 7 representa un punto de acceso ilustrativo.

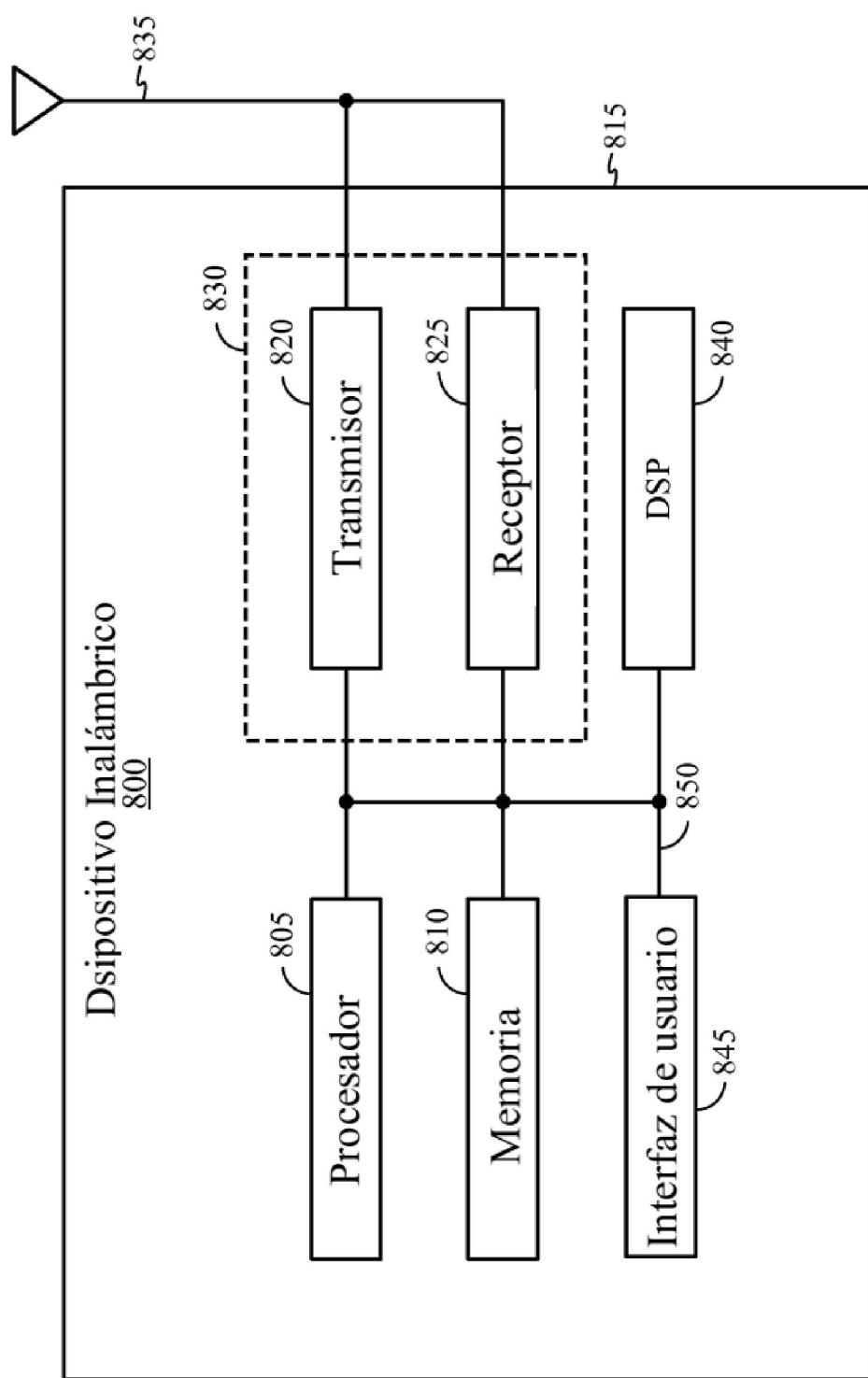

La Figura 8 representa un diagrama de bloques funcional de un dispositivo inalámbrico ilustrativo.

De acuerdo con la práctica común, las características representadas en los dibujos pueden no estar a escala. Por consiguiente, las dimensiones de las características representadas pueden expandirse o reducirse arbitrariamente para mayor claridad. De acuerdo con la práctica común, algunos de los dibujos se simplifican para mayor claridad. Por lo tanto, los dibujos pueden no representar todos los componentes de un aparato o procedimiento en particular. Además, los mismos números de referencia denotan características similares en toda la memoria descriptiva y las figuras.

## 20 Descripción detallada

### Introducción

Se proporcionan procedimientos y aparatos dirigidos a una matriz de memoria de acceso aleatorio estática (SRAM) de alta densidad que tiene un patrón metálico avanzado. Por ejemplo, se proporciona un nuevo diseño de matriz SRAM que incluye una primera capa de metal vertical y una primera capa de metal horizontal simple cortadas para permitir un mejor margen de procedimiento, costos reducidos y soluciones de diseño de periferia de memoria simplificadas. El diseño SRAM propuesto permite un patrón de la primera capa de metal simétrico unidireccional (vertical), reduciendo así el número efectivo de máscaras.

En un ejemplo, se proporciona un procedimiento para fabricar una SRAM. El procedimiento incluye formar, mediante el uso de una técnica de modelado doble autoalineante (SADP), una pluralidad de primeras líneas metálicas sustancialmente paralelas orientadas en una primera dirección en una primera capa. El procedimiento también incluye grabar las primeras líneas metálicas sustancialmente paralelas, mediante el uso de una máscara de corte, en una segunda dirección sustancialmente perpendicular a la primera dirección, para separar las primeras líneas metálicas sustancialmente paralelas en una pluralidad de islas que tienen los primeros lados respectivos que están alineados en la primera dirección y los segundos lados respectivos que están alineados en la segunda dirección. El procedimiento también incluye formar, en una segunda capa, una pluralidad de segundas líneas metálicas orientadas en la primera dirección. Una isla en la pluralidad de las islas puede configurarse como uno de una línea de bits, un conductor de potencia positivo y un conductor de potencia negativo. Una segunda línea metálica en la pluralidad de segundas líneas metálicas puede configurarse como una línea de palabras (WL). La WL y la pluralidad de islas están en la primera capa metálica, pero se pueden modelar secuencialmente con un conjunto específico de órdenes.

Los aparatos y procedimientos ilustrativos divulgados en la presente memoria abordan ventajosamente las necesidades de la industria presentadas desde hace mucho tiempo, así como otras necesidades no identificadas previamente, y que mitigan las deficiencias de los procedimientos y aparatos convencionales. Por ejemplo, las ventajas proporcionadas por los aparatos y procedimientos divulgados en la presente memoria incluyen mejoras en los costes de fabricación, la velocidad de fabricación, el recuento de máscaras, la densidad del circuito y el rendimiento de fabricación con respecto a las técnicas convencionales. El aparato proporcionado también es escalable.

En el texto y los dibujos de la presente solicitud se divultan realizaciones ilustrativas. Pueden idearse realizaciones alternativas sin apartarse del ámbito de la invención. Además, los elementos convencionales de las presentes enseñanzas pueden no describirse en detalle, o pueden omitirse, para evitar oscurecer aspectos de las enseñanzas actuales.

Como se usa en la presente memoria, el término "ilustrativo" significa "que sirve como un ejemplo, instancia, o ilustración". Cualquier realización descrita como "ilustrativa" no se debe interpretar necesariamente como preferente o ventajosa con respecto a otras realizaciones. Asimismo, el término "realizaciones de la invención" no requiere que todas las realizaciones de la invención incluyan la característica, ventaja o modo de funcionamiento discutidos. El uso de los términos "en un ejemplo", "un ejemplo", "en una característica", y/o "una característica" en esta memoria descriptiva no se refieren necesariamente a la misma característica y/o ejemplo. Además, una característica y/o estructura particular se puede combinar con una o más de otras características y/o estructuras. Además, al menos una parte del aparato descrito en la presente memoria puede configurarse para realizar al menos una parte de un procedimiento descrito en la presente memoria.

Debe notarse que los términos "conectado", "acoplado" o cualquier variante de estos, significan cualquier conexión o acoplamiento, ya sea directo o indirecto, entre elementos, y puede abarcar la presencia de un elemento intermedio entre dos elementos que están "conectados" o "acoplados" entre sí mediante el elemento intermedio. El acoplamiento y/o conexión entre los elementos puede ser físico, lógico, o sus combinaciones. Como se emplea en la

5 presente memoria, los elementos se pueden "conectar" o "acoplar" entre sí, por ejemplo, mediante el uso de uno o más alambres, cables y/o conexiones eléctricas impresas, así como mediante el uso de energía electromagnética. La energía electromagnética puede tener longitudes de onda en la región de radiofrecuencia, la región de microondas y/o la región óptica (tanto visible como invisible). Estos son varios ejemplos no limitantes y no

10 exhaustivos.

Debe entenderse que el término "señal" puede incluir cualquier señal, como una señal de datos, una señal de audio, una señal de vídeo, una señal multimedia, una señal analógica y/o una señal digital. La información y las señales se pueden representar mediante el uso de cualquiera de una variedad de diferentes tecnologías y técnicas. Por ejemplo, los datos, una instrucción, una etapa de procedimiento, un comando, información, una señal, un bit y/o un símbolo descritos en esta descripción se pueden representar mediante un voltaje, una corriente, una onda electromagnética, un campo magnético y/o partícula, un campo óptico y/o partícula, y cualquier combinación de los mismos.

20 Cualquier referencia en la presente memoria a un elemento que utilice una designación como "primero," "segundo," etc., no limita la cantidad y/o el orden de esos elementos. Más bien, estas designaciones se utilizan como un procedimiento conveniente para distinguir entre dos o más elementos y/o instancias de un elemento. Por lo tanto, una referencia a los primer y segundo elementos no significa que sólo puedan emplearse dos elementos, o que el primer elemento deba preceder necesariamente al segundo elemento. También, a menos que se indique lo contrario, un conjunto de elementos puede comprender uno o más elementos. Además, la terminología de la forma "al menos uno de: A, B o C" usada en la descripción o las reivindicaciones pueden interpretarse como "A o B o C o cualquier combinación de estos elementos".

30 La terminología usada en la presente memoria es solo con el objetivo de describir las realizaciones particulares y no pretende ser limitante. Como se usa en la presente memoria, las formas singulares "un", "una", y "el/la" pretenden incluir las formas plurales también, a menos que el contexto claramente indique lo contrario. Además, los términos "comprende", "que comprende", "incluye", e "que incluye", cuando se utilizan en la presente memoria especifican la presencia de las características, números enteros, etapas, operaciones, elementos, y/o componentes indicados, pero no excluyen la presencia y/o adición de una o más características, números enteros, etapas, operaciones, elementos, componentes, y/o grupos de estos.

35 40 Los aparatos proporcionados pueden ser parte y/o acoplarse a un dispositivo electrónico que tiene una memoria, tal como, pero sin limitarse a, al menos uno de un dispositivo móvil, un teléfono móvil, un dispositivo inalámbrico, un asistente de datos personales (PDA), un ordenador de mano, un ordenador portátil, un receptor GPS, un dispositivo de navegación, una cámara, un reproductor de audio, una videocámara, una consola de juegos, un reloj, un cronómetro, una calculadora, un televisor, una pantalla plana, un monitor de ordenador, una pantalla automática (por ejemplo, una pantalla de odómetro, etc.), un control de cabina, una pantalla de cabina, una pantalla acoplada a una cámara (por ejemplo, una cámara de visión trasera y/o vista lateral en un vehículo), un marco de fotografía electrónica, una valla publicitaria electrónica, un letrero electrónico y un proyector.

45 50 El término "dispositivo móvil" puede describir, y no se limita a, un teléfono móvil, un dispositivo de comunicación móvil, un buscapersonas, un asistente digital personal, un administrador de información personal, un ordenador de mano móvil, un ordenador portátil, un dispositivo inalámbrico, un módem inalámbrico y/u otros tipos de dispositivos electrónicos portátiles que normalmente lleva una persona y que tienen capacidades de comunicación (por ejemplo, inalámbrico, celular, infrarrojo, radio de corto alcance, etc.). Además, los términos "equipo de usuario" (UE), "terminal móvil", "dispositivo móvil" y "dispositivo inalámbrico" pueden ser intercambiables.

#### Abreviaturas

55 La siguiente lista de abreviaturas y acrónimos de uso frecuente se proporciona para ayudar a comprender la divulgación actual y no se proporcionan como limitaciones.

6T SRAM: memoria de acceso aleatorio estática de seis transistores

BL - línea de bits

BLb - complemento de línea de bits

60 CORTAR: eliminar material depositado previamente (por ejemplo, mediante ablación, grabado y similares)

Ge - germanio

LE - litografía seguida de grabado

LELE - litografía seguida de grabado seguido de una segunda litografía seguida de un segundo grabado

65 LELELE: litografía seguida de grabado seguido de una segunda litografía seguida de un segundo grabado seguido de una tercera litografía seguida de un tercer grabado.

M0, M1 - capa de metal número cero, capa de metal número uno, etc.

MD1: una primera de dos capas de metal en el medio de la línea apilada debajo de la capa de metal uno.

MD2: una segunda de dos capas de metal en el medio de la línea apilada debajo de la capa de metal uno.

MP - contacto metálico en el medio de la línea para puerta de polisilicio.

NMOS - semiconductor de óxido metálico de tipo n

5 PD - bajada

PG - paso

PMOS - semiconductor de óxido metálico tipo p

PO - Polisilicio

PU - subida

10 SADP - patrón doble autoalineado

Si - silicio

SL - línea fuente

SRAM - memoria estática de acceso aleatorio

UE - equipo de usuario

15 V0, V1- número de capa de acceso de interconexión vertical (es decir, a través de)

WL - línea de palabras

#### Descripción de las figuras

20 La Figura 2 representa un esquema de una célula de bits de alto rendimiento ilustrativa 200 que es un ejemplo de una matriz de memoria estática de acceso aleatorio (SRAM) de alta densidad que tiene un patrón metálico avanzado. La célula de bits 200 incluye dos transistores semiconductores de óxido metálico de tipo p (PMOS) configurados como transistores de paso (PG) 205A-205B acoplados a las respectivas entradas 210A-210B de un circuito de enclavamiento biestable 215. Los dos transistores PMOS configurados como transistores de paso 205A-205B pueden fabricarse de un material que tenga una mayor movilidad de canal que el silicio, como el germanio silicio (SiGe). El circuito de enclavamiento biestable 215 incluye un par de inversores de semiconductores de óxido metálico complementarios (CMOS) compuestos por transistores PMOS de subida (PU) 220A-220B acoplados en serie con sus respectivos transistores de semiconductores de óxido metálico (NMOS) de tipo n de bajada (PD) 225A-225B. Como se representa en la Figura 2, las puertas y salidas de los transistores PMOS 220A-220B están acopladas de forma cruzada con los respectivos transistores NMOS 225A-225B.

30 En funcionamiento, con la potencia aplicada, se puede escribir un bit en la célula de bits de alto rendimiento 200, la célula de bits de alto rendimiento 200 puede retener el bit y el bit se puede leer desde la célula de bits de alto rendimiento 200. Cuando se desconecta la potencia de la célula de bits de alto rendimiento 200, la célula de bits de alto rendimiento 200 ya no retiene el bit. Los transistores de paso 205A-205B controlan el acceso entre las líneas de bits (BL, BLb) y el circuito de enclavamiento biestable 215 para controlar la escritura, retención y lectura de un bit mediante el circuito de enclavamiento biestable 215.

40 La Figura 2 también representa la realización de una operación de lectura de baja potencia de la célula de bits de alto rendimiento ilustrativa 200. Las líneas de bits se descargan previamente a sustancialmente cero voltios. La línea de palabras (WL) se mantiene baja para encender los transistores de paso 205A-205B y permitir el flujo de corriente (es decir, el acceso) entre las líneas de bits y el circuito de enclavamiento biestable 215. Como resultado, la célula lee el flujo de corriente a través de una de las líneas de bits, de los transistores de paso 205A-205B y uno de los PU PMOS 220A-220B a VDD (el transistorPMOS a través del cual la célula lee el flujo de corriente depende del 45 estado del circuito de enclavamiento biestable 215). Esto eleva el voltaje en una de las líneas de bits a sustancialmente VDD, dejando la otra línea de bits sustancialmente a un potencial de tierra. Se puede utilizar un amplificador de detección acoplado a las líneas de bits para determinar qué línea de bits se ha elevado - identificando así si la célula de bits de alto rendimiento 200 almacena un "0" lógico o un "1" lógico.

50 La Figura 3 representa un procedimiento 300 relacionado para fabricar una célula de bits SRAM de alta densidad que tiene un patrón metálico avanzado, tal como la célula de bits de alto rendimiento ilustrativa 200. Las células de bits representadas se pueden acoplar para formar una matriz de células de bits de SRAM de alta densidad que tienen un patrón metálico avanzado.

55 En la etapa 305, se forma una estructura de puerta de polisilicio (PO) (por ejemplo, el PG 205A-205B) mediante el uso de técnicas de litografía-grabado-litografía-grabado (LELE) o de doble patrón de autoalineación (SADP) y luego se corta.

60 Las técnicas de SADP pueden usarse para formar estructuras que tienen un tamaño de característica en una dimensión crítica que es más pequeña (por ejemplo, aproximadamente dos veces más pequeña) que una dimensión crítica de un aparato litográfico. Las técnicas SADP son particularmente útiles para fabricar líneas paralelas de material.

65 En un ejemplo, una técnica SADP incluye formar una máscara espaciadora que tiene un tamaño de característica que es dos veces más pequeño que la dimensión crítica estándar de un aparato litográfico. En primer lugar, se

deposita sobre un sustrato una capa de material de polisilicio de la que se van a formar las estructuras. Luego, se forma una máscara espaciadora sobre esta capa de material.

- 5 La máscara espaciadora se forma mediante el uso de una primera deposición fotolitográfica de material de sacrificio con una máscara de plantilla, en la dimensión crítica estándar del aparato litográfico, seguida de un primer grabado a través de una máscara litográfica en la dimensión crítica del aparato litográfico. Luego, se realiza una segunda deposición fotolitográfica del segundo material para formar la máscara espaciadora, seguida de un segundo grabado para eliminar una profundidad particular del segundo material. Sigue un tercer grabado para eliminar el material de sacrificio, que deja la máscara espaciadora formada por el segundo material sin eliminar en el segundo grabado. Un 10 cuarto grabado, a través de la máscara espaciadora, del material de polisilicio previamente dispuesto forma las estructuras que tienen el tamaño de característica en la dimensión crítica que es más pequeña que la dimensión crítica estándar del aparato litográfico. Por lo tanto, cada línea de la máscara espaciadora produce dos líneas. A continuación, se puede quitar la máscara espaciadora.

- 15 En la etapa 310, las estructuras MD1 y MP se forman mediante el uso de las respectivas técnicas LELE.

- En la etapa 315, se forman estructuras a través de nivel cero (V0) mediante el uso de una técnica LELE o una técnica de litografía-grabado-litografía-grabado-litografía-grabado (LELELE). Además, las estructuras de metal de nivel uno (M1) se crean formando las primeras líneas metálicas (representadas como las líneas verticales de extrema izquierda, centro y extrema derecha) en una sola dirección mediante el uso de una técnica LE, luego las líneas metálicas se cortan (por ejemplo, de forma continua) a intervalos sustancialmente iguales mediante el uso de una máscara de corte. Por lo tanto, las primeras líneas metálicas se cortan en una dirección sustancialmente perpendicular a la dirección de las primeras líneas metálicas para separar las primeras líneas metálicas sustancialmente paralelas en una pluralidad de islas que tienen los primeros lados respectivos que están 20 sustancialmente alineados en la dirección de las primeras líneas metálicas y los segundos lados respectivos que están sustancialmente alineados perpendiculares a las primeras líneas metálicas. Esto da como resultado islas en la pluralidad de islas que están alineadas, en lugar de escalonadas. Despues del corte, se forman dos líneas metálicas configuradas como líneas de palabra (WL) paralelas a las primeras líneas metálicas. Ver Figura 4 para obtener 25 detalles adicionales.

- 30 En la etapa 320, se forman estructuras a través de nivel cero (V1) mediante el uso de una técnica LELE. Además, las estructuras metálicas de nivel dos (M2) se forman al formar las segundas líneas metálicas en una sola dirección mediante el uso de técnicas LELE o SADP. Las segundas líneas metálicas se configuran como líneas VSS y BL.

- 35 La Figura 4 representa un detalle ilustrativo 400 sobre la fabricación de la línea de palabras (WL) de una capa de metal (M1) en el procedimiento ilustrativo 300. Específicamente, en un ejemplo, una isla VDD, BL y/o VSS formada durante la técnica de corte en la etapa 315 puede ser tan grande como  $2.760 \text{ nm}^2$  cuando el ancho de WL es sustancialmente de 40 nm ( $40 \text{ nm} \times 69 \text{ nm} = 2.760 \text{ nm}^2$ ). Por lo tanto, con este diseño se puede facilitar un área de almohadilla de aterrizaje más grande que la mínima permitida. Además, con este diseño se puede proporcionar 40 también un área de almohadilla de aterrizaje mínima permitida.

- 45 La Figura 5 también representa un procedimiento 500 relacionado para fabricar una célula de bits SRAM de alta densidad que tiene un patrón metálico avanzado, tal como la célula de bits de alto rendimiento ilustrativa 200. Las células de bits representadas se pueden acoplar para formar una matriz de células de bits de memoria estática de acceso aleatorio de alta densidad que tienen un patrón metálico avanzado.

- En la etapa 505, se forma una estructura de PO mediante el uso de técnicas LELE o SADP y luego se corta.

- 50 En la etapa 510, las estructuras MD1 y MP se forman mediante el uso de las respectivas técnicas LELE.

- En la etapa 515, se forman estructuras a través del nivel cero (V0) mediante el uso de una técnica LELELE. Además, las estructuras de metal de nivel uno (M1) se crean formando las primeras líneas metálicas (representadas como las líneas verticales de extrema izquierda, centro y extrema derecha) en una sola dirección mediante el uso de una técnica LE, luego las líneas metálicas se cortan a intervalos sustancialmente iguales mediante el uso de una 55 máscara de corte. En la etapa 515, el corte puede ser continuo, a excepción de una isla configurada como VSS (por ejemplo, cada tercera isla). No separar la línea VSS en dos islas separadas permite que dos líneas VSS adyacentes (por ejemplo, como se muestra en la etapa 320) se combinen en una sola línea VSS. Esta combinación reduce la capacitancia de la línea de bits, lo que mejora el rendimiento eléctrico de la célula de bit. Además, las primeras líneas metálicas se cortan en una dirección sustancialmente perpendicular a la dirección de las primeras líneas 60 metálicas para separar las primeras líneas metálicas sustancialmente paralelas en una pluralidad de islas que tienen los primeros lados respectivos que están sustancialmente alineados en la dirección de las primeras líneas metálicas y los segundos lados respectivos que están sustancialmente alineados perpendiculares a las primeras líneas metálicas (a excepción de la isla configurada como VSS). Esto da como resultado islas alineadas, en lugar de escalonadas. Despues del corte, se forman dos líneas metálicas configuradas como líneas de palabra (WL) 65 paralelas a las primeras líneas metálicas.

En la etapa 520, se forman estructuras a través de nivel cero (V1) (representadas como cajas negras) mediante el uso de una técnica LELE. Además, las estructuras metálicas de nivel dos (M2) se forman al formar las segundas líneas metálicas en una sola dirección mediante el uso de técnicas LELE o SADP. Las segundas líneas metálicas se configuran como líneas VSS y BL.

5 La Figura 6 representa un sistema de comunicación ilustrativo 600 en el que se puede emplear ventajosamente una realización de la divulgación. Para facilitar la ilustración, la Figura 6 muestra tres unidades remotas 605, 615 y 625 y dos estaciones base 620A-B. El sistema de comunicación 600 puede tener más o menos unidades remotas y más o menos estaciones base. Las unidades remotas 605, 615 y 625 incluyen al menos una parte de una realización 610A-C de la divulgación como se discute adicionalmente en la presente memoria. La Figura 6 también muestra señales de enlace directo 630 desde las estaciones base 620A-B y las unidades remotas 605, 615 y 625, así como señales de enlace inverso 635 de las unidades remotas 605, 615 y 625 a las estaciones base 620A-B.

10 15 En la Figura 6, la unidad remota 605 se muestra como un teléfono móvil, la unidad remota 615 se muestra como un ordenador portátil y la unidad remota 625 se muestra como una unidad remota de ubicación fija en un sistema de bucle local inalámbrico. En ejemplos, las unidades remotas 615 pueden ser un dispositivo móvil, un teléfono móvil, una unidad de sistemas de comunicación personal (PCS) de mano, una unidad de datos portátil tal como un asistente de datos personales, un dispositivo habilitado para GPS, un dispositivo de navegación, un decodificador, un reproductor de música, un dispositivo móvil, un reproductor de video, una unidad de entretenimiento o cualquier otro dispositivo que almacene o recupere datos o instrucciones informáticas, o cualquier combinación de los mismos. Aunque la Figura 6 representa unidades remotas de acuerdo con las enseñanzas de la divulgación, la divulgación no se limita a estas unidades remotas ilustrativas. Las realizaciones de la divulgación se pueden emplear de manera adecuada en cualquier dispositivo que incluya memoria SRAM.

20 25 30 35 40 La Figura 7 representa un de punto de acceso (AP) ilustrativo 700. El punto de acceso 700 puede ser, por ejemplo, cualquiera de las estaciones base 620A-B. Como se muestra, el punto de acceso 700 incluye un procesador de datos TX 710, un modulador de símbolos 720, una unidad transmisora (TMTR) 730, una o más antenas (por ejemplo, las antenas 740A-B), una unidad receptora (RCVR) 750, un demodulador de símbolos 760, un procesador de datos RX 770 y un procesador de información de configuración 780, que realizan diversas operaciones para comunicarse con uno o más dispositivos móviles (por ejemplo, los dispositivos de usuario 705A-B). El punto de acceso 700 también puede incluir uno o más controladores y/o procesadores (ilustrados en singular como el controlador/procesador 785) y una memoria 790 (por ejemplo, la célula de bits de alto rendimiento 200) configurada para almacenar datos o instrucciones relacionados. Juntas, a través de un bus 795, estas unidades pueden realizar el procesamiento de acuerdo con una tecnología o tecnologías de radio apropiada utilizadas para la comunicación, así como otras funciones para el punto de acceso 700. La célula de bits de alto rendimiento ilustrativa 200 puede ser parte de un circuito dentro y/o acoplado a una parte del punto de acceso 700, tal como el procesador de datos TX 710, el modulador de símbolos 720, la unidad transmisora 730, la unidad receptora 750, el demodulador de símbolos 760, el procesador de datos RX 770 y/o el procesador de información de configuración 780 y/o el controlador/procesador 785. En un ejemplo, cualquiera de las estaciones base 620A-B y/o el punto de acceso 700 se configura para realizar al menos una parte de un procedimiento descrito en la presente memoria.

45 50 55 El punto de acceso 700 puede proporcionar una interfaz aérea de red de área local inalámbrica (WLAN) (por ejemplo, de acuerdo con un protocolo IEEE 802.11x) y/o una interfaz aérea celular (por ejemplo, de acuerdo con un protocolo LTE). El punto de acceso 700 puede comunicarse con un dispositivo de usuario (por ejemplo, los dispositivos de usuario 705A-B), y un dispositivo de usuario (por ejemplo, los dispositivos de usuario 705A-B) puede comunicarse con el punto de acceso 700. En general, el punto de acceso 700 puede proporcionar una interfaz aérea (por ejemplo, de acuerdo con un protocolo IEEE 802.11x) sobre una parte sin licencia del espectro inalámbrico, como una banda de radio industrial, científica y médica (ISM), y/o puede proporcionar una interfaz aérea (por ejemplo, de acuerdo con un protocolo LTE) sobre una parte con licencia de la banda inalámbrica reservada para comunicaciones celulares. El punto de acceso 700 también puede configurarse para proporcionar conectividad celular (por ejemplo, LTE) sobre una parte sin licencia del espectro inalámbrico. Este tipo de operación celular sin licencia puede incluir el uso de un operador con licencia de anclaje que opere en una parte con licencia del espectro inalámbrico (por ejemplo, Enlace descendente suplementario (SDL) LTE) y una parte sin licencia del espectro inalámbrico (por ejemplo, LTE sin licencia), o puede ser una configuración independiente que funcione sin utilizar un operador con licencia de anclaje (por ejemplo, LTE independiente).

60 65 La Figura 8 ilustra varios componentes que se pueden utilizar en un dispositivo inalámbrico 800 (por ejemplo, un dispositivo móvil) que se pueden emplear dentro del sistema de comunicación 600. El dispositivo inalámbrico 800 es un ejemplo de un dispositivo que puede configurarse para incluir el aparato descrito en la presente memoria. El dispositivo inalámbrico 800 puede ser, por ejemplo, cualquiera de las tres unidades remotas 605, 615 y 625. El dispositivo inalámbrico 800 puede ser un dispositivo móvil, tal como un dispositivo de usuario (por ejemplo, los dispositivos de usuario 705A-B).

El dispositivo inalámbrico 800 puede incluir un procesador 805 que controla el funcionamiento del dispositivo inalámbrico 800. El procesador 805 también puede denominarse unidad central de procesamiento (CPU). Una memoria 810, que puede incluir tanto memoria de sólo lectura (ROM) como memoria de acceso aleatorio (RAM) (por

ejemplo, la célula de bits de alto rendimiento 200), proporciona instrucciones y datos al procesador 805. Una parte de la memoria 810 también puede incluir una memoria de acceso aleatorio no volátil (NVRAM). El procesador 805 realiza operaciones lógicas y aritméticas en base a instrucciones de programa almacenadas dentro de la memoria 810. Las instrucciones en la memoria 810 se pueden ejecutar para implementar los procedimientos descritos en la

5 presente memoria.

El procesador 805 puede comprender o ser un componente de un sistema de procesamiento implementado con uno 10 o más procesadores. El uno o más procesadores se pueden implementar con un microprocesador, un microcontrolador, un procesador de señal digital (DSP), una matriz de puerta programable en campo (FPGA), un dispositivo lógico programable (PLD), un controlador, una máquina de estado, lógica cerrada, un componente de hardware discreto, una máquina de estado finito de hardware dedicado y/o cualquier otra entidad adecuada que 15 pueda calcular y/o manipular información.

El sistema de procesamiento también puede incluir un medio legible por máquina no transitorio que almacena 20 software. Software puede significar cualquier tipo de instrucciones, ya sea que se denomine software, firmware, software intermedio, microcódigo, lenguaje de descripción de hardware y/o de otro modo. Las instrucciones pueden incluir código (por ejemplo, en formato de código fuente, formato de código binario, formato de código ejecutable o cualquier otro formato de código adecuado). Las instrucciones, cuando se ejecutan por uno o más procesadores, 25 pueden transformar el procesador (por ejemplo, el procesador 805) en un procesador de propósito especial que hace que el procesador realice una función descrita en la presente memoria.

El dispositivo inalámbrico 800 también puede incluir una carcasa 815, un transmisor 820 y un receptor 825 para 25 aceptar la transmisión y recepción de datos entre el dispositivo inalámbrico 800 y una ubicación remota. El transmisor 820 y el receptor 825 se pueden combinar en un transceptor 830. Una antena 835 puede acoplarse a la carcasa 815 y acoplarse eléctricamente al transceptor 830. El dispositivo inalámbrico 800 también puede incluir (no mostrado) múltiples transmisores, múltiples receptores, múltiples transceptores y/o múltiples antenas.

El dispositivo inalámbrico 800 puede comprender además un procesador de señal digital (DSP) 840 que se configura 30 para procesar datos. El dispositivo inalámbrico 800 también puede comprender además una interfaz de usuario 845. La interfaz de usuario 845 puede comprender un teclado, un micrófono, un altavoz y/o una pantalla. La interfaz de usuario 845 puede incluir cualquier elemento y/o componente que transmita información a un usuario del dispositivo inalámbrico 800 y/o reciba información del usuario.

Los diversos componentes del dispositivo inalámbrico 800 pueden acoplarse entre sí mediante un sistema de bus 35 850. El sistema de bus 850 puede incluir un bus de datos, por ejemplo, así como un bus de potencia, un bus de señales de control y/o un bus de señales de estado además del bus de datos. Los expertos en la técnica valorarán que los componentes del dispositivo inalámbrico 800 pueden acoplarse todos para aceptar o proporcionar entradas entre sí mediante el uso de algún otro mecanismo.

40 La célula de bits de alto rendimiento ilustrativa 200 puede ser parte de un circuito dentro, y/o acoplada, a una parte del dispositivo inalámbrico 800, tal como el procesador 805, la memoria 810, el transmisor 820, el receptor 825, y/o el DSP 840. En un ejemplo, cualquiera de las estaciones base 620A-B y/o el dispositivo inalámbrico 800 se configura para realizar al menos una parte de un procedimiento descrito en la presente memoria.

45 Aunque se ilustran varios componentes separados en la Figura 8, los expertos en la técnica reconocerán que uno o más de los componentes pueden combinarse o implementarse comúnmente. Por ejemplo, el procesador 805 puede usarse para implementar no solo la funcionalidad descrita anteriormente con respecto al procesador 805, sino también para implementar la funcionalidad descrita anteriormente con respecto al DSP 840. Además, cada uno de 50 los componentes ilustrados en la Figura 8 se pueden implementar mediante el uso de una pluralidad de elementos separados.

55 Los expertos en la técnica apreciarán además que los diversos bloques lógicos ilustrativos, módulos, circuitos, y etapas de algoritmos que se describen en torno a las realizaciones divulgadas en la presente memoria se pueden implementar como hardware electrónico, software informático, o combinaciones de ambos. Para ilustrar claramente esta intercambiabilidad de hardware y software, diversos componentes, bloques, módulos, circuitos, y etapas ilustrativos se han descrito anteriormente generalmente en términos de su funcionalidad. Si tal funcionalidad se implementa como hardware o software depende de la solicitud particular y las restricciones de diseño impuestas en el sistema general. Los expertos en la técnica pueden implementar la funcionalidad que se describe de diversas formas para cada aplicación particular, pero tales decisiones de implementación no se deben interpretar como causa 60 de una desviación del ámbito de la presente invención.

65 En algunos aspectos, las enseñanzas en la presente memoria se pueden emplear en un sistema de acceso múltiple capaz de soportar la comunicación con múltiples usuarios compartiendo los recursos del sistema disponibles (por ejemplo, al especificar uno o más de ancho de banda, potencia de transmisión, codificación, entrelazado, etc.). Por ejemplo, las enseñanzas en la presente memoria se pueden aplicar a cualquiera o combinaciones de las siguientes tecnologías: Sistemas de acceso múltiple por división de código (CDMA), CDMA de múltiples portadoras

(MCCDMA), CDMA de banda ancha (W-CDMA), sistemas de acceso de paquetes de alta velocidad (HSPA, HSPA+), sistemas de acceso múltiple por división de tiempo (TDMA), sistema de acceso múltiple por división de frecuencia (FDMA), sistemas FDMA de portadora única (SC-FDMA), sistemas de acceso múltiple por división de frecuencia ortogonal (OFDMA) u otras técnicas de acceso múltiple. Se puede diseñar un sistema de comunicación inalámbrica que emplee las enseñanzas en la presente memoria para implementar uno o más estándares, tales como IS-95, cdma2000, IS-856, W-CDMA, TDSCDMA y otros estándares. Una red de CDMA puede implementar una tecnología de radio tal como Acceso Universal por Radio Terrestre (UTRA), cdma2000 o alguna otra tecnología. UTRA incluye W-CDMA y Baja velocidad de chip (LCR). La tecnología cdma2000 cubre los estándares IS-2000, IS-95 e IS-856. Una red TDMA puede implementar una tecnología de radio como el Sistema Global para Comunicaciones Móviles (GSM). Una red OFDMA puede implementar una tecnología de radio como UTRA Evolucionada (E-UTRA), IEEE 802.11, IEEE 802.16, IEEE 802.20, Flash-OFDM.RTM., etc. UTRA, E-UTRA, y GSM son parte del Sistema Universal de Telecomunicaciones Móviles (UMTS). Las enseñanzas en la presente memoria se pueden implementar en un sistema 3GPP de Evolución a largo plazo (LTE), un sistema de banda ancha ultra móvil (UMB) y otros tipos de sistemas. LTE es una versión de UMTS que usa E-UTRA. UTRA, E-UTRA, GSM, UMTS y LTE se describen en documentos de una organización denominada "Proyecto de Asociación de Tercera Generación" (3GPP), mientras que cdma2000 se describe en documentos de una organización denominada "Proyecto de Asociación de Tercera Generación 2" (3GPP2). Aunque ciertos aspectos de la divulgación se pueden describir mediante el uso de la terminología 3GPP, debe entenderse que las enseñanzas en la presente memoria se pueden aplicar a la tecnología 3GPP (por ejemplo, Re199, Re15, Re16, Re17), así como a la tecnología 3GPP2 (por ejemplo, 1xRTT, 1xEV-D0 RelO, RevA, RevB) y otras. Las técnicas se pueden utilizar en redes e interfaces emergentes y futuras, que incluyen Evolución a largo plazo (LTE).

Al menos una parte de los procedimientos, secuencias y/o algoritmos descritos en torno a las realizaciones divulgadas en la presente memoria pueden incorporarse directamente en el hardware, en un módulo de software ejecutado por un procesador, o en una combinación de los dos. En un ejemplo, un procesador incluye múltiples componentes de hardware discretos. Un módulo de software puede encontrarse en la memoria RAM, en la memoria flash, en la memoria ROM, en la memoria EPROM, la memoria EEPROM, los registros, el disco duro, un disco extraíble, un CD-ROM, y/o en cualquier otra forma de medio de almacenamiento conocido en la técnica. Un medio de almacenamiento ilustrativo (por ejemplo, una memoria) puede acoplarse al procesador de manera que el procesador pueda leer la información desde, y escribir la información en, el medio de almacenamiento. Como alternativa, el medio de almacenamiento se puede integrar al procesador.

Además, muchas realizaciones se describen en términos de secuencias de acciones a ejecutar, a modo de ejemplo, por elementos de un dispositivo informático. Las acciones descritas en la presente memoria pueden ser realizadas por un circuito específico (por ejemplo, un circuito integrado específico de aplicación (ASIC)), por instrucciones de programa que se ejecutan por uno o más procesadores, o por una combinación de ambos. Además, una secuencia de acciones descritas en la presente memoria puede considerarse que se incorpora en su totalidad, dentro de cualquier forma de medio de almacenamiento legible por ordenador que tenga almacenado un conjunto correspondiente de instrucciones informáticas que, al ejecutarse, causarán que un procesador asociado (como un procesador de propósito especial) realice al menos una parte de una función descrita en la presente memoria. Por lo tanto, los diversos aspectos de la invención pueden materializarse de varias formas diferentes, todas las cuales se han contemplado dentro del ámbito de la materia objeto reivindicada. Además, para cada una de las realizaciones descritas en la presente memoria, un circuito correspondiente a cualquiera de tales realizaciones puede describirse en la presente memoria como, por ejemplo, "lógica configurada para" realizar una acción descrita.

Una realización de la invención puede incluir un medio legible por ordenador que incorpore un procedimiento descrito en la presente memoria. Por consiguiente, la invención no se limita a ejemplos ilustrados y cualquier medio para realizar las funciones descritas en la presente memoria se incluye en las realizaciones de la invención.

Los dispositivos y procedimientos divulgados pueden diseñarse y configurarse en un archivo ejecutable por ordenador que esté en un formato compatible con un Sistema de Base de Datos Gráfica dos (GDSII), un formato compatible con un Estándar abierto de intercambio de sistema de objetos (OASIS) y/o GERBER (por ejemplo, RS-274D, RS-274X, etc.), que se almacenan en un medio legible por ordenador no transitorio (es decir, no transitorio). El archivo se proporciona a un manipulador de fabricación que confecciona mediante el uso de un dispositivo litográfico, en base al archivo, un dispositivo integrado. La deposición de un material para formar al menos una parte de una estructura descrita en la presente memoria se puede realizar mediante el uso de técnicas de deposición tales como la deposición física de vapor (PVD, por ejemplo, pulverización catódica), la deposición química de vapor mejorada con plasma (PECVD), la deposición química térmica de vapor (CVD) y/o recubrimiento por rotación. El grabado de un material para formar al menos una parte de una estructura descrita en la presente memoria se puede realizar mediante el uso de técnicas de grabado tales como grabado con plasma. En un ejemplo, el dispositivo integrado está en una oblea semiconductor. La oblea semiconductor se puede cortar en un molde semiconductor y empacarse en un chip semiconductor. El chip semiconductor se puede emplear en un dispositivo descrito en la presente memoria (por ejemplo, un dispositivo móvil).

Nada de lo que se indica o ilustra en la presente solicitud tiene la intención de dedicar ningún componente, etapa, característica, objeto, beneficio, ventaja o equivalente al público, independientemente de si el componente, etapa, característica, objeto, beneficio, ventaja o equivalente se menciona en las reivindicaciones.

- 5 Si bien esta divulgación describe realizaciones ilustrativas de la invención, debe tenerse en cuenta que se podrían realizar varios cambios y modificaciones en la presente memoria sin apartarse del ámbito de la invención tal como se define en las reivindicaciones adjuntas.

## REIVINDICACIONES

1. Un procedimiento para fabricar una memoria estática de acceso aleatorio, que comprende:

5 formar, mediante el uso de una técnica de modelado doble autoalineante, una pluralidad de primeras líneas metálicas paralelas orientadas en una primera dirección en una primera capa; grabar las primeras líneas metálicas paralelas, mediante el uso de una máscara de corte en una segunda dirección perpendicular a la primera dirección, para separar las primeras líneas metálicas paralelas en una pluralidad de islas que tienen los primeros lados respectivos que están alineados en la primera dirección y los segundos lados respectivos que están alineados en la segunda dirección;

10 formar, en una segunda capa, una pluralidad de segundas líneas metálicas orientadas en la primera dirección; y formar un transistor de paso de silicio-germanio de óxido metálico-silicio tipo p que incluye una puerta acoplada a una segunda línea metálica en la segunda pluralidad de líneas metálicas y un drenaje acoplado a una isla en la pluralidad de islas.

15 2. El procedimiento de la reivindicación 1, en el que una segunda línea metálica en la pluralidad de segundas líneas metálicas está configurada como una línea de palabras.

20 3. El procedimiento de la reivindicación 1, que comprende además integrar la memoria estática de acceso aleatorio en al menos uno de entre un dispositivo móvil, un decodificador, reproductor de música, reproductor de video, unidad de entretenimiento, dispositivo de navegación, dispositivo de comunicaciones, asistente digital personal, datos de ubicación fija unidad, y un ordenador.

25 4. Un medio legible por ordenador no transitorio, que comprende:

instrucciones ejecutables del dispositivo litográfico almacenadas en el mismo, y un archivo ejecutable por ordenador almacenado en el medio legible por ordenador que se proporciona a un gestor de fabricación para ejecutar un procedimiento para fabricar una memoria estática de acceso aleatorio que incluye:

30 formar, mediante el uso de una técnica de modelado doble autoalineante, una pluralidad de primeras líneas metálicas paralelas orientadas en una primera dirección en una primera capa; grabar las primeras líneas metálicas paralelas, mediante el uso de una máscara de corte en una segunda dirección perpendicular a la primera dirección, para separar las primeras líneas metálicas paralelas en una pluralidad de islas que tienen los primeros lados respectivos alineados en la primera dirección y los segundos lados respectivos 35 alineados en la segunda dirección, en el que al menos una de las islas de la pluralidad de isla está configurada como una línea de bits;

35 formar, en una segunda capa, una pluralidad de segundas líneas metálicas orientadas en la primera dirección; y formar un transistor de paso de silicio-germanio de óxido metálico-silicio tipo p que incluye una puerta acoplada a una segunda línea metálica en la segunda pluralidad de líneas metálicas y un drenaje acoplado a una isla en la pluralidad de islas.

40 5. El medio legible por ordenador no transitorio de la reivindicación 4, en el que el procedimiento comprende además configurar una isla en la pluralidad de islas como una línea de palabras.

(Técnica anterior)

Figura 1

Figura 2

|          |                             |                     |                                                                                       |                                                                |

|----------|-----------------------------|---------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Diagrama | Fin, PO                     | MD1, MP             | V0, M1                                                                                | V1, M2                                                         |

|          | $\delta^{21}$               | MD1_c1<br>MD1_c2    | WL<br>WL                                                                              | VSS<br>BL<br>Vdd<br>BL<br>VSS<br>VSS<br>BL<br>Vdd<br>BL<br>VSS |

| Modelado | PO, LELE (o SADP)<br>+corte | MD1 LELE<br>MP LELE | V0, LELE<br>M1,<br>LE(V)+corte+LE(V)<br>Último LE para WL<br>Patrón de corte continuo | V1, LELE<br>M2, LELE (o SADP)                                  |

Mín área M1 = 40x69 n ( $=2760 \text{ nm}^2$ )

300 → 305 → 310 → 315 → 320

Figura 3

|          |                          |                     |                                                                                                   |                                                                              |

|----------|--------------------------|---------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Diagrama | Fin, PO                  | MD1, MP             | V0, M1                                                                                            | V1, M2                                                                       |

|          | 62n                      | MD1 c1<br>MD1 c2    | WL<br>V0<br>Vdd<br>Vss<br>BL<br>30n<br>50n<br>120n<br>50n<br>BL<br>Vdd<br>BL<br>Vss               | WL<br>V1<br>Vdd<br>Vss<br>BL<br>50n<br>120n<br>50n<br>BL<br>Vdd<br>BL<br>Vss |

| Modelado | PO, LELE (o SADP) +corte | MD1 LELE<br>MP LELE | V0, LELE<br>M1,<br>LE(V)+corte+LE(V)<br>Último LE para WL.<br>Corte de patrón de ruptura<br>@ Vss | V1, LELE<br>M2, LELE (o SADP)                                                |

Figura 5

Figura 6

Figura 7

Figura 8