## (19) World Intellectual Property **Organization**

International Bureau

#

(43) International Publication Date 8 April 2004 (08.04.2004)

**PCT**

### (10) International Publication Number WO 2004/029636 A1

(51) International Patent Classification<sup>7</sup>: 31/00, H04B 17/00

G01R 1/04,

(21) International Application Number:

PCT/IB2003/003987

(22) International Filing Date:

12 September 2003 (12.09.2003)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

0222556.3

28 September 2002 (28.09.2002)

- (71) Applicant (for all designated States except US): KONIN-KLIJKE PHILIPS ELECTRONICS N.V. [NL/NL]; Groenewoudseweg 1, NL-5621 BA Eindhoven (NL).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): GUTHRIE, Brian, J. [GB/GB]; c/o Philips Intellectual Property & Standards, Cross Oak Lane, Redhill, Surrey RH1 5HA (GB). SPENCER, Adrian, G. [GB/GB]; c/o Philips Intellectual

Property & Standards, Cross Oak Lane, Redhill, Surrey RH1 5HA (GB).

- (74) Agent: WHITE, Andrew, G.; Philips Intellectual Property & Standards, Cross Oak Lane, Redhill, Surrey RH1 5HA (GB).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

with international search report

[Continued on next page]

(54) Title: RF CHIP TESTING METHOD AND SYSTEM

(57) Abstract: A method and system for testing RF chips for radio specification compliance is described. The system comprises a test board (80) having a plurality of interconnected sockets (82a,b,c) for receiving chips to be tested. In testing, signals generated by transmitter circuitry (20) within a group of test chips are used to test the receiver (30) functionality of the other chips loaded in the system. Hence, for tests requiring several analogue radio signals, a plurality of chips are tested at the same time using signals generated from other chips. Additionally, the system does not require expensive dedicated RF analogue signal generating equipment.

## WO 2004/029636 A1

before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

1

#### DESCRIPTION

#### RF CHIP TESTING METHOD AND SYSTEM

The present invention relates to radio frequency (RF) testing methods and further relates to a testing system suitable for practising such methods. The present invention has particular, but not exclusive, application in the testing of the RF functionality of integrated circuit chips and the compliance of such functionality with an intended radio standard or specification.

10

15

5

Radio frequency integrated circuit (IC or 'chip') manufacturing requires testing to determine whether the manufactured ICs are compliant with a radio standard (e.g. Bluetooth<sup>TM</sup>, GSM<sup>TM</sup>, IEEE802.15.4) and operational in other respects. Typically, a pick and place machine will place the chip device to be tested in a suitably constructed test board or 'test head' of specialised automated test equipment (ATE). The ATE applies the appropriate test signals to the device under test (DUT) and passes or rejects the device. Such individual chip testing exhibits a problem in that it is time consuming and hence adds to the overall manufacturing cost.

20

25

Another particular problem in testing the functionality of an RF chip for compliance with a radio standard exists in that the specification may require the ATE to generate several specific analogue RF signals at the same time in order to test, for example, the interference performance of the receiver of the DUT. Special signal generating hardware is therefore required, adding cost to the ATE, and therefore expense to the manufacturer. Furthermore, the application of such signals is often via long probes brought down into contact with the pin-out of the chips, requiring a specially constructed and controlled test suite. The use of such probes results in unspecified and difficult to quantify losses reducing the accuracy of any such test.

30

It is therefore an object of the present invention to provide an improved method and system for RF chip testing.

2

According to a first aspect of the present invention there is provided a method for testing a plurality of integrated circuit chips for compliance with a radio standard, each chip having transmission means and receiving means for sending and receiving RF signals, the method comprising:

• placing the chips in close proximity to one another,

10

15

20

25

30

- testing the transmission means of each chip with respect to a known good reference chip,

- selecting a number of the chips to form a generating group, the remaining chips forming a receiving group, and

- testing the receiving group using signals generated by the generating group.

According to a further aspect of the present invention there is provided a testing system for testing a plurality of integrated circuit chips, each chip having transmission means and receiving means for sending and receiving RF signals, the system comprising:

a computer having communication, control and data acquisition means for communicating with, controlling and acquiring data from testing means to which it is connected,

the testing means comprising a plurality of chip sockets adapted to physically accept and electronically interface with a chip placed therein, and wherein each socket is provided with signal propagation and attenuation means for sending and receiving signals to each of the other sockets under the control of the computer,

and where in operation the computer selects a group of chips to generate test signals which are propagated via the propagation means to a reception test group of chips.

The method and system of the present invention implement applicant's appreciation that many compliance tests in the RF field require a number of signals to be generated, and that the RF chips being tested may be utilised in the system to generate such signals. Hence, a system is provided in which a group of chips, having passed transmission generation tests for example, are

3

utilised to generate the signals required to test the reception hardware of the other chips.

Preferably, the number of chips selected corresponds to the number of signals required for the particular test. For example, in an interference test a "wanted" signal with two other "interfering signals" must be generated on certain specified channels to determine the quality of the receiver. In such an example test, three chips are therefore required to be selected for the test. If one considers the situation where there are eight chips mounted in the system, then such an interference test requires that three chips are selected (the generating group) to provide the three signals to the remaining five chips (the receiving test group). Following the test, three of the five chips just tested may be selected for the generation group and these then provide the signals to the previous generating group. Hence, such an interference test only requires two "passes" to test all eight chips, and no extra signal generating hardware. This compared with eight individual tests required in a conventional system which in addition requires signal generating hardware to generate the three signals for the above example test, and individual probing (which has the disadvantage of including unknown losses due to such probing).

10

15

20

25

30

Advantageously, each chip's signal may be attenuated via programmable attenuators before being provided to the test group of chips. This allows for imbalance in transmission and reception power required for a test. For example the Bluetooth specification requires a transmission power of 0dBm whilst the chips receiving hardware requires a signal of the order of -70dBm, therefore the signals generated by the group of chips require 70dB attenuation.

In a preferred embodiment, the computer is a standard PC with a digital data acquisition card to interface it to the test board. The control and test routines and analysis of data captured by the card are provided in software. Hence this digital test equipment is relatively inexpensive and flexible enabling different tests for different radio specifications to be installed or downloaded as required by the customer.

4

The present invention will now be described, by way of example only, and with reference to the accompanying drawings wherein:

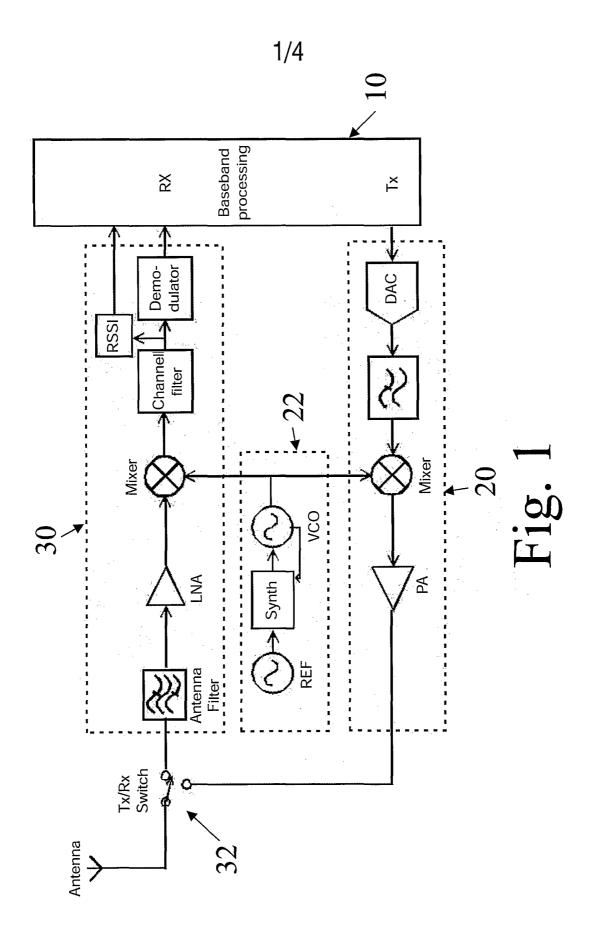

Figure 1 is a block diagram of the circuitry of an RF chip being a device under test (DUT);

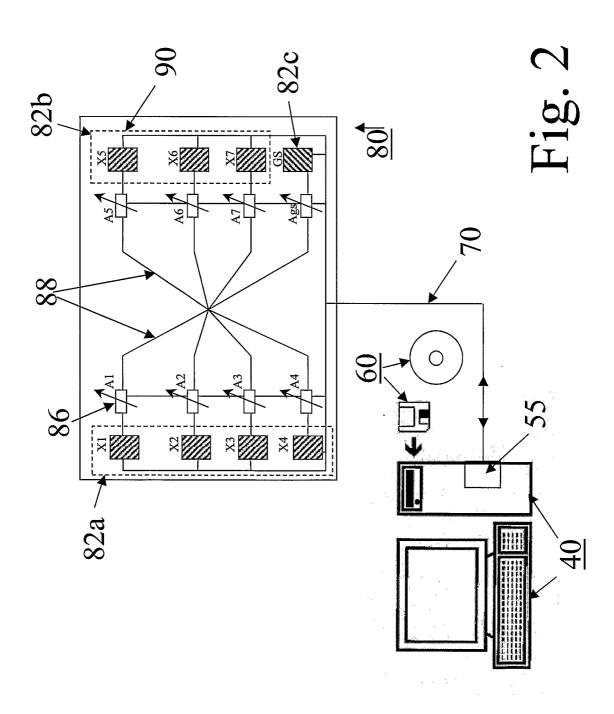

Figure 2 is a schematic diagram of a system for testing a chip as shown in Fig. 1;

5

10

15

20

25

30

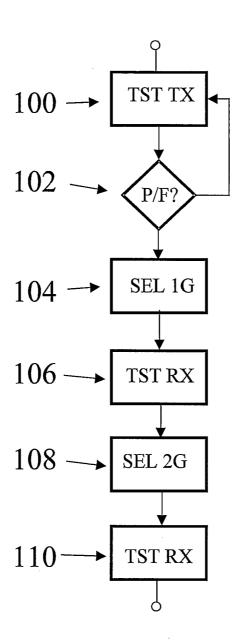

Figure 3 is flow diagram representing example steps of a method embodying the invention;

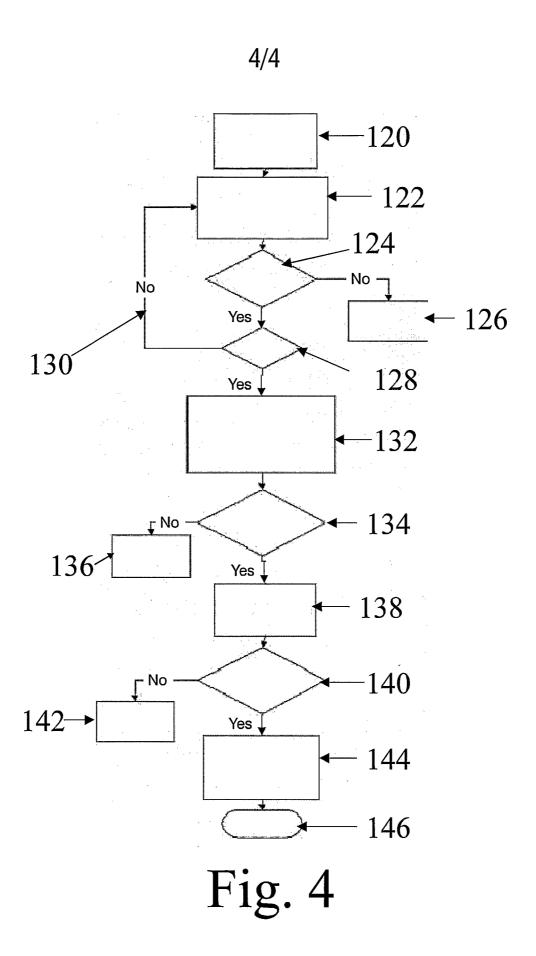

Figure 4 is another flow diagram representing example steps of a method embodying the invention in which intermodulation and other receiver tests are performed.

It should be noted that the Figures are diagrammatic and not drawn to scale. Relative dimensions and proportions of parts of these Figures have been shown exaggerated or reduced in size, for the sake of clarity and convenience in the drawings. The same reference signs are generally used to refer to corresponding or similar features in modified and different embodiments.

Figure 1 shows a typical transceiver architecture for an RF chip. This architecture comprises a baseband section 10 connected with a transmission chain 20 comprising a digital to analog converter (DAC) for converting the intended digital signal to an analogue signal, a mixing stage where the signal is mixed with the output of a frequency synthesiser block 22 and a power amplifier for amplifying the resulting signal. A receiving chain 30 comprises an antenna filter, a low noise amplifier, a mixing stage, channel filtering and demodulating stage. Such a general transceiver having transmission and reception means for generating and transmitting/receiving signals is well known to those skilled in the art. In an application, for example a mobile phone or personal digital assistant (PDA), the transceiver is connected to an antenna for radiating or receiving radiated signals. In a testing environment, prior to incorporation in a final product such as a mobile phone, the transceiver (Tx) 20 and receiver (Rx) 30 blocks are connected to relevant pins of the chip

5

(if packaged) or a pad/probe applied to the appropriate test location on the silicon die containing the transceiver circuitry (if testing is prior to packaging).

An integrated circuit for producing for example, Bluetooth signals may do so via such an architecture as shown in Fig. 1, together with a layered protocol. The Bluetooth protocol or specification as laid out in the Bluetooth specification v1.1 requires the radio performance of such a chip to meet certain test requirements. Pages 20-32 of the aforementioned specification, which are incorporated herein for reference and to which the reader is now directed, specify among others the following tests: output power and power control of the transmitter, sensitivity, interference performance, intermodulation characteristic and receiver signal strength indicator.

10

15

20

25

30

It is to be noted that several of these tests require a number of signals to be generated at the same time. In particular, characterisation of the receiver for interference performance involves co-channel and adjacent channel tests which each require two transmission signals to be generated. The characterisation and testing of the intermodulation characteristics of the receiver require three signals to be generated - a wanted signal at a first frequency  $f_0$  with a power level 6dB over the reference sensitivity level, a static sine wave signal at another frequency  $f_1$  with a power level of -39 dBm and a bluetooth modulated signal at a further frequency  $f_2$  with a power level of -39dBm, such that  $f_0$  -  $2f_1$  - $f_2$  and  $mod(f_2$ - $f_1)$  = n\*1 MHz where n can be 3, 4, or 5. In general the Bit Error Rate (BER) is measured and evaluated against a predetermined level (e.g. 0.1%) to provide a pass/fail for these tests.

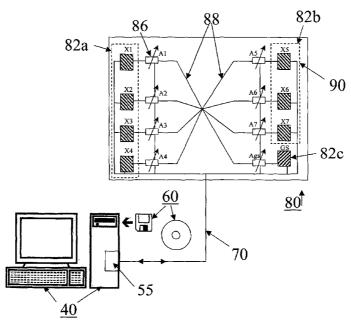

Figure 2 is a diagram of a digital testing system embodying the present invention. The system comprises a computer in the form of a PC 40 having a display and a digital acquisition card (DAQ) 55, a suitable example being National Instruments<sup>™</sup> PCI 7030/6030E. Testing routines, control and analysis software are provided with the computer on suitable media 60, or may be downloaded over a suitable internet link (not shown). The computer and DAQ are connected to a test board or "test head" 80 via a SCSI link 70 although other suitable interface links 70 may be used (IEEE1394 'Firewire', and USB being common examples).

6

The board 80 comprises in this embodiment eight chip sockets 82a,b,c (labelled X1,X2 to X7, and GS in the diagram) for accepting radio chips for testing. Each socket interfaces electronically (via techniques well known in the art such as tensioned pins or solderbump pads) with the chip mounted therein. Suitably designed tracks 88 with programmable attenuators 86 (A1 to A7, Ags) for interconnecting and propagating signals from one chip socket to another are provided. Control and input/output (I/O) data is passed between the computer 40 and sockets via the test head link 70. In this embodiment the socket 82c is provided for a "golden sample" chip. This chip has been previously tested and characterised and is used as a reference with which to compare the characteristics of other chips just manufactured.

10

15

20

25

30

Figure 3 illustrates a flow chart example of a testing method performed by the system of Figure 2, and as implemented by software 60. In the method chips are loaded into sockets 82a,b. The golden sample socket 82c is loaded with a golden sample. In the basic method according to the invention the transmission circuitry 20 of each chip is tested (step 100) with respect to the golden sample. For example the power output of each transceiver may be measured and compared with the known golden sample power output which is within the specified Bluetooth requirements. After testing all of the loaded chips X1-X7, the computer determines (step 102) whether the result was a pass or fail for each chip and stores the result in memory. The testing then moves onto testing the receiver chain 30 of each chip for specification compliance.

In step 104 the computer selects a first group of chips (for example the chips mounted in sockets X5, X6 and X7 as denoted by the dashed box labelled 82b in Figure 2) which will form a signal generating group for generating the signals which must be received by the remaining test chips 82a in order to test the receiver circuitry 30 of those remaining chips. Under the control of the computer the receiving group of chips are each subjected to the signals generated by the first group, thereby testing the receiver circuitry 30 of those chips in parallel (step 106). In this embodiment, the transmitted signals from X5, X6 and X7 are attenuated by the programmable attenuators A5, A6,

10

15

20

25

30

A7 and then passed down signal propagation tracks 88 to the receiver test group 82a of X1, X2, X3 and X4. Following step 106, the generating group becomes a receiving group to enable testing of the receiver circuitry of those chips, and a new second generating group is selected ('SEL 2G' step 108) to generate the test signals. The receiving group (which acted as the first generating group previously) is subsequently tested in step 110 and the results from the tests analysed.

Hence, RF analogue signals which are required for testing the receiver functionality of a radio chip are generated "on-board" by a group of chips which themselves form part of the test. Additionally, the signals are routed to the test chips in parallel, hence saving time and effectively testing the receiver group of chips instantaneously.

Figure 4 illustrates a flowchart giving a particular example of testing requirements which are necessary for evaluating a Bluetooth<sup>™</sup> radio chip and wherein a methodology embodying the invention is applied. In this particular example seven chips labelled X1 to X7 are to be tested with respect to a golden sample for transmission characteristics (power output and control) and receiver characteristics (intermodulation, co-channel, adjacent channel, sensitivity and Receiver Signal Strength Indicator (RSSI)), wherein:

- block 120 IC's X<sub>i</sub> (i=1 to 7) are loaded as is the golden sample chip, following which;

- block 122 IC X<sub>i</sub> transmits a signal s<sub>i</sub> at a first frequency f1 to the golden sample chip, and attenuator A<sub>i</sub> is programmed to reduce the power of signal s<sub>i</sub> after which;

- in block 124 the BER of the signal s<sub>i</sub> as received by the golden sample is analysed and a decision is made as to whether the transmitter of X<sub>i</sub> is either:

- o not within specification (block 126), X<sub>i</sub> is characterised as a reject and is not included in any further tests,

- o or is within specification, the result is stored and

- in block 128, a determination is made (is i<7?) whether all chips have been tested. If there are still chips to be tested then i=i+1 and the

5

10

15

20

25

30

program flow follows path 130 back to block 122. Once all chips have been tested (i=7) then the program flow moves to the next required tests in block 132;

- Block 132 Intermodulation tests are performed to determine receiver characteristics. X1, X3 and X3 selected to provide a wanted signal, an interfering signal and a co-channel signal respectively. A1, A2 and A3 are programmed to limit outputs;

- Block 134 the signals are provided by X1, X2 and X3 to the remaining chips X4, X5, X6 and X7 and the results analysed for each IC as to whether it:

- Fails block 136 IC is rejected as receiver not within specification

- o Or passes in which case flow moves to

- Block 138 wherein X4, X5 and X6 are selected to generate the intermodulation test signals and A4, A5 and A6 programmable attenuators are programmed to limit outputs, following which:

- Block 140, the signals are provided by X4, X5 and X6 to the remaining chips X1, X2, X3 and the results analysed for each IC as to whether it:

- Fails block 142 IC is rejected as receiver not within specification

- Or passes in which case flow moves to

- Block 144 wherein the remaining RF tests (co-channel, Adjacent channel, sensitivity and RSSI calibration are performed on those chips which have previously passed the transmitter tests (block 124) and the intermodulation receiver tests (blocks 134 and 140) after which

- those IC which have passed all tests are noted as being within test specification requirements.

In the above embodiments an example testing system and methods were described with reference to packaged Bluetooth<sup>TM</sup> radio chips.

In an alternative embodiment the sockets for accepting chips are replaced with suitably designed solder pads on which singulated die may be placed. Testing may then be executed as described previously. Hence, in this

9

embodiment a manufacturer is able to test integrated circuit chips in the form of singulated die before packaging, thereby enabling faster quality testing "upstream" of the packaging process.

Those skilled in the art of testing will recognise that implementing the example testing flow charts of Fig. 3 and Fig. 4 is a matter of software design for the digital testing equipment designer. The overall software control, interfacing and analysis aspects of the testing system may be routinely implemented by those skilled in the art of designing and building test heads and testing systems. Other well known features of automatic testing equipment, such as a "pick and place" machine for handling and loading/unloading chips from the test head, and the marking of chips with ink in the event of a test failure, although not mentioned in the above embodiments, will be recognised as being compatible with the above.

10

15

20

25

30

Furthermore, in the foregoing embodiments, the method and system aspects of the present invention were described as applied to packaged chips or singulated die IC, the IC being a Bluetooth<sup>TM</sup> compatible design. Those skilled in the art will recognise that the testing method and systems aspects of the present invention can readily be applied to other different radio chips requiring confirmation of conformity with a particular specification for which those chips are designed. Many radio chips require testing for so-called "front end linearity," with the radio specification specifying the linearity and absolute standards required. For example, radio standards such as IEEE802.15.4 ('ZigBee'), 'GSM', and the so called '3G' telephony standards require radio chips which can benefit from specification testing equipment and methods embodying the present invention.

From reading the present disclosure, other modifications will be apparent to persons skilled in the art. Such modifications may involve other features which are already known in the design, manufacture and use of RF testing systems, test heads and component parts thereof and which may be used instead of or in addition to features already described herein without departing from the spirit and scope of the present invention.

10

#### **CLAIMS**

1. A method for testing a plurality of integrated circuit chips for compliance with a radio standard, each chip having transmission means and receiving means for sending and receiving RF signals, the method comprising:

- placing the chips in close proximity to one another,

- testing (100) the transmission means of each chip with respect to a known good reference chip,

- selecting (104) a number of the chips to form a generating group,

the remaining chips forming a receiving group, and

- testing the receiving group (106) using signals generated by the generating group.

- 2. A method according to claim 1, wherein the chips are mounted on a test board prior to testing.

- 3. A method according to claim 1 or claim 2, wherein the selection of generating and receiving groups (104, 106) is repeated (108, 110) until all chips have been tested.

20

5

10

- 4. A method according to claim 3, wherein the number of chips selected to form a generating group is determined at least in part by the testing requirements.

- 5. A method according to claim 4, wherein the testing requirements specify a test requiring at least two generated signals.

- 6. A method according to claim 4 or claim 5, wherein the testing requirements specify an intermodulation test requiring three generated signals.

11

7. A testing system for testing a plurality of integrated circuit chips, each chip having transmission means (10, 20) and receiving means (10, 30) for sending and receiving RF signals, the system comprising:

a computer (40) having communication, control and data acquisition means (55) for communicating with, controlling and acquiring data from testing means to which it is connected,

the testing means (80) comprising a plurality of chip sockets (82a, b, c) adapted to physically accept and electronically interface with a chip placed therein, and wherein each socket is provided with signal propagation (88) and attenuation means (86) for sending and receiving signals to each of the other sockets under the control of the computer (40),

and where in operation the computer selects a group of chips (82b) to generate test signals which are propagated via the propagation means to a reception test group of chips (82a).

15

20

25

10

5

- 8. A system according to claim 7, wherein the sockets are located on a test board 80.

- 9. A system according to claim 7 or claim 8, wherein the signals generated by the selected group are radio frequency signals.

- 10. A test board (80) comprising a plurality of chip sockets (82a, b, c) adapted to physically accept and electronically interface with a chip placed therein, and wherein each socket is provided with signal propagation (88) and attenuation means (86) for sending and receiving test signals generated by at least one chip to each of the other sockets.

- 11. A computer program comprising instructions for performing a method according to any of claims 1 to 4 when run on a testing computer (40).

12

12. A computer readable storage medium (60) having recorded thereon data representing instructions for performing a method according to any of claims 1 to 6 when said data is loaded on a testing computer (40).

5

2/4

3/4

Fig. 3

#### INTERNATIONAL SEARCH REPORT

PCT/IB 03/03987

A. CLASSIFICATION OF SUBJECT MATTER IPC 7 G01R1/04 G01R31/00 H04B17/00

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

$\begin{array}{ccc} \text{Minimum documentation searched (classification system followed by classification symbols)} \\ IPC & 7 & G01R & H04B \end{array}$

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, PAJ, WPI Data

| C. DOCUM   | ENTS CONSIDERED TO BE RELEVANT                                                                                       |                       |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                   | Relevant to claim No. |  |  |

| Α          | US 5 337 316 A (WEISS ET AL.) 9 August 1994 (1994-08-09) column 1, line 42 - column 2, line 37; figures 1-5          |                       |  |  |

| <b>A</b>   | US 5 481 186 A (HEUTMAKER ET AL.) 2 January 1996 (1996-01-02) 3 column 1, line 54 - column 2, line 26; figures 1,2   | 1,7,9                 |  |  |

| A          | PATENT ABSTRACTS OF JAPAN vol. 2002, no. 11, & JP 2002 214292 A (ADVANTEST CORP), 31 July 2002 (2002-07-31) abstract | 7,10                  |  |  |

|            | -/                                                                                                                   |                       |  |  |

| χ Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | χ Patent family members are listed in annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "A" document defining the general state of the art which is not considered to be of particular relevance  "E" earlier document but published on or after the international filing date  "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means  "P" document published prior to the international filing date but later than the priority date claimed | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art. |

| Date of the actual completion of the international search  29 January 2004                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Date of mailing of the international search report $10/02/2004$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Name and mailing address of the ISA  European Patent Office, P.B. 5818 Patentlaan 2  NL – 2280 HV Rijswijk  Tel. (+31–70) 340–2040, Tx. 31 651 epo nl,  Fax: (+31–70) 340–3016                                                                                                                                                                                                                                                                                                                                                                        | Authorized officer  Iwansson, K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## **INTERNATIONAL SEARCH REPORT**

PCT/IB 03/03987

| C (Continu | ation) DOCUMENTS CONSIDERED TO BE RELEVANT                                         |                                       | PC1/1B 03/0398/       |  |  |

|------------|------------------------------------------------------------------------------------|---------------------------------------|-----------------------|--|--|

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages | · · · · · · · · · · · · · · · · · · · | Relevant to claim No. |  |  |

| A          | DE 32 29 749 A (SIEMENS)<br>16 February 1984 (1984-02-16)                          |                                       | 1,2,7-10              |  |  |

| Α          | abstract; figures 1-3<br><br>US 6 396 291 B1 (AKRAM)                               |                                       | 1,2,7-10              |  |  |

|            | 28 May 2002 (2002-05-28) column 3, line 34 - line 60; figure 1                     |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    | :                                     |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

|            |                                                                                    |                                       |                       |  |  |

## INTERNATIONAL SEARCH REPORT

PCT/IB 03/03987

| Patent document<br>cited in search report |    |            |                                  | Patent family<br>member(s)                                                        | Publication date                                                                 |  |

|-------------------------------------------|----|------------|----------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| US 5337316                                | Α  | 09-08-1994 | NONE                             |                                                                                   |                                                                                  |  |

| US 5481186                                | A  | 02-01-1996 | CA<br>DE<br>DE<br>EP<br>JP<br>JP | 2156655 A1<br>69528333 D1<br>69528333 T2<br>0706271 A2<br>3022281 B2<br>8274821 A | 04-04-1996<br>31-10-2002<br>17-04-2003<br>10-04-1996<br>15-03-2000<br>18-10-1996 |  |

| JP 2002214292                             | Α  | 31-07-2002 | WO                               | 02056042 A1                                                                       | 18-07-2002                                                                       |  |

| DE 3229749                                | Α  | 16-02-1984 | DE                               | 3229749 A1                                                                        | 16-02-1984                                                                       |  |

| US 6396291                                | B1 | 28-05-2002 | US                               | 6208157 B1                                                                        | 27-03-2001                                                                       |  |