(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7635301号

(P7635301)

(45)発行日 令和7年2月25日(2025.2.25)

(24)登録日 令和7年2月14日(2025.2.14)

|                          |                       |

|--------------------------|-----------------------|

| (51)国際特許分類               | F I                   |

| H 1 0 D 30/67 (2025.01)  | H 1 0 D 30/67 1 0 1 T |

| H 0 1 L 21/768 (2006.01) | H 0 1 L 21/90 B       |

| H 0 1 L 23/522 (2006.01) | H 1 0 D 86/40 1 0 1 B |

| H 1 0 D 86/40 (2025.01)  | H 1 0 D 64/20         |

| H 1 0 D 64/20 (2025.01)  | H 1 0 D 64/23 M       |

請求項の数 2 (全100頁) 最終頁に続く

|                   |                               |          |                                 |

|-------------------|-------------------------------|----------|---------------------------------|

| (21)出願番号          | 特願2023-101689(P2023-101689)   | (73)特許権者 | 000153878                       |

| (22)出願日           | 令和5年6月21日(2023.6.21)          |          | 株式会社半導体エネルギー研究所                 |

| (62)分割の表示         | 特願2022-45298(P2022-45298)の分割  |          | 神奈川県厚木市長谷398番地                  |

| 原出願日              | 平成30年1月24日(2018.1.24)         | (72)発明者  | 佐藤 優一                           |

| (65)公開番号          | 特開2023-130375(P2023-130375 A) |          | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内 |

| (43)公開日           | 令和5年9月20日(2023.9.20)          | (72)発明者  | 方堂 涼太                           |

| 審査請求日             | 令和5年7月4日(2023.7.4)            |          | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内 |

| (31)優先権主張番号       | 特願2017-13142(P2017-13142)     | (72)発明者  | 飯田 裕太                           |

| (32)優先日           | 平成29年1月27日(2017.1.27)         |          | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内 |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                       | (72)発明者  | 森若 智昭                           |

|                   |                               |          | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内 |

最終頁に続く

(54)【発明の名称】 半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

半導体層と、

前記半導体層上の凹部を有する第1の絶縁層と、

前記半導体層と電気的に接続され、前記第1の絶縁層を貫通する第1の導電層と、

前記第1の絶縁層上に位置し、開口を有する第2の絶縁層と、

前記開口の内壁と接する領域と、前記凹部と接する領域と、前記第1の導電層の上面と接する領域と、前記第1の導電層の上面と接しない領域と、を有する第2の導電層と、を有し、

前記開口は、前記凹部と重なる領域と、前記第1の導電層と重なる領域と、を有し、

前記第1の導電層の上面に前記第2の導電層が接する領域において、前記第1の導電層は曲面部を有し、

前記第1の導電層の上面に前記第2の導電層が接しない領域において、前記第1の導電層は、曲面部を有さず、

前記曲面部は、前記第1の絶縁層の上面より上の部分に位置している半導体装置。

## 【請求項2】

請求項1において、

前記第2の絶縁層は、第3の絶縁層と、前記第3の絶縁層の上に配置された第4の絶縁層と、を有し、

前記第3の絶縁層及び前記第4の絶縁層の一方は、圧縮応力を有し、

前記第3の絶縁層及び前記第4の絶縁層の他方は、引っ張り応力を有する半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の一態様は、容量素子、半導体装置、記憶装置ならびにこれらの作製方法に関する。または、本発明の一態様は、半導体ウエハ、モジュールおよび電子機器に関する。

【0002】

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。表示装置（液晶表示装置、発光表示装置など）、投影装置、照明装置、電気光学装置、蓄電装置、記憶装置、半導体回路、撮像装置および電子機器などは、半導体装置を有すると言える場合がある。

10

【0003】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。

【背景技術】

【0004】

近年、半導体装置の開発が進められ、LSIやCPUやメモリが主に用いられている。CPUは、半導体ウエハから切り離された半導体集積回路（少なくともトランジスタ及びメモリ）を有し、接続端子である電極が形成された半導体素子の集合体である。

20

【0005】

LSIやCPUやメモリなどの半導体回路（ICチップ）は、回路基板、例えばプリント配線板に実装され、様々な電子機器の部品の一つとして用いられる。

【0006】

また、絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタを構成する技術が注目されている。該トランジスタは集積回路（IC）や画像表示装置（単に表示装置とも表記する）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

30

【0007】

また、酸化物半導体を用いたトランジスタは、非導通状態において極めてリーク電流が小さいことが知られている。例えば、酸化物半導体を用いたトランジスタのリーク電流が低いという特性を応用した低消費電力のCPUなどが開示されている（特許文献1参照。）。また、例えば、酸化物半導体を用いたトランジスタのリーク電流が低いという特性を応用して、長期にわたり記憶内容を保持することができる記憶装置などが、開示されている（特許文献2参照。）。

【先行技術文献】

【特許文献】

40

【0008】

【文献】特開2012-257187号公報

【文献】特開2011-151383号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明の一態様は、微細化または高集積化が可能な容量素子または半導体装置を提供することを課題の一つとする。本発明の一態様は、生産性の高い容量素子または半導体装置を提供することを課題の一つとする。本発明の一態様は、静電容量の大きい容量素子を提供することを課題の一つとする。本発明の一態様は、良好な電気特性を有する半導体装置

50

を提供することを課題の一つとする。本発明の一態様は、良好な信頼性を有する半導体装置を提供することを課題の一つとする。

#### 【0010】

本発明の一態様は、長期間においてデータの保持が可能な半導体装置または記憶装置を提供することを課題の一つとする。本発明の一態様は、情報の書き込み速度が速い半導体装置または記憶装置を提供することを課題の一つとする。本発明の一態様は、消費電力を抑えることができる半導体装置または記憶装置を提供することを課題の一つとする。本発明の一態様は、単位面積当たりの記憶容量が大きい半導体装置または記憶装置を提供することを課題の一とする。本発明の一態様は、新規な半導体装置または記憶装置を提供することを課題の一つとする。

10

#### 【0011】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

#### 【課題を解決するための手段】

#### 【0012】

金属酸化物を有するトランジスタの上に、少なくとも一部が該トランジスタと重なるように容量素子を設けることにより、半導体装置の占有面積を低減し、微細化または高集積化を図ることができる。さらに、トランジスタの上に絶縁体を配置し、該絶縁体に形成された開口に埋め込むように容量素子を設けることにより、半導体装置の占有面積を低減し、且つ容量素子の静電容量を大きくすることができる。

20

#### 【0013】

さらに、トランジスタと容量素子との間に、水または水素などの不純物の透過を抑制する機能を有する絶縁体を設けることにより、容量素子などに起因する不純物がトランジスタに混入することを抑制できるので、電気特性および信頼性の良好なトランジスタを提供することができる。

#### 【0014】

また、不純物の透過を抑制する機能を有する絶縁体を貫通して、トランジスタと容量素子を電気的に接続する導電体が設けられる。該導電体の上部を、湾曲面を有する形状にすることで、該導電体と容量素子の下部電極の接触抵抗を低減し、半導体装置に良好な電気特性を与えることができる。

30

#### 【0015】

本発明の一態様は、第1の絶縁体と、第1の絶縁体を貫通するように配置された、第1の導電体と、第1の絶縁体の上に配置され、第1の絶縁体および第1の導電体に達する開口が形成された、第2の絶縁体と、開口の内壁、第1の絶縁体、および第1の導電体に接して配置された第2の導電体と、第2の導電体の上に配置された、第3の絶縁体と、第3の絶縁体の上に配置された、第4の導電体と、を有し、第1の絶縁体の第2の導電体と接する領域の膜厚は、第1の絶縁体の該領域以外の膜厚より薄く、第1の導電体は、第1の絶縁体の、第2の導電体と接する領域の上面より上の部分において、湾曲面を有する、容量素子である。

40

#### 【0016】

また、本発明の他の一態様は、トランジスタと、容量素子と、を有し、トランジスタは、金属酸化物と、金属酸化物と電気的に接続された、第1の導電体と、を有し、容量素子は、金属酸化物の上に配置され、第1の導電体が貫通している第1の絶縁体と、第1の絶縁体の上に配置され、第1の絶縁体および第1の導電体に達する開口が形成された、第2の絶縁体と、開口の内壁、第1の絶縁体、および第1の導電体に接して配置された第2の導電体と、第2の導電体の上に配置された、第3の絶縁体と、第3の絶縁体の上に配置された、第4の導電体と、を有し、第1の絶縁体は、第2の絶縁体より、水素の透過を抑制する機能が高い、半導体装置である。

50

## 【0017】

上記において、第1の導電体は、第1の絶縁体の、第2の導電体と接する領域の上面より上の部分において、湾曲面を有する、ことが好ましい。また、上記において、第1の導電体は、第1の絶縁体の、第2の導電体と接する領域の上面より下の部分において、底面と側面のなす角が90°以上である、ことが好ましい。また、上記において、第1の絶縁体の第2の導電体と接する領域の膜厚は、第1の絶縁体の該領域以外の膜厚より薄くなつてもよい。

## 【0018】

また、上記において、第1の絶縁体は、アルミニウムおよび酸素を含む、ことが好ましい。また、上記において、第2の絶縁体は、第5の絶縁体と、該第5の絶縁体の上に配置された第6の絶縁体と、を有し、第5の絶縁体および第6の絶縁体の一方は、圧縮応力を有し、第5の絶縁体および第6の絶縁体の他方は、引っ張り応力を有する、ことが好ましい。また、上記において、第4の導電体は、開口を埋め込むように形成され、第4の導電体は、第2の絶縁体と重なる領域を有し、第4の導電体の当該領域の上面の平均面粗さが2nm以下である、ことが好ましい。また、上記において、金属酸化物は、Inと、元素M(MはAl、Ga、Y、またはSn)と、Znと、を含む、ことが好ましい。

10

## 【0019】

また、本発明の他の一態様は、金属酸化物を有するトランジスタの上に第1の絶縁体を形成する工程と、第1の絶縁体の上に第2の絶縁体を形成する工程と、第1の絶縁体および第2の絶縁体に、トランジスタのソースおよびドレインの一方に達する第1の開口と、トランジスタのソースおよびドレインの他方に達する第2の開口を形成する工程と、第1の開口に第1の導電体を埋め込み、第2の開口に第2の導電体を埋め込む工程と、第2の絶縁体、第1の導電体、および第2の導電体の上に第3の絶縁体を形成する工程と、ドライエッチング処理を行い、第1の絶縁体および第1の導電体に達する第3の開口を形成する工程と、第3の開口の内壁、第1の絶縁体、および第1の導電体に接して、第3の導電体を形成する工程と、第3の導電体の上に第4の絶縁体を形成する工程と、第4の絶縁体の上に第4の導電体を形成する工程と、を有し、第1の絶縁体として、第2の絶縁体よりも、水素の透過を抑制する機能が高い絶縁体を用い、ドライエッチング処理において、少なくとも第1の導電体の上面が露出した段階で、エッチングガスに、炭素とフッ素を含み、かつ該炭素の原子数比が該フッ素の原子数比の50%以上であるガスを含む、半導体装置の作製方法である。

20

## 【0020】

また、上記において、第3の絶縁体を形成する工程において、PECVD法を用いて第1の酸化シリコンを成膜し、第1の酸化シリコンの上に、APCVD法を用いて第2の酸化シリコンを成膜する、ことが好ましい。また、上記において、第4の導電体を形成する工程において、第4の導電体を成膜し、第4の導電体の上に第5の絶縁体を成膜し、第4の導電体が露出するようにCMP処理を行うことが好ましい。また、上記のドライエッチング処理において、エッチングガスにアルゴンを含み、アルゴンの流量が、エッチングガス全体の流量の90%以上である、ことが好ましい。

30

## 【0021】

また、上記において、第1の絶縁体は、アルミニウムを含むターゲットを用いて、酸素を含む雰囲気でスパッタリング法で成膜する、ことが好ましい。また、上記において、金属酸化物は、Inと、元素M(MはAl、Ga、Y、またはSn)と、Znと、を含むターゲットを用いてスパッタリング法で成膜する、ことが好ましい。

40

## 【発明の効果】

## 【0022】

本発明の一態様により、微細化または高集積化が可能な容量素子または半導体装置を提供することができる。本発明の一態様により、生産性の高い容量素子または半導体装置を提供することができる。本発明の一態様により、静電容量の大きい容量素子を提供することができる。本発明の一態様により、良好な電気特性を有する半導体装置を提供すること

50

ができる。本発明の一態様により、良好な信頼性を有する半導体装置を提供することができる。

【0023】

本発明の一態様により、長期間においてデータの保持が可能な半導体装置または記憶装置を提供することができる。本発明の一態様により、情報の書き込み速度が速い半導体装置または記憶装置を提供することができる。本発明の一態様により、消費電力を抑えることができる半導体装置または記憶装置を提供することができる。本発明の一態様により、単位面積当たりの記憶容量が大きい半導体装置または記憶装置を提供することができる。本発明の一態様により、新規な半導体装置または記憶装置を提供することができる。

【0024】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

【図面の簡単な説明】

【0025】

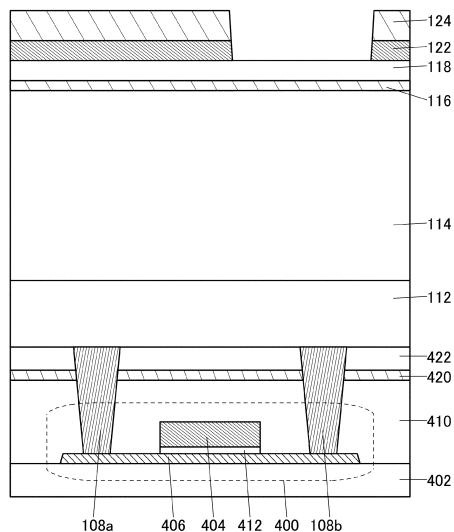

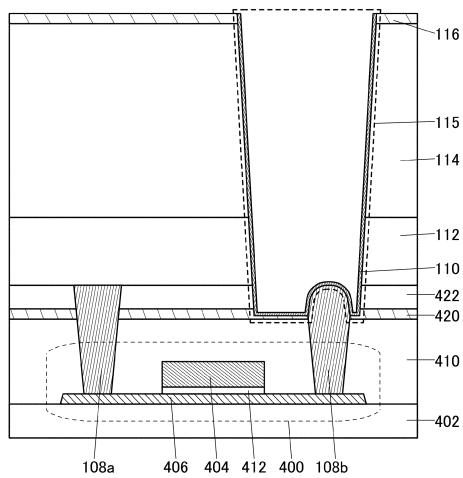

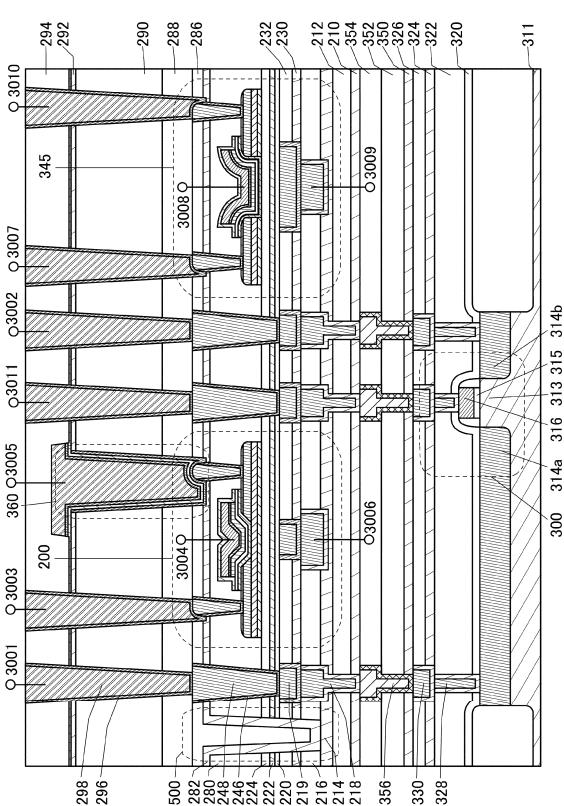

【図1】本発明の一態様に係る半導体装置の断面図。

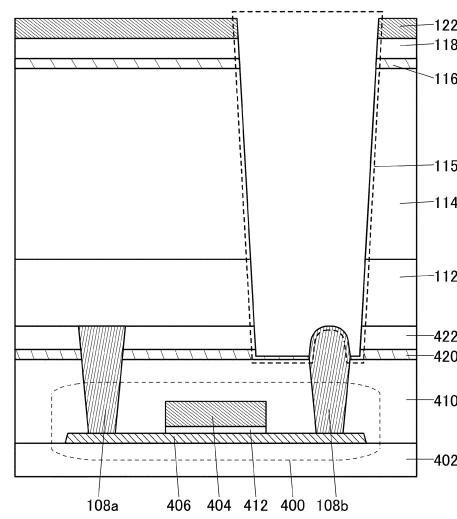

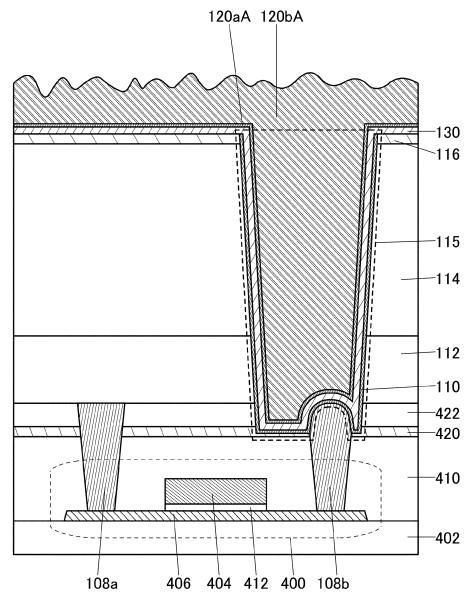

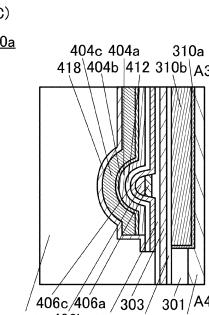

【図2】本発明の一態様に係る半導体装置の作製方法を示す断面図。

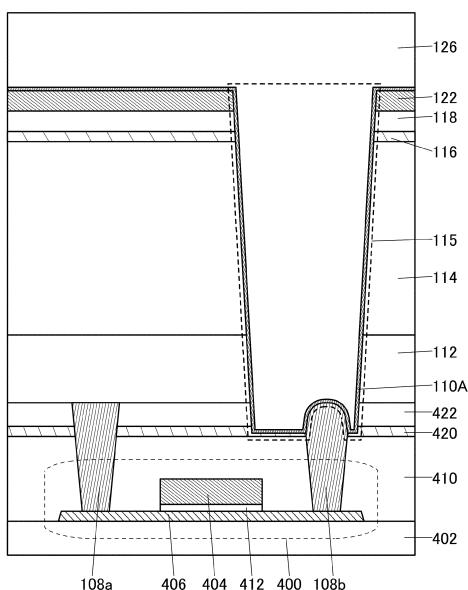

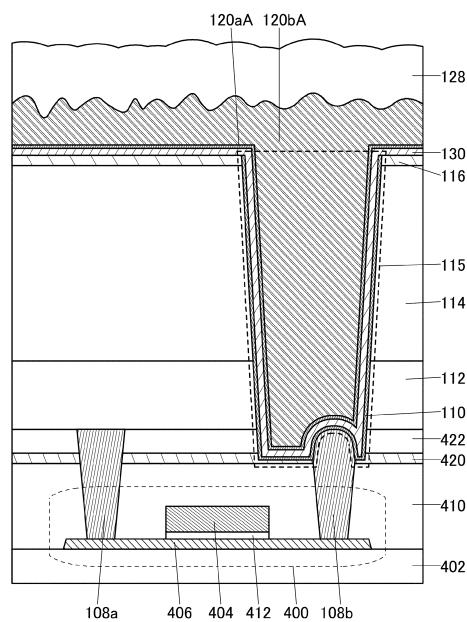

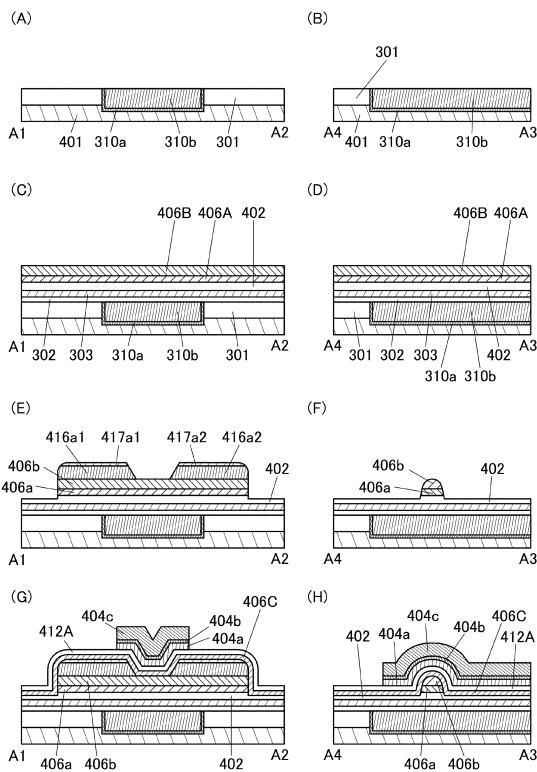

【図3】本発明の一態様に係る半導体装置の作製方法を示す断面図。

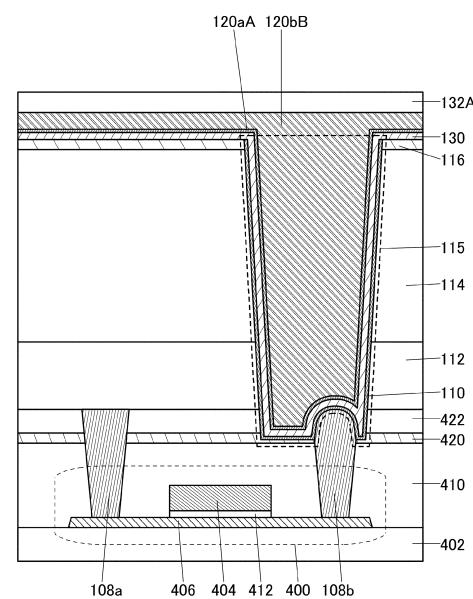

【図4】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図5】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図6】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図7】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図8】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図9】本発明の一態様に係る半導体装置の作製方法を示す断面図。

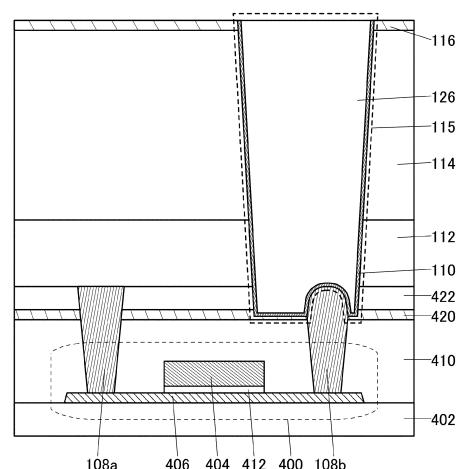

【図10】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図11】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図12】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図13】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図14】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図15】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図16】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図17】本発明の一態様に係る半導体装置の断面図。

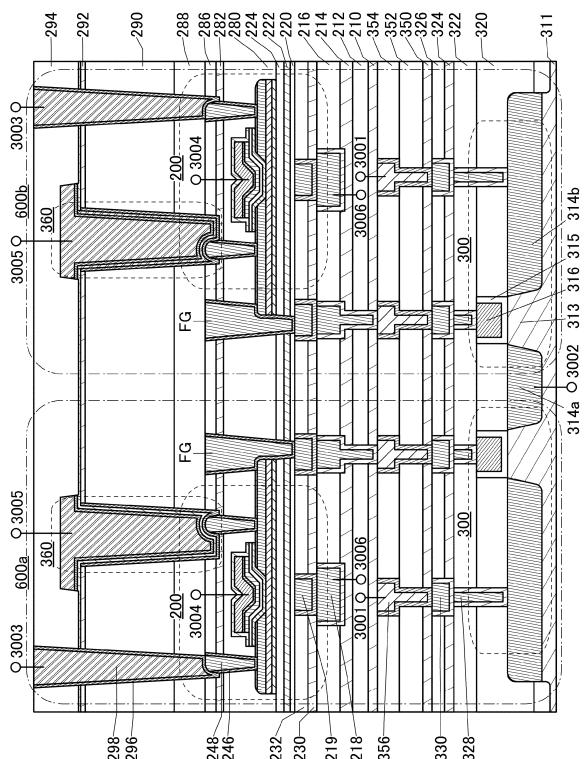

【図18】本発明の一態様に係る半導体装置の断面図。

【図19】本発明の一態様に係る半導体装置の断面図。

【図20】本発明の一態様に係る半導体装置の上面図および断面図。

【図21】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図22】本発明の一態様に係る半導体装置の作製方法を示す断面図。

【図23】本発明の一態様に係る半導体装置の上面図および断面図。

【図24】本発明の一態様に係る半導体装置の上面図および断面図。

【図25】本発明の一態様に係る半導体装置の上面図および断面図。

【図26】本発明の一態様に係る金属酸化物の原子数比の範囲を説明する図。

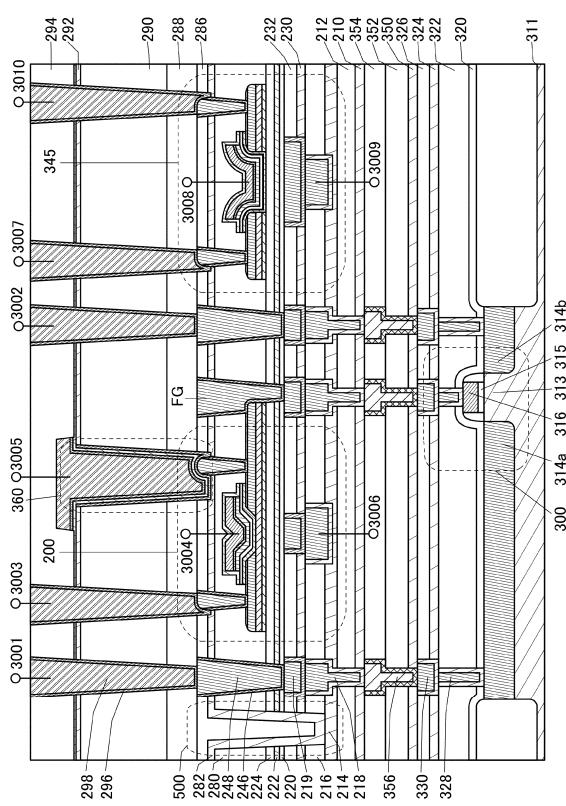

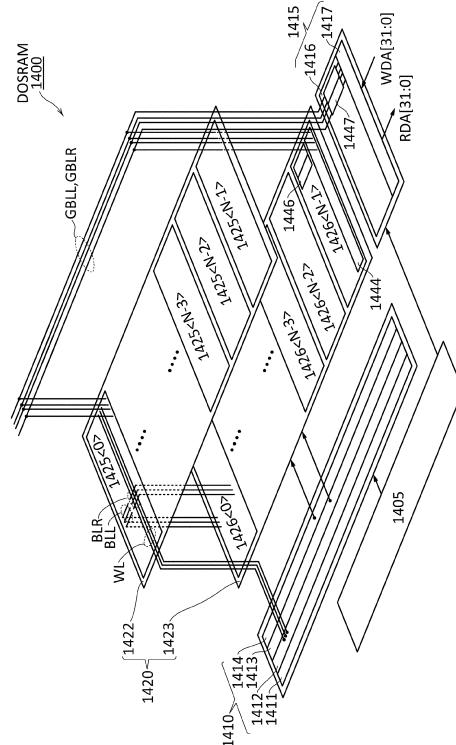

【図27】本発明の一態様に係る記憶装置の構成を示す断面図。

【図28】本発明の一態様に係る記憶装置の構成を示す断面図。

【図29】本発明の一態様に係る記憶装置の構成を示す断面図。

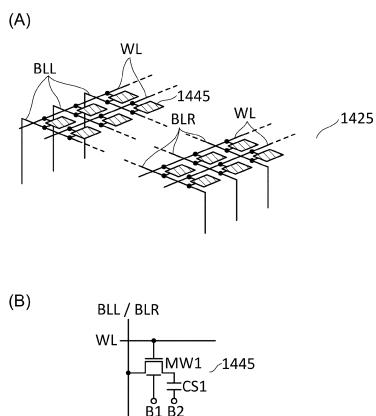

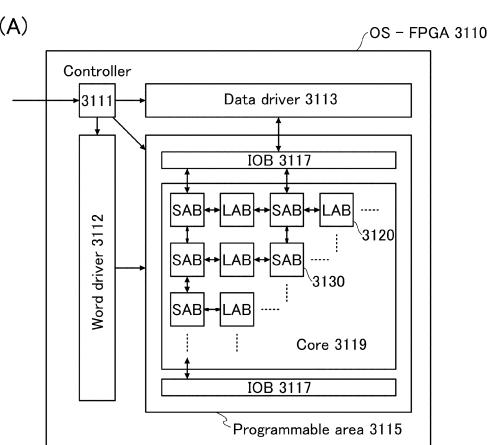

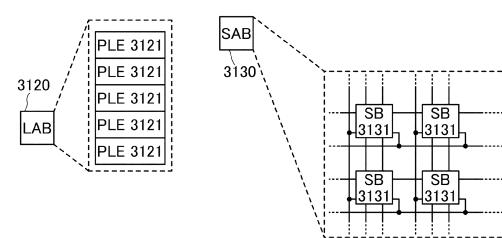

【図30】本発明の一態様に係る記憶装置の構成例を示すブロック図。

【図31】本発明の一態様に係る記憶装置の構成例を示すブロック図、および回路図。

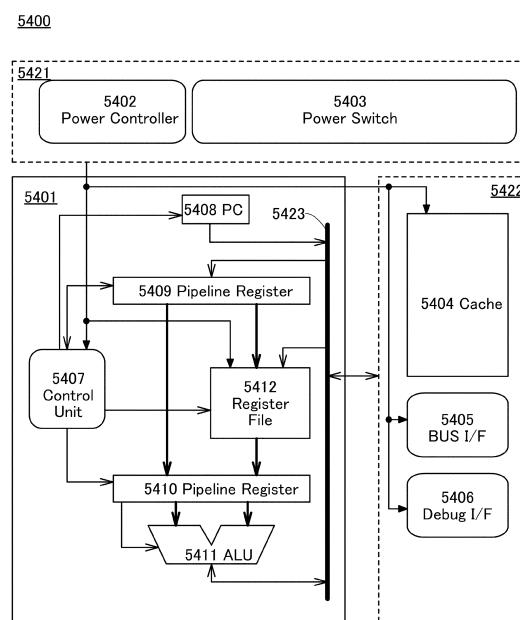

【図32】本発明の一態様に係る半導体装置の構成例を示すブロック図。

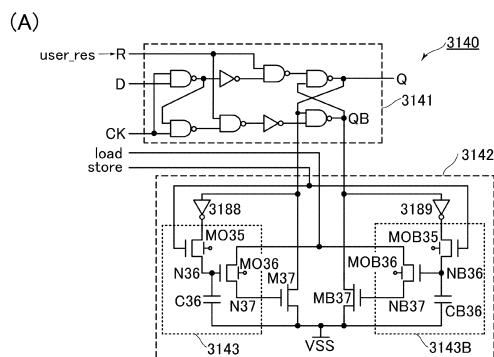

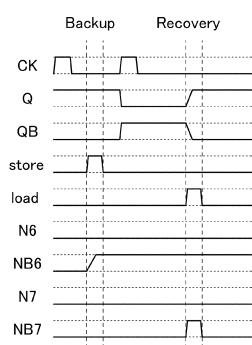

【図33】本発明の一態様に係る半導体装置の構成例を示すブロック図、回路図、および半導体装置の動作例を示すタイミングチャート。

10

20

30

40

50

【図34】本発明の一態様に係る半導体装置の構成例を示すブロック図。

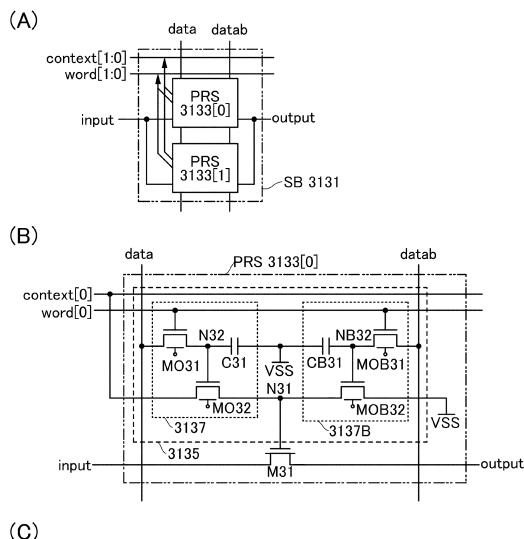

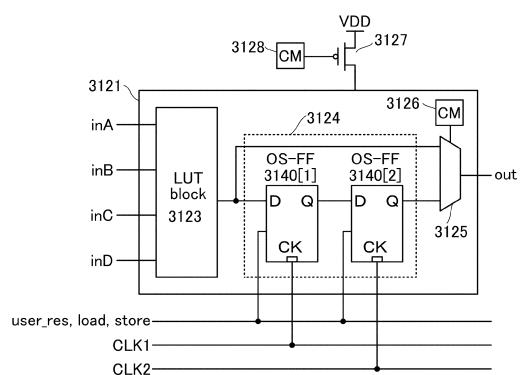

【図35】本発明の一態様に係る半導体装置の構成例を示す回路図、および半導体装置の動作例を示すタイミングチャート。

【図36】本発明の一態様に係る半導体装置を示すブロック図。

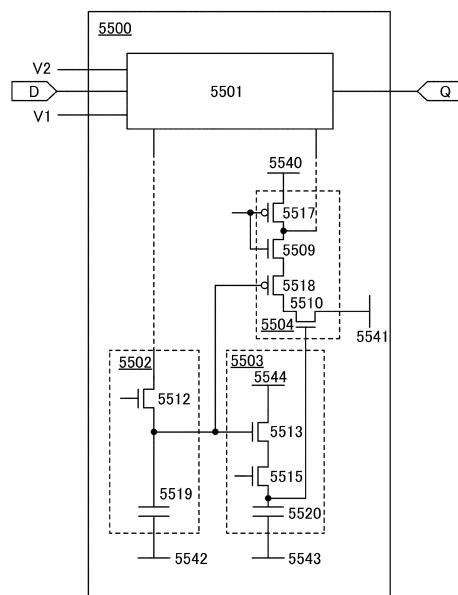

【図37】本発明の一態様に係る半導体装置を示す回路図。

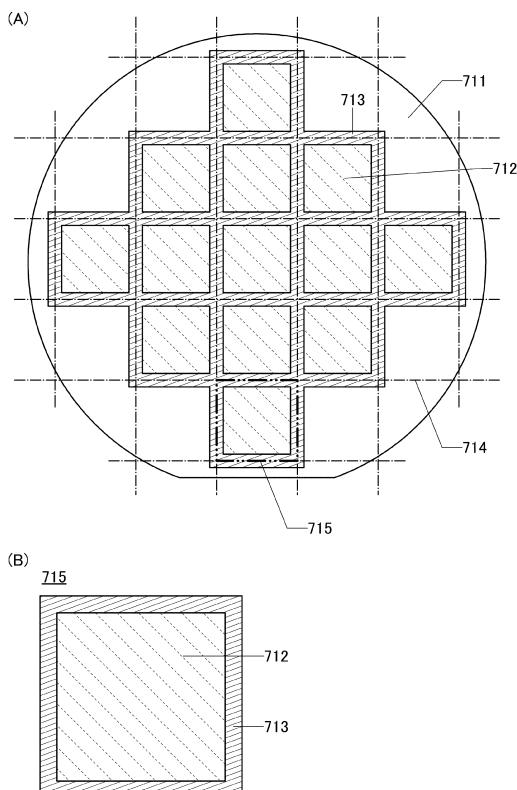

【図38】本発明の一態様に係る半導体ウエハの上面図。

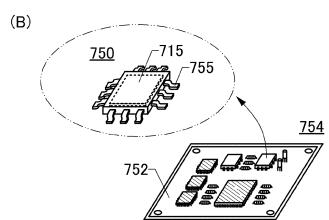

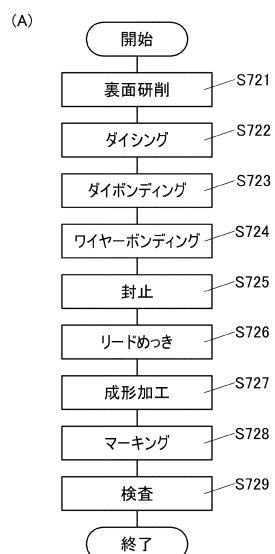

【図39】電子部品の作製工程例を説明するフローチャートおよび電子部品の斜視模式図。

【図40】本発明の一態様に係る電子機器を示す図。

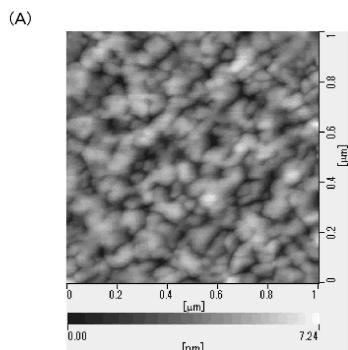

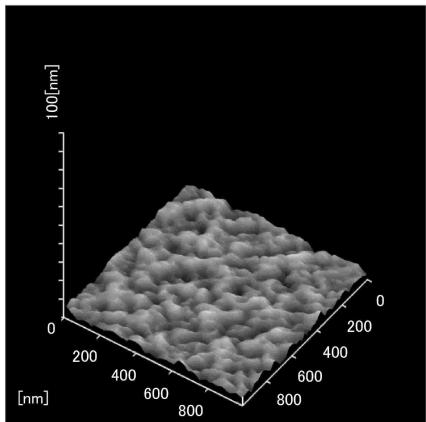

【図41】本発明の実施例に係るAFM画像。

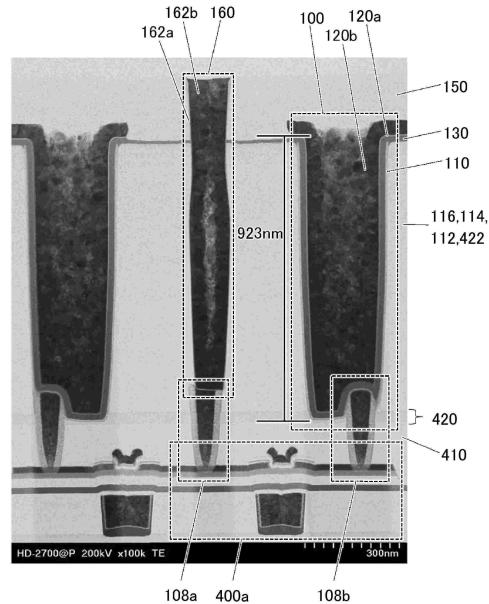

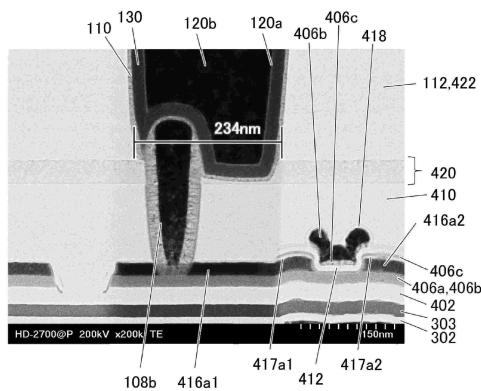

【図42】本発明の実施例に係る断面SEM像。

【図43】本発明の実施例に係る断面SEM像。

【発明を実施するための形態】

【0026】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

【0027】

また、図面において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模式的に示したものであり、図面に示す形状又は値などに限定されない。例えば、実際の製造工程において、エッチングなどの処理により層やレジストマスクなどが意図せずに目減りすることがあるが、理解を容易とするために省略して示すことがある。また、図面において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する場合がある。また、同様の機能を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

【0028】

また、特に上面図（「平面図」ともいう。）や斜視図などにおいて、発明の理解を容易とするため、一部の構成要素の記載を省略する場合がある。また、一部の隠れ線などの記載を省略する場合がある。

【0029】

また、本明細書などにおいて、第1、第2等として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。そのため、例えば、「第1の」を「第2の」又は「第3の」などと適宜置き換えて説明することができる。また、本明細書等に記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

【0030】

また、本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。

【0031】

例えば、本明細書等において、XとYとが接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とが、本明細書等に開示されているものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に記載されているものとする。

【0032】

ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、

10

20

30

40

50

層、など)であるとする。

【0033】

XとYとが直接的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子(例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など)が、XとYとの間に接続されていない場合であり、XとYとの電気的な接続を可能とする素子(例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など)を介さずに、XとYとが、接続されている場合である。

【0034】

XとYとが電気的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子(例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など)が、XとYとの間に1個以上接続されることが可能である。なお、スイッチは、オンオフが制御される機能を有している。つまり、スイッチは、導通状態(オン状態)、または、非導通状態(オフ状態)になり、電流を流すか流さないかを制御する機能を有している。または、スイッチは、電流を流す経路を選択して切り替える機能を有している。なお、XとYとが電気的に接続されている場合は、XとYとが直接的に接続されている場合を含むものとする。

10

【0035】

XとYとが機能的に接続されている場合の一例としては、XとYとの機能的な接続を可能とする回路(例えば、論理回路(インバータ、NAND回路、NOR回路など)、信号変換回路(DA変換回路、AD変換回路、ガンマ補正回路など)、電位レベル変換回路(電源回路(昇圧回路、降圧回路など)、信号の電位レベルを変えるレベルシフタ回路など)、電圧源、電流源、切り替え回路、增幅回路(信号振幅または電流量などを大きく出来る回路、オペアンプ、差動增幅回路、ソースフォロワ回路、パッファ回路など)、信号生成回路、記憶回路、制御回路など)が、XとYとの間に1個以上接続されることが可能である。なお、一例として、XとYとの間に別の回路を挟んでいても、Xから出力された信号がYへ伝達される場合は、XとYとは機能的に接続されているものとする。なお、XとYとが機能的に接続されている場合は、XとYとが直接的に接続されている場合と、XとYとが電気的に接続されている場合とを含むものとする。

20

【0036】

また、本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。そして、ドレイン(ドレイン端子、ドレン領域またはドレン電極)とソース(ソース端子、ソース領域またはソース電極)の間にチャネル形成領域を有しており、チャネル形成領域を介して、ソースとドレインの間に電流を流すことができるものである。なお、本明細書等において、チャネル形成領域とは、電流が主として流れる領域をいう。

30

【0037】

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができる場合がある。

40

【0038】

なお、チャネル長とは、例えば、トランジスタの上面図において、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソース(ソース領域またはソース電極)とドレイン(ドレン領域またはドレン電極)との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

50

## 【0039】

チャネル幅とは、例えば、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

## 【0040】

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅（以下、「実効的なチャネル幅」ともいう。）と、トランジスタの上面図において示されるチャネル幅（以下、「見かけ上のチャネル幅」ともいう。）と、が異なる場合がある。例えば、ゲート電極が半導体の側面を覆う場合、実効的なチャネル幅が、見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつゲート電極が半導体の側面を覆うトランジスタでは、半導体の側面に形成されるチャネル形成領域の割合が大きくなる場合がある。その場合は、見かけ上のチャネル幅よりも、実効的なチャネル幅の方が大きくなる。

10

## 【0041】

このような場合、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

20

## 【0042】

そこで、本明細書では、見かけ上のチャネル幅を、「囲い込みチャネル幅（S C W : S u r r o u n d e d C h a n n e l W i d t h ）」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面T E M像などを解析することなどによって、値を決定することができる。

30

## 【0043】

なお、半導体の不純物とは、例えば、半導体を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物と言える。不純物が含まれることにより、例えば、半導体のD O S ( D e n s i t y o f S t a t e s ) が高くなることや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第13族元素、第14族元素、第15族元素、および酸化物半導体の主成分以外の遷移金属などがあり、例えば、水素、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。酸化物半導体の場合、水も不純物として機能する場合がある。また、酸化物半導体の場合、例えば不純物の混入によって酸素欠損を形成する場合がある。また、半導体がシリコンである場合、半導体の特性を変化させる不純物としては、例えば、酸素、水素を除く第1族元素、第2族元素、第13族元素、第15族元素などがある。

40

## 【0044】

なお、本明細書等において、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものである。例えば、好ましくは酸素が55原子%以上65原子%以下、窒素が1原子%以上20原子%以下、シリコンが25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の濃度範囲で含まれるものと定義する。また、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものである。例えば、好ましくは窒素が55原子%以上65原子%以下、酸素が1原子%以上20原子%以下、シリコンが25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の濃度

50

範囲で含まれるものという。

【0045】

また、本明細書等において、「膜」という用語と、「層」という用語とは、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

【0046】

また、本明細書等において、「絶縁体」という用語を、絶縁膜または絶縁層と言い換えることができる。また、「導電体」という用語を、導電膜または導電層と言い換えることができる。また、「半導体」という用語を、半導体膜または半導体層と言い換えることができる。

10

【0047】

また、本明細書等に示すトランジスタは、明示されている場合を除き、電界効果トランジスタとする。また、本明細書等に示すトランジスタは、明示されている場合を除き、nチャネル型のトランジスタとする。よって、そのしきい値電圧（「 $V_{th}$ 」ともいう。）は、明示されている場合を除き、0Vよりも大きいものとする。

【0048】

また、本明細書等において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「略平行」とは、二つの直線が-30°以上30°以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。また、「略垂直」とは、二つの直線が60°以上120°以下の角度で配置されている状態をいう。

20

【0049】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

【0050】

なお、本明細書において、バリア膜とは、水素などの不純物および酸素の透過を抑制する機能を有する膜のことであり、該バリア膜に導電性を有する場合は、導電性バリア膜と呼ぶことがある。

30

【0051】

本明細書等において、金属酸化物（metal oxide）とは、広い表現での金属の酸化物である。金属酸化物は、酸化物絶縁体、酸化物導電体（透明酸化物導電体を含む）、酸化物半導体（oxide Semiconductorまたは単にOSともいう）などに分類される。例えば、トランジスタの活性層に金属酸化物を用いた場合、当該金属酸化物を酸化物半導体と呼称する場合がある。つまり、OS FETと記載する場合においては、酸化物または酸化物半導体を有するトランジスタと換言することができる。

【0052】

（実施の形態1）

<半導体装置の構成例>

40

以下では、本発明の一態様に係るトランジスタ400および容量素子100を有する半導体装置の一例について説明する。

【0053】

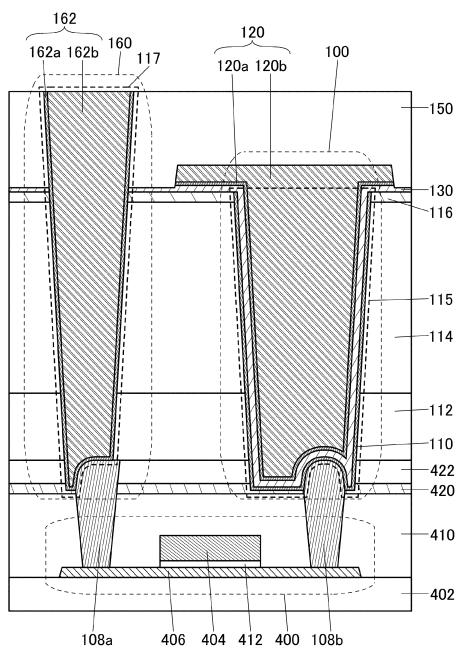

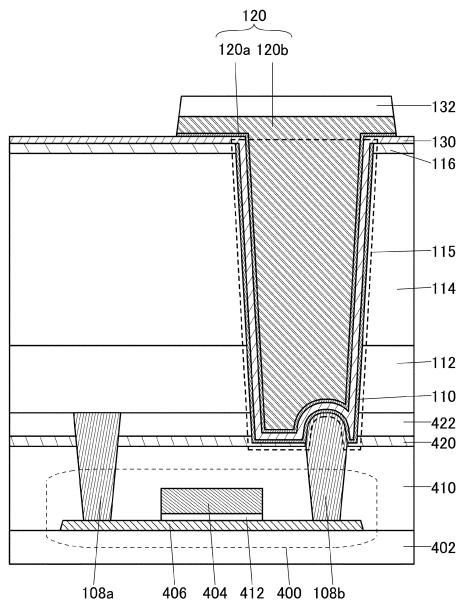

図1は、トランジスタ400および容量素子100を有する半導体装置の断面図である。容量素子100は、水または水素などの不純物の透過を抑制する機能を有する絶縁体420を間に挟んで、トランジスタ400の上に配置される。容量素子100とトランジスタ400は、絶縁体420を貫通して配置される導電体108bによって電気的に接続される。このように、絶縁体420および導電体108bは、容量素子100とトランジスタ400の間に配置されるので、トランジスタ400が絶縁体420および導電体108bを有しているともいえるし、容量素子100が絶縁体420および導電体108bを有

50

しているということもできる。

【0054】

トランジスタ400は、酸化物406を有しており、酸化物406の少なくとも一部はトランジスタ400のチャネル形成領域として機能する。酸化物406は、基板(図示せず。)の上に設けられた絶縁体402の上に配置されることが好ましい。また、トランジスタ400は、酸化物406の上に導電体404を有し、酸化物406と導電体404の間に絶縁体412を有する。ここで、導電体404はトランジスタ400のゲートとして機能し、絶縁体412は導電体404に対応するゲート絶縁体として機能する。例えば、酸化物406の導電体404と重なる領域がトランジスタ400のチャネル形成領域として機能し、酸化物406の導電体404と重ならない領域の一部がトランジスタ400のソース領域およびドレイン領域の一方として機能し、酸化物406の導電体404と重ならない領域の他の一部がトランジスタ400のソース領域およびドレイン領域の他方として機能する。

【0055】

酸化物406のソース領域およびドレイン領域の一方として機能する領域と電気的に接続されるように導電体108aが配置され、酸化物406のソース領域およびドレイン領域の他方として機能する領域と電気的に接続されるように導電体108bが配置される。よって、導電体108aは、トランジスタ400のソース電極およびドレイン電極の一方として機能し、導電体108bは、トランジスタ400のソース電極およびドレイン電極の他方として機能する、ということができる。また、酸化物406、絶縁体412および導電体404を覆って絶縁体410が配置されることが好ましい。導電体108aおよび導電体108bは絶縁体410に形成された開口を埋め込むように形成されることが好ましい。

【0056】

トランジスタ400の酸化物406のチャネル形成領域において、酸素欠損を低減し、水素または水などの不純物を低減することで、トランジスタ400に良好な電気特性を与え、信頼性を向上させることができる。なお、トランジスタ400の構成の詳細な例については、後述する。

【0057】

<容量素子の構成例>

容量素子100は、酸化物406、絶縁体412、導電体404、および絶縁体410の上に配置される。絶縁体422、絶縁体112、絶縁体114、および絶縁体116に形成された開口115の内壁、絶縁体420、および導電体108bに接して配置された導電体110と、導電体110の上に配置された絶縁体130と、絶縁体130の上に配置された導電体120aおよび導電体120bを有する。なお、以下において、導電体120aおよび導電体120bをまとめて導電体120という場合がある。

【0058】

ここで、導電体110は容量素子100の下部電極として機能し、導電体120は容量素子100の上部電極として機能し、絶縁体130は、容量素子100の誘電体として機能する。容量素子100は、開口115において、底面だけでなく、側面においても上部電極と下部電極とが誘電体を挟んで対向する構成となっており、単位面積当たりの静電容量を大きくすることができる。そして、開口115の深さを深くするほど、容量素子100の静電容量を大きくすることができる。このように容量素子100の単位面積当たりの静電容量を大きくすることにより、半導体装置の微細化または高集積化を推し進めることができる。

【0059】

絶縁体420は、上層、例えば容量素子100などから水または水素などの不純物がトランジスタ400などに混入するのを防ぐバリア絶縁膜として機能できる。絶縁体420は、水または水素などの不純物の透過を抑制する機能を有する絶縁性材料を用いることが好ましく、例えば、酸化アルミニウムなどを用いることが好ましい。これにより、水素、

水などの不純物が絶縁体420より下層に拡散するのを抑制することができる。なお、絶縁体420は、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子( $N_2O$ 、 $NO$ 、 $NO_2$ など)、銅原子などの不純物の少なくとも一の透過を抑制する機能を有することが好ましい。また、以下において、不純物の透過を抑制する機能を有する絶縁性材料について記載する場合も同様である。例えば、絶縁体420は、絶縁体422、絶縁体112、および絶縁体114のいずれかより、水、または水素の透過を抑制する機能が高いことが好ましい。

#### 【0060】

ここで、絶縁体420は、スパッタリング法を用いて成膜された酸化物絶縁体を用いることが好ましく、例えば酸化アルミニウムを用いることが好ましい。このような絶縁体420を用いることにより、絶縁体410の絶縁体420と接する面を介して絶縁体410に酸素を供給し、絶縁体410を酸素過剰な状態にできる。これにより、絶縁体410を介して絶縁体412および酸化物406に酸素を供給することができる。

10

#### 【0061】

さらに、絶縁体420は、酸素(例えば、酸素原子または酸素分子など)の透過を抑制する機能を有する絶縁性材料、例えば酸化アルミニウムを用いることが好ましい。これにより、絶縁体410、酸化物406などに含まれる酸素が上方拡散するのを抑制することができる。これにより、酸化物406に効果的に酸素を供給することができる。

#### 【0062】

このように絶縁体420を設け、トランジスタ400の酸化物406のチャネル形成領域において、酸素欠損を低減し、水素または水などの不純物を低減することで、トランジスタ400に良好な電気特性を与え、信頼性を向上させることができる。

20

#### 【0063】

また、絶縁体420は、絶縁体422、絶縁体112、および絶縁体114に開口115を形成する際に、エッチングストップとして機能することが好ましい。よって、絶縁体420は、絶縁体422、絶縁体112、および絶縁体114の少なくともいずれかと、構成元素、組成などが異なることが好ましく、例えば、酸化アルミニウムを用いることが好ましい。このように、絶縁体420がエッチングストップとして機能することにより、容量素子100が絶縁体410に接して形成され、容量素子100の絶縁体410に接した部分から、容量素子100に含まれる不純物が絶縁体410を介してトランジスタ400に拡散することを防ぐことができる。

30

#### 【0064】

このとき、絶縁体420および導電体108bは、開口115の底部となる。言い換えると、開口115は、絶縁体420および導電体108bに達する開口ということができる。また、図1に示すように、絶縁体420の開口115と重なる領域、言い換えると、絶縁体420の導電体110と接する領域の膜厚は、絶縁体420の当該領域以外の膜厚より薄くなる場合がある。つまり、絶縁体420の当該領域は凹んだ形状になる場合がある。

#### 【0065】

なお、絶縁体420に積層して、絶縁体420と同様の元素を有する絶縁体を、ALD法を用いて成膜してもよい。このように、絶縁体420にALD法で成膜された絶縁体を積層することにより、段切れ、クラック、ピンホールなどが形成されることなく、トランジスタ400を覆うことができる。これにより、水素、水などの不純物に対する絶縁体420のバリア性をより顕著に向上させることができる。

40

#### 【0066】

絶縁体420の上に絶縁体422が配置されることが好ましい。絶縁体422としては、例えば酸化窒化シリコンなどを用いればよい。導電体108aおよび導電体108bは、絶縁体410、絶縁体420、および絶縁体422に形成された開口に埋め込まれるよう形成すればよい。このため、導電体108aまたは導電体108bの上面の一部と、絶縁体422の上面の高さが略一致する場合がある。

50

## 【0067】

ここで、絶縁体422を設けておくことで、導電体108aおよび導電体108bを形成するための研磨処理（例えば、化学的機械研磨（Chemical Mechanical Polishing: CMP）処理など）を容易に行うことができる。なお、絶縁体422は、導電体108aおよび導電体108bを形成できるならば、必ずしも設ける必要はない。

## 【0068】

絶縁体410および絶縁体420に設けられる開口、および当該開口に埋め込まれる導電体108bの断面形状は、絶縁体420の、導電体110と接する領域の上面より下の部分において、逆テーパー形状となる場合がある。つまり、当該部分において、導電体108bは、側面のテーパー角度が90°以上である場合がある。また、当該部分において、導電体108bは、底面と側面のなす角が90°以上である場合があるということもできる。なお、当該部分において、導電体108bの側面が絶縁体402の上面に対して略垂直であってもよい。

10

## 【0069】

また、導電体108bは、絶縁体420の、導電体110と接する領域の上面より上の部分において、湾曲面を有することが好ましい。例えば、導電体108bの当該部分において、導電体108bの側面と、導電体108bの上面との間に、湾曲面を有することが好ましい。つまり、導電体108bの当該部分において、側面の端部と上面の端部は、湾曲して連続していることが好ましい。

20

## 【0070】

このように、導電体108bは、絶縁体420より上の部分と、下の部分で形状が異なることが好ましい。特に、導電体108bの上の部分の湾曲面で導電体110と接することにより、導電体108bと導電体110の接触抵抗を低減することができる。これにより、トランジスタ400のソースまたはドレインのいずれかと、容量素子100の下部電極との電気的接続を良好にできる。よって、容量素子100とトランジスタ400を有する半導体装置に良好な電気特性を与えることができる。

30

## 【0071】

絶縁体422の上に絶縁体112が配置され、絶縁体112の上に絶縁体114が配置される。上記の通り、開口115の深さ、すなわち絶縁体112と絶縁体114の膜厚の合計を大きくすることにより、容量素子100の静電容量を大きくすることができます。しかしながら、絶縁体112と絶縁体114の膜厚を大きくすることにより、これらの絶縁体の内部応力も大きくなり、基板の反りなどが発生する場合がある。そこで、本実施の形態に示す容量素子100においては、絶縁体112および絶縁体114の一方は圧縮応力を有し、絶縁体112および絶縁体114の他方は引っ張り応力を有することが好ましい。つまり、絶縁体112および絶縁体114は、積層することで互いの内部応力を相殺し、積層された絶縁体全体の内部応力を低減することが好ましい。

## 【0072】

絶縁体112および絶縁体114は、同種の元素を用いる構成としてもよく、例えば、有機シランガス（例えば、TEOS（Tetra-Ethyl-Ortho-Silicic acid）など）を用いて成膜した酸化シリコンを用いればよい。この場合、絶縁体112の組成と絶縁体114の組成を異なるものとし、互いの内部応力の向きを異ならせることができが好ましい。例えば、絶縁体112と絶縁体114を同じ種類の有機シランガス（例えば、TEOSなど）を用いて、異なる種類の化学気相成長（CVD: Chemical Vapour Deposition）法を用いて成膜してもよい。

40

## 【0073】

なお、基板の反りが発生しない程度に、内部応力が低減されているなら、絶縁体112および絶縁体114のいずれか一方のみの構成にしてもよい。

## 【0074】

絶縁体114の上に絶縁体116が配置されることが好ましい。絶縁体116は、開口

50

115内でエッティングを行うときに、導電体110とともにエッティングストップとして機能することが好ましい。よって、絶縁体116は、絶縁体114と構成元素、組成などが異なることが好ましく、例えば、絶縁体116として、窒化シリコンを用いることができる。また、絶縁体116の上面と導電体110の最上面（導電体110の開口115の縁に接する部分と言い換えてよい。）が略一致することが好ましい。絶縁体116と導電体110によって、絶縁体114、絶縁体112、絶縁体422、および絶縁体420が覆われていることが好ましい。なお、絶縁体116は、必ずしも設ける必要はない。

#### 【0075】

絶縁体422、絶縁体112、絶縁体114、および絶縁体116に開口115が形成されている。ここで、絶縁体422の側面、絶縁体112の側面、絶縁体114の側面、および絶縁体116の側面は、開口115の内壁といいうことができる。また、導電体108bの上部、および絶縁体420の開口115と重なる部分は開口115の底部といいうことができる。

10

#### 【0076】

図1に示すように、開口115の断面形状は深い位置ほど、内径が小さくなる形状にすることができる。また、開口115の内壁が絶縁体402の上面に対して略垂直な断面形状にしてもよい。また、開口115を上面から見た形状は、四角形としてもよいし、四角形以外の多角形状としてもよいし、多角形状において角部を湾曲させた形状としてもよいし、橢円を含む円形状としてもよい。ここで、開口115とトランジスタ400の重なる面積が多い方が好ましい。このような構成にすることにより、容量素子100とトランジスタ400を有する半導体装置の占有面積を増やすことなく、静電容量を大きくすることができます。

20

#### 【0077】

開口115の内壁および底面に接して、導電体110が配置される。導電体110は容量素子100の下部電極として機能し、例えば窒化チタンなどを用いることができる。例えば、ALD法またはCVD法などを用いて導電体110となる導電膜を成膜することにより、開口115のアスペクト比が大きくても被覆性良く導電体110を形成することができる。ここで、上記のように導電体108bの上部が湾曲面を有し、当該湾曲面に接して導電体110が形成されることにより、導電体110と導電体108bの接触抵抗を低減することができる。

30

#### 【0078】

導電体110および絶縁体116を覆って絶縁体130が配置される。絶縁体130は容量素子100の誘電体として機能し、例えば、酸化ハフニウム、ハフニウムシリケート（ $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ )）、窒素が添加されたハフニウムシリケート（ $HfSi_xO_yN_z$  ( $x > 0$ ,  $y > 0$ ,  $z > 0$ )）、窒素が添加されたハフニウムアルミニート（ $HfAl_xO_yN_z$  ( $x > 0$ ,  $y > 0$ ,  $z > 0$ )）、または酸化イットリウムなどのhig h-k材料を用いることが好ましい。このようなhig h-k材料を用いることで、絶縁体130を厚くしても容量素子100の静電容量を十分確保することができる。絶縁体130を厚くすることにより、導電体110と導電体120の間に生じるリーク電流を抑制することができる。

40

#### 【0079】

また、例えば、ALD法またはCVD法などを用いて絶縁体130となる絶縁膜を成膜することにより、開口115のアスペクト比が大きくても被覆性良く絶縁体130を形成することができる。また、絶縁体130は、導電体120と重なる領域の膜厚が、該領域以外の膜厚より厚い場合がある。

#### 【0080】

また、導電体110の最上面が絶縁体116の上面と略一致する、言い換えると導電体110が開口115からはみ出さないことで、絶縁体130でより確実に導電体110を覆うことができるので、導電体110と導電体120が短絡することを抑制することができる。

50

## 【0081】

開口115を覆って、絶縁体130の上に導電体120が配置される。図1に示すように、導電体120は、導電体120aと、導電体120aの上に配置された導電体120bの積層膜にすることが好ましい。導電体120は容量素子100の上部電極として機能し、例えば導電体120aとして窒化チタンなどを、導電体120bとしてタンゲステンなどを用いることができる。例えば、ALD法またはCVD法などを用いて導電体120aとなる導電膜、および導電体120bとなる導電膜を成膜することにより、開口115のアスペクト比が大きくて被覆性良く導電体120aおよび導電体120bを形成することができる。

## 【0082】

また、導電体120は、開口115からはみ出して絶縁体116と重なる領域を有することが好ましい。当該領域を有するには、フォトリソグラフィ法などを用いて導電体120aおよび導電体120bを形成すればよい。このとき、導電体120bの絶縁体116と重なる領域の上面の平均面粗さ( $R_a$ )は、4nm以下、好ましくは2nm以下、より好ましくは1nm以下とすればよい。このように、導電体120bの上面が、開口115の縁の近傍と重なる領域において、良好な平坦性を有していることで、フォトリソグラフィの露光工程において、当該領域で乱反射が起こることを抑制できる。特に、露光に電子ビームを用いる場合、金属膜の上面の凹凸による乱反射の影響がより顕著になるので、これを防ぐため、当該領域の平坦性を向上させることが好ましい。このように、当該領域の平坦性を向上させることで、フォトリソグラフィをより精密に行うことができる。

10

## 【0083】

なお、本明細書等において、平均面粗さ( $R_a$ )とは、JIS B 0601:2001(ISO 4287:1997)で定義されている算術平均粗さを、曲面に対して適用できるよう三次元に拡張したものであり、基準面から指定面までの偏差の絶対値を平均した値で表現される。

## 【0084】

平均面粗さ( $R_a$ )は、指定面を $Z = F(X, Y)$ で表すとき、基準面から指定面までの偏差の絶対値を平均した値で表現され、次の式で与えられる。

## 【0085】

## 【数1】

30

$$R_a = \frac{1}{S_0} \int_{Y_1}^{Y_2} \int_{X_1}^{X_2} |F(X, Y) - Z_0| dX dY$$

## 【0086】

ここで、指定面とは、粗さ計測の対象となる面であり、座標( $X_1, Y_1, F(X_1, Y_1)$ ), ( $X_1, Y_2, F(X_1, Y_2)$ ), ( $X_2, Y_1, F(X_2, Y_1)$ ), ( $X_2, Y_2, F(X_2, Y_2)$ )の4点で表される四角形の領域とする。

## 【0087】

また、指定面をXY平面に投影した長方形の面積を $S_0$ 、基準面の高さ(指定面の平均の高さ)を $Z_0$ とする。平均面粗さ( $R_a$ )は原子間力顕微鏡(AFM: Atomic Force Microscope)にて測定可能である。

40

## 【0088】

なお、導電体120は、必ずしも積層膜にしなくてもよく、例えば、導電体120aおよび導電体120bのいずれか一方を用いる構成にしてもよい。

## 【0089】

導電体120および絶縁体130を覆って絶縁体150が配置されることが好ましい。絶縁体150は、絶縁体410に用いることができる絶縁体を用いればよい。

## 【0090】

また、上記において、導電体108b上に形成される容量素子100の構成について説

50

明したが、導電体 108a 上にも接続部 160 が形成されることが好ましい。接続部 160 が設けられることで、トランジスタ 400 の導電体 108a と、各種回路素子または配線などと、を容易に接続させることができる。

【0091】

接続部 160 は、絶縁体 422、絶縁体 112、絶縁体 114、絶縁体 116、絶縁体 130、および絶縁体 150 に形成された開口 117 に埋め込まれるように形成される。接続部 160 は、開口 117 の内壁、絶縁体 420、および導電体 108a に接して配置された導電体 162a と、導電体 162a の内側に形成された導電体 162b と、を有する。なお、以下において、導電体 162a および導電体 162b をまとめて導電体 162 という場合がある。

10

【0092】

ここで、絶縁体 420 および導電体 108a は、開口 117 の底部となる。言い換えると、開口 117 は、絶縁体 420 および導電体 108a に達する開口ということができる。また、図 1 に示すように、絶縁体 420 の開口 117 と重なる領域、言い換えると、絶縁体 420 の導電体 162a と接する領域の膜厚は、絶縁体 420 の当該領域以外の膜厚より薄くなる場合がある。つまり、絶縁体 420 の当該領域は凹んだ形状になる場合がある。

【0093】

導電体 108a は導電体 108b と同様の構成を有する。よって、絶縁体 410 および絶縁体 420 に設けられる開口、および当該開口に埋め込まれる導電体 108a の断面形状は、絶縁体 420 の、導電体 162a と接する領域の上面より下の部分において、逆テーパー形状となる場合がある。つまり、当該部分において、導電体 108a の側面のテーパー角度が 90° 以上である場合がある。また、当該部分において、導電体 108a の側面と絶縁体 402 の上面とのなす角が 90° 以上である場合があるといふこともできる。なお、当該部分において、導電体 108a の側面が絶縁体 402 の上面に対して略垂直であってもよい。

20

【0094】

また、導電体 108a は、絶縁体 420 の、導電体 162a と接する領域の上面より上の部分において、湾曲面を有することが好ましい。例えば、導電体 108a の当該部分において、導電体 108a の側面と、導電体 108a の上面との間に、湾曲面を有することが好ましい。つまり、導電体 108a の当該部分において、側面の端部と上面の端部は、湾曲して連続していることが好ましい。なお、図 1 に示すように、導電体 108a の当該部分において、導電体 162a と接しない、言い換えると開口 117 と重ならない領域については、湾曲面が形成されない。

30

【0095】

このように、導電体 108a は、絶縁体 420 より上の部分と、下の部分で形状が異なることが好ましい。特に、導電体 108a の上の部分の湾曲面で導電体 162a と接することにより、導電体 108a と導電体 162a の接触抵抗を低減することができる。これにより、トランジスタ 400 のソースまたはドレインのいずれかと、接続部 160 との電気的接続を良好にすることができます。

40

【0096】

導電体 162 は、導電体 120 と同様の構成を用いることができる。よって、導電体 162a は導電体 120a と、導電体 162b は導電体 120b と同様の構成を用いることが好ましい。なお、導電体 162 は、必ずしも積層膜にしなくてもよく、例えば、導電体 162a および導電体 162b のいずれか一方を用いる構成にしてもよい。

【0097】

次に、トランジスタ 400、容量素子 100 および接続部 160 などの構成材料について説明する。

【0098】

[ 基板 ]

50

容量素子 100 およびトランジスタ 400 を有する半導体装置を形成する基板としては、例えば、絶縁体基板、半導体基板または導電体基板を用いればよい。絶縁体基板としては、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板（イットリア安定化ジルコニア基板など）、樹脂基板などがある。また、半導体基板としては、例えば、シリコン、ゲルマニウムなどの半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムからなる化合物半導体基板などがある。さらには、前述の半導体基板内部に絶縁体領域を有する半導体基板、例えば SOI (Silicon On Insulator) 基板などがある。導電体基板としては、黒鉛基板、金属基板、合金基板、導電性樹脂基板などがある。または、金属の窒化物を有する基板、金属の酸化物を有する基板などがある。さらには、絶縁体基板に導電体または半導体が設けられた基板、半導体基板に導電体または絶縁体が設けられた基板、導電体基板に半導体または絶縁体が設けられた基板などがある。または、これらの基板に素子が設けられたものを用いてもよい。基板に設けられる素子としては、容量素子、抵抗素子、スイッチ素子、発光素子、記憶素子などがある。

#### 【0099】

また、基板として、可とう性基板を用いてもよい。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。なお、基板として、繊維を編みこんだシート、フィルムまたは箔などを用いてもよい。また、基板が伸縮性を有してもよい。また、基板は、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有してもよい。または、元の形状に戻らない性質を有してもよい。基板は、例えば、5 μm 以上 700 μm 以下、好ましくは 10 μm 以上 500 μm 以下、さらに好ましくは 15 μm 以上 300 μm 以下の厚さとなる領域を有する。基板を薄くすると、トランジスタを有する半導体装置を軽量化することができる。また、基板を薄くすることで、ガラスなどを用いた場合にも伸縮性を有する場合や、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有する場合がある。そのため、落下などによって基板上の半導体装置に加わる衝撃などを緩和することができる。即ち、丈夫な半導体装置を提供することができる。

#### 【0100】

可とう性基板である基板としては、例えば、金属、合金、樹脂もしくはガラス、またはそれらの繊維などを用いることができる。可とう性基板である基板は、線膨張率が低いほど環境による変形が抑制されて好ましい。可とう性基板である基板としては、例えば、線膨張率が  $1 \times 10^{-3} / K$  以下、 $5 \times 10^{-5} / K$  以下、または  $1 \times 10^{-5} / K$  以下である材質を用いればよい。樹脂としては、例えば、ポリエステル、ポリオレフィン、ポリアミド（ナイロン、アラミドなど）、ポリイミド、ポリカーボネート、アクリルなどがある。特に、アラミドは、線膨張率が低いため、可とう性基板である基板として好適である。

#### 【0101】

##### 〔絶縁体〕

絶縁体としては、絶縁性を有する酸化物、窒化物、酸化窒化物、窒化酸化物、金属酸化物、金属酸化窒化物、金属窒化酸化物などがある。

#### 【0102】

トランジスタを、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体で囲うことによって、トランジスタの電気特性を安定にすることができる。例えば、絶縁体 420 として、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体を用いればよい。

#### 【0103】

水素などの不純物および酸素の透過を抑制する機能を有する絶縁体としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオ

ジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。

【0104】

例えば、絶縁体420としては、酸化アルミニウム、酸化ハフニウム、酸化マグネシウム、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジムまたは酸化タンタルなどの金属酸化物、窒化酸化シリコンまたは窒化シリコンなどを用いればよい。

【0105】

絶縁体402、絶縁体412、絶縁体410、絶縁体422、絶縁体112、絶縁体114、絶縁体116および絶縁体150としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、絶縁体402、絶縁体412、絶縁体410、絶縁体422、絶縁体112、絶縁体114、絶縁体116および絶縁体150としては、酸化シリコン、酸化窒化シリコン、窒化酸化シリコンまたは、窒化シリコンを有することが好ましい。

10

【0106】

絶縁体412および絶縁体130は、比誘電率の高い絶縁体を有することが好ましい。例えば、絶縁体412および絶縁体130は、酸化ガリウム、酸化ハフニウム、酸化ジルコニウム、アルミニウムおよびハフニウムを有する酸化物、アルミニウムおよびハフニウムを有する酸化窒化物、シリコンおよびハフニウムを有する酸化物、シリコンおよびハフニウムを有する酸化窒化物またはシリコンおよびハフニウムを有する窒化物などを有することが好ましい。または、絶縁体412および絶縁体130は、酸化シリコンまたは酸化窒化シリコンと、比誘電率の高い絶縁体と、の積層構造を有することが好ましい。酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため、比誘電率の高い絶縁体と組み合わせることで、熱的に安定かつ比誘電率の高い積層構造とすることができます。例えば、絶縁体412および絶縁体130において、酸化アルミニウム、酸化ガリウムまたは酸化ハフニウムを酸化物406と接する構造とすることで、酸化シリコンまたは酸化窒化シリコンに含まれるシリコンが、酸化物406に混入することを抑制することができる。また、例えば、絶縁体412および絶縁体130において、酸化シリコンまたは酸化窒化シリコンを酸化物406と接する構造とすることで、酸化アルミニウム、酸化ガリウムまたは酸化ハフニウムと、酸化シリコンまたは酸化窒化シリコンと、の界面にトラップセンターが形成される場合がある。該トラップセンターは、電子を捕獲することでトランジスタのしきい値電圧をプラス方向に変動させることができる場合がある。

20

【0107】

絶縁体410、絶縁体422、絶縁体112、絶縁体114、および絶縁体150は、比誘電率の低い絶縁体を有することが好ましい。例えば、絶縁体410、絶縁体422、絶縁体112、絶縁体114、および絶縁体150は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコンまたは樹脂などを有することが好ましい。または、絶縁体410、絶縁体422、絶縁体112、絶縁体114、および絶縁体150は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコンまたは空孔を有する酸化シリコンと、樹脂と、の積層構造を有することが好ましい。酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため、樹脂と組み合わせることで、熱的に安定かつ比誘電率の低い積層構造とすることができます。樹脂としては、例えば、ポリエステル、ポリオレフィン、ポリアミド(ナイロン、アラミドなど)、ポリイミド、ポリカーボネートまたはアクリルなどがある。

30

【0108】

[導電体]

導電体404、導電体108a、導電体108b、導電体120b、および導電体16

40

50

2 b としては、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タンクスチール、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニウム、ベリリウム、インジウム、ルテニウムなどから選ばれた金属元素を1種以上含む材料を用いることができる。また、リン等の不純物元素を含有させた多結晶シリコンに代表される、電気伝導度が高い半導体、ニッケルシリサイドなどのシリサイドを用いてもよい。

#### 【0109】

また、上記導電体、特に導電体110、導電体120a、および導電体162aとして、酸化物406に適用可能な金属酸化物に含まれる金属元素および酸素を含む導電性材料を用いてもよい。また、前述した金属元素および窒素を含む導電性材料を用いてもよい。例えば、窒化チタン、窒化タンタルなどの窒素を含む導電性材料を用いてもよい。また、インジウム錫酸化物、酸化タンクスチールを含むインジウム酸化物、酸化タンクスチールを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、シリコンを添加したインジウム錫酸化物を用いてもよい。また、窒素を含むインジウムガリウム亜鉛酸化物を用いてもよい。このような材料を用いることで、酸化物406に含まれる水素を捕獲することができる場合がある。または、外方の絶縁体などから混入する水素を捕獲することができる場合がある。

10

#### 【0110】

また、上記の材料で形成される導電層を複数積層して用いてもよい。例えば、前述した金属元素を含む材料と、酸素を含む導電性材料と、を組み合わせた積層構造としてもよい。また、前述した金属元素を含む材料と、窒素を含む導電性材料と、を組み合わせた積層構造としてもよい。また、前述した金属元素を含む材料と、酸素を含む導電性材料と、窒素を含む導電性材料と、を組み合わせた積層構造としてもよい。

20

#### 【0111】

##### <容量素子の作製方法>

次に、本発明に係るトランジスタ400および容量素子100を有する半導体装置の作製方法を、図2から図16を用いて説明する。

#### 【0112】

半導体装置の作製方法は、酸化物406を有するトランジスタ400上に絶縁体420を形成する工程と、絶縁体420の上に絶縁体422を形成する工程と、絶縁体420および絶縁体422に、トランジスタ400のソースおよびドレインの一方に達する第1の開口と、トランジスタ400のソースおよびドレインの他方に達する第2の開口を形成する工程と、第1の開口に導電体108aを埋め込み、第2の開口に導電体108bを埋め込む工程と、絶縁体422、導電体108b、および導電体108aの上に絶縁体112、絶縁体114などを形成する工程と、ドライエッチング処理を行い、絶縁体420および導電体108bに達する開口115を形成する工程と、開口115の内壁、絶縁体420、および導電体108bに接して、導電体110を形成する工程と、導電体110の上に絶縁体130を形成する工程と、絶縁体130の上に導電体120を形成する工程と、を有する。

30

#### 【0113】

以下では、主に、トランジスタ400の上に容量素子100を作製する方法の詳細について説明する。なお、トランジスタ400の作製方法例、つまり、絶縁体422を形成し、導電体108aおよび導電体108bを開口に埋め込むまでの工程については、後述する。

40

#### 【0114】

以下、本実施の形態に係る半導体装置などに用いる、導電体（導電体膜、導電体層など）ということもできる。）、絶縁体（絶縁体膜、絶縁体層など）ということもできる。）、半導体（半導体膜、半導体層など）ということもできる。）、酸化物（酸化膜、酸化層など）ということもできる。）の成膜は、スパッタリング法、CVD法、分子線エピタキシー（MBE: Molecular Beam Epitaxy）法、パルスレーザ堆積（PLD

50

: P u l s e d L a s e r D e p o s i t i o n ) 法または A L D 法などを用いて行うことができる。

【 0 1 1 5 】

なお、 C V D 法は、 プラズマを利用する プラズマ C V D ( P E C V D : P l a s m a E n h a n c e d C V D ) 法、 熱を利用する 熱 C V D ( T C V D : T h e r m a l C V D ) 法、 光を利用する 光 C V D ( P h o t o C V D ) 法などに分類できる。さらに用いる原料ガスによって 金属 C V D ( M C V D : M e t a l C V D ) 法、 有機金属 C V D ( M O C V D : M e t a l O r g a n i c C V D ) 法に分けることができる。また、 成膜チャンバーの圧力によって、 大気圧下で成膜を行なう 常圧 C V D ( A P C V D : A t m o s p h e r i c P r e s s u r e C V D ) 法、 大気圧より低い 減圧状態で成膜を行う 減圧 C V D ( L P C V D : L o w P r e s s u r e C V D ) 法、 などに分けることができる。

10

【 0 1 1 6 】

プラズマ C V D 法は、 比較的低温で高品質の膜が得られる。また、 熱 C V D 法は、 プラズマを用いないため、 被処理物への プラズマダメージを小さくすることが可能な成膜方法である。 例えば、 半導体装置に含まれる 配線、 電極、 素子 ( トランジスタ、 容量素子など ) などは、 プラズマから電荷を受け取ることで チャージアップする場合がある。 このとき、 蓄積した電荷によって、 半導体装置に含まれる 配線、 電極、 素子などが 破壊される場合がある。 一方、 プラズマを用いない 熱 C V D 法の場合、 こういった プラズマダメージが生じないため、 半導体装置の歩留まりを高くすることができる。 また、 熱 C V D 法では、 成膜中の プラズマダメージが生じないため、 欠陥の少ない膜が得られる。

20

【 0 1 1 7 】

また、 A L D 法も、 被処理物への プラズマダメージを小さくすることが可能な成膜方法である。 また、 A L D 法も、 成膜中の プラズマダメージが生じないため、 欠陥の少ない膜が得られる。

【 0 1 1 8 】

C V D 法および A L D 法は、 ターゲットなどから放出される粒子が 堆積する 成膜方法とは異なり、 被処理物の表面における 反応により 膜が形成される 成膜方法である。 したがって、 被処理物の 形状の影響を受けにくく、 良好な 段差被覆性を有する 成膜方法である。 特に、 A L D 法は、 優れた 段差被覆性と、 優れた 厚さの 均一性を有するため、 アスペクト比の高い 開口の表面を被覆する場合などに 好適である。 ただし、 A L D 法は、 比較的 成膜速度が遅いため、 成膜速度の速い C V D 法などの他の成膜方法と組み合わせて用いることが 好ましい場合もある。

30

【 0 1 1 9 】

C V D 法および A L D 法は、 原料ガスの 流量比によって、 得られる膜の組成を 制御することができる。 例えば、 C V D 法および A L D 法では、 原料ガスの 流量比によって、 任意の組成の膜を 成膜することができる。 また、 例えば、 C V D 法および A L D 法では、 成膜しながら 原料ガスの 流量比を 变化させることによって、 組成が 連続的に 变化した膜を 成膜することができる。 原料ガスの 流量比を 变化させながら 成膜する場合、 複数の 成膜室を 用いて 成膜する場合と 比べて、 搬送や 圧力調整に 掛かる時間の分、 成膜に 掛かる時間を 短くすることができる。 したがって、 半導体装置の 生産性を 高めることができる場合がある。

40

【 0 1 2 0 】

また、 スパッタリング法としては、 スパッタ用電源に 直流電源を用いる D C ( D i r e c t C u r r e n t ) スパッタリング法、 さらに パルス的に バイアスを 与える パルス D C スパッタ法、 スパッタ用電源に 高周波電源を用いる R F ( R a d i o F r e q u e n c y ) スパッタリング法を 用いて もよい。 また、 チャンバー内部に 磁石機構を 備えた マグネットロンスパッタリング法、 成膜中に 基板にも 電圧を かける バイアススパッタリング法、 反応性ガス 霧 囲気で 行う 反応性スパッタリング法などを 用いて もよい。 また、 平行平板型スパッタリング装置を 用いた 成膜法である、 P E S P ( p a r a l l e l e l l e c t r o d e s p u t t e r i n g ) 、 又は 対向ターゲット式スパッタリング装置を 用いた 成

50

膜法である、V D S P (v a p o r d e p o s i t i o n s p u t t e r i n g) を用いてもよい。

【 0 1 2 1 】

また、上記の方法で成膜された膜の加工は、リソグラフィー法などを用いて行えばよい。リソグラフィー法では、まず、マスクを介してレジストを露光する。次に、露光された領域を、現像液を用いて除去または残存させてレジストマスクを形成する。次に、当該レジストマスクを介してエッチング処理することで導電体、半導体または絶縁体などを所望の形状に加工することができる。例えば、K r F エキシマレーザ光、A r F エキシマレーザ光、E U V (E x t r e m e U l t r a v i o l e t) 光などを用いて、レジストを露光することでレジストマスクを形成すればよい。また、基板と投影レンズとの間に液体(例えば水)を満たして露光する、液浸技術を用いてもよい。また、前述した光に代えて、電子ビームやイオンビームを用いてもよい。なお、電子ビームやイオンビームを用いる場合には、マスクは不要となる。なお、レジストマスクの除去には、アッシングなどのドライエッチング処理を行う、ウェットエッチング処理を行う、ドライエッチング処理後にウェットエッチング処理を行う、またはウェットエッチング処理後にドライエッチング処理を行うことができる。

【 0 1 2 2 】

また、レジストマスクの代わりに絶縁体や導電体からなるハードマスクを用いてもよい。ハードマスクを用いる場合、加工される膜(以下、被加工膜という。)の上にハードマスク材料となる絶縁膜や導電膜を形成し、その上にレジストマスクを形成し、ハードマスク材料をエッチングすることで所望の形状のハードマスクを形成することができる。被加工膜のエッチングは、レジストマスクを除去してから行っても良いし、レジストマスクを残したまま行っても良い。後者の場合、エッチング中にレジストマスクが消失することができる。上記被加工膜のエッチング後にハードマスクをエッチングにより除去しても良い。一方、ハードマスクの材料が後工程に影響が無い、あるいは後工程で利用できる場合、必ずしもハードマスクを除去する必要は無い。

【 0 1 2 3 】

上記のマスクを形成したのち、被加工膜の加工は、ドライエッチング法やウェットエッチング法を用いることができる。ドライエッチング法による加工は微細加工に適している。

【 0 1 2 4 】

ドライエッチング装置としては、平行平板型電極を有する容量結合型プラズマ(C C P : C a p a c i t i v e l y C o u p l e d P l a s m a)エッチング装置を用いることができる。以下、当該エッチング装置を平行平板型ドライエッチング装置またはC C Pエッチング装置と呼ぶ場合がある。平行平板型電極を有する容量結合型プラズマエッチング装置は、平行平板型電極の一方の電極に高周波電源を印加する構成でもよい。または平行平板型電極の一方の電極に複数の異なる高周波電源を印加する構成でもよい。または平行平板型電極それぞれに同じ周波数の高周波電源を印加する構成でもよい。または平行平板型電極それぞれに周波数の異なる高周波電源を印加する構成でもよい。または高密度プラズマ源を有するドライエッチング装置を用いることができる。高密度プラズマ源を有するドライエッチング装置は、例えば、誘導結合型プラズマ(I C P : I n d u c t i v e l y C o u p l e d P l a s m a)エッチング装置などを用いることができる。

【 0 1 2 5 】

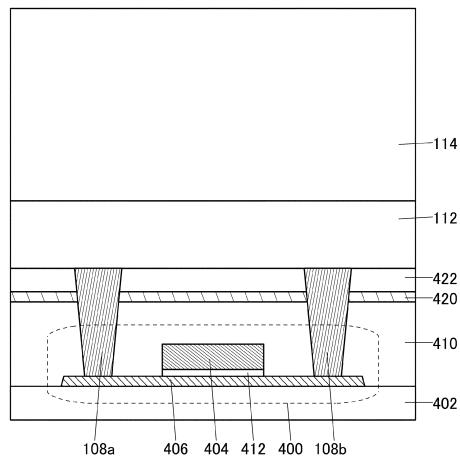

まず、導電体108a、導電体108b、および絶縁体422の上に絶縁体112を成膜し、絶縁体112の上に絶縁体114を成膜する(図2参照。)。絶縁体112および絶縁体114の膜厚を調整することにより、容量素子100の静電容量を選択することができる。容量素子100に求められる静電容量に合わせて絶縁体112および絶縁体114の膜厚を適宜設定すればよい。

【 0 1 2 6 】

上述のように、絶縁体112と絶縁体114は互いの内部応力を相殺するように、一方

10

20

30

40

50

が圧縮応力を有し、他方が引っ張り応力を有することが好ましい。よって、絶縁体112と絶縁体114は、異なる成膜方法を用いることなどで、互いの組成を異なるものにすることが好ましい。

【0127】

本実施の形態では、例えば、絶縁体112として酸化シリコンを、成膜ガスにTEOSを用いたPECVD法によって成膜し、絶縁体114として酸化シリコンを、成膜ガスにTEOSを用いたAPCVD法によって成膜する。

【0128】

このようにして、絶縁体112と絶縁体114の積層膜の内部応力を低減し、基板の反りを低減することにより、後述する開口115を形成する際に、当該工程に用いるマスクの露光をより精密に行うことができる。

10

【0129】

また、絶縁体112は、導電体108aおよび導電体108bの上面に接するので、絶縁体112は絶縁体114より、導電体108aおよび導電体108bを酸化させる能力が低いことが好ましい。

【0130】

なお、本実施の形態では、絶縁体112と絶縁体114の2層構造にしているが、これに限られるものではない。基板の反りが発生しない程度に、内部応力が低減されているなら、絶縁体を3層以上の構造にしてもよいし、絶縁体112および絶縁体114のいずれか一方のみの単層構造としてもよい。

20

【0131】

次に、絶縁体114の上に絶縁体116を成膜する。絶縁体116は、開口115内でエッチングを行うときに、導電体110とともにエッチングストップとして機能することが好ましい。また、絶縁体116は、後の工程でCMP処理を行う際に、当該CMP処理のストッパーとして機能することが好ましい。よって、絶縁体116は、絶縁体114および後述する絶縁体118と構成元素、組成などが異なることが好ましい。例えば、絶縁体114および絶縁体118として酸化窒化シリコンを用いる場合、絶縁体116として窒化シリコンを用いればよい。本実施の形態では、例えば、絶縁体116を、PECVD法を用いて成膜する。なお、絶縁体116は必ずしも設ける必要はない。

【0132】

30

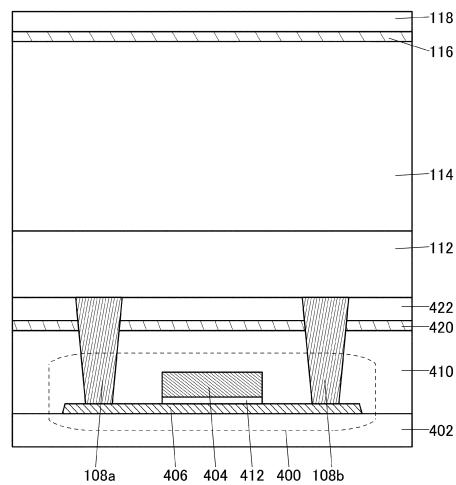

次に、絶縁体116の上に絶縁体118を成膜する（図3参照。）。絶縁体118は、後の工程でCMP処理を行う際に、当該CMP処理のストッパーとして機能することが好ましい。絶縁体118としては、絶縁体422に用いることができる絶縁体を用いればよい。例えば、導電体122Aとしてタンゲステンを用いる場合、絶縁体118として酸化窒化シリコンを用いればよい。本実施の形態では、例えば、絶縁体118を、PECVD法を用いて成膜する。なお、絶縁体118は必ずしも設ける必要はない。

【0133】

次に、絶縁体118の上に、ハードマスクとなる導電体122A、およびハードマスクとなる絶縁体124Aを成膜する（図4参照。）。導電体122Aおよび絶縁体124Aは、後の工程で開口115を形成するときのハードマスクとして機能する。本実施の形態では、例えば、導電体122Aとしてタンゲステンを、スパッタリング法を用いて成膜し、絶縁体124Aとして窒化シリコンを、スパッタリング法を用いて成膜する。なお、導電体122Aと絶縁体124Aも内部応力を調整して、基板の反りを低減することが好ましい。

40

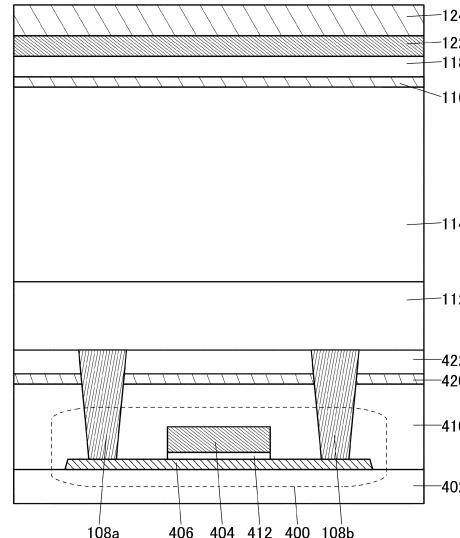

【0134】

次に、絶縁体124Aの上にレジストマスクを形成し、当該レジストマスクを用いて導電体122Aおよび絶縁体124Aをエッチングして、ハードマスク122およびハードマスク124を形成する（図5参照。）。ハードマスク122およびハードマスク124は開口115を形成するためのハードマスクであり、導電体108bと重なる領域に、絶縁体118に達する開口を有する。また、絶縁体124Aの上に有機塗布膜を成膜しても

50

よい。有機塗布膜を絶縁体 124A とレジストマスクの間に形成することで、密着性を向上させることができる場合がある。

【0135】

なお、エッティングには、ドライエッティングを用いることが好ましい。当該ドライエッティングには、例えば、C<sub>4</sub>F<sub>6</sub>ガス、C<sub>5</sub>F<sub>6</sub>ガス、C<sub>4</sub>F<sub>8</sub>ガス、CF<sub>4</sub>ガス、SF<sub>6</sub>ガス、CHF<sub>3</sub>ガス、C<sub>12</sub>ガス、BC<sub>13</sub>ガスまたはSiC<sub>14</sub>ガスなどを単独または2以上以上のガスを混合して用いることができる。または、上記ガスに酸素ガス、ヘリウムガス、アルゴンガスまたは水素ガスなどを適宜添加することができる。これらのエッティングガスは、エッティングする対象（ハードマスク122、ハードマスク124および有機塗布膜）に合わせて適宜切り替えて用いることができる。ドライエッティング装置としては上記の装置を用いることができるが、対向する電極それぞれに周波数の異なる高周波電源を接続する構成の平行平板型ドライエッティング装置の使用が好ましい。

10

【0136】

ここで、上記のように、基板の反りを低減しておくことで、当該開口を精密に形成することができる。

【0137】

次に、ハードマスク122およびハードマスク124を用いてエッティングし、絶縁体422、絶縁体112、絶縁体114、絶縁体116、および絶縁体118に開口115を形成する（図6参照。）。開口115は、少なくとも一部が導電体108bと重なるように形成され、導電体108bおよび絶縁体420に達する開口である。上記の通り開口115はアスペクト比が大きいので、異方性エッティングを行うことが好ましい。なお、本工程のエッティング処理は、図5に示すハードマスク122およびハードマスク124の形成から外気に曝さず連続して行うことが好ましい。

20

【0138】

アスペクト比が大きい開口115を形成する異方性エッティングには、ドライエッティングを用いることが好ましい。当該ドライエッティングには、例えば、C<sub>4</sub>F<sub>6</sub>ガス、C<sub>5</sub>F<sub>6</sub>ガス、C<sub>4</sub>F<sub>8</sub>ガス、CF<sub>4</sub>ガス、SF<sub>6</sub>ガス、CHF<sub>3</sub>ガス、C<sub>12</sub>ガス、BC<sub>13</sub>ガスまたはSiC<sub>14</sub>ガスなどを単独または2以上以上のガスを混合して用いることができる。または、上記ガスに酸素ガス、ヘリウムガス、アルゴンガスまたは水素ガスなどを適宜添加することができる。これらのエッティングガスは、エッティングする対象（絶縁体118、絶縁体116、絶縁体114、絶縁体112、および絶縁体422）に合わせて適宜切り替えて用いることができる。

30

【0139】

ドライエッティング装置としては上記の装置を用いることができるが、対向する電極それぞれに周波数の異なる高周波電源を接続する構成の平行平板型ドライエッティング装置は、比較的容易に異方性エッティングを行うことができるので、当該ドライエッティング装置を用いることが好ましい。

【0140】

開口115を形成する際に、上記のように導電体108bの上部に湾曲面を形成することが好ましい。導電体108bの上部に湾曲面を形成するには、本ドライエッティング処理において、少なくとも導電体108bの上面が露出した段階で、イオン化したエッティングガスを導電体108bの上面に衝突させることが好ましい。これにより、導電体108bの上部の角を削り、湾曲面を形成することができる。

40

【0141】

平行平板型ドライエッティング装置などでは、基板を設置した側の電極で陰極降下を形成し、セルフバイアスを生じさせることができる。このとき、チャンバー中のプラズマ化したエッティングガスに含まれる陽イオンは、セルフバイアスに引き寄せられて、基板側に衝突する。よって、セルフバイアスを大きくすることにより、導電体108bの上面により強くイオンを衝突させて、導電体108bの上部に湾曲面を比較的容易に形成することができる。セルフバイアスを大きくするには、例えば、基板を設置した側の電極に大きい電

50

力（例えば、当該電極に対向する電極に印加した電力より大きい電力）を印加すればよい。ここで、上記のように、対向する電極それぞれに周波数の異なる高周波電源を接続する構成の平行平板型ドライエッティング装置を用いることで、プラズマ放電を行うための高周波電源と、セルフバイアスをかけるための高周波電源と、をそれぞれ独立して制御することができます。

#### 【0142】

また、チャンバー中の陽イオンの平均自由行程を長くすることにより、当該陽イオンを基板面に垂直に近い角度で入射させることができる。これにより、開口115の深い位置でも当該陽イオンを開口115の底面に衝突させることができる。チャンバー中の陽イオンの平均自由行程を長くするには、例えば、プラズマの密度が小さくなり過ぎない程度にチャンバー内の圧力を低くすることが好ましい。

10

#### 【0143】

また、チャンバー中の陽イオンの量を増やすことにより、導電体108bの上部の湾曲面を比較的容易に形成することができる。チャンバー中の陽イオンの量を増やすには、例えば、エッティングガスとして、陽イオン化しやすく、反応性の低いアルゴンガスを含ませればよい。このとき、アルゴンガスの流量は、エッティングガス全体の流量の50%以上、好ましくは70%以上、より好ましくは90%以上とすればよい。

#### 【0144】

このように、少なくとも導電体108bの上面が露出した段階で、イオン化したエッティングガスを導電体108bの上面に衝突させることにより、導電体108bの上部の角を削り取り、湾曲面を形成することができる。このとき、導電体108bの上部だけでなく、絶縁体420の上面もイオンの衝突に曝されるため、絶縁体420の開口115と重なる領域は、絶縁体420の他の領域より膜厚が小さくなる場合がある。つまり、絶縁体420の当該領域は凹んだ形状になる場合がある。

20

#### 【0145】

また、上記エッティング工程において、少なくとも導電体108bの上面が露出した段階で、エッティングガスに、炭素を多く含むガスを添加することが好ましい。具体的には、当該炭素を多く含むガスは、炭素とフッ素を含み、かつ炭素の原子数比がフッ素の原子数比の50%以上であることが好ましい。このような炭素を多く含むガスとしては、例えば、C<sub>4</sub>F<sub>6</sub>ガス、C<sub>5</sub>F<sub>6</sub>ガス、またはC<sub>4</sub>F<sub>8</sub>ガスなどを、単独または2以上のガスを混合して用いることができる。または、上記ガスに酸素ガス、ヘリウムガス、アルゴンガスまたは水素ガスなどを適宜添加することができる。

30

#### 【0146】

このような炭素を多く含むガスを添加してエッティングを行うことにより、当該ガスがプラズマで分解され、炭素化合物が開口115の底面に堆積する。つまり、開口115の底面では陽イオンの衝突と、炭素化合物の堆積が並行して生じる。これにより、陽イオンは堆積した炭素分子を介して絶縁体420に衝突するので、絶縁体420の開口115と重なる領域が、過剰にエッティングされて、凹んだ部分が貫通するのを防ぐことができる。特に、陽イオンの衝突により、開口115が絶縁体420を貫通し、絶縁体410に達するのを防ぐことができる。

40

#### 【0147】

また、エッティングガスに、上記のような炭素を多く含むガスを添加する場合、さらに酸素ガスをエッティングガスに添加することが好ましい。炭素を多く含むガスと、酸素ガスが存在している雰囲気でプラズマを生成することで、炭素を多く含むガスに含まれる炭素が、酸素と結合して炭素酸化物となる。これにより、炭素を多く含むガスから生成される、上記炭素化合物の生成量が低減する。つまり、エッティングガス中の炭素を多く含むガスの流量を多くすると炭素化合物の量が多くなり、エッティングガス中の酸素ガスの流量を多くすると炭素化合物の量が少なくなる。よって、エッティングガス中の炭素を多く含むガスと、酸素ガスの流量によって、炭素化合物の堆積量を調整することができる。

#### 【0148】

50

また、上記の炭素化合物は、開口 115 の内壁にも付着する。開口 115 の内壁に付着した炭素化合物は、開口 115 の内壁の保護膜として機能することができる。これにより開口 115 の内壁が過剰にエッティングされ、開口 115 の内径が過剰に拡張されるのを防ぐことができる。よって、上記エッティング工程において、エッティングガスに、上記の炭素を多く含むガスを添加することで、開口 115 のアスペクト比を比較的容易に大きくすることができる。

#### 【0149】

また、開口 115 のエッティングが進行するにつれ、開口 115 のアスペクト比が増大する。開口 115 のアスペクト比が大きくなるにつれ、上記炭素化合物が開口 115 の深い位置に到達しにくくなる。これは、絶縁体 420 の貫通、または開口 115 のボーリング形状などの、形状不良を発生させる要因となりうる。このため、上記エッティング工程において、エッティングの進行に合わせて、エッティングガス（例えば、上記炭素を多く含むガス）の流量を段階的に増やすことが好ましい。これにより、開口 115 の深い位置でも、開口 115 の浅い位置と同程度の炭素化合物の供給を行うことが可能になる。これにより、開口 115 のエッティングを、絶縁体 420 の上面、または絶縁体 420 の膜中で停止させることができる。

10

#### 【0150】

なお、エッティング後に、ハードマスク 124、およびハードマスク 124 上のレジストマスクを除去することが好ましい。当該レジストマスクの除去は、アッシングなどのドライエッティング処理を行う、またはウェットエッティング処理を行う、またはドライエッティング処理後にウェットエッティング処理を行う、またはウェットエッティング処理後にドライエッティング処理を行うことによってできる。また、上記エッティング工程の途中で当該レジストマスクおよびハードマスク 124 が除去されるようにしてもよい。

20

#### 【0151】

次に、開口 115 およびハードマスク 122 を覆って導電体 110A を成膜する（図 7 参照。）。導電体 110A は後の工程で容量素子 100 の下部電極になる。導電体 110A は、アスペクト比の大きい開口 115 の内壁および底面に接して形成されることが好ましい。このため、導電体 110A は、ALD 法または CVD 法などの被覆性の良い成膜方法を用いて成膜することが好ましく、本実施の形態では、例えば、ALD 法を用いて窒化チタンを成膜する。

30

#### 【0152】

また、ALD 法などの成膜方法を用いて導電体 110A を成膜することにより、導電体 108b の上部の湾曲面に対して被覆性良く導電体 110A を成膜することができる。これにより、導電体 110 と導電体 108b の接触抵抗を低減することができる。

#### 【0153】

次に、導電体 110A の上に充填剤 126 を成膜する（図 7 参照。）。充填剤 126 は、この後の工程で行う CMP 处理ができる程度に、開口 115 を埋め込むことができればよい。よって、開口 115 内に空洞などが形成されていてもよい。充填剤 126 は絶縁体を用いてもよいし、導電体を用いてもよい。本実施の形態では、例えば、充填剤 126 として、APCVD 法を用いて酸化シリコンを成膜する。

40

#### 【0154】

次に、CMP 处理を行って、絶縁体 116 より上の層を除去し、導電体 110 を形成する。（図 8 参照。）。上記のように、絶縁体 118 および絶縁体 116 は CMP 处理に対するストッパーとして機能するので、CMP 处理を段階的に行うことができる。例えば、1 段階目で絶縁体 118 より上に位置する、充填剤 126、導電体 110A、およびハードマスク 122 を除去し、2 段階目で絶縁体 116 より上に位置する、充填剤 126、導電体 110A、および絶縁体 118 を除去すればよい。

#### 【0155】

これにより、開口 115 の縁において、導電体 110 と絶縁体 116 が接するように形成されるので、絶縁体 116 と導電体 110 によって、絶縁体 114、絶縁体 112、絶

50

縁体 422、および絶縁体 420 を覆うことができる。

【0156】

次に、エッティング処理を行って、開口 115 内の充填剤 126 を除去する（図 9 参照）。エッティング処理としては、ウェットエッティング法およびドライエッティング法のいずれを用いてもよいが、開口 115 内の充填剤 126 を除去するにあたって、ウェットエッティング法を用いた方が容易な場合がある。ウェットエッティングを用いる場合、エッチャントとしてフッ酸系の溶液などを用いればよい。

【0157】

ここで、上記のように、絶縁体 114、絶縁体 112、絶縁体 422、および絶縁体 420 は、絶縁体 116 および導電体 110 によって覆われているので、エッティングされるのを防ぐことができる。

10

【0158】

次に、導電体 110 および絶縁体 116 の上に絶縁体 130 を成膜する（図 10 参照）。絶縁体 130 は後の工程で容量素子 100 の誘電体になる。絶縁体 130 は、アスペクト比の大きい開口 115 の内側に設けられた導電体 110 に接して形成されることが好ましい。このため、絶縁体 130 は、ALD 法または CVD 法などの被覆性の良い成膜方法を用いて成膜することが好ましく、本実施の形態では、例えば、ALD 法を用いて酸化ハフニウムを成膜する。

【0159】

また、ALD 法などの成膜方法を用いて絶縁体 130 を成膜し、被覆性良く導電体 110 を覆うことで、容量素子 100 の上部電極と下部電極が短絡することを防ぐことができる。

20

【0160】

また、絶縁体 130 として上記の Higaki 材料、特にハフニウムを含む酸化物を用いる場合は、結晶構造を有せしめ、比誘電率を増加させるために、加熱処理を行うことができる。

【0161】

次に、絶縁体 130 の上に導電体 120aA を成膜し、導電体 120aA の上に導電体 120bA を成膜する（図 10 参照。）。導電体 120aA および導電体 120bA は後の工程で容量素子 100 の上部電極になる。少なくとも導電体 120aA は、アスペクト比の大きい開口 115 の内側に設けられた絶縁体 130 に接して形成されることが好ましい。このため、導電体 120aA は、ALD 法または CVD 法などの被覆性の良い成膜方法を用いて成膜することが好ましく、本実施の形態では、例えば、ALD 法を用いて窒化チタンを成膜する。また、導電体 120bA は、CVD 法などの埋め込み性の良い成膜方法を用いて成膜することが好ましく、本実施の形態では、例えば、金属 CVD 法を用いてタンゲステンを成膜する。

30

【0162】

なお、金属 CVD 法を用いて導電体 120bA を成膜した場合、図 10 に示すように、導電体 120bA の上面の平均面粗さが大きくなることがある。また、上面視における、導電体 120bA の、開口 115 の中央部近傍と重なる領域が、開口 115 に合わせて凹む場合がある。

40

【0163】

このように、導電体 120aA および導電体 120bA を成膜することで、開口 115 中に埋め込み性良く、容量素子 100 の上部電極を設けることができるので、容量素子 100 の静電容量を大きくすることができる。

【0164】

なお、本実施の形態では、導電体 120aA と導電体 120bA の 2 層構造にしているが、これに限られるものではない。開口 115 中に埋め込み性良く、容量素子 100 の上部電極を設けられるなら、導電体を 3 層以上の構造にしてもよいし、導電体 120aA と導電体 120bA のいずれか一方のみの単層構造としてもよい。

50

## 【0165】

次に、導電体120bAの上に膜128を成膜することが好ましい(図11参照。)。膜128は、この後の工程で行うCMP処理ができる程度の膜厚を有することが好ましい。膜128は絶縁体を用いてもよいし、導電体を用いてもよい。本実施の形態では、例えば、膜128として、PECVD法を用いて酸化窒化シリコンを成膜する。

## 【0166】

次に、CMP処理を行って、膜128を除去し、導電体120bAの上面を露出させる。(図12参照。)。このとき、導電体120bAの上面もCMP処理が行われ、上面の平坦性が向上した導電体120bBが形成される。このように、導電体120bAの上に膜128を積層してCMP処理を行うことにより、少なくとも導電体120bBの絶縁体116と重なる領域の、上面の平均面粗さ(Ra)を4nm以下、好ましくは2nm以下、より好ましくは1nm以下にすることができる。このように、導電体120bBの上面の平均面粗さを小さくすることにより、後の工程で行う導電体120aAおよび導電体120bBのフォトリソグラフィをより精密に行うことができる。なお、上記のように、上面視における、導電体120bAの、開口115の中央部近傍と重なる領域が凹んでいる場合、当該領域の平坦性が向上されない場合がある。

10

## 【0167】

なお、導電体120bBの上面の平坦性が十分に得られるならば、膜128を成膜せずに、導電体120bAに直接CMP処理を行ってもよい。

## 【0168】

次に、導電体120bBの上に、ハードマスクとなる絶縁体132Aを成膜する(図12参照。)。絶縁体132Aは、後の工程で導電体120aおよび導電体120bを形成するときのハードマスクとして機能する。本実施の形態では、例えば、絶縁体132Aとして酸化窒化シリコンを、PECVD法を用いて成膜する。

20

## 【0169】

次に、絶縁体132Aの上にレジストマスクを形成し、当該レジストマスクを用いて絶縁体132Aをエッティングして、ハードマスク132を形成する(図13参照。)。上記の通り、導電体120bBの上面の平均面粗さを低減しておくことで、フォトリソグラフィ法を用いて比較的容易にレジストマスクを形成することができる。ハードマスク132は、導電体120aおよび導電体120bを形成するためのハードマスクであり、開口115を覆うように形成される。ここで、ハードマスク132は、開口115からはみ出して絶縁体116と重なる領域を有することが好ましい。なお、エッティングには、ドライエッティングを用いることができる。

30

## 【0170】

次に、ハードマスク132を用いて、導電体120aAおよび導電体120bBをエッティングして、導電体120aおよび導電体120bを形成する(図13参照。)。エッティングとしては、ウェットエッティング処理またはドライエッティング処理を行うことができる。本実施の形態では、ドライエッティング処理を行う。このようにして、導電体110、絶縁体130、および導電体120を有する容量素子100が形成される。

40

## 【0171】

次に、エッティング処理を行って、ハードマスク132を除去する(図14参照。)。エッティングとしては、ウェットエッティング処理またはドライエッティング処理などを行うことができる。本実施の形態では、ウェットエッティング処理を行う。このとき、絶縁体130の導電体120と重ならない領域の上部が当該ウェットエッティング処理によって除去される場合がある。これにより、絶縁体130の導電体120と重なる領域の膜厚が、それ以外の領域より厚くなる場合がある。

## 【0172】

次に、導電体120および絶縁体130の上に絶縁体150を成膜することが好ましい(図15参照。)。ここで絶縁体150は層間絶縁膜として機能する。本実施の形態では、例えば、絶縁体150として酸化窒化シリコンを、PECVD法によって成膜する。

50

## 【0173】

次に、絶縁体422、絶縁体112、絶縁体114、絶縁体116、絶縁体130、および絶縁体150に開口117を形成する(図16参照。)。開口117は、少なくとも一部が導電体108aと重なるように形成され、導電体108aおよび絶縁体420に達する開口である。上記の通り開口117はアスペクト比が大きいので、異方性エッチングを行うことが好ましい。

## 【0174】

開口117は、開口115と同様の方法を用いてエッチングすればよい。これにより、アスペクト比の大きい開口117を形成することができる。また、開口117と重なる領域において、上記の導電体108bと同様に、導電体108aの上部に湾曲面を形成することができる。

10

## 【0175】

次に、開口117に埋め込むように、導電体162aおよび導電体162bを形成する(図16参照。)。導電体162aの形成は、導電体120aについての記載を参照することができる。また、導電体162bの形成は、導電体120bについての記載を参照することができる。このようにして、導電体108aと電気的に接続される接続部160を形成することができる。

## 【0176】

以上により、トランジスタ400および容量素子100を有する半導体装置を作製することができる(図16参照。)。図2乃至図16に示すように、本実施の形態に示す半導体装置の作製方法を用いることで、トランジスタ400の上に容量素子100の少なくとも一部が重なるように形成できるので、半導体装置の占有面積を増やすことなく、静電容量を大きくすることができます。また、上記の容量素子、および半導体装置を生産性良く作製することができる。

20

## 【0177】

## &lt;半導体装置の変形例&gt;

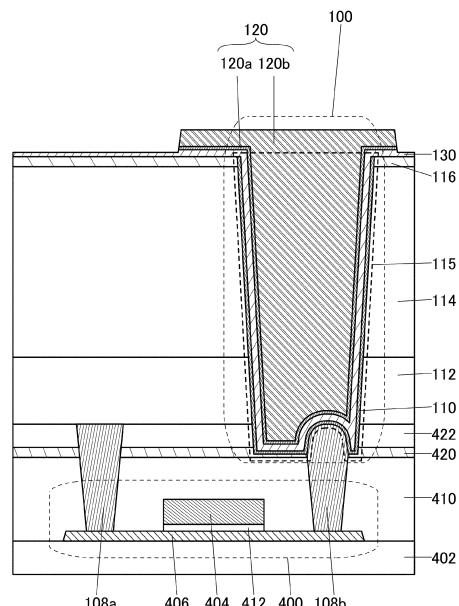

本実施の形態に示す半導体装置は図1に示すものに限られるものではない。以下では、図17から図19を用いて、本実施の形態に示す半導体装置の変形例について説明する。

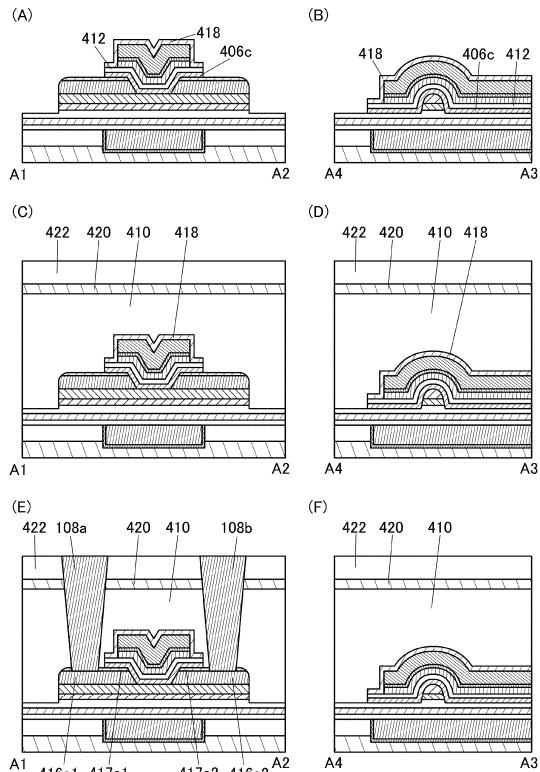

## 【0178】

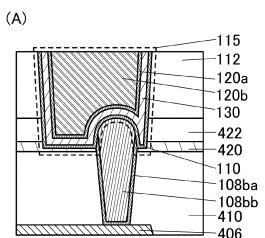

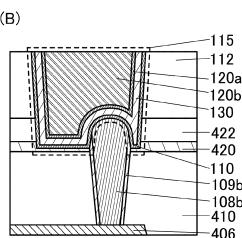

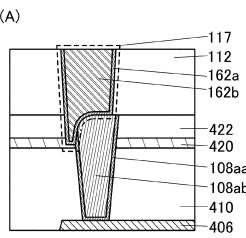

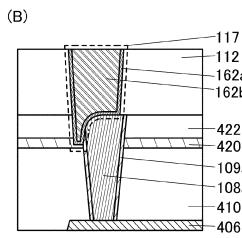

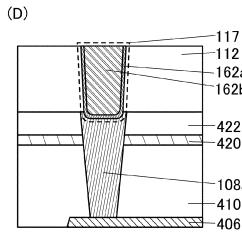

まず、図17(A)から図17(D)を用いて、導電体108b近傍の構造が、図1と異なる半導体装置について説明する。

30

## 【0179】

図17(A)に示す半導体装置は、導電体108bが導電体108baと導電体108bbの積層構造になっている点において、図1に示す半導体装置と異なる。ここで、導電体108bbは、タンゲステン、銅、またはアルミニウムを主成分とする、比較的電気伝導性の高い導電性材料を用いてもよい。また、導電体108baは、水または水素などの不純物の透過を抑制する機能を有する導電性材料を用いることが好ましい。例えば、タンタル、窒化タンタル、チタン、窒化チタン、ルテニウムまたは酸化ルテニウムなどを用いることが好ましい。また、水または水素などの不純物の透過を抑制する機能を有する導電性材料は、単層または積層で用いてもよい。該導電性材料を用いることで、絶縁体410などから水素、水などの不純物が、導電体108baおよび導電体108bbを通じて酸化物406に混入するのを抑制することができる。また、導電体108baは、例えばALD法またはCVD法などを用いて成膜することで被覆性良く成膜することができる。

40

## 【0180】

図17(B)に示す半導体装置は、導電体108bが埋め込まれた絶縁体410および絶縁体420の開口の内壁を、絶縁体109bが覆っている点において、図1に示す半導体装置と異なる。ここで、絶縁体109bは、絶縁体420に用いることができる絶縁体を用いることが好ましい。絶縁体109bとしては、水または水素などの不純物の透過を抑制する機能を有する絶縁性材料を用いることが好ましく、例えば、酸化アルミニウムなどを用いることが好ましい。これにより、絶縁体410などから水素、水などの不純物が

50

、導電体 108b を通じて酸化物 406 に混入するのを抑制することができる。また、絶縁体 109b は、例えば A L D 法または C V D 法などを用いて成膜することで被覆性良く成膜することができる。

【 0181 】

図 17 (C) に示す半導体装置は、導電体 108b の一部が開口 115 と重なっていない点において、図 1 に示す半導体装置と異なる。このように、本実施の形態に示す半導体装置は、少なくとも開口 115 、言い換えると容量素子 100 が導電体 108b の一部に重なる構成にすればよい。図 17 (C) に示すように、導電体 108b の上部の開口 115 と重なる領域には湾曲面が形成されるが、導電体 108b の上部の開口 115 と重ならない領域には湾曲面が形成されず、導電体 108b の上部の角が残っている。

10

【 0182 】

図 17 (D) に示す半導体装置は、導電体 108b の上部に角が残っている点において、図 1 に示す半導体装置と異なる。導電体 110 と導電体 108b の接触抵抗を十分低減できる場合、導電体 108b の上部に角を有する形状にしてもよい。このように、導電体 108b の上部に角を残したままにするには、例えば、図 6 に示す開口 115 を形成する工程において、セルフバイアスを小さくして、導電体 108b の上面に衝突するイオンの衝撃を弱くすればよい。

【 0183 】

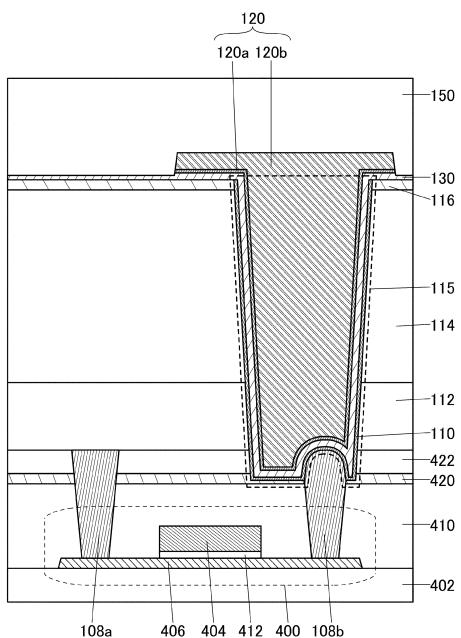

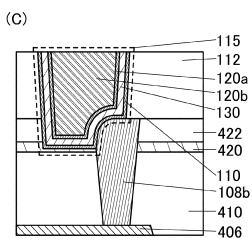

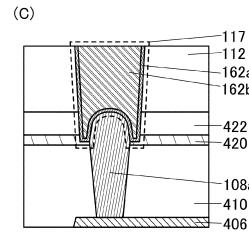

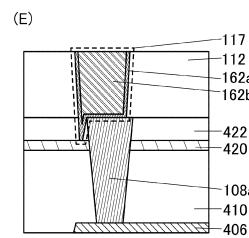

次に、図 18 (A) から図 18 (E) を用いて、導電体 108a 近傍の構造が、図 1 と異なる半導体装置について説明する。

20

【 0184 】

図 18 (A) に示す半導体装置は、導電体 108a が導電体 108aa と導電体 108ab の積層構造になっている点において、図 1 に示す半導体装置と異なる。ここで、導電体 108aa は、タンゲステン、銅、またはアルミニウムを主成分とする、比較的電気伝導性の高い導電性材料を用いてもよい。また、導電体 108aa は、水または水素などの不純物の透過を抑制する機能を有する導電性材料を用いることが好ましい。例えば、タンタル、窒化タンタル、チタン、窒化チタン、ルテニウムまたは酸化ルテニウムなどを用いることが好ましい。また、水または水素などの不純物の透過を抑制する機能を有する導電性材料は、単層または積層で用いてもよい。該導電性材料を用いることで、絶縁体 410 などから水素、水などの不純物が、導電体 108aa および導電体 108ab を通じて酸化物 406 に混入するのを抑制することができる。また、導電体 108aa は、例えば A L D 法または C V D 法などを用いて成膜することで被覆性良く成膜することができる。

30

【 0185 】

図 18 (B) に示す半導体装置は、導電体 108a が埋め込まれた絶縁体 410 および絶縁体 420 の開口の内壁を、絶縁体 109a が覆っている点において、図 1 に示す半導体装置と異なる。ここで、絶縁体 109a は、絶縁体 420 に用いることができる絶縁体を用いることが好ましい。絶縁体 109a としては、水または水素などの不純物の透過を抑制する機能を有する絶縁性材料を用いることが好ましく、例えば、酸化アルミニウムなどを用いることが好ましい。これにより、絶縁体 410 などから水素、水などの不純物が、導電体 108a を通じて酸化物 406 に混入するのを抑制することができる。また、絶縁体 109a は、例えば A L D 法または C V D 法などを用いて成膜することで被覆性良く成膜することができる。

40

【 0186 】

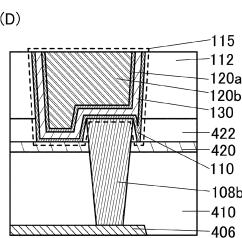

図 18 (C) に示す半導体装置は、開口 117 が導電体 108a の全体と重なる点において、図 1 に示す半導体装置と異なる。図 18 (C) に示すように、導電体 108a の上部全体と開口 117 が重なっているので、導電体 108a の上部に角は残存せず、湾曲面が形成されている。

【 0187 】

図 18 (D) に示す半導体装置は、開口 117 が導電体 108a の上面の端部と重なっていない点において、図 1 に示す半導体装置と異なる。図 18 (D) に示すように、導電

50

体 108a の上面の端部に開口 117 が重なっていないので、導電体 108a の上部に角が形成されている。また、図 18 (D) に示すように、導電体 108a の上面の中央部が凹んだ形状になる場合がある。

【0188】

図 18 (E) に示す半導体装置は、導電体 108a の上部に角が残っている点において、図 1 に示す半導体装置と異なる。導電体 162a と導電体 108a の接触抵抗を十分低減できる場合、導電体 108a の上部に角を有する形状にしてもよい。このように、導電体 108a の上部に角を残したままにするには、例えば、開口 117 を形成する工程において、セルフバイアスを小さくして、導電体 108a の上面に衝突するイオンの衝撃を弱くすればよい。

10

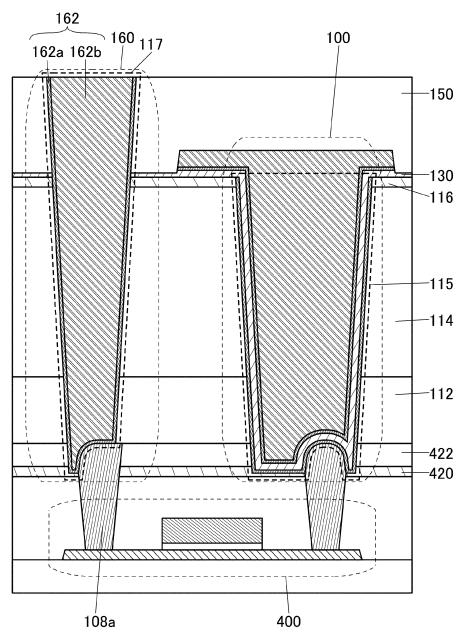

【0189】

また、図 1 に示す半導体装置は、トランジスタと容量素子と、を一つずつ有する構成としたが、本実施の形態に示す半導体装置はこれに限られるものではない。例えば、図 19 に示すように、トランジスタ 400a および容量素子 100a と、トランジスタ 400b および容量素子 100b と、を有する構成にしてもよい。ここで、トランジスタ 400a とトランジスタ 400b が導電体 108a および接続部 160 を共有する構成にしてもよい。図 19 に示すトランジスタ 400a およびトランジスタ 400b はトランジスタ 400 の記載を参照することができ、容量素子 100a および容量素子 100b は容量素子 100 の記載を参照することができる。

【0190】

20

図 19 に示す半導体装置は、例えば、後述する記憶装置のメモリセルなどに用いることができる。トランジスタ 400a とトランジスタ 400b が導電体 108a および接続部 160 を共有する構成にすることにより、トランジスタと容量素子一組当たりの上面視における占有面積を低減することができるので、半導体装置をさらに高集積化させることができる。よって、当該半導体装置を用いた記憶装置の単位面積当たりの記憶容量を増加させることができる。

【0191】

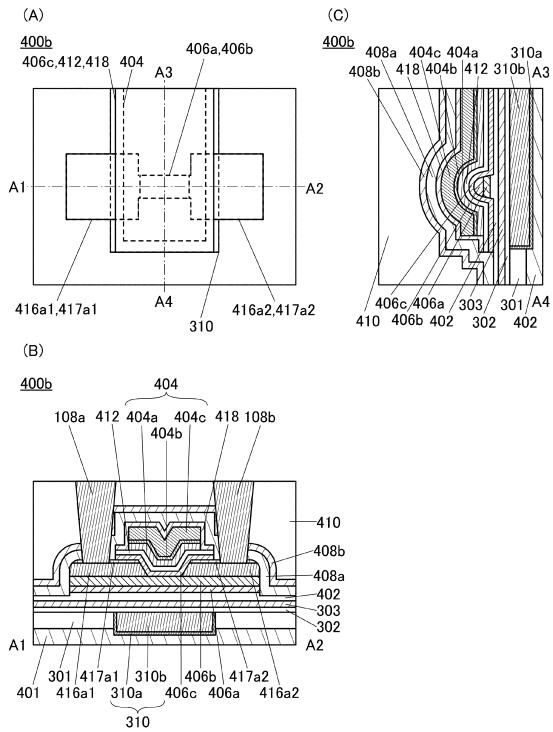

<トランジスタの構成例>

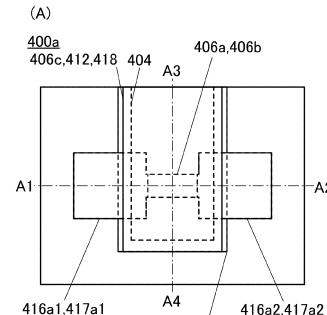

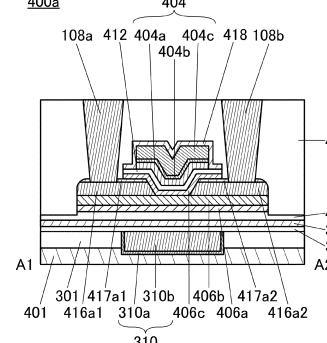

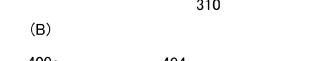

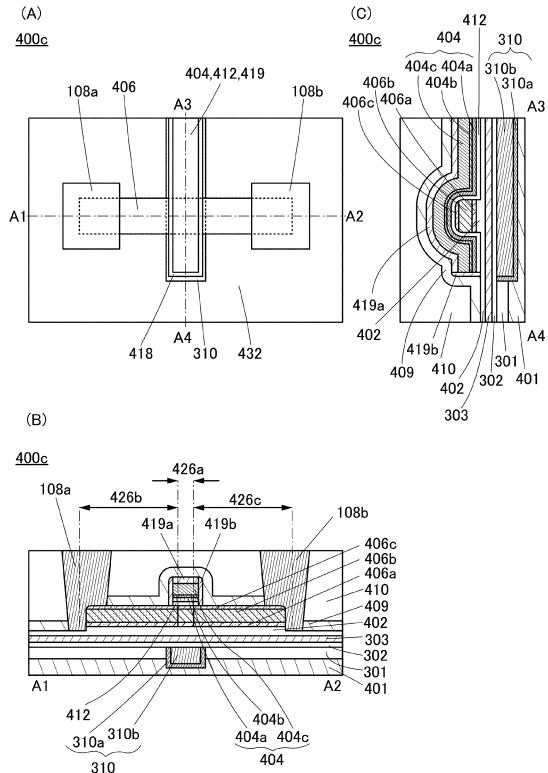

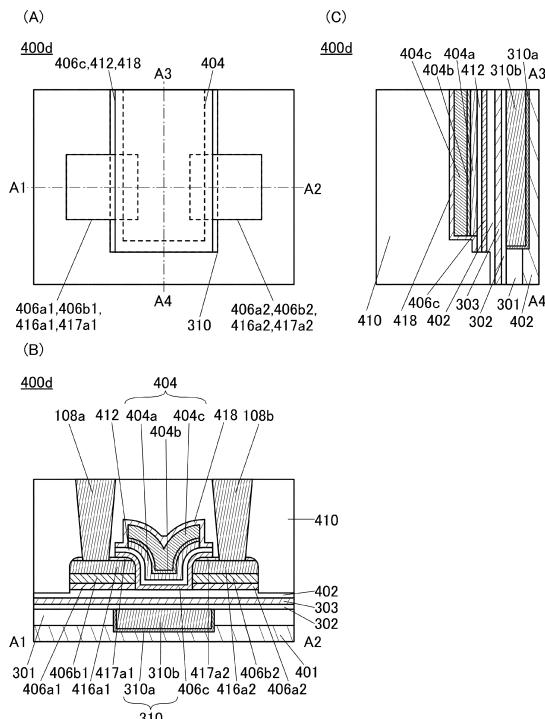

次に、上記のトランジスタ 400 の構成例について、図 20 から図 26 を用いて説明する。図 20 (A) は、本発明の一態様に係るトランジスタ 400a の上面図である。また、図 20 (B) は、図 20 (A) に A1 - A2 の一点鎖線で示す部位の断面図である。つまりトランジスタ 400a のチャネル長方向の断面図を示す。図 20 (C) は、図 20 (A) に A3 - A4 の一点鎖線で示す部位の断面図である。つまりトランジスタ 400a のチャネル幅方向の断面図を示す。図 20 (A) の上面図では、図の明瞭化のために一部の要素を省いて図示している。なお、トランジスタのチャネル長方向とは、基板と水平な面内において、ソース (ソース領域またはソース電極) 及びドレイン (ドレイン領域またはドレイン電極) 間において、キャリアが移動する方向を意味し、チャネル幅方向は、基板と水平な面内において、チャネル長方向に対して垂直の方向を意味する。

30

【0192】

図 20 (A) (B) (C) に示すように、トランジスタ 400a は、導電体 310 (導電体 310a 及び導電体 310b) と、導電体 310 の上に配置された絶縁体 302、絶縁体 303 及び絶縁体 402 と、絶縁体 302、絶縁体 303 及び絶縁体 402 の上に配置された酸化物 406a と、酸化物 406a の上に配置された酸化物 406b と、酸化物 406b の上に、離間して配置された導電体 416a1 及び導電体 416a2 と、酸化物 406b、導電体 416a1 及び導電体 416a2 の上に配置された酸化物 406c と、酸化物 406c の上に配置された絶縁体 412 と、少なくとも一部が酸化物 406b と重なるように、絶縁体 412 の上に配置された導電体 404 (導電体 404a、導電体 404b 及び導電体 404c) と、を有する。

40

【0193】

また、上記のように、絶縁体 402、酸化物 406a、酸化物 406b、酸化物 406

50

c、導電体416a1、導電体416a2、絶縁体412、および導電体404などの上に絶縁体410が配置される。また、絶縁体410、バリア膜417a1、およびバリア膜417a2に形成された開口に導電体108aおよび導電体108bが形成される。また、図20には図示していないが、上記のように絶縁体410の上に絶縁体420が配置される。

【0194】

導電体310は、絶縁体301に形成された開口に設けられている。絶縁体301の開口の内壁に接して導電体310aが形成され、さらに内側に導電体310bが形成されている。ここで、導電体310aおよび導電体310bの上面の高さと、絶縁体301の上面の高さは同程度にできる。導電体310は、ゲート電極の一方として機能できる。

10

【0195】

ここで、導電体310aは、水または水素などの不純物が透過しにくい導電性材料を用いることが好ましい。また、例えば、タンタル、窒化タンタル、ルテニウムまたは酸化ルテニウムなどを用いることが好ましく、単層または積層とすればよい。これにより、絶縁体401より下層から水素、水などの不純物が導電体310を通じて上層に拡散するのを抑制することができる。なお、導電体310aは、水素原子、水素分子、水分子、酸素原子、酸素分子、窒素原子、窒素分子、酸化窒素分子( $N_2O$ 、 $NO$ 、 $NO_2$ など)、または銅原子などの不純物の少なくとも一が透過しにくいことが好ましい。また、以下において、不純物が透過しにくい導電性材料について記載する場合も同様である。導電体310aが酸素の透過を抑制する機能を持つことにより、導電体310bが酸化により導電率が低下することを防ぐことができる。

20

【0196】

絶縁体301は、基板(図示せず)の上に設けられた絶縁体401の上に配置されている。絶縁体401は、下層から水または水素などの不純物がトランジスタに混入するのを防ぐバリア絶縁膜として機能できる。絶縁体401は、水または水素などの不純物が透過しにくい絶縁性材料を用いることが好ましく、例えば、酸化アルミニウムなどを用いることが好ましい。これにより、水素、水などの不純物が絶縁体401より上層に拡散するのを抑制することができる。なお、絶縁体401は、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子( $N_2O$ 、 $NO$ 、 $NO_2$ など)、銅原子などの不純物の少なくとも一が透過しにくいことが好ましい。また、以下において、不純物が透過しにくい絶縁性材料について記載する場合も同様である。

30

【0197】

また、絶縁体401は、酸素(例えば、酸素原子または酸素分子など)が透過しにくい絶縁性材料を用いることが好ましい。これにより、絶縁体402などに含まれる酸素が下方拡散するのを抑制することができる。これにより、酸化物406bに効果的に酸素を供給することができる。

【0198】

また、絶縁体303は、水または水素などの不純物、および酸素が透過しにくい絶縁性材料を用いることが好ましく、例えば、酸化アルミニウムまたは酸化ハフニウムなどを用いることが好ましい。これにより、絶縁体303より下層から水素、水などの不純物が絶縁体303より上層に拡散するのを抑制することができる。さらに、絶縁体402などに含まれる酸素が下方拡散するのを抑制することができる。

40

【0199】

絶縁体402は、加熱により酸素が放出される絶縁体を用いて形成することができる。具体的には、昇温脱離ガス分析法(TDS(Thermal Desorption Spectroscopy))にて、酸素原子に換算した酸素の脱離量が $1.0 \times 10^{-18} \text{ atoms/cm}^3$ 以上、好ましくは $3.0 \times 10^{-20} \text{ atoms/cm}^3$ 以上である絶縁体を用いることが好ましい。なお、加熱により放出される酸素を「過剰酸素」ともいう。このような絶縁体402を酸化物406aに接して設けることにより、酸化物406bに効果的に酸素を供給することができる。なお、上記TDS分析時における膜の表面温

50

度としては 100 以上 700 以下、または 100 以上 500 以下の範囲が好ましい。

【0200】

また、絶縁体 402 中の水、水素または窒素酸化物などの不純物濃度が低減されていることが好ましい。例えば、絶縁体 402 の水素の脱離量は、TDSにおいて、50 から 500 の範囲において、水素分子に換算した脱離量が、絶縁体 402 の面積当たりに換算して、 $2 \times 10^{15} \text{ molecules/cm}^2$  以下、好ましくは  $1 \times 10^{15} \text{ molecules/cm}^2$  以下、より好ましくは  $5 \times 10^{14} \text{ molecules/cm}^2$  以下であればよい。

【0201】

絶縁体 302、絶縁体 303、および絶縁体 402 は、ゲート絶縁膜として機能できる。なお、トランジスタ 400a では、ゲート絶縁膜として絶縁体 302、絶縁体 303、および絶縁体 402 が積層された絶縁膜を用いているが、本実施の形態に示す半導体装置はこれに限られるものではない。例えば、ゲート絶縁膜として、絶縁体 302、絶縁体 303、および絶縁体 402 のいずれか 2 層または 1 層を用いてもよい。

【0202】

次に、酸化物 406a、酸化物 406b 及び酸化物 406c に用いることができる、酸化物半導体として機能する金属酸化物（以下、酸化物半導体ともいう）について説明する。なお、本明細書等において、窒素を有する金属酸化物も金属酸化物（metal oxide）と総称する場合がある。また、窒素を有する金属酸化物を、金属酸窒化物（metal oxy nitride）と呼称してもよい。

【0203】

酸化物 406a、酸化物 406b 及び酸化物 406c として用いる金属酸化物は、少なくともインジウムを含むことが好ましい。特にインジウムおよび亜鉛を含むことが好ましい。また、それらに加えて、元素 M（元素 M は、ガリウム、アルミニウム、シリコン、ホウ素、イットリウム、銅、バナジウム、ベリリウム、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タンゲステン、またはマグネシウムなどから選ばれた一種、または複数種）が含まれていることが好ましい。

【0204】

また、上記金属酸化物は、エネルギーギャップが 2 eV 以上、好ましくは 2.5 eV 以上である。このように、エネルギーギャップの広い金属酸化物を用いることで、トランジスタのオフ電流を低減することができる。

【0205】

ここで、金属酸化物が、インジウム、元素 M 及び亜鉛を有する場合を考える。なお、金属酸化物が有するインジウム、元素 M、及び亜鉛の原子数比のそれぞれの項を [In]、[M]、および [Zn] とする。

【0206】

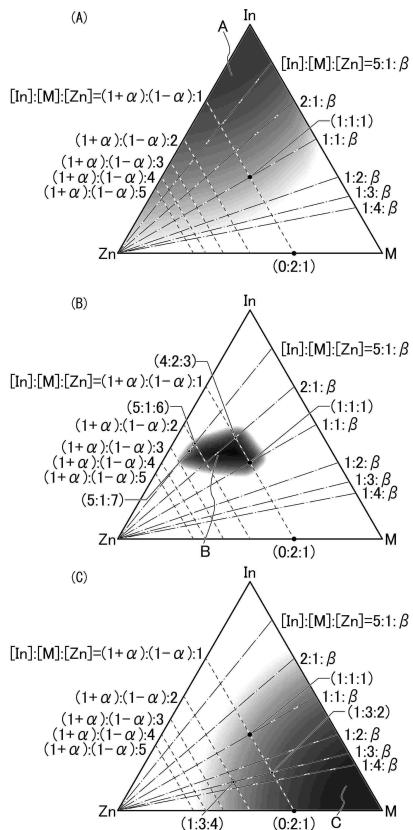

以下に、図 26 (A)、図 26 (B)、および図 26 (C) を用いて、酸化物 406a、酸化物 406b 及び酸化物 406c に用いることができる金属酸化物が有するインジウム、元素 M および亜鉛の原子数比の好ましい範囲について説明する。なお、図 26 (A)、図 26 (B)、および図 26 (C) には、酸素の原子数比については記載しない。

【0207】

図 26 (A)、図 26 (B)、および図 26 (C) において、破線は、 $[In] : [M] : [Zn] = (1 + \dots) : (1 - \dots) : 1$  の原子数比 (-1 1) となるライン、 $[In] : [M] : [Zn] = (1 + \dots) : (1 - \dots) : 2$  の原子数比となるライン、 $[In] : [M] : [Zn] = (1 + \dots) : (1 - \dots) : 3$  の原子数比となるライン、 $[In] : [M] : [Zn] = (1 + \dots) : (1 - \dots) : 4$  の原子数比となるライン、および $[In] : [M] : [Zn] = (1 + \dots) : (1 - \dots) : 5$  の原子数比となるラインを表す。

10

20

30

40

50

## 【0208】

また、一点鎖線は、 $[In] : [M] : [Zn] = 5 : 1 : 0$  の原子数比となるライン、 $[In] : [M] : [Zn] = 2 : 1 : 0$  の原子数比となるライン、 $[In] : [M] : [Zn] = 1 : 1 : 0$  の原子数比となるライン、 $[In] : [M] : [Zn] = 1 : 2 : 0$  の原子数比となるライン、 $[In] : [M] : [Zn] = 1 : 3 : 0$  の原子数比となるライン、および $[In] : [M] : [Zn] = 1 : 4 : 0$  の原子数比となるラインを表す。

## 【0209】

また、図26(A)、図26(B)、および図26(C)に示す、 $[In] : [M] : [Zn] = 0 : 2 : 1$  の原子数比、およびその近傍値の金属酸化物は、スピネル型の結晶構造をとりやすい。

10

## 【0210】

また、金属酸化物中に複数の相が共存する場合がある(二相共存、三相共存など)。例えば、原子数比が $[In] : [M] : [Zn] = 0 : 2 : 1$ の近傍値である場合、スピネル型の結晶構造と層状の結晶構造との二相が共存しやすい。また、原子数比が $[In] : [M] : [Zn] = 1 : 0 : 0$ の近傍値である場合、ビックスバイト型の結晶構造と層状の結晶構造との二相が共存しやすい。金属酸化物中に複数の相が共存する場合、異なる結晶構造の間ににおいて、結晶粒界が形成される場合がある。

## 【0211】

図26(A)に示す領域Aは、金属酸化物が有する、インジウム、元素M、および亜鉛の原子数比の好ましい範囲の一例について示している。

20

## 【0212】

金属酸化物は、インジウムの含有率を高くすることで、金属酸化物のキャリア移動度(電子移動度)を高くすることができます。従って、インジウムの含有率が高い金属酸化物はインジウムの含有率が低い金属酸化物と比較してキャリア移動度が高くなる。

## 【0213】

一方、金属酸化物中のインジウムおよび亜鉛の含有率が低くなると、キャリア移動度が低くなる。従って、原子数比が $[In] : [M] : [Zn] = 0 : 1 : 0$ 、およびその近傍値である場合(例えば図26(C)に示す領域C)は、絶縁性が高くなる。

## 【0214】

例えば、酸化物406bに用いる金属酸化物は、キャリア移動度が高い、図26(A)の領域Aで示される原子数比を有することが好ましい。一方、酸化物406a及び酸化物406cに用いる金属酸化物は、絶縁性が比較的高い、図26(C)の領域Cで示される原子数比を有することが好ましい。

30

## 【0215】

特に、図26(B)に示す領域Bでは、領域Aの中でも、キャリア移動度が高く、信頼性が高い優れた金属酸化物が得られる。

## 【0216】

なお、領域Bは、 $[In] : [M] : [Zn] = 4 : 2 : 3$ から $4 : 1$ 、およびその近傍値を含む。近傍値には、例えば、 $[In] : [M] : [Zn] = 5 : 3 : 4$ が含まれる。また、領域Bは、 $[In] : [M] : [Zn] = 5 : 1 : 6$ 、およびその近傍値、および $[In] : [M] : [Zn] = 5 : 1 : 7$ 、およびその近傍値を含む。

40

## 【0217】

また、金属酸化物として、In-M-Zn酸化物を用いる場合、スパッタリングターゲットとしては、多結晶のIn-M-Zn酸化物を含むターゲットを用いると好ましい。なお、成膜される金属酸化物の原子数比は、上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス40%の変動を含む。例えば、金属酸化物の成膜に用いるスパッタリングターゲットの組成が $In : Ga : Zn = 4 : 2 : 4 : 1$ [原子数比]の場合、成膜される金属酸化物の組成は、 $In : Ga : Zn = 4 : 2 : 3$ [原子数比]の近傍となる場合がある。また、金属酸化物の成膜に用いるスパッタリングターゲットの組

50

成が  $In : Ga : Zn = 5 : 1 : 7$  [原子数比] の場合、成膜される金属酸化物の組成は、 $In : Ga : Zn = 5 : 1 : 6$  [原子数比] の近傍となる場合がある。

【0218】

なお、金属酸化物が有する性質は、原子数比によって一義的に定まらない。同じ原子数比であっても、形成条件により、金属酸化物の性質が異なる場合がある。例えば、金属酸化物をスパッタリング装置にて成膜する場合、ターゲットの原子数比からずれた原子数比の膜が形成される。また、成膜時の基板温度によっては、ターゲットの [Zn] よりも、膜の [Zn] が小さくなる場合がある。従って、図示する領域は、金属酸化物が特定の特性を有する傾向がある原子数比を示す領域であり、領域 A 乃至領域 C の境界は厳密ではない。

10

【0219】

また、トランジスタには、キャリア密度の低い金属酸化物を用いることが好ましい。金属酸化物のキャリア密度を低くする場合においては、金属酸化物中の不純物濃度を低くし、欠陥準位密度を低くすればよい。本明細書等において、不純物濃度が低く、欠陥準位密度の低いことを高純度真性または実質的に高純度真性と言う。例えば、酸化物 406b におけるキャリア密度が  $8 \times 10^{11} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{10} / \text{cm}^3$  未満であり、 $1 \times 10^{-9} / \text{cm}^3$  以上とすればよい。高純度真性または実質的に高純度真性である金属酸化物は、キャリア発生源が少ないため、キャリア密度を低くすることができる。

【0220】

また、高純度真性または実質的に高純度真性である金属酸化物は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。

20

【0221】

また、金属酸化物のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い金属酸化物にチャネル形成領域が形成されるトランジスタは、電気特性が不安定となる場合がある。

【0222】

従って、トランジスタの電気特性を安定にするためには、金属酸化物中の不純物濃度を低減することが有効である。また、金属酸化物中の不純物濃度を低減するためには、近接する膜中の不純物濃度も低減することが好ましい。不純物としては、水素、アルカリ金属、アルカリ土類金属、シリコン等がある。

30

【0223】

ここで、金属酸化物における各不純物の影響について説明する。

【0224】

金属酸化物において、第 14 族元素の一つであるシリコンや炭素が含まれると、金属酸化物において欠陥準位が形成される。このため、金属酸化物におけるシリコンや炭素の濃度と、金属酸化物との界面近傍のシリコンや炭素の二次イオン質量分析法 (SIMS : Secondary Ion Mass Spectrometry) により得られる濃度を、 $2 \times 10^{18} \text{ atoms} / \text{cm}^3$  以下、好ましくは  $2 \times 10^{17} \text{ atoms} / \text{cm}^3$  以下とする。

40

【0225】

また、金属酸化物にアルカリ金属またはアルカリ土類金属が含まれると、欠陥準位を形成し、キャリアを生成する場合がある。従って、アルカリ金属またはアルカリ土類金属が含まれている金属酸化物を用いたトランジスタはノーマリーオン特性となりやすい。このため、金属酸化物中のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。具体的には、SIMS により得られる金属酸化物中のアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18} \text{ atoms} / \text{cm}^3$  以下、好ましくは  $2 \times 10^{16} \text{ atoms} / \text{cm}^3$  以下とする。

【0226】

50

また、金属酸化物に含まれる水素は、金属原子と結合する酸素と反応して水になるため、酸素欠損 ( $V_o$ ) を形成する場合がある。該酸素欠損 ( $V_o$ ) に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することができる。従って、水素が含まれている金属酸化物を用いたトランジスタはノーマリーオン特性となりやすい。このため、金属酸化物中の水素はできる限り低減されていることが好ましい。具体的には、金属酸化物において、S I M S により得られる水素濃度を、 $1 \times 10^{20}$  atoms / cm<sup>3</sup> 未満、好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup> 未満、より好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup> 未満、さらに好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup> 未満とする。

#### 【0227】

なお、金属酸化物中の酸素欠損 ( $V_o$ ) は、酸素を金属酸化物に導入することで、低減することができる。つまり、金属酸化物中の酸素欠損 ( $V_o$ ) に、酸素が補填されることで、酸素欠損 ( $V_o$ ) は消失する。従って、金属酸化物中に、酸素を拡散させることで、トランジスタの酸素欠損 ( $V_o$ ) を低減し、信頼性を向上させることができる。

#### 【0228】

なお、酸素を金属酸化物に導入する方法として、例えば、金属酸化物に接して、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物を設けることができる。つまり、酸化物には、化学量論的組成よりも酸素が過剰に存在する領域（以下、過剰酸素領域ともいう）が形成されていることが好ましい。特に、トランジスタに金属酸化物を用いる場合、トランジスタ近傍の下地膜や、層間膜などに、過剰酸素領域を有する酸化物を設けることで、トランジスタの酸素欠損を低減し、信頼性を向上させることができる。

#### 【0229】

不純物が十分に低減された金属酸化物をトランジスタのチャネル形成領域などに用いることで、安定した電気特性を付与することができる。

#### 【0230】

また、酸化物 406b に用いられる金属酸化物は、C A C (C l o u d - A l i g n e d C o m p o s i t e) 構成を有することが好ましい。以下では、本発明の一態様で開示されるトランジスタに用いることができる C A C (C l o u d - A l i g n e d C o m p o s i t e) - O S の構成について説明する。

#### 【0231】

C A C - O S または C A C - m e t a l o x i d e とは、材料の一部では導電性の機能と、材料の一部では絶縁性の機能とを有し、材料の全体では半導体としての機能を有する。なお、C A C - O S または C A C - m e t a l o x i d e を、トランジスタの活性層に用いる場合、導電性の機能は、キャリアとなる電子（またはホール）を流す機能であり、絶縁性の機能は、キャリアとなる電子を流さない機能である。導電性の機能と、絶縁性の機能とを、それぞれ相補的に作用させることで、スイッチングさせる機能（On / Off させる機能）を C A C - O S または C A C - m e t a l o x i d e に付与することができる。C A C - O S または C A C - m e t a l o x i d e において、それぞれの機能を分離させることで、双方の機能を最大限に高めることができる。

#### 【0232】

また、C A C - O S または C A C - m e t a l o x i d e は、導電性領域、及び絶縁性領域を有する。導電性領域は、上述の導電性の機能を有し、絶縁性領域は、上述の絶縁性の機能を有する。また、材料中において、導電性領域と、絶縁性領域とは、ナノ粒子レベルで分離している場合がある。また、導電性領域と、絶縁性領域とは、それぞれ材料中に偏在する場合がある。また、導電性領域は、周辺がぼけてクラウド状に連結して観察される場合がある。

#### 【0233】

また、C A C - O S または C A C - m e t a l o x i d e において、導電性領域と、絶縁性領域とは、それぞれ 0.5 nm 以上 10 nm 以下、好ましくは 0.5 nm 以上 3 nm 以下のサイズで材料中に分散している場合がある。

10

20

30

40

50

## 【0234】

また、CAC-OSまたはCAC-metal oxideは、異なるバンドギャップを有する成分により構成される。例えば、CAC-OSまたはCAC-metal oxideは、絶縁性領域に起因するワイドギャップを有する成分と、導電性領域に起因するナローギャップを有する成分と、により構成される。当該構成の場合、キャリアを流す際に、ナローギャップを有する成分において、主にキャリアが流れる。また、ナローギャップを有する成分が、ワイドギャップを有する成分に相補的に作用し、ナローギャップを有する成分に連動してワイドギャップを有する成分にもキャリアが流れる。このため、上記CAC-OSまたはCAC-metal oxideをトランジスタのチャネル形成領域に用いる場合、トランジスタのオン状態において高い電流駆動力、つまり大きなオン電流、及び高い電界効果移動度を得ることができる。

10

## 【0235】

すなわち、CAC-OSまたはCAC-metal oxideは、マトリックス複合材(matrix composite)、または金属マトリックス複合材(metal matrix composite)と呼称することもできる。

## 【0236】

また、上記金属酸化物は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体と、に分けられる。非単結晶酸化物半導体としては、例えば、CAAC-OS(c-axis aligned crystalline oxide semiconductor)、多結晶酸化物半導体、nc-OS(nanocrystalline oxide semiconductor)、擬似非晶質酸化物半導体(a-like OS: amorphous-like oxide semiconductor)および非晶質酸化物半導体などがある。

20

## 【0237】

CAAC-OSは、c軸配向性を有し、かつa-b面方向において複数のナノ結晶が連結し、歪みを有した結晶構造となっている。なお、歪みとは、複数のナノ結晶が連結する領域において、格子配列の揃った領域と、別の格子配列の揃った領域との間で格子配列の向きが変化している箇所を指す。

## 【0238】

ナノ結晶は、六角形を基本とするが、正六角形状とは限らず、非正六角形状である場合がある。また、歪みにおいて、五角形、および七角形などの格子配列を有する場合がある。なお、CAAC-OSにおいて、歪み近傍においても、明確な結晶粒界(グレインバウンダリーともいう)を確認することはできない。即ち、格子配列の歪みによって、結晶粒界の形成が抑制されていることがわかる。これは、CAAC-OSが、a-b面方向において酸素原子の配列が稠密でないことや、金属元素が置換することで原子間の結合距離が変化することなどによって、歪みを許容することができるためと考えられる。

30

## 【0239】

また、CAAC-OSは、インジウム、および酸素を有する層(以下、In層)と、元素M、亜鉛、および酸素を有する層(以下、(M, Zn)層)とが積層した、層状の結晶構造(層状構造ともいう)を有する傾向がある。なお、インジウムと元素Mは、互いに置換可能であり、(M, Zn)層の元素Mがインジウムと置換した場合、(In, M, Zn)層と表すこともできる。また、In層のインジウムが元素Mと置換した場合、(In, M)層と表すこともできる。

40

## 【0240】

CAAC-OSは結晶性の高い酸化物半導体である。一方、CAAC-OSは、明確な結晶粒界を確認することはできないため、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。また、酸化物半導体の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、CAAC-OSは不純物や欠陥(酸素欠損など)の少ない酸化物半導体ともいえる。従って、CAAC-OSを有する酸化物半導体は、物理的性質が安定する。そのため、CAAC-OSを有する酸化物半導体は熱に強く、信頼性が高い。

50

## 【0241】

n c - O S は、微小な領域（例えば、1 nm 以上 10 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。また、n c - O S は、異なるナノ結晶間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O S は、分析方法によっては、a - l i k e O S や非晶質酸化物半導体と区別が付かない場合がある。

## 【0242】

a - l i k e O S は、n c - O S と非晶質酸化物半導体との間の構造を有する酸化物半導体である。a - l i k e O S は、鬆または低密度領域を有する。即ち、a - l i k e O S は、n c - O S および C A A C - O S と比べて、結晶性が低い。

10

## 【0243】

酸化物半導体は、多様な構造をとり、それぞれが異なる特性を有する。本発明の一態様の酸化物半導体は、非晶質酸化物半導体、多結晶酸化物半導体、a - l i k e O S 、n c - O S 、C A A C - O S のうち、二種以上を有していてもよい。

## 【0244】

酸化物 406a および酸化物 406c に用いる金属酸化物は、元素 M（元素 M は、Al、Ga、Si、B、Y、Ti、Fe、Ni、Ge、Zr、Mo、La、Ce、Nd、Hf、Ta、W、Mg、V、Be、または Cu のいずれか一つ、または複数）を含む酸化物である。酸化物 406a および酸化物 406c は、例えば、In - Ga - Zn 酸化物、酸化ガリウム、酸化ホウ素などを用いることができる。

20

## 【0245】

ここで、酸化物 406a および酸化物 406c に用いる金属酸化物において、構成元素中の元素 M の原子数比が、酸化物 406b に用いる金属酸化物における、構成元素中の元素 M の原子数比より大きいことが好ましい。また、酸化物 406a および酸化物 406c に用いる金属酸化物において、In に対する元素 M の原子数比が、酸化物 406b に用いる金属酸化物における、In に対する元素 M の原子数比より大きいことが好ましい。

## 【0246】

また、酸化物 406a および酸化物 406c に用いる金属酸化物は、非単結晶構造であると好ましい。非単結晶構造は、例えば、C A A C - O S 、多結晶構造、微結晶構造、または非晶質構造を含む。酸化物 406a および酸化物 406c に用いる金属酸化物は、C A A C 構造を有していてもよい。よって、酸化物 406a および酸化物 406c に用いる金属酸化物は、複数の I G Z O のナノ結晶が c 軸配向を有し、かつ a - b 面においては配向せずに連結した層状の結晶構造を有していてもよい。

30

## 【0247】

また、酸化物 406a および酸化物 406c に用いる金属酸化物は、酸化物 406b に用いる金属酸化物より高い結晶性を有していてもよい。ここで、酸化物 406a および酸化物 406c に用いる金属酸化物は、例えば、酸素を含む雰囲気下で成膜した酸化物とすればよい。これにより、酸化物 406a および酸化物 406c に高い結晶性を有せしめることができる。また、酸化物 406a および酸化物 406c の形状の安定を図ることができる。

40

## 【0248】

以上のような金属酸化物を酸化物 406c として用いて、酸化物 406c の伝導帯下端のエネルギーが、酸化物 406b の伝導帯下端のエネルギーより高くなることが好ましい。また、言い換えると、酸化物 406c の電子親和力が、酸化物 406b の電子親和力より小さいことが好ましい。ここで、電子親和力とは、真空準位と伝導帯下端のエネルギー準位の差を指す。

## 【0249】

また同様に、以上のような金属酸化物を酸化物 406a として用いて、酸化物 406a の伝導帯下端のエネルギーが、酸化物 406b の伝導帯下端のエネルギーより高くなることが好ましい。また、言い換えると、酸化物 406a の電子親和力が、酸化物 406b の

50

電子親和力より小さいことが好ましい。

【0250】

ここで、酸化物406a、酸化物406b及び酸化物406cにおいて、伝導帯下端のエネルギー準位はなだらかに変化する。換言すると、連続的に変化または連続接合するともいうことができる。このようにするために、酸化物406aと酸化物406bとの界面、または酸化物406bと酸化物406cとの界面において形成される混合層の欠陥準位密度を低くするとよい。

【0251】

具体的には、酸化物406aと酸化物406b、酸化物406bと酸化物406cが、酸素以外に共通の元素を有する（主成分とする）ことで、欠陥準位密度が低い混合層を形成することができる。例えば、酸化物406bがIn-Ga-Zn酸化物の場合、酸化物406a、酸化物406cとして、In-Ga-Zn酸化物、Ga-Zn酸化物、酸化ガリウムなどを用いるとよい。

10

【0252】

このとき、キャリアの主たる経路は酸化物406bおよびその近傍となる。酸化物406aと酸化物406bとの界面、および酸化物406bと酸化物406cとの界面における欠陥準位密度を低くすることができるため、界面散乱によるキャリア伝導への影響が小さく、高いオン電流が得られる。

【0253】

トラップ準位に電子が捕獲されることで、捕獲された電子は固定電荷のように振る舞うため、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。酸化物406a、酸化物406cを設けることにより、トラップ準位を酸化物406bより遠ざけることができる。当該構成とすることで、トランジスタのしきい値電圧がプラス方向にシフトすることを防止することができる。

20

【0254】

なお、本実施の形態ではトランジスタに用いる金属酸化物を上述の3層構造としているが、本発明の一態様はこれに限定されない。例えば、酸化物406aまたは酸化物406cの一方がない2層構造としても構わない。または、酸化物406aの上もしくは下、または酸化物406cの上もしくは下に、前述した半導体のいずれか一を有する4層構造としても構わない。または、酸化物406aの上、酸化物406aの下、酸化物406cの上、酸化物406cの下のいずれか二箇所以上に、酸化物406a、酸化物406bおよび酸化物406cとして例示した半導体のいずれか一を有するn層構造（nは5以上の整数）としても構わない。

30

【0255】

本実施の形態に示すトランジスタは、以上に示す酸化物406a、酸化物406b及び酸化物406cを有することが好ましい。

【0256】

酸化物406aは、絶縁体402の上面に接して配置されることが好ましい。酸化物406bは酸化物406aの上面に接して配置されることが好ましい。

【0257】

また、酸化物406bは、第1の領域、第2の領域、および第3の領域を有する。第3の領域は、上面図において第1の領域と第2の領域に挟まれる。本実施の形態に示すトランジスタは、酸化物406bの第1の領域上に接して導電体416a1を有する。また、酸化物406bの第2の領域上に接して導電体416a2を有する。酸化物406bの第1の領域または第2の領域の一方は、ソース領域として機能でき、他方はドレイン領域として機能できる。また、酸化物406bの第3の領域はチャネル形成領域として機能できる。

40

【0258】

酸化物406cは、酸化物406bの第3の領域に接して、酸化物406a、酸化物406b、導電体416a1、416a2、及びバリア膜417a1、417a2の上に配

50

置されることが好ましい。また、酸化物 406c が、酸化物 406a 及び酸化物 406b の側面を覆う構成にしてもよい。図 20 (C) に示すように、酸化物 406a 及び酸化物 406b のチャネル幅方向の側面が酸化物 406c に接することが好ましい。さらに、第 1 のゲート電極としての機能を有する導電体 404 は、第 1 のゲート絶縁体としての機能を有する絶縁体 412 を介して酸化物 406b の第 3 の領域の全体を覆うように配置される。

#### 【0259】

また、酸化物 406c は、酸化物 406a および酸化物 406b の全体を覆うように配置してもよい。例えば、酸化物 406a 及び酸化物 406b のチャネル長方向の側面が酸化物 406c に接する構成にしてもよい。

10

#### 【0260】

導電体 416a1 及び導電体 416a2 は、離間して配置され、酸化物 406b の上面に接して配置されることが好ましい。ここで、導電体 416a1 は、ソース電極またはドレイン電極の一方として機能でき、導電体 416a2 は、ソース電極またはドレイン電極の他方として機能できる。

#### 【0261】

また、図 20 (A) (B) に示すように、導電体 416a1 の一方の側端部は、酸化物 406a の一方の側端部及び酸化物 406b の一方の側端部と略一致することが好ましい。また、同様に、導電体 416a2 の一方の側端部は、酸化物 406a の他方の側端部及び酸化物 406b の他方の側端部と略一致することが好ましい。このような構成により、酸化物 406a 及び酸化物 406b の側面が導電体 416a1 及び導電体 416a2 に接しないので、酸化物 406a 及び酸化物 406b の側面において、酸素が引き抜かれて酸素欠損が形成されることを防ぐことができる。また、酸化物 406a 及び酸化物 406b の側面が導電体 416a1 及び導電体 416a2 に接しないので、酸化物 406a 及び酸化物 406b の側面から導電体 416a1 及び導電体 416a2 に起因する不純物が浸入することを防ぐことができる。

20

#### 【0262】

ここで、互いに向かい合う導電体 416a1 の側端部と導電体 416a2 の側端部との距離、即ちトランジスタのチャネル長は、10 nm 以上 300 nm 以下、代表的には 20 nm 以上 180 nm 以下とする。

30

#### 【0263】

また、導電体 416a1 及び導電体 416a2 の互いに向かい合う側面と底面のなす角が 90° 未満のテーオー角を有することが好ましい。導電体 416a1 及び導電体 416a2 の互いに向かい合う側面と底面のなす角が 45° 以上 75° 以下であることが好ましい。このように導電体 416a1 及び導電体 416a2 を形成することにより、酸化物 406c を導電体 416a1 及び導電体 416a2 が形成する段差部にも被覆性良く成膜することができる。これにより、酸化物 406c が段切れなどを起こして、酸化物 406b と絶縁体 412 などが接するのを防ぐことができる。

#### 【0264】

また、導電体 416a1 の上面に接してバリア膜 417a1 が配置され、導電体 416a2 の上面に接してバリア膜 417a2 が設けられることが好ましい。バリア膜 417a1 及びバリア膜 417a2 は、水素や水などの不純物および酸素の透過を抑制する機能を有する。バリア膜 417a1 及びバリア膜 417a2 として、例えば、酸化アルミニウムなどを用いることができる。これにより、導電体 416a1 及び導電体 416a2 の酸化に周囲の過剰酸素が用いられることを防ぐことができる。また、導電体 416a1 および導電体 416a2 の酸化による電気抵抗値の増加を防ぐことができる。なお、導電体の電気抵抗値の測定は、2 端子法などを用いて測定することができる。なお、バリア膜 417a1、417a2 を設けない構成としてもよい。

40

#### 【0265】

また、導電体 404 と導電体 416a1 の間に、絶縁体 412、酸化物 406c に加え

50

て、バリア膜 417a1 を有しているので、導電体 404 と導電体 416a1 の間の寄生容量を小さくすることができる。同様に、導電体 404 と導電体 416a2 の間に、絶縁体 412、酸化物 406c に加えて、バリア膜 417a2 を有しているので、導電体 404 と導電体 416a2 の間の寄生容量を小さくすることができる。よって、本実施の形態に示すトランジスタは、周波数特性に優れたトランジスタとなる。

#### 【0266】

絶縁体 412 はゲート絶縁膜として機能でき、酸化物 406c の上面に接して配置されることが好ましい。絶縁体 412 は、絶縁体 402 と同様に、加熱により酸素が放出される絶縁体を用いて形成することが好ましい。このような絶縁体 412 を酸化物 406c の上面に接して設けることにより、酸化物 406b に効果的に酸素を供給することができる。また、絶縁体 402 と同様に、絶縁体 412 中の水または水素などの不純物濃度が低減されていることが好ましい。

10

#### 【0267】

導電体 404 は、導電体 404a、導電体 404b 及び導電体 404c が積層された構成とすることが好ましい。絶縁体 412 上に導電体 404a が配置され、導電体 404a 上に導電体 404b が配置され、導電体 404b 上に導電体 404c が配置される。絶縁体 412 および導電体 404 は、酸化物 406b と重なる領域を有する。また、導電体 404a、導電体 404b および導電体 404c の側端部は概略一致する。ここで、導電体 404 はゲート電極の他方として機能する。また、ゲート電極としての機能を有する導電体 404 のチャネル長方向の幅は、10 nm 以上 300 nm 以下、好ましくは、20 nm 以上 180 nm 以下とする。

20

#### 【0268】

言い換えると、導電体 310 及び導電体 404 の一方はゲート電極として機能でき、他方はバックゲート電極として機能できる。ゲート電極とバックゲート電極で半導体のチャネル形成領域を挟むように配置される。バックゲート電極の電位は、ゲート電極と同電位としてもよいし、接地電位や、任意の電位としてもよい。また、バックゲート電極の電位をゲート電極と連動させず独立して変化させることで、トランジスタのしきい値電圧を変化させることができる。

#### 【0269】

導電体 404a は、酸化物で導電性を有するものが好ましい。例えば、酸化物 406a、酸化物 406b または酸化物 406c として用いることができる金属酸化物を用いることができる。特に、In - Ga - Zn 系酸化物のうち、導電性が高い、金属の原子数比が [In] : [Ga] : [Zn] = 4 : 2 : 3 から 4.1、およびその近傍値のものを用いることが好ましい。このような導電体 404a を設けることで、導電体 404b 及び導電体 404c への酸素の透過を抑制し、導電体 404b 及び導電体 404c が酸化によって電気抵抗値が増加することを防ぐことができる。また、酸化物 406b に過剰酸素を供給することができる。

30

#### 【0270】

導電体 404b は、導電体 404a に窒素などの不純物を添加して導電体 404a の導電性を向上できる導電体が好ましい。例えば導電体 404b は、窒化チタンなどを用いることが好ましい。

40

#### 【0271】

ここで、ゲート電極の機能を有する導電体 404 が、絶縁体 412 及び酸化物 406c を介して、酸化物 406b の第 3 の領域近傍の上面及びチャネル幅方向の側面を覆うように設けられる。従って、ゲート電極としての機能を有する導電体 404 の電界によって、酸化物 406b の第 3 の領域近傍の上面及びチャネル幅方向の側面を電気的に取り囲むことができる。導電体 404 の電界によって、チャネル形成領域を電気的に取り囲むトランジスタの構造を、surrounded channel (s-channel) 構造とよぶ。そのため、酸化物 406b の第 3 の領域近傍の上面及びチャネル幅方向の側面にチャネルを形成することができるので、ソース - ドレイン間に大電流を流すことができ、導

50

通時の電流（オン電流）を大きくすることができる。また、酸化物 406b の第 3 の領域近傍の上面及びチャネル幅方向の側面が、導電体 404 の電界によって取り囲まれていることから、非導通時の電流（オフ電流）を小さくすることができる。

#### 【0272】

また、導電体 404 上にバリア膜 418 が設けられていることが好ましい。ここで、バリア膜 418 は、酸素が透過しにくい材料を用いることが好ましく、例えば酸化アルミニウムなどを用いることができる。これにより、導電体 404 の酸化に周囲の過剰酸素が用いられるのを防ぐことができる。このように、バリア膜 418 はゲートを保護するゲートキャップとしての機能を有する。なお、バリア膜 418 を設けない構成としてもよい。

#### 【0273】

##### [絶縁体]

トランジスタを、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体で囲うことによって、トランジスタの電気特性を安定にすることができる。例えば絶縁体 401、及び絶縁体 420 として、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体を用いればよい。また、絶縁体 303 に水素などの不純物および酸素の透過を抑制する機能を有する絶縁体を用いてもよい。絶縁体 401、絶縁体 303、及び絶縁体 420 は、絶縁体 402 などより、水または水素などの不純物が透過しにくい絶縁性材料を用いて形成することが好ましい。

#### 【0274】

水素などの不純物および酸素の透過を抑制する機能を有する絶縁体としては、例えば、酸化アルミニウム、酸化窒化アルミニウム、酸化マグネシウム、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルなどの金属酸化物、窒化酸化シリコン、窒化シリコンまたは窒化アルミニウムなどを単層で、または積層で用いればよい。

#### 【0275】

絶縁体 401 および絶縁体 420 が酸化アルミニウムを有することで、酸化物 406a、酸化物 406b および酸化物 406c に水素などの不純物が混入することを抑制することができる。また、例えば、絶縁体 401 および絶縁体 420 が酸化アルミニウムを有することで、上述の酸化物 406a、酸化物 406b および酸化物 406c へ添加された過剰酸素の外方拡散を低減することができる。

#### 【0276】

絶縁体 301、絶縁体 302、絶縁体 303、絶縁体 402 および絶縁体 412 としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、絶縁体 301、絶縁体 302、絶縁体 303、絶縁体 402 および絶縁体 412 としては、酸化シリコンまたは酸化窒化シリコンを有することが好ましい。

#### 【0277】

また、絶縁体 302、絶縁体 303、絶縁体 402 および絶縁体 412 は、ゲート絶縁膜として機能するので比誘電率の高い絶縁体を有することが好ましい。例えば、絶縁体 302、絶縁体 303、絶縁体 402 および絶縁体 412 は、酸化ガリウム、酸化ハフニウム、アルミニウムおよびハフニウムを有する酸化物、アルミニウムおよびハフニウムを有する酸化窒化物、シリコンおよびハフニウムを有する酸化物、またはシリコンおよびハフニウムを有する酸化窒化物などを有することが好ましい。または、絶縁体 302、絶縁体 303、絶縁体 402 および絶縁体 412 は、酸化シリコンまたは酸化窒化シリコンと、比誘電率の高い絶縁体と、の積層構造を有することが好ましい。酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため、比誘電率の高い絶縁体と組み合わせることで、熱的に安定かつ比誘電率の高い積層構造とすることができます。例えば、酸化アルミニウム、酸化ガリウムまたは酸化ハフニウムを酸化物 406c 側に有することで、酸化シリコンまたは酸化窒化シリコンに含まれるシリコンが、酸化物 406b に混入することを抑制す

10

20

30

40

50

ることができる。また、例えば、酸化シリコンまたは酸化窒化シリコンを酸化物 406c 側に有することで、酸化アルミニウム、酸化ガリウムまたは酸化ハフニウムと、酸化シリコンまたは酸化窒化シリコンとの界面にトラップセンターが形成される場合がある。該トラップセンターは、電子を捕獲することでトランジスタのしきい値電圧をプラス方向に変動させることができる場合がある。

【0278】

絶縁体 410 は、比誘電率の低い絶縁体を有することが好ましい。例えば、絶縁体 410 は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコンまたは樹脂などを有することが好ましい。または、絶縁体 410 は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコンまたは空孔を有する酸化シリコンと、樹脂との積層構造を有することが好ましい。酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため、樹脂と組み合わせることで、熱的に安定かつ比誘電率の低い積層構造とすることができます。樹脂としては、例えば、ポリエステル、ポリオレフィン、ポリアミド（ナイロン、アラミドなど）、ポリイミド、ポリカーボネートまたはアクリルなどがある。

【0279】

バリア膜 417a1 およびバリア膜 417a2 としては、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体を用いてもよい。バリア膜 417a1 およびバリア膜 417a2 によって、酸化物 406c 及び絶縁体 412 中の過剰酸素が、導電体 416a1 および導電体 416a2 へと拡散することを防止することができる。

【0280】

バリア膜 417a1 およびバリア膜 417a2 としては、例えば、酸化アルミニウム、酸化マグネシウム、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルなどの金属酸化物、窒化酸化シリコンまたは窒化シリコンなどを用いればよい。

【0281】

[導電体]

導電体 404、導電体 310、導電体 416a1、導電体 416a2、導電体 108a、導電体 108b としては、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タンクステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニウム、ベリリウム、インジウムなどから選ばれた金属元素を 1 種以上含む材料を用いることができる。また、リン等の不純物元素を含有させた多結晶シリコンに代表される、電気伝導度が高い半導体、ニッケルシリサイドなどのシリサイドを用いてもよい。

【0282】

また、前述した金属元素および酸素を含む導電性材料を用いてもよい。また、前述した金属元素および窒素を含む導電性材料を用いてもよい。例えば、窒化チタン、窒化タンタルなどの窒素を含む導電性材料を用いてもよい。また、インジウム錫酸化物 (ITO : I<sub>n</sub>dium T<sub>i</sub>n O<sub>x</sub>ide)、酸化タンクステンを含むインジウム酸化物、酸化タンクステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、シリコンを添加したインジウム錫酸化物を用いてもよい。また、窒素を含むインジウムガリウム亜鉛酸化物を用いてもよい。

【0283】

また、上記の材料で形成される導電層を複数積層して用いてもよい。例えば、前述した金属元素を含む材料と、酸素を含む導電性材料と、を組み合わせた積層構造としてもよい。また、前述した金属元素を含む材料と、窒素を含む導電性材料と、を組み合わせた積層構造としてもよい。また、前述した金属元素を含む材料と、酸素を含む導電性材料と、窒

10

20

30

40

50

素を含む導電性材料と、を組み合わせた積層構造としてもよい。

【0284】

なお、トランジスタのチャネル形成領域に酸化物を用いる場合は、ゲート電極として前述した金属元素を含む材料と、酸素を含む導電性材料と、を組み合わせた積層構造を用いることが好ましい。この場合は、酸素を含む導電性材料をチャネル形成領域側に設けるとよい。酸素を含む導電性材料をチャネル形成領域側に設けることで、当該導電性材料から離脱した酸素がチャネル形成領域に供給されやすくなる。

【0285】

例えば、導電体310bとしては、タングステン、ポリシリコン等の導電性材料を用いればよい。また、絶縁体401と接する導電体310aとしては、例えば、チタン、窒化チタン、または窒化タンタルなどのバリア層（拡散防止層）を積層または単層で用いることができる。

10

【0286】

絶縁体401に不純物が透過しにくい絶縁性材料を用い、絶縁体401と接する、導電体310aに不純物が透過しにくい導電性材料を用いることで、トランジスタへの不純物の拡散をさらに抑制することができる。よって、トランジスタの信頼性をさらに高めることができる。

【0287】

また、バリア膜417a1、417a2、およびバリア膜418として上記の不純物が透過しにくい導電性材料を用いてもよい。バリア膜417a1、417a2、およびバリア膜418に導電性材料を用いる場合は、酸素が放出されにくい、および／または吸収されにくい導電性材料を用いることが好ましい。

20

【0288】

<トランジスタの作製方法>

以下では、本発明の一態様に係る図20に示すトランジスタの作製方法を図21および図22を用いて説明する。図21および図22では、図20（B）に示す一点鎖線A1-A2の断面に対応する断面図と、図20（C）に示す一点鎖線A3-A4の断面に対応する断面図と、を示している。

【0289】

なお、以下において、絶縁体を形成するための絶縁性材料、導電体を形成するための導電性材料、酸化物半導体として機能する酸化物などは、スパッタリング法、スピンドル法、CVD法、ALD法、MBE法、または、PLD法などを適宜用いて形成することができる。

30

【0290】

まず、基板（図示せず）の上に絶縁体401、絶縁体301を順に成膜する。本実施の形態では、基板として単結晶シリコン基板（p型の半導体基板、またはn型の半導体基板を含む）を用いる。また、本実施の形態では、絶縁体401として、スパッタリング法を用いて酸化アルミニウム膜を成膜し、絶縁体301としてCVD法を用いて酸化窒化シリコン膜を成膜する。

【0291】

また、例えば、絶縁体401の上または下に積層して、ALD法を用いて酸化アルミニウム膜を成膜してもよい。

40

【0292】

次に、絶縁体301に絶縁体401に達する開口（溝、トレンチまたは穴などを含む。）を形成する。当該開口の形成はウェットエッチングを用いてもよいが、ドライエッチングを用いるほうが微細加工には好ましい。また、絶縁体401は、絶縁体301をエッチングして開口を形成する際のエッティングストップ膜として機能する絶縁体を選択することが好ましい。例えば、開口を形成する絶縁体301に酸化シリコンまたは酸化窒化シリコンを用いた場合は、絶縁体401は窒化シリコン、酸化アルミニウム、酸化ハフニウムなどを用いるとよい。このとき、絶縁体401の、絶縁体301の開口と重なる部分がエッ

50

チングによって凹状に形成される場合がある。

【0293】

次に、導電体310aとなる導電膜、および導電体310bとなる導電膜を成膜する。本実施の形態では、導電体310aとなる導電膜としてスパッタリング法で成膜した窒化タンタルとALD法で成膜した窒化チタンの積層膜を用いる。また、導電体310bとなる導電膜としてCVD法で成膜したタンゲステン膜を用いる。

【0294】

次に、CMP処理を行うことで、絶縁体301上の、導電体310aとなる導電膜、及び導電体310bとなる導電膜を除去する(図21(A)(B)参照)。その結果、開口のみに、導電体310a及び導電体310bが残存することで上面が平坦な導電体310を形成することができる。

10

【0295】

次に、絶縁体301上および導電体310上に絶縁体302を成膜する。本実施の形態では、絶縁体302として、CVD法を用いて酸化窒化シリコン膜を成膜する。

【0296】

次に、絶縁体302上に絶縁体303を成膜する。本実施の形態では、絶縁体303として、ALD法を用いて酸化ハフニウム膜を成膜する。

【0297】

次に、絶縁体303上に絶縁体402を成膜する。本実施の形態では、絶縁体402として、CVD法を用いて酸化窒化シリコン膜を成膜する。

20

【0298】

次に、第1の加熱処理を行うと好ましい。第1の加熱処理は、250以上650以下、好ましくは300以上500以下で行えばよい。また、本実施の形態に示すトランジスタの下層に銅を含んで形成された配線などを設ける場合、第1の加熱処理の温度を410以下にすることが好ましい。第1の加熱処理は、不活性ガス雰囲気で行う。第1の加熱処理は減圧状態で行ってもよい。第1の加熱処理によって、絶縁体402に含まれる水素や水などの不純物を除去することなどができる。本実施の形態では、第1の加熱処理として窒素ガス雰囲気で温度を400として加熱処理を行う。

【0299】

次に、絶縁体402の上に酸化物406aとなる酸化膜406Aを成膜し、酸化膜406Aの上に酸化物406bとなる酸化膜406Bを成膜する(図21(C)(D)参照)。

30

【0300】

酸化膜406A、及び酸化膜406Bは、スパッタリング法を用いて成膜することが好ましい。スパッタリング法で成膜することで酸化膜406A、及び酸化膜406Bの密度を高められるため、好適である。スパッタリングガスには、希ガス(代表的にはアルゴン)、酸素、または、希ガスおよび酸素の混合ガスを適宜用いればよい。また、スパッタリングガスに窒素を含めてもよい。また、基板を加熱しながら成膜を行ってもよい。

【0301】

スパッタリングガスは高純度化することが好ましい。例えば、スパッタリングガスとして用いる酸素ガスやアルゴンガスは、露点が-40以下、好ましくは-80以下、より好ましくは-100以下、より好ましくは-120以下にまで高純度化したガスを用いることで酸化膜406A、及び酸化膜406Bに水分等が取り込まれることを可能な限り防ぐことができる。

40

【0302】

また、スパッタリング装置におけるチャンバーは、酸化膜406A、及び酸化膜406Bにとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空( $5 \times 10^{-7}$ Paから $1 \times 10^{-4}$ Pa程度まで)排気することができる。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体、特に炭素または水素を含む気体が逆流しないようにしておくこ

50

とが好ましい。

【0303】

また、スパッタリング装置の電源には、DC電源、AC電源、またはRF電源を用いればよい。

【0304】