(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4625712号

(P4625712)

(45) 発行日 平成23年2月2日(2011.2.2)

(24) 登録日 平成22年11月12日(2010.11.12)

(51) Int.CI.

H04L 12/28 (2006.01)

F 1

H04L 12/28 2000Z

請求項の数 7 (全 10 頁)

(21) 出願番号 特願2005-117345 (P2005-117345)

(22) 出願日 平成17年4月14日 (2005.4.14)

(65) 公開番号 特開2006-295825 (P2006-295825A)

(43) 公開日 平成18年10月26日 (2006.10.26)

審査請求日 平成20年3月21日 (2008.3.21)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100094134

弁理士 小山 廣毅

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

最終頁に続く

(54) 【発明の名称】半導体集積回路及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

周辺機器のケーブル接続状況及び内部又は外部のCPUの動作状況に応じて動作モードを切り替える半導体集積回路であつて、

周辺機器のケーブルの信号を送受信する下位インターフェースと、

前記下位インターフェースと前記CPUとの間の通信を行う上位インターフェースとを備え、

前記下位インターフェースは、

少なくとも1本の周辺機器のケーブルが挿されたとき、第1の信号を第1の論理レベルに変化させる一方、すべての周辺機器のケーブルが抜かれたとき、前記第1の信号を第2の論理レベルに変化させる挿抜検出回路と、

前記第1の信号の論理レベルが変化してから所定時間後に、前記第1の信号が前記第1の論理レベルのとき、第2の信号を第1の論理レベルに設定する一方、前記第1の信号が前記第2の論理レベルのとき、前記第2の信号を第2の論理レベルに設定する検出確定回路とを有するものであり、

前記第2の信号が前記第2の論理レベルのとき、前記挿抜検出回路のみが動作する第1のモードで動作し、前記第2の信号が前記第1の論理レベルであり、かつ、前記CPUが休止状態であるとき、前記下位インターフェースのみが動作する第2のモードで動作し、前記第2の信号が前記第1の論理レベルであり、かつ、前記CPUが動作状態であるとき、前記下位インターフェース及び前記上位インターフェースのいずれもが動作する第3のモード

10

20

で動作する

ことを特徴とする半導体集積回路。

【請求項 2】

請求項 1 に記載の半導体集積回路において、

前記検出確定回路は、

前記第 1 の信号の論理レベルが変化したとき、与えられたクロック信号のパルスカウントを開始し、当該パルスカウント値が所定値となったとき、当該パルスカウントを停止し、かつ、このときの前記第 1 の信号の論理レベルに応じて前記第 2 の信号の論理レベルを設定するカウンタ回路と、

前記第 1 の信号の論理レベルが変化したとき、前記クロック信号の生成を開始し、前記パルスカウントが停止したときであって前記第 1 の信号が前記第 1 の論理レベルのとき又は前記第 2 の信号が前記第 2 の論理レベルのとき、前記クロック信号の生成を停止するクロック生成回路とを有するものであり、

前記下位インターフェースは、前記第 2 の信号が前記第 1 の論理レベルであり、かつ、前記 C P U が動作状態であるとき、前記クロック信号を前記上位インターフェースに供給するものであり、

前記上位インターフェースは、前記クロック信号の供給により動作するものであることを特徴とする半導体集積回路。

【請求項 3】

請求項 1 に記載の半導体集積回路において、

前記第 2 のモードの有効及び無効のいずれかを選択するモード選択部を備えたことを特徴とする半導体集積回路。

【請求項 4】

請求項 1 に記載の半導体集積回路において、

前記周辺機器との通信は、I E E E 1 3 9 4 規格に準拠したものであり、

前記下位インターフェースは、物理層であることを特徴とする半導体集積回路。

【請求項 5】

請求項 1 に記載の半導体集積回路において、

前記周辺機器との通信は、H D M I 規格に準拠したものであり、

前記下位インターフェースは、物理層であることを特徴とする半導体集積回路。

【請求項 6】

ケーブルの接続状態を検出する半導体集積回路であって、

少なくとも 1 本のケーブルが挿されたとき、第 1 の信号を第 1 の論理レベルに変化させる一方、すべてのケーブルが抜かれたとき、前記第 1 の信号を第 2 の論理レベルに変化させる挿抜検出回路と、

前記第 1 の信号の論理レベルが変化したとき、与えられたクロック信号のパルスカウントを開始し、当該パルスカウント値が所定値となったとき、当該パルスカウントを停止し、かつ、このときの前記第 1 の信号の論理レベルに応じて第 2 の信号の論理レベルを設定するカウンタ回路と、

前記第 1 の信号の論理レベルが変化したとき、前記クロック信号の生成を開始し、前記パルスカウントが停止したときであって前記第 1 の信号が前記第 2 の論理レベルのとき又は前記第 2 の信号が所定の論理レベルのとき、前記クロック信号の生成を停止するクロック生成回路とを備え、

前記第 2 の信号をケーブル接続検出信号として出力することを特徴とする半導体集積回路。

【請求項 7】

請求項 1 に記載の半導体集積回路を備え、

前記半導体集積回路の動作モードをユーザーインターフェースに表示する

10

20

30

40

50

ことを特徴とする電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路及び電子機器に関し、特に、ケーブルの接続状況及びCPUの動作状況に応じた半導体集積回路及び電子機器の電力制御技術に属する。

【背景技術】

【0002】

I E E E (Institute of Electrical and Electronic Engineers) 1394 や H D M I (High-Definition Multimedia interface) などのインタフェース規格は、機器動作中にケーブルの挿抜が可能なわゆるホットプラグに対応している。このため、これらインタフェース規格に準拠したシステムは、ケーブルの挿抜を検出する挿抜検出回路を備えている。

【0003】

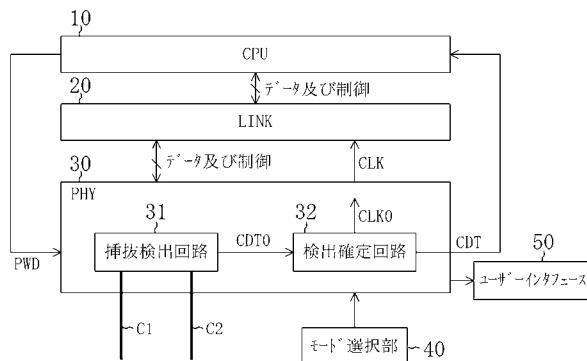

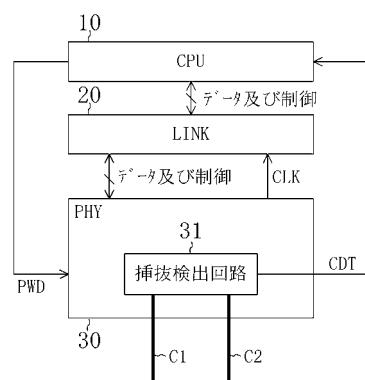

図6は、従来のI E E E 1394 インタフェース機器の構成を示す。これまで、CPU 10、リンク層 (LINK) 20 及び物理層 (PHY) 30 は、それぞれ、個別のチップで実現されていたが、近年、PHY 30 及びLINK 20 を1チップに実装した半導体集積回路が登場している。

【0004】

PHY 30 における挿抜検出回路31は、PHY 30 がパワーダウンモード中であっても、ある周辺機器のケーブルC1や別の周辺機器のケーブルC2が接続されたことを検出可能なように給電されている（例えば、特許文献1参照）。挿抜検出回路31によってケーブル接続が検出されたとき、信号CDTの論理レベルが変化する。CPU 10 は、この論理レベルの変化に基づいてケーブル接続を検知し、PHY 30 の復帰制御を行う。具体的には、CPU 10 は、信号PWDによりPHY 30 に動作の開始を指示する。動作を開始したPHY 30 は、クロック信号CLKを生成し、パワーダウンモード中のLINK 20 に供給する。LINK 20 は、クロック信号CLKの供給により動作を開始する（例えば、特許文献2参照）。

【0005】

上述のI E E E 1394 インタフェースでは、ケーブル未接続時に動作不要なPHY 30 及びLINK 20 についてパワーダウン制御することによって消費電力の低減を図ることができる。しかし、CPU 10 はケーブルの接続状態を検知するために動作している必要がある。これは、CPU 10 までもがパワーダウンしてしまうと、挿抜検出回路31によってケーブル接続が検出されてもPHY 30 の復帰制御ができなくなり、ケーブルC1及びC2が接続されている場合に周辺機器間でデータ転送の中継（リピーター動作）ができなくなるからである。このように、上述のI E E E 1394 インタフェースでは、PHY 30 のリピーターとしての機能を有効にしつつインターフェース機器全体としてのさらなる低消費電力化を図ることは困難である。

【0006】

一方、CPU 10 の動作状態にかかわらず、挿抜検出回路31によるケーブル接続の検出によって、パワーダウン中のPHY 30 を復帰制御することも可能である。これによると、CPU 10 がパワーダウンしていても、ケーブルC1及びC2が接続されるとパワーダウン中のPHY 30 が復帰し、リピーターとして機能する（例えば、特許文献3参照）。

【特許文献1】特開平11 45130号公報（第5～6頁、第1図）

【特許文献2】特開平10 341248号公報（第4頁、第1図）

【特許文献3】特開2001 42975号公報（第4頁、第2図）

【発明の開示】

【発明が解決しようとする課題】

【0007】

10

20

30

40

50

一般に、ケーブルの挿抜の際、数 ms ~ 数 10 ms の期間でケーブル接続状態及び切断状態が交互に繰り返されるいわゆるチャタリングが発生する。このため、ケーブル接続検出信号(信号 CDT)にはチャタリングに起因するノイズが重畠される。このようなノイズを含むケーブル接続信号をインターフェース機器の制御に使用することは誤動作の原因となるため好ましくない。したがって、ケーブル接続検出信号からチャタリングに起因するノイズを除去する必要がある。

#### 【0008】

また、上述したように、CPU10がパワーダウン中にPHY30をリピーターとして動作させる場合であっても、PHY30が復帰することによってクロック信号CLKがLINK20に供給され、LINK20も復帰してしまう。リピーター動作は、PHY30のみが動作すれば可能であるため、インターフェース機器全体としての低消費電力化の観点から、LINK20はパワーダウンのままにしておくことが好ましい。

10

#### 【0009】

上記問題に鑑み、本発明は、IEEE1394やHDMIなどの、いわゆるホットプラグに対応し、かつ、CPUの介在無しに周辺機器間のデータ転送が可能な通信インターフェース規格に準拠した半導体集積回路の低消費電力化を課題とする。

#### 【課題を解決するための手段】

#### 【0010】

上記課題を解決するために本発明が講じた手段は、周辺機器のケーブル接続状況及び内部又は外部のCPUの動作状況に応じて動作モードを切り替える半導体集積回路として、周辺機器のケーブルの信号を送受信する下位インターフェースと、この下位インターフェースとCPUとの間の通信を行う上位インターフェースとを備えたものとする。ここで、下位インターフェースは、少なくとも1本の周辺機器のケーブルが挿されたとき、第1の信号を第1の論理レベルに変化させる一方、すべての周辺機器のケーブルが抜かれたとき、第1の信号を第2の論理レベルに変化させる挿抜検出回路と、第1の信号の論理レベルが変化してから所定時間後に、第1の信号が第1の論理レベルのとき、第2の信号を第1の論理レベルに設定する一方、第1の信号が第2の論理レベルのとき、第2の信号を第2の論理レベルに設定する検出確定回路とを有するものとする。そして、上記の半導体集積回路は、第2の信号が第2の論理レベルのとき、挿抜検出回路のみが動作する第1のモードで動作し、第2の信号が第1の論理レベルであり、かつ、CPUが休止状態であるとき、下位インターフェースのみが動作する第2のモードで動作し、第2の信号が第1の論理レベルであり、かつ、CPUが動作状態であるとき、下位インターフェース及び上位インターフェースのいずれもが動作する第3のモードで動作するものとする。

20

#### 【0011】

この発明によると、挿抜検出回路によってケーブルの挿抜が検出され、検出確定回路によって所定時間後の第1の信号の論理レベルに応じて第2の信号の論理レベルが設定される。これにより、ケーブルの挿抜の際に発生するチャタリングが収束した後にケーブルの接続の有無を確定することができ、ケーブル接続検出信号としての第2の信号はチャタリングに起因するノイズを含まない。そして、本発明に係る半導体集積回路の動作モードは、この第2の信号の論理レベル及びCPUの動作状態に応じて、挿抜検出回路のみ動作する第1のモード、下位インターフェースのみ動作する第2のモード、及び、下位インターフェース及び上位インターフェースのいずれもが動作する第3のモードに切り替わる。特に、第2のモードでは、リピーターとして動作を確保しつつ半導体集積回路全体としての低消費電力化が可能となる。

30

#### 【0012】

具体的には、検出確定回路は、第1の信号の論理レベルが変化したとき、与えられたクロック信号のパルスカウントを開始し、このパルスカウント値が所定値となったとき、このパルスカウントを停止し、かつ、このときの第1の信号の論理レベルに応じて第2の信号の論理レベルを設定するカウンタ回路と、第1の信号の論理レベルが変化したとき、上記のクロック信号の生成を開始し、パルスカウントが停止したときであって第1の信号が

40

50

第1の論理レベルのとき又は第2の信号が第2の論理レベルのとき、上記のクロック信号の生成を停止するクロック生成回路とを有する。また、下位インターフェースは、第2の信号が第1の論理レベルであり、かつ、CPUが動作状態であるとき、クロック信号を前記上位インターフェースに供給する。そして、上位インターフェースは、上記のクロック信号の供給により動作する。

【0013】

好ましくは、上記の半導体集積回路は、第2のモードの有効及び無効のいずれかを選択するモード選択部を備えたものとする。

【0014】

具体的には、上記の半導体集積回路において、周辺機器との通信は、IIEEE1394 10規格又はHDMI規格に準拠したものであり、下位インターフェースは、物理層である。

【0015】

また、本発明が講じた手段は、電子機器として、上記の半導体集積回路を備え、その動作モードをユーザーインターフェースに表示するものとする。

【発明の効果】

【0016】

本発明によると、いわゆるホットプラグに対応し、かつ、CPUの介在無しに周辺機器間のデータ転送が可能な通信インターフェース規格に準拠した半導体集積回路に、リピーター動作のために必要最小限の部分のみが動作する動作モードが追加され、半導体集積回路全体としての低消費電力化が可能となる。

【発明を実施するための最良の形態】

【0017】

以下、本発明を実施するための最良の形態について、図面を参照しながら説明する。図1は、本発明の一実施形態に係る半導体集積回路の構成を示す。本実施形態に係る半導体集積回路は、例えば、IIEEE1394 規格に準拠したデータ通信を行うものであり、下位インターフェースとしてPHY30、上位インターフェースとしてLINK20、及びモード選択部40を備えている。CPU10は、本半導体集積回路の内部及び外部のいずれにあってもよい。なお、ここでいう上位インターフェースとは、周辺機器とCPU10との間のインターフェースのうち下位インターフェース以外の部分を指しており、リンク層(LINK20)のみならず、トランザクション層や、IEC61883、MPEG処理やSBP2などのアプリケーション層をも含むものである。

【0018】

PHY30は、挿抜検出回路31及び検出確定回路32を備えている。挿抜検出回路31は、各周辺機器のケーブルC1及びC2の接続/切断を検出し、ケーブル接続状態に応じて信号CDT0の論理レベルを決定する。具体的には、信号CDT0は、ケーブルが未接続の状態ではLoレベルであり、ケーブルが接続された状態ではHiレベルとなる。すなわち、信号CDT0は、少なくとも1本のケーブルが接続されたとき、Hiレベルに設定され、すべてのケーブルが切断されたとき、Loレベルに設定される。

【0019】

上述したように、信号CDT0にはチャタリングに起因するノイズが含まれている。検出確定回路32は、信号CDT0に含まれるチャタリングに起因するノイズを除去し、ケーブル接続検出信号として信号CDTを出力する。すなわち、検出確定回路32は、ケーブルの接続又は切断に伴うチャタリングが収束するのに十分な時間が経過した後、そのときの信号CDT0をケーブル接続検出信号として確定し、このケーブル接続検出信号として信号CDTを出力する。

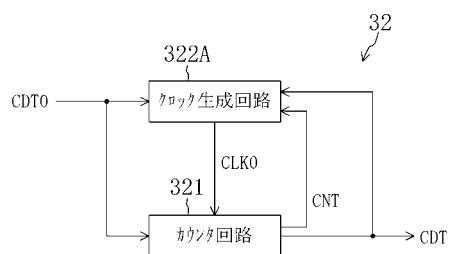

【0020】

図2は、一実施形態に係る検出確定回路32の構成を示す。カウンタ回路321は、ケーブルが接続又は切断されたことによる信号CDT0の論理レベルの変化から、クロック生成回路322Aによって生成されたクロック信号CLK0のパルスカウントを開始し、パルスカウント値が所定値となったとき、パルスカウントを停止する。そして、パルスカ

10

20

30

40

50

ウントを停止した信号 CDT0 の論理レベルが Hi レベルのとき、信号 CDT を Hi レベルに設定し、信号 CDT0 の論理レベルが Lo レベルのとき、信号 CDT を Lo レベルに設定する。なお、カウンタ回路 321 は、パルスカウントを行っている間、信号 CNT を Hi レベルに設定する。

【0021】

クロック生成回路 322A は、信号 CDT0 の論理レベルが変化したとき、クロック信号 CLK0 の生成を開始する。そして、カウンタ回路 321 によるパルスカウントが停止したとき、信号 CDT を参照して、信号 CDT が Hi レベルであれば、クロック信号 CLK0 の生成を継続する。一方、信号 CDT が Lo レベルであれば、クロック信号 CLK0 の生成を停止する。すなわち、確定したケーブル接続検出信号に基づいて、クロック信号 CLK0 の生成を継続するか否かが決定される。10

【0022】

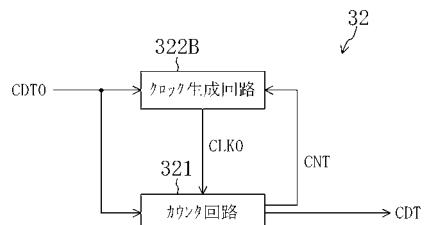

図 3 は、別の実施形態に係る検出確定回路 32 の構成を示す。カウンタ回路 321 は上記の通りである。一方、クロック生成回路 322B は、カウンタ回路 321 によるパルスカウントが停止したとき、信号 CDT0 を参照して、信号 CDT0 が Hi レベルであれば、クロック信号 CLK0 の生成を継続する。一方、信号 CDT0 が Lo レベルであれば、クロック信号 CLK0 の生成を停止する。

【0023】

上記のクロック信号 CLK0 は、カウンタ回路 321 によってパルスカウントされるだけではなく、PHY30 及び LINK20 の動作の基ともなる。図 1 に戻り、PHY30 は、クロック信号 CLK0 の供給により動作する。すなわち、少なくとも 1 本のケーブルが接続されると、パワーダウン中の PHY30 は復帰する。もちろん、従来と同様に、CPU10 からの信号 PWD による復帰制御も可能である。20

【0024】

なお、クロック信号 CLK0 が生成されると直ちに PHY30 を復帰させるのではなく、さらに、信号 CDT が Hi レベルであるという条件を加えて、PHY30 を復帰させるようにしてもよい。これにより、チャタリングが発生している不安定な期間における PHY30 の復帰制御が抑止され、より安定した復帰制御が可能となる。

【0025】

PHY30 は、さらに、信号 CDT が Hi レベルであり、かつ、CPU10 が動作状態であるとき、クロック信号 CLK としてクロック信号 CLK0 を LINK20 に供給する。LINK20 は、クロック信号 CLK の供給によりパワーダウン状態から復帰する。換言すると、CPU10 が休止状態であるとき、ケーブル接続によって PHY30 は動作するが、LINK20 にクロック信号 CLK が供給されないため、LINK20 は引き続きパワーダウンしたままとなる。30

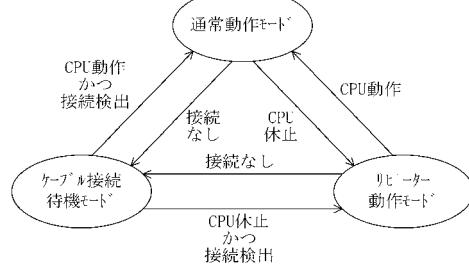

【0026】

以上のように、本実施形態に係る半導体集積回路は、信号 CDT が Lo レベルのとき、挿抜検出回路 31 のみが動作するケーブル接続待機モード（待機モードとも称する。）で動作し、信号 CDT が Hi レベルであり、かつ、CPU10 が休止状態であるとき、PHY30 のみが動作するリピーター動作モード（リピーターモードとも称する。）で動作し、信号 CDT が Hi レベルであり、かつ、CPU10 が動作状態であるとき、PHY30 及び LINK20 のいずれもが動作する通常動作モード（通常モードとも称する。）で動作する。図 4 は、これら動作モードの遷移図である。ケーブルが未接続の場合、本半導体集積回路は待機モードで動作している。そして、少なくとも 1 本のケーブルが接続されたとき、CPU10 が動作していれば通常モードに遷移し、休止していればリピーターモードに遷移する。40

【0027】

リピーターモードでは、PHY30 のみ動作しており、接続された周辺機器間のデータ転送の中継が可能であるとともに、LINK20 がパワーダウンしていることにより半導体集積回路全体としての消費電力が低減される。リピーターモード中に CPU10 が動作50

を開始すると、本半導体集積回路は通常モードに遷移する。このときに初めてパワーダウン中のLINK20が復帰する。これにより、接続された周辺機器とCPU10との間の通信が可能となる。一方、リピーターモード中にすべての周辺機器のケーブルが切断されると、本半導体集積回路は待機モードに遷移する。

#### 【0028】

通常モードでは、CPU10、LINK20及びPHY30のすべてが動作しており、接続された周辺機器間のデータ転送の中継が可能であるだけではなく、CPU10と各周辺機器との間の通信も可能である。通常モード中にCPU10がパワーダウン状態となると、本半導体集積回路はリピーターモードに遷移する。このとき、LINK20はパワーダウンするが、周辺機器とCPU10との間の通信はもはや行われないため特に問題はない。一方、通常モード中にすべての周辺機器のケーブルが切断されると、本半導体集積回路は待機モードに遷移する。

#### 【0029】

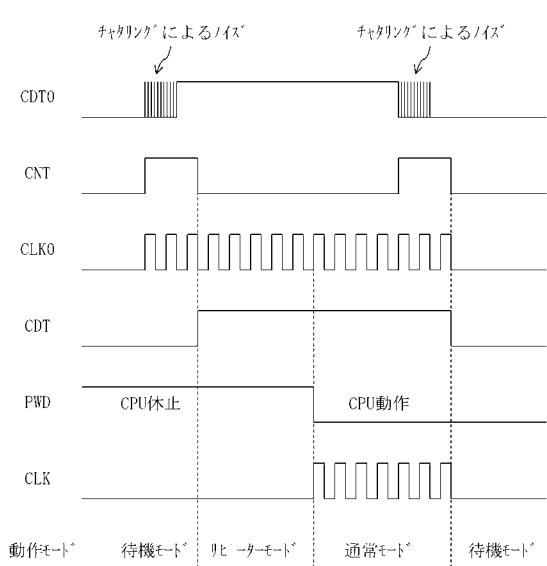

次に、上記各信号の変化と動作モードの遷移について、図5のタイミングチャートを参照しながら説明する。待機モード中にケーブルが接続されたとき、信号CDT0はHiレベルに変化する。信号CDT0がHiレベルに変化することによって、クロック信号CLK0の生成が開始されるとともに、パルスカウントが開始され、信号CNTはHiレベルとなる。所定数のパルスをカウントしてパルスカウントが停止すると、信号CNTはLoレベルとなる。このとき、信号CDT0は、チャタリングによるノイズが十分に収束した状態となっており、信号CDTは、このときの信号CDT0の論理レベルに基づいてHiレベルとなる。また、このとき、信号CDTがHiレベルである（又は信号CDT0がHiレベルである）ことから、クロック信号CLK0の生成は継続される。

#### 【0030】

図5の例では、信号CDTがHiレベルとなったとき、信号PWDはHiレベルであり、CPUは休止状態にある。したがって、クロック信号CLKは出力されず、リピーターモードに遷移する。そして、CPUが動作状態となり、信号PWDがLoレベルに変化する。これにより、クロック信号CLKの出力が開始され、通常モードに遷移する。

#### 【0031】

ケーブルが切断されたとき、信号CDT0はLoレベルに変化する。信号CDT0がLoレベルに変化することによって、クロック信号CLK0のパルスカウントが開始され、信号CNTはHiレベルとなる。所定数のパルスをカウントしてパルスカウントが停止すると、信号CNTはLoレベルとなる。このとき、信号CDT0は、チャタリングによるノイズが十分に収束した状態となっており、信号CDTは、このときの信号CDT0の論理レベルに基づいてHiレベルとなる。また、このとき、信号CDTがLoレベルである（又は信号CDT0がLoレベルである）ことから、クロック信号CLK0の生成停止によって、クロック信号CLKも出力されなくなり、再び待機モードに遷移する。

#### 【0032】

図1に戻り、モード選択部40は、リピーターモードを有効にするか又は無効にするかのいずれかを選択する。モード選択部40は、例えば、半導体集積回路の入力端子であり、この入力端子のオン／オフによりリピーターモードの有効／無効が静的に切り替わる。リピーターモードを無効にしたとき、本半導体集積回路は従来と同様のものとなる。これにより、現行製品と同等な機能を要望するセットカスタマ（LSI使用者）は、設計変更などをしてことなく、本実施形態に係る半導体記憶装置を用いることができる。また、モード選択部40は、リピーターモードの有効／無効を動的に切り替えるようにしてよい。これにより、例えば、本半導体集積回路を備えた電子機器が内部バッテリーで動作しているときにはリピーターモードを有効にし、CPU10がパワーダウンしているときにはLINK20もパワーダウンさせて消費電力を抑制する一方、商用電源で動作しているときには、CPU10の動作に連動してLINK20を動作させることができる。

#### 【0033】

10

20

30

40

50

ユーザーインターフェース 50 は、本実施形態に係る半導体集積回路を備えた電子機器の一部であり、本半導体集積回路の動作モードを表示する。これにより、ユーザーは、電子機器が現在どの動作モードで動作しているのかを知ることができる。

【0034】

なお、本発明に係る半導体集積回路はHDMIインターフェースについても上記と同様の効果を奏する。また、本発明は、イーサネット（登録商標）に係るルータ装置やスイッチングハブ装置にも適用可能である。ルータ装置の場合、OSI参照モデルにおける物理層、データリンク層及びネットワーク層が下位インターフェースに相当し、スイッチングハブ装置の場合、物理層及びデータリンク層が下位インターフェースに相当する。

【産業上の利用可能性】

10

【0035】

本発明に係る半導体集積回路は、比較的少ない消費電力でリピーターとして動作するため、IEEE1394又はHDMIなどのインターフェースを有する周辺機器が複数接続される電子機器、例えば、デジタルテレビジョン装置などに有用である。

【図面の簡単な説明】

【0036】

【図1】本発明の一実施形態に係る半導体集積回路の構成図である。

【図2】一実施形態に係る検出確定回路の構成図である。

【図3】別の実施形態に係る検出確定回路の構成図である。

【図4】本発明に係る半導体集積回路における動作モードの遷移図である。

20

【図5】本発明の一実施形態に係る半導体集積回路のタイミングチャートである。

【図6】従来のIEEE1394インターフェースの構成図である。

【符号の説明】

【0037】

10 C P U

20 リンク層（上位インターフェース）

30 物理層（下位インターフェース）

31 挿抜検出回路

32 検出確定回路

40 モード選択部

30

50 ユーザーインターフェース

321 カウンタ回路

322A, 322B クロック生成回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(74)代理人 100115691

弁理士 藤田 篤史

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(72)発明者 田平 由弘

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 高橋 学志

大阪府門真市大字門真1006番地 松下電器産業株式会社内

審査官 福岡 裕貴

(56)参考文献 特開2003-44184 (JP, A)

特開2001-24675 (JP, A)

特開2001-42975 (JP, A)

特開平10-341248 (JP, A)

特開平11-45130 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04L 12/28-12/46