(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6465792号

(P6465792)

(45) 発行日 平成31年2月6日(2019.2.6)

(24) 登録日 平成31年1月18日(2019.1.18)

(51) Int.Cl.

F 1

H03K 17/06 (2006.01)

H03K 17/06

O 6 3

H03K 17/687 (2006.01)

H03K 17/687

A

H03K 19/0185 (2006.01)

H03K 19/0185

2 1 O

請求項の数 21 (全 14 頁)

(21) 出願番号 特願2015-504676 (P2015-504676)

(86) (22) 出願日 平成25年4月2日 (2013.4.2)

(65) 公表番号 特表2015-520537 (P2015-520537A)

(43) 公表日 平成27年7月16日 (2015.7.16)

(86) 國際出願番号 PCT/US2013/034949

(87) 國際公開番号 WO2013/151998

(87) 國際公開日 平成25年10月10日 (2013.10.10)

審査請求日 平成28年3月31日 (2016.3.31)

(31) 優先権主張番号 13/438,927

(32) 優先日 平成24年4月4日 (2012.4.4)

(33) 優先権主張国 米国(US)

(73) 特許権者 592054856

クリー インコーポレイテッド

C R E E I N C.

アメリカ合衆国 ノースカロライナ州 2

7703 ダラム シリコン ドライブ

4600

(74) 代理人 110000578

名古屋国際特許業務法人

(72) 発明者 キャラナン ロバート ジェイ.

アメリカ合衆国 ノースカロライナ州 2

7612 ローリー ベネットウッドコート 5629

審査官 小林 正明

最終頁に続く

(54) 【発明の名称】高電圧ドライバ

## (57) 【特許請求の範囲】

## 【請求項 1】

低電圧入力信号に直流バイアスをかけて直流バイアス信号を供給するように構成されたソースバイアス回路と、

P型電界効果トランジスタであって、

前記直流バイアス信号を受信するように構成された第1ソースと、

第1低電圧源から第1低電圧直流電源信号を受信するように構成された第1ゲートと、

前記直流バイアス信号と前記第1低電圧直流電源信号とに基づいて、高電圧出力部を介して、高電圧出力信号を供給するように構成された第1ドレインと

を備え、

前記ソースバイアス回路は、

前記低電圧入力部と前記第1ソースとの間に接続され、前記低電圧入力信号を受信するように構成された第1容量素子と、

アノードとカソードとを有する第1ダイオード素子であって、前記カソードは、前記第1ソースに接続され、前記アノードは、前記第1ゲートに接続され、前記第1低電圧直流電源信号を受信及び整流するように構成された第1ダイオード素子と

を備え、

前記ソースバイアス回路と前記P型電界効果トランジスタとは、前記低電圧入力信号を受信及び変換して前記高電圧出力信号を供給するように構成された高電圧ドライバを形成している、P型電界効果トランジスタと、

10

20

N型電界効果トランジスタであって、

前記低電圧入力部に接続された第2ソースと、

前記第1低電圧源とは別の第2低電圧源から第2低電圧直流電源信号を受信するように構成された第2ゲートと、

前記高電圧出力部に接続された第2ドレインと

を備える、N型電界効果トランジスタと

を備える、回路。

**【請求項2】**

請求項1に記載の回路であって、

前記第1低電圧源は、さらに、前記低電圧入力信号を変換して前記高電圧出力信号を供給するためのエネルギーを供給するように構成されている、回路。 10

**【請求項3】**

請求項1に記載の回路であって、

前記ソースバイアス回路は、さらに、低電圧入力部を介して前記低電圧入力信号を受信するように構成され、

前記第1ドレインは、さらに、前記高電圧出力信号を前記高電圧出力部を介して供給するように構成されている、回路。

**【請求項4】**

請求項1に記載の回路であって、

前記第1容量素子及び前記第1ダイオード素子は、さらに、前記低電圧入力信号と前記第1低電圧直流電源信号とに基づいて前記直流バイアス信号を供給するように構成されている、回路。 20

**【請求項5】**

請求項1に記載の回路であって、

前記第2低電圧源は、前記第1低電圧直流電源信号を受信し、前記第2低電圧直流電源信号が前記第1低電圧直流電源信号に基づいているようにさらに構成されている、回路。

**【請求項6】**

請求項1に記載の回路であって、

前記第1低電圧直流電源信号の電圧は、前記第2低電圧直流電源信号の電圧の2倍にほぼ等しい、回路。 30

**【請求項7】**

請求項1に記載の回路であって、

前記高電圧ドライバは、さらに、前記P型電界効果トランジスタをオフ状態からオン状態に移行させる前に、前記N型電界効果トランジスタをオン状態からオフ状態に移行させるように構成されている、回路。

**【請求項8】**

請求項1に記載の回路であって、

前記第1ソースと前記第1ドレインとの間の最大電圧は、前記第1低電圧直流電源信号の電圧以下である、回路。

**【請求項9】**

請求項8に記載の回路であって、

前記第1ゲートと前記第1ドレインとの間の最大電圧は、前記第1低電圧直流電源信号の電圧以下である、回路。 40

**【請求項10】**

請求項1に記載の回路であって、

前記高電圧出力信号の電圧振幅は、前記低電圧入力信号の電圧振幅よりも大きい、回路。

。

**【請求項11】**

請求項10に記載の回路であって、

前記高電圧出力信号の前記電圧振幅は、前記低電圧入力信号の前記電圧振幅の約2倍の 50

大きさである、回路。

**【請求項 1 2】**

請求項1 1に記載の回路であって、

前記高電圧出力信号の前記電圧振幅は、約 6 ボルトに等しく、

前記低電圧入力信号の前記電圧振幅は、約 3 . 3 ボルトに等しい、回路。

**【請求項 1 3】**

請求項1 1に記載の回路であって、

前記高電圧出力信号の前記電圧振幅は、約 19 . 4 ボルトに等しく、

前記低電圧入力信号の前記電圧振幅は、約 10 ボルトに等しい、回路。

**【請求項 1 4】**

請求項 1 に記載の回路であって、

低電圧論理ドライバは、前記低電圧入力信号を供給するように構成されている、回路。

**【請求項 1 5】**

請求項1 4に記載の回路であって、

さらに、

前記低電圧論理ドライバを備えている、回路。

**【請求項 1 6】**

請求項 1 に記載の回路であって、

高ゲート駆動電圧電界効果トランジスタのゲートは、前記高電圧出力信号を受信するよう構成されている、回路。

**【請求項 1 7】**

請求項1 6に記載の回路であって、

さらに、

前記高ゲート駆動電圧電界効果トランジスタを備えている、回路。

**【請求項 1 8】**

請求項1 6に記載の回路であって、

前記高ゲート駆動電圧電界効果トランジスタは、炭化ケイ素製の電界効果トランジスタである、回路。

**【請求項 1 9】**

低電圧入力部を有する高電圧ドライバであって、第 1 ソースと、第 1 低電圧直流電源に接続された第 1 ゲートと、前記高電圧ドライバの高電圧出力部に接続された第 1 ドレインとを備える P 型電界効果トランジスタと、前記低電圧入力部に接続された第 2 ソースと、前記第 1 低電圧直流電源とは別の第 2 低電圧直流電源から第 2 低電圧直流電源信号を受信するよう構成された第 2 ゲートと、前記高電圧出力部に接続された第 2 ドレインとを備える N 型電界効果トランジスタと、前記低電圧入力部と前記第 1 ソースとの間に接続されたソースバイアス回路であって、前記低電圧入力部と前記第 1 ソースとの間に接続され、前記低電圧入力部から低電圧入力信号を受信するよう構成された容量素子と、アノードとカソードとを有するダイオード素子であって、前記カソードは、前記第 1 ソースに接続され、前記アノードは、前記第 1 ゲートに接続され、前記第 1 低電圧直流電源から第 1 低電圧直流電源信号を受信及び整流するよう構成されたダイオード素子とを備える、ソースバイアス回路とを備える、高電圧ドライバと、

前記低電圧入力部に接続された低電圧論理ドライバと

を備え、

前記高電圧出力部の電圧振幅能力は、前記低電圧入力部の電圧振幅能力よりも高い、回路。

**【請求項 2 0】**

高ゲート駆動電圧電界効果トランジスタと、

低電圧入力部を有する高電圧ドライバであって、第 1 ソースと、第 1 低電圧直流電源に接続され、低電圧直流電源信号を受信するよう構成されている第 1 ゲートと、前記高電圧ドライバの高電圧出力部を介して前記高ゲート駆動電圧電界効果トランジスタのゲート

10

20

30

40

50

に接続された第1ドレインとを備え、前記低電圧直流電源信号に基づいて高電圧出力信号を供給するように構成されたP型電界効果トランジスタと、前記低電圧入力部に接続された第2ソースと、前記第1低電圧直流電源とは別の第2低電圧直流電源から第2低電圧直流電源信号を受信するように構成された第2ゲートと、前記高電圧出力部に接続された第2ドレインとを備えるN型電界効果トランジスタと、前記低電圧入力部と前記第1ソースとの間に接続されたソースバイアス回路であって、前記低電圧入力部と前記第1ソースとの間に接続され、前記低電圧入力部から低電圧入力信号を受信するように構成された容量素子と、アノードとカソードとを有するダイオード素子であって、前記カソードは、前記第1ソースに接続され、前記アノードは、前記第1ゲートに接続され、前記第1低電圧直流電源から前記低電圧直流電源信号を受信及び整流するように構成されたダイオード素子とを備える、ソースバイアス回路とを備える、高電圧ドライバと

を備え、

10

前記高電圧出力部の電圧振幅能力は、前記低電圧入力部の電圧振幅能力よりも高い、回路。

#### 【請求項 21】

請求項20に記載の回路であって、

前記高ゲート駆動電圧電界効果トランジスタは、炭化ケイ素製の電界効果トランジスタである、回路。

#### 【発明の詳細な説明】

##### 【発明の詳細な説明】

20

##### 【0001】

##### 【開示分野】

本開示の実施形態は、デジタル回路、及び例えばドライバ等の特定のデジタル回路で用いられる高電圧電界効果トランジスタ及び低電圧電界効果トランジスタに関する。

##### 【背景】

電界効果トランジスタ(FET)は、電界を利用して、半導体材料内のチャネルの導電性を制御するトランジスタである。チャネルがアクティブチャネルである場合、多数電荷キャリアである電子または正孔がFETのソースからFETのドレインへとチャネルを通って流れる。チャネルの導電性は、FETのゲートとソースとの間に印加された電位の関数となる。この点において、エンハンスマントモードのみのFETでは、ゲートとソースとの間の電圧がFETのしきい電圧を超えると、多数電荷キャリアがドレインからソースへと流れることが可能になるような低抵抗のチャネルが確立される。反対に、ゲートとソースとの間の電圧がFETのしきい電圧よりも下回ると、多数電荷キャリアの流れが妨げられるような高抵抗のチャネルが確立される。

30

##### 【0002】

FETを電子スイッチとして用いる場合、FETは、電流がソースとドレインとの間を流れることができるオン状態か、または、電流がソースとドレインとの間を流れることが妨げられるオフ状態のどちらかを有している。よって、FETは、ゲートとソースとの間の電圧がFETのしきい電圧を超えると、オン状態で動作し得る。反対に、ゲートとソースとの間の電圧がFETのしきい電圧を下回ると、FETはオフ状態で動作し得る。したがって、FETのソースをグラウンドに接続した場合には、オン状態とオフ状態とを確実に正しく選択するために、FETのゲートに供給する制御信号の電圧振幅は、しきい電圧を超えなければならない。

40

##### 【0003】

接合型FET(JFET)は、JFETのゲートとJFETのチャネルとの間にP-N接合を備えている。通常、JFETは、JFETのP-N接合を通る順方向電流の流れを妨げるデプレッションモードのみのデバイスである。金属酸化物半導体FET(MOSFET)は、MOSFETの金属ゲートとMOSFETのチャネルとの間に酸化物層を備えており、ゲートをチャネルから絶縁している。なお、MOSFETという用語は、MOSFETにおいて、ゲートをチャネルから絶縁するために、金属ゲートの代わりである半導

50

体ゲートとMOSFETのチャネルとの間に酸化物層を有するFETを表すためにも一般的に使用されている。半導体ゲートは、多結晶シリコンを含んでいてもよい。本開示では、MOSFETという用語は、ゲートとチャネルとの間に酸化物層を有するあらゆるFETを含む。MOSFETは、エンハンスマントモードのみのデバイスでも、デプレッションモードのみのデバイスでも、あるいはエンハンスマントモード・デプレッションモードのデバイスであってもよい。N型FETは、N型半導体材料を有するソース及びドレインを備え、P型FETは、P型半導体材料を有するソース及びドレインを備えている。

#### 【0004】

MOSFETを電子スイッチとして使用して、デジタルシステム内に一般的に用いられる論理回路を構成してもよい。このような論理回路は通常、論理回路に用いられるMOSFETのしきい電圧に適合する出力電圧振幅をもたらす。しかしながら、デジタルシステムの中には、高速、高電圧、高熱、大電流等の特殊な用途に、ある種のMOSFETが使用され得る。このようなMOSFETは、そのデジタルシステム内の他のMOSFETよりも低い相互コンダクタンス、及び／または高いしきい電圧を有することがあり、これにより電圧振幅と所望のゲート電圧との不適合が生じ得る。よって、標準電圧振幅を有する入力信号を受信して、高ゲート駆動電圧MOSFETを正常に駆動するために使用可能なり大きな電圧振幅を有する出力信号を供給するインターフェイス回路が必要とされている。

#### 【概要】

本開示の実施形態は、低電圧入力部と高電圧出力部とを有する高電圧ドライバを備える回路に関する。高電圧ドライバは、P型電界効果トランジスタ(PFET)とソースバイアス回路とを備えている。ソースバイアス回路は、低電圧入力部を介して低電圧入力信号を受信し、この低電圧入力信号に直流(DC)バイアスをかけてDCバイアス信号を供給する。PFETは、第1ソースと第1ゲートと第1ドレインとを有している。第1ソースは、DCバイアス信号を受信する。第1ゲートは、第1低電圧DC電源信号を受信する。第1ドレインは、DCバイアス信号と第1低電圧DC電源信号とに基づいて、高電圧出力信号を高電圧出力部を介して供給する。この点に関して、高電圧ドライバは、低電圧入力信号を受信及び変換して、高電圧出力信号の電圧振幅が低電圧入力信号の電圧振幅よりも大きくなるように、高電圧出力信号を供給する。

#### 【0005】

低電圧入力信号にDCバイアスをかけることによって、ソースバイアス回路は、高電圧出力信号の電圧振幅を低電圧入力信号の電圧振幅よりも大きくする。回路の一実施形態において、回路は、さらに、低電圧入力部に接続された低電圧論理ドライバを備えている。これより、低電圧論理ドライバは、低電圧入力信号を低電圧入力部を介して供給する。高電圧ドライバの一実施形態において、ソースバイアス回路は、低電圧入力部と第1ソースとの間に接続されている。第1ゲートは、第1低電圧DC電源信号を供給する第1低電圧DC電源に接続されている。第1ドレインは、高電圧出力部に接続されている。この点に関して、高電圧出力信号の電圧振幅は、低電圧入力信号の電圧振幅よりも大きいので、高電圧出力部の電圧振幅能力は、低電圧入力部の電圧振幅能力よりも高い。

#### 【0006】

回路の一実施形態において、回路は、高ゲート駆動電圧電界効果トランジスタ(FET)をさらに備えている。高ゲート駆動電圧FETは、他のFETよりも低い相互コンダクタンス及び／または高いしきい電圧を有し得る。これより、高ゲート駆動電圧FETは、オフ状態からオン状態に正しく移行するために、他のFETよりも高いゲート電圧を必要とし得る。したがって、高ゲート駆動電圧FETを正常に動作させるために、高電圧出力信号のより大きな電圧振幅が必要となり得る。よって、第1ドレインは、高電圧出力部を介して高ゲート駆動電圧FETのゲートに接続されている。高ゲート駆動電圧FETの一実施形態において、高ゲート駆動電圧FETは炭化ケイ素製のFETである。

#### 【0007】

当業者であれば、添付図面に関連する以下の詳細な説明を読めば、本開示の範囲を理解

10

20

30

40

50

するとともに、本開示の追加の態様を実現するであろう。

**【図面の簡単な説明】**

**【0008】**

本明細書に組み込まれ、かつ本明細書の一部を形成する添付図面は、本開示のいくつかの態様を図示しており、本記述とともに本開示の原理の説明に供する。

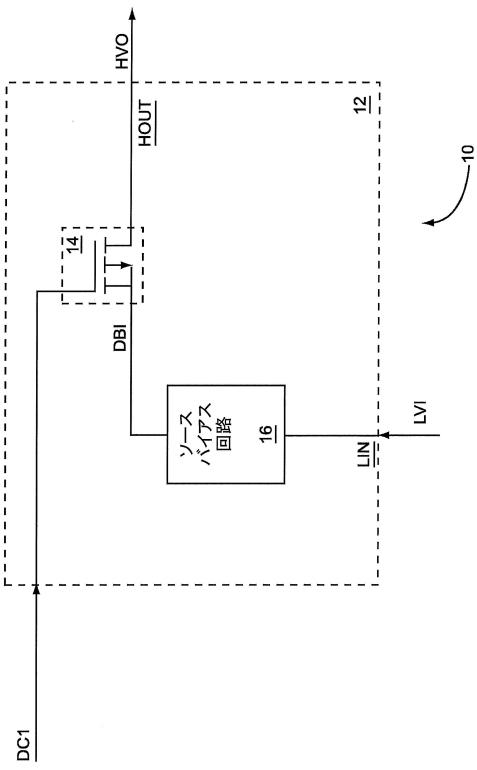

**【図1】**本開示の一実施形態に係る高電圧ドライバを備える回路を図示している。

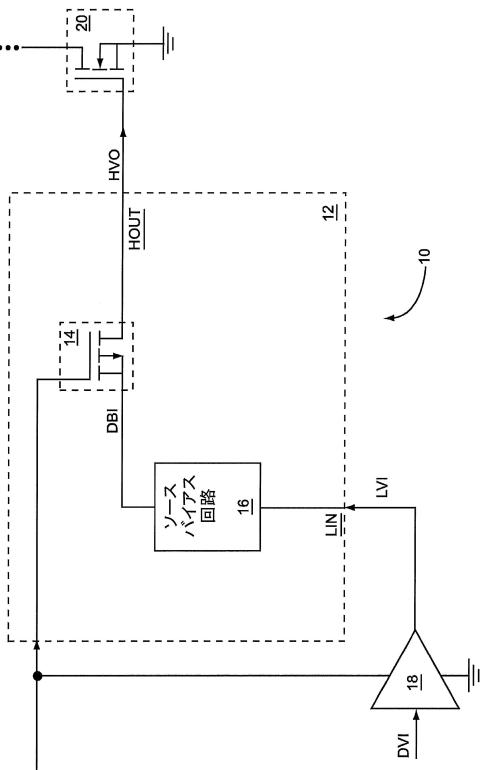

**【図2】**回路の代替の実施形態に係る、低電圧論理ドライバと高ゲート駆動電圧電界効果トランジスタとをさらに備える回路を図示している。

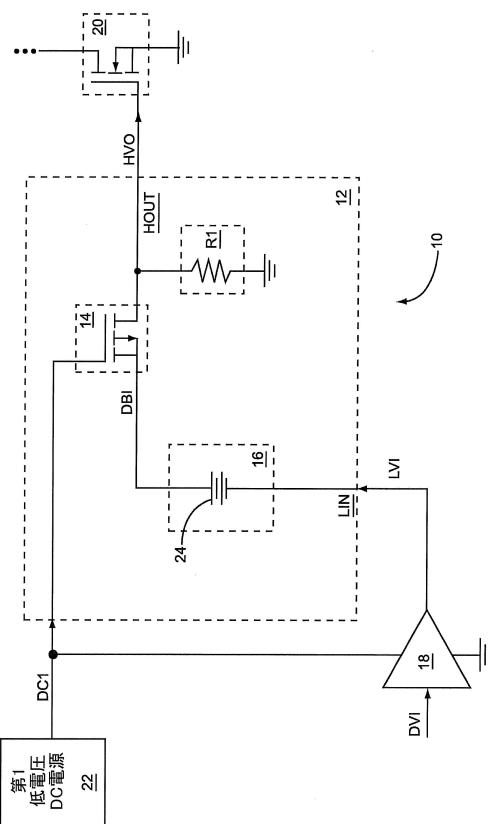

**【図3】**回路の追加の実施形態に係る第1低電圧DC電源をさらに備える回路を図示している。

10

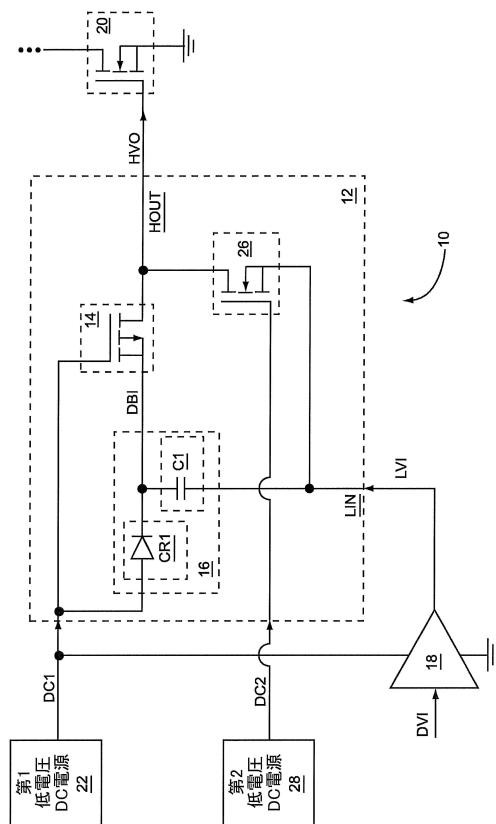

**【図4】**回路の別の実施形態に係る第2低電圧DC電源をさらに備える回路を図示している。

**【図5】**回路のさらなる実施形態に係る回路を図示している。

**【図6】**回路の追加された実施形態に係る回路を図示している。

**【図7】**回路の追加の実施形態に係る回路を図示している。

**【発明を実施するための形態】**

**【0009】**

**[詳細な説明]**

以下に記載された実施形態は、当業者が本開示を実施できるようにするために必要な情報を示しているとともに、本開示を実施する最良の形態を説明している。添付図面を踏まえて以下の説明を読めば、当業者であれば本明細書にて特に述べなくても、本開示の概念を理解し、これらの概念の用途を認識するであろう。これらの概念や用途が本開示及び添付の請求項の範囲の範囲内にあることは理解されるべきである。

20

**【0010】**

本開示の実施形態は、低電圧入力部と高電圧出力部とを有する高電圧ドライバを備える回路に関する。高電圧ドライバは、P F E T (P型電界効果トランジスタ)と、ソースバイアス回路とを備えている。ソースバイアス回路は、低電圧入力部を介して低電圧入力信号を受信し、この低電圧入力信号にDCバイアスをかけてDCバイアス信号を供給する。P F E Tは、第1ソースと、第1ゲートと、第1ドレインとを有している。第1ソースは、DCバイアス信号を受信する。第1ゲートは、第1低電圧DC電源信号を受信する。第1ドレインは、DCバイアス低電圧入力信号と第1低電圧DC電源信号とに基づいて、高電圧出力信号を高電圧出力部を介して供給する。この点に関して、高電圧ドライバは、低電圧入力信号を受信及び変換して、高電圧出力信号の電圧振幅が低電圧入力信号の電圧振幅よりも大きくなるように、高電圧出力信号を供給する。

30

**【0011】**

低電圧入力信号にDCバイアスをかけることによって、ソースバイアス回路は、高電圧出力信号の電圧振幅を低電圧入力信号の電圧振幅よりも大きくする。回路の一実施形態において、回路はさらに、低電圧入力部に接続された低電圧論理ドライバを備えている。これにより、低電圧論理ドライバは、低電圧入力信号を低電圧入力部を介して供給する。高電圧ドライバの一実施形態において、ソースバイアス回路は、低電圧入力部と第1ソースとの間に接続されている。第1ゲートは、第1低電圧DC電源信号を供給する第1低電圧DC電源に接続されている。第1ドレインは、高電圧出力部に接続されている。この点に関して、高電圧出力信号の電圧振幅は低電圧入力信号の電圧振幅よりも大きいので、高電圧出力部の電圧振幅能力は、低電圧入力部の電圧振幅能力よりも高い。

40

**【0012】**

回路の一実施形態において、回路は、高ゲート駆動電圧電界効果トランジスタ(F E T)をさらに備えている。高ゲート駆動電圧F E Tは、他のF E Tよりも、低い相互コンダクタンス、及び／または高いしきい電圧を有してもよい。これにより、高ゲート駆動電圧F E Tは、オフ状態からオン状態に正しく移行するためには、他のF E Tよりも高いゲート電圧が必要となり得る。したがって、高ゲート駆動電圧F E Tを正常に動作させるため

50

には、高電圧出力信号の電圧振幅をより大きくする必要があり得る。よって、第1ドレインは、高電圧出力部を介して高ゲート駆動電圧FETのゲートに接続されている。高ゲート駆動電圧FETの一実施形態において、高ゲート駆動電圧FETは、炭化ケイ素製のFETである。

#### 【0013】

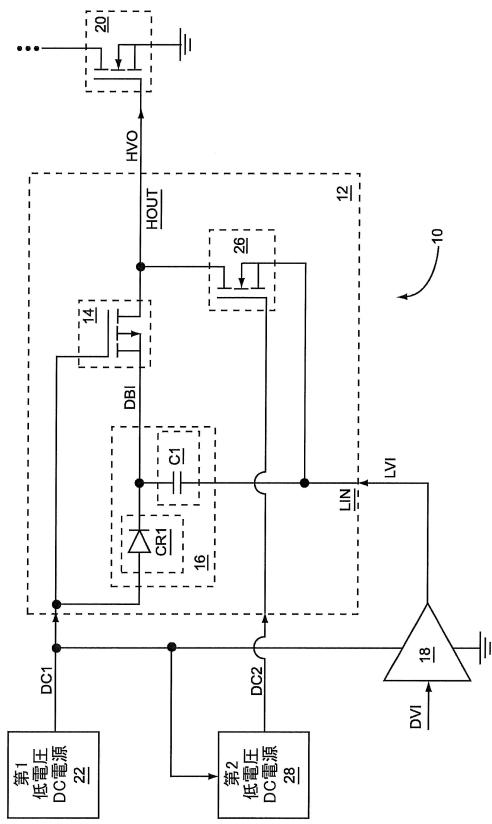

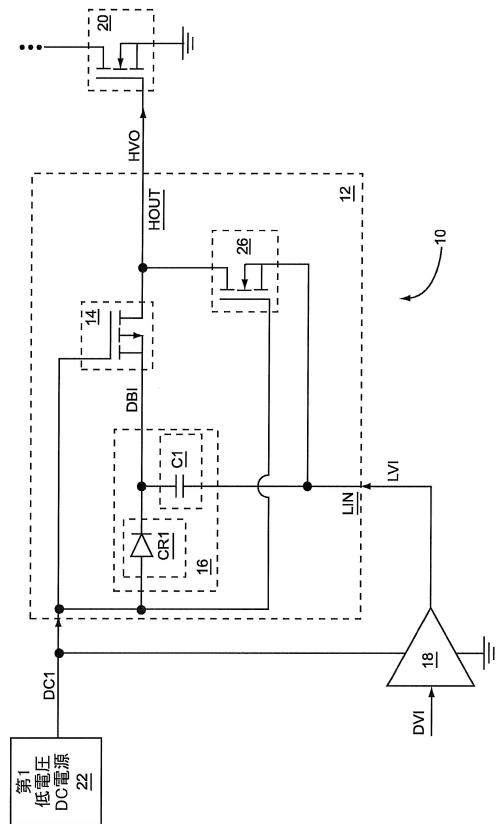

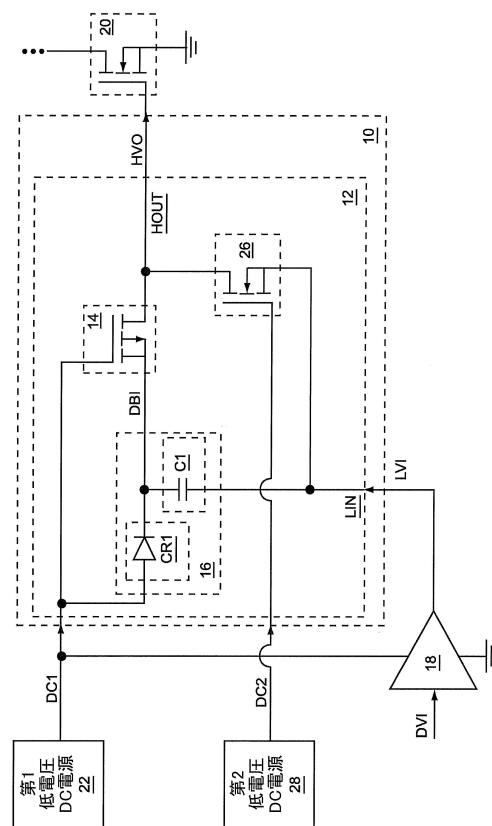

図1は、本開示の一実施形態に係る高電圧ドライバ12を備える回路10を図示している。高電圧ドライバ12は、低電圧入力部LINと高電圧出力部HOUTとを有している。さらに、高電圧ドライバ12は、PFET14とソースバイアス回路16とを備えている。この点において、PFET14とソースバイアス回路16とが高電圧ドライバ12を形成している。PFET14は、第1ソースと第1ゲートと第1ドレインとを有している。ソースバイアス回路16は、低電圧入力部LINを介して低電圧入力信号LVIを受信し、低電圧入力信号LVIにDCバイアスをかけてDCバイアス信号DBIを供給する。第1ソースは、DCバイアス信号DBIを受信する。第1ゲートは、第1低電圧DC電源信号DC1を受信する。第1ドレインは、DCバイアス信号DBIと第1低電圧DC電源信号DC1とに基づいて、高電圧出力信号HVOを高電圧出力部HOUTを介して供給する。この点に関して、高電圧ドライバ12は、低電圧入力信号LVIを受信及び変換して、高電圧出力信号HVOの電圧振幅が低電圧入力信号LVIの電圧振幅よりも大きくなるように、高電圧出力信号HVOを供給する。

10

#### 【0014】

低電圧入力信号LVIにDCバイアスをかけることによって、ソースバイアス回路16は、高電圧出力信号HVOの電圧振幅を低電圧入力信号LVIの電圧振幅よりも大きくする。高電圧ドライバ12の一実施形態において、高電圧出力信号HVOの電圧振幅は、低電圧入力信号LVIの電圧振幅の約2倍程度である。高電圧ドライバ12の第1の例示的な実施形態において、高電圧出力信号HVOの電圧振幅は、約6ボルトに等しく、低電圧入力信号LVIの電圧振幅は、約3.3ボルトに等しい。高電圧ドライバ12の第2の例示的な実施形態において、高電圧出力信号HVOの電圧振幅は、約19.4ボルトに等しく、低電圧入力信号LVIの電圧振幅は、約10ボルトに等しい。

20

#### 【0015】

ソースバイアス回路16は、低電圧入力信号LVIと第1ソースとの間に接続されている。第1ドレインは、高電圧出力部HOUTに接続されている。この点に関して、高電圧出力信号HVOの電圧振幅は、低電圧入力信号LVIの電圧振幅よりも大きいので、高電圧出力部HOUTの電圧振幅能力は、低電圧入力部LINの電圧振幅能力よりも高い。PFET14の一実施形態において、PFET14は、金属酸化物半導体FET(MOSFET)である。PFET14の代替の実施形態において、PFET14は、接合型FET(JFET)である。PFET14の追加の実施形態において、PFET14は、任意の種類のFETである。回路10の一実施形態において、ソースバイアス回路16は、低電圧入力信号LVIと第1ソースとの間に直接接続されており、第1ドレインは、高電圧出力部HOUTと直接接続されている。

30

#### 【0016】

図2は、回路10の代替の実施形態に係る回路10を図示している。図2に図示された回路10は、図1に図示された回路10と同様であるが、図2に図示された回路10は、低電圧論理ドライバ18と高ゲート駆動電圧FET20とをさらに備えている点が異なる。低電圧論理ドライバ18は、低電圧入力部LINに接続されている。さらに、低電圧論理ドライバ18は、ドライバ入力信号DVIを受信して、低電圧入力信号LVIを低電圧入力部LINを介して高電圧ドライバ12に供給する。これにより、低電圧入力信号LVIは、ドライバ入力信号DVIに基づいている。高ゲート駆動電圧FET20のゲートは、高電圧出力部HOUTを介して第1ドレインに接続されている。これにより、高ゲート駆動電圧FET20のゲートは、高電圧出力部HOUTを介して高電圧出力信号HVOを受信する。高ゲート駆動電圧FET20のソースは、グラウンドに接続されている。高ゲート駆動電圧FET20のドレインは、他の回路構成(図示せず)に接続されている。回

40

50

路 1 0 の一実施形態において、低電圧論理ドライバ 1 8 は、低電圧入力部 L I N に直接接続され、高ゲート駆動電圧 F E T 2 0 のゲートは、高電圧出力部 H O U T を介して第 1 ドレインに直接接続されている。

#### 【 0 0 1 7 】

高ゲート駆動電圧 F E T は、他の F E T よりも、低い相互コンダクタンス、及び / または高いしきい電圧を有し得る。これにより、高ゲート駆動電圧 F E T 2 0 は、オフ状態からオン状態に正しく移行するためには、他の F E T よりも高いゲート電圧が必要となり得る。したがって、高ゲート駆動電圧 F E T 2 0 を正常に動作させるためには、高電圧出力信号 H V O のより大きな電圧振幅が必要となり得る。この点に関して、高電圧ドライバ 1 2 の例示的な実施形態では、高電圧ドライバ 1 2 は、高電圧論理ドライバ、高電圧ゲートドライバ、あるいはその両方である。高ゲート駆動電圧 F E T 2 0 の一実施形態において、高ゲート駆動電圧 F E T 2 0 は、S i C 製の F E T である。S i C 製の F E T は、高速、高電圧、高熱、大電流等、またはこれらの任意の組み合わせが要求される用途に用いられ得る。高ゲート駆動電圧 F E T 2 0 の一実施形態において、図 2 に図示されているように、高ゲート駆動電圧 F E T 2 0 は、N 型 F E T である。高ゲート駆動電圧 F E T 2 0 の代替の実施形態において、高ゲート駆動電圧 F E T 2 0 は、P 型 F E T である。高ゲート駆動電圧 F E T 2 0 の一実施形態において、高ゲート駆動電圧 F E T 2 0 は、M O S F E T である。高ゲート駆動電圧 F E T 2 0 の代替の実施形態において、高ゲート駆動電圧 F E T 2 0 は、J F E T である。高ゲート駆動電圧 F E T 2 0 の追加の実施形態において、高ゲート駆動電圧 F E T 2 0 は、任意の種類の F E T である。10

#### 【 0 0 1 8 】

図 3 は、回路 1 0 の追加の実施形態に係る回路 1 0 を図示している。図 3 に図示された回路 1 0 は、図 2 に図示された回路 1 0 と同様であるが、図 3 に図示された回路 1 0 は、第 1 低電圧 D C 電源 2 2 をさらに備えている点が異なる。第 1 低電圧 D C 電源 2 2 は、第 1 ゲートと低電圧論理ドライバ 1 8 とに接続されている。これにより、第 1 低電圧 D C 電源 2 2 は、第 1 低電圧 D C 電源信号 D C 1 を供給する。この点において、第 1 低電圧 D C 電源 2 2 は、低電圧入力信号 L V I を変換して高電圧出力信号 H V O を生成するためのエネルギーを供給する。回路 1 0 の一実施形態において、第 1 低電圧 D C 電源 2 2 は、第 1 ゲートと低電圧論理ドライバ 1 8 とに直接接続されている。20

#### 【 0 0 1 9 】

高電圧ドライバ 1 2 はさらに、第 1 ドレインとグラウンドとの間に接続された第 1 抵抗素子 R 1 を備えている。ソースバイアス回路 1 6 は、低電圧入力部 L I N と第 1 ソースとの間に接続された電池 2 4 を備えている。電池 2 4 は、陽極と陰極とを有しており、陽極が第 1 ソースに接続され、陰極が低電圧入力部 L I N に接続されている。陰極は、陽極に対して正である。したがって、電池 2 4 は、D C バイアス信号 D B I が低電圧入力信号 L V I に対して正バイアスを有するように、低電圧入力信号 L V I に D C バイアスをかける。30

#### 【 0 0 2 0 】

高電圧ドライバ 1 2 の動作の説明を示す。低電圧入力信号 L V I が論理ロー ( L O W ) である場合、低電圧入力信号 L V I は約 0 ボルトに等しくなり得る。これにより、D C バイアス信号 D B I の電圧は正であり、電池 2 4 の電圧にほぼ等しい。したがって、D C バイアス信号 D B I の電圧と第 1 低電圧 D C 電源信号 D C 1 の電圧との間の差が P F E T 1 4 のしきい電圧よりも小さければ、P F E T 1 4 はオフ状態になる。その結果、第 1 抵抗素子 R 1 は、高電圧出力信号 H V O を論理ローである約 0 ボルトに引き下げる事になる。しかしながら、低電圧入力信号 L V I が論理ハイ ( H I G H ) である場合、低電圧入力信号 L V I は、第 1 低電圧 D C 電源信号 D C 1 の電圧にほぼ等しい。その結果、D C バイアス信号 D B I の電圧は、第 1 低電圧 D C 電源信号 D C 1 の電圧と電池 2 4 の電圧との和に等しくなる。したがって、D C バイアス信号 D B I の電圧と第 1 低電圧 D C 電源信号 D C 1 の電圧との間の差が P F E T 1 4 のしきい電圧よりも大きければ、P F E T 1 4 はオン状態になる。その結果、P F E T 1 4 は、論理ハイである D C バイアス信号 D B I にほ4050

ぼ等しくなるように高電圧出力信号 HVO を駆動する。

#### 【0021】

この点に関して、高電圧ドライバ 12 は、第 1 低電圧 DC 電源信号 DC1 の電圧にはぼ等しい低電圧入力信号 LVI の電圧振幅を、第 1 低電圧 DC 電源信号 DC1 の電圧と電池 24 の電圧との和にはぼ等しい高電圧出力信号 HVO の電圧振幅に変換する。さらに、低電圧入力信号 LVI が論理ローである場合、高電圧出力信号 HVO は論理ローである。反対に、低電圧入力信号 LVI が論理ハイである場合、高電圧出力信号 HVO は論理ハイである。

#### 【0022】

回路 10 の一実施形態において、第 1 ソースと第 1 ドレインとの間の最大電圧は、第 1 低電圧 DC 電源信号 DC1 の電圧以下である。10 回路 10 の一実施形態において、第 1 ゲートと第 1 ドレインとの間の最大電圧は、第 1 低電圧 DC 電源信号 DC1 の電圧以下である。回路 10 の一実施形態において、第 1 ソースと第 1 ゲートとの間の最大電圧は、第 1 低電圧 DC 電源信号 DC1 の電圧以下である。

#### 【0023】

回路 10 の例示的な実施形態において、電池 24 の電圧は、第 1 低電圧 DC 電源信号 DC1 の電圧にはぼ等しく、PFET14 は、エンハンスマントモードのみの FET である。20 したがって、高電圧出力信号 HVO の電圧振幅は、低電圧入力信号 LVI の電圧振幅の約 2 倍に等しい。さらに、低電圧入力信号 LVI が論理ローである場合、第 1 ソースと第 1 ゲートとの間の電圧はゼロにはぼ等しく、PFET14 をオフ状態に強制する。低電圧入力信号 LVI が論理ハイの場合、第 1 ソースと第 1 ゲートとの間の電圧は、第 1 低電圧 DC 電源信号 DC1 の電圧にはぼ等しく、第 1 低電圧 DC 電源信号 DC1 の電圧が PFET14 のしきい電圧よりも大きければ、PFET14 をオン状態に強制する。

#### 【0024】

図 4 は、回路 10 の別の実施形態に係る回路 10 を図示している。図 4 に図示された回路 10 は、図 3 に図示された回路 10 と同様であるが、図 4 に図示された回路 10 は第 2 低電圧 DC 電源 28 をさらに備えている点が異なる。加えて、高電圧ドライバ 12 は、N 型 FET (NFET) 26 をさらに備え、ソースバイアス回路 16 は、第 1 容量素子 C1 と第 1 ダイオード素子 CR1 とを備えている。NFET26 は、第 2 ソースと、第 2 ゲートと、第 2 ドレインとを有している。第 2 ゲートは、第 2 低電圧 DC 電源 28 に接続されている。30 第 2 ソースは、低電圧入力部 LIN に接続されている。第 2 ドレインは、高電圧出力部 HOUT に接続されている。第 1 容量素子 C1 は、低電圧入力部 LIN と第 1 ソースとの間に接続されている。第 1 ダイオード素子 CR1 は、アノードとカソードとを有し、カソードが第 1 ソースに接続され、アノードが第 1 ゲートに接続されている。高電圧ドライバ 12 の一実施形態において、NFET26 は、第 1 抵抗素子 R1 (図 3) を機能的に置き換え、第 1 容量素子 C1 及び第 1 ダイオード素子 CR1 は、電池 24 (図 3) を機能的に置き換える。

#### 【0025】

回路 10 の一実施形態において、第 2 ゲートは、第 2 低電圧 DC 電源 28 に直接接続され、40 第 2 ソースは、低電圧入力部 LIN に直接接続され、第 2 ドレインは、高電圧出力部 HOUT に直接接続され、第 1 容量素子 C1 は、低電圧入力部 LIN と第 1 ソースとの間に直接接続され、第 1 ダイオード素子 CR1 は、アノードとカソードとを有し、カソードは第 1 ソースに直接接続され、アノードは第 1 ゲートに直接接続されているか、あるいはこれらの任意の組み合わせである。

#### 【0026】

第 1 容量素子 C1 は、低電圧入力部 LIN を介して低電圧入力信号 LVI を受信する。50 第 1 ダイオード素子 CR1 は、低電圧入力信号 LVI を受信及び整流して、第 1 容量素子 C1 に供給する。これにより、第 1 容量素子 C1 及び第 1 ダイオード素子 CR1 は、低電圧入力信号 LVI と第 1 低電圧 DC 電源信号 DC1 とに基づいて、DC バイアス信号 DBI を供給する。低電圧入力信号 LVI が論理ローである場合、低電圧入力信号 LVI は、

約 0 ボルトに等しくなり得る。よって、第 1 低電圧 DC 電源 22 は、第 1 容量素子 C1 の両端間の電圧が第 1 低電圧 DC 電源信号 DC1 の電圧から第 1 ダイオード素子 CR1 の両端間の電圧降下、つまり約 0.6 ボルトに等しくなり得る電圧を差し引いた電圧になるまで、第 1 ダイオード素子 CR1 を介して第 1 容量素子 C1 を充電する。低電圧入力信号 LVI が論理ハイに移行すると、低電圧入力信号 LVI は、第 1 低電圧 DC 電源信号 DC1 の電圧にほぼ等しい電圧へと移行し、これにより第 1 ダイオード素子 CR1 に逆バイアスをかけ得る。この点において、第 1 容量素子 C1 は電池 24 ( 図 3 ) と同様に機能する。しかしながら、第 1 容量素子 C1 の放電を防ぐために、第 1 抵抗素子 R1 ( 図 3 ) は NFE T26 に置き換えられている。

## 【 0027 】

10

第 2 低電圧 DC 電源 28 は、第 2 低電圧 DC 電源信号 DC2 を供給する。これにより、第 2 ゲートは、第 2 低電圧 DC 電源信号 DC2 を受信する。第 2 ソースは、低電圧入力部 LIN を介して低電圧入力信号 LVI を受信する。低電圧入力信号 LVI が論理ローである場合、低電圧入力信号 LVI は約 0 ボルトに等しくなり得る。すでに述べたように、DC バイアス信号 DBI の電圧と第 1 低電圧 DC 電源信号 DC1 の電圧との間の差が PFE T14 のしきい電圧よりも小さければ、PFE T14 はオフ状態になる。さらに、第 2 低電圧 DC 電源信号 DC2 の電圧が NFE T26 のしきい電圧よりも大きければ、NFE T26 はオン状態になり、これにより高電圧出力信号 HVO を論理ローである約 0 ボルトに引き下げることになる。

## 【 0028 】

20

すでに述べたように、低電圧入力信号 LVI が論理ハイである場合、DC バイアス信号 DBI の電圧と第 1 低電圧 DC 電源信号 DC1 の電圧との間の差が PFE T14 のしきい電圧よりも大きければ、PFE T14 はオン状態になり、これにより高電圧出力信号 HVO を論理ハイをもたらすように駆動することになる。さらに、第 2 低電圧 DC 電源信号 DC2 の電圧と低電圧入力信号 LVI との間の差が NFE T26 のしきい電圧よりも小さければ、もしくは、低電圧入力信号 LVI が第 2 ゲート / 第 2 ソースに逆バイアスをかけるのであれば、NFE T26 はオフ状態になる。この点において、PFE T14 がオン状態である場合、NFE T26 はオフ状態である。反対に、NFE T26 がオン状態である場合、PFE T14 はオフ状態である。

## 【 0029 】

30

高電圧ドライバ 12 の一実施形態において、第 1 容量素子 C1 の放電を防ぐために、PFE T14 がオフ状態からオン状態へと移行する前に、NFE T26 がオン状態からオフ状態へと移行する。さらに、高電圧ドライバ 12 の一実施形態において、NFE T26 がオフ状態からオン状態へと移行する前に、PFE T14 がオン状態からオフ状態へと移行する。回路 10 の一実施形態において、第 1 低電圧 DC 電源信号 DC1 の電圧は、第 2 低電圧 DC 電源信号 DC2 の電圧の 2 倍にほぼ等しい。

## 【 0030 】

NFE T26 の一実施形態において、NFE T26 は MOSFET である。NFE T26 の代替の実施形態において、NFE T26 は JFET である。NFE T26 の追加の実施形態において、NFE T26 は任意の種類の FET である。回路 10 の一実施形態において、高ゲート駆動電圧 FET20 の相互コンダクタンスは、NFE T26 の相互コンダクタンスよりも大きい。回路 10 の例示的な実施形態において、高ゲート駆動電圧 FET20 のターンオンゲート電圧は、NFE T26 のターンオン電圧の約 2 倍程度である。回路 10 の一実施形態において、高ゲート駆動電圧 FET20 のターンオン電圧は、PFE T14 のターンオン電圧よりも高い。回路 10 の例示的な実施形態において、高ゲート駆動電圧 FET20 のターンオン電圧は、PFE T14 のターンオン電圧の約 2 倍程度である。

## 【 0031 】

図 5 は回路 10 のさらなる実施形態に係る回路 10 を図示している。図 5 に図示された回路 10 は、図 4 に図示された回路 10 と同様であるが、図 5 に図示された回路 10 では

40

50

、第2低電圧DC電源28は第1低電圧DC電源信号DC1を受信し、第1低電圧DC電源信号DC1に基づいて第2低電圧DC電源信号DC2を供給する点が異なる。回路10の一実施形態において、第1低電圧DC電源信号DC1の電圧は、第2低電圧DC電源信号DC2の電圧の2倍にほぼ等しい。第2低電圧DC電源28の一実施形態において、第2低電圧DC電源28は、DC-DCCコンバータ、抵抗分圧器、チャージポンプ、リニアコンバータ、ツエナーダイオードを用いたコンバータ等、またはこれらの任意の組み合わせである。

【0032】

図6は、回路10の追加の実施形態に係る回路10を図示している。図6に図示された回路10は、図4に図示された回路10と同様であるが、図6に図示された回路10では、第2低電圧DC電源28を省略し、第2ゲートは第1低電圧DC電源22に接続されている点が異なる。この点に関して、第2ゲートは、第1低電圧DC電源信号DC1を受信する。回路10の一実施形態において、第2ゲートは、第1低電圧DC電源22に直接接続されている。

10

【0033】

図7は、回路10の追加の実施形態に係る回路10を図示している。図7に図示された回路10は図4に図示された回路10と同様であるが、図7に図示された回路10では、低電圧論理ドライバ18と、高ゲート駆動電圧FET20と、第1低電圧DC電源22と、第2低電圧DC電源28とが回路10の外部に設けられている点が異なる。回路10の代替の実施形態において、回路10は、高ゲート駆動電圧FET20と、第1低電圧DC電源22と、第2低電圧DC電源28とのうちのいずれか、あるいは全てを備えている。本開示の代替の実施形態において、高ゲート駆動電圧FET20と、第1低電圧DC電源22と、第2低電圧DC電源28とのうちのいずれか、あるいは全てが省略されている。

20

【0034】

当業者であれば、本開示の実施形態の改良及び修正を認識するであろう。このような改良及び修正は全て、本明細書に開示された概念及び本明細書に続く特許請求の範囲の範囲内であるとみなされる。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

---

フロントページの続き

(56)参考文献 特開平07-249740(JP,A)

特開2005-012944(JP,A)

特開平11-068531(JP,A)

特開2001-160745(JP,A)

特開2011-101209(JP,A)

特開平08-242155(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 17/06

H03K 17/687

H03K 19/0185