(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5667840号

(P5667840)

(45) 発行日 平成27年2月12日(2015.2.12)

(24) 登録日 平成26年12月19日(2014.12.19)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/749 | (2006.01) | HO1L 29/74 | 601A |

| HO1L 29/74  | (2006.01) | HO1L 29/74 | G    |

| HO1L 29/786 | (2006.01) | HO1L 29/78 | 618B |

| HO1L 29/78  | (2006.01) | HO1L 29/78 | 618G |

| HO1L 29/12  | (2006.01) | HO1L 29/78 | 626A |

請求項の数 1 (全 23 頁) 最終頁に続く

(21) 出願番号

特願2010-249520 (P2010-249520)

(22) 出願日

平成22年11月8日 (2010.11.8)

(65) 公開番号

特開2011-124560 (P2011-124560A)

(43) 公開日

平成23年6月23日 (2011.6.23)

審査請求日

平成25年8月23日 (2013.8.23)

(31) 優先権主張番号

特願2009-259900 (P2009-259900)

(32) 優先日

平成21年11月13日 (2009.11.13)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 渡邊 一徳

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 儀同 孝信

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタ乃至第9のトランジスタと、容量素子と、第1の配線と、第2の配線と、第3の配線と、を有し、

前記第1のトランジスタ乃至前記第9のトランジスタにおいて、チャネルが形成される半導体層は酸化物半導体を含み、

前記酸化物半導体は、Inと、Gaと、Znとを含み、

前記第1の配線には、第1の電位が供給され、

前記第2の配線には、第2の電位が供給され、

前記第3の配線には、第3の電位が供給され、

前記第1の電位、及び前記第2の電位は、前記第3の電位よりも高い電位であり、

前記第1のトランジスタのゲートは、入力端子に電気的に接続され、

前記第1のトランジスタのソースまたはドレインの一方は、前記第3の配線に電気的に接続され、

前記第1のトランジスタのソースまたはドレインの他方は、前記第2のトランジスタのソースまたはドレインの一方に電気的に接続され、

前記第2のトランジスタのゲートは、前記第7のトランジスタのソースまたはドレインの一方に電気的に接続され、

前記第2のトランジスタのゲートは、前記第8のトランジスタのソースまたはドレインの一方に電気的に接続され、

10

20

前記第2のトランジスタのソースまたはドレインの他方は、前記第3のトランジスタのソースまたはドレインの一方電気的に接続され、

前記第2のトランジスタのソースまたはドレインの他方は、前記第4のトランジスタのソースまたはドレインの一方電気的に接続され、

前記第2のトランジスタのソースまたはドレインの他方は、前記第6のトランジスタのゲートに電気的に接続され、

前記第3のトランジスタのゲートは、前記第1の配線に電気的に接続され、

前記第3のトランジスタのソースまたはドレインの他方は、前記第2の配線に電気的に接続され、

前記第4のトランジスタのゲートは、前記第5のトランジスタのソースまたはドレインの一方電気的に接続され、10

前記第4のトランジスタのゲートは、前記第6のトランジスタのソースまたはドレインの一方電気的に接続され、

前記第4のトランジスタのゲートは、前記容量素子の第1電極に電気的に接続され、

前記第4のトランジスタのゲートは、前記第8のトランジスタのゲートに電気的に接続され、

前記第4のトランジスタのゲートは、前記第9のトランジスタのゲートに電気的に接続され、

前記第4のトランジスタのソースまたはドレインの他方は、前記第3の配線に電気的に接続され、20

前記第5のトランジスタのゲートは、前記第1の配線に電気的に接続され、

前記第5のトランジスタのソースまたはドレインの他方は、前記第2の配線に電気的に接続され、

前記第6のトランジスタのソースまたはドレインの他方は、前記第3の配線に電気的に接続され、

前記第7のトランジスタのゲートは、前記第1の配線に電気的に接続され、

前記第7のトランジスタのソースまたはドレインの他方は、前記第2の配線に電気的に接続され、

前記第8のトランジスタのソースまたはドレインの他方は、前記第3の配線に電気的に接続され、30

前記第9のトランジスタのソースまたはドレインの一方は、出力端子に電気的に接続され、

前記第9のトランジスタのソースまたはドレインの他方は、前記第3の配線に電気的に接続され、

前記容量素子は、第2電極が前記第3の配線に電気的に接続されていることを特徴とする半導体装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体装置、またはその駆動方法に関する。40

#### 【0002】

また、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。例えば、表示装置や、集積回路は半導体装置に含まれる。

#### 【背景技術】

#### 【0003】

パワー・デバイスとして知られているサイリスタは、単結晶シリコン基板内に形成され、電流等のトリガー信号により、導通状態を保持する構成となっている（例えば特許文献1を参照）。

#### 【0004】

サイリスタは、p型半導体層とn型半導体層を交互に配置したp n p n層で構成され、等50

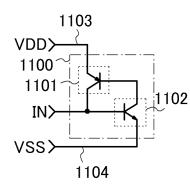

価回路で表すと、n p n構造のバイポーラトランジスタ（以下n p n型トランジスタという）と、p n p構造のバイポーラトランジスタ（以下p n p型トランジスタ）で構成される。具体的な回路構成について、図12に示す。

#### 【0005】

図12は、n p n型トランジスタ1101、p n p型トランジスタ1102を有するサイリスタ1100を示している。サイリスタ1100における、n p n型トランジスタ1101のエミッタ端子は高電源電位VDDが供給される配線1103に接続され、n p n型トランジスタ1101のコレクタ端子はトリガー信号が供給される入力端子IN及びp n p型トランジスタ1102のベース端子に接続され、n p n型トランジスタ1101のベース端子がp n p型トランジスタ1102のコレクタ端子に接続され、p n p型トランジスタ1102のエミッタ端子は低電源電位VSSが供給される配線1104に接続される。

10

#### 【0006】

図12のサイリスタの動作について簡単に述べる。トリガー信号がL信号（低レベル信号、低電位信号ともいう）になると、p n p型トランジスタ1102のコレクタ端子とエミッタ端子との間が非導通状態（オフ状態ともいう）となり、p n p型トランジスタ1102のコレクタ端子を流れる電流（以下、コレクタ電流）もほとんど検出されない。その結果、n p n型トランジスタ1101のベース端子を流れる電流（以下ベース電流）がほとんど検出されないため、n p n型トランジスタ1101もオフ状態となり、配線1103と配線1104の間に電流はほとんど流れない。また、トリガー信号がH信号（高レベル信号、高電位信号ともいう）になると、p n p型トランジスタ1102のコレクタ端子とエミッタ端子との間が導通状態（オン状態ともいう）となり、p n p型トランジスタ1102のコレクタ端子にコレクタ電流が検出される。その結果、n p n型トランジスタ1101のベース電流が流れることとなり、n p n型トランジスタ1101が導通状態となる。

20 n p n型トランジスタ1101が導通状態となると、n p n型トランジスタ1101のコレクタ電流が検出され、p n p型トランジスタ1102の導通状態が継続することとなる。そしてサイリスタ1100は、n p n型トランジスタ1101のコレクタ電流にp n p型トランジスタ1102のコレクタ電流が加算された大電流を配線1103と配線1104の間に流すといった特性を有している。

30

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

【特許文献1】特開平11-354774号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

図12に示すサイリスタでは、単結晶半導体基板内にpn接合を組み合わせて構成するため、絶縁ゲート型トランジスタ（IGFET：Insulated Gate Field Effect Transistor、またはMISFET：Metal Insulator Semiconductor Field Effect Transistorともいう）を形成するプロセスと組み合わせて形成する場合、プロセスの複雑化を招くこととなる。また、半導体層として珪素膜を形成して構成された絶縁ゲート型トランジスタである薄膜トランジスタでサイリスタを形成する場合、印加する電圧への耐圧等の問題があり、所望の機能が得られないといった問題がある。

40

#### 【0009】

そこで本発明の一形態は、プロセスの複雑化を招くことなく、サイリスタとしての機能を実現することの出来る半導体装置を提供することを課題の一とする。

#### 【課題を解決するための手段】

#### 【0010】

本発明の一態様は、第1乃至第9絶縁ゲート型トランジスタ、容量素子、第1の高電源電

50

位が供給される第1の配線、第2の高電源電位が供給される第2の配線、及び低電源電位が供給される第3の配線を有し、第1絶縁ゲート型トランジスタは、ゲートが入力端子に電気的に接続され、第1端子が第3の配線に電気的に接続され、第2端子が第2絶縁ゲート型トランジスタの第1端子に電気的に接続され、第2絶縁ゲート型トランジスタは、ゲートが第7絶縁ゲート型トランジスタの第1端子及び第8絶縁ゲート型トランジスタの第1端子に電気的に接続され、第2端子が、第3絶縁ゲート型トランジスタの第1端子、第4絶縁ゲート型トランジスタの第1端子、及び第6絶縁ゲート型トランジスタのゲートに電気的に接続され、第3絶縁ゲート型トランジスタは、ゲートが第1の配線に電気的に接続され、第2端子が第2の配線に電気的に接続され、第4絶縁ゲート型トランジスタは、ゲートが第5絶縁ゲート型トランジスタの第1端子、第6絶縁ゲート型トランジスタの第1端子、容量素子の第1電極、第8絶縁ゲート型トランジスタのゲート、及び第9絶縁ゲート型トランジスタのゲートに電気的に接続され、第2端子が第3の配線に電気的に接続され、第5絶縁ゲート型トランジスタは、ゲートが第1の配線に電気的に接続され、第2端子が第2の配線に電気的に接続され、第7絶縁ゲート型トランジスタは、ゲートが第1の配線に電気的に接続され、第2端子が第3の配線に電気的に接続され、第8絶縁ゲート型トランジスタは、第2端子が第3の配線に電気的に接続され、第9絶縁ゲート型トランジスタは、第1端子が出力端子に電気的に接続され、第2端子が第3の配線に電気的に接続され、容量素子は、第2電極が第3の配線に電気的に接続されている半導体装置である。 10

## 【0011】

20

本発明の一態様において、第1乃至第9絶縁ゲート型トランジスタの半導体層は、酸化物半導体で構成される半導体装置でもよい。

## 【0012】

本発明の一態様において、抵抗素子を有し、抵抗素子は、第1端子が第1絶縁ゲート型トランジスタのゲートに電気的に接続され、第2端子が第3の配線に電気的に接続される半導体装置でもよい。

## 【0013】

本発明の一態様において、酸化物半導体は、二次イオン質量分析法で検出される水素濃度が $1 \times 10^{-6} / \text{cm}^3$ 以下である半導体装置でもよい。

## 【0014】

30

本発明の一態様において、酸化物半導体は、キャリア濃度が $1 \times 10^{14} / \text{cm}^3$ 未満である半導体装置でもよい。

## 【0015】

本発明の一態様において、第4絶縁ゲート型トランジスタのゲート、第5絶縁ゲート型トランジスタの第1端子、第6絶縁ゲート型トランジスタの第1端子、容量素子の第1電極、及び第8絶縁ゲート型トランジスタのゲートが電気的に接続されたノードの電位は、バッファ回路を介して、第9絶縁ゲート型トランジスタのゲートに供給される半導体装置でもよい。

## 【0016】

40

本発明の一態様において、バッファ回路は、第10乃至第13絶縁ゲート型トランジスタを有し、第10絶縁ゲート型トランジスタは、ゲートが第1の配線に電気的に接続され、第1端子が第2の配線に電気的に接続され、第2端子が第11絶縁ゲート型トランジスタの第1端子及び第13絶縁ゲート型トランジスタのゲートに電気的に接続され、第11絶縁ゲート型トランジスタは、ゲートが第4絶縁ゲート型トランジスタのゲート、第5絶縁ゲート型トランジスタの第1端子、第6絶縁ゲート型トランジスタの第1端子、容量素子の第1電極、及び第8絶縁ゲート型トランジスタのゲートに電気的に接続され、第2端子が第3の配線に電気的に接続され、第12絶縁ゲート型トランジスタは、ゲートが第1の配線に電気的に接続され、第1端子が第2の配線に電気的に接続され、第2端子が第13絶縁ゲート型トランジスタの第1端子及び第9絶縁ゲート型トランジスタのゲートに電気的に接続され、第13絶縁ゲート型トランジスタは、第2端子が第3の配線に電気的に接

50

続されている半導体装置でもよい。

【0017】

本発明の一態様において、バッファ回路は、第10乃至第13絶縁ゲート型トランジスタを有し、第10絶縁ゲート型トランジスタは、ゲートが第2絶縁ゲート型トランジスタのゲート、第7絶縁ゲート型トランジスタの第1端子、及び第8絶縁ゲート型トランジスタの第1端子に電気的に接続され、第1端子が第2の配線に電気的に接続され、第2端子が第11絶縁ゲート型トランジスタの第1端子及び第13絶縁ゲート型トランジスタのゲートに電気的に接続され、第11絶縁ゲート型トランジスタは、ゲートが第4絶縁ゲート型トランジスタのゲート、第5絶縁ゲート型トランジスタの第1端子、第6絶縁ゲート型トランジスタの第1端子、容量素子の第1電極、第8絶縁ゲート型トランジスタのゲート、及び第12絶縁ゲート型トランジスタのゲートに電気的に接続され、第2端子が第3の配線に電気的に接続され、第12絶縁ゲート型トランジスタは、第1端子が第2の配線に電気的に接続され、第2端子が第13絶縁ゲート型トランジスタの第1端子及び第9絶縁ゲート型トランジスタのゲートに電気的に接続され、第13絶縁ゲート型トランジスタは、第2端子が第3の配線に電気的に接続されている半導体装置でもよい。

10

【0018】

本発明の一態様において、第1の高電源電位と第2の高電源電位は、等電位である半導体装置でもよい。

【発明の効果】

【0019】

20

本発明の一形態によれば、プロセスの複雑化を招くことなく、印加する電圧への耐圧を向上させ、サイリスタとしての機能を実現することの出来る半導体装置を提供することができる。

【図面の簡単な説明】

【0020】

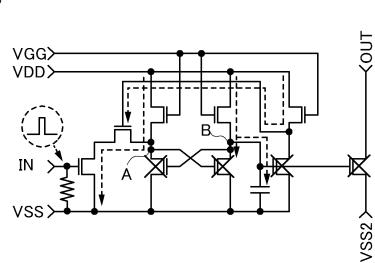

【図1】本発明の一態様の半導体装置を説明する図。

30

【図2】本発明の一態様の半導体装置を説明する図。

【図3】本発明の一態様の半導体装置を説明する図。

【図4】本発明の一態様の半導体装置を説明する図。

【図5】本発明の一態様の半導体装置を説明する図。

【図6】本発明の一態様の半導体装置を説明する図。

【図7】本発明の一態様の半導体装置を説明する図。

【図8】本発明の一態様の半導体装置を説明する図。

【図9】本発明の一態様の半導体装置を説明する図。

【図10】本発明の一態様の半導体装置を説明する図。

【図11】半導体装置の応用例を説明する図。

【図12】サイリスタを説明する図。

【発明を実施するための形態】

【0021】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じ物を指し示す符号は異なる図面間において共通とする。

40

【0022】

なお、各実施の形態の図面等において示す各構成の、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケールに限定されない。

【0023】

なお本明細書にて用いる第1、第2、第3、乃至第N（Nは自然数）という用語は、構成

50

要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

**【0024】**

(実施の形態1)

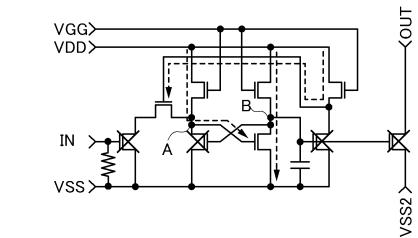

本実施の形態では、半導体装置の回路構成について図1乃至図4を参照して説明し、次いで、その動作について説明していくことにする。

**【0025】**

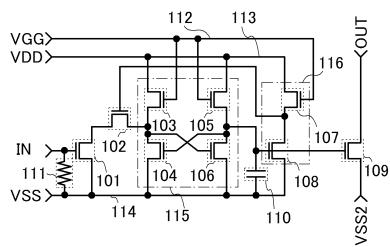

図1において、本実施の形態で示すサイリスタと同等の機能を有する半導体装置は、第1絶縁ゲート型トランジスタ101、第2絶縁ゲート型トランジスタ102、第3絶縁ゲート型トランジスタ103、第4絶縁ゲート型トランジスタ104、第5絶縁ゲート型トランジスタ105、第6絶縁ゲート型トランジスタ106、第7絶縁ゲート型トランジスタ107、第8絶縁ゲート型トランジスタ108、第9絶縁ゲート型トランジスタ109、容量素子110、抵抗素子111を有する。半導体装置が有する各素子は、入力端子INに供給されるトリガー信号、第1の配線112に供給される第1の高電源電位VGG、第2の配線113に供給される第2の高電源電位VDD、第3の配線114に供給される低電源電位VSS(第1の低電源電位ということもある)によって、第9絶縁ゲート型トランジスタ109の第1端子と第2端子との間を流れる電流を制御する。なお半導体装置を構成する第1絶縁ゲート型トランジスタ乃至第9絶縁ゲート型トランジスタはnチャネル型の絶縁ゲート型トランジスタである。

**【0026】**

第1絶縁ゲート型トランジスタ101は、ゲートが入力端子INに接続され、第1端子が第3の配線114に接続され、第2端子が第2絶縁ゲート型トランジスタ102の第1端子に接続される。第2絶縁ゲート型トランジスタ102は、ゲートが第7絶縁ゲート型トランジスタ107の第1端子及び第8絶縁ゲート型トランジスタ108の第1端子に接続され、第2端子が、第3絶縁ゲート型トランジスタ103の第1端子、第4絶縁ゲート型トランジスタ104の第1端子、及び第6絶縁ゲート型トランジスタ106のゲートに接続される。第3絶縁ゲート型トランジスタ103は、ゲートが第1の配線112に接続され、第2端子が第2の配線113に接続される。第4絶縁ゲート型トランジスタ104は、ゲートが第5絶縁ゲート型トランジスタ105の第1端子、第6絶縁ゲート型トランジスタ106の第1端子、容量素子110の第1電極、第8絶縁ゲート型トランジスタ108のゲート、及び第9絶縁ゲート型トランジスタ109のゲートに接続され、第2端子が第3の配線114に接続される。第5絶縁ゲート型トランジスタ105は、ゲートが第1の配線112に接続され、第2端子が第2の配線113に接続される。第6絶縁ゲート型トランジスタ106は、第2端子が第3の配線114に接続される。第7絶縁ゲート型トランジスタ107は、ゲートが第1の配線112に接続され、第2端子が第2の配線113に接続される。第8絶縁ゲート型トランジスタ108は、第2端子が第3の配線114に接続される。第9絶縁ゲート型トランジスタ109は、第1端子が出力端子OUTに接続され、第2端子が第2の低電源電位VSS2が供給される端子に接続される。容量素子110は、第2電極が第3の配線114に接続される。

**【0027】**

なお、第3絶縁ゲート型トランジスタ103及び第4絶縁ゲート型トランジスタ104、並びに第5絶縁ゲート型トランジスタ105及び第6絶縁ゲート型トランジスタ106によってインバータ回路が形成され、インバータ回路を組み合わせることによって、スタティックなメモリ回路115を構成している。また、第7絶縁ゲート型トランジスタ107及び第8絶縁ゲート型トランジスタ108によりインバータ回路116を構成している。そのため、インバータ回路を構成する、第3絶縁ゲート型トランジスタ103、第5絶縁ゲート型トランジスタ105、及び第7絶縁ゲート型トランジスタ107は、それぞれ第2の配線113より電流を流すための抵抗素子(または一定の電流を流すための定電流源ともいう)として機能すればよい。また、第9絶縁ゲート型トランジスタ109の第2端子に供給される第2の低電源電位VSS2は、第9絶縁ゲート型トランジスタ109のゲ

10

20

30

40

50

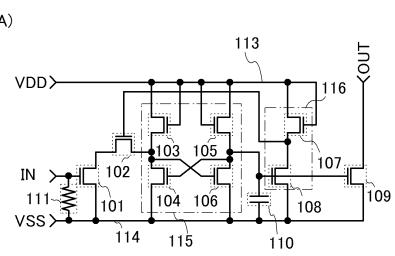

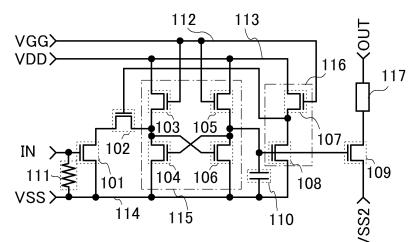

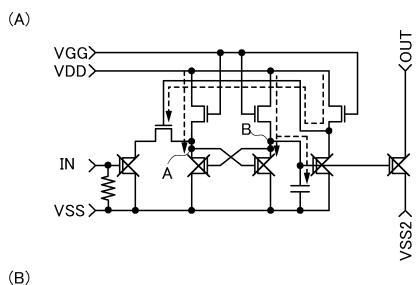

ートに第2の高電源電位VDDに基づく電位が供給された際に第9絶縁ゲート型トランジスタT09を導通させる電位であればよく、低電源電位VSSであってもよい。すなわち、図1に記載の半導体装置は、図2(A)に示すように、第1の高電源電位VGGが供給される第1の配線112を省略し、及び/または第2の低電源電位VSS2が供給される端子を、第1の低電源電位VSSが供給される第3の配線114に接続する構成としてもよい。

#### 【0028】

また第9絶縁ゲート型トランジスタT09の第1端子に接続された出力端子OUTには、図2(B)に示すように負荷117が接続されていてもよい。第9絶縁ゲート型トランジスタT09の第1端子と第2端子との間が導通することで、負荷に電流が流れることとなる。10

#### 【0029】

また入力端子INと第3の配線114との間には抵抗素子111が設けられており、抵抗素子111の第1の端子が入力端子INに接続され、第2の端子が第3の配線114に接続されている。抵抗素子111を設けることにより、入力端子INにトリガー信号以外の信号(ノイズ等)が入力された際、第1絶縁ゲート型トランジスタT01が誤動作することを防止することが出来る。抵抗素子111としては、半導体層をメアンダ状、または蛇行させて引き回すことにより形成すればよい。

#### 【0030】

容量素子110は、第3絶縁ゲート型トランジスタT03の第1端子側のノードの容量値と、第5絶縁ゲート型トランジスタT05の第1端子側のノードの容量値とを異ならせるために設けるものである。容量素子110としては、絶縁層を導電体で挟持する構造により形成すればよい。また第3絶縁ゲート型トランジスタT03及び第5絶縁ゲート型トランジスタT05は、同じ大きさの絶縁ゲート型トランジスタとすることが好ましい。20

#### 【0031】

なお半導体装置を構成する各絶縁ゲート型トランジスタの半導体層として、酸化物半導体を用いる。酸化物半導体を絶縁ゲート型トランジスタの半導体層として用いることにより、アモルファスシリコン等のシリコン系半導体材料と比較して電界効果移動度を高めることが出来る。また単結晶半導体基板内にpn接合を組み合わせてサイリスタを構成する場合に比べ、酸化物半導体を絶縁ゲート型トランジスタの半導体層として用いる絶縁ゲート型トランジスタでは基板上に構成材料を積層して形成することとなる。そのため半導体装置の作成の際、基板面積等の制限、プロセスの複雑化が低減されることとなる。なお酸化物半導体としては、例えば、酸化亜鉛(ZnO)、酸化スズ(SnO<sub>2</sub>)なども用いることができる。また、ZnOにInやGaなどを添加することもできる。30

#### 【0032】

次いで本実施の形態の構成において、各絶縁ゲート型トランジスタの半導体層に用いる酸化物半導体層について説明する。

#### 【0033】

本実施の形態で用いる酸化物半導体は、酸化物半導体に含まれる水素が $1 \times 10^{-6} / cm^3$ 以下となるように、酸化物半導体に含まれる水素若しくはOH基の除去をする。そしてキャリア濃度を $5 \times 10^{14} / cm^3$ 未満、好ましくは $1 \times 10^{12} / cm^3$ 未満、より好ましくは $1 \times 10^{11} / cm^3$ 以下とした酸化物半導体膜でチャネル領域が形成される絶縁ゲート型トランジスタが構成されるものである。なお、酸化物半導体層中の水素濃度測定は、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectroscopy)で行えばよい。40

#### 【0034】

エネルギーギャップは2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上として、ドナーを形成する水素等の不純物を極力低減し、キャリア濃度を $1 \times 10^{14} / cm^3$ 未満、好ましくは $1 \times 10^{12} / cm^3$ 未満、より好ましくは $1 \times 10^{11} / cm^3$ 以下となるようにする。即ち、酸化物半導体層のキャリア濃度は、限りなくゼロに50

する。

**【0035】**

このように酸化物半導体層に含まれる水素を徹底的に除去することにより高純度化された酸化物半導体層を絶縁ゲート型トランジスタのチャネル形成領域に用いた絶縁ゲート型トランジスタは、オフ電流が  $1 \times 10^{-16} \text{ A}$  以下とすることができます。つまり絶縁ゲート型トランジスタの非導通状態において、酸化物半導体層は絶縁体とみなせて回路設計を行うことができる。一方で、酸化物半導体層は、絶縁ゲート型トランジスタの導通状態においては、非晶質シリコンで形成される半導体層よりも高い電流供給能力を見込むことができる。

**【0036】**

なお本明細書で説明するオフ電流とは、絶縁ゲート型トランジスタが非導通状態（オフ状態ともいう）のときに、ソースとドレインとの間、すなわち第1端子と第2端子との間に流れる電流をいう。nチャネル型の絶縁ゲート型トランジスタでは、ゲートとソースとの間に印加される電圧が閾値電圧（ $V_{th}$ ）以下の場合に、ソースとドレインとの間を流れ電流のことをいう。

**【0037】**

なお酸化物半導体膜としては、四元系金属酸化物である In - Sn - Ga - Zn - O 膜や、三元系金属酸化物である In - Ga - Zn - O 膜、In - Sn - Zn - O 膜、In - Al - Zn - O 膜、Sn - Ga - Zn - O 膜、Al - Ga - Zn - O 膜、Sn - Al - Zn - O 膜や、二元系金属酸化物である In - Zn - O 膜、Sn - Zn - O 膜、Al - Zn - O 膜、Zn - Mg - O 膜、Sn - Mg - O 膜、In - Mg - O 膜や、In - O 膜、Sn - O 膜、Zn - O 膜などの酸化物半導体膜を用いることができる。また、上記酸化物半導体膜に SiO<sub>2</sub> を含んでもよい。

**【0038】**

また、酸化物半導体膜は、InMO<sub>3</sub> (ZnO)<sub>m</sub> ( $m > 0$ ) で表記される薄膜を用いることができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。InMO<sub>3</sub> (ZnO)<sub>m</sub> ( $m > 0$ ) で表記される構造の酸化物半導体のうち、MとしてGaを含む構造の酸化物半導体を、上記した In - Ga - Zn - O 酸化物半導体とよび、その薄膜を In - Ga - Zn - O 膜ともよぶこととする。

**【0039】**

なお第1の高電源電位VGG及び第2の高電源電位VDDとは、基準電位より高い電位の信号のことであり、低電源電位VSS、第2の低電源電位VSS2とは基準電位以下の電位の信号のことをいう。なお第1の高電源電位VGG、第2の高電源電位VDD、低電源電位VSS、第2の低電源電位VSS2とともに、絶縁ゲート型トランジスタが動作できる程度の電位、すなわち高電源電位に基づく信号がゲートに印加されることで理想的な絶縁ゲート型トランジスタ（しきい値電圧が0V）がオン状態となり、低電源電位に基づく信号が印加されることで理想的な絶縁ゲート型トランジスタがオフ状態となる電位であることが望ましい。

**【0040】**

なお、電圧とは、ある電位と、基準の電位（例えばグラウンド電位）との電位差のことを示す場合が多い。よって、電圧、電位、電位差を、各々、電位、電圧と言い換えることが可能である。

**【0041】**

なお、絶縁ゲート型トランジスタの構成は、様々な形態をとることができ、特定の構成に限定されない。例えば、ゲート電極が2個以上のマルチゲート構造を適用することができる。

**【0042】**

また、チャネル領域の上下にゲート電極が配置されている構造を適用することができる。なお、チャネル領域の上下にゲート電極が配置される構成にすることにより、複数の絶縁

10

20

30

40

50

ゲート型トランジスタが並列に接続されたような構成とすることも可能である。

#### 【0043】

なお、AとBとが接続されている、と明示的に記載する場合は、AとBとが電気的に接続されている場合と、AとBとが機能的に接続されている場合と、AとBとが直接接続されている場合とを含むものとする。ここで、A、Bは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層など）であるとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも含むものとする。

#### 【0044】

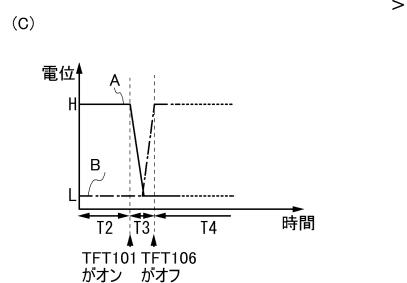

ついで図1に示すサイリスタと同等の機能を有する半導体装置の動作について図3及び図4を用いて説明する。なお図3、及び図4での説明において、第2絶縁ゲート型トランジスタ102の第2端子、第3絶縁ゲート型トランジスタ103の第1端子、第4絶縁ゲート型トランジスタ104の第1端子、及び第6絶縁ゲート型トランジスタ106のゲートの接続されたノードをノードA（図中、A）と略記する。また図3、及び図4での説明において、第4絶縁ゲート型トランジスタ104のゲート、第5絶縁ゲート型トランジスタ105の第1端子、第6絶縁ゲート型トランジスタ106の第1端子、容量素子110の第1電極、第8絶縁ゲート型トランジスタ108のゲート、及び第9絶縁ゲート型トランジスタ109のゲートの接続されたノードをノードB（図中、B）と略記する。

10

#### 【0045】

まず第1の配線112乃至第3の配線114に各電源電位が供給されることによって、ノードA及びノードBが所定の電位になる動作について説明する。なお、当該動作をリセット動作（または第1の動作ともいう）ともいう。

20

#### 【0046】

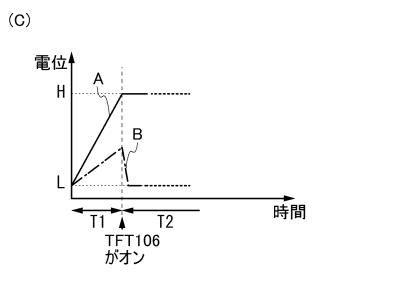

まず、第1の配線112に第1の高電源電位VGG、第2の配線113に第2の高電源電位VDD、第3の配線114に低減源電位VSSが供給されることによって、第3絶縁ゲート型トランジスタ103、第5絶縁ゲート型トランジスタ105、及び第7絶縁ゲート型トランジスタ107を介して、第2の配線113より電流が流れる（図3（A）点線矢印参照）。そして、第3絶縁ゲート型トランジスタ103に流れる電流によりノードAの電位が上昇する。また、第5絶縁ゲート型トランジスタ105に流れる電流によりノードBの電位が上昇する。また第7絶縁ゲート型トランジスタ107に流れる電流により第2絶縁ゲート型トランジスタ102のゲートの電位が上昇する。なお当該動作は、図3（C）の第1の期間T1に相当するものである。図3（C）は時間に応じた電位の変化について、ノードAの電位を実線、ノードBの電位を一点鎖線で示している。

30

#### 【0047】

なお、図3（C）では、第2の配線113に供給される第2の高電源電位VDDに基づく電位を”H”と示し、第3の配線113に供給される低電源電位VSSに基づく電位を”L”と示している。

#### 【0048】

第1の期間T1での電流の流れによって、第3絶縁ゲート型トランジスタ103に流れる電流によるノードAの電位の上昇と、第5絶縁ゲート型トランジスタ105に流れる電流によるノードBの電位の上昇とでは、図3（C）に示すように、電位の上昇勾配が異なることとなる。先に説明したように、第3絶縁ゲート型トランジスタ103及び第5絶縁ゲート型トランジスタ105と同じ大きさの絶縁ゲート型トランジスタとして供給される電流量は変わらないものの、ノードBには容量素子110が設けられることで電位の上昇勾配がノードAに比べて緩やかとなる。

40

#### 【0049】

また第1の期間T1では、第7絶縁ゲート型トランジスタ107に流れる電流により第2絶縁ゲート型トランジスタ102のゲートの電位が上昇し、第2絶縁ゲート型トランジスタ102が導通状態となる。なお入力端子INには、第1絶縁ゲート型トランジスタ101を導通状態とするためのトリガー信号が入力されないため、第1絶縁ゲート型トランジ

50

スタ 1 0 1 は非導通状態となる。また第 1 の期間 T 1 では、ノード A 及びノード B の電位が上昇過程にあり、第 4、第 6、第 8、及び第 9 絶縁ゲート型トランジスタは非導通状態となる。なお説明のため、図 3 (A)、(B)、図 4 (A)、(B) では非導通状態の絶縁ゲート型トランジスタについて、×印を付している。

#### 【 0 0 5 0 】

次いで、ノード A 及びノード B の電位が上昇することで、各絶縁ゲート型トランジスタの導通状態または非導通状態が変化する動作について説明する。なお、当該動作を初期化動作（または第 2 の動作ともいう）ともいう。

#### 【 0 0 5 1 】

第 1 の期間 T 1 での説明のように、ノード A とノード B との電位の上昇勾配に差が生じることで、ノード A が先に電位 “H” となる。すると第 6 絶縁ゲート型トランジスタ 1 0 6 が導通状態となり、ノード B の電位が電位 “L” に下降することとなる（図 3 (B) 点線矢印参照）。またノード B の電位が電位 “L” となることで、第 4 絶縁ゲート型トランジスタ 1 0 4、第 8 絶縁ゲート型トランジスタ 1 0 8、及び第 9 絶縁ゲート型トランジスタ 1 0 9 が非導通状態を保持することとなる。なお当該動作は、図 3 (C) の第 2 の期間 T 2 に相当するものである。10

#### 【 0 0 5 2 】

第 2 の期間 T 2 での電流の流れによって、ノード A とノード B の電位を制御する第 4 絶縁ゲート型トランジスタ 1 0 4 及び第 6 絶縁ゲート型トランジスタ 1 0 6 の導通状態、または非導通状態が確定することとなる。具体的には、ノード A では電位 “H” を保持し、ノード B では電位 “L” を保持し続けることとなる。即ち、第 1 の配線 1 1 2 からの第 1 の高電源電位 VGG、第 2 の配線 1 1 3 からの第 2 の高電源電位 VDD、第 3 の配線 1 1 4 からの低電源電位 VSS の供給がある限り、第 2 の期間 T 2 では上述の電位を保持することとなる。そのため、第 9 絶縁ゲート型トランジスタ 1 0 9 は非導通状態を保持することとなる。絶縁ゲート型トランジスタの非導通状態においては、半導体層に酸化物半導体を用いた場合、酸化物半導体層は絶縁体とみなすことができ、出力端子 OUT より流れる電流を小さく保持することができる。20

#### 【 0 0 5 3 】

また第 2 の期間 T 2 では、第 1 の期間 T 1 と同様に、第 7 絶縁ゲート型トランジスタ 1 0 7 に流れる電流により第 2 絶縁ゲート型トランジスタ 1 0 2 のゲートの電位が上昇し、第 2 絶縁ゲート型トランジスタ 1 0 2 が導通状態となる。なお入力端子 IN には、第 1 絶縁ゲート型トランジスタ 1 0 1 を導通状態とするためのトリガー信号が入力されないため、第 1 絶縁ゲート型トランジスタ 1 0 1 は非導通状態となる。30

#### 【 0 0 5 4 】

次いで、入力端子 IN よりトリガー信号を入力した際のノード A 及びノード B の電位の変化により、各絶縁ゲート型トランジスタの導通状態または非導通状態が変化する動作について説明する。なお、当該動作をトリガー入力動作（または第 3 の動作ともいう）ともいう。

#### 【 0 0 5 5 】

なおトリガー信号は、第 1 絶縁ゲート型トランジスタ 1 0 1 を導通状態とするためのパルス信号であり、具体的には、サイリスタとして機能する半導体装置の出力端子 OUT、即ち第 9 絶縁ゲート型トランジスタ 1 0 9 に電流を流すために、トリガー信号として H 信号が入力されるものとなる。なお、一旦半導体装置の出力端子 OUT に電流が流れた後は、サイリスタと同様にトリガー信号を L 信号としても、出力端子 OUT は電流を流し続ける動作を保持することとなる。40

#### 【 0 0 5 6 】

第 2 の期間 T 2 での説明のように、初期化動作により、ノード A では電位 “H” を保持し、ノード B では電位 “L” を保持した状態となっている。そこに入力端子 IN よりトリガー信号が供給されると、第 1 絶縁ゲート型トランジスタ 1 0 1 及び第 2 絶縁ゲート型トランジスタ 1 0 2 が導通状態となり、ノード A より第 3 の配線 1 1 4 に向けて電流が流れる50

こととなる(図4(A)点線矢印参照)。すなわち、ノードAの電位が下降することとなり、電位“L”まで下降すると、第6絶縁ゲート型トランジスタ106が非導通状態となる。なお当該動作は、図4(C)の第3の期間T3に相当するものである。

#### 【0057】

次いで、入力端子INより入力したトリガー信号がL信号となった際の各絶縁ゲート型トランジスタの導通状態または非導通状態が変化する動作について説明する。なお、当該動作を保持動作(または第4の動作ともいう)ともいう。

#### 【0058】

第3の期間T3での説明のように、トリガー入力動作により、ノードAの電位が電位“L”に低下し、第6絶縁ゲート型トランジスタ106が非導通状態となる。第6絶縁ゲート型トランジスタ106が非導通状態となると、ノードBの電位が電位“L”から上昇し、電位“H”となる。そしてノードBの電位が電位“H”になると、第4絶縁ゲート型トランジスタ104が導通状態となり、ノードAとノードBの電位を制御する第4絶縁ゲート型トランジスタ104及び第6絶縁ゲート型トランジスタ106の導通状態、または非導通状態が確定することとなる(図4(B)点線矢印参照)。その結果、第4絶縁ゲート型トランジスタ104、第8絶縁ゲート型トランジスタ108、及び第9絶縁ゲート型トランジスタ109が導通状態となる。なお当該動作は、図4(C)の第4の期間T4に相当するものである。

#### 【0059】

なお第4の期間T4においては、トリガー信号はL信号となり、第1絶縁ゲート型トランジスタ101は非導通状態となる。また第4の期間T4においては、第8絶縁ゲート型トランジスタ108が導通状態となることで、第2絶縁ゲート型トランジスタ102のゲートの電位が下降し、第2絶縁ゲート型トランジスタ102が非導通状態となる。

#### 【0060】

以上の動作により、第9絶縁ゲート型トランジスタ109は導通状態を保持することとなる。なお出力端子OUTより流れる電流値によるが、第9絶縁ゲート型トランジスタ109は、流れる電流値が大きくなるよう、他の第1乃至第8絶縁ゲート型トランジスタより、半導体層の幅を大きく設計しておくことが好ましい。酸化物半導体層は、絶縁ゲート型トランジスタの導通状態においては、非晶質シリコンで形成される半導体層よりも高い電流供給能力を見込むことができ好適である。

#### 【0061】

なお第9絶縁ゲート型トランジスタ109が導通状態になってから再度非導通状態にする際は、第1の配線112乃至第3の配線114への各電源電位の供給を停止する動作を行えばよい。なお当該動作を停止動作ともいう。そして再度動作させる際は、上述の動作をリセット動作として行えばよい。

#### 【0062】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【0063】

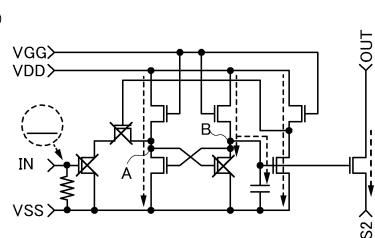

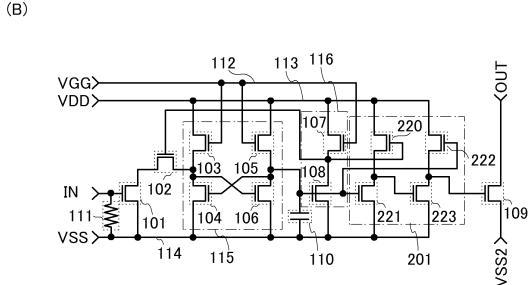

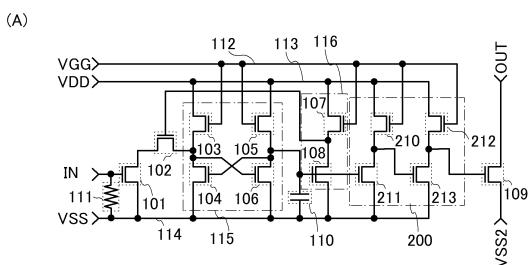

(実施の形態2)

本実施の形態では、半導体装置の回路構成について図5を参照して説明する。本実施の形態では、上記実施の形態1において、第4絶縁ゲート型トランジスタ104のゲート、第5絶縁ゲート型トランジスタ105の第1端子、第6絶縁ゲート型トランジスタ106の第1端子、容量素子110の第1電極、及び第8絶縁ゲート型トランジスタ108のゲートが電気的に接続されたノードと、第9絶縁ゲート型トランジスタ109のゲートとの間に、バッファ回路を設ける構成について説明する。なお、半導体装置の動作等、実施の形態1と同様の箇所については説明を省略するものとする。

#### 【0064】

図5(A)に示すサイリスタと同等の機能を有する半導体装置が、実施の形態1の図1で説明した半導体装置と異なる点は、バッファ回路200を有する点にある。図5(A)に

10

20

30

40

50

示すバッファ回路 200 は、第 10 絶縁ゲート型トランジスタ 210、第 11 絶縁ゲート型トランジスタ 211、第 12 絶縁ゲート型トランジスタ 212、第 13 絶縁ゲート型トランジスタ 213 を有する。第 10 絶縁ゲート型トランジスタ 210 は、ゲートが第 1 の配線 112 に接続され、第 1 端子が第 2 の配線 113 に接続され、第 2 端子が第 11 絶縁ゲート型トランジスタ 211 の第 1 端子及び第 13 絶縁ゲート型トランジスタ 213 のゲートに接続される。第 11 絶縁ゲート型トランジスタ 211 は、ゲートが第 4 絶縁ゲート型トランジスタ 104 のゲート、第 5 絶縁ゲート型トランジスタ 105 の第 1 端子、第 6 絶縁ゲート型トランジスタ 106 の第 1 端子、容量素子 110 の第 1 電極、及び第 8 絶縁ゲート型トランジスタ 108 のゲートに接続され、第 2 端子が第 3 の配線 114 に接続される。第 12 絶縁ゲート型トランジスタ 212 は、ゲートが第 1 の配線 112 に接続され、第 1 端子が第 2 の配線 113 に接続され、第 2 端子が第 13 絶縁ゲート型トランジスタ 213 の第 1 端子及び第 9 絶縁ゲート型トランジスタ 109 のゲートに接続される。第 13 絶縁ゲート型トランジスタ 213 は、第 2 端子が第 3 の配線 114 に接続される。

10

## 【0065】

図 5 (A) に示すようにバッファ回路として、インバータ回路 116 のようなインバータ回路を偶数段 (図 5 (A) では 2 段) 組み合わせた構成とすることにより、絶縁ゲート型トランジスタサイズを順次大きくすることによる電流供給能力の向上が見込め、第 9 絶縁ゲート型トランジスタ 109 の絶縁ゲート型トランジスタサイズを大きくして出力端子 OUT を流れる電流値を大きくすることができる。

## 【0066】

また図 5 (B) には、図 5 (A) と異なる構成のバッファ回路 201 を有する半導体装置の構成について示す。図 5 (B) に示すバッファ回路 201 は、第 10 絶縁ゲート型トランジスタ 220、第 11 絶縁ゲート型トランジスタ 221、第 12 絶縁ゲート型トランジスタ 222、第 13 絶縁ゲート型トランジスタ 223 を有する。第 10 絶縁ゲート型トランジスタ 220 は、ゲートが第 2 絶縁ゲート型トランジスタ 102 のゲート、第 7 絶縁ゲート型トランジスタ 107 の第 1 端子、及び第 8 絶縁ゲート型トランジスタ 108 の第 1 端子に接続され、第 1 端子が第 2 の配線 113 に接続され、第 2 端子が第 11 絶縁ゲート型トランジスタ 221 の第 1 端子及び第 13 絶縁ゲート型トランジスタ 223 のゲートに接続される。第 11 絶縁ゲート型トランジスタ 221 は、ゲートが第 4 絶縁ゲート型トランジスタ 104 のゲート、第 5 絶縁ゲート型トランジスタ 105 の第 1 端子、第 6 絶縁ゲート型トランジスタ 106 の第 1 端子、容量素子 110 の第 1 電極、第 8 絶縁ゲート型トランジスタ 108 のゲート、及び第 12 絶縁ゲート型トランジスタ 222 のゲートに接続され、第 2 端子が第 3 の配線 114 に接続される。第 12 絶縁ゲート型トランジスタ 222 は、第 1 端子が第 2 の配線 113 に接続され、第 2 端子が第 13 絶縁ゲート型トランジスタ 223 の第 1 端子及び第 9 絶縁ゲート型トランジスタ 109 のゲートに接続される。第 13 絶縁ゲート型トランジスタ 223 は、第 2 端子が第 3 の配線 114 に接続される。

30

## 【0067】

図 5 (B) に示すバッファ回路 201 では、インバータ回路 116 のようなインバータ回路とは異なり、第 10 絶縁ゲート型トランジスタ 220 と第 11 絶縁ゲート型トランジスタ 221、第 12 絶縁ゲート型トランジスタ 222 と第 13 絶縁ゲート型トランジスタ 223 が共に導通状態となる期間を削減することができ、保持動作時において第 2 の配線 113 から第 3 の配線 114 に流れる電流を低減することができる。

40

## 【0068】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

## 【0069】

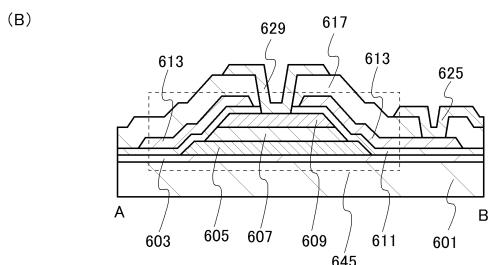

## (実施の形態 3)

本実施の形態では、上記実施の形態の絶縁ゲート型トランジスタに用いられる、絶縁ゲート型トランジスタの構造について、図 6 を用いて説明する。

## 【0070】

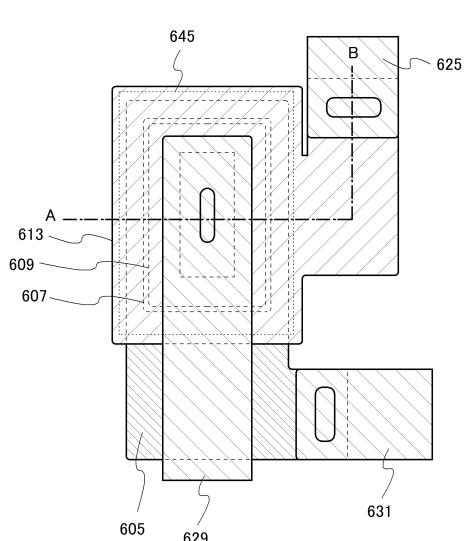

図6(A)は絶縁ゲート型トランジスタ645の上面図であり、図6(B)は図6(A)の一点鎖線A-Bの断面図に相当する。

#### 【0071】

図6(B)に示すように、基板601上に形成された絶縁膜603上に、第1の電極605、酸化物半導体膜607、及び第2の電極609が積層される。また、第1の電極605、酸化物半導体膜607、及び第2の電極609を覆うように、ゲート絶縁膜611が設けられている。ゲート絶縁膜611上には、第3の電極613が設けられている。ゲート絶縁膜611及び第3の電極613上には層間絶縁膜として機能する絶縁膜617が設けられている。絶縁膜617には、開口部が形成されており、開口部において第1の電極605と接続する配線631(図6(A)参照)、第2の電極609と接続する配線629、第3の電極613と接続する配線625が形成される。

10

#### 【0072】

第1の電極605は、絶縁ゲート型トランジスタ645のソース電極またはドレイン電極の一方として機能する。第2の電極609は、絶縁ゲート型トランジスタ645のソース電極またはドレイン電極の他方として機能する。第3の電極613は、絶縁ゲート型トランジスタ645のゲート電極として機能する。

#### 【0073】

本実施の形態では、ゲート電極として機能する第3の電極613が環状であることを特徴とする。ゲート電極として機能する第3の電極613を環状とすることで、絶縁ゲート型トランジスタのチャネル幅を大きくすることができます。このため、絶縁ゲート型トランジスタを流れる電流値を大きくすることができます。

20

#### 【0074】

基板601は、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。基板601としては、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

#### 【0075】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いるとよい。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。一般に酸化ホウ素( $B_2O_3$ )と比較して酸化バリウム( $BaO$ )を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$ より $BaO$ を多く含むガラス基板を用いることが好ましい。

30

#### 【0076】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いてもよい。他にも、結晶化ガラスなどを用いることができる。

#### 【0077】

絶縁膜603は、酸化シリコン膜、酸化窒化シリコン膜など酸化物絶縁膜、または窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などの窒化物絶縁膜で形成する。また、絶縁膜603は積層構造でもよく、例えば、基板601側から上記した窒化物絶縁膜のいずれか一つ以上と、上記した酸化物絶縁膜のいずれか一つ以上の積層構造とすることができます。

40

#### 【0078】

第1の電極605及び第2の電極609は、Al、Cu、Cr、Ta、Ti、Mo、Wなどの金属材料、または該金属材料を成分とする合金材料などで形成する。また、Al、Cuなどの金属層の上面及び下面の一方または双方にCr、Ta、Ti、Mo、Wなどの高融点金属層を積層させた構成としても良い。また、Al膜に生ずるヒロックやウィスカの発生を防止する元素(Si、Ti、Ta、W、Mo、Cr、Nd、Sc、Y)が添加されているAl材料を用いることで耐熱性を向上させることができる。また、第1の電極605は、単層構造、または二層以上の積層構造とすることができます。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、

50

タンゲステン膜上にチタン膜を積層する二層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造などが挙げられる。また、アルミニウムに、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素を単数、または複数組み合わせた膜、合金膜、もしくは窒化膜を用いてもよい。

#### 【0079】

また第1の電極605及び第2の電極609は導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )、酸化インジウム酸化スズ合金( $In_2O_3-SnO_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛合金( $In_2O_3-ZnO$ )または金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。10

#### 【0080】

酸化物半導体膜607としては、四元系金属酸化物である $In-Sn-Ga-Zn-O$ 膜や、三元系金属酸化物である $In-Ga-Zn-O$ 膜、 $In-Sn-Zn-O$ 膜、 $In-Al-Zn-O$ 膜、 $Sn-Ga-Zn-O$ 膜、 $Al-Ga-Zn-O$ 膜、 $Sn-Al-Zn-O$ 膜や、二元系金属酸化物である $In-Zn-O$ 膜、 $Sn-Zn-O$ 膜、 $Al-Zn-O$ 膜、 $Zn-Mg-O$ 膜、 $Sn-Mg-O$ 膜、 $In-Mg-O$ 膜や、 $In-O$ 膜、 $Sn-O$ 膜、 $Zn-O$ 膜などの酸化物半導体膜を用いることができる。また、上記酸化物半導体膜中に $SiO_2$ を含んでもよい。

#### 【0081】

また、酸化物半導体膜607は、 $InMO_3(ZnO)_m$ ( $m > 0$ )で表記される薄膜を用いることができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。 $InMO_3(ZnO)_m$ ( $m > 0$ )で表記される構造の酸化物半導体のうち、MとしてGaを含む構造の酸化物半導体を、上記した $In-Ga-Zn-O$ 酸化物半導体とよび、その薄膜を $In-Ga-Zn-O$ 膜ともよぶこととする。20

#### 【0082】

本実施の形態で用いる酸化物半導体膜607は、酸化物半導体膜に含まれる水素が $5 \times 10^{-19} / cm^3$ 以下、好ましくは $5 \times 10^{-18} / cm^3$ 以下、より好ましくは $5 \times 10^{-17} / cm^3$ 以下であり、酸化物半導体膜に含まれる水素が除去されている。即ち、酸化物半導体膜の主成分以外の不純物が極力含まれないように高純度化されている。また、酸化物半導体膜607のキャリア濃度が $5 \times 10^{14} / cm^3$ 以下、好ましくは $1 \times 10^{14} / cm^3$ 以下、好ましくは $5 \times 10^{12} / cm^3$ 以下、好ましくは $1 \times 10^{12} / cm^3$ 以下である。即ち、酸化物半導体膜のキャリア濃度は、限りなくゼロに近い。また、エネルギーギャップは2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。なお、酸化物半導体膜中の水素濃度は、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectroscopy)で検出することができる。また、キャリア濃度は、ホール効果測定により測定することができる。

#### 【0083】

酸化物半導体膜607の厚さは、30nm以上3000nm以下とするとよい。酸化物半導体膜607の厚さを薄くすることで、絶縁ゲート型トランジスタのチャネル長を小さくすることが可能であり、オン電流及び電界効果移動度の高い絶縁ゲート型トランジスタを作製することができる。一方、酸化物半導体膜607の厚さを厚くすることで、代表的には100nm以上3000nm以下とすることで、大電力用の半導体装置を作製することができる。40

#### 【0084】

ゲート絶縁膜611は、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、または酸化アルミニウム膜を単層でまたは積層して形成することができる。ゲート絶縁膜611は、酸化物半導体膜607と接する部分が酸素を含むことが好ましく、特に好ましくは酸化シリコン膜により形成する。酸化シリコン膜を用いることで、酸50

化物半導体膜 607 に酸素を供給することができ、特性を良好にすることができる。

【0085】

また、ゲート絶縁膜 611 として、ハフニウムシリケート ( $HfSiO_x$ )、N が添加された  $HfSiO_xNy$ 、ハフニウムアルミネート ( $HfAlO_x$ )、酸化ハフニウム、酸化イットリウムなどの  $hig h-k$  材料を用いることでゲートリーク電流を低減できる。さらには、 $hig h-k$  材料と、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、または酸化アルミニウム膜のいずれか一以上との積層構造とすることができる。ゲート絶縁膜 611 の厚さは、50 nm 以上 500 nm 以下とするとい。ゲート絶縁膜 611 の厚さを薄くすることで、電界効果移動度の高い絶縁ゲート型トランジスタを作製することができ、駆動回路を同一基板に作製することができる。一方、ゲート絶縁膜 611 の厚さを厚くすることで、ゲートリーク電流を低減することができる。

10

【0086】

ゲート電極として機能する第 3 の電極 613 は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンゲステンから選ばれた元素、または上述した元素を成分とする合金や、上述した元素を組み合わせた合金膜などを用いて形成することができる。また、マンガン、マグネシウム、ジルコニウム、ベリリウムのいずれか一または複数から選択された材料を用いてもよい。また、第 3 の電極 613 は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造などがある。また、アルミニウムに、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素の膜、または複数組み合わせた合金膜、もしくは窒化膜を用いてもよい。

20

【0087】

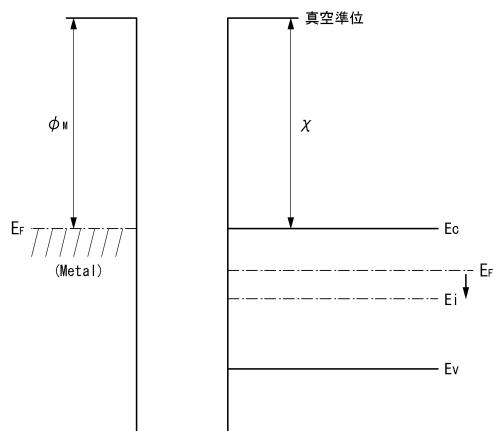

次に、酸化物半導体膜 607 を有する絶縁ゲート型トランジスタの動作について図 7 乃至図 10 を用いて説明する。

【0088】

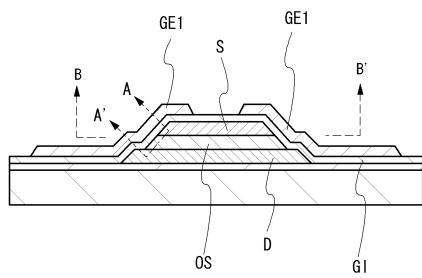

図 7 は、本実施の形態に示す酸化物半導体膜を用いた絶縁ゲート型トランジスタの断面図を示す。ドレイン電極 (D) 上に酸化物半導体膜 (OS) 及びソース電極 (S) が積層され、ドレイン電極、酸化物半導体膜、及びソース電極上にゲート絶縁膜 (GI) が設けられ、その上に分離されたゲート電極 (GE1) が設けられている。

30

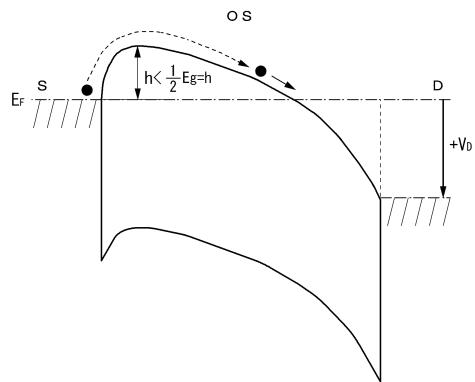

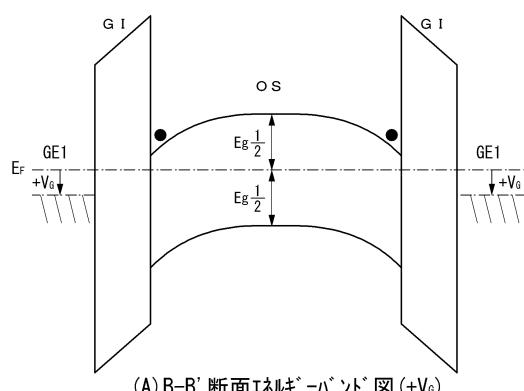

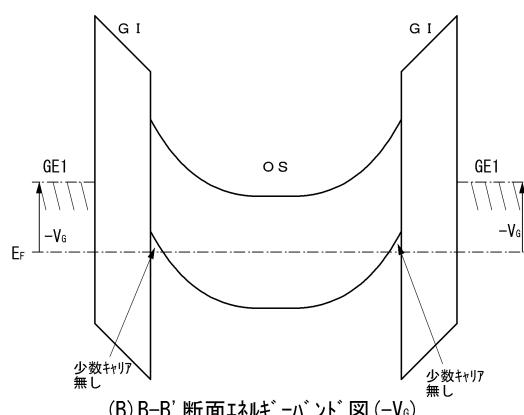

【0089】

図 8 は、図 7 に示す A - A' 断面におけるエネルギーバンド図（模式図）を示す。図 8 (A) はソースとドレインの間の電圧を等電位 ( $V_D = 0 V$ ) とした場合を示し、図 8 (B) はソースに対しドレインに正の電位 ( $V_D > 0$ ) を加えた場合を示す。

【0090】

図 9 は、図 7 における B - B' の断面におけるエネルギーバンド図（模式図）である。図 9 (A) はゲート (GE1) に正の電位 (+VG) が印加された状態であり、ソースとドレインとの間にキャリア（電子）が流れるオン状態（通電状態）を示している。また、図 9 (B) は、ゲート (GE1) に負の電位 (-VG) が印加された状態であり、オフ状態（非通電状態、少数キャリアは流れない状態）である場合を示す。

40

【0091】

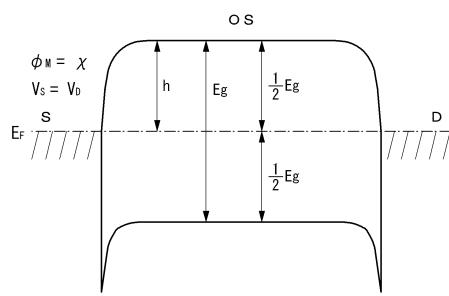

図 10 は、真空準位と金属の仕事関数 ( $\phi_M$ )、酸化物半導体膜の電子親和力 ( $\phi_A$ ) の関係を示す。

【0092】

金属は縮退しており、フェルミ準位は伝導帯内に位置する。一方、従来の酸化物半導体膜は一般に n 型であり、その場合のフェルミ準位 ( $E_f$ ) は、バンドギャップ中央に位置する真性フェルミ準位 ( $E_i$ ) から離れて、伝導帯寄りに位置している。なお、酸化物半導体膜において水素の一部はドナーとなり n 型化する一つの要因であることが知られている。

50

【0093】

これに対して本実施の形態に係る酸化物半導体膜は、n型不純物である水素を酸化物半導体膜から除去し、酸化物半導体膜の主成分以外の不純物が極力含まれないように高純度化することにより真性(i型)としたものである。すなわち、不純物を添加してi型化するのではなく、水素、水、水酸基または水素化物などの不純物を極力除去したことにより、高純度化されたi型(真性半導体)またはそれに近づけることを特徴としている。そうすることにより、フェルミ準位(Ef)は真性フェルミ準位(Ei)と同じレベルにすることができる。

#### 【0094】

酸化物半導体膜のバンドギャップ(Eg)が3.15eVである場合、電子親和力( )は4.3eVと言われている。ソース電極及びドレイン電極を構成するチタン(Ti)の仕事関数は、酸化物半導体膜の電子親和力( )とほぼ等しい。この場合、金属-酸化物半導体膜界面において、電子に対してショットキー型の障壁は形成されない。10

#### 【0095】

すなわち、金属の仕事関数(M)と酸化物半導体膜の電子親和力( )が等しい場合、両者が接触すると図8(A)で示すようなエネルギー-band図(模式図)が示される。

#### 【0096】

図8(B)において黒丸( )は電子を示し、ドレインに正の電位が印加されると、電子はバリア(h)を越えて酸化物半導体膜に注入され、ドレインに向かって流れる。この場合、バリア(h)の高さは、ゲート電圧とドレイン電圧に依存して変化するが、正のドレイン電圧が印加された場合には、電圧印加のない図8(A)のバリアの高さすなわちバンドギャップ(Eg)の1/2よりもバリアの高さ(h)は小さい値となる。20

#### 【0097】

このとき電子は、図9(A)で示すようにゲート絶縁膜と高純度化された酸化物半導体膜との界面における、酸化物半導体膜側のエネルギー的に安定な最低部を移動する。

#### 【0098】

また、図9(B)において、ゲート電極(GE1)に負の電位が印加されると、少数キャリアであるホールは実質的にゼロであるため、電流は限りなくゼロに近い値となる。

#### 【0099】

例えば、絶縁ゲート型トランジスタのチャネル幅Wが $1 \times 10^{-4} \mu m$ でチャネル長が $3 \mu m$ の素子であっても、常温におけるオフ電流が $1 \times 10^{-13} A$ 以下ときわめて低く、サブスレッショルドスイシング値(S値)が $0.1 V / dec.$ (ゲート絶縁膜厚 $100 nm$ )が得られる。30

#### 【0100】

このように、酸化物半導体膜の主成分以外の不純物、代表的には水素、水、水酸基または水素化物などが極力含まれないように高純度化することにより、絶縁ゲート型トランジスタの動作を良好なものとすることができます。特に、オフ電流を低減することができる。

#### 【0101】

ところで、チャネルが基板と概略平行に形成される横型絶縁ゲート型トランジスタにおいては、チャネルのほかにソース及びドレインを設ける必要があり、基板における絶縁ゲート型トランジスタの占有面積が大きくなってしまい、微細化の妨げとなる。しかしながら、縦型絶縁ゲート型トランジスタにおいては、ソース、チャネル、及びドレインを積層するため、基板表面における占有面積を低減することができる。この結果、絶縁ゲート型トランジスタの微細化が可能である。40

#### 【0102】

また、縦型絶縁ゲート型トランジスタのチャネル長は、酸化物半導体膜の厚さで制御できるため、酸化物半導体膜607の厚さを薄くすることでチャネル長の小さい絶縁ゲート型トランジスタとすることが可能である。チャネル長を小さくすることで、ソース、チャネル、及びドレインの直列抵抗を低減できるため、絶縁ゲート型トランジスタのオン電流および電界効果移動度を上昇させることができる。また、本実施の形態に示す絶縁ゲート型トランジスタのゲート電極は環状であり、チャネル幅を大きくすることが可能であるため50

、オン電流を上昇させることができる。また、水素濃度が低減され高純度化された酸化物半導体膜を有する絶縁ゲート型トランジスタは、オフ電流が極めて低く、オフ時では電流がほとんど流れない絶縁状態となる。このため、酸化物半導体膜の厚さを薄くし、縦型絶縁ゲート型トランジスタのチャネル長を小さくしても、非導通状態のオフ電流がほとんど無い絶縁ゲート型トランジスタとすることができます。

#### 【0103】

このように、水素濃度が低減され高純度化された酸化物半導体膜を用いることで、動作速度が速く、オン時には大電流を流すことができ、オフ時にはほとんど電流を流さない絶縁ゲート型トランジスタを作製することができる。

#### 【0104】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【0105】

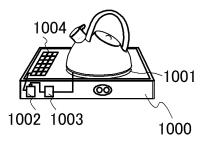

##### (実施の形態4)

本実施の形態では、上記実施の形態で説明したサイリスタとして機能する半導体装置の用途について説明する。上記実施の形態で説明した半導体装置は、例えば、コンピュータ等の画像を表示しうるディスプレイなどの電子機器のバッテリーの電力調整装置の他、電磁調理器又は固定電源の電力で駆動する乗物類（自転車等）等に設ける電力調整装置として使用することができる。

#### 【0106】

なお電力調整装置とは、所定のトリガー信号によって電流を負荷に流す装置をいう。

#### 【0107】

図11を参照して、半導体装置を有する電力調整装置を備えた応用例の一例について説明する。

#### 【0108】

図11(A)は、半導体装置を有する電力調整装置を備えた応用例として、電磁調理器1000を示している。電磁調理器1000は、コイル部1001に電流を流すことによって生じる電磁誘導を利用して調理器等を加熱するものである。また電磁調理器1000は、コイル部1001に流す電流を供給するためのバッテリー1002及び電力調整装置1003、バッテリー1002を充電するための太陽電池1004を有する。なお図11(A)では、バッテリー1002を充電するための手段として太陽電池1004を示したが他の手段で充電する構成でもよい。サイリスタとして機能する半導体装置を具備する電力調整装置1003は、酸化物半導体層を具備する絶縁ゲート型トランジスタを有することでオフ電流を低減でき、電磁調理器1000の非加熱時における低消費電力化を図ることができる。

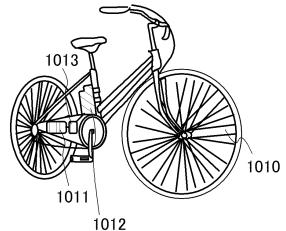

#### 【0109】

図11(B)は、半導体装置を有する電力調整装置を備えた応用例として、電動自転車1010を示している。電動自転車1010は、モーター部1011に電流を流すことによって動力を得るものである。また電動自転車1010は、モーター部1011に流す電流を供給するためのバッテリー1012及び電力調整装置1013を有する。なお図11(B)では、バッテリー1012を充電するための手段は特に図示しないが、別途発電機等を設けて充電する構成でもよい。サイリスタとして機能する半導体装置を具備する電力調整装置1013は、酸化物半導体層を具備する絶縁ゲート型トランジスタを有することでオフ電流を低減でき、電動自転車1010の非動作時における低消費電力化を図ることができる。なお、図11(B)ではペダルを図示したが、なくてもよい。

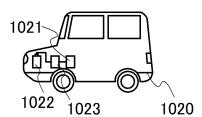

#### 【0110】

図11(C)は、半導体装置を有する電力調整装置を備えた応用例として、電気自動車1020を示している。電気自動車1020は、モーター部1021に電流を流すことによって動力を得るものである。また電気自動車1020は、モーター部1021に流す電流を供給するためのバッテリー1022及び電力調整装置1023を有する。なお図11

10

20

30

40

50

(C)では、バッテリー1022を充電するための手段は特に図示しないが、別途発電機等を設けて充電する構成でもよい。サイリスタとして機能する半導体装置を具備する電力調整装置1023は、酸化物半導体層を具備する絶縁ゲート型トランジスタを有することでオフ電流を低減でき、電気自動車1020の非動作時における低消費電力化を図ることができる。

#### 【0111】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【符号の説明】

##### 【0112】

|      |              |    |

|------|--------------|----|

| 101  | 絶縁ゲート型トランジスタ | 10 |

| 102  | 絶縁ゲート型トランジスタ |    |

| 103  | 絶縁ゲート型トランジスタ |    |

| 104  | 絶縁ゲート型トランジスタ |    |

| 105  | 絶縁ゲート型トランジスタ |    |

| 106  | 絶縁ゲート型トランジスタ |    |

| 107  | 絶縁ゲート型トランジスタ |    |

| 108  | 絶縁ゲート型トランジスタ |    |

| 109  | 絶縁ゲート型トランジスタ |    |

| 110  | 容量素子         | 20 |

| 111  | 抵抗素子         |    |

| 112  | 配線           |    |

| 113  | 配線           |    |

| 114  | 配線           |    |

| 115  | メモリ回路        |    |

| 116  | インバータ回路      |    |

| 117  | 負荷           |    |

| 200  | バッファ回路       |    |

| 201  | バッファ回路       |    |

| 210  | 絶縁ゲート型トランジスタ | 30 |

| 211  | 絶縁ゲート型トランジスタ |    |

| 212  | 絶縁ゲート型トランジスタ |    |

| 213  | 絶縁ゲート型トランジスタ |    |

| 220  | 絶縁ゲート型トランジスタ |    |

| 221  | 絶縁ゲート型トランジスタ |    |

| 222  | 絶縁ゲート型トランジスタ |    |

| 223  | 絶縁ゲート型トランジスタ |    |

| 601  | 基板           |    |

| 603  | 絶縁膜          |    |

| 605  | 電極           | 40 |

| 607  | 酸化物半導体膜      |    |

| 609  | 電極           |    |

| 611  | ゲート絶縁膜       |    |

| 613  | 電極           |    |

| 617  | 絶縁膜          |    |

| 625  | 配線           |    |

| 629  | 配線           |    |

| 631  | 配線           |    |

| 645  | 絶縁ゲート型トランジスタ |    |

| 1000 | 電磁調理器        | 50 |

|         |              |

|---------|--------------|

| 1 0 0 1 | コイル部         |

| 1 0 0 2 | バッテリー        |

| 1 0 0 3 | 電力調整装置       |

| 1 0 0 4 | 太陽電池         |

| 1 0 1 0 | 電動自転車        |

| 1 0 1 1 | モーター部        |

| 1 0 1 2 | バッテリー        |

| 1 0 1 3 | 電力調整装置       |

| 1 0 2 0 | 電気自動車        |

| 1 0 2 1 | モーター部        |

| 1 0 2 2 | バッテリー        |

| 1 0 2 3 | 電力調整装置       |

| 1 1 0 0 | サイリスタ        |

| 1 1 0 1 | n p n型トランジスタ |

| 1 1 0 2 | p n p型トランジスタ |

| 1 1 0 3 | 配線           |

| 1 1 0 4 | 配線           |

10

【図1】

【図2】

(B)

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

(A) A-A' 断面エネルギー-バンド図

(B) 電圧印加時のエネルギー-バンド図

【図9】

(A) B-B' 断面エネルギー-バンド図 (+Vg)

【図10】

(B) B-B' 断面エネルギー-バンド図 (-Vg)

【図 1 1】

(A)

【図 1 2】

(B)

(C)

---

フロントページの続き

## (51)Int.Cl.

|         |                   | F I                   |

|---------|-------------------|-----------------------|

| H 0 1 L | 27/04 (2006.01)   | H 0 1 L 29/78 6 5 3 D |

| H 0 1 L | 21/8234 (2006.01) | H 0 1 L 29/78 6 5 2 T |

| H 0 1 L | 27/088 (2006.01)  | H 0 1 L 29/78 6 5 6 A |

| H 0 1 L | 21/822 (2006.01)  | H 0 1 L 27/08 1 0 2 J |

| H 0 1 L | 29/423 (2006.01)  | H 0 1 L 27/04 F       |

| H 0 1 L | 29/49 (2006.01)   | H 0 1 L 29/58 G       |

## (56)参考文献 特開平03-206709 (JP, A)

特開2010-152347 (JP, A)

特開2008-089874 (JP, A)

特開2007-257812 (JP, A)

特開2003-332446 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

|         |               |

|---------|---------------|

| H 0 1 L | 2 9 / 7 4 9   |

| H 0 1 L | 2 1 / 8 2 2   |

| H 0 1 L | 2 1 / 8 2 3 4 |

| H 0 1 L | 2 7 / 0 4     |

| H 0 1 L | 2 7 / 0 8 8   |

| H 0 1 L | 2 9 / 1 2     |

| H 0 1 L | 2 9 / 4 2 3   |

| H 0 1 L | 2 9 / 4 9     |

| H 0 1 L | 2 9 / 7 4     |

| H 0 1 L | 2 9 / 7 8     |

| H 0 1 L | 2 9 / 7 8 6   |

| H 0 1 L | 2 7 / 0 4     |

| G 0 9 G | 3 / 3 6       |