(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-62912

(P2004-62912A)

(43) 公開日 平成16年2月26日(2004.2.26)

(51) Int.C1.<sup>7</sup>

G O 6 K 19/07

F 1

G O 6 K 19/00

N

テーマコード(参考)

5 B 0 3 5

審査請求 未請求 請求項の数 10 O L (全 11 頁)

(21) 出願番号 特願2003-279418 (P2003-279418)

(22) 出願日 平成15年7月24日 (2003.7.24)

(31) 優先権主張番号 10/202051

(32) 優先日 平成14年7月24日 (2002.7.24)

(33) 優先権主張国 米国(US)

(71) 出願人 503003854

ヒューレット・パッカード デベロップメント カンパニー エル.ピー.

アメリカ合衆国 テキサス州 77070

ヒューストン 20555 ステイト

ハイウェイ 249

(74) 代理人 100099623

弁理士 奥山 尚一

(74) 代理人 100096769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

(74) 代理人 100114591

弁理士 河村 英文

最終頁に続く

(54) 【発明の名称】 固体記憶装置

## (57) 【要約】

【課題】 大容量で高い転送速度性能を有する記憶装置を提供する。

【解決手段】 原子分解能記憶装置(ARS)と磁気ランダム・アクセス・メモリ装置(MRAM)とのいずれか1つを含むメモリ装置114と、コントローラ400と、記憶装置100を別の装置に直接に接続するために使用される一体型コネクタ104とを含んでなる固体記憶装置100を提供する。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

原子分解能記憶装置（A R S）と磁気ランダム・アクセス・メモリ装置（M R A M）とのいずれか1つを含むメモリ装置と、

コントローラと、

前記記憶装置を別の装置に直接に接続するために使用される一体型コネクタとを含んでなる固体記憶装置。

**【請求項 2】**

前記コネクタが、ユニバーサル・シリアル・バス（U S B）コネクタを含む請求項1に記載の記憶装置。 10

**【請求項 3】**

前記コントローラが、コネクタ・インターフェースと、バッファ・システムと、プロセッサと、メモリ装置インターフェースとを含む請求項1に記載の記憶装置。

**【請求項 4】**

少なくとも1つの原子分解能記憶装置と、

コントローラと、

前記記憶装置を別の装置に直接に接続するために使用される一体型ユニバーサル・シリアル・バス・コネクタとを含んでなる固体記憶装置。

**【請求項 5】**

前記ユニバーサル・シリアル・バス・コネクタが、A型のユニバーサル・シリアル・バス・コネクタを含む請求項4に記載の記憶装置。 20

**【請求項 6】**

前記ユニバーサル・シリアル・バス・コネクタが、B型のユニバーサル・シリアル・バス・コネクタを含む請求項4に記載の記憶装置。

**【請求項 7】**

前記コントローラが、コネクタ・インターフェースと、バッファ・システムと、プロセッサと、メモリ装置インターフェースとを含む請求項4に記載の記憶装置。

**【請求項 8】**

少なくとも1つの磁気ランダム・アクセス・メモリ装置と、

コントローラと、

前記記憶装置を別の装置に直接に接続するために使用される一体型ユニバーサル・シリアル・バス・コネクタとを含んでなる固体記憶装置。

**【請求項 9】**

前記コントローラが、コネクタ・インターフェースと、バッファ・システムと、プロセッサと、メモリ装置インターフェースとを含む請求項8に記載の記憶装置。

**【請求項 10】**

原子分解能記憶装置と磁気ランダム・アクセス・メモリ装置とのいずれか1つを備えるメモリ装置を含む記憶装置を提供するステップと、

該記憶装置にある一体型U S Bコネクタを使用して、データを書き込むかまたは該記憶装置からデータを読み込む別の装置に該記憶装置を直接に接続して、該データを読み書きすることができるようにするステップと

を含んでなる、データを読み書きするための方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、固体記憶装置に関する。より詳細には、本発明は、記憶装置を別の装置に直接に接続することを可能にする一体型コネクタを含む固体記憶装置に関する。

**【背景技術】**

10

20

30

40

50

**【0002】**

近年、固体記憶装置の人気が高まっている。例えば、フラッシュ・メモリが、デジタル・カメラや音楽再生装置などの携帯型電子装置へと一般に利用されるようになってきている。固体記憶装置の最近の進歩によって、入手可能ないくつかの装置は、フロッピーディスクやZIPディスクなどのより一般的な記憶装置と同じように使用することができる代替の記憶装置を作成するために使用できる十分な容量を含むようになってきている。

**【0003】**

残念ながら、そのようなほとんどの記憶装置は、記憶装置を（例えば、ホストなどの）別の装置に接続するための中間のハードウェアを必要とする。最近になって、ホスト装置に直接に接続することができるいくつかの固体記憶装置が紹介されてきたが、そのようなほとんどの装置は、記憶容量が限られていたり転送速度性能が限られていたりする。10

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

以上のことから、別の装置に直接に接続するように適合されて大きい記憶容量および／または高い性能を提供する記憶装置を有することが望ましいことが分かるであろう。

**【課題を解決するための手段】****【0005】**

本発明は、固体記憶装置に関する。1つの構成において、この記憶装置は、原子分解能記憶（atomic resolution storage：以下、「ARS」とよぶ）装置と磁気ランダム・アクセス・メモリ（以下、「MRAM」とよぶ）装置のいずれか1つを含むメモリ装置と、コントローラと、記憶装置を別の装置に直接に接続するために使用される一体型コネクタとを含む。20

**【0006】**

本発明は、以下の図面を参照してより良く理解することができる。図面内の構成要素は、必ずしも実寸とは限らず、むしろ本発明の原理を明瞭に示すために強調されている。

**【発明を実施するための最良の形態】****【0007】**

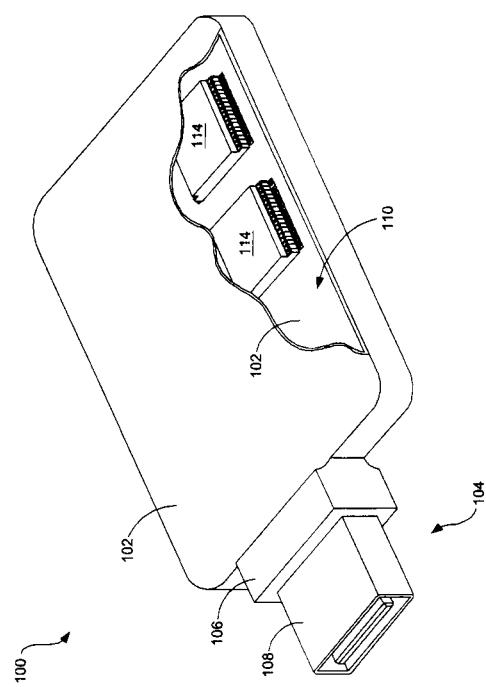

次に、いくつかの図全体を通して同じ数字が対応する部分を示す図面をより詳細に参照すると、図1～図3は、ホスト装置などの別の装置に直接に接続するよう構成された記憶装置100を示す。図1に示されるように、記憶装置100は、一体型コネクタ104を含むハウジング102を一般に含む。一般に、コネクタ104は、オーバーモールド・ブート（overmold boot）106とプラグ108とを含みうる。例えば、コネクタ104は、ユニバーサル・シリアル・バス（以下、「USB」とよぶ）シリーズの「A」型プラグ・コネクタを含む。本明細書では特定の形のコネクタを説明して図に示すが、当業者は、例えばSCSI、IDE、IEEE1394（Firewire（登録商標））、CompactFlash（登録商標）、MultimediaCard（登録商標）、またはSecureDigital（登録商標）を含む代替のタイプのコネクタが実現可能であることを理解されよう。30

**【0008】**

ハウジング102は、1つ以上の固体記憶装置114が取り付けられたプリント回路基板（printed circuit board：以下、「PCB」とよぶ）112を含む内部空間110を定義する。本明細書ではPCBを示して説明するが、当業者は、フレックス回路や厚膜などの代替の実装技術を使用できることを理解されよう。通常、メモリ装置114は、PCB112の（片面または両面などの）表面に実装され、各メモリ装置が基板上の他の装置（またはデバイス）と電気的に通信して大きい記憶容量を実現するように電気的に接続されている。メモリ装置114のそれぞれは、一般に、複数のメモリ装置をハウジング102内に入れることができるような小さいサイズである。例えば、各メモリ装置114は、約1センチメートル（cm）の幅および長さと、約1ミリメートル（mm）の厚さとを有することができる。後でより詳しく解説するように、メモリ装置114は、原子分解能記

憶（A R S）装置または磁気ランダム・アクセス・メモリ（M R A M）装置を含むことが好ましい。例えば、記憶装置100は、携帯し易いように、長さが約35cm、幅が約25cm、厚さが約4cmにそれぞれすることができる。

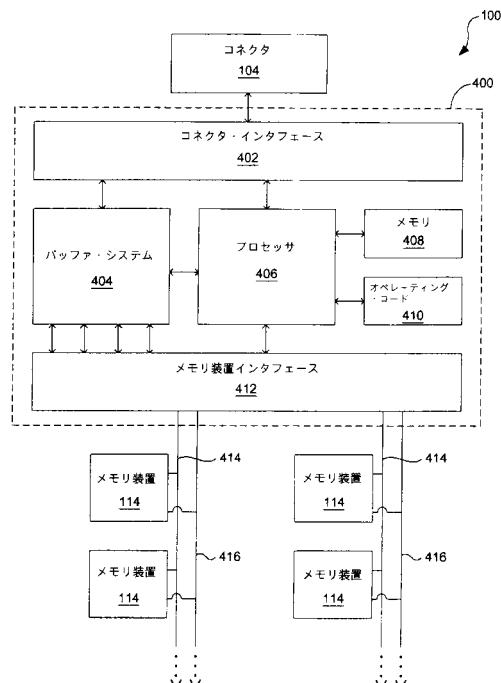

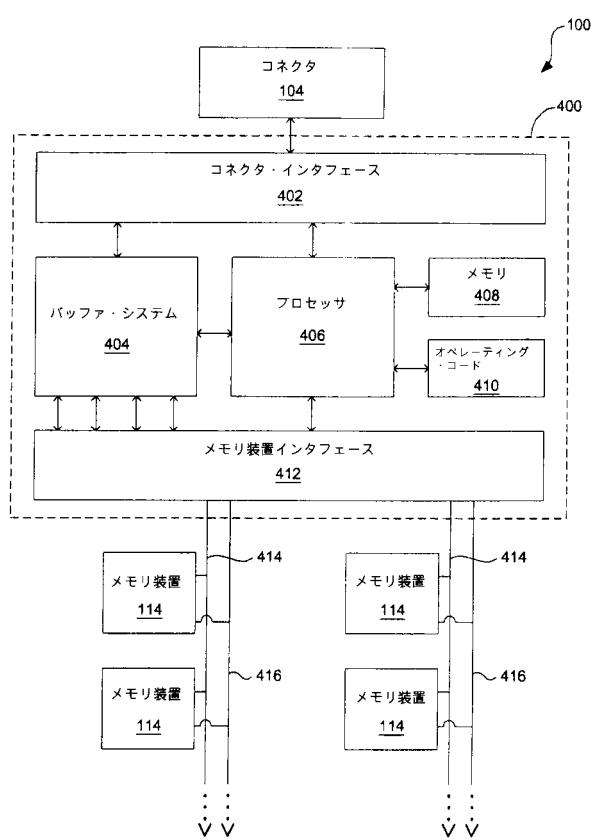

#### 【0009】

図4は、記憶装置100のブロック図を示す。この図に示されるように、メモリ装置100は、コネクタ104と、コントローラ400と、1つ以上のメモリ装置114とを一般に含む。コントローラ400は、一般に、記憶装置100の動作を制御し管理するために使用される半導体装置を含む。例えば、コントローラ400は、コネクタ・インターフェース402と、バッファ・システム404と、プロセッサ406と、メモリ408と、オペレーティング・コード410と、メモリ装置インターフェース412とを含む。コネクタ・インターフェース402は、その名前が示す通り、コネクタ104とコントローラ400との間のインターフェースを提供し、これによって、接続方式により必要とされるプロトコルに従うよう構成されている。例えば、コネクタ104がUSBコネクタの場合には、コネクタ・インターフェース402は、シリアル差分信号方式（serial differential signaling scheme）に従ってデータ・ロックを送受信するUSBインターフェースである。バッファ・システム404は、（例えば、メモリ装置114に書き込まれるデータ・ロックなどの）データを受け取って一時的に記憶することができるバッファ・メモリとバッファ・マネージャとを含む。

10

#### 【0010】

プロセッサ406は、記憶装置100の動作を制御するように構成されており、（例えば、ファームウェアなどの）オペレーティング・コード410に従って、他のコントローラ構成要素の動作を制御する。オペレーティング・コードを示したが、代わりに、適切なハードウェアによって処理を行うことができる。プロセッサ406は、コネクタ・インターフェース402から記憶コマンドを受け取るように構成されており、1つ以上のデータ・ロックを特定の記憶装置アドレスに書き込むようにメモリ装置インターフェース412を構成する。メモリ装置インターフェース412は、プロセッサ406が書き込みコマンドおよび／または読み出しコマンドを受け取ったときに、1つ以上のデータ線414と、アドレス線および制御線416とを使用して、様々なメモリ装置114と対話するように構成されている。

20

#### 【0011】

データを記憶装置100に書き込むとき、コネクタ・インターフェース402が、コネクタ104を介して書き込みコマンドを受け取り、プロセッサ406に転送する。コマンドは、書き込むデータ・ロックの番号と共に書き込むデータに関連した線形アドレス（linear address）を一般に指定する。書き込みコマンドに従って、コネクタ・インターフェース402は、（コネクタ104を介して）データ・ロックを受け取り、そのデータ・ロックと関連したインターフェース・プロトコルに必要な任意のフォーマット情報を処理して取り出す。データはバッファ・システム404内にバッファされ、コマンドはプロセッサ406に転送される。書き込みコマンドは線形アドレスを指定するので、アドレスは、プロセッサ406によって適切な記憶装置アドレスに変換される（つまり、マッピングされる）。プロセッサ406は、計算するときのリソースとしてメモリ408を使用することができる。そして、プロセッサ406は、記憶装置アドレス情報をメモリ装置インターフェース412に転送し、通常はこれとほぼ同時に、バッファ・システム404が、様々なアドレスに記憶されるデータをメモリ装置インターフェース412に転送できるようにする。記憶するデータと記憶装置アドレス情報を受け取った後に、メモリ装置インターフェース412は、記憶装置100に適したフォーマットにデータを再構成し、データが指定された記憶装置アドレスに書き込まれるようにする。

30

#### 【0012】

読み出し中に、コネクタ・インターフェース402は、コネクタ104を介して読み出しコマンドを受け取り、プロセッサ406に転送する。またその一方で、コマンドは、読み出すデータに関連した線形アドレスを一般に指定する。プロセッサ406は、線形アドレ

40

50

スを記憶装置アドレスにマップし、メモリ装置インターフェース 412 を介して、適切な記憶装置アドレスに記憶されたデータをフェッチし、それをデータ・ロックへと編成し、それをバッファ・システム 404 に渡す。バッファ・システム 404 が（例えば、1つ以上のデータ・ロックなどの）データを受け取った後に、そのデータは、適切なコネクタ・フォーマット（例えば、USB フォーマット）にフォーマットされ、そして、コネクタ・インターフェース 402 とコネクタ 104 とを介して（例えば、ホストなどの）要求装置に転送される。

#### 【0013】

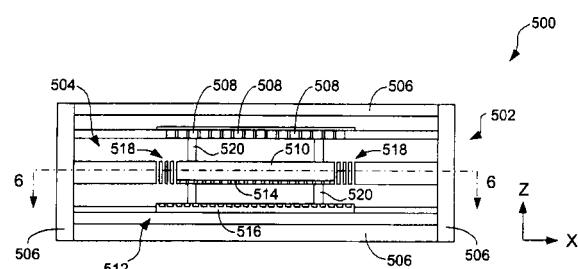

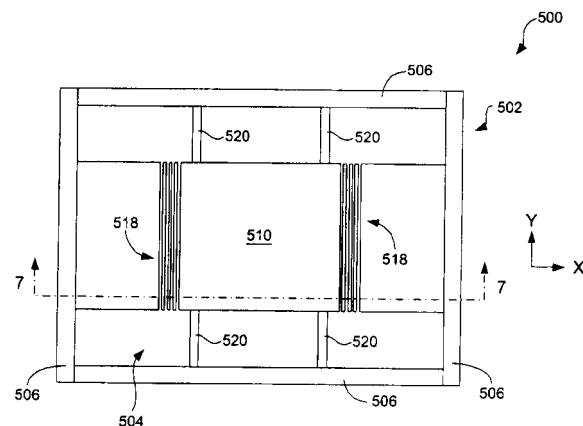

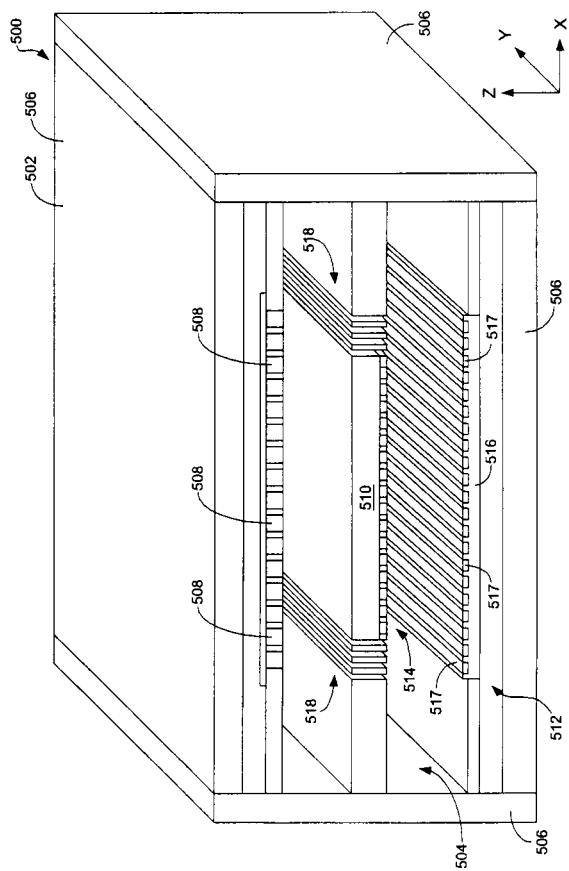

メモリ装置 114 は、大量のデータを記憶することができる実質的に任意の装置を含みうるが、メモリ装置は、1つの実施形態において、その低コストと大容量の ARS 装置とを含む。図 5～図 7 は、以上説明したメモリ装置 114 の構造に適した1つの ARS 装置 500 の内部構造を示す。適切な ARS 装置の例が、引用することにより本明細書の一部をなすものとする米国特許第 5,557,596 号公報に開示されて詳細に説明されている。図 5～図 7 に示したように、メモリ装置 500 は、内部空間 504 を構成する外側ケーシング 502 を一般に含む。例えば、ケーシング 502 は、内部空間 504 を定義する複数の壁 506 を含みうる。一般に、ケーシング 502 の壁 506 は、内部空間 504 内を真空に保持できるよう互いに封止される。例えば、ケーシング 502 は、少なくとも約  $10^{-3}$  torr の真空に内部空間 504 内を保持する。ケーシング 502 の特定の構成を示したが、このケーシングは、当業者には容易に明らかであろう多くの異なる形態をとらうことを理解されたい。

#### 【0014】

内部空間 504 内には、記憶媒体 510 に対面する複数の電子エミッタ 508 がある。図 4 に関して説明したように、記憶媒体 510 は、（図 5～図 7 に示されていない）複数の記憶域を含む。好ましい実施形態において、記憶媒体 510 の各記憶域は、1つ以上のデータ・ビットを記憶する役割をもつ。

#### 【0015】

電子エミッタ 508 は、電子エミッタに所定の電位差が印加されたときに、記憶媒体 510 の記憶域に向けて電子ビーム流を放射するよう構成される。必要なエミッタ 508 と記憶媒体 510 との間の距離と、エミッタのタイプと、スポット・サイズ（つまり、ビット・サイズ）とにより、電子ビームの集束に電子光学が有効なことがある。放射された電子を加速または減速、および／または放射された電子を集束するために、記憶媒体 510 にも電圧が印加される。

#### 【0016】

電子エミッタ 508 のそれぞれは、多くの異なる記憶域を利用して記憶域 510 に対してデータを読み書きすることができる。電子エミッタ 508 のそれぞれとそれに関連付けられた記憶域との間のアライメントを容易にするために、図 2 に示された X 方向と Y 方向とに、電子エミッタと記憶媒体 510 とをそれぞれ互いに相対的に移動させることができる。この相対的な移動を行うために、メモリ装置 500 は、電子エミッタ 508 に対して記憶媒体 510 を走査するマイクロムーバ 512 を含みうる。図 5 および図 7 に示されるように、マイクロムーバ 512 は、記憶媒体 510 に接続された回転子 514 と、回転子と対向する固定子 516 と、記憶媒体の横に位置決めされた1つ以上のばね 518 とを含みうる。当該技術分野においてよく知られているように、回転子 514 を望み通りに移動させる場所を作るために、固定子 516 の電極 517 に適切な電位を印加することによって、回転子 514 の移動とそれによる記憶媒体 510 の移動とを行うことができる。

#### 【0017】

マイクロムーバ 512 がこの仕方で移動されると、各エミッタ 508 が特定の記憶域の上に位置決めされるように、マイクロムーバは、X-Y 平面内の様々な位置に記憶媒体 510 を走査する。使用するマイクロムーバ 512 は、電子エミッタ 508 の下に記憶域を高精度で位置決めするのに十分な範囲と解像度とを有することが好ましい。例えば、マイクロムーバ 512 は、半導体微細加工処理によって作成することができる。電子エミッタ

10

20

30

40

50

508と記憶媒体510との間の相対的な移動が記憶媒体の移動によって行われるよう説明したが、代わりに、そのような相対的な移動は、電子エミッタを移動するか、または電子エミッタと記憶媒体との両方を移動することによって得られることが理解されるであろう。さらに、本明細書に特定のマイクロムーバ512を示して説明したが、当業者は、代替の移動手段を使用してそのような相対的な移動が得られることが理解されるであろう。

#### 【0018】

放射ビームと記憶域のアライメントとは、偏向器（図示せず）によってさらに容易することができる。例えば、エミッタ508の隣に位置決めされた静電偏向器および／または電磁偏向を使用して、静電気的または電磁気的に電子ビームを偏向することによって、記憶媒体510の表面に電子ビームをラスタ化することができる。電子ビームを偏向する様々な手法は、走査型電子顕微鏡（SEM）に関する文献に見ることができる。10

#### 【0019】

電子エミッタ508は、生成される電子ビームによって記憶媒体の記憶域に情報を読み書きする役割をもつ。したがって、電子エミッタ508は、記憶媒体510に所望のビット密度を達成できるほど十分に細くて媒体に対する読み書きに必要な様々な出力密度を提供する電子ビームを生成することが好ましい。

#### 【0020】

図5および図6に示したように、メモリ装置500は、内部空間504の適切な場所に記憶媒体510を支持する1つ以上の支持体520をさらに含みうる。支持体が設けられている場合には、記憶媒体510がX方向および／またはY方向に移動するときにたわむ薄肉の微細加工されたビームを支持体520は一般に含む。図5および図6に示されるように、ケーシング502の壁506に支持体520をそれぞれ接続することができる。20

#### 【0021】

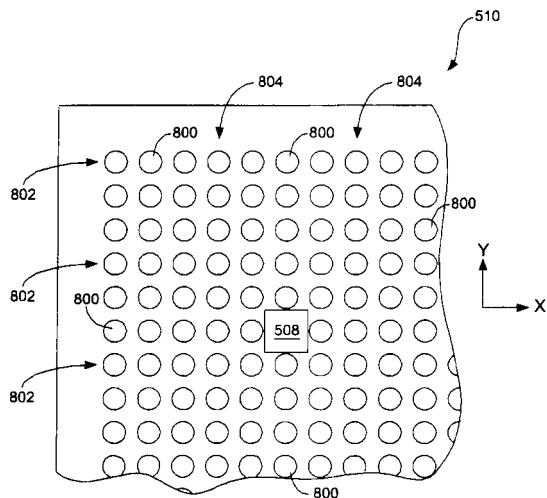

好ましい実施形態において、複数のエミッタを含む二次元配列の内部に電子エミッタ508が含まれる。例えば、X方向とY方向との両方に約5～100マイクロメートルのエミッタ・ピッチで $100 \times 100$ 個の配列の電子エミッタ508を設けることができる。以上に説明したように、一般に、各エミッタ508は、記憶媒体510の複数の記憶域にアクセスするために使用される。図8は、この関係の概略的な表現を示す。詳細には、この図は、記憶媒体510の複数の記憶域800の上に位置決めされた単一の電子エミッタ508を示す。図8に示されるように、記憶域800は、電子エミッタ508のような2次元配列内に含まれる。詳細には、記憶域800は、記憶媒体510の表面上の独立した行802および列804に配列される。好ましい実施形態において、各エミッタ508は、所定数の行802の全体の長さのうちの一部分だけを担当する。したがって、各エミッタ508は、通常、特定の行802および列804の記憶域800のマトリクスにアクセスすることができる。単一の電子エミッタ508によってアクセスされるそれぞれの行802は、単一の外部回路に接続されることが好ましい。30

#### 【0022】

記憶域800をアドレス指定するとき、マイクロムーバ512が起動され、記憶媒体510（および／または、電子エミッタ508）が移動されて記憶域が特定の電子エミッタに位置合わせされる。一般に、各エミッタ508は、数万から数億の記憶域800にこの仕方でアクセスすることができる。記憶媒体510は、任意の2つの記憶域800間に約1～100ナノメートルの周期を有することができ、マイクロムーバ512の範囲は約5～100マイクロメートルでありうる。当業者に理解されるように、各電子エミッタ508は、同時にアドレス指定されるか、または多重方式によりアドレス指定されてもよい。並列のアクセス方式を使用して、メモリ装置500のデータ転送速度を大幅に高めることができる。

#### 【0023】

メモリ装置500の書き込みは、電子エミッタ508によって生成される電子ビームの出力密度を一時的に高めて、記憶媒体510の記憶域800の表面状態を変更することによ40

って行われる。例えば、変更された状態が「1」ビットを表すことができ、変更されていない状態が「0」ビットを表すことができる。さらに、必要に応じて、記憶域を様々な程度に変更して、複数のビットを表すことができる。好ましい実施形態において、記憶媒体510は、電子ビームによって構造状態を結晶から非晶質に変化させることができる材料から成る。ある材料の例では、テルル化ゲルマニウム(GeTe)およびGeTeを主成分とする三元合金(ternary alloys)である。非晶質状態から結晶状態に変化させるときは、ビームパワー密度を高めてから徐々に下げればよい。この温度の上昇および下降により、非晶質領域が加熱されて徐々に冷却され、その結果、領域が結晶状態にアニールする時間ができる。結晶状態から非晶質状態に変化させるときは、ビームパワー密度を高レベルに増加してから急激に下げる。本明細書では、記憶媒体510の一時的な変更について説明するが、追記型(write-once-read-many:以下、「WORM」とよぶ)機能が必要な場合には永久的な変更が可能であることが理解されるであろう。

10

## 【0024】

読み出しは、記憶域800に対する電子ビームの作用または電子ビームに対する記憶域の作用を観察することによって行われる。読み出し中に、電子ビームの出力密度は、さらに書き込みが行われないよう十分に低く保持される。第1の読み出し方法では、読み出しは、比較的に低い(すなわち、書き込みに必要な電子ビームより低い)出力密度の電子ビームを記憶媒体510に印加したときの二次電子および/または後方拡散電子を収集することによって行われる。非晶質状態が、結晶質状態とは異なる二次電子放出効率(second electron emission coefficient:以下、「SEEC」とよぶ)と後方拡散電子効率(backsattered electron coefficient:以下、「BEC」とよぶ)とを有するため、読み出し電子ビームを照射したときに、記憶域800から異なる数の二次電子および後方拡散電子が放射される。二次電子および後方拡散電子の数を測定することによって、記憶域506の状態を決定することができる。読み書きのための装置の例は、米国特許第5,557,596号公報に記載されている。

20

## 【0025】

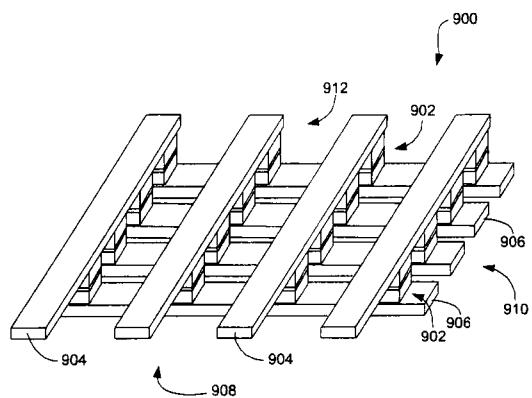

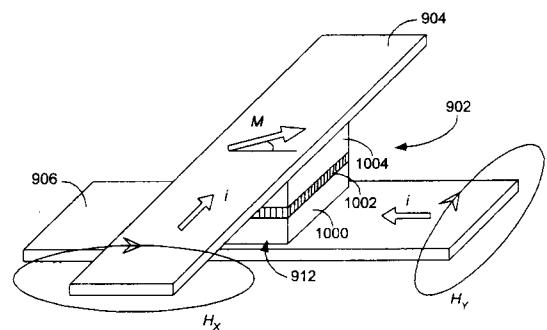

代替の好ましい構成では、メモリ装置514はMRAM装置を含む。一般に、MRAM装置にはARS装置などの記憶容量はないが、MRAM装置の使用は、MRAM装置がデータを高速で読み書きすることができるという転送速度性能の点で有利である。図9および図10は、メモリ装置514の構造に適したMRAM装置900の内部構造を示す。図9に示されるように、MRAM装置900は、磁区としてはたらく複数のセル902と、複数の導体バー904および906とを含む固体装置である。一般に、バー904および906は、第1の平面のバーが第2の平面のバーと実質的に垂直に位置させられた状態であり、平行な第1の平面908と第2の平面910とに配列される。この垂直の構成により、バー904および906は、交点912を形成する。図9に示したように、通常、バー904および906によって形成された各交点912において、2つの平面908および910の中間に1つのセル902が配置される。したがって、図10の詳細図に示したように、各セル902は、2つのバーの交点912において第1のバー904と第2のバー906との間に挟まれている。図10に示したように、各セル902は、通常、ピン留め磁気層1000(つまり、所定の方向に永久的に磁化された層)と、比較的に薄い誘電体層1002と、自由磁気センス層1004(つまり、磁化方向を選択的に変化させることができる層)とを含む。例えば、バー904および906とそれに関連したセル902とを1つ以上の基板上に形成して、一体型装置を作成することができる。

30

## 【0026】

使用する際に、導体バー904および906に電流*i*を流して磁界H<sub>x</sub>とH<sub>y</sub>を作成することにより書き込みが達成される。これらの磁界によって、センス層1004の磁化方向を選択的にピン留め磁気層1000の磁化方向と一致させるかまたはその逆にするのに十分な合成ベクトル追加磁力Mが交点912に作り出される。そして、センス層1004と誘電体層1002とピン留め層の磁化方向に依存するピン留め層1000とを通る2つの導体バー904および906のトンネル効果磁気抵抗接合の抵抗の差を測定することによっ

40

50

て、センス層の磁気の書き込み状態の検出を達成することができる。

【0027】

以上の説明および図面において、例示のために本発明の特定の実施形態を詳細に開示してきたが、当業者は、特許請求の範囲において説明する本発明の範囲を逸脱することなくその変形および修正を行うことができることが理解されるであろう。

【図面の簡単な説明】

【0028】

【図1】一体型コネクタを有する記憶装置例の斜視図である。

【図2】図1に示した記憶装置の平面図である。

【図3】図1および図2に示した記憶装置の側面図である。 10

【図4】図1～図3に示した記憶装置のブロック図である。

【図5】図1～図4に示した記憶装置において使用することができる第1の例のメモリ装置の概略側面図である。

【図6】線6-6に沿って切断した図5のメモリ装置の概略断面図である。

【図7】線7-7に沿って切断した図6および図7のメモリ装置の概略断面斜視図である。

。

【図8】図5～図7に示したメモリ装置の記憶媒体の部分概略図である。

【図9】図1～図4に示した記憶装置に使用することができる第2のメモリ装置の内部構造例を示す概略図である。

【図10】図9に示したメモリ装置の詳細図である。 20

【符号の説明】

【0029】

100 固体記憶装置

104 一体型コネクタ

114 メモリ装置

400 コントローラ

402 コネクタ・インターフェース

404 バッファ・システム

406 プロセッサ

412 メモリ装置インターフェース

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 アンドリュー・エム・スペンサー

アメリカ合衆国アイダホ州83616, イーグル, イースト・ストーニーブルック・コート 17

32

(72)発明者 トマス・シー・アンソニー

アメリカ合衆国カリフォルニア州94087, サニーヴェイル, ピメント・アヴェニュー 116

1

(72)発明者 コリン・エイ・ストップス

アメリカ合衆国アイダホ州83616, ボイジー, ロングホーン 457

(72)発明者 サラ・エム・プランデンバーガー

アメリカ合衆国アイダホ州83704, ボイジー, ノース・ハンプトン 2577

(72)発明者 スティーヴン・シー・ジョンソン

アメリカ合衆国アイダホ州83616, イーグル, ノース・コンスタンス・プレイス 2540

Fターム(参考) 5B035 AA01 AA02 BB09 CA11 CA29